國立臺灣大學電機資訊學院電信工程學研究所

碩士論文

Graduate Institute of Communication Engineering

College of Electrical Engineering and Computer Science

National Taiwan University

Master's Thesis

應用於量子計算之低溫微波電路及量測系統

Cryogenic Microwave Electronics and Measurement

Systems for Quantum Computing Applications

陳士允

Shih-Yun Chen

指導教授：陳士元 博士

Advisor: Shih-Yuan Chen, Ph.D.

中華民國 113 年 7 月

July, 2024

# 國立臺灣大學碩士學位論文

## 口試委員會審定書

MASTER'S THESIS ACCEPTANCE CERTIFICATE

NATIONAL TAIWAN UNIVERSITY

應用於量子計算之低溫微波電路及量測系統

Cryogenic Microwave Electronics and Measurement

Systems for Quantum Computing Applications

本論文係 陳士允 (姓名) R10942016 (學號) 在國立臺灣大學電信工程學研究所完成之碩士學位論文，於民國 113 年 7 月 18 日承下列考試委員審查通過及口試及格，特此證明。

The undersigned, appointed by the Graduate Institute of Communication Engineering on 18 (date) 7 (month) 2024 (year) have examined a Master's Thesis entitled above presented by Chen, Shih-Yun (name) R10942016 (student ID) candidate and hereby certify that it is worthy of acceptance.

口試委員 Oral examination committee:

eSigned by:

陳士允

07/16/2024 @ 15:54 UTC

eSigned by:

林坤祐

07/17/2024 @ 04:00 UTC

eSigned by:

李峻賓

07/18/2024 @ 04:36 UTC

(指導教授 Advisor)

eSigned by:

李峻賓

07/18/2024 @ 04:06 UTC

所長 Director: 魏玄宇

# 致謝

以這本論文，作為在臺大這幾年懵懂學習、研究的紀錄，真摯感謝這一路上所有關心過、幫助過、陪伴過我的人。

感謝我的指導教授 陳士元博士。感謝教授在研究課題上讓我自由探索，並適時提出許多精闢的建議。也感謝教授對我莫大的包容，儘管常常在研究上過於發散，在報告時不夠嚴謹，在時辰上流於匆忙，但教授總是以正向鼓勵、關心，讓我在這無盡挫折的學海中，仍抱有一絲熱情。

感謝口試委員 李峻賈教授、林坤佑教授與 梁啟德教授。感謝教授們在龐雜的內容中提出諸多值得改進的要點與建議，讓研究的內容更立體透徹，也更完整了整本論文。

感謝 王暉教授與大學專題時幫助過我的學長姊。感謝教授引領我進入研究的殿堂，在這段時期打下的基礎，深深幫助我得以持續發展與探索。感謝子豪、煒智、毓閔、牧恆、梓洋、羚毓、瑋軒等等學長姊，感謝他們在研究上的耐心解惑，也感謝他們對我的各種幫助。

感謝天文所的 章朝盛博士與詔敬。感謝他們在研究期間的無私幫助，讓這本論文的許多量測與討論得以完成。

感謝實驗室的大家。感謝已經畢業的士銘、昶劭、廷揚、炯佑、昀廷，是這些神人讓研究學習顯得引人入勝，讓我讚嘆也學習他們的高效與積極；感謝照顧我的聖偉、瑞福、欣融，時常關心我這孤僻性格，在工作之餘關懷我的身心健康，為我在台北的生活添增不少風采與回憶。感謝冠勛和 Saurav 一起窩居環安衛的日子，還有與其他學弟妹這一兩年來的珍貴快樂時光。

感謝慕召、旻叡、承學、峻維，在這麼艱困複雜龐大的跨領域研究，感謝有這

些夥伴的扶持幫忙，不僅僅是研究上的討論、實驗量測，研究生活中的歡樂，也讓這竭蹶摸索的過程不是孤身試險，而是充滿對未來的憧憬與展望。

感謝最愛我的爸媽。感謝他們永遠對我的支持與關心，儘管我時常不會表達，也可能過於專注自己的生活與研究，但他們給我莫大的空間與自由，讓我可以無憂的探索與嘗試。將這本論文獻給我的爸媽，是他們的努力，成就我有環境與能力持續地研究學習，並努力成為更好的人。

感謝這一路上點點滴滴幫助過我的人，在臺大相遇過、歡笑過、一起追尋過理想的人。謹以此謝誌珍重感念大家。

## 中文摘要

量子計算被視為是顛覆人類生活與科技的重要技術之一。除了核心的量子元件，其用於控制和讀取量子位元之傳統半導體積體電路也是量子計算系統發展中不可或缺的基石。本論文中，我們將探究射頻/微波技術在數個與量子計算相關的應用。

本論文的第一部分聚焦於設計並實現一應用於固態自旋量子位元讀取系統中之低溫互補式金屬氧化物半導體低雜訊放大器。此次設計提出之創新電路架構，有效緩解在傳統雜訊消除技術中各參數間之拮抗，實現了在增益、雜訊指數、頻寬和功耗方面的綜合性高性能指標。

論文的第二部分則著墨於低溫樣品測量系統之建立，開發、設計與測試樣品量測載板套件，並討論了多種低溫微波量測相關之應用與其所需之考量。為了在低溫環境中進行微波量測與校正，我們規劃並開發了與樣品載板套件相容之校正系統。作為校正系統中的重要元件之一，我們透過提出的系統化設計程序，並應用 LC 梯形低通濾波器理論，實現了一顆低溫寬頻單極四擲 (SP4T) 切換器。在將此固態切換器與校正量測載板整合後，我們驗證了此校正與量測系統之效能，並顯示其可有效提升在極低溫量測設備中之校正準確度，能為未來相關之量子元件提供更可靠的微波測量環境，加速量子計算領域之發展。

**關鍵字：** 低溫互補式金屬氧化物半導體低雜訊放大器、低溫射頻切換器、低溫微波量測系統、低溫  $S$  參數校正技術。

# ABSTRACT

Quantum computing has recently become one of the most captivating keywords in the field of science and technology. In addition to the core quantum devices, control and readout circuitries developed based on conventional solid-state and electronic technologies are also indispensable cornerstones in system integration and scaling up. In this thesis, we explored and investigated the application of RF/microwave technologies in several quantum computing-related areas.

The first part of this thesis focuses on a cryo-CMOS low-noise amplifier designed specifically for use in readout circuitries for solid-state spin qubit systems. A novel topology is proposed to alleviate the trade-offs in the noise-canceling technique, achieving a superior figure of merit in terms of gain, noise figure, bandwidth, and power consumption.

In the establishment of a cryogenic measurement system based on a dilution fridge, a prototype of sample holder kits is presented. Various considerations regarding several different applications are discussed. For performing calibration in a cryogenic environment, we designed a calibration system integrated with the sample holder kits. A cryogenic broadband single-pole-four-throw (SP4T) switch is developed with a proposed systematic design procedure utilizing LC-ladder low-pass filter theory. The implemented calibration system, incorporating the solid-state switch, achieves enhanced calibration accuracy within cryogenic microwave measurements, paving the way for advanced research in quantum-computing-relevant microwave devices.

**Keywords** – Cryo-CMOS low noise amplifiers (LNAs), cryogenic RF switches, cryogenic microwave measurement, cryogenic *S*-parameter calibration.

# CONTENTS

|                                                                                         |          |

|-----------------------------------------------------------------------------------------|----------|

| 口試委員會審定書 .....                                                                          | ii       |

| 致謝 .....                                                                                | iii      |

| 中文摘要 .....                                                                              | v        |

| ABSTRACT .....                                                                          | vi       |

| CONTENTS .....                                                                          | vii      |

| LIST OF FIGURES .....                                                                   | x        |

| LIST OF TABLES .....                                                                    | xvii     |

| <b>Chapter 1 Introduction .....</b>                                                     | <b>1</b> |

| <b>Chapter 2 A Cryo-CMOS LNA for Spin Qubit Reflectometry Readout Applications.....</b> | <b>6</b> |

| 2.1    Introduction .....                                                               | 6        |

| 2.1.1    Literature Review of CMOS Noise Canceling LNAs in VHF and UHF Bands .....      | 6        |

| 2.1.2    Design Considerations for Cryogenic Operation .....                            | 10       |

| 2.1.3    Literature Review of Cryogenic LNAs .....                                      | 14       |

| 2.2    Circuit Design.....                                                              | 17       |

| 2.2.1    Single Inverter Design.....                                                    | 21       |

| 2.2.2    Inverter Pair and Mutual Noise-Canceling.....                                  | 28       |

| 2.2.3    Input Stage Design .....                                                       | 35       |

| 2.2.4    Combining Stage .....                                                          | 37       |

| 2.2.5    Output Driver.....                                                             | 38       |

| 2.2.6    On-Chip Bypass Networks and Circuit Stability.....                             | 41       |

| 2.3    Experimental Results.....                                                        | 43       |

|                  |                                                                                          |           |

|------------------|------------------------------------------------------------------------------------------|-----------|

| 2.4              | Summary.....                                                                             | 49        |

| <b>Chapter 3</b> | <b>Design of a Broadband SP4T Switch for Cryogenic Measurement and Calibration .....</b> | <b>51</b> |

| 3.1              | Introduction .....                                                                       | 51        |

| 3.1.1            | Literature Review of Broadband RF Switches .....                                         | 51        |

| 3.1.2            | Literature Review of Cryogenic RF Switches .....                                         | 54        |

| 3.2              | Circuit Design.....                                                                      | 55        |

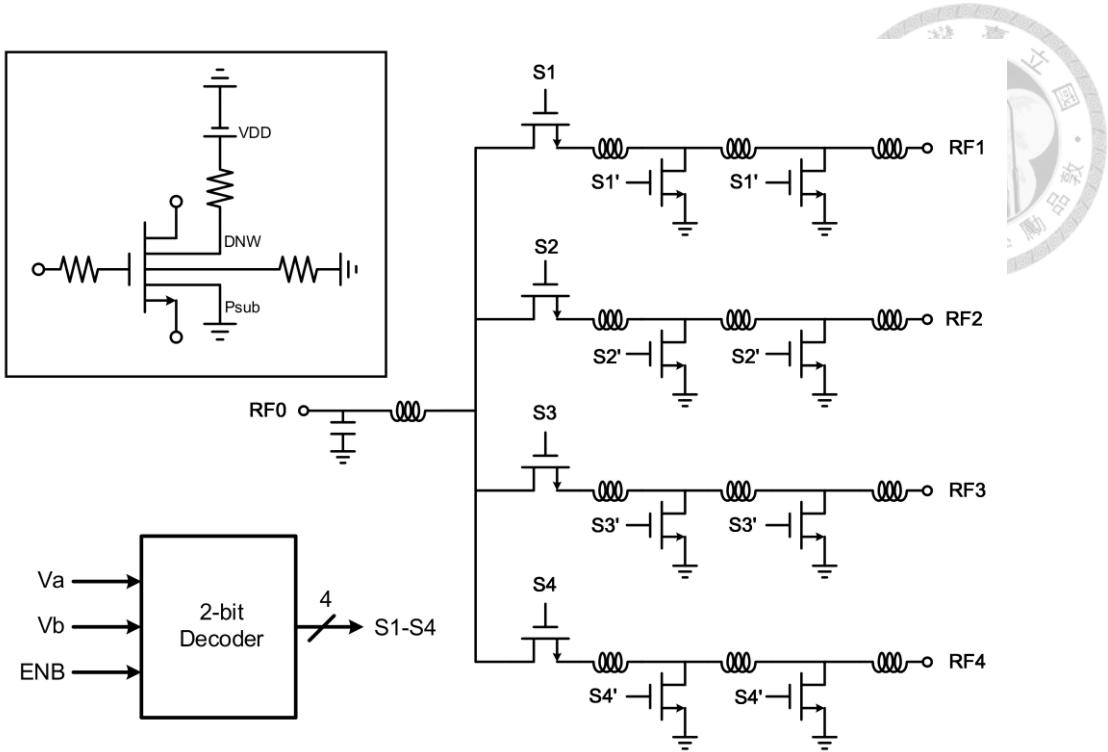

| 3.2.1            | Transistor Configuration .....                                                           | 55        |

| 3.2.2            | Circuit Schematics.....                                                                  | 57        |

| 3.2.3            | Design Procedure.....                                                                    | 57        |

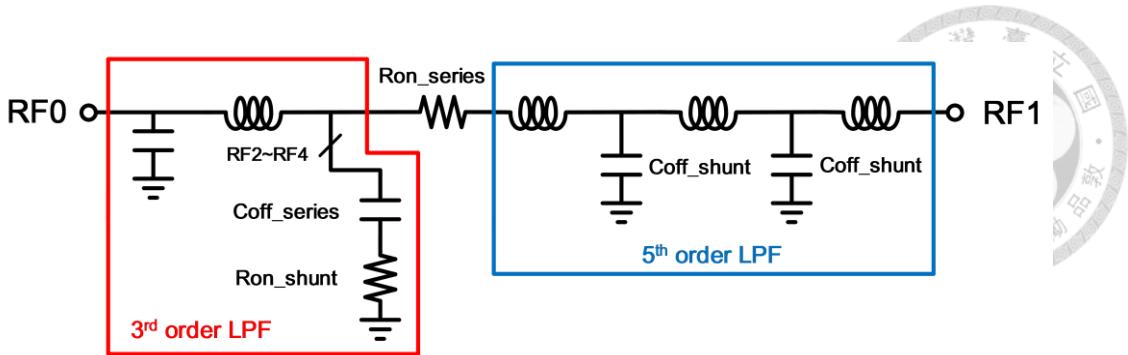

| 3.2.3.1          | RHS Output Series-First LC LPF .....                                                     | 58        |

| 3.2.3.2          | Series Transistors.....                                                                  | 62        |

| 3.2.3.3          | LHS Input Shunt-First LC LPF .....                                                       | 64        |

| 3.3              | Experimental Results.....                                                                | 65        |

| 3.3.1            | Room Temperature Measurement Results .....                                               | 66        |

| 3.3.2            | 4 K Temperature Measurement Results .....                                                | 68        |

| 3.4              | Summary.....                                                                             | 70        |

| <b>Chapter 4</b> | <b>Sample Holder Design and RF Characterization within Dilution Fridge.....</b>          | <b>73</b> |

| 4.1              | Introduction .....                                                                       | 73        |

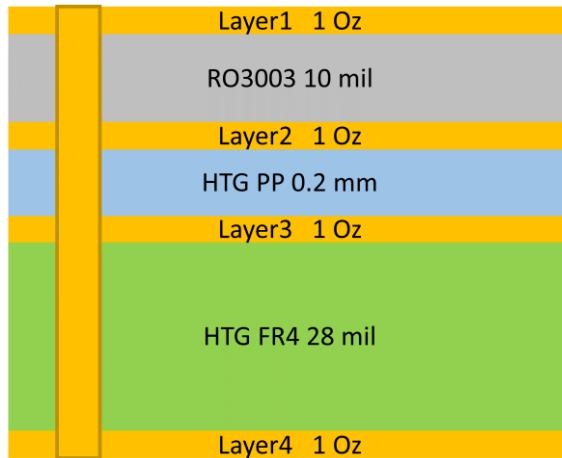

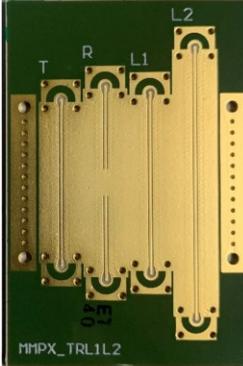

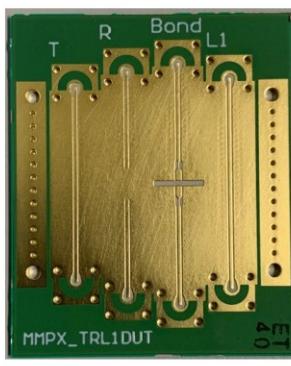

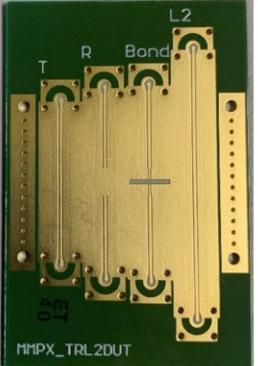

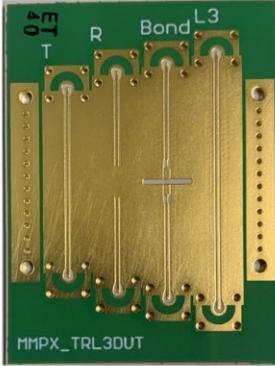

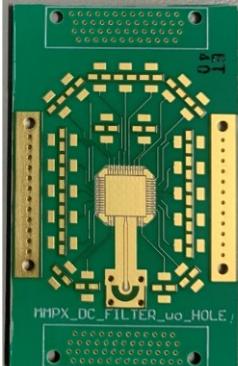

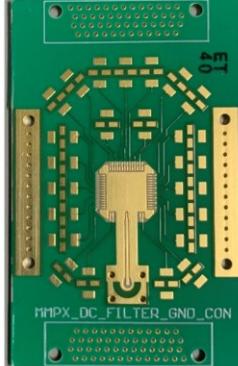

| 4.2              | Design of First-Phase Testing Boards .....                                               | 75        |

| 4.2.1            | Material Selection.....                                                                  | 75        |

| 4.2.2            | Considerations of Testing Scenarios .....                                                | 78        |

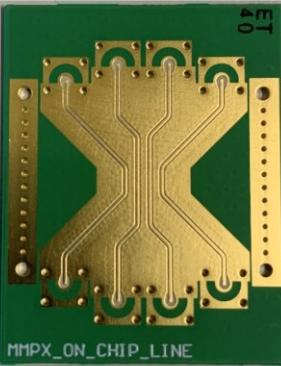

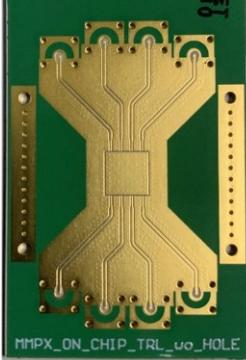

| 4.2.3            | RF Routing Design .....                                                                  | 84        |

| 4.2.4            | Wire Bonding Issues.....                                                                 | 90        |

|                  |                                                        |            |

|------------------|--------------------------------------------------------|------------|

| 4.3              | RF Characterization within Sample Puck.....            | 94         |

| 4.3.1            | Raw Data Measurement.....                              | 94         |

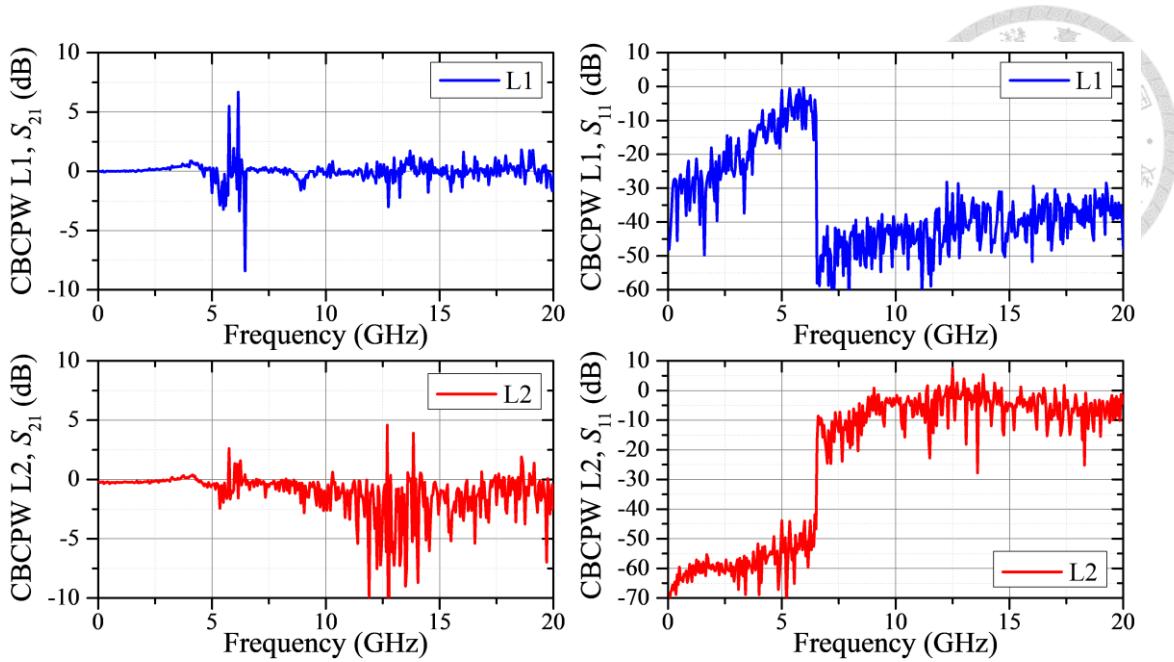

| 4.3.2            | TRL Calibration at Room Temperature .....              | 101        |

| 4.4              | RF Characterization within Dilution Fridge .....       | 108        |

| 4.5              | Summary.....                                           | 120        |

| <b>Chapter 5</b> | <b>S-parameter Calibration in mK System.....</b>       | <b>122</b> |

| 5.1              | Introduction .....                                     | 122        |

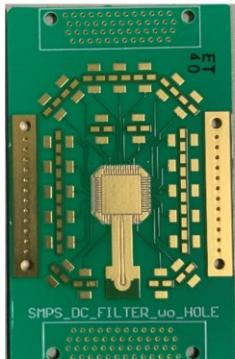

| 5.2              | Design of Second-Phase Testing Boards.....             | 125        |

| 5.2.1            | Multiple Board Structure .....                         | 125        |

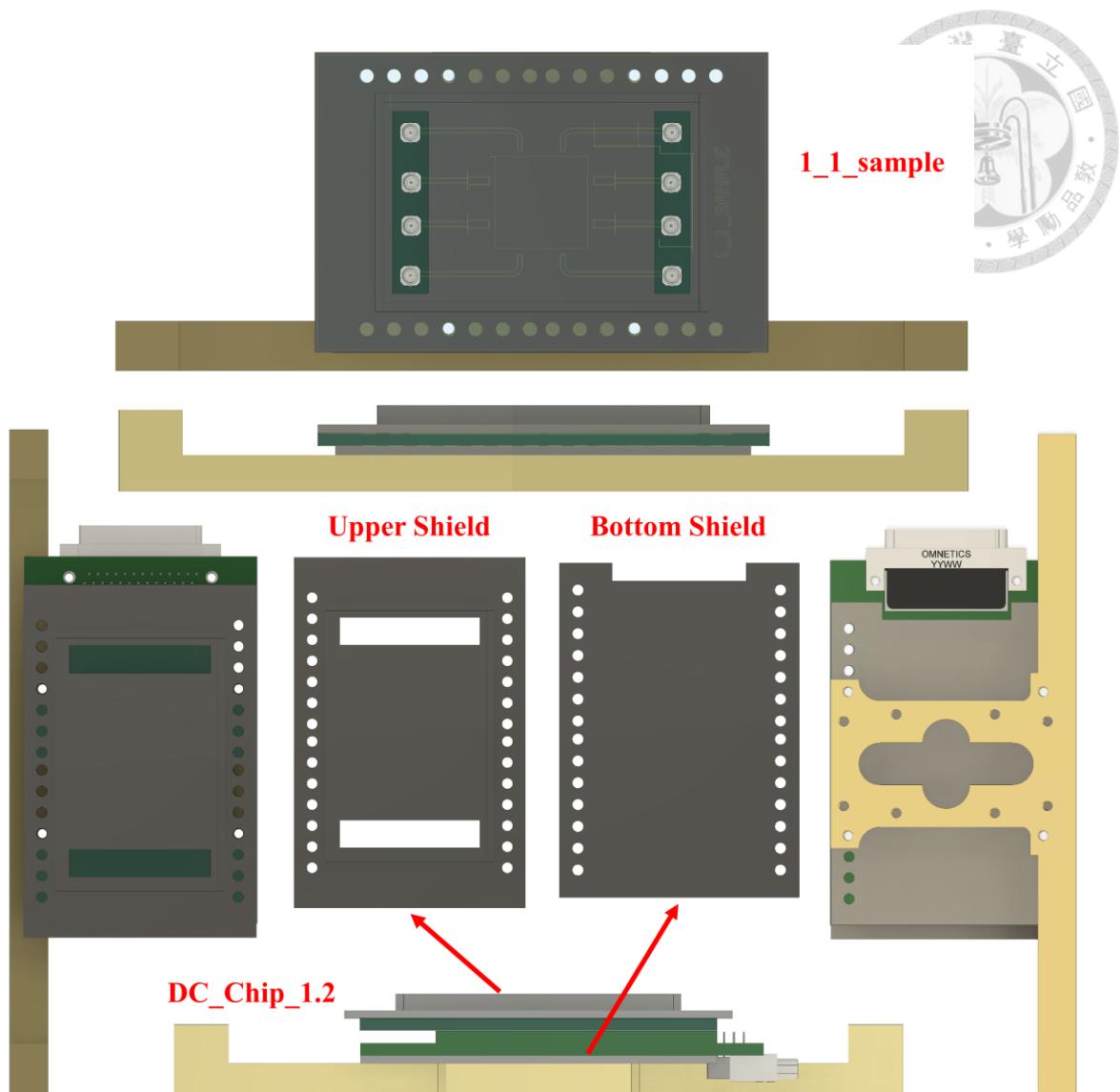

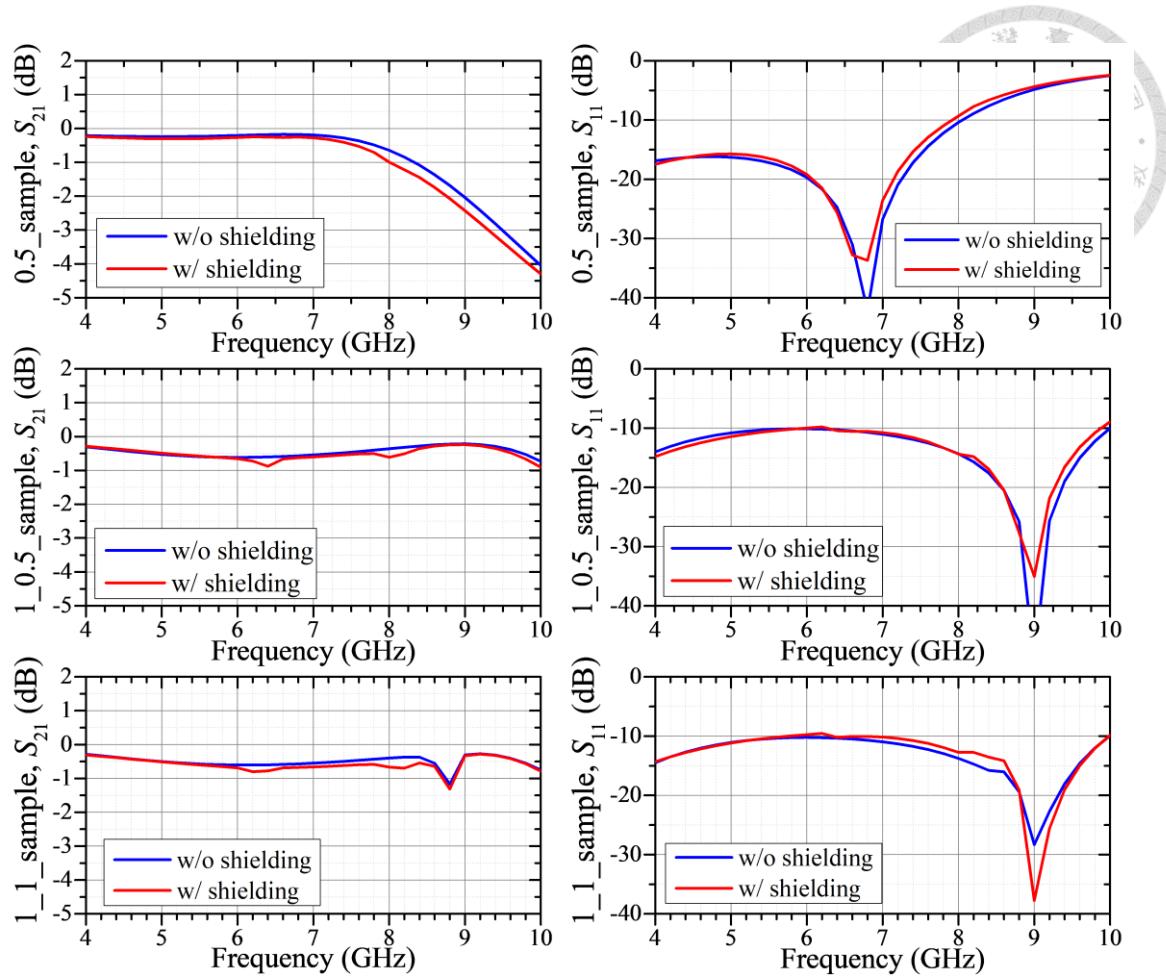

| 5.2.2            | Sample Holder Design for Superconducting Devices ..... | 128        |

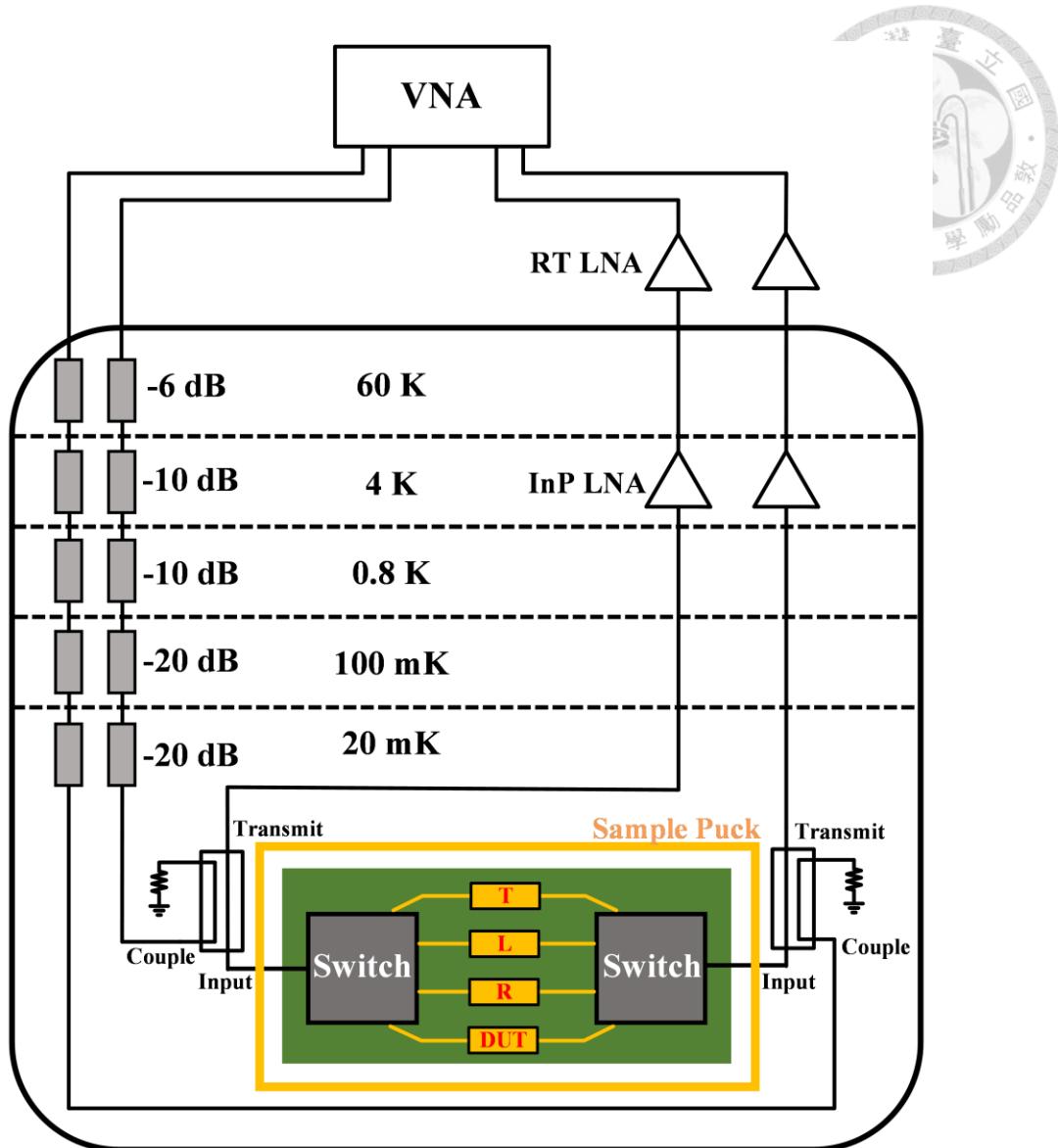

| 5.2.3            | Calibration Scheme Proposal.....                       | 136        |

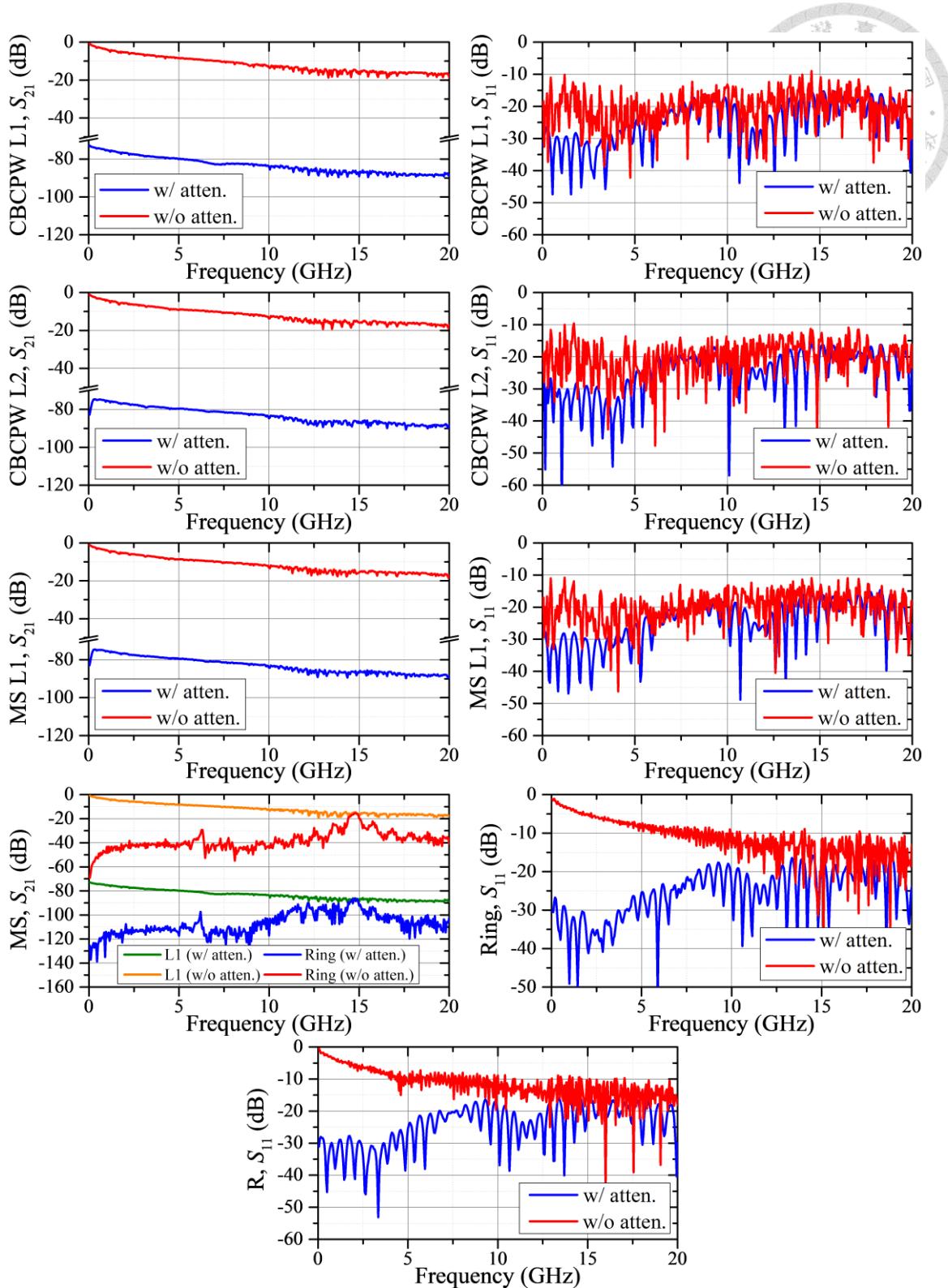

| 5.3              | Room Temperature Validation Results .....              | 141        |

| 5.4              | Summary.....                                           | 151        |

| <b>Chapter 6</b> | <b>Conclusion .....</b>                                | <b>153</b> |

| 6.1              | Summary.....                                           | 153        |

| 6.2              | Future Work.....                                       | 154        |

| References ..... |                                                        | 156        |

# LIST OF FIGURES

|                                                                                                                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1: Schematic diagram of noise-canceling technique implemented with a shunt-feedback common-source amplifier stage. ....                                                                                                | 17 |

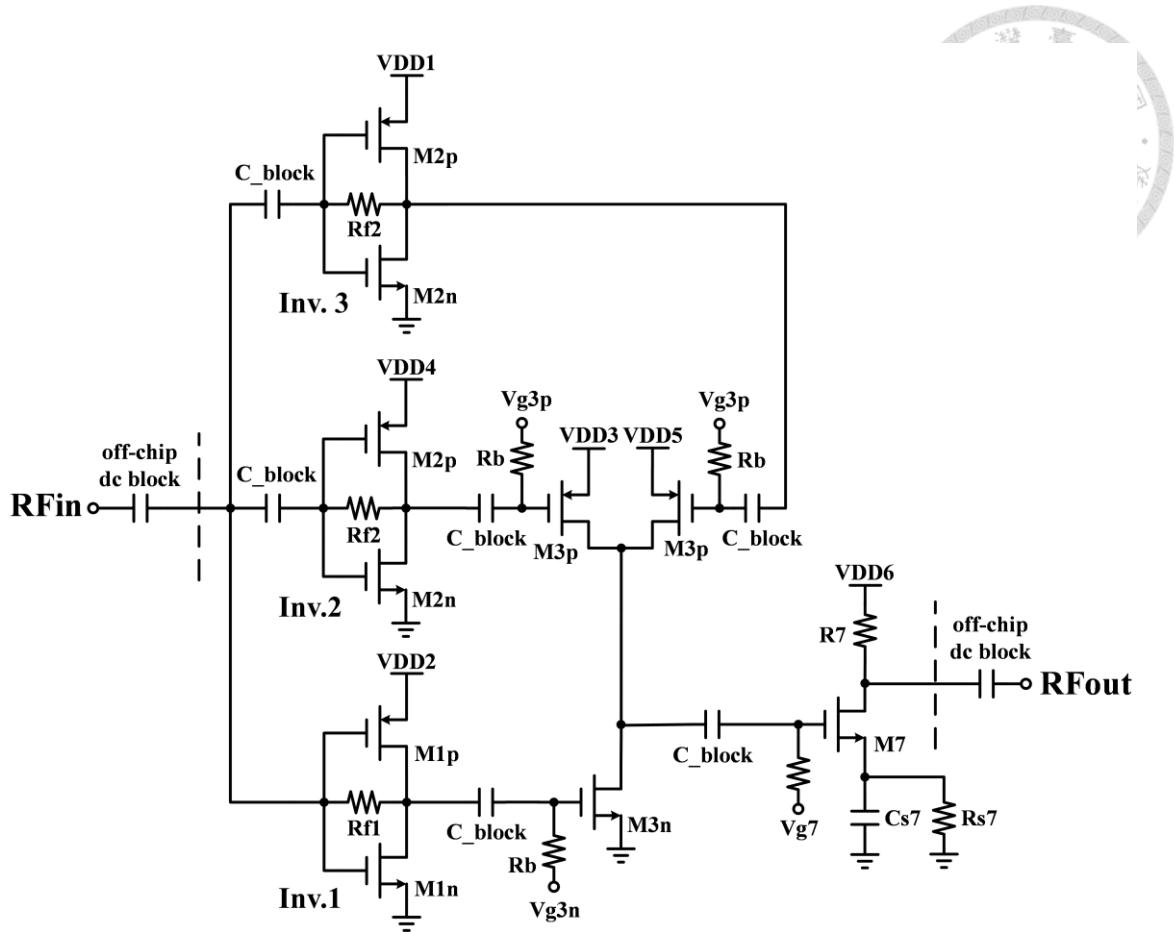

| Figure 2.2: Schematic diagram of the proposed cryo-CMOS LNA. ....                                                                                                                                                               | 19 |

| Figure 2.3: Schematic diagram of the noise-canceling mechanism of the noise contributions from the transistors of Inverter 1 in the proposed cryo-CMOS LNA. ....                                                                | 20 |

| Figure 2.4: Schematic diagram for calculating gain and noise power of an inverter amplifier stage. (a) Gain and input impedance. (b) Noise of the feedback resistor. (c) noise of the transistor. ....                          | 22 |

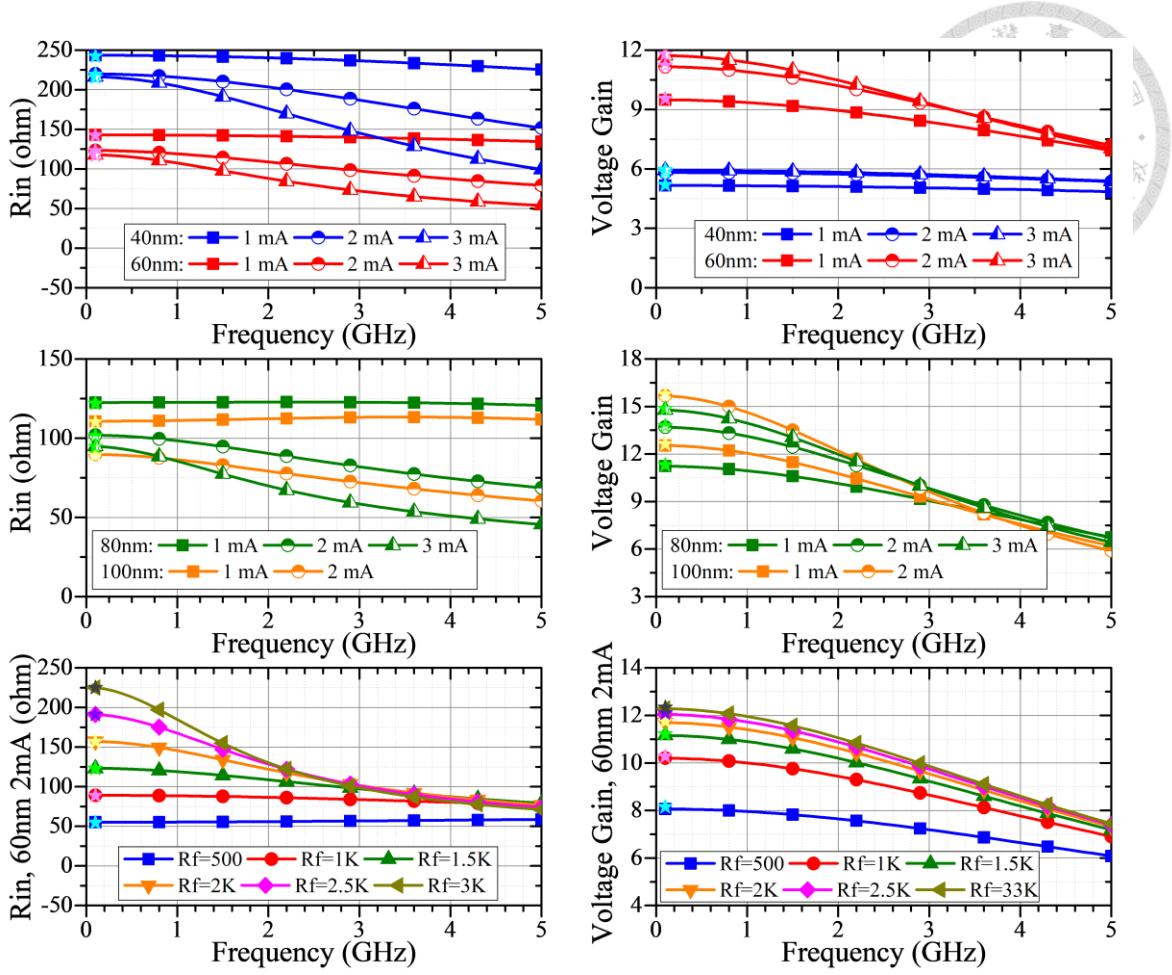

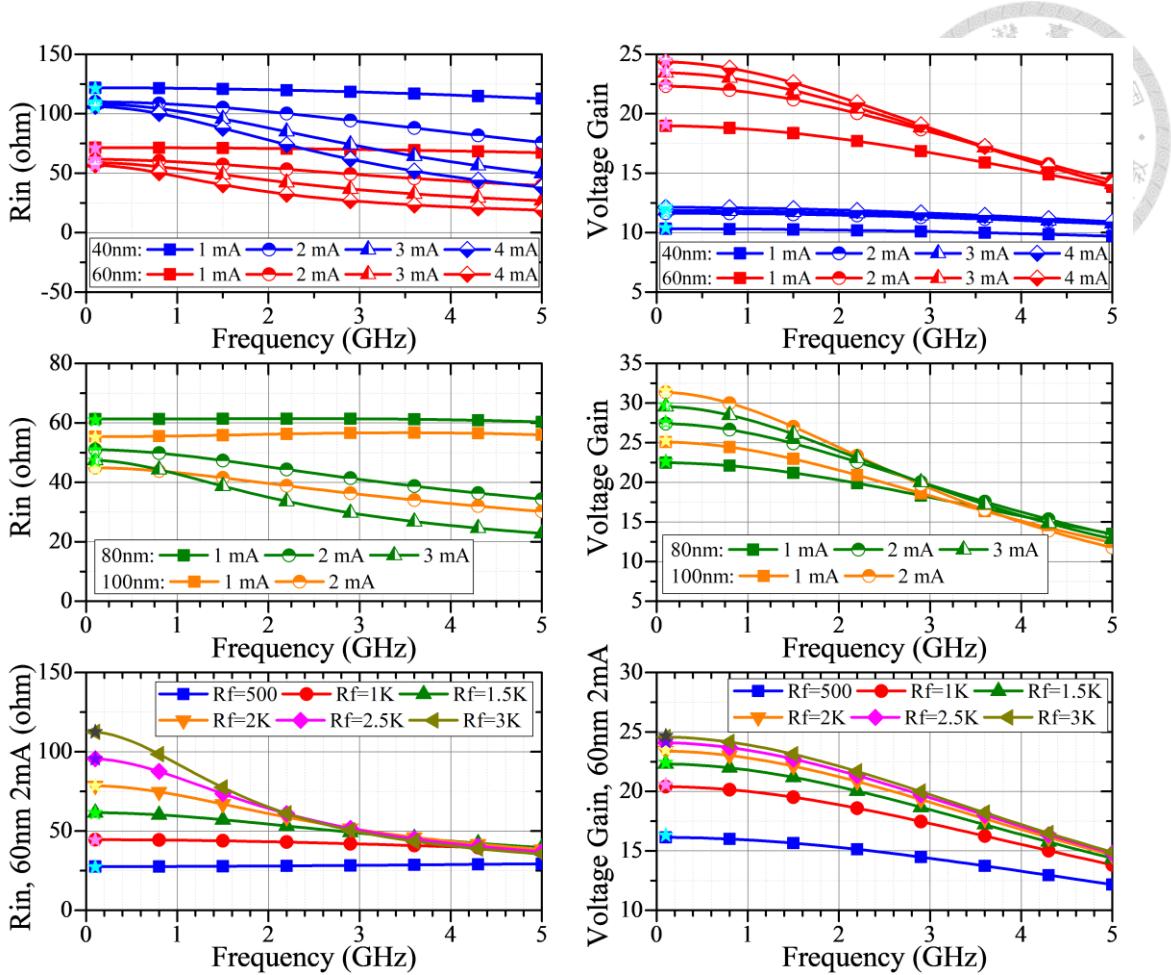

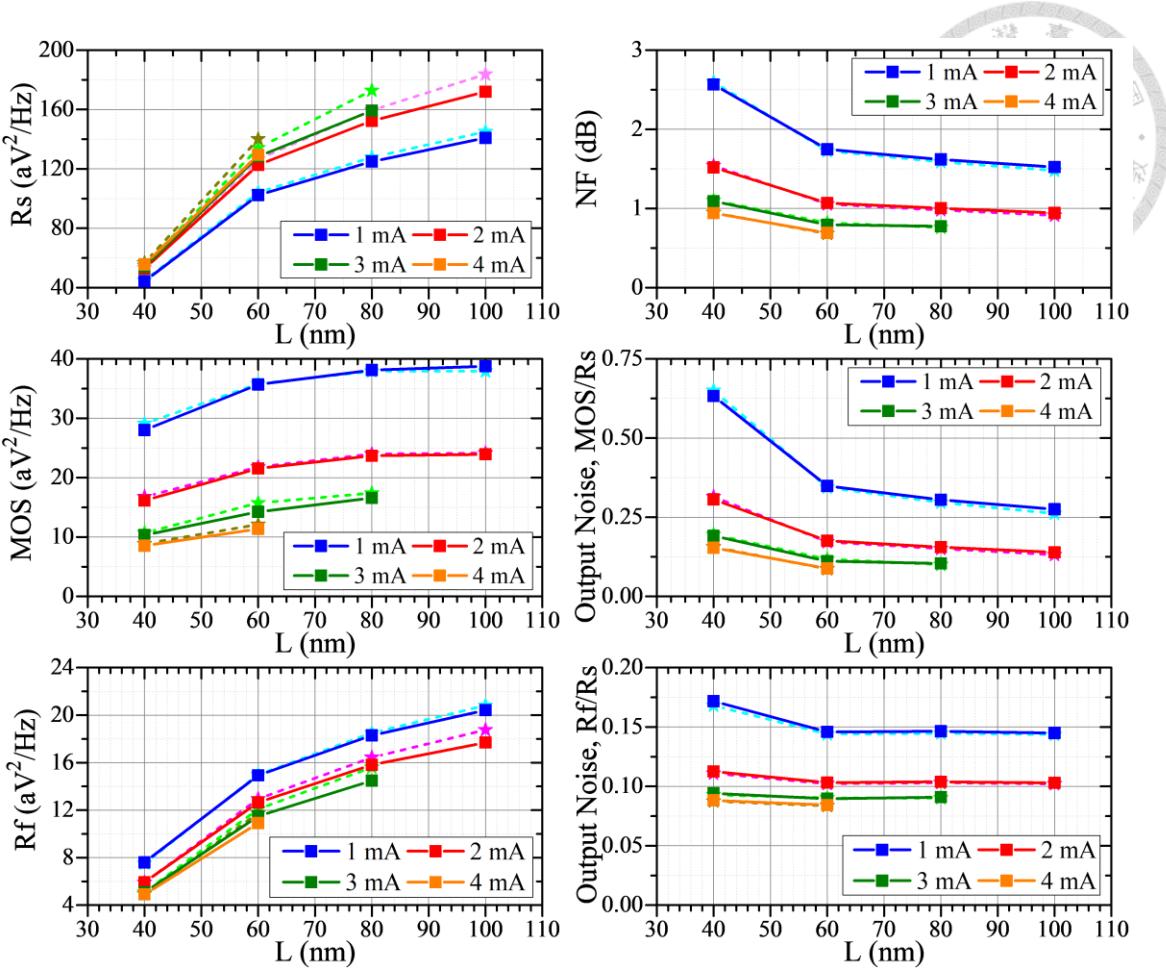

| Figure 2.5: Simulated and calculated small-signal responses of an inverter amplifier with different power consumption levels, gate lengths, and feedback resistors. ....                                                        | 24 |

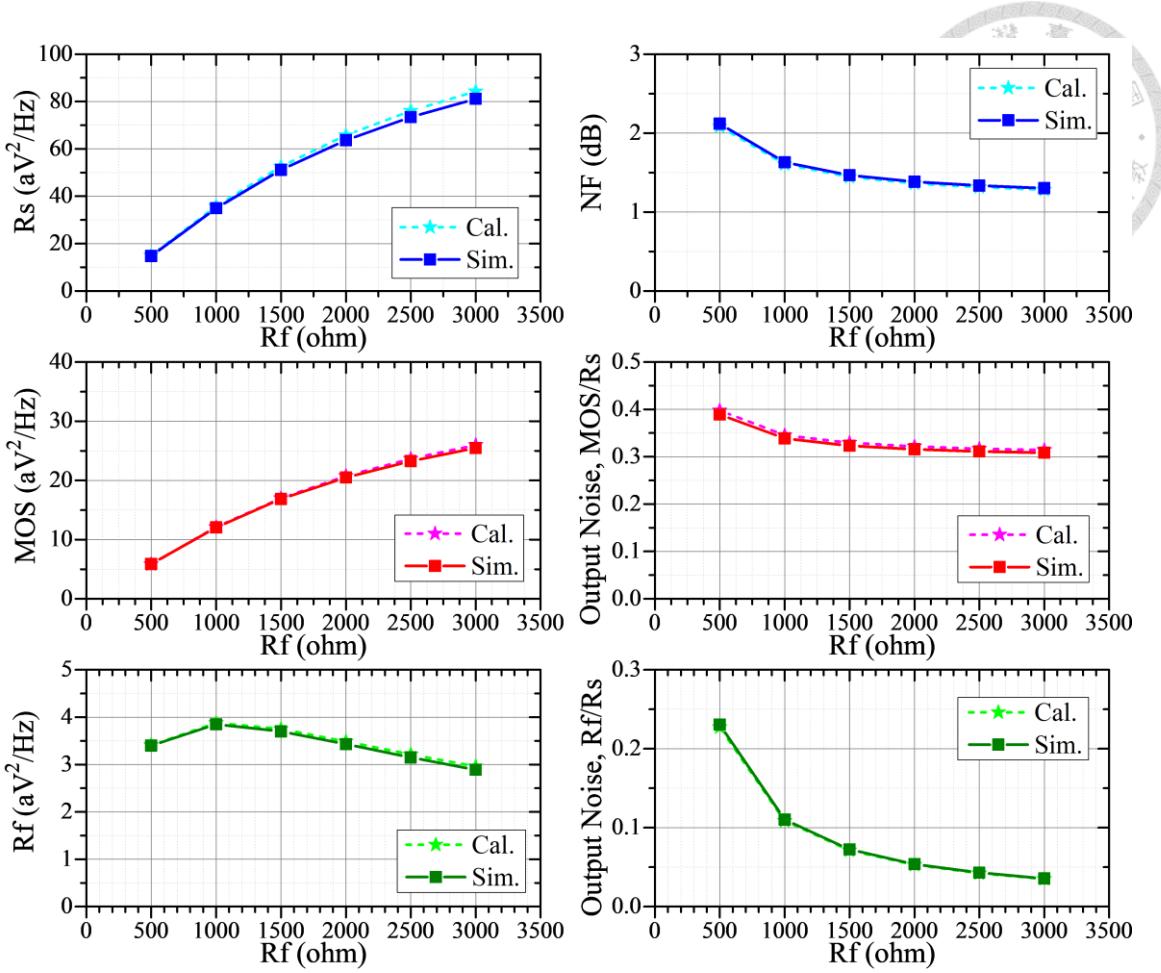

| Figure 2.6: Simulated and calculated output noise power contributions from various sources, output noise power ratios, and noise figure of an inverter amplifier with different power consumption levels and gate lengths. .... | 26 |

| Figure 2.7: Simulated and calculated output noise power contributions from various sources, output noise power ratios, and noise figure of an inverter amplifier with different feedback resistor values. ....                  | 27 |

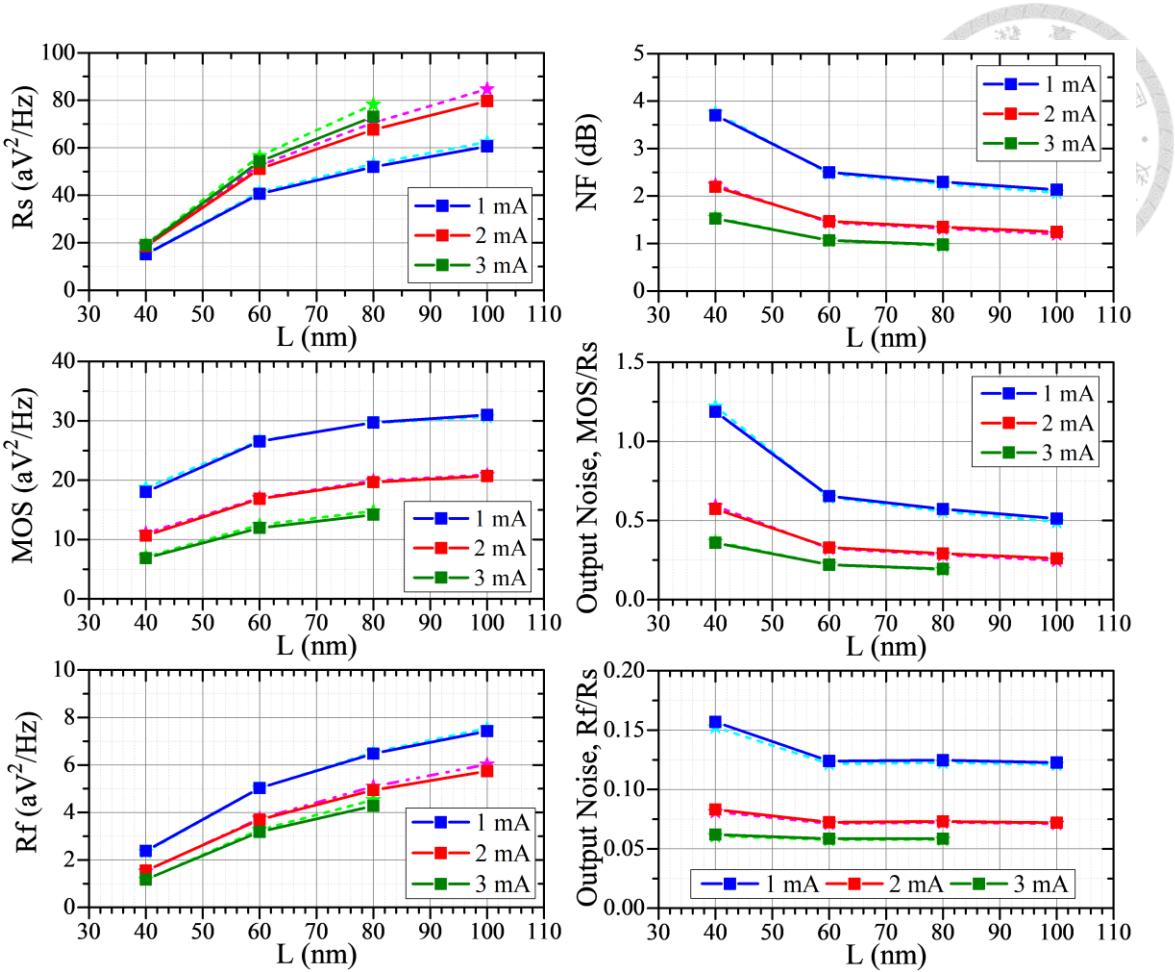

| Figure 2.8: Simulated and calculated small-signal responses of inverter amplifier pair with different power consumption levels, gate lengths, and feedback resistors. ....                                                      | 29 |

| Figure 2.9: Schematic diagram for calculating the noise power contribution from the feedback resistors of inverter amplifier pair. ....                                                                                         | 30 |

| Figure 2.10: Schematic diagram for calculating the noise power contribution from the transistors of inverter amplifier pair. ....                                                                                               | 31 |

| Figure 2.11: Simulated and calculated output noise power contributions from various sources, output noise power ratios, and noise figure of an inverter amplifier pair with                                                     |    |

|                                                                                                                                                                                                                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| different power consumption levels and gate lengths. ....                                                                                                                                                                                                                                                                       | 32 |

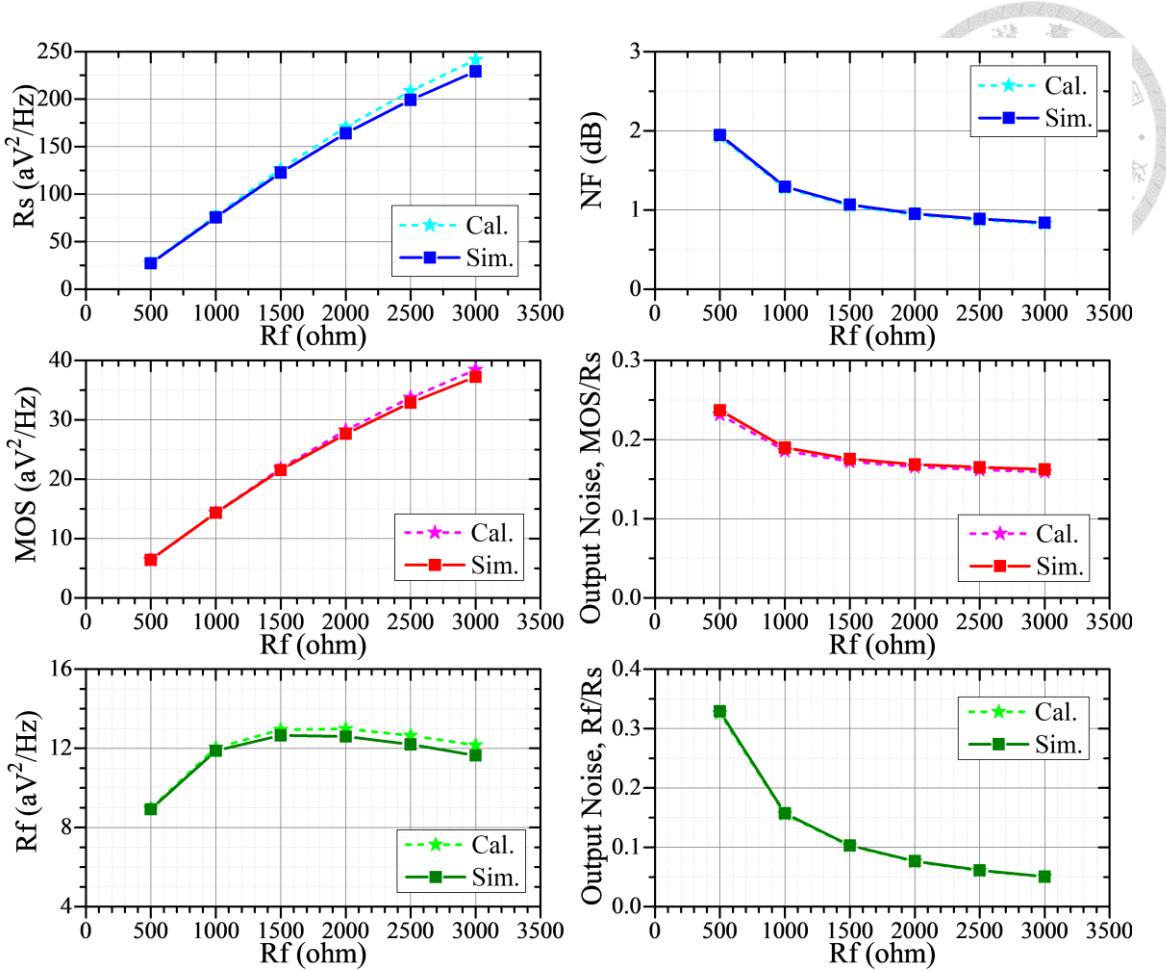

| Figure 2.12: Simulated and calculated output noise power contributions from various sources, output noise power ratios, and noise figure of an inverter amplifier pair with different feedback resistor values. ....                                                                                                            | 33 |

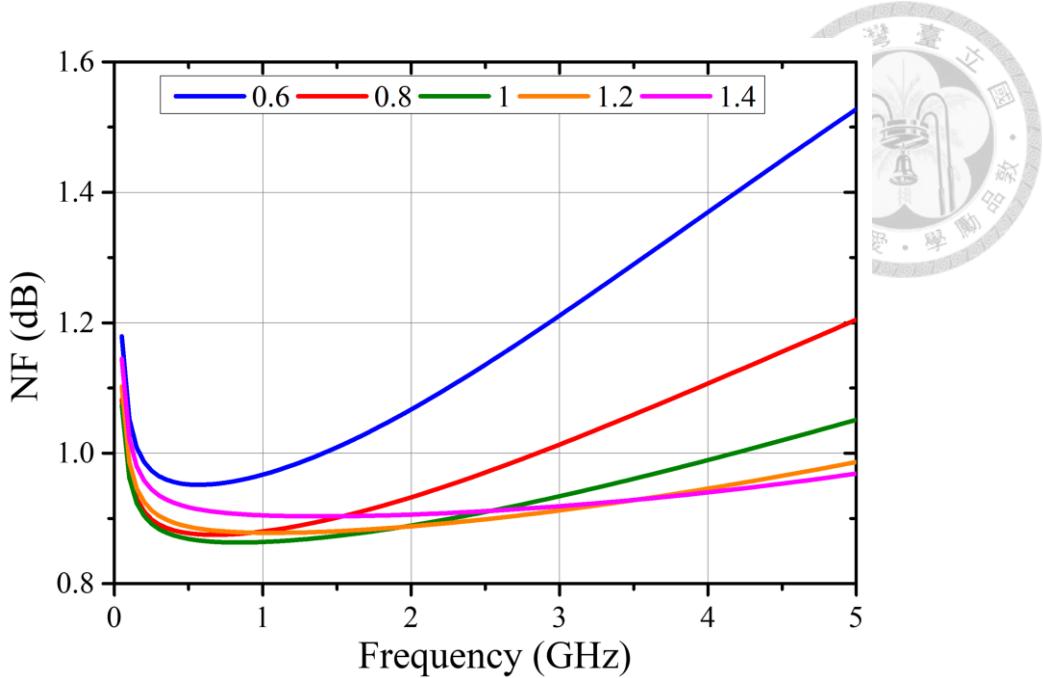

| Figure 2.13: Simulated noise figure with varying gain coefficient for Inverter 2 and Inverter 3 at the combining stage, while maintaining unity gain for Inverter 1. ....                                                                                                                                                       | 37 |

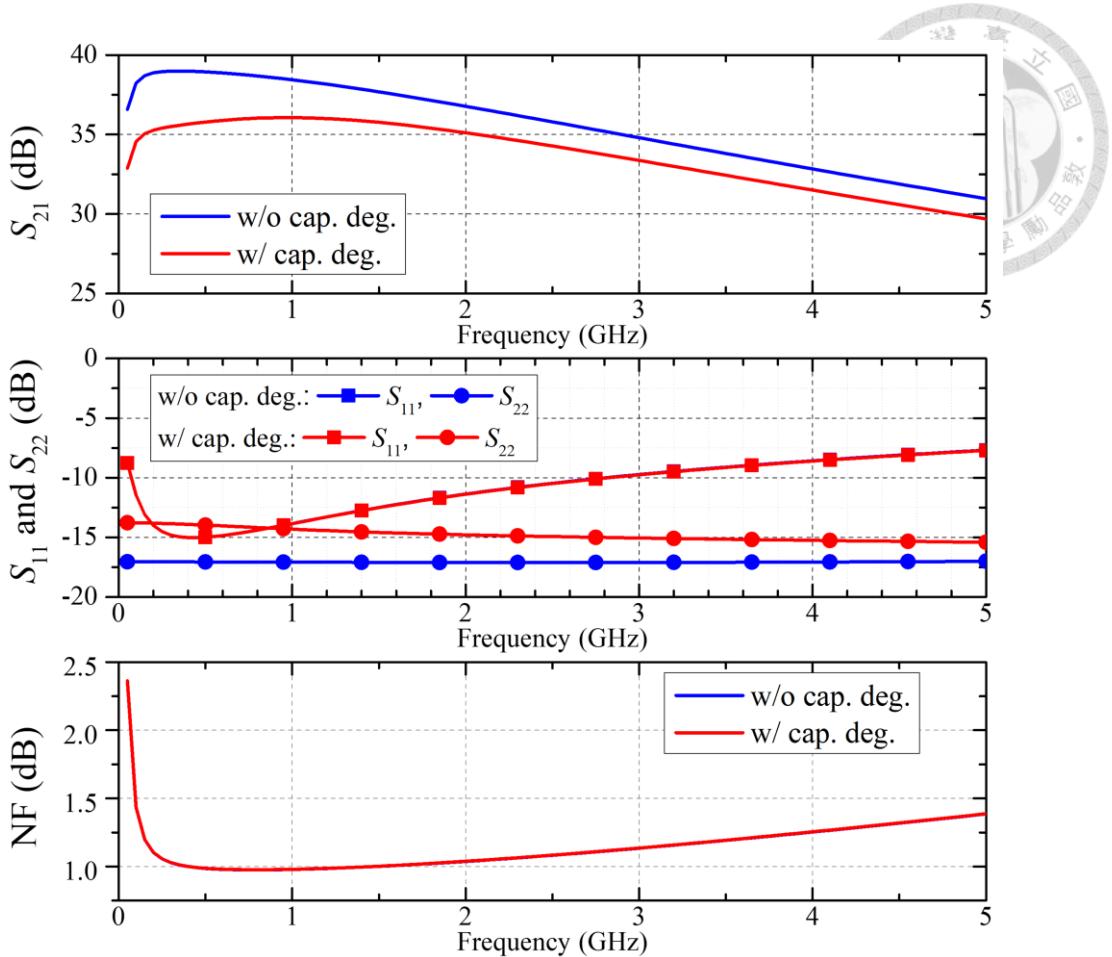

| Figure 2.14: Pre-simulated responses of the proposed LNA with and without adopting the capacitive degeneration technique at the output driver stage. ....                                                                                                                                                                       | 39 |

| Figure 2.15: Simulated responses of the on-chip bypass networks. ....                                                                                                                                                                                                                                                           | 40 |

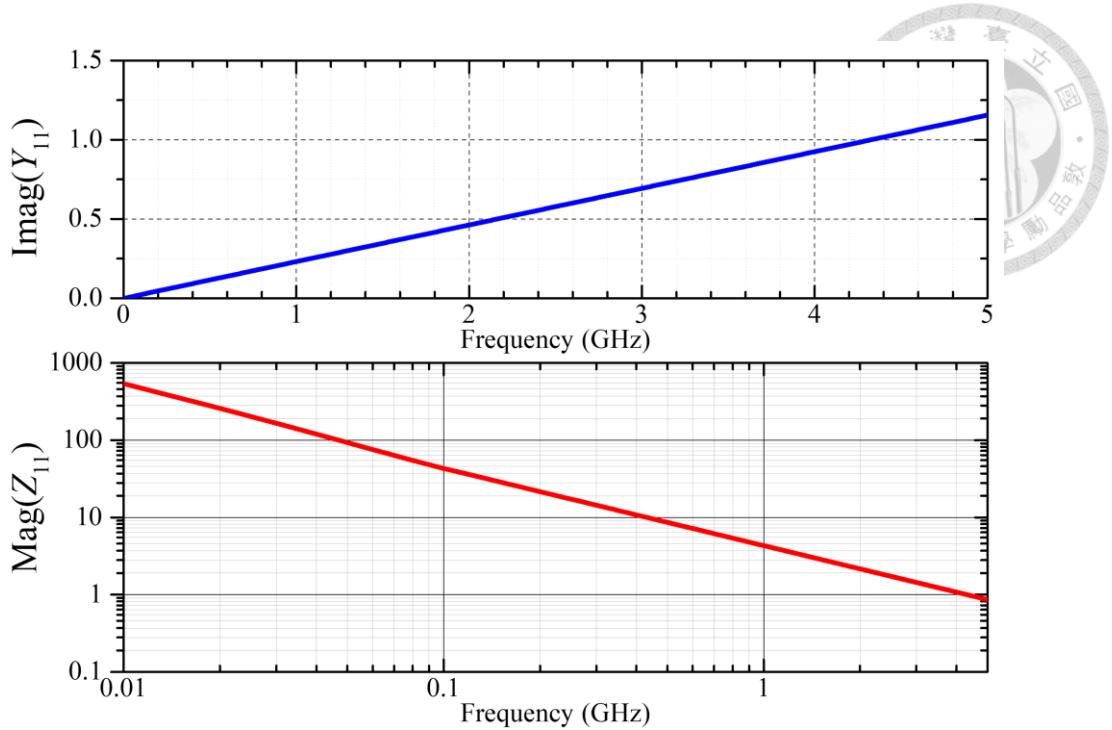

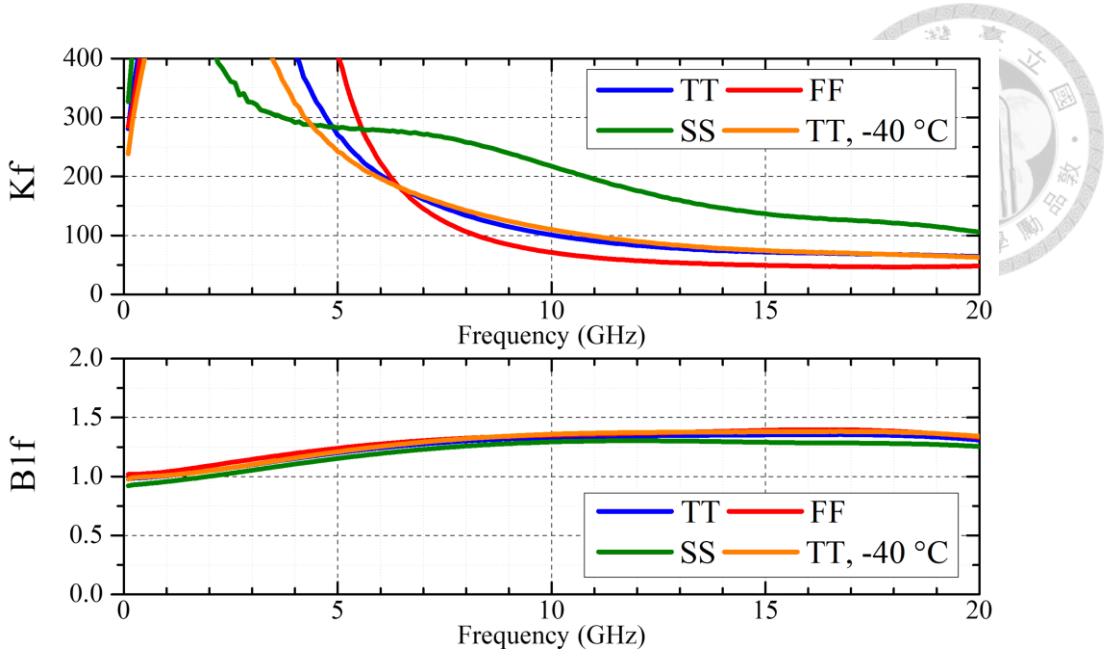

| Figure 2.16: Post-simulated stability results of the proposed LNA across various process corners and temperatures. ....                                                                                                                                                                                                         | 41 |

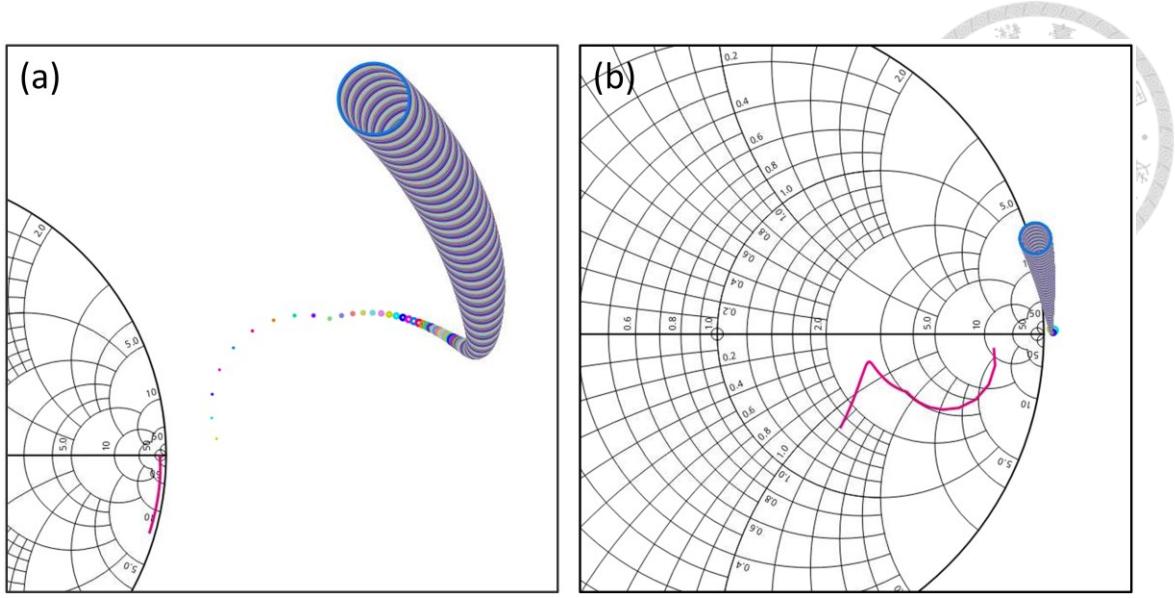

| Figure 2.17: Inter-stage stability simulation of the proposed LNA. (a) Load stability circles of the input sub-section and $S_{11}$ of the output sub-section with a 50-ohm load resistance. (b) Source stability circles of the output sub-section and $S_{22}$ of the input sub-section with a 50-ohm source resistance. .... | 42 |

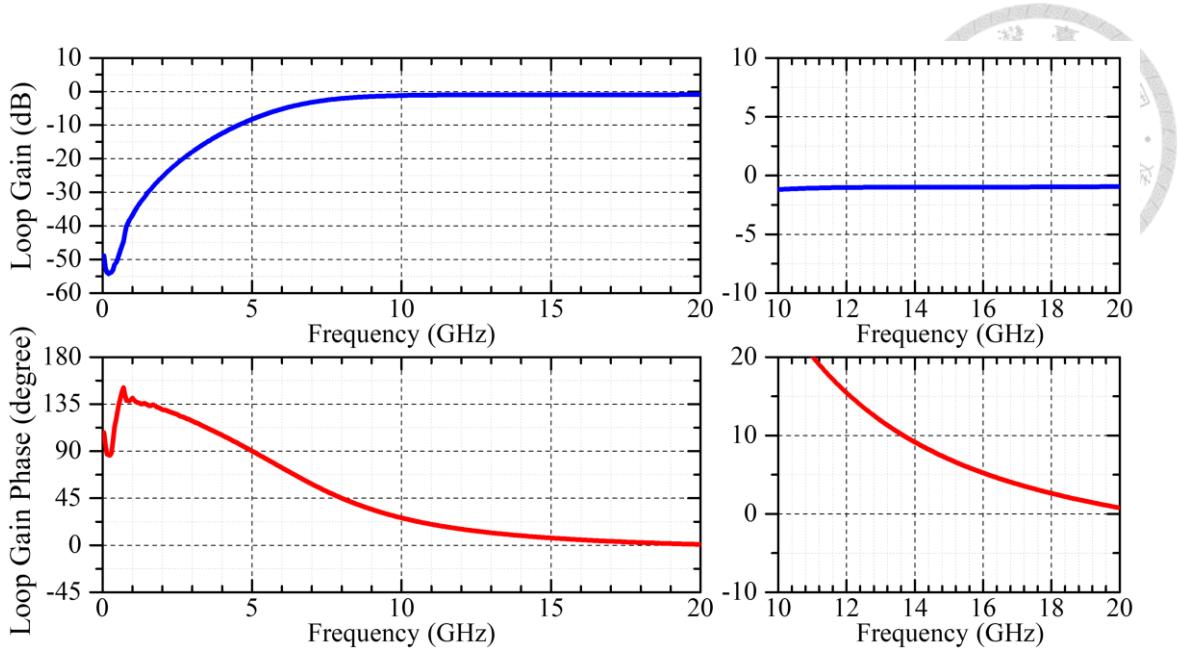

| Figure 2.18: Post-simulation results of loop gain and loop gain phase of the input sub-section of the proposed LNA. ....                                                                                                                                                                                                        | 43 |

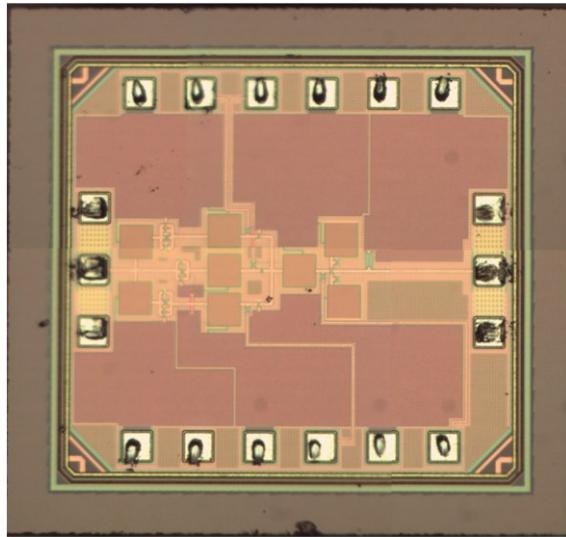

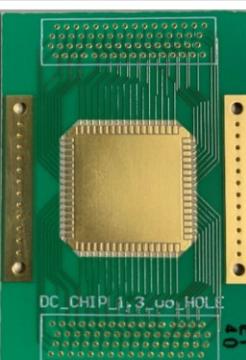

| Figure 2.19: Chip photograph of the proposed cryo-CMOS LNA. ....                                                                                                                                                                                                                                                                | 44 |

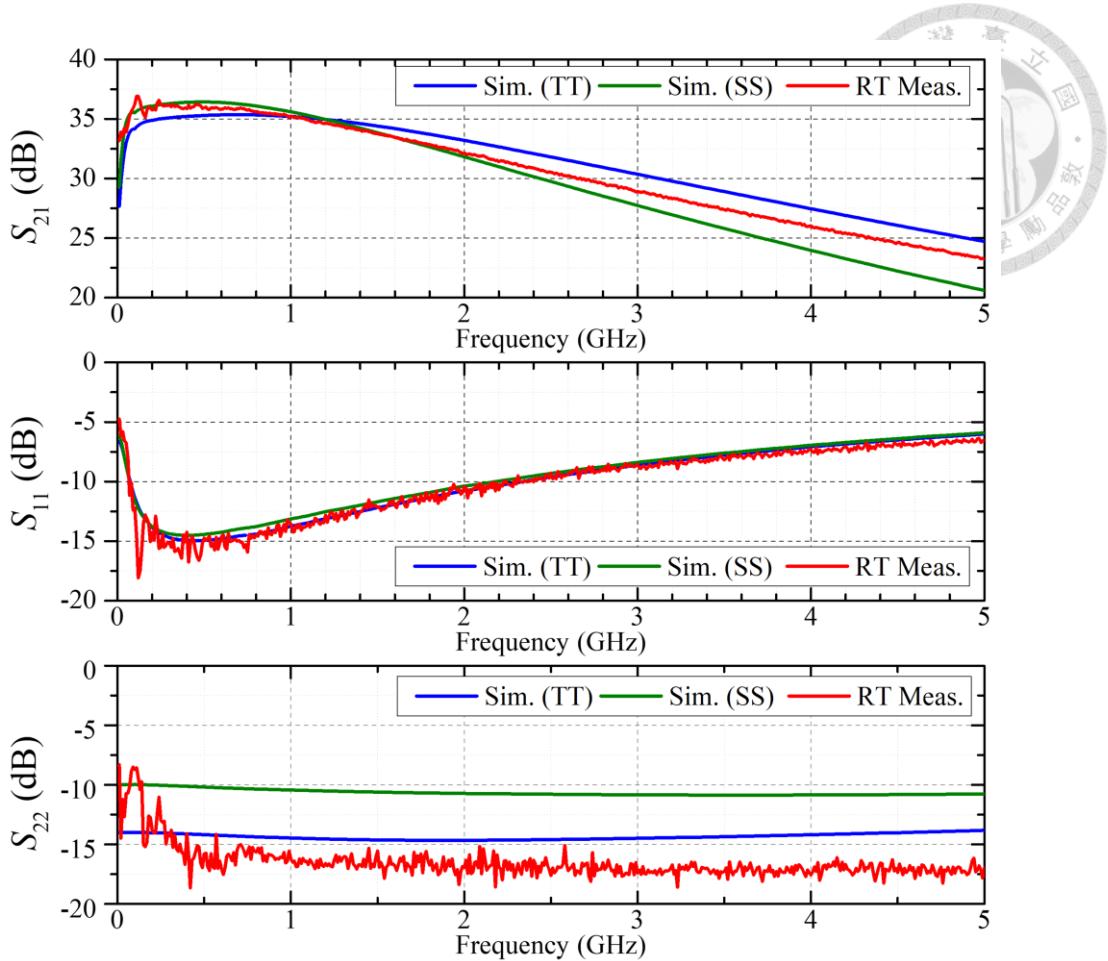

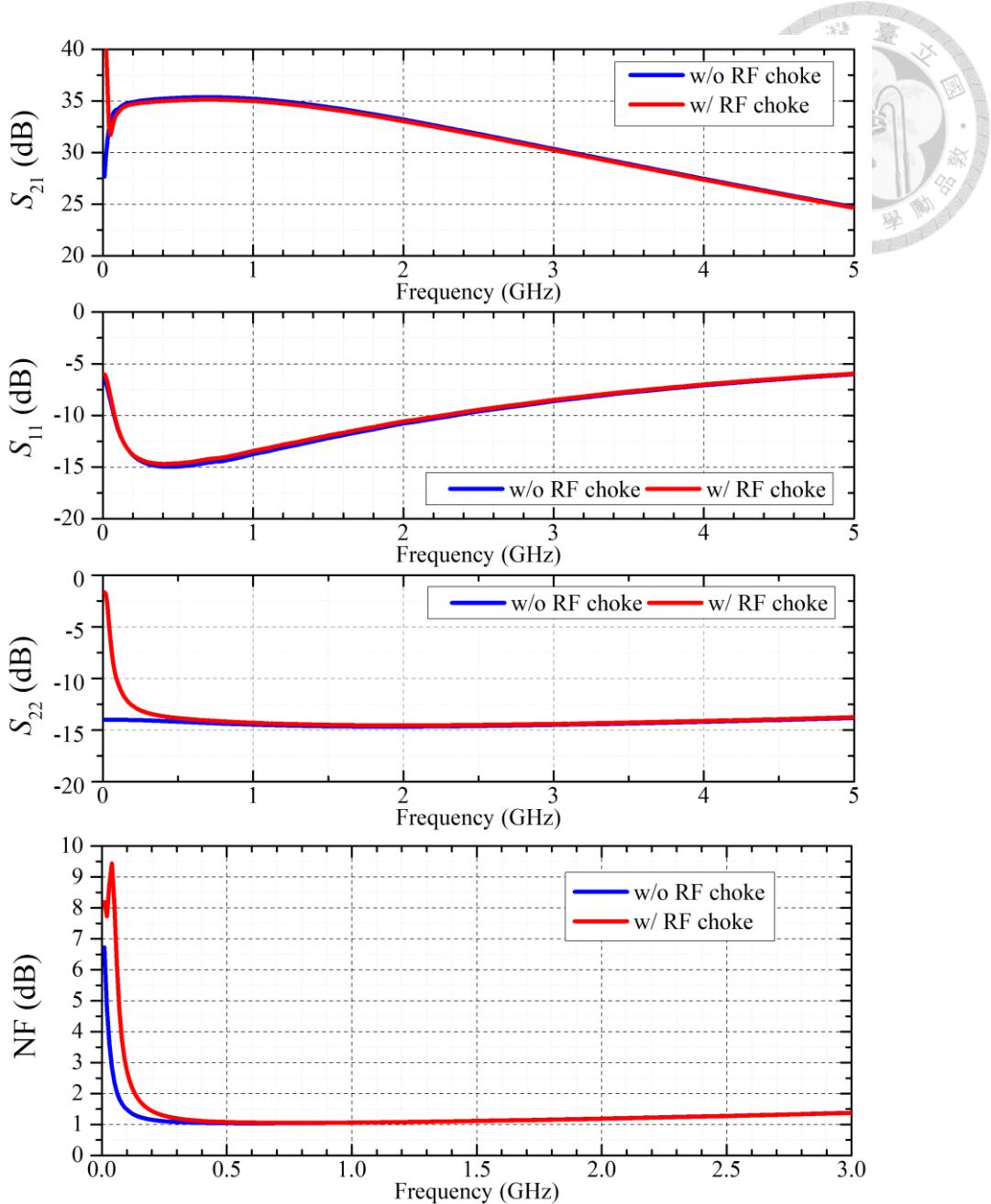

| Figure 2.20: Measured and post-simulated (in TT and SS corners) S-parameter responses of the proposed cryo-CMOS LNA. ....                                                                                                                                                                                                       | 45 |

| Figure 2.21: Measured and post-simulated (in TT and SS corners) noise figure of the proposed cryo-CMOS LNA. ....                                                                                                                                                                                                                | 46 |

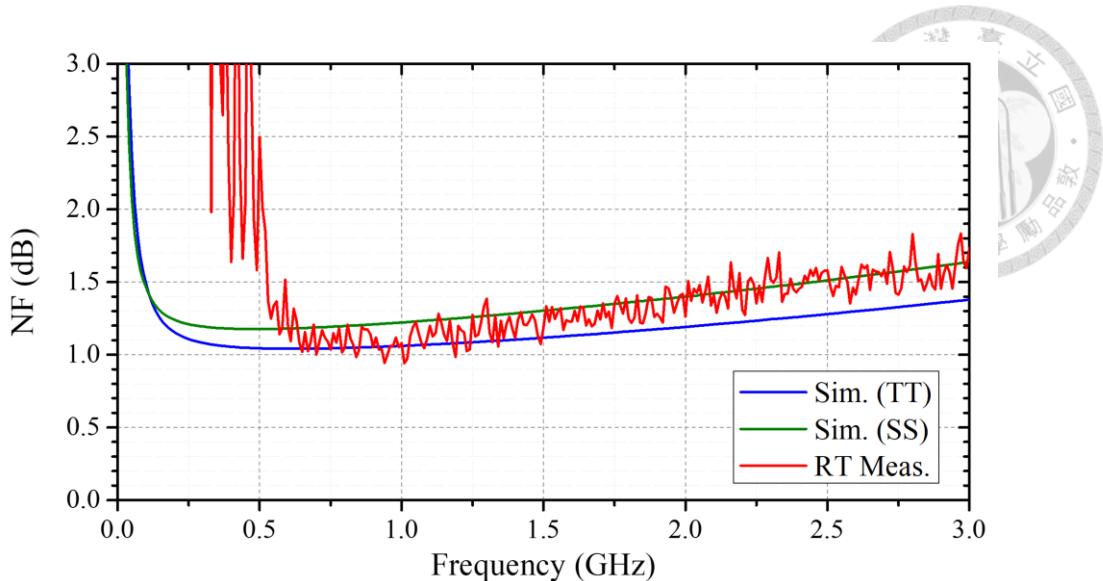

| Figure 2.22: Comparison of post-simulation results of the proposed cryo-CMOS LNA with and without RF chokes before the ideal supply voltage source. ....                                                                                                                                                                        | 47 |

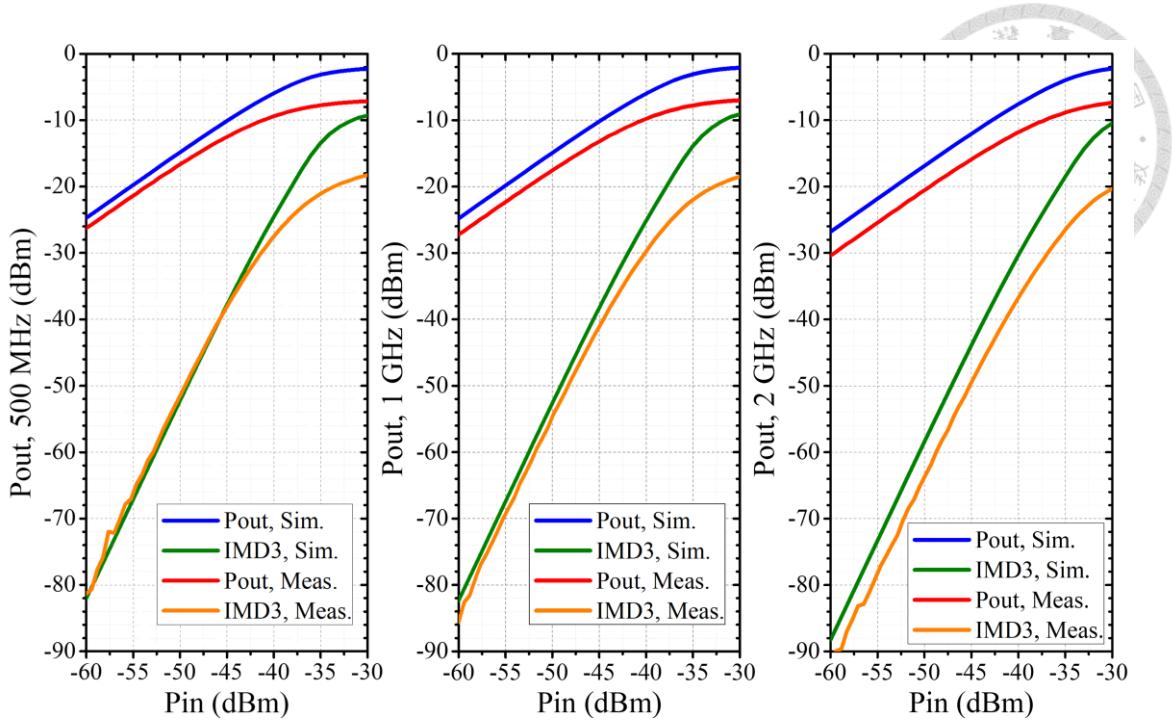

| Figure 2.23: Measured and post-simulated (TT) large signal results of the proposed cryo-                                                                                                                                                                                                                                        |    |

|                                                                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| CMOS LNA at 500 MHz, 1 GHz, and 2 GHz.....                                                                                                                                | 48 |

| Figure 3.1: Schematic diagram of the proposed SP4T switch.....                                                                                                            | 56 |

| Figure 3.2: Equivalent circuit model of the proposed switch (activating RF1). .....                                                                                       | 57 |

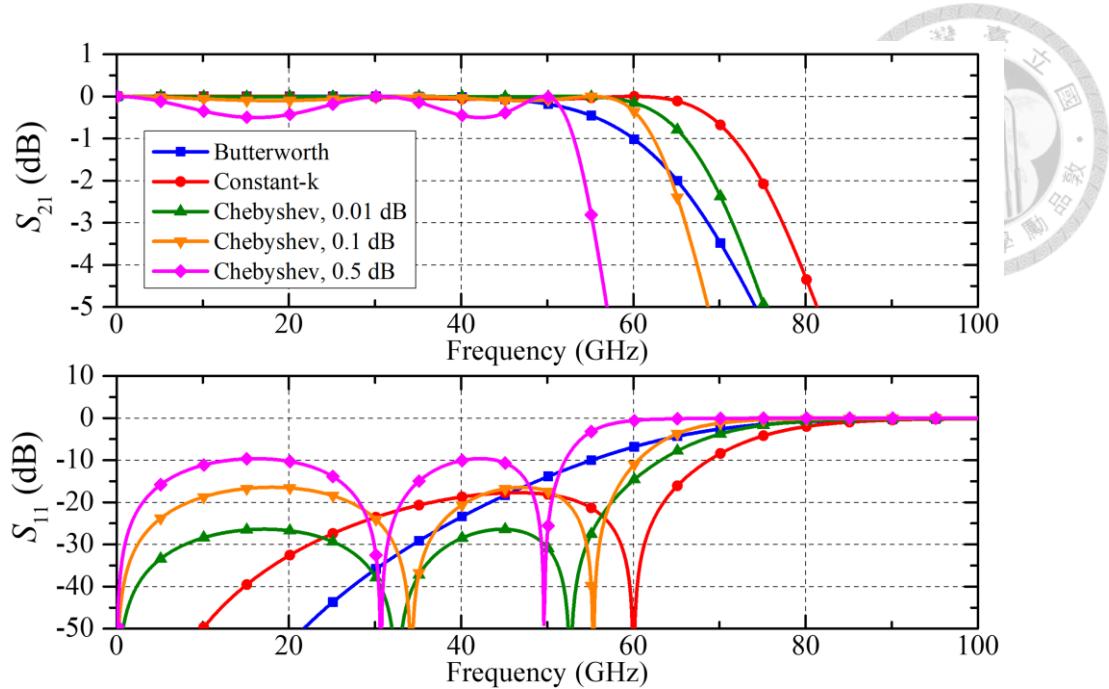

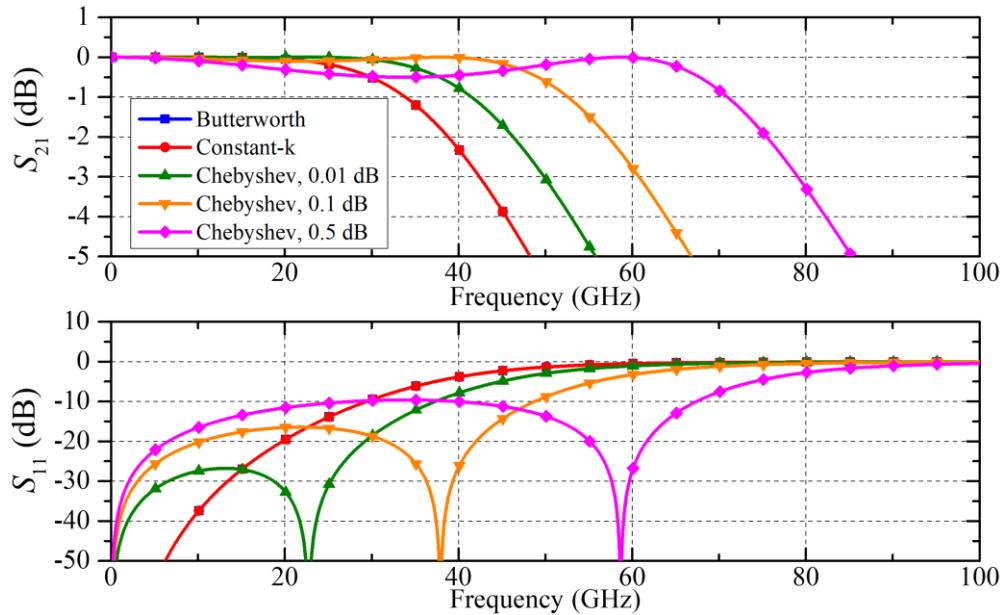

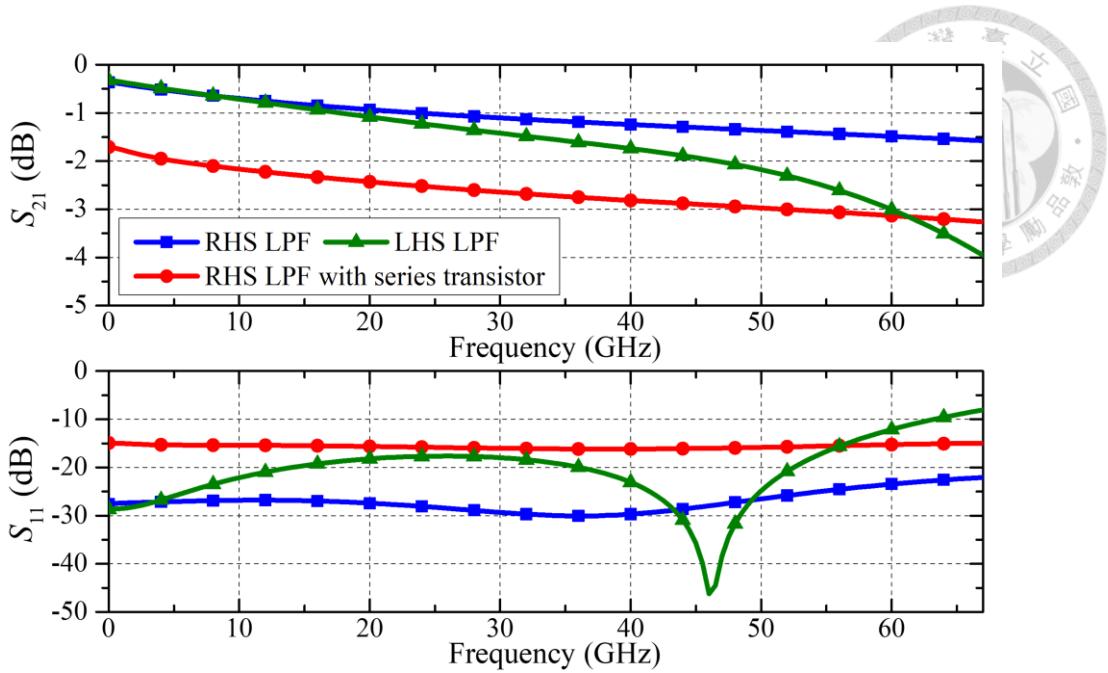

| Figure 3.3: Simulated responses of the series-first fifth-order LC-ladder LPFs. ....                                                                                      | 59 |

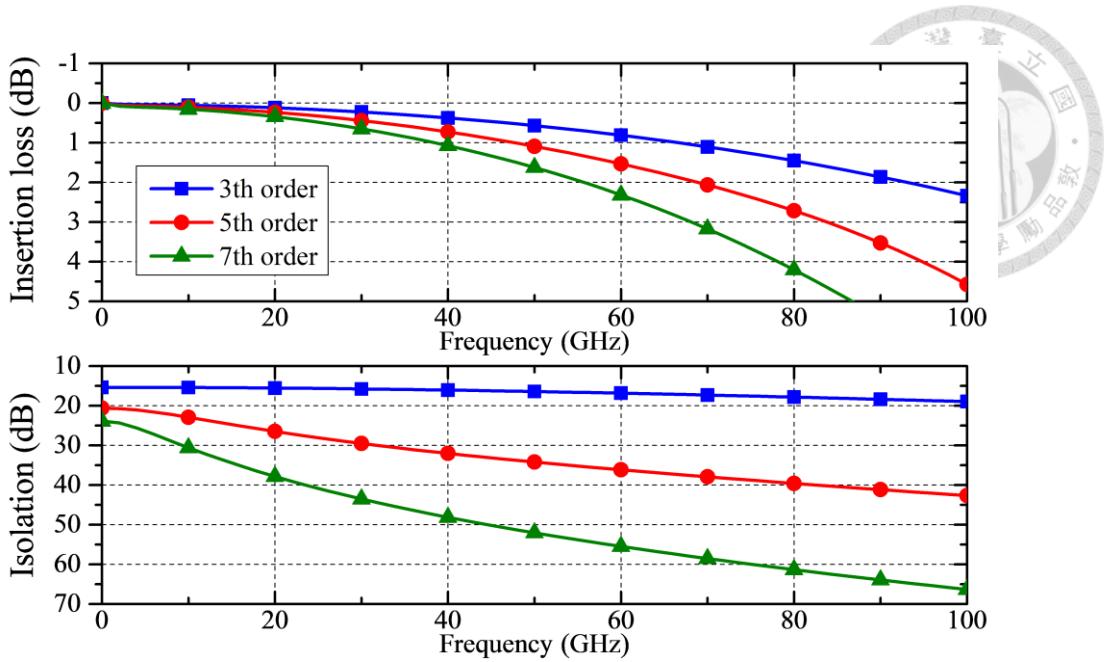

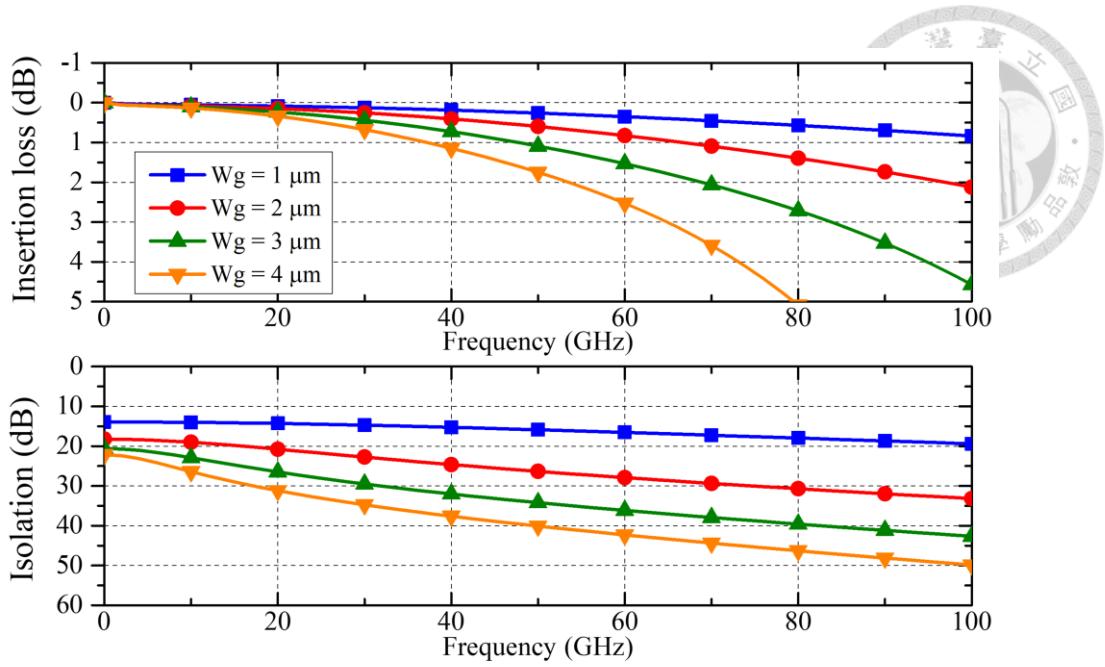

| Figure 3.4: Simulated responses of RHS output series-first constant-k filters with different numbers of shunt transistors (different orders of constant-k filters). ..... | 60 |

| Figure 3.5: Simulated responses of RHS output series-first fifth-order constant-k filters with different shunt transistor widths. ....                                    | 61 |

| Figure 3.6: Simulated responses of a single branch with varying widths of series transistors connected to the RHS output series-first LC LPF.....                         | 62 |

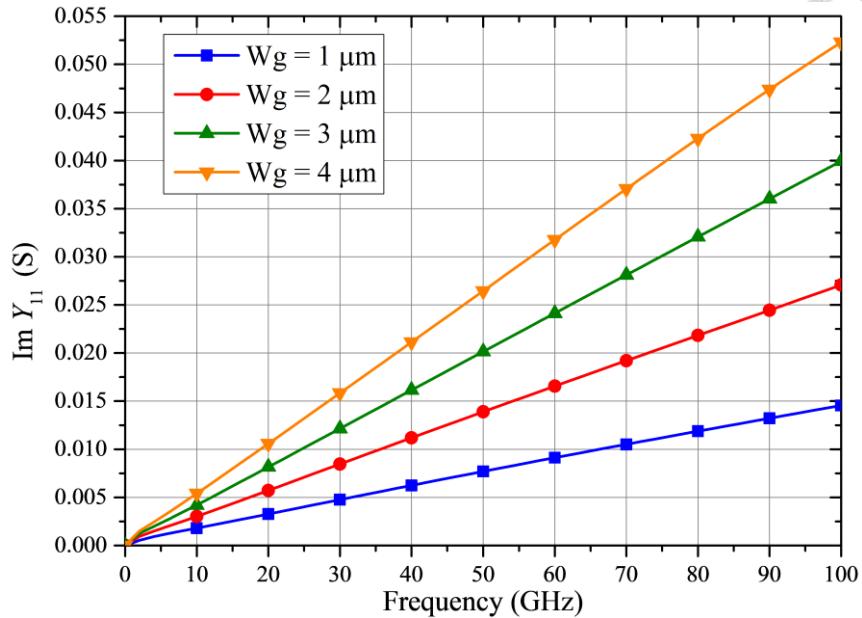

| Figure 3.7: Imaginary part of $Y_{11}$ of the SP4T switch (activating RF1) without input matching circuitry, while varying the widths of the series transistors. ....     | 63 |

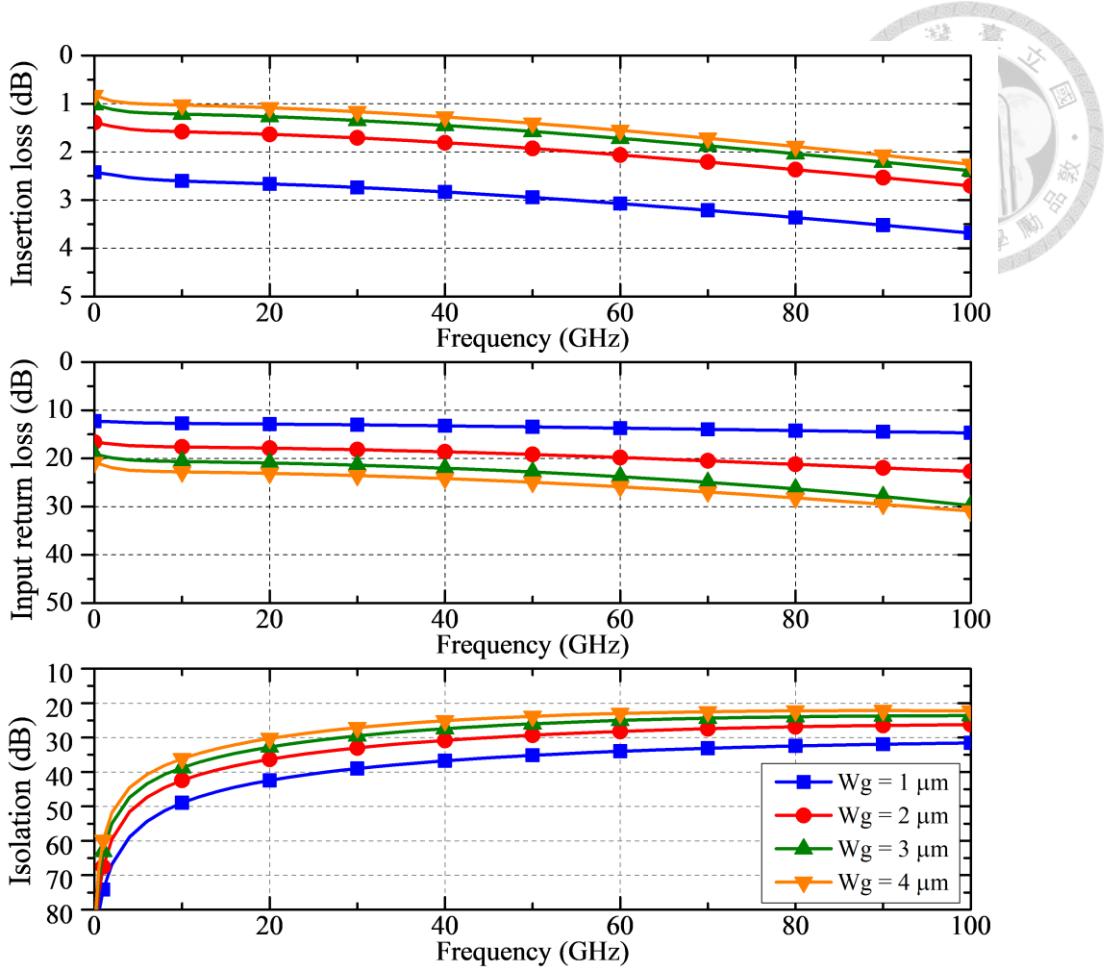

| Figure 3.8: Simulated responses of the shunt-first third-order LC-ladder LPFs. ....                                                                                       | 63 |

| Figure 3.9 : Post-simulated responses of the RHS LPF, the LHS LPF, and the RHS LPF with the series transistor. ....                                                       | 64 |

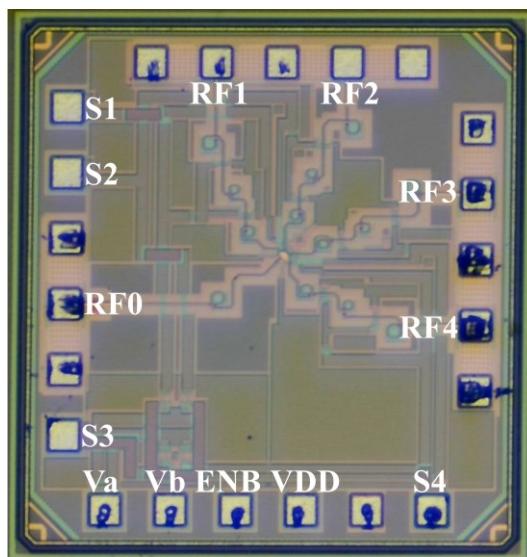

| Figure 3.10: Chip photograph of the proposed SP4T switch. ....                                                                                                            | 65 |

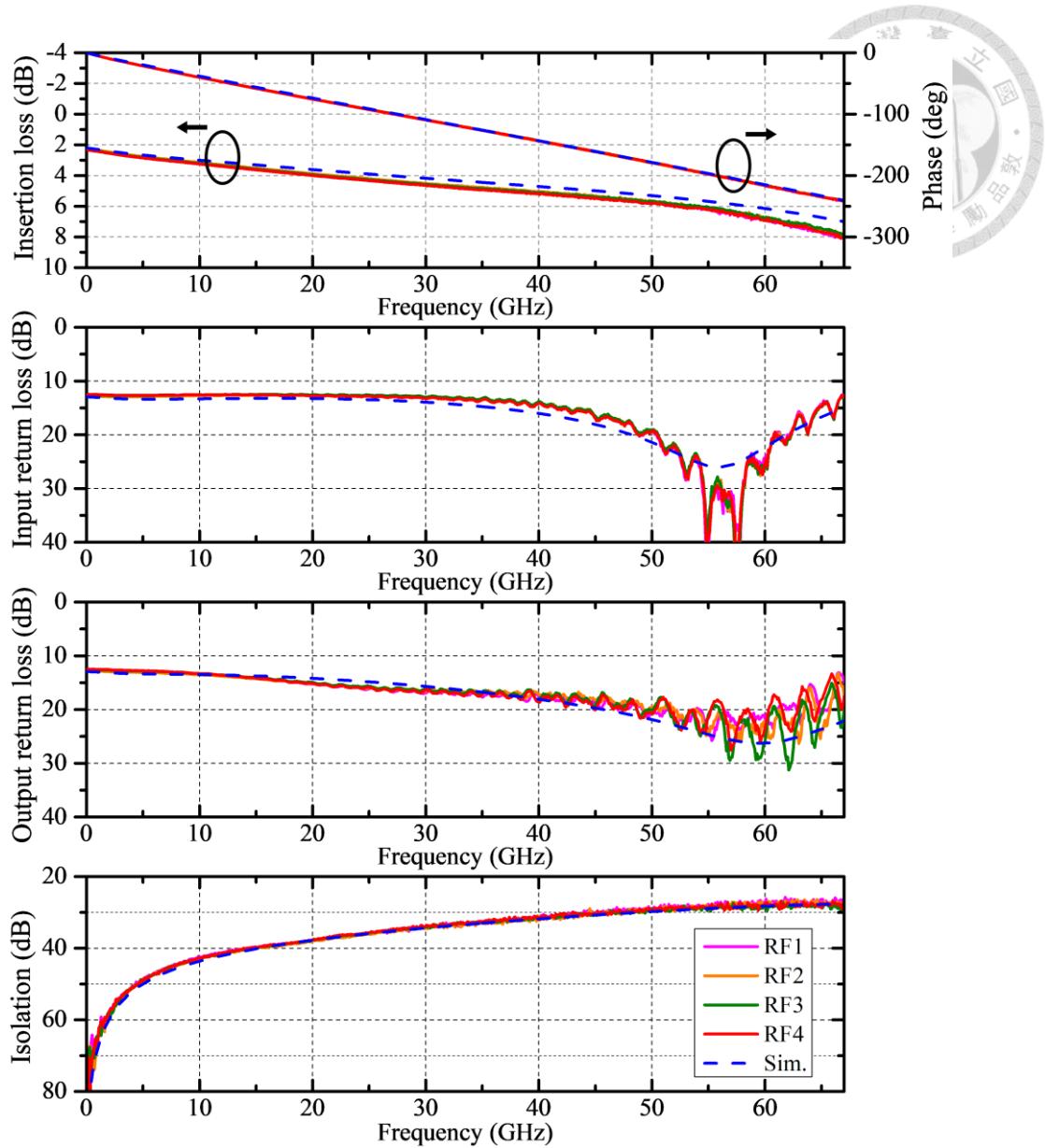

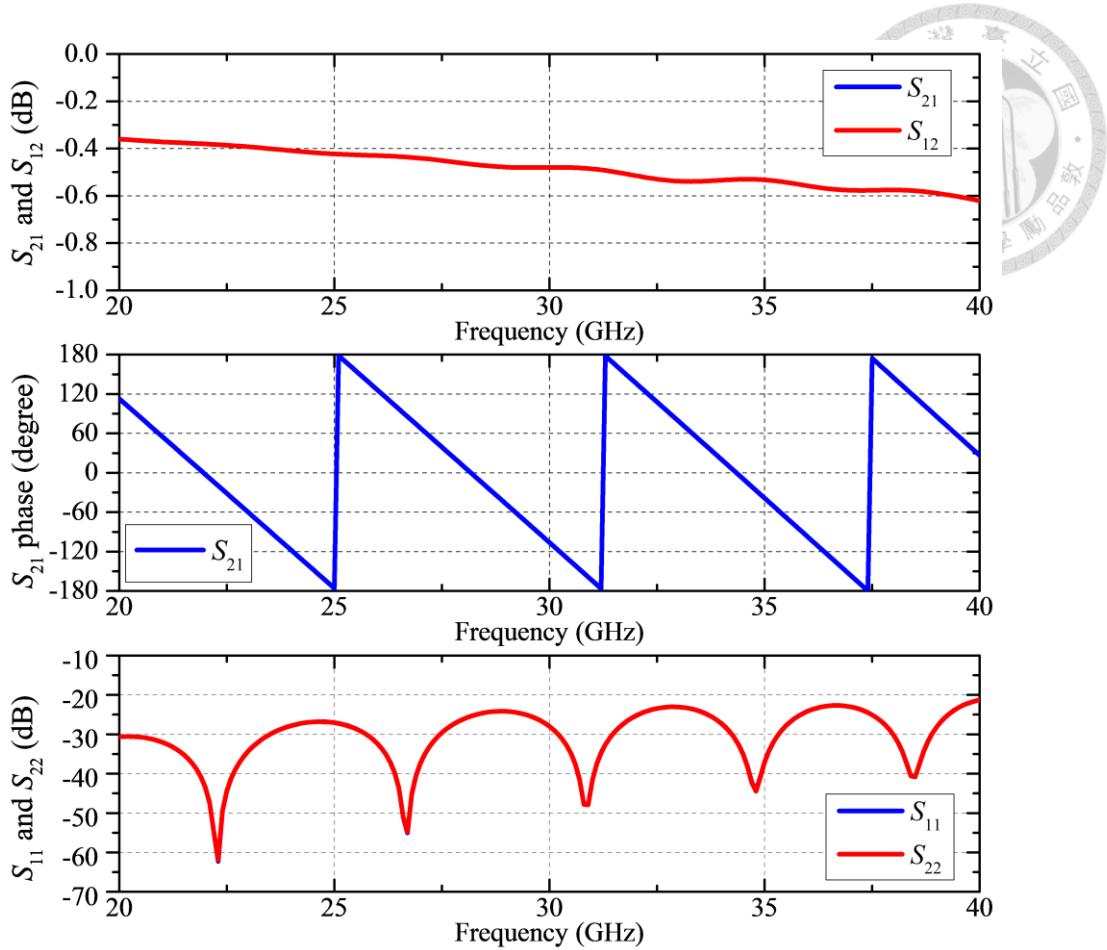

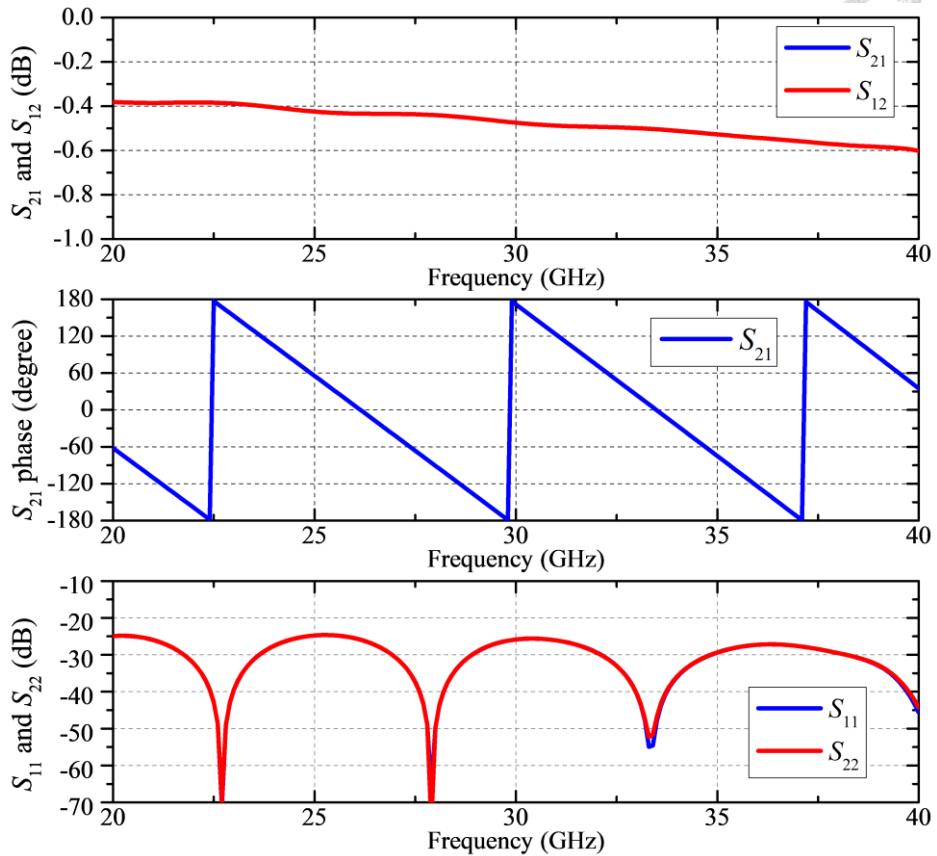

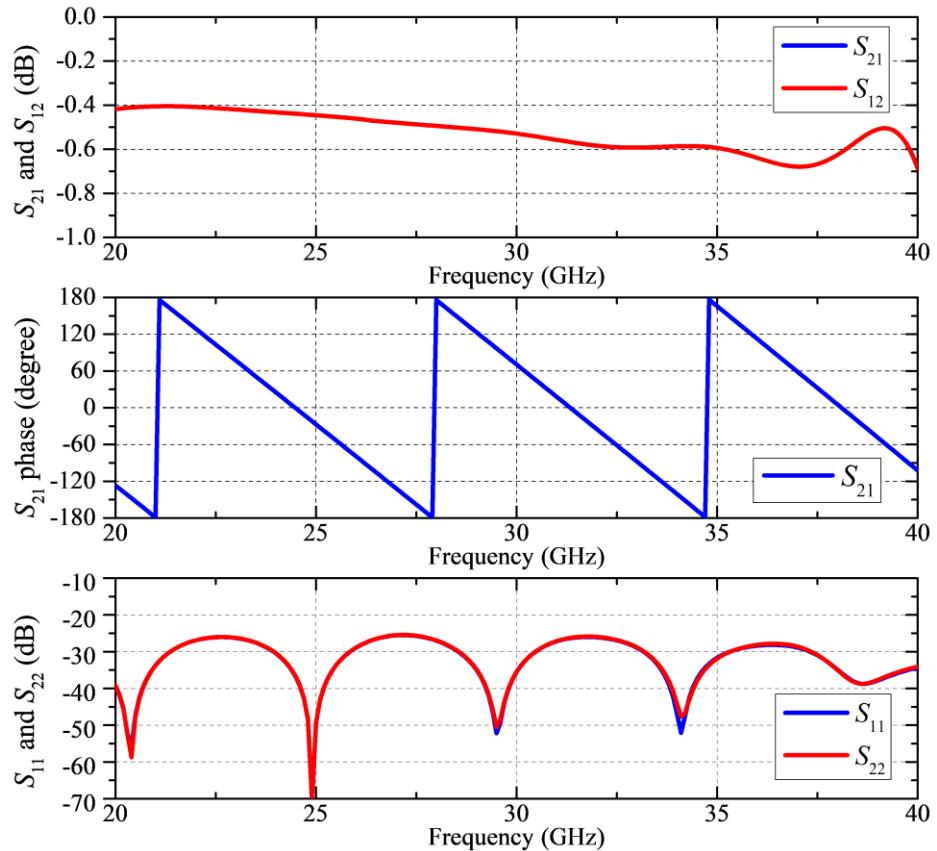

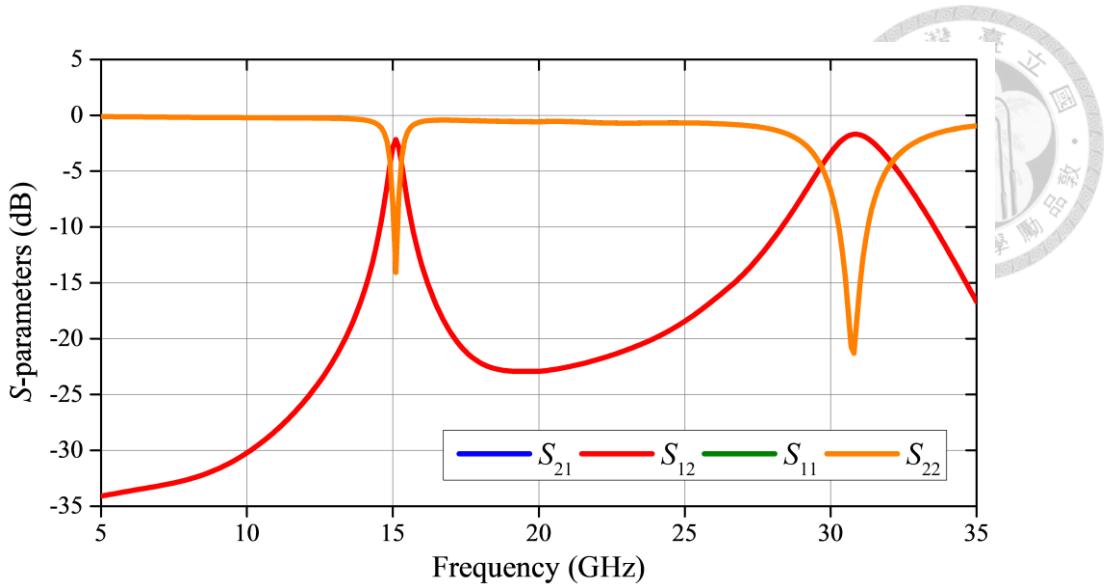

| Figure 3.11: Simulated and measured $S$ -parameter results at room temperature. ....                                                                                      | 66 |

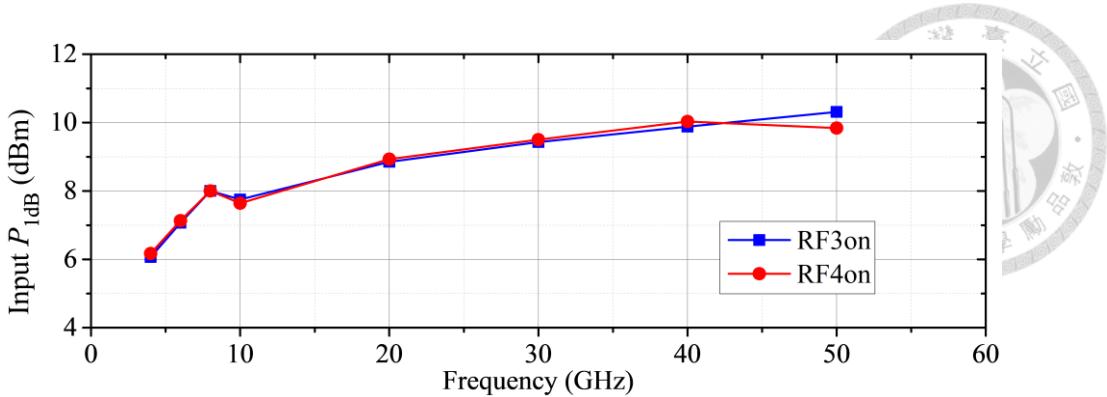

| Figure 3.12: Measured input $P1\text{dB}$ at room temperature (activating RF3 and RF4)...                                                                                 | 68 |

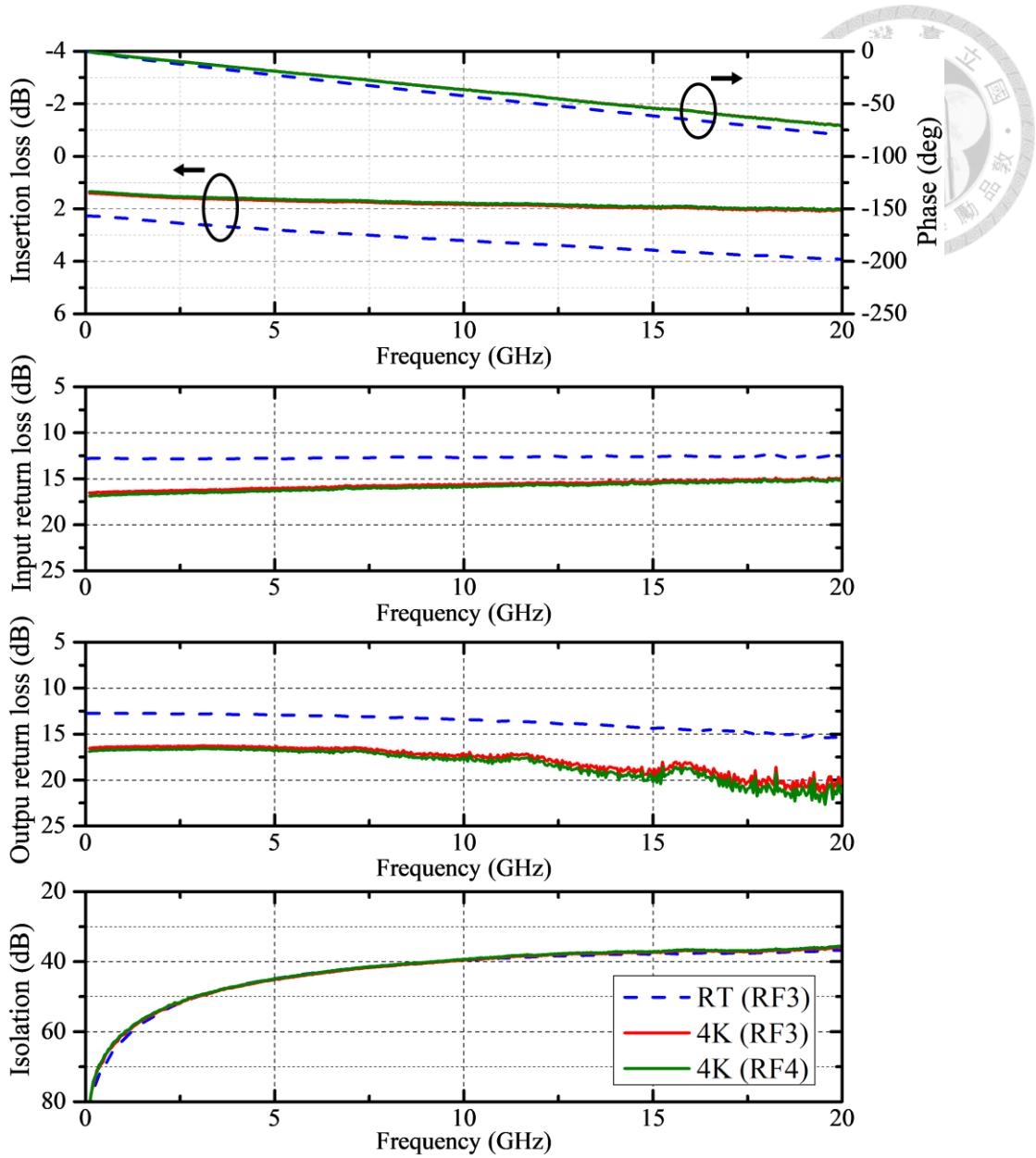

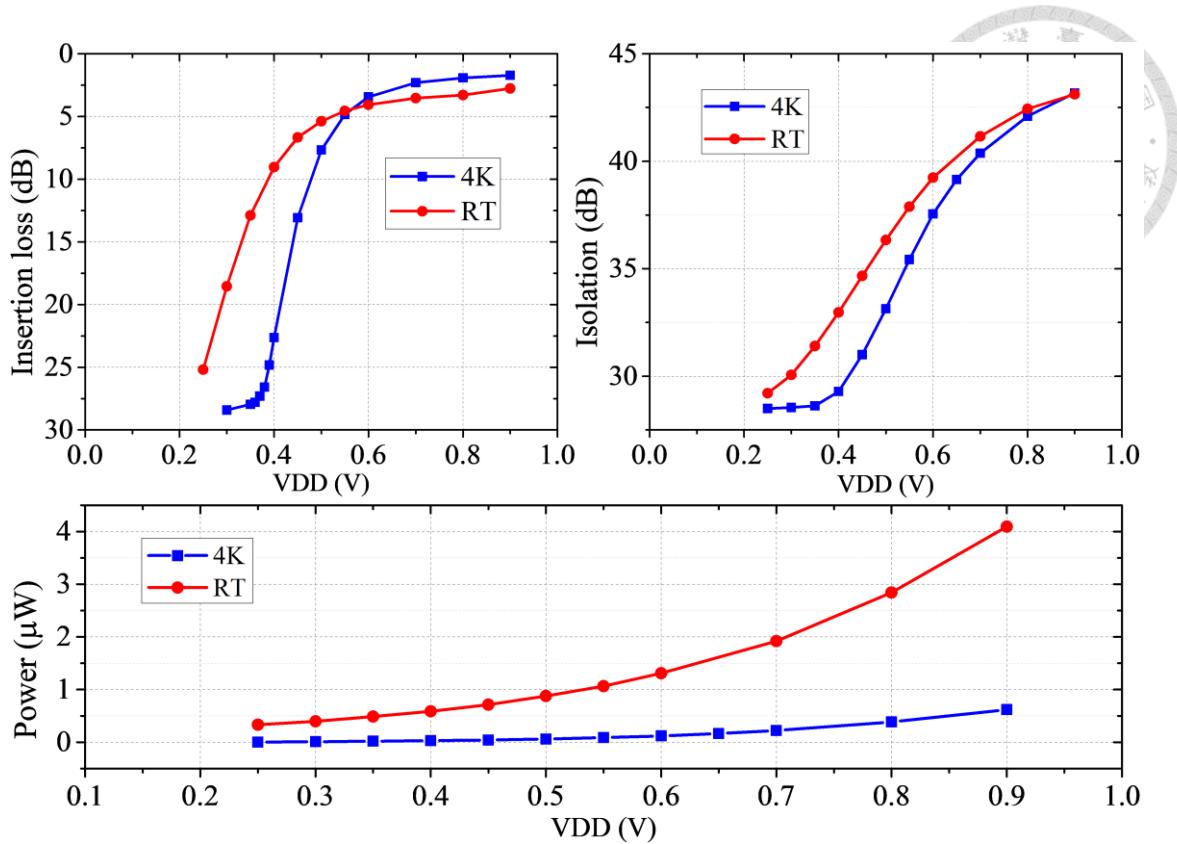

| Figure 3.13: $S$ -parameter results measured at RT and 4 K.....                                                                                                           | 69 |

| Figure 3.14: Power consumption, insertion loss, and isolation at 6 GHz for various ....                                                                                   | 70 |

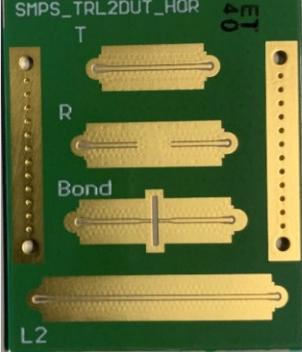

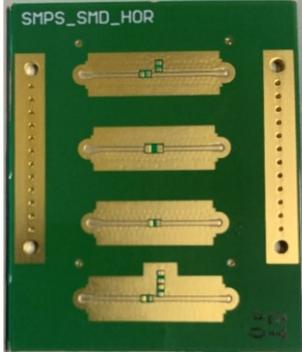

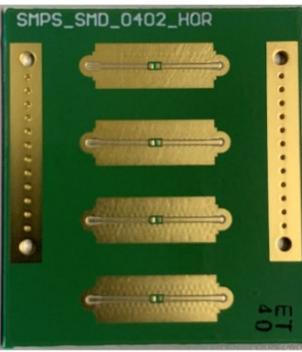

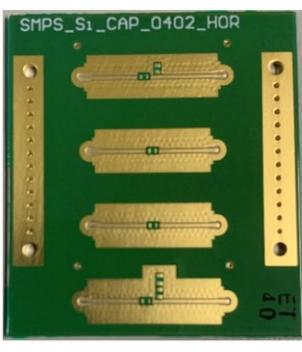

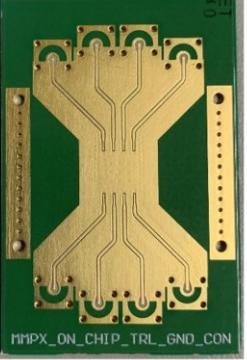

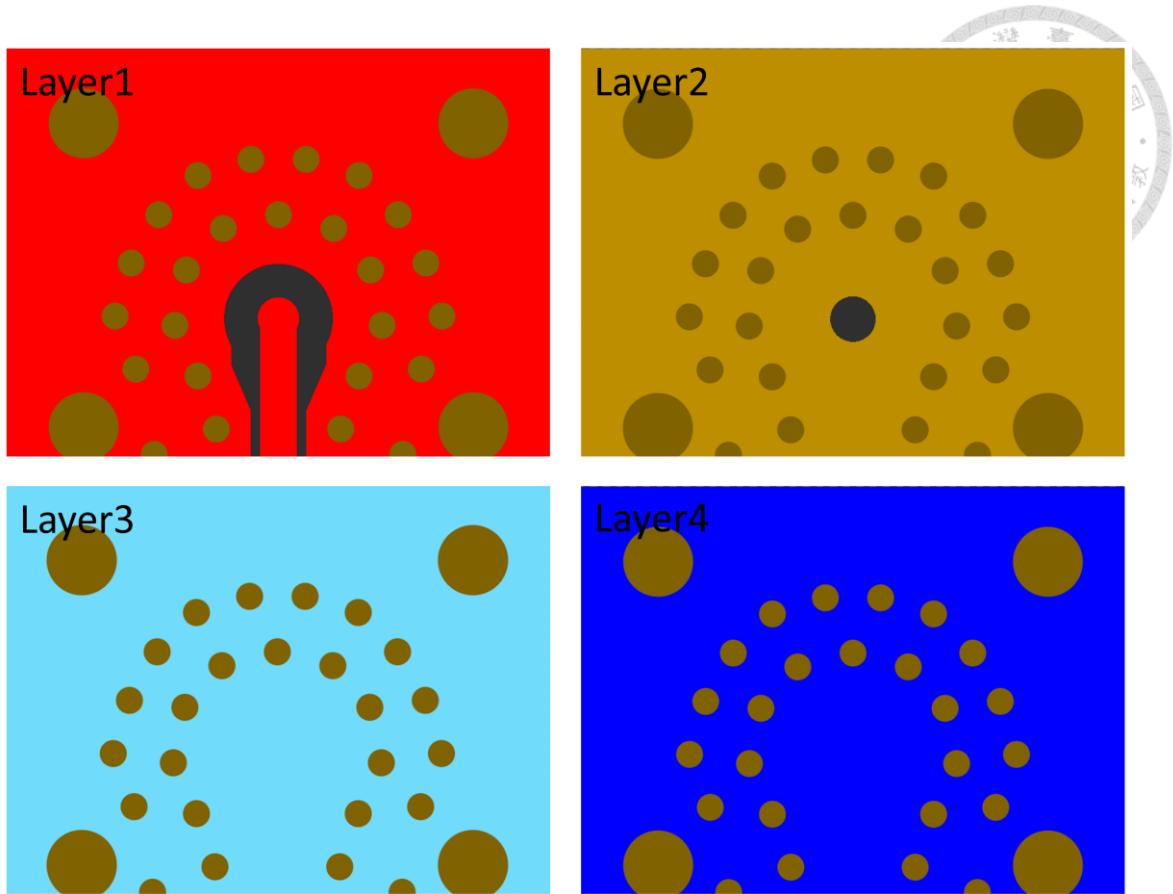

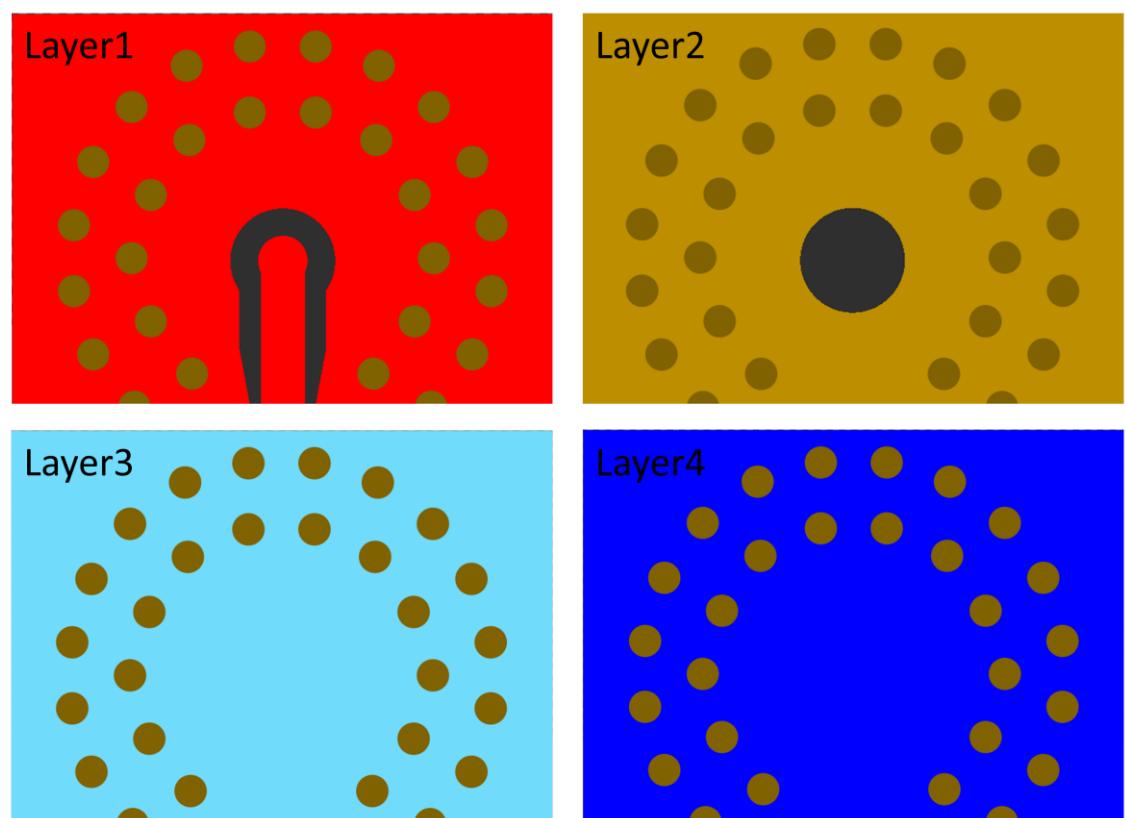

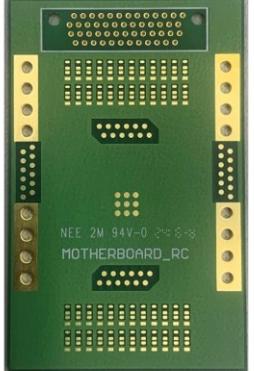

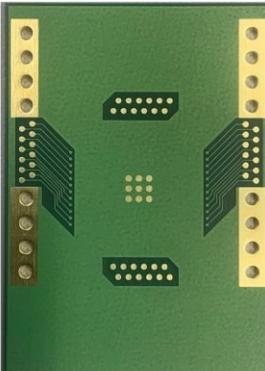

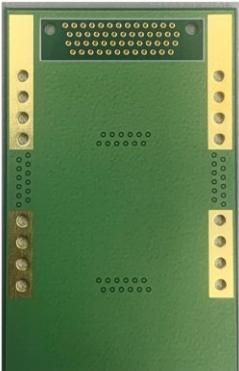

| Figure 4.1: PCB stacking arrangement of the first-phase testing boards. ....                                                                                              | 76 |

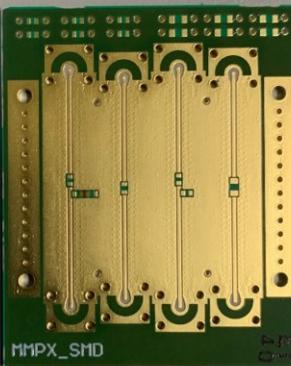

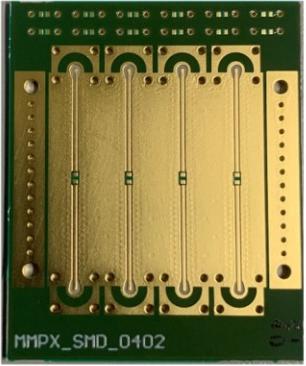

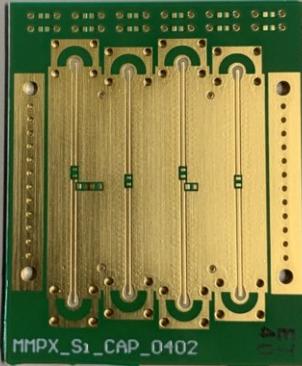

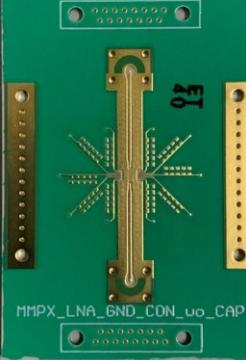

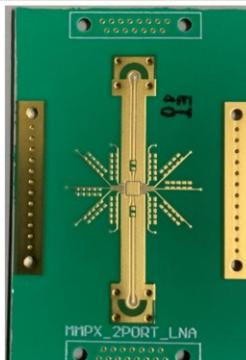

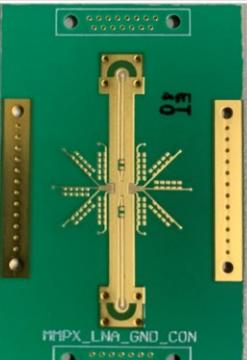

| Figure 4.2: Footprints of the four layers for MMPX connectors.....                                                                                                        | 85 |

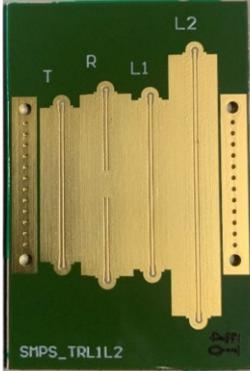

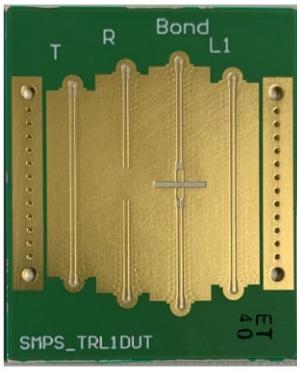

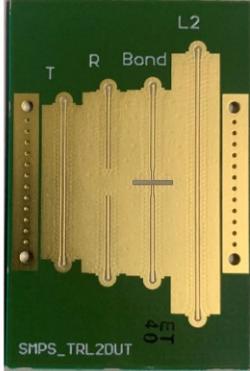

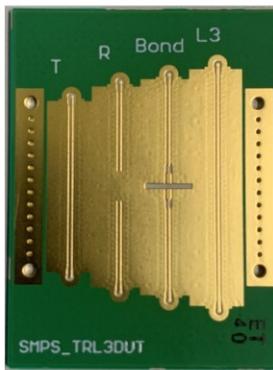

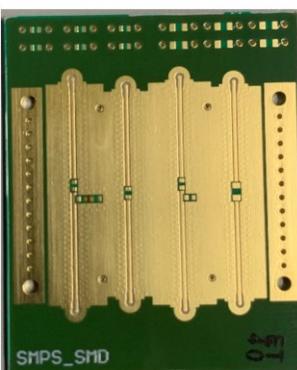

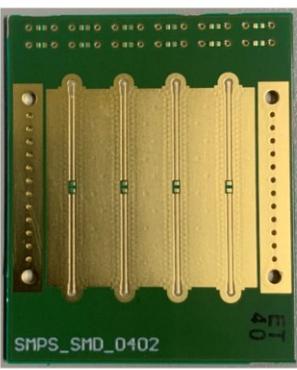

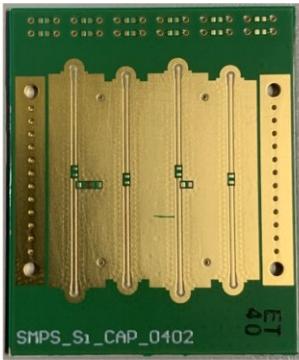

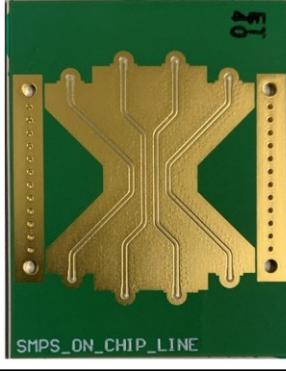

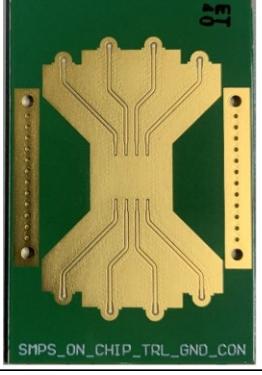

| Figure 4.3: Footprints of the four layers for SMPS connectors.....                                                                                                        | 85 |

| Figure 4.4: Simulated responses of CBCPW L1 standard with MMPX connectors.....                                                                                            | 86 |

| Figure 4.5: Simulated responses of CBCPW L1 standard with SMPS connectors.....                                                                                            | 87 |

|                                                                                                                                                                                                                                                                                                                                 |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.6: Simulated responses of MS L1 standard with SMPS connectors. ....                                                                                                                                                                                                                                                    | 87  |

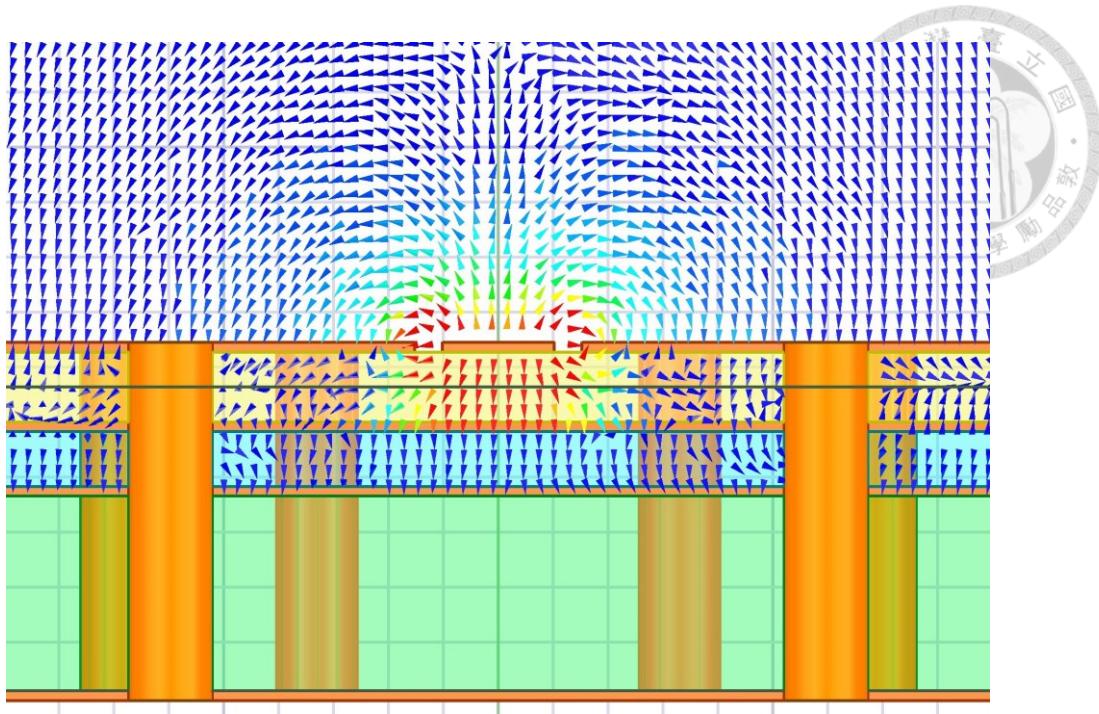

| Figure 4.7: The cross-sectional electric field vector of CBCPW transmission lines. ....                                                                                                                                                                                                                                         | 88  |

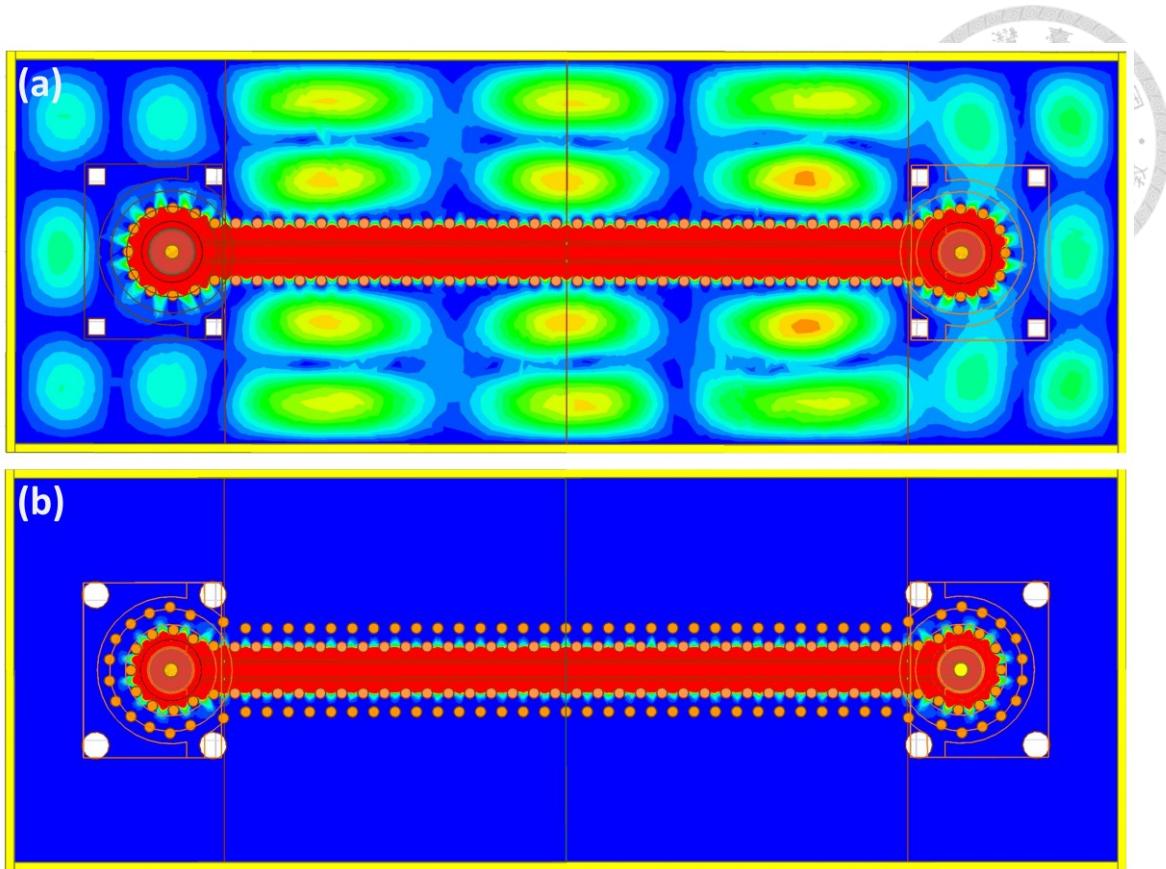

| Figure 4.8: The complex magnitude of the electric field in the RO3003 laminate. (a) With a single layer of vias. (b) With a double layer of vias. ....                                                                                                                                                                          | 89  |

| Figure 4.9: Simulated responses of ring resonator with SMPS connectors. ....                                                                                                                                                                                                                                                    | 90  |

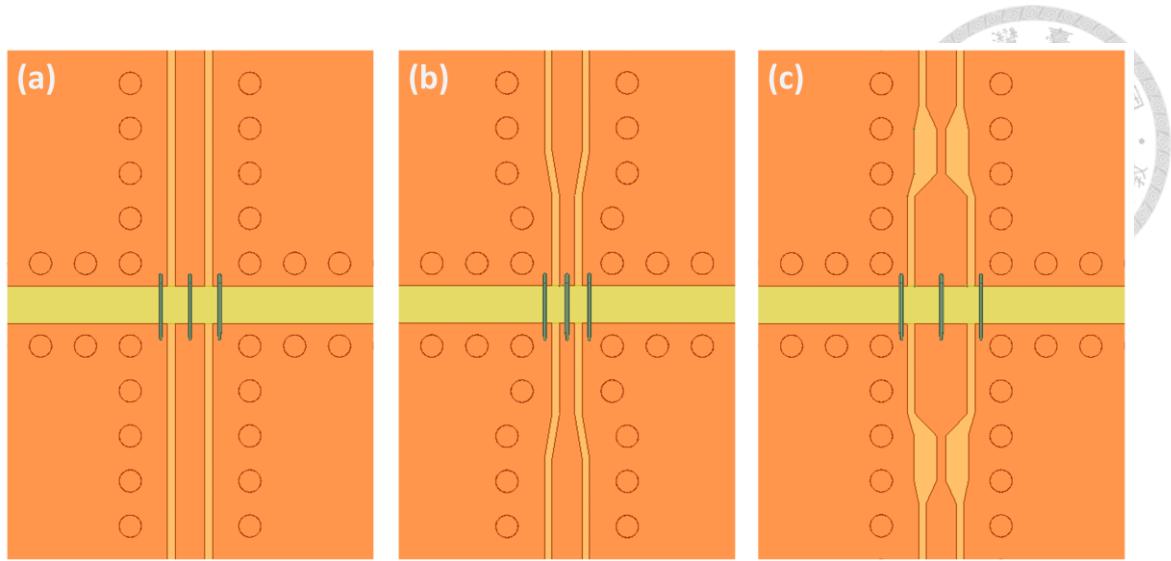

| Figure 4.10: Transmission-line-to-bond-wire transition structures under test. (a) Same structure extending CBCPW transmission lines. (b) Shrink-sized wire bonding pads. (c) Impedance-matching structure compensating the bond wire effect at high frequencies.                                                                | 91  |

| Figure 4.11: Simulated responses of the three different wire bonding structures. ....                                                                                                                                                                                                                                           | 92  |

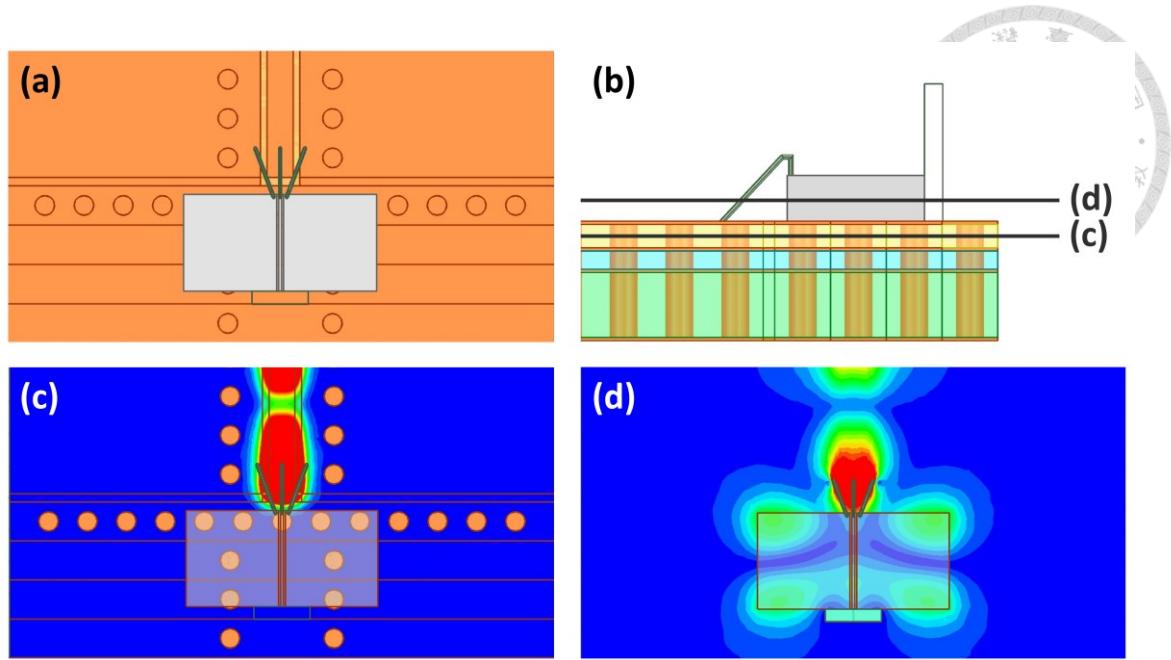

| Figure 4.12: EM simulation of the sample holder CBCPW transmission line bond wiring to a fictitious DUT, featuring an aluminum CPW line on a Si substrate. (a) Top view of the setup. (b) Side view of the setup. The lines indicate the slicing planes, on which the complex E fields at 40 GHz are shown in (c) and (d). .... | 93  |

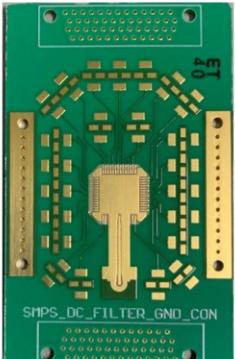

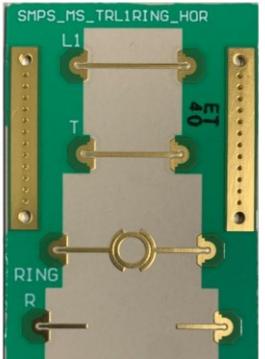

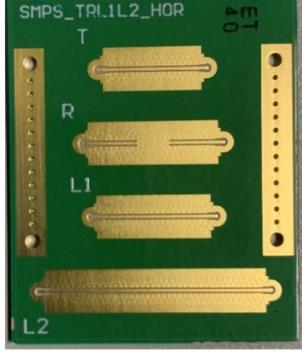

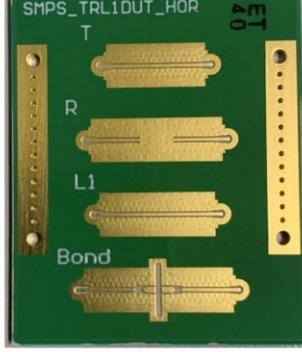

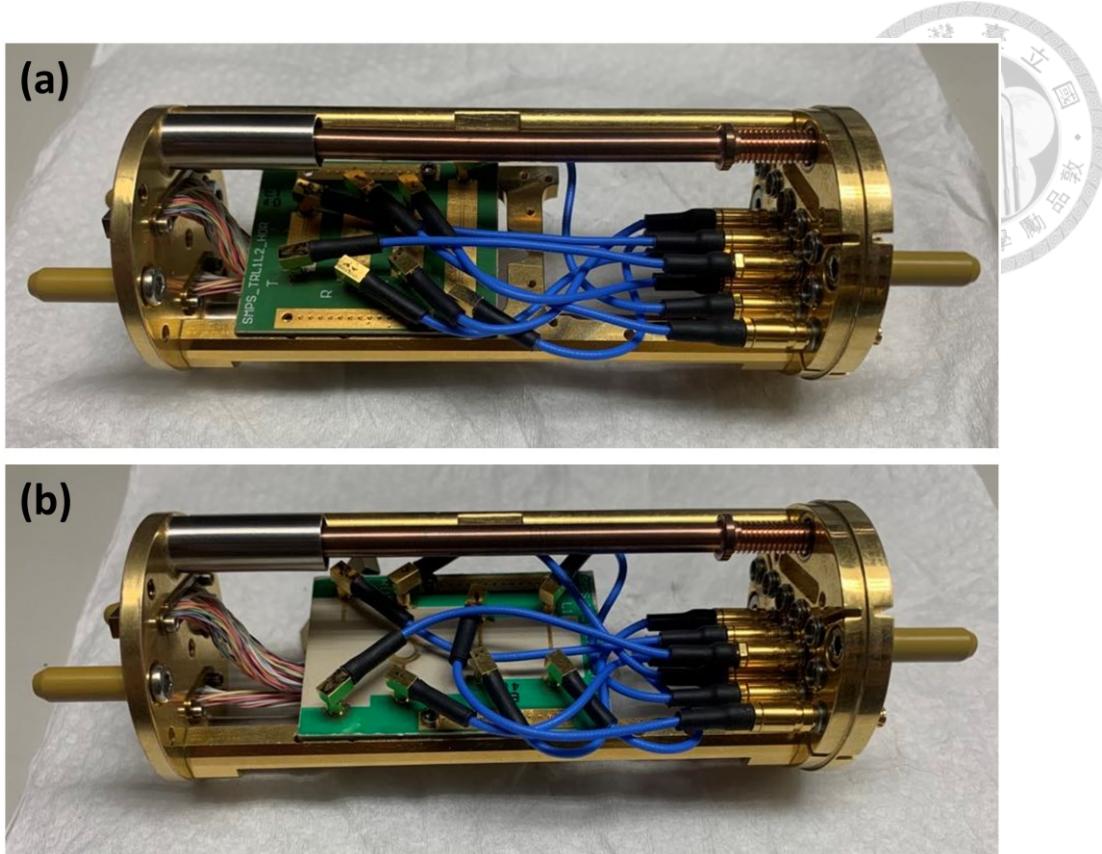

| Figure 4.13: Boards assembled within the sample puck. (a) SMPS_TRL1L2_HOR board. (b) SMPS_MS_TRL1RING_HOR board.....                                                                                                                                                                                                            | 94  |

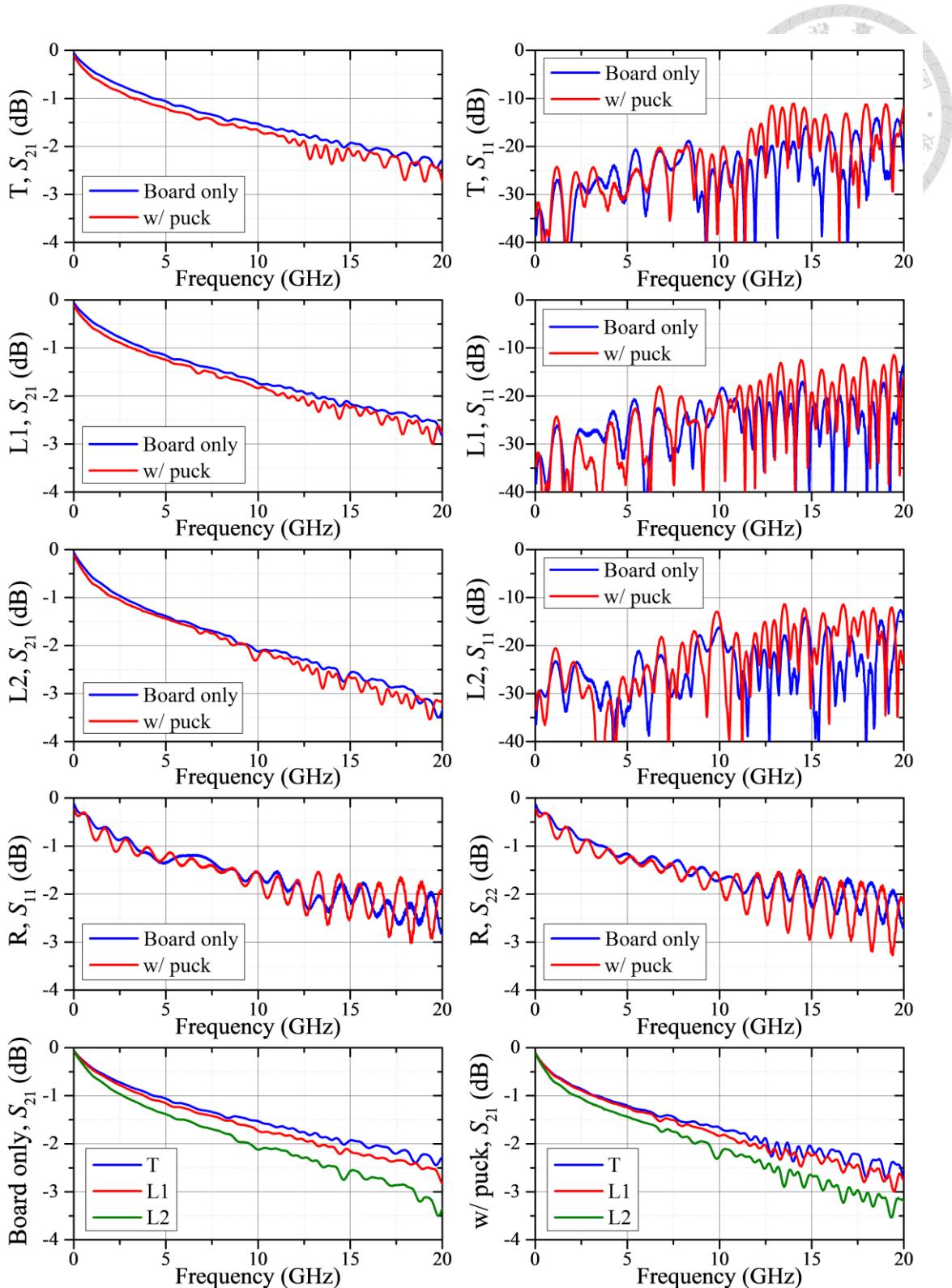

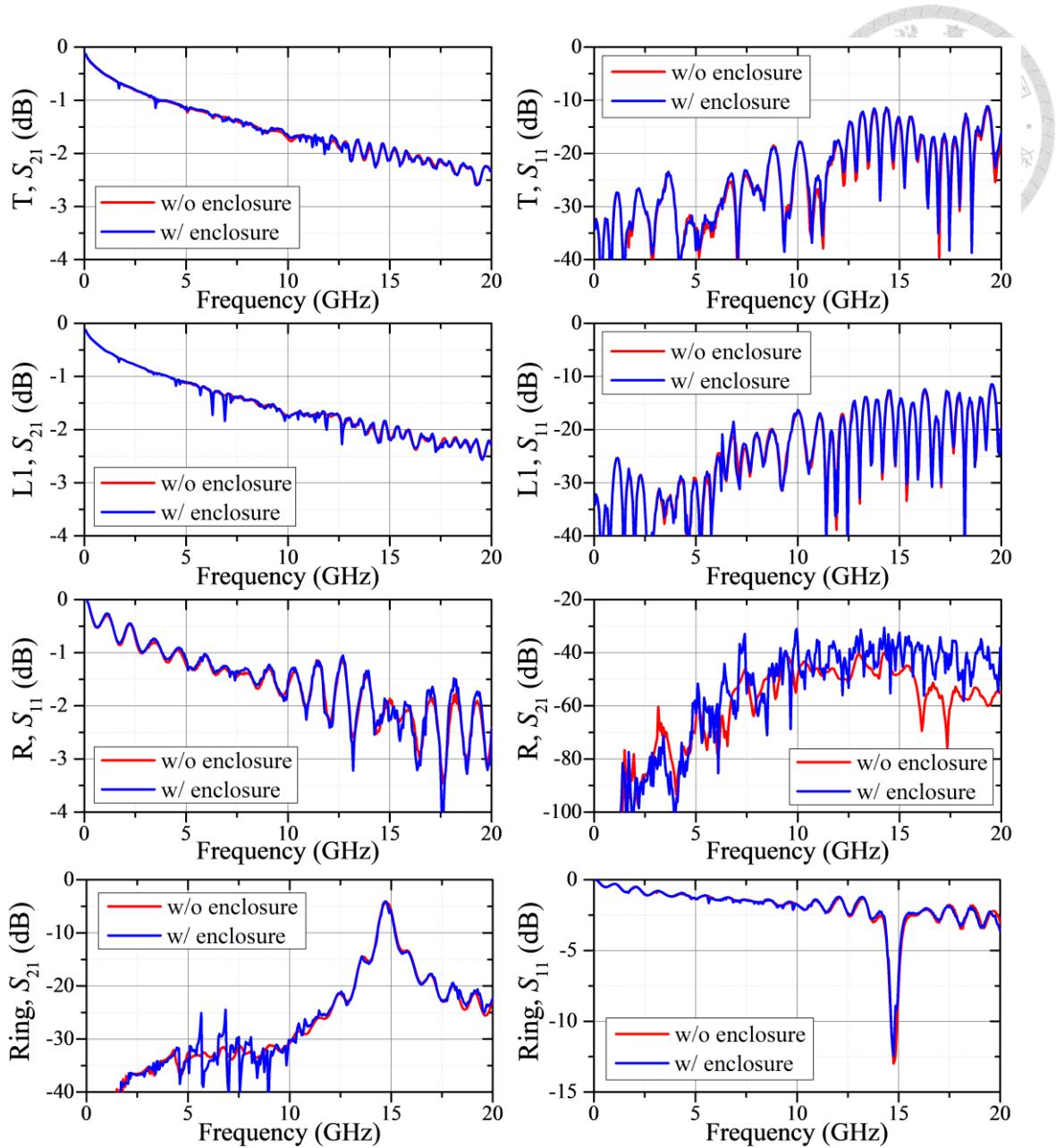

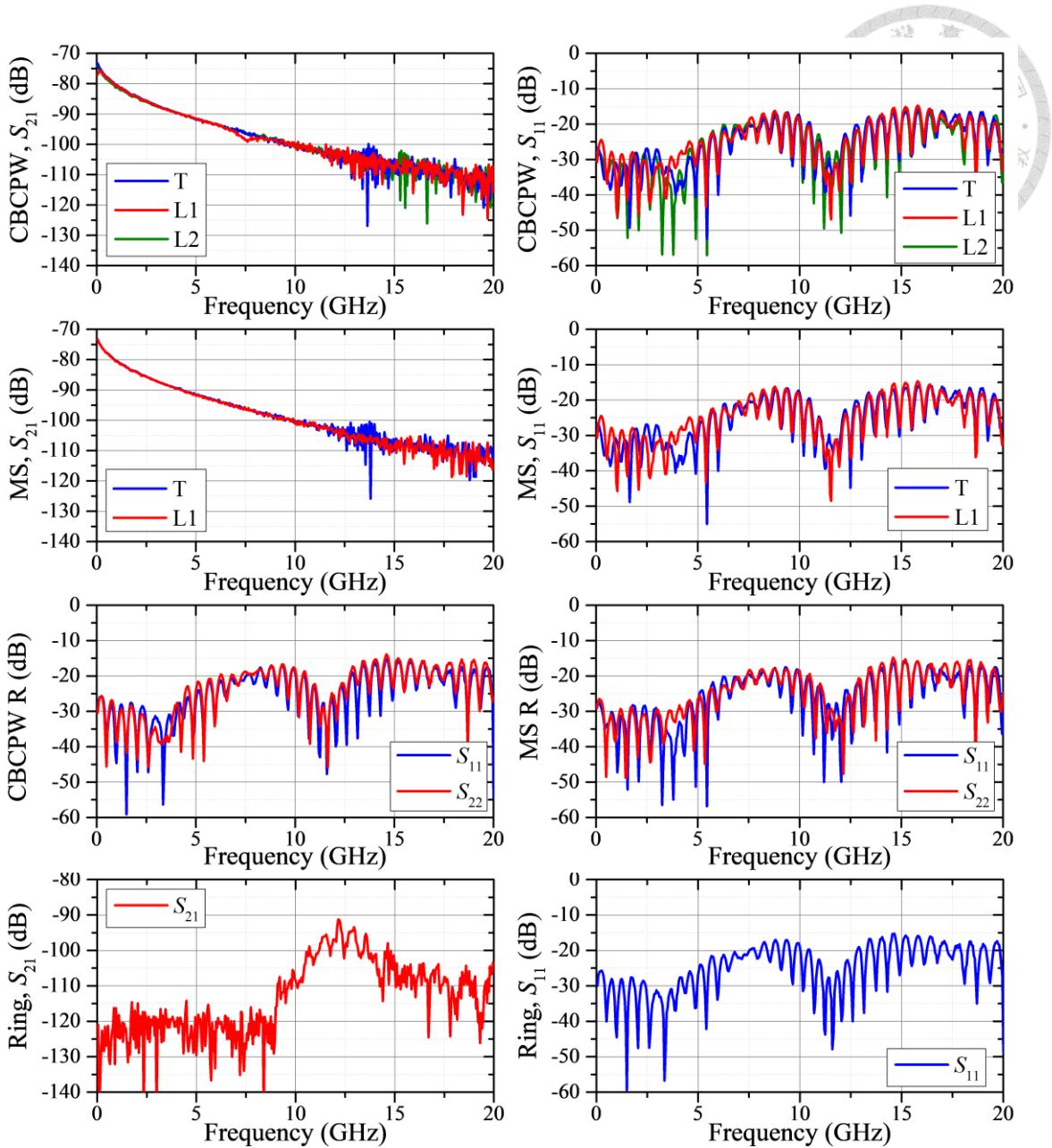

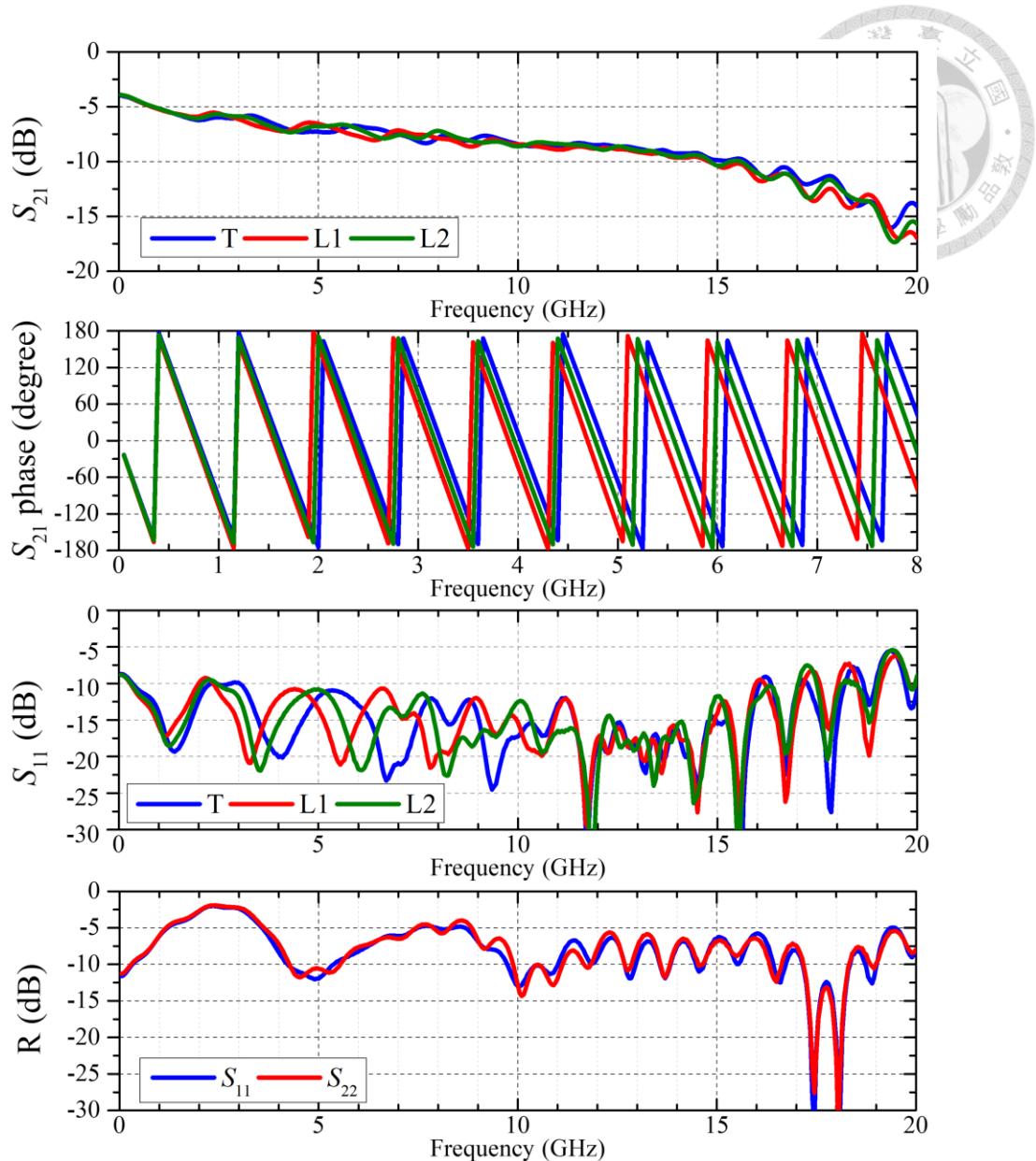

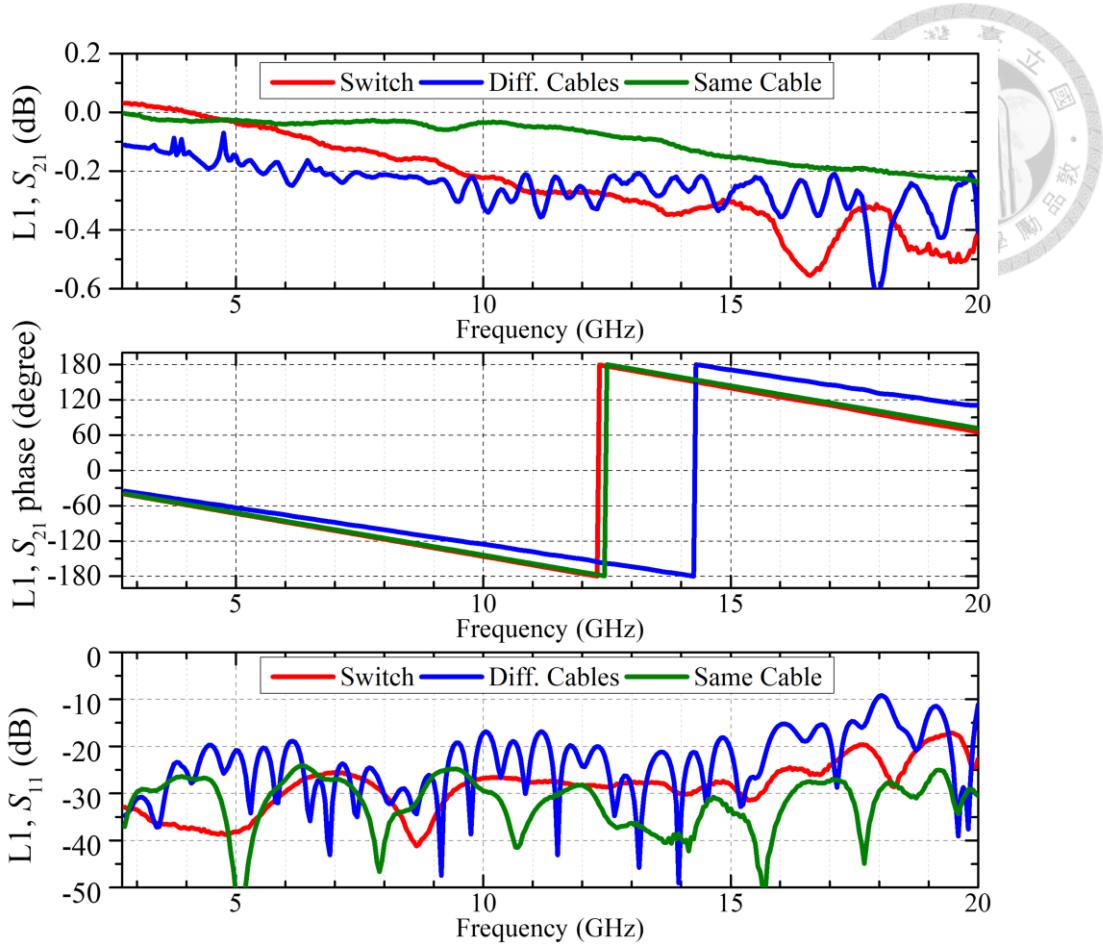

| Figure 4.14: Measured responses of the SMPS_TRL1L2_HOR board alone and within the sample puck (without enclosure). ....                                                                                                                                                                                                         | 96  |

| Figure 4.15: Measured responses of the SMPS_MS_TRL1RING_HOR board alone and within the sample puck (without enclosure). ....                                                                                                                                                                                                    | 97  |

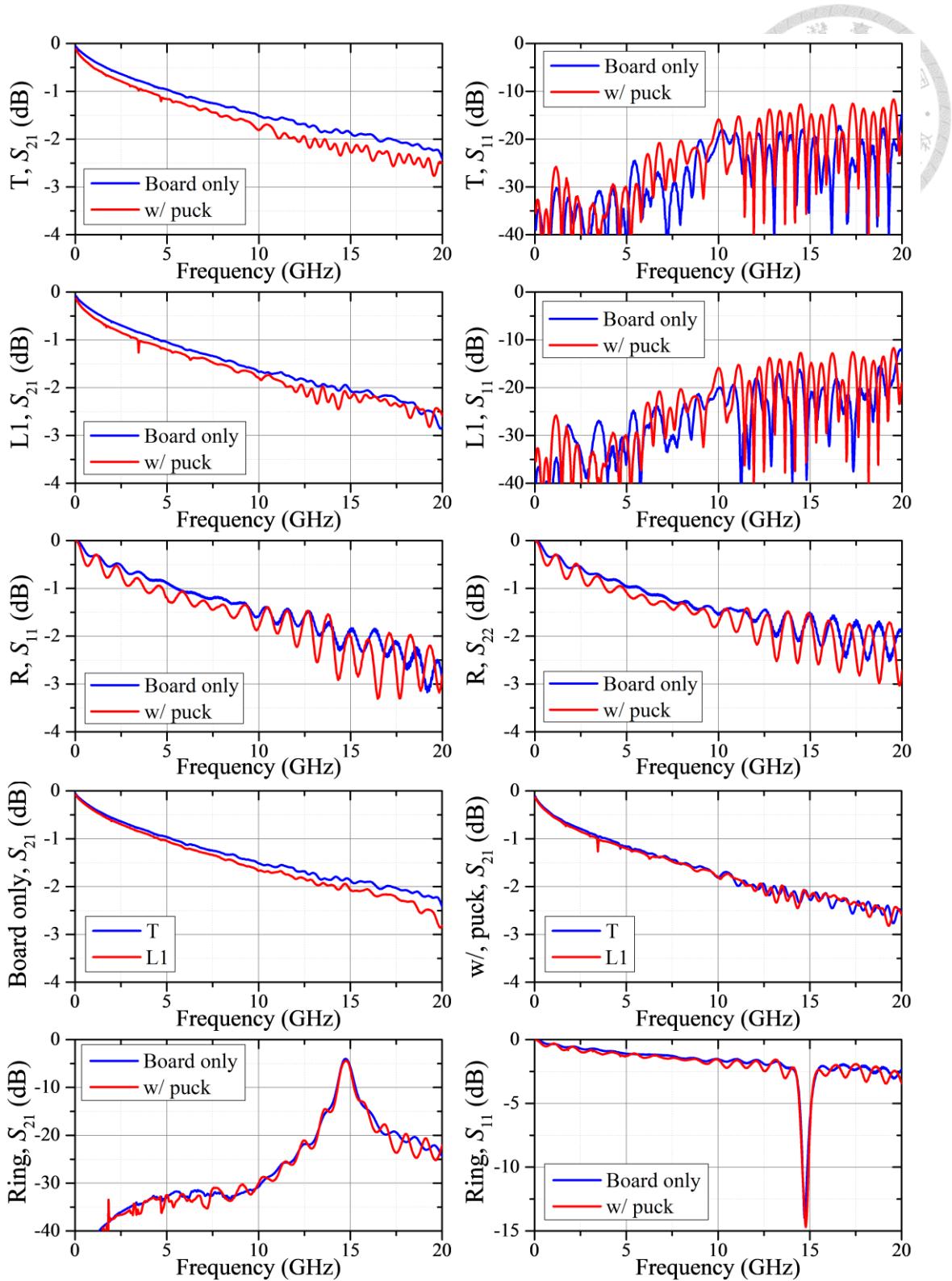

| Figure 4.16: Measured responses of the SMPS_TRL1L2_HOR board with and without the sample puck enclosure. ....                                                                                                                                                                                                                   | 99  |

| Figure 4.17: Measured responses of the SMPS_MS_TRL1RING_HOR board with and without the sample puck enclosure. ....                                                                                                                                                                                                              | 100 |

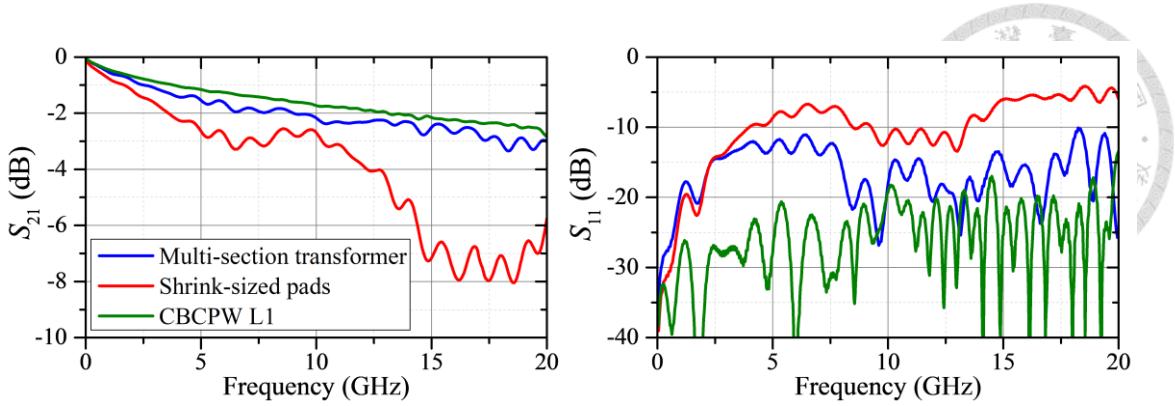

| Figure 4.18: Overall measured responses of transmission-line-to-bond-wire transition structures, compared with L1 responses. ....                                                                                                                                                                                               | 101 |

|                                                                                                                                                                                                                                                                                                                                                                                 |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

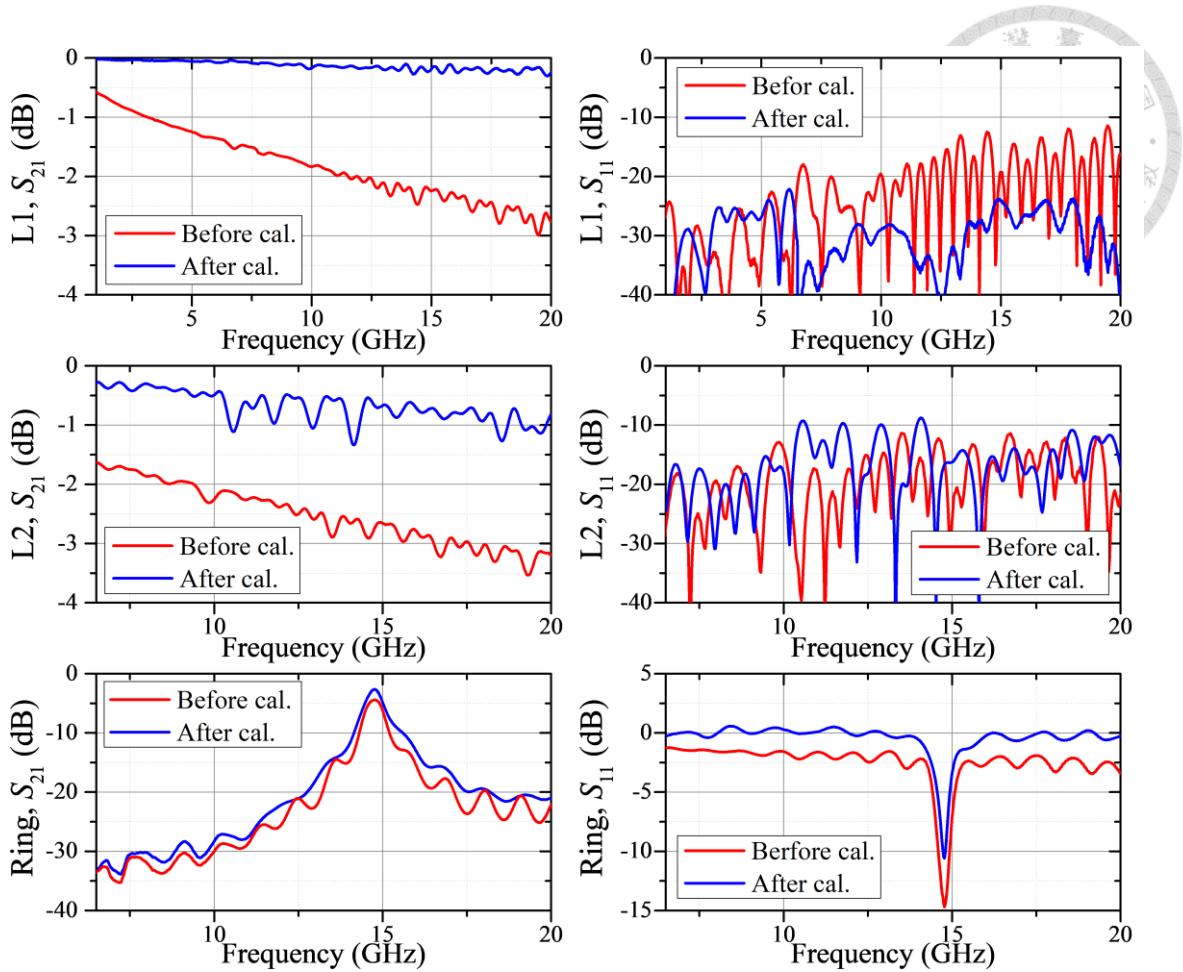

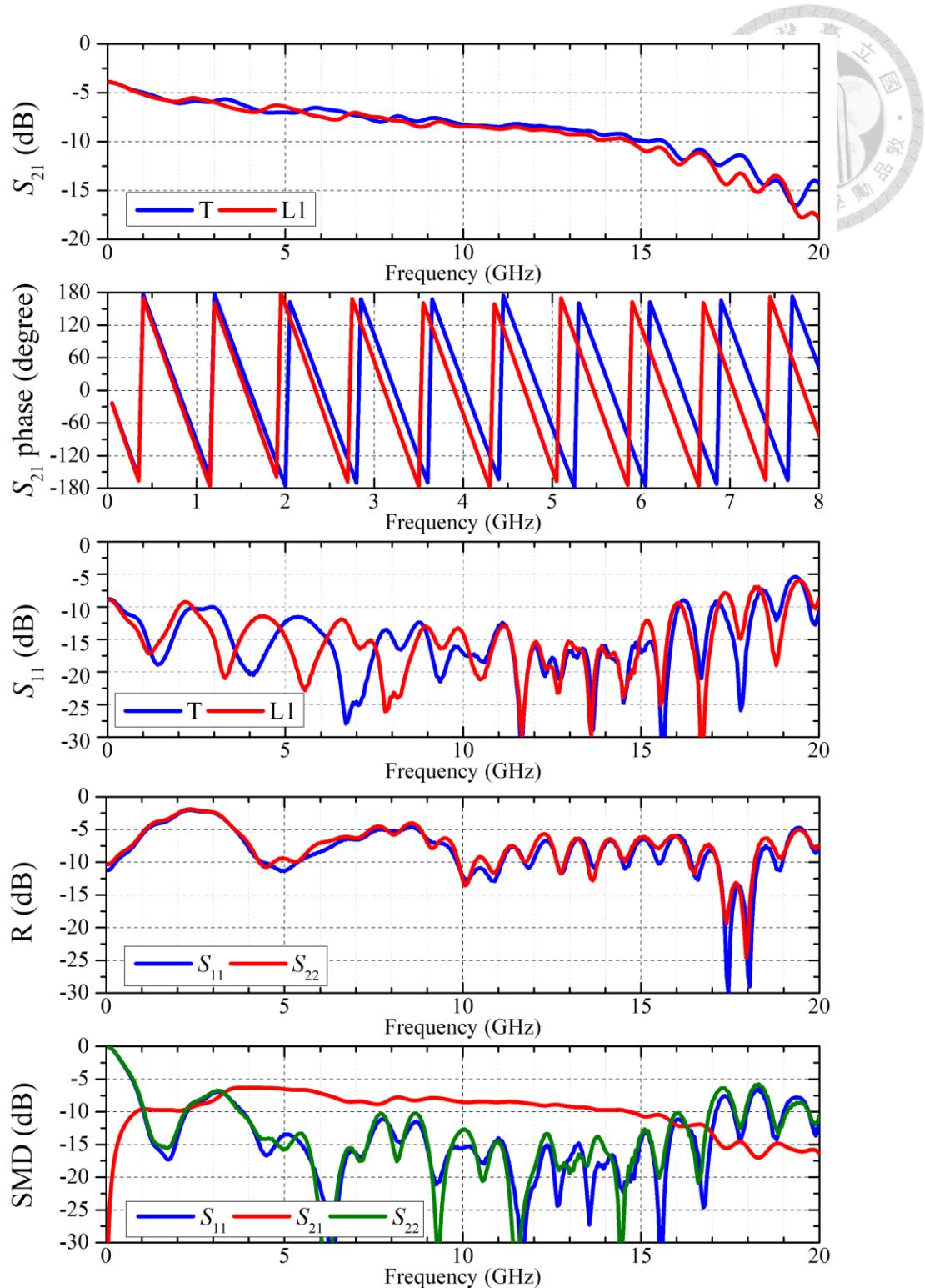

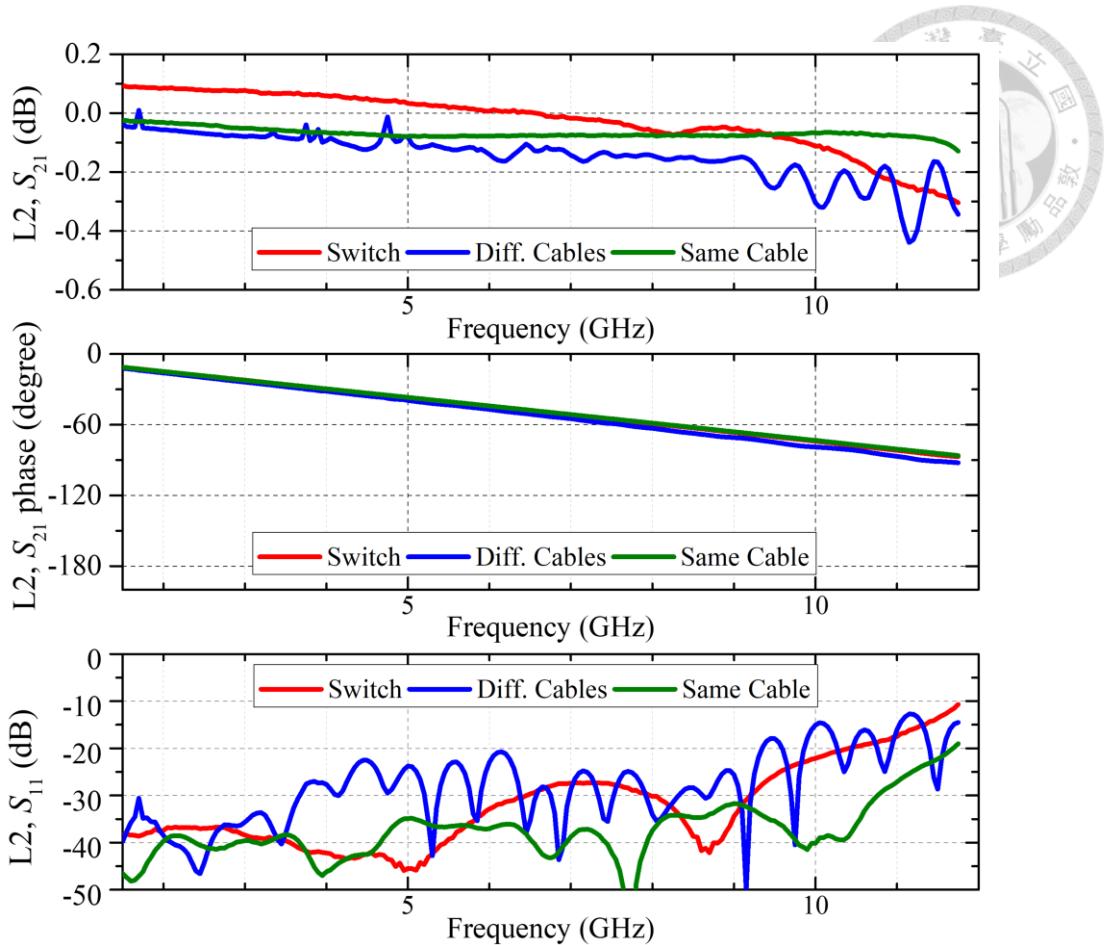

| Figure 4.19: Measured responses of L1, L2 and the ring resonator as DUTs within the sample puck, before and after the TRL calibration. ....                                                                                                                                                                                                                                     | 102 |

| Figure 4.20: Calibrated responses of L1, L2 and the ring resonator as DUTs, measured with the board alone and within the sample puck. ....                                                                                                                                                                                                                                      | 104 |

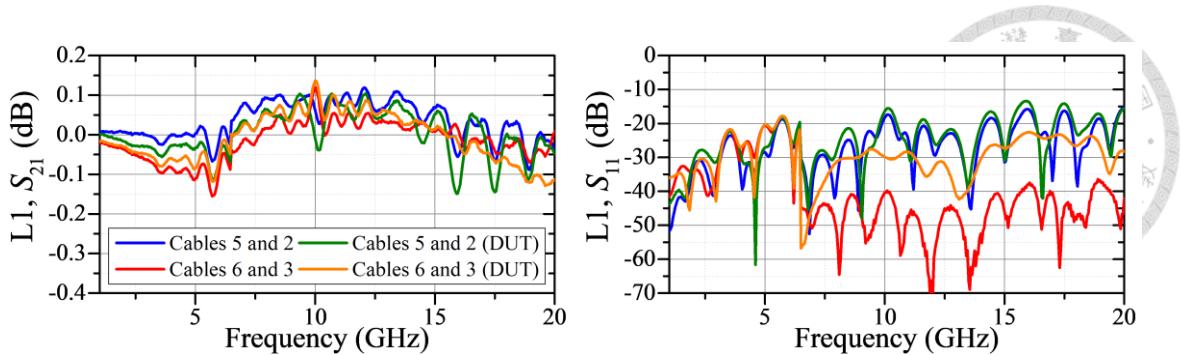

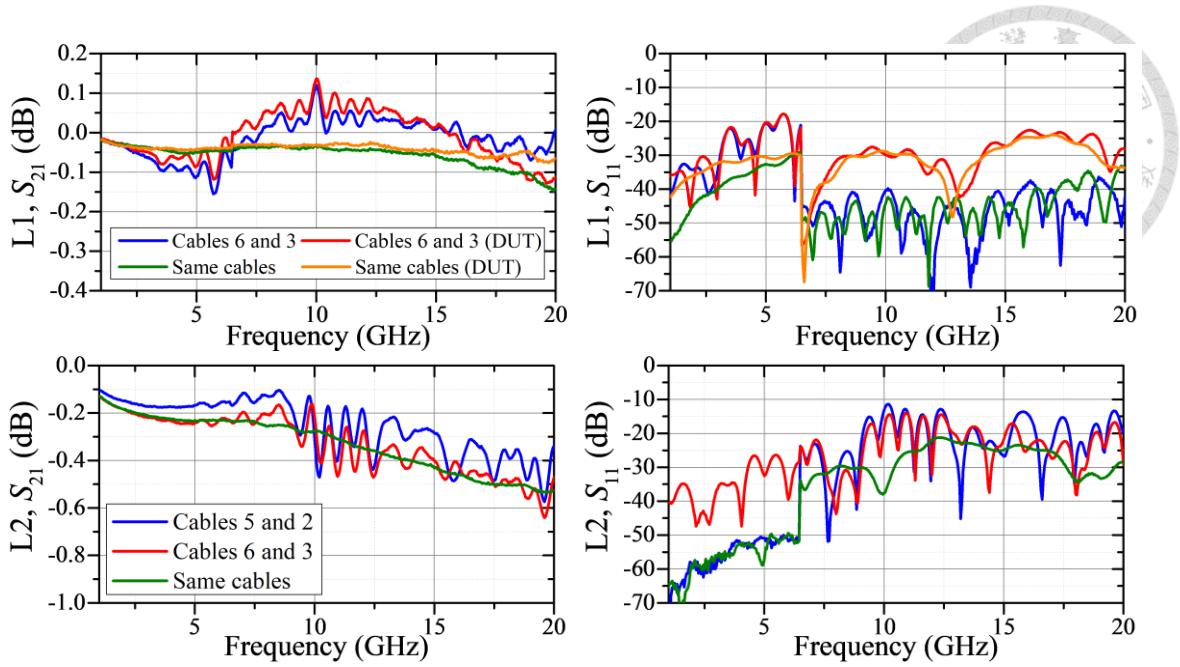

| Figure 4.21: Calibrated responses of L1 as DUT, measured using cables 5 and 2 or cables 6 and 3. The label ‘DUT’ indicates results measured for L1 on the SMPS_TRL1DUT_HOR board, while the unlabeled results are for L1 on the SMPS_TRL1L2_HOR board. ....                                                                                                                     | 105 |

| Figure 4.22: Calibrated responses of L1 and L2 as DUTs, measured using cables 6 and 3 or cables 5 and 2, also compared with the cases that using the same two blue cables throughout the calibration and measurement. The label ‘DUT’ indicates results measured for L1 on the SMPS_TRL1DUT_HOR board, while the unlabeled results are for L1 on the SMPS_TRL1L2_HOR board..... | 106 |

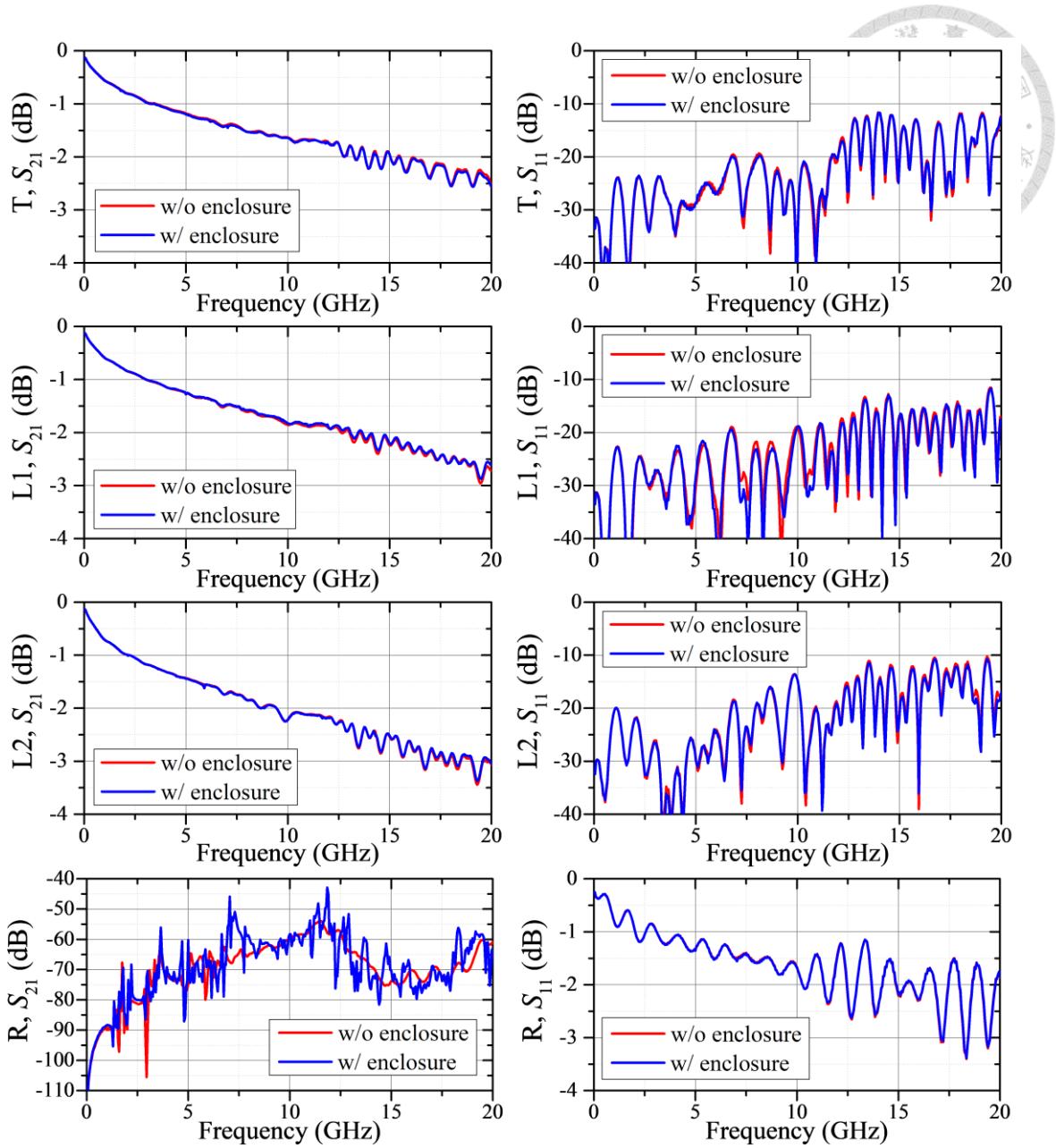

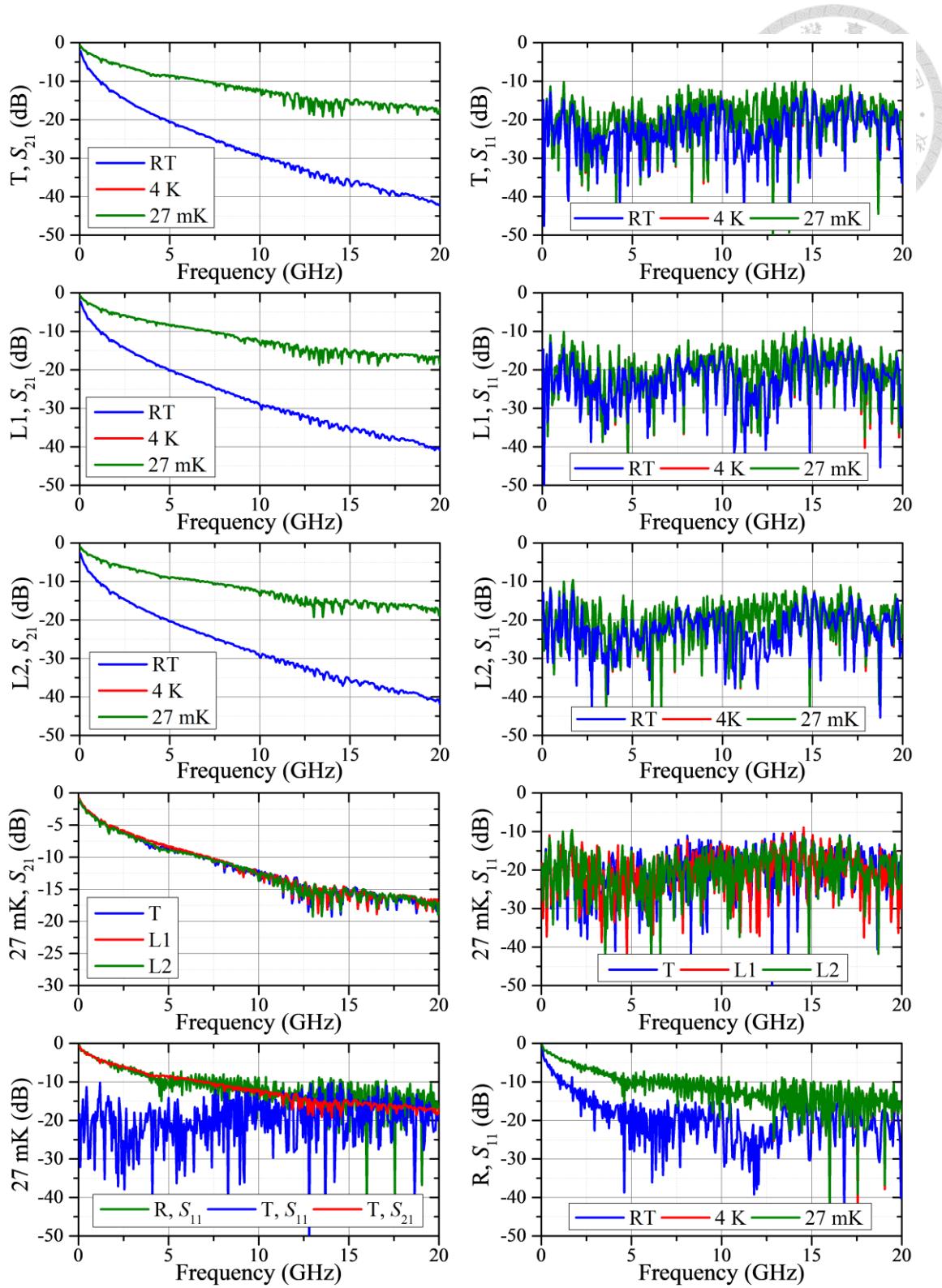

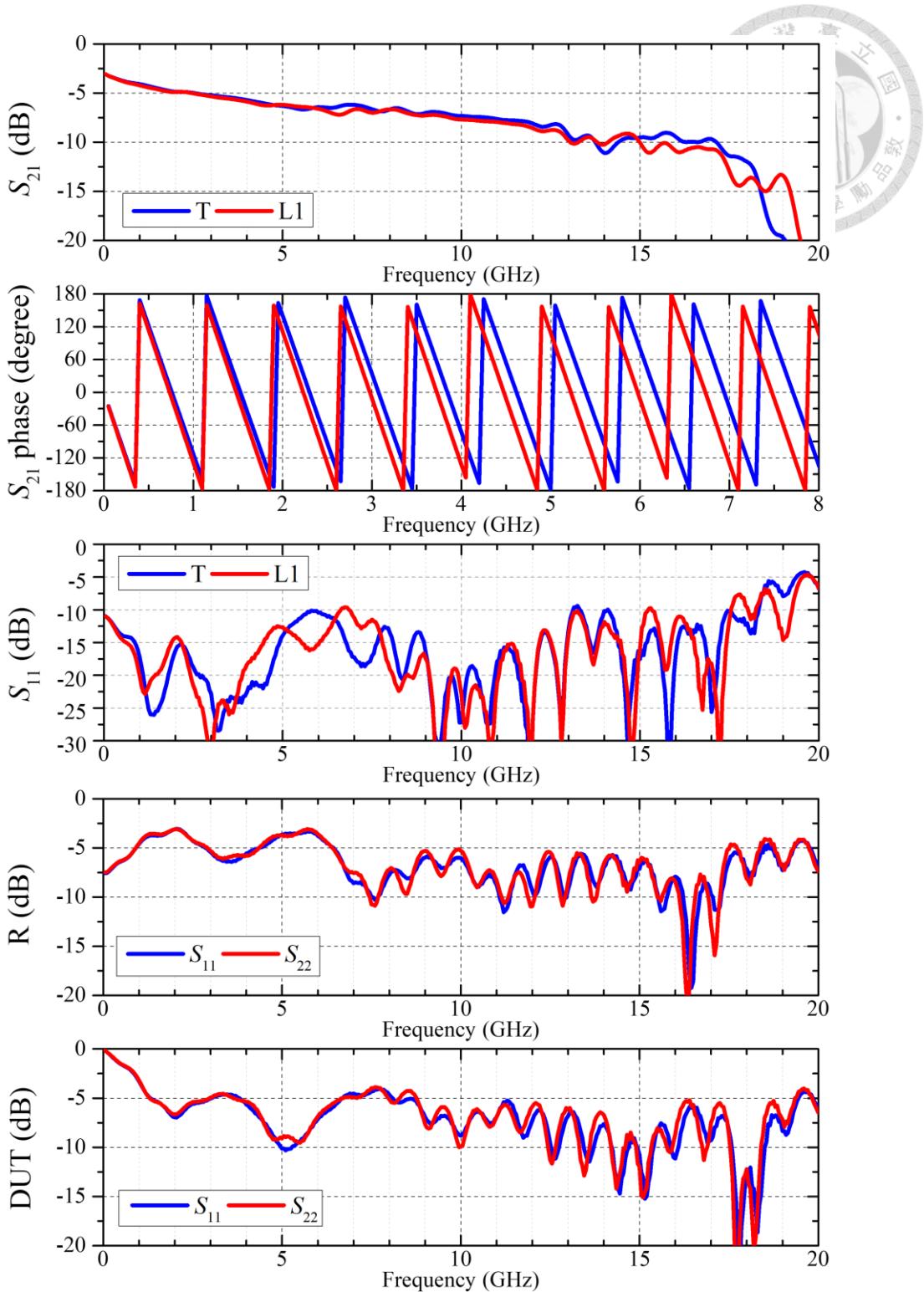

| Figure 4.23: Measured responses of the first-phase testing boards within the dilution fridge (with attenuators) at room temperature. ....                                                                                                                                                                                                                                       | 109 |

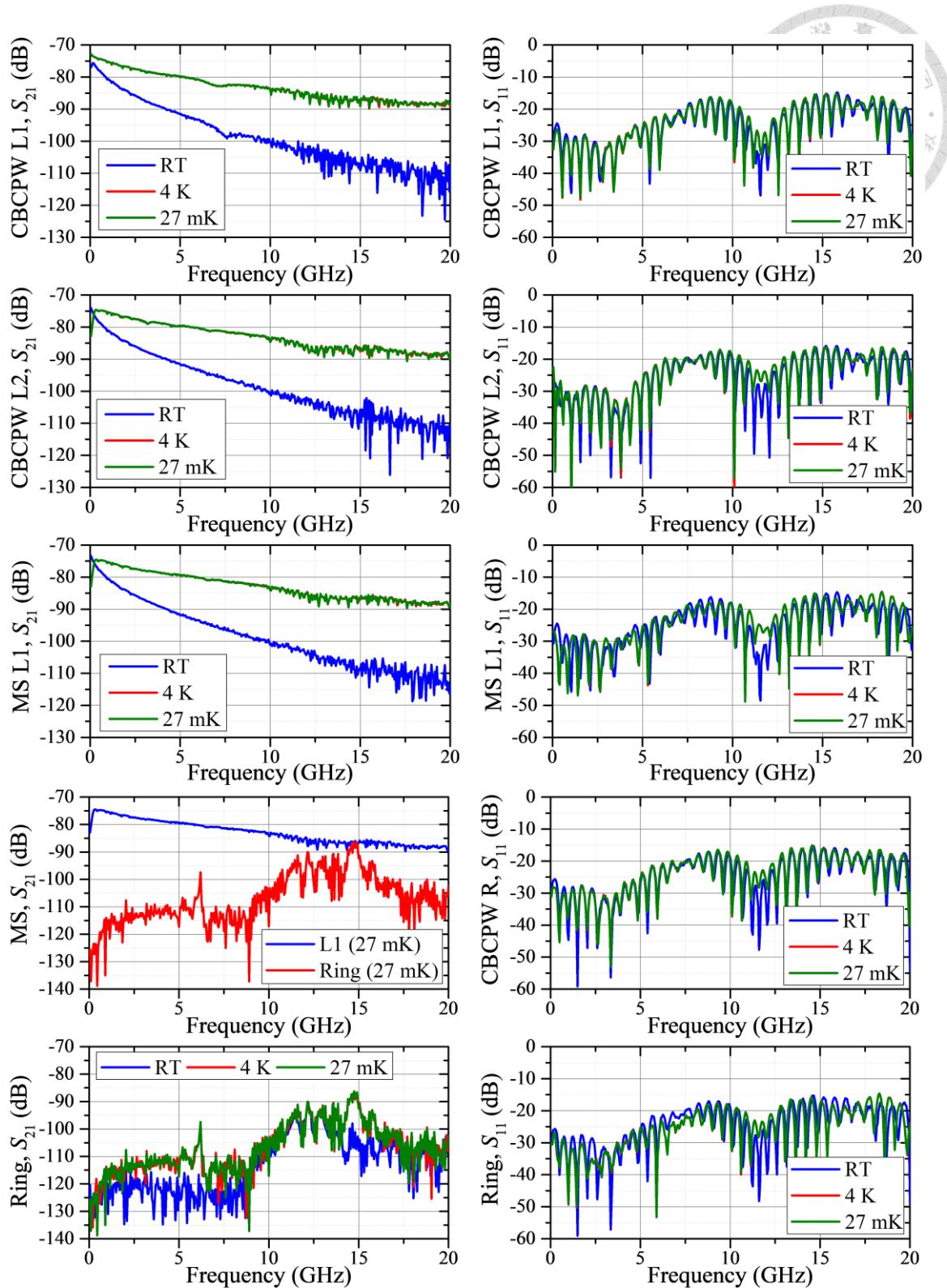

| Figure 4.24: Comparison of the measured responses of the first-phase testing boards within the dilution fridge (with attenuators) at various temperatures. ....                                                                                                                                                                                                                 | 111 |

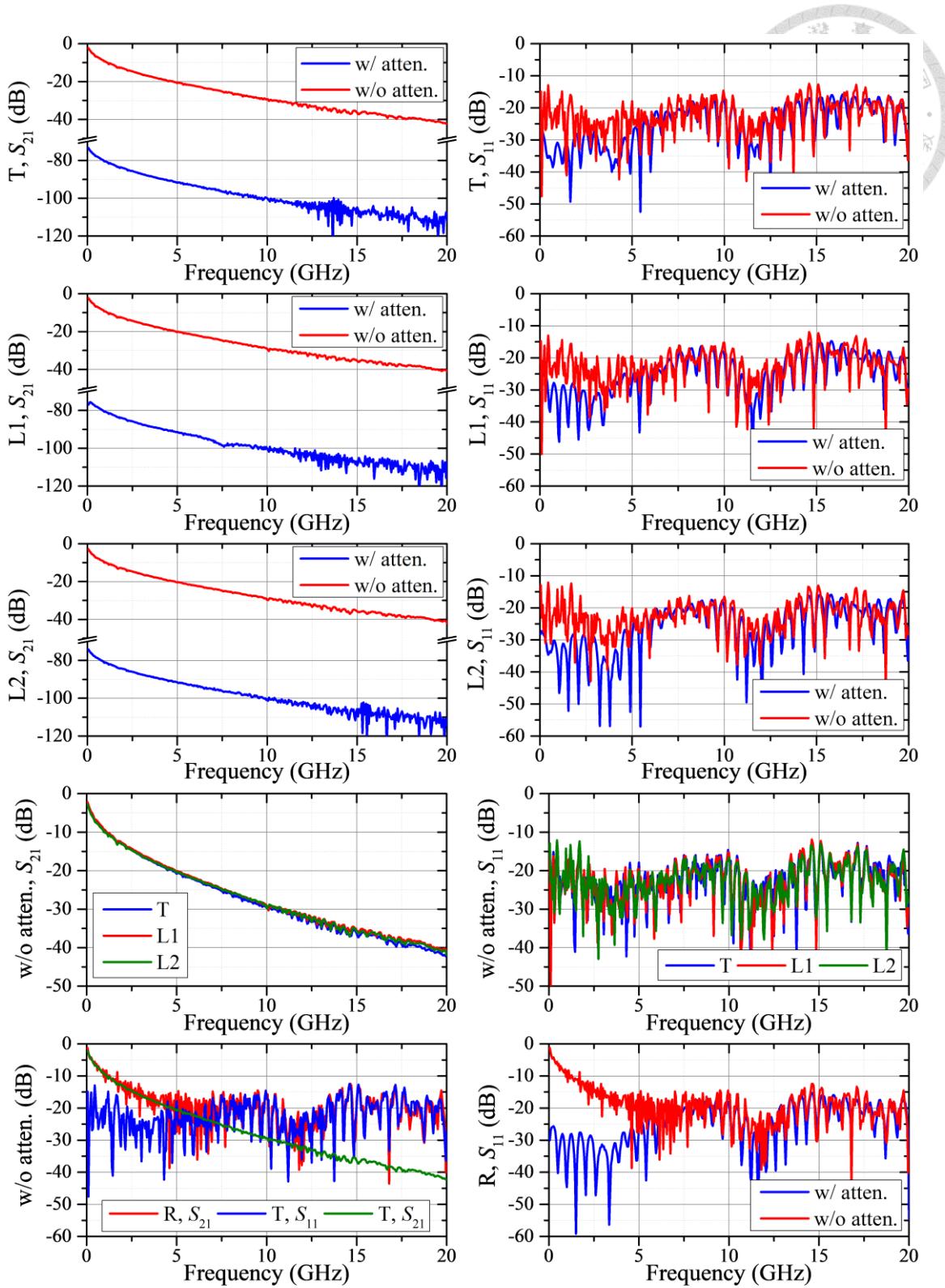

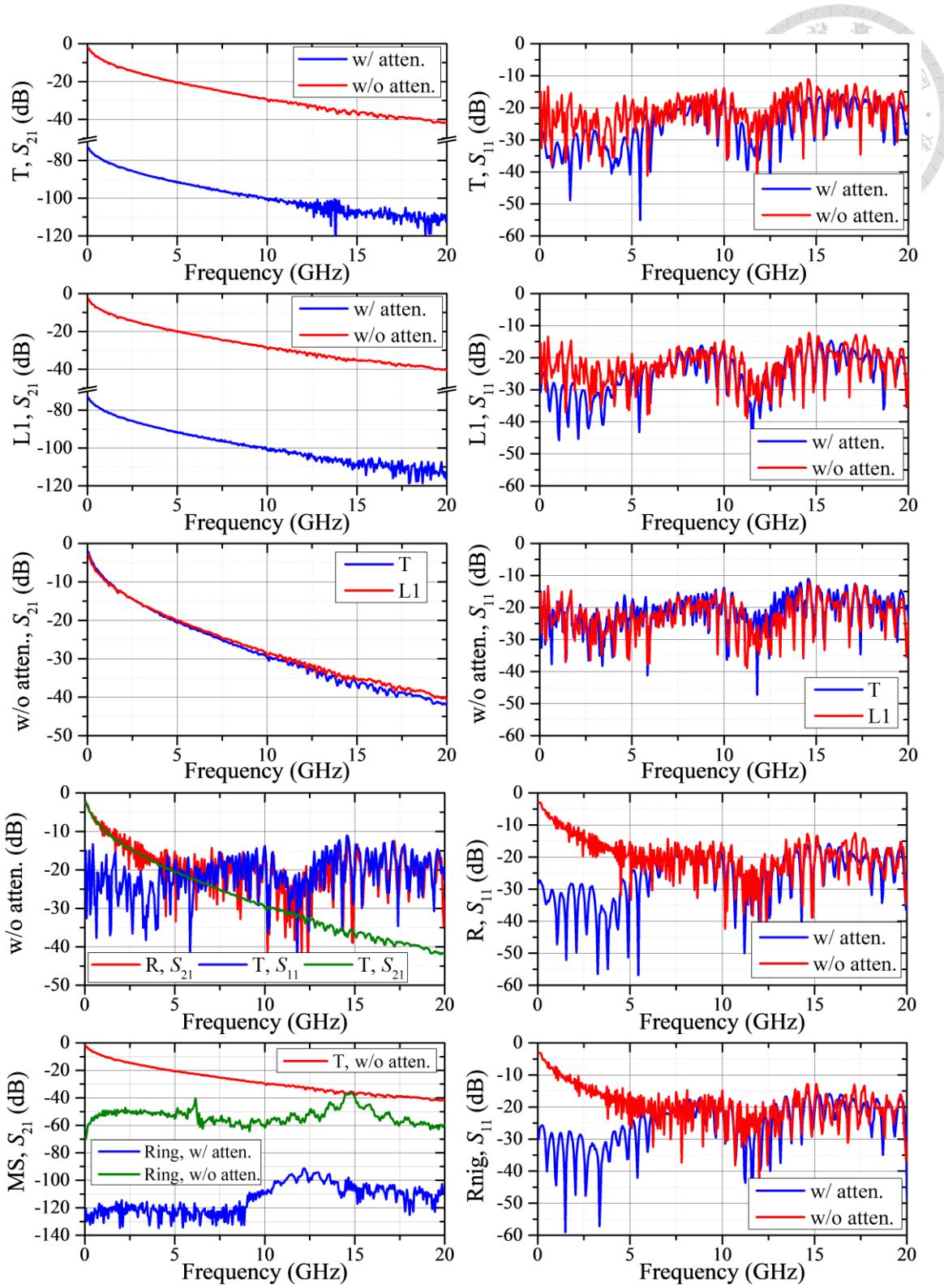

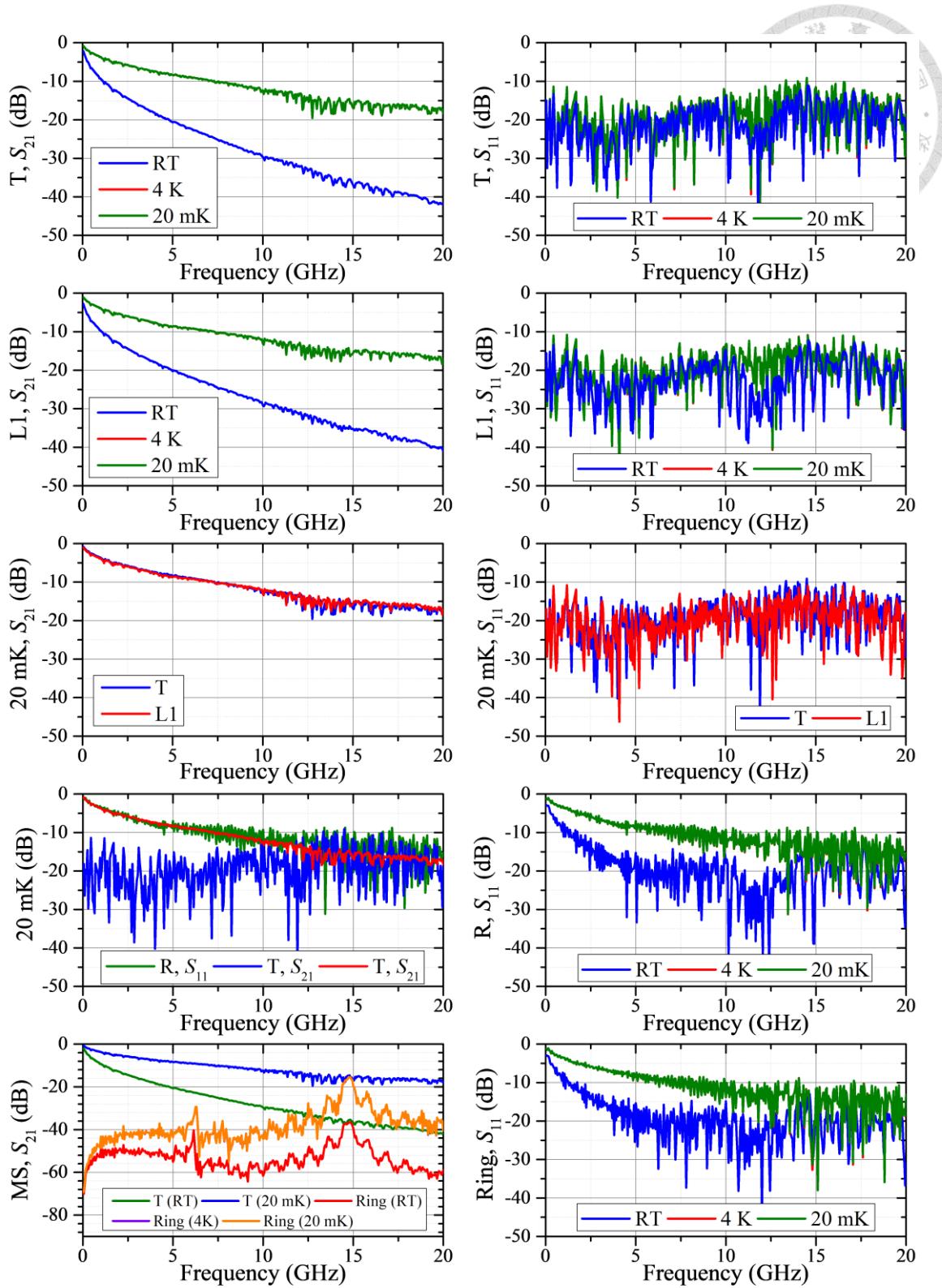

| Figure 4.25: Measured responses of the SMPS_TRL1L2_HOR board within the dilution fridge, with and without attenuators, at room temperature. ....                                                                                                                                                                                                                                | 113 |

| Figure 4.26: Measured responses of the SMPS_MS_TRL1RING_HOR board within the dilution fridge, with and without attenuators, at room temperature. ....                                                                                                                                                                                                                           | 115 |

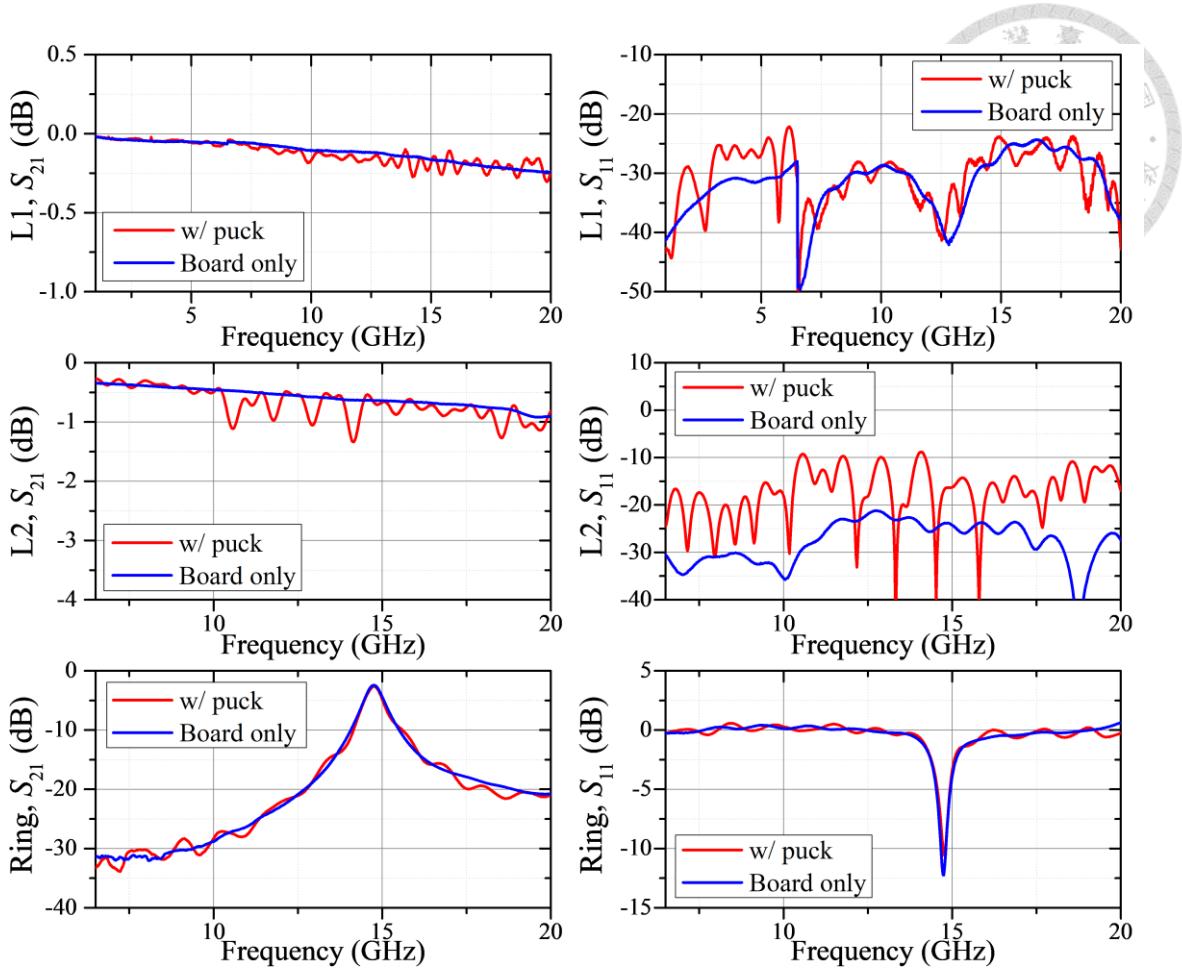

| Figure 4.27: Measured responses of the SMPS_TRL1L2_HOR board within the dilution fridge (without attenuators) at various temperatures. ....                                                                                                                                                                                                                                     | 116 |

| Figure 4.28: Measured responses of the SMPS_MS_TRL1RING_HOR board within the dilution fridge (without attenuators) at various temperatures. ....                                                                                                                                                                                                                                | 117 |

|                                                                                                                                                                        |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.29: Measured responses of the first-phase testing boards within the dilution<br>fridge, with and without attenuators, at a temperature of 27 mK.....          | 118 |

| Figure 4.30: Calibrated responses of L1 and L2 on the SMPS_TRL1L2_HOR board as<br>DUTs within the dilution fridge without attenuators, at a temperature of 27 mK. .... | 120 |

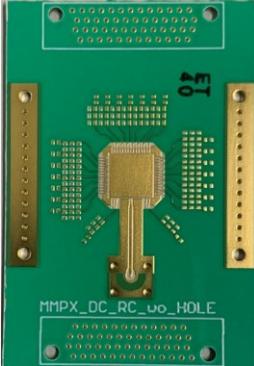

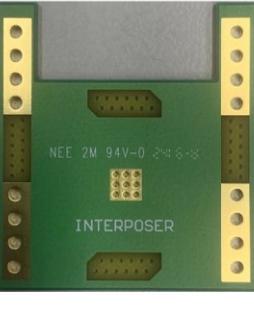

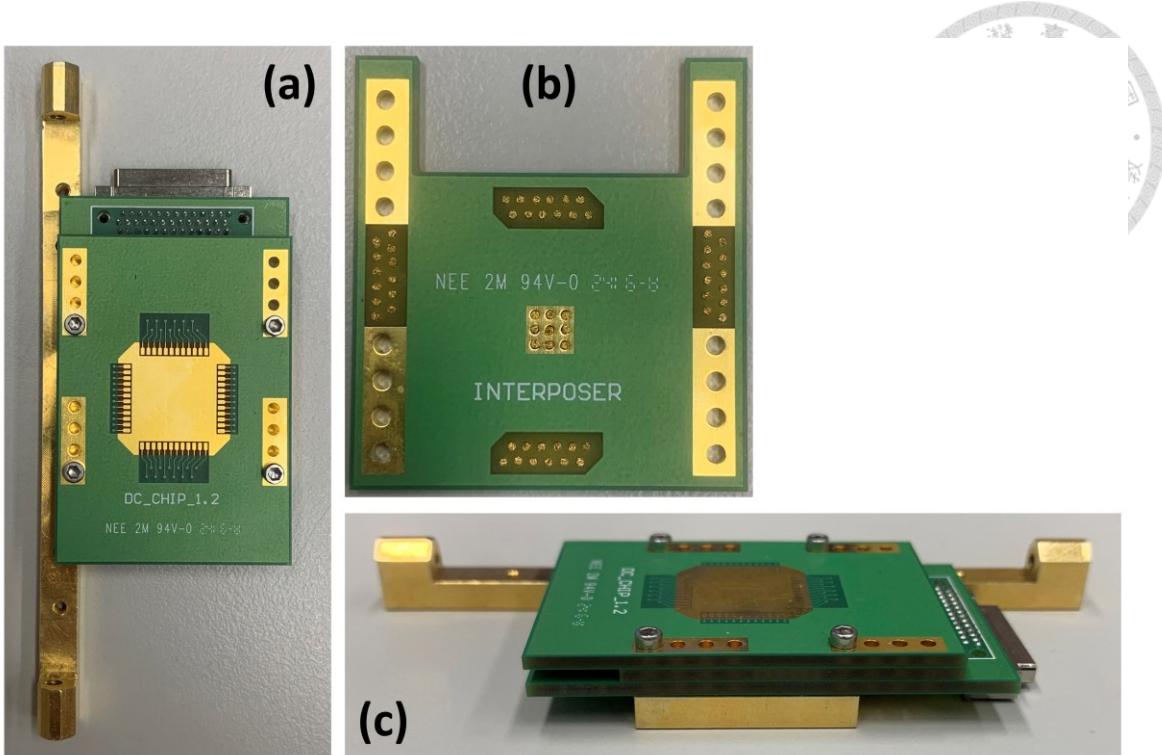

| Figure 5.1: Multi-board sample holder after assembling. (b) Interposer filled with the<br>Fuzz Buttons for interconnections.....                                       | 127 |

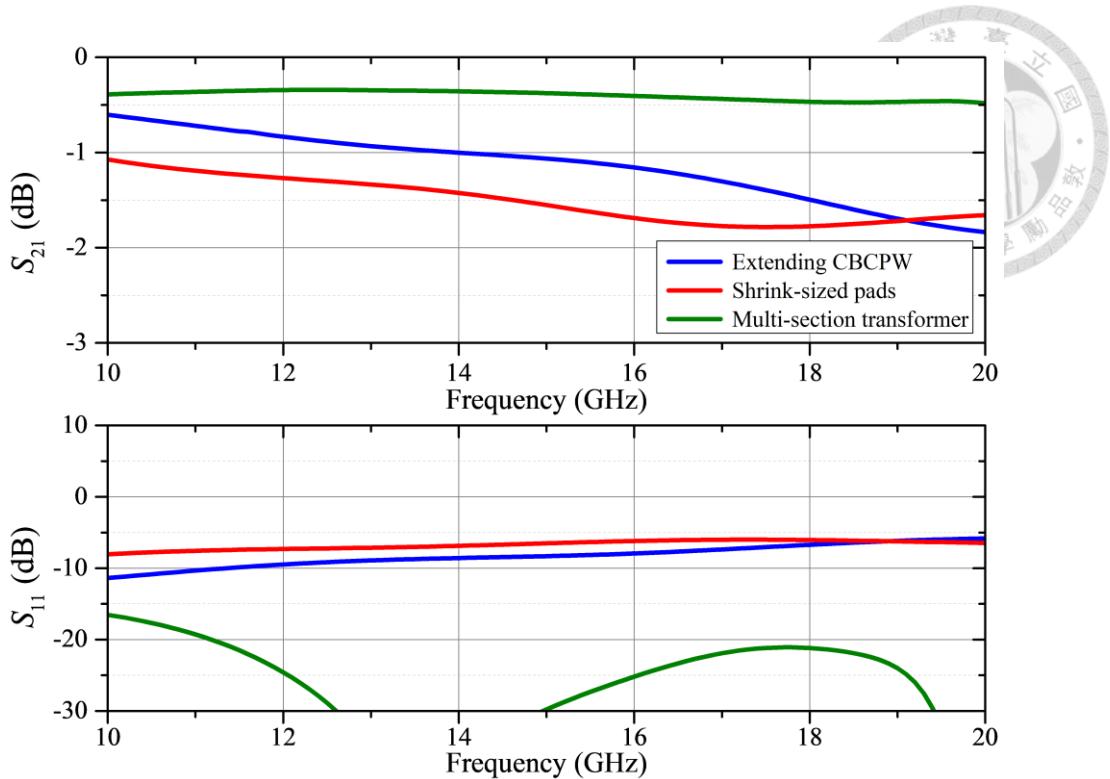

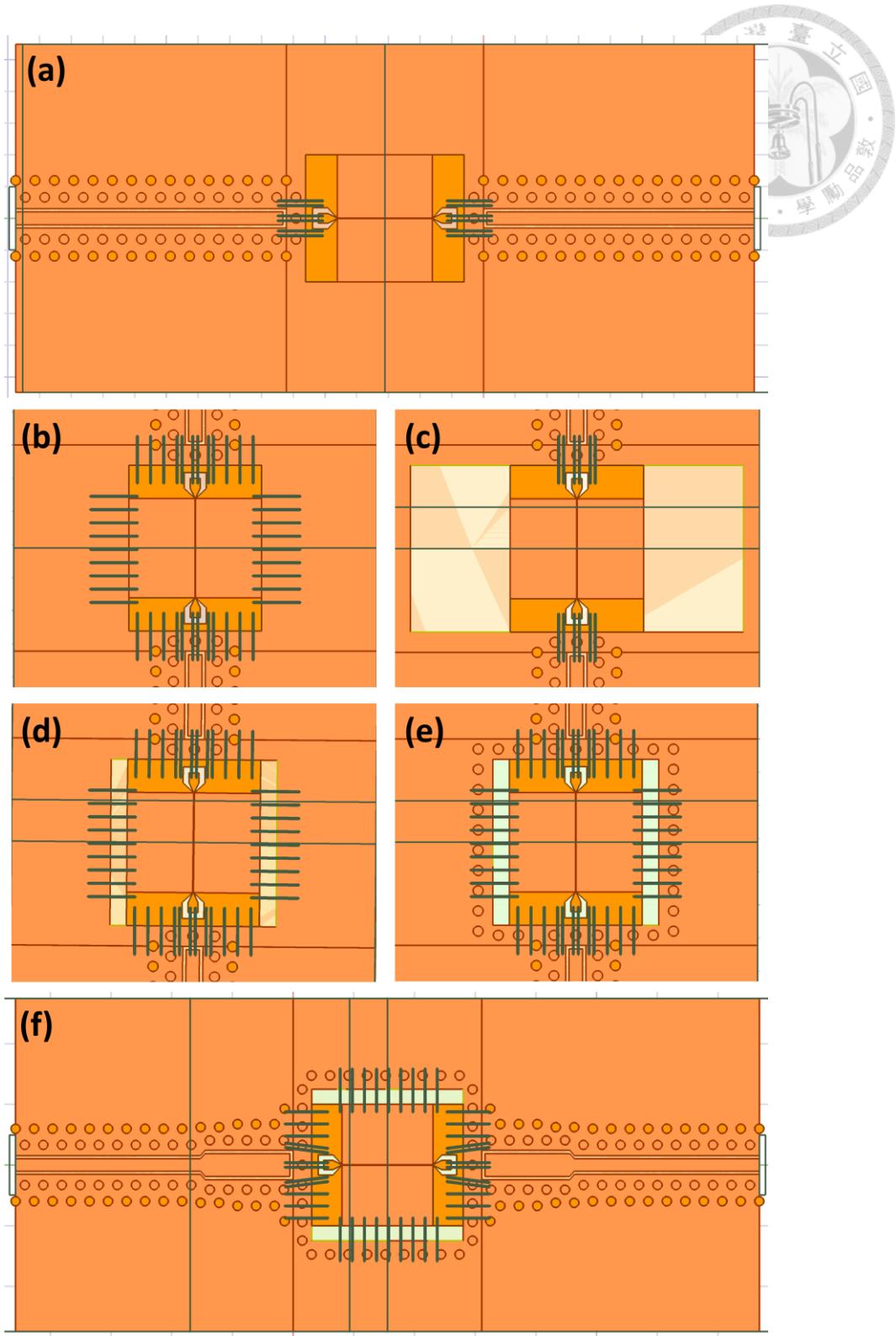

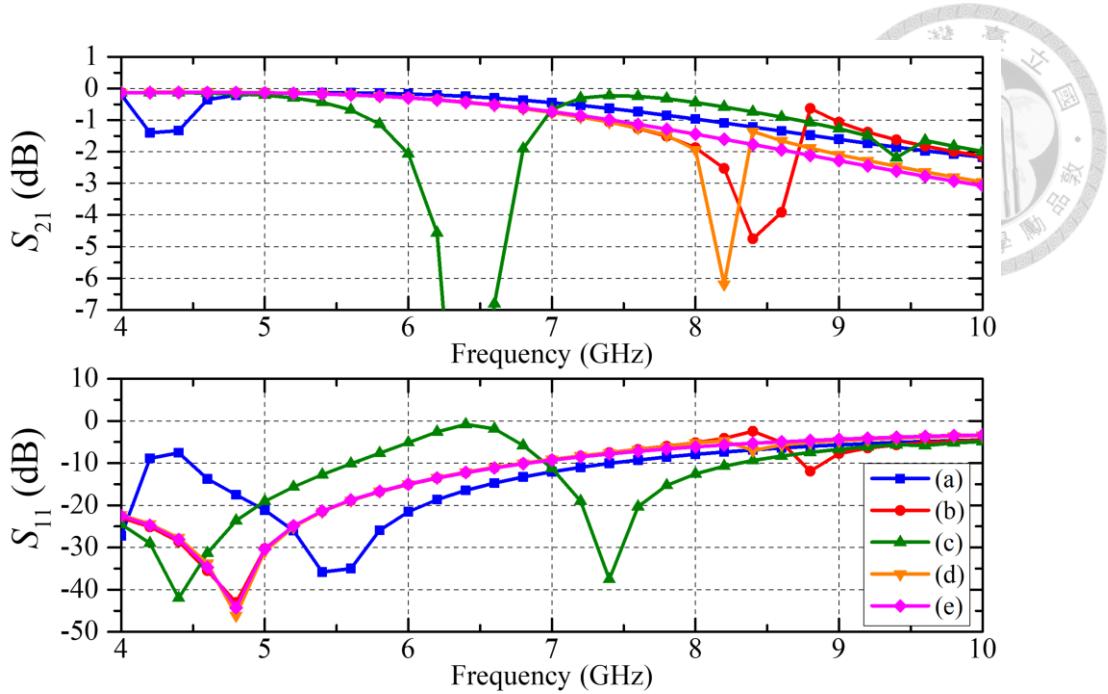

| Figure 5.2: Different configurations for the 0.5_sample board EM simulations. ....                                                                                     | 130 |

| Figure 5.3: Simulated responses of different configurations for the 0.5_sample board.<br>.....                                                                         | 131 |

| Figure 5.4: Simulated responses of the 0.5_sample board with and without impedance<br>matching network. ....                                                           | 132 |

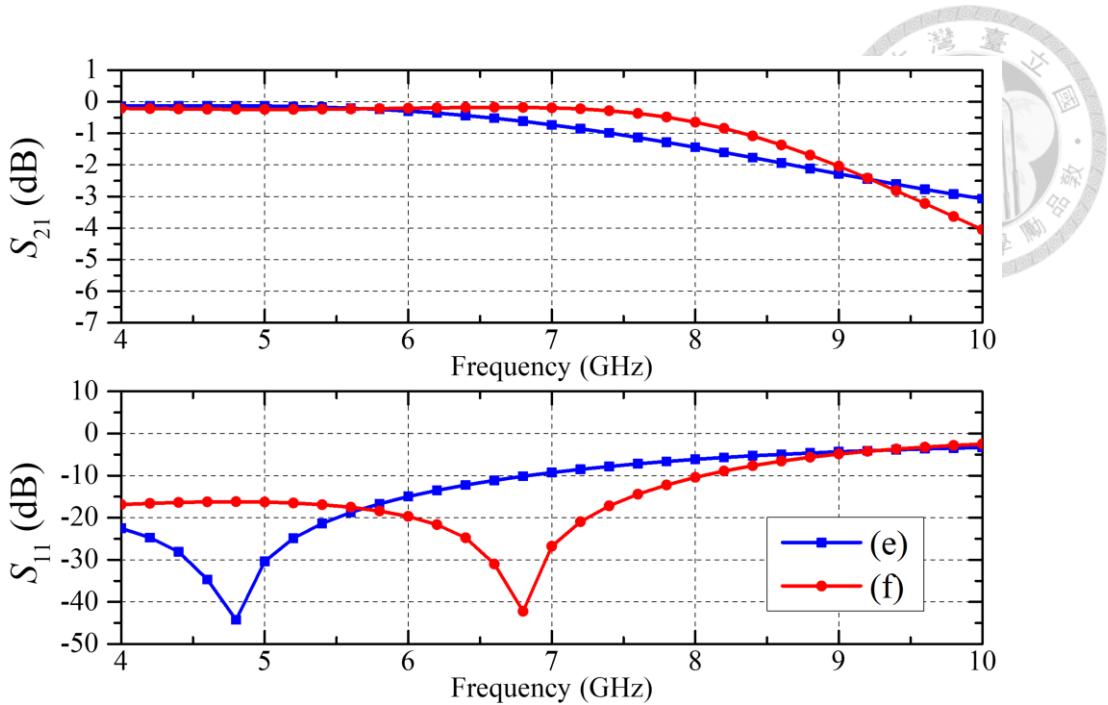

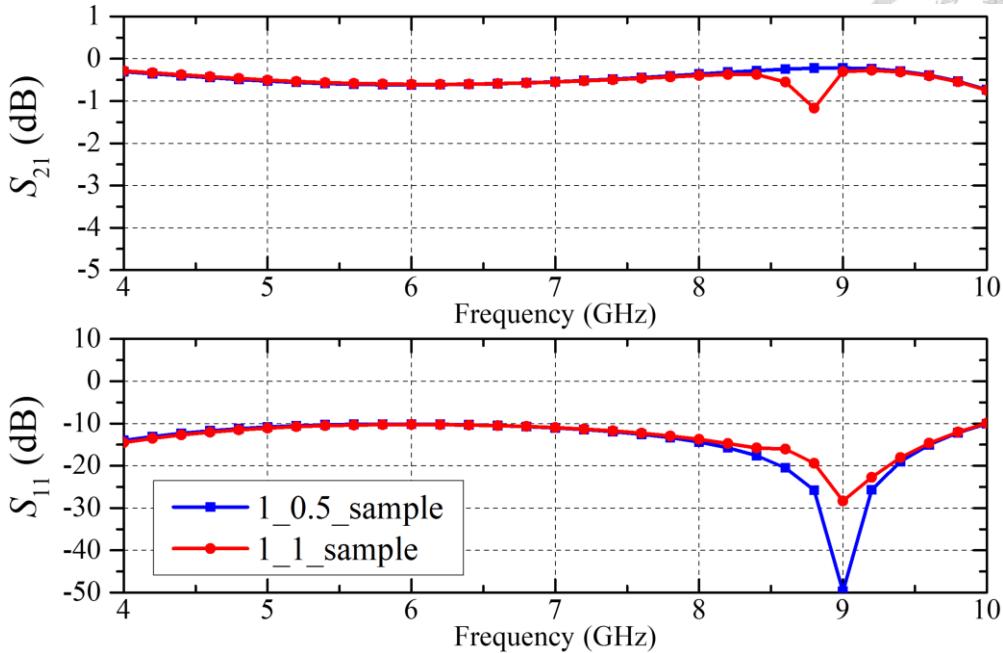

| Figure 5.5: Simulated responses of the 1_0.5_sample board and the 1_1_sample board.<br>.....                                                                           | 133 |

| Figure 5.6: Second-layer magnetic shielding design.....                                                                                                                | 134 |

| Figure 5.7: Simulated responses of three different sample holders, with and without the<br>second-layer upper magnetic shielding. ....                                 | 135 |

| Figure 5.8: Schematic diagram of the setup for the proposed calibration scheme within<br>the dilution fridge. ....                                                     | 137 |

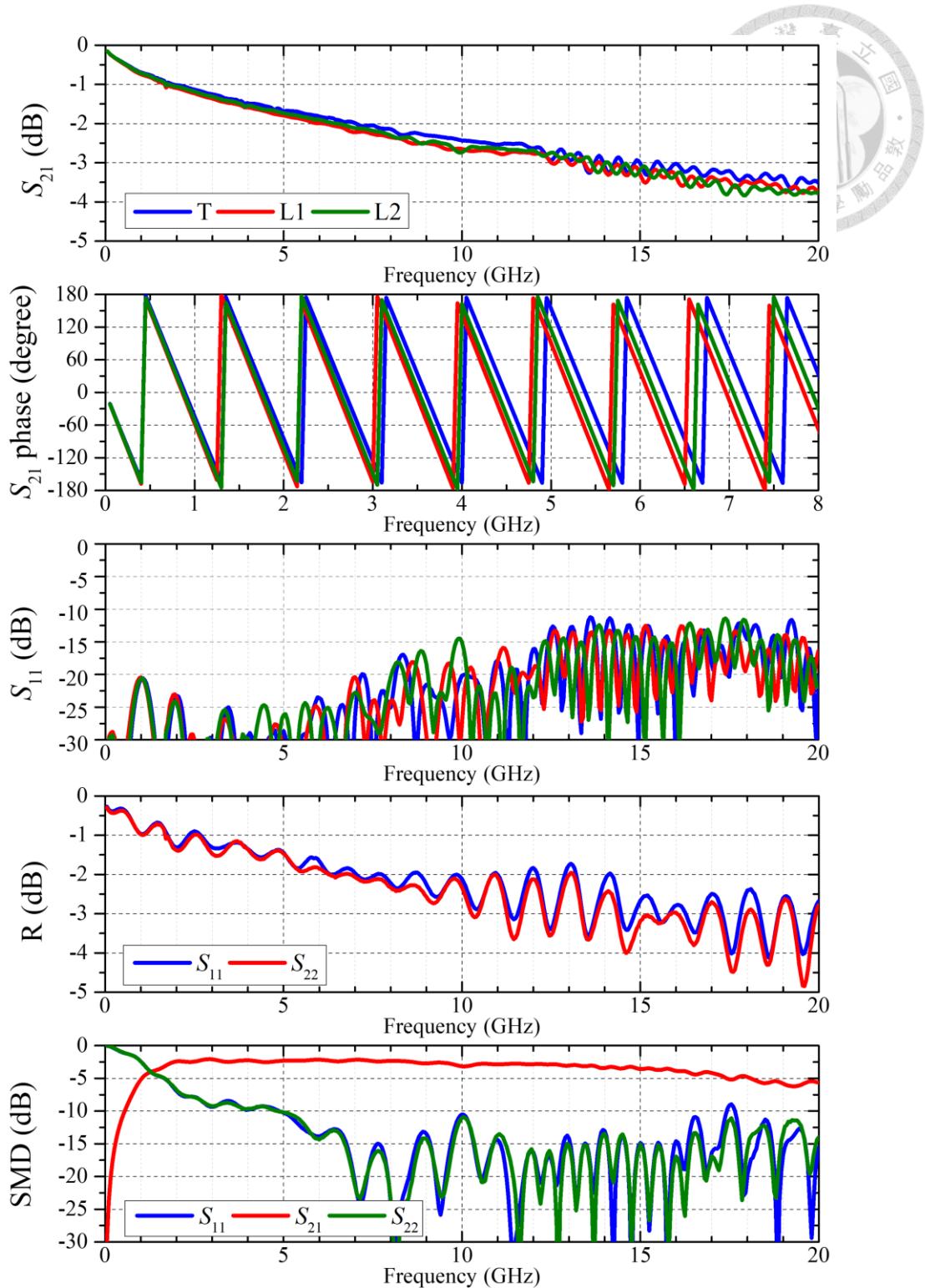

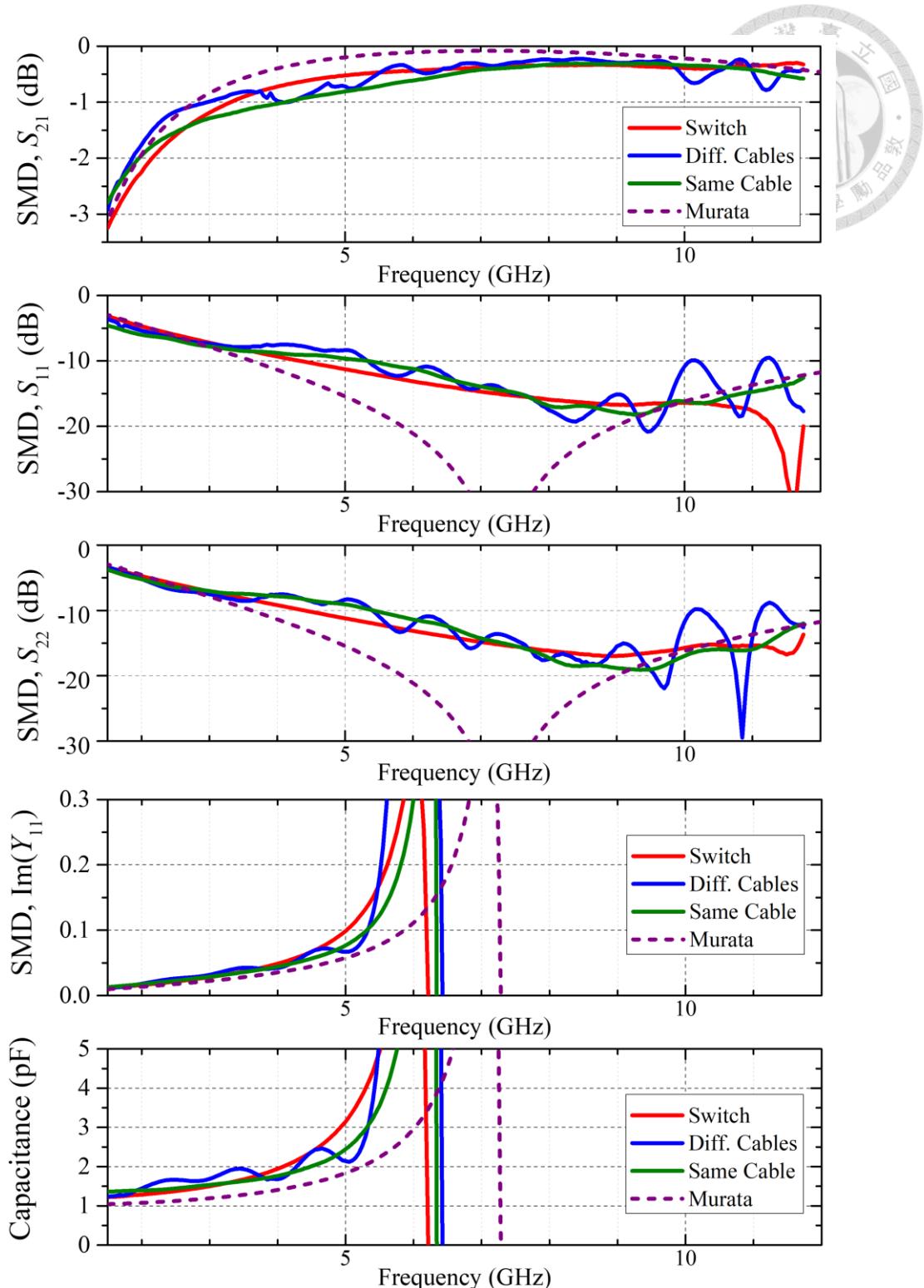

| Figure 5.9: Measured responses of the SP4T_TRL1L2 board. ....                                                                                                          | 142 |

| Figure 5.10: Measured responses of the SP4T_TRL1SMD board. ....                                                                                                        | 143 |

| Figure 5.11: Measured responses of the CMD230_TRL board. ....                                                                                                          | 144 |

| Figure 5.12: Measured responses of the TRL1L2 and TRL1SMD boards with eight<br>different cables within the sample puck. ....                                           | 145 |

| Figure 5.13: Comparison of calibrated responses with L1 as the DUT and L2 as the Line<br>standard under different setup configurations. ....                           | 146 |

|                                                                                                                                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.14: Comparison of calibrated responses with L2 as the DUT and L1 as the Line standard under different setup configurations. ....                               | 148 |

| Figure 5.15: Comparison of calibrated responses with a 1 pF SMD ceramic C0G capacitor as the DUT and L1 as the Line standard under different setup configurations. .... | 149 |

## LIST OF TABLES

|                                                                                                        |     |

|--------------------------------------------------------------------------------------------------------|-----|

| Table 2.1: Comparison of RT and cryogenic LNAs.....                                                    | 50  |

| Table 3.1: Comparison of RT and cryogenic SP4T switches and multiplexers.....                          | 72  |

| Table 4.1: List of the first-phase testing boards. ....                                                | 84  |

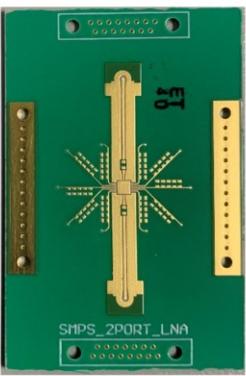

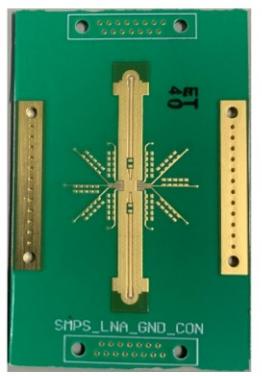

| Table 5.1: List of the second-phase FR4 testing boards.....                                            | 126 |

| Table 5.2: List of the second-phase sample holder boards for superconducting device measurements. .... | 128 |

| Table 5.3: List of second-phase testing boards for S-parameter calibrations.....                       | 140 |

# Chapter 1 Introduction

Quantum computing is acknowledged as a pivotal technology with the potential to revolutionize numerous fields across human society. Various forms of quantum accelerators are being developed, originating from diverse fields within physics and advancing through engineering innovations. Superconducting qubits have quickly emerged as a forefront platform in quantum computing research, facilitated by their relative ease of fabrication and development in laboratory settings [1]. With the advancement bolstered by collaboration among several prominent research groups and industry partnerships, the technology has achieved a notable milestone in demonstrating quantum supremacy [2]. On the other hand, despite slower development, semiconductor spin qubits are highly regarded as promising candidates due to their seamless integration into mature semiconductor manufacturing processes. With their capacity for miniaturization, scalability, and potential ability to operate at higher temperatures, semiconductor spin qubits have become a robust contender in advancing quantum computing towards practical applications [3].

Apart from the core quantum devices, the control and readout electronics implemented in semiconductor integrated circuits (ICs) are also essential in the development of quantum computing systems. In early laboratory research on quantum devices, experimental setups typically involve bulky commercial measuring instruments at room temperature, located outside the dilution fridge. This arrangement requires complex routing through the cooling stages to the base temperature stage where the device operates. For practical quantum algorithms requiring thousands to millions of qubits, using such extensive general-purpose equipment is impractical. Moreover, these complex systems increase the issues of mismatches, synchronization problems, and other potential errors. To address these challenges, integrating specially designed control and readout

electronics that operate in the cryogenic environment within the dilution fridge is widely proposed as part of the envisioned architecture for scaling up quantum systems. Several studies in the literature have demonstrated system-on-chips (SoCs) manipulating and acquiring quantum signals from the corresponding qubit platforms [4-7]. The periphery integrated circuitries within the cryogenic system not only reduce complex routing issues during quantum system scaling but also envision potential on-chip integration with core quantum devices. These specially designed circuits, positioned near the quantum device with minimized electrical paths, are beneficial for enabling multiple operations within the limited decoherence time of the qubits. The reduced round-trip time thereby facilitates more complex operations, including error correction schemes, applied to the qubit systems.

Motivated by the development of integrated periphery electronics, the first part of this thesis delves into designing a cryogenic low-noise amplifier (LNA), serving as the initial input block in the readout receiver chain. In laboratory setups involving a few qubit levels, this critical amplifying block facing the quantum device is typically realized using III-V compound semiconductor LNAs (such as InP and GaAs processes) or SiGe HBT LNAs. These technologies are chosen for their superior noise and gain performance compared to bulk CMOS processes. Moreover, advanced experiments are integrating superconducting parametric amplifiers as the first stage of the readout channels, offering noise performance near the quantum limit that significantly surpasses solid-state amplifiers. However, these amplifier electronics, implemented in various technologies, present challenges when integrating with SoC systems typically realized in CMOS processes for digital circuitry. This often requires discrete connectorized packaging of these amplifiers for connection in the readout cable paths from quantum devices to receiver chips. This approach runs counter to the vision of integrating traditional control

and readout ICs directly with quantum devices to facilitate qubit scaling.

To enhance the performance of low-noise amplifiers in bulk CMOS processes, Chapter 2 introduces a cryo-CMOS low-noise amplifier designed for spin qubit reflectometry readout applications. Reflectometry readout of spin qubits shortens measurement acquisition time by widening the bandwidth of the receiver chain with an up-converted carrier tone. Typically, operational frequencies for reflectometry readout in spin qubits range from hundreds of MHz to a few GHz in the literature. The first part of Chapter 2 discusses topology selection for the frequency band used in spin qubit reflectometry readouts, reviews relevant literature at room temperature, and considers cryogenic design, alongside evaluating reported cryogenic LNAs for spin qubit readouts. Later in this chapter, a novel topology is introduced to alleviate inherent trade-offs in traditional noise-canceling techniques. The proposed LNA is designed and implemented using a 40-nm CMOS process, with detailed derivations of the small-signal and noise responses of the circuits. Despite unresolved issues in noise measurement results at low frequencies, the fabricated circuit demonstrates superior performance at room temperature compared to other reported works in the literature.

The second part of this thesis focuses on another aspect related to quantum device measurements. As part of the initial phase in constructing experimental environments for quantum-related research, alongside cryogenic and vacuum facilities, the second part of the thesis explores the development of electrical and microwave measurement systems at cryogenic temperatures. Chapter 3 introduces a cryogenic broadband single-pole-four-throw (SP4T) RF switch, which serves as an essential element of the refined cryogenic calibration system presented in Chapter 5. The chapter outlines a systematic design procedure for analyzing and synthesizing such a broadband switch. By decomposing the SP4T switch into two low-pass filters connected with the on-resistance of the series

transistor in the middle, a three-step design approach is proposed. Utilizing LC-ladder low-pass filter theory allows for precise synthesis of the SP4T switch response tailored to specific applications. Measurements of the implemented circuit are conducted at both room temperature and 4 K. The SP4T switch achieves a broad bandwidth of 67 GHz and high isolation at room temperature, with power leakage reduced to as low as 0.6  $\mu$ W at 4 K. This ensures operation within the cooling power limits of the dilution fridge's base temperature stage, making it well-suited for integration as the core component of the cryogenic calibration system detailed in Chapter 5.

Chapter 4 discusses various studies and considerations involved in constructing measurement systems for quantum devices. This includes material selection suitable for cryogenic temperatures and the electrical and mechanical design of testing boards for diverse applications. The chapter also emphasizes efforts in designing high-frequency routings and addressing microwave transmission challenges. To improve microwave measurements of quantum devices within the dilution fridge, a straightforward calibration scheme is implemented to de-embed responses contributed by the cryogenic system apart from the device in this initial experiment phase. Despite encountering significant errors within the straightforward calibration scheme, the experiments in this chapter confirm the suitability of selected materials for constructing cryogenic measurement systems.

To improve the cryogenic calibration scheme, the first part of Chapter 5 revises the sample holder design for more practical applications. A multi-board structure is implemented, with various daughterboards designed for specific experiments. This includes a series of sample holders for superconducting device measurements, addressing the box-mode issue and incorporating the necessary magnetic shielding for sensitive samples under test. Later, a refined calibration scheme is proposed, incorporating additional directional couplers and cryogenic amplifiers within the dilution fridge to

enhance the sensitivity of measurements, accommodating the extremely low input power required for quantum devices. To minimize calibration errors within the system, the proposed scheme includes two on-board solid-state RF switches, replacing the bulky connectorized electromechanical switches commonly used in the literature. The broadband SP4T switch introduced in Chapter 3 is integrated into the calibration and measurement board, which also serves as a daughterboard compatible with the multi-board system. Compared to a set of control groups using the straightforward calibration approach in Chapter 4, the refined calibration scheme in Chapter 5 successfully eliminates fluctuation ripples in the calibrated responses. The experiments in this chapter demonstrate an improved calibration system for microwave measurements of quantum devices, facilitating a more detailed understanding of quantum devices in future research by reducing environmental interference within the measurement setup.

# Chapter 2 A Cryo-CMOS LNA for Spin Qubit

## Reflectometry Readout Applications

### 2.1 Introduction

#### 2.1.1 Literature Review of CMOS Noise Canceling LNAs in VHF and UHF Bands

The design of a low noise amplifier (LNA) typically involves parameters such as gain, noise figure, input matching, stability, power, and linearity. In particular, the challenge of ensuring broadband low input return loss when interfacing with the RF environment ahead of the receiver chain is a key factor in determining suitable topology candidates. An interesting review of the early histories to the 2010s of broadband LNAs can be found in [8]. Various techniques incorporating passive LC components and transformers are widely explored in the literature [9, 10]. However, the need for functionality at relatively low frequencies around 100 MHz presents difficulties for the matching network. This requires the use of large inductors at the LNA input, which can introduce loss, degrade both gain and noise performance, and necessitate a large footprint.

To achieve the desired broadband return loss starting from dc, in addition to passive LC approaches, three primary topologies are reported to realize input matching by synthesizing the resistive part of the input impedance. Firstly, the common-gate (CG) LNA, which utilizes the intrinsic input impedance from the source of common-gate transistors, is one of the most popular topologies. Secondly, the resistive feedback topology incorporates a shunt resistor with common-source (CS) transistors, enabling input matching by carefully selecting the value of the feedback resistor in conjunction with the amplifier's gain. Finally, the active feedback topology achieves the desired input

resistance using a source follower in the feedback route of a CS transistor.

Despite realizing the input matching at low frequencies, the three topologies above suffer from various trade-offs between input return loss and other parameters. In the case of CG LNAs, some studies attempt to mitigate the effects on intrinsic input impedance when aiming for better noise figures by incorporating feedback mechanisms to decouple the two parameters [11, 12]. Nevertheless, akin to the resistive-feedback and active-feedback configurations, reducing the noise figure often entails increasing the transconductance of the transistors, leading to higher power consumption. Furthermore, in the pursuit of ultra-low noise characteristics, the continuous increase in transconductance can still impact input matching, often resulting in inadequate noise performance. A more prevalent approach in CG LNA design involves employing feed-forward techniques, wherein the noise figure is significantly improved through the gain-boosting mechanism, thereby easing the design trade-offs with input power matching. However, to mitigate the additional noise contribution from feed-forward circuitries, the approach is usually implemented in a differential configuration with passive components [13, 14].

To explore noise reduction techniques and efforts to decouple input power matching, a noise-canceling concept is proposed in [15]. Leveraging the inherent phase opposition between the signal and noise voltages at the input and output nodes of the main amplifier block, this mechanism integrates an additional gain block parallel to the main amplifier. Through a combining network of the two paths, it theoretically cancels out the channel noise of the main amplifier while concurrently amplifying the signal from both routes. This innovative approach effectively mitigates the dependency of the main amplifier's noise behavior on its transconductance, rendering it independent of input matching considerations. The main amplifier block is commonly constructed using either a CG

transistor or a resistive-feedback CS transistor to achieve the intended input matching. By incorporating the additional CS gain block, noise-canceling LNAs can be divided into two classifications: CG-CS noise-canceling LNAs and shunt-feedback noise-canceling LNAs.

In the literature, considerable effort has been dedicated to studying the CG-CS noise-canceling topology, primarily due to its potential to function as a single-to-differential balun amplifier [16]. Various enhancements to this topology, such as the gm-boosting technique for the CG cell [17] and the current-reuse technique for power reduction [18], continue to be actively explored, keeping the CG-CS noise-canceling topology a dynamic area of research. Given the stringent linearity requirements in communication systems, much of the research also focuses on improving the behavior of IP2 and IP3 [19, 20]. Nonetheless, this topology necessitates a dc path for the CG transistor at the input port, which mandates either an off-chip inductor or an on-chip current source or inductor. The former complicates measurement and future system integration, while the latter often compromises input-referred noise, thus hindering the potential for achieving ultra-low noise performance. In addition to the CG-CS topology, there are numerous captivating reports of broadband LNAs in differential form that exhibit outstanding performance, with some adopting a noise-canceling approach [21]. However, the necessity for differential signals to achieve proper phase implementation is incompatible with the single-ended receiver used in spin qubit readout reflectometry.

On the other hand, given the need for an inductor-less and single-ended design, the shunt-feedback noise-canceling topology emerges as a preferred choice. Following the early exploration in [15], there have also been several studies exploring the shunt-feedback noise-canceling approach. In [22], a CG gain block is introduced to address the trade-off between gain and bandwidth associated with the feedback resistor value, while

also improving the output buffer's driving capability through the implementation of a resistive shunt-feedback CS block. Despite the inductorless nature promoted within this topology, some studies also utilize on-chip inductors to mitigate capacitive degradation at higher frequencies, thereby widening the bandwidth and preserving the noise-canceling relationship [23, 24]. Similar to the CG-CS topology, the demand in communication system applications prompts several studies to focus on analyzing and improving linearity, particularly through the utilization of pMOS-nMOS pairs for intermodulation distortion cancellation [25, 26].

Further exploration aimed at improving the trade-off between gain and input matching on the feedback resistor of the main amplifier block reveals a few novel topological approaches. [27] introduces a source follower feedback on the auxiliary CS transistor. This active feedback introduces an additional impedance parallel to the original input matching of the main amplifier block, enabling an adjustment in the feedback resistor while maintaining the desired input impedance. This increased feedback resistor enhances the overall gain, reducing the noise contribution from the auxiliary transistors and consequently lowering the noise figure. However, the noise power generated by the additional feedback source follower transistor limits the low noise potential of this topology, especially under a limited power budget. In a subsequent study detailed in [28], a global resistive feedback is integrated at the combination node of the main and auxiliary paths. This topology effectively introduces a shunt impedance in parallel at the input node, allowing for adjustment of the feedback resistor value previously constrained by the input return loss. In addition to mitigating the trade-off between input matching and gain, the circuitry implements self-forward-body-bias (SFBB) on both pMOS-nMOS pairs of the main and auxiliary amplifier blocks, enhancing the transconductance within the limitations of the supply voltage. Furthermore, the design also emphasizes selecting

pMOS-nMOS biasing points and sizes to further reduce higher-order nonlinearities through small signal analysis.

### 2.1.2 Design Considerations for Cryogenic Operation

The brief review in the previous subsection mainly focuses on the reported works in the literature operating at room temperature. Nonetheless, the targeted application of the proposed LNA in this chapter requires functionality at a cryogenic temperature of around 4 K. Therefore, before delving into the literature review of cryogenic LNAs, it is also important to investigate device characterization in a cryogenic environment.

Since the research of interest primarily focuses on analog and radio-frequency circuits, only specific aspects of cryogenic characterization will be discussed. Within this scope, [29] provides an impressive review of the related fields. For standard bulk CMOS processes, [30] and [31] report and analyze dc and analog-design parameters across several technology nodes with different channel lengths. Generally, the threshold voltage of the devices increases due to carrier freeze-out caused by the increased ionization energy. Nevertheless, carrier mobility increases due to the reduction in phonon scattering, resulting in higher drain current and transconductance in strong saturation. However, this enhancement in effective channel mobility is limited by ballistic transport restrictions in short-channel devices, reducing the extent of the improvement. More pertinent to digital circuits, the steeper subthreshold slope reduces leakage current and enhances switching speed. Alongside the high driving current, this feature is advantageous for efficient digital logic implementation. It's worth mentioning that some non-idealities observed in long-channel devices, such as the kink effect and the resulting hysteresis in current sweeping, are mitigated with advanced short-channel devices. For analog circuits, the  $G_m/Id$  ratio and intrinsic gain of transistors are often of interest. The  $G_m/Id$  ratio improves in the weak inversion region, though a slight reduction is observed in the strong inversion region.

This feature suggests improved power efficiency for analog circuits biased in the weak inversion region. At the same gate voltage in the strong inversion region, transistors exhibit nearly constant output conductance with varying temperature, and the increased transconductance at cryogenic temperatures results in improved intrinsic gain. Interestingly, under a constant overdrive voltage, a lower intrinsic gain is reported at cryogenic temperatures due to an increase in the channel length modulation factor, which reduces output resistance. Nonetheless, intrinsic gain generally improves for short-channel processes in the weak inversion region.

[32] and [33] report the low-temperature RF performances of bulk CMOS transistors in a body-tied-to-source CPW configuration. The junction capacitance within the devices moderately decreases due to incomplete ionization of dopants in the bulk well, while the external capacitance from metal routings remains nearly unchanged. The gate capacitance reduces because of an additional series capacitance to the gate oxide capacitance caused by the increased depletion region. Overall, this reduction in capacitance and increase in transconductance result in an improved current gain cutoff frequency, which is beneficial and can be traded for lower power consumption while maintaining the required speed at low temperatures. Gate resistance decreases until around 50 K due to increased mobility, then saturates and slightly increases near 4 K due to the freeze-out of gate polysilicon. Other external parasitic resistances, representing the resistance of the electrodes and interconnections between terminals, decrease as the temperature lowers. These changes lead to an improved maximum oscillation frequency, with slight saturation near 4 K where gate resistance increases. By employing a two-phase procedure, notably SOLT calibration and open-short de-embedding techniques, the *S*-parameter behaviors at cryogenic temperatures are also examined. The enhancement of  $S_{21}$  can be attributed to the increase in transconductance. Regarding return loss-related parameters, while  $S_{11}$

remains nearly constant at low temperatures,  $S_{22}$  shows slight variations due to the decrease in output resistance.

In LNA design, the noise performance at cryogenic temperatures is also crucial. The primary noise power contribution in a typical room temperature low noise amplifier comes from channel white noise and thermal noise from gate resistance due to the input-referred effect. Fortunately, gate resistance generally decreases with temperature, resulting in a reduction of noise contribution. Regarding noise within the device, [34] provides an interesting examination of the source at low-temperature. As conventional thermal noise reduces proportionally with the temperature, the saturated improvements of the LNA works at cryogenic oppose the model. This is explained by the ballistic transport of the short channel device under high field reinforces the reduction of phonon scattering at low-temperature, resulting dominance of non-equilibrium shot noise in the channel. Under this scenario, for cryogenic applications, the optimization of low noise performance may lay in device selection of reducing shot noise, instead of thermal white noise, such as using longer channel devices.

For RF/mm-wave designers, the performance of on-chip passive components is also crucial. In [35], several types of on-chip resistors are examined, revealing significantly increased resistance with the n-well resistors due to carrier freeze-out at cryogenic temperatures. Conversely, the n-poly and p-active resistors exhibit rather steady resistance values. Furthermore, the p-n-p BJT, often incorporated in bandgap reference circuitries and temperature sensors, also deteriorates owing to carrier freeze-out in the base. [36] offers a compelling review of the extraction of cryogenic models for an MoM capacitor and a transformer, as well as a resonance tank comprising both components. In the case of the rotative inter-digitated MoM capacitor, the core capacitance experiences a slight increase due to variations in the dielectric constant. Meanwhile, the quality factor

improves at lower frequencies owing to reductions in dielectric and metal loss. However, this improvement diminishes above certain frequencies when the dielectric loss improvement ceases. Concerning the multi-turn transformer, shielding is excluded due to increased substrate resistance at low temperatures caused by carrier freeze-out. Overall, the inductance decreases slightly, while the coupling factor and quality factor increase. The decrease in inductance is attributed to reduced interior current resulting from increased conductivity, thereby reducing the skin depth and interior inductance. Meanwhile, the quality factor improves due to increased conductivity and reduced substrate loss, and the increase in coupling factor is attributed to variations in parasitic capacitance. The reduction of inductance and effective substrate coupling capacitance also enhances self-resonance and peak quality factor frequency. The transformer-based resonator tank follows a similar trend as the transformer, with increased quality factor, higher resonance frequency, and a larger ratio of the first and second resonance frequency due to an increase in coupling factor, resulting in a wider bandwidth. The insertion loss of the resonator tank also decreases, with the Z-parameters enhanced at higher frequencies, leading to increased transfer function. Overall, operating at cryogenic temperatures benefits the performance of high-frequency integrated circuits.

Apart from the characterizations briefly reviewed above, other issues such as self-heating, mismatch, and increased flicker noise are also discussed in the literature. It's worth noting that while the references mentioned above focus on bulk CMOS technologies, several other studies concentrate on examining FDSOI processes. This technology exhibits reduced coupling loss and enables back-gate biasing to tackle the incremental threshold voltage issue at cryogenic temperatures. Finally, while there have been some explorations into the development of compact cryogenic models [37, 38], the studies in this chapter continue to rely on the available standard room-temperature model

for simulation.

### 2.1.3 Literature Review of Cryogenic LNAs

Research on low-noise amplifiers operating in cryogenic environments has been a focus in the field of radio astronomy for decades [39]. Numerous studies have explored various technology nodes, aiming for extremely low power consumption, high gain, and performance near the quantum noise limit [40]. III-V compound semiconductor technologies, such as GaAs and InP, have attracted significant attention due to their inherent characteristics of high gain, high speed, and low noise performance, leading to impressive and pioneering results. Because of their advanced development, commercially available or custom III-V compound semiconductor LNAs are commonly used in experimental setups for quantum processors and quantum-related research. While GaAs HEMT LNAs achieve outstanding noise temperature and high gain in the 4 to 8 GHz frequency range for superconducting qubits, they suffer from immense power consumption due to the required high supply voltage [41]. In contrast, reported InP HEMT LNAs not only demonstrate superb noise and gain performance but also sustain these advantages even with reduced supply voltages. This results in state-of-the-art performance at cryogenic temperatures, featuring sub-mW power consumption and noise temperatures in the few K range [42, 43]. In recent years, despite their inherently inferior minimum noise temperature in the frequency range of 4 to 8 GHz compared to InP processes, SiGe BJT technologies have emerged as candidates in this field, thanks to their cost efficiency and integration capabilities within large-scale multifunctional systems. Using a cryogenic noise-optimized process, researchers implemented a two-stage LNA for superconducting qubit readout in [44]. This design achieved remarkable performance metrics, including a mere 1 mW power consumption, over 30 dB gain, and a noise temperature of 2.6 K at an ambient temperature of 17 K. In the lower frequency range

spanning from hundreds of MHz to around 3 GHz, which is typically utilized for reflectometry readout of semiconductor spin qubits, fewer reports on InP LNAs are available. In contrast, SiGe LNAs demonstrate state-of-the-art performance in this domain. Lowering the supply voltage headroom, as detailed in [45], a two-stage LNA with RC-feedback achieves sub-mW power consumption while still maintaining 32 dB gain and a noise temperature of 4.6 K at an ambient temperature of 15 K.

With an increasing number of demonstrations showcasing integrated system-on-chip control and readout circuitries, research on implementing cryogenic LNAs utilizing bulk CMOS processes also gains interest and significance. In the field of superconducting qubit readout, common-source amplifiers or cascode amplifiers have been demonstrated, employing narrow-band noise matching through source degeneration techniques [46, 47]. By incorporating transformer-based tanks, a broadband characteristic can be achieved, showcased by the front-end LNA in the integrated readout receiver in [6]. Additionally, [48] presents an enhanced topology, integrating wideband matching techniques with reduced noise contribution from the cascode transistor, resulting in a sub-1 dB noise figure at room temperature and over 35 dB gain. However, despite the theoretical capability of the aforementioned source-degeneration-type topology to approach the minimum noise temperature of the device with low-loss passive components at cryogenic temperatures, the demonstrated power consumptions remain substantial. Addressing this issue, [49] introduces a resistive-feedback cascode inverter topology, consuming only 3.5 mW at room temperature, with a remarkable gain of 54 dB. However, due to the low biasing current, the intrinsic noise performance degrades, necessitating, as their analysis reveals, the addition of a superconducting parametric amplifier in front of the receiver chain. [50] explores a compelling study featuring a hybrid CMOS LNA tailored for radio-astronomy applications in the frequency range of 0.9 to 1.8 GHz. While the circuit

achieves an impressive gain of 32 dB and an exceptionally low noise temperature of 12 K at room temperature, it consumes an overwhelming power of 105mW. These studies shed light on the challenges and opportunities of pursuing ultra-low noise performance within stringent power limitations at cryogenic temperatures.

Compared to their superconducting counterparts, there have been fewer studies on cryogenic LNAs for spin qubit reflectometry readout. An early demonstration in [35] implements a conventional shunt-feedback noise-canceling LNA with cascode transistors, alongside device characterizations. The LNA chain exhibits a gain of 40 dB and a noise figure of 0.8 dB, which, at a temperature of 4 K, is enhanced to a gain of 57 dB and a noise figure of 0.1 dB. However, the circuit's bandwidth is limited to around 400 MHz at room temperature and 500 MHz at 4 K. Additionally, with the inclusion of three subsequent amplifying stages and an output buffer driver, the circuitry consumes 80 mW at room temperature, increasing to 91 mW at 4 K, with 54.9 mW attributed to the LNA core. In the readout receiver chain described in [5], a 1.4 mW differential negative and positive dual-feedback CG LNA is constructed. However, the low-power design yields a noise figure lower than 3 dB at room temperature, necessitating the incorporation of an additional III-V compound semiconductor LNA in the readout chain before the receiver. In [51] and a subsequent extending article in [52], two noise-canceling LNAs are introduced. The first LNA utilizes a conventional topology enhanced with the self-forward-body-bias (SFBB) technique to mitigate the increased threshold voltage at cryogenic temperatures. Despite the high power consumption associated with this technique, the LNA achieves an exceptional noise figure of 0.63 dB at room temperature and a noise temperature of 2.2 K at 4 K ambient temperature. The second LNA abandons the SFBB technique in favor of a source-follower feedback method on the auxiliary amplifier. This approach provides additional flexibility in input matching and eases the

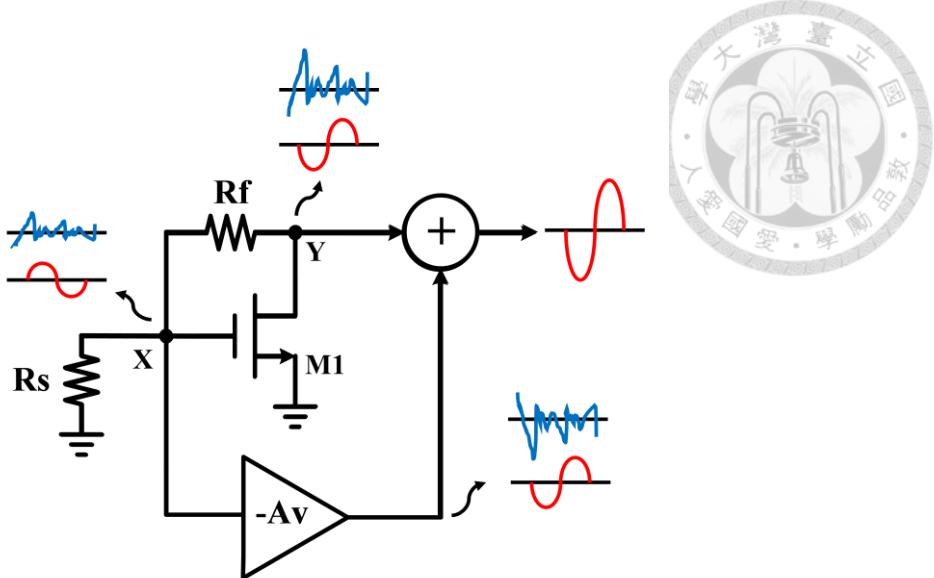

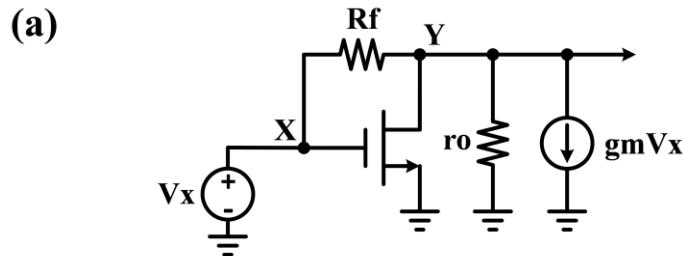

Figure 2.1: Schematic diagram of noise-canceling technique implemented with a shunt-feedback common-source amplifier stage.

constraints imposed by the feedback resistor trade-off on the main inverter amplifier. In [53], the same research group explores another topology that also applies the SFBB technique to the main inverter amplifier. By incorporating inductors, they propose a two-fold current reuse structure for the auxiliary and combining transistors, which effectively reduces power consumption. This LNA achieves less than 10 mW power consumption at 4 K, with a noise temperature of only 6.8 K and a gain of 31 dB over a frequency range of 0.01 to 2.6 GHz.

## 2.2 Circuit Design

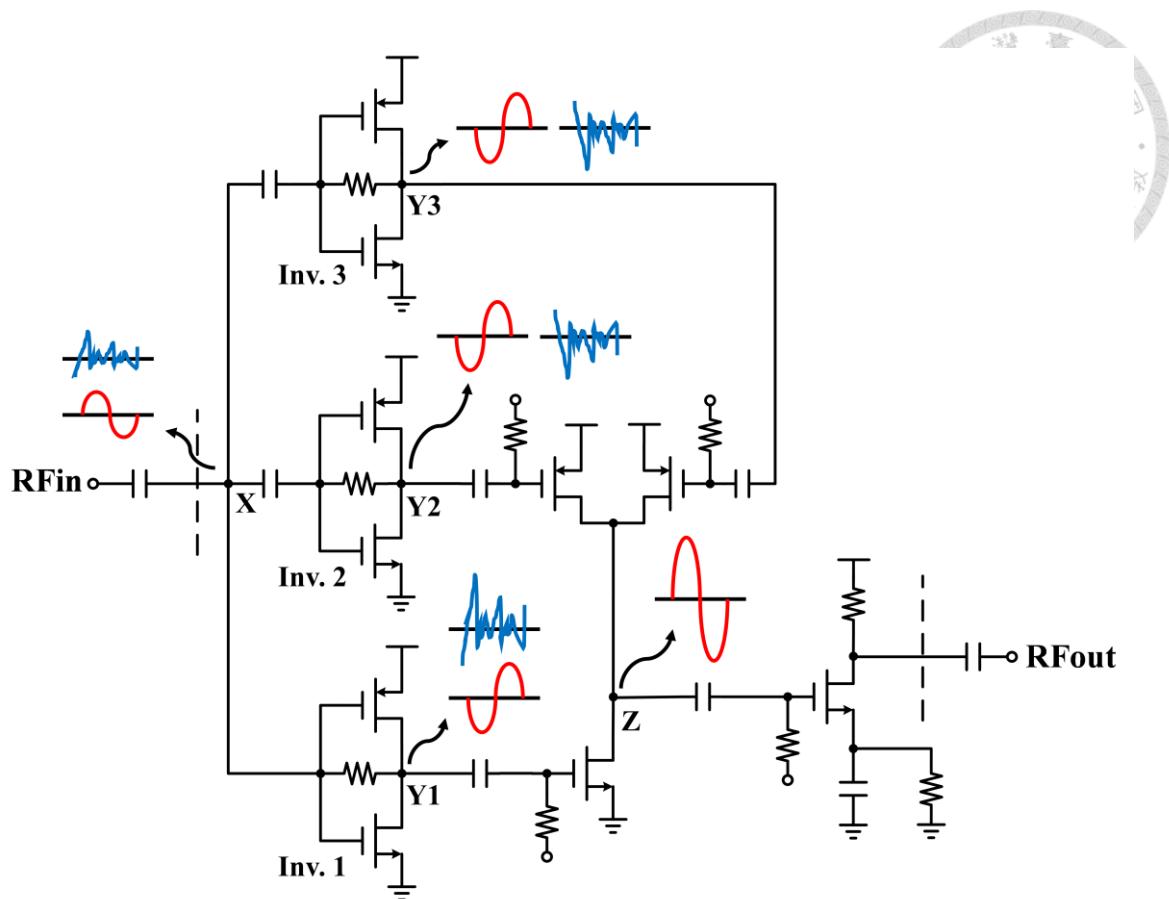

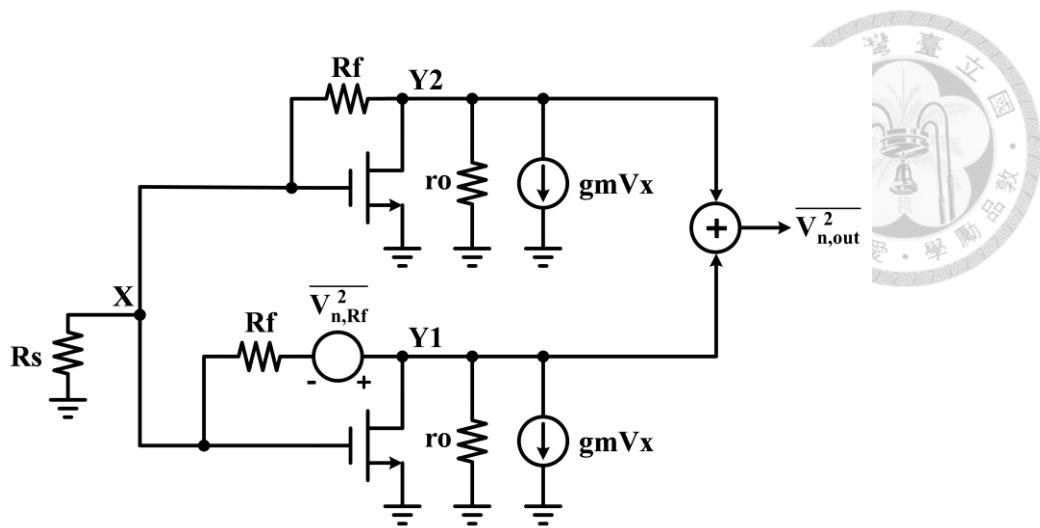

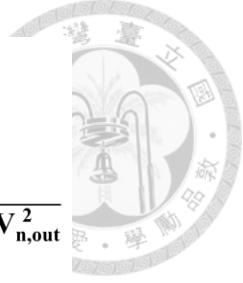

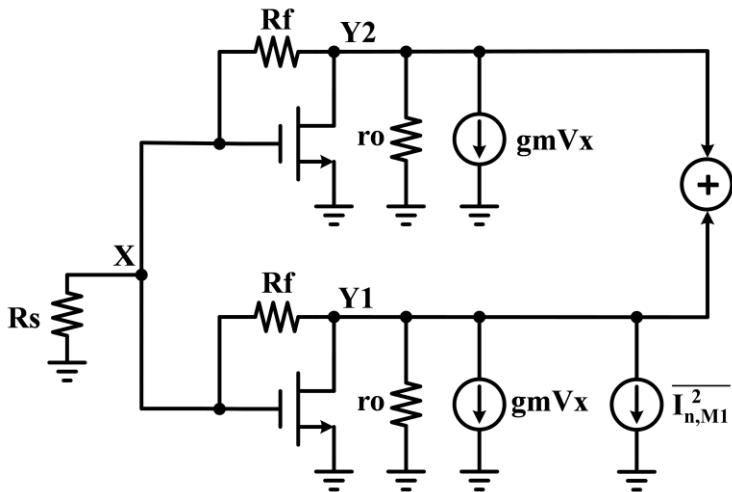

As discussed in Sec. 2.1.1, the resistive-feedback common source (CS) amplifier stage is chosen as the input block of the LNA due to the single-ended requirement in reflectometry readout and its easier future system-on-chip integration, as it eliminates the need for an off-chip biasing inductor required in common-gate transistors. Figure 2.1 illustrates the schematic diagram of conventional noise-canceling technique implemented with a resistive-feedback CS amplifier stage. The noise current from the resistive-feedback CS transistor M1 introduces a corresponding noise voltage at the drain node, depicted by the blue fluctuations at node Y. This noise current flows back through the

feedback resistor  $R_f$ , creating reduced noise voltage fluctuations at the circuit's input node with the same polarity, as shown at node X. The noise-canceling technique introduces an auxiliary amplifier stage parallel to the resistive-feedback CS amplifier. This auxiliary block amplifies the noise voltage at node X, producing a noise voltage at its output node with reversed polarity. By using an ideal voltage combiner and carefully tuning the auxiliary amplification, the noise contribution of transistor M1 can be fully cancelled and mitigated at the output node of the circuit. On the other hand, the input signal at node X undergoes amplification and polarity reversal by both the resistive-feedback CS amplifier and the auxiliary amplifier, as shown by the red sinusoidal waveform in Figure 2.1. The summation of these two paths with the same polarity results in a combined amplified output signal at the output node after the combining stage.

In practical implementation, this conventional noise-canceling architecture encounters several challenges and shortcomings. Firstly, although the technique ideally eliminates the noise contribution of transistor M1 in the main resistive-feedback CS block, it does not address the noise issues of the auxiliary amplifier. This often results in significant power consumption and may require additional current sources for the auxiliary amplifier to reduce inherent noise by increasing the transistor's transconductance. Secondly, there is a trade-off between voltage gain and input impedance within the shunt-feedback CS topology. The need for input matching in a general LNA limits the voltage gain of the input amplifying block. Insufficient first-stage amplification is undesirable as it can increase the noise contribution of subsequent stages in the receiving chain. Finally, the circuit's inadequate gain is further exacerbated by the common practice in the literature of using common-drain transistors in the combining stage. In applications like wireless communication or radio receivers, employing a

Figure 2.2: Schematic diagram of the proposed cryo-CMOS LNA.

source-follower in the combining stage enhances circuit linearity, which is a primary focus in these studies. However, source followers lack the ability to drive loads with low impedance, often resulting in less than unity amplification in this stage, leading to a reduced overall gain for the LNAs. In contrast, for our targeted application, where the reflected signal from quantum devices in the reflectometry readout is often below -130 dBm, the circuit linearity can be compromised in favor of superior gain and noise performance.

Figure 2.2 shows the schematic diagram of the proposed cryo-CMOS LNA. In contrast to the conventional topology, where typically only the core input amplifier is realized with a resistive-feedback CS amplifier, the proposed design employs resistive-feedback CS amplifiers for both the core input amplifier and the auxiliary amplifier blocks. Additionally, a pMOS transistor is integrated into the resistive-feedback CS amplifier as

Figure 2.3: Schematic diagram of the noise-canceling mechanism of the noise contributions from the transistors of Inverter 1 in the proposed cryo-CMOS LNA.

an active load, enhancing the transconductance of the inverter amplifier without increasing power consumption. At the combining stage, rather than employing source followers, all combining paths utilize common source amplifiers. This approach allows for further amplification of the voltage gain from the first stage, albeit at the expense of reduced linearity.

Figure 2.3 illustrates the noise canceling mechanism of the proposed topology. The blue noise waveform represents the noise contribution from the transistors of Inverter 1. At node Y1, both the pMOS and nMOS transistors of Inverter 1 introduce noise fluctuations at their drains. These noise currents flow through the feedback resistor of Inverter 1, creating voltage fluctuations at the input node X with reduced amplitude but the same polarity. These fluctuations are then amplified by Inverter 2 and Inverter 3, resulting in noise voltages with reversed polarity at nodes Y2 and Y3. The common

source amplifiers at the combining stage further amplify and reverse the polarity of these noise signals. At node Z, the resulting noise fluctuation from Inverter 1's transistors is cancelled out due to the opposite polarity contributions from Inverter 2 and Inverter 3. Similarly, the noise contributions from the transistors of auxiliary Inverter 2 and Inverter 3 can be analyzed, where Inverter 1 acts as the noise canceling path, reducing noise fluctuations originating from these auxiliary amplifiers. Conversely, the input signal at node X is amplified through the three separate paths, combined, and magnified at node Z with the same polarity. As a result, the proposed approach effectively cancels the noise contributions of both the core amplifier block and the auxiliary amplifier block, while enhancing the overall voltage gain of the LNA through the summation of three parallel paths and the utilization of common source transistors at the combining stage.

Following the combining stage, an output driver stage employs a common source amplifier is implemented to sustain the overall voltage gain of the LNA. As previously mentioned, a source follower is not suitable for driving the low characteristic impedance of 50 ohms typical in RF systems. The proposed LNA also incorporates capacitive degeneration technique at the output driver stage, thereby broadening the 3-dB gain bandwidth.

Finally, several dc blocking capacitors are added to independently adjust the supply voltage and current of each branch during measurements. This is preferable because predicting the cryogenic performance of the circuit is challenging due to the absence of a compact model. The following subsections delve into the details of the proposed LNA circuit design, beginning with an analysis of the single inverter design.

### 2.2.1 Single Inverter Design

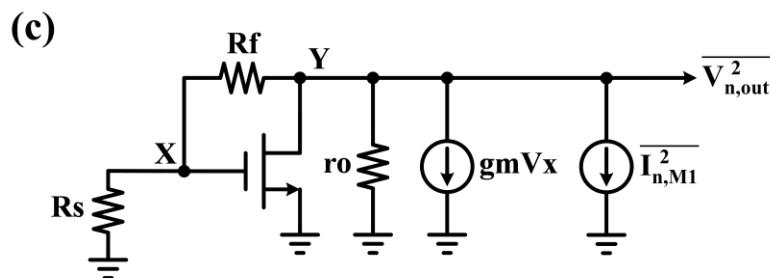

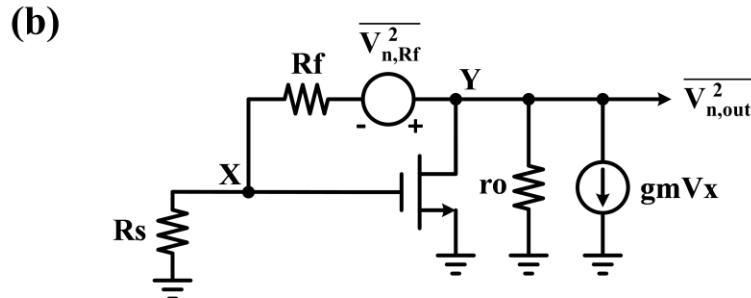

Beginning with the core block of our proposed LNA, this subsection delves into the analysis of noise and small-signal responses of an inverter amplifier. Figure 2.4 (a) depicts

Figure 2.4: Schematic diagram for calculating gain and noise power of an inverter amplifier stage. (a) Gain and input impedance. (b) Noise of the feedback resistor. (c) noise of the transistor.

the schematic diagram used to compute the small-signal response of an inverter amplifier.

The transconductance and output impedance of both the pMOS and nMOS transistors are combined to simplify the analysis. Following simple calculation, the low-frequency voltage gain from node X to node Y can be derived as:

$$A_v = -\frac{(g_m R_f - 1) r_o}{r_o + R_f} \quad (2.1)$$

Similarly, the low-frequency input resistance of the inverter amplifier as seen from node X is calculated as:

$$R_{in} = \frac{r_o + R_f}{1 + g_m r_o} \quad (2.2)$$

After calculating the low-frequency small-signal responses of the inverter amplifier, the output thermal noise power contributed by the feedback resistor and the transistors

can also be determined. Illustrated in Figure 2.3 (b), the thermal noise voltage of the feedback resistor at the output node can be derived as:

$$\overline{V_{n,out,Rf}^2} = 4k_B T R_f \left[ \frac{r_o(g_m R_s + 1)}{r_o(g_m R_s + 1) + R_f + R_s} \right]^2 \quad (2.3)$$