# 國立臺灣大學電機資訊學院電子工程學研究所

# 碩士論文

Graduate Institute of Electronics Engineering

College of Electrical Engineering and Computer Science

National Taiwan University

Master's Thesis

# 利用約束測試模式和斷言驗證 進行 RTL Bug 自動定位

Automatic RTL Bug Localization by

Constrained Pattern Generation and Assertion Validation

陳孟宏

Meng-Hung Chen

指導教授: 黃鐘揚 博士

Advisor: Chung-Yang (Ric) Huang Ph.D.

中華民國 113 年 8 月

August, 2024

# **Acknowledgements**

在這兩年的碩士旅途中,我有幸獲得許多人的幫助,在此要一一表達由衷的感謝。

首先,我由衷感謝我的指導教授,黃鐘揚(Ric)教授,謝謝教授的博學多聞和豐富的業界經驗,讓我在每次咪挺的過程中總能獲益良多、獲得教授許多回饋豐富我的知識;也很謝謝教授的悉心指導,讓我碩士生活取得研究與生活平衡,不只有每天在做研究,還有許多的運動局,例如籃球、跑步、爬山,甚至還有實驗室旅遊及僅有一次的老師歸國二十週年 DVLab 旅行,十分感謝教授的用心良苦。

再來,我很感謝我的家人們總能做我最強的支柱和後盾,讓我能無後顧之憂的專心讀完碩士並完成此份論文,每當做到疲乏的時候,家裡永遠是最好的避風港、充電站,讓我能稍微回家喘口氣好好休息後繼續奮戰。

再來當然要感謝在這兩年中遇到的實驗室夥伴們,很謝謝 R10 的學長姐 Gordon、Jasmine、Arvind、Anita、嘉豪、謹譯、慕德,不論是修課上、研究上、或是人生規劃上,你們總是不厭其煩回答我的各種疑問。謝謝同屆 R11 的失業救濟戰友:文山兄弟黨-子瑜和彥儒老哥,以及竣哥,這兩年總是和你們打打鬧鬧吃吃喝喝,從碩零進來跟竣哥陌生,還要另外開群組討論怎麼回覆竣哥、到一起開始架構起 GV tool、中間一起跟教授去跑路跑、然後轉眼間到了碩二上一起焦慮

找工作跟刷 leetcode、到碩二下換成焦慮論文,於是被推坑荒野亂鬥到現在三個月準備邁入無課一萬盃、還在最水深火熱的五月在兩次咪挺前去了一趟日本,很謝謝彥儒老哥在碩論最忙的五月排了一趟日本行,雖然文山兄弟黨都要退租還是沒去過你們家,但很謝謝你們讓我的碩班生活多了許多精彩。最後當然不能忘記感謝 R12 和 R13 的學弟妹們(雖然只有虹伶姐是學妹),謝謝 Wish、Bob、虹伶姐、建亨、瀞桓、亦翔、翔淳,常常也受到你們的幫助,不論是問問題、一起打 CAD 比賽、向你們要論文實驗需要的 design、講一些幹的、或是被你們詢問問題時都能收穫很多,尤其感謝翔淳和亦翔在最後一個實驗衝刺時幫了我很大的忙。雖然 R13 的學弟們只有在咪挺和實驗室宜蘭遊時遇到,但跟你們玩真的很好玩,尤其可以直接湊人十排荒野亂鬥真的很爽,之後一定有機會再見。

同時也很感謝助理 Sherry,謝謝 Sherry 和 Sherry 的先生偶爾投餵國外來的很酷的零嘴,讓每天都窩在實驗室的我能夠解嘴饞,也很謝謝 Sherry 對帳務的專業,讓實驗室每年的經費都能有條不紊的被使用,也讓我買到用起來很舒服的簡報筆、電競螢幕和機械鍵盤。

還有很謝謝跑步團 Ric、John、Wish、彥儒、瀞桓、昊晨,一起以路跑為目標,巔峰時期一週二到三練,讓我不只每天坐在電腦桌前而壞了身體健康,也讓我重新愛上了跑步,當成一個固定紓壓的管道,也在畢業前半年陸續達到了自己目標:台北馬初半馬破二(109分鐘)、台大校馬 5km 達到配速 4:17(24分鐘)、puma 10km 也跑進前百名(48分鐘)。

我也很謝謝這一路上願意錄取我當實習生的各公司主管們,讓我汲取業界經驗,也更好在做研究發想演算法時以實習經驗做過的事情套用進來。也很謝謝女朋友在我做研究壓力大到不行時會陪我出去透透氣放空沈澱一下,休息是為了走更長遠的路,沈靜過後總是能充飽電繼續重拾熱情衝刺研究。

最後我一定要感謝的是竣哥的實驗室椅子,謝謝這個椅子讓我每天都能落實 包包不落地政策,讓我的書包總能保持乾淨。

要感謝的人事物不勝枚舉,非常感謝你們在我的求學旅途中幫助、支持、鼓勵我,有你們才能讓我的碩班生活順利結束,願我們情誼長存。

陳孟宏 2024

# 中文摘要

由於IC設計規模和複雜度的不斷增長,RTL設計中的除錯變得越來越具有挑戰性。傳統上,工程師會生成測試模式並分析密集的波形文件,以追踪模擬結果,並與參考模型的正確結果進行比較。這個過程非常耗時且困難,因為涉及的信號眾多,包括輸入信號、輸出信號、內部信號和存儲器端口信號。

本論文介紹了我們的錯誤定位工具,可以自動過濾不相關的信號並突出顯示 最有可能與錯誤相關的信號。通過根據信號的懷疑程度進行排序,並識別這些信 號影響條件語句的控制路徑,該工具引導工程師找到最可能的問題區域。這顯著 減少了除錯的時間和精力,使工程師能夠專注於最相關的信號和控制路徑,從而 簡化了除錯密集波形和廣泛信號數據的複雜任務。這種方法將傳統上艱巨的 RTL 除錯任務轉變為更加可管理和高效的過程。

關鍵字:錯誤偵測、斷言、通用驗證方法學、驗證環境、積體電路設計

# **Abstract**

Debugging in RTL design is increasingly challenging due to the growing scale and complexity of IC designs. Traditionally, designers generate test patterns and analyze dense waveform files to trace simulation results and compare them with the golden results from a reference model. This process is time-consuming and difficult because of the numerous signals involved, including input, output, internal, and memory port signals.

This thesis introduces a novel bug localization tool that automates the filtering of unrelated signals and highlights those most likely associated with bugs. By ranking signals based on their suspected degrees and identifying the control paths where these signals influence conditional statements, the tool guides designers to the most likely problem areas. This significantly reduces debugging time and effort by allowing designers to focus on the most relevant signals and control paths, thereby simplifying the complex task of debugging dense waveforms and extensive signal data. This approach transforms RTL debugging from a traditionally arduous task into a more manageable and efficient process.

doi:10.6342/NTU202403664

Keywords: Bug Diagnosing, Assertion, UVM, Verification Environment, Integrated Cir-

cuit Design

# **Contents**

|         |       | F                                       | Page |

|---------|-------|-----------------------------------------|------|

| Ackno   | wledg | ements                                  | i    |

| 中文擂     | 要     |                                         | iv   |

| Abstra  | act   |                                         | V    |

| Conte   | nts   |                                         | vii  |

| List of | Figur | res                                     | X    |

| List of | Table | es                                      | xiii |

| Chapt   | er 1  | Introduction                            | 1    |

| 1       | 1.1   | Problem Statement and Motivation        | 1    |

| 1       | 1.2   | Related Works                           | 3    |

| 1       | 1.3   | Contributions                           | 6    |

| 1       | 1.4   | Thesis Organization                     | 8    |

| Chapt   | er 2  | Background Knowledge                    | 10   |

| 2       | 2.1   | Terminology Definitions                 | 10   |

| 2       | 2.2   | SystemVerilog Assertions                | 12   |

| 2       | 2.3   | Verification Approaches for RTL Designs | 13   |

|         | 2.3.1 | Simulation-Based Verification           | 14   |

|         | 2.3.2 | Formal-Based Verification               | 14   |

doi:10.6342/NTU202403664

|       | 2.3.3 | Assertion-Based Verification                                | 45 |

|-------|-------|-------------------------------------------------------------|----|

|       | 2.4   | UVM                                                         | 16 |

| :     | 2.5   | Third Party Tools Utilized in Our Flow                      | 20 |

|       | 2.5.1 | SDM—Output Matcher                                          | 21 |

|       | 2.5.2 | HARM—Assertion Miner                                        | 21 |

|       | 2.5.3 | Pyverilog—Code Analyzer                                     | 21 |

|       | 2.5.4 | Icarus Verilog—Simulator                                    | 22 |

|       | 2.5.5 | Synopsys VCS—Simulator                                      | 22 |

|       | 2.5.6 | Synopsys VC Formal—Formal Verifier                          | 23 |

| Chapt | ter 3 | Overview of the Bug Localization Flow                       | 24 |

|       | 3.1   | How Our Tool Guides Designers to Debug                      | 24 |

|       | 3.2   | The Architecture of Our Framework                           | 25 |

|       | 3.3   | Relation between the Design and Assertions                  | 29 |

|       | 3.4   | Assumptions to the Design                                   | 31 |

|       | 3.5   | Basic Categories for RTL Designs                            | 33 |

| Chapt | ter 4 | Preparation Phase : Configuration File Setting              | 38 |

|       | 4.1   | Configuration File Parameters                               | 38 |

|       | 4.2   | Setting the Configuration File through User Interface       | 46 |

| Chapt | ter 5 | Assertion Generation Phase: Valid Assertion Mining from the |    |

| DUV   |       |                                                             | 49 |

|       | 5.1   | Overview of the Assertion Mining Algorithm                  | 49 |

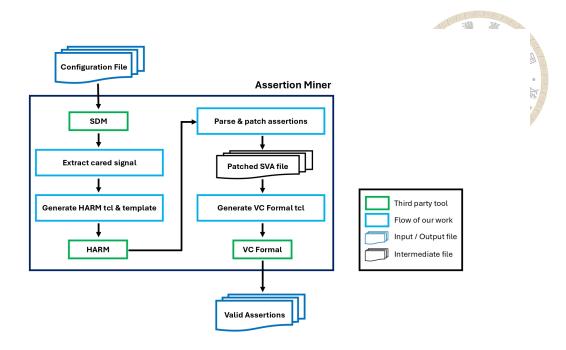

|       | 5.2   | Assertion Mining by HARM                                    | 51 |

|       | 5.3   | Formal Verifying Assertions by VC Formal                    | 54 |

| Chapter 6  | Assertion Validation Phase : Suspected Assertion Screening  | 58                |

|------------|-------------------------------------------------------------|-------------------|

| 6.1        | Overview of the Suspected Assertion Screening Algorithm     | 58 <sub>101</sub> |

| 6.2        | Assertion Pattern Generation Algorithm                      | 60                |

| 6.3        | Automatic Testbench Generation Algorithm                    | 65                |

| 6.4        | Results Comparison with the Reference Model                 | 70                |

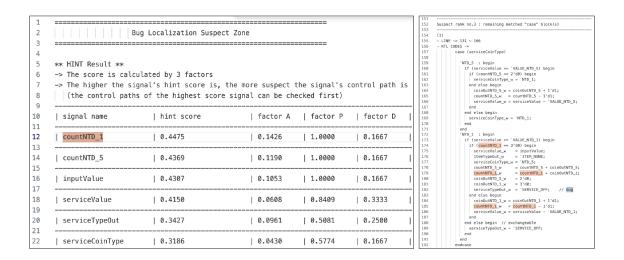

| Chapter 7  | <b>Bug Localization Phase : Bug Localizing in RTL Codes</b> | <b>79</b>         |

| 7.1        | Mapping Suspected Assertions to RTL Codes                   | 80                |

| 7.2        | Weighting Hint Signals                                      | 82                |

| 7.3        | Bug Localization Results and Debugging Hints for Designers  | 87                |

| Chapter 8  | <b>Experimental Results</b>                                 | 90                |

| 8.1        | A Brief Overview of the Blind Test Case                     | 90                |

| 8.2        | A Brief Overview of the Demo Cases                          | 94                |

| 8.3        | Results                                                     | 102               |

| Chapter 9  | Conclusion and Future Work                                  | 107               |

| 9.1        | Conclusion                                                  | 107               |

| 9.2        | Future Work                                                 | 108               |

| References |                                                             | 110               |

| Appendix A | — Input Pattern Format                                      | 116               |

| Appendix B | 3 — Output Result Format                                    | 118               |

# **List of Figures**

| 1.1 | The example of debugging process <b>without</b> our tool                     | 2  |

|-----|------------------------------------------------------------------------------|----|

| 1.2 | The example of debugging process with our tool                               | 3  |

| 2.1 | The example of VCD file. (a) text format, (b) visualization as a waveform    | 11 |

| 2.2 | The example of the (a) immediate assertion, and (b) concurrent assertions    | 13 |

| 2.3 | UVM's fundamental architecture                                               | 17 |

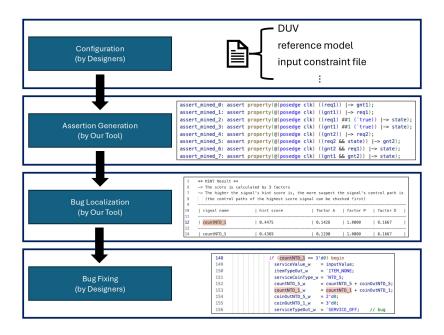

| 3.1 | The flow of guiding designers to do bug localization with our tool           | 25 |

| 3.2 | The overview of our framework                                                | 26 |

| 3.3 | The configuration file template                                              | 27 |

| 3.4 | The detailed flow of Assertion Miner                                         | 28 |

| 3.5 | Demonstration of bug localization results: Sorted Hint Signals and Sus-      |    |

|     | pect Control Paths                                                           | 29 |

| 3.6 | The relationship between the DUV, the reference model, and assertion         |    |

|     | candidates                                                                   | 31 |

| 3.7 | The sample waveforms illustrating the input valid signal                     | 34 |

| 3.8 | The sample waveforms illustrating the output valid signal                    | 36 |

| 3.9 | The block diagram example of the DUV containing SRAM (left) or DRAM          |    |

|     | (right)                                                                      | 37 |

| 4.1 | The examples illustrating the configuration file parameters                  | 45 |

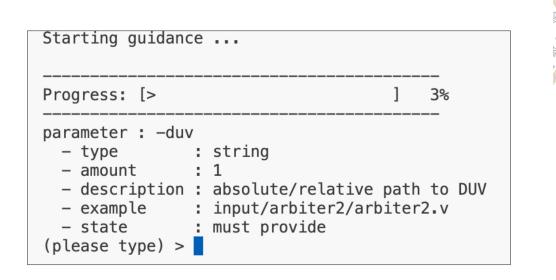

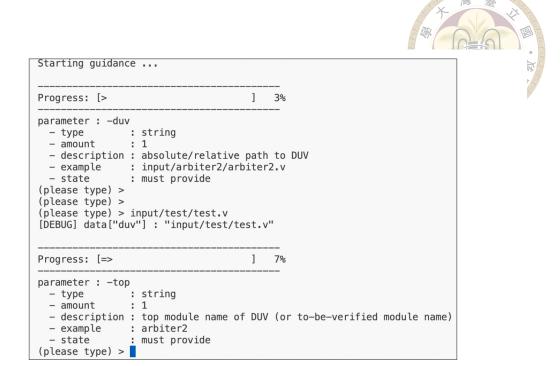

| 4.2 | The demonstration of the configuration file user interface (start setting) . | 47 |

| 4.3 | The demonstration of the configuration file user interface (successfully set |    |

|     | for string or int type)                                                      | 48 |

| 4.4 | The demonstration of the configuration file user interface (successfully set | kir .        |

|-----|------------------------------------------------------------------------------|--------------|

|     | for array type and map type)                                                 | 48           |

| 5.1 | The illustration of concepts in SDM's algorithm includes: (a) sequential     |              |

|     | matching, (b) approximate string matching, and (c) sequential matching       |              |

|     | in the set cover problem                                                     | 51           |

| 5.2 | The example of HARM's template includes: (a) the command used to             |              |

|     | automatically generate the template, and (b) the basic template produced     |              |

|     | by the aforementioned command                                                | 52           |

| 5.3 | The comparison of the template before and after applying the "Modify_HARM    | _Template()" |

|     | function includes: (a) the original basic template generated by HARM,        |              |

|     | and (b) the modified template produced by our tool                           | 53           |

| 5.4 | The example of the assertion log file generated by HARM                      | 54           |

| 5.5 | The example of the DUV with patched assertions                               | 55           |

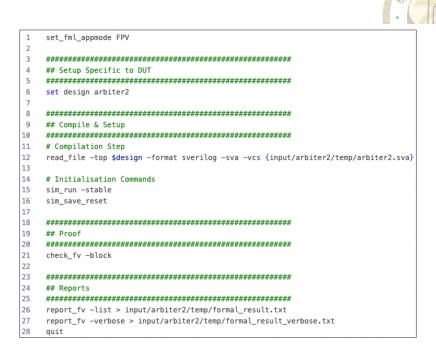

| 5.6 | The example of VC Formal setup                                               | 56           |

| 5.7 | The example of VC Formal report                                              | 56           |

| 5.8 | The illustration of the state space relationship among the golden assertion  |              |

|     | provided by designers, the reference model, and the DUV                      | 57           |

| 6.1 | The illustration of the concept behind the "Generate Assertion Pattern Al-   |              |

|     | gorithm"                                                                     | 63           |

| 6.2 | The illustration of the concept of "output valid interval" and "output valid |              |

|     | duration"                                                                    | 65           |

| 6.3 | The illustration of the signal dependency among input activated constraints  | 69           |

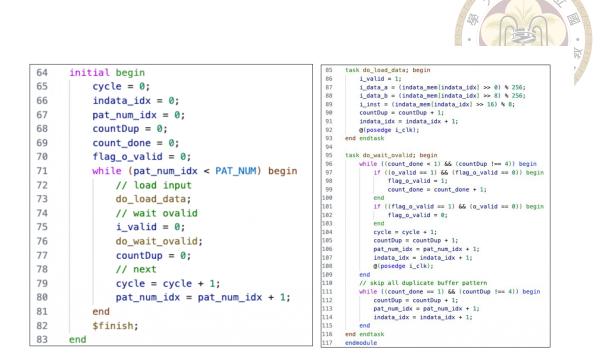

| 6.4 | The example of generated testbench (basic declaration)                       | 70           |

| 6.5 | The example of generated testbench (load data, wait ovalid task)             | 71           |

| 6.6 | The example of generated testbench (has input activation constraint)         | 71           |

| 6.7 | The example of comparing the results between the reference model and         |              |

|     | the DUV (no output valid signal)                                             | 74           |

| 6.8 | The concept of comparing the results between the reference model and the     |              |

|     | DUV using UVM's monitor and scoreboard (has output valid signals)            | 75           |

| 6.9  | The example of comparing the results between the reference model and             | ON  |

|------|----------------------------------------------------------------------------------|-----|

|      | the DUV (has output valid signals)                                               | 5   |

| 6.10 | The illustration of the concept behind the "Hauristic Method for Assertion       | 700 |

|      | Filtering Algorithm"                                                             | 3   |

| 7.1  | The example illustrating the categorization method described in [1] 82           | 2   |

| 7.2  | The illustration of the concept of control branches in $factor_P$ 85             | 5   |

| 7.3  | The example of sorted hint signals provided to designers                         | 3   |

| 7.4  | The example of the suspected control path containing bugs                        | 3   |

| 7.5  | The example of the information used to calculate the score of hint signals       |     |

|      | provided to designers                                                            | 9   |

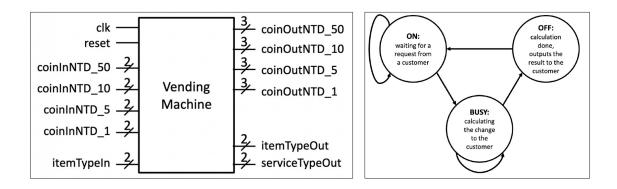

| 8.1  | Spec of Vending Machine                                                          | 1   |

| 8.2  | The debugging process from the designer's perspective                            | 3   |

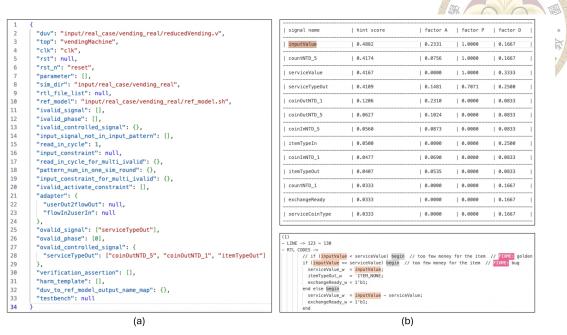

| 8.3  | (a) Configuration setting, and (b) final bug localization result of Vending      |     |

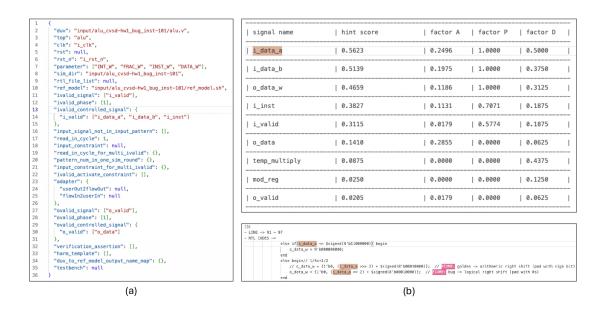

|      | Machine                                                                          | 4   |

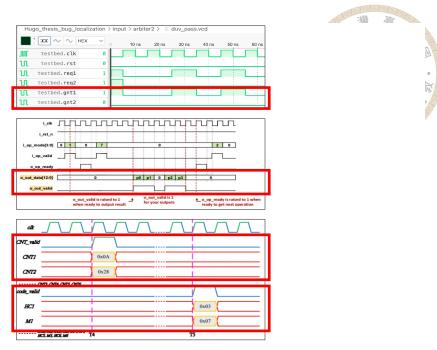

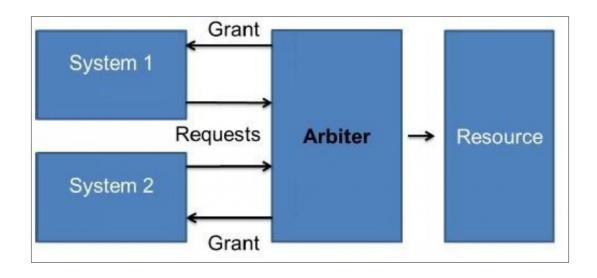

| 8.4  | Spec of Arbiter                                                                  | 5   |

| 8.5  | (a) Configuration setting, and (b) final bug localization result of Arbiter . 96 | 5   |

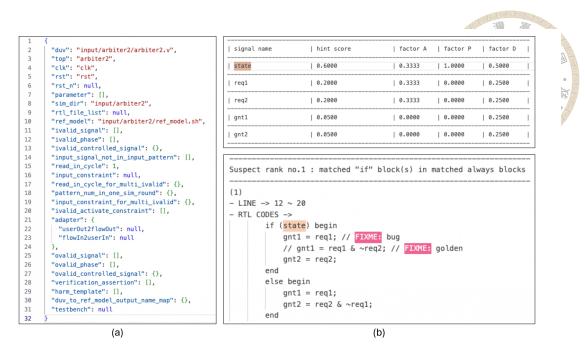

| 8.6  | Spec of ALU                                                                      | 7   |

| 8.7  | (a) Configuration setting, and (b) final bug localization result of ALU 97       | 7   |

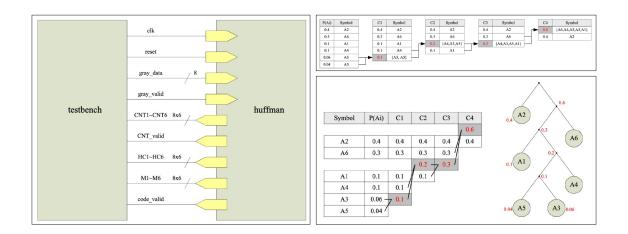

| 8.8  | Spec of Huffman Encoder                                                          | 9   |

| 8.9  | (a) Configuration setting, and (b) final bug localization result of Huffman      |     |

|      | Encoder                                                                          | )   |

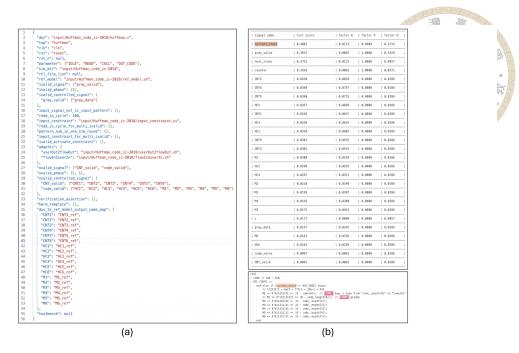

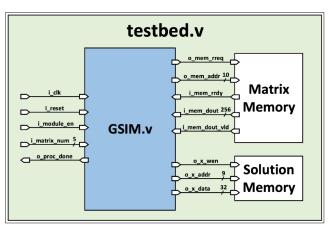

| 8.10 | Spec of GSIM                                                                     | 1   |

| 8.11 | (a) Configuration setting, and (b) final bug localization result of GSIM 10      | 1   |

| 8.12 | Spec of Convolution Engine                                                       | 3   |

| 8.13 | (a) Configuration setting, and (b) final bug localization result of Convo-       |     |

|      | lution Engine                                                                    | 3   |

| A.1  | The example to illustrate the concept of the input format                        | 7   |

| B.2  | The example of the output format in a CSV file                                   | 9   |

# **List of Tables**

| 8.1 | The Ranking of Hint Signals of DUVs in Section 8.1 and 8.2           | 104 |

|-----|----------------------------------------------------------------------|-----|

| 8.2 | Design scale of DUVs in Section 8.1 and 8.2                          | 104 |

| 8.3 | The Number of Assertions of DUVs in Section 8.1 and 8.2              | 105 |

| 8.4 | Computational Time and Memory Utilization of DUVs in Section 8.1 and |     |

|     | 8.2                                                                  | 105 |

doi:10.6342/NTU202403664

# **Chapter 1 Introduction**

This chapter lays the groundwork for the thesis by presenting the problem statement and motivation, reviewing related works, highlighting the contributions of the research, and outlining the organization of the thesis. Section 1.1 defines the research problem and explains the motivation behind addressing this issue, emphasizing its significance in the field. In section 1.2, a review of existing literature and related works is provided, illustrating the current state of research and identifying gaps that this thesis aims to fill. In section 1.3, the key contributions of the research are outlined, showcasing the novel aspects and advancements introduced by this work. Section 1.4 provides a structured overview of the thesis and details the content and focus of each chapter to guide the reader through the document.

### 1.1 Problem Statement and Motivation

In the process of RTL design, designers inevitably encounter situations that require debugging. However, as the scale and complexity of IC designs increase, the debugging process becomes critically challenging. Typically, designers generate test patterns to target the RTL design, spend significant time tracing the simulation results in waveform files, and compare them with the golden results produced by a reference model written in a

doi:10.6342/NTU202403664

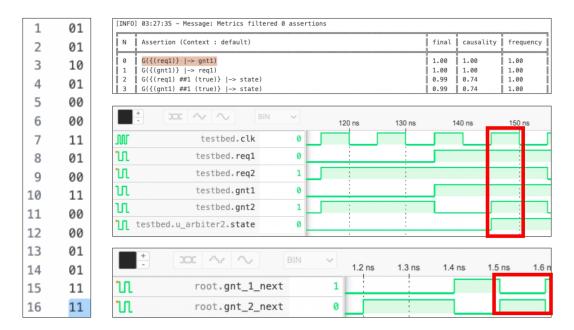

high-level language like C/C++ or Python. However, as shown in Fig. 1.1, waveforms are usually very dense (right figure) and contain numerous signals to be filtered (left figure), including input, output, internal, and memory port signals, making bug diagnosis and localization extremely difficult.

Figure 1.1: The example of debugging process without our tool

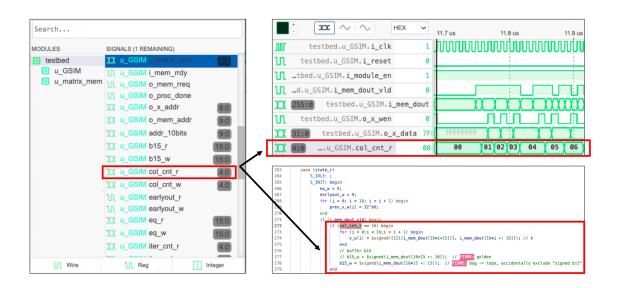

Hence, a bug localization tool that can automatically filter out unrelated signals and focus on a few highly probable signals would be extremely beneficial. This tool will rank signals by their suspected degrees and identify the control paths (e.g. always blocks, if/ case statements) where these signal candidates control the conditional statements. Designers could then follow the tool's guidance to begin debugging from the most suspected zones, significantly reducing debugging time by narrowing down the search space for potential bugs. This thesis successfully develops such a bug localization tool. As illustrated in Fig. 1.2, unlike in Fig. 1.1, our tool allows designers to focus on the most suspected signals related to the bug's root cause (e.g. the signal  $col\_cnt\_r$ ). Designers can start debugging by observing the behavior of these signals in the waveform file or examining the control path's coding logic within the RTL design. The tool also extracts and provides

these control paths, significantly aiding designers in bug detection. This approach prevents designers from having to sift through dense waveforms and numerous signals from scratch, effectively eliminating the "needle in a haystack" problem.

Figure 1.2: The example of debugging process with our tool

#### 1.2 Related Works

In the IC design verification process, beyond the traditional methods of simulation-based and formal verification, there is an approach that enhances both: "assertion-based" verification [2]. By embedding assertions [3] within the design or testbench, these assertions are checked during simulation or formal verification to ensure the design behaves as expected, aiding in the early detection of errors by monitoring design behavior. Assertion-based verification leverages the strengths and mitigates the weaknesses of simulation-based and formal verification. For example, assertions can enhance simulation-based verification by catching errors early, while formal verification can be used to prove critical properties that are difficult to cover with simulation alone.

However, writing assertions is a time-consuming and error-prone task, and the effectiveness of assertion-based verification depends on the quality and coverage of the assertions. To address this, many papers have proposed methods for automatically generating assertions. These include using decision tree-based algorithms on simulation results to mine assertions and applying formal verification to remove incorrect ones [4–7], using automatic test pattern generation (ATPG) algorithms [8], or abstracting between the RTL and its transaction-level model (TLM) for assertion-based verification [9, 10]. However, these methods often limit assertions to specific templates or applications, such as mining for security detection [11], and may not generate temporal assertions.

To overcome these limitations, other methods have been proposed, such as adopting any linear temporal logic (LTL) formula defined by designers, mining propositions from simulation traces, permuting combinations in designer-provided templates, and verifying correctness [12, 13]. Recently, large language models (LLMs) like GPT-4 have been used to generate and reason about assertions based on RTL design and designer specifications [14]. Although this approach is still immature and requires curated datasets, careful guidance, and significant costs for GPT-4 tokens, it represents a pioneering effort in assertion mining algorithms.

While these papers focus on automatically generating assertions, they do not consider the quality of the generated assertions or use this information to guide designers in bug localization. Therefore, another research focus is on proposing various metrics to evaluate and rank assertions based on different aspects, depending on the designer's intent. Assertion quality can be assessed by code coverage in RTL codes [15], activation frequency in simulation runs, correlation with other assertions through contingency tables [16, 17], belief-fail rate by analyzing absent scenarios in the simulation trace [18], or static analysis

between the assertion and the RTL code to evaluate importance, complexity, and dominance [19, 20].

Although there are various approaches to verify RTL designs, including simulation-based, formal verification-based, and assertion-based methods, effectively utilizing verification results to automatically detect and localize potential bugs is a critical challenge in modern IC development due to increasing design complexity and scalability. Simulation-based verification, while widely used, is inherently incomplete because it is impractical to exhaustively simulate all possible patterns. Formal techniques like model checking promise to address this issue through comprehensive state-space traversal but suffer from scalability issues with complex designs.

Several works have focused on automatic bug localization, which can be categorized into three main approaches: analysis-based, ML-based, and assertion-based. In analytical methods, some approaches [21] prioritize suspected bug locations by analyzing whether control path statements affect erroneous output signals or whether masking the data path impacts the erroneous output, calculating a confidence score for RTL lines. However, this method is only suitable for small, specific designs. Other papers [22, 23] use dynamic approaches, applying simulation patterns and extracting erroneous results compared to a golden reference, then forming a constraint formula for the unexpected result and using word-level satisfiability (SAT) solvers to identify potential bug candidates, but they encounter similar limitations as [21]. Additionally, [24] combines model checking with Bayesian networks to analyze counterexample hints and guide potential buggy subregions.

Machine learning techniques have also been proposed to predict possible bug locations [25, 26], but collecting sufficient training data of RTL designs with inserted bugs

that cover numerous designs and bug types remains a critical challenge. To address the scalability issues of formal techniques and the accuracy concerns of machine learning, assertion-based bug localization offers a compromise. Papers like [27] perform numerous simulation runs to generate assertions based on simulation traces, viewing common assertions as the most suspected candidates and mapping them back to RTL codes. [28] mines assertions from passing simulation traces, treating them as golden assertions, and uses these with additional simulations to localize possible bug zones by analyzing where assertions fail. [1] enhances counterexamples by inserting redundant propositions into assertions from failed simulation traces, ranking these suspected assertions and mapping them back to RTL codes by analyzing the control paths with antecedent signals.

However, these papers often rely solely on information from the buggy design and use intuitive methods to determine whether the mined assertions are golden or suspected, which may be inaccurate without considering the actual specification or reference model behavior. Therefore, in the next section, we will explore the new directions our work addresses, highlighting the advantages and contributions it brings to the field.

### 1.3 Contributions

In our work, we aim to provide an end-to-end automated approach for bug localization by generating assertions for the target design and identifying the most suspected bug positions, offering guidance to designers to assist in the debugging process. Our contributions are as follows:

1. **Development of a comprehensive verification flow**: We have created an end-toend flow for building a verification environment aimed at bug localization. This

doi:10.6342/NTU202403664

flow encompasses automatic assertion generation, assertion ranking and filtering, and bug localization within RTL code sections. Designers only need to provide the target design and basic settings, as detailed in Chapter 4, to receive guidance on the most suspected bug positions to begin their debugging process.

- 2. Adaptability to various RTL designs: Our approach is adaptable to a wide range of RTL designs, not just specific ones like the RISC-V processor as seen in previous works. This provides flexibility and broad applicability in the verification process.

- 3. **Handling diverse bug types**: Beyond generalizing RTL designs, our method is also versatile with respect to different types of bugs. It is not restricted to simple mutations (e.g. changing "<" to ">") and is applicable to both safety and liveness bugs, as discussed in Chapter 2.

- 4. **Accurate bug localization hints**: We have developed a metric to evaluate and rank suspected signals that may be causing the bug. Experiments demonstrate our ability to accurately identify the signal with the highest suspected score, as elaborated in Chapter 8.3.

Since our work is an end-to-end tool covering four phases—preparation, assertion generation, assertion validation, and bug localization—each phase can be explored as a separate research direction. To streamline our entire workflow, we utilize several off-the-shelf third-party tools. Below, we highlight the original contributions of our work:

1. **Configuration settings in the preparation phase**: We design a series of parameters to build a verification environment for general RTL designs, not limited to specific types such as ALU, MIPS, or RISC-V.

- 2. Constrained random simulation method in the assertion validation phase: After automatically generating numerous assertions using a third-party tool [29], we propose a constrained random simulation method to select only hundreds of useful assertions from tens of thousands, aiding our bug localization process.

- 3. **Metrics in the bug localization phase**: After selecting the useful assertions, we map them back to the RTL code [1]. We design a metric to calculate the suspicious score related to bugs for each controlling signal, and locate the bug position on the control path of the most suspected controlling signal.

## 1.4 Thesis Organization

This thesis is organized into four main parts: introduction and background (Chapters 1-2), framework overview (Chapter 3), detailed component analysis (Chapters 4-7), and results with future directions (Chapters 8-9).

Chapter 1 provides an overview of the research problem, objectives, and the significance of the study.

In Chapter 2, essential background information and related work are discussed to provide context and foundation for the research.

While in Chapter 3, a comprehensive explanation of our bug localization framework is presented, outlining the overall methodology and approach.

Chapter 4 describes the initial setup process, including how to configure the files necessary for the framework.

In Chapter 5, detailed methods for generating valid assertions from the Design Under

Verification (DUV) are explained.

In Chapter 6, techniques for filtering and validating suspected assertions to narrow down potential bugs are discussed.

In Chapter 7, the process of localizing bugs within RTL codes using the filtered assertions is elaborated.

Chapter 8 presents the experimental findings, demonstrating the effectiveness of the proposed methods.

And finally Chapter 9 summarizes the research contributions and discusses potential future directions for further improvement and research.

# **Chapter 2 Background Knowledge**

In this chapter, we provide the necessary background knowledge for understanding the subsequent work. First, we explain several key terms that will be frequently used throughout the thesis (Section 2.1). Then, we introduce assertions and assertion-based verification in Sections 2.2 and 2.3, which are the core concepts of the thesis. Next, we elaborate on the architecture of the Universal Verification Methodology (UVM), a standardized methodology for verifying IC designs, where our work utilizes similar concepts to build the verification process (Section 2.4). Finally, we discuss the third-party tools used in our flow (Section 2.5).

## 2.1 Terminology Definitions

This section provides comprehensive definitions for key terms used throughout the thesis.

**Definition 2.1.1** (**Design Under Verification (DUV)**). The DUV is the specific IC design or module being tested and verified to ensure it functions correctly according to its specifications. Specifically, it refers to the target design in the verification process.

**Definition 2.1.2** (**Reference Model**). A reference model is a high-level, often abstract, version of the design that serves as a correct behavioral standard against which the DUV

doi:10.6342/NTU202403664

is compared during verification.

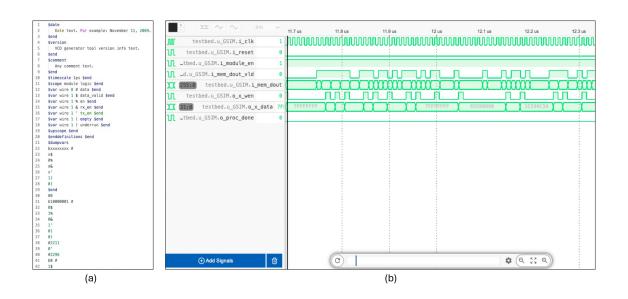

**Definition 2.1.3** (Value Change Dump (VCD)). A VCD file is a standard format for recording the activity of digital signals in a simulation. It logs changes in signal values over time, helping designers analyze the behavior of the DUV. The example of a VCD file in text format and its visualization as a waveform is illustrated in Fig. 2.1.

Figure 2.1: The example of VCD file. (a) text format, (b) visualization as a waveform

**Definition 2.1.4** (**Liveness Bug**). A liveness bug in RTL design indicates something good fails to happen (system does not make progress or complete tasks), which can be localized by our tool.

**Definition 2.1.5** (Safety Bug). A safety bug in RTL design indicates something bad happens (system enters an incorrect or hazardous state), which can also be localized by our tool.

**Definition 2.1.6** (Control Path Block). These are structures within an RTL design that dictate the flow of control in the circuit. Examples include:

- Always Block: Executes its statements whenever a specified condition or event occurs.

- If Statement: Executes a block of code based on whether a condition is true or false.

- Case Statement: Selects and executes one block of code from multiple options based on the value of an expression.

## 2.2 SystemVerilog Assertions

SystemVerilog Assertions (SVAs) are a powerful feature of the SystemVerilog hard-ware description and verification language [30]. SVAs enable designers to specify expected behaviors and properties of their digital designs formally. By embedding these assertions directly into the design or testbench, designers can automatically check that the design adheres to these specified behaviors during simulation or formal verification processes.

Assertions can be classified into two main types, as illustrated in Fig. 2.2:

- Immediate Assertions: These are checked at the moment they are encountered during simulation. They are typically used for simple checks within procedural code. We can view it as a *if* statement.

- Concurrent Assertions: These are continuously monitored throughout simulation time. They are used to specify complex temporal properties and sequences of events.

```

1 assert (A == B) $display ("OK. A equals B");

2 else $error("It's gone wrong");

(a)

1 assert property (!(Read && Write));

1 assert property (@(posedge Clock) Req |-> ##[1:2] Ack);

(b)

```

Figure 2.2: The example of the (a) immediate assertion, and (b) concurrent assertions

Using SystemVerilog Assertions helps in early detection and diagnosis of design errors, improving the reliability and robustness of the verification process.

# 2.3 Verification Approaches for RTL Designs

In this section, we delve into the various verification approaches used in RTL design. Verification is a critical step in the design process, ensuring that the design functions correctly and meets its specifications. We will explore three primary methods: simulation-based verification, formal-based verification, and assertion-based verification. Each of these methods has its unique strengths and limitations, and understanding them is essential for effective and efficient verification of complex IC designs.

#### 2.3.1 Simulation-Based Verification

Simulation-based verification is the most widely used method for verifying RTL designs. It involves simulating the design with a series of test vectors to check for correct functionality. This approach mimics the behavior of the design under different scenarios by applying input stimuli and observing the outputs.

#### • Key Features:

- Dynamic Nature: Simulation checks the design's behavior over time, allowing designers to observe how the design responds to a sequence of inputs.

- Flexibility: It can handle complex scenarios and interactions within the design, providing detailed insights into the design's performance.

- Visualization: Designers can visualize the simulation results using waveform viewers, which help in diagnosing and debugging issues.

#### • Limitations:

- Coverage: Achieving exhaustive coverage can be challenging, as it is impractical to simulate all possible input combinations and states.

- Time-Consuming: Simulations can be slow, especially for large and complex designs, making it difficult to verify all aspects of the design comprehensively.

#### 2.3.2 Formal-Based Verification

Formal-based verification uses mathematical methods to prove the correctness of a design with respect to its specifications. Unlike simulation, which tests the design against

a set of test cases, formal verification exhaustively explores all possible states and inputs to ensure the design's correctness.

#### • Key Features:

- Exhaustiveness: Formal verification can provide complete coverage by exploring all possible states and input combinations.

- Proof of Correctness: It can formally prove that certain properties hold true for the design, providing a higher level of assurance.

- Scalability Issues: Although powerful, formal methods can struggle with scalability, especially for large designs with complex state spaces.

#### • Limitations:

- Complexity: Setting up formal verification requires a deep understanding of both the design and formal methods, making it more complex than simulationbased verification.

- Resource-Intensive: Formal verification can be computationally expensive,

requiring significant time and computational resources.

#### 2.3.3 Assertion-Based Verification

Assertion-based verification combines elements of both simulation and formal verification. It involves embedding assertions, which are statements of expected behavior, directly into the design or testbench. These assertions are then checked dynamically during simulation or statically during formal verification.

#### • Key Features:

- Early Detection: Assertions help in early detection of design errors by continuously monitoring the design's behavior against specified properties.

- Reusability: Assertions can be reused across different verification environments, improving verification efficiency.

- Complementary: It complements both simulation and formal methods by providing a mechanism to check specific properties during the verification process.

#### • Limitations:

- Writing Assertions: The effectiveness of assertion-based verification depends

on the quality and coverage of the assertions, which can be time-consuming

and error-prone to write.

- Tool Support: Effective assertion-based verification requires good tool support for writing, checking, and debugging assertions.

#### 2.4 UVM

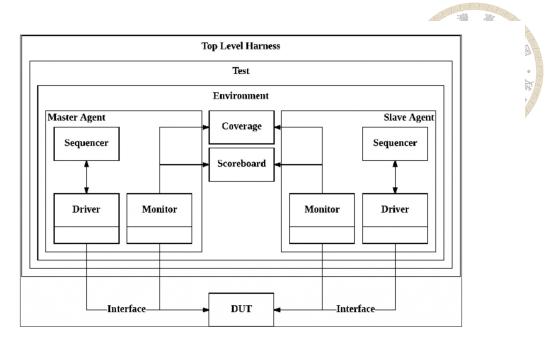

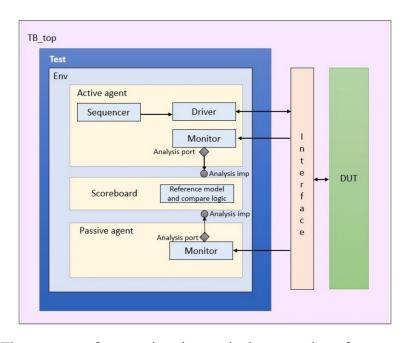

Universal Verification Methodology (UVM) is an advanced verification methodology for verifying IC designs [31, 32]. It is a standardized, comprehensive framework developed by Accellera, an industry consortium, to address the challenges associated with verifying complex designs in a systematic and scalable manner. UVM leverages object-oriented programming principles and builds on top of the SystemVerilog language to provide a robust and reusable verification environment. The basic architecture of UVM is shown in Fig. 2.3

Figure 2.3: UVM's fundamental architecture

#### • Key Components of UVM

#### 1. Verification Components:

- **Driver**: Drives stimulus to the Design Under Verification (DUV).

- Monitor: Observes the DUV's outputs and collects data for analysis.

- Sequencer: Manages the sequence of operations and drives the data through the driver.

- Agent: Combines driver, monitor, and sequencer to encapsulate a com plete verification environment for a specific interface or protocol.

#### 2. Testbench Structure:

- Environment: A container for all the components of the testbench, including agents, scoreboards, and coverage collectors.

- **Test**: Specifies the stimulus and configuration for the environment.

- Sequence: A series of transactions or operations applied to the DUV.

- Scoreboard: Compares the actual output of the DUV with the expected

output to check for correctness.

#### 3. Configuration and Factory:

- Configuration: UVM allows for easy configuration and reconfiguration

of the testbench components without modifying the code.

- Factory: A mechanism for creating objects dynamically, enabling greater flexibility and reuse of components.

- 4. **Phases**: UVM divides the verification process into well-defined phases, such as build, connect, run, and cleanup phases, to ensure orderly and predictable execution of the testbench.

- 5. **Transaction-Level Modeling (TLM)**: TLM allows communication between components at a high level of abstraction, improving simulation speed and simplifying the testbench architecture.

#### Benefits of UVM

- Reusability: UVM promotes reusability of verification components across different projects and designs, reducing development time and effort.

- Scalability: UVM's modular approach and standardized structure make it scalable for complex designs, allowing for easy expansion and maintenance of the verification environment.

- 3. **Consistency**: By following a standardized methodology, UVM ensures consistency in verification practices across different teams and projects, facilitating better collaboration and understanding.

- 4. **Efficiency**: UVM's automation features, such as the factory and configuration mechanisms, enhance verification efficiency by reducing manual intervention

and enabling rapid iteration and testing.

5. Comprehensive Coverage: UVM supports advanced verification techniques like constrained random stimulus generation, functional coverage, and assertions, ensuring thorough and robust verification of the DUV.

#### • Example Workflow in UVM

#### 1. Testbench Development:

- Define the testbench architecture using UVM components such as drivers,

monitors, sequencers, and agents.

- Implement the DUV interface and connect the UVM components to the DUV.

#### 2. Configuration:

- Configure the testbench components and specify the desired verification scenarios.

- Use the UVM configuration database to manage configuration settings dynamically.

#### 3. Stimulus Generation:

- Develop sequences to generate the desired stimulus for the DUV.

- Use constrained random generation and directed tests to cover different aspects of the design.

#### 4. Simulation and Analysis:

- Run simulations and collect coverage data.

- Use the scoreboard and functional coverage collectors to analyze the DUV's behavior and ensure it meets the specifications.

#### 5. Debugging and Refinement:

- Identify and debug issues using UVM's rich set of debugging tools and features.

- Refine the testbench and stimulus based on the results to achieve higher coverage and validation confidence.

By providing a detailed and systematic approach to verification, UVM plays a crucial role in ensuring the quality and reliability of modern IC designs. Hence, in our tool, we incorporate UVM concepts into our algorithm. For example, we generate constrained random patterns and apply these to both the DUV and the reference model, similar to the functions of the "sequencer" and "driver" in UVM. We then extract the valid output results from the DUV and compare them with the reference model's results for further analysis, akin to the roles of the "monitor" and "scoreboard" in UVM. By utilizing the UVM architecture, our tool constructs a complete verification environment that effectively supports the bug localization process.

## 2.5 Third Party Tools Utilized in Our Flow

In this section, we introduce the third-party tools integrated into our verification framework to enhance the efficiency and accuracy of the bug localization process. Each of these tools plays a vital role, contributing unique capabilities that complement our methodology. By leveraging these specialized tools, we create a robust and comprehensive verification environment. The following sections provide detailed descriptions of each tool and its specific function within our framework.

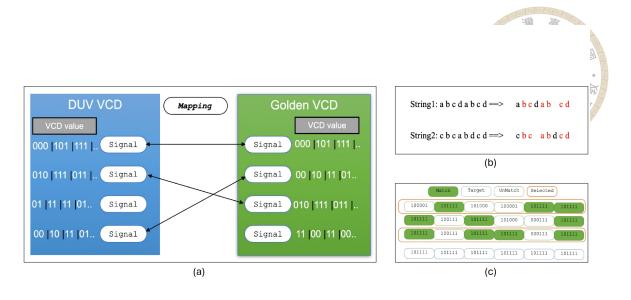

### 2.5.1 SDM—Output Matcher

SDM (Sequential Design Matching) [33] is a tool designed to analyze waveform files by comparing temporal patterns of specific signal occurrences. It superimposes correct and erroneous waveforms, identifies potential error locations, and generates a new consolidated waveform file. This allows engineers to use standard waveform viewers for quick error identification and correction. SDM is integral in validating the DUV by comparing its behavior with a reference model, enabling efficient error detection and localization.

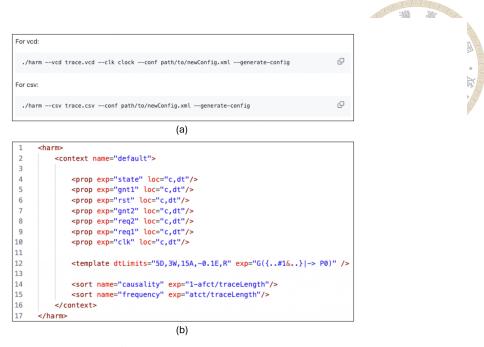

#### 2.5.2 HARM—Assertion Miner

HARM (Hint-Based Assertion Miner) [29, 34] is a tool crafted to produce linear temporal logic (LTL) assertions using user-specified hints and simulation traces from the DUV. It operates without requiring access to the DUV source code, relying exclusively on simulation data. By leveraging user-provided LTL templates, propositions, and ranking metrics, HARM refines its search space to generate high-quality assertions. This capability empowers verification engineers to integrate their expertise into the automated assertion generation process, enhancing verification efficiency and accuracy significantly.

## 2.5.3 Pyverilog—Code Analyzer

Pyverilog [35, 36] is an open-source hardware design and analysis framework written in Python. It provides a powerful toolset for parsing, analyzing, and transforming Verilog HDL (Hardware Description Language) code. In our verification framework, Pyverilog is utilized as a code analyzer to parse the RTL design, extract essential information, and perform static analysis. This tool helps in understanding the design structure, identify-

ing control paths, and generating intermediate representations that are crucial for further processing in the bug localization workflow.

### 2.5.4 Icarus Verilog—Simulator

Icarus Verilog [37, 38] is an open-source Verilog simulation and synthesis tool. It supports a wide range of Verilog standards and is widely used for simulation purposes. In our framework, Icarus Verilog serves as one of the primary simulators for running test patterns against the DUV. It generates simulation results that are used to compare the behavior of the DUV with the reference model, facilitating the identification of discrepancies and potential bugs. Its open-source nature and flexibility make it a valuable tool in our verification process.

### 2.5.5 Synopsys VCS—Simulator

Synopsys VCS (Verilog Compiler Simulator) [39, 40] is a highly advanced and widely used commercial simulator for RTL designs. It offers high-performance simulation capabilities, comprehensive debug features, and support for a variety of verification methodologies. In our verification framework, VCS is employed to perform detailed and high-fidelity simulations of the DUV. It helps in generating accurate simulation results that are essential for verifying the design's correctness and for subsequent bug localization steps. VCS's robust features and industry-standard reliability make it a critical component of our verification toolkit.

#### 2.5.6 Synopsys VC Formal—Formal Verifier

Synopsys VC Formal [41] is a formal verification tool that uses mathematical techniques to prove the correctness of digital designs. Unlike simulation-based approaches, formal verification exhaustively explores all possible states and scenarios to ensure that the design adheres to its specifications. In our framework, VC Formal is utilized to formally verify the assertions generated during the bug localization process. It helps in proving or disproving these assertions, providing a higher level of confidence in the design's correctness. VC Formal's rigorous analysis capabilities make it indispensable for ensuring thorough verification and robust bug localization.

## Chapter 3 Overview of the Bug Localization Flow

In this chapter, we begin by exploring how our tool intuitively guides designers through the debugging process (Section 3.1). Following this, we delve into the architecture of our framework, detailing the interplay between its various components (Section 3.2). Also, we examine the intricate relationship between the design and generated assertions, highlighting the critical role assertions play in aiding the bug localization process (Section 3.3). Finally, we make assumptions (Section 3.4) and categorize (Section 3.5) target designs for our tool.

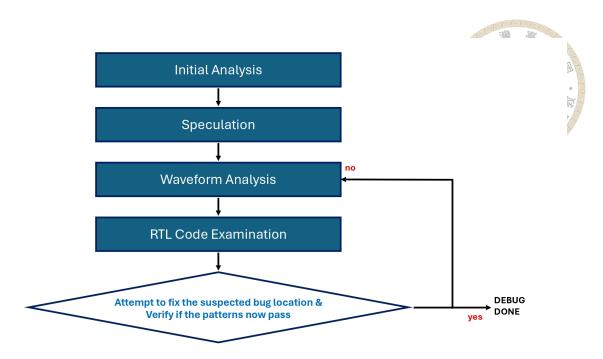

#### 3.1 How Our Tool Guides Designers to Debug

Our tool guides designers through a structured debugging process designed to enhance efficiency and accuracy. The flow in Fig. 3.1 begins with designers' setting up the configuration file and tailoring the tool to their specific design requirements. Following this initial setup, our tool takes over. First, it automatically generates a large number of assertions to address issues that would be time-consuming and error-prone to write manually. Then, it filters these assertions to isolate valid ones, further pinpointing potential

issues within the design.

Once the assertions have been processed, our tool identifies the most likely location of the bug, providing designers with a targeted area to investigate. This pinpointed approach significantly reduces the time and effort needed to locate and understand the root cause of the problem. Finally, designers use this information to fix the bug in the RTL code, completing the cycle of detection and correction. This systematic flow not only accelerates the debugging process but also enhances the reliability and performance of RTL designs.

Figure 3.1: The flow of guiding designers to do bug localization with our tool

#### 3.2 The Architecture of Our Framework

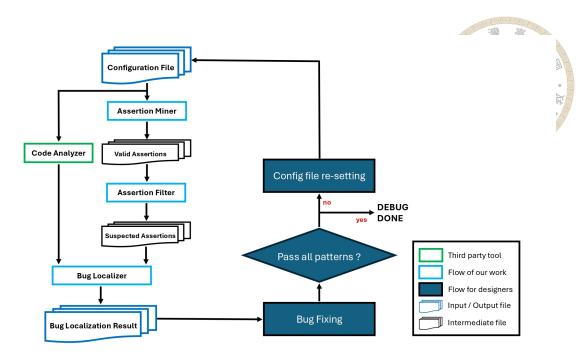

In this section, we will provide an overview of our framework, which is composed of four major parts as shown in Fig. 3.2.

1. **Preparation Phase—Configuration File**: The primary goal of this phase is to configure the settings for the subsequent phases. To start, designers should set the

Figure 3.2: The overview of our framework

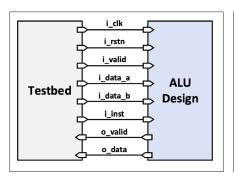

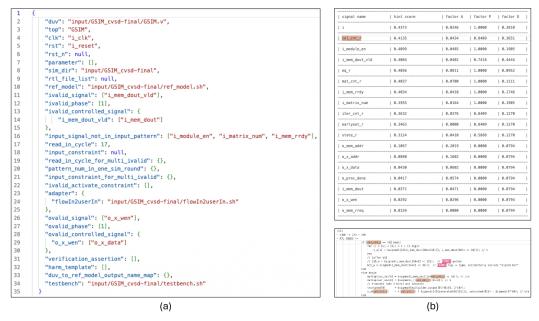

configuration file, as shown at the top of Fig. 3.2. This file contains crucial information for our tool to build the verification environment, including the path to the DUV, the module name to be verified, the clock signal name, whether the reset signal is negative or positive edge-triggered, and other more complex settings. The configuration file template is shown in Fig. 3.3, with detailed explanations provided in Chapter 4.

2. **Assertion Generation Phase - Assertion Miner**: With the configured settings, our objective in this stage is to automatically generate numerous valid assertions to comprehensively outline the operational scope of the DUV. The definition of *valid assertions* will be clarified later. As depicted in Fig. 3.4, we first use the third-party tool SDM to align output signals between the DUV and the reference model. Subsequently, our tool extracts and preprocesses the necessary information. We then utilize another third-party tool, HARM, which automatically extracts assertions from the DUV based on simulation results provided in the configuration file. These ex-

```

"top": null,

"clk": null,

"rst": null,

"rst_n": null,

"parameter": [],

"sim_dir": null,

"rtl_file_list": null,

"ref_model": null,

"ivalid_signal": [],

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

"ivalid_phase": [],

"ivalid controlled signal": {},

"input_signal_not_in_input_pattern": [],

"read_in_cycle": null,

"input_constraint": null,

"read_in_cycle_for_multi_ivalid": {},

"pattern_num_in_one_sim_round": {},

"input_constraint_for_multi_ivalid": {},

"ivalid activate constraint": [],

"adapter": {

"userOut2flowOut": null,

"flowIn2userIn": null

ovalid_signal": [],

"ovalid phase": [],

"ovalid_controlled_signal": {},

"verification_assertion": [],

"harm_template": [],

"duv_to_ref_model_output_name_map": {},

"testbench": null

```

(6)6<u>1</u>

潜意

Figure 3.3: The configuration file template

tracted assertions are integrated into the DUV and subsequently analyzed by another third-party tool VC Formal. This tool categorizes the assertions into *proven*, *falsified*, and *vacuous* states using formal verification techniques. From these, we select assertions in the proven state as our candidates for valid assertions, focusing only on correct signal implications relevant to the DUV for our bug localization process. Further details will be elaborated in Chapter 5.

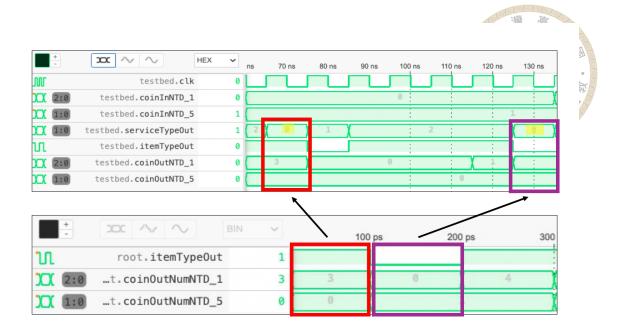

3. Assertion Validation Phase—Assertion Filter: In the Assertion Generation Phase, we produce many valid assertions as candidates, but they are not necessarily correct according to the reference model or the spec. Because the DUV may contain bugs relative to the reference model, assertions generated from the DUV's simulation results may also be flawed with respect to the reference model, even if they appear correct for the DUV. Therefore, the primary goal at this stage is to further filter and validate these assertions to determine which ones are genuinely valid for both the DUV and the reference model, and which are suspected, being valid for the

Figure 3.4: The detailed flow of Assertion Miner

DUV but failing against the reference model. Our algorithm retains these suspected assertions for the final phase of bug localization. The rationale behind this approach will be discussed in Section 3.3, and the detailed algorithms for this stage will be explored in Chapter 6.

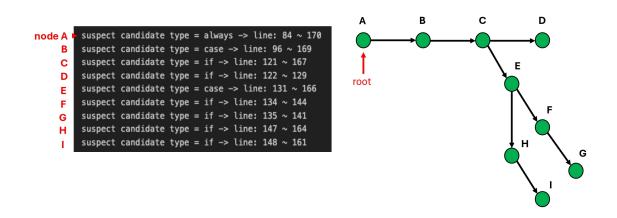

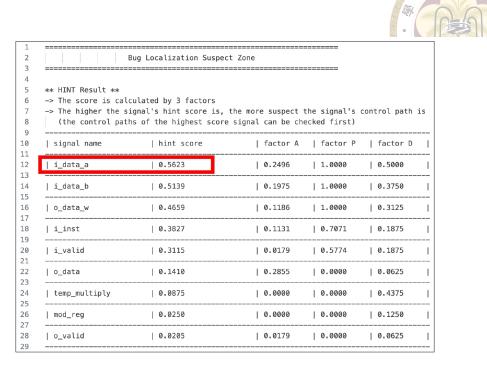

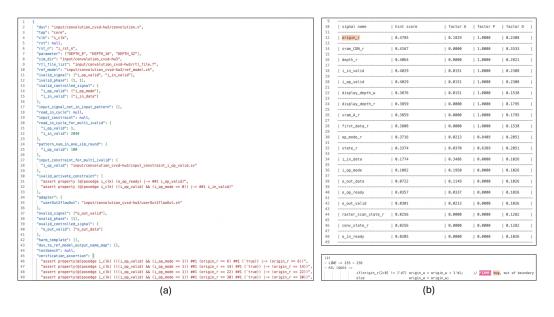

4. **Bug Localization Phase—Bug Localizer**: Before proceeding, let's discuss the final results we will provide to designers. As shown in Fig. 3.5, we offer two types of guidance to assist in debugging. First, the *Sorted Hint Signals* (left figure) lists a few signals, sorted by the likelihood of a bug appearing in the control path conditional statements associated with these signals. Second, the *Suspect Control Paths* (right figure) highlights specific code sections under suspect control paths for designers to check in sequence.

Referring back to Fig. 3.2, after obtaining the final assertion candidates from the Assertion Validation Phase, we use the filtering information of signals in the assertions' antecedents to calculate a hint score for each signal. The higher a signal's

hint score, the more likely a bug is present in its control path, forming the basis of the Sorted Hint Signals guidance.

Additionally, with the aid of Pyverilog, we extract the abstract syntax tree (AST) of the DUV. This allows us to identify line numbers, signals, assigned values, and other control path information. By combining this structural information with the signal hint scores, we can pinpoint Suspect Control Paths for designers, directing them to begin their debugging efforts there. Detailed explanations will be provided in Chapter 7.

Figure 3.5: Demonstration of bug localization results: Sorted Hint Signals and Suspect Control Paths

#### 3.3 Relation between the Design and Assertions

In Section 3.2 (Assertion Validation Phase), we noted that assertions in the proven state from VC Formal would serve as our valid assertion candidates. In this section, we will explain the relationship between the DUV, the reference model, and these valid as-

sertion candidates to clarify the rationale behind this choice.

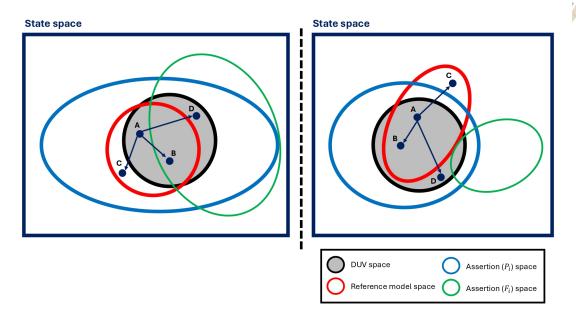

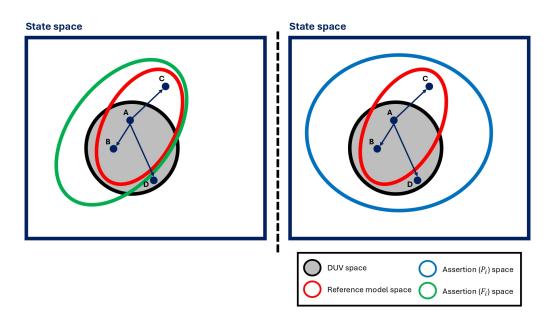

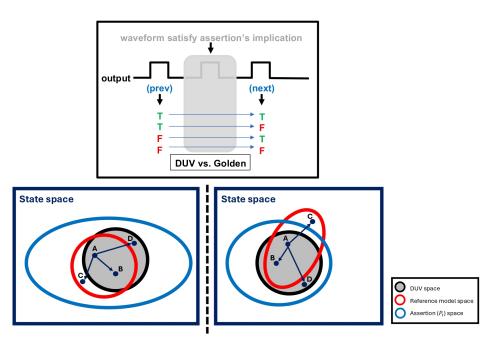

As depicted in Fig. 3.6, we assume the state space of the DUV is represented by the black circle (though we cannot precisely outline this space). The state space of the reference model is represented by red circles, which may overlap with the DUV's space. The overlapping area indicates shared functionality: starting from the same initial state and given the same input set, both the DUV and the reference model will transit to the same next state, producing identical output results (from point *A* to point *B* in Fig. 3.6).

For the assertions mined from HARM, we verify their correctness regarding the DUV using VC Formal, which categorizes them into *proven*, *falsified*, and *vacuous* states. Here, we focus on the *proven* and *falsified* states. Assertions in the falsified state (green circle) do not encompass the entire DUV state space, as a falsified status in formal verification means the DUV eventually reaches a counterexample for the assertion. Consequently, we cannot guarantee the relationship between the DUV and the falsified assertions, so we do not consider them as valid assertion candidates. However, assertions in the proven state (blue circle) consistently cover the DUV state space. Although we cannot determine the relationship between the reference model's state space and the proven assertions' state space (as shown in the left and right parts of Fig. 3.6), we can still utilize the proven assertions for the bug localization process.

If there is a bug in the DUV, starting from the same state and given an input set, the DUV will transit to a different state compared to the reference model. For instance, starting from the point A with a given input set, the reference model should transit to the point C, but the DUV transits to the point D. This unexpected behavior might be caused by a bug. Therefore, we will further examine this unexpected behavior using the waveforms

of assertions in the proven state that intersect with the unexpected waveform. Detailed explanations will be provided in Chapter 6.

Figure 3.6: The relationship between the DUV, the reference model, and assertion candidates

#### 3.4 Assumptions to the Design

In this section, we will outline the key assumptions underlying our algorithm with respect to the target DUV and its corresponding reference model. These assumptions are critical for ensuring the accuracy and effectiveness of our bug localization tool. Understanding these foundational premises will provide clarity on the conditions and constraints within which our tool operates.

For the DUV, the following assumptions are made based on its description language, circuit type, functionality, and input-output ports.

1. The DUV should be implemented in Verilog or SystemVerilog: In our implementation, most random simulation processes use the open-source third party tool

Icarus Verilog as simulator. This tool primarily supports (System) Verilog applications and has limited support for VHDL and other hardware description languages. Therefore, our tool handles only DUVs written in (System) Verilog.

- 2. **The DUV should be a sequential design**: In our work, we will not address the bug localization flow in combinational designs, as another algorithm, called Engineering Change Order (ECO), is used to identify and correct rectification points in combinational DUVs. This topic is beyond the scope of our discussion.

- 3. The DUV and the reference model should perform the same task: The reference model serves as a golden reference during the verification process. Ensuring it matches the RTL design allows for accurate comparison and validation, helping to identify discrepancies and bugs early in the design cycle. Besides, consistency between the two ensures that simulations in our flow provide meaningful insights and effective bug localization.

- 4. The DUV should have the same input ports as the reference model: In our simulation process, we assume that the DUV operates on the same input pattern as the reference model. This means both should have identical input ports, including the width and order of each input signal.

While for the reference model, We **do not** require it to have a similar structure to the DUV; instead, we treat it as a black box that operates on the same set of inputs as the DUV and outputs the expected results. The reference model can be implemented in any language, from hardware description languages like SystemVerilog to high-level languages such as C/C++ or Python. Additionally, we **do not** expect the reference model to follow any naming conventions related to the DUV, nor do we require it to match the

DUV's time series cycle-by-cycle.

- 1. The functionalities of the reference model should satisfy the spec. The reference model encapsulates the intended behavior and functionalities of the design. Ensuring the RTL design matches the reference model guarantees that the final hardware adheres to the specified requirements and behaves as intended.

- 2. The reference model is considered bug-free: The reference model serves as the gold standard against which the RTL design is verified. If the reference model contains bugs, it cannot provide a reliable baseline, leading to incorrect conclusions about the RTL design's correctness. Hence, considering the reference model as bug-free is essential for reliable verification, efficient debugging, and trustworthy simulation results.

#### 3.5 Basic Categories for RTL Designs

To meet the needs of our tool, we categorize the RTL designs into several aspects, each corresponding to specific parts of the configuration settings which will be discussed in Chapter 4. The following sections will introduce the specific cases we need to address:

#### 1. Input:

• Whether there exists (an) input valid signal to indicate the readiness of input data: In certain designs, there may be no input valid signal indicating the readiness of input data, whereas other designs incorporate at least one input valid signal that can be set high to indicate the validity of the input data. The sample waveforms in Fig. 3.7 illustrate different scenarios: from top to bottom,

they depict cases without an input valid signal, with one input valid signal, and with more than one input valid signal.

Figure 3.7: The sample waveforms illustrating the input valid signal

- Whether the data requires more than one cycle to input: In certain designs, input data is processed in a single cycle, indicating that the input valid signal, if present, remains active for only one cycle, as depicted in the top one of Fig. 3.7. Conversely, other designs input data over multiple cycles, as shown in the center and the bottom example of Fig. 3.7.

- The spec defines constraints between input signals: In some designs, certain input signals must adhere to constraints outlined in the spec. For instance, input points might need to be non-collinear. These constraints will be specified in the configuration file discussed in Chapter 4, and we will utilize the third-party tool VCS to handle these requirements.

- The format of input patterns provided by the designer to the DUV differs

from the format defined by our tool: In our tool, we establish a standard-

ized input format where the order of input signals in the pattern follows the declaration order in the DUV. Detailed guidelines will be provided in Chapter 4. However, variations in the designer's input format, such as different order of signals in input patterns, may lead to errors during random pattern generation and automatic input to the DUV. Therefore, in Chapter 4, we will discuss an approach akin to the adapter used in UVM architecture to address this challenge.

#### 2. Output:

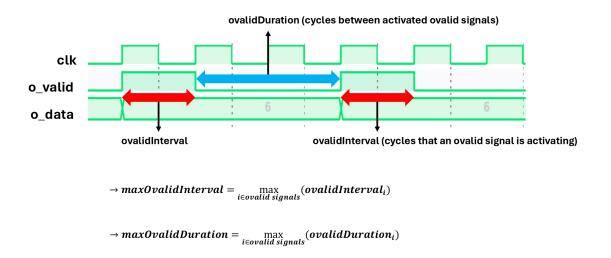

- Whether there exists (an) output valid signal to indicate the readiness of output results: In certain designs, there may be no output valid signal indicating the readiness of output results, whereas other designs incorporate at least one output valid signal that can be set high to indicate the validity of the output results. The sample waveforms in Fig. 3.8 illustrate different scenarios: from top to bottom, they depict cases without an output valid signal, with one output valid signal, and with more than one output valid signal.

- Whether the results requires more than one cycle to output: In some designs, the output results are generated in a single cycle, meaning the output valid signal, if present, lasts for only one cycle, as depicted in the bottom one of Fig. 3.8. Conversely, other designs output results over multiple cycles, as shown in the center example of Fig. 3.8.

- 3. Clock: In our work, we focus solely on synchronous designs due to the limitations of the open-source third-party tools we use. Consequently, we do not handle designs that involve different clock domains, clock gating, or other asynchronous techniques.

Figure 3.8: The sample waveforms illustrating the output valid signal

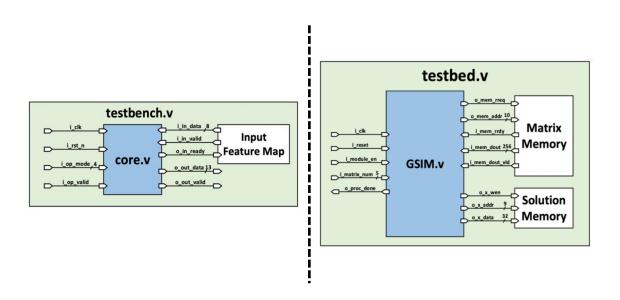

#### 4. Memory:

- The DUV contains SRAM: SRAM in an RTL design is used for high-speed, temporary data storage and retrieval, contributing to efficient data processing and control. Sometimes, the DUV will use SRAM to temporarily store a series of inputs for later use. The block diagram example is depicted on the left side of Fig. 3.9.

- The DUV contains DRAM: DRAM in an RTL design is used for large, costeffective data storage and buffering, supporting various applications that require extensive memory capacity and temporary data storage. Sometimes, the DUV will interact with the memory to frequently write and read data. The block diagram example is depicted on the right side of Fig. 3.9.

Figure 3.9: The block diagram example of the DUV containing SRAM (left) or DRAM (right)

# Chapter 4 Preparation Phase: Configuration File Setting

In this chapter, we will delve into the detailed parameter information required for the configuration file, a crucial component for setting up our tool. We will cover each parameter in depth to ensure that readers understand their significance and how to properly configure them (Section 4.1). Additionally, we will guide the reader through the process of setting the configuration file using our user interface, making the setup process intuitive and straightforward (Section 4.2). By the end of this chapter, we expect that the reader will have a comprehensive understanding of the configuration file parameters and the steps necessary to configure them correctly.

#### 4.1 Configuration File Parameters

In this section, we will introduce the 27 parameters in the configuration file, categorized into five groups. Some parameters are mandatory, such as the path to the DUV and the clock signal name, while others are optional, depending on the properties of the DUV, such as included RTL files and constraints for input signals. The introduction will proceed with an overview of the five categories, and examples of these settings can be found in

#### 1. **Design information**:

- -duv: (mandatory) Designers should provide either the absolute path or a relative path (relative to the root directory of our tool) to specify the location of the DUV.

- -top: (mandatory) In the verification process, we often employ a divide-and-conquer technique by verifying submodules individually instead of verifying the entire design starting from the top module. Therefore, designers should specify the particular module they intend to perform bug localization on and provide this information in the corresponding parameter. Our tool will treat this module as the pseudo top module.

- -clk: (mandatory) In a sequential design, the clock signal is essential as it governs the behavior and validity of other signals. Designers need to specify the clock signal name here, since the clock signal in different DUVs may not follow common naming conventions such as "clk" or "i clk".

- -rst / -rst\_n: (mandatory) In a sequential design, a reset signal may be used to initialize all internal or output values. This reset signal can be either positive or negative edge-triggered, activating on the rising or falling edge of the clock signal, respectively, and corresponds to -rst or -rst\_n ("\_n" standing for "negative"). However, during verification, we typically distinguish the reset signal from other functional verifications. Therefore, we require designers to specify the reset signal name so our algorithm can appropriately ignore it.

- -parameter: (optional) In the DUV, some constants might be predefined us-

ing the keyword *define* (e.g. define INT\_WIDTH 8) or declared directly in the module parameter list (e.g. module top #(INT\_WIDTH = 8)). If any parameters are used in control paths (e.g. always, if, case statements), designers need to list them here so that our bug localization algorithm can ignore them.

- -rtl\_file\_list: (optional) For the DUV, there might be additional RTL files, such as submodules or memory files. However, the third-party tool Pyverilog requires that the input file be flattened, meaning other RTL files cannot be included directly in the DUV. Therefore, designers need to compile a file list that includes all these additional files.

- -ref\_model: (mandatory) In our tool, we need a spec to determine whether the DUV's behavior is correct. Therefore, designers must provide a reference model to serve as the spec. To ensure generality, designers should supply a script file in this parameter to execute their reference model. The command and arguments should follow the format: ./<script\_file> <input\_pattern> <output result>.

#### 2. Simulation information:

- -sim\_dir: (mandatory) The third-party tool SDM matches the output signals between the DUV and the reference model based on the simulation results' waveforms. As introduced in Chapter 2, SDM requires the files "duv\_pass.vcd", "duv\_fail.vcd", "golden\_pass.csv", and "golden\_fail.csv", generated from the DUV passing and failing patterns, respectively. Designers should place these four files in a directory and specify that directory in this parameter.

- -adapter: (optional) The concept of this parameter is similar to an adapter in UVM. Since we cannot ensure that designers' input pattern formats for the

DUV and the reference model, or the output result format from the reference model, will always match our tool's format (introduced in Appendix A and B), designers should provide a converter. This converter will translate their formats to our tool's format and vice versa. Specifically, we need an adapter that converts from our tool's input pattern format to their input pattern format and from their output format to our tool's output format. This allows us to generate input patterns, execute them on their reference model, and retrieve the results for our bug localization process.

#### 3. Supplemental information to enhance bug localization:

- -verification\_assertion: (optional) While our tool can automatically generate numerous assertions as candidates for bug localization, designers can enhance the results by providing their own verification assertions. Since designers have deeper knowledge of their own designs, their assertions can improve the accuracy of bug localization. These provided assertions will also be filtered through our process and used in the bug localization phase. Note that our algorithm requires these assertions to be written in SystemVerilog Assertions (SVA) and to be concurrent assertions with implications.

- -harm\_template: (optional) As discussed in Chapter 2, the assertions generated by HARM follow a predefined assertion mining template (the details will be introduced in Chapter 5). While our tool employs well-tuned parameters for automatic assertion mining, designers, possessing deeper insights into the DUV, can enhance this process. They have the flexibility to introduce additional LTL templates, propositions, or ranking metrics to guide HARM in generating more contextually relevant assertions for the DUV.

- -duv\_to\_ref\_model\_output\_name\_map: (optional) This parameter addresses a limitation in our tool. Occasionally, the third-party tool SDM exhibits instability in matching output signals, resulting in mismatches where certain DUV output signals may erroneously correspond to reference model output signals. Therefore, until the SDM algorithm is enhanced, if designers encounter errors such as segmentation faults in our tool, it is likely due to incorrect output signal matching. Designers can mitigate this issue by specifying the mapping between the names of output signals in the DUV and their counterparts in the reference model.

- -testbench: (optional) Our tool can automatically generate a testbench for the DUV using the information provided in the configuration file. However, this automation does not apply when the DUV involves DRAM due to the complexity of interactions, which cannot be standardized for testbench generation. Therefore, designers are required to directly provide their own testbench to facilitate the bug localization process.

#### 4. Input valid signal:

- -ivalid\_signal: (optional) If the DUV has input valid signals indicating the readiness of input signals (Fig.3.7), designers need to list these in this parameter to enable automatic testbench generation in our tool.

- -ivalid\_phase: (optional) If the DUV has input valid signals specified in ivalid\_signal, designers must also indicate the value or phase at which these

signals are activated, usually 1. This typically means that when the input valid

signals are high, the input signals are ready.

- -ivalid controlled signal: (optional) Sometimes, there may be multiple input

valid signals, each controlling different input signals. Therefore, it is necessary to map each input valid signal to its respective controlled input signals. This mapping enables our tool to precisely control the input data in the automatically generated testbench.

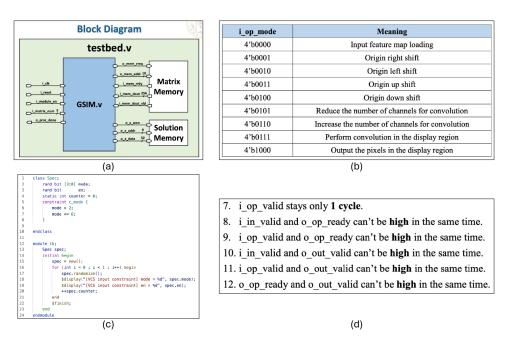

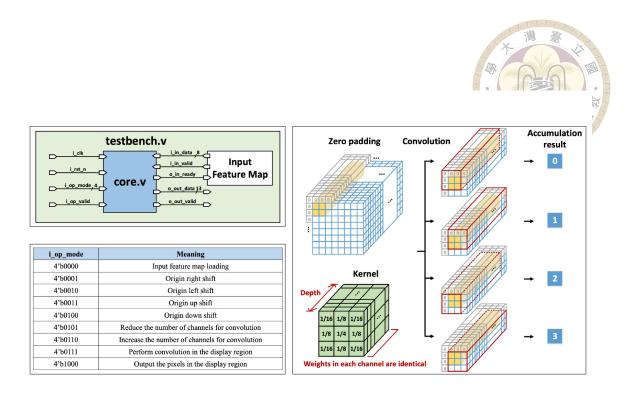

- -input\_signal\_not\_in\_input\_pattern: (optional) In our process, we generate constrained random patterns to simulate the DUV, excluding the clock signal, reset signal, and input valid signal, as these are used in the testbench to control the simulation. However, as shown in Fig. 4.1 (a), there may be additional input signals that neither control the input data (input valid signal) nor constitute the input data (input signal). These signals, such as i\_module\_en, i\_matrix\_num, and i\_mem\_rrdy in the block diagram, indicate module or memory readiness or act as counters. They are used in the testbench and should not be part of the input patterns. Therefore, designers need to specify these signals to avoid generating random patterns for them.

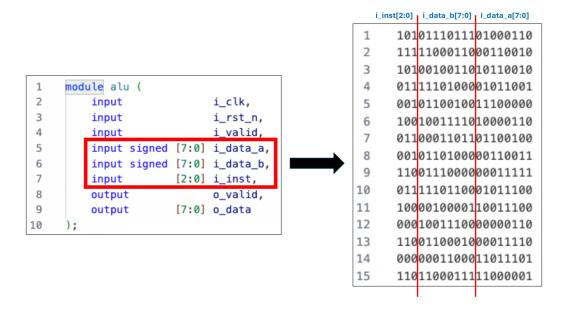

- -input\_constraint/-input\_constraint\_for\_multi\_ivalid: (optional) As shown in Fig. 4.1 (b), input signals sometimes need to follow constraints specified in the design specification rather than being purely random in our flow. For instance, the value of the four-bit signal "i\_op\_mode" Fig. 4.1 (b) should be in the range from 0 to 8. To address this, designers should follow our provided template, as depicted in Fig. 4.1 (c), to create an input constraint file written in SVA format. The template is straightforward: declare a class to write constraints inside and initialize the class in the top module. This information allows us to use the third-party tool VCS for constrained random simulation. The difference between these two parameters is that if there

are multiple input valid signals, the input signals controlled by each input valid signal should have their own input constraint files specified under input\_constraint\_for\_multi\_ivalid. This is because input valid signals control their respective input signals independently.

- -ivalid\_activate\_constraint: (optional) As shown in Fig. 4.1 (d), sometimes the input valid signals must adhere to constraints specified in the design specification, such as certain signals not being high simultaneously. Therefore, designers need to provide these constraints in SVA format. These assertions should be written as concurrent assertions with implications, similar to those specified in the -verification assertion parameter.

- -read\_in\_cycle / -read\_in\_cycle\_for\_multi\_ivalid: (mandatory) To automatically generate the testbench, designers must specify the number of cycles an input valid signal needs to remain high to input data. In some DUVs, there may be multiple input valid signals, each functioning independently. For example, in the last figure of Fig. 3.7, the input signal i\_op\_mode, controlled by i\_op\_valid, lasts for one cycle to read an operation, whereas the input signal i\_in\_data, controlled by i\_in\_valid, lasts for 2048 cycles to read all pixels in an image. Therefore, if the DUV has multiple input valid signals, designers should specify the read-in cycle for each under the parameter -read\_in\_cycle\_for\_multi\_valid.

- -pattern\_num\_in\_one\_sim\_round: (optional, the default value is 1) Some input signals require several patterns to form a meaningful action, which we refer to as "pattern number in one simulation round". For example, in Fig. 4.1 (b), the input signal i op mode determines the DUV's operation, and the spec

mandates that the first operation must be "load image (4'b0000)". If we simulate this input signal with just one random pattern under the given constraint, the simulation would repeatedly load the image and then terminate, which is unproductive. Therefore, we can set this parameter to 100, indicating that after loading the image, 99 additional random operations can be performed in this simulation iteration. These 100 patterns collectively represent a "meaningful action".

Figure 4.1: The examples illustrating the configuration file parameters

#### 5. Output valid signal:

- *-ovalid\_signal*: (optional) If the DUV has output valid signals indicating the readiness of output signals (Fig.3.8), designers need to list these in this parameter to enable automatic testbench generation in our tool.