國立臺灣大學電機資訊學院電子工程研究所

碩士論文

Graduate Institute of Electronics Engineering

College of Electrical Engineering and Computer Science

National Taiwan University

Master's Thesis

應用於低功耗鐵電記憶體之鐵電電容面積比

最佳化設計

Area Ratio Optimization for Low-Power

FeMFET Memory

陳彥宇

Yen-Yu Chen

指導教授：胡璧合博士

Advisor: Pi-Ho Hu, Ph.D.

中華民國 113 年 7 月

July 2024

# 摘要

鐵電電晶體(Ferroelectric Field-Effect Transistor, FeFET)作為一個有潛力的新興記憶體，如何降低其寫入電壓及增加記憶體視窗(Memory Window, MW)是一大挑戰。過去研究指出可以透過使用後段製程(Back-End-of-Line, BEOL)相容鐵電電容與前段製程(Front-End-of-Line, FEOL)電晶體串聯的結構，並調整兩者間的面積比(Area Ratio, AR)來增加記憶體視窗；也有其他研究指出透過使用高介電係數的側壁Spacer材料來增加記憶體視窗。然而，過去文獻缺少針對後段鐵電電容與前段電晶體面積比的最佳化探討，因此本論文將研究不同寫入電壓、鐵電參數及側壁材料對鐵電電晶體最佳化面積比的關係，並使用對應的等效電容模型來解釋觀察到的現象。論文最後研究鐵電電晶體陣列(FeFET Array)，探討鐵電電晶體在不同面積比與側壁材料的設計下受寫入干擾(Write Disturbance)的影響。

首先，我們探討鐵電電晶體在側壁材料為  $\text{Si}_3\text{N}_4$  的情況下，不同寫入電壓、殘餘極化(Remant Polarization,  $P_r$ )及矯頑電場(Coercive Field,  $E_c$ )與最佳化面積比(Optimized Area Ratio,  $AR^*$ )以及最佳化記憶體視窗(Optimized Memory Window,  $MW^*$ )的關係。我們發現最佳化面積比隨著寫入電壓上升會跟著上升，並且發現部分鐵電參數在高寫入電壓(4.5 V)下其最佳化面積比( $AR^* = 1$ )，代表在該情況減小面積比(AR)並不能增加記憶體視窗(MW)。在分析不同的鐵電參數組合及面積比對鐵電記憶體視窗的影響後，研究發現在低寫入電壓(2 V)下，鐵電電晶體在殘餘極化為  $15 \mu\text{C}/\text{cm}^2$ 、矯頑電場為  $1.2 \text{ MV}/\text{cm}$ ，有最大的最佳化記憶體視窗  $0.89 \text{ V}$ 。

本論文接著研究鐵電電晶體在殘餘極化為  $15 \mu\text{C}/\text{cm}^2$ 、矯頑電場為  $1.2 \text{ MV}/\text{cm}$  及 2 V 寫入電壓下，不同側壁材料對於最佳化記憶體視窗的影響。研究發現鐵電電晶體在使用高介電係數側壁( $k = 30$ )於面積比為 1 時，相比空氣側壁有較大的記憶體視窗；而在面積比為 0.1 時，使用空氣側壁的鐵電電晶體( $k = 1$ )則比使用高介電係

數側壁的鐵電電晶體有更大的記憶體視窗。鐵電電晶體在使用空氣側壁，其最佳化記憶體視窗為 0.95 V。

論文最後使用殘餘極化為  $15 \mu\text{C}/\text{cm}^2$ 、矯頑電場為  $1.2 \text{ MV}/\text{cm}$  之鐵電電晶體，探討在低寫入電壓(2 V)下鐵電電晶體陣列受寫入干擾的影響，並分析受寫入干擾後的記憶體視窗。研究發現隨著面積比減小或是使用高介電係數側壁均能使寫入干擾的影響降低。考慮到使用高介電係數側壁會使電晶體的總電容增加進而降低操作速度，因此最後折衷的選擇是使用空氣側壁，並藉由減小面積比(AR)來降低寫入干擾的影響。我們將  $\text{Si}_3\text{N}_4$  側壁且  $\text{AR} = 1$  的鐵電電晶體做為我們比較的基準線，在考慮了寫入干擾後的記憶體視窗，使用空氣側壁的鐵電電晶體其最佳化記憶體視窗為 0.74 V，相較於基準線的最佳化記憶體視窗為 0.13 V，記憶體視窗有 450% 的改善。從以上結果可以知道減小面積比對於在低功耗的鐵電電晶體可以改善記憶體視窗(MW)，並且對於陣列的應用具有更好的抗寫入干擾能力。

**關鍵字：**鐵電電晶體、低功耗、記憶體視窗、側壁、寫入干擾

# Abstract

Ferroelectric field-effect transistors (FeFETs) are promising for emerging memory technologies, but reducing write voltage and increasing the memory window are vital challenges. Previous research suggests enhancing the memory window by connecting a ferroelectric capacitor with a MOSFET device, adjusting the area ratio of the ferroelectric layer to the MOSFET, and using high-k dielectric constant spacer materials. However, the optimization of the area ratio has rarely been examined. This thesis investigates the optimized area ratio (ferroelectric layer to MOS) to achieve the optimized memory window (MW) under various write voltages, ferroelectric parameters, and spacer materials. We use an equivalent capacitance model to explain the results. Finally, this thesis investigates the effects of different area ratios and spacer materials on write disturbance in FeFET arrays.

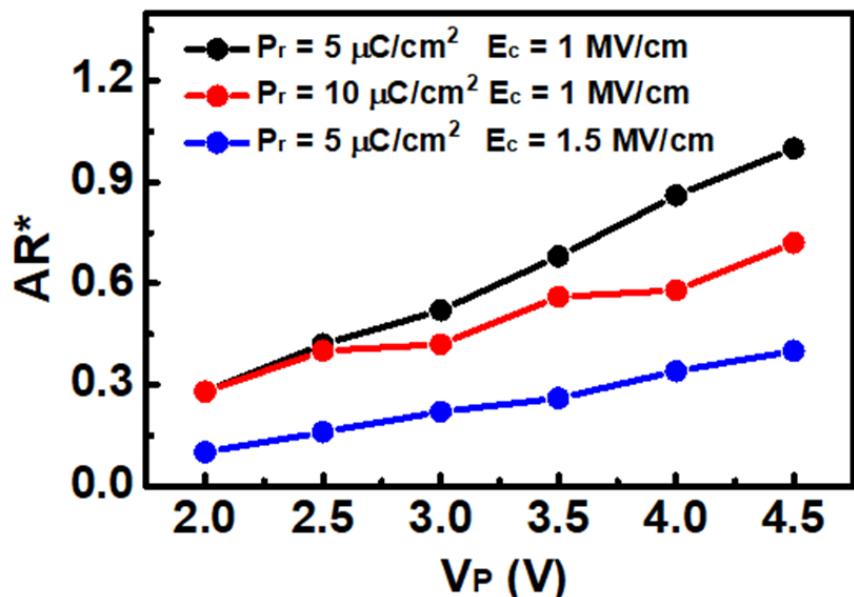

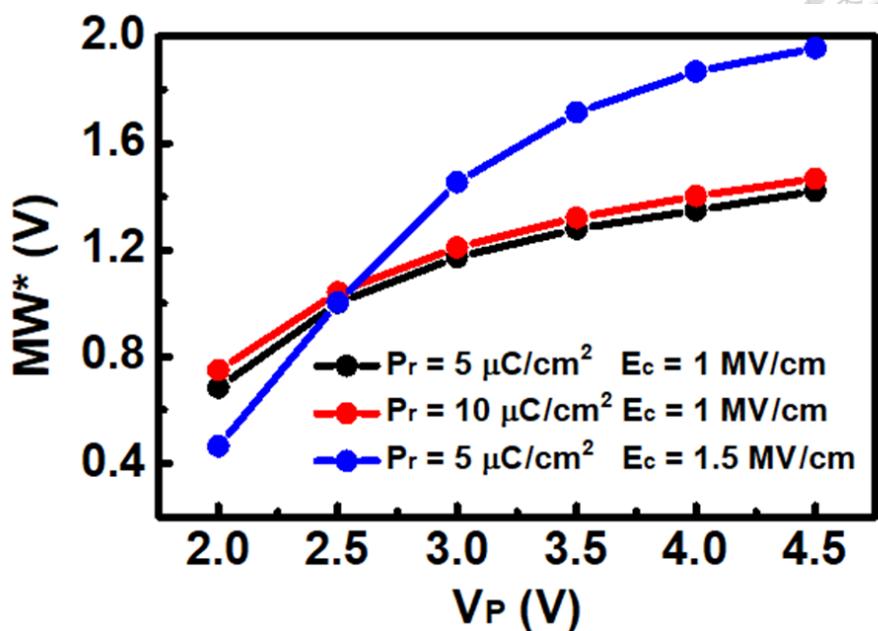

First, we investigated the relationship between the optimized area ratio (AR\*) and the optimized memory window (MW\*) of FeFETs with  $\text{Si}_3\text{N}_4$  as the spacer material under different write voltages, remanent polarization ( $P_r$ ), and coercive fields ( $E_c$ ). We found that the optimized area ratio increases with the rise in write voltage. Additionally, we discovered that at a high write voltage (4.5 V), some ferroelectric parameters have an  $\text{AR}^* = 1$ , indicating that reducing the area ratio does not necessarily increase the memory window. Through analysis of the impact of different ferroelectric parameters and area ratios on the optimized memory window of FeFETs, this research found that at a low write voltage of 2 V, FeFETs exhibit the largest optimized memory window of 0.89 V with a remanent polarization of  $15 \mu\text{C}/\text{cm}^2$  and a coercive field of 1.2 MV/cm.

This study further investigates how different spacer materials affect the optimized memory window of FeFET at a remanent polarization of  $15 \mu\text{C}/\text{cm}^2$ , a coercive field of

1.2 MV/cm, and a write voltage of 2 V. We found that FeFET with high-k dielectric constant spacer ( $k = 30$ ) have a larger memory window at  $AR = 1$  compared to air spacer. However, at  $AR = 0.1$ , FeFET with air spacer ( $k = 1$ ) shows a larger memory window. The optimized memory window for FeFET with air spacer is 0.95 V.

The study concludes by examining the impact of write disturbance on a FeFET array with a remanent polarization of  $15 \mu\text{C}/\text{cm}^2$ , a coercive field of 1.2 MV/cm, and a write voltage of 2 V. We found that reducing the area ratio or using a high-k dielectric constant spacer can lessen the write disturbance. However, high-k dielectric spacer increases total capacitance and reduces speed, so the preferred solution is to use an air spacer and reduce AR. Compared to a baseline FeFET memory with  $\text{Si}_3\text{N}_4$  spacer and  $AR = 1$ , the optimized memory window for FeFET with air spacer is 0.74 V, a 450% improvement over the baseline's 0.13 V. The results indicate that reducing AR can improve MW in low-power FeFETs and enhance immunity to write disturbances in array applications.

**Keywords:** FeFET, low-power, memory window, spacer, write disturbance

# 目次

|                              |      |

|------------------------------|------|

| 摘要 .....                     | I    |

| ABSTRACT .....               | III  |

| 目次 .....                     | V    |

| 圖次 .....                     | VII  |

| 表次 .....                     | XIII |

| 第一章 導論 .....                 | 1    |

| 1.1 新興記憶體 .....              | 1    |

| 1.2 鐵電性材料及鐵電記憶體 .....        | 3    |

| 1.2.1 鐵電性材料 .....            | 3    |

| 1.2.2 鐵電材料原理 .....           | 4    |

| 1.2.3 鐵電記憶體種類 .....          | 6    |

| 1.3 鐵電場效電晶體 .....            | 7    |

| 1.3.1 操作原理 .....             | 7    |

| 1.3.2 記憶體視窗 .....            | 9    |

| 1.4 鐵電電晶體記憶體視窗最佳化 .....      | 10   |

| 1.4.1 浮動閘極鐵電場效電晶體 .....      | 10   |

| 1.4.2 鐵電電晶體最佳化面積比相關文獻 .....  | 12   |

| 1.4.3 藉由高介電係數側壁改善記憶體視窗 ..... | 18   |

| 1.5 鐵電電晶體陣列 .....            | 20   |

| 1.5.1 AND 陣列 .....           | 20   |

| 1.5.2 1T1FeFET 陣列 .....      | 22   |

| 1.6 研究動機 .....               | 24   |

| 1.7 論文架構 .....               | 25   |

|                                               |           |

|-----------------------------------------------|-----------|

| <b>第二章 鐵電模型與研究方法 .....</b>                    | <b>26</b> |

| 2.1 前言 .....                                  | 26        |

| 2.2 Preisach Model.....                       | 27        |

| 2.3 元件參數與模擬方法.....                            | 30        |

| <b>第三章 不同操作條件對 AR*及 MW*之影響分析.....</b>         | <b>34</b> |

| 3.1 前言 .....                                  | 34        |

| 3.2 AR*及 MW*與不同鐵電參數及電壓關係(固定側壁) .....          | 35        |

| 3.2.1 AR*及 MW*與不同參數及寫入電壓的關係 .....             | 35        |

| 3.2.2 AR*及 MW*在 2 V 及 4.5 V 寫入電壓下的等高線圖分析..... | 39        |

| 3.3 AR*及 MW*於 2 V 寫入電壓下，與不同側壁的關係 .....        | 45        |

| 3.3.1 AR*及 MW*在 2 V 寫入電壓下，考慮不同側壁關係 .....      | 45        |

| 3.3.2 AR*及 MW*在 2 V 寫入電壓下，考慮不同側壁的等高線圖分析       |           |

| 47                                            |           |

| 3.3.3 在 2 V 寫入電壓下，不同側壁對電荷分布之分析 .....          | 49        |

| 3.4 等效電容模型圖 .....                             | 53        |

| 3.5 在 2 V 寫入電壓下，不同 AR 及側壁對於寫入干擾之分析 .....      | 57        |

| <b>第四章 總結 .....</b>                           | <b>65</b> |

| <b>參考文獻 .....</b>                             | <b>66</b> |

# 圖次

|                                                                                                                                    |    |

|------------------------------------------------------------------------------------------------------------------------------------|----|

| 圖 1.1 記憶體層級圖，從上到下的容量越來越高但存取速度會變慢。SCM 具有在 DRAM 和 FLASH 間的存取速度[1]。 .....                                                             | 2  |

| 圖 1.2 鐵電性材料發展時間圖，PZT 具有在製程上的問題，而 $HfO_2$ 可以與現有邏輯製程兼容[3]。 .....                                                                     | 3  |

| 圖 1.3 鐵電 PV 特性圖， $P_R$ 代表了當外在電場移除後剩下的極化量，而 $E_C$ 則是翻轉鐵電層所需的小電場[5]。 .....                                                           | 4  |

| 圖 1.4 不同摻雜比例 HZO 的 PV 圖，可以發現在摻雜比例為 0.5 時鐵電性最為明顯[6]。 .....                                                                          | 5  |

| 圖 1.5 鐵電記憶體種類:(A)FERAM，(B)FEFET，(C)FTJ[3]。三種鐵電記憶體皆是透過不同極化方向，使讀取電流產生差異。 .....                                                       | 6  |

| 圖 1.6 鐵電場效電晶體在兩個極化方向的電流差異，正寫入電壓可以使通道累積電子；負寫入電壓則是累積電洞[8]。 .....                                                                     | 7  |

| 圖 1.7 鐵電場效電晶體記憶體視窗，記憶體視窗為兩個臨界電壓相減[8]。 .....                                                                                        | 8  |

| 圖 1.8 考慮去極化場後的極化量 VS 時間，可以發現當殘餘極化太大時，在寫入電壓移除後儲存的極化量反而會變小[10]。 .....                                                                | 9  |

| 圖 1.9 (A)傳統鐵電電晶體，(B)加入浮動閘極的鐵電電晶體，可以自由調整鐵電層的面積[11]。 .....                                                                           | 10 |

| 圖 1.10 後段製程鐵電電容及前端製程電晶體，藉由金屬連接鐵電電容與下方電晶體[12]。 .....                                                                                | 11 |

| 圖 1.11 (A)不同面積比對總電荷的影響，越小的面積雖然在寫入時可以增加跨壓，但總電荷可能會減小，(B)不同面積比對閘極電壓差關係， $\Delta VMOS$ 存在一個最大值，AR 再繼續減小反而會減少 $\Delta VMOS$ [14]。 ..... | 12 |

|                                                                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

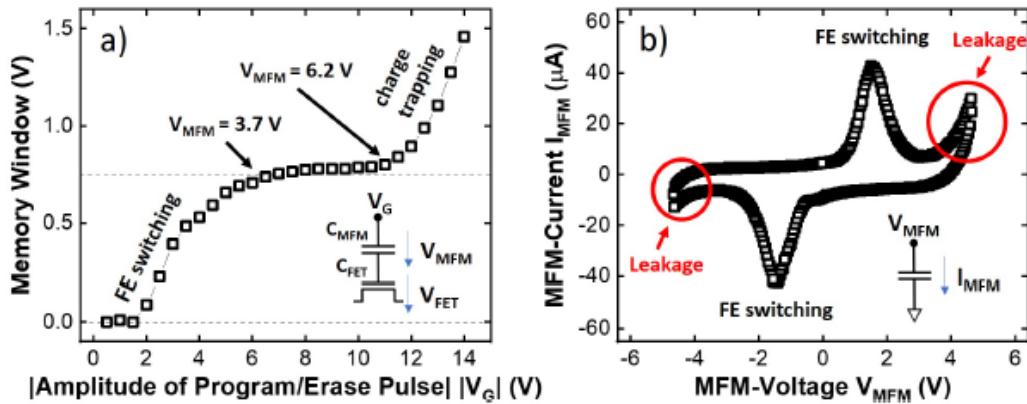

| 圖 1.12 (A)不同閘極電壓對記憶體視窗影響(考慮鐵電翻轉及電荷捕捉效應)，電壓過大時，因電荷捕捉反而會增加 MW，(B)不同鐵電層電壓對鐵電層電流影響，電壓過大時會產生漏電流[13]。 .....                                                  | 13 |

| 圖 1.13 閘極電壓對記憶體視窗影響(不同 AR)，可以發現 AR 越小 MW 越大[13]。 .....                                                                                                 | 13 |

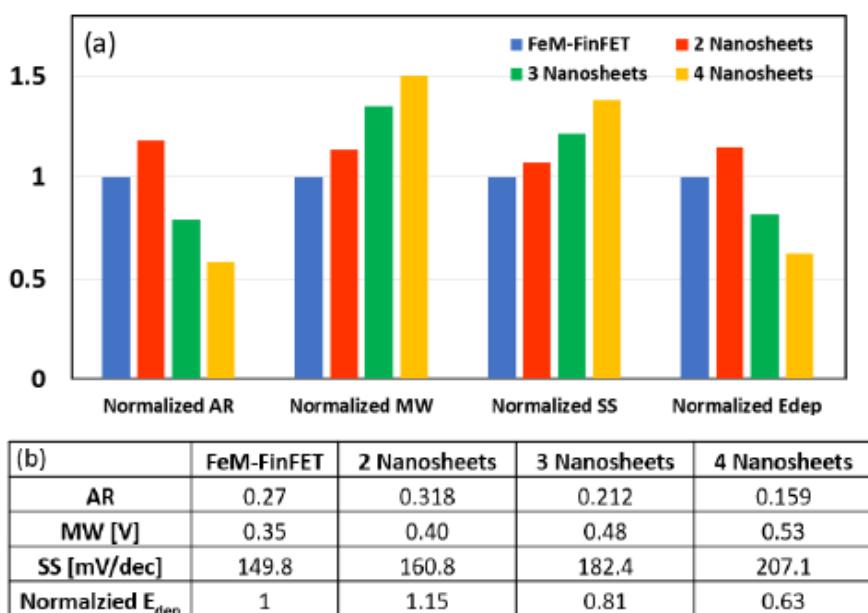

| 圖 1.14 (A)FE-FINFET，其 AR=1， (B)FEM-FINFET，藉由加入浮動閘極使 AR<1，(C)FE-NANOSHEET，較 FINFET 的電容來得大使其可以在相同電壓有更大的 MW，(D)FEM-NANOSHEET，加入浮動閘極並且有更大的電晶體電容[11]。 ..... | 15 |

| 圖 1.15 不同電晶體的 $I_D$ - $V_G$ (A)FINFET，(B)NANOSHEET。NANOSHEET 因本身具有較大的電晶體電容，因此在 1.5 V 寫入電壓下會有較 FINFET 來得大的 MW[11]。 .....                                | 15 |

| 圖 1.16 FEM-FINFET 與不同層數 NANOSHEET 的比較圖，當 AR 減小時 MW 會跟著上升，但 SS 會減小[11]。 .....                                                                           | 16 |

| 圖 1.17 (A)UTBSOI 結構圖，(B)等效電容模型。藉由增加在下面電晶體的電容，可以增加在寫入時落在鐵電層的跨壓[16]。 .....                                                                               | 18 |

| 圖 1.18 不同側壁介電常數在 $V_{WRITE}=5$ V 時的 MW，側壁的介電常數越高，MW 越大[17]。 .....                                                                                      | 19 |

| 圖 1.19 (A)本徵電晶體在不同氧化層厚度及寫入電壓下的 MW 等高線圖，(B)具有 $HfO_2$ 側壁電晶體，在不同氧化層厚度及寫入電壓下的 MW 等高線圖[17]。 19                                                             | 19 |

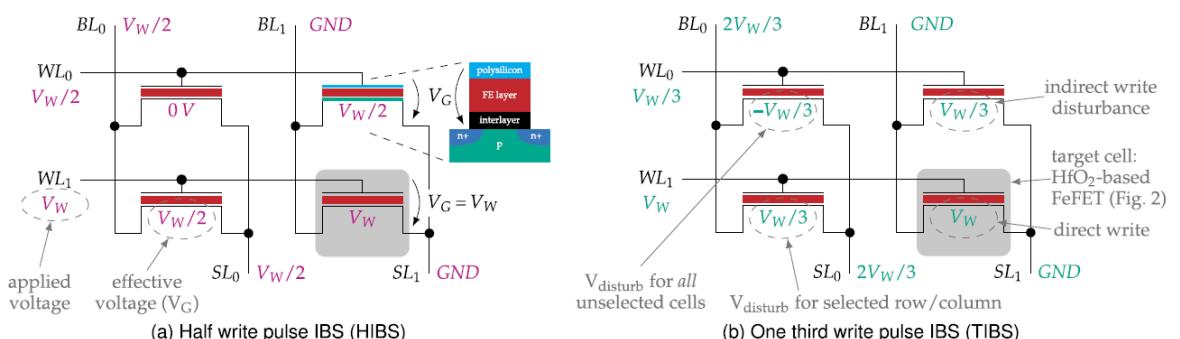

| 圖 1.20 AND 陣列 (A) $V_w/2$ 寫入法，(B) $V_w/3$ 寫入法。兩種寫入法都能使得未選取單元受到的干擾電壓減小[17]。 .....                                                                       | 20 |

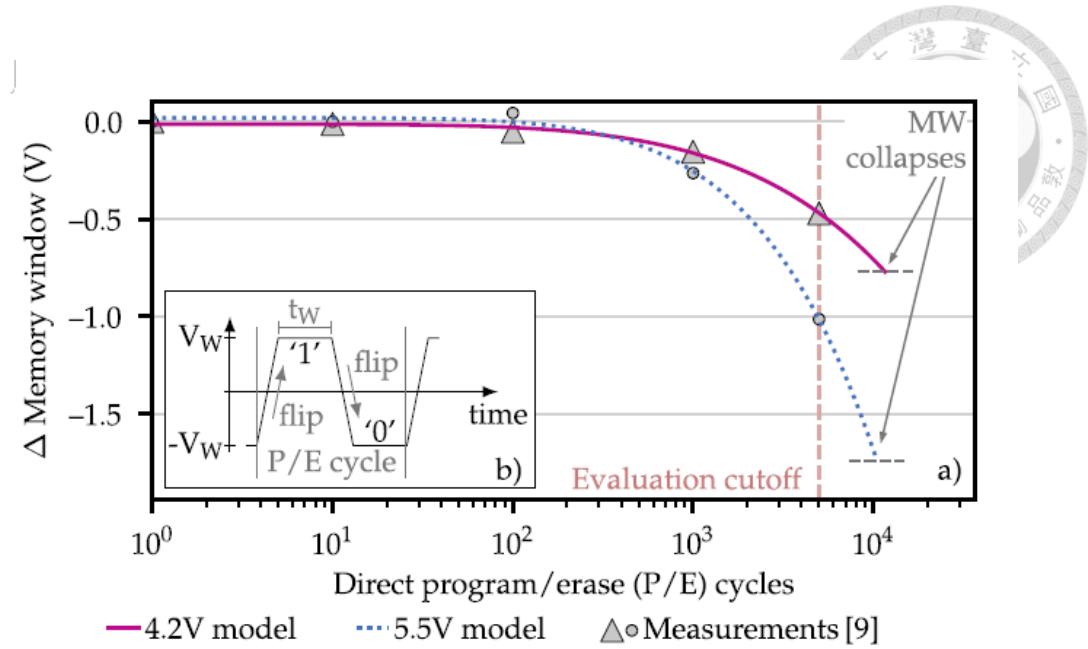

| 圖 1.21 在不同寫入電壓下的 MW 變化量 vs P/E 循環，當 P/E 循環上升到臨界值 MW 皆會衰減[17]。 .....                                                                                    | 21 |

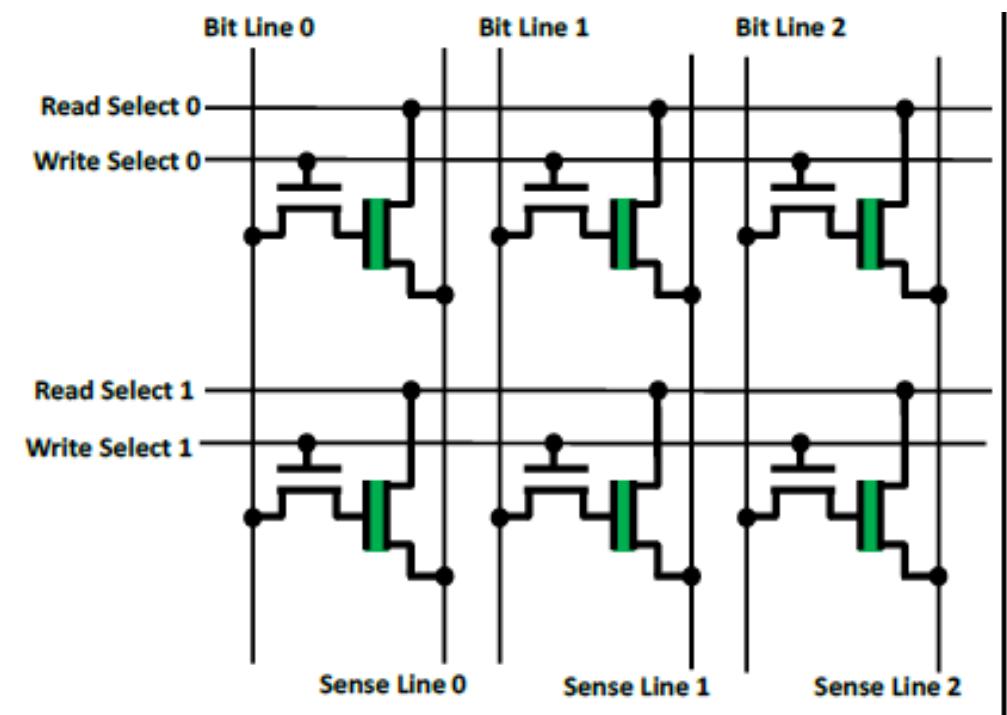

| 圖 1.22 1T1FEFET 陣列，藉由加入存取電晶體來避免寫入干擾[18]。 .....                                                                                                         | 22 |

|                                                                                                                                                                                                                                                                                     |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 圖 1.23 1T1FEFET(A)未選取單元的偏壓情況，(B)選取單元的偏壓情況。V <sub>GS</sub> 最大會是 2 倍的寫入電壓，對於電晶體可靠度會有影響[18]。 .....                                                                                                                                                                                     | 23 |

| 圖 2.1 (A)單晶域鐵電層 P-E 關係，(B)正負矯頑電壓分布，(C)多晶域鐵電層 P-E 特性。鐵電層的極化為鐵電極化加上介電極化[19]。 .....                                                                                                                                                                                                    | 27 |

| 圖 2.2 鐵電層次循環圖。鐵電層藉由操作電壓的轉折點來決定新的極化量，可用於描述遲滯現象[20]。 .....                                                                                                                                                                                                                            | 28 |

| 圖 2.3 鐵電動態切換模型(A)描述動態切換的微分方程式，(B)其微分方程式解的圖，(C)不同寫入電壓及寫入時長的模型與實驗數據校正。隨著寫入電壓上升，鐵電層翻轉越快[20]。 .....                                                                                                                                                                                     | 29 |

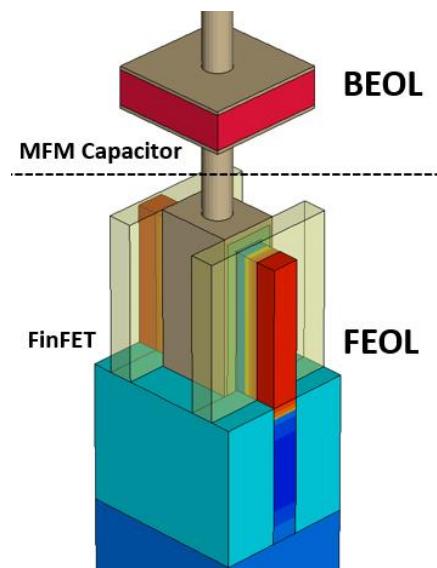

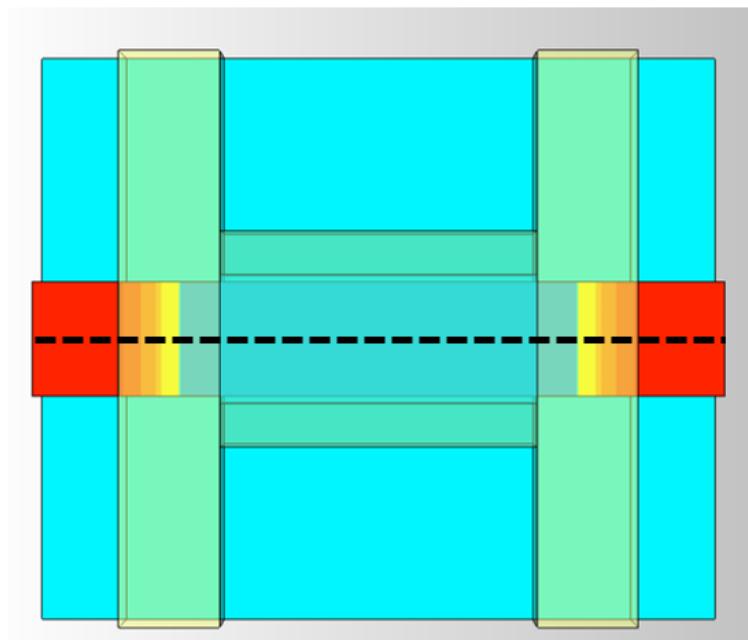

| 圖 2.4 前端製程電晶體與後段製程鐵電電容串聯結構圖，下方的電晶體為根據 IRDS ROADMAP 7NM 設計的 FINFET。 .....                                                                                                                                                                                                            | 30 |

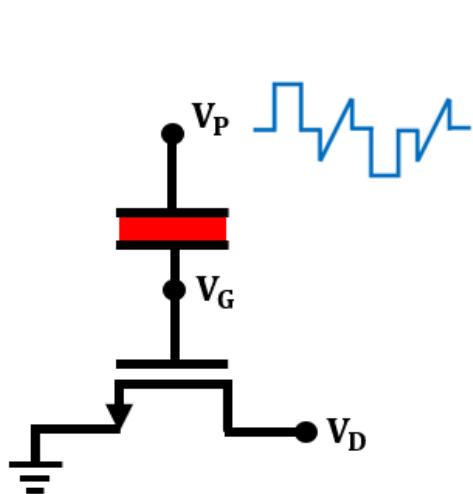

| 圖 2.5 等效電路模型，讀取及寫入皆是在鐵電電容的上極板。 .....                                                                                                                                                                                                                                                | 31 |

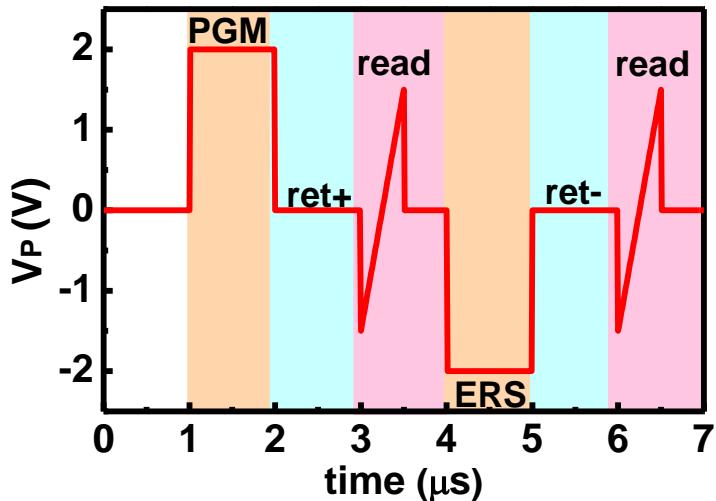

| 圖 2.6 量測 MW 的波型圖，在讀取階段讀取電壓為-1.5 V~1.5 V。 .....                                                                                                                                                                                                                                      | 32 |

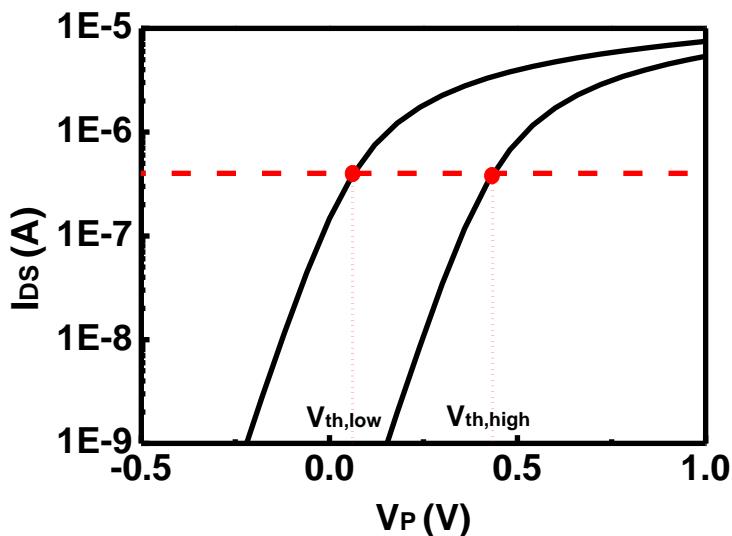

| 圖 2.7 用定汲極電流法量測 MW，紅色虛線是我們取 V <sub>TH</sub> 的電流準位為 4 $\mu$ A。 .....                                                                                                                                                                                                                 | 32 |

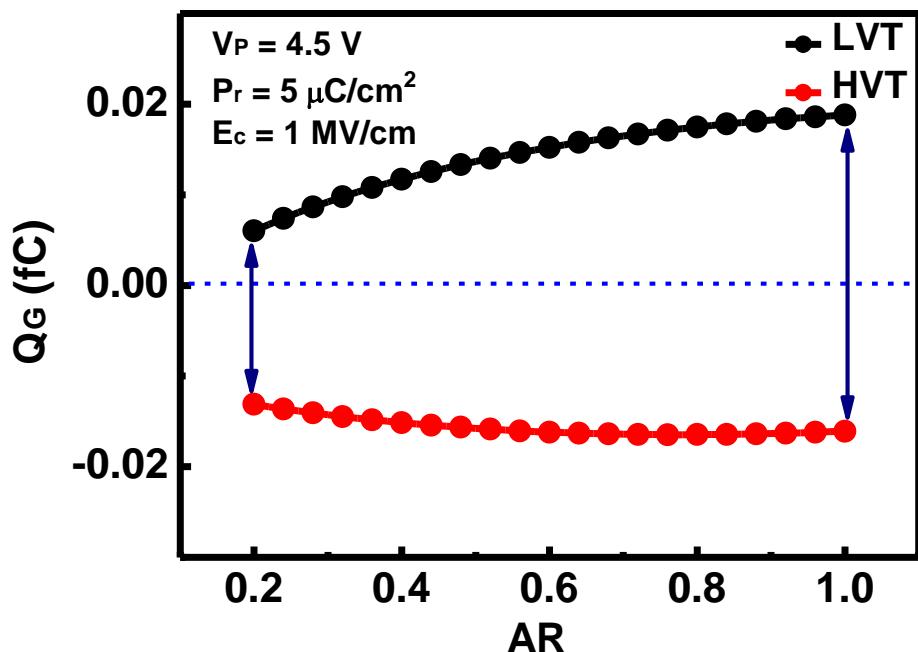

| 圖 2.8 AR* 以及 MW* 示意圖( $P_R = 5\text{MC}/\text{CM}^2$ 及 $E_C = 1\text{MV}/\text{CM}$ )，紅色星星代表最大 MW 的位置為 MW*，對應的 AR 即為 AR*。 .....                                                                                                                                                     | 33 |

| 圖 3.1 不同面積比的 $I_{DS}$ - $V_P$ 圖，以 $P_R = 5\text{MC}/\text{CM}^2$ 及 $E_C = 1\text{MV}/\text{CM}$ 為例。越小的 AR 具有越大的 MW。 .....                                                                                                                                                           | 35 |

| 圖 3.2 面積比對記憶體視窗影響(不同鐵電參數及寫入電壓)(A) $P_R = 5\text{MC}/\text{CM}^2$ 及 $E_C = 1\text{MV}/\text{CM}$ ，(B) $P_R = 10\text{MC}/\text{CM}^2$ 及 $E_C = 1\text{MV}/\text{CM}$ ，(C) $P_R = 5\text{MC}/\text{CM}^2$ 及 $E_C = 1.5\text{MV}/\text{CM}$ ，橘色星星代表 MW* 的位置。MW* 的位置跟鐵電參數及寫入電壓有關。 ..... | 36 |

| 圖 3.3 寫入電壓對最佳化面積比影響，AR* 隨著寫入電壓增加會跟著增加，並且反比於矯頑電場及殘餘極化。 .....                                                                                                                                                                                                                         | 37 |

|                                                                                                                                                                                                                                                                      |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 圖 3.4 寫入電壓對最佳化記憶體視窗影響，MW*隨殘餘極化的影響較小。在寫入電壓小於 2.5 V 時， $E_C = 1.5 \text{ MV/CM}$ 反而有較小的 MW。 .....                                                                                                                                                                      | 38 |

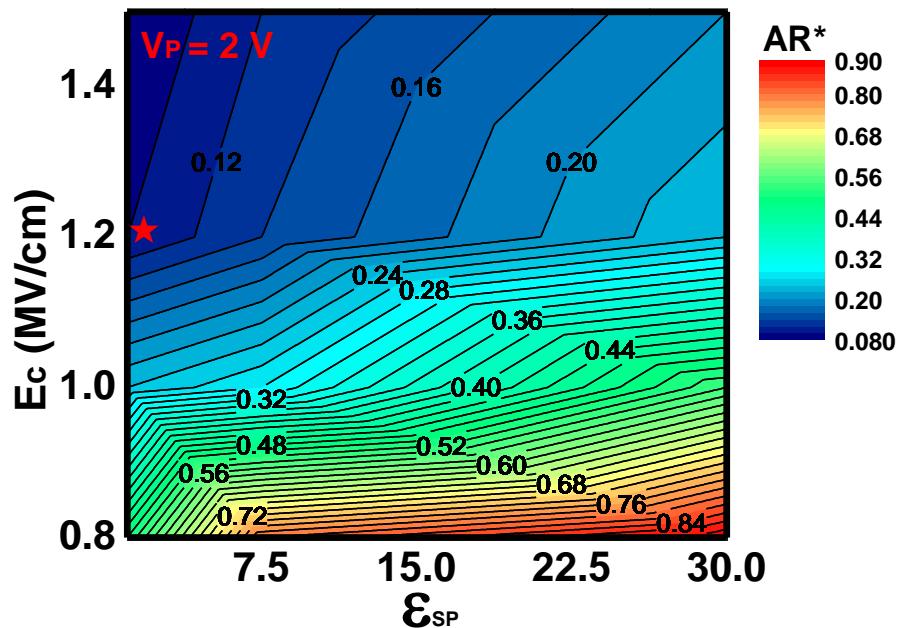

| 圖 3.5 在 2 V 寫入電壓下，AR*的等高線圖，粉色星星代表了最大的 MW*對應之 AR*，隨著矯頑電場增加 AR*跟著減小。 .....                                                                                                                                                                                             | 40 |

| 圖 3.6 在 2 V 寫入電壓下，MW*的等高線圖，藍色星星代表了最大的 MW*。最大的 MW*發生在 $P_R = 15 \text{ MC/CM}^2$ 以及 $E_C = 1.2 \text{ MV/CM}$ 。 .....                                                                                                                                                 | 40 |

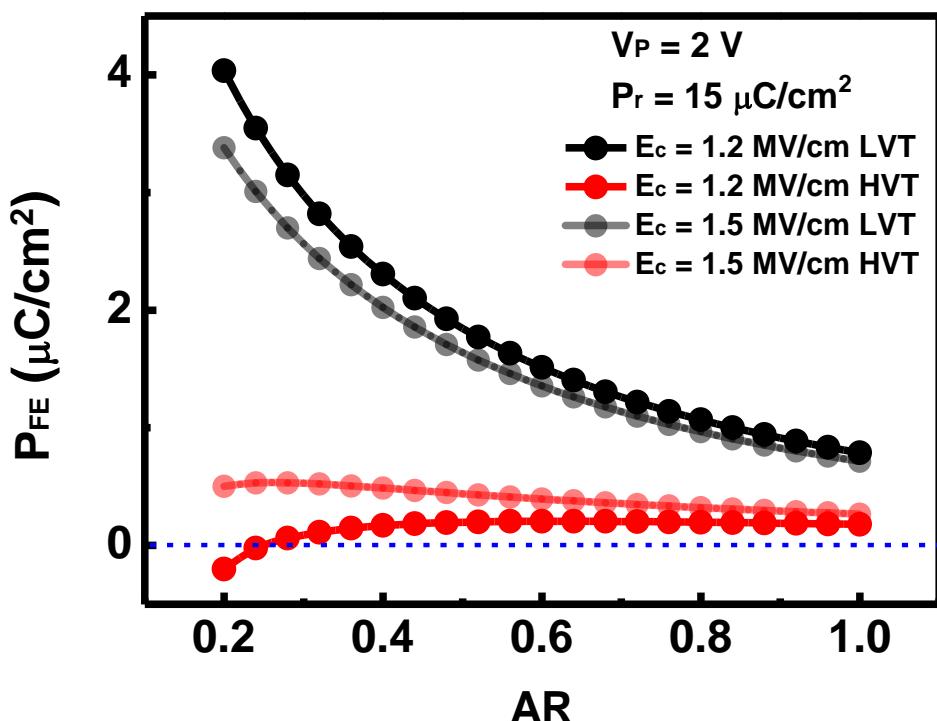

| 圖 3.7 在 2 V 寫入電壓下，考慮不同矯頑電場影響下寫入極化量隨 AR 變化，藍色虛線代表極化量為零。可以發現 $E_C = 1.2 \text{ MV/CM}$ ，在 LVT/HVT 有較大的極化量差異。 .....                                                                                                                                                     | 41 |

| 圖 3.8 在 4.5 V 寫入電壓下，AR*的等高線圖，粉色星星代表了最大的 MW*對應之 AR*。在該圖的左下角 $AR^* = 1$ ，代表減小 AR 反而會減小 MW。 .....                                                                                                                                                                       | 42 |

| 圖 3.9 在 4.5 V 寫入電壓下，MW*的等高線圖，藍色星星代表了最大的 MW*。最大的 MW*發生在 $P_R = 15 \text{ MC/CM}^2$ 以及 $E_C = 1.5 \text{ MV/CM}$ 。 .....                                                                                                                                               | 43 |

| 圖 3.10 在 4.5V 寫入電壓下，寫入極化量隨 AR 變化，藍色虛線代表極化量為零。隨著 AR 減小在 LVT/HVT 的極化量差異增加。 .....                                                                                                                                                                                       | 44 |

| 圖 3.11 在 4.5V 寫入電壓下，寫入在開極電荷量隨 AR 變化，藍色虛線代表極化量為零。隨著 AR 減小在 LVT/HVT 的總電荷差異減少。 .....                                                                                                                                                                                    | 44 |

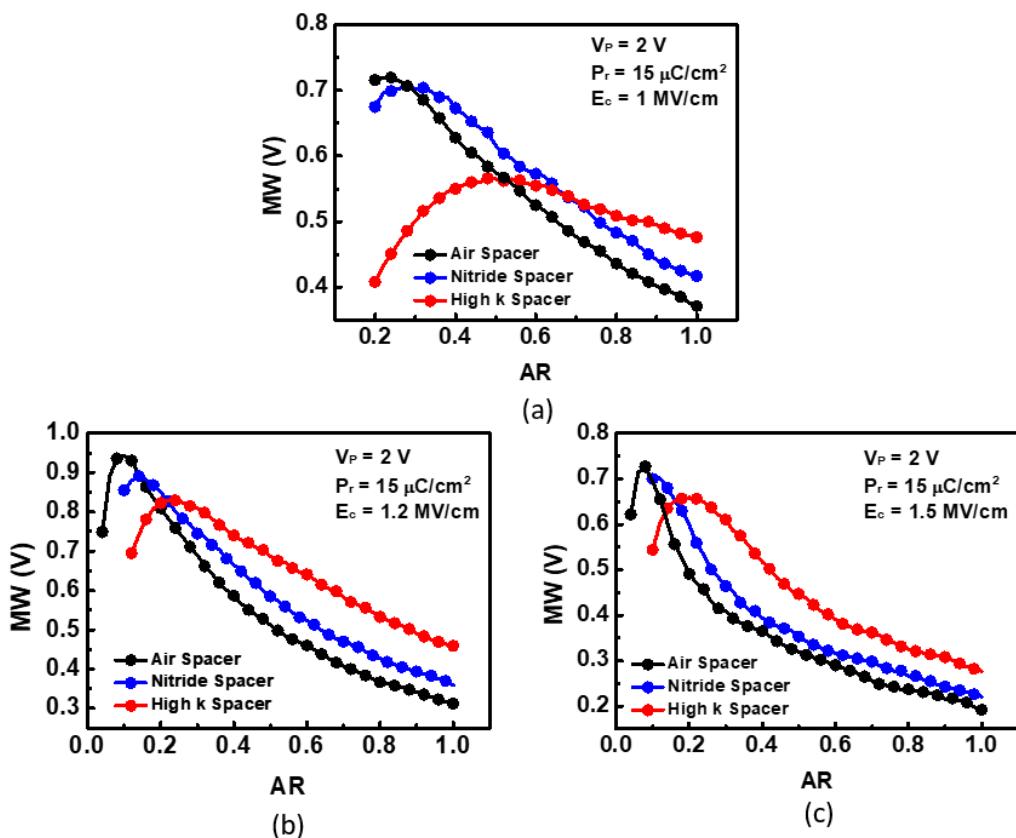

| 圖 3.12 2 V 寫入電壓下，不同面積比，對記憶體視窗影響(不同側壁材料)(A) $P_R = 15 \text{ MC/CM}^2$ 及 $E_C = 1 \text{ MV/CM}$ ，(B) $P_R = 15 \text{ MC/CM}^2$ 及 $E_C = 1.2 \text{ MV/CM}$ ，(C) $P_R = 15 \text{ MC/CM}^2$ 及 $E_C = 1.5 \text{ MV/CM}$ 。高介電係數側壁在 AR 較大的地方具有優勢，但小 AR 地方則不具有優勢。 ..... | 46 |

| 圖 3.13 在 2V 寫入電壓下，考慮不同側壁介電係數的 AR*等高線圖，紅色星星代表了最大的 MW*對應之 AR*。隨著側壁介電常數增加對應的 AR*跟著增加。 .....                                                                                                                                                                             | 47 |

|                                                                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

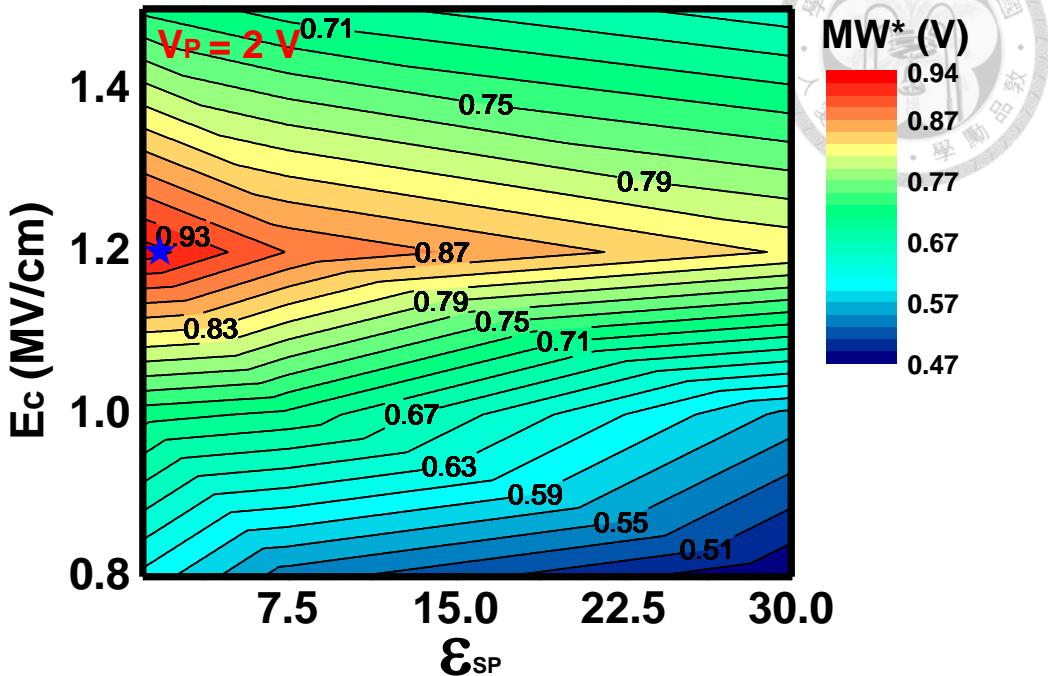

| 圖 3.14 在 2 V 寫入電壓下，中考慮不同側壁介電係數的 MW*等高線圖，藍色星星代表了最大的 MW*。可以發現即使考慮了側壁的影響，擁有最大的 MW*之鐵電參數也是發生在 $P_R = 15 \text{MC/CM}^2$ 及 $E_C = 1.2 \text{MV/CM}$ 。 ..... | 48 |

| 圖 3.15 從頂部看的 FINFET，我們觀察的電荷分布為沿著黑色虛線的通道。 ....                                                                                                          | 49 |

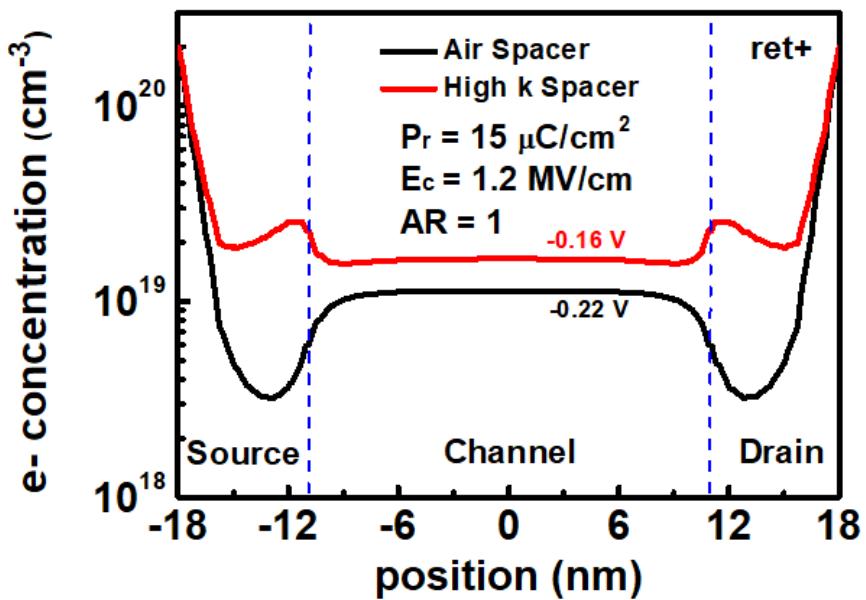

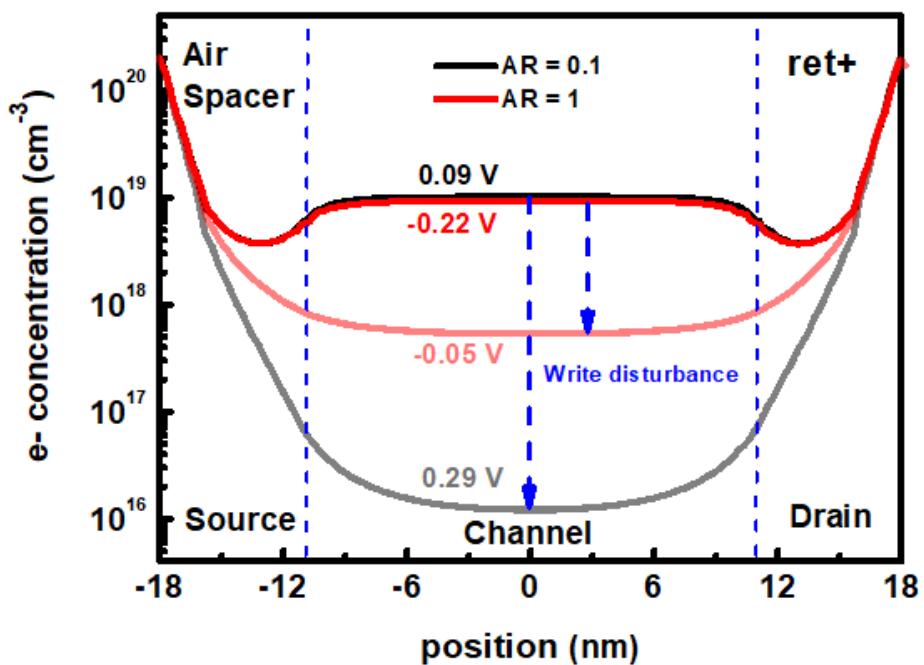

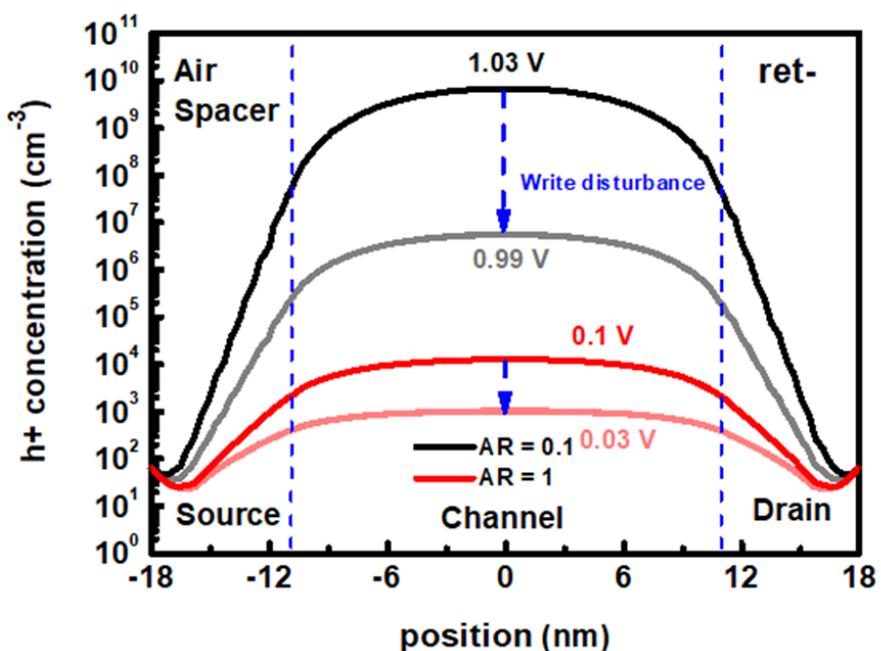

| 圖 3.16 在 2 V 寫入電壓下，於 RET <sup>+</sup> ，AR=1 的電子分布圖。可以發現高介電系數側壁在通道具有較高的電子濃度，但因為分壓效應使其臨界電壓較空氣側壁高一點。 .....                                                | 51 |

| 圖 3.17 在 2 V 寫入電壓下，於 RET <sup>+</sup> ，AR=1 的電洞分布圖。可以發現高介電系數側壁在通道具有較高的電洞濃度，並且有較高的臨界電壓。 .....                                                           | 51 |

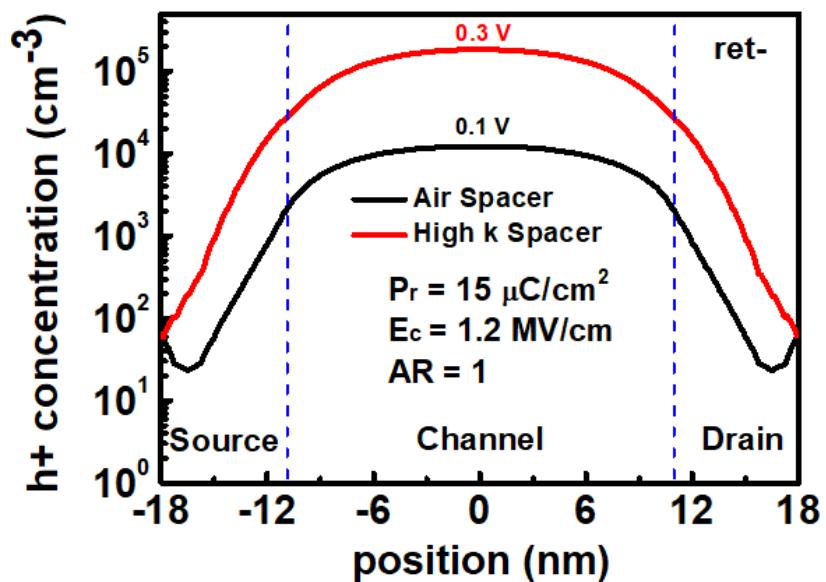

| 圖 3.18 在 2 V 寫入電壓下，於 RET <sup>+</sup> ，AR=0.1 的電子分布圖。可以發現空氣側壁在通道具有較高的電子濃度，並且有較低的臨界電壓。 .....                                                            | 52 |

| 圖 3.19 在 2 V 寫入電壓下，於 RET <sup>-</sup> ，AR=0.1 的電洞分布圖。高介電係數具有較高的電洞濃度並有較高的臨界電壓。 .....                                                                    | 52 |

| 圖 3.20 寫入階段時的等效電容模型， $C_{\text{MOS}}$ 代表了電晶體的等效電容包含了側壁寄生電容 $C_{\text{SP}}$ 以及電晶體氧化層與通道電容串聯之 $C_{\text{IS}}$ 。 .....                                    | 54 |

| 圖 3.21 保存階段時的等效電容模型， $Q_G$ 為全部感應在閘極的電荷; $Q_{\text{CHANNEL}}$ 為受閘極控制的通道電荷。越高介電係數的側壁會使得 $Q_{\text{CHANNEL}}$ 減小。 .....                                   | 54 |

| 圖 3.22 (A)1FEFET 陣列架構，1 號為受干擾的單元(B)用以量測寫入干擾的波型圖。先對 1 號單元寫 1 後再寫入 0 在鄰近的單元，即可量測受干擾後的臨界電壓。 .....                                                         | 58 |

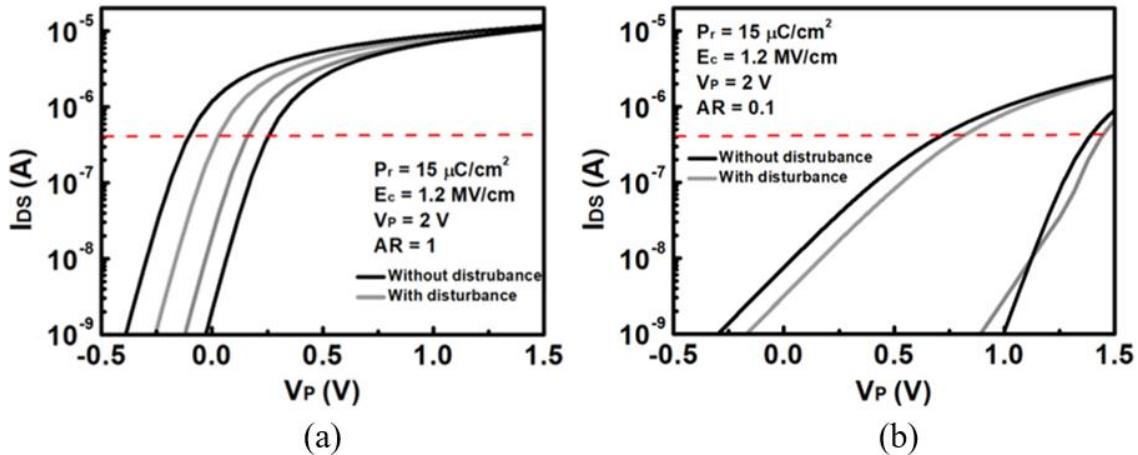

| 圖 3.23 受寫入干擾的 $I_{\text{DS}}\text{-}V_{\text{P}}$ 圖 (A) AR = 1，(B) AR = 0.1。可以發現 AR = 0.1 受干擾的程度較低。 .....                                              | 59 |

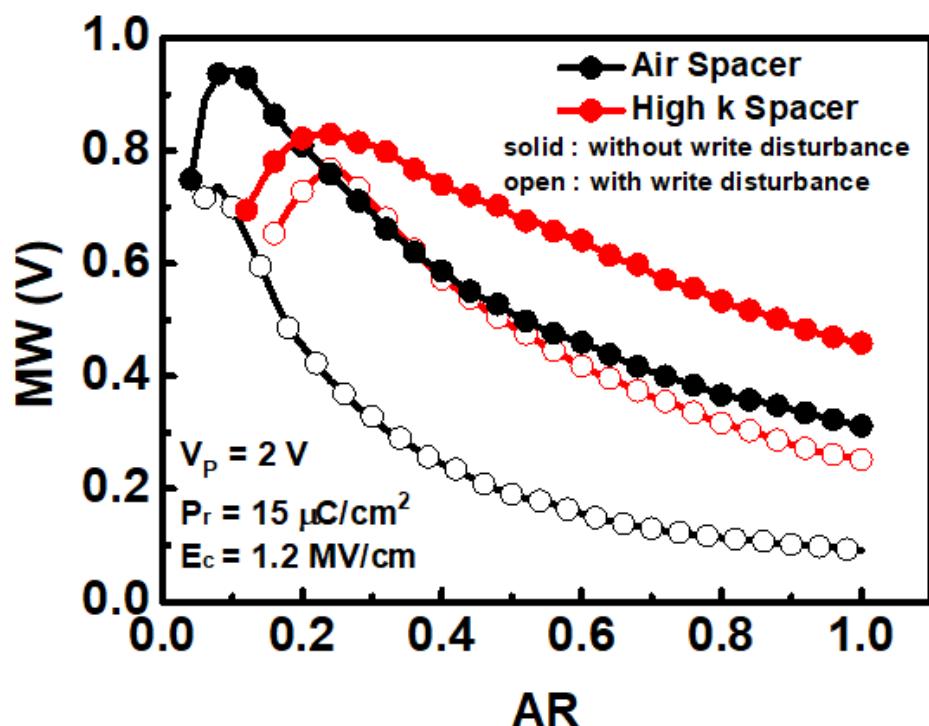

| 圖 3.24 在 2 V 寫入電壓下，不同面積比及側壁對受干擾記憶體視窗影響。隨著 AR 減小或是使用高介電係數側壁，MW 受干擾較小。 .....                                                                             | 60 |

|                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------|----|

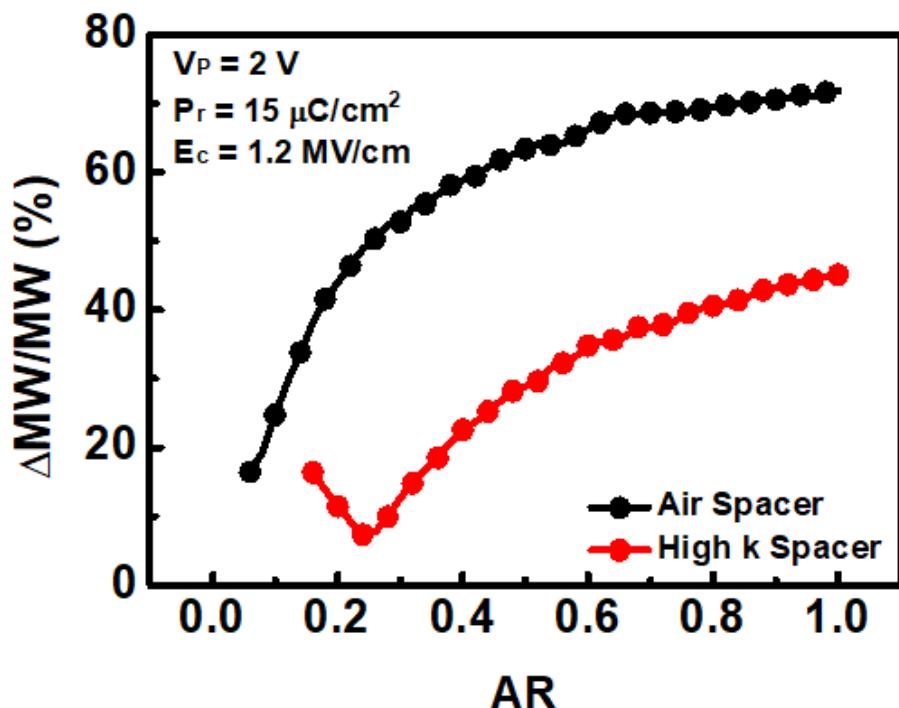

| 圖 3.25 考慮空氣側壁及高介電係數側壁受干擾的 MW 改變百分比，AR 減小有助於減少 MW 的改變百分比。 .....                                                                  | 60 |

| 圖 3.26 使用空氣側壁比較 AR = 0.1 及 AR = 1 在受寫入干擾前後，RET+的電子分布。AR = 0.1 受到較大的干擾電壓，因此在受干擾後電子濃度小於 AR = 1，且有較高的臨界電壓。 .....                   | 62 |

| 圖 3.27 使用空氣側壁比較 AR = 0.1 及 AR = 1 在受寫入干擾前後，RET-的電洞分布。AR = 0.1 受到較大的干擾電壓，但在受干擾前有較高的電洞濃度，在受干擾後電洞濃度仍比 AR = 1 來得高，且具有較高的臨界電壓。 ..... | 62 |

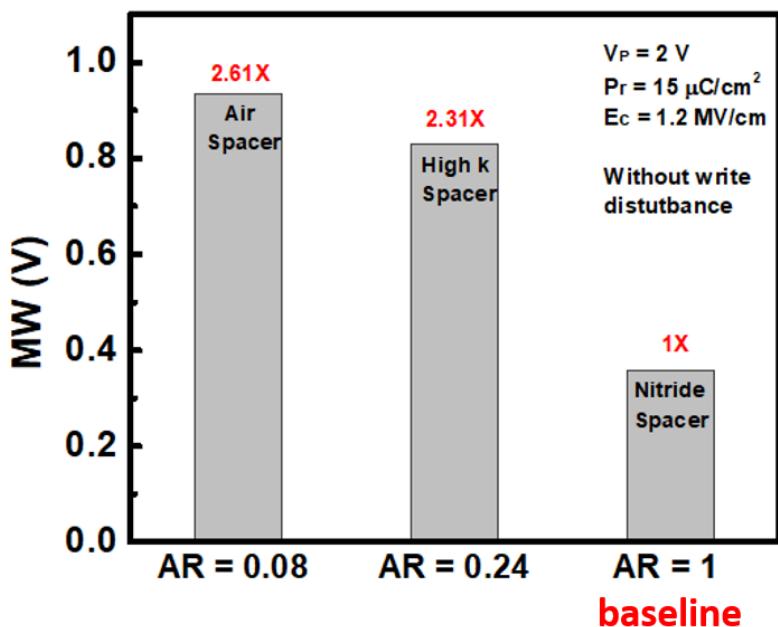

| 圖 3.28 不同側壁之最佳化記憶體視窗與基準線比較圖(未受寫入干擾)。空氣側壁的 MW* 相較於基準線改善了 161%.....                                                               | 64 |

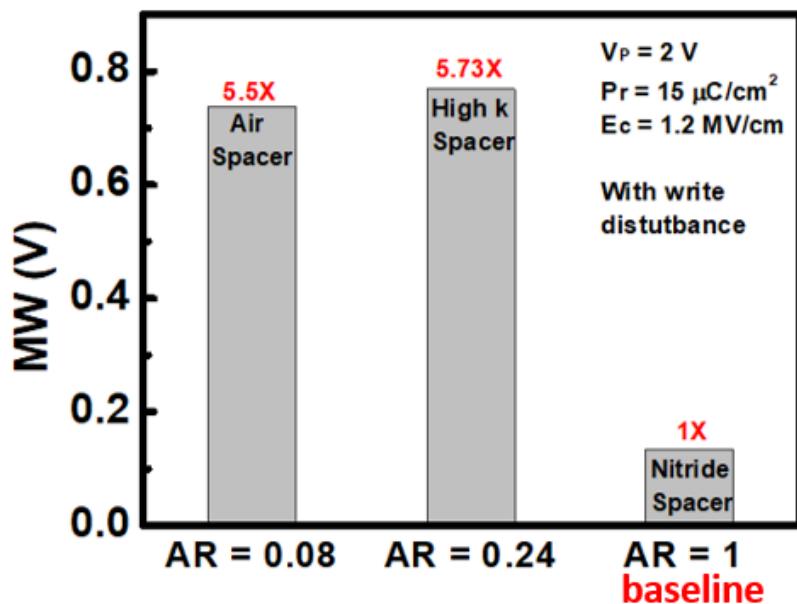

| 圖 3.29 不同側壁之最佳化記憶體視窗與基準線比較圖(受寫入干擾)。空氣側壁的 MW* 相較於基準線改善了 450%.....                                                                | 64 |

# 表次

|                                                                                    |    |

|------------------------------------------------------------------------------------|----|

| 表 1.1 新興記憶體性能比較圖，FEFET 本身具有較高的開關比並且允許多位元的<br>操作[2]。 .....                          | 2  |

| 表 1.2 不同鐵電記憶體特性比較，FEMFET 不僅可以使操作電壓下降，還能減少在<br>IL 層的跨壓[15]。 .....                   | 17 |

| 表 2.1 本論文中 7NM FINFET 之元件參數，其中 $W_F$ 是金屬 TiN 的功函數。 .....                           | 31 |

| 表 3.1 最佳化面積比與寫入電壓、鐵電參數及側壁之關係。可以發現 $AR^*$ 與寫入<br>電壓及側壁介電係數成正比，並與殘餘極化及矯頑電場成反比。 ..... | 56 |

| 表 3.2 1FEFET 陣列的寫入、讀取電壓表。對於未受選取的單元只會受到三分之一<br>的干擾電壓。 .....                         | 58 |

# 第一章 導論

## 1.1 新興記憶體

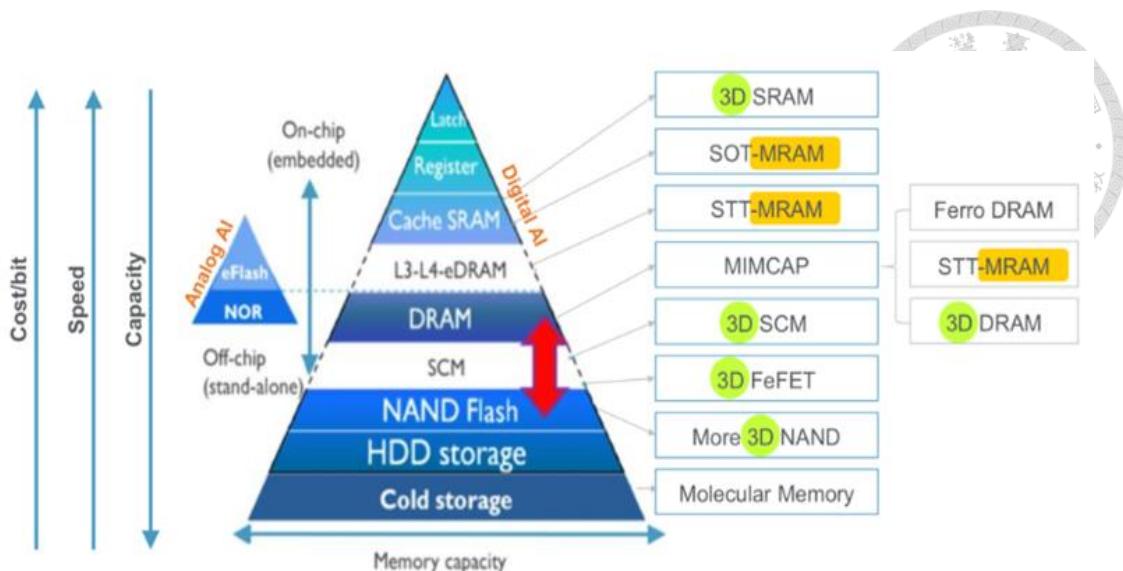

近幾年由於人工智慧以及物聯網的發展，龐大的資料運算使得儲存單元變得相當重要，具有低功耗及快速寫入的記憶體是熱門的研究方向。而在現今的處理器架構中，記憶體的層級主要可以分為暫存器、快取、主記憶體、主儲存等層級，如圖 1.1 的記憶體層級所示[1]。離 CPU 最近的主要是暫存器(Register)，提供 CPU 儲存正在運算或已運算完的資料。而下一級主要為快取(Cache)，主要由靜態隨機存取記憶體(Static Random Access Memory, SRAM)所組成，負責將原先已算過或常使用的資料先存在快取中，減少 CPU 在抓取資料時所需的時間。再下一級就是主記憶體主要由動態隨機存取記憶體(Dynamic Random Access Memory, DRAM)所組成，負責儲存系統正在運行中的程式以及資料，最後一級即為負責資料儲存的硬碟主要有固態硬碟(Solid-State Drive, SSD)中常見的 NAND 快閃記憶體(NAND Flash Memory)，以及硬碟(Hard Disk Drive, HDD)，他們負責儲存所有的資料以及具有非揮發性的特性，使其在電源關閉後資料仍不會消失。

在記憶體層級中越往上的速度越快但具有的容量也越小同時成本也越高，而每次存取資料花費在資料傳輸的時間對於現在需要高速以及龐大資料運算的 AI 或是伺服器的應用而言是不足的。因此有人提出一個介於主記憶體以及硬碟間的儲存級記憶體(Storage Class Memory)，其具有非揮發性的特性以及介於 DRAM 以及 FLASH 間的存取速度使其成為熱門的主題。而 SCM 中的記憶體中最熱門的候選人即為新興記憶體(Emerging Memory)，包含了鐵電記憶體(Ferroelectric Memory)、電阻式隨機存取記憶體(RRAM)、磁阻式隨機存取記憶體(MRAM)、相轉化記憶體(PCM)等其特性比較圖[2]，如表 1.1 所示。其中鐵電記憶體具有非常低的寫入能量( $\sim 1\text{fJ}$ )以及相對高的開關比( $\sim 10^3$ )，並且允許多位元的操作非常適合用於 AI 模型的訓練，因此鐵電記憶體是新興記憶體中非常具有潛力的一大主題。

圖 1.1 記憶體層級圖，從上到下的容量越來越高但存取速度會變慢。SCM 具有在 DRAM 和 FLASH 間的存取速度[1]。

| Technology                       | CMOS Mainstream Memories |             |                     |                     | Memristive Emerging Memories |                     |          |            |                   |

|----------------------------------|--------------------------|-------------|---------------------|---------------------|------------------------------|---------------------|----------|------------|-------------------|

|                                  | NOR Flash                | NAND Flash  | RRAM                | PCM                 | STT-MRAM                     | FeRAM               | FeFET    | SOT-MRAM   | Li-ion            |

| ON/OFF Ratio                     | $10^4$                   | $10^4$      | $10\text{--}10^2$   | $10^2\text{--}10^4$ | 1.5-2                        | $10^2\text{--}10^3$ | 5-50     | 1.5-2      | $40\text{--}10^3$ |

| Multilevel operation             | 2 bit                    | 4 bit       | 2 bit               | 2 bit               | 1 bit                        | 1 bit               | 5 bit    | 1 bit      | 10 bit            |

| Write voltage                    | <10 V                    | >10 V       | <3V                 | <3V                 | <1.5 V                       | <3 V                | <5 V     | <1.5 V     | <1 V              |

| Write time                       | 1-10 $\mu$ s             | 0.1-1 ms    | <10 ns              | ~50 ns              | <10 ns                       | ~30 ns              | ~10 ns   | <10 ns     | <10 ns            |

| Read time                        | ~50 ns                   | ~10 $\mu$ s | <10 ns              | <10 ns              | <10 ns                       | <10 ns              | <10 ns   | <10 ns     | <10 ns            |

| Stand-by power                   | Low                      | Low         | Low                 | Low                 | Low                          | Low                 | Low      | Low        | Low               |

| Write energy (J/bit)             | ~100 pJ                  | ~10 fJ      | 0.1-1 pJ            | 10 pJ               | ~100 fJ                      | ~100 fJ             | <1 fJ    | <100 fJ    | ~100 fJ           |

| Linearity                        | Low                      | Low         | Low                 | Low                 | None                         | None                | Low      | None       | High              |

| Drift                            | No                       | No          | Weak                | Yes                 | No                           | No                  | No       | No         | No                |

| Integration density              | High                     | Very High   | High                | High                | High                         | Low                 | High     | High       | Low               |

| Retention                        | Long                     | Long        | Medium              | Long                | Medium                       | Long                | Long     | Medium     | -                 |

| Endurance                        | $10^5$                   | $10^4$      | $10^5\text{--}10^8$ | $10^6\text{--}10^9$ | $10^{15}$                    | $10^{10}$           | $>10^5$  | $>10^{15}$ | $>10^5$           |

| Suitability for DNN training     | No                       | No          | No                  | No                  | No                           | No                  | Moderate | No         | Yes               |

| Suitability for DNN inference    | Yes                      | Yes         | Moderate            | Yes                 | No                           | No                  | Yes      | No         | Yes               |

| Suitability for SNN applications | Yes                      | No          | Yes                 | Yes                 | Moderate                     | Yes                 | Yes      | Moderate   | Moderate          |

表 1.1 新興記憶體性能比較圖，FeFET 本身具有較高的開關比並且允許多位元的操作[2]。

## 1.2 鐵電性材料及鐵電記憶體

### 1.2.1 鐵電性材料

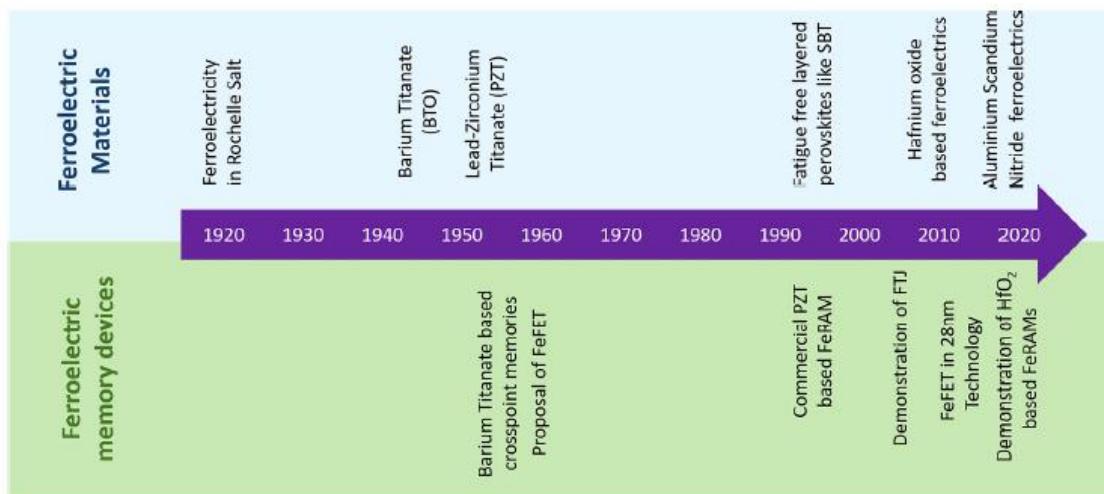

鐵電性材料的發展如圖 1.2 所示[3]，可以看到鐵電材料在 100 多年前就已被人們所知。使用 PZT 所製成的鐵電記憶體已有量產但因其在製程上會有  $Pb/O_2$  擴散問題使其無法與現有邏輯製程相容[4] 並且薄膜在一定厚度下鐵電性會急遽下降，無法繼續微縮。而到了 2010 年初，基於二氧化鈿( $HfO_2$ )的鐵電材料正式被提出，由於二氧化矽在微縮到幾奈米以下會有嚴重的漏電流問題，二氧化鈿本身具有相對高的介電係數(~30)可以在相同厚度下實現更大的電容，在先進製程中被廣泛用於電晶體的介電層，用以減少在微縮過程中所造成的閘極漏電流。因此基於二氧化鈿的鐵電材料不僅可與現有的先進製程相容，並且具有微縮特性，使鐵電記憶體成為新興記憶體的熱門候選人。

圖 1.2 鐵電性材料發展時間圖，PZT 具有在製程上的問題，而  $HfO_2$  可以與現有邏輯製程兼容[3]。

## 1.2.2 鐵電材料原理

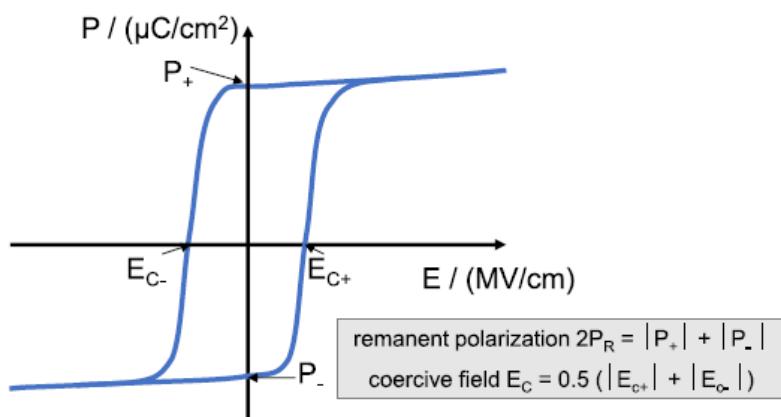

鐵電材料具有記憶效應可以從圖 1.3 來解釋[5]，當今天寫入的電場大於鐵電層本身的矯頑電場(Coercive Filed,  $E_c$ )時，鐵電層的偶極會翻轉。而在電場移除後，極化量並不會消失，殘餘的極化量稱為殘餘極化(Remant Polarization,  $P_r$ )，而若希望改寫極化方向只需要施加反向電場使其大於矯頑電場即可。其具有永久極化特性，可以做為非揮發性記憶體使用。

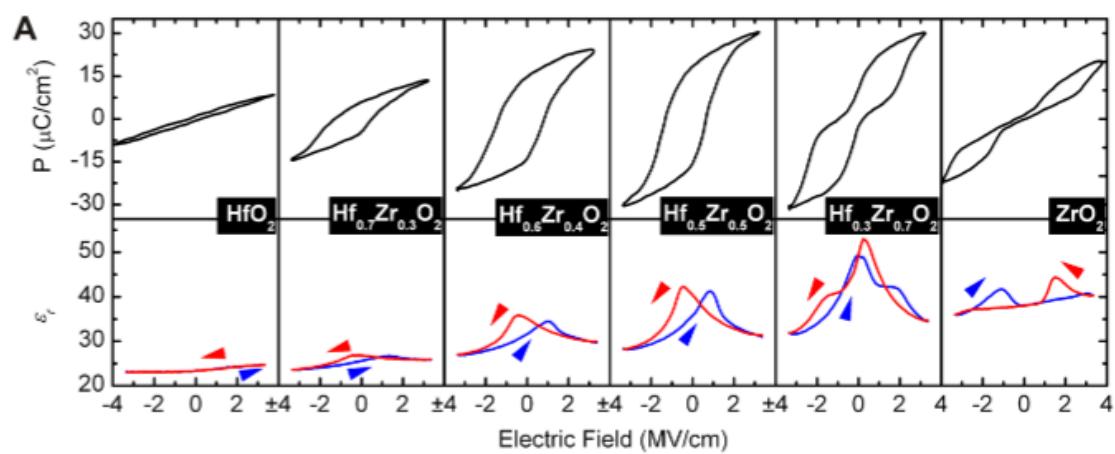

基於二氧化鉿的鐵電材料主要是藉由參雜其他元素使其能穩定在鐵電相，最常見的參雜元素為鋯(Zr)，根據不同參雜比例，其 PV 特性也會有所不同。過小的比例鐵電性不明顯，過大的參雜比例則是會展現出反鐵電性。因此一般而言常見的 HZO 摻雜比例是 0.5，如圖 1.4 所示[6]。而基於二氧化鉿的元件具有較高的矯頑電場，使其相對於 PZT/SBT 等鐵電材料可以更有效的抵禦去極化場(Depolarization Field,  $E_{dep}$ )[7]。去極化場的成因主要為金屬本身並非完美導體，因此無法完全屏蔽外在電場，以及介電層的存在導致無法完全補償因極化所產生的電荷，因此即使今天外在電壓移除後，在鐵電層仍會有不為零的反向電場，使得儲存的極化量會隨時間減少。而越高的矯頑電場意味著偶極越難被翻轉，因此在相同的去極化場下，其受到的影響會較小。

圖 1.3 鐵電 PV 特性圖， $P_r$  代表了當外在電場移除後剩下的極化量，而  $E_c$  則是翻轉鐵電層所需的最小電場[5]。

圖 1.4 不同摻雜比例 HZO 的 PV 圖，可以發現在摻雜比例為 0.5 時鐵電性最為明顯[6]。

### 1.2.3 鐵電記憶體種類

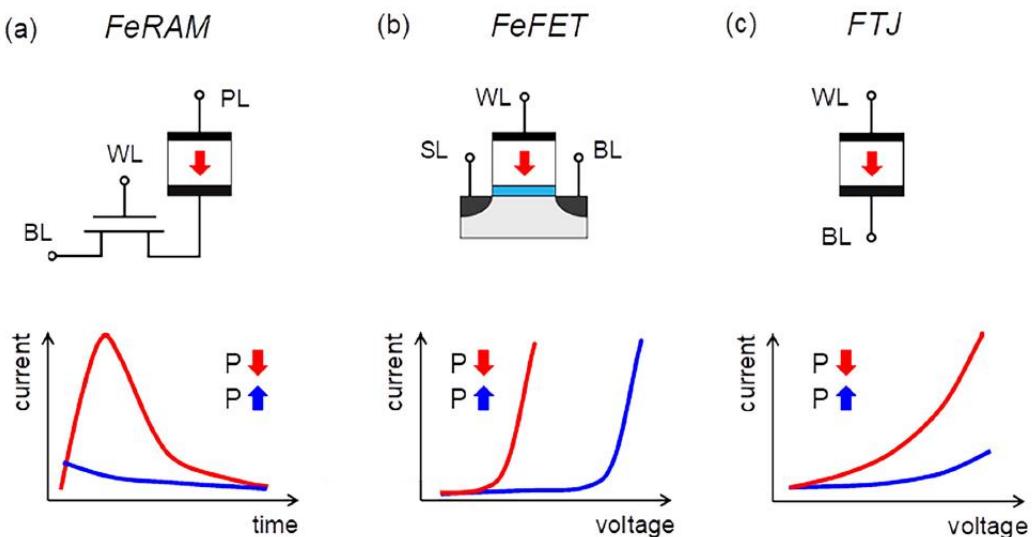

而根據其架構鐵電記憶體可以細分為三種分別是：鐵電隨機存取記憶體(FeRAM)、鐵電場效電晶體(FeFET)、鐵電穿隧結(FTJ)[3]，如圖 1.5 所示。在圖 1.5 (a) 中的 FeRAM 具有與 DRAM 非常相似的結構，僅是將原本電容器中的介電質換成具有鐵電特性的材料，其操作原理為讀取鐵電中的極化狀態，不同的極化方向會使位元線(Bit Line, BL)電壓產生改變，因此可以藉由微小的電壓改變來判斷其儲存的數據。在圖 1.5 (b) 中的 FeFET 則是將傳統電晶體的介電層換成鐵電層，其原理為藉由寫入的極化方向去改變電晶體的臨界電壓(Threshold Voltage,  $V_{th}$ )，在讀取的時候，因兩個態臨界電壓的不同因此讀出的電流會有差異，可以藉由電流差異來判斷儲存的資料。最後在圖 1.5 (c) 中，FTJ 藉由鐵電的極化方向而改變所看到的能障高度，不同能障高度對應到不同的阻值，使得讀取的電流不同，可以用來儲存 0 或 1。

圖 1.5 鐵電記憶體種類：(a)FeRAM，(b)FeFET，(c)FTJ[3]。三種鐵電記憶體皆是透過不同極化方向，使讀取電流產生差異。

## 1.3 鐵電場效電晶體

### 1.3.1 操作原理

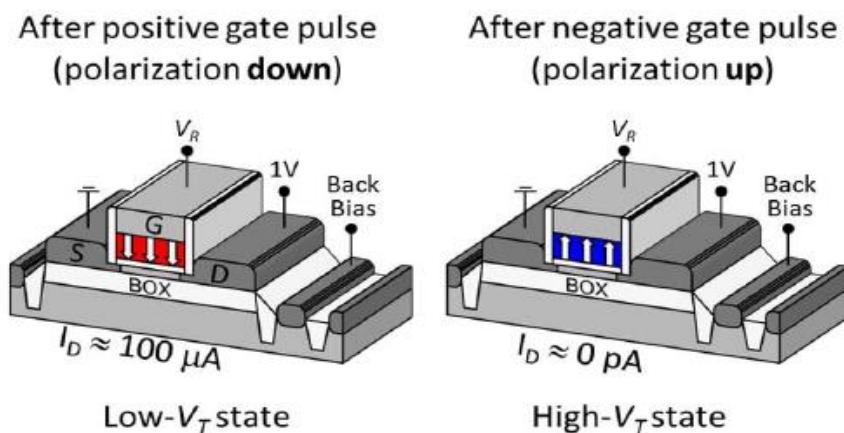

鐵電場效電晶體(FeFET)是藉由將傳統 MOSFET 的介電層替換成具有鐵電性的鐵電層，其操作原理為藉由在寫入時給不同的寫入電壓，將鐵電層寫到不同極化方向進而調節其臨界電壓[8]，如圖 1.6 所示。以 NMOS 為例，在寫入時，給予閘極(Gate)足夠的正電壓時使鐵電層的偶極皆指向下方時，可以使通道產生電子，因此臨界電壓會往左平移，使電晶體更容易打開，而若在寫入時若是給予負電壓則會在通道累積更多的電洞，因此臨界電壓會往右平移。在讀取時因兩個態的臨界電壓有差異，讀出的電流會有所不同，因此可藉由讀出的電流來判斷儲存在 FeFET 中的資料。

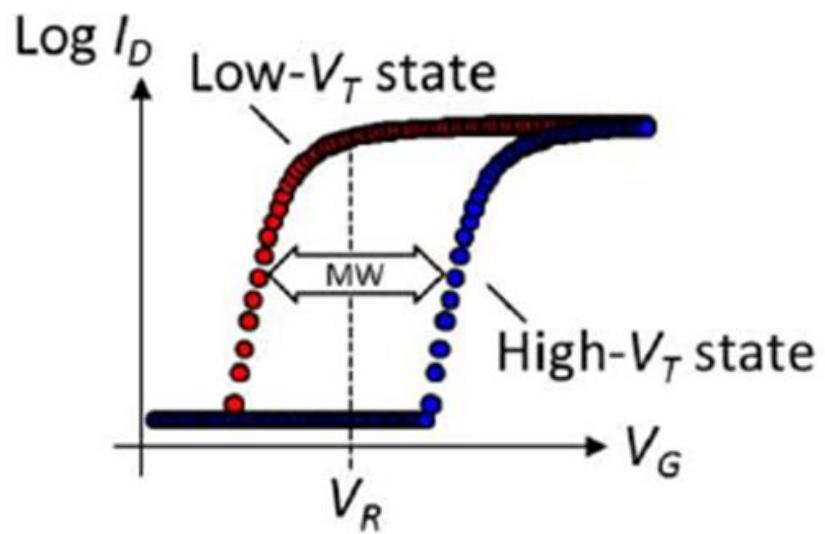

而衡量 FeFET 一個重要的指標為記憶體視窗(Memory Window, MW)，如圖 1.7 所示，圖中兩條曲線分別代表了在不同極化方向下所量測的電流電壓關係。記憶體視窗(Memory Window, MW)的定義即為兩者的臨界電壓差：

$$MW = V_{th,high} - V_{th,low}$$

越大的 MW 代表了 0 與 1 可以被越容易的區分，太小的 MW 在考慮變異度後可能會使兩個態靠的太近進而使 0 跟 1 無法被分辨導致錯誤。

圖 1.6 鐵電場效電晶體在兩個極化方向的電流差異，正寫入電壓可以使通道累積電子；負寫入電壓則是累積電洞[8]。

圖 1.7 鐵電場效電晶體記憶體視窗，記憶體視窗為兩個臨界電壓相減[8]。

### 1.3.2 記憶體視窗

理論上對於 MFIS (Metal-Ferroelectric-Insulator-Semiconductor)結構的鐵電記憶體，其最大的 MW 為[9]:

$$MW_{\max} = 2E_c t_{FE} \left(1 - \frac{\epsilon_{FE} E_c}{\eta P_s}\right) \doteq 2E_c t_{FE} = 2V_c \quad (1)$$

$$\tanh(\eta) = \frac{P_r}{P_s} \quad (2)$$

其中  $t_{FE}$  為鐵電層的厚度， $V_c$  為矯頑電壓。一般而言電晶體本身在反轉區時所對應的面電荷密度( $\sim 10^{-2} \mu\text{C}/\text{cm}^2$ )比  $P_r$  小很多， $P_r$  增加雖然可以產生更多偶極，但對於 MW 影響並不大。從式(1)和式(2)可以發現在殘餘極化以及飽和極化比值固定時，鐵電層的殘餘極化對於 MW 最大值的影響很小，在一階近似下可以認為只與鐵電的矯頑電場有關。但上述公式並未考慮去極化場的影響，過高的  $P_r$  會有較高的去極化場，使其儲存的極化量會減少。如圖 1.8 所示[10]，可以發現  $P_r = 20 \mu\text{C}/\text{cm}^2$  相較於  $P_r = 5 \mu\text{C}/\text{cm}^2$  在寫完後反而有更小的極化量，因此對於鐵電記憶體來說  $P_r$  是需要最佳化的。雖然理論上  $E_c$  越大可以有越大的 MW，但也代表著需要更高的寫入電壓去翻轉偶極，若今天寫入電壓不足以翻轉偶極的話，會使得鐵電不是操作在接近飽和循環上(Saturation Loop)，而是操作在次循環(Minor Loop)，進一步使 MW 減小。而對於低壓操作的情況往往不是操作在飽和循環，使得在低壓的條件下越大的  $E_c$  並不一定有最大的 MW。

圖 1.8 考慮去極化場後的極化量 vs 時間，可以發現當殘餘極化太大時，在寫入電壓移除後儲存的極化量反而會變小[10]。

## 1.4 鐵電電晶體記憶體視窗最佳化

### 1.4.1 浮動閘極鐵電場效電晶體

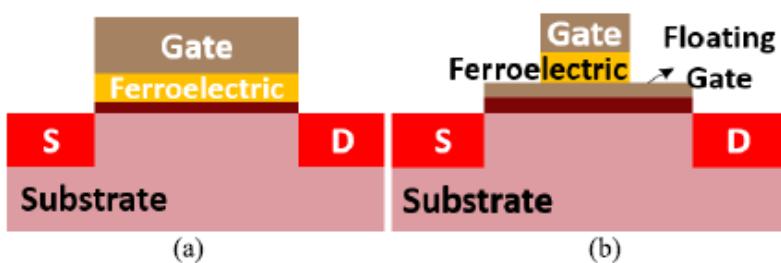

鐵電記憶體雖有相較於 Flash 較低的寫入電壓( $4\text{ V} \sim 5\text{ V}$ )，但相對於先進製程而言仍是相對高的電壓。因此如何降低鐵電記憶體寫入電壓，並保有一定的 MW 是一個很重要的議題。在傳統鐵電電晶體的結構中因為 IL (Interfacial Layer)層的存在，在寫入時大多的跨壓都落在 IL 層上，不僅有可靠度的問題，MW 也會減小。導致寫入電壓需要比矯頑電壓大上許多，才能有足夠的 MW。

過去有許多人提出可以藉由加入浮動閘極(Floating Gate)在鐵電層以及氧化層間[11]，並且調整鐵電層與電晶體層的面積比 (Area Ratio, AR)來改善 MW，並降低寫入電壓，如圖 1.9(b)所示。而另一種變形則是將鐵電電容做在後段製程，以及電晶體做在前端製程，如圖 1.10 所示[12]。後段製程的鐵電電容不僅具有較低的熱積存，使得在熱退火過程中鐵電相更容易形成[13]，並且具有可調性的面積比可以增加 MW。

圖 1.9 (a)傳統鐵電電晶體，(b)加入浮動閘極的鐵電電晶體，可以自由調整鐵電層的面積[11]。

圖 1.10 後段製程鐵電電容及前端製程電晶體，藉由金屬連接鐵電電容與下方電晶體[12]。

## 1.4.2 鐵電電晶體最佳化面積比相關文獻

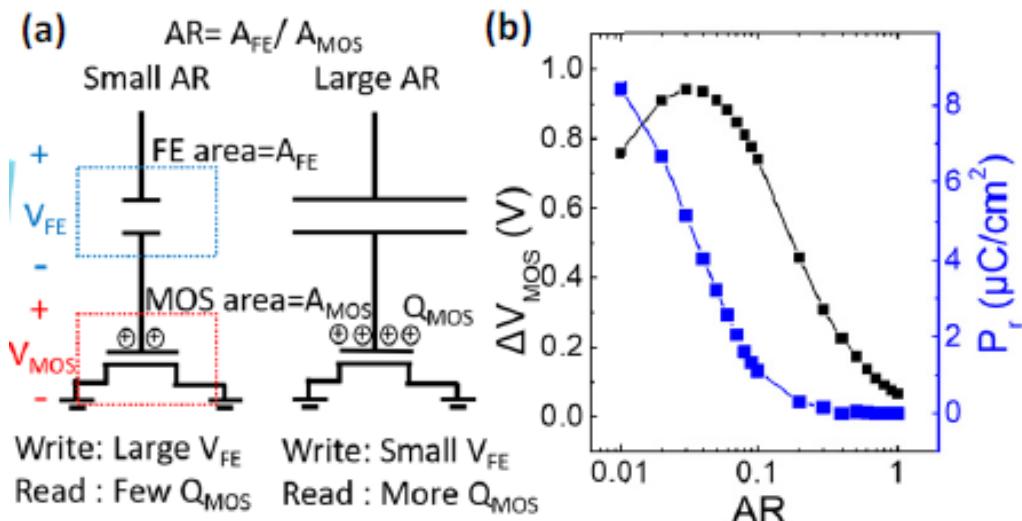

減小面積比增加 MW 的原理，如圖 1.11(a)所示[14]。AR 定義為鐵電電容與電晶體面積比。在寫入階段時，落在鐵電層的電壓會與鐵電電容成反比，而當下方電晶體面積固定時，鐵電層面積越小則落在上面的跨壓越大，所寫入的極化量會越大如圖 1.11(b)中的藍線。但總電荷等於極化量乘以面積，當面積減小到一定的值後，在通道感應出的載子數降低，此時 MW 就不再增加而是減少，因此可以發現存在一個最佳的 AR 使得 MW 可以達到最大值如圖 1.11 (b)中黑線的峰值。

圖 1.11 (a)不同面積比對總電荷的影響，越小的面積雖然在寫入時可以增加跨壓，但總電荷可能會減小，(b)不同面積比對閘極電壓差關係， $\Delta V_{MOS}$ 存在一個最大值，AR 再繼續減小反而會減少 $\Delta V_{MOS}$ [14]。

在圖 1.12 中，D. Lehninger et al. [13]發現在不同電壓下的 MW 變化，在 0 V ~ 6 V 的區間隨電壓增加，鐵電層翻轉的偶極變多，使得 MW 會隨之增加。在 6 V ~ 12 V 間會出現一個平台，原因為能翻轉的偶極達到飽和，因此 MW 並不會隨電壓增加而增加。但在大於 12V 的區域，由於電洞被捕獲使其 MW 隨之增大，但 MFM 也開始產生漏電流。圖 1.13[13]則是考慮不同 AR 的影響，可以發現在相同電壓下 AR 越小對應的 MW 越大，若希望在 10 V 以內的寫入電壓可以有最大的 MW，並

且 MFM 不要有漏電流的話， $AR = 0.6$  是最佳的解。而在該圖中也可以發現 AR 越小，出現平台的電壓也越低，呼應了減小 AR 可以增加落在鐵電層上的跨壓。而過大的 AR 在 10 V 內鐵電層的偶極會無法全部翻轉，如  $AR = 1.8 \sim 29$ 。因此不會出現如圖 1.12 的平台。

圖 1.12 (a)不同閘極電壓對記憶體視窗影響(考慮鐵電翻轉及電荷捕捉效應)，電壓過大時，因電荷捕捉反而會增加 MW，(b)不同鐵電層電壓對鐵電層電流影響，電壓過大時會產生漏電流[13]。

圖 1.13 閘極電壓對記憶體視窗影響(不同 AR)，可以發現 AR 越小 MW 越大[13]。

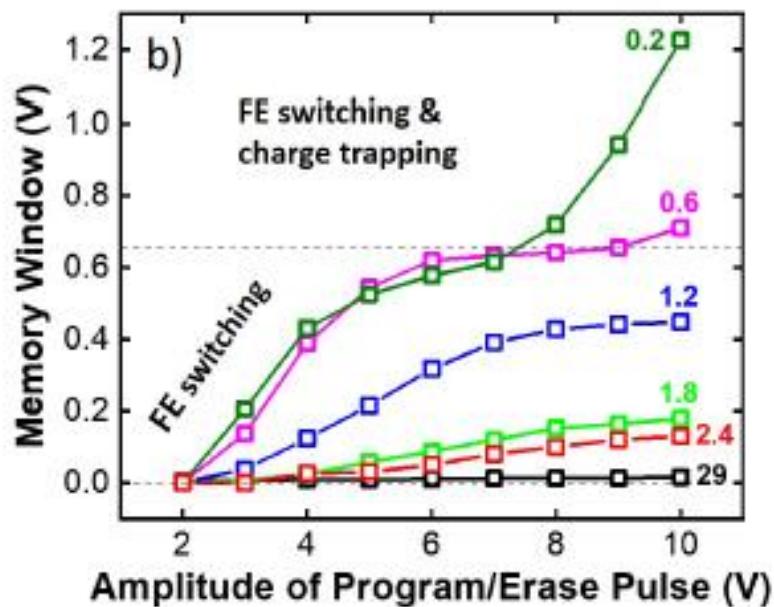

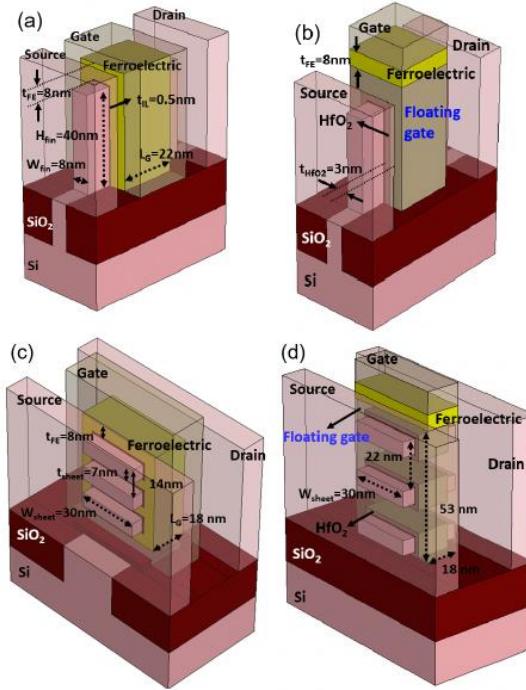

前面所介紹的都是基於平面電晶體，G. Choe et al. [11]在圖 1.14 中，考慮了基於 FinFET 以及 Nanosheet 的鐵電電晶體。圖 1.14 (a)中的結構是傳統的鐵電電晶體  $AR = 1$ ，圖 1.14(b)則是加了浮動閘極的結構，稱為 FeM-FinFET，其  $AR < 1$ 。從圖 1.15(a)可以看到同樣在 4 V 的寫入電壓，圖 1.15(b)具有比圖 1.15 (a)要高兩倍以上的 MW，代表減小鐵電層面積可以有效增加 MW。FinFET 由於本身是三維結構，在搭配相同面積的鐵電電容下，FinFET 電晶體本身的電容相較平面電晶體來得更大，因此在寫入時會有更多的跨壓落在 FinFET 的鐵電層。而基於將電晶體等效電容變大的想法，G. Choe et al. [11]在圖 1.14(c)及圖 1.14 (d)展示了以 Nanosheet 所做成的鐵電電晶體，在圖 1.15(b)可以發現 Nanosheet 在寫入電壓降低到 1.5V 時仍有 0.47V 的 MW，相當於圖 1.15 (a)中 Fe-FinFET 在 4V 時的 MW，因此使用浮動閘極的 Nanosheet 相較於 Fe-FinFET 更能增加寫入時落在鐵電層上的跨壓，使其可以操作在更低的寫入電壓。若 Nanosheet 的層數增加電晶體電容也會隨之增加，在圖 1.16 中 G. Choe et al. [11]比較了 FeM-FinFET 與不同層數 Nanosheet 的 FeMFET，可以看到越多層的 Nanosheet 其 MW 也越大，但 SS 越差，原因在於越小的 AR，代表大多的跨壓皆落在鐵電層上，意味著對於電晶體閘極的控制力越差，因此 SS 會上升。另一個值得注意的是越多層的 Nanosheet 具有越小的去極化場(Depolarization Field)，因整體的總電容增加，使得在相同極化量下落在鐵電層的電場會減小，進而使鐵電層的偶極反轉速度減緩。

圖 1.14 (a)Fe-FinFET，其  $AR = 1$ ，(b)FeM-FinFET，藉由加入浮動閘極使  $AR < 1$ ，(c)Fe-Nanosheet，較 FinFET 的電容來得大使其可以在相同電壓有更大的 MW，(d)FeM-Nanosheet，加入浮動閘極並且有更大的電晶體電容[11]。

圖 1.15 不同電晶體的  $I_D$ - $V_G$  (a)FinFET，(b)Nanosheet。Nanosheet 因本身具有較大的電晶體電容，因此在 1.5 V 寫入電壓下會有較 FinFET 來得大的 MW[11]。

圖 1.16 FeM-FinFET 與不同層數 Nanosheet 的比較圖，當 AR 減小時 MW 會跟著上升，但 SS 會減小[11]。

最後，是關於不同鐵電記憶體的比較，如表 1.2 所示，K. Ni et al. [15]將可以調變 AR 的架構稱為 FeMFET，其相較於傳統的 FeFET 而言可以允許更低的寫入電壓，並且減小在電晶體 IL 層的跨壓，進一步改善耐受力(endurance)的問題。加入浮動閘極，使 FeMFET 不像 FeFET 有電荷捕捉效應(charge trapping)，可以改善 MW。而 FeMFET 相較於 FeRAM 的最大優勢是可進行多位元的操作，使其可以應用於人工智慧(Artificial Intelligence, AI)以及記憶體內運算(Computing in Memory, CIM)。

| Decreased $A_{FE}/A_{MOS}$                                      |             | FeRAM           | FeFET           | FeMFET |

|-----------------------------------------------------------------|-------------|-----------------|-----------------|--------|

| <input type="radio"/> $E_{FE}$ increases,<br>$E_{IL}$ decreases |             |                 |                 |        |

| <input type="radio"/> Write Voltage decreases                   |             |                 |                 |        |

| <input type="radio"/> No charge trapping in FE                  |             |                 |                 |        |

| <input type="radio"/> Improved endurance                        |             |                 |                 |        |

| $A_{FE}/A_{MOS}$                                                | N/A         | 1               | Tunable         |        |

| Read scheme                                                     | Destructive | Non-Destructive | Non-Destructive |        |

| Write voltage                                                   | 3 V         | 4 V             | 1.8 V           |        |

| Charge trapping                                                 | None        | Significant     | None            |        |

| Endurance                                                       | Good        | Bad             | Good            |        |

| Multi-bits                                                      | Bad         | Good            | Good            |        |

表 1.2 不同鐵電記憶體特性比較，FeMFET 不僅可以使操作電壓下降，還能減少在 IL 層的跨壓[15]。

### 1.4.3 藉由高介電係數側壁改善記憶體視窗

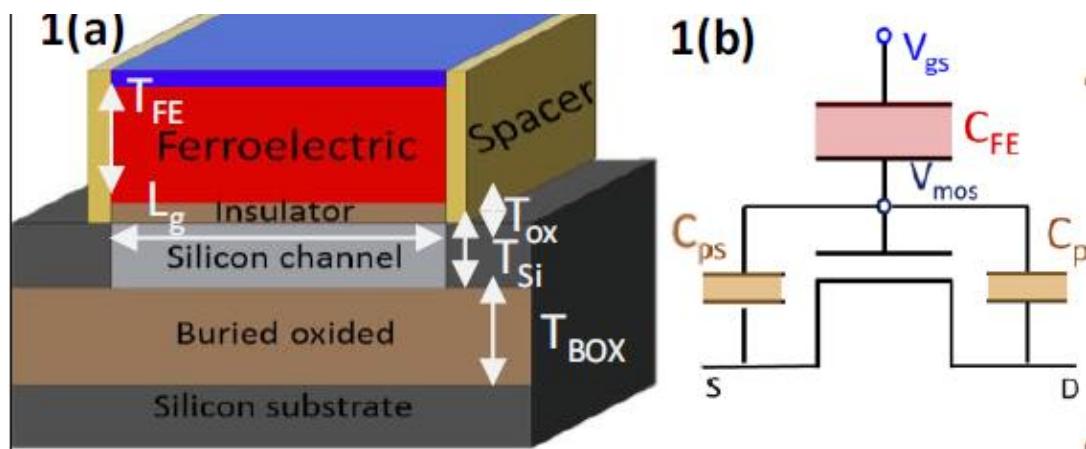

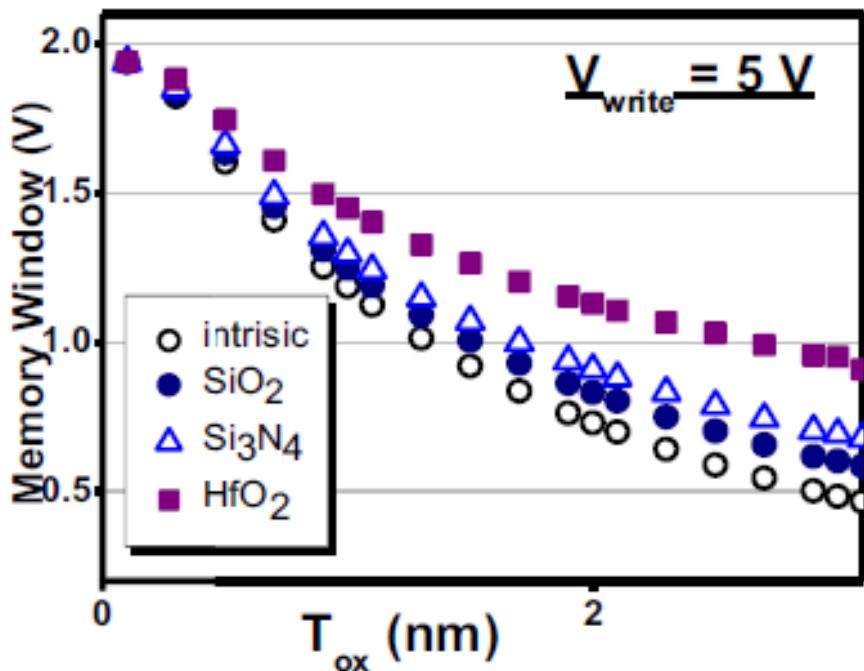

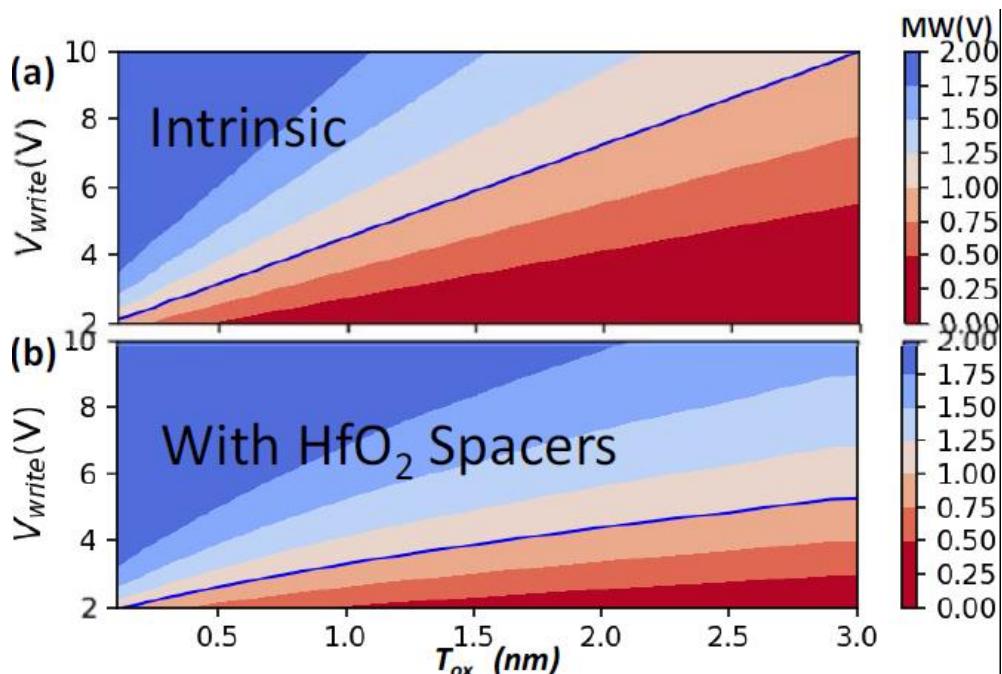

除了藉由減小鐵電電容面積來增加 MW，F. -C. Wu et al. [16]提出了使用高介電係數側壁(High  $k$  Spacer)也能改善 MW，在圖 1.17(a)中，使用了 UTBSOI 結構的鐵電電晶體，而圖 1.17(b)是其等效電容圖，根據前面所提及的分壓公式，電晶體的等效電容越大落在鐵電層的跨壓就會越大，儲存在鐵電層的極化量也會隨之上升。而提升側壁的介電係數可以增加電晶體的等效電容有助於改善 MW。圖 1.18 中可以看到在固定氧化層厚度下，使用  $\text{HfO}_2$  的側壁的鐵電電晶體，具有比未加側壁的鐵電電晶體更大的 MW。有了高介電係數的側壁，我們可以降低寫入電壓並保持一定的 MW，如圖 1.19 中在固定氧化層為 2nm 的情況，要達到 0.75V 的 MW 使用高介電係數的側壁，寫入電壓可以從 7V 降低至 4V。因此高介電係數的側壁可以降低寫入電壓，並維持一定的 MW，具有在低功耗應用的潛力。

圖 1.17 (a)UTBSOI 結構圖，(b)等效電容模型。藉由增加在下面電晶體的電容，可以增加在寫入時落在鐵電層的跨壓[17]。

圖 1.18 不同側壁介電常數在  $V_{\text{write}} = 5 \text{ V}$  時的 MW，側壁的介電常數越高，MW 越大[17]。

圖 1.19 (a)本徵電晶體在不同氧化層厚度及寫入電壓下的 MW 等高線圖，(b)具有  $\text{HfO}_2$  側壁電晶體，在不同氧化層厚度及寫入電壓下的 MW 等高線圖[17]。

## 1.5 鐵電電晶體陣列

### 1.5.1 AND 陣列

用一顆鐵電電晶體來儲存一個比特(bit)是最傳統的作法，最常見的架構為 AND 陣列，如圖 1.20 所示。由於在同一列(row)中，所有電晶體皆共用同一條字元線(Word Line, WL)。在寫入某一個單元(cell)時，與他同一列的其他單元會受到寫入干擾(Writing Disturb)，為了減小寫入干擾，有人提出了兩種寫入法(Writing Scheme)來解緩寫入干擾[17]。

P. R. Gennslar et al. [17]在圖 1.20(a)中使用了  $V_w/2$  的寫入法，這個寫入法確保了除了正在寫入的單元外，其他單元最多只會受到一半的寫入電壓干擾，。若希望進一步減少干擾的話，圖 1.20 (b)中使用了  $V_w/3$  的寫入法，這樣可以保證在寫入時，未選取單元只會受到三分之一的寫入電壓干擾。但即使採用了  $V_w/3$  的寫入法來減小未選取單元所受的干擾，一旦寫入/擦除循環到  $10^3$  以上 MW 就會開始產生嚴重的衰減，如圖 1.21 所示，可以看到越大的寫入電壓會衰減的越快，因此該結構的陣列雖然是最為簡單的，但可靠度會是一個很大的挑戰。

圖 1.20 AND 陣列 (a) $V_w/2$  寫入法，(b) $V_w/3$  寫入法。兩種寫入法都能使得未選取單元受到的干擾電壓減小[18]。

圖 1.21 在不同寫入電壓下的 MW 變量 vs P/E 循環，當 P/E 循環上升到臨界值

MW 皆會衰減[18]。

## 1.5.2 1T1FeFET 陣列

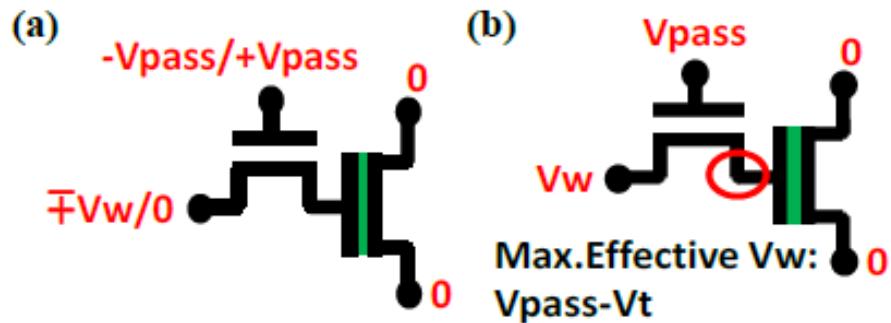

為了使陣列可操作的循環變多，過去許多人提出了使用 1T1FeFET 所組成的陣列來避免寫入干擾[18]。B.-K. Huang et al. [18]在圖 1.22 中，藉由在鐵電電晶體的閘極加一顆存取電晶體(Pass Transistor)，在寫入階段時，同一列的所有存取電晶體皆會打開，但因為寫入電壓是給在汲極(Drain)，因此其他單元並不會受到寫入干擾。其偏壓情況如圖 1.23 所示。注意到  $V_{\text{pass}}$  需要大於等於  $V_w$  才能將欲寫入的電壓傳出去，但這樣的陣列會有兩個缺點，第一為電晶體的  $V_{GS}$  最大會等於  $2V_w$  對於電晶體可靠度會有影響，第二為真正傳到鐵電電晶體的最大電壓是  $V_{\text{pass}}-V_{\text{th}}$  會使得寫入效率下降，因此 MW 會減少。

該陣列架構相較於 AND 陣列來說具有優異的抗干擾能力，但壞處為需要使用兩顆電晶體去儲存一個比特，使得陣列的密度減小，並且由於寫入效率下降使得若要實現相同 MW，寫入電壓會比 AND 陣列稍微來得高。

圖 1.22 1T1FeFET 陣列，藉由加入存取電晶體來避免寫入干擾[19]。

圖 1.23 1T1FeFET(a)未選取單元的偏壓情況，(b)選取單元的偏壓情況。 $V_{GS}$  最大會是 2 倍的寫入電壓，對於電晶體可靠度會有影響[19]。

## 1.6 研究動機

鐵電電晶體做為一大有潛力新興記憶體，如何降低其寫入電壓，並保持一定 MW 是大家努力的方向，過去有許多調整鐵電電容與電晶體面積比改善 MW 的研究。而過去的論文都指出存在一個最佳的面積比，使得 MW 可以達到最大值。但沒有人研究過該最佳的面積比與寫入電壓及各鐵電參數間的關係，如殘餘極化、矯頑電場等。另一方面，關於高介電係數側壁可以增加 MW 的研究並沒有很多，因此本研究探討關於最佳化面積比及最佳化記憶體視窗與不同側壁材料的關係。

本研究將使用 Sentarus TCAD 內建的鐵電模型來模擬，並且以 MATLAB 計算模擬完的  $I_D$ - $V_G$  來得到 MW。我們會使用電容分壓模型、電荷守恆來解釋最佳化面積比以及最佳化 MW 與寫入電壓跟各個參數的關係。使之後的設計者可以根據其電晶體及鐵電電容的參數，知道大約在什麼範圍的面積比可以擁有最大的 MW。接著我們會討論不同面積比對於設計鐵電電晶體陣列的影響，探討記憶體單元受到寫入干擾後的 MW，如何隨著鐵電參數以及不同面積比去改變。最後我們會提出一個可應用於低壓操作的最佳化設計方法，使得鐵電電晶體寫入電壓可以下降並具有抗寫入干擾的能力。

## 1.7 論文架構

本論文由四個章節所組成，第一章是導論，介紹鐵電元件的歷史及特性，並探討過去研究中關於透過改變面積比優化記憶體視窗的論文，也探討在陣列上的應用以及遭遇的困難。第二章為鐵電模型與研究方法，介紹在 Sentarus TCAD 中我們使用的 Preisach Model，以及該論文如何進行關於尋找最佳化面積比的流程。第三章是關於不同寫入電壓以及不同鐵電參數對最佳化面積比，以及最佳化記憶體視窗的影響，並且會使用電容分壓以及電荷守恆模型用以解釋觀察到的趨勢。而接著會進一步探討不同側壁材料的影響，最後是應用到陣列上對於寫入干擾的抵抗能力。第四章是總結，將統整本研究，並比較在 2 V 寫入電壓下，經過最佳化的鐵電電晶體與基準線的記憶體視窗。

## 第二章 鐵電模型與研究方法

### 2.1 前言

在本章節我們將介紹在 TCAD 中所使用的鐵電模型 Preisach Model，以及介紹在該篇論文中所使用的模擬方法。我們根據 2018 IRDS Roadmap 中 7 nm 技術節點來設計我們的電晶體，並使用 TCAD 中的 mixed mode 來模擬電晶體與鐵電電容串聯而成的鐵電電晶體。並說明我們如何量測 MW，以及關於本研究中所會用到的參數定義如 AR\*、MW\*。

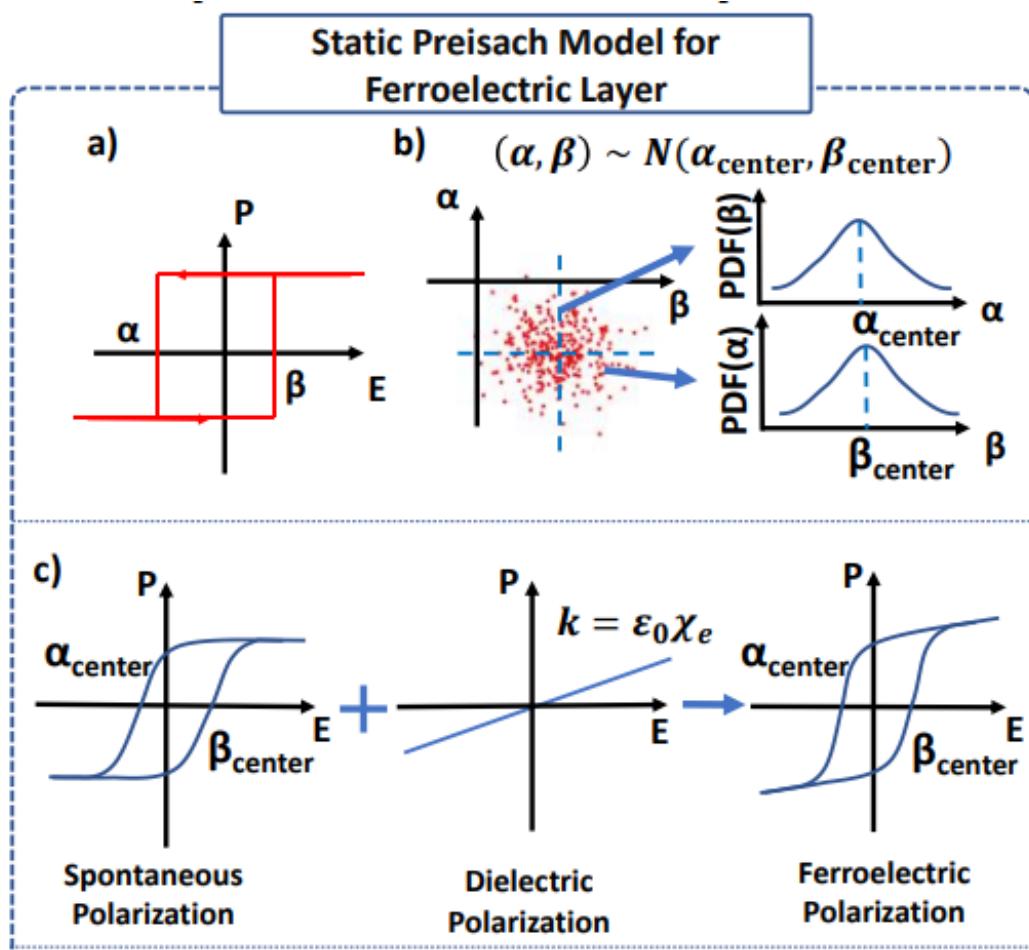

## 2.2 Preisach Model

在 Sentarus TCAD 中，用以描述鐵電現象的模型為 Preisach Model，他可用以描述多晶域的鐵電層[19]。對於單晶域而言，其鐵電層要產生極化翻轉，需要施加的外在電場超過矯頑電場( $E_c$ )，如圖 2.1(a)所示。圖 2.1 (b)的 $\alpha$  及  $\beta$  分別代表在某單一晶域的正與負矯頑電場，它會呈現一個常態分佈，其平均值就是我們平常所稱的  $E_c$ 。在該模型中鐵電層被切成非常多個晶域，每個晶域都有各自的矯頑電場，因此儘管施加的電場並未超過矯頑電場，仍會有非常少數的偶極被翻轉。其 P-E 特性如圖 2.1(c)，不同於單晶域的翻轉行為，它是呈現連續性的翻轉。而鐵電層也具有介電的特性使得永久偶極翻轉完後並不會飽和，而是呈現  $P$  正比於  $E$  的特性。

圖 2.1 (a)單晶域鐵電層 P-E 關係，(b)正負矯頑電壓分布，(c)多晶域鐵電層 P-E 特性。鐵電層的極化為鐵電極化加上介電極化[20]。

在 Preisach Model 中[20][21]，我們計算極化量的過程如下，我們根據外在的電場  $E$  去計算輔助電場  $E_{aux}$  (auxiliary field)，並用一個材料相依時間常數  $\tau_E$  去描述如式(1):

$$\frac{dE_{aux}(t)}{dt} = \frac{E(t) - E_{aux}(t)}{\tau_E} \quad (1)$$

可以看到在  $\tau_E=0$  的情況  $E(t)$  會等於  $E_{aux}(t)$ ，代表穩態。

接著我們可以使用上面所獲得的  $E_{aux}$  來計算輔助極化量  $P_{aux}$ ，如方程式(2):

$$P_{aux}(E_{aux}) = cP_s \tanh(w(E_{aux} \pm E_c)) + P_{off} \quad (2)$$

$$F(E_{aux}) = P_s \tanh(w(E_{aux} \pm E_c)) \quad (3)$$

其中  $P_s$  代表了鐵電層的飽和極化(Saturation polarization)、 $E_c$  為矯頑電場(Coercive field)， $w = \frac{1}{2E_c} \ln \left( \frac{P_s + P_r}{P_s - P_r} \right)$  為跟鐵電參數有關的因子。當上式的  $c=1$  以及  $P_{off}=0$ ，其描述的即為鐵電層的飽和循環定義為  $F(E_{aux})$  如方程式(3)。而當今天鐵電層若操作在次循環時，鐵電層的極化量就需透過伸縮常數  $c$  以及平移常數  $P_{off}$  來描述，可用以描述鐵電層的遲滯現象，它記錄了當今天外在電壓從增加到減少或減少到增加的轉折點，如圖 2.2 所示。並且記錄該點的極化量，以此去推算新的 P-E 路徑圖，其表達式如方程式(4)、(5)所示:

圖 2.2 鐵電層次循環圖。鐵電層藉由操作電壓的轉折點來決定新的極化量，可用於描述遲滯現象[20]。

$$c = \frac{P_{aux}(E_A) - P_{aux}(E_B)}{F(E_A) - F(E_B)}$$

$$P_{off} = \frac{P_{aux}(E_B)F(E_A) - P_{aux}(E_A)F(E_B)}{F(E_A) - F(E_B)}$$

可以看出次循環是以飽和循環做伸縮平移得到的圖形，也可以看出在次循環我們皆有  $c < 1$  的結果，代表了在次循環的極化量會小於飽和循環。

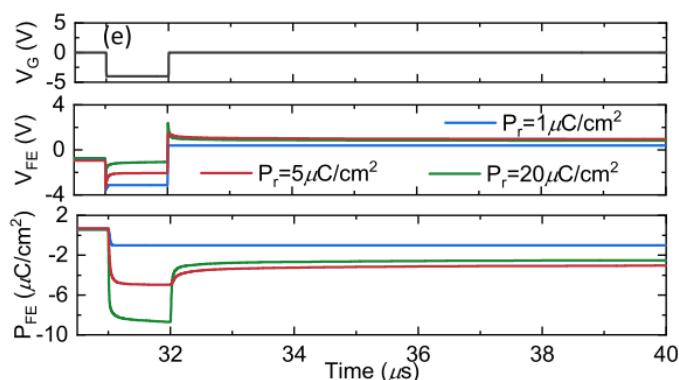

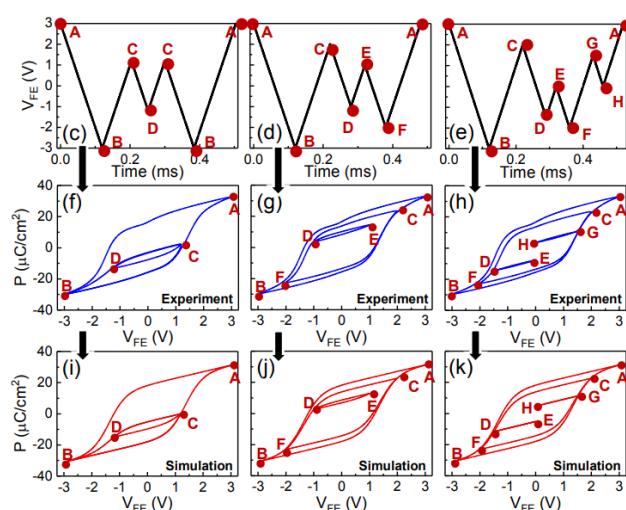

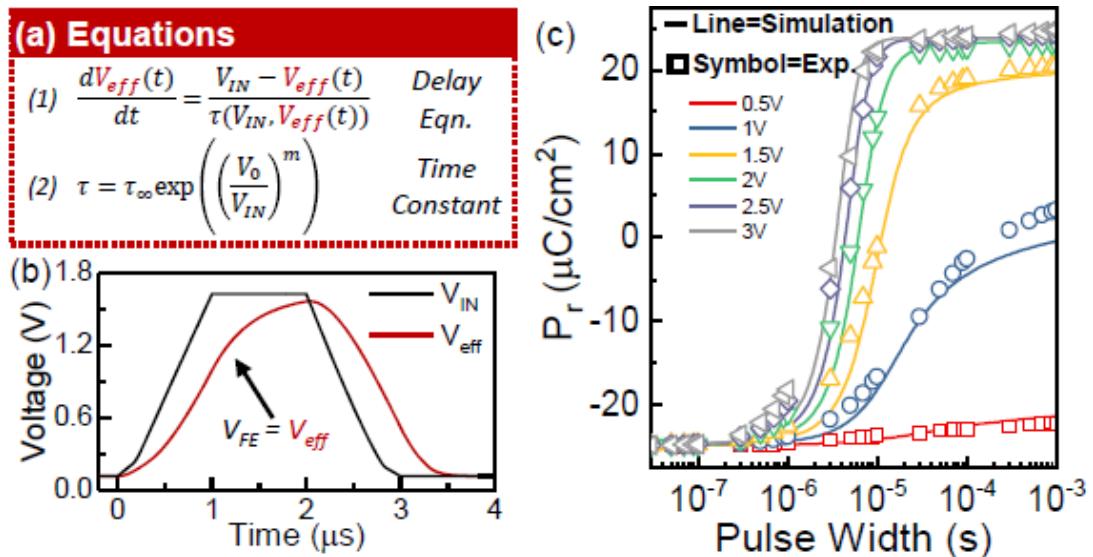

鐵電層動態切換的模型可以用圖 2.6 來解釋，圖 2.3 (a)中使用了 RC 延遲模型來描述其切換的行為，可以看到在圖 2.4 (b)中，落在鐵電層上的電壓會隨著時間增加逐漸趨於寫入的電壓值，並且注意到時間常數是鐵電層電壓的函數，越高的電壓意味著越快的切換速度，可以從圖 2.5 (c)中觀察到該現象。越高的電壓鐵電層越快翻轉完，符合實驗的數據。而在我們 TCAD 中由於時間常數只能設為常數，並不能描述動態切換的行為。因此我們會將寫入時長設為時間常數的 10 倍以確保鐵電層順利翻轉。

圖 2.6 鐵電動態切換模型(a)描述動態切換的微分方程式，(b)其微分方程式解的圖，(c)不同寫入電壓及寫入時長的模型與實驗數據校正。隨著寫入電壓上升，鐵電層翻轉越快[20]。

## 2.3 元件參數與模擬方法

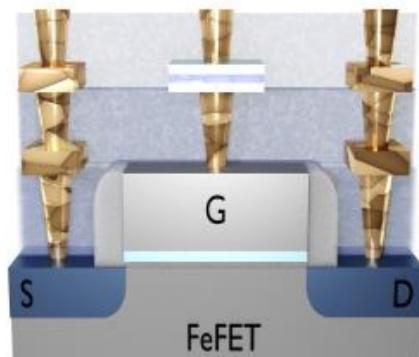

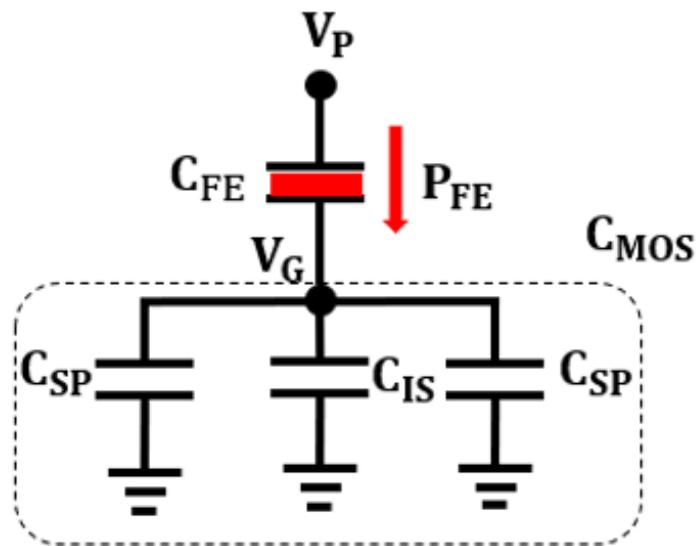

本研究使用的電晶體為 7 nm 技術節點下的 FinFET，其元件的參數是參考 2018 年 IRDS 的 Roadmap [22]，鐵電材料是藉由在電晶體閘極串聯一個後段製程相容的鐵電電容，用以實現鐵電電晶體的功能。其整體結構如圖 2.7 所示，等效電路模型如圖 2.8 所示， $V_P$  為在寫入以及讀取的節點電壓， $V_G$  為浮動閘極的電壓，電晶體的參數則如表 2.1 所示。如無特別說明本研究中 FinFET 的側壁皆為  $\text{Si}_3\text{N}_4$ ，其介電常數為 7.5。我們在 TCAD 中鐵電層的厚度固定為 10 nm 並且固定  $\text{Pr}/\text{Ps} = 0.9$ 。本研究中將研究改變鐵電電容與電晶體面積比(Area ratio, AR)對於 MW 的影響，調整 AR 的方式是藉由固定下方電晶體大小，調整鐵電電容的長寬以實現不同大小的面積比。在下一章將探討在不同寫入電壓(2 V ~ 4.5 V, 間距為 0.5 V)及不同參數如殘餘極化( $\text{Pr}$ )、矯頑電場( $\text{Ec}$ )、側壁下，最佳化 MW ( $\text{MW}^*$ ) 及對應的最佳化 AR ( $\text{AR}^*$ ) 是如何隨這些參數改變。本研究中所使用的鐵電材料為 HZO 其  $\text{Pr}$  分別為 5、10、15、20  $\mu\text{C}/\text{cm}^2$  及  $\text{Ec}$  為 0.8、1、1.2、1.5 MV/cm [3][23]，因此共有 16 種組合。而 AR 則是從 0.2 ~ 1 (間距為 0.02)，若在該區間找不到最大值則會往下做到 0.1，若在 1 ~ 0.1 也找不到最大值就會繼續往下做到 0.02。

圖 2.7 前端製程電晶體與後段製程鐵電電容串聯結構圖，下方的電晶體為根據 IRDS Roadmap 7nm 設計的 FinFET。

圖 2.8 等效電路模型，讀取及寫入皆是在鐵電電容的上極板。

|             |                            |

|-------------|----------------------------|

| $L_g$       | 22 nm                      |

| $W_{fin}$   | 40 nm                      |

| $H_{fin}$   | 8 nm                       |

| $T_{HfO_2}$ | 3 nm                       |

| $T_{SiO_2}$ | 0.5 nm                     |

| $L_{sp}$    | 7 nm                       |

| $L_{sd}$    | 7 nm                       |

| $H_{box}$   | 50 nm                      |

| $H_{sub}$   | 100 nm                     |

| $N_{sub}$   | $10^{17} (\text{cm}^{-3})$ |

| $N_{S/D}$   | $10^{20} (\text{cm}^{-3})$ |

| $W_F$       | 4.5 eV                     |

表 2.1 本論文中 7nm FinFET 之元件參數，其中  $W_F$  是金屬 TiN 的功函數。

在 TCAD 中，我們使用如圖 2.9 的波型來量測 MW，其中 PGM / ERS 分別代表將鐵電層寫入 LVT (Low  $V_{th}$  state) 及 HVT (High  $V_{th}$  state) 的操作，而 ret+ / ret- 則代表了在正/負寫入電壓移除後鐵電層的狀態。而在讀取時使用三角波從 -1.5 V ~ 1.5 V，以獲得汲極電流對電壓關係，而電晶體的汲極電壓( $V_D$ )，在寫入時固定為 0 V 讀取時固定為 0.05 V。在  $E_c = 1.5 \text{ MV/cm}$  的例子中，因其 MW 過大會導致  $V_{th,high}$  在小 AR 區域超過 1.5 V，因此讀取電壓會使用 -2 V ~ 2 V。本模擬中量測  $V_{th}$  的方法是採用定汲極電流法 (Constant drain current method) 在  $I_{DS} = \frac{W}{L} \times 10^{-7} = 4 \mu\text{A}$ ，

其中  $W$  及  $L$  為 FinFET 的等效寬度，其值為  $2H_{fin} + W_{fin} = 88\text{ nm}$  及 閘極長度  $22\text{ nm}$ ，如圖 2.10 所示。從對應電流讀取對應於在鐵電電容上所施加的電壓即為  $V_{th}$ ，將  $V_{th, high}$  及  $V_{th, low}$  相減即可獲得 MW。

圖 2.9 量測 MW 的波型圖，在讀取階段讀取電壓為  $-1.5\text{ V} \sim 1.5\text{ V}$ 。

圖 2.10 用定汲極電流法量測 MW，紅色虛線是我們取  $V_{th}$  的電流準位為  $4\text{ } \mu\text{A}$ 。

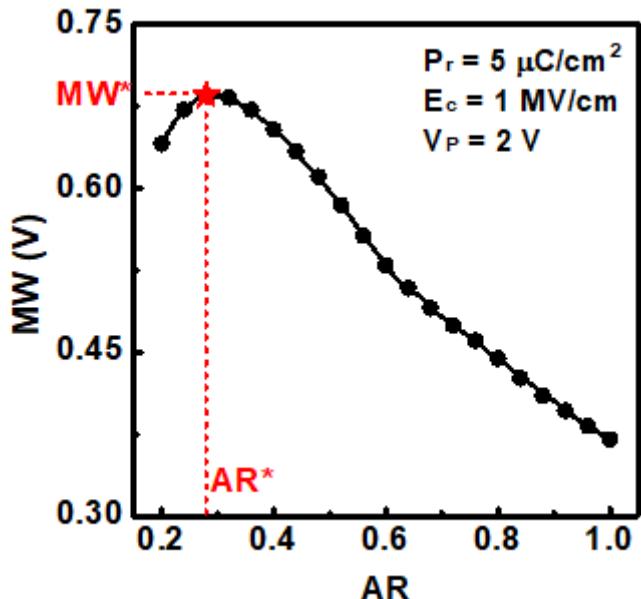

接著，我們會量測在不同參數下，MW 隨著 AR 的變化曲線，找出其  $AR^*$  以及  $MW^*$ 。以圖 2.11 為例，可以發現在  $AR = 0.28$  有最大的  $MW = 0.68\text{ V}$ ，因此  $AR^* = 0.28$  及  $MW^* = 0.68\text{ V}$ 。而在得到所有鐵電參數的  $AR^*$  以及  $MW^*$  後，我們

會從中找出最大的  $MW^*$ ，該組參數代表了藉由改變 AR 在該電壓下，能達到最好 MW 的鐵電參數。接著會探討在不同側壁材料下， $MW^*$  跟  $AR^*$  是否會因側壁改變而產生變化，最後將前面得到的最佳設計參數，應用在低功耗( $V_P = 2$  V)鐵電電晶體陣列上，並探討不同 AR 及側壁材料對於寫入干擾(Write Disturbance)的影響。

圖 2.11  $AR^*$  以及  $MW^*$  示意圖( $P_r = 5 \mu\text{C}/\text{cm}^2$  及  $E_c = 1 \text{MV}/\text{cm}$ )，紅色星星代表最大 MW 的位置為  $MW^*$ ，對應的 AR 即為  $AR^*$ 。

# 第三章 不同操作條件對 AR\* 及 MW\* 之影響分析

## 3.1 前言

過去許多研究已提出藉由改變 AR，在低電壓下實現大 MW，但過去沒有研究指出 AR\* 及 MW\* 如何隨著鐵電元件參數以及側壁改變。因此本章節我們將使用 TCAD 模擬各寫入電壓下 ( $V_P = 2\text{ V} \sim 4.5\text{ V}$ ) 不同鐵電參數如殘餘極化、矯頑電場、側壁對於 AR\* 以及 MW\* 的影響。我們會先模擬在不同條件下的 AR\* 及 MW\*，觀察其現象並整理出規律後，再使用對應的等效電容模型以及電荷守恆定律來解釋。最後會將前面所得到的最佳鐵電元件參數應用在陣列上，並分析在 2 V 的低寫入電壓下寫入干擾(write disturb)跟 AR 以及側壁的關係。

## 3.2 AR\*及 MW\*與不同鐵電參數及電壓關係(固定側壁)

### 3.2.1 AR\*及 MW\*與不同參數及寫入電壓的關係

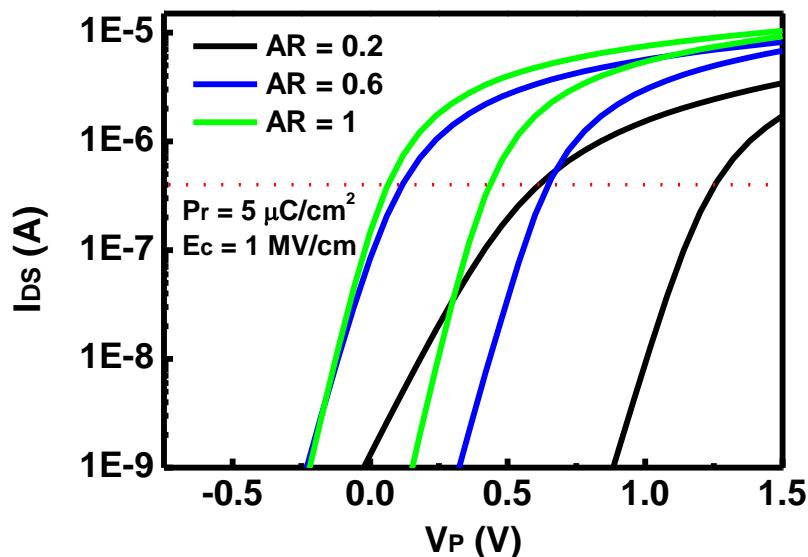

在本小節，我們探討不同電壓下以及不同鐵電參數，在改變 AR 對於 MW 的影響。本小節中，側壁固定為  $\text{Si}_3\text{N}_4$  其介電常數為 7.5。我們針對每一組寫入電壓及不同鐵電參數去量測不同 AR 的  $I_{DS}$  -  $V_P$ ，如圖 3.1 所示，並量測其 MW。可以發現隨著 AR 從 1 減小到 0.2，MW 會逐漸增加，符合前人的研究結果。可以注意到隨著 AR 逐漸減小電晶體的開電流(on current)也會逐漸減小，原因在於鐵電電容的面積減小，使其在通道中感應的電荷量變少，因此電晶體的開電流會下降。

圖 3.1 不同面積比的  $I_{DS}$  -  $V_P$  圖，以  $P_r = 5 \mu\text{C}/\text{cm}^2$  及  $E_c = 1 \text{MV}/\text{cm}$  為例。越小的 AR 具有越大的 MW。

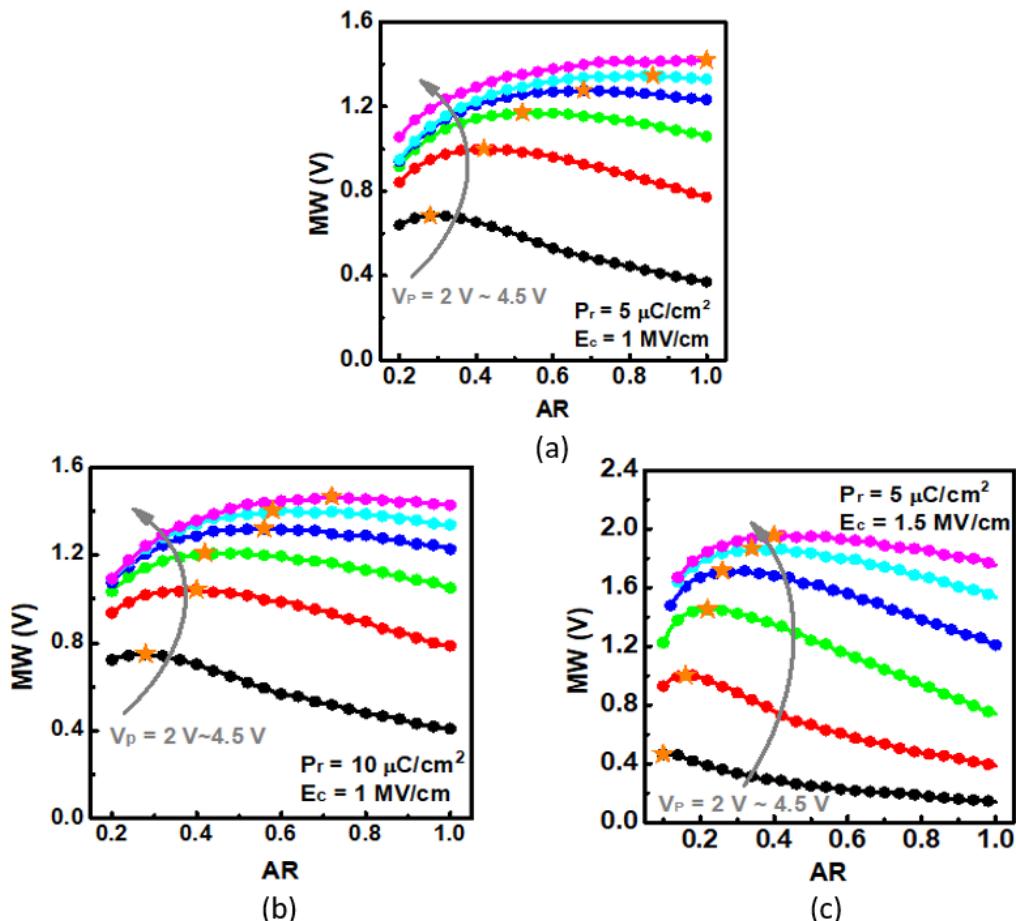

接著，我們針對不同的殘餘極化以及矯頑電場去做不同電壓下，MW 對 AR 的圖。如圖 3.2 所示，我們以橘色星星代表 MW\*。隨著電壓從 2V 逐漸增加至 4.5V 的過程中，AR\* 會隨著逐漸增加，代表了在越高的電壓條件下，藉由減小 AR 來增

加 MW 的優勢會逐漸變小。而在圖 3.2(a)中，可以看到在  $V_p=4.5$  V 下，某些鐵電參數的  $AR^*$  幾乎等於 1，相當於一般傳統鐵電電晶體的情況，意味著在某些鐵電參數及高電壓下，並不需要透過減小 AR 以增大 MW。而觀察圖 3.2 的(a)與(b)可以發現在高電壓下，隨著殘餘極化增加  $AR^*$  會減小，代表若今天殘餘極化過小的話減小 AR，會使總電荷變少導致 MW 減小。接著，觀察圖 3.2 的(a)與(c)發現隨著矯頑電場增加， $AR^*$  的位置明顯變小，因為越高的矯頑電場，意味著需要越高的寫入電壓去翻轉偶極，因此減小 AR 可以有效增加落在鐵電層上的電壓使偶極翻轉，進而增加 MW。

圖 3.2 面積比對記憶體視窗影響(不同鐵電參數及寫入電壓)(a)  $P_r=5\mu\text{C}/\text{cm}^2$  及  $E_c=1\text{MV}/\text{cm}$ ，(b)  $P_r=10\mu\text{C}/\text{cm}^2$  及  $E_c=1\text{MV}/\text{cm}$ ，(c)  $P_r=5\mu\text{C}/\text{cm}^2$  及  $E_c=1.5\text{MV}/\text{cm}$ ，橘色星星代表  $MW^*$  的位置。 $MW^*$  的位置跟鐵電參數及寫入電壓有關。

為了更容易看出在  $AR^*$  與  $MW^*$  與寫入電壓的關係，我們可以觀察圖 3.3 及圖 3.4 中， $AR^*$  及  $MW^*$  與  $V_P$  的關係，可以發現雖然不同殘餘極化對於  $AR^*$  具有影響，但最後  $MW^*$  跟殘餘極化的關係很小，符合我們在前面所講的  $MW$  的最大值在一級近似下只與矯頑電場有關。而在寫入電壓小於 2.5V 的情況下  $E_c = 1.2 \text{ MV/cm}$  反而擁有較  $E_c = 1.5 \text{ MV/cm}$  較大的  $MW$ ，原因為雖然減小  $AR$  可以增加鐵電層在寫入時的跨壓，但無法使其超過矯頑電場進而導致偶極無法翻轉。因此在低電壓操作下，具有大矯頑電場的鐵電電晶體  $MW$  反而比小矯頑電場的鐵電電晶體來得小。

圖 3.3 寫入電壓對最佳化面積比影響， $AR^*$  隨著寫入電壓增加會跟著增加，並且反比於矯頑電場及殘餘極化。

圖 3.4 寫入電壓對最佳化記憶體視窗影響， $MW^*$ 隨殘餘極化的影響較小。在寫入電壓小於 2.5 V 時， $E_c = 1.5 \text{ MV}/\text{cm}$  反而有較小的  $MW$ 。

### 3.2.2 AR\*及 MW\*在 2 V 及 4.5 V 寫入電壓下的等高

#### 線圖分析

由 3.2 節的結果，我們知道在 AR\* 與 MW\* 跟寫入電壓有強烈的關係，因此在本小節我們針對 16 種鐵電參數組合去探討在 2 V 及 4.5 V 中，AR\* 以及 MW\* 的等高線圖(殘餘極化分別為:  $5 \mu\text{C}/\text{cm}^2$ 、 $10 \mu\text{C}/\text{cm}^2$ 、 $15 \mu\text{C}/\text{cm}^2$ 、 $20 \mu\text{C}/\text{cm}^2$  以及 矯頑電場分別為  $0.8 \text{ MV}/\text{cm}$ 、 $1 \text{ MV}/\text{cm}$ 、 $1.2 \text{ MV}/\text{cm}$ 、 $1.5 \text{ MV}/\text{cm}$ )。前面探討的 MW\* 是針對某一組鐵電參數下在特定電壓的最大值，若我們考慮不同鐵電參數在特定寫入電壓下的 MW\*，從中得到的最大值即為在該電壓下所能達到的最大 MW，對應的鐵電參數組合以及 AR\* 即為該電壓下的最佳解。

在圖 3.5 及圖 3.6 中，我們先探討在 2 V 寫入電壓的情形，可以看到 AR\* 對於矯頑電場的依賴性比殘餘極化來得高，隨著矯頑電場的增加 AR\* 會跟著減少，AR\* 的等高線圖大致平行於殘餘極化的軸，意味著在該電壓下 AR\* 與殘餘極化關係並不大。圖 3.5 中的粉色星星，代表了具有最大 MW\* 的鐵電參數其殘餘極化為  $15 \mu\text{C}/\text{cm}^2$  以及矯頑電場為  $1.2 \text{ MV}/\text{cm}$ ，對應的 MW 為  $0.89 \text{ V}$ 。在該電壓下，由於鐵電層並非操作在飽和循環，因此越大的矯頑電場不一定會有越大的 MW。而越大的殘餘極化，因會有較大的去極化場會進一步減少 MW，綜合上述結果後，最佳的鐵電參數組合並非發生在最大的矯頑電場及殘餘極化的點，而從模擬結果我們能推論在低電壓的操作下，鐵電元件的矯頑電場及殘餘極化皆需要做最佳化。

圖 3.5 在 2 V 寫入電壓下，AR\*的等高線圖，粉色星星代表了最大的 MW\*對應之 AR\*，隨著矯頑電場增加 AR\*跟著減小。

圖 3.6 在 2 V 寫入電壓下，MW\*的等高線圖，藍色星星代表了最大的 MW\*。最大的 MW\*發生在  $P_r = 15 \mu\text{C}/\text{cm}^2$  以及  $E_c = 1.2 \text{ MV}/\text{cm}$ 。

為了定量解釋在 2 V 寫入電壓下，殘餘極化為  $15 \mu\text{C}/\text{cm}^2$ ，矯頑電場為 1.5 MV/cm 會具有較 1.2 MV/cm 還要小的 MW，我們可以分別觀察在寫入電壓移除後儲存於鐵電層的極化量。在圖 3.7 中，隨著 AR 變小極化量跟著上升，意味著減小 AR 確實可以增加寫在鐵電層上的電壓，進而增加極化量。而不論是在 LVT 或是 HVT，矯頑電場為 1.2 MV/cm 在寫入後皆具有較高的極化量，因此其會有較 1.5 MV/cm 較高的 MW。而從該圖也能發現在 HVT 的情況，極化量在某些 AR 並不會小於零，意味著寫入電壓並不足以翻轉鐵電層的偶極，而隨著 AR 減小矯頑電場為 1.2 MV/cm 的在 HVT 的極化量會小於零，意味著減小 AR 可以使鐵電層更容易翻轉偶極，進而增加 MW。

圖 3.7 在 2 V 寫入電壓下，考慮不同矯頑電場影響下寫入極化量隨 AR 變化，藍色虛線代表極化量為零。可以發現  $E_c = 1.2 \text{ MV}/\text{cm}$ ，在 LVT/HVT 有較大的極化量差異。

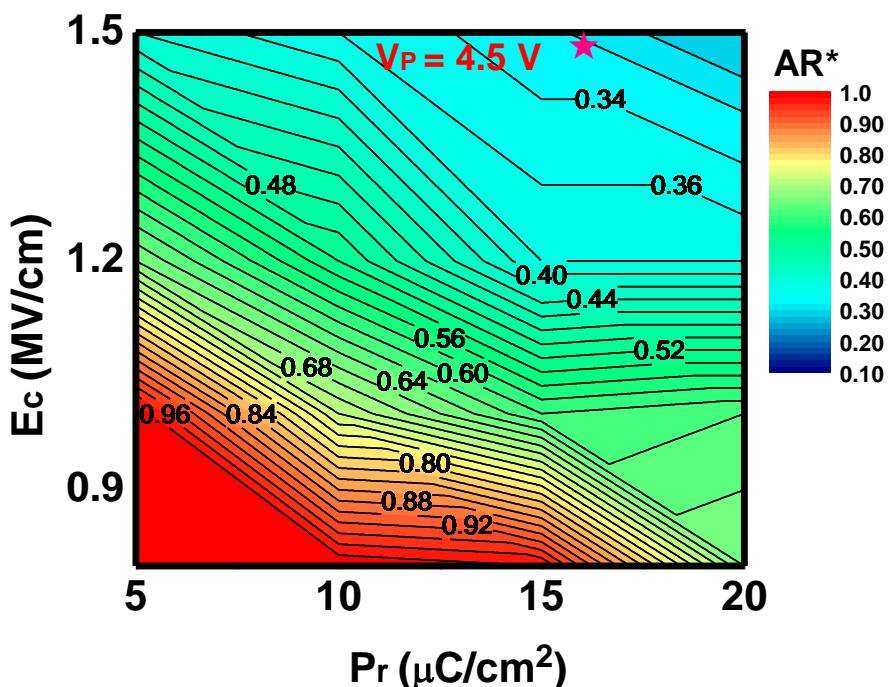

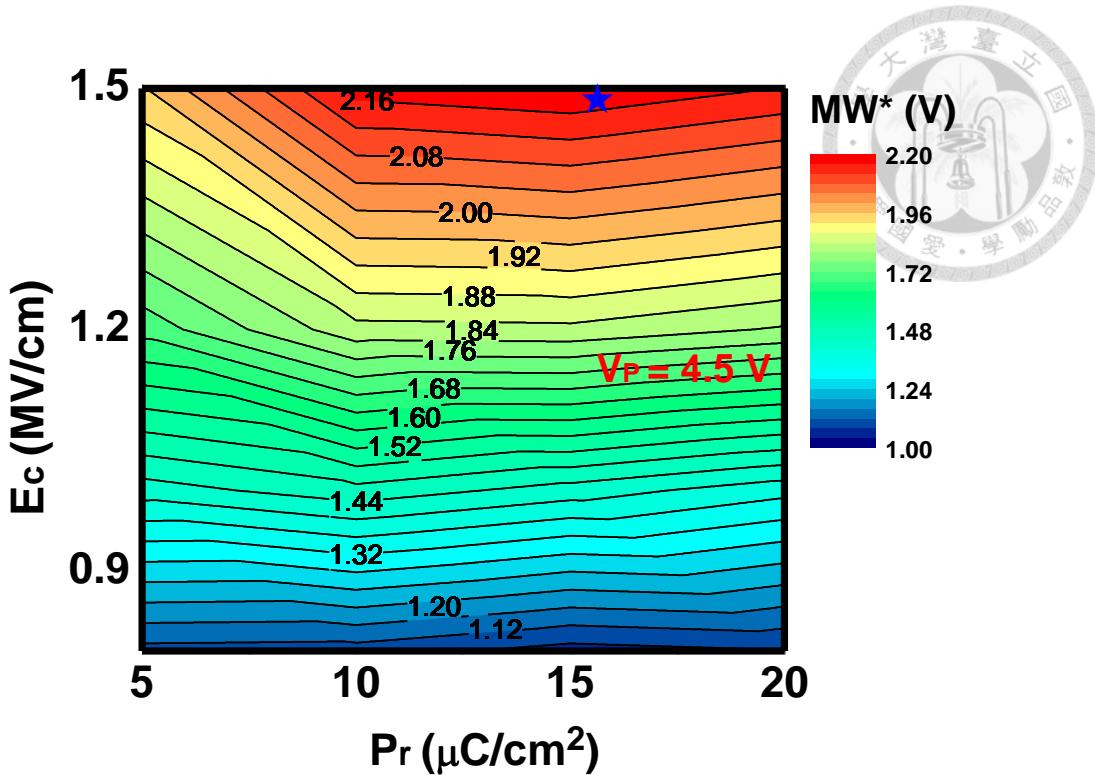

接著在圖 3.8 及圖 3.9 中，我們探討在 4.5 V 寫入電壓的情形，可以看到  $AR^*$  同樣隨著矯頑電場變大跟著變小，而在該電壓下  $AR^*$  對於殘餘極化的依賴性較 2 V 時來得高，因寫入電壓高使其操作在接近飽和循環，當寫入電壓移除後的極化量可以視為與殘餘極化成正比。在通道上所能產生的最大電荷量為定值，因此越高的殘餘極化所需的  $AR^*$  會越小。因為寫入電壓夠高因此 MW 會很接近其理論最大值，可以看到在圖 3.9 中 MW\* 大致只與矯頑電場有關，並且 MW 最大值發生在殘餘極化為  $15 \mu\text{C}/\text{cm}^2$  以及矯頑電場為  $1.5 \text{ MV}/\text{cm}$ ，對應的 MW 為  $2.2 \text{ V}$ 。與 2 V 寫入電壓不同的是在該電壓下越高的矯頑電場會具有最大的 MW 符合前人所提出的理論值，而由於去極化場的影響因此最大的 MW 對應的殘餘極化並不是越大越好，此點與 2 V 寫入電壓情形相同。

圖 3.8 在 4.5 V 寫入電壓下， $AR^*$  的等高線圖，粉色星星代表了最大的  $MW^*$  對應之  $AR^*$ 。在該圖的左下角  $AR^* = 1$ ，代表減小  $AR$  反而會減小  $MW$ 。

圖 3.9 在 4.5 V 寫入電壓下，MW\*的等高線圖，藍色星星代表了最大的 MW\*。最大的 MW\*發生在  $P_r = 15 \mu\text{C}/\text{cm}^2$  以及  $E_c = 1.5 \text{ MV}/\text{cm}$ 。

從圖 3.8 及圖 3.9 中，可以發現在殘餘極化為  $5 \mu\text{C}/\text{cm}^2$  以及矯頑電場為  $1\text{MV}/\text{cm}$  的點，其  $AR^* = 1$  代表了減小 AR 並無助於改善 MW。為了解釋此現象我們觀察在正負電壓寫完後的極化量以及在閘極總電荷隨著 AR 的關係，分別如圖 3.10 及圖 3.11 所示。在圖 3.10 可以發現隨著 AR 從 1 減小到 0.2 對於 LVT 及 HVT 兩個狀態的極化量皆是增加，但如果考慮總電荷的影響需要將其乘以鐵電層的面積，如圖 3.11 所示。可以看到總電荷隨著 AR 從 1 減小到 0.2，不論是在 LVT 或是 HVT 皆是減少。而在矯頑電場為  $1\text{MV}/\text{cm}$  較明顯是因為其值較小，因此在 4.5 V 的寫入電壓很容易就能超過其值進而翻轉偶極，因此減小 AR，反而會使通道感應出來的總電荷減少，進而減小 MW。

圖 3.10 在 4.5V 寫入電壓下，寫入極化量隨 AR 變化，藍色虛線代表極化量為零。

隨著 AR 減小在 LVT/HVT 的極化量差異增加。

圖 3.11 在 4.5V 寫入電壓下，寫入在閘極電荷量隨 AR 變化，藍色虛線代表極化量為零。隨著 AR 減小在 LVT/HVT 的總電荷差異減少。

### 3.3 AR\*及 MW\*於 2 V 寫入電壓下，與不同側壁的關係

#### 3.3.1 AR\*及 MW\*在 2 V 寫入電壓下，考慮不同側壁關係

從 3.2 節的討論，我們知道在 2 V 的寫入電壓下，最佳的 MW\*為 0.89 V，對應的鐵電參數分別是殘餘極化為  $15 \mu\text{C}/\text{cm}^2$  及矯頑電場為  $1.2 \text{ MV}/\text{cm}$ 。而 3.2 節中，我們的側壁是固定的，其材料為  $\text{Si}_3\text{N}_4$ ，對應的介電常數為 7.5。而前人的研究曾提過使用高介電係數側壁可以增加 MW [17]。而從 MW 的理論值知道殘餘極化對於 MW 的影響較小，因此本小節將固定殘餘極化為  $15 \mu\text{C}/\text{cm}^2$ ，並探討在 2 V 寫入電壓下，矯頑電場以及側壁對 MW\* 及 AR\* 的影響。

本小節將使用三種不同側壁，在 2 V 寫入電壓下探討 MW 隨 AR 的變化，分別為空氣側壁(Air Spacer)、 $\text{Si}_3\text{N}_4$  側壁(Nitride Spacer)、高介電係數側壁(High  $k$  Spacer)其介電常數分別為 1、7.5 以及 30。我們探討在殘餘極化為  $15 \mu\text{C}/\text{cm}^2$  下在考慮不同側壁下 MW 隨 AR 的變化如圖 3.12 所示。可以發現對於三種矯頑電場而言，AR\*與側壁的介電常數皆是正相關，原因為隨著側壁結構的介電常數上升，落在鐵電層上的跨壓會增加，因此不需要過小的 AR，即可使鐵電層的偶極產生翻轉，AR\*會較低介電係數的側壁來得大。AR 接近 1 時，在寫入時落在鐵電層上的跨壓較小，因此使用高介電係數的側壁可以有效的使 MW 增加，符合前人的研究。但隨著 AR 減小，空氣側壁結構反而擁有較大的 MW，推論是當鐵電層面積一直縮小後，總電荷會減小。而越高介電係數的側壁會分走越多的電荷，使得真正落在受閘極控制的通道內的電荷減少，此時會減小 MW。因此對於三種矯頑電場而言，MW\*皆可藉由將側壁結構的介電係數減小而進一步增加。

圖 3.12 2 V 寫入電壓下，不同面積比，對記憶體視窗影響(不同側壁材料)(a)  $P_r = 15\mu\text{C/cm}^2$  及  $E_c = 1\text{MV/cm}$ ，(b)  $P_r = 15\mu\text{C/cm}^2$  及  $E_c = 1.2\text{MV/cm}$ ，(c)  $P_r = 15\mu\text{C/cm}^2$  及  $E_c = 1.5\text{MV/cm}$ 。高介電係數側壁在 AR 較大的地方具有優勢，但小 AR 地方則不具有優勢。

### 3.3.2 AR\*及 MW\*在 2 V 寫入電壓下，考慮不同側壁的等高線圖分析

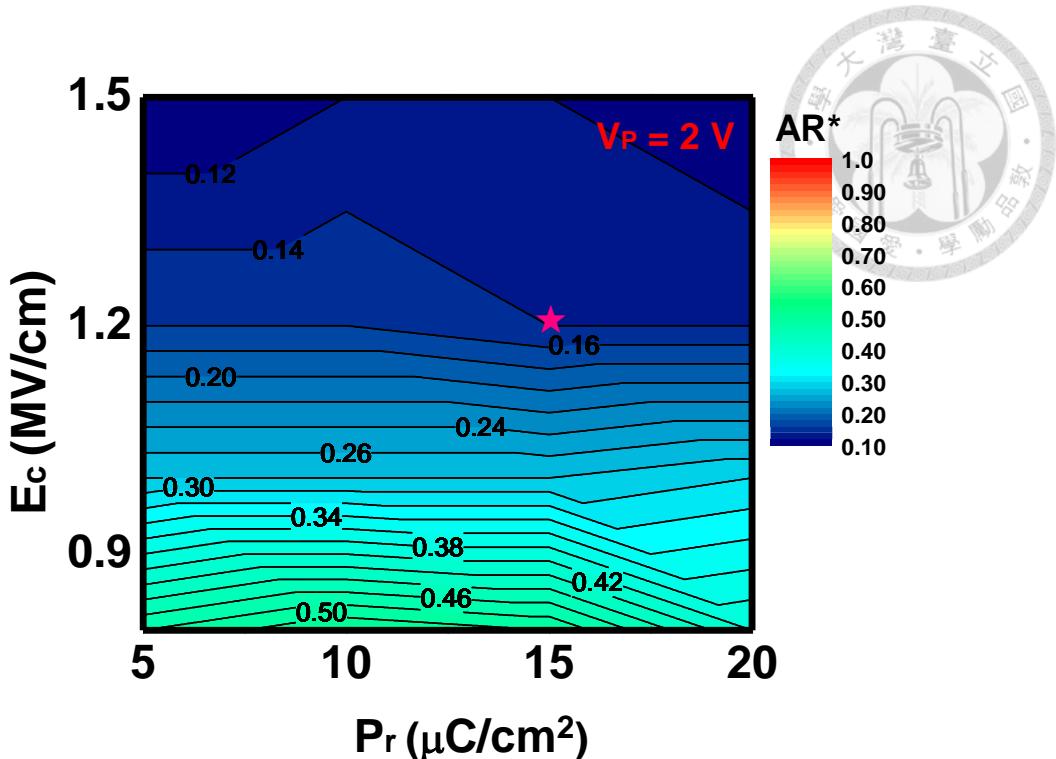

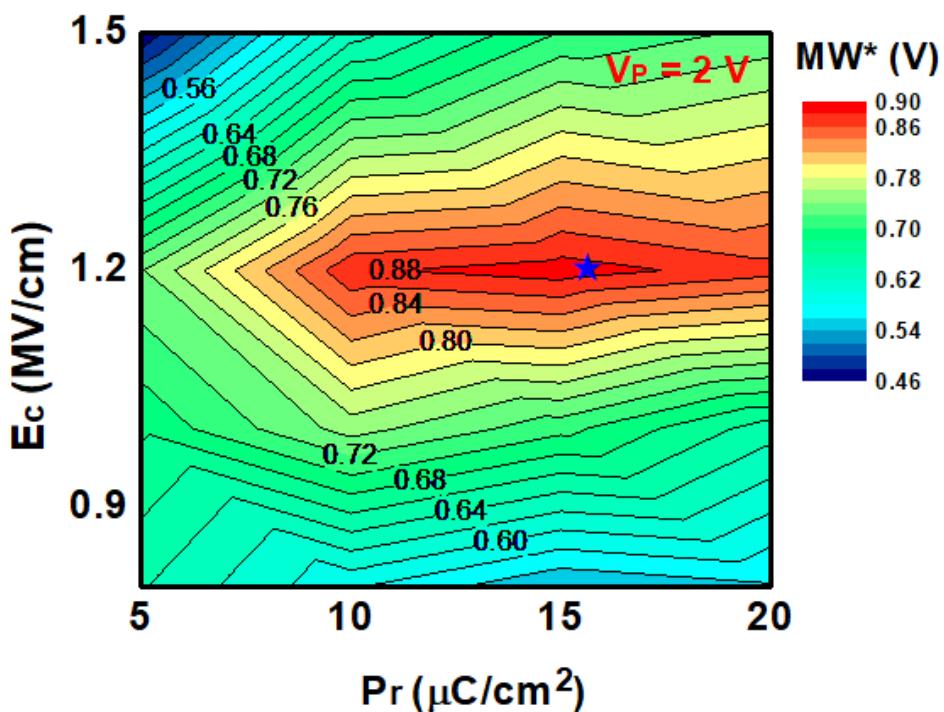

接著探討在 2 V 寫入電壓下，固定殘餘極化為  $15 \mu\text{C}/\text{cm}^2$ ，去探討側壁介電係數以及矯頑電場的等高線圖，如圖 3.13 及圖 3.14 所示。在圖 3.13 中可以發現在固定側壁下， $\text{AR}^*$  隨著矯頑電場增加而減小，與前一節結果相同。而固定矯頑電場下，隨著側壁的介電係數上升  $\text{AR}^*$  也跟著上升。而圖 3.14 中不論側壁的介電係數為何，最大的  $\text{MW}^*$  皆發生在矯頑電場為  $1.2 \text{ MV}/\text{cm}$  的地方，對於不同矯頑電場而言， $\text{MW}^*$  皆發生在側壁的介電係數為 1 的情形。從上述結果可以發現，若今天使用的結構不允許改變  $\text{AR}$ ，如傳統的 FeFET，此時使用高介電係數的側壁會有較大的  $\text{MW}$  與前人研究相符。而在本研究中因考慮了  $\text{AR}$  為可調的變數，因此隨著  $\text{AR}$  變小，空氣側壁的優勢會出現。

圖 3.13 在 2 V 寫入電壓下，考慮不同側壁介電係數的  $\text{AR}^*$  等高線圖，紅色星星代表了最大的  $\text{MW}^*$  對應之  $\text{AR}^*$ 。隨著側壁介電常數增加對應的  $\text{AR}^*$  跟著增加。

圖 3.14 在 2 V 寫入電壓下，中考慮不同側壁介電係數的 MW\* 等高線圖，藍色星星代表了最大的 MW\*。可以發現即使考慮了側壁的影響，擁有最大的 MW\* 之鐵電參數也是發生在  $P_r = 15\mu\text{C}/\text{cm}^2$  及  $E_c = 1.2 \text{ MV}/\text{cm}$ 。

### 3.3.3 在 2 V 寫入電壓下，不同側壁對電荷分布之分析

前一小節對於側壁如何影響 AR\* 及 MW\* 只做了定性說明，為了定量分析為何在不同 AR 下不同側壁對於 MW 會有不一樣的效果。本小節中，將針對擁有最大的 MW\* 的鐵電參數，其殘餘極化為  $15 \mu\text{C}/\text{cm}^2$  以及矯頑電場為  $1.2 \text{ MV}/\text{cm}$ ，接著分析不同側壁在寫完當下儲存在通道內的電荷分布。在前一節中由於側壁結構固定，因此可以直接分析在閘極的總電荷，而在本小節中，因側壁的介電常數不同，對於電荷分布會有較明顯的影響，因此觀察在通道的電荷分布會較洽當。

電荷分布為延著 FinFET 頂部的通道中線，如圖 3.15 所示，而觀察的時間點，分別為寫完正電壓的 ret+ 以及寫完負電壓的 ret-，在 ret+ 時由於寫入的為 LVT 態，因此我們觀察其電子濃度，而在 ret- 時由於是寫入 HVT 態，因此我們觀察其電洞濃度。在接下來的討論中，我們將分別觀察  $\text{AR} = 1$  以及  $\text{AR} = 0.1$  的電荷分布，並以電荷分布來解釋為何不同側壁在不同 AR 會有不一樣的優勢。

圖 3.15 從頂部看的 FinFET，我們觀察的電荷分布為沿著黑色虛線的通道。

我們先觀察在  $AR = 1$  時，沿著通道的電荷分布如圖 3.16 及圖 3.17 所示，可以發現不論是在 ret+ /ret- 時，高介電係數側壁在通道區域，均具有較空氣側壁來得高的電子/電洞濃度，代表在寫入階段時寫入了較高的電壓，進而增加了寫進去的極化量，因此高介電係數側壁在  $AR = 1$  相較於空氣側壁具有較高的 MW。另外因為分壓效應，高介電係數側壁落在電晶體上的電壓會較小，因此其臨界電壓在 ret+ 為 -0.16 V 比空氣側壁的 -0.22 V 要高一些。而在 ret- 高介電係數側壁則是具有較高的臨界電壓 0.3 V，空氣側壁則是 0.1 V。兩者相減後，使得在  $AR = 1$  的地方，高介電係數側壁有較高的 MW。

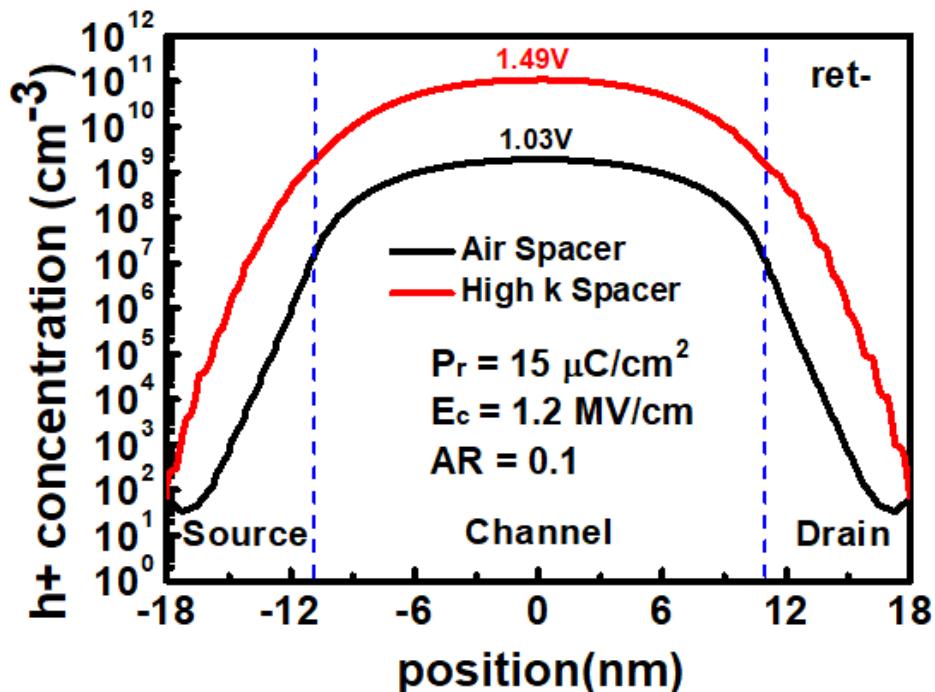

接著，我們觀察在  $AR = 0.1$  時，沿著通道的電荷分布，如圖 3.18 及圖 3.19 所示，可以發現在 ret- 時，高介電係數側壁在通道仍具有較高的電洞濃度，使其具有較高的臨界電壓 1.49 V，空氣側壁則是 1.03 V。但在 ret+ 時空氣側壁在通道則展現更高的電子濃度，其臨界電壓為 0.09 V，高介電係數側壁則是 0.79 V。因 MW 為兩個臨界電壓相減，因此可以推論對於  $AR = 0.1$  而言，在 ret+ 空氣側壁改善的幅度較高介電係數側壁高，使其具有較高的 MW。

圖 3.16 在 2V 寫入電壓下，於  $\text{ret}^+$ ， $\text{AR} = 1$  的電子分布圖。可以發現高介電系數側壁在通道具有較高的電子濃度，但因為分壓效應使其臨界電壓較空氣側壁高一點。

圖 3.17 在 2V 寫入電壓下，於  $\text{ret}^+$ ， $\text{AR} = 1$  的電洞分布圖。可以發現高介電系數側壁在通道具有較高的電洞濃度，並且有較高的臨界電壓。

圖 3.18 在 2V 寫入電壓下，於 ret+，AR = 0.1 的電子分布圖。可以發現空氣側壁在通道具有較高的電子濃度，並且有較低的臨界電壓。

圖 3.19 在 2V 寫入電壓下，於 ret-，AR = 0.1 的電洞分布圖。高介電係數具有較高的電洞濃度並有較高的臨界電壓。

### 3.4 等效電容模型圖

在本小節中，我們將建立鐵電電容與電晶體的等效電容模型[13][15]，並用此模型來說明在前面觀察到的 AR\* 以及 MW\* 跟鐵電參數、寫入電壓、側壁的關係。

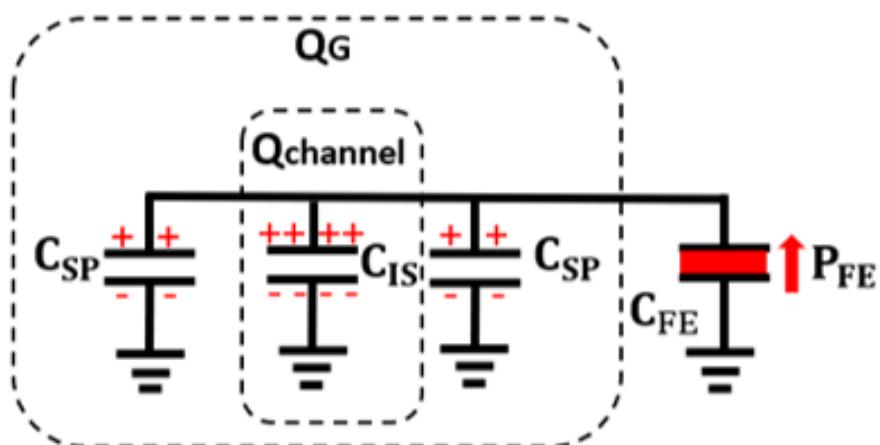

首先，我們先考慮在寫入階段時，該系統的等效模型如圖 3.20 所示，可以看到總共有四個電容分別為鐵電電容  $C_{FE}$ 、電晶體的氧化層與通道串聯電容  $C_{IS}$  以及源極/汲極的側壁電容  $C_{SP}$ 。我們可以將電晶體的等效電容視為  $C_{IS}$  與  $2C_{SP}$  並聯，並將其記為  $C_{MOS}$ 。在寫入時我們關注的是落在鐵電層上的跨壓  $V_{FE}$ ，其表達式由式(1)給出。可以發現該跨壓由兩項所組成，第一項為透過兩個電容分壓決定，越大的寫入電壓或是越小的  $C_{FE}/C_{MOS}$  皆可以增加落在鐵電層上的跨壓，因此在較低的寫入電壓透過減小兩者的面積比，可以使 MW 增加。另一項則是由鐵電的偶極所產生的反向電壓，注意到第二項在寫入電壓移除後即是去極化場其中  $A_{FE}$  代表了鐵電層的面積。當寫入電壓移除後，該項會導致偶極產生翻轉，因此  $P_{FE}$  並非越大越好，而是會有一個中間最佳的值，符合 3.2 節所觀察到的。

而在寫入電壓移除後即保存階段(Retention)，我們可以觀察儲存在通道內的電荷來判斷寫的好壞，其等效模型圖如圖 3.21 所示。由式(2)可以知道由於側壁導致的寄生電容使得落在通道內的電荷為在閘極的總電荷( $Q_G = P_{FE}A_{FE}$ )減去側壁的電荷( $2C_{SP}V_{FE}$ )，第一項為鐵電層所產生的總電荷，隨著鐵電面積減小極化量會增加，但若極化量增加的量不及面積減小的量，會導致總電荷減少進而減小 MW。而第二項則是隨著 AR 變小，以及側壁的介電係數上升會越明顯，因此時落在鐵電層上的跨壓增加，以及第一項的總電荷會跟著減小使其變為不可忽略。因此從該式可以得到 MW 會隨著面積減小先增加後減少，並且在  $AR \ll 1$  時空氣側壁會具有較大的 MW，符合我們在 3.2 節所觀察的結果。

$$V_{FE} = \frac{1}{1 + C_{FE}/C_{MOS}} V_P - \frac{P_{FE}A_{FE}}{C_{MOS} + C_{FE}} \quad (1)$$

$$Q_{\text{channel}} = Q_G - 2C_{SP}V_{FE} = P_{FE}A_{FE} - 2C_{SP}V_{FE} \quad (2)$$

## Write

圖 3.20 寫入階段時的等效電容模型， $C_{MOS}$  代表了電晶體的等效電容包含了側壁寄生電容  $C_{SP}$  以及電晶體氧化層與通道電容串聯之  $C_{IS}$ 。

## Retention

圖 3.21 保存階段時的等效電容模型， $Q_G$  為全部感應在閘極的電荷； $Q_{channel}$  為受閘極控制的通道電荷。越高介電係數的側壁會使得  $Q_{channel}$  減小。

接著，我們將藉由上面的兩個公式來說明在 3.2、3.3 節所觀察到的  $AR^*$  與各參數的關係如表 3.1 所示。由式(1)與式(2)知減小  $AR$  雖然有助於改善落在鐵電層上的跨壓，但有可能會減少閘極的電荷，因此存在一個  $AR^*$  使得在該條件下，能實現最大的 MW。而該如何決定這個  $AR^*$ ，可以從基本的鐵電操作原理來思考，鐵電層的矯頑電壓代表了翻轉偶極所需要的最小電壓因此當今天落在鐵電層上的電壓超過其矯頑電壓後，再增加電壓對於產生偶極的能力會減小很多，若此時繼續減小  $AR$ ，則會使得總電荷減少，因此我們可以將  $AR^*$  發生的位置近似為當在寫入階段時，落在鐵電層上的跨壓剛好等於矯頑電壓時的  $AR$ 。

首先，我們先解釋為何隨著寫入電壓升高  $AR^*$  會隨之上升，當今天寫入電壓增加時，意味著  $C_{FE}/C_{MOS}$  並不需要太小，即可使落在鐵電層上的跨壓超過矯頑電壓，因此當寫入電壓上升時  $AR^*$  會跟著增加。

而當殘餘極化上升時，可以考慮當電晶體通道達到強反轉時，其電子濃度是固定的，此時落在閘極的總電荷可以近似為與  $P_{rAFE}$  成正比，在通道電荷濃度固定的情況下，越大的殘餘極化對應的  $AR^*$  會越小。

而當矯頑電場上升時，在固定電壓下，要使落在鐵電層上的跨壓超過矯頑電壓會相對困難，因此減小  $C_{FE}/C_{MOS}$  可以有效地增加落在鐵電層上的跨壓使 MW 增加，因此其對應的  $AR^*$  會隨之減小。

而當側壁的介電係數上升時， $C_{FE}/C_{MOS}$  會減小，使得落在鐵電層上的跨壓增加因此不需要過小的  $AR$ ，即可讓其超過矯頑電壓，因此  $AR^*$  會跟著上升。但從式(2)知道越高介電係數的側壁會讓受閘極控制的電荷減小。當  $AR = 1$  時由於總電荷較多，以及  $V_{FE}$  較小因此該效應不明顯；而當  $AR$  減小至 0.1 時總電荷會減小，以及  $V_{FE}$  會增加，因此高介電係數側壁的在通道的電荷就會比空氣側壁來得少，使對應的 MW\* 減小。因此在  $AR = 0.1$  時，空氣側壁有較大的 MW。

| Parameter         | AR*          |

|-------------------|--------------|

| $V_P \uparrow$    | $\uparrow$   |

| $P_r \uparrow$    | $\downarrow$ |

| $E_c \uparrow$    | $\downarrow$ |

| $C_{SP} \uparrow$ | $\uparrow$   |

表 3.1 最佳化面積比與寫入電壓、鐵電參數及側壁之關係。可以發現 AR\*與寫入電壓及側壁介電係數成正比，並與殘餘極化及矯頑電場成反比。

## 3.5 在 2 V 寫入電壓下，不同 AR 及側壁對於寫入干擾之分析

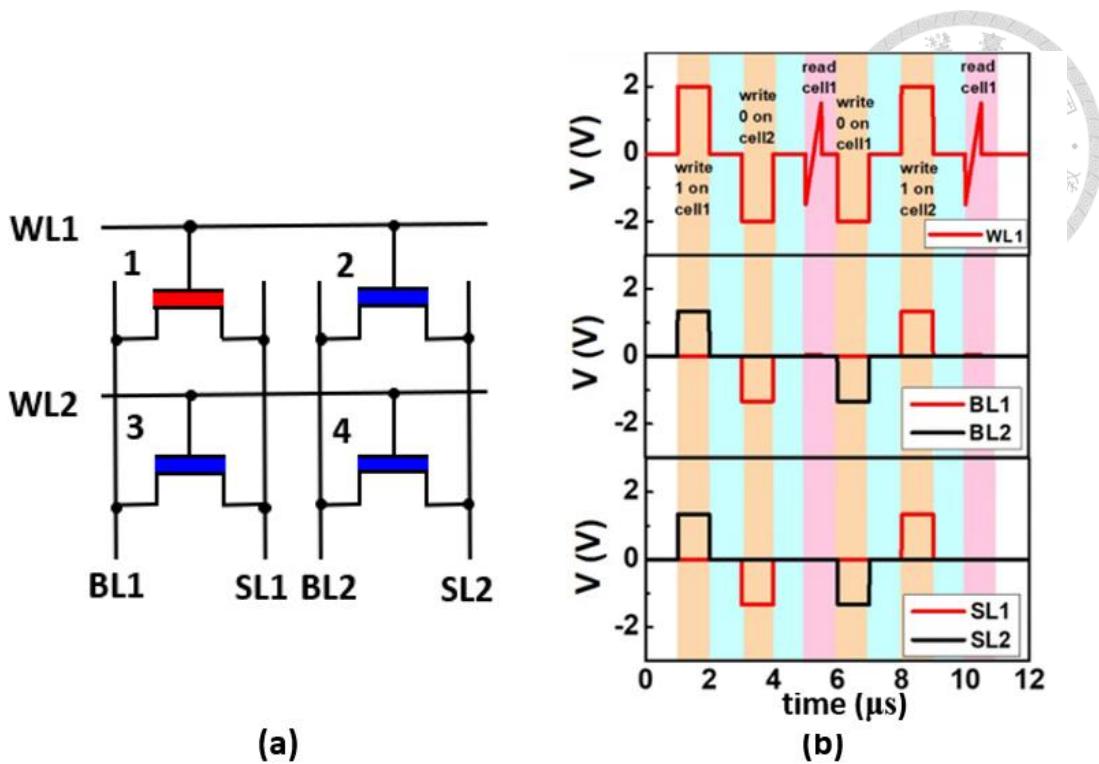

從 3.2 節跟 3.3 節的分析，我們知道在 2 V 的寫入電壓下，殘餘極化為  $15 \mu\text{C}/\text{cm}^2$  以及 矯頑電場為  $1.2 \text{ MV}/\text{cm}$  的鐵電元件具有最佳的 MW\*。本小節將使用該組鐵電參數來分析在  $2 \times 2$  1FeFET 陣列上，不同 AR 以及側壁材料對於寫入干擾(Write disturbance)的影響，並與未受干擾的 MW 做比較。

在圖 3.22 (a)的 1FeFET 的陣列中，同一列的鄰近單元因共用 WL 的關係，因此在寫 2 號單元時，1 號單元的資料就會被改寫，因此需要使用能減少干擾的寫入法，過去有許多人提出使用  $V_p/2$  或  $V_p/3$  的寫入法[18]。在本節中我們將使用  $V_p/3$  的寫入法來減小寫入干擾的影響。每一個操作對應的電壓，如表 3.2 所示。此寫入法確保了在同一列或行的未選取單元，最多只會受到寫入電壓的三分之一的干擾，因此可以避免過多的偶極翻轉，而造成 0 與 1 無法區分。為了分析寫入干擾的影響，我們將使用圖 3.22 (b)的波型來量測受寫入干擾後的 MW。我們先將 1 號單元進行寫 1 的操作，接著將 2 號單元進行寫 0 的操作，此時 1 號單元原本的 1 會受到干擾。接著使用三角波量測受干擾的 1 號單元的 LVT，之後用同樣的方法量測受干擾的 1 號單元的 HVT，將兩者相減即是受干擾的 MW。

圖 3.22 (a)1FeFET 陣列架構, 1 號為受干擾的單元(b)用以量測寫入干擾的波型圖。

先對 1 號單元寫 1 後再寫入 0 在鄰近的單元，即可量測受干擾後的臨界電壓。

| Operation | Selected WL                    | Selected BL | Selected SL | Unselected WL | Unselected BL/SL |

|-----------|--------------------------------|-------------|-------------|---------------|------------------|

| Write 0   | $-V_p$                         | 0 V         | 0 V         | $V_p/3$       | $-2V_p/3$        |

| Write 1   | $V_p$                          | 0 V         | 0 V         | $-V_p/3$      | $2V_p/3$         |

| Read      | $-V_{read}$<br>$\sim V_{read}$ | 0.05 V      | 0 V         | 0 V           | 0 V              |

表 3.2 1FeFET 陣列的寫入、讀取電壓表。對於未受選取的單元只會受到三分之一的干擾電壓。

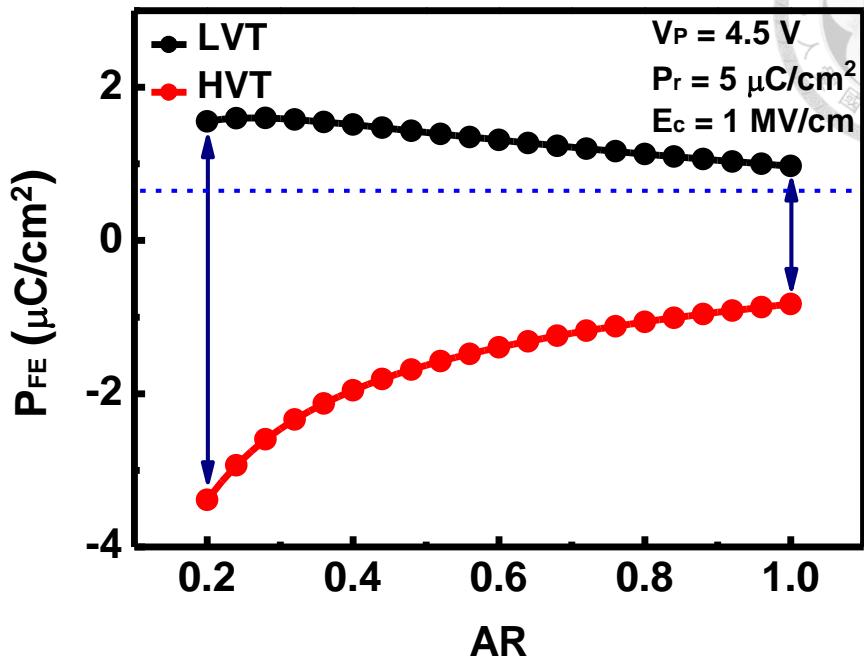

我們先觀察不同 AR 受到寫入干擾的  $I_{DS}$ - $V_p$  圖，如圖 3.23 所示，可以發現  $AR = 1$  受干擾程度較  $AR = 0.1$  要來得明顯。從直覺上來看  $AR = 0.1$  會受到較大的干擾電壓，但最後受干擾的 MW 却與原先相差不大，原因在於  $AR = 0.1$  在寫入時翻轉的偶極較多，因此即使受到較大的干擾電壓仍具有相對多的偶極，對於 MW 的

影響相對較小;相反的  $AR = 1$  本身在寫入時翻轉的偶極就較少，因此儘管干擾電壓較小，剩下的偶極會過少，使其使其無法產生足夠的 MW。

圖 3.23 受寫入干擾的  $ID_s$ - $V_p$  圖 (a)  $AR = 1$ ，(b)  $AR = 0.1$ 。可以發現  $AR = 0.1$  受干擾的程度較低。

接著我們來探討對於不同 AR 以及側壁材料，在受到寫入干擾後的 MW 與未受到寫入干擾前的比較圖，在圖 3.24 中黑色代表了空氣側壁，而紅色代表了高介電係數側壁，實心跟空心分別代表了未受干擾前的 MW 及受寫入干擾後的 MW。可以發現在受到寫入干擾後， $AR^*$ 大致與受寫入干擾前的位置相同，但  $MW^*$ 會減小，隨著 AR 減小受干擾的程度也會跟著下降，如圖 3.25 所示。 $\Delta MW/MW$ 定義為未受寫入干擾的 MW 減去受寫入干擾的 MW 最後除以未受寫入干擾的 MW，而從圖 3.25 發現使用高介電係數側壁相較於空氣側壁有助於減小受干擾的百分比。

在高介電係數側壁的  $AR^*$ 可以達到僅有 7.4%的 MW 改變百分比，其對應的  $MW^*$ 為 0.77 V;而在空氣側壁的  $AR^*$ 雖然仍有 19%的 MW 改變量，但其  $MW^*$ 仍有 0.74 V。隨著高介電係數側壁 AR 減小到  $AR^*$ 以下後，受干擾的百分比會上升，原因為未受干擾的 MW 跟著下降，導致改變百分比會跟著上升，從上述結果我們可以推論  $AR^*$ 不僅具有最大的 MW，它還具有最佳的抗寫入干擾能力。

圖 3.24 在 2V 寫入電壓下，不同面積比及側壁對受干擾記憶體視窗影響。隨著 AR 減小或是使用高介電係數側壁，MW 受干擾較小。

圖 3.25 考慮空氣側壁及高介電係數側壁受干擾的 MW 變更百分比，AR 減小有助於減少 MW 的變更百分比。

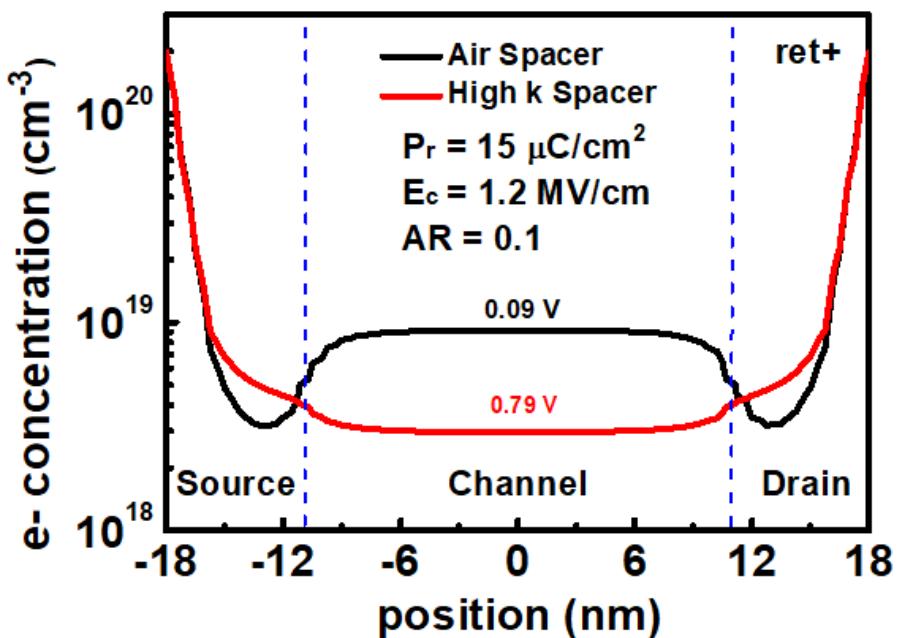

我們可以觀察在寫完當下的電荷分布來解釋上面的現象，從上述的結果可以總結為具有較小  $C_{FE}/C_{MOS}$  者會具有較佳的抗寫入干擾能力。因此我們可以固定側壁材料為空氣，探討 AR 這個因子對於寫入干擾的影響即可。圖 3.26 及圖 3.27 中可以看到  $AR = 0.1$ ，因受到較大的干擾電壓，因此其電子或電洞濃度的改變相較  $AR = 1$  還要多。在 ret+ 時， $AR = 0.1$  在受到寫入干擾後其臨界電壓從 0.09 V 增加至 0.29 V，而  $AR = 1$  則是從 -0.22 V 增加至 -0.05 V， $AR = 0.1$  改變得較  $AR = 1$  來得多。但在 ret- 時， $AR = 1$  在受到干擾後其臨界電壓從 0.1 V 減小至 0.03 V，而  $AR = 0.1$  則是從 1.03 V 減小至 0.99 V。原本  $AR = 0.1$  在未受干擾前即具有較大的 MW，因此儘管在受干擾後， $AR = 0.1$  在 ret+ 時改變的比較多，對於 MW 的影響仍相對  $AR = 1$  較小，從而導致  $AR = 0.1$  有比  $AR = 1$  較優異的抗寫入干擾能力。

從以上的結果可以知道較小  $C_{FE}/C_{MOS}$  者，會具有較佳的抗寫入干擾能力。其原理為在寫入時有較大的跨壓，因此本身的偶極較多即使受到的干擾電壓較大，但其偶極的改變量仍相對於  $C_{FE}/C_{MOS}$  較大者來得小，因此減小 AR 不僅有提升 MW 的好處，更能提升在陣列上的抗寫入干擾能力。

圖 3.26 使用空氣側壁比較  $\text{AR} = 0.1$  及  $\text{AR} = 1$  在受寫入干擾前後， $\text{ret+}$ 的電子分布。 $\text{AR} = 0.1$  受到較大的干擾電壓，因此在受干擾後電子濃度小於  $\text{AR} = 1$ ，且有較高的臨界電壓。

圖 3.27 使用空氣側壁比較  $\text{AR} = 0.1$  及  $\text{AR} = 1$  在受寫入干擾前後， $\text{ret-}$ 的電洞分布。 $\text{AR} = 0.1$  受到較大的干擾電壓，但在受干擾前有較高的電洞濃度，在受干擾後電洞濃度仍比  $\text{AR} = 1$  來得高，且具有較高的臨界電壓。

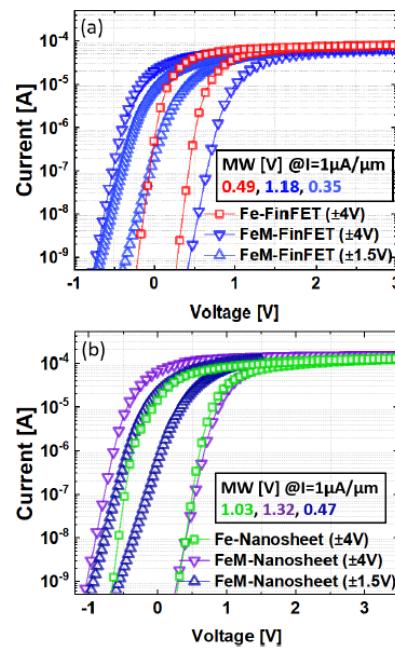

最後，我們來比較使用不同 AR 以及側壁結構對於未受干擾 MW 以及受干擾 MW 的提升。我們將 AR = 1 且使用  $\text{Si}_3\text{N}_4$  側壁的鐵電電晶體當作基準線，其 MW 為 0.36 V。圖 3.28 中顯示了相較於基準線，我們將 AR 減小至 0.24，並使用高介電係數側壁相較於基準線，MW 提升至 0.83 V 有 131% 的改善。若進一步將側壁材料換成空氣並將 AR 減小至 0.08，可以再將 MW 提升至 0.94 V 有 161% 的改善。

上述所提的是針對未受干擾的 MW，而在圖 3.29 中，則是比較在受到干擾後的 MW。可以看到基準線的 MW 僅有 0.13 V，若我們使用高介電係數側壁，並將 AR 減小至 0.24，可以將 MW 提升至 0.77 V 有 473% 的改善，但若我們使用空氣側壁，並將 AR 減小至 0.08，此時 MW 為 0.74 V 有 450% 的改善。雖然高介電係數側壁有較好的抵禦抗寫入干擾的能力，但其會增加電晶體的等效電容，對於速度上會有所影響。而空氣側壁雖在受寫入干擾後的 MW 會略小於高介電係數側壁，但可以使操作速度提升。因此藉由減小 AR 並使用空氣側壁，不僅能使在未受干擾的 MW 達到 0.94 V，並可以保證在受干擾後仍具有 0.74 V 的 MW。而注意到對於空氣側壁而言，未受寫入干擾前的 MW 對應的 AR\* 為 0.1，而受寫入干擾後的 MW 對應的 AR\* 為 0.08，因此我們會選擇將鐵電的 AR 設計為 0.08，以保證受寫入干擾後有最大的 MW。

最後，我們在考慮受寫入干擾後的 MW 後得出的最佳鐵電參數解為殘餘極化為  $15 \mu\text{C}/\text{cm}^2$ 、矯頑電場為  $1.2 \text{ MV}/\text{cm}$ 、 $\text{AR} = 0.08$ 、空氣側壁其對應受干擾的 MW 為 0.74 V 相對於基準線的鐵電電晶體改善了 450%。

圖 3.28 不同側壁之最佳化記憶體視窗與基準線比較圖(未受寫入干擾)。空氣側壁的 MW\* 相較於基準線改善了 161%

圖 3.29 不同側壁之最佳化記憶體視窗與基準線比較圖(受寫入干擾)。空氣側壁的 MW\* 相較於基準線改善了 450%

## 第四章 總結

首先，我們探討鐵電電晶體在各寫入電壓下不同鐵電參數的  $MW^*$ ，可以得到  $AR^*$  正比於寫入電壓並反比於矯頑電場及殘餘極化。而在低電壓(2 V)的條件下具有最大的  $MW^*$  的鐵電參數為：殘餘極化為  $15 \mu\text{C}/\text{cm}^2$ 、矯頑電場為  $1.2 \text{ MV}/\text{cm}$ 。對應的  $AR^*$  及  $MW^*$  分別為 0.14 及 0.89 V。

接著，我們固定鐵電電晶體的殘餘極化為  $15 \mu\text{C}/\text{cm}^2$ 、矯頑電場為  $1.2 \text{ MV}/\text{cm}$ ，探討不同側壁材料對  $MW^*$  的影響。在本研究中觀察到，在  $AR$  接近 1 的地方高介電側係數壁材料有較大的  $MW$ ，符合前人的研究。但隨著  $AR$  減小空氣側壁的優勢顯現出來，空氣側壁具有更大的  $MW$ ，其  $AR^*$  及  $MW^*$  分別為 0.1 及 0.95 V。

為了解釋模擬觀察到的結果，我們使用等效電容模型以及電荷守恆定律來解釋前面所觀測到的現象，並將  $AR^*$  的位置近似為當寫入的電場大約為矯頑電場時的值，用以解釋前面所觀察到的現象。

最後，我們將使用鐵電電晶體的殘餘極化為  $15 \mu\text{C}/\text{cm}^2$ 、矯頑電場為  $1.2 \text{ MV}/\text{cm}$  探討在陣列的表現。我們以  $2 \times 2$  的陣列作為研究對象，來探討不同  $AR$  及側壁對於寫入干擾的影響。從而發現，減小  $AR$  不僅具有提升  $MW$  的好處，還能減小寫入干擾的影響。雖然在受寫入干擾後的  $MW$  高介電係數側壁有更佳的  $MW$ ，但考慮到總電容增加會影響速度，因此最終折衷的解為使用空氣側壁，並藉由減小  $AR$  來改善寫入干擾的影響。最後我們將  $\text{Si}_3\text{N}_4$  側壁且  $AR = 1$  的鐵電電晶體做為我們比較的基準線。在考慮了寫入干擾後的記憶體視窗，使用空氣側壁的鐵電電晶體其最佳化記憶體視窗為 0.74 V 相較於基準線的最佳化記憶體視窗為 0.13 V，記憶體視窗有 450% 的改善。

本篇研究中給出  $AR^*$  與各參數及寫入電壓關係，並得到在不同  $AR$  下對於側壁介電常數的選擇是不同的。最後探討應用於 2 V 低功耗的鐵電電晶體陣列，發現減小  $AR$  有助於改善寫入干擾的影響，對於低功耗鐵電電晶體應用有很大的優勢。

# 參考文獻

- [1] M. Lapedus, "A new memory contender?" 2018. [Online]. Available: <https://semiengineering.com/a-new-memory-contender/>

- [2] V. Milo, G. Malavena, C. M. Compagnoni and D. Ielmini, "Memristive and CMOS devices for neuromorphic computing", *Materials*, vol. 13, no. 1, pp. 166, Jan. 2020.

- [3] T. Mikolajick et al., "Next generation ferroelectric materials for semiconductor process integration and their applications", *J. Appl. Phys.*, vol. 129, no. 10, Mar. 2021.

- [4] J. Müller et al., "Ferroelectric hafnium oxide based materials and devices: Assessment of current status and future prospects", *ECS J. of Solid State Sci. and Tech.*, vol. 4, no. 5, pp. N30-N35, 2015.

- [5] T. Mikolajick, U. Schroeder and S. Slesazeck, "The past the present and the future of ferroelectric memories", *IEEE Trans. Electron Devices*, vol. 67, no. 4, pp. 1434-1443, 2020.

- [6] J. Müller et al., " Ferroelectricity in simple binary ZrO<sub>2</sub> and HfO<sub>2</sub> ", *Nano Lett.*, vol. 12, no. 8, pp. 4318-4323, 2012.

- [7] N. Gong and T.-P. Ma, " Why is FE-HfO<sub>2</sub> more suitable than PZT or SBT for scaled nonvolatile 1-T memory cell? A retention perspective ", *IEEE Electron Device Lett.*, vol. 37, no. 9, pp. 1123-1126, Sep. 2016.

- [8] M. Trentzsch et al., "A 28nm HKMG super low power embedded NVM technology based on ferroelectric FETs", *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, 2016..

- [9] K. Toprasertpong, M. Takenaka and S. Takagi, "Memory window in ferroelectric field-effect transistors: Analytical approach", *IEEE Trans. Electron Devices*, vol. 69, no. 12, pp. 7113-7119, Dec. 2022.

- [10] S. Deng, Z. Liu, X. Li, T. P. Ma and K. Ni, "Guidelines for ferroelectric FET reliability optimization: Charge matching", *IEEE Electron Device Lett.*, vol. 41, no. 9, pp. 1348-1351, Sep. 2020.

- [11] G. Choe and S. Yu, "Multigate ferroelectric transistor design toward 3-nm technology node", *IEEE Trans. Electron Devices*, vol. 68, no. 11, pp. 5908-5911, Nov. 2021.

- [12] D. Lehninger, H. Mahne, T. Ali, R. Hoffmann, R. Olivo, M. Lederer, et al., "Integration of BEoL compatible 1T1C FeFET memory into an established CMOS technology", *Proc. IEEE Int. Memory Workshop (IMW)*, pp. 1-4, May 2022.

- [13] D. Lehninger, R. Hoffmann, A. Sunbul, H. Mähne, T. Kämpfe, K. Bernert, et al., "Ferroelectric FETs with separated capacitor in the back-end-of-line: Role of the capacitance ratio", *IEEE Electron Device Lett.*, vol. 43, no. 11, pp. 1866-1869, Nov. 2022.

- [14] M.-H. Yan et al., "BEOL-compatible multiple metal-ferroelectric-metal (m-MFM) FETs designed for low voltage (2.5 V) high density and excellent reliability", *IEDM Tech. Dig.*, pp. 4.6.1-4.6.4, Dec. 2020.

- [15] K. Ni et al., "SoC logic compatible multi-bit FeMFET weight cell for neuromorphic applications", *IEDM Tech. Dig.*, pp. 3.2.1-13.2.4, Dec. 2018.

- [16] F. -C. Wu, W. -X. You and P. Su, "Simulation and Design of Ultra-Thin-Body FeFET NVMs Considering Minor Loop Operation," *2020 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA)*, pp. 78-79, Aug. 2020.

- [17] P. R. Genssler, V. M. van Santen, J. Henkel and H. Amrouch, "On the reliability of FeFET on-chip memory", *IEEE Trans. Comput.*, vol. 71, no. 4, pp. 947-958, Mar. 2022.

- [18] B.-K. Huang, W.-X. You and P. Su, "Comparison of 2-T FeFET nonvolatile memory cells: Gate select vs. drain select", *Proc. Int. Symp. VLSI Technol. Syst. Appl. (VLSI-TSA)*, pp. 1-2, Apr. 2021.

- [19] Z. Fu, C. Chen, J. Luo, Q. Huang and R. Huang, "Device modeling and application simulation of ferroelectric-FETS with dynamic multi-domain behavior", *Proc. China Semiconductor Technol. Int. Conf. (CSTIC)*, pp. 1-4, Jun. 2020.

- [20] K. Ni, M. Jerry, J. A. Smith and S. Datta, "A circuit compatible accurate compact model for ferroelectric-FETs", *Proc. IEEE Symp. VLSI Technol.*, pp. 131-132, Jun. 2018.

- [21] "Sentaurus™ Device User Guide"

- [22] "Int. Roadmap for Device and Systems (IRDS)", 2018."

- [23] J. Kim, J. Mohan, S. R. Summerfelt and J. Kim, " Ferroelectric  $\text{Hf}_{0.5}\text{Zr}_{0.5}\text{O}_2$  thin films: A review of recent advances ", *JOM*, vol. 71, pp. 246-255, Jan. 2019.