國立臺灣大學電機資訊學院電信工程學研究所

碩士論文

Graduate Institute of Communication Engineering

College of Electrical Engineering and Computer Science

National Taiwan University

Master's Thesis

150 GHz 低雜訊放大器與 300 GHz 次諧波混頻器之設計

Design of a 150 GHz Low-Noise Amplifier and 300 GHz Sub-Harmonic Mixers

王裕翔

Yu-Hsiang Wang

指導教授：鄭宇翔 博士

Advisor: Yu-Hsiang Cheng, Ph.D.

中華民國 114 年 1 月

January, 2025

國立臺灣大學碩士學位論文

口試委員會審定書

MASTER'S THESIS ACCEPTANCE CERTIFICATE

NATIONAL TAIWAN UNIVERSITY

150 GHz 低雜訊放大器與

300 GHz 次諧波混頻器之設計

Design of a 150 GHz Low-Noise Amplifier and

300 GHz Sub-Harmonic Mixers

本論文係王裕翔（學號 R10942118）在國立臺灣大學電信工程學研究所完成之碩士學位論文，於民國 114 年 1 月 14 日承下列考試委員審查通過及口試及格，特此證明。

The undersigned, appointed by the Graduate Institute of Communication Engineering on 14, January, 2025 have examined a Master's Thesis entitled above presented by Yu-Hsiang Wang (student ID:R10942118) candidate and hereby certify that it is worthy of acceptance.

口試委員 Oral examination committee:

鄭宇翔 翁政翰 林大坤

(指導教授 Advisor)

系（所、學位學程）主管 Director: 魏宏宇

## 誌謝

回顧碩士生涯，最想感謝的是指導教授鄭宇翔老師，很感謝老師總是不辭辛勞又苦口婆心的帶領著我們，無論是研究上或是生活中，都給予了非常多寶貴的意見，也很常帶我們去校外參訪很多新奇的知識拓展視野。此外，要感謝口試委員蔡政翰老師及林坤佑老師，兩位老師在口試時提供了許多中肯而精闢的建議，幫助我將論文內容修正得更加完整與扎實。謝謝老師們的用心與指導，讓這段研究歷程變得充實且有意義。

同時很感謝實驗室的大家，一起度過了風風雨雨：楚軒、兆發、李勁、金鴻、兆宏、岳融、盛鈞、尹涵、祈安、金輝、柏任、奕綺及學弟們，謝謝你們一路上的陪伴與相挺，讓這段碩士生活更加有趣，也更值得回憶。再來特別感謝雲杉學長，不論是量測過程中提供協助，還是研究上的經驗分享和建議，都幫助了我非常大。最後，最深的感謝獻給我的家人。謝謝你們一直以來的支持與陪伴，在我低潮或焦慮時，始終在背後默默鼓勵我，給我力量走到現在。有你們的理解與包容，是我能安心追求研究與完成學業的最大後盾。

## 摘要

本論文講述了太赫茲頻段中低雜訊放大器與次諧波混頻器的設計與實現，並以此分為兩大部分，首先第一部分介紹了一種在 D 頻段具有極高增益的低雜訊放大器，其由 40 奈米 CMOS 製程所實現四級的  $G_{\max}$ -core 放大器。傳統上，構建  $G_{\max}$ -core 具有無限多種組合方式，通常使用三種線性、無損及互易的元件所組成嵌入網路，然而本論文提出了一種使用變壓器所構成的 Y 嵌入網路，能夠改良傳統上只能使用單一偏壓的侷限性，將閘極與漏極分開偏壓，這種方法不僅降低了功耗，也實現了更高的增益與更低的雜訊指數。測量結果表示其在 143.5 GHz 達到峰值增益 27.74 dB，3 dB 帶寬為 7 GHz，雜訊指數約為 9 dB。

第二部分設計了兩種 300 GHz 可上/下變頻的次諧波混頻器，皆為使用 65 奈米 CMOS 製程，藉由挑選不同的電路架構，能使電晶體的電阻值產生 LO 的周期性變化，最後經由並聯電晶體來產生 LO 的二倍頻再與 IF/RF 端進行上/下變頻。其模擬結果表明其轉換增益分別為 -16.4 dB 與 -20.4 dB，皆無使用 DC pad，不僅大幅縮小晶片面積，並實現了零功耗。

關鍵字：太赫茲、亞太赫茲、CMOS、變壓器、低雜訊放大器、次諧波混頻器、 $G_{\max}$ -core

# Abstract

This paper discusses the design and implementation of low-noise amplifiers and sub-harmonic mixers in the sub-terahertz and terahertz frequency bands, dividing the content into two main sections.

Firstly, the initial part introduces a low-noise amplifier with extremely high gain in the D-band, composed of a four-stage  $G_{\max}$ -core amplifier realized in a 40-nm CMOS process. Traditionally, constructing the  $G_{\max}$ -core offers infinitely many combinations, typically achieved using a network composed of three linear, lossless, and reciprocal elements. However, this paper proposes a Y-embedded network constructed with transformers, which improves upon the limitations of traditional single-bias configurations. By biasing the gate and drain separately, this method not only reduces power consumption but also achieves higher gain and lower noise figure. Measurement results demonstrate a peak gain of 27.74 dB at 143.5 GHz, with a 3 dB bandwidth of 7 GHz and a noise figure of approximately 9 dB.

In the second part, two sub-harmonic mixers with tunable frequency up to 300 GHz are designed, both utilizing a 65-nm CMOS process. By selecting different circuit architectures, the resistance value of the transistors can be varied periodically to generate LO frequency. Finally, the LO doubling is achieved by parallel transistors, enabling up/down frequency conversion with IF/RF ports. Simulation results show conversion gains of -16.4 dB and -20.4 dB respectively, without using DC pads, leading to significant reduction in chip area and zero power consumption.

Keywords: Terahertz, Sub-terahertz, CMOS, Transformers, Low-noise amplifier, Sub-harmonic mixer,  $G_{\max}$ -core

# 目次

|                                                                      |          |

|----------------------------------------------------------------------|----------|

| 口試委員審定書.....                                                         | i        |

| 誌謝.....                                                              | ii       |

| 摘要.....                                                              | iii      |

| Abstract.....                                                        | iv       |

| 目次.....                                                              | v        |

| 圖次.....                                                              | ix       |

| 表次.....                                                              | xvi      |

| <b>Chapter 1 緒論.....</b>                                             | <b>1</b> |

| 1.1 研究背景與動機.....                                                     | 1        |

| 1.2 文獻回顧.....                                                        | 2        |

| 1.2.1 150 GHz 低雜訊放大器.....                                            | 2        |

| 1.2.2 300 GHz 混頻器.....                                               | 3        |

| 1.3 論文貢獻.....                                                        | 6        |

| 1.4 章節概要.....                                                        | 6        |

| <b>Chapter 2 應用於 150 GHz 之高增益低雜訊放大器 .....</b>                        | <b>7</b> |

| 2.1 簡介.....                                                          | 7        |

| 2.2 G <sub>max</sub> -core 原理與介紹 .....                               | 8        |

| 2.2.1 G <sub>ma</sub> / G <sub>ms</sub> / U / G <sub>max</sub> ..... | 8        |

|       |                             |    |

|-------|-----------------------------|----|

| 2.2.2 | $G_{\max}$ -core 滿足條件 ..... | 10 |

| 2.2.3 | 增益平面 .....                  | 11 |

| 2.2.4 | Y 和 Z 嵌入網路 .....            | 13 |

| 2.3   | 電路架構 .....                  | 17 |

| 2.4   | 電路設計與流程 .....               | 18 |

| 2.4.1 | 偏壓選擇 .....                  | 18 |

| 2.4.2 | 電晶體尺寸選擇 .....               | 22 |

| 2.4.3 | 電晶體走線影響 .....               | 25 |

| 2.4.4 | $G_{\max}$ -core 設計 .....   | 26 |

| 2.4.5 | 變壓器設計 .....                 | 28 |

| 2.4.6 | 穩定度 .....                   | 31 |

| 2.4.7 | Bypass 電路 .....             | 33 |

| 2.4.8 | 電路佈局與 Post-sim 結果 .....     | 35 |

| 2.5   | 量測與結果 .....                 | 39 |

| 2.5.1 | S 參數量測 .....                | 39 |

| 2.5.2 | $OP_{1dB}$ 量測 .....         | 42 |

| 2.5.3 | NF 量測 .....                 | 43 |

|                                        |                          |           |

|----------------------------------------|--------------------------|-----------|

| 2.6                                    | 問題與討論.....               | 46        |

| <b>Chapter 3 300 GHz 之次諧波混頻器 .....</b> |                          | <b>47</b> |

| 3.1                                    | 簡介.....                  | 47        |

| 3.2                                    | 次諧波換頻器原理與介紹.....         | 48        |

| 3.2.1                                  | 疊接式次諧波換頻器 .....          | 48        |

| 3.2.2                                  | 並列式次諧波換頻器 .....          | 49        |

| 3.2.3                                  | 電路設計規格 .....             | 51        |

| 3.3                                    | 串接式開關 SHM 電路架構.....      | 52        |

| 3.4                                    | 串接式開關 SHM 電路設計與流程.....   | 54        |

| 3.4.1                                  | LO 馬遜巴倫設計 .....          | 54        |

| 3.4.2                                  | 偏壓與電晶體尺寸選擇 .....         | 57        |

| 3.4.3                                  | 電晶體走線 .....              | 61        |

| 3.4.4                                  | 匹配網路 .....               | 63        |

| 3.4.5                                  | 串接式 SHM Post-sim 結果..... | 66        |

| 3.4.6                                  | 串接式 SHM 電路佈局.....        | 70        |

| 3.5                                    | 串接式開關 SHM 量測與結果.....     | 71        |

| 3.5.1                                  | 串接式下變頻之轉換增益模擬與量測 .....   | 71        |

| 3.5.2                                  | 串接式上變頻之轉換增益模擬與量測 .....   | 76        |

|                  |                          |           |

|------------------|--------------------------|-----------|

| 3.6              | 並接式開關 SHM 電路架構.....      | 81        |

| 3.7              | 並接式開關 SHM 電路設計與流程.....   | 82        |

| 3.7.1            | 並接式電路設計 .....            | 82        |

| 3.7.2            | 並接式 SHM Post-sim 結果..... | 84        |

| 3.7.3            | 並接式 SHM 電路佈局.....        | 87        |

| 3.8              | 並接式開關 SHM 量測與結果.....     | 88        |

| 3.8.1            | 並接式下變頻之轉換增益模擬與量測 .....   | 89        |

| 3.8.2            | 並接式上變頻之轉換增益模擬與量測 .....   | 92        |

| 3.9              | 問題與討論.....               | 95        |

| <b>Chapter 4</b> | <b>結論.....</b>           | <b>97</b> |

| REFERENCE.....   |                          | 98        |

## 圖次

|                                            |    |

|--------------------------------------------|----|

| 圖 1.1 亞太赫茲與太赫茲相關收發機研究 .....                | 1  |

| 圖 2.1 太赫茲頻段在大氣衰減之下的影響 .....                | 7  |

| 圖 2.2 增益之轉折點與 K 值 .....                    | 9  |

| 圖 2.3 構成之 LLR 網路 .....                     | 10 |

| 圖 2.4 $K=1$ 之拋物線 .....                     | 12 |

| 圖 2.5 增益平面 .....                           | 13 |

| 圖 2.6 Y 嵌入網路 .....                         | 13 |

| 圖 2.7 Y 嵌入網路移動軌跡 .....                     | 14 |

| 圖 2.8 Z 嵌入網路 .....                         | 15 |

| 圖 2.9 Z 嵌入網路移動軌跡 .....                     | 16 |

| 圖 2.10 二種元件構成的 Y 嵌入網路 .....                | 16 |

| 圖 2.11 三種元件構成的 Y 嵌入網路 .....                | 17 |

| 圖 2.12 提出之四級 $G_{MAX}$ -CORE 電路架構 .....    | 18 |

| 圖 2.13 單一級之 Y 嵌入網路 .....                   | 18 |

| 圖 2.14 $U$ VS. $ID/W$ 之模擬 .....            | 19 |

| 圖 2.15 $V_{DS}=0.9$ V 時之 $GM$ 與 $VG$ ..... | 20 |

| 圖 2.16 $NF_{MIN}$ VS. $ID/W$ 之模擬 .....     | 21 |

| 圖 2.17 $U/NF_{MIN}$ VS. $ID/W$ 之模擬 .....   | 21 |

|                                                                 |    |

|-----------------------------------------------------------------|----|

| 圖 2.18 U VS. WIDTH 與 FINGER .....                               | 23 |

| 圖 2.19 NF <sub>MIN</sub> VS. WIDTH 與 FINGER .....               | 23 |

| 圖 2.20 RN 對 WIDTH 與 FINGER 作圖 .....                             | 24 |

| 圖 2.21 掃描 WIDTH 與 FINGER 之 MAG/MSG .....                        | 24 |

| 圖 2.22 電晶體走線佈局 .....                                            | 25 |

| 圖 2.23 電晶體走線之 G <sub>MAX</sub> 與 F <sub>MAX</sub> 影響 .....      | 25 |

| 圖 2.24 (A)傳統 LLR 嵌入網路 (B)提出基於變壓器之嵌入網路 (C)變壓器嵌入網<br>路之等校模型 ..... | 26 |

| 圖 2.25 傳輸線與其等效模型 .....                                          | 27 |

| 圖 2.26 提出基於變壓器嵌入網路之 Y 參數模型 .....                                | 27 |

| 圖 2.27 變壓器嵌入網路於增益平面上之移動軌跡 .....                                 | 28 |

| 圖 2.28 垂直耦合之變壓器 .....                                           | 29 |

| 圖 2.29 邊緣耦合之變壓器 .....                                           | 29 |

| 圖 2.30 第一級 G <sub>MAX</sub> -CORE .....                         | 30 |

| 圖 2.31 第二級 G <sub>MAX</sub> -CORE .....                         | 30 |

| 圖 2.32 第三級 G <sub>MAX</sub> -CORE .....                         | 31 |

| 圖 2.33 第四級 G <sub>MAX</sub> -CORE .....                         | 31 |

| 圖 2.34 單一級之穩定度 .....                                            | 32 |

| 圖 2.35 級間穩定測試 .....                                             | 32 |

|                                         |    |

|-----------------------------------------|----|

| 圖 2.36 級間穩定皆無相交 .....                   | 32 |

| 圖 2.37 兩路之 BYPASS 電路 .....              | 33 |

| 圖 2.38 第一路電容 .....                      | 33 |

| 圖 2.39 第二路電容 .....                      | 34 |

| 圖 2.40 隔離度模擬 .....                      | 34 |

| 圖 2.41 單一級之 Y 嵌入網路 .....                | 35 |

| 圖 2.42 提出之四級 $G_{MAX}$ -CORE 電路架構 ..... | 35 |

| 圖 2.43 整體穩定度之 K 值 .....                 | 36 |

| 圖 2.44 整體穩定度之 $MU$ 及 $MU'$ .....        | 36 |

| 圖 2.45 S 參數之模擬 .....                    | 37 |

| 圖 2.46 NF 與 $NF_{MIN}$ 之模擬 .....        | 37 |

| 圖 2.47 $P_{1DB}$ 之模擬 .....              | 38 |

| 圖 2.48 LNA 晶片佈局不含 GND 及 DUMMY .....     | 38 |

| 圖 2.49 LNA 完整晶片佈局 .....                 | 39 |

| 圖 2.50 LNA 晶片之顯微鏡圖 .....                | 39 |

| 圖 2.51 S 參數之量測架設 .....                  | 40 |

| 圖 2.52 S 參數模擬與量測 .....                  | 41 |

| 圖 2.53 穩定度之模擬與量測 .....                  | 41 |

| 圖 2.54 $OP_{1DB}$ 之量測架設 .....           | 42 |

|                                                                |    |

|----------------------------------------------------------------|----|

| 圖 2.55 OP <sub>1DB</sub> 之模擬與量測 .....                          | 43 |

| 圖 2.56 NF 量測架構 .....                                           | 44 |

| 圖 2.57 NF 量測架設 .....                                           | 44 |

| 圖 2.58 NF 之模擬與量測 .....                                         | 46 |

| 圖 3.1 疊接式 LO 次諧波混頻器 .....                                      | 49 |

| 圖 3.2 疊接式 LO 次諧波混頻器之波形 .....                                   | 49 |

| 圖 3.3 並列式 LO 次諧波混頻器 .....                                      | 50 |

| 圖 3.4 並列式 LO 次諧波混頻器之波形 .....                                   | 50 |

| 圖 3.5 預計應用及規格 .....                                            | 51 |

| 圖 3.6 串接式開關 SHM 電路架構 .....                                     | 52 |

| 圖 3.7 串接式開關 SHM 等效電阻模型 .....                                   | 53 |

| 圖 3.8 具有補償線之馬遜巴倫 .....                                         | 54 |

| 圖 3.9 補償線馬遜巴倫之 3D 佈局圖 .....                                    | 55 |

| 圖 3.10 補償線馬遜巴倫之 S <sub>21</sub> 與 S <sub>31</sub> 插入損耗模擬 ..... | 56 |

| 圖 3.11 補償線馬遜巴倫之相位與振幅不平衡 .....                                  | 56 |

| 圖 3.12 導通電阻開關比對比電晶體尺寸 .....                                    | 57 |

| 圖 3.13 關閉時之能量洩漏對比電晶體尺寸 .....                                   | 58 |

| 圖 3.14 導通切換速度對比電晶體尺寸 .....                                     | 58 |

| 圖 3.15 C <sub>ON</sub> 對比電晶體尺寸 .....                           | 59 |

|                                                          |    |

|----------------------------------------------------------|----|

| 圖 3.16 C <sub>OFF</sub> 對比電晶體尺寸 .....                    | 59 |

| 圖 3.17 MIXER-CORE 對比電晶體尺寸 .....                          | 60 |

| 圖 3.18 電晶體走線佈局 .....                                     | 62 |

| 圖 3.19 電晶體走線之 F <sub>T</sub> 與 F <sub>MAX</sub> 影響 ..... | 62 |

| 圖 3.20 RF 端阻抗匹配路徑 .....                                  | 63 |

| 圖 3.21 RF 端之反射損失 .....                                   | 64 |

| 圖 3.22 LO 端阻抗匹配路徑 .....                                  | 65 |

| 圖 3.23 LO 端之反射損失 .....                                   | 65 |

| 圖 3.24 本文提出之串接式開關次諧波混頻器架構 .....                          | 67 |

| 圖 3.25 串接式 LO 功率對比轉換增益之模擬 .....                          | 67 |

| 圖 3.26 串接式 RF 頻率對比轉換增益之模擬 .....                          | 68 |

| 圖 3.27 串接式 LO 頻率對比轉換增益之模擬 .....                          | 68 |

| 圖 3.28 串接式 IF 頻率對比轉換增益之模擬 .....                          | 69 |

| 圖 3.29 串接式 RF 功率對比轉換增益之模擬 .....                          | 69 |

| 圖 3.30 串接式開關 SHM 電路佈局 .....                              | 70 |

| 圖 3.31 串接式開關 SHM 晶片之顯微鏡圖 .....                           | 71 |

| 圖 3.32 下變頻之量測架設方塊圖 .....                                 | 73 |

| 圖 3.33 下變頻量測實際架設圖 .....                                  | 73 |

| 圖 3.34 串接式 LO 功率對比轉換增益下變頻之量測 .....                       | 74 |

|                                              |    |

|----------------------------------------------|----|

| 圖 3.35 串接式 IF 頻率對比轉換增益下變頻之量測 .....           | 74 |

| 圖 3.36 串接式 LO 頻率對比轉換增益下變頻之量測 .....           | 75 |

| 圖 3.37 串接式 RF 頻率對比轉換增益下變頻之量測 .....           | 75 |

| 圖 3.38 串接式 RF 功率對比轉換增益下變頻之量測 .....           | 76 |

| 圖 3.39 上變頻之量測架設方塊圖 .....                     | 77 |

| 圖 3.40 上變頻量測實際架設圖 .....                      | 77 |

| 圖 3.41 串接式 LO 功率對比轉換增益上變頻之量測 .....           | 78 |

| 圖 3.42 串接式 IF 頻率對比轉換增益上變頻之量測 .....           | 78 |

| 圖 3.43 串接式 LO 頻率對比轉換增益上變頻之量測 .....           | 79 |

| 圖 3.44 串接式 RF 頻率對比轉換增益上變頻之量測 .....           | 79 |

| 圖 3.45 串接式 IF 功率對比轉換增益上變頻之量測 .....           | 80 |

| 圖 3.46 並接式開關 SHM 電路架構 .....                  | 81 |

| 圖 3.47 並接式開關 SHM 等效電阻模型 .....                | 82 |

| 圖 3.48 串接與並接式之 $R_{ON}$ 頻率響應比較 .....         | 83 |

| 圖 3.49 串接與並接式之 $R_{OFF}$ 頻率響應比較 .....        | 83 |

| 圖 3.50 串接與並接式之 $R_{OFF}/R_{ON}$ 頻率響應比較 ..... | 84 |

| 圖 3.51 並接式 LO 功率對比轉換增益之模擬 .....              | 85 |

| 圖 3.52 並接式 RF 頻率對比轉換增益之模擬 .....              | 86 |

| 圖 3.53 並接式 LO 頻率對比轉換增益之模擬 .....              | 86 |

|                                    |    |

|------------------------------------|----|

| 圖 3.54 並接式 IF 頻率對比轉換增益之模擬 .....    | 87 |

| 圖 3.55 並接式 RF 功率對比轉換增益之模擬 .....    | 87 |

| 圖 3.56 並接式開關 SHM 電路佈局 .....        | 88 |

| 圖 3.57 並接式開關 SHM 晶片之顯微鏡圖 .....     | 89 |

| 圖 3.58 並接式 LO 功率對比轉換增益下變頻之量測 ..... | 90 |

| 圖 3.59 並接式 IF 頻率對比轉換增益下變頻之量測 ..... | 90 |

| 圖 3.60 並接式 LO 頻率對比轉換增益下變頻之量測 ..... | 91 |

| 圖 3.61 並接式 RF 頻率對比轉換增益下變頻之量測 ..... | 91 |

| 圖 3.62 並接式 RF 功率對比轉換增益下變頻之量測 ..... | 92 |

| 圖 3.63 並接式 LO 功率對比轉換增益上變頻之量測 ..... | 93 |

| 圖 3.64 並接式 IF 頻率對比轉換增益上變頻之量測 ..... | 93 |

| 圖 3.65 並接式 LO 頻率對比轉換增益上變頻之量測 ..... | 94 |

| 圖 3.66 並接式 RF 頻率對比轉換增益上變頻之量測 ..... | 94 |

| 圖 3.67 並接式 IF 功率對比轉換增益上變頻之量測 ..... | 95 |

| 圖 3.68 RF 關閉，LO 開啟時出現的 TONE.....   | 96 |

| 圖 3.69 LO 之 1/12 訊號頻譜 .....        | 96 |

## 表次

|                                 |    |

|---------------------------------|----|

| 表 1.1 低雜訊放大器文獻比較 .....          | 3  |

| 表 1.2 300 GHz 混頻器文獻比較 .....     | 5  |

| 表 2.1 150 GHz 低雜訊放大器之設計目標 ..... | 8  |

| 表 3.1 次諧波混頻器之設計目標 .....         | 51 |

# Chapter 1 緒論

## 1.1 研究背景與動機

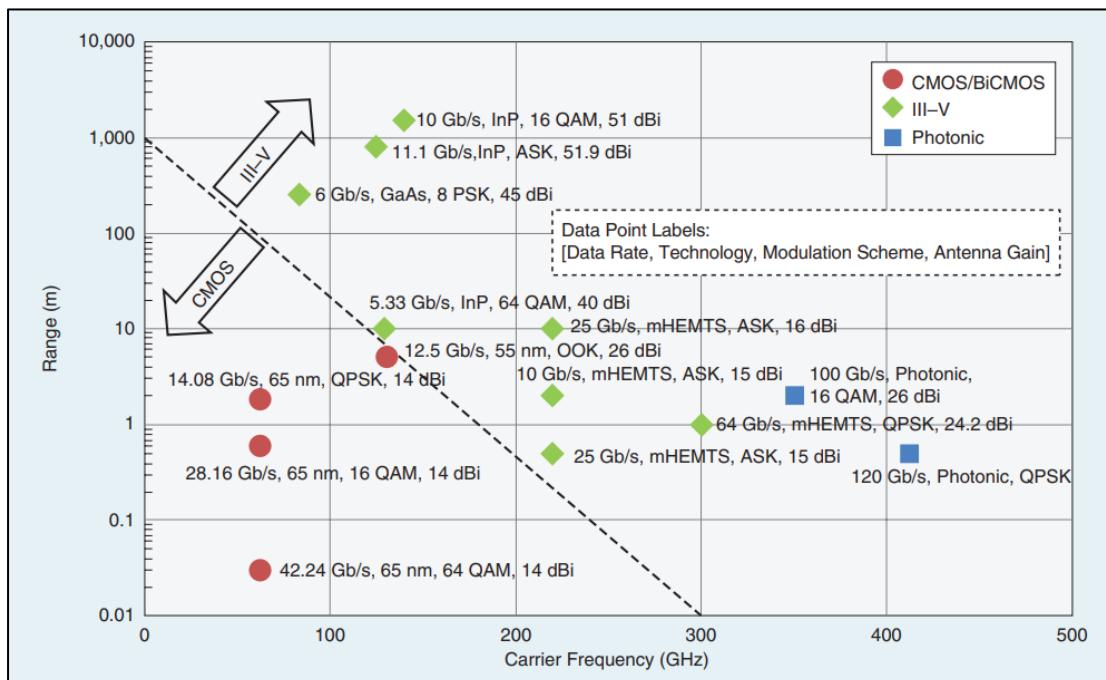

隨著通訊技術的不斷發展，為了實現更快的資料傳輸速度，人們逐漸將重心轉向高頻段的發展[1][2]，根據 Shannon 定理，資料傳輸的容量與頻帶寬度成正比，這促使了近年來往更高頻率的探索和發展。因此，亞太赫茲(sub-THz)與太赫茲(THz)頻段成為了熱門研究領域，亞太赫茲頻段介在 0.1 THz 至 0.3 THz，而太赫茲頻段介在 0.3 THz 至 3 THz 頻段。由於這些頻段的波長較短，使得電路及元件都能相對應的縮小，但其缺點為容易受到通道路徑和大氣衰減的影響，使得這些應用通常為短距離(5 - 20 m)和中距離(50 - 200 m)的高速資料傳輸。圖 1.1[3]整理了近年來積體電路所實踐的收發機研究，為了有效利用頻寬並提高抗干擾的能力，較高的載波頻率通常使用較簡單如 ASK 或 QPSK 的調變方式，文獻[4]則統整了目前關於 100 Gb/s 及更高速率之收發機。

圖 1.1 亞太赫茲與太赫茲相關收發機研究

根據 Friis 公式，在接收機之中第一級貢獻了整體的主要雜訊，因此通常會

將低雜訊放大器(LNA)來作為整體接收機的第一級。然而，在 THz 頻段中主要會受限於製程的電晶體最大震盪頻率( $f_{max}$ )，無法在超過  $f_{max}$  的頻率下實現放大器。雖然 III-IV 化合物製程擁有較高的  $f_{max}$ ，能在此頻段提供良好的性能，但是價格昂貴並且取得困難。而 CMOS 製程雖然  $f_{max}$  較低，但成本低廉並且能與基頻上的數位電路高度整合，成為發展的首選。因此在 THz 頻段中，提出了混頻器優先(mixer-first)的架構，然而將混頻器作為第一級取代 LNA，存在著輸出增益不足、雜訊指數高及會有 LO 洩漏等問題，這些都是目前所需面臨的挑戰。

## 1.2 文獻回顧

### 1.2.1 150 GHz 低雜訊放大器

目前在 D 頻段中已有許多低雜訊放大器研究文獻[5][6][7]。cascode 電路[8][9][10][11]加入退化電感[12][13]能夠拿來做匹配和減少雜訊，與差動中和電容技術[14][15][16][17][18]都廣泛被使用。然而在亞太赫茲頻率以上，受限於  $f_{max}$  和被動元件高損耗的限制，通常需要更多級來彌補損失的增益。因此有陸續文獻研究接近  $f_{max}$  的  $G_{max}$ -core 放大器[19][20][21]，其利用線性、無損且互易的元件來組成嵌入網路，使其能達到最大的增益，並可設計藉由這無限種組合來同時達到雜訊匹配[22]。然而由於結構限制會導致只使用一種偏壓  $V_G$  等於  $V_D$ ，這增加不必要的功耗並降低性能。文獻[23]提出了一種解決方案，通過將獨立的偏置 Z 網絡納入設計中來應對這一挑戰。

表 1.1 低雜訊放大器文獻比較

| Reference              | [6]                  | [18]                 | [22]                 | [23]                 | This Work            |

|------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Technology             | 40 nm<br>CMOS        | 45 nm<br>CMOS        | 65 nm<br>CMOS        | 40 nm<br>CMOS        | 40 nm<br>CMOS        |

| Topology               | Differential<br>5 CG | Differential<br>4 CS | Single-ended<br>2 CS | Single-ended<br>7 CS | Single-ended<br>4 CS |

| $f_{\max}$ (GHz)       | -                    | -                    | 310                  | 275                  | 275                  |

| $f_0$ (GHz)            | 146.5                | 141.2                | 152.2                | 180                  | 143                  |

| Gain (dB)              | 20.9                 | 16                   | 17.9                 | 14.8                 | 27.74                |

| NF (dB)                | 6.2                  | 8                    | 6.2                  | 11                   | 8                    |

| 3dB BW (GHz)           | 31                   | 31.5                 | 13                   | 11                   | 7.5                  |

| $OP_{1dB}$ (dBm)       | 1.2                  | 1.5                  | -6.9                 | -6.2                 | -2.5                 |

| $P_{DC}$ (mW)          | 49                   | 75                   | 13.7                 | 23.9                 | 27.1                 |

| Area ( $\text{mm}^2$ ) | 0.38                 | 0.36                 | 0.19                 | 0.41                 | 0.35                 |

### 1.2.2 300 GHz 混頻器

300 GHz 頻段的混頻器受限於低  $f_{\max}$ ，較難有效的去利用，文獻[24]使用 40 奈米 CMOS 製程，進行了兩次上變頻到 300 GHz，一開始是使用單平衡混頻器上變頻到  $IF_2$ ，再將變頻一次的  $IF_2$  及洩漏進來的 LO 經過平方混頻器產生  $(IF_2+LO)^2$  項，除了 RF 項之外，會產生不必要的  $IF_2$  及 LO 項，這些會需要增加更大的互補訊號電路來去抵銷他，且為了在發射機上產生更大的輸出功率，也需要更多的功率組合，這些元件的設計都增加了電路的複雜度，以及更大的晶片面積。

文獻[25]是使用 80 奈米 InP 製程的被動電阻式混頻器，其高線性度的特性可滿足高階調變的需求，而此設計之中隔離度的考量是整體關鍵，先天上 RF-IF 隔離度較差，如何設計高隔離度除了避免訊號間的干擾，IF 及 RF 阻抗轉換比增加會進而使轉換增益提升。文獻[26]是使用 InP 250 奈米的單平衡混頻器，有著尚可的隔離度和轉換增益，輸入平衡的信號可以避免掉原本單平衡會洩漏的 LO 項，解調變時輸入的射頻訊號會產生  $\tanh$  形式的電流，這些可以抑制 LO 偶次諧波，便可以很有效的減少直接轉換下的危害，但是頻譜效率不夠好，對更高階的調變有些隱憂。

文獻[27]使用 40 奈米 CMOS 製程，使用 6 倍的 LO 乘法鏈輸出較低功率的 LO 再搭配上雙平衡混頻器，再藉由 rat-race balun 輸出射頻訊號，整體而言有著不錯的轉換增益以及線性度。文獻[6]則是使用 65 奈米 CMOS 製程，提出了一種新型的低損寬帶 Marchand balun 來作為射頻訊號的平衡輸入，搭配雙平衡混頻器使用，線性度不錯也能改善 LO 到 IF 的洩漏，但轉換增益較差，LO 功率為 0 dBm 時的轉換增益約 -18.5 dB。

表 1.2 300 GHz 混頻器文獻比較

| Reference               | [24]                      | [25]                      | [26]            | [27]             | [28]             |

|-------------------------|---------------------------|---------------------------|-----------------|------------------|------------------|

| Topology                | Single-balanced<br>Square | Single-ended<br>Resistive | Single-balanced | Doubled-balanced | Doubled-balanced |

| Technology              | 40nm<br>CMOS              | 80nm InP                  | 250nm InP       | 40nm<br>CMOS     | 65nm<br>CMOS     |

| Freq (GHz)              | 289-311                   | 270-302                   | 280-320         | 268-313          | 270-290          |

| f <sub>LO</sub> (GHz)   | 145                       | 270                       | 300             | 300              | 140              |

| P <sub>LO</sub> (dBm)   | 5.5                       | 5                         | -5              | -4.4             | 6                |

| Conv. Gain (dB)         | -                         | -15                       | -15             | -19              | -16              |

| OP <sub>1dB</sub> (dBm) | -21.3                     | -16                       | -               | -17              | -17              |

| P <sub>DC</sub> (mW)    | 19.95                     | 0                         | 22              | -                | 0                |

| Area (mm <sup>2</sup> ) | -                         | 1                         | 0.99            | -                | 0.12             |

### 1.3 論文貢獻

在本論文中，成功設計了操作頻率於 150 GHz 的低雜訊放大器，為了解決 Gmax-core 閘極和漏極能夠獨立分開給偏壓，提出了一種基於變壓器的嵌入式網絡，以實現四級的 Gmax-core。測量結果顯示，最小噪聲指數為 8 dB，峰值增益為 27.74 dB，在此頻段中增益相當高，並且僅消耗 27.1 mW 直流功率。其次，設計了操作頻率於 300 GHz 串接式和並接式開關次諧波混頻器，雖然量測結果未如預期，但提供了一新型的架構，成功驗證了混頻功能與可行之設計方向。本研究涵蓋放大器與混頻器兩大關鍵電路，建構完整的超高頻接收端前級設計流程，並對 CMOS 製程下高頻混頻器之開關阻抗行為進行深入分析，對未來高頻通訊晶片設計具備參考與實用價值。

### 1.4 章節概要

本論文共分為四章，各章之內容安排如下：第一章為緒論，主要說明本研究的背景與動機。第二章針對 150 GHz 低雜訊放大器進行深入探討，包括其原理、架構、電路設計，並呈現模擬與量測結果。第三章介紹兩種工作於 300 GHz 的次諧波混頻器，分別闡述其運作原理與電路架構、設計流程，並分析其模擬與量測結果。最後，第四章為本論文之總結與未來展望。

# Chapter 2 應用於 150 GHz 之高增益低雜訊放大器

## 2.1 簡介

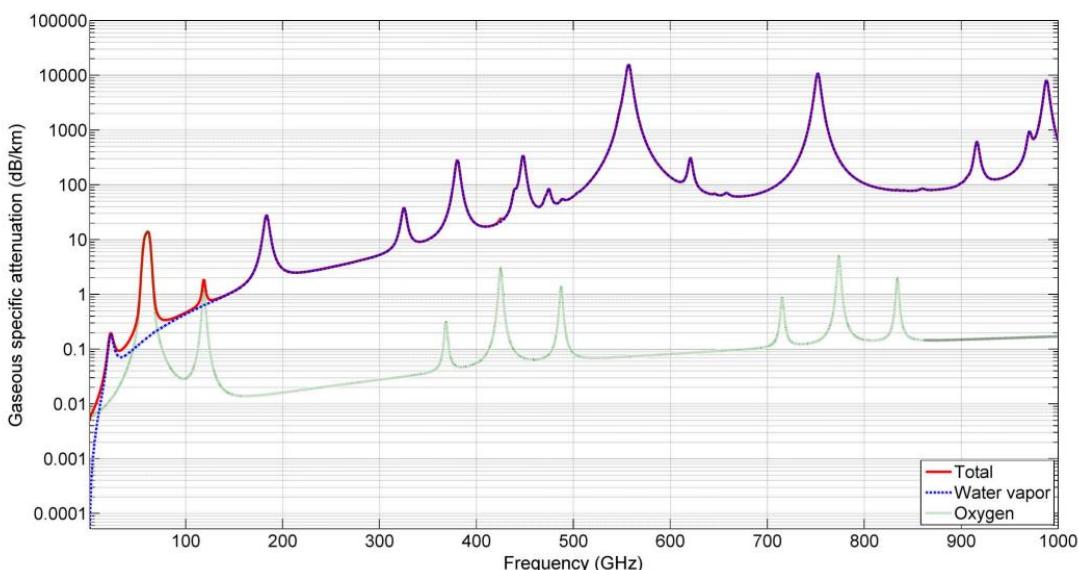

近年來 Sub-THz 頻段已實現多項創新應用，包括無線通訊、化學檢測、生醫與成像等[29][30]，相較於第五世代無線通訊(5G) 28 GHz、38 GHz、60 GHz 頻段相比，Sub-THz 擁有更高的載波頻率，可提供更大的頻寬與更高速的資料傳輸率，有利於未來 6G 或更進階系統的發展與應用。

然而，如圖 2.1 所示，為 1 THz 以下的大氣衰減量，隨著頻率變化的情形可以觀察到，隨著頻率上升，訊號在空氣中的衰減量也顯著增加[31]，此衰減主要來自於水氣與氧氣分子的吸收，且在特定頻率如 60 GHz、120 GHz、180 GHz、325 GHz 等處出現明顯吸收峰值，這些頻率對於無線傳輸構成重大限制。

因此，雖然 Sub-THz 頻段在資料速率上具有潛在優勢，其高頻特性也意味著大氣吸收嚴重，不利於長距離傳輸。這促使相關應用更適合用於短距離、高密度環境(如室內通訊、感測網路)，並在實務設計上需配合波束成形、高增益天線與低功耗架構等技術進行補償與優化。

圖 2.1 太赫茲頻段在大氣衰減之下的影響

在本章節中，我們實現了操作於 150 GHz 之高增益低雜訊放大器，採用

TSMC 40 nm 1P9M 無厚金屬製程技術，為了能在 D-band 頻段內實現優異的增益，本設計使用四級的  $G_{\max}$ -core 架構，與傳統以傳輸線構成的嵌入網路不同，本設計中提出一種基於變壓器之 Y 嵌入網路架構，使用變壓器作為嵌入網路的元件，不僅有助於實現線性、無損與互易(LLR)之條件，更能有效解決傳統設計中閘極與漏極需設定相同偏壓所導致的多餘功耗問題。透過此創新架構，本研究成功驗證了其在同時降低雜訊指數與提升增益方面的可行性與優勢，於太赫茲頻段中具有高度潛力。

表 2.1 150 GHz 低雜訊放大器之設計目標

| Frequency | Gain    | Noise Figure | Return Loss | $P_{DC}$ | Size                |

|-----------|---------|--------------|-------------|----------|---------------------|

| 150 GHz   | > 30 dB | < 8 dB       | < -10 dB    | < 30 mW  | 0.5 mm <sup>2</sup> |

## 2.2 $G_{\max}$ -core 原理與介紹

### 2.2.1 $G_{ma}$ / $G_{ms}$ / $U$ / $G_{\max}$

為了深入理解  $G_{\max}$ -core 之設計理念，本節將介紹幾種常見的增益定義，包括最大穩定增益(Maximum Stable Gain,  $G_{ms}$ )、最大可用增益(Maximum Available Gain,  $G_{ma}$ )、最大單向化增益(Unilateral Gain,  $U$ )與最大可實現增益(Maximum Achievable Gain,  $G_{\max}$ )。這些增益指標可用來評估放大器在不同條件下的理論性能，並作為嵌入網路設計的重要依據。

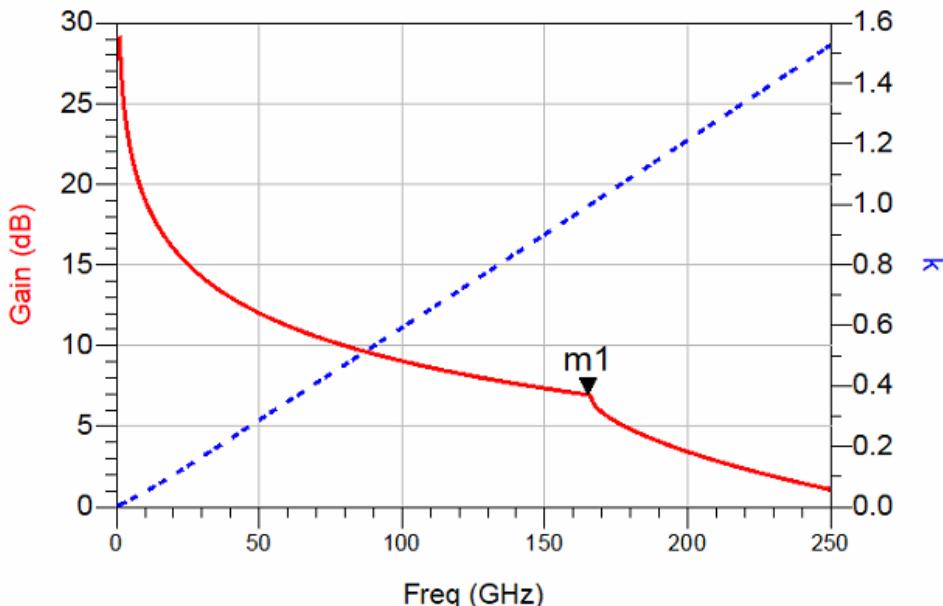

如圖 2.2 所示，電晶體的增益曲線在 165 GHz 處出現明顯的轉折點，此處的 Rollett 穩定因子 K 值剛好等於 1，表示系統處於穩定與不穩定的交界。165 GHz 以下屬於有條件穩定區，此區域雖有較高增益潛力，但反射係數較大，可能導致系統不穩定。而 165 GHz 以上則為無條件穩定區，穩定性提升但增益略為下降。

在此基礎上，定義了兩種增益，低於轉折點頻率在有條件穩定區中，透過共

軛匹配並避開不穩定點後所能實現的最大穩定增益( $G_{ms}$ )。而高於轉折點頻率為無條件穩定，其共軛匹配下的增益稱為最大可用增益( $G_{ma}$ )。

$$G_{ma} = \left| \frac{S_{21}}{S_{12}} \right| (K - \sqrt{K^2 - 1}) \quad (2.1)$$

$$G_{ms} = \left| \frac{S_{21}}{S_{12}} \right| \quad (2.2)$$

圖 2.2 增益之轉折點與 K 值

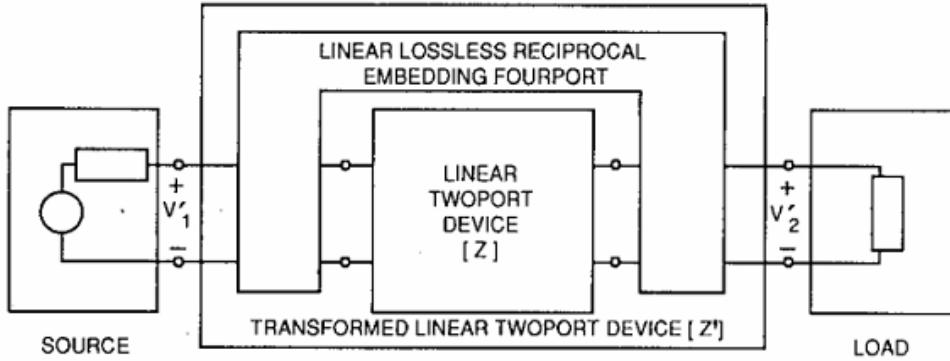

最大單向化增益(Unilateral Gain, U)又稱為 Mason 增益[32]，是評估電晶體在輸出無回授( $S_{12} = 0$ )下能達到的最大增益，在此情況下，嵌入網路需滿足三項條件：線性(Linear)、無損(Lossless)與互易(Reciprocal)，此類網路統稱為 LLR 網路，如圖 2.3 所示。U 的公式表示如下，實際上因  $S_{12}$  往往不為 0，U 為理論指標，但仍可用此觀念作為後續  $G_{max}$  推導的基礎。

$$U = \frac{\left| \frac{S_{21}}{S_{12}} - 1 \right|^2}{2k \left| \frac{S_{21}}{S_{12}} \right| - 2Re \left( \frac{S_{21}}{S_{12}} \right)} \quad (2.3)$$

圖 2.3 構成之 LLR 網路

當嵌入網路滿足 LLR 條件時，電晶體在該結構下能達成的最大理論增益即為最大可實現增益( $G_{max}$ )。此值可由 Mason 增益 U 推導而得，如下式所示：

$$G_{max} = (2U - 1) + \left(2\sqrt{U(U - 1)}\right) \approx 4U \quad (2.4)$$

由此可知， $G_{max}$  僅與 U 有關，而 U 在 LLR 條件下不會因不同的嵌入網路而改變，故  $G_{max}$  所對應的嵌入網路架構亦可能有無限多種組合。這提供了設計者極大的靈活性，只需滿足 LLR 條件，即可透過不同架構實現等效上的最大增益。

## 2.2.2 $G_{max}$ -core 滿足條件

$G_{max}$ -core 的設計目標是實現最大可實現增益( $G_{max}$ )，為此需滿足特定的嵌入網路條件。根據文獻中對 U 與 S 參數之間的關係，可先定義轉移函數  $A = \left| \frac{S_{21}}{S_{12}} \right|$ ，代回(2.3)可將 U 改寫為

$$U = \frac{|A - 1|^2}{2k|A| - 2Re(A)} \quad (2.5)$$

另一方面，將最大可用增益  $G_{ma}$  的表達式(2.1)代入上式(2.5)並整理，可推導出 U 與  $G_{ma}$ 、A 之間的數學關係：

$$U = \frac{\frac{G_{ma}^2}{a^2} - 2\frac{G_{ma}}{a}\cos(\vartheta) + 1}{(\frac{a^2 + 1}{a})(\frac{G_{ma}}{a}) - 2\frac{G_{ma}}{a}\cos(\vartheta)} \quad (2.6)$$

其中  $a = k - \sqrt{k^2 - 1}$ ,  $\vartheta = \text{phase}(A)$

進一步將(2.6)式整理，可得  $G_{ma}$  關於  $U$ 、 $a$ 、 $\vartheta$  的表達式：

$$G_{ma} = \frac{1}{2} [ Ua^2 - 2a \cos(\vartheta)(U - 1) + U \\ + \sqrt{(Ua^2 - 2a \cos(\vartheta)(U - 1) + U)^2 - 4a^2} ] \quad (2.7)$$

由此可見， $G_{ma}$  會受到三個參數影響，分別為耦合程度  $a$ 、相位角  $\vartheta$ 、以及增益  $U$ 。若欲使  $G_{ma}$  達到理論最大值，則(2.7)必須滿足以下條件，分別為  $a = 1$  且  $\cos(\vartheta) = -1$ ，而這兩項條件可進一步對應(2.8)與(2.9)式：

$$K = 1 \quad (2.8)$$

$$\text{phase}\left(\frac{S_{21}}{S_{12}}\right) = \text{phase}\left(\frac{Y_{21}}{Y_{12}}\right) = \pm\pi \quad (2.9)$$

可根據(2.1) (2.8) (2.9)，合併得出最終  $G_{max}$  條件為：

$$\frac{S_{21}}{S_{12}} = \frac{Y_{21}}{Y_{12}} = -G_{max} \quad (2.10)$$

最終，將(2.8)與(2.9)代回(2.7)，可得出  $G_{max}$  之數學式：

$$G_{ma} = G_{max} = (2U - 1) + \left(2\sqrt{U(U - 1)}\right) \approx 4U \quad (2.11)$$

此推導證實在滿足 LLR 條件下， $G_{max}$ -core 所能達成的最大理論增益與  $U$  成正比。

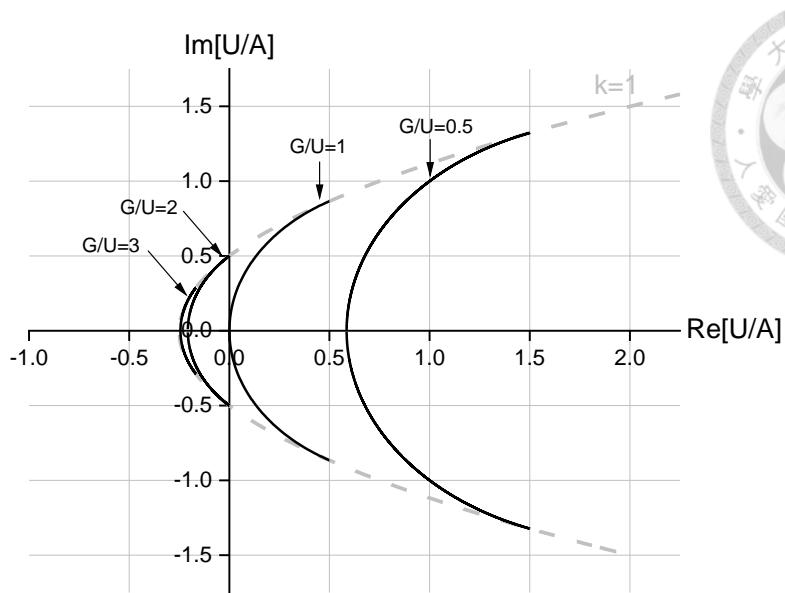

### 2.2.3 增益平面

參考文獻[33][34]可將  $G_{ma}$  簡化成僅與  $U$  和  $A$  相關之關係式(2.12)，為了將  $G_{ma}$  提升至  $G_{max}$ ，可以從調整  $U$  或轉移函數  $A$  著手。然而， $U$  在電路中是只與電晶體有關的正實數，並不會受到 LLR 嵌入網路的變化所影響。因此，我們只能利用轉移函數  $A$ ，通過設計不同的 LLR 嵌入網路，使得  $G_{ma}$  能夠達至  $G_{max}$ 。

$$\frac{G_{ma}}{U} = \left| \frac{A - G_{ma}}{A - 1} \right|^2$$

若假設  $|A| \gg 1$  時，可從[33]將(2.12)簡化為(2.13)

$$\frac{U}{G_{ma}} = (Re\left(\frac{U}{A}\right) - \frac{U}{G_{ma}})^2 + (Im\left(\frac{U}{A}\right))^2$$

可以從(2.13)得知，將此視為圓之方程式，其中 X 軸為  $Re\left(\frac{U}{A}\right)$ ，Y 軸為  $Im\left(\frac{U}{A}\right)$ ，圓心在  $(\frac{U}{G_{ma}}, 0)$ ，半徑為  $\sqrt{\frac{U}{G_{ma}}}$ 。不同定值的  $\frac{U}{G_{ma}}$  分別有著各自的圓，

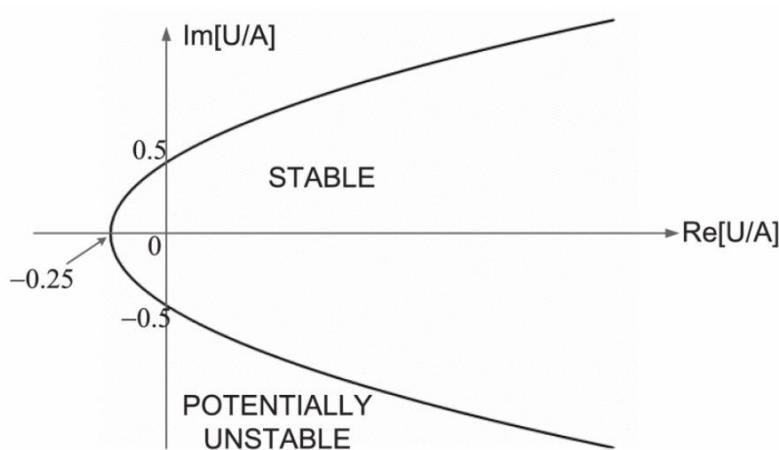

然而會受到穩定度影響，並非此圓上任一點皆滿足增益平面的條件，為了找出穩定性與增益平面之關係，[34][35]給出在  $K = 1$  時之曲線方程式為

$$(Im\left(\frac{U}{A}\right))^2 = Re\left(\frac{U}{A}\right) + \frac{1}{4} \quad (2.14)$$

此拋物線將平面劃分出兩個區域，如圖 2.4 所示，分別代表著內部區域為  $K > 1$ ，外面區域則為  $K < 1$ 。(2.13)中的每個圓皆會與(2.14)相切，其中相切的兩點會將圓劃分出左半弧和右半弧，然而只有左半弧為有效的，原因在於圓的切點往右半弧移動時，K 值會隨之增加，但  $|A|$  却會同時減少，這意味著(2.1)式  $G_{ma}$  值會下降，並無法保持為常數。因此，只有左半弧之軌跡可當作增益平面使用。圖 2.5 表示了在  $G_{ma}$  分別為  $3U$ 、 $2U$ 、 $U$ 、 $0.5U$  時之增益平面，可從其得知  $G_{ma}$  越大時曲線會越往左移，直到達到最大值  $G_{max}$ (約為  $4U$ )。

圖 2.4  $K = 1$  之拋物線

圖 2.5 增益平面

#### 2.2.4 Y 和 Z 嵌入網路

為了實現最大可實現增益  $G_{\max}$ ，本節探討兩種常見的嵌入網路實現形式：Y型嵌入網路 (Admittance Embedding Network) 與 Z型嵌入網路 (Impedance Embedding Network)。透過加入滿足 LLR 條件之被動元件，這些嵌入網路可調整電晶體在增益平面上之移動，用來逼近  $G_{\max}$  之對應位置，提升整體增益。

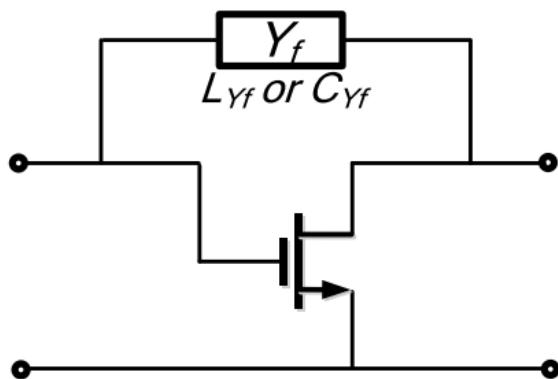

常見的 Y 嵌入網路是在雙埠電晶體上並聯一個 LLR 元件  $Y_f$  (如電感  $L_{Yf}$  或  $C_{Yf}$  電容)，如圖 2.6 所示，進而改變整體的導納矩陣。

圖 2.6 Y 嵌入網路

其等效的 Y 參數矩陣  $Y_{EF}$  可表示為：

$$Y_{EF} = \begin{bmatrix} Y_{11} & Y_{12} \\ Y_{21} & Y_{22} \end{bmatrix} + \begin{bmatrix} Y_f & -Y_f \\ -Y_f & Y_f \end{bmatrix} \quad (2.15)$$

其中  $Y_f$  為新加入的 LLR 元件之導納，因此可以從增益平面上找出新的嵌入網路

點  $\frac{U}{A_{EF}}$ ：

$$\frac{U}{A_{EF}} = \frac{U(Y_{12} - Y_f)}{Y_{21} - Y_f} \quad (2.16)$$

當  $|Y_f| \ll |Y_{21}|$  時，可將其近似為：

$$\frac{U}{A_{EF}} \approx \frac{U}{A} - \frac{UY_f}{Y_{21}} = \frac{U}{A} + \frac{U|Y_f|}{|Y_{21}|} e^{j(\pm\frac{\pi}{2} - \angle Y_{21})} \quad (2.17)$$

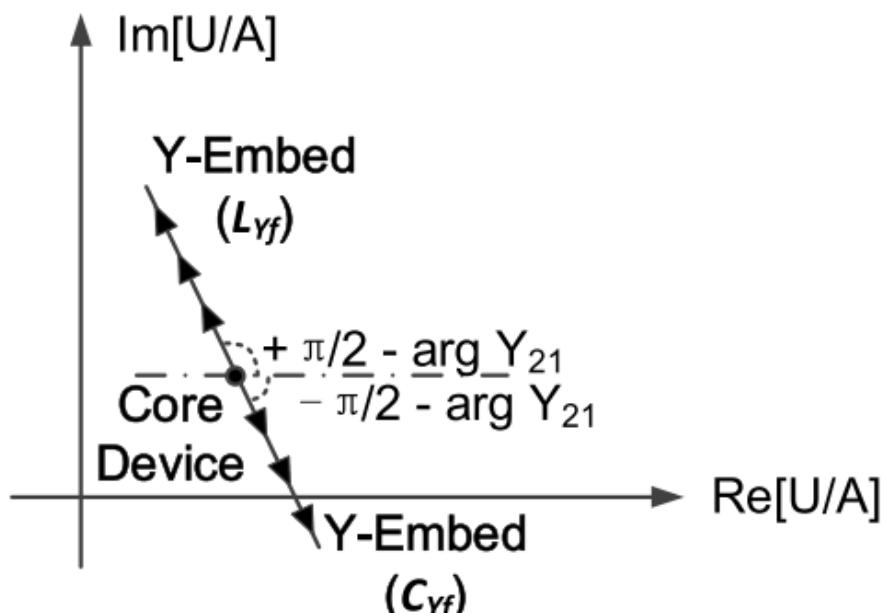

由(2.17)可得，Y 嵌入網路所增加的大小為  $\frac{U|Y_f|}{|Y_{21}|}$ ，若  $Y_f$  為電感，代表著  $Y_f < 0$ ，其對應的相位為  $\frac{\pi}{2} - \angle Y_{21}$ 。若  $Y_f$  為電容，代表著  $Y_f > 0$ ，其對應的相位為  $-\frac{\pi}{2} - \angle Y_{21}$ ，可從增益平面上觀察出其移動軌跡如圖 2.7 所示。

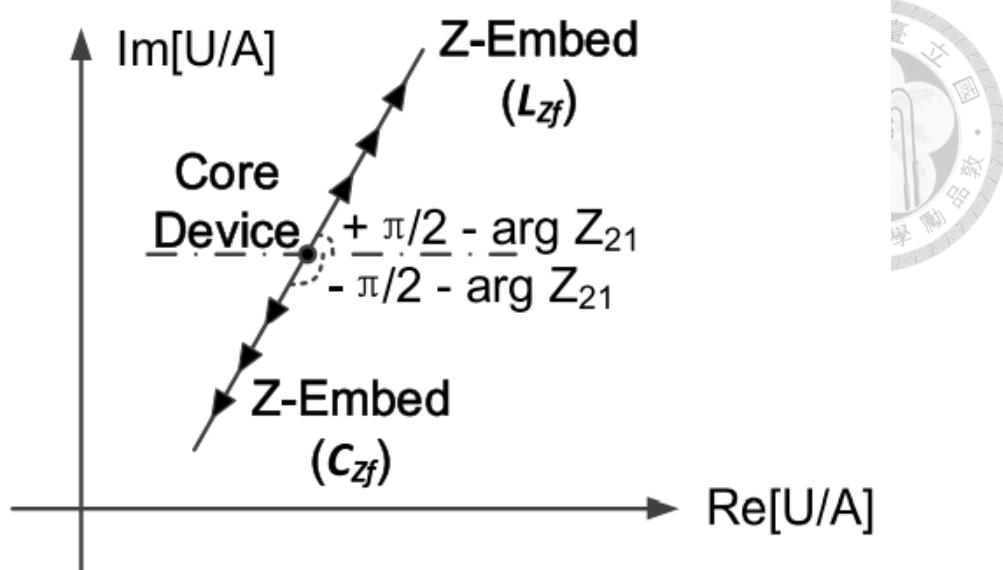

圖 2.7 Y 嵌入網路移動軌跡

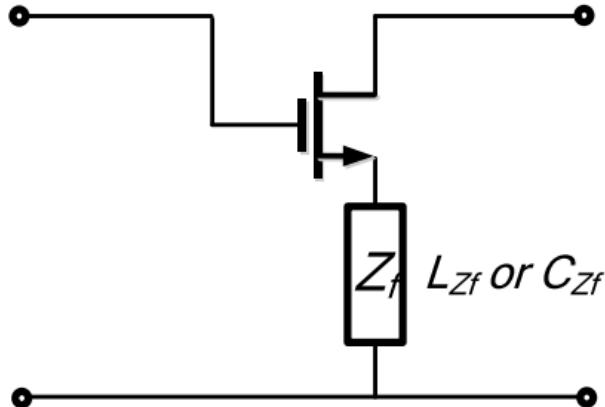

圖 2.8 Z 嵌入網路

圖 2.8 中顯示 Z 型嵌入網路結構，其在輸出端或輸入端串接 LLR 元件  $Z_f$  (如電感  $L_{Zf}$  或  $C_{Zf}$  電容)。Z 型網路的等效 Z 參數矩陣  $Z_{EF}$  為：

$$Z_{EF} = \begin{bmatrix} Z_{11} & Z_{12} \\ Z_{21} & Z_{22} \end{bmatrix} + \begin{bmatrix} Z_f & Z_f \\ Z_f & Z_f \end{bmatrix} \quad (2.15)$$

其中， $Z_f$  為新加入的 LLR 元件之阻抗，因此可以從增益平面上找出新的嵌入網路點  $\frac{U}{A_{EF}}$ ：

$$\frac{U}{A_{EF}} = \frac{U(Z_{12} + Z_f)}{Z_{21} + Z_f} \quad (2.16)$$

在  $|Z_f| \ll |Z_{21}|$  的條件下，可將其近似為：

$$\frac{U}{A_{EF}} \approx \frac{U}{A} + \frac{UZ_f}{Z_{21}} = \frac{U}{A} + \frac{U|Z_f|}{|Z_{21}|} e^{j(\pm\frac{\pi}{2} - \angle Z_{21})} \quad (2.17)$$

由(2.17)可得，Z 嵌入網路所增加的大小為  $\frac{U|Z_f|}{|Z_{21}|}$ ，若  $Z_f$  為電感，代表著  $Z_f > 0$ ，其對應的相位為  $\frac{\pi}{2} - \angle Z_{21}$ 。若  $Z_f$  為電容，代表著  $Z_f < 0$ ，其對應的相位為  $-\frac{\pi}{2} - \angle Z_{21}$ ，可從增益平面上觀察出其移動軌跡如圖 2.9 所示。

圖 2.9 Z 嵌入網路移動軌跡

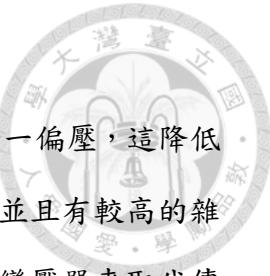

常見的 Y 嵌入網路會使用二種或三種元件來達至  $G_{\max}$ [36]，如圖 2.10 為使用兩種元件來組合，然而為了滿足(2.8)(2.9)，會使得滿足的組合條件在增益平面上為唯一解，因此較難被廣泛利用。使用三種 LLR 元件來組 Y 嵌入網路，如圖 2.11 所示，此 Y 嵌入網路在滿足條件下仍有無限多種組合，能夠更簡單的滿足設計需求，而偏壓的設計上會將閘極和漏極使用同個偏壓來減少複雜性。

圖 2.10 二種元件構成的 Y 嵌入網路

圖 2.11 三種元件構成的 Y 嵌入網路

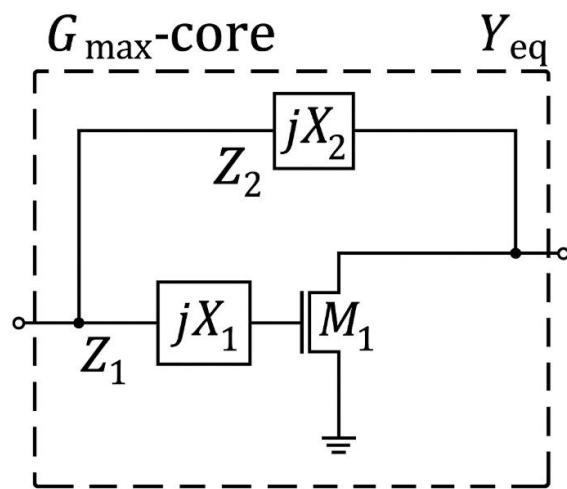

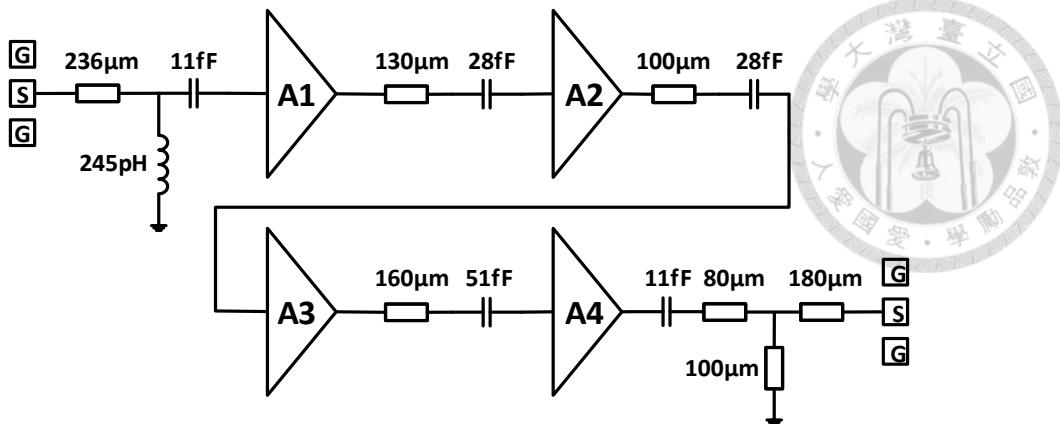

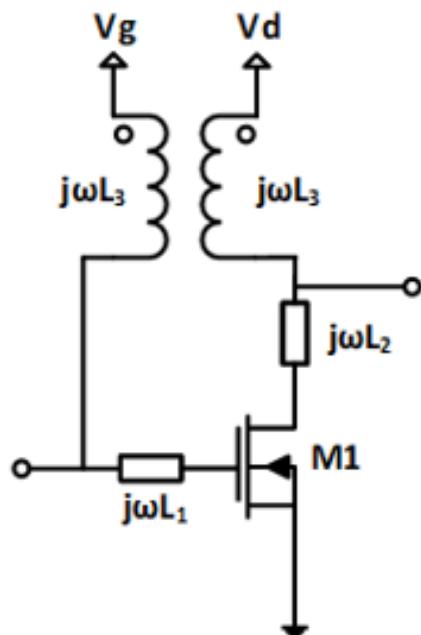

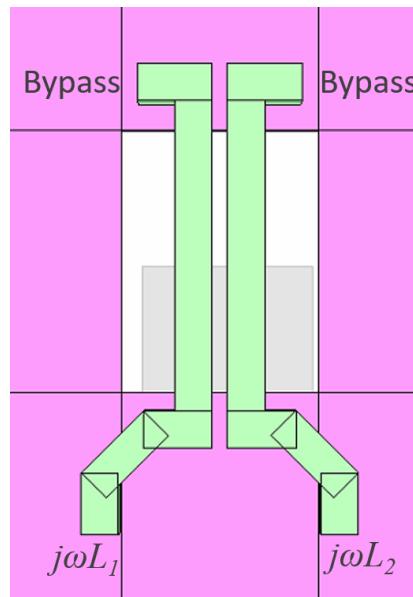

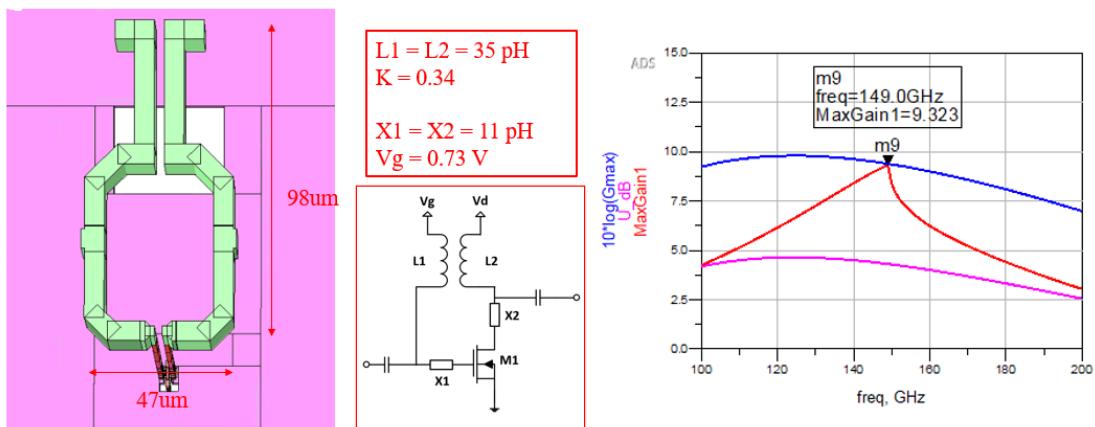

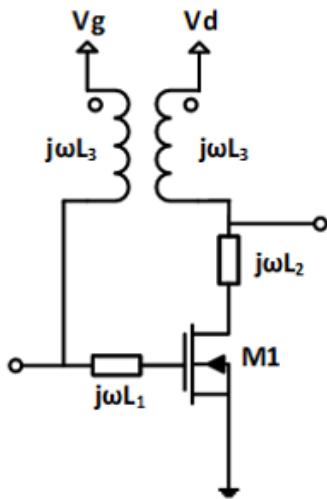

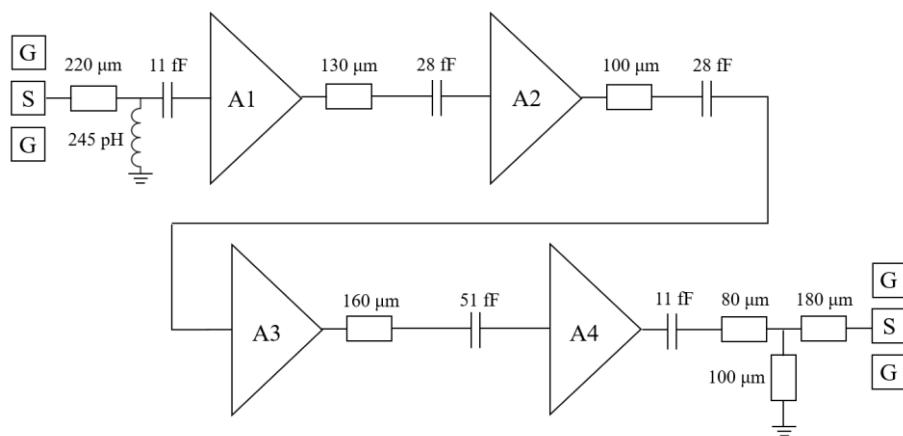

## 2.3 電路架構

本文採用四級的  $G_{max}$ -core 構建成 150 GHz 之低雜訊放大器，圖 2.12 為整體電路架構，其中 A1~A4 由各級之  $G_{max}$ -core 來組成，每一級如圖 2.13 所示，主要由三種 LLR 元件構成，分別為變壓器和兩個電感。為提升設計靈活性與增益，可藉由變壓器來給定不同的偏壓條件，可降低功耗、雜訊並且提升了增益，詳細之  $G_{max}$ -core 設計考參考 2.3.4 節。為了實踐出更低的雜訊，可藉由調整  $G_{max}$ -core 的三項 LLR 元件參數，在無限多種的組合中，找尋較相近的  $S_{opt}$  阻抗與  $S_{11}$  阻抗，同時兼顧雜訊匹配和共軛匹配，並且盡量減少匹配網路所造成損耗。

圖 2.12 提出之四級  $G_{\max}$ -core 電路架構

圖 2.13 單一級之 Y 嵌入網路

## 2.4 電路設計與流程

### 2.4.1 偏壓選擇

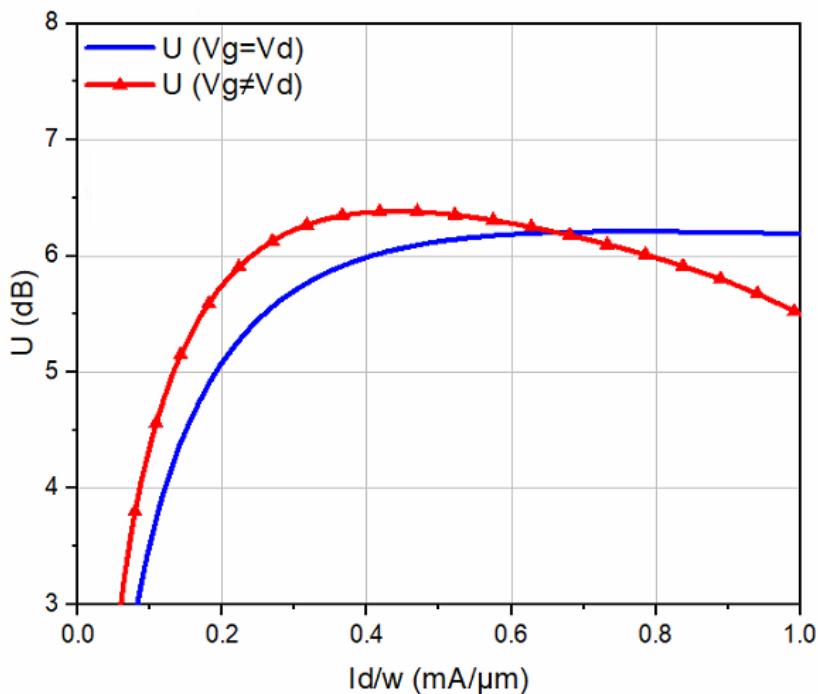

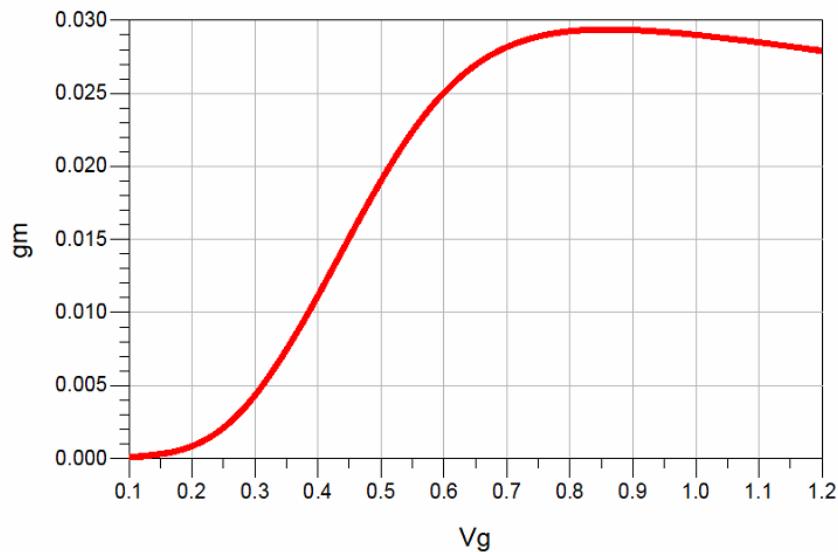

在設計  $G_{\max}$ -core 架構放大器時，偏壓條件對元件傳輸特性與  $U$  增益具有顯著影響。本節針對偏壓設定進行分析，並比較兩種情況，分別為閘極與汲極偏壓相同( $V_g = V_d$ )與不同( $V_g \neq V_d$ )的操作模式。透過模擬對比不同偏壓對於  $U$  值的影響，進一步推估其對整體  $G_{\max}$  達成的可行性與效率。

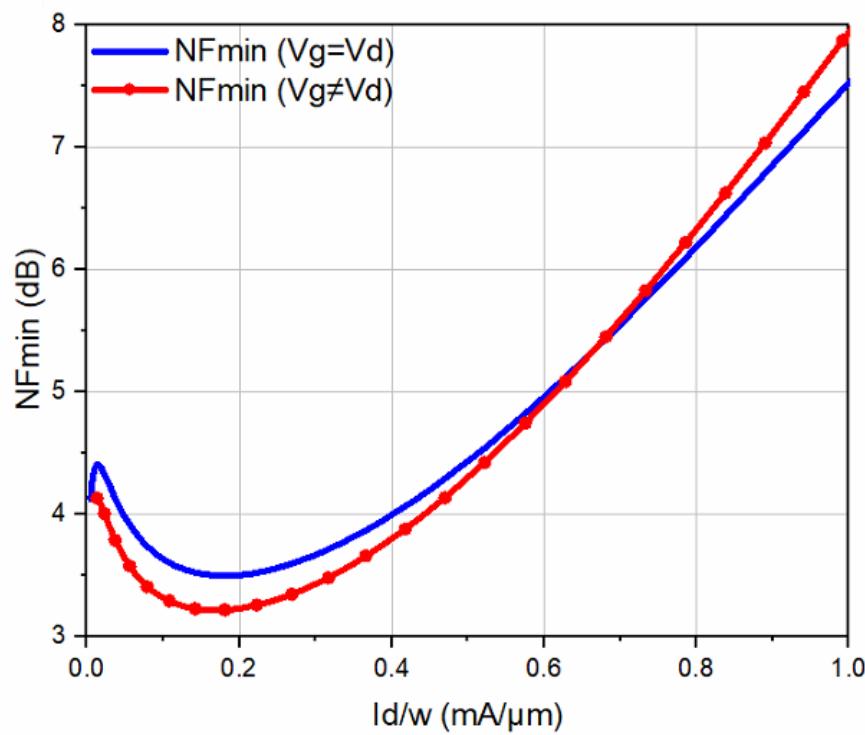

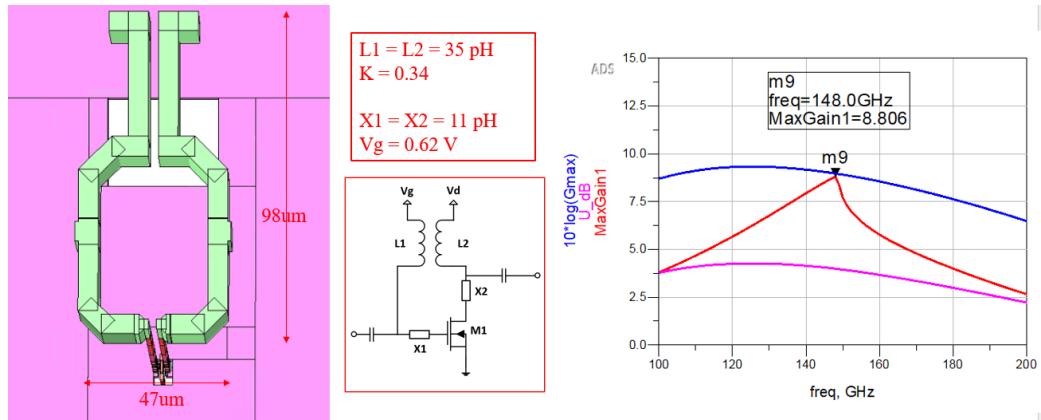

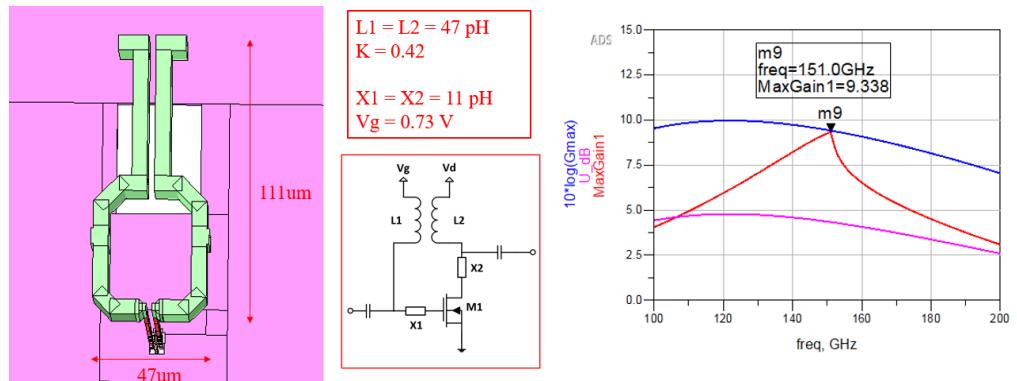

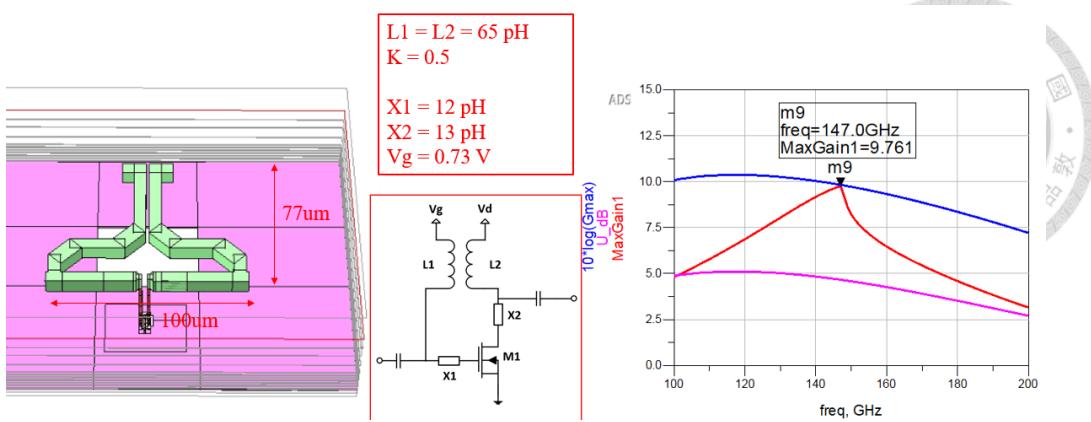

為了排除尺寸影響，利用歸一化電流密度  $Id/w$  來作為橫軸，如圖 2.14 錯誤！找不到參照來源。所示，模擬結果顯示在  $Id/w$  小於  $0.65 \text{ mA}/\mu\text{m}$  時，其  $U$  值為  $Vg \neq Vd$  的特性較佳，此分界點在  $Vd$  為  $0.9 \text{ V}$  時對應的  $Vg$  為  $0.88 \text{ V}$ ，偏壓點操作在 A 類。圖 2.15 所示為  $gm$  對  $Vg$  做掃描，太大的  $Vg$  不僅會使  $gm$  達到飽和，還會增加不必要的功率。在  $Vg \neq Vd$  的情況下，最佳  $U$  值為  $6.38 \text{ dB}$  操作在  $Id/w$  為  $0.44 \text{ mA}/\mu\text{m}$ ，其對應的  $Vg$  為  $0.75 \text{ V}$ 。

圖 2.14  $U$  vs.  $Id/w$  之模擬

圖 2.15  $V_{DS} = 0.9$  V 時之  $gm$  與  $V_g$

圖 2.16 比較了在相同或不同偏壓情況下對  $Id/w$  掃描的最小雜訊係數  $NF_{min}$ ，在  $Id/w$  為  $0.68$  mA/ $\mu m$  以前，其對應的  $V_g$  為小於  $0.9$  V 時，不同偏壓有較低的  $NF_{min}$ ，在  $V_g$  不等於  $V_d$  的情況下，最佳  $NF_{min}$  值為  $3.21$  dB 操作在  $Id/w$  為  $0.17$  mA/ $\mu m$ ，其對應的  $V_g$  為  $0.54$  V。表明了不同偏壓的設定可以優化雜訊性能，從而在設計低雜訊放大器中實現更高的效率。

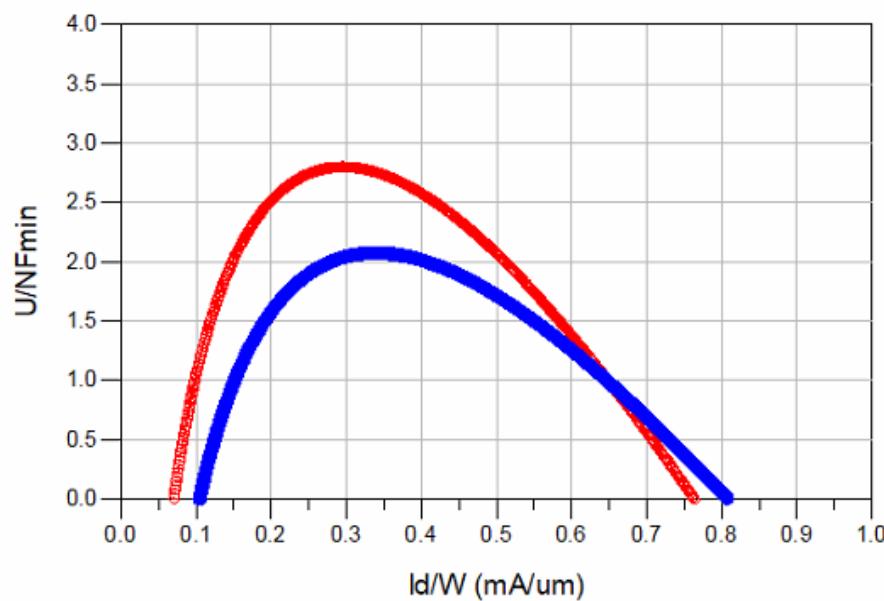

圖 2.17 比較了在  $U$  值與  $NF_{min}$  同時權衡之下的綜合性能，綜合性能值越高，代表著更能夠同時兼顧  $U$  值與  $NF_{min}$  的表現，在  $Id/w$  為  $0.64$  mA/ $\mu m$  以前，不同偏壓的特性在表現上較佳。根據上述原因，可以統整出使用變壓器進行偏壓分離能夠實現更好的性能。

根據規格要求，為了能夠希望有  $30$  dB 的增益，本論文不希望第一級只為了達到最低的  $NF_{min}$  而使增益過低，因此，第一級操作在圖 2.17 之峰值點上， $Id/w$  為  $0.29$  mA/ $\mu m$  其對應的  $V_g$  為  $0.62$  V，能夠同時兼顧  $U$  與  $NF_{min}$  值。而二、三與四級偏壓選擇  $U$  值較高且  $gm$  佳的  $0.42$  mA/ $\mu m$ ，對應其  $V_g$  為  $0.73$  V。這樣的設計確保了整體增益和雜訊之間的平衡，滿足系統的性能需求。

圖 2.16  $NF_{min}$  vs.  $Id/w$  之模擬

圖 2.17  $U/NF_{min}$  vs.  $Id/w$  之模擬

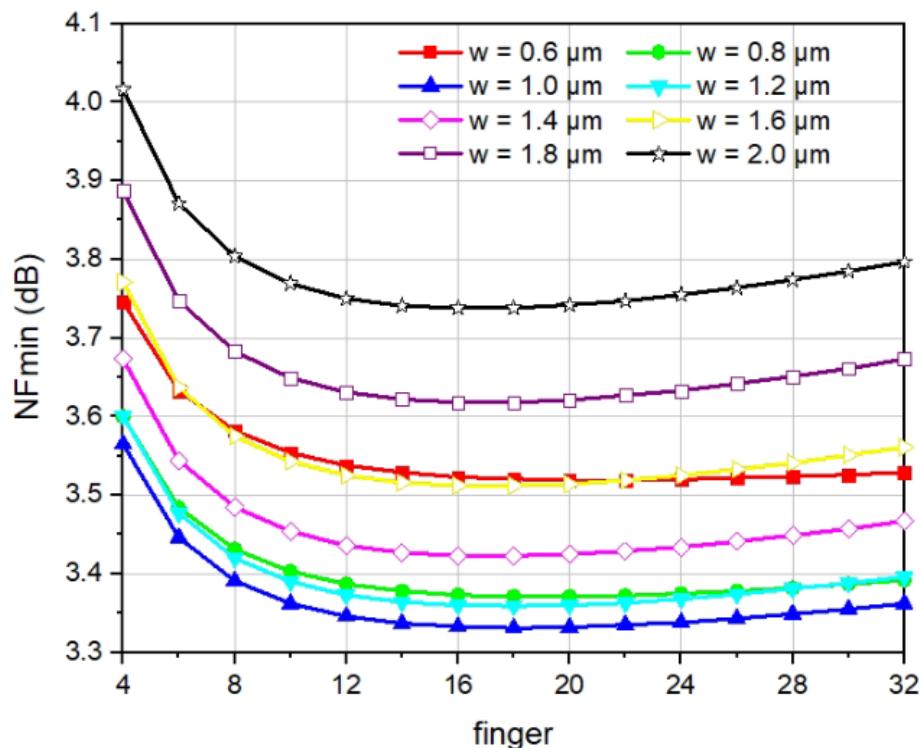

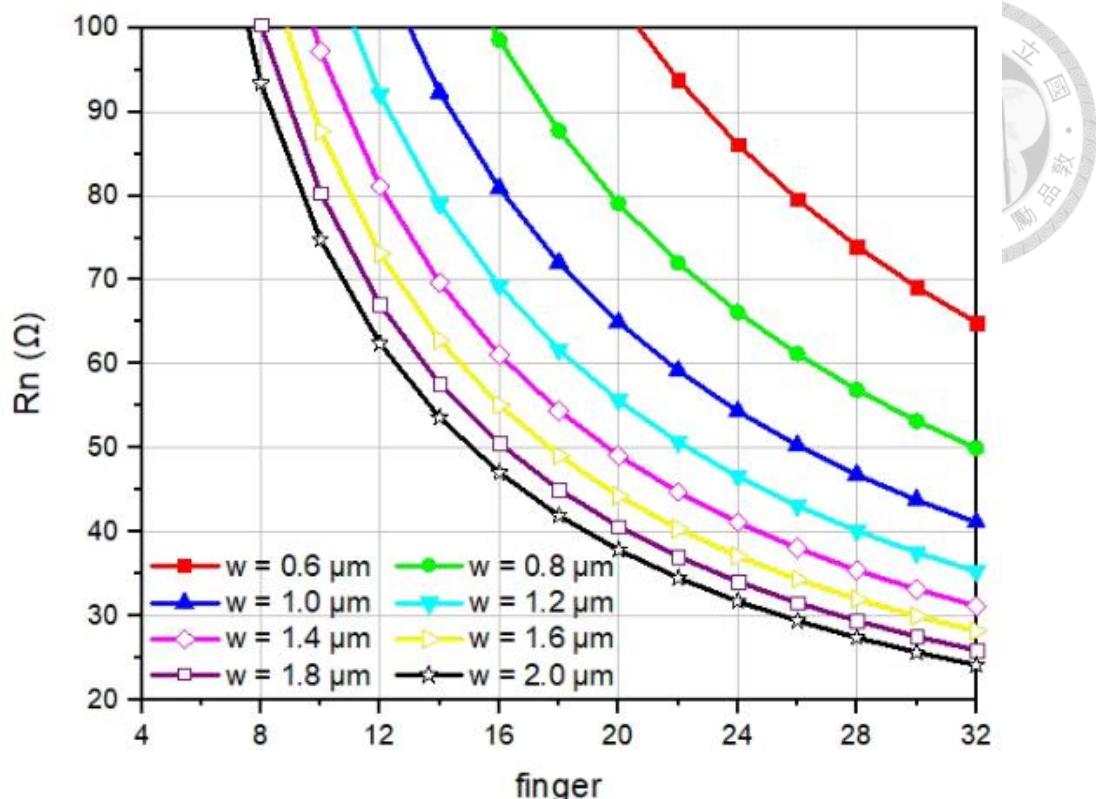

### 2.4.2 電晶體尺寸選擇

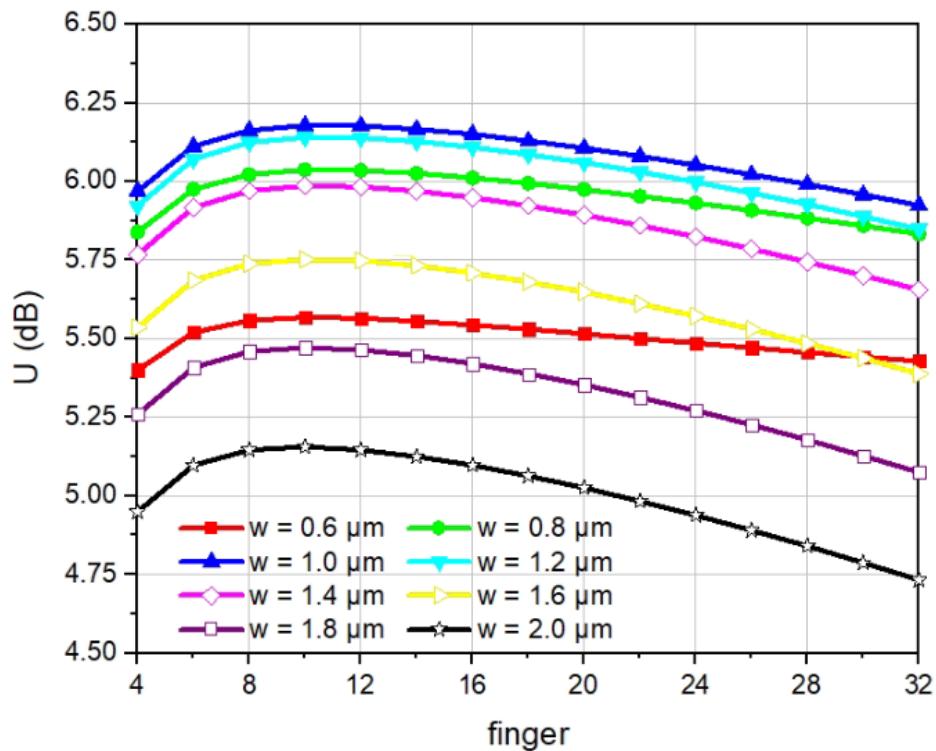

電晶體尺寸上的選擇，會先利用  $U$  和  $NF_{min}$  來對 finger 作圖，並且掃描了不同的 width 值從  $0.6 \mu m$  至  $2 \mu m$ 。可由圖 2.18 得知  $U$  值在固定 width 時，finger 數增加至約為 10 左右，更長的總寬度造成的寄生值會超過並聯時的閘級電阻變小的影響而使  $U$  值更低，其 width 在  $1 \mu m$  時有最好的表現。圖 2.19 得知  $NF_{min}$  其 width 和 finger，同樣都為  $1 \mu m$  時整體皆有較佳的表現。

接下來考慮  $R_n$ ，圖 2.20 掃描了不同的 width 和 finger 數對  $R_n$  的影響， $R_n$  主要影響整體電路的雜訊，可參考(2.18)式， $G_s$  為當雜訊匹配時的源阻抗、 $Y_s$  為源導納、 $Y_{n_{opt}}$  為匹配的最佳源導納。其意味著當電路在雜訊匹配時， $Y_s - Y_{n_{opt}} = 0$ ，整體 NF 會等於  $NF_{min}$ ，但若不匹配，隨著  $R_n$  的值越大，整體 NF 也會顯著的增加。綜合來說 width 和 finger 數越大， $R_n$  會隨之下降，然而，隨著 finger 數的增加， $U$  值會降低， $NF_{min}$  也會略微增加。

$$NF = NF_{min} + \left( \frac{R_n}{G_s} \right) \times |Y_s - Y_{n_{opt}}|^2 \quad (2.18)$$

綜合以上結論，本文選出合適的尺寸來比較其 MSG/MAG，如圖 2.21 所示。在毫米波的設計之中，由於需要考慮到實際元件所帶來的損耗，這些損耗會提高其穩定度，因此通常會將轉折頻率點略微超過操作頻率，因此，本文選擇  $1\mu m$  的 width 和 20 的 finger 數來做為電晶體尺寸。

圖 2.18  $U$  vs. width 與 finger

圖 2.19  $NF_{min}$  vs. width 與 finger

圖 2.20 Rn 對 width 與 finger 作圖

圖 2.21 掃描 width 與 finger 之 MAG/MSG

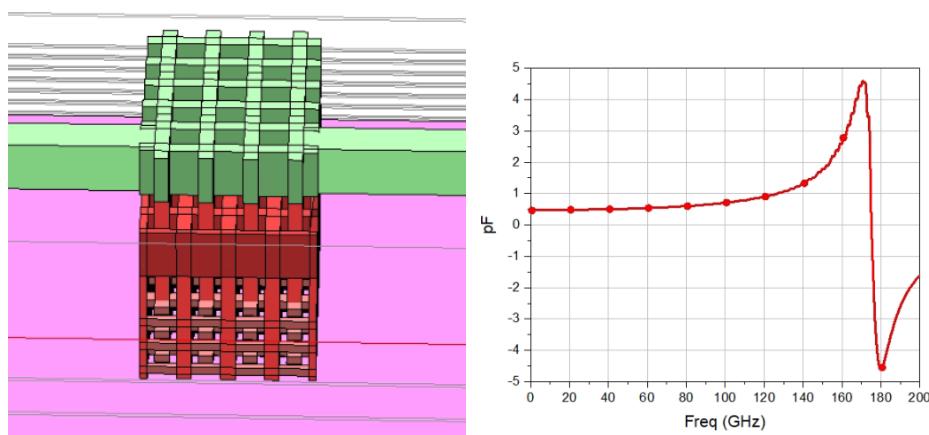

### 2.4.3 電晶體走線影響

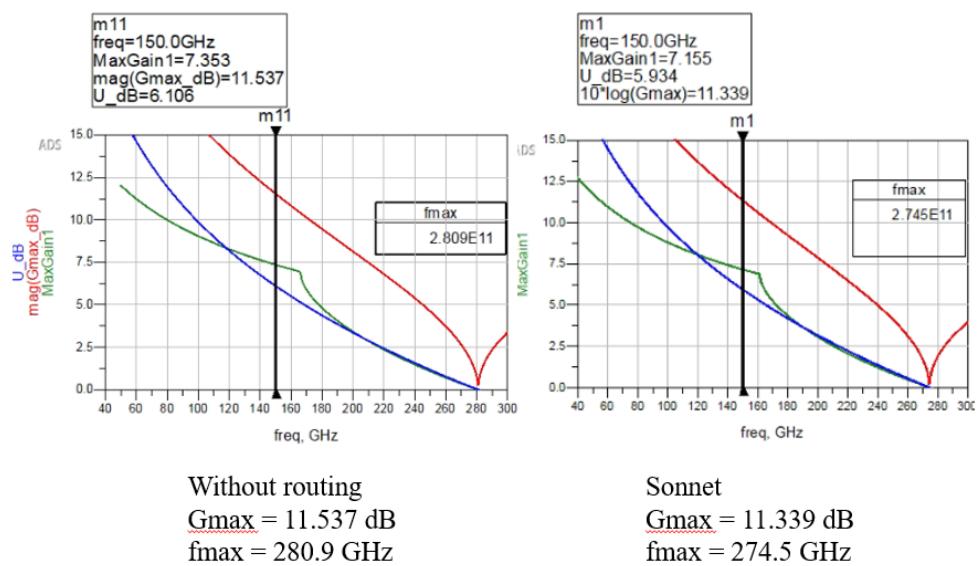

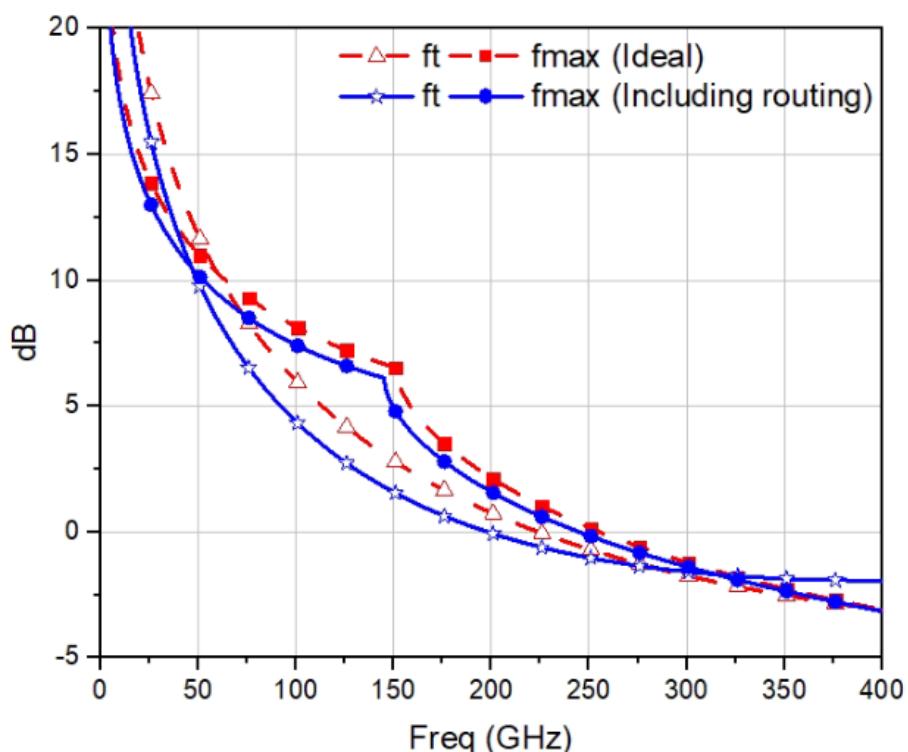

在 Sub-THz 設計中，電晶體與金屬層之間的連結路徑會顯著的影響元件的高頻性能，特別在於高於 100 GHz 頻率下，金屬走線的寄生效應影響不能忽略其影響，本文額外萃取出電晶體從 GDSB 端拉出來至 M9 的走線，如圖 2.22 所示，因 TSMC PDK 的電晶體模型只確認 30 GHz 內的頻率響應，而從電晶體端口拉出至 M9 的寄生電感值會隨頻率升高而增加，這些皆為必要走線且無法忽略的寄生值。藉由 EM 模擬其  $f_{max}$ ，圖 2.23 表明原本未包含走線的  $f_{max}$  為 280.9 GHz，受走線的寄生電感和電容影響降為 274.5 GHz，每一級的  $G_{max}$  則約降 0.2 dB。

圖 2.22 電晶體走線佈局

圖 2.23 電晶體走線之  $G_{max}$  與  $f_{max}$  影響

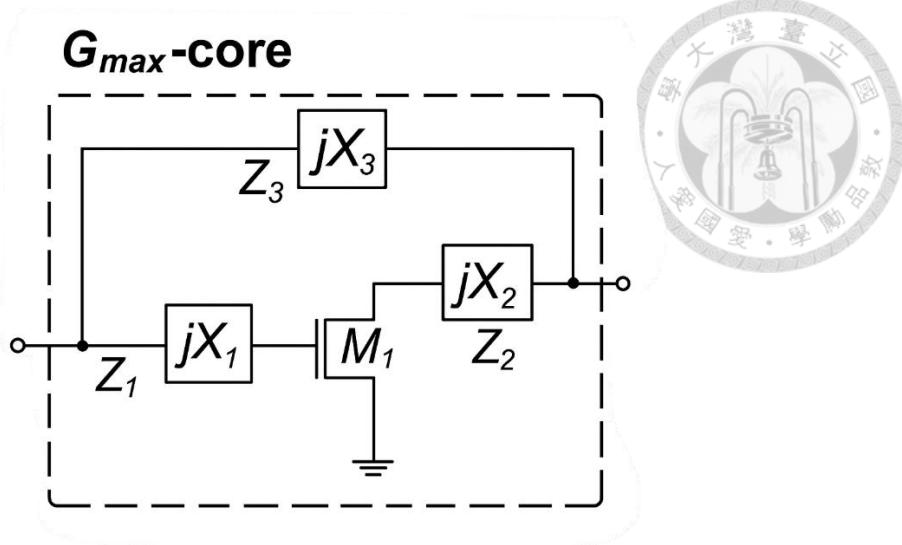

#### 2.4.4 $G_{\max}$ -core 設計

傳統中  $G_{\max}$ -core 為圖 2.24 (a)，僅同時向閘極和漏極端施加一偏壓，這降低了佈局和面積的複雜性，然而於 2.3.1 節中證明了會降低其增益並且有較高的雜訊。所提出的  $G_{\max}$ -core 架構如圖 2.24 (b) 所示，每一級都利用變壓器來取代傳統的  $jX_3$  元件，構成的嵌入網路便能將不同的偏壓同時施加到閘極和漏極端。其小訊號模型可見圖 2.24 (c)，M 表示為變壓器之互感，若互感值過小，訊號容易直接經由  $j\omega M$  直接短路到地造成增益下降。

圖 2.24 (a)傳統 LLR 嵌入網路 (b)提出基於變壓器之嵌入網路 (c)變壓器嵌入網路之等校模型

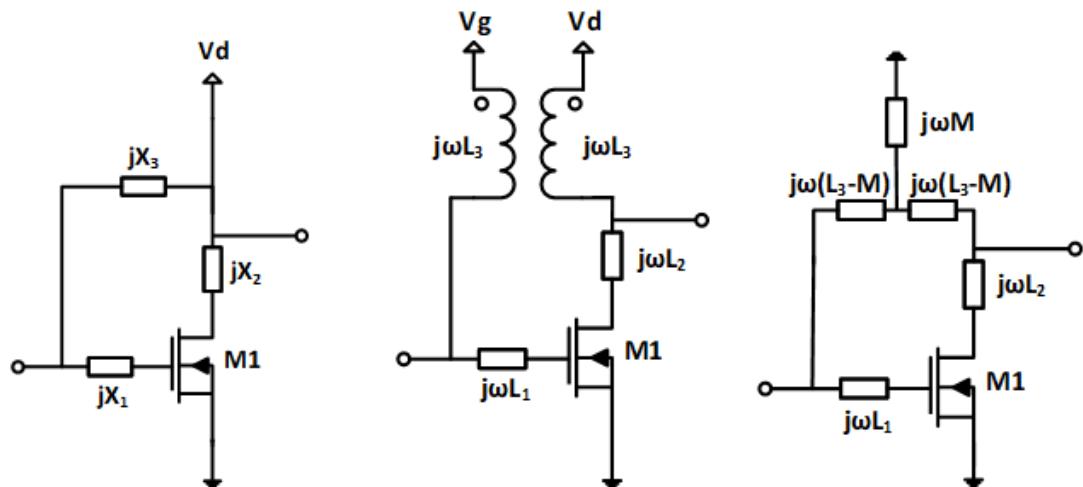

由[37][38]可得知，無損的傳輸線參照圖 2.25 可視為一電感  $L_M$  和  $S_1$ 、 $S_2$  的並聯， $L_M$  值如(2.19)所示， $Z_0$ 為傳輸線的特性阻抗， $l$ 為傳輸線的長度。在短輸線的前提下( $\beta l = \frac{2\pi l}{\lambda} \approx 0$ )， $S_1$ 與  $S_2$  之 $\tan(\beta l) \approx \sin(\beta l)$ 相消後為零，故可以忽略不計。

$$\omega L_M = Z_0 \sin(\beta l) \quad (2.19)$$

因此傳輸線其 Y 參數可表示為

$$\begin{bmatrix} Y_{11}^{Li} & Y_{12}^{Li} \\ Y_{21}^{Li} & Y_{22}^{Li} \end{bmatrix} = \begin{bmatrix} 1 & -1 \\ j\omega L_i & j\omega L_i \\ -1 & 1 \\ j\omega L_i & j\omega L_i \end{bmatrix} \quad (2.20)$$

圖 2.25 傳輸線與其等效模型

而變壓器的 Y 參數可從圖 2.24 (c)表示為

$$\begin{bmatrix} Y_{11}^{TF} & Y_{12}^{TF} \\ Y_{21}^{TF} & Y_{22}^{TF} \end{bmatrix} = \begin{bmatrix} \frac{-j\omega L_3}{\omega^2(L_3^2 - M^2)} & \frac{j\omega M}{\omega^2(L_3^2 - M^2)} \\ \frac{j\omega M}{\omega^2(L_3^2 - M^2)} & \frac{-j\omega L_3}{\omega^2(L_3^2 - M^2)} \end{bmatrix}. \quad (2.21)$$

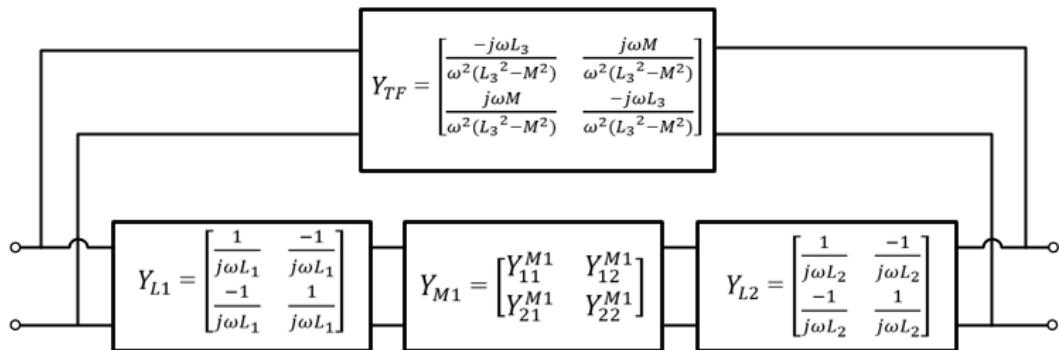

最終由上述推出其整體的 Y 參數模型，整體 Y 參數會由變壓器  $Y_{TF}$  並聯傳輸線  $Y_{L1}$ 、電晶體  $Y_{M1}$  及傳輸線  $Y_{L2}$  構成，如圖 2.26 所示，故可求出其整體 Y 參數， $Y_{12}^{eq}$  與  $Y_{21}^{eq}$  為已知，若能夠滿足(2.8)(2.9)式，則可達成  $G_{max}$ 。

$$Y_{12}^{eq} = \frac{Y_{12}^{L1} Y_{12}^{M1} Y_{12}^{L2}}{(Y_{22}^{L1} + Y_{11}^{M1})(Y_{22}^{M1} + Y_{11}^{L2}) - (Y_{12}^{M1} Y_{21}^{M1})} + Y_{12}^{TF} \quad (2.22)$$

$$Y_{21}^{eq} = \frac{Y_{21}^{L1} Y_{21}^{M1} Y_{21}^{L2}}{(Y_{22}^{L1} + Y_{11}^{M1})(Y_{22}^{M1} + Y_{11}^{L2}) - (Y_{12}^{M1} Y_{21}^{M1})} + Y_{21}^{TF} \quad (2.23)$$

圖 2.26 提出基於變壓器嵌入網路之 Y 參數模型

## 2.4.5 變壓器設計

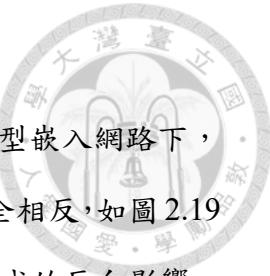

首先在嵌入網路中使用變壓器而不使用電容的原因在於 Y 型嵌入網路下，電容器在增益平面上的移動軌跡與達成  $G_{max}$ -core 之路徑恰好完全相反，如圖 2.19 所示，若使用電容器，需要額外的 LLR 元件來補償電容器所造成的反向影響，從而導致不必要的損耗與增益下降，這也為傳統上通常只使用電感來代替電容的主要原因，而使用所提出的變壓器能夠更有效的達成  $G_{max}$ -core 並且能夠將閘級和漏級偏壓分離。

圖 2.27 變壓器嵌入網路於增益平面上之移動軌跡

本文採用邊緣耦合的方式來構成變壓器，主要考量的原因是因為變壓器的極性，只有當極性在同一側時，Y 嵌入網路才可以等效為一個電感，如錯誤! 找不到參照來源。 (b)所示。若兩邊的極性相反， $Y_{21}$  會與原始相位相差 180 度，使增益平面的軌跡運動類似於電容，這會使要達到  $G_{max}$  更加困難。雖然垂直耦合比起邊緣耦合來說能提供更高的 K 值，但垂直耦合中正確的極性必須在佈局中交叉，如錯誤! 找不到參照來源。所示。這種額外的交叉會導致上下之間電感值的差異增加，不僅對設計帶來限制，還會顯著影響其互易性。

圖 2.28 垂直耦合之變壓器

相比之下，邊緣耦合雖然耦合係數較低，但在佈局之中能夠更簡單去實現，如圖 2.29 所示。然而當耦合係數較小時，圖 2.24 (c) 中  $j\omega M$  的值較小，信號會較容易短路到地，正回授的信號連帶減少，導致增益下降。此外，當耦合係數趨近於零時， $G_{max-core}$  將逐漸成唯一解，因為  $L_3$  會與  $L_1$  和  $L_2$  一起等效為新的  $L'_1$  和  $L'_2$ ，這將使設計過程更加困難。因此為了提高耦合係數，兩側之間的距離需被最小化，最小距離受 DRC 所限制。

圖 2.29 邊緣耦合之變壓器

採用變壓器的  $G_{\max}$ -core 設計如圖 2.30 至圖 2.33 所示，理論上能有無限多種組合，本文將每一級都偏在 150 GHz 左右，缺點是犧牲了頻寬，但是能夠帶來高的增益，若輸入輸出的匹配網路估為 2 dB 的損耗，級間損耗也為 2 dB，那麼在  $G_{\max}$ -core 增益一級約為 9 dB 的前提下，估計四級至少能夠達到有 26 dB 的增益。

圖 2.30 第一級  $G_{\max}$ -core

圖 2.31 第二級  $G_{\max}$ -core

圖 2.32 第三級  $G_{\max}$ -core

圖 2.33 第四級  $G_{\max}$ -core

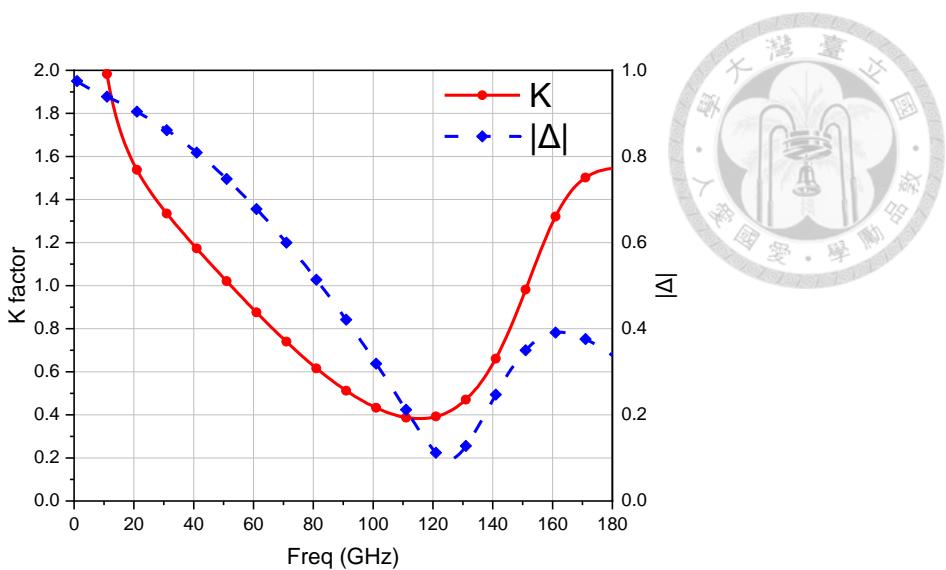

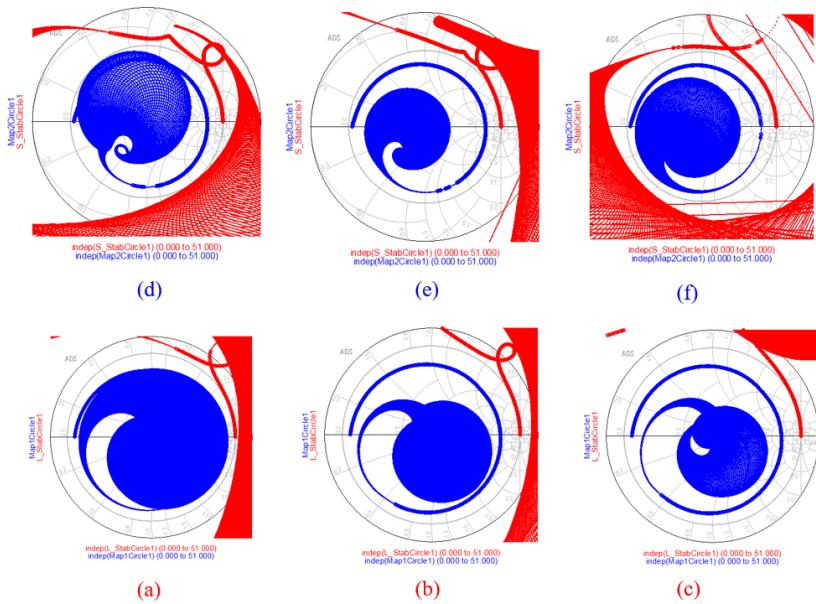

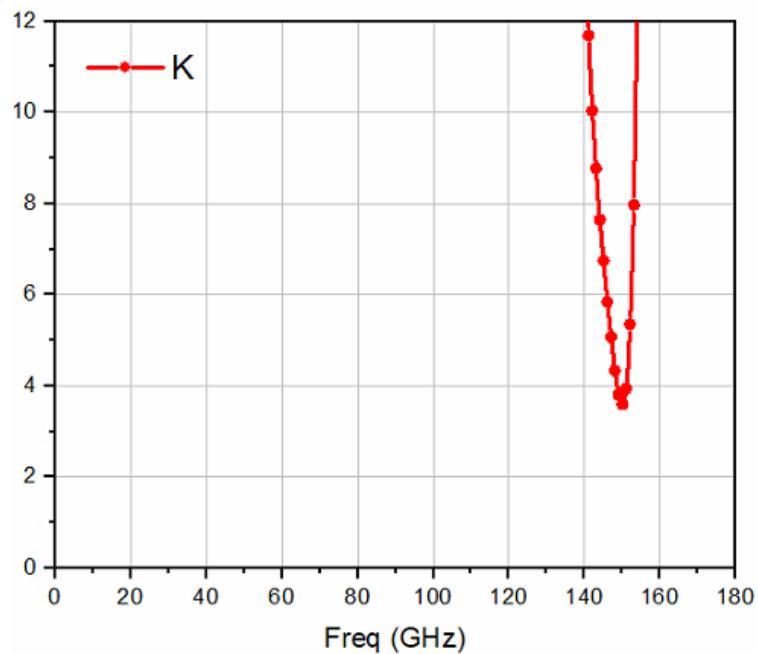

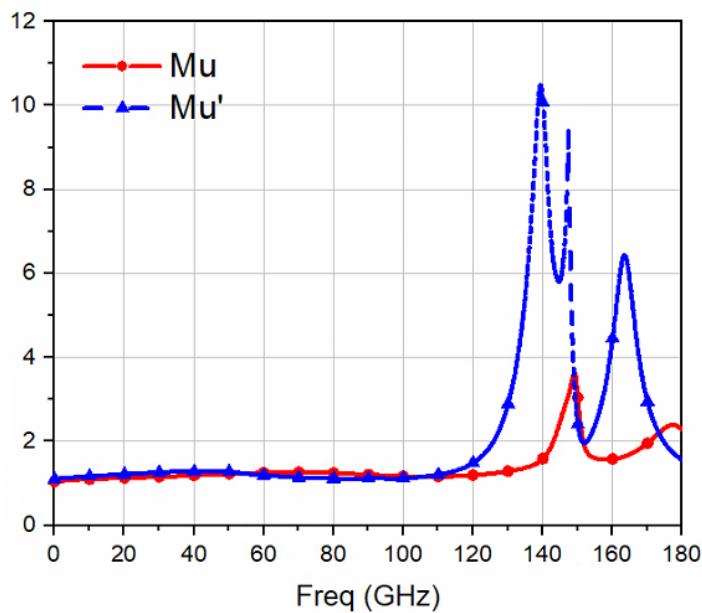

#### 2.4.6 穩定度

根據單一級  $G_{\max}$ -core 之模擬結果，其操作頻率在 150 GHz 附近的  $K$  值約略等於 1，位於臨界穩定的邊緣，如圖 2.34 所示， $K$  值在 50~150 GHz 的頻率區間內皆低於 1， $|\Delta|$  值則隨頻率呈現下降趨勢，顯示該頻段內穩定性仍具一定風險。

然而，實際應用中每一級  $G_{\max}$ -core 會搭配匹配網路，這些匹配網路用來進行阻抗匹配並且穩定性會提高，因此，即使單一級可能不穩定，經過整體的匹配網路後系統穩定性仍可維持。為了驗證級間的影響是否導致整體穩定性，本文也進行了級間的穩定性測試，如圖 2.35 所示，分別針對各級之間來觀察 Smith 圖是否重疊，其結果如圖 2.36 所示，各級之間無相交代表在操作頻率內皆為穩定狀態。

圖 2.34 單一級之穩定度

圖 2.35 級間穩定測試

圖 2.36 級間穩定皆無相交

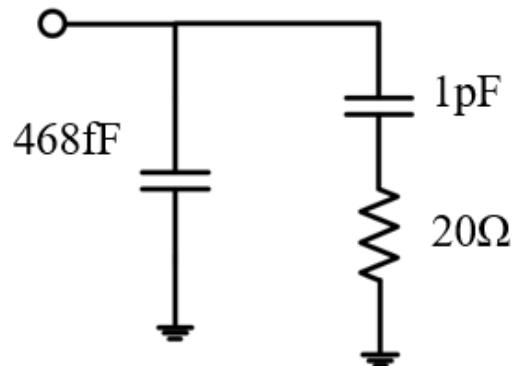

#### 2.4.7 Bypass 電路

圖 2.37 所示，本文設計之 bypass 電路採用雙路徑的結構，電容架構參考文獻[39]，其特點是能夠在高頻下有較高的自震頻率，透過金屬堆疊於各層間均勻分佈，滿足製程的金屬密度與 DRC 規範，並能夠穩定偏壓網路。第一路徑由  $468\text{ fF}$  的金屬堆疊電容所構成，如圖 2.38 所示，使操作頻率內經過電容為短路，第二路徑由  $1\text{ pF}$  的金屬堆疊電容與  $20\Omega$  的電阻構成，圖 2.39 所示，確保低頻也能夠穩定。設計上的考量分別為第一路在頻帶內隔離度- $20\text{dB}$  以下，第二路則考慮低頻時的阻抗響應，最終結果如圖 2.40 所示。

圖 2.37 兩路之 Bypass 電路

圖 2.38 第一路電容

圖 2.39 第二路電容

圖 2.40 隔離度模擬

## 2.4.8 電路佈局與 Post-sim 結果

本文採用四級的  $G_{\max}$ -core 構建成 150 GHz 之低雜訊放大器，使用 TSMC 40 nm 製程，考慮製程模型、金屬走線與匹配網路等非理想因素。各級的放大器 A1~A4 均採用如圖 2.411 所示之單一級  $G_{\max}$ -core，由兩電感、變壓器和電晶體 M1 構成。整體系統配置如圖 2.42 所示，可藉由調整  $G_{\max}$ -core 在無限多種的組合，找尋較相近的  $S_{opt}$  阻抗與  $S_{11}$  阻抗，使得能同時兼顧雜訊匹配和共軛匹配，盡量減少匹配網路所造成的損耗。

圖 2.41 單一級之 Y 嵌入網路

圖 2.42 提出之四級  $G_{\max}$ -core 電路架構

級間匹配主要使用一傳輸線和一電容同時作為匹配和 DC Block，而由於為了滿足  $G_{\max}$ -core 條件，會將每一級操作頻率的穩定度 K 值剛好設在 1，剛好介

在有可能不穩定的臨界值，因此整體穩定度與級間穩定度需要特別注意且加以考量，圖 2.43 為模擬之整體 K 值，全頻段皆大於 1。圖 2.44 為其  $\mu_u$  及  $\mu'_u$ ，全頻段皆大於 1，因此介在無條件穩定。

圖 2.43 整體穩定度之 K 值

圖 2.44 整體穩定度之  $\mu_u$  及  $\mu'_u$

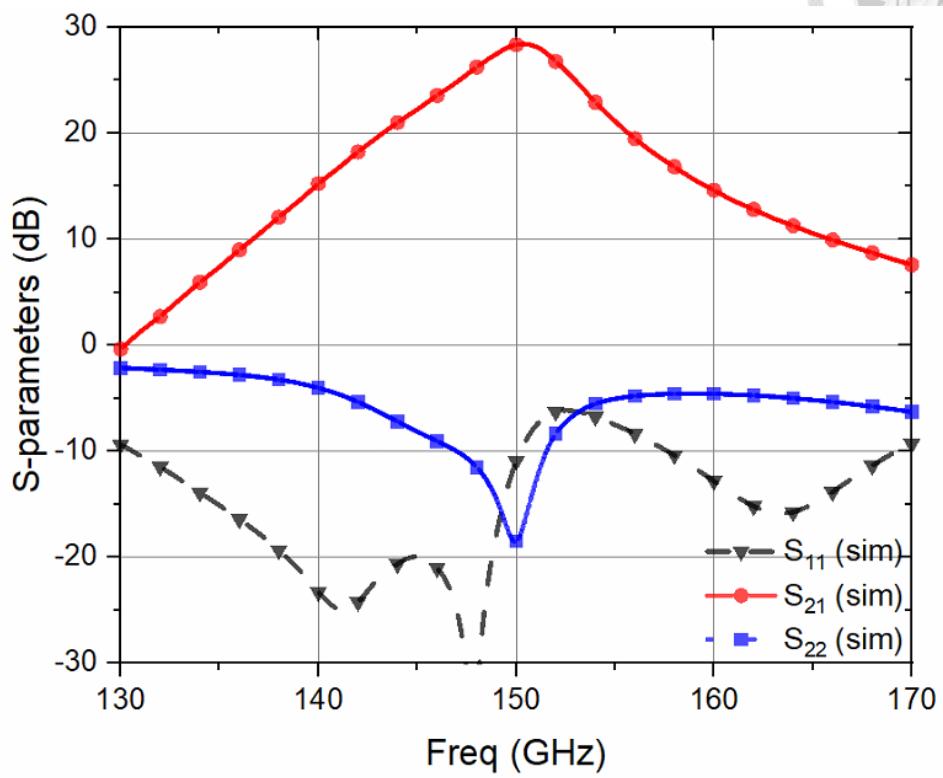

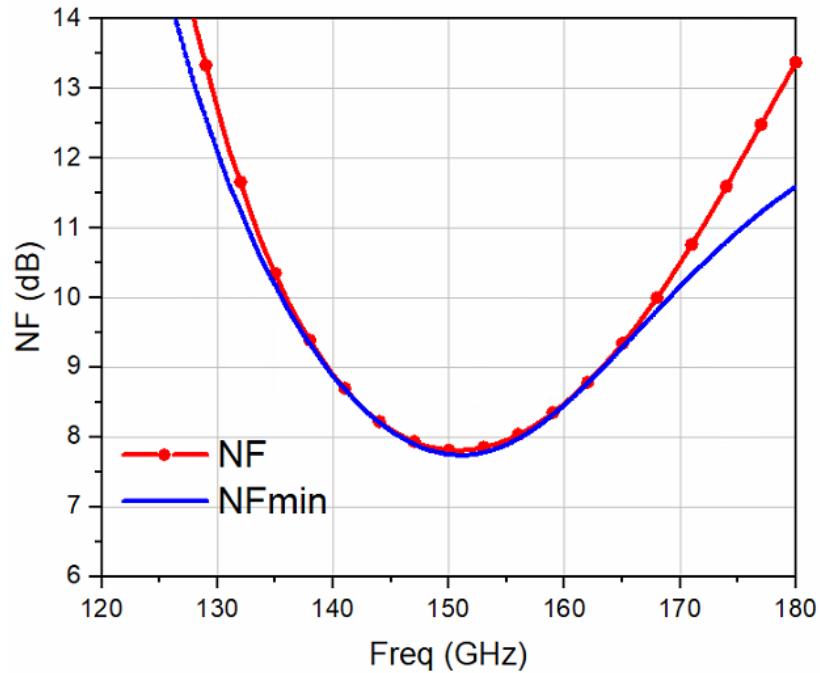

最終 S 參數的模擬結果如圖 2.45 所示，其峰值增益在 150 GHz 為 28.2 dB，3 dB 頻寬從 147.4 GHz 至 152.8 GHz。圖 2.46 為其 NF 與 NFmin，最佳雜

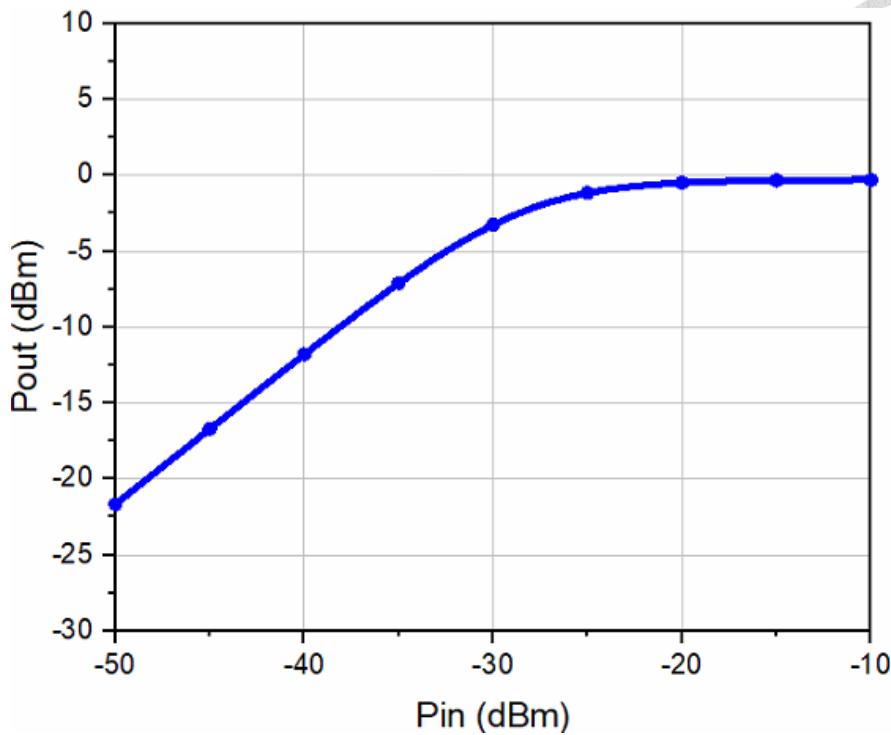

訊點為 150.4 GHz，其對應之 NF 為 7.81 dB， $NF_{min}$  為 7.75 dB。P1dB 結果如圖 2.47 所示，在 150 GHz 時 OP1dB 為 -4 dBm。

圖 2.45 S 參數之模擬

圖 2.46 NF 與  $NF_{min}$  之模擬

圖 2.47  $P_{1dB}$  之模擬

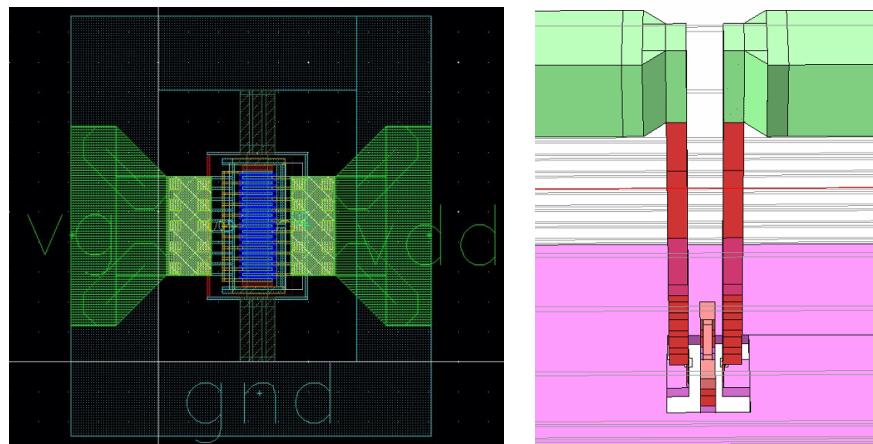

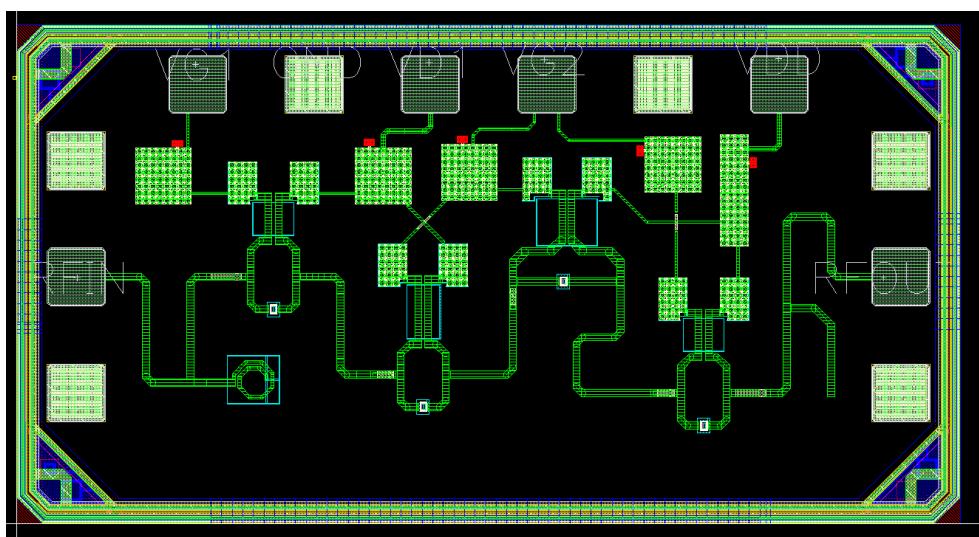

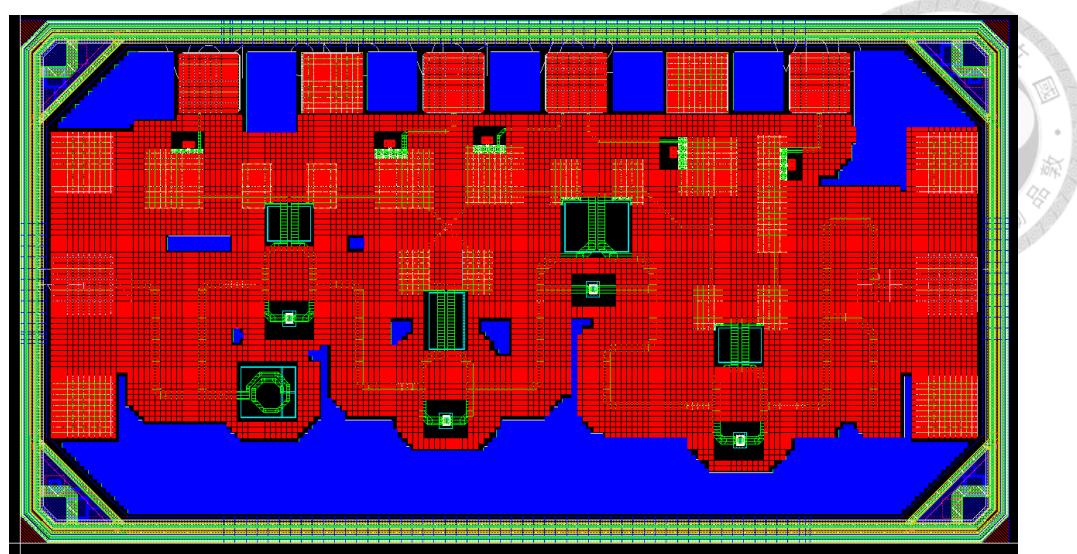

圖 2.48 及圖 2.49 為本文低雜訊放大器之晶片佈局，使用 TSMC 40 nm 1P9M 製程，無厚金屬造成被動元件損耗較大，本文並利用頂層金屬 M9 進行主要射頻訊號走線與輸入輸出 pad 連接，接地層使用 M1 及 M2 來滿足 DRC 密度限制，每個 RF 及 DC pad 的間距為  $100 \mu\text{m}$ ，整體晶片大小為  $811 \times 429 \mu\text{m}^2$ 。

圖 2.48 LNA 晶片佈局不含 GND 及 Dummy

圖 2.49 LNA 完整晶片佈局

## 2.5 量測與結果

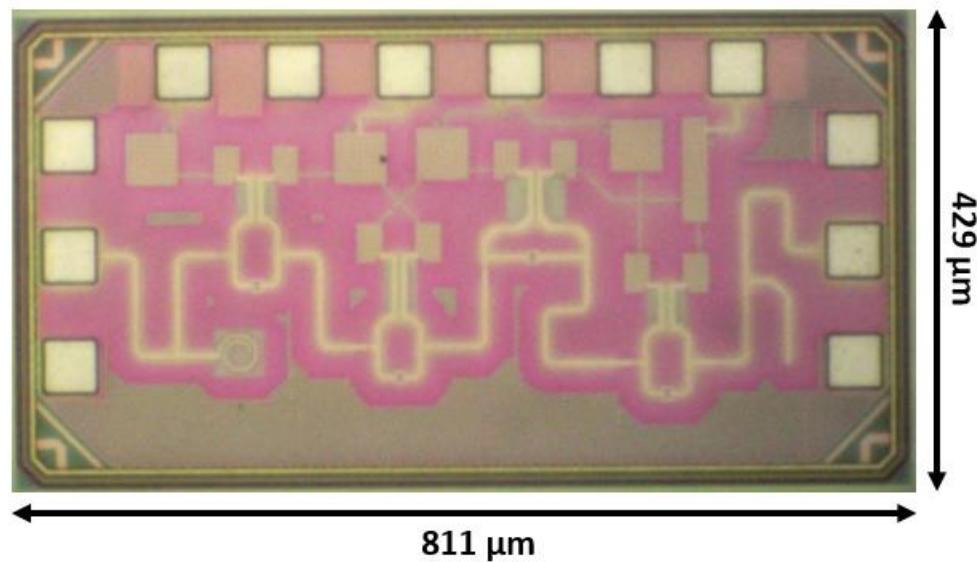

圖 2.50 LNA 晶片之顯微鏡圖

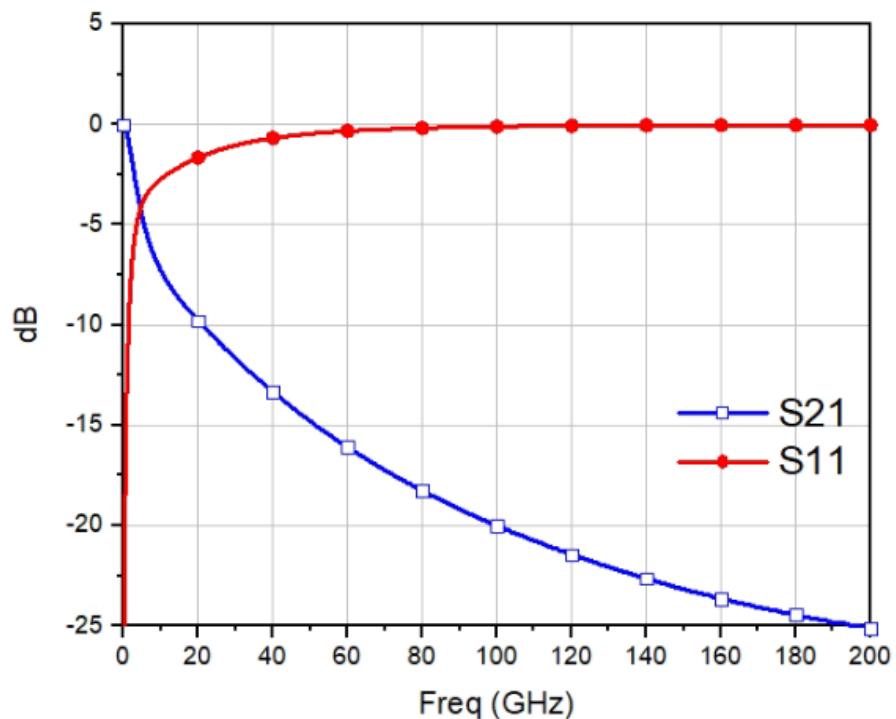

### 2.5.1 S 參數量測

所提出的 LNA 晶片圖如圖 2.50 所示，晶片面積包含 RF 和 DC pad 為  $811 \times 429 \mu\text{m}^2$ ，利用鎊線連接 DC pad 至 PCB 板，GSG 之 RF pad 與 DC pad 間距皆為  $100 \mu\text{m}$ ，在  $0.9\text{V}$  之  $V_{DD}$  電壓下的總功率消耗為  $27.1 \text{ mW}$ 。

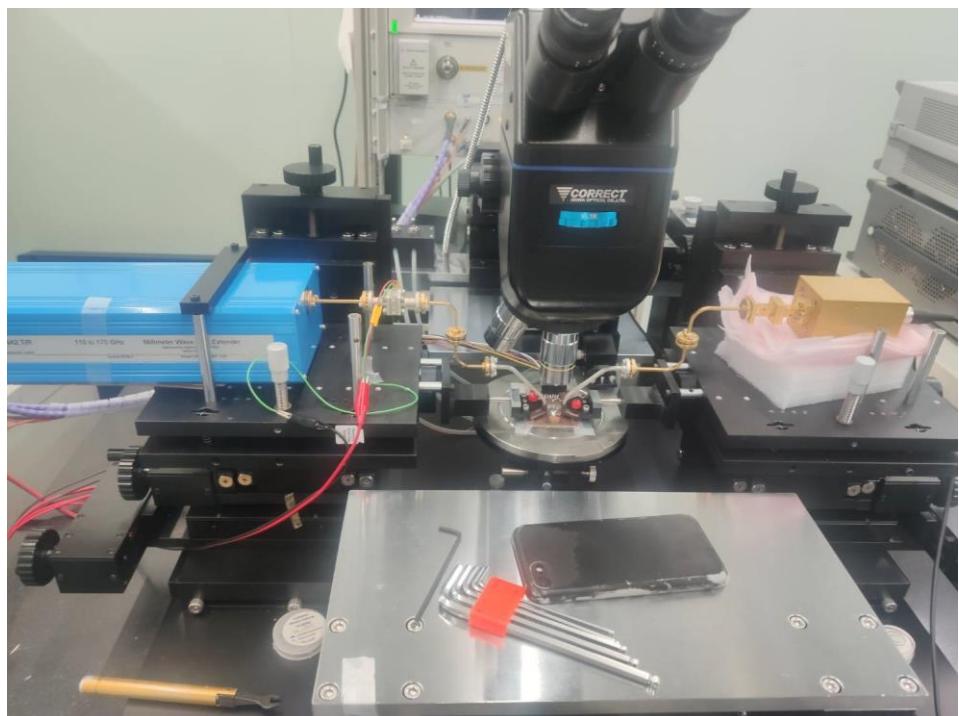

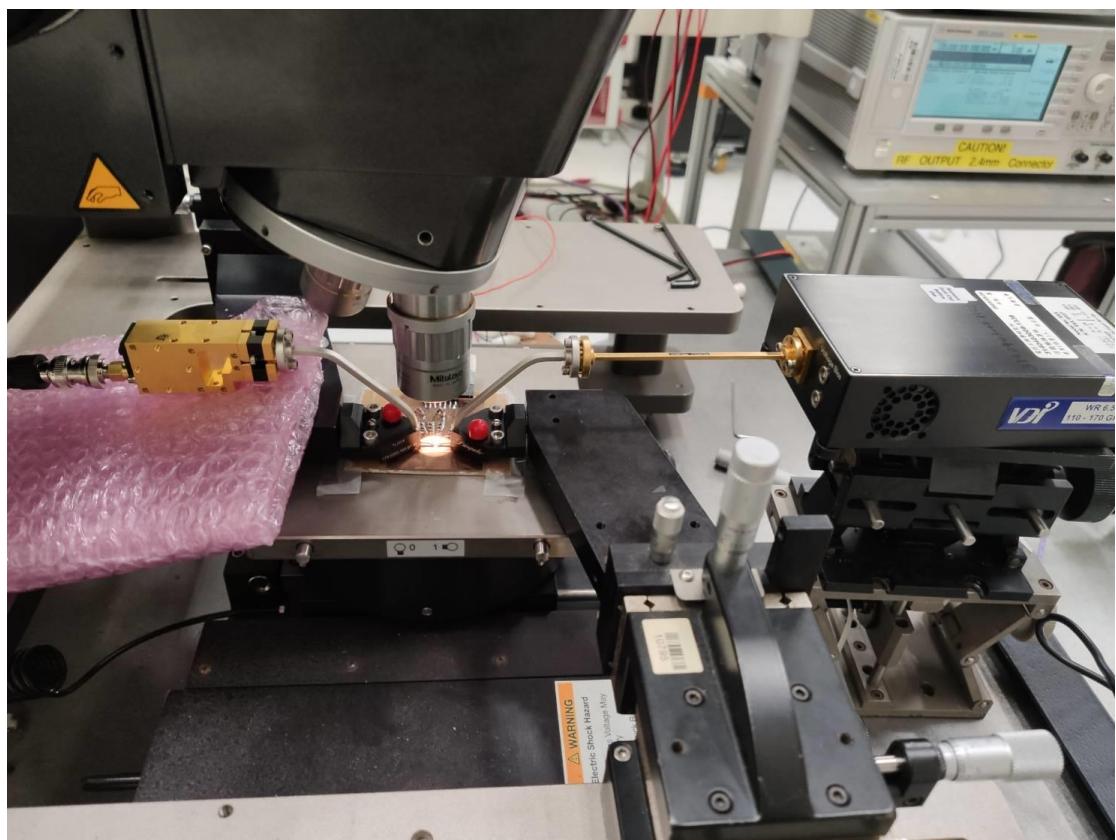

S 參數量測於台灣半導體研究中心(Taiwan Semiconductor Research Institute, TSRI)協助量測，儀器架設如圖 2.51 所示，使用向量網路分析儀(Keysight PNA-X N5242B)、毫米波控制器(Agilent N5262A)和 G-band 頻率延伸模組(OML V05VNA2-T/R)，能夠將 S 參數量測頻率延伸至 140 至 220 GHz。

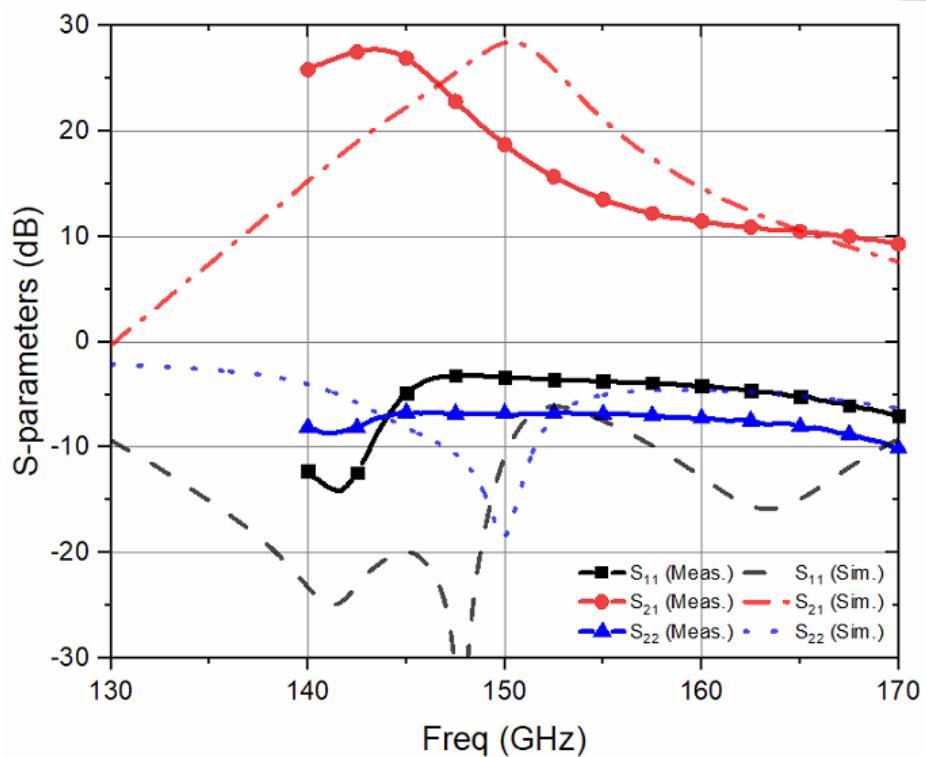

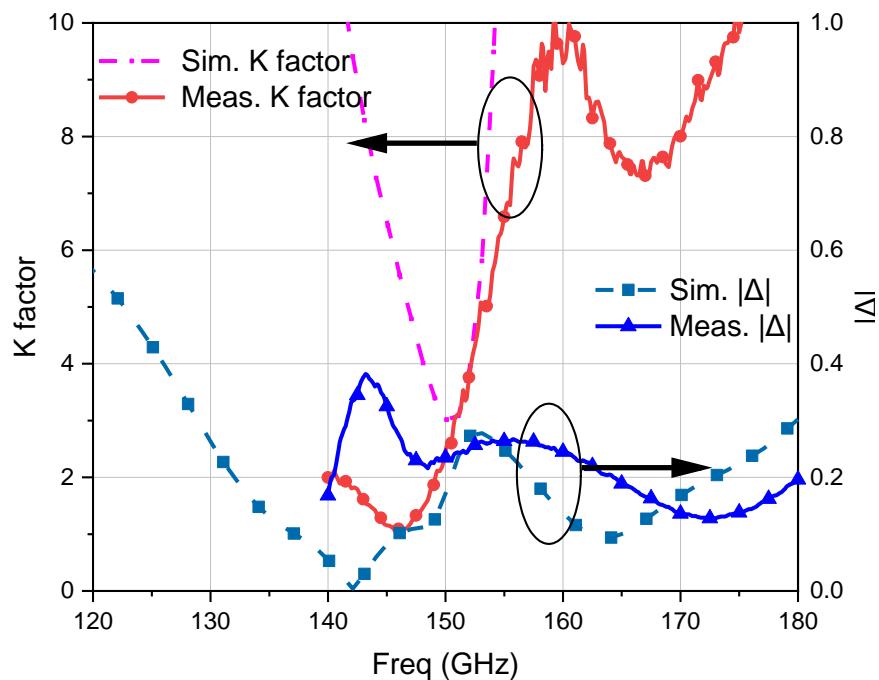

圖 2.52 為模擬與量測的 S 參數，量測在 143.5 GHz 達到 27.7 dB 的峰值增益，3 dB 頻寬為 7.5 GHz。模擬則是在 150 GHz 達到 28.2 dB 之峰值增益，量測比模擬的頻率低了 6.5 GHz，其原因可分為兩種，其一為 TSMC 的電晶體模型只針對小於 30 GHz 的頻率，對於高頻模型並不準確，其二為介質的介電常數會有誤查，這些都可能為造成頻偏的原因。圖 2.53 表示了量測中全頻段穩定因子 k 值  $> 1$  和  $|\Delta| = |S_{11}S_{22} - S_{12}S_{21}| < 1$ ，介於無條件穩定。

圖 2.51 S 參數之量測架設

圖 2.52 S 參數模擬與量測

圖 2.53 穩定度之模擬與量測

### 2.5.2 OP<sub>1dB</sub> 量測

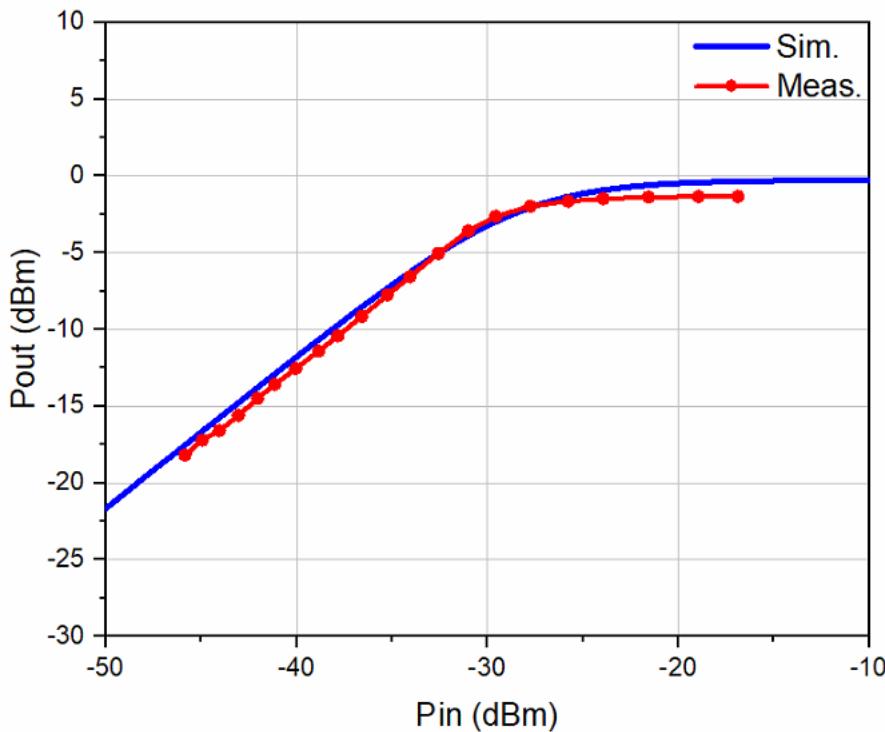

圖 2.54 為大訊號的量測架測，使用兩埠網路分析儀(Keysight E8361C)、毫米波控制器(Agilent N5260A)以及頻率延伸模組(OML V06VNA2-T/R)作為訊號源輸入，針對 S 參數所量測到的峰值增益頻率 143 GHz 打出訊號源，並通過 WR6 衰減器來調整輸入功率，輸出使用 Erickson PM5 來檢測輸出功率，以此架構量測 OP<sub>1dB</sub>，量測結果如圖 2.55 所示，模擬與量測上相近，OP<sub>1dB</sub> 為-2.5 dBm。

圖 2.54 OP<sub>1dB</sub> 之量測架設

圖 2.55 OP<sub>1dB</sub> 之模擬與量測

### 2.5.3 NF 量測

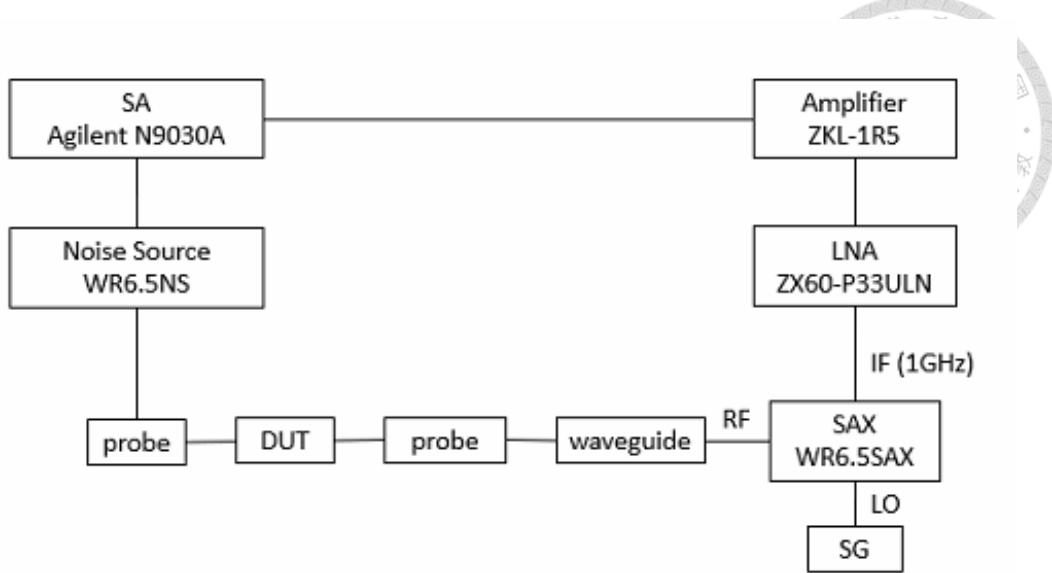

雜訊量測上參考[40]使用 Y 因子來作為量測方法，實際架設如圖 2.56 所示，雜訊源(VDI WR6.5NS)主要控制雜訊的開啟與關閉，可由 ENR (Excess noise ratio) 得知其開啟與關閉的功率比， $T_{on}$ 為雜訊源開啟時的等效雜訊溫度， $T_{off}$ 為雜訊源關閉時的等效溫度， $T_0$ 則為環境溫度，通常情況下 $T_{off} = T_0 = 290K$ ， $T_{on}$ 取決於雜訊源實際特性，此雜訊源在 110-170 GHz 的 ENR 約為 10 dB，換算 $T_{on}$ 約為 3190 K。

$$\text{ENR(dB)} = 10 \times \log \left( \frac{T_{on} - T_{off}}{T_0} \right) \quad (2.24)$$

連接待測物之後，因頻率太高無法直接連接頻譜分析儀(Agilent N9030A)，因此使用降頻器(VDI WR6.5SAX)先將 D-band 訊號降頻至 1 GHz 再利用低頻放大器(ZX60-P33ULN、ZKL-1R5)加強其增益，避免頻譜分析儀在測量 Y 因子時，因增益太小而接收不到訊號。

圖 2.56 NF 量測架構

圖 2.57 NF 量測架設

$$Y = \frac{T_{hot}}{T_{cold}} \quad (2.25)$$

Y 因子其定義為(2.25)所示， $T_{hot}$ 與 $T_{cold}$ 分別代表雜訊源開啟與關閉時，包

含待測物、降頻器及低頻放大器的整體系統雜訊溫度，可分別如下表示

$$T_{hot} = T_{on} + (L_1 - 1) \times 290 + T_{DUT} \times L_1 + \frac{(L_2 - 1) \times L_1 \times 290}{G_{DUT}} + \frac{T_{mixer} \times L_1 \times L_2}{G_{DUT}} \quad (2.26)$$

$$T_{cold} = T_{cold} + (L_1 - 1) \times 290 + T_{DUT} \times L_1 + \frac{(L_2 - 1) \times L_1 \times 290}{G_{DUT}} + \frac{T_{mixer} \times L_1 \times L_2}{G_{DUT}} \quad (2.27)$$

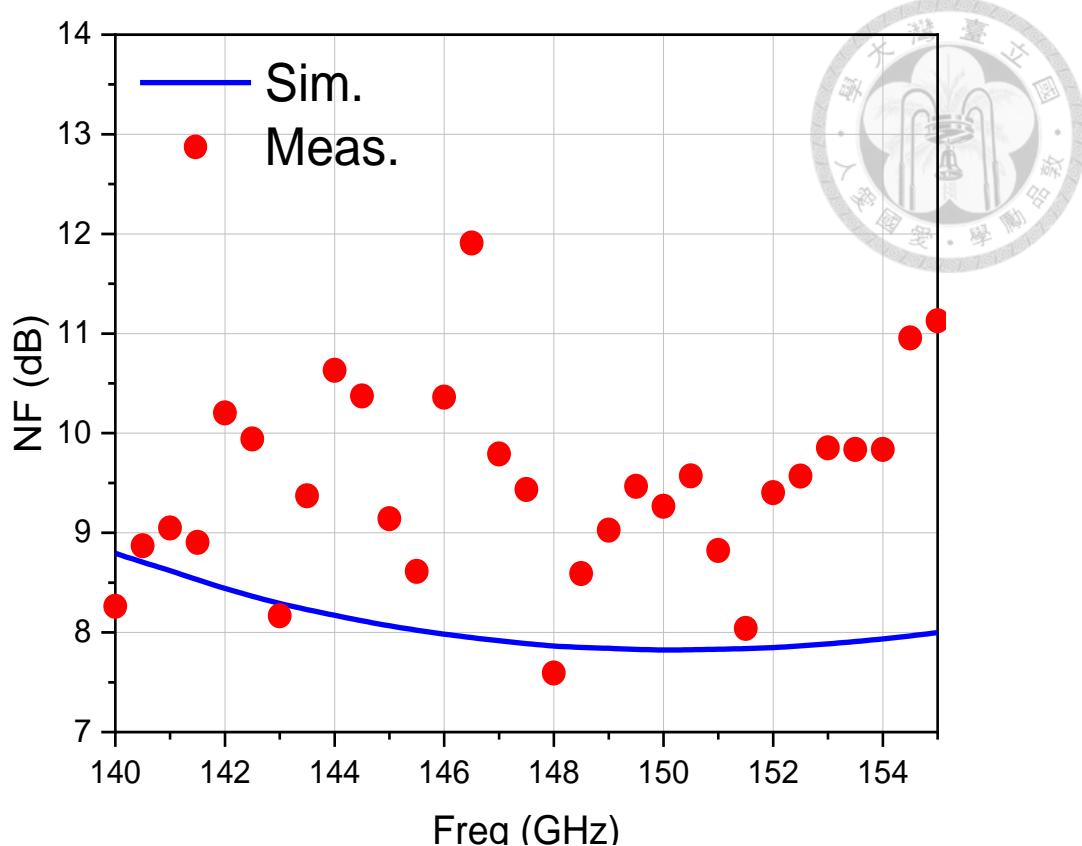

$L_1$ 為輸入的探針與波導管損耗， $L_2$ 為輸出的探針與波導管損耗， $T_{mixer}$ 為降頻器與低頻放大器之等校雜訊溫度，最後可由(2.26)與(2.27)整理出待測物其等校雜訊溫度 $T_{DUT,DSB}$  (2.28)，需要注意的是 D-band 訊號經由混頻器降頻至 1 GHz 時，無法分辨出訊號是位於 LO 的上邊帶或是下邊帶，量測結果如圖 2.58 所示，雜訊指數在此頻段約為 9 dB，與模擬相比高了 1 dB 左右。

$$T_{DUT,DSB} = \frac{1}{L_1} \left[ \frac{T_{on} - Y \times T_{off}}{Y - 1} - (L_1 - 1) \times 290 - \frac{(L_2 - 1) \times L_1 \times 290}{G_{DUT}} - \frac{T_{mixer} \times L_1 \times L_2}{G_{DUT}} \right] \quad (2.28)$$

$$T_{DUT,DSB}(\text{dB}) = 10 \times \log \left( \frac{T_{DUT,DSB}}{290} + 1 \right) \quad (2.29)$$

圖 2.58 NF 之模擬與量測

## 2.6 問題與討論

此次的設計中，由於未加入 ESD 電路，造成在打磅線和量測過程中損壞率較高，這是未來可以從中新增。除此之外，此晶片在量測過程中面臨最大的問題是頻偏，偏向低頻 6.5 GHz，主要原因來自電晶體模型的不準確。並且，由於需要高增益，犧牲掉了較多的頻寬，導致 150 GHz 的增益實際上只剩約 19 dB。近年來已有許多文章針對  $G_{max}$ -core 的頻寬進行優化，未來的設計希望能夠可以從電晶體的模型去修正，或是能增加更大的頻寬，以更好符合應用的需求。

## Chapter 3 300 GHz 之次諧波混頻器

### 3.1 簡介

隨著 6G 通訊技術的快速發展，操作頻率逐漸邁向 THz 頻段，其中 300 GHz 頻段已成為實現超高速無線通訊的重要研究領域。然而，受限於現有半導體製程的特性，傳統混頻器於此高頻段中所需之高功率本地振盪器(LO)較難實現，使得次諧波混頻器(Subharmonic Mixer, SHM)成為高頻無線通訊系統中極具潛力的替代方案。

次諧波混頻器能夠利用非線性元件產生的二次諧波來達成混頻，其最大的優勢是允許 LO 的輸入頻率及功率大幅降低，有效解決高頻下難以產生大功率 LO 訊號的挑戰。本章節介紹應用於 280 – 305 GHz (IEEE 802.15.3d Channel 67) 頻段的新型次諧波混頻器，該設計採用 65nm CMOS 製程，提出一個創新的混頻架構，並透過電路模擬和實作驗證其效能。

本章內容架構如下：第 3.2 節將說明次諧波混頻器的基本原理與現有的典型架構；第 3.3 節介紹本研究提出的電路架構；第 3.4 節詳細描述電路設計的實作過程及關鍵元件選用；第 3.5 節進一步展示模擬與實際量測結果的比較，最後第 3.6 節則針對實際設計與量測中所遇到的問題進行分析與討論，以提供未來研究的建議與方向。

## 3.2 次諧波換頻器原理與介紹

### 3.2.1 疊接式次諧波換頻器

在亞太赫茲與太赫茲頻段中，高頻 LO 訊號難以直接產生，主要受限於 CMOS 製程中較低的最大震盪頻率  $f_{max}$ 。若要在此頻段實現足夠功率的 LO，常需額外搭配複雜的倍頻鏈與功率放大器，造成系統設計與功耗的負擔。因此，次諧波混頻器被廣泛應用於此頻段，其優點在於允許使用一半頻率的 LO 訊號進行混頻操作，能有效緩解 LO 訊號產生的挑戰。

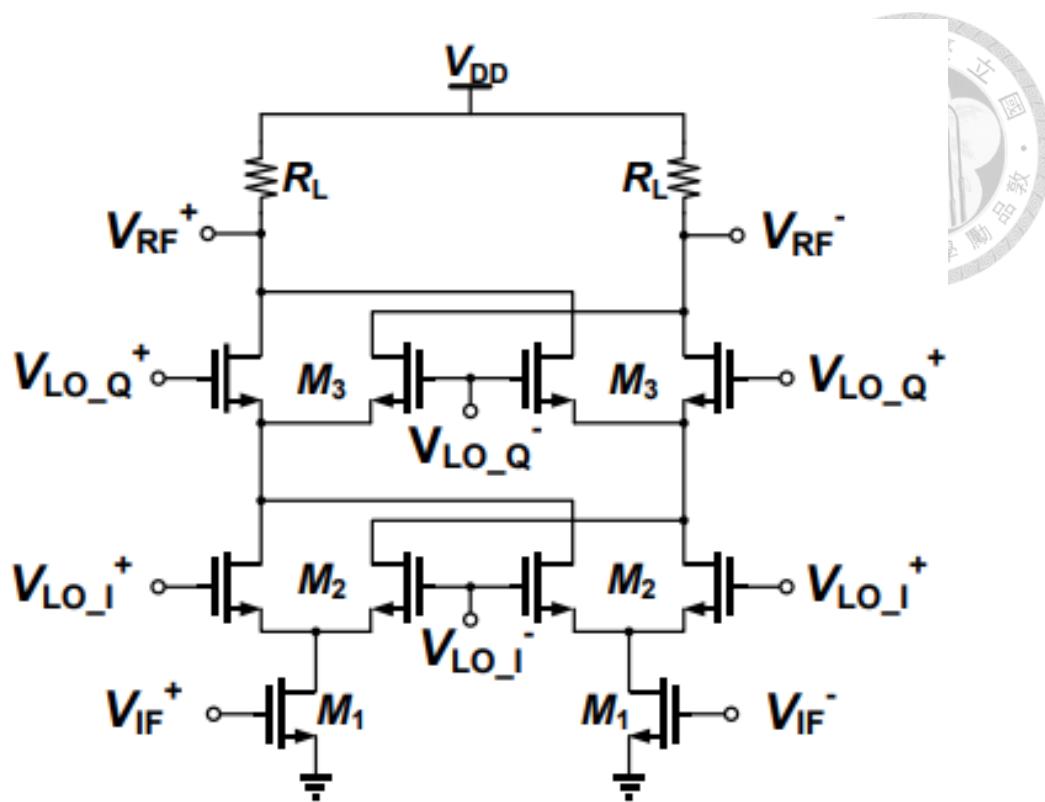

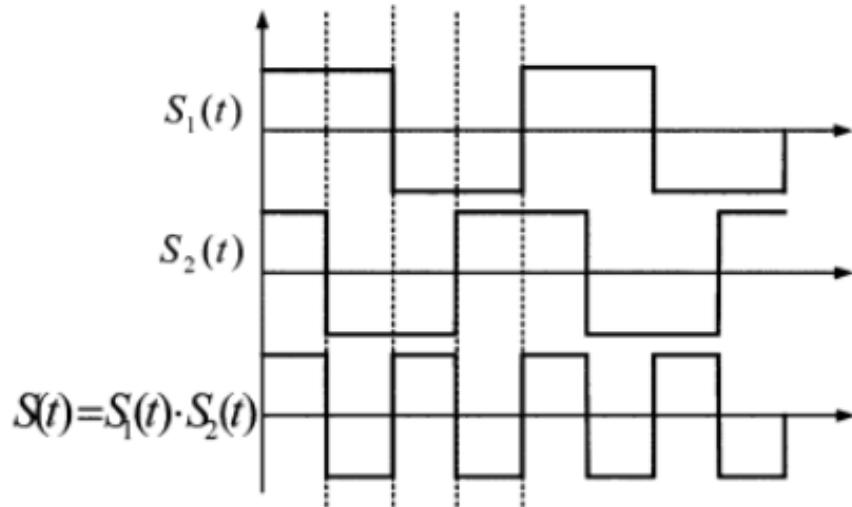

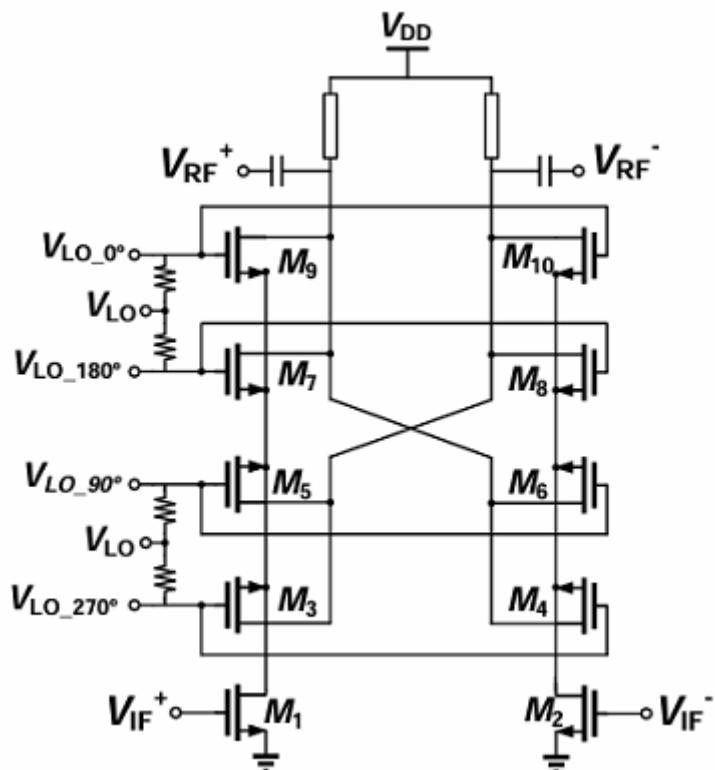

次諧波混頻器常見的主要架構可分為疊接式 LO (Stacked-LO) 及並列式 LO (Leveled-LO) 混頻器，圖 3.1 為疊接式 LO 之次諧波混頻器[41]，其架構於  $M_2$  電晶體輸入 LO 的  $I^+$  及  $I^-$  訊號，其對應的波形為  $S_1(t)$  如圖 3.2 所示。 $M_3$  電晶體則輸入 LO 的  $Q^+$  及  $Q^-$  訊號，其對應的波形為  $S_2(t)$ 。其中 I 及 Q 為相差 90 度之正交訊號，在此分別表示為  $\cos(\omega_{LO}t)$  及  $\sin(\omega_{LO}t)$ ，則等校之 LO 開關訊號可視為其兩者乘積，波形為  $S(t)$ ：

$$S(t) = \cos(\omega_{LO}t) \sin(\omega_{LO}t) = \frac{1}{2} \sin(2\omega_{LO}t) \quad (3.1)$$

此即代表電路產生了 LO 的偶次諧波，進而與 RF 訊號來進行混頻，此架構之優點為有良好的 2LO-IF 隔離度，也能有效抑制基頻與奇次諧波，並能操作於更小的 LO 訊號。然而由於此結構需要四相位的 LO 訊號，並且需要較大的  $V_{DD}$  來確保  $M_1$ 、 $M_2$  及  $M_3$  電晶體操作在合適的電壓。

圖 3.1 疊接式 LO 次諧波混頻器

圖 3.2 疊接式 LO 次諧波混頻器之波形

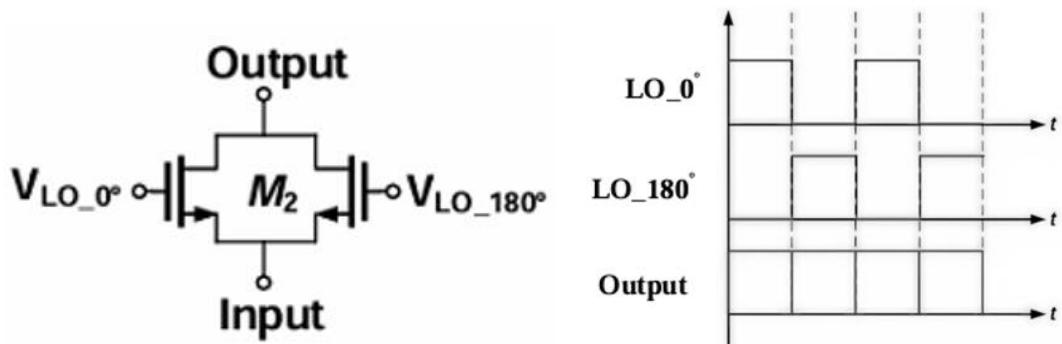

### 3.2.2 並列式次諧波換頻器

圖 3.3 為傳統的並列式次諧波混頻器[42]，相較於疊接式架構，不需要堆疊多級電晶體，電路結構相對單純，更適合操作在高頻低電壓的條件下，然而也需要

要更大的 LO 驅動功率，圖 3.4 為單一開關級的波形， $LO^+$  與  $LO^-$  會輸入在其兩側，使得輸出會有兩倍的 LO 訊號，其整體架構較為單純，適合操作在低電壓及更高的頻率下，然而需要額外注意 LO 的洩漏。

圖 3.3 並列式 LO 次諧波混頻器

圖 3.4 並列式 LO 次諧波混頻器之波形

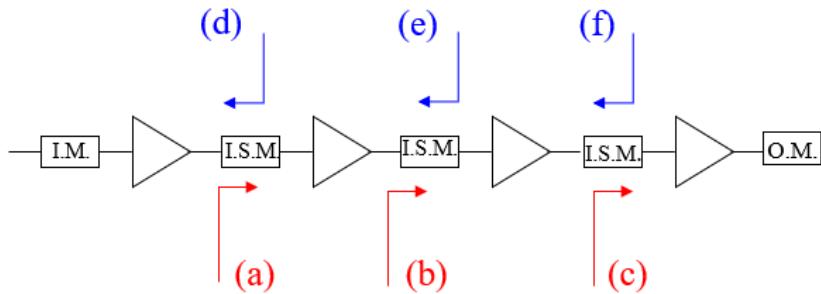

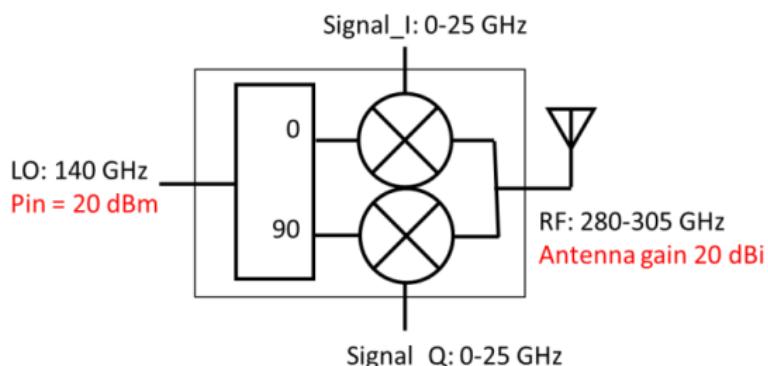

### 3.2.3 電路設計規格

本文之次諧波混頻器預計應用在 6G 通訊之 300 GHz 無線收發系統，針對應用頻段 IEEE 802.15.3d 之 Channal67 (280-305 GHz)，來進行高速之無線收發機設計。近年來也有許多文獻關於 300 GHz 之高速傳輸通訊 [24][25][27][43][44][45][46]，也有文獻[47]發表在 300 GHz 使用 InP 製程於距離 9.8m 能夠達到 120 Gb/s，然而因為 InP 製程取得不易並且價格昂貴，因此也特別參考了 CMOS 製程於 2019 發表[43]能驗 0.03m 傳輸距離達到 80 Gb/s 的資料傳輸。預計使用之架構如圖 3.5 所示，包含了一耦合器、兩個次諧波混頻器以及天線，本文針對其中之次諧波混頻器來進行設計，預計規格如表 3.1 所示，整體設計期望能在不依靠高階製程與功率放大器的情況下，完成 300 GHz 頻段的無線高速傳輸模組。

圖 3.5 預計應用及規格

表 3.1 次諧波混頻器之設計目標

| RF Frequency | LO frequency | Return Loss | P <sub>DC</sub> | Conversion loss | Noise Figure |

|--------------|--------------|-------------|-----------------|-----------------|--------------|

| 280-305 GHz  | 140 GHz      | < -10 dB    | 0               | 20 dB           | 20 dB        |

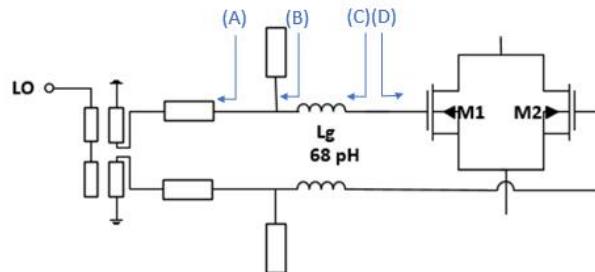

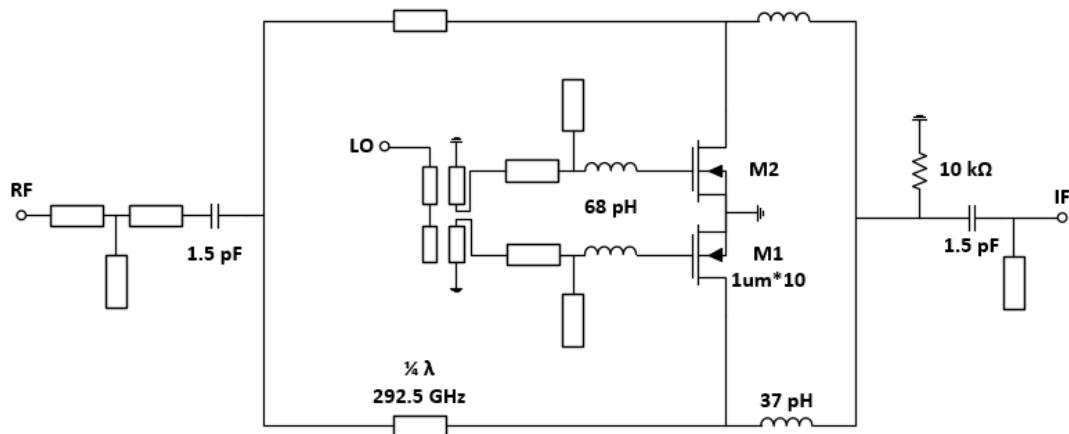

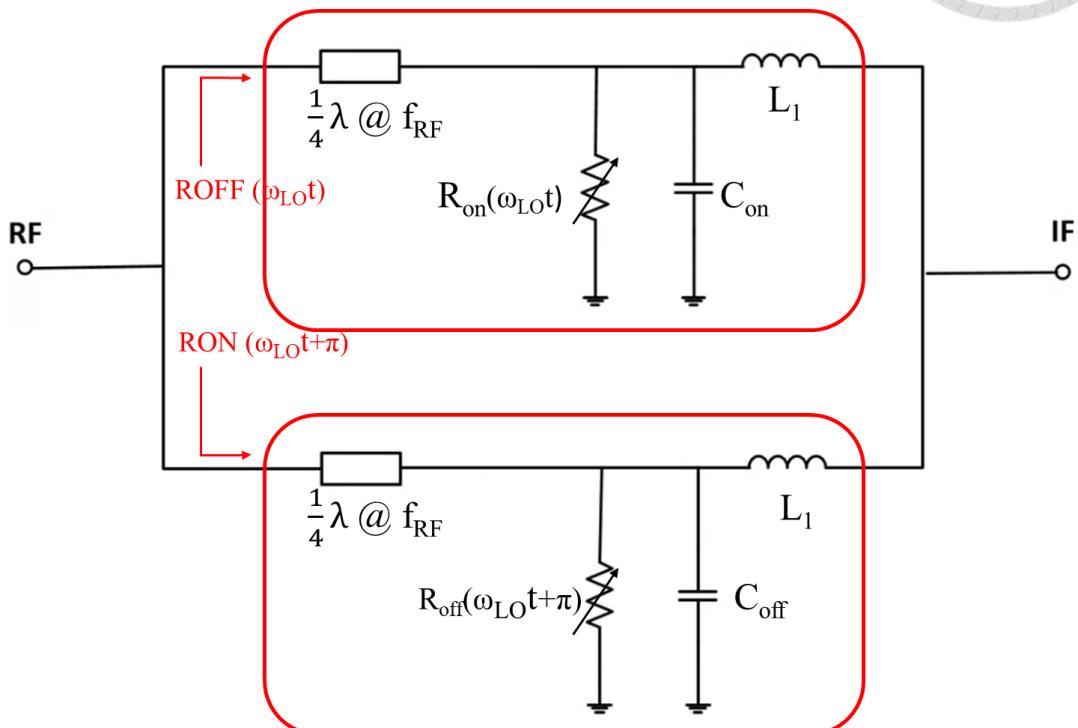

### 3.3 串接式開關 SHM 電路架構

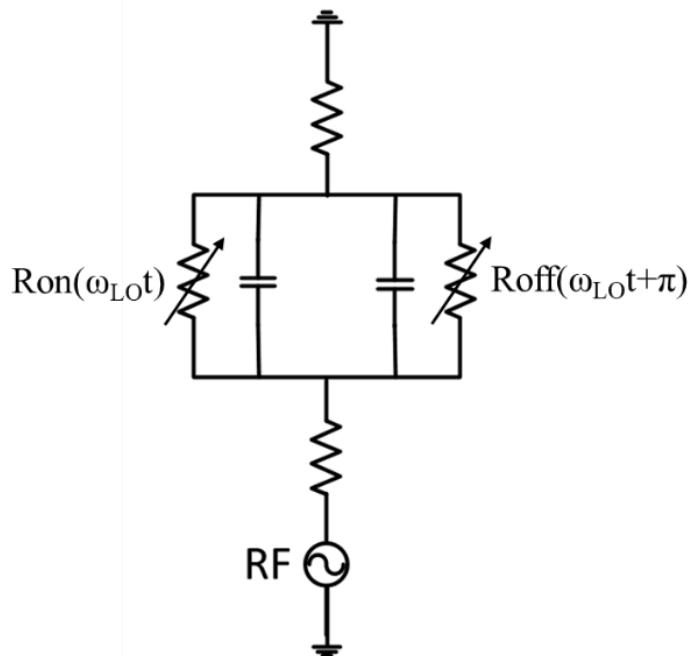

本研究提出之第一種次諧波混頻器，採用電阻式之次諧波雙開關混頻器，如圖 3.6 所示。由兩個電晶體 M1 與 M2 所構成，這兩個電晶體開關與 IF 和 RF 串接，在此稱為串接式開關 SHM，以用來跟後續文章的 SHM 作區別。閘極分別由互補的 LO 訊號所驅動，且無額外  $V_g$  與  $V_d$  偏壓供應，使其操作於弱反轉區附近。此設計可有效的簡化偏壓電路無額外功耗，同時透過其非線性導通行為產生所需之二次諧波，實現次諧波混頻功能。

圖 3.6 串接式開關 SHM 電路架構

由於 M1 與 M2 僅由 LO 訊號交錯控制導通，其導通狀態可視為隨時間變化的非線性電阻函數，如圖 3.7 所示分別記為當電晶體導通時  $R_{on}(\omega_{LO}t)$ ，與電晶體處於截止時  $R_{off}(\omega_{LO}t + \pi)$ ，兩者形成交錯開關，整體可建模為一個隨著時間變化的並聯阻抗  $Z_p(\omega_{LO}t)$ ：

$$Z_p(\omega_{LO}t) = R_{on}(\omega_{LO}t) // R_{off}(\omega_{LO}t + \pi) = \frac{R_{on}(\omega_{LO}t) * R_{off}(\omega_{LO}t + \pi)}{R_{on}(\omega_{LO}t) + R_{off}(\omega_{LO}t + \pi)} \quad (3.2)$$

此等效阻抗  $Z_p(\omega_{LO}t)$  會隨著時間呈現週期性變化，並且(3.2)式乘積下導致

偶次諧波的頻譜產生。若將電晶體導通函數視為方波函數 $g_1(t)$ 與 $g_2(t)$ ，其疊加結果為：

$$g_{total}(t) = g_1(t) + g_2(t) = a_0 + a_2 \cos(2\omega_{LO}t) + a_4 \cos(4\omega_{LO}t) \quad (3.3)$$

所有奇次諧波成分將互相抵消，僅保留偶數次項，其中以 $(2\omega_{LO}t)$ 為最主要分量。當 RF 注入該節點後，與此 2LO 進行非線性乘積，即可實現次諧波混頻，其 IF 頻率為：

$$f_{IF} = |f_{RF} - 2f_{LO}| \quad (3.4)$$

此外，由於本架構中 MOSFET 的汲極與並無提供偏壓，即  $V_{DS} = 0$ ，使其在物理上汲極與源極呈現電氣對稱，在此條件下兩端阻抗相同，無故定訊號方向，整體架構可自然實現上變頻與下變頻的雙向混頻操作，無須額外路徑即可收發共用，具有高度整合性與架構的靈活性。

圖 3.7 串接式開關 SHM 等效電阻模型

## 3.4 串接式開關 SHM 電路設計與流程

### 3.4.1 LO 馬遜巴倫設計

馬遜巴倫(Marchand Balun)是一種廣泛應用於射頻與毫米波電路的平衡轉換元件，具備結構對稱、較大的頻寬等優點。其基本原理為透過兩段 $\frac{1}{4}\lambda$ 耦合線，將單端訊號轉換為具有等幅反相信號的差動輸出，廣泛應用於混頻器、功率放大器與相位陣列系統等高頻模組中。

傳統的馬遜巴倫結構由兩對耦合線組成，其中一對接地並作為反向輸出，另一對則提供正向輸出，兩者之間藉由耦合與傳輸線電氣長度形成所需的相位與幅度關係。理想情況下，該結構可提供 $180^\circ$ 相位差與良好的幅度平衡。其頻寬特性主要由耦合係數與線長所控制，理論上可實現比傳統巴倫結構更寬的操作頻段。

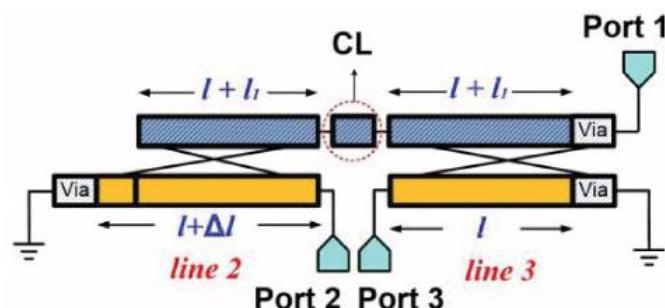

然而，在實際 CMOS 製程中，由於金屬層數限制與耦合能力有限，馬遜巴倫在高頻時常會遭遇相位或振幅不平衡的問題。為此，常搭配補償線[48][49]以修正非理想特性，如圖 3.8 所示，調整中間補償線的特性阻抗來提升其震幅和相位不平衡表現。

圖 3.8 具有補償線之馬遜巴倫

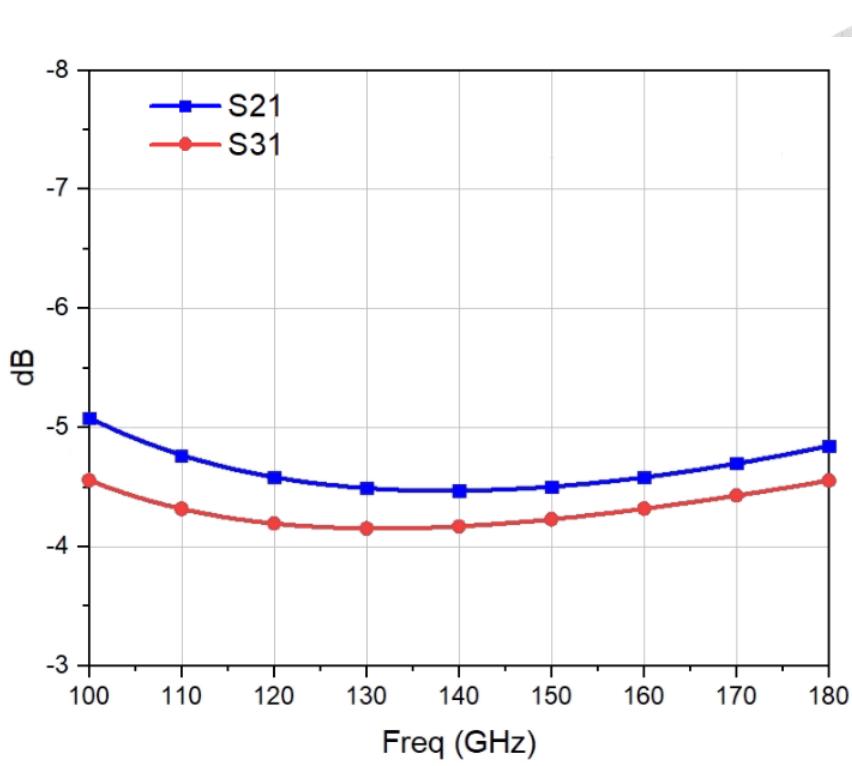

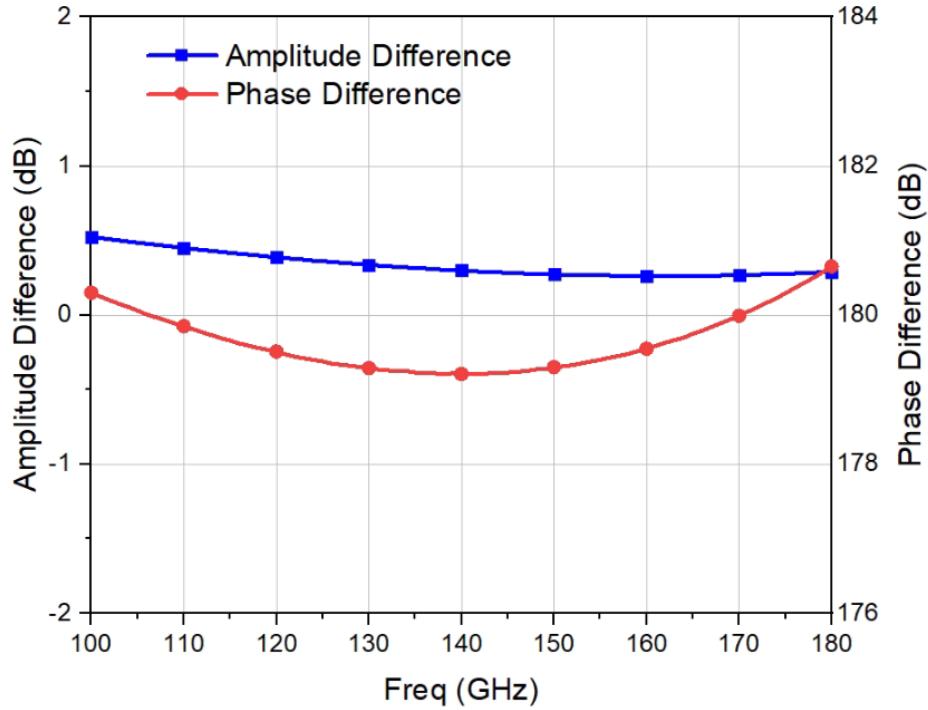

為了提供互補的 LO 輸入，本設計採用三埠式補償線馬遜巴倫作為平衡轉換器，將單端的 LO 訊號轉換為對稱差動輸出，以驅動電晶體開關。圖 3.9 所示，所提出之馬遜巴倫在中間引入了補償線，可藉由調整補償線的寬和長度，有效改善振幅與相位不平衡。模擬結果如圖 3.10 和錯誤! 找不到參照來源。所示，在 100 GHz 至 180 GHz 操作頻段內  $S_{21}$  與  $S_{31}$  皆維持在 -5 dB 以內，振幅不平衡則小於 0.5 dB，且相位差穩定維持在  $180^\circ$ ，相位不平衡亦控制在  $1^\circ$  以內，顯示本設計具有良好的寬頻平衡特性。

圖 3.9 補償線馬遜巴倫之 3D 佈局圖

圖 3.10 補償線馬遜巴倫之  $S_{21}$  與  $S_{31}$  插入損耗模擬

圖 3.11 補償線馬遜巴倫之相位與振幅不平衡

### 3.4.2 偏壓與電晶體尺寸選擇

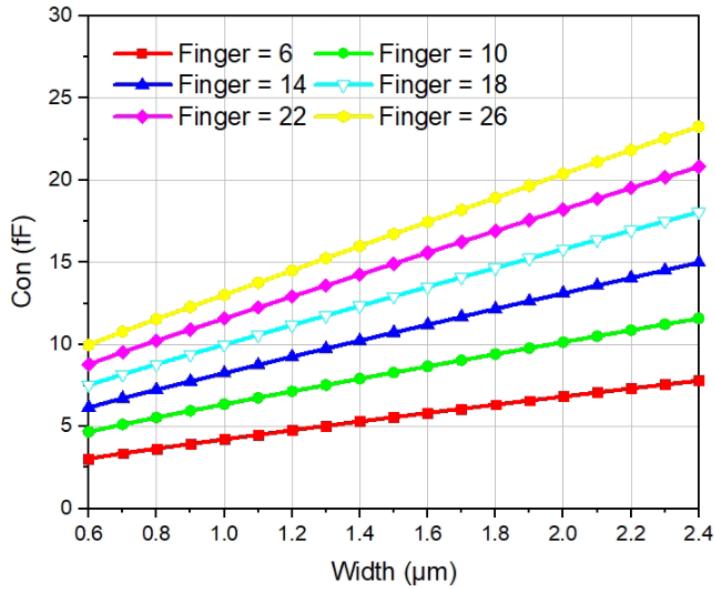

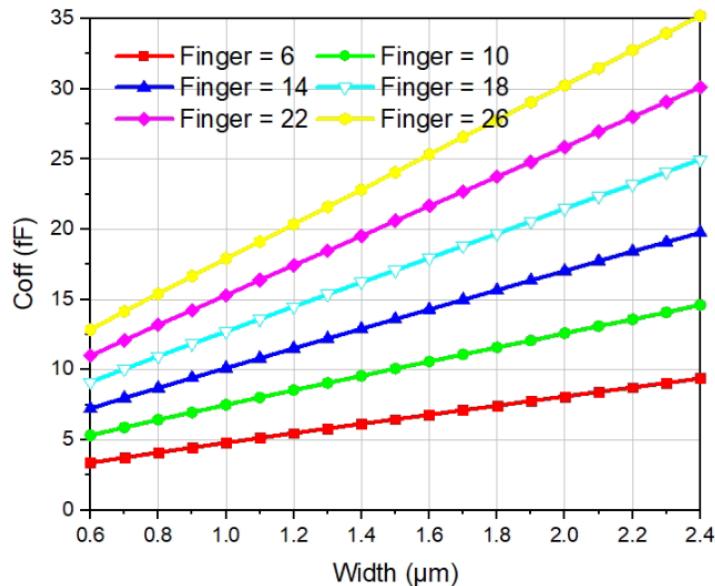

為了優化次諧波混頻器核心開關特性，本研究首先針對電晶體之開關行為進行特性分析。由於所設計之次諧波混頻器主要以開關動作實現非線性混頻，電晶體尺寸直接影響導通電阻、關閉時的隔離度，以及寄生電容對高頻訊號的影響。因此，選定三項常見之開關效能指標作為初步評估依據，分別為開關比值  $R_{off}/R_{on}$ 、關閉狀態之能量洩漏  $R_{on} * C_{off}$ ，以及導通切換速度  $R_{on} * C_{on}$ 。

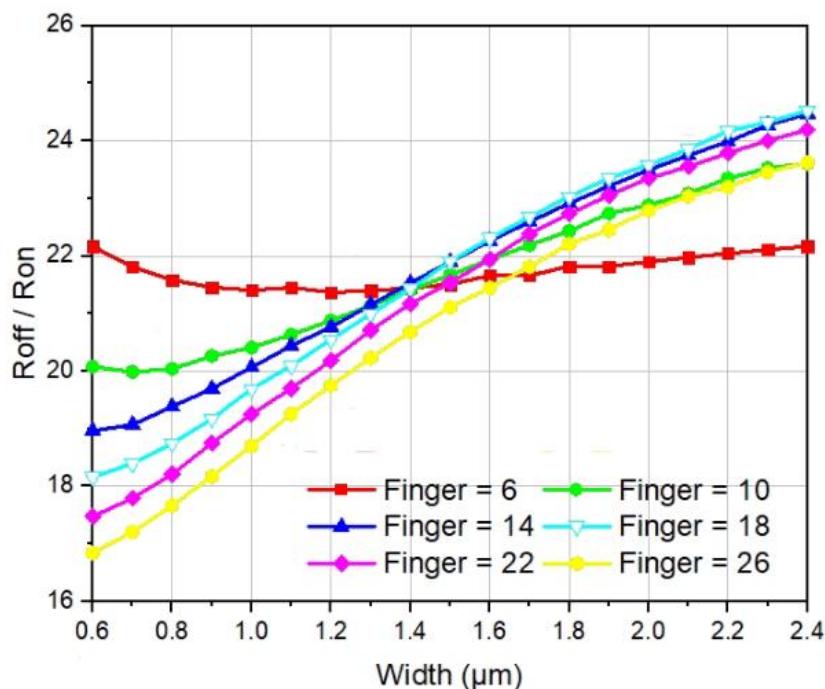

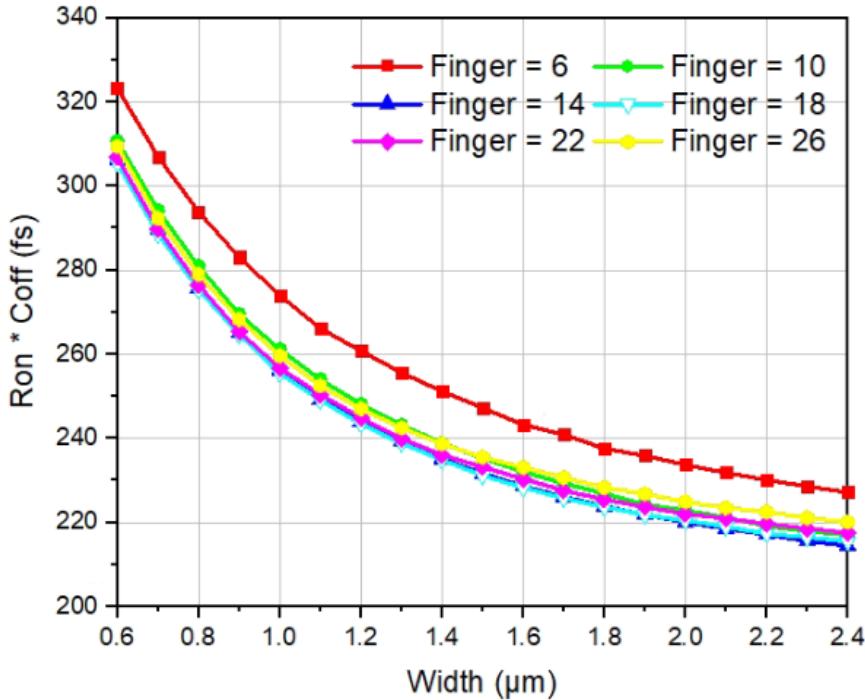

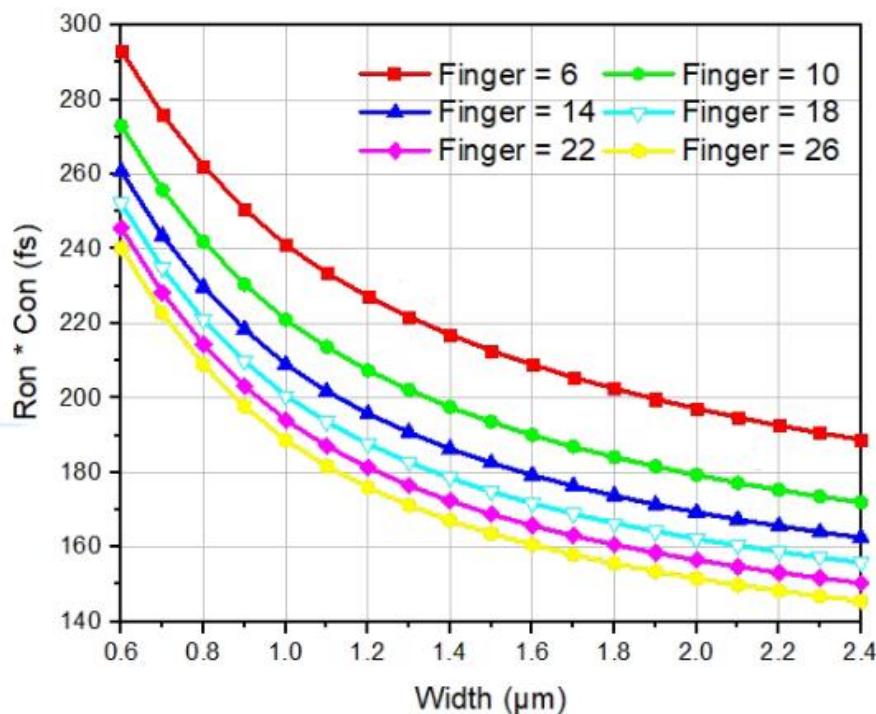

首先從  $R_{off}/R_{on}$  指標觀察，如圖 3.12 所示，固定 LO 頻率為 140 GHz 時，隨著 width 與 finger 數增加， $R_{off}/R_{on}$  顯著提升，表示開關導通與關閉狀態之阻抗差異增大，能有效改善開關理想性，有助於抑制不必要的雜訊。另一方面，如圖 3.13 與圖 3.14 所示， $R_{on} * C_{off}$  與  $R_{on} * C_{on}$  均隨尺寸增加而減少，代表導通切換速度加快，且關閉狀態下的漏洩路徑亦同步減小，初步顯示較大的電晶體尺寸能有效改善開關響應速度與關閉隔離特性。

圖 3.12 導通電阻開關比對比電晶體尺寸

圖 3.13 關閉時之能量洩漏對比電晶體尺寸

圖 3.14 導通切換速度對比電晶體尺寸

然而，單純以開關特性為判斷標準並不足以完整評估次諧波混頻器之整體性能。實際上，隨著電晶體尺寸增加，寄生電容  $C_{on}$  與  $C_{off}$  亦會同步提升。如圖 3.15 與圖 3.16 所示， $C_{on}$  與  $C_{off}$  隨著尺寸增加呈現線性增加趨勢，特別在 finger 數增

加時更加明顯。這種寄生電容的增加，將直接影響 LO 端負載，造成 LO 切換速度下降，且會額外引入訊號耦合路徑，導致倍頻效率與混頻純度下降。

圖 3.15  $C_{on}$  對比電晶體尺寸

圖 3.16  $C_{off}$  對比電晶體尺寸

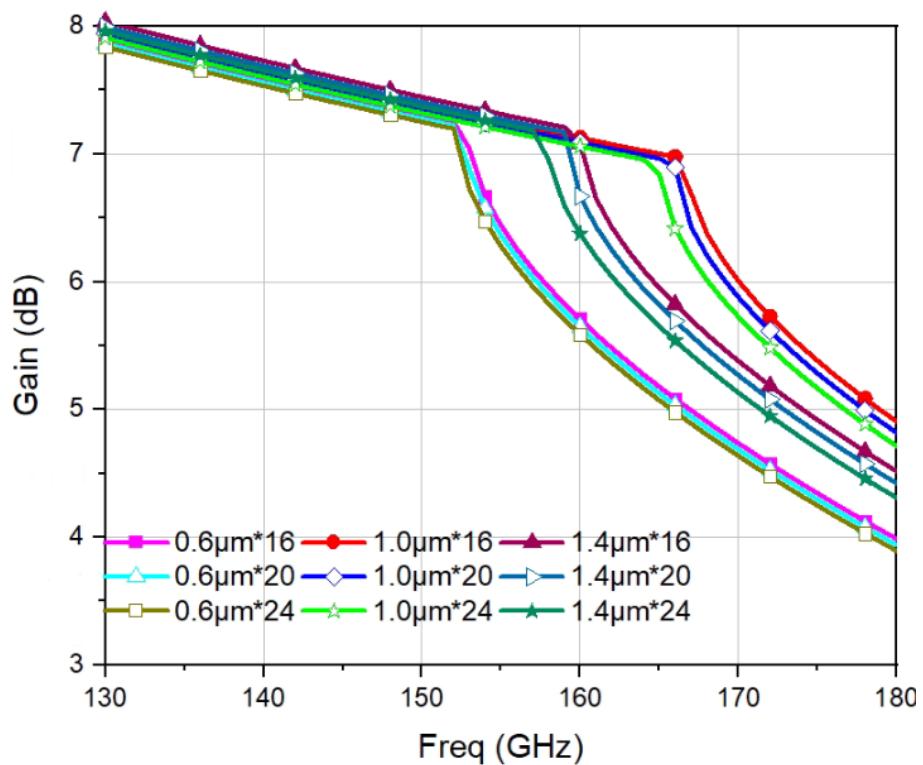

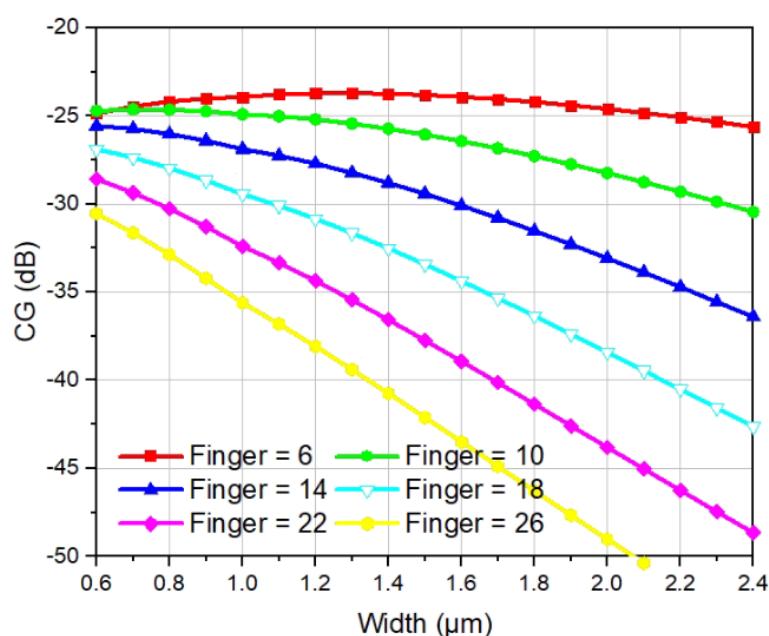

為驗證此推論，本研究額外進行完整次諧波混頻器核心之轉換增益模擬，探討不同尺寸對整體性能之影響。結果如圖 3.17 所示，儘管在單一電晶體的開關特性

指標中，finger 與 width 越大性能越佳，但實際量測的轉換增益 CG 在尺寸超過一定範圍後開始明顯下降。特別是在 finger 數達 18 或以上時，CG 呈現快速下滑趨勢，推估原因雖然 Ron 持續降低，但過大之 gate 負載造成 LO 波形邊緣劣化，無法有效產生理想的二次諧波，額外的  $C_{on}$  與  $C_{off}$  增加使輸出因為耦合而受到干擾，從而導致整體 CG 下降。

綜合以上分析結果，本研究決定採取開關特性與整體 CG 均衡折衷之設計策略。在 LO 輸入功率已達飽和的條件下，最終選定單指寬度為  $1\text{ }\mu\text{m}$ 、finger 數為 10 之電晶體尺寸。此尺寸於  $R_{off}/R_{on}$ 、 $R_{on} * C_{off}$ ，以及  $R_{on} * C_{on}$  均可達到良好水準，且  $C_{on}$  與  $C_{off}$  不至於過大影響 LO 波形，整體 CG 於  $300\text{ GHz}$  次諧波混頻操作中仍可維持高於  $-25\text{ dB}$  的良好轉換增益表現。

圖 3.17 mixer-core 對比電晶體尺寸

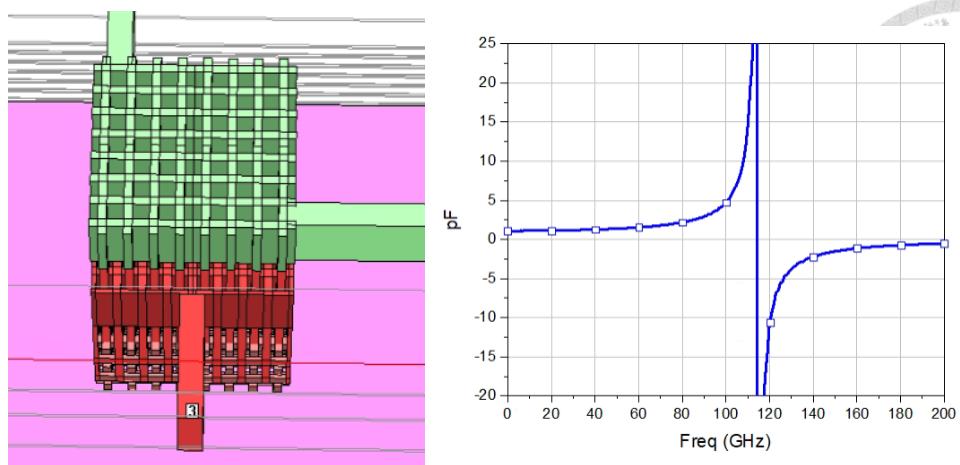

### 3.4.3 電晶體走線

由於本次設計之次諧波混頻器操作頻段目標為 280-305 GHz，對電晶體高頻性能提出極高要求，特別是在 CMOS 製程下，金屬走線所引入之額外寄生效應於高頻下尤為明顯。TSMC PDK 所提供之電晶體模型頻率驗證範圍多限制於 30 GHz 以內，然而實際電路佈線中，從 Gate/Source/Drain 端口至最高金層層 M9 的走線長度與過孔堆疊將額外引入寄生電感及電容效應，對於混頻器高頻性能與開關速度產生不可忽略之影響。

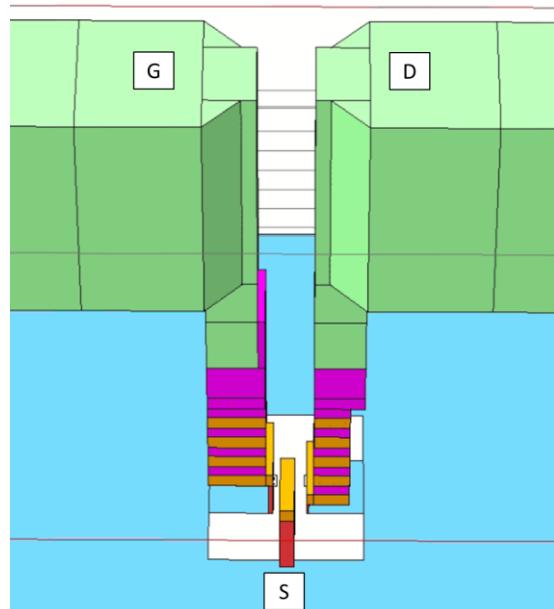

為評估此效應，本研究針對混頻器核心電晶體於兩種不同條件下進行高頻特性分析，分別為僅含理想元件模型與包含完整走線之電路佈局。實際完整的走線結構如圖 3.18 所示，經由多層過孔堆疊後，從 M9 金屬層連接至外部電路，模擬結果如圖 3.19 所示，理想條件下，電晶體  $f_t$  與  $f_{max}$  分別為 224 GHz 與 255 GHz，然而包含走線後， $f_t$  降低至 198 GHz， $f_{max}$  下降至 245 GHz，結果顯示分別下降 26 GHz 與 10 GHz。此外，走線寄生效應除了拉低  $f_t$  與  $f_{max}$  外，亦會使開關切換速度降低，對於次諧波倍頻特別在操作於 2LO 頻率時，gate 負載效應將直接影響開關邊緣斜率，進而降低二次諧波成分強度，造成轉換增益衰減。因此針對未來設計優化時，透過縮短走線長度、優化過孔佈局與減少高層金屬寄生效應等方式，能夠進一步降低  $f_t$  與  $f_{max}$  下降幅度，提升整體高頻性能。

圖 3.18 電晶體走線佈局

圖 3.19 電晶體走線之  $f_t$  與  $f_{max}$  影響

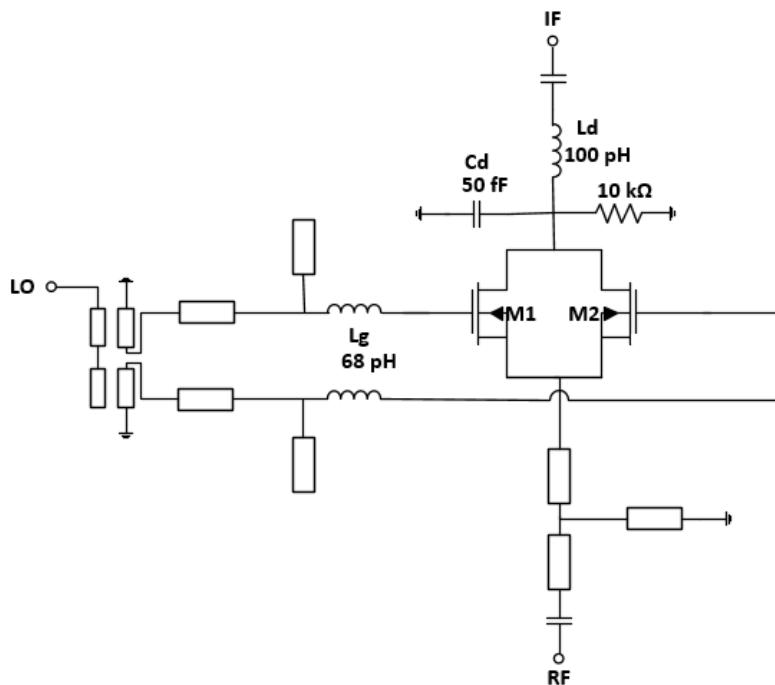

### 3.4.4 匹配網路

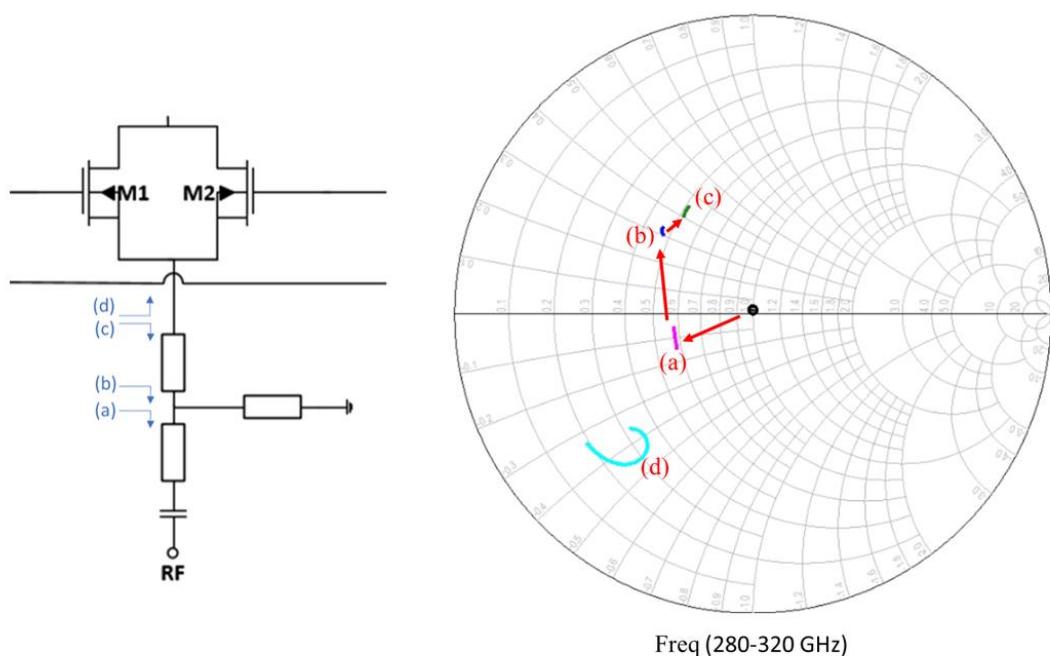

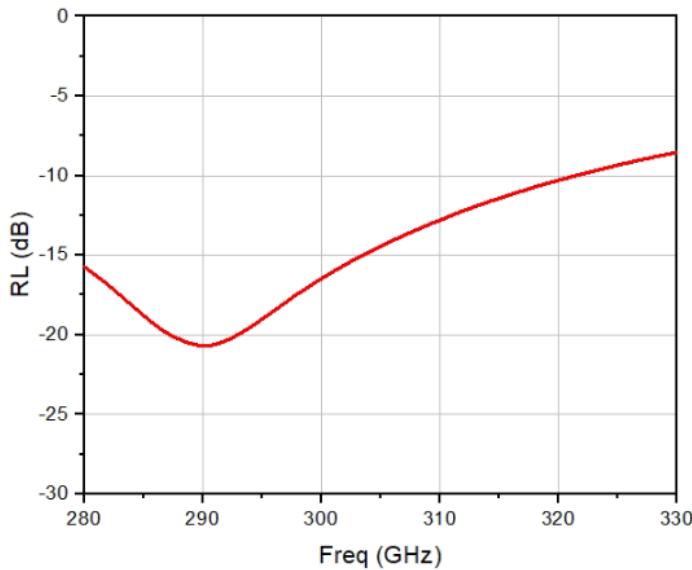

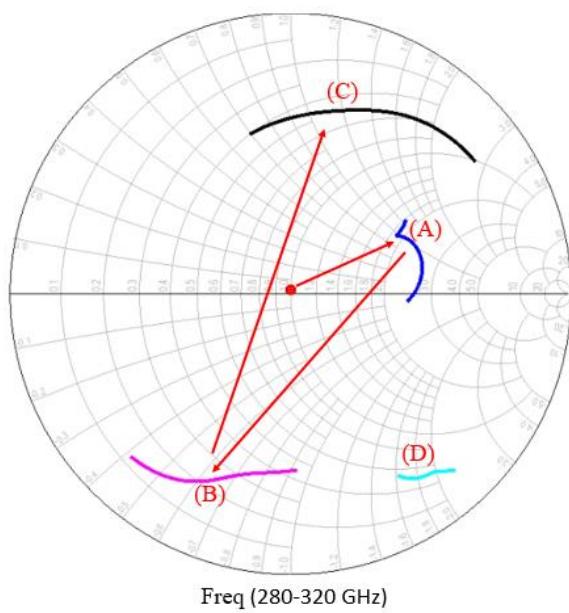

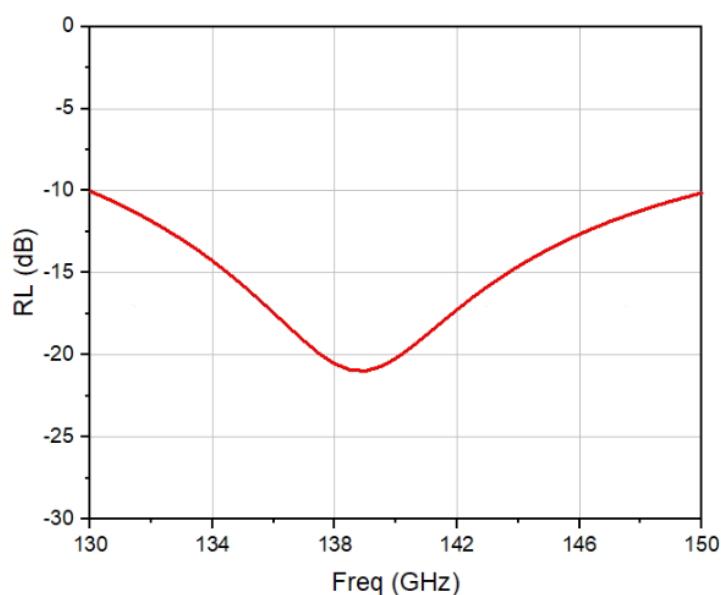

本次設計之次諧波混頻器為單端 RF 輸入，圖 3.20 為 RF 匹配網路之電路架構與對應之史密斯圖匹配路徑。匹配網路由一組串聯的 DC Block 電容和 T 型傳輸線所構成。RF pad 端經過佈局優化，其特性阻抗約為  $50\Omega$ ，透過匹配網路將  $50\Omega$  轉換至電晶體輸入端之共軛阻抗，以達成最大功率轉移。

圖中標示(a)至(c)段分別對應每段匹配元件之阻抗轉換過程，其中(c)段的傳輸線為接回電晶體所需的線段，亦兼具拉開(b)段短路傳輸線與其他元件之距離，此段額外引入點反射損耗，但可有效避免產生額外的耦合效應，整體匹配性能仍可接受。圖 3.21 為 RF 端之反射損耗，於目標頻段 280–305 GHz 內，反射損耗皆優於  $-10\text{ dB}$ ，特別在 290 GHz 附近可達  $-20\text{ dB}$ ，顯示匹配網路於本次設計頻段內具備良好寬頻匹配特性。整體匹配網路設計除有效提升功率耦合效率外，亦有助於減少反射造成之雜訊效應，確保混頻器輸入端之訊號完整性。

圖 3.20 RF 端阻抗匹配路徑

圖 3.21 RF 端之反射損失

LO 端採用單端輸入，經由馬遜巴倫轉換為互補的差動 LO 輸出，其操作頻段為 140 GHz。由於次諧波混頻器需透過二次諧波產生倍頻效應，LO 端主要功能為驅動開關電晶體產生所需非線性特性，因此 LO 端不僅須提供穩定的差動驅動，亦需具備較高的輸入功率傳輸效率。為減少輸入端反射、提升驅動能力，於 LO 端設計輸入匹配網路，使 LO 有效轉換至電晶體輸入端之共軛阻抗，以實現最大功率轉移並降低匹配損耗。

圖 3.22 為 LO 匹配網路電路架構與對應之史密斯圖匹配路徑。匹配網路主要由傳輸線和電感所組成，透過匹配網路逐步轉換至電晶體之共軛輸入阻抗，以達成最佳能量傳遞。由於 LO 為大訊號，因此實際匹配的結果可由圖 3.23 之反射損失來觀察，於 130 至 150 GHz 頻段內反射損失均優於-10 dB，中心頻率可達-20 dB 以下，驗證匹配網路具備良好之匹配效果。此匹配網路設計可有效提升 LO 輸入功率傳輸效率，並避免 LO 波形劣化，確保開關電晶體於高頻段具備足夠驅動能力，提升整體混頻器之倍頻與混頻效率。

Freq (280-320 GHz)

圖 3.22 LO 端阻抗匹配路徑

圖 3.23 LO 端之反射損失

### 3.4.5 串接式 SHM Post-sim 結果

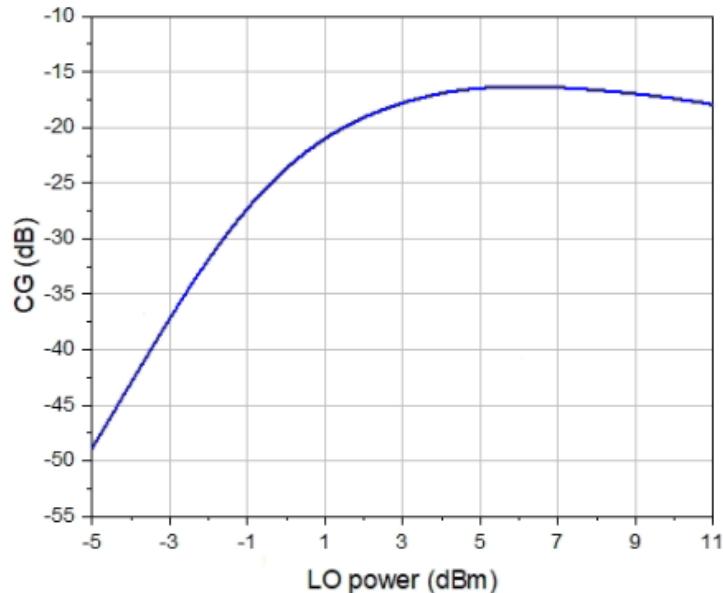

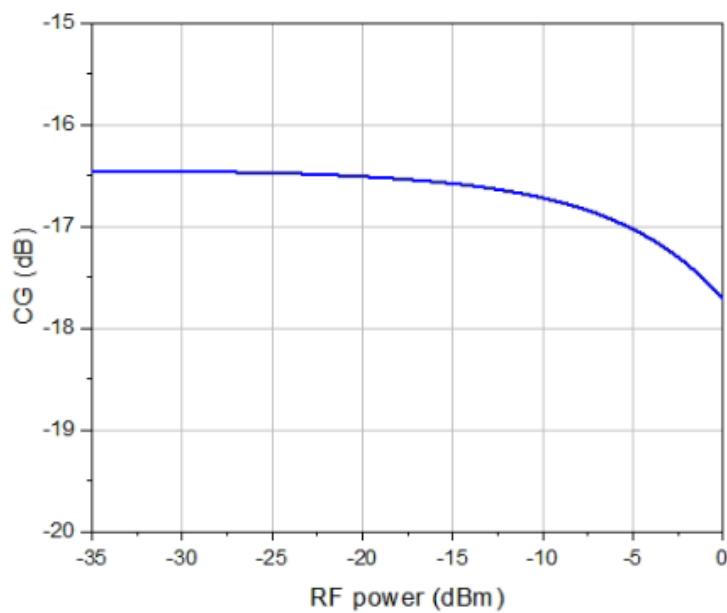

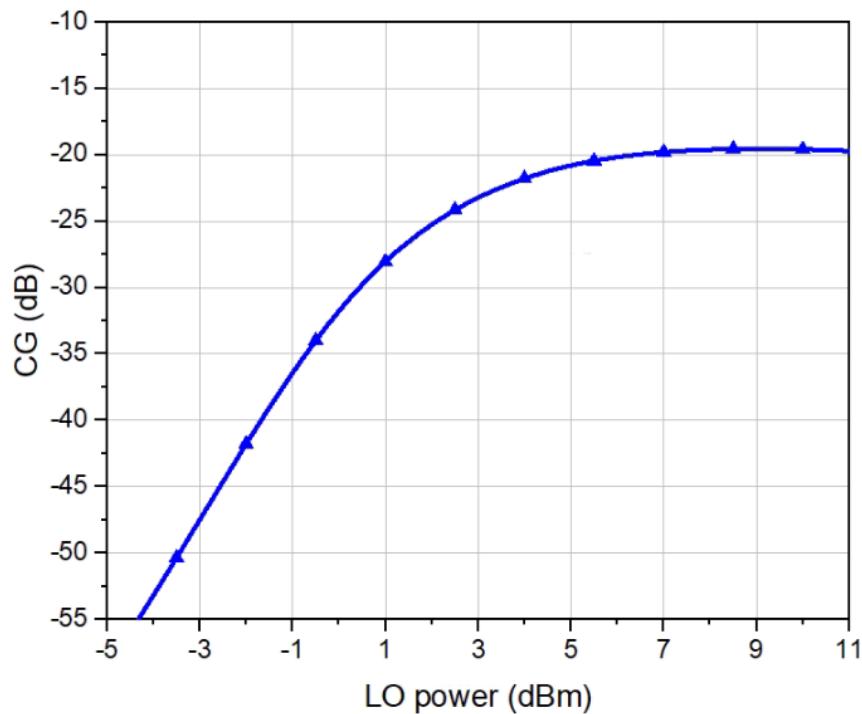

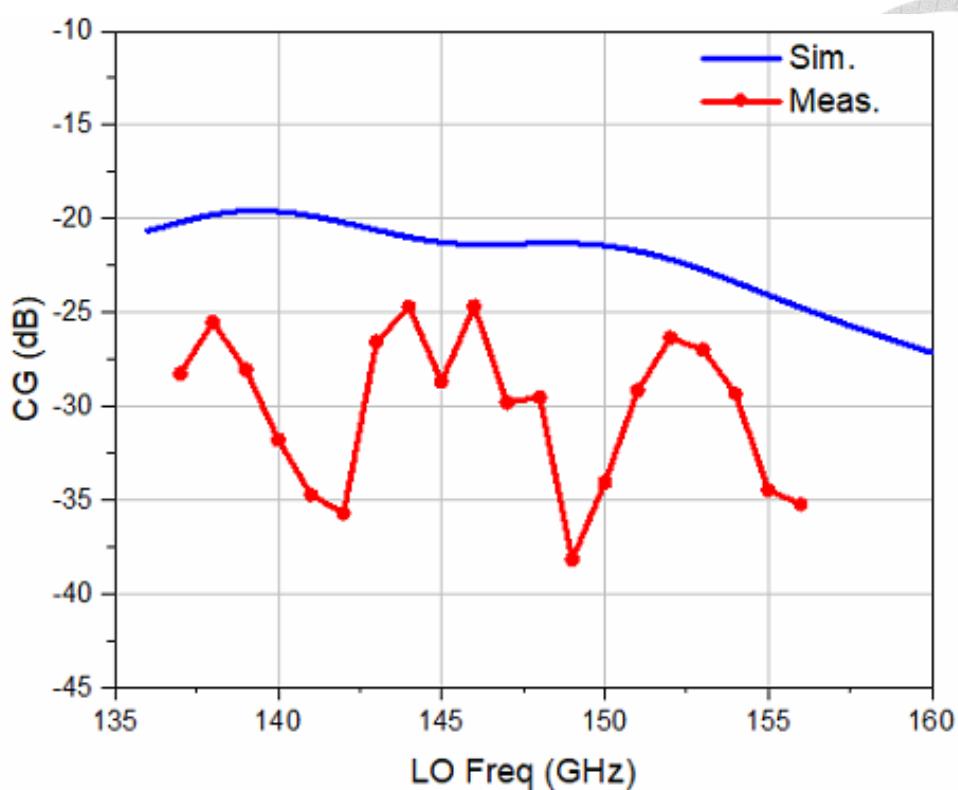

圖 3.24 為本文的次諧波混頻器電路架構，於最終佈局後模擬下，當 RF 頻率為 292 GHz、LO 頻率為 140 GHz 時進行下變頻，圖 3.25 顯示了混頻器轉換增益(CG)隨 LO 輸入功率變化之關係，隨著 LO 功率增加，轉換增益亦逐漸提升，並於 LO 輸入功率達 5 dBm 時趨於飽和，對應了最佳驅動區間。當 LO 功率過低時，由於開關電晶體導通不完全，造成轉換增益快速下降，影響混頻效率。綜合考量轉換增益與 LO 功率需求，本文後續設計與模擬皆以 LO 為 5 dBm 來做為操作條件。

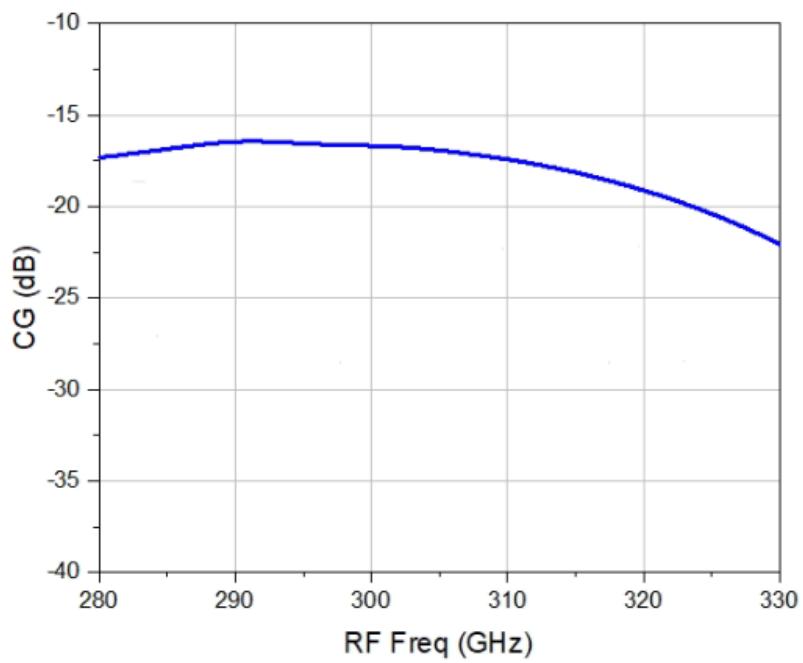

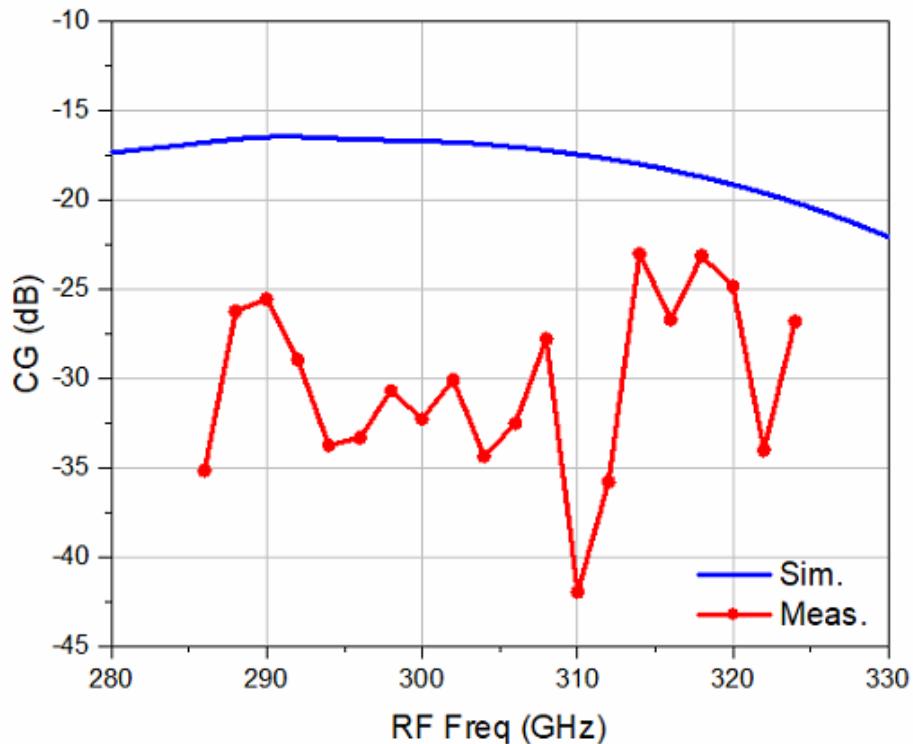

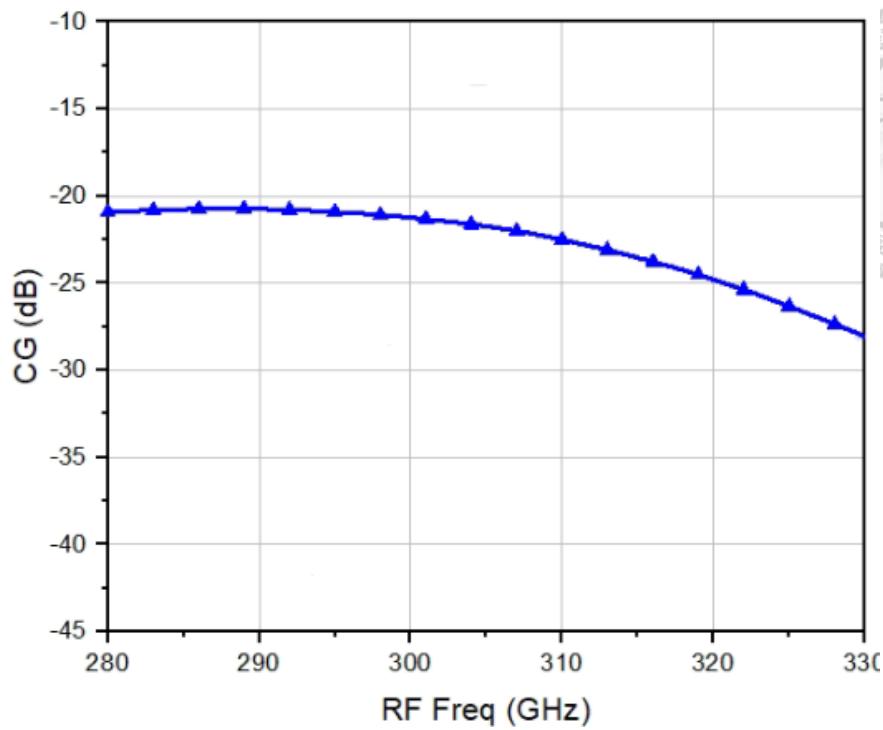

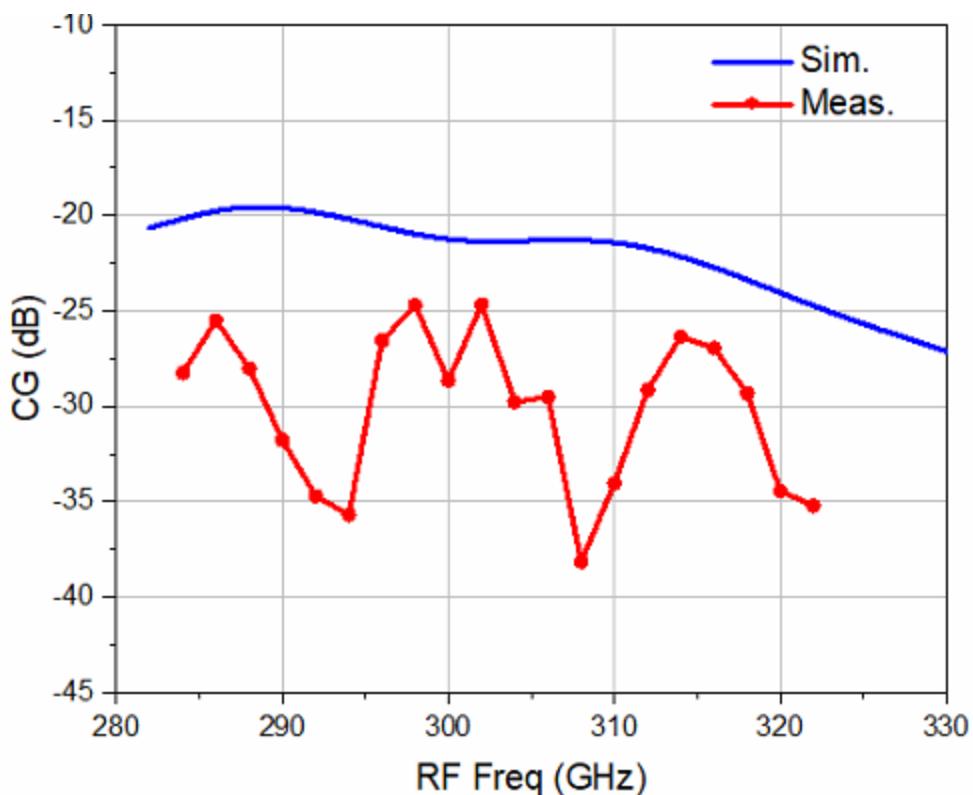

圖 3.26 為混頻器在 IF 頻率固定為 12 GHz 時，轉換增益隨 RF 輸入頻率變化之模擬結果。於 RF 頻率 292 GHz 時，轉換增益為最佳值 -16.44 dB。3 dB 頻寬可涵蓋 280-320 GHz，展現出本設計於 RF 端具備寬頻操作特性。

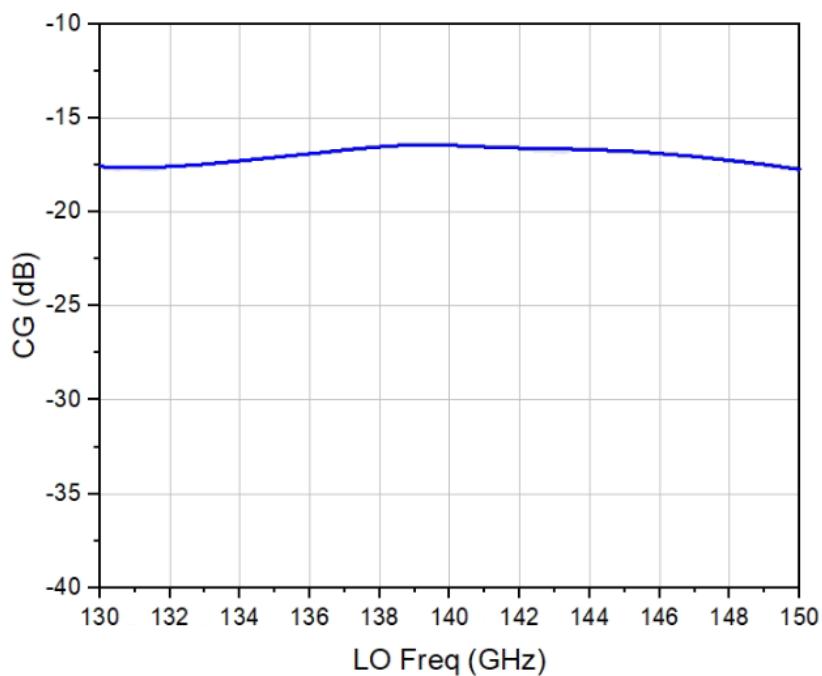

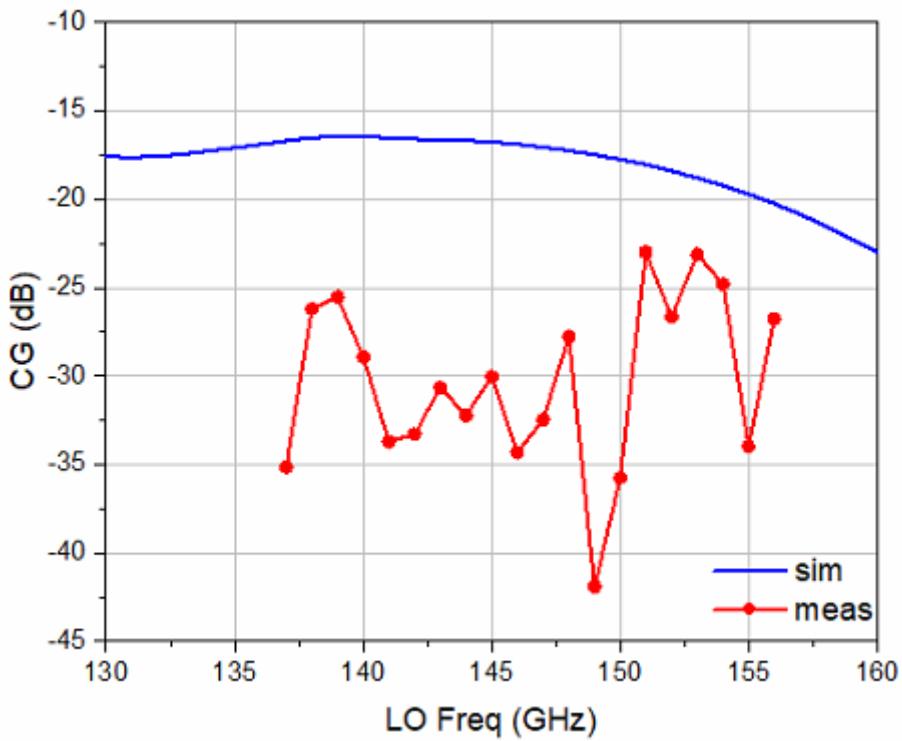

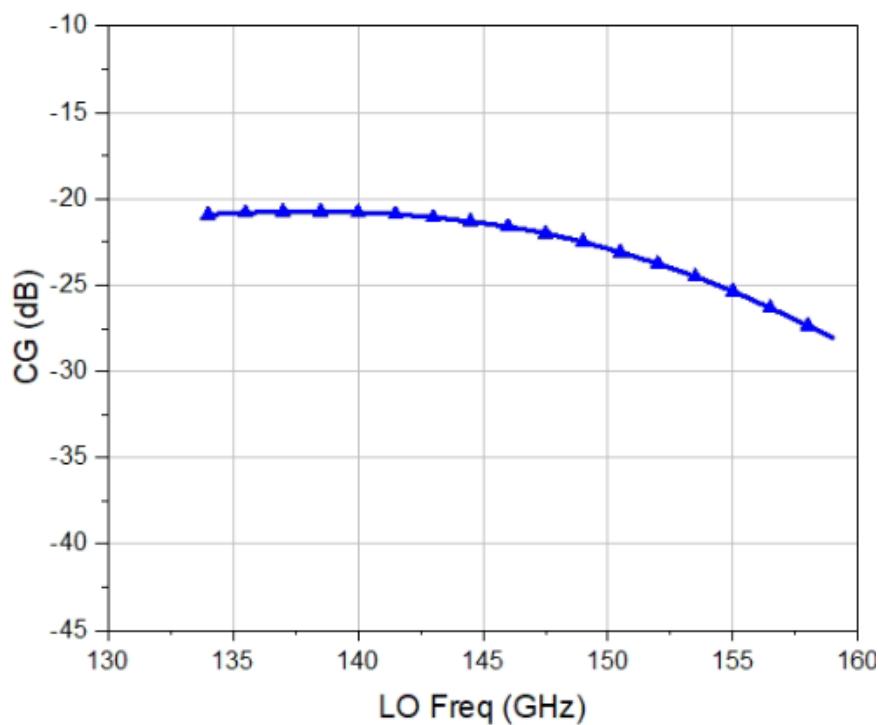

圖 3.27 為混頻器在 IF 頻率固定為 12 GHz 時，LO 頻率於 130-150 GHz 掃描之轉換增益頻率響應。模擬結果可見，轉換增益於頻段內表現穩定，最佳值出現在 LO 為 140 GHz 時轉換增益為 -16.44 dB。整體而言，設計於目標頻段 140 GHz 附近能維持穩定的轉換增益，具備良好的 LO 頻率容錯性，有利於實際應用中 LO 頻率微調與系統整合。

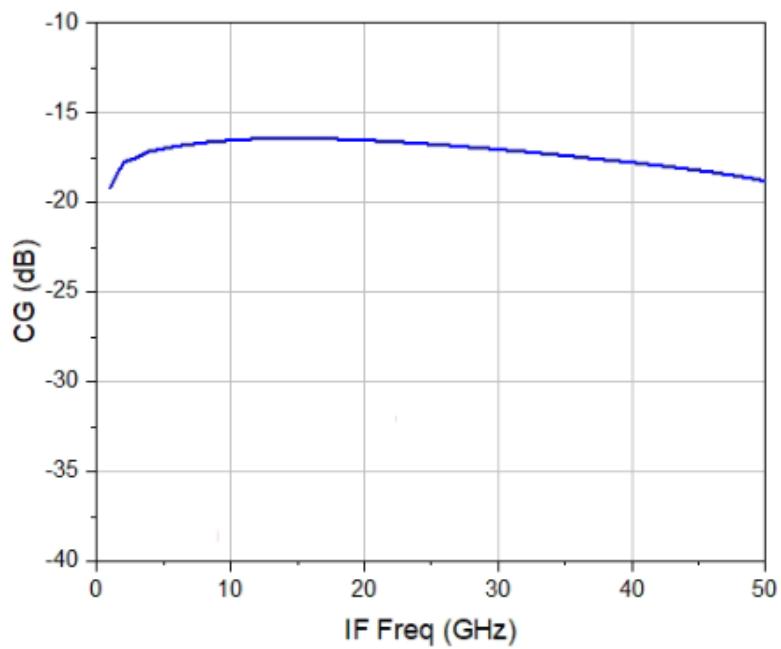

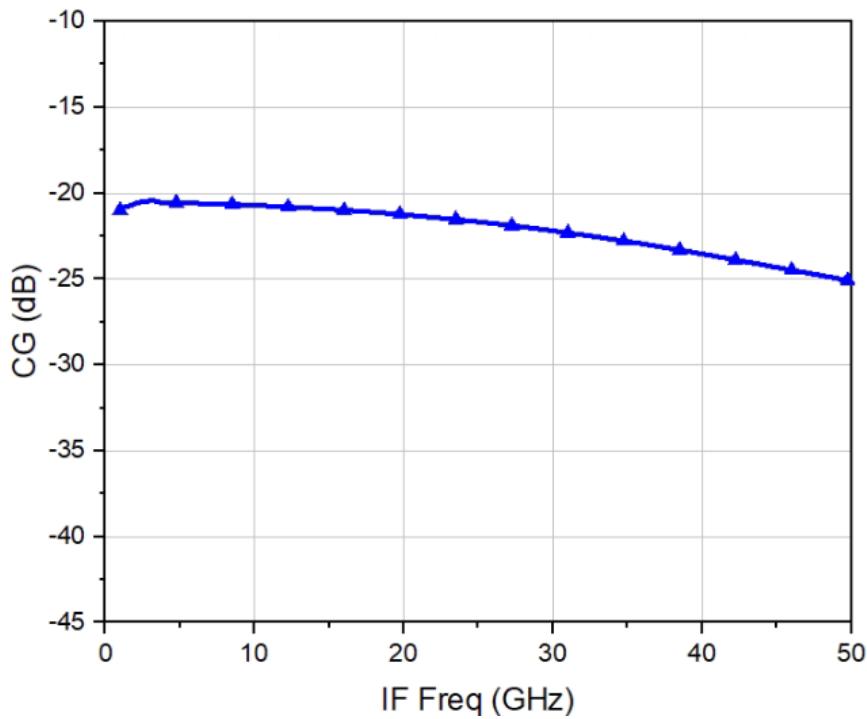

圖 3.28 為混頻器在 LO 頻率固定為 140 GHz 時，掃描不同 IF 頻率下之轉換增益響應。模擬結果顯示，於 50 GHz 內，轉換增益皆優於 -19 dB，最高值在 IF 為 13 GHz 時轉換增益為 -16.45 dB，適用於寬頻 IF 訊號處理。

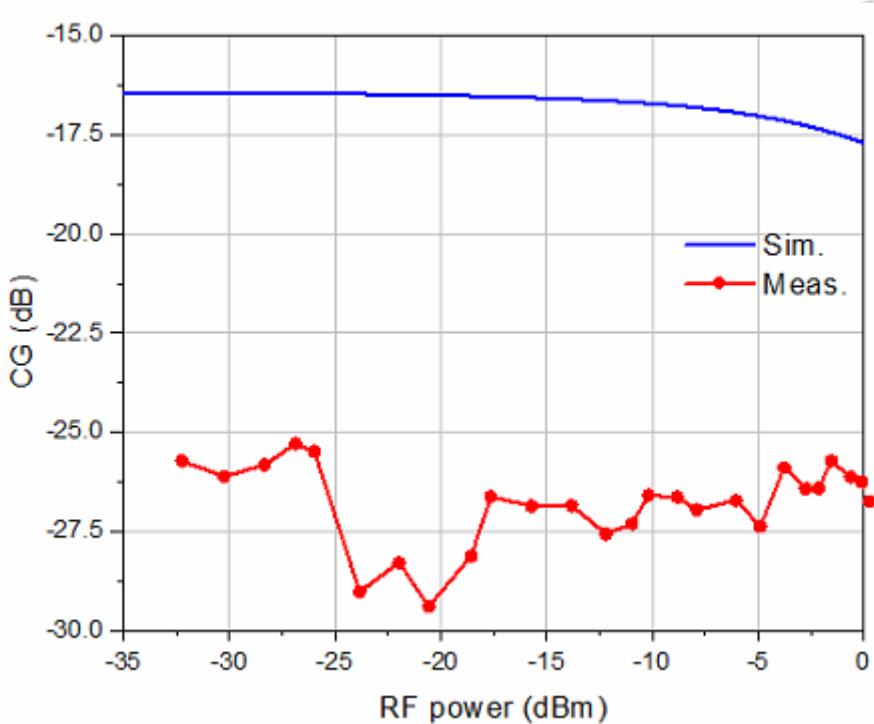

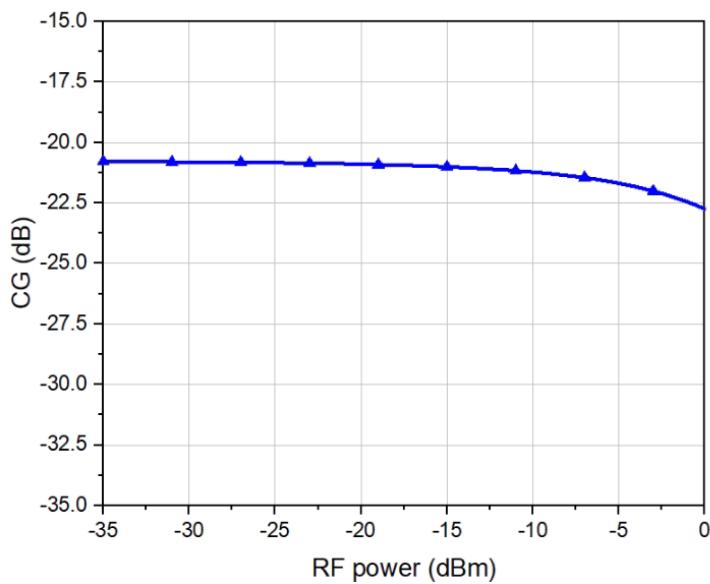

圖 3.29 顯示混頻器於 LO 頻率固定 140 GHz、RF 頻率固定 292 GHz 下，轉換增益隨著 RF 功率變化之模擬結果。隨著 RF 功率逐漸增加，轉換增益緩慢下降，對應其  $IP_{1dB}$  為 -1.5 dBm。整體而言，透過佈局優化與匹配設計，本次次諧波混頻器可同時滿足寬頻與高增益等設計目標。

圖 3.24 本文提出之串接式開關次諧波混頻器架構

圖 3.25 串接式 LO 功率對比轉換增益之模擬

圖 3.26 串接式 RF 頻率對比轉換增益之模擬

圖 3.27 串接式 LO 頻率對比轉換增益之模擬

圖 3.28 串接式 IF 頻率對比轉換增益之模擬

圖 3.29 串接式 RF 功率對比轉換增益之模擬

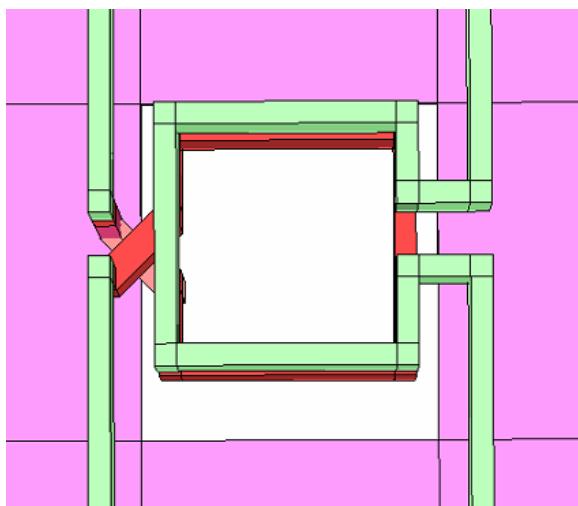

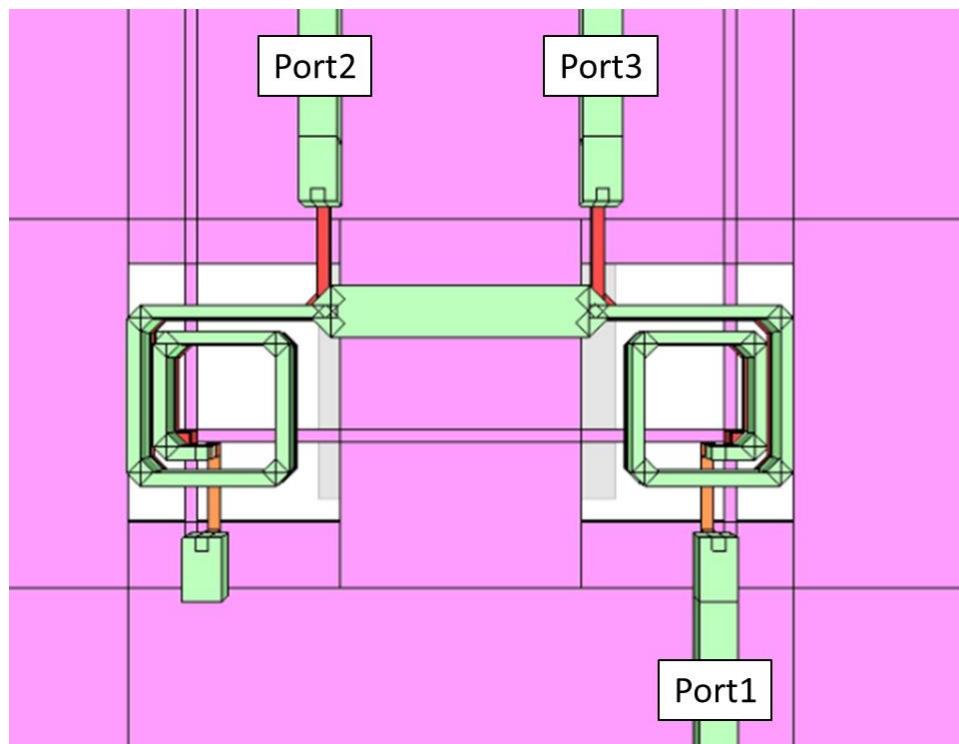

### 3.4.6 串接式 SHM 電路佈局

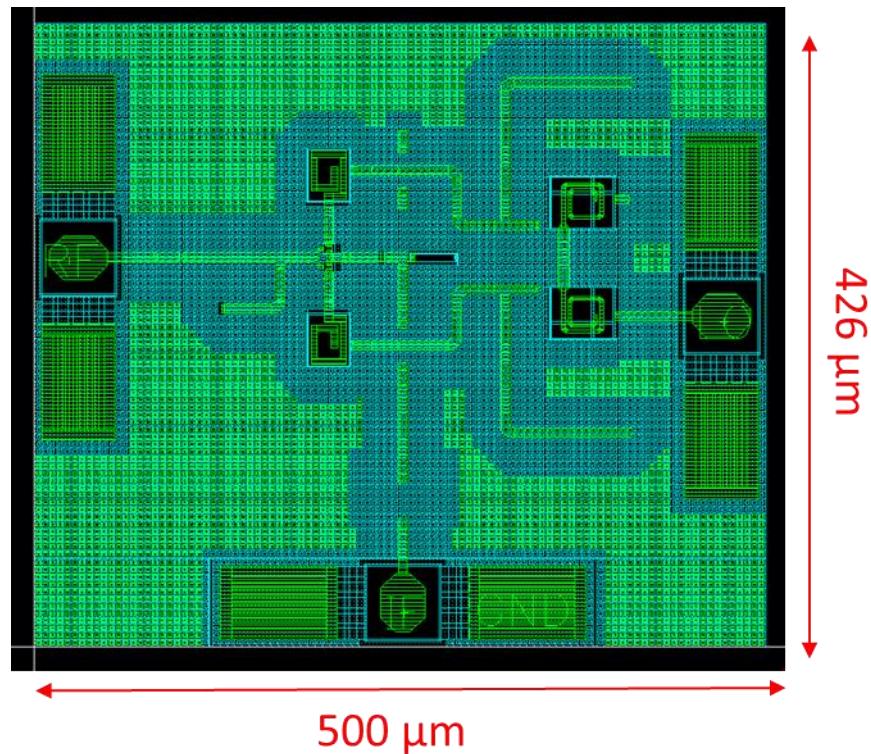

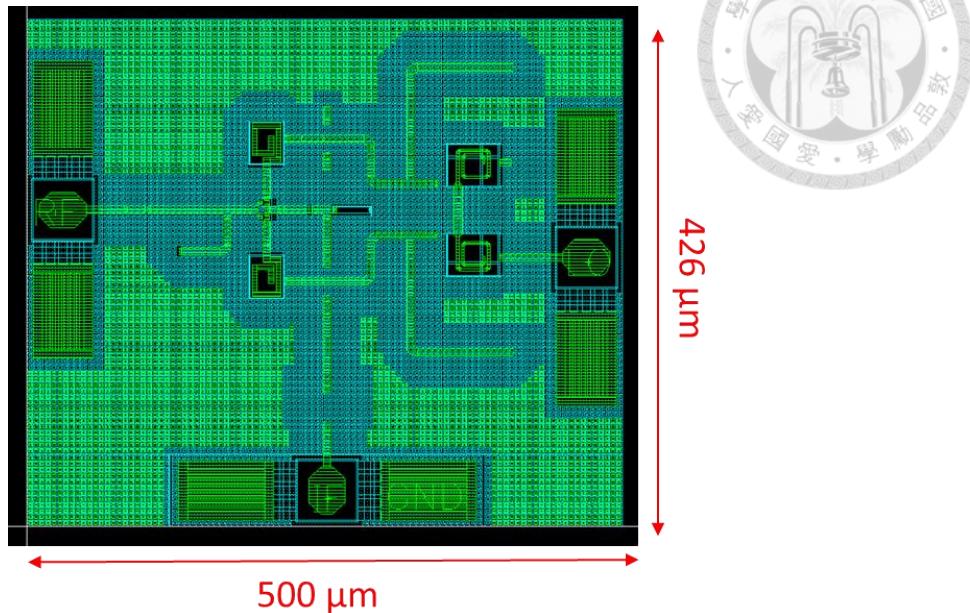

圖 3.30 為本文次諧波混頻之晶片佈局，使用 TSMC 65 nm 1P9M 製程，利用厚金屬 M9 層來進行主要射頻訊號走線與輸入輸出 pad，能減少被動元件的損耗，接地層使用 M1 及 M2 來滿足 DRC 密度限制，整體晶片大小為  $500 \times 426 \mu\text{m}^2$ 。

圖 3.30 串接式開關 SHM 電路佈局

### 3.5 串接式開關 SHM 量測與結果

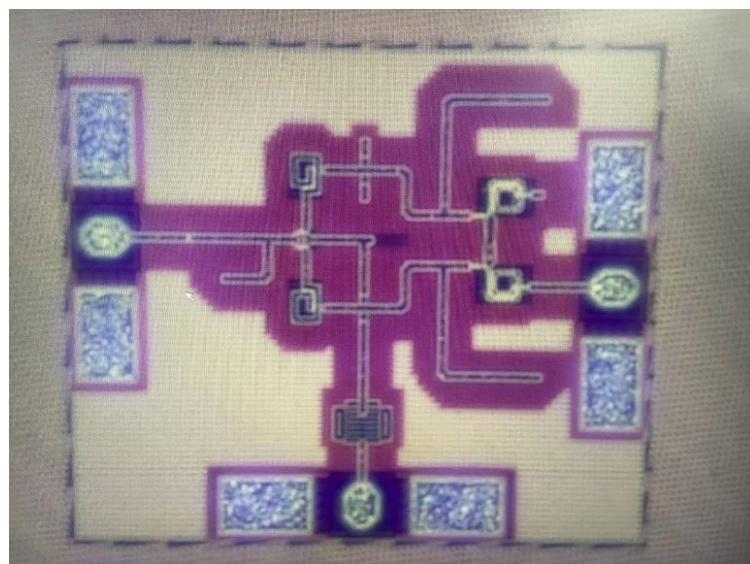

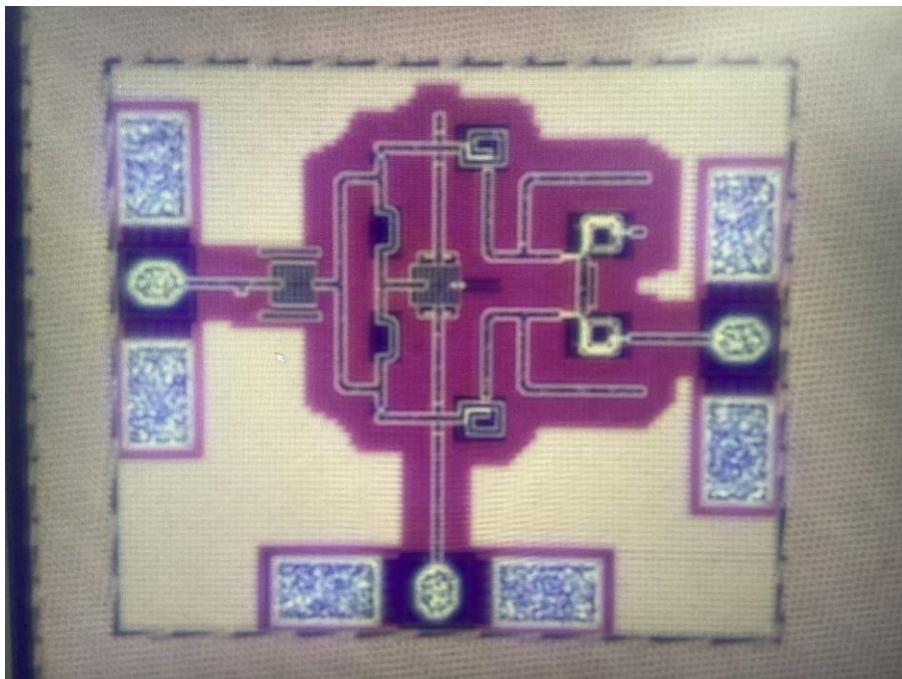

所提出的次諧波混頻器晶片圖如圖 3.31 所示，整體晶片面積包含 RF、IF 和 LO pad，總面積為  $500 \times 426 \mu\text{m}^2$ ，GSG pad 之中心到中心的間距設計為  $85 \mu\text{m}$ ，其中 GND pad 加長設計，使其可兼容不同規格探針，涵蓋  $75\text{-}100 \mu\text{m}$  間距，提升量測靈活性。考量開關電晶體採用 LO 驅動之次諧波混頻結構，電路於操作時  $V_{DS}$  及  $V_G$  為 0，不需額外使用 DC pad 及 ESD 電路，有效簡化電路結構與佈局設計。此一無偏壓結構亦使電路具備雙向操作特性，可依應用需求作為上變頻或下變頻混頻器使用，且不額外消耗直流功率，兼具高整合度與低功耗特性。

圖 3.31 串接式開關 SHM 晶片之顯微鏡圖

#### 3.5.1 串接式下變頻之轉換增益模擬與量測

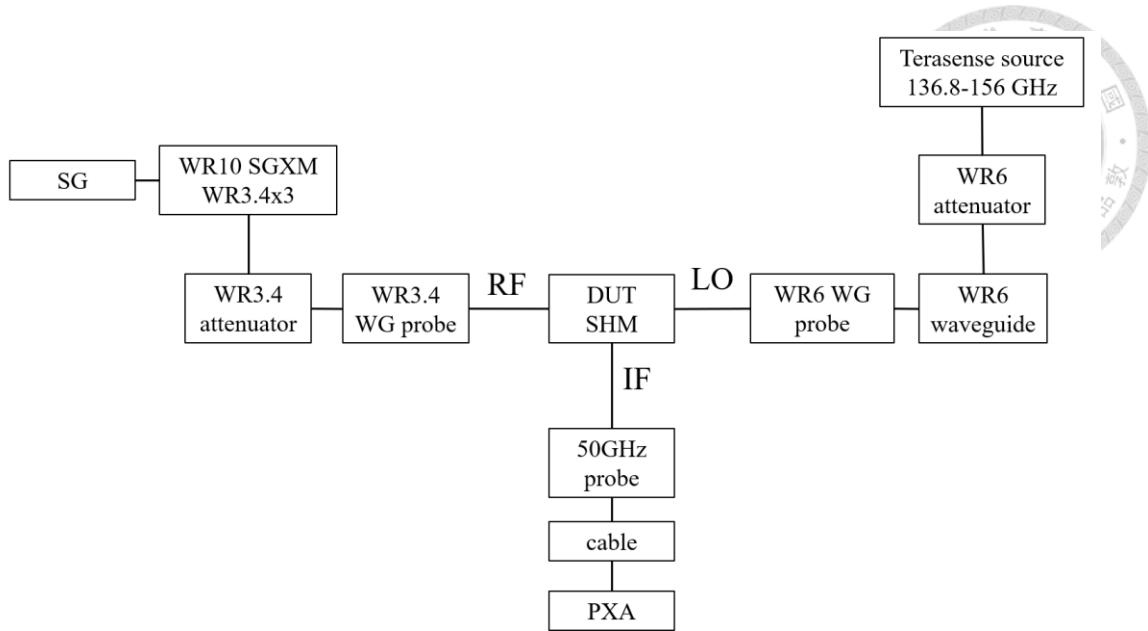

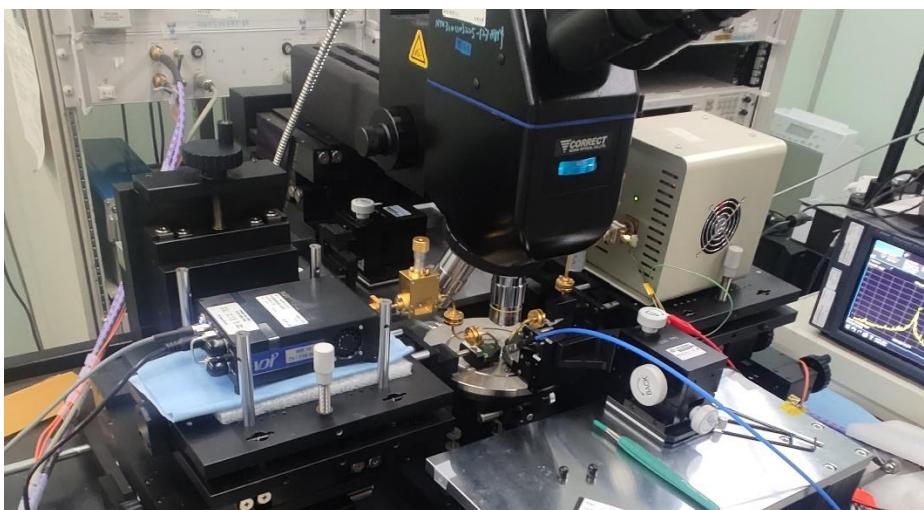

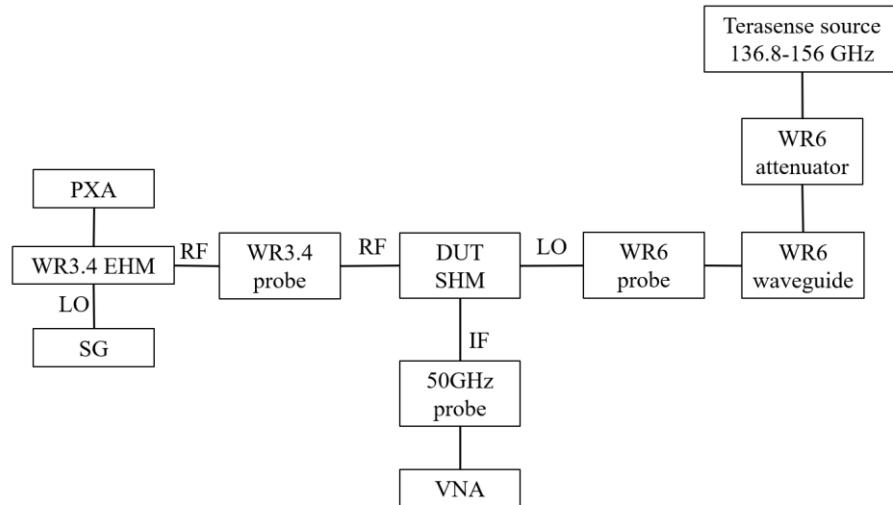

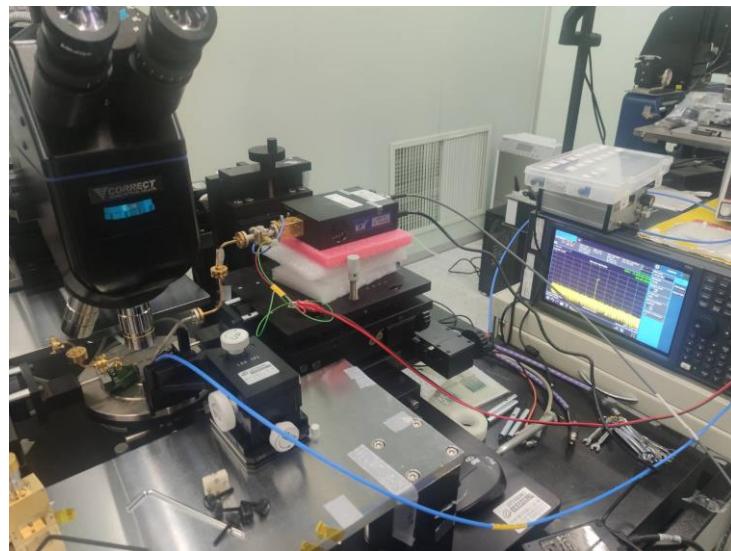

圖 3.32 和圖 3.33 為本次次諧波混頻器下變頻量測之架設圖。RF 訊號將訊號產生器 Agilent E8247C 產生的訊號經由 WR10 訊號源模組 VDI WR10 SGXM 6 倍頻上升至 75 到 110 GHz，接續透過三倍頻器 VDI WR3.4X3FUHP 至 225 到 330 GHz。由於輸出的功率約為 6 dBm 左右，超過本混頻器 RF 的  $P_{1\text{dB}}$  壓縮點，因此於 RF 端額外增加衰減器 CMI VA3R，將 RF 訊號衰減至 -25 dBm 左右，確保

量測條件符合線性操作範圍。

LO 的輸入訊號可由 Terasense 訊號源模組產生，頻率範圍涵蓋 136.8 到 156 GHz，最大輸出功率可達 20 dBm，由於該訊號源雖可主動調整輸出功率，但於調整輸出功率過程時可能會無法鎖定住頻率及功率，瞬間回饋大功率訊號至儀器可能會導致受損，故於 LO 端也額外增加 WR6 的衰減器，用以抑制過大的反射功率。IF 輸出端則為連接頻譜分析儀 Keysight PXA N9030B 用來量測降頻後的訊號大小。

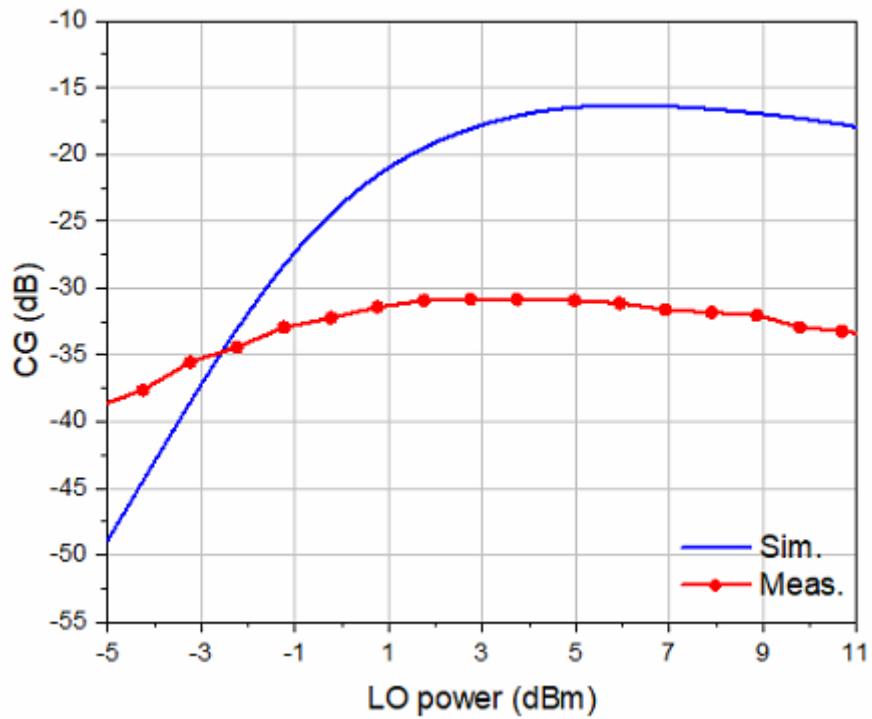

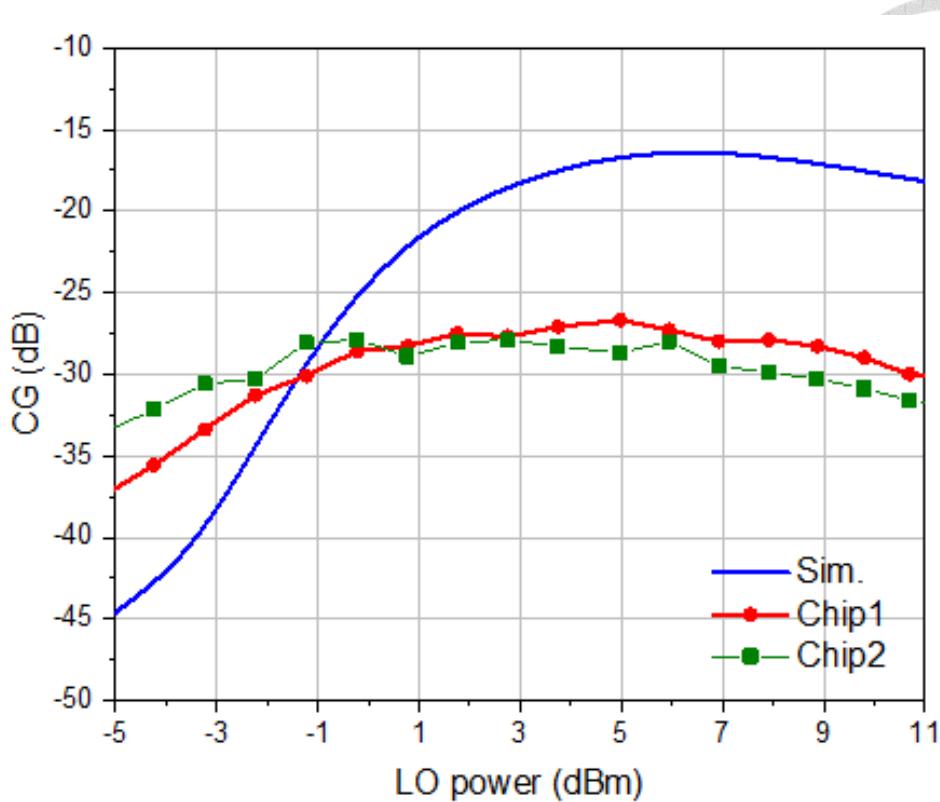

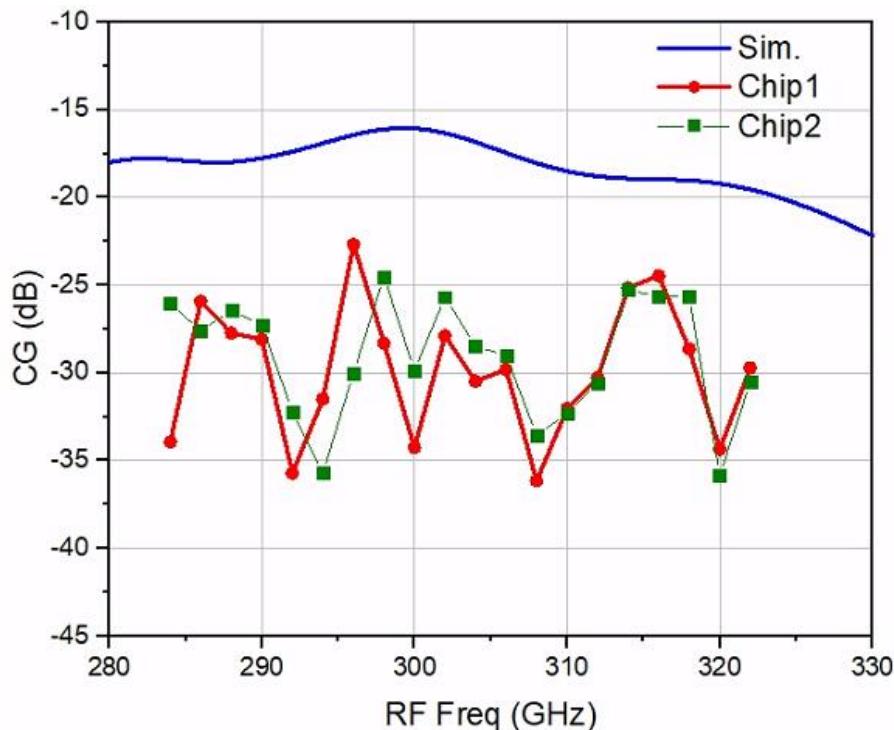

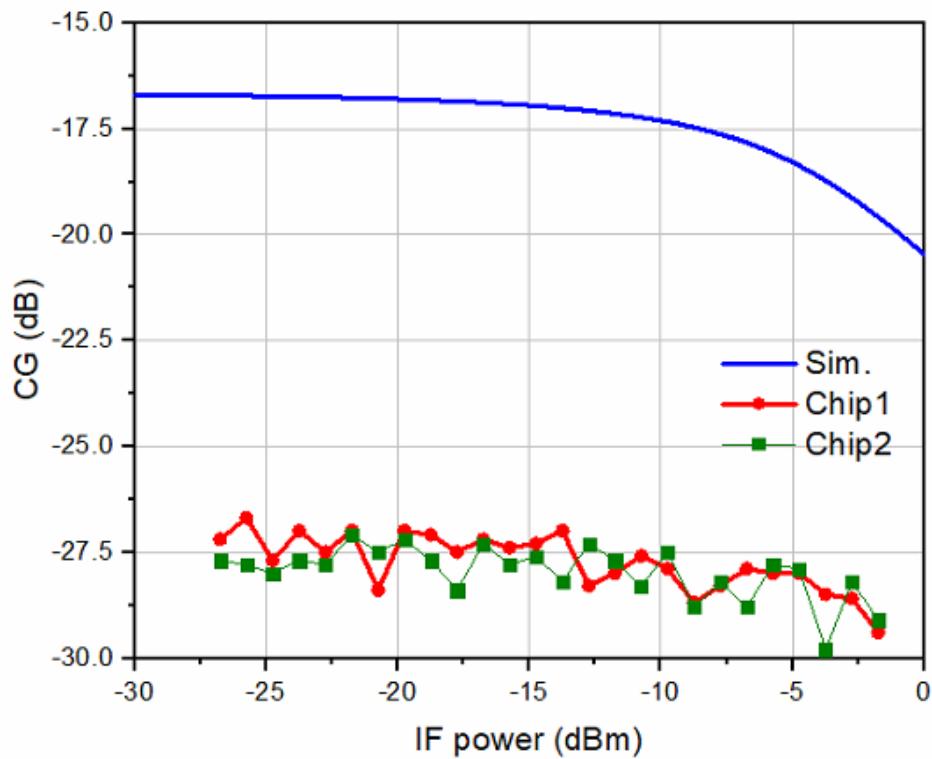

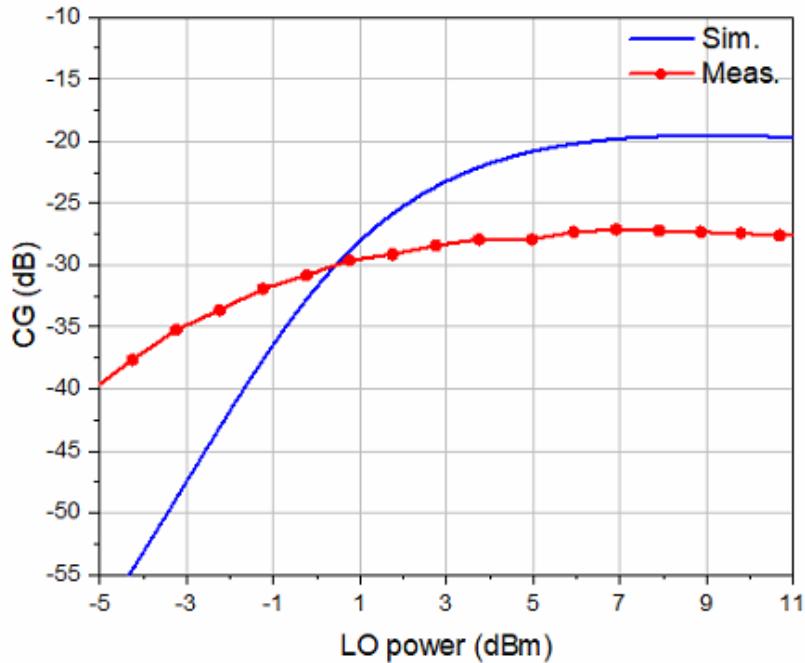

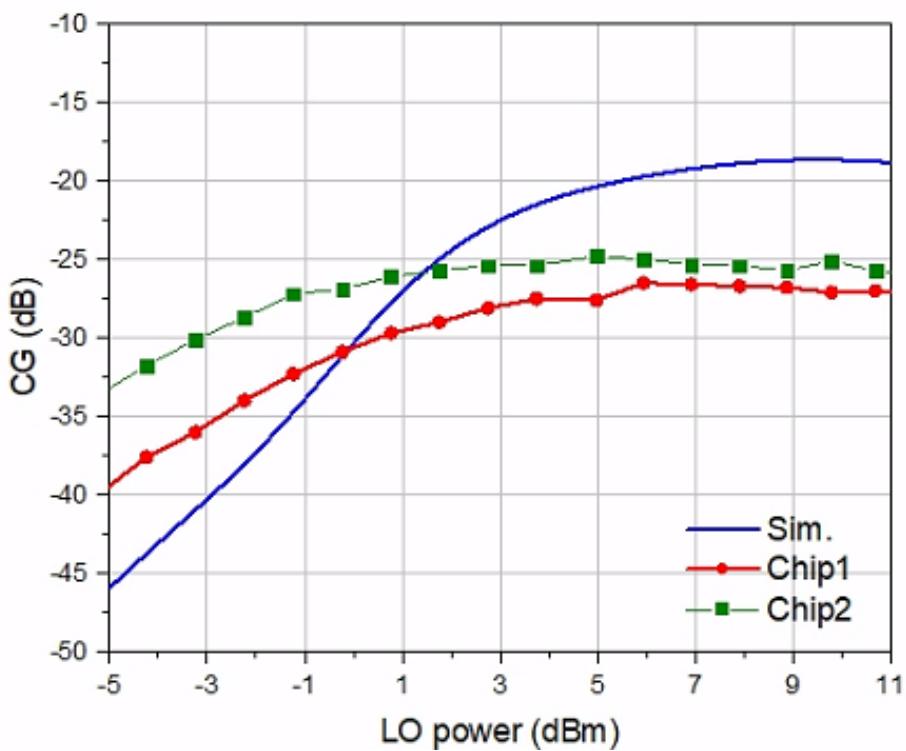

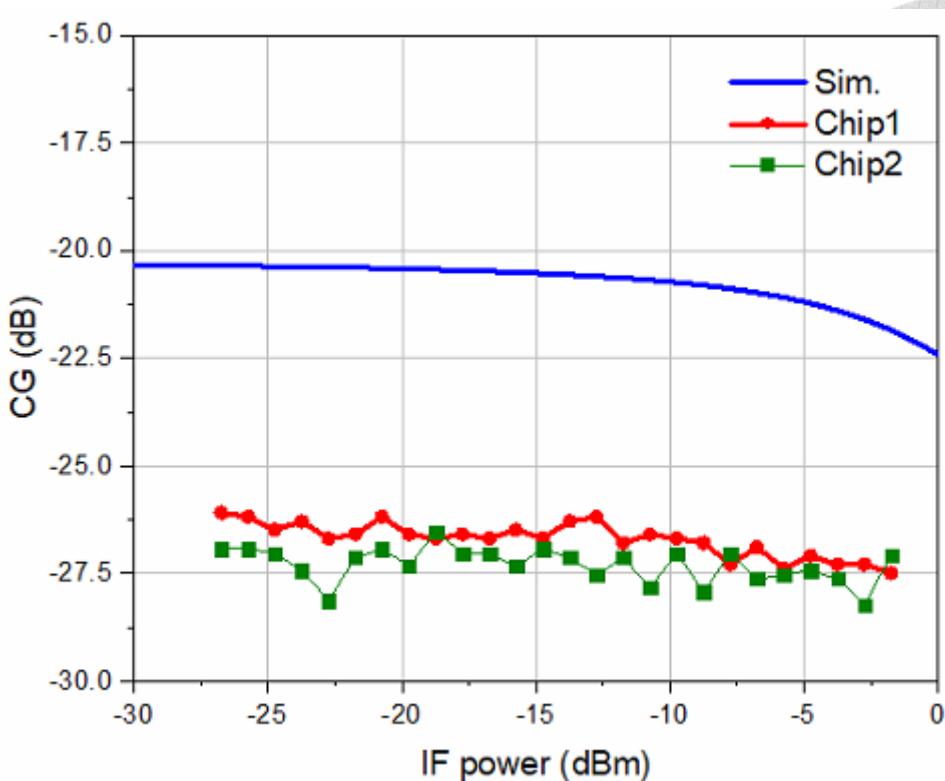

圖 3.34 為 LO 功率對比轉換增益之模擬與量測，當固定 LO 頻率為 140 GHz、RF 頻率 292 GHz 時，轉換增益峰值出現在 LO 為 5 dBm，其轉換增益為 -30.9 dBm，對比模擬的轉換增益 -16.4 dBm，雖然與模擬相差許多，但考量最佳驅動點皆落於 5 dBm，後續量測皆以此功率條件進行。

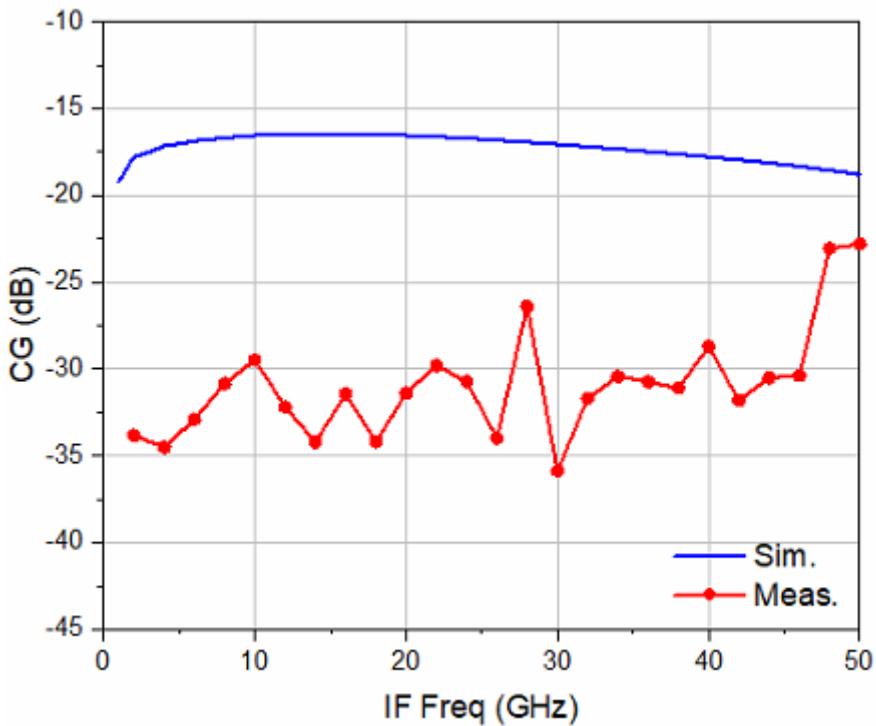

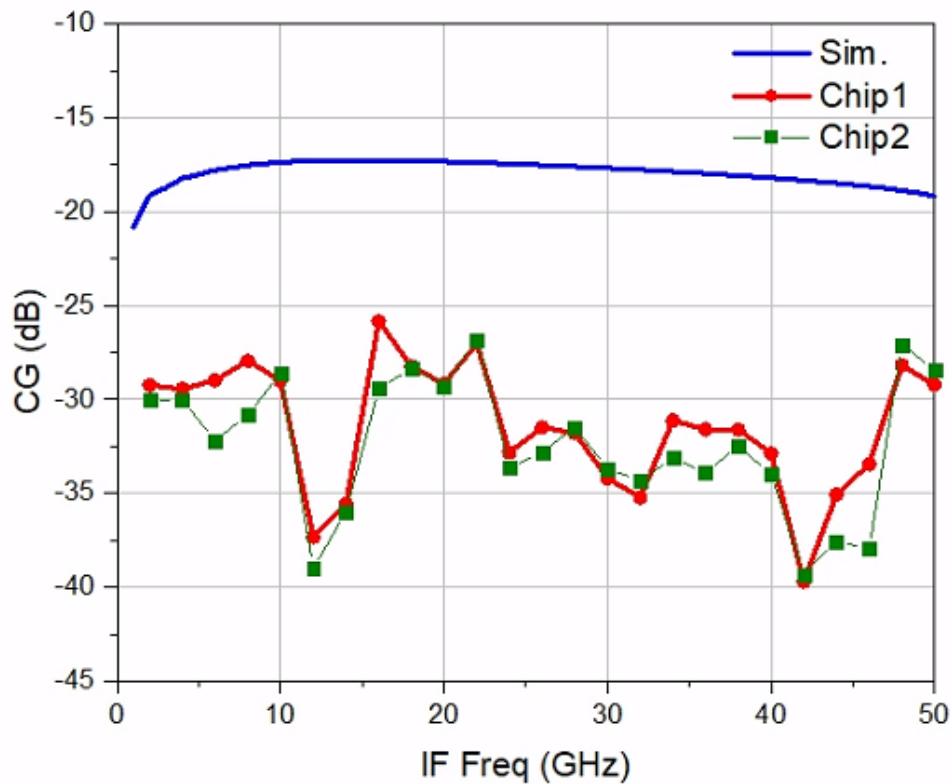

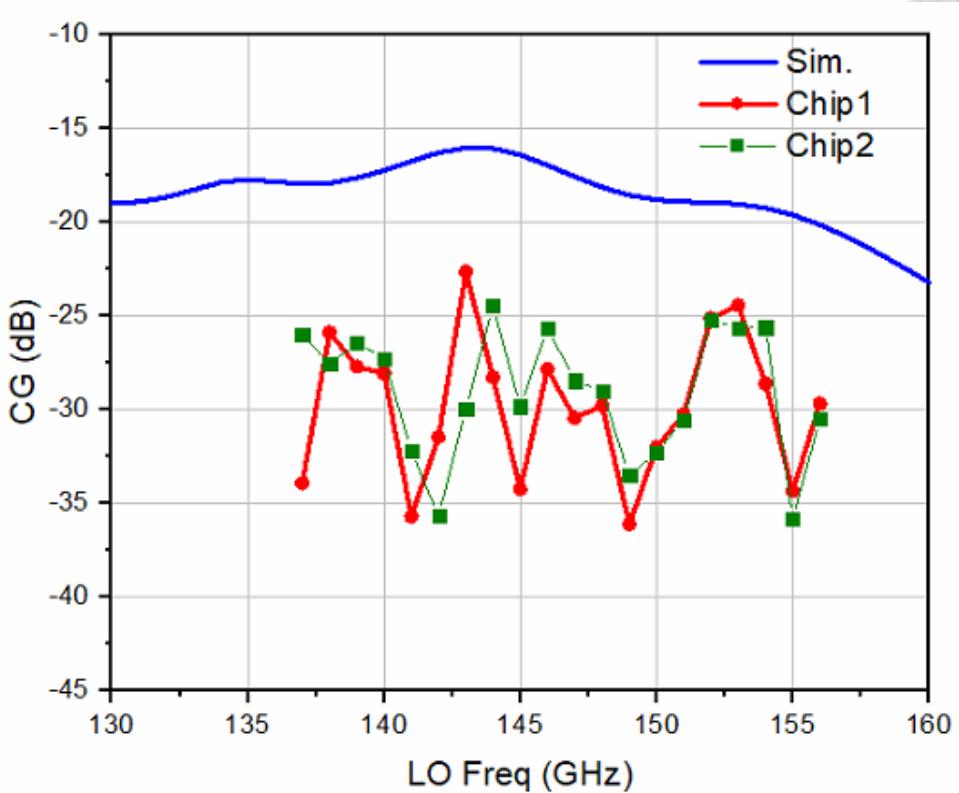

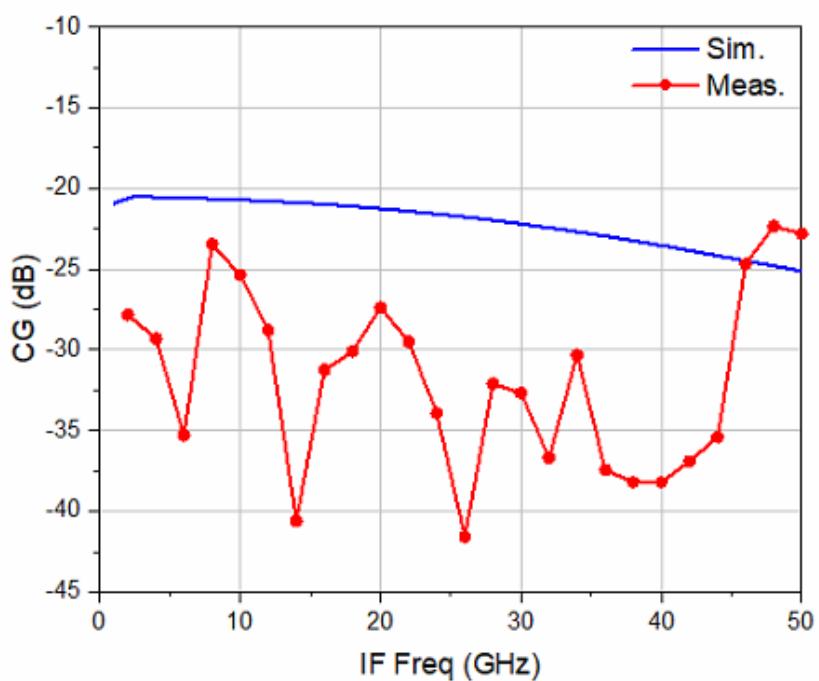

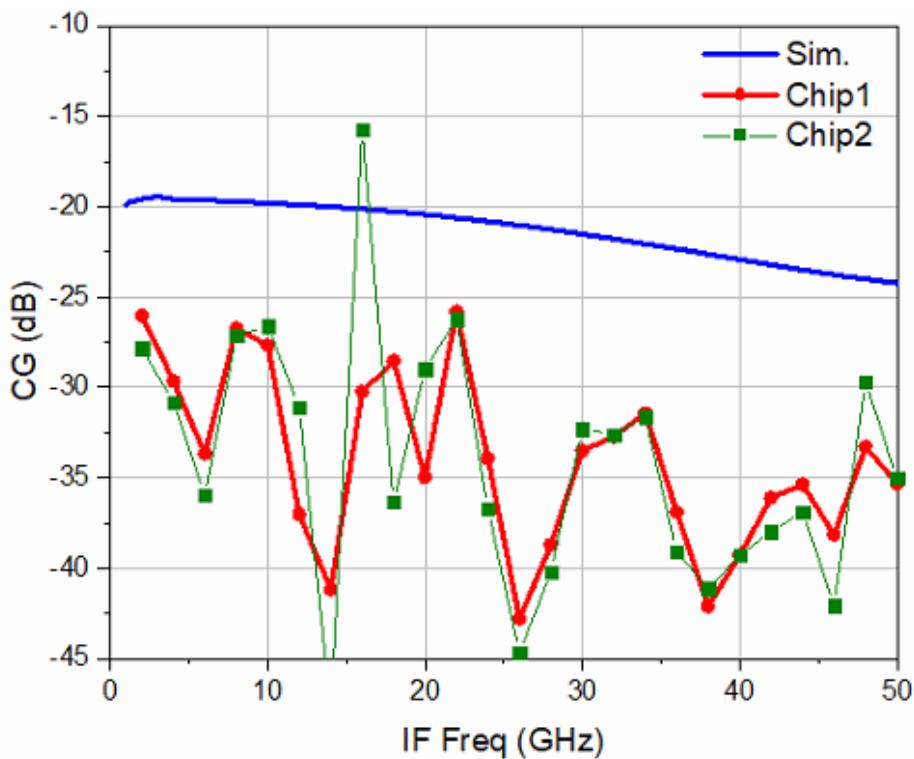

圖 3.35 為固定 LO 在 140 GHz，IF 頻率的轉換增益，量測平均轉換增益約 -31 dB，低於模擬 14 dB。圖 3.36 為 IF 在 12 GHz 時 LO 頻率的轉換增益，圖 3.3737 為 IF 在 12 GHz 時 RF 頻率的轉換增益，其相近頻率轉換增益變化較大，同樣低於模擬約 14 dB。圖 3.38 為 RF 在 292 GHz，LO 在 140 GHz，RF 功率之轉換增益，轉換增益約為 -27 dB，但隨著 RF 輸入功率增加，趨勢較不穩定，無法明確觀察出  $P_{1dB}$ 。整體而言，量測結果與模擬在頻率響應趨勢差不多，但整體轉換增益低於模擬約 15 dB，並且數值較為不穩。

圖 3.32 下變頻之量測架設方塊圖

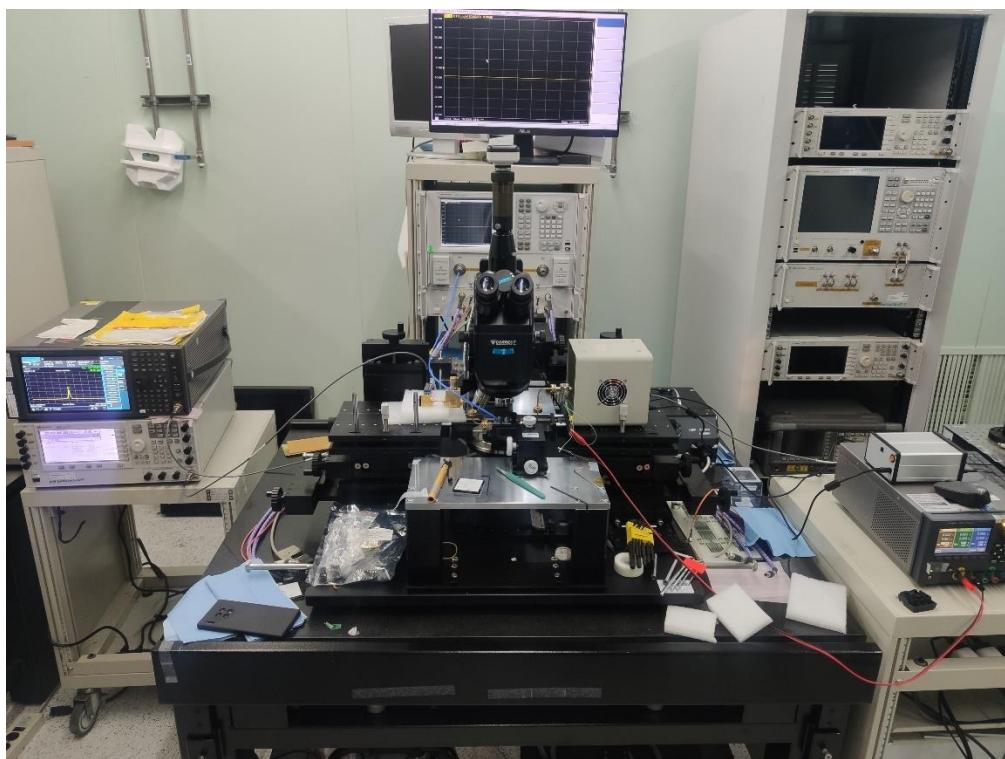

圖 3.33 下變頻量測實際架設圖

圖 3.34 串接式 LO 功率對比轉換增益下變頻之量測

圖 3.35 串接式 IF 頻率對比轉換增益下變頻之量測

圖 3.36 串接式 LO 頻率對比轉換增益下變頻之量測

圖 3.37 串接式 RF 頻率對比轉換增益下變頻之量測

圖 3.38 串接式 RF 功率對比轉換增益下變頻之量測

### 3.5.2 串接式上變頻之轉換增益模擬與量測

圖 3.39 和圖 3.40 為上變頻之量測架設, IF 訊號可透過 Agilent PNA E8361C 做為輸入。LO 的輸入訊號可由 Terasense 訊號源模組產生, 能在 136.8 到 156 GHz 產生最大 20 dBm 的功率, 並且額外加入 WR6 衰減器, 來避免儀器反射功率過大造成損毀。RF 輸出端因頻率在 300 GHz 且輸出功率太小無法使用功率計做為量測, 因此需額外接下變頻器 VDI WR3.4EHM 至 1 GHz, 訊號產生器 Agilent E8247C 做為此下變頻器的 LO, 最後輸出接上 Keysight PXA N9030B 來量測降頻後的訊號大小。

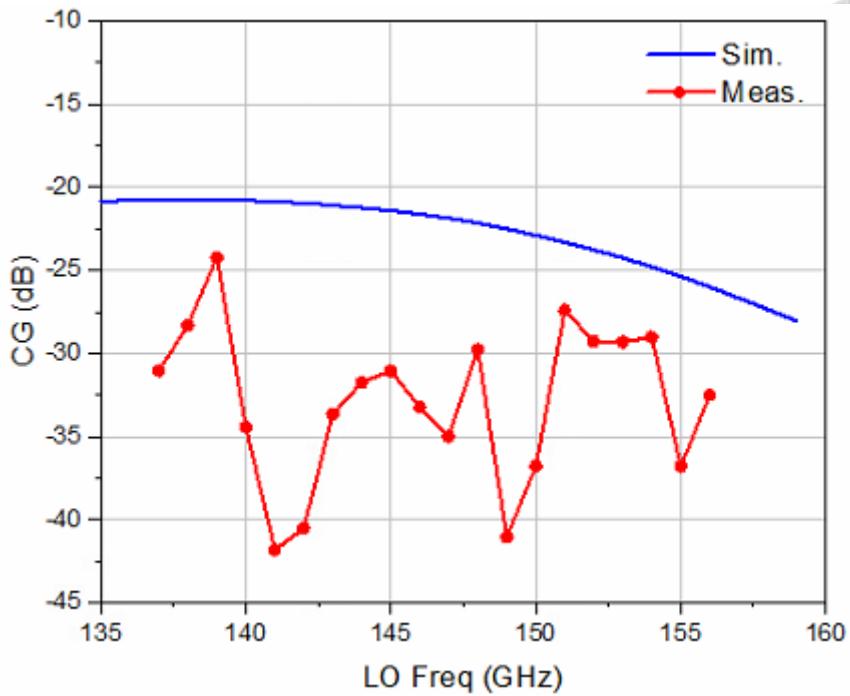

圖 3.41 為 LO 功率對比轉換增益之模擬與量測, 當固定 LO 為 140 GHz 時, 峰值在 LO 為 5 dBm 時, 量測之轉換增益為 -26.6 dBm, 對比模擬的轉換增益 -16.5 dBm, 與模擬相差 10 dB, 後續皆以最佳 LO 的功率 5 dBm 來做量測。

圖 3.42 為固定 LO 在 140 GHz, IF 頻率的轉換增益, 平均轉換增益約 -32 dB,

低於模擬 15 dB。圖 3.43 圖 3.36 為 IF 在 10 GHz 時，LO 頻率的轉換增益平均為-30 dB，圖 3.44 為 IF 在 10 GHz 時，RF 頻率的轉換增益平均為-30 dB，其相近頻率變化較大，低於模擬約 13 dB。圖 3.45 為 RF 在 290 GHz，LO 在 140 GHz，RF 功率對比的轉換增益，轉換增益約為-27.5 dB，IP<sub>1dB</sub> 為-10 dBm。

圖 3.39 上變頻之量測架設方塊圖

圖 3.40 上變頻量測實際架設圖

圖 3.41 串接式 LO 功率對比轉換增益上變頻之量測

圖 3.42 串接式 IF 頻率對比轉換增益上變頻之量測

圖 3.43 串接式 LO 頻率對比轉換增益上變頻之量測

圖 3.44 串接式 RF 頻率對比轉換增益上變頻之量測

圖 3.45 串接式 IF 功率對比轉換增益上變頻之量測

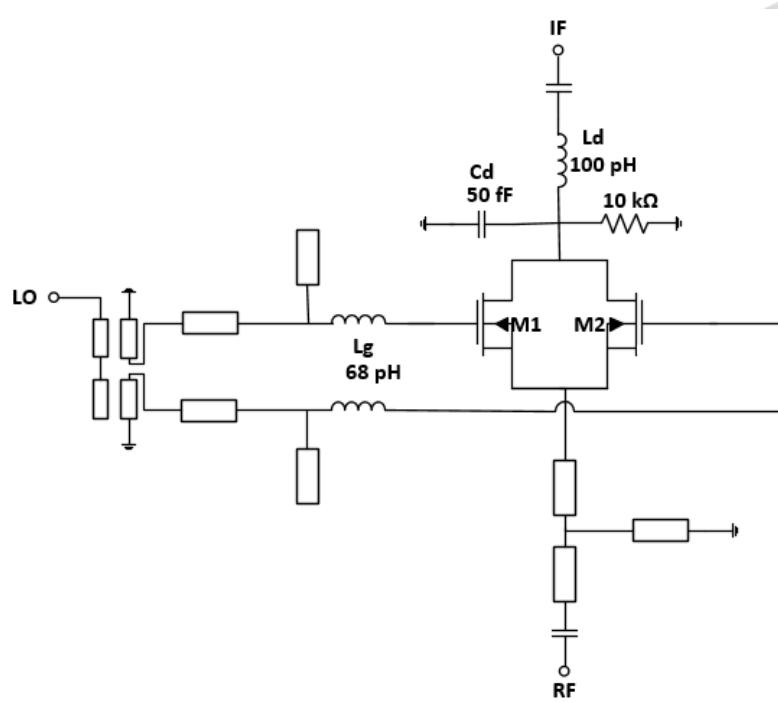

### 3.6 並接式開關 SHM 電路架構

本文提出第二種之次諧波混頻器架構，仍採用電阻式之次諧波雙開關混頻器。原理，如圖 3.46 所示，整體由兩個電晶體 M1 與 M2 所構成，並透過互補的差動 LO 控制電晶體開關，形成交錯導通與截止效果。這兩個電晶體開關分別與 IF 和 RF 並接，在此稱為並接式開關 SHM。本設計中無額外  $V_g$  與  $V_d$  偏壓供應，使其操作於弱反轉區附近。此設計可有效的簡化偏壓電路無額外功耗，同時透過其非線性導通行為產生所需之二次諧波，實現次諧波混頻功能。

圖 3.46 並接式開關 SHM 電路架構

由於 M1 與 M2 僅由 LO 訊號交錯控制導通，其導通狀態可視為隨時間變化的非線性電阻函數，如圖 3.47 所示分別記為當電晶體導通時  $R_{on}(\omega_{Lo}t)$ ，與電晶體處於截止時  $R_{off}(\omega_{Lo}t + \pi)$ ，兩者形成交錯開關， $L_1$  用來與開關的寄生電容共振。當 M1 電晶體為導通時，低阻抗會經過  $\frac{1}{4}\lambda$ ，使 RF 端看進去為高阻抗  $ROFF(\omega_{Lo}t)$ 。反之，M2 電晶體關閉時，高阻抗會經過  $\frac{1}{4}\lambda$ ，使 RF 端看進去為低阻抗  $RON(\omega_{Lo}t + \pi)$ 。這兩種阻抗會隨著 LO 呈現週期性變化，如同(3.2)式與圖 3.7 之原理，所有奇次諧波成分將互相抵消，僅保留偶數次項，其中以  $(2\omega_{Lo}t)$  為最主要分量。當 RF 注入該節點後，與此 2LO 進行非線性乘積，即可實現次諧波混頻。

此種  $\frac{1}{4}\lambda$  傳輸線與開關結構的組合，等效於對 RF 頻率下的  $R_{on}$  與  $R_{off}$  進行阻抗變換，預期使兩者阻抗比值進一步放大，增強開關狀態的分離效果，有助於提升轉換增益與抑制洩漏，實現更有效率的次諧波混頻轉換。

圖 3.47 並接式開關 SHM 等效電阻模型

## 3.7 並接式開關 SHM 電路設計與流程

### 3.7.1 並接式電路設計

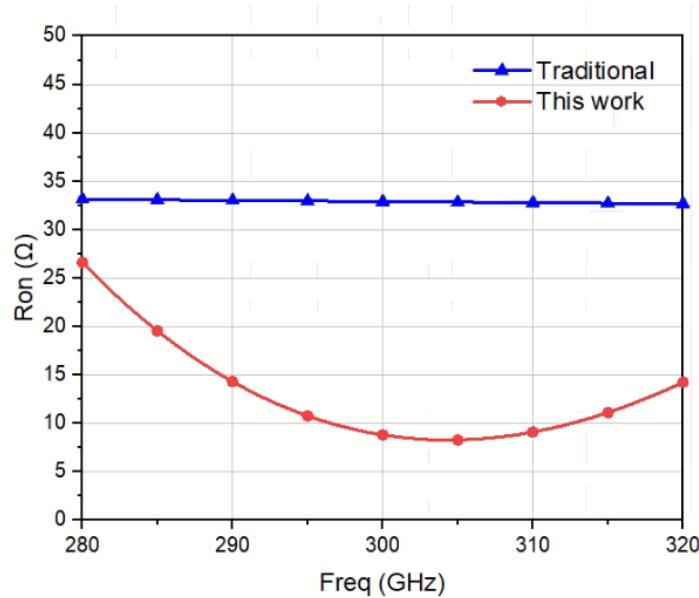

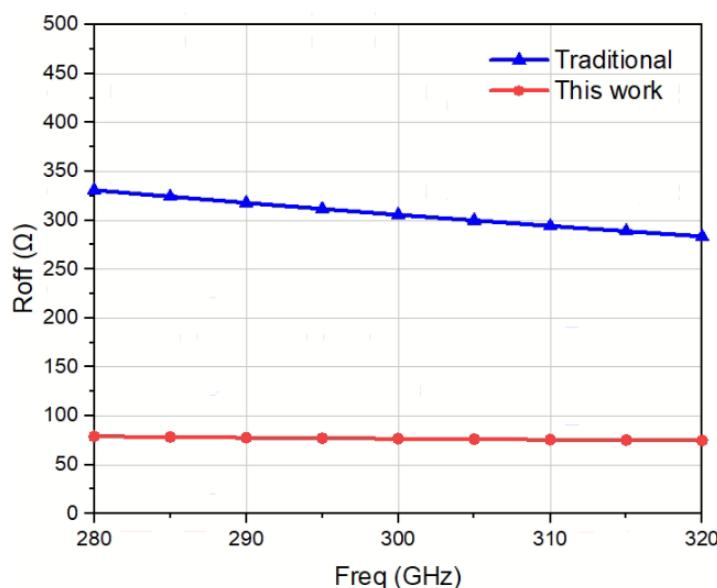

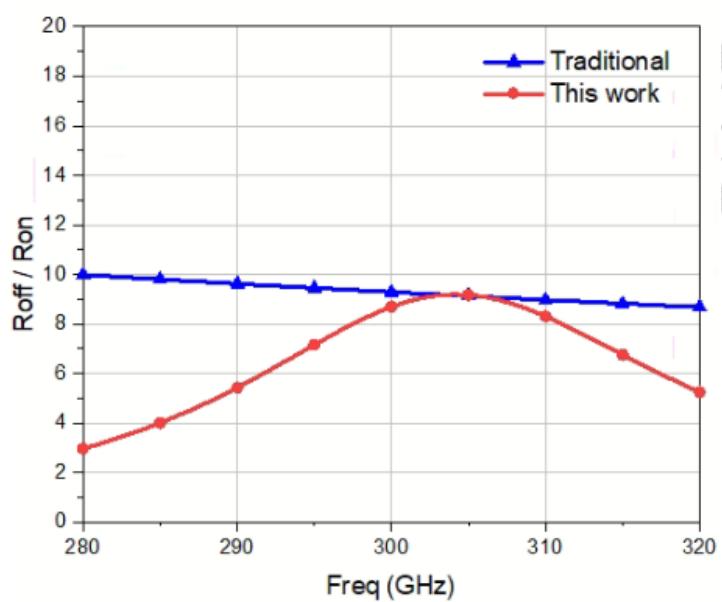

並接式開關次諧波混頻 SHM 電路的架構與前述串接式開關 SHM 架構高度相似，主要差異在於開關電晶體的連接位置改為並聯配置而非串聯。因此，在設計流程上，馬遜巴倫的設計、開關電晶體尺寸的選擇以及走線方式皆沿用相同的方法。相關設計細節已於第 3.4 節論述，在此不再贅述。

在  $R_{on}$  與  $R_{off}$  性能方面，模擬結果如圖 3.48 和圖 3.49 顯示，由於開關位置的改變，本並接式架構可以利用四分之一波長傳輸線的阻抗轉換來顯著降低導通電阻  $R_{on}$ ，其  $R_{on}$  數值甚至優於傳統串接式開關架構所達到的水準。然而，由

於電晶體本身的  $R_{on}$  在 300 GHz 下約為  $33 \Omega$ ，並未低至理想值，經過  $\frac{1}{4}\lambda$  阻抗

轉換後， $R_{off}$  未能如預期般獲得提升，反而低於傳統架構下的  $R_{off}$ 。因此如圖 3.50 所示，整體的  $R_{off} / R_{on}$  比值隨之下降。

整體而言，本並接式開關 SHM 架構在混頻效率與訊號隔離方面並未展現出明顯的優勢。然而，作為一種新穎的次諧波混頻電路架構，此設計仍具備可行性，提供了一個值得進一步探索與研究的方向。

圖 3.48 串接與並接式之  $R_{on}$  頻率響應比較

圖 3.49 串接與並接式之  $R_{off}$  頻率響應比較

圖 3.50 串接與並接式之  $R_{OFF}/R_{ON}$  頻率響應比較

### 3.7.2 並接式 SHM Post-sim 結果

圖 3.46 為本文的次諧波混頻器電路架構，於最終佈局後模擬下，當 RF 頻率為 292 GHz、LO 頻率為 140 GHz 時進行下變頻，圖 3.51 顯示了混頻器轉換增益隨 LO 輸入功率變化之關係，隨著 LO 功率增加，轉換增益亦逐漸提升，並於 LO 輸入功率達 5 dBm 時趨於飽和，對應了最佳驅動區間。當 LO 功率過低時，由於開關電晶體導通不完全，造成轉換增益快速下降，影響混頻效率。綜合考量轉換增益與 LO 功率需求，本文後續設計與模擬皆以 LO 為 5 dBm 來做為操作條件。

圖 3.52 為混頻器在 IF 頻率固定為 12 GHz 時，轉換增益隨 RF 輸入頻率變化之模擬結果。於 RF 頻率 288 GHz 時，轉換增益為最佳值 -20.73 dB。3 dB 頻寬可涵蓋 280-315 GHz，展現出本設計於 RF 端具備寬頻操作特性。

圖 3.53 為混頻器在 IF 頻率固定為 12 GHz 時，LO 頻率於 130-150 GHz 掃描之轉換增益頻率響應。模擬結果可見，轉換增益於頻段內表現穩定，最佳值出現在 LO 為 138 GHz 時轉換增益為 -20.73 dB。整體而言，設計於目標頻段 140 GHz

附近能維持穩定的轉換增益，具備良好的 LO 頻率容錯性，有利於實際應用中 LO 頻率微調與系統整合。

圖 3.54 為混頻器在 LO 頻率固定為 140 GHz 時，掃描不同 IF 頻率下之轉換增益響應。模擬結果顯示，於 40 GHz 內，轉換增益皆優於 -23.35 dB，最高值在 IF 為 3 GHz 時轉換增益為 -20.35 dB，適用於寬頻 IF 訊號處理。

圖 3.55 顯示混頻器於 LO 頻率固定 140 GHz、RF 頻率固定 292 GHz 下，轉換增益隨著 RF 功率變化之模擬結果。隨著 RF 功率逐漸增加，轉換增益緩慢下降，對應其  $IP_{1dB}$  為 -4.5 dBm。整體而言，透過佈局優化與匹配設計，本次次諧波混頻器可同時滿足寬頻與高增益等設計目標。

圖 3.51 並接式 LO 功率對比轉換增益之模擬

圖 3.52 並接式 RF 頻率對比轉換增益之模擬

圖 3.53 並接式 LO 頻率對比轉換增益之模擬

圖 3.54 並接式 IF 頻率對比轉換增益之模擬

圖 3.55 並接式 RF 功率對比轉換增益之模擬

### 3.7.3 並接式 SHM 電路佈局

圖 3.56 為並接式次諧波混頻之晶片佈局，使用 TSMC 65 nm 1P9M 製程，利用厚金屬 M9 層來進行主要射頻訊號走線與輸入輸出 pad，能減少被動元件的損耗，接地層使用 M1 及 M2 來滿足 DRC 密度限制，整體晶片大小為  $500 \times 426$

$\mu\text{m}^2$ 。

圖 3.56 並接式開關 SHM 電路佈局

### 3.8 並接式開關 SHM 量測與結果

所提出的次諧波混頻器晶片圖如圖 3.57 所示，晶片面積包含 RF、IF 和 LO pad 總面積為  $500 \times 426 \mu\text{m}^2$ ，GSG pad 之中心到中心的間距設計為  $85 \mu\text{m}$ ，其中 GND pad 加長設計，使其可兼容不同規格探針，涵蓋  $75\text{-}100 \mu\text{m}$  間距，提升量測靈活性。考量開關電晶體採用 LO 驅動之次諧波混頻結構，電路於操作時  $V_{DS}$  及  $V_G$  為 0，不需額外使用 DC pad 及 ESD 電路，有效簡化電路結構與佈局設計。此一無偏壓結構亦使電路具備雙向操作特性，可依應用需求作為上變頻或下變頻混頻器使用，且不額外消耗直流功率，兼具高整合度與低功耗特性。

圖 3.57 並接式開關 SHM 晶片之顯微鏡圖

### 3.8.1 並接式下變頻之轉換增益模擬與量測

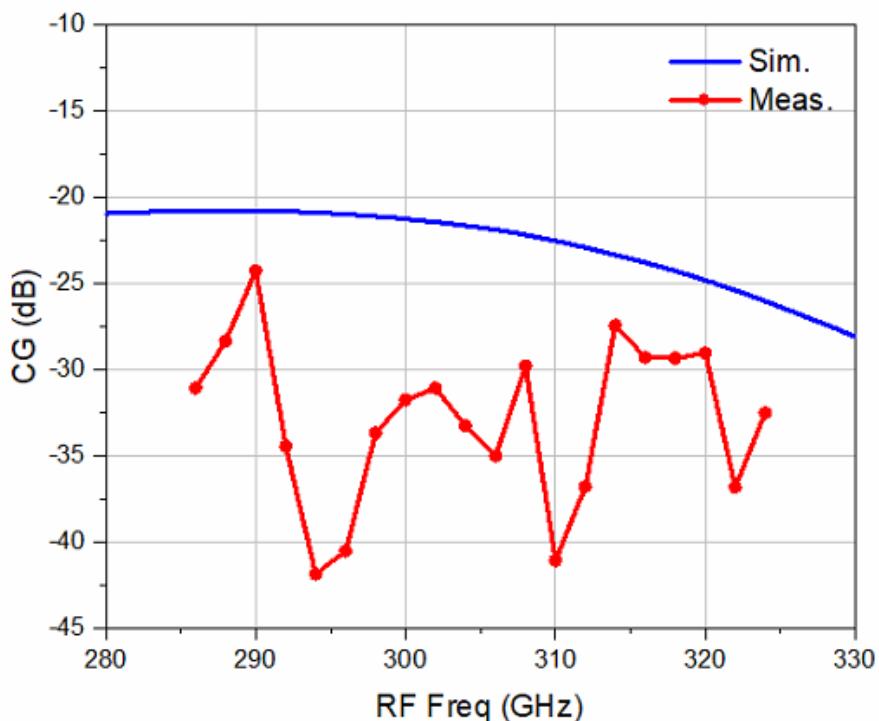

量測架設與 71 相同，量測架設圖可參照圖 3.32 及圖 3.33。圖 3.58 為 LO 功率對比轉換增益之模擬與量測，當固定 LO 為 140 GHz 時，峰值在 LO 為 7 dBm 時，量測之轉換增益為 -27.1 dBm，對比模擬的轉換增益 -19.8 dBm，與模擬相比下降 7.3 dB，考量與前電路做對比，後續皆以 LO 的功率 5 dBm 來做量測。圖 3.59 為固定 LO 在 140 GHz，IF 頻率的轉換增益，量測平均轉換增益約 -35 dB，低於模擬 13 dB。圖 3.60 為 IF 在 12 GHz 時 LO 頻率的轉換增益平均為 -34 dB，圖 3.61 為 IF 在 12 GHz 時 RF 頻率的轉換增益，其相近頻率轉換增益變化較大，平均低於模擬約 13 dB。圖 3.62 為 RF 在 292 GHz，LO 在 140 GHz，RF 功率之轉換增益，轉換增益約為 -31 dB。整體而言，量測結果與模擬在頻率響應趨勢差不多，但整體轉換增益低於模擬約 13 dB，並且數值較為不穩。

圖 3.58 並接式 LO 功率對比轉換增益下變頻之量測

圖 3.59 並接式 IF 頻率對比轉換增益下變頻之量測

圖 3.60 並接式 LO 頻率對比轉換增益下變頻之量測

圖 3.61 並接式 RF 頻率對比轉換增益下變頻之量測

圖 3.62 並接式 RF 功率對比轉換增益下變頻之量測

### 3.8.2 並接式上變頻之轉換增益模擬與量測

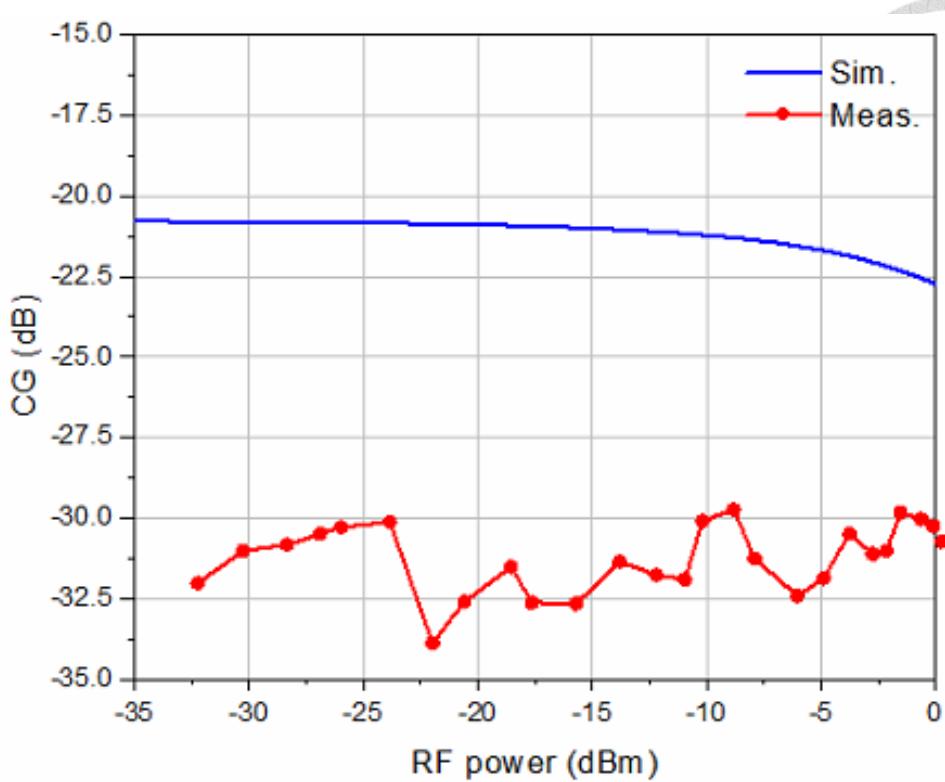

量測架設與 76 相同，量測架設圖可參照圖 3.39 及圖 3.40。圖 3.63 為 LO 功率對比轉換增益之模擬與量測，當固定 LO 為 140 GHz 時，峰值在 LO 為 5 dBm 時，量測之轉換增益為 -24.7 dBm，對比模擬的轉換增益 -20.3 dBm，與模擬相差 4.3 dB，後續皆以最佳 LO 的功率 5dBm 來做量測。圖 3.64 為固定 LO 在 140 GHz，IF 頻率的轉換增益，平均轉換增益約 -35 dB，低於模擬約 14 dB。圖 3.65 圖 3.36 為 IF 在 10 GHz 時，LO 頻率的轉換增益平均為 -30 dB，圖 3.66 為 IF 在 10 GHz 時，RF 頻率的轉換增益平均為 -30 dB，其相近頻率變化較大，低於模擬約 9 dB。圖 3.67 為 RF 在 290 GHz，LO 在 140 GHz，RF 功率對比的轉換增益，轉換增益約為 -26.5 dB，IP<sub>1dB</sub> 為 -3.5 dBm。

圖 3.63 並接式 LO 功率對比轉換增益上變頻之量測

圖 3.64 並接式 IF 頻率對比轉換增益上變頻之量測

圖 3.65 並接式 LO 頻率對比轉換增益上變頻之量測

圖 3.66 並接式 RF 頻率對比轉換增益上變頻之量測

圖 3.67 並接式 IF 功率對比轉換增益上變頻之量測

### 3.9 問題與討論

此次次諧波混頻器設計中兩個電路於量測整體轉換增益皆低於模擬結果約 15 dB，量測之中，量測過程中亦觀察到一特殊現象：當 RF 未接入訊號下針，僅 LO 開啟時，IF 端輸出仍出現一個額外頻譜成分，其頻率剛好在 LO 的 1/12，如圖 3.68 所示。由於本次量測架設所使用之波導具有明確的截止頻率，理論上可有效抑制訊號源本身可能存在之低頻雜訊，因此推測該額外頻譜成分可能來自於混頻器電路本身。

進一步分析可能原因，推測為 LO 經由混頻器內部非線性效應產生自混頻或除頻效應所致。然而，在 ADS 模擬下相同條件並未觀察到類似除頻現象，且實驗過程亦更換過不同 LO 訊號源時，該額外頻譜成分之頻率由 LO/12 變化為 LO/24，尚未釐清真正的原因，可能與實際硬體路徑或未知寄生效應相關。

由於高頻量測環境中寄生效應難以完全量化，加上訊號源、波導與探針接觸

等多重因素均可能影響最終轉換增益表現，導致量測與模擬結果存在約 15 dB 的落差。受限於目前量測條件與可用設備，尚未能進一步釐清該額外頻譜成分的明確來源，將作為後續研究與優化改善之重點方向。

圖 3.68 RF 關閉，LO 開啟時出現的 tone

圖 3.69 LO 之 1/12 訊號頻譜

## Chapter 4 結論

本論文設計實作了三個晶片，包括一個低雜訊放大器與兩個次諧波混頻器。首先，所設計之 LNA 採用 TSMC 40 nm CMOS 製程，操作頻率於 150 GHz。其模擬與量測結果高度吻合，實現了 27.74 dB 的高增益，僅出現約 6.5 GHz 的頻率偏移，整體性能表現優異，可作為高頻接收機的前級電路。其次，採用串接式開關架構的 SHM 在模擬與量測中均成功證實了次諧波混頻的可行性，但實測轉換增益較模擬預期值低約 15 dB。最後，並接式開關架構 SHM 利用四分之一波長傳輸線來放大元件導通與關閉狀態的阻抗差異，但由於  $\lambda/4$  變換未能如預期有效提升關閉狀態阻抗，導致整體性能下降，實測轉換增益亦較模擬值低約 13 dB。

綜合而言，LNA 為本論文最具價值的成果，展現了卓越的高增益表現與良好的模擬/量測一致性；兩款 SHM 則分別體現了傳統架構與富於創新的探索性架構，對毫米波前端電路設計具有參考價值與研究意義。

## REFERENCE

- [1] E. Calvanese Strinati et al., "6G: The Next Frontier: From Holographic Messaging to Artificial Intelligence Using Subterahertz and Visible Light Communication," in IEEE Vehicular Technology Magazine, vol. 14, no. 3, pp. 42-50, Sept. 2019.

- [2] M. Giordani, M. Polese, M. Mezzavilla, S. Rangan and M. Zorzi, "Toward 6G Networks: Use Cases and Technologies," in IEEE Communications Magazine, vol. 58, no. 3, pp. 55-61, March 2020.

- [3] C. Carlowitz and M. Dietz, "Integrated Front-End Approaches for Wireless 100 Gb/s and Beyond: Enabling Efficient Ultra-High Speed Wireless Communication Systems," in IEEE Microwave Magazine, vol. 24, no. 8, pp. 16-34, Aug. 2023.

- [4] J. L. Gonzalez-Jimenez, "Channel-bonding CMOS transceiver for 100 Gbps wireless point-to-point links," CEA-LETI, Grenoble, France, Tech. Rep., 2019.

- [5] T. H. Jang, K. P. Jung, J. -S. Kang, C. W. Byeon and C. S. Park, "120-GHz 8-Stage Broadband Amplifier With Quantitative Stagger Tuning Technique," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 67, no. 3, pp. 785-796, March 2020.

- [6] I. Kim, H. Koo, W. Kim and S. Hong, "A 131–162-GHz Wideband CMOS LNA Using Asymmetric Frequency Responses of Triple-Coupled Transformers," in IEEE Microwave and Wireless Technology Letters, vol. 33, no. 11, pp. 1544-1547.

- [7] D. -H. Kim, D. Kim and J. -S. Rieh, "A D -Band CMOS Amplifier With a New Dual-Frequency Interstage Matching Technique," in IEEE Transactions on Microwave Theory and Techniques, vol. 65, no. 5, pp. 1580-1588, May 2017.

- [8] G. Feng, C. C. Boon, F. Meng, X. Yi and C. Li, "An 88.5–110 GHz CMOS Low-Noise Amplifier for Millimeter-Wave Imaging Applications," in IEEE Microwave and Wireless Components Letters, vol. 26, no. 2, pp. 134-136, Feb. 2016.

- [9] D.-R. Lu, Y.-C. Hsu, J.-C. Kao, J.-J. Kuo, D.-C. Niu, and K.-Y. Lin, "A 75.5-to-120.5-GHz, high-gain CMOS low-noise amplifier," in IEEE MTT-S Int. Microw. Symp. Dig., Jun. 2012, pp. 1–3.

- [10] E. Aguilar, A. Hagelauer, D. Kissinger, and R. Weigel, "A low-power wideband D-Band LNA in a 130 nm BiCMOS technology for imaging applications," in IEEE 18th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Jan 2018.

- [11] E. Kobal, T. Siriburanon, R. B. Staszewski and A. Zhu, "A Compact, Low-Power, Low-NF, Millimeter-Wave Cascode LNA With Magnetic Coupling Feedback in 22-nm FD-SOI CMOS for 5G Applications," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 70, no. 4, pp. 1331-1335, April 2023.

- [12] R. Chikkanagouda and C. P. Raj P., "W-band CMOS LNA with 29 dB Gain and 5.2 dB Noise Figure for mm-wave Imaging Applications," 2019 International Conference on Communication and Signal Processing (ICCSP), Chennai, India, 2019, pp. 0783-0786.

- [13] A. Ç. Ulusoy, M. Kaynak, V. Valenta, B. Tillack and H. Schumacher, "A 110 GHz LNA with 20dB gain and 4dB noise figure in an  $0.13\mu\text{m}$  SiGe BiCMOS technology," 2013 IEEE MTT-S International Microwave Symposium Digest (MTT), Seattle, WA, USA, 2013, pp. 1-3.

- [14] I. Cheol Yoo, D. Ouk Cho, D. -W. Kang, B. Koo and C. Woo Byeon, "A 120

GHz gm-boosting Low-Noise Amplifier in 40-nm CMOS," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 72, no. 1, pp. 153-157, Jan. 2025.

-

- [15] C. J. Lee, H. Nam, D. Kim, S. -K. Kim and D. Y. Lee, "A D-Band Variable Gain Low Noise Amplifier in a 28-nm CMOS Process for 6G Wireless Communications," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 71, no. 1, pp. 131-135, Jan. 2024.

- [16] Z. Xu, Q. J. Gu, I. Ku and M. -C. F. Chang, "A compact, fully differential D-band CMOS amplifier in 65nm CMOS," 2010 IEEE Asian Solid-State Circuits Conference, Beijing, China, 2010, pp. 1-4.

- [17] Z. Deng and A. M. Niknejad, "A layout-based optimal neutralization technique for mm-wave differential amplifiers," 2010 IEEE Radio Frequency Integrated Circuits Symposium, Anaheim, CA, USA, 2010, pp. 355-358.

- [18] A. Hamani, A. Siligaris, B. Blampey, C. Dehos and J. L. Gonzalez Jimenez, "A 125.5-157 GHz 8 dB NF and 16 dB of Gain D-band Low Noise Amplifier in CMOS SOI 45 nm," 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 2020, pp. 197-200.

- [19] C. -k. Lu, Y. -S. Wang, C. -C. Chiong and H. Wang, "A 140 GHz Low-Noise Amplifier with 22-dB Gain and 8.2-dB Noise Figure in 65-nm CMOS," 2024 IEEE Asia-Pacific Microwave Conference (APMC), Bali, Indonesia, 2024, pp. 351-353.

- [20] K. -S. Choi, H. Lee, B. Yun and S. -G. Lee, "A D-Band Low-Noise and High-Gain Receiver Front-End Adopting Gmax-Driven Active Mixer," in IEEE Transactions on Microwave Theory and Techniques, vol. 72, no. 9, pp. 5576-5587, Sept. 2024.

- [21] F. He, Q. Xie and Z. Wang, "Analysis and Design of a Novel Gain-Boosting Technique Based on Lossy Series Embedding Network for Near-fmax Embedded Amplifier," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 71, no. 2, pp. 874-884, Feb. 2024.

- [22] B. Yun, D. -W. Park, H. U. Mahmood, D. Kim and S. -G. Lee, "A D-Band High-Gain and Low-Power LNA in 65-nm CMOS by Adopting Simultaneous Noise- and Input-Matched Gmax-Core," in IEEE Transactions on Microwave Theory and Techniques, vol. 69, no. 5, pp. 2519-2530, May 2021.

- [23] H. -S. Chen and J. Y. -C. Liu, "A 180-GHz Low-Noise Amplifier With Recursive Z-Embedding Technique in 40-nm CMOS," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 69, no. 12, pp. 4649-4653, Dec. 2022.

- [24] K. Takano et al., "17.9 A 105Gb/s 300GHz CMOS transmitter," 2017 IEEE International Solid-State Circuits Conference (ISSCC), 2017, pp. 308-309.

- [25] H. Hamada et al., "300-GHz. 100-Gb/s InP-HEMT Wireless Transceiver Using a 300-GHz Fundamental Mixer," 2018 IEEE/MTT-S International Microwave Symposium - IMS, 2018, pp. 1480-1483.

- [26] H. -J. Song, J. -Y. Kim, K. Ajito, N. Kukutsu and M. Yaita, "50-Gb/s Direct Conversion QPSK Modulator and Demodulator MMICs for Terahertz Communications at 300 GHz," in IEEE Transactions on Microwave Theory and Techniques, vol. 62, no. 3, pp. 600-609, March 2014.

- [27] S. Hara et al., "A 32Gbit/s 16QAM CMOS receiver in 300GHz band," 2017 IEEE MTT-S International Microwave Symposium (IMS), 2017, pp. 1703-1706.

- [28] G. Su et al., "A H-band double balanced passive down-conversion mixer in a 65 nm bulk CMOS," 2017 10th UK-Europe-China Workshop on Millimetre Waves and Terahertz Technologies (UCMWT), 2017, pp. 1-4.

- [29] K. David and H. Berndt, "6G vision and requirements: Is there any need for beyond 5G? " IEEE Veh. Technol. Mag., vol. 13, no. 3, pp. 72–80, 2018.

- [30] G. Berardinelli, N. H. Mahmood, I. Rodriguez Larrad, and P. E. Mogensen, "Beyond 5G wireless IRT for Industry 4.0: Design principles and spectrum aspects," in Proc. IEEE Global Communications Conf. Workshops, 2018.

- [31] V. Petrov, T. Kurner and I. Hosako, "IEEE 802.15.3d: First Standardization Efforts for Sub-Terahertz Band Communications toward 6G," in IEEE Communications Magazine, vol. 58, no. 11, pp. 28-33, November 2020.

- [32] M. S. Gupta, "Power gain in feedback amplifiers, a classic revisited," in IEEE Transactions on Microwave Theory and Techniques, vol. 40, no. 5, pp. 864-879, May 1992.

- [33] H. Bameri and O. Momeni, "A High-Gain mm-Wave Amplifier Design: An Analytical Approach to Power Gain Boosting," in IEEE Journal of Solid-State Circuits, vol. 52, no. 2, pp. 357-370, Feb. 2017.

- [34] A. Singhakowinta and A. Boothroyd, "Gain capability of two-port amplifiers", Int. J. Electron., vol. 21, no. 6, pp. 549-560, 1966.

- [35] Z. Wang and P. Heydari, "A Study of Operating Condition and Design Methods to Achieve the Upper Limit of Power Gain in Amplifiers at Near-  $f_{\max}$  Frequencies," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 64, no. 2, pp. 261-271, Feb. 2017.

- [36] D. -W. Park, D. R. Utomo, B. H. Lam, J. -P. Hong and S. -G. Lee, "A 280-/300-GHz Three-Stage Amplifiers in 65-nm CMOS With 12-/9-dB Gain and 1.6/1.4% PAE While Dissipating 17.9 mW," in IEEE Microwave and Wireless Components Letters, vol. 28, no. 1, pp. 79-81, Jan. 2018.

- [37] D. -W. Park, D. R. Utomo, B. H. Lam, S. -G. Lee and J. -P. Hong, "A 230–260-

GHz Wideband and High-Gain Amplifier in 65-nm CMOS Based on Dual-Peak Gmax -Core," in IEEE Journal of Solid-State Circuits, vol. 54, no. 6, pp. 1613-1623, June 2019.

-

- [38] L. N. Dworsky, Modern Transmission Line Theory and Applications, New York, NY, USA:Wiley, 1979.

- [39] I. Sarkas et al., "Silicon-based radar and imaging sensors operating above 120 GHz," 2012 19th International Conference on Microwaves, Radar & Wireless Communications, Warsaw, Poland, 2012, pp. 91-96.

- [40] L. -J. Huang, C. -C. Chiong, Y. -S. Wang, H. Wang, T. -W. Huang and C. -C. Chien, "A D-band Low-Noise Amplifier in 28-nm CMOS Technology for Radio Astronomy Applications," 2023 18th European Microwave Integrated Circuits Conference (EuMIC), Berlin, Germany, 2023, pp. 369-372.

- [41] T. -H. Wu, S. -C. Tseng, C. -C. Meng and G. -W. Huang, "GaInP/GaAs HBT Sub-Harmonic Gilbert Mixers Using Stacked-LO and Leveled-LO Topologies," in IEEE Transactions on Microwave Theory and Techniques, vol. 55, no. 5, pp. 880-889, May 2007.

- [42] M. Goldfarb, E. Balboni and J. Cavey, "Even harmonic double-balanced active mixer for use in direct conversion receivers," in IEEE Journal of Solid-State Circuits, vol. 38, no. 10, pp. 1762-1766, Oct. 2003.

- [43] S. Lee et al., "9.5 An 80Gb/s 300GHz-Band Single-Chip CMOS Transceiver," 2019 IEEE International Solid-State Circuits Conference - (ISSCC), San Francisco, CA, USA, 2019, pp. 170-172.

- [44] I. Abdo et al., "A 300GHz Wireless Transceiver in 65nm CMOS for IEEE802.15.3d Using Push-Push Subharmonic Mixer," 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 2020, pp.

623-626.

- [45] S. Kang, S. V. Thyagarajan and A. M. Niknejad, "A 240 GHz Fully Integrated Wideband QPSK Transmitter in 65 nm CMOS," in IEEE Journal of Solid-State Circuits, vol. 50, no. 10, pp. 2256-2267, Oct. 2015.

- [46] H. -R. Jeon, B. -H. Yun, H. -K. Lee, S. -G. Lee and K. -S. Choi, "A 250-GHz Wideband Direct-Conversion CMOS Receiver Adopting Baseband Equalized Low-Loss Resistive Passive Mixer," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 70, no. 10, pp. 3852-3856, Oct. 2023.

- [47] H. Hamada et al., "300-GHz 120-Gb/s Wireless Transceiver with High-Output-Power and High-Gain Power Amplifier Based on 80-nm InP-HEMT Technology," 2019 IEEE BiCMOS and Compound semiconductor Integrated Circuits and Technology Symposium (BCICTS), Nashville, TN, USA, 2019, pp. 1-4.

- [48] P. -H. Tsai, Y. -H. Lin, J. -L. Kuo, Z. -M. Tsai and H. Wang, "Broadband Balanced Frequency Doublers With Fundamental Rejection Enhancement Using a Novel Compensated Marchand Balun," in IEEE Transactions on Microwave Theory and Techniques, vol. 61, no. 5, pp. 1913-1923, May 2013.

- [49] Y. -C. Wu, Y. -J. Hwang, C. -C. Chiong, B. -Z. Lu and H. Wang, "An Innovative Joint-Injection Mixer With Broadband If and RF for Advanced Heterodyne Receivers of Millimeter-Wave Astronomy," in IEEE Transactions on Microwave Theory and Techniques, vol. 68, no. 12, pp. 5408-5422, Dec. 2020.