國立臺灣大學

重點科技研究學院元件材料與異質整合碩士學位學程

碩士論文

Master Program for Semiconductor Devices, Materials, and Hetero-integration

Graduate School of Advanced Technology

National Taiwan University

Master's Thesis

二硫化鉬鐵電場效電晶體於記憶體的應用

MoS<sub>2</sub> Ferroelectric Field-Effect Transistors for Memory

Applications

吳昊陽

Hao-Yang Wu

指導教授：李峻霄 教授

Advisor: Professor Jiun-Yun Li

中華民國 114 年 4 月

April, 2025

## 誌謝

感謝指導教授李峻寰教授於碩士期間的悉心教導，兩年來指導我如何進行研究，並教我做報告與口頭表達的方法，使我獲益良多。

感謝李敏鴻教授與蘇俊榮教授擔任口試委員，於口試中給予寶貴指導，使本論文內容更加完整。

感謝重點科技學院提供獎學金資助，以及院辦人員的平時協助與照顧。亦感謝實驗室助理平時幫忙。

感謝實驗室學長姐們教我如何做製程、量測、繪圖與分析實驗結果，也時常與我討論數據以及背後物理。在我報告結束後，給予我許多建議，使我持續進步，最後可以順利畢業。

感謝父母支持我完成學業，感謝哥哥平時關心，感謝女友妹儀陪伴。

## 摘要

二維材料在奈米尺度下展現良好電性，如高載子遷移率，使其成為有希望延續摩爾定律的選擇。隨著人工智慧發展，記憶體需求增加，二氧化鉻鐵電材料記憶體引起關注，因其與現代積體電路製程相容，有快速寫入速度與低功耗優點。鐵電場效電晶體(FeFETs)是單電晶體記憶體元件，並具有高保存時間(retention)與高耐久度(endurance)優點，可在未來運用於記憶體內運算(In-Memory Computing)。然而，隨著元件尺度微縮，傳統半導體塊材面臨限制，如載子遷移率因表面散射下降、短通道效應與散熱等挑戰。二維半導體本身無懸浮鍵特性，使通道載子具有高遷移率而不受表面散射影響，與減少漏電流優點。這篇論文研究二維材料通道鐵電場效電晶體，二硫化鉑(MoS<sub>2</sub>)作為通道，氧化鉻鋯(Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>, HZO)作為鐵電閘極介電質。首先，製作以二氧化矽作為閘極介電質之二硫化鉑電晶體並進行電性分析，隨後，將氧化層替換為氧化鉻鋯，製作鐵電場效電晶體並進行電性分析。

第一部分，製作二硫化鉑電晶體，使用高摻雜矽基板作為底閘極，二氧化矽作為閘極氧化層，鉻/金作為源極/汲極金屬，在充滿氮氣的手套箱環境中利用機械式剝離法分離塊材二硫化鉑，並用乾式轉移將薄膜轉移到元件上。二硫化鉑厚度 100 奈米之電晶體展現良好電流開關比  $10^5$ (過驅電壓 1.1 伏特)，與次臨界擺幅 150 mV/dec。另一元件二硫化鉑厚度 20 奈米之電晶體，額外使用石墨烯作為源極/汲極接觸金屬，電流開關比提升至  $10^6$ ，石墨烯功函數隨電壓上升而下降，與二硫化鉑形成較好的歐姆接觸。此外，元件次臨界擺幅提升至 90 mV/dec，石墨烯是狄拉克(Dirac)材料，減少電子密度在費米能階之上的分佈，使電子注入通道更集中。

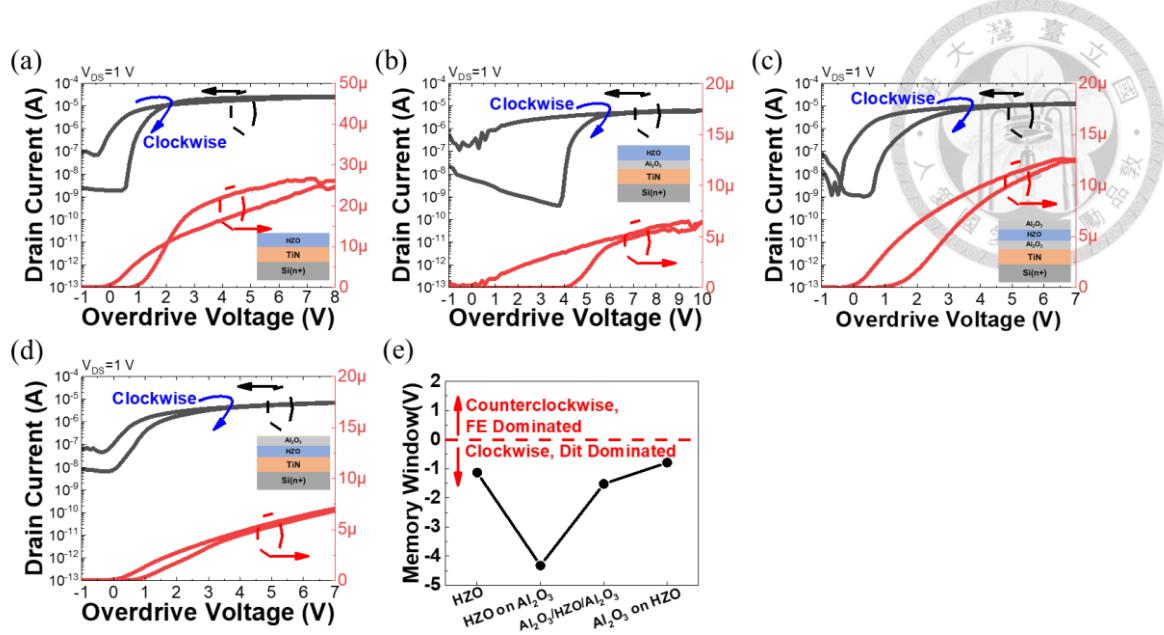

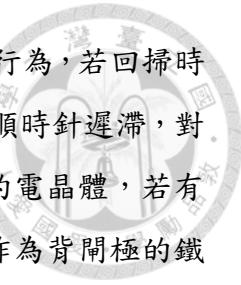

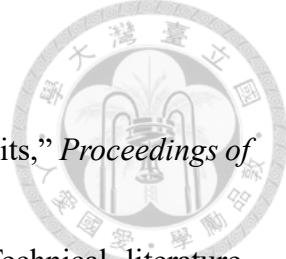

第二部分，分別在金屬-鐵電(介電層)-半導體(MF(I)S)電容結構與二維材料鐵電電晶體中比較四種不同鐵電氧化鉻鋯與氧化鋁堆疊。對於電容，氧化鋁堆疊在氧化鉻鋯上展現最大剩餘極化值，在退火時上方氧化鋁有助於形成氧化鉻鋯鐵電特性。對於二維材料鐵電電晶體，只有氧化鋁堆疊在氧化鉻鋯上的元件展現逆時針  $I_D-V_G$ ，對應其鐵電電晶體特性。其他元件展現順時針  $I_D-V_G$ ，歸因於閘極電壓掃描時於氧化層/半導體介面發生電荷捕捉效應，較高濃度的介面電荷抵消鐵電遲滯現象。

關鍵字：二硫化鉑、二維、氧化鉻鋯、鐵電、鐵電記憶體

# Abstract

Two-dimensional (2D) materials exhibit excellent electrical properties at a nanometer scale, such as high carrier mobility, making them a promising candidate to extend Moore's Law. With the growing demand for memory driven by advancements in artificial intelligence (AI), HfO<sub>2</sub>-based ferroelectric materials are considered promising candidate for non-volatile memory due to their VLSI compatibility, fast write speeds, and low power consumption. FeFETs, as one-transistor (1T) memory device with high retention and endurance, hold potential for future in-memory computing. However, as devices are further scaled down, bulk semiconductors face limitations, such as decreased carrier mobility due to surface scattering, short-channel effects, and heat dissipation challenges. 2D semiconductors with dangle-bond-free nature allow these materials to maintain high carrier mobility and reduce the leakage current. This study focuses on 2D-based FeFETs using MoS<sub>2</sub> as a channel material and Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> (HZO) as a ferroelectric gate dielectric. First, MoS<sub>2</sub> MOSFETs with SiO<sub>2</sub> as a dielectric layer are fabricated and characterized. Then replacing the oxide with ferroelectric HZO to fabricate FeFETs and investigate their device characteristics.

In the first part, 2D FETs were fabricated with highly doped Si substrates serving as a bottom gate, followed by the deposition of SiO<sub>2</sub> as a gate dielectric and Cr/Au as electrodes to the source/drain (S/D). Then MoS<sub>2</sub> thin films are mechanically exfoliated and dry transferred onto the sample in a nitrogen-filled glove box to finish the processes. 2D FET with 100 nm-thick MoS<sub>2</sub> achieved a high current on/off ratio of 10<sup>5</sup> under an overdrive voltage 1.1 V and a subthreshold swing (SS) 150 mV/dec. Additionally, another device with MoS<sub>2</sub> 20 nm-thick, using graphene as the S/D contact, the on/off ratio is improved to 10<sup>6</sup>. The workfunction of graphene decreases as the voltage increases, forming a better Ohmic contact with MoS<sub>2</sub>. Furthermore, the SS is improved to 90 mV/dec, which might be attributed to the density-state switching by using graphene as a Dirac source.

In the second part, four different oxide stacks of Al<sub>2</sub>O<sub>3</sub> and ferroelectric HZO are investigated in metal-ferroelectric(interlayer)-semiconductor (MF(I)S) capacitors and 2D FeFETs. For the capacitors, the stack with Al<sub>2</sub>O<sub>3</sub> on HZO shows higher remnant polarization. The presence of the cap Al<sub>2</sub>O<sub>3</sub> during rapid thermal annealing (RTA) step leads to an enhancement of the ferroelectricity. For 2D FeFETs, only the stack of Al<sub>2</sub>O<sub>3</sub>

on HZO showed counterclockwise hysteresis loop of I-V characteristics, a signature of ferroelectric switching. Other devices show clockwise hysteresis loops, which is attributed to the charge trapping effects at the oxide/semiconductor interface during the gate sweeps. A higher density of charge trapping may counterbalance the ferroelectricity.

**Keywords:** MoS<sub>2</sub>, 2D, HZO, Ferroelectric, FeFETs

# 目次

|                              |           |

|------------------------------|-----------|

| 誌謝 .....                     | i         |

| 摘要 .....                     | ii        |

| Abstract .....               | iii       |

| 目次 .....                     | v         |

| 圖次 .....                     | vi        |

| 表次 .....                     | x         |

| <b>第 1 章 引言 .....</b>        | <b>1</b>  |

| 1.1 研究動機 .....               | 1         |

| 1.2 二維材料 .....               | 2         |

| 1.3 鐵電記憶體 .....              | 4         |

| 1.4 論文架構 .....               | 9         |

| <b>第 2 章 二硫化鉬場效電晶體 .....</b> | <b>10</b> |

| 2.1 二硫化鉬場效電晶體文獻回顧 .....      | 10        |

| 2.2 二硫化鉬材料分析 .....           | 13        |

| 2.3 元件製作流程 .....             | 15        |

| 2.4 元件電性量測 .....             | 17        |

| 2.5 低溫量測 .....               | 20        |

| 2.6 結論 .....                 | 22        |

| <b>第 3 章 二維鐵電場效電晶體 .....</b> | <b>24</b> |

| 3.1 二維鐵電場效電晶體文獻回顧 .....      | 24        |

| 3.2 元件製程流程 .....             | 32        |

| 3.3 元件電性量測 .....             | 34        |

| 3.4 結論 .....                 | 43        |

| <b>第 4 章 結論與未來工作 .....</b>   | <b>45</b> |

| 4.1 結論 .....                 | 45        |

| 4.2 未來工作 .....               | 46        |

| 參考文獻 .....                   | 47        |

# 圖次

|                                                                                                             |    |

|-------------------------------------------------------------------------------------------------------------|----|

| 圖 1.1 根據 IRDS 繪製的電晶體預測藍圖[3]。 .....                                                                          | 1  |

| 圖 1.2 不同電性二維材料[12]。 .....                                                                                   | 2  |

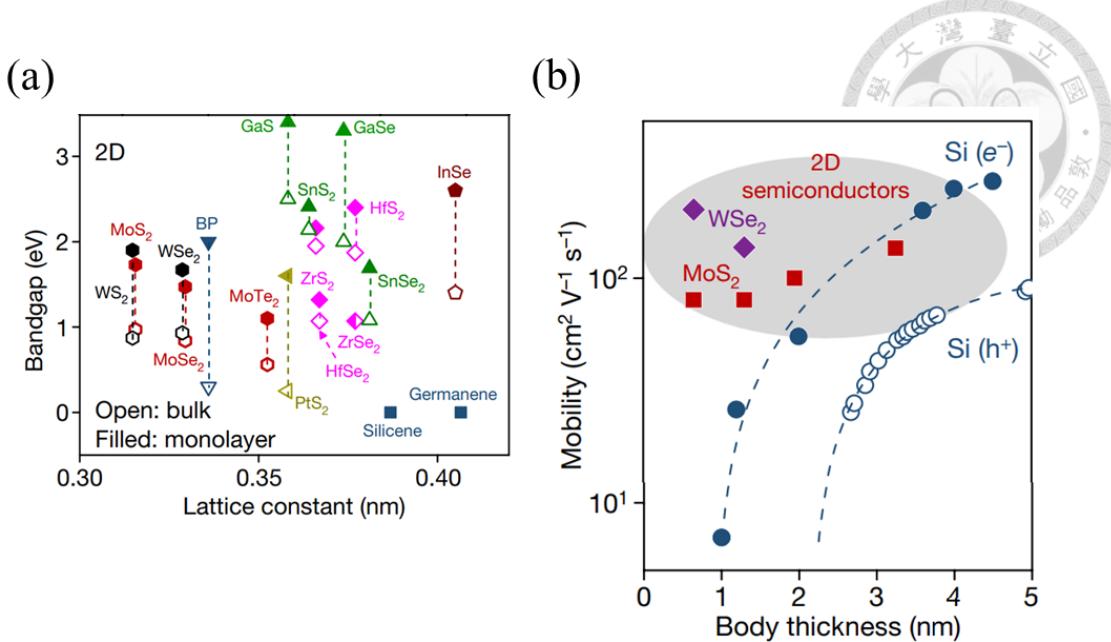

| 圖 1.3 (a)不同二維材料的能隙與晶格常數的關係圖(實心點為塊材，空心點為單層二維材料)，(b)二維材料與矽載子遷移率與通道厚度之關係圖[10]。 .....                           | 3  |

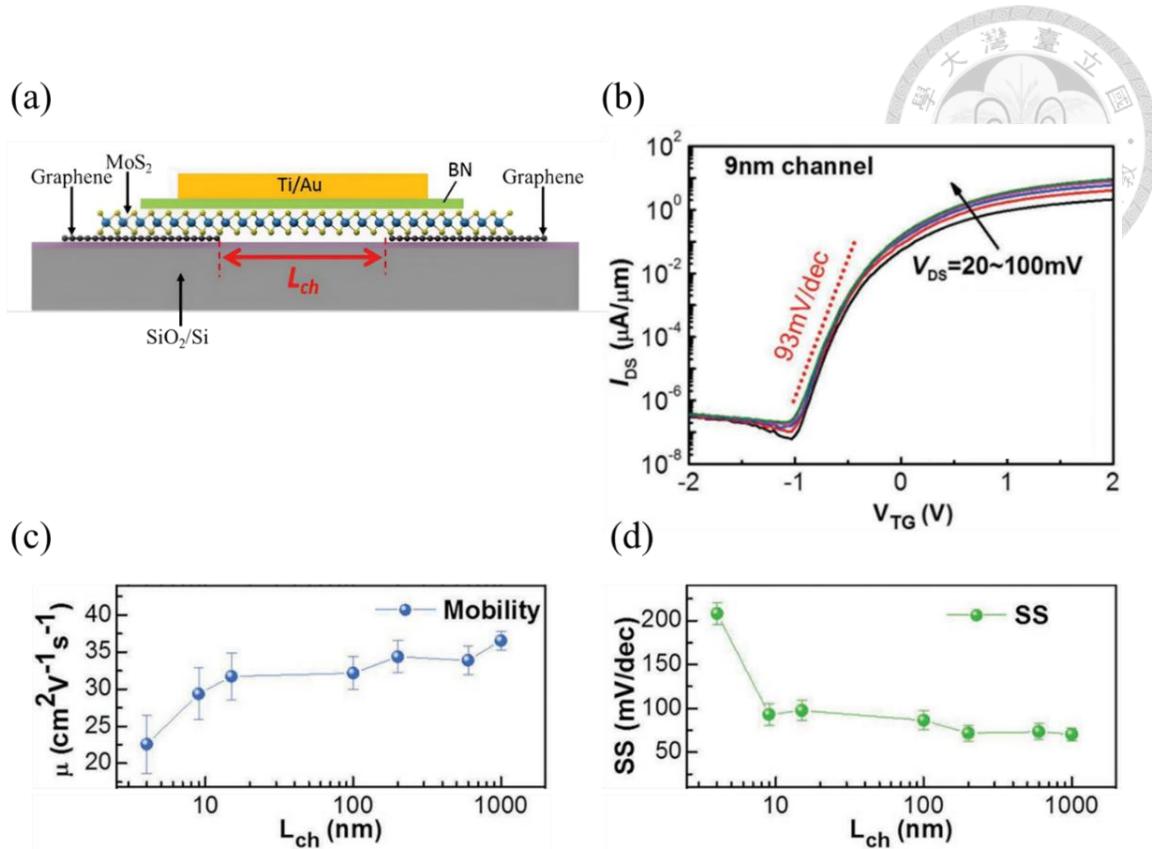

| 圖 1.4 二維材料電晶體之(a)元件示意圖，(b)通道長度 9 nm 之電晶體 $I_D-V_G$ 電性量測結果，(c)載子遷移率-通道長度關係圖與(d)臨界值擺幅-通道長度關係圖[15]。 .....      | 4  |

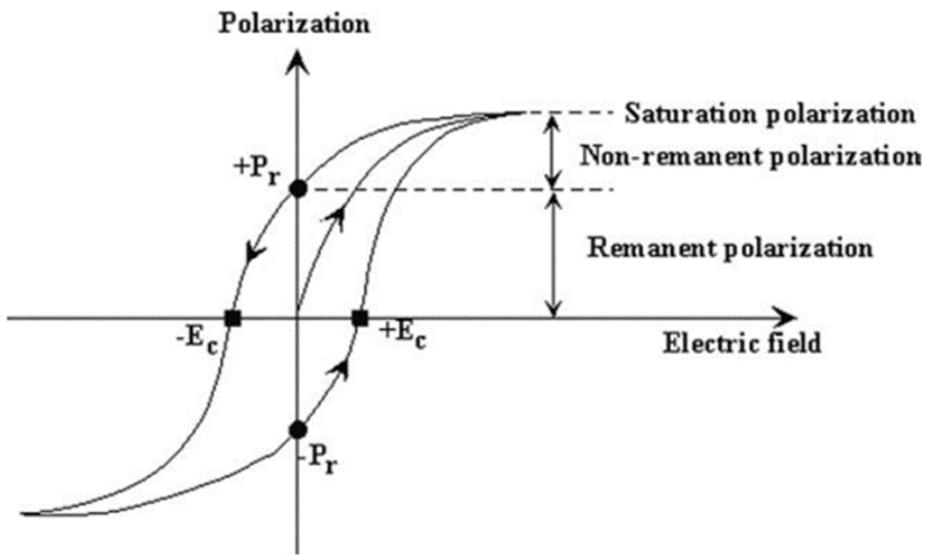

| 圖 1.5 鐵電材料之極化-電場關係圖[18]。 .....                                                                              | 5  |

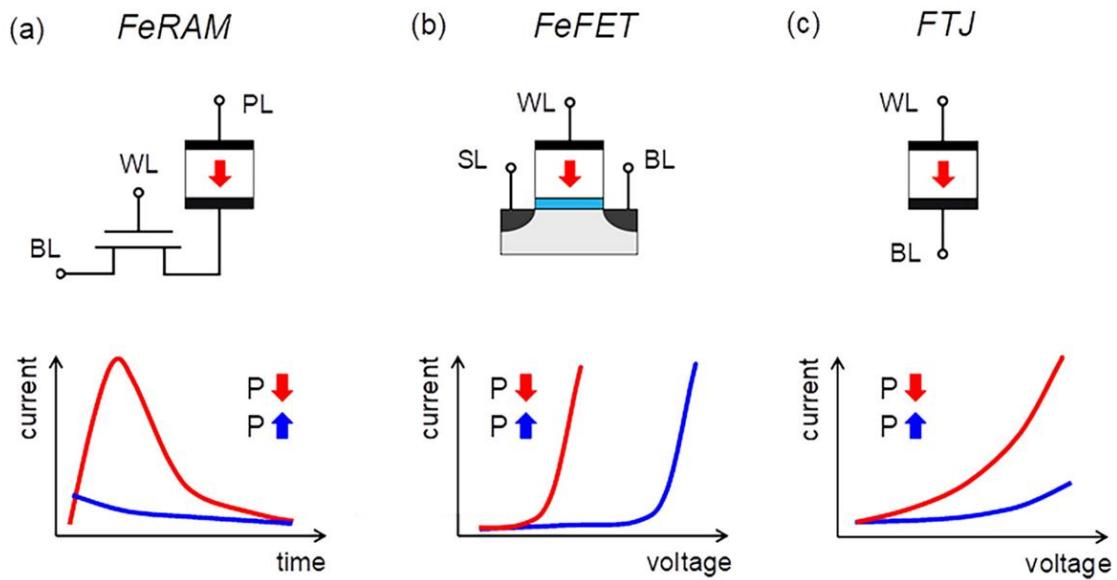

| 圖 1.6 (a)鐵電隨機存取記憶體(FeRAM)，(b)鐵電場效電晶體(FeFET)與(c)鐵電穿隧接面(FTJ)[19]。 .....                                       | 6  |

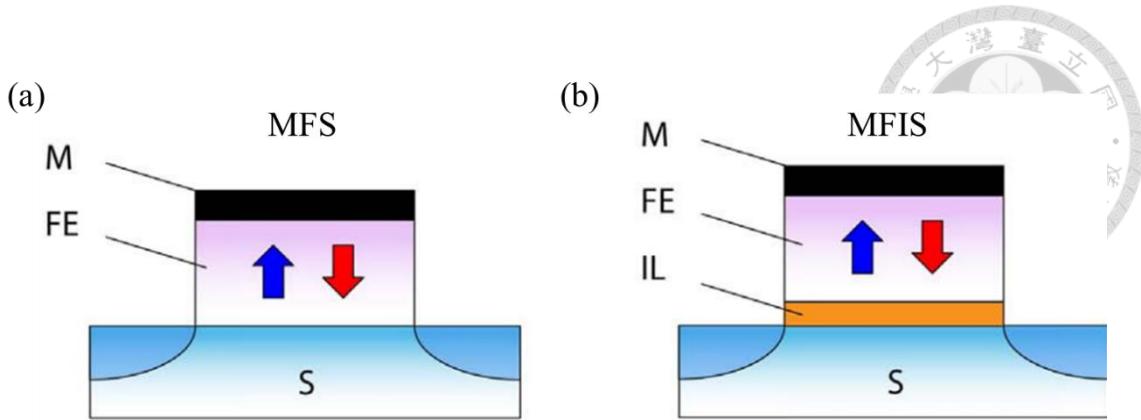

| 圖 1.7 (a)MFS 結構與(b)MFIS 結構之 FeFET 元件示意圖[25]。 .....                                                          | 7  |

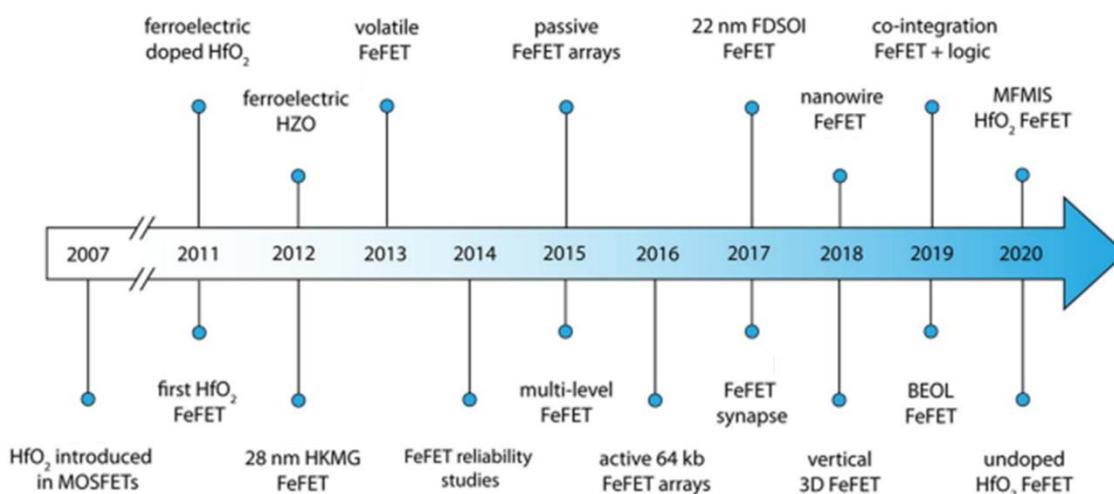

| 圖 1.8 $HfO_2$ 鐵電材料之 FeFET 發展演進圖[25]。 .....                                                                  | 7  |

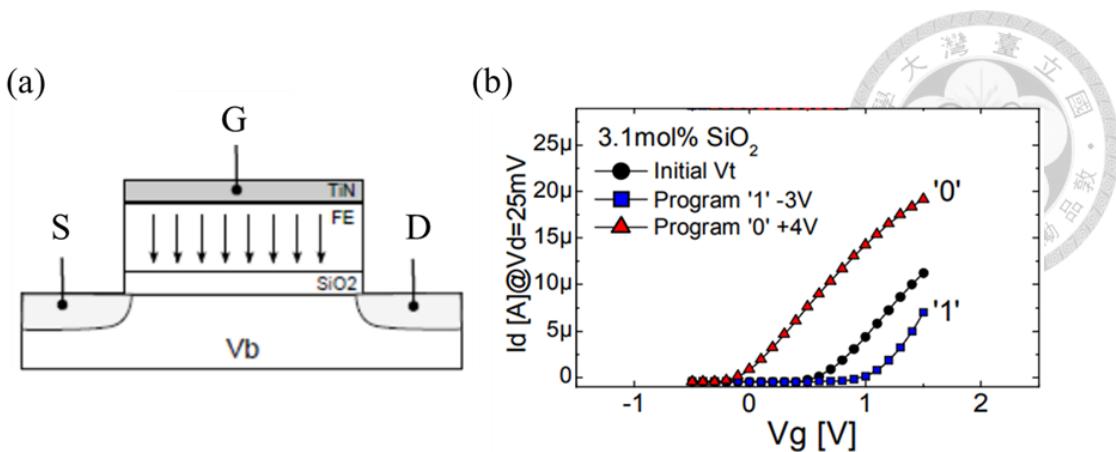

| 圖 1.9 $HfO_2$ 鐵電材料 FeFET 之(a)元件結構圖與(b) $I_D-V_G$ 電性量測結果[28]。 .....                                          | 8  |

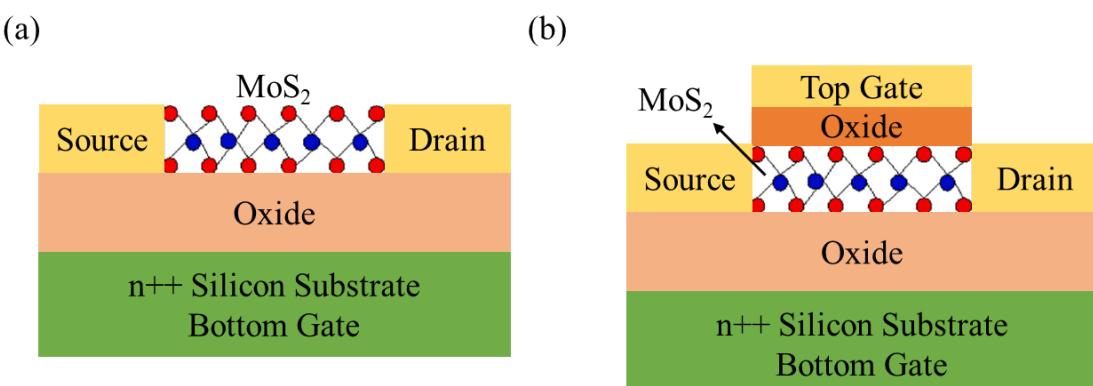

| 圖 2.1 (a)底閘極結構與(b)雙閘極結構(包含頂閘極與底閘極)之二硫化鉬場效電晶體結構示意圖。 .....                                                    | 10 |

| 圖 2.2 單層二硫化鉬作為通道的場效電晶體之(a)元件結構示意圖，(b)背閘極掃描 $I_D-V_G$ 量測結果與(c)頂閘極 $I_D-V_G$ 量測結果[39]。 .....                  | 11 |

| 圖 2.3 (a)二硫化鉬與金屬銻(Sc)、鈦(Ti)、鎳(Ni)與鉑(Pt)能帶示意圖與(b)多層二硫化鉬背閘極電晶體改變不同接觸金屬之 $I_D$ 對應 $V_{GS}-V_{TH}$ 量測結果[42]。 .. | 11 |

| 圖 2.4 (a)放置於真空 4 小時與未經過特別處理之二硫化鉬背閘極電晶體 $I_D-V_G$ 量測結果，圖中插圖為元件示意圖。(b)放置於在不同濕度下之 $I_D-V_G$ 量測結果[43]。 .....    | 12 |

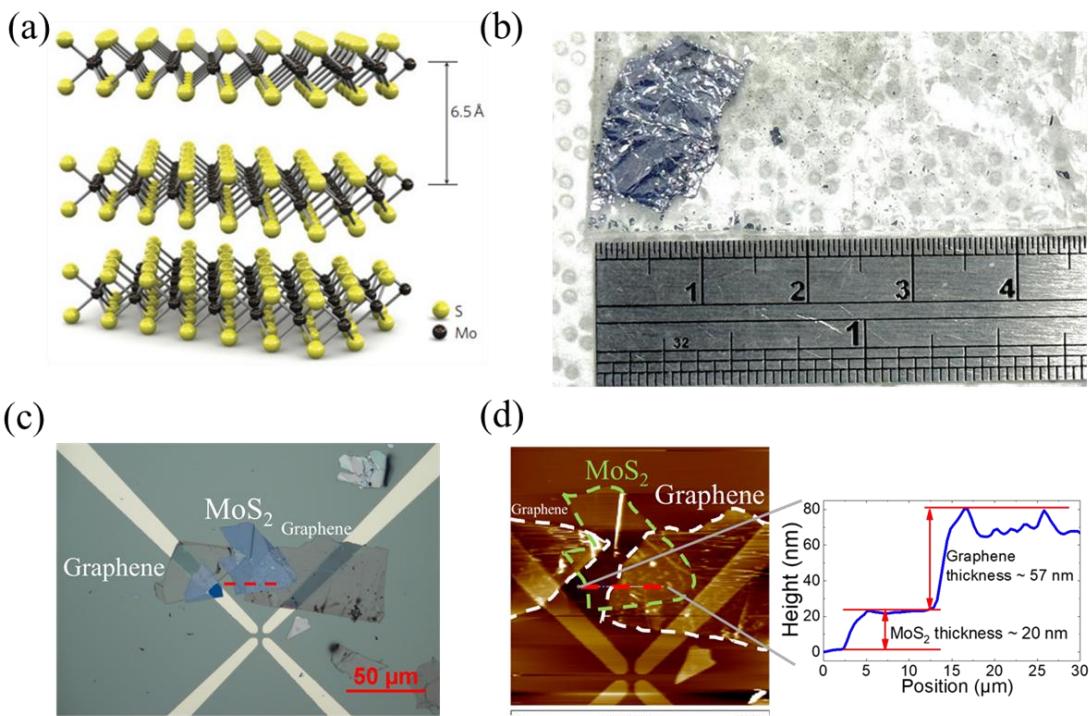

| 圖 2.5 (a)二硫化鉬晶體結構側視圖[38]，(b)二硫化鉬塊材照片，(c)二硫化鉬與石墨烯光學顯微鏡照片(紅色虛線為剖面)與(d)二硫化鉬與石墨烯 AFM 掃描結果與剖面高度(沿紅色虛線)。 .....    | 13 |

| 圖 2.6 (a)二硫化鉬拉曼光譜，圖中兩張插圖為振動模態示意圖[44]。(b)二硫化鉬光致發光光譜。 .....                                                   | 14 |

| 圖 2.7 二硫化鉬場效電晶體製程流程示意圖。 .....                                                                               | 15 |

|                                                                                                                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

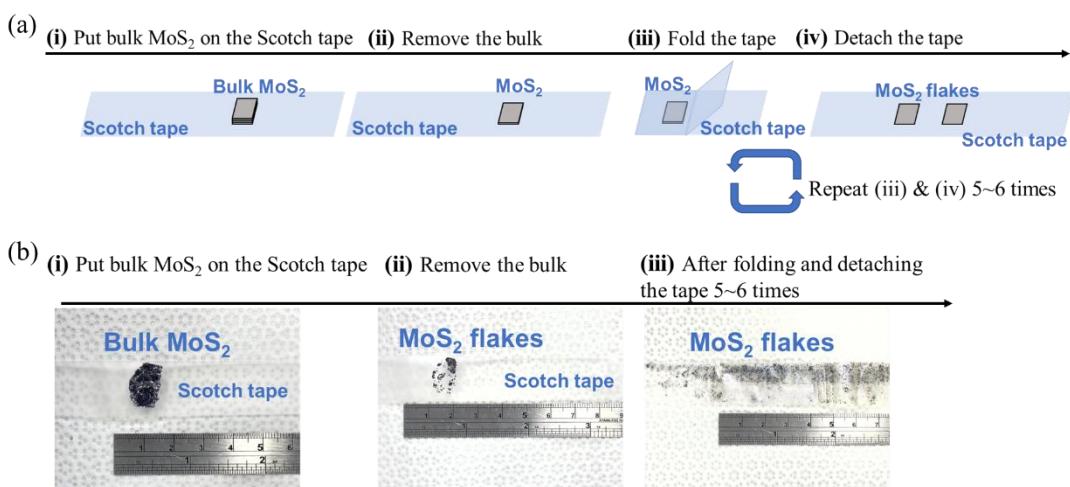

| 圖 2.8 機械式剝離法分離二硫化鉬(a)流程示意圖與(b)實際照片。 .....                                                                                                                                                                             | 16 |

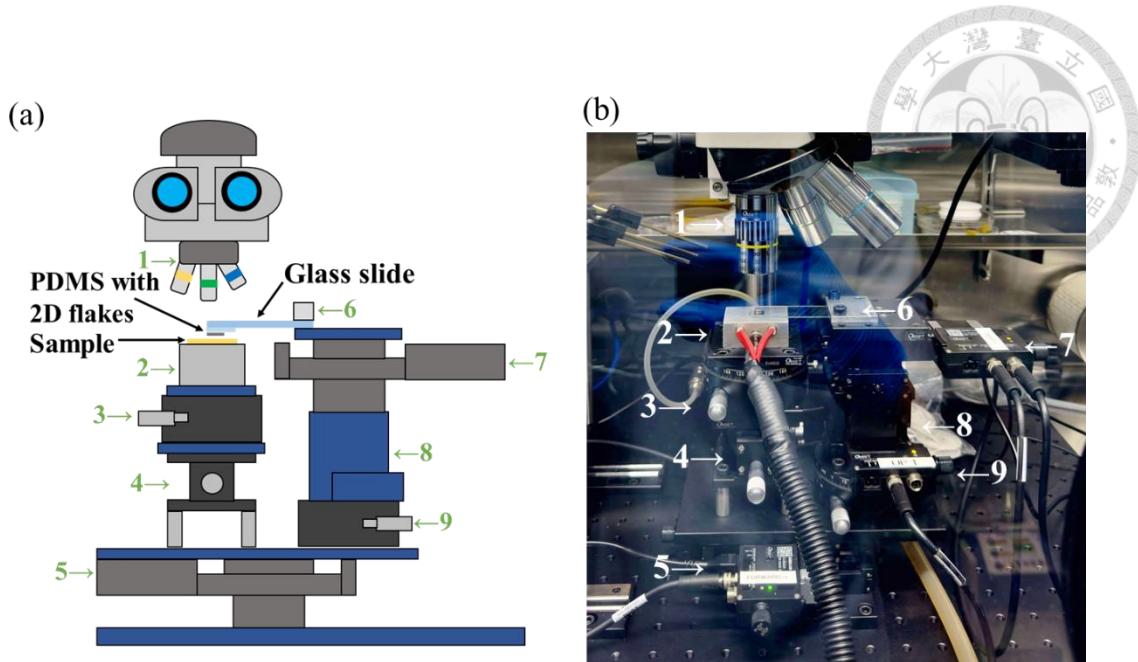

| 圖 2.9 手套箱內轉移系統之(a)示意圖和(b)實際照片。 .....                                                                                                                                                                                  | 17 |

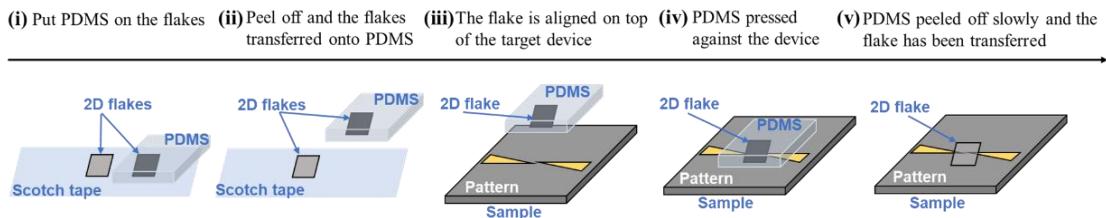

| 圖 2.10 透過 PDMS 轉移二硫化鉬之流程示意圖。 .....                                                                                                                                                                                    | 17 |

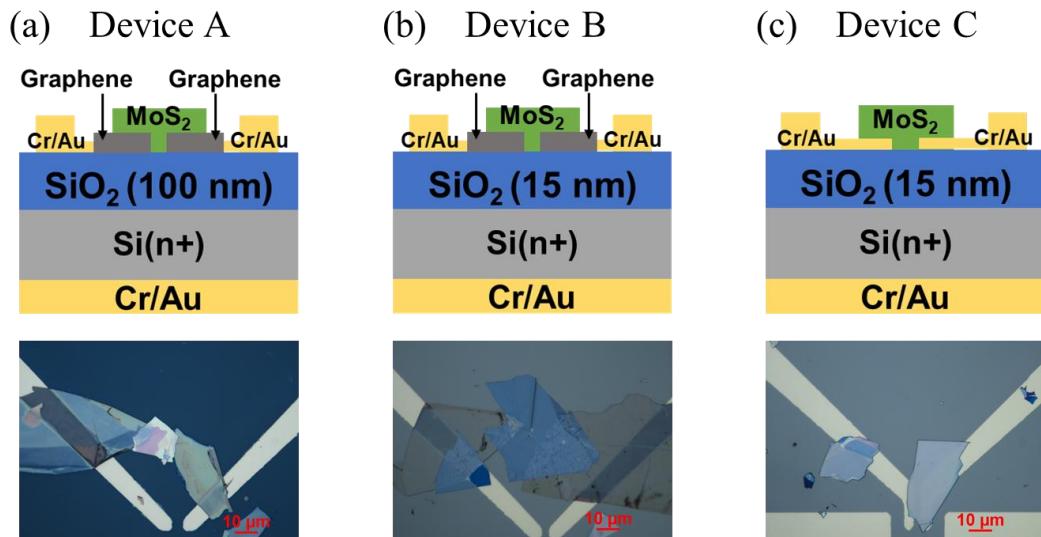

| 圖 2.11 二硫化鉬電晶體之元件示意圖與光學顯微鏡照片。條件分別為:(a)元件 A，<br>氧化層二氧化矽厚度 100 nm，石墨烯做為接觸金屬。(b)元件 B，氧化層<br>二氧化矽厚度 15 nm，石墨烯做為接觸金屬。(c)元件 C，氧化層二氧化矽<br>厚度 15 nm，沒有石墨烯作為接觸金屬。 .....                                                        | 18 |

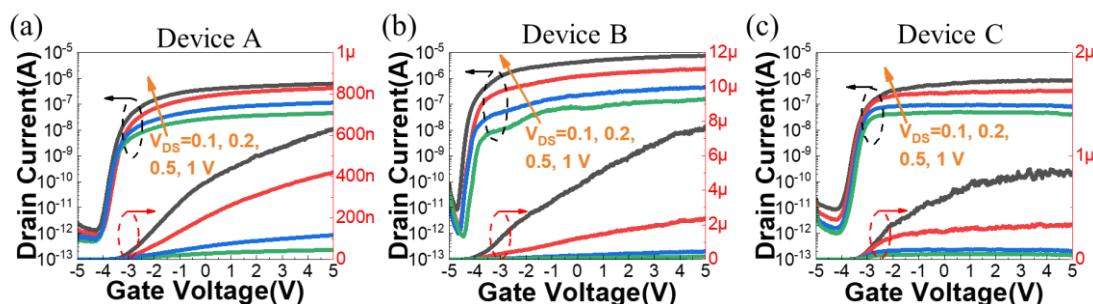

| 圖 2.12 二硫化鉬電晶體之 $I_D-V_G$ 量測結果。分別為：(a)元件 A，(b)元件 B 與(c)<br>元件 C。 .....                                                                                                                                                | 18 |

| 圖 2.13 (a)三種不同元件導通電流與(b)次臨界擺幅最小值。 .....                                                                                                                                                                               | 19 |

| 圖 2.14 利用(a)一般金屬或(b)狄拉克材料作為源極之狀態密度與波茲曼分布的載<br>子數量示意圖[54]。 .....                                                                                                                                                       | 20 |

| 圖 2.15 (a)二硫化鉬電晶體變溫量測之 $I_D-V_G$ 曲線，(b)臨界電壓對於溫度關係圖與<br>(c)次臨界擺幅對於溫度關係圖。 .....                                                                                                                                         | 21 |

| 圖 2.16 (a)不同溫度下的費米-狄拉克分布[58]，(b)不同溫度下的載子密度[58]與(c)<br>局域態示意圖[59]。 .....                                                                                                                                               | 21 |

| 圖 3.1 鐵電材料晶格結構示意圖：(a)PZT[60]，(b)PVDF[61]與(c)HZO[27]。 .....                                                                                                                                                            | 24 |

| 圖 3.2 在基於 $HfO_2$ 薄膜中摻雜、改變表面位能與提供應力後，可能形成相變示意<br>圖，包括單斜晶相(Monoclinic)、正交晶相(Orthorhombic)、四方晶相<br>(Tetragonal)，圖中綠色圓圈代表 Hf 原子，紅色圓圈代表 O 原子，而金色圓<br>圈標示為貢獻極化的 O 原子[65]。 .....                                            | 26 |

| 圖 3.3 不同比例的 $Hf_xZr_{1-x}O_2$ 氧化層之金屬-氧化層-金屬結構電容極化-電場[67]。<br>.....                                                                                                                                                    | 26 |

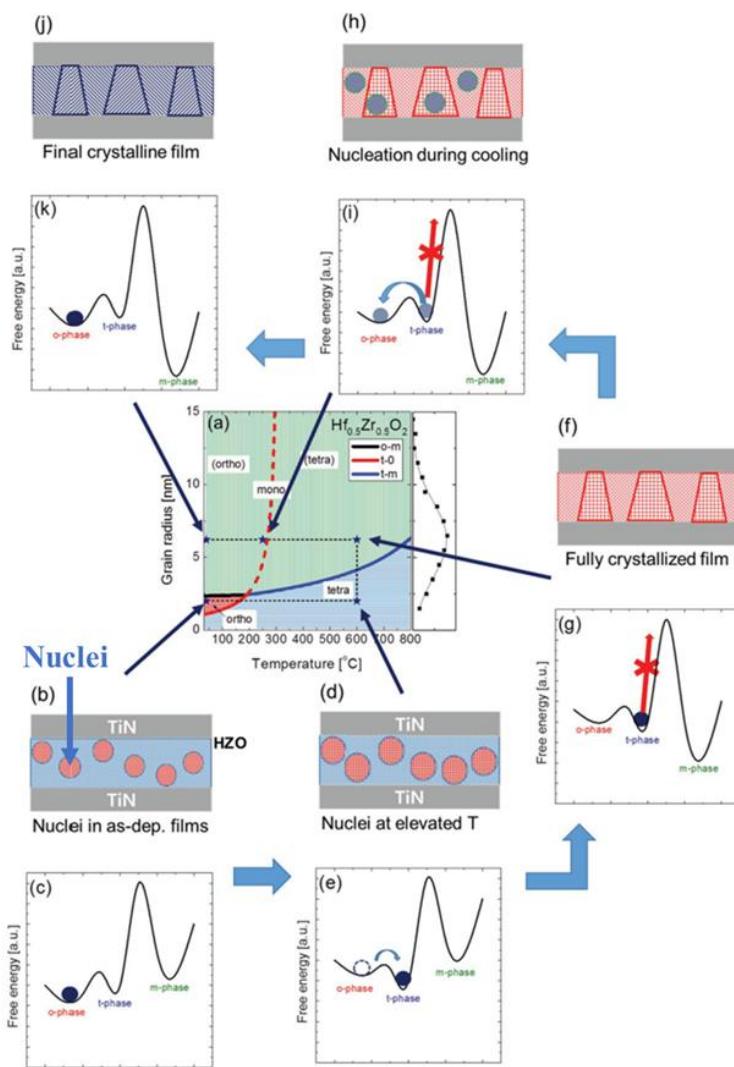

| 圖 3.4 在不同退火階段垂直高度 9.2 nm $Hf_{0.5}Zr_{0.5}O_2$ 晶格與自由能變化示意圖，(a)<br>三相圖，(b)沉積完薄膜示意圖與(c)三相自由能圖，(d)升溫時薄膜示意圖與<br>(e)薄膜三相自由能圖，(f)達到最高溫時薄膜示意圖與(g)薄膜三相自由能圖，<br>(h)降溫時薄膜示意圖與(i)薄膜三相自由能圖，(j)退火完薄膜示意圖與(k)薄<br>膜三相自由能圖[68]。 ..... | 27 |

| 圖 3.5 (a)MFS 結構示意圖[70]，(b)FeFET $I_D-V_G$ 曲線[71]，(c)圖解法判定臨界電壓                                                                                                                                                         |    |

|                                                                                                                                                                            |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 下的操作電場，其中 $E_+$ 與 $E_-$ 分別代表兩個臨界電壓分別對應的電場， $\sigma_0$ 為半導體在臨界電壓時的通道載子密度[70]，(d)MFIS 結構示意圖[70]。.28                                                                          |    |

| 圖 3.6 (a)背閘極鐵電場效電晶體元件示意圖，(b)背閘極鐵電場效電晶體極化向上<br>(朝向通道)示意圖與(c)背閘極鐵電場效電晶體極化向下示意圖[60]。.....29                                                                                   |    |

| 圖 3.7 閘極/鐵電氧化層/二硫化鉬能帶圖(a)鐵電極化方向朝向通道(低阻態)[73]，<br>(b)鐵電極化方向朝向閘極(高阻態)[73]與(c) $I_D-V_G$ 逆時針遲滯曲線示意圖<br>[32]。 .....                                                            | 29 |

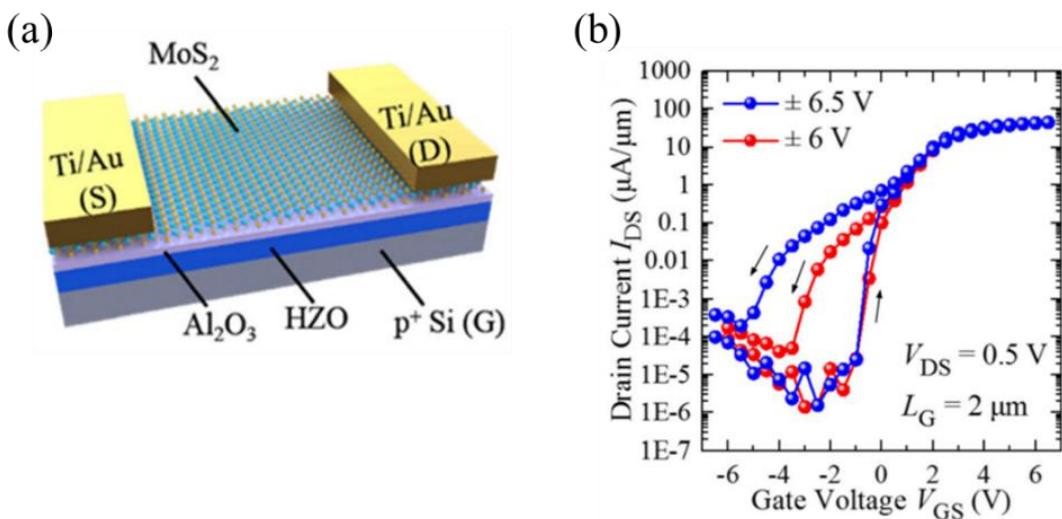

| 圖 3.8 二硫化鉬鐵電場效電晶體(a)元件示意圖與(b)其 $I_D-V_G$ 圖[74]。 .....                                                                                                                      | 30 |

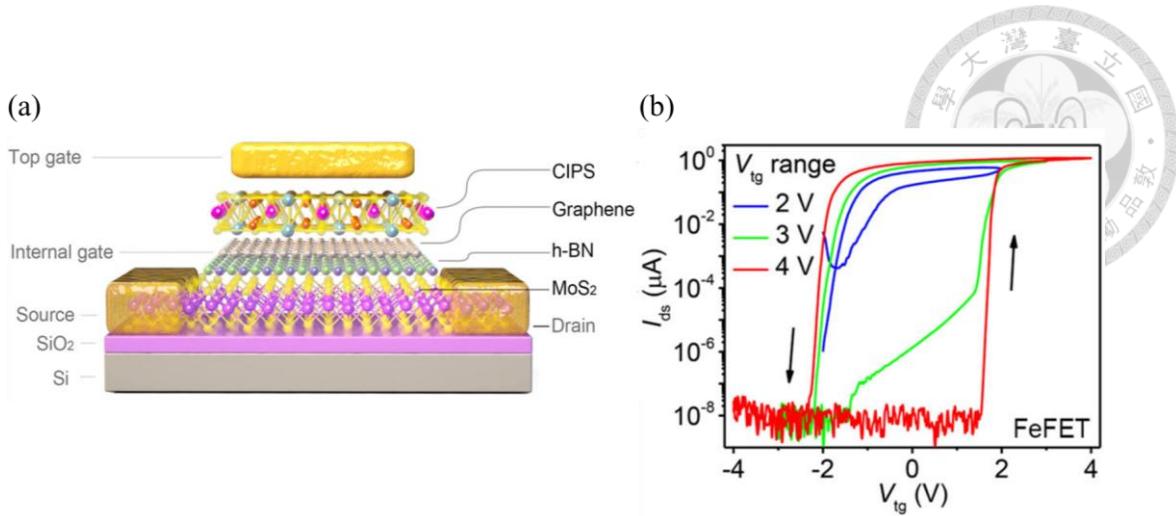

| 圖 3.9 金屬-鐵電-金屬-介電層-半導體(MFMIS)結構堆疊之二硫化鉬鐵電場效電<br>晶體(a)元件示意圖與(b)其 $I_D-V_G$ 圖[75]。 .....                                                                                      | 31 |

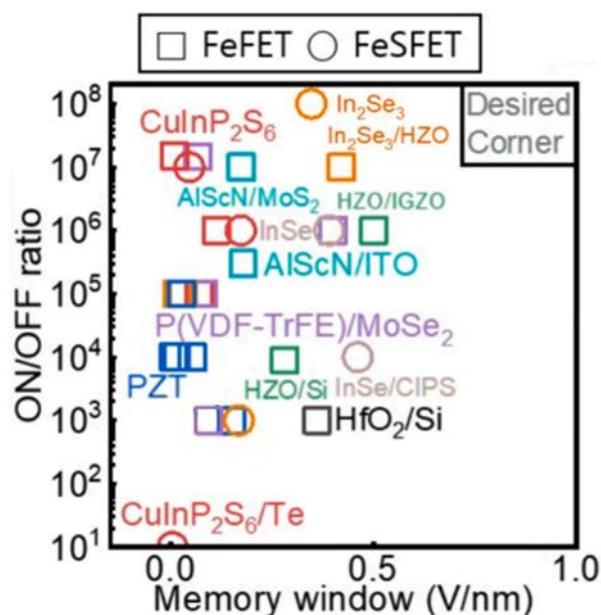

| 圖 3.10 比較不同鐵電電晶體(方形框)與鐵電半導體電晶體(圓形框)[77]。 .....                                                                                                                             | 31 |

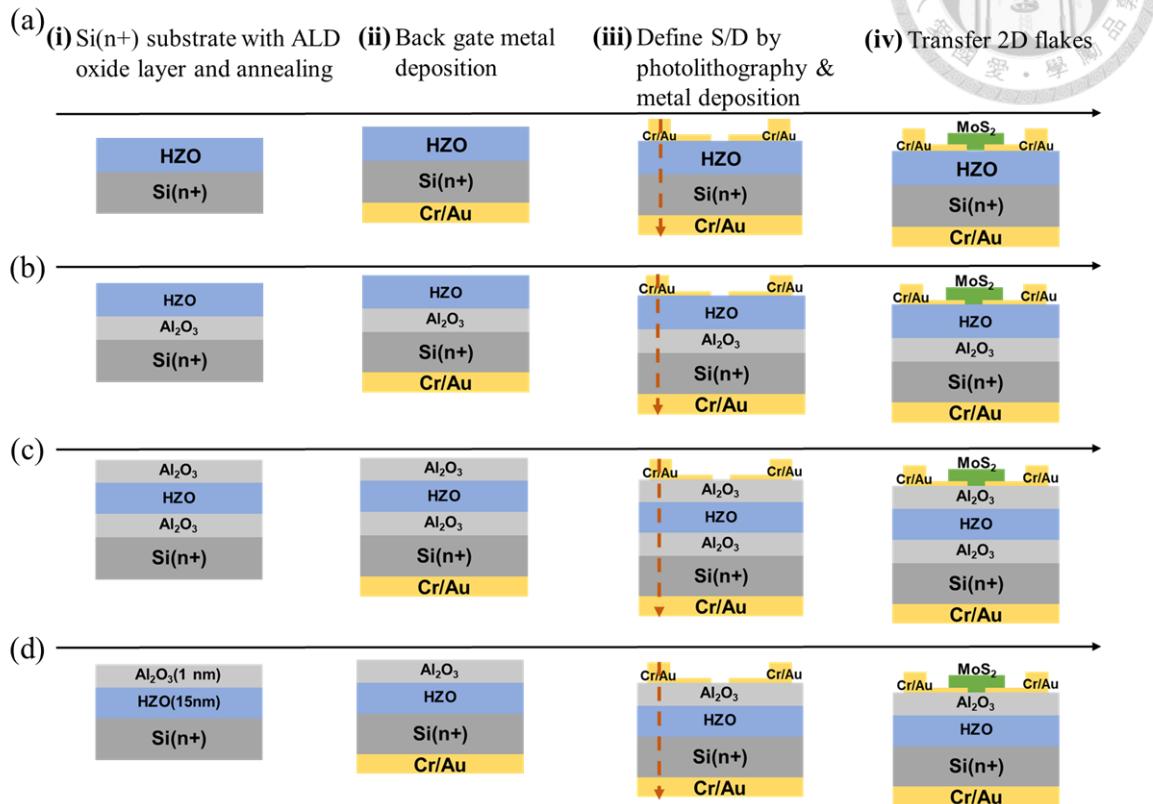

| 圖 3.11 二維材料鐵電場效電晶體包含四種不同氧化層堆疊製程流程示意圖(a)氧<br>化層為 HZO，(b)氧化層為 HZO/ $Al_2O_3$ ，(c)氧化層為 $Al_2O_3/HZO/Al_2O_3$ 與<br>(d)氧化層為 $Al_2O_3/HZO$ 。 .....                               | 33 |

| 圖 3.12 ALD 循環示意圖(以 $Al_2O_3$ 為例)[79]。 .....                                                                                                                                | 33 |

| 圖 3.13 金屬-鐵電層(+介面層)-矽(MF(+I)S)結構電容極化-電壓(P-V)量測結果，右<br>下插圖為元件示意圖(a)HZO 厚度 10 nm，(b)HZO 厚度 15 nm 與(c)HZO 厚<br>度 15 nm 並有額外一層 TiN 形成 MF(+I)M 結構。 .....                        | 34 |

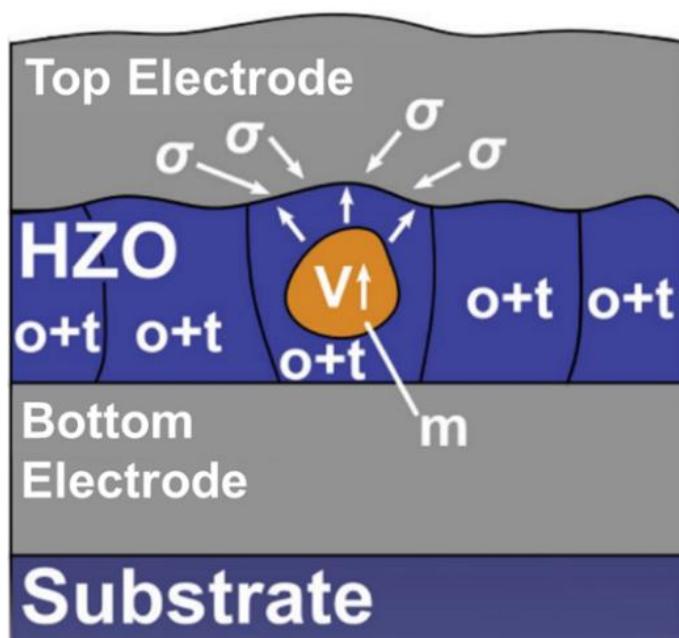

| 圖 3.14 鐵電 HZO 電容覆蓋效應(Capping effect)示意圖[80]。 .....                                                                                                                         | 35 |

| 圖 3.15 比較不同電容的剩餘極化值。 .....                                                                                                                                                 | 37 |

| 圖 3.16 (a)矽與氧化層間介面偶極示意圖，(b)對於 MIS 結構翻轉不同極化方向能<br>量示意圖與(c)對於 MIM 結構翻轉不同極化方向能量示意圖[84]。 .....                                                                                 | 37 |

| 圖 3.17 HZO 厚度 10 nm 不同氧化層堆疊之鐵電電晶體 $I_D-V_{OV}$ 曲線與總結，圖中<br>插圖為氧化層堆疊示意圖(a)HZO，(b)HZO/ $Al_2O_3$ ，(c) $Al_2O_3/HZO/Al_2O_3$ ，<br>(d) $Al_2O_3/HZO$ 。(e)記憶體視窗對應不同氧化層堆疊。 ..... | 38 |

| 圖 3.18 (a)MFS 結構中存在介面電荷示意圖，(b)圖解法判定有介面電荷情況下於<br>臨界電壓的操作電場，(c)有固定介面電荷情況下於臨界電壓的操作電場，<br>(d)有非對稱介面電荷情況下於臨界電壓的操作電場[70]。 .....                                                  | 39 |

| 圖 3.19 缺陷存在於矽-氧化層-二硫化鉬示意圖(a)水氧被吸附在二硫化鉬表面，(b)                                                                                                                               |    |

|                                                                                                                                                                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 於氧化層靠近半導體側與氧化層，(c)二硫化鉬本質缺陷[85]。.....                                                                                                                                                                                                                                  | 40 |

| 圖 3.20 HZO 厚度 15 nm 不同氧化層堆疊之鐵電電晶體 Id-Vov 曲線與總結，圖中<br>插圖為氧化層堆疊示意圖(a)HZO，(b)HZO/Al <sub>2</sub> O <sub>3</sub> ，(c)Al <sub>2</sub> O <sub>3</sub> /HZO/Al <sub>2</sub> O <sub>3</sub> ，<br>(d)Al <sub>2</sub> O <sub>3</sub> /HZO。(e)記憶體視窗對應不同氧化層堆疊。.....               | 41 |

| 圖 3.21 沒有足夠電洞平衡極化示意圖[90]。.....                                                                                                                                                                                                                                        | 42 |

| 圖 3.22 HZO 厚度 15 nm 不同氧化層堆疊加上額外 TiN 之鐵電電晶體 Id-Vov 曲線<br>與總結，圖中插圖為氧化層堆疊示意圖 (a)HZO，(b)HZO/Al <sub>2</sub> O <sub>3</sub> ，<br>(c)Al <sub>2</sub> O <sub>3</sub> /HZO/Al <sub>2</sub> O <sub>3</sub> ，(d)Al <sub>2</sub> O <sub>3</sub> /HZO。(e)記憶體視窗對應不同氧化層堆疊。<br>..... | 43 |

## 表次

|                                                              |    |

|--------------------------------------------------------------|----|

| 表 1.1 不同記憶體的參數特性比較[35]。                                      | 8  |

| 表 3.1 比較不同鐵電材料氧化層，包含 PZT、PVDF 與基於 HfO <sub>2</sub> 鐵電材料[60]。 | 25 |

# 第 1 章 引言

## 1.1 研究動機

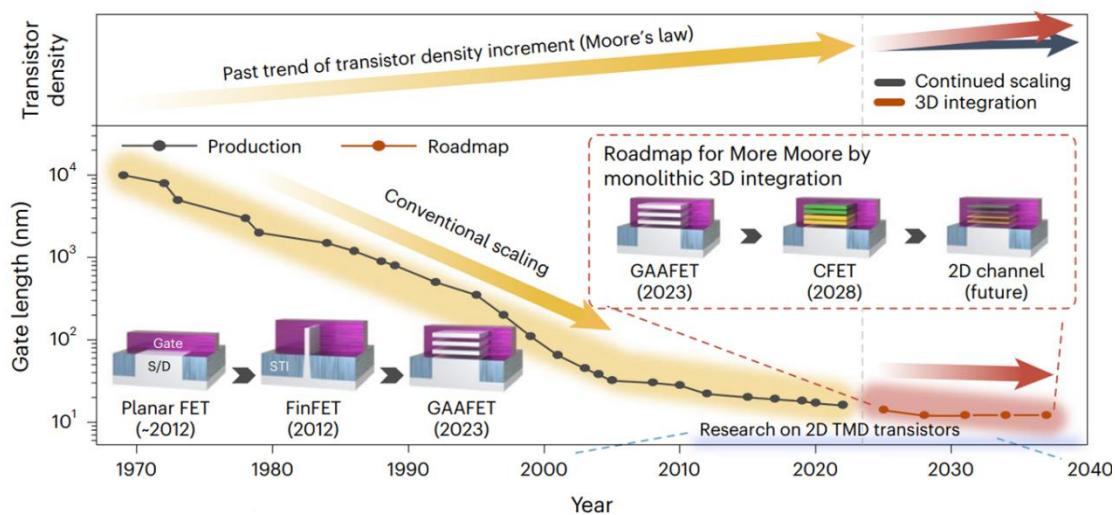

在 1965 年，摩爾預測積體電路上的元件數量每年可增加一倍(元件尺寸微縮約 0.7 倍)[1]，後來逐漸轉變為每兩年增加一倍[2]，摩爾定律持續有效並維持了數十年，根據國際元件和系統藍圖(International Roadmap for Devices and Systems, IRDS)預測(圖 1.1)[3]，過去實踐摩爾定律的主要策略為縮小電晶體尺寸，但隨著電晶體微縮所面臨的短通道效應(Short-Channel Effect)[4]與散熱(Heat Dissipation)[5]問題，逐漸將電晶體創新的策略改為功能性微縮，如應變矽(Strained Silicon)減少電子有效質量以提高載子遷移率[6]，或使用高介電係數(high-k)材料作為氧化層，增加氧化層厚度以減少漏電流[7]，並提供較好的閘極控制能力，後續也出現有別於平面電晶體(Planar FET)的結構，如鰭式電晶體(FinFET)與環繞閘極電晶體(Gate-All-Around FET)，藉由增加閘極與通道接觸面積，在微縮尺度下實現更好的通道控制能力，這些發明使得摩爾定律延續。然而，傳統通道材料如矽、應變矽鋒(SiGe)或三-五族材料，其厚度持續下降會因為量子限制(Quantum confinement)與表面散射機制[8]使遷移率下降，可能成為延續摩爾定律的瓶頸，因此，透過 3D 整合技術(Monolithic 3D Integration)將元件垂直堆疊，成為持續增加電晶體密度的可行途徑，但是在整合元件上定位單晶通道較困難，同時存在製程熱預算限制(Thermal Budget)[9]問題。另一方面，二維材料本身為層狀結構，載子限制在厚度非常薄的通道中，這些數原子厚度的二維材料具有無懸浮鍵(dangle-bond-free)特性，使通道

圖 1.1 根據 IRDS 繪製的電晶體預測藍圖[3]。

載子具有高遷移率[10]，不會如同傳統通道材料受表面散射影響。此外，開極電壓對數原子厚度的二維材料通道的控制精確，在通道長度微縮趨勢下，具有潛力不受短通道效應影響[11]，二維材料成為有希望延續摩爾定律的選擇，本論文使用二維材料作為電晶體通道進行研究，並於後續介紹二維材料與二維材料電晶體。

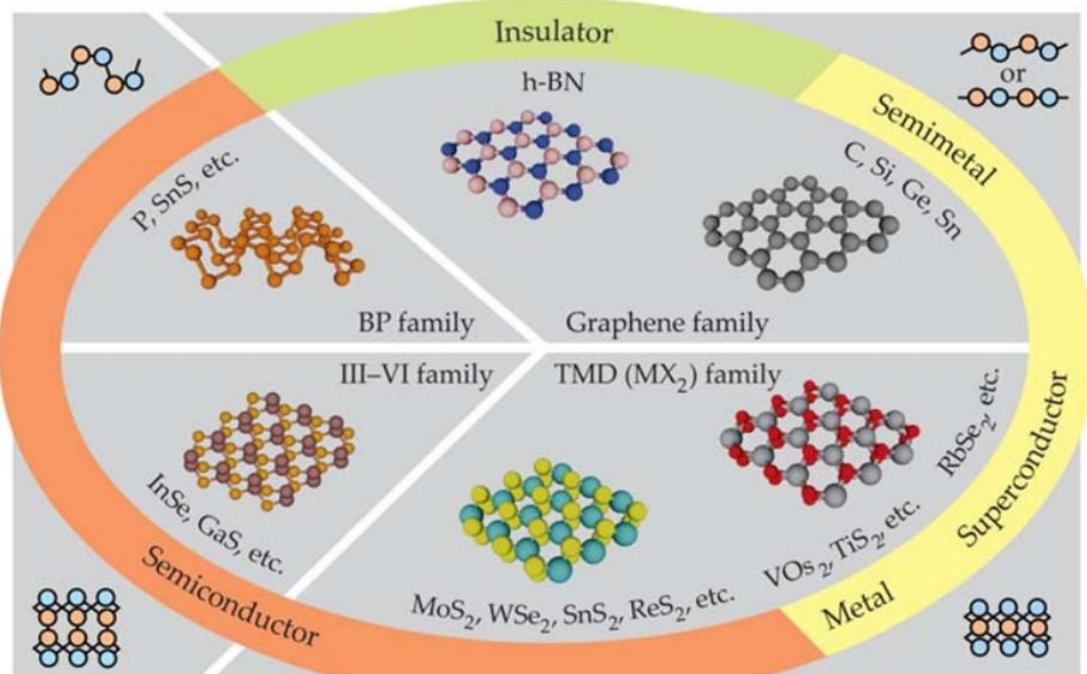

## 1.2 二維材料

二維材料在垂直方向只有單層，平面內以較強的共價鍵結合，層與層間以較弱的凡德瓦力(Van der Waals force)連結，因此可以將單層二維材料從塊材(Bulk)剝離，單層材料與剩餘的結構幾乎不會受到損傷，而層狀結構相對容易轉移到其他基板，實現較好的異質接面。這些二維材料涵蓋各種電性，不同電性二維材料分類(圖 1.2)[12]，包含絕緣體如氮化硼(BN)、半導體如二硫化鉬(MoS<sub>2</sub>)與半金屬如石墨烯(Graphene)，單獨或是混合搭配這些層狀材料，有望設計出新型的薄膜電子元件系統。作為半導體的二維材料能隙範圍約在 0.5-3 eV，不同二維材料的能隙對應晶格常數如圖 1.3 所示，大部分屬過渡金屬二硫族化物(Transition-Metal Dichalcogenides, TMDs)，一個過渡金屬如鉬、鎢(W)、釤(V)與兩個相同硫化物如硫(S)、硒(Se)、碲(Te)鍵結形成 MX<sub>2</sub> 分子結構，二硫化鉬與二硒化鎢分別對應到 n-type 與 p-type 電

圖 1.2 不同電性二維材料[12]。

圖 1.3 (a)不同二維材料的能隙與晶格常數的關係圖(實心點為塊材，空心點為單層二維材料)，(b)二維材料與矽載子遷移率與通道厚度之關係圖[10]。

晶體通道材料，這兩種材料備受關注因其皆具有較大能隙與高載子遷移率[13]。與傳統的電晶體通道矽相比，載子遷移率對應通道厚度的關係如圖 1.3(b)所示，二硫化鉑與二硒化鎢在通道厚度在小於 3 nm 時仍保持良好的載子遷移率，而矽的載子遷移率自通道厚度小於 5 nm 後顯著下降，二維材料電子局限於單層中，載子遷移不受不受表面散射機制影響，因此不隨通道厚度下降而降低載子遷移率[10]。目前，單層 TMDs 材料的晶圓級(Wafer-scale)成長已經實現，可以透過化學氣相沉積(Chemical vapor deposition ,CVD)製程成長單層二硫化鉑於藍寶石基板[14]，與現代製程技術相容，具有量產潛力。

在文獻[15]中，Xie 等人製作二維材料場效電晶體，元件結構示意圖如圖 1.4(a)所示，半導體通道為單層二硫化鉑，氮化硼作為上方閘極絕緣層，並額外使用石墨烯做為源極/汲極接觸金屬，定義出通道長度(Channel length,  $L_{ch}$ )，石墨烯的費米能階可由電壓調變，與二硫化鉑形成歐姆接觸(Ohmic contact)[16]，提供較大導通電流。通道長度 9 nm 的二維材料電晶體  $I_D$ - $V_G$  電性量測結果如圖 1.4(b)所示，頂部閘極掃描範圍在 -2~2 V 下，電晶體展現大於  $10^7$  電流開關比(On/Off ratio)，與 93 mV/dec 良好臨界值擺幅。單層二硫化鉑中電子有相對大的有效質量(Effective mass)，減少源極與汲極間穿隧，降低了次臨界擺幅值[17]，在通道長度 9 nm 下，僅有約為 0.3 pA/ $\mu$ m 的關閉(Off)電流。載子遷移率對應通道長度關係圖如圖 1.4(c)所示，

圖 1.4 二維材料電晶體之(a)元件示意圖，(b)通道長度 9 nm 之電晶體  $I_D$ - $V_G$  電性量測結果，(c)載子遷移率-通道長度關係圖與(d)臨界值擺幅-通道長度關係圖[15]。

隨著電晶體通道長度減短，載子遷移率有下降的趨勢，但在通道長度僅有 4 nm 時仍保有大於  $20 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  的載子遷移率。臨界值擺幅與通道長度的關係圖如圖 1.4(d)所示，對於通道長度大於 9 nm 的電晶體，臨界值擺幅小於  $100 \text{ mV/dec}$ ，電晶體保有良好開關效率，當通道長度僅有 4 nm 時，臨界值擺幅約大於  $200 \text{ mV/dec}$ 。總結這篇文獻，二維材料電晶體在極短通道(9 nm)下仍保有相對高載子遷移率，與低臨界值擺幅值，展現出對短通道效應抗性，顯示二維材料運用於電晶體微縮發展的潛力。

### 1.3 鐵電記憶體

鐵電典型的 P-E 關係圖如圖 1.5 所示[18]，鐵電材料在沒有施加電場時仍然保有極化，稱為剩餘極化(Remant polarization,  $P_r$ )，施加一個大於正矯頑電場(Coercive field,  $E_c$ )或是小於負矯頑電場的電場，可以翻轉鐵電材料的極化方向，鐵電材料具有兩個穩定的極化狀態，極化狀態可以藉由電場改變，移除電場後鐵電材料仍存在剩餘極化，此特性可以運用於非揮發(Non-Volatile)記憶體元件。常見的鐵

圖 1.5 鐵電材料之極化-電場關係圖[18]。

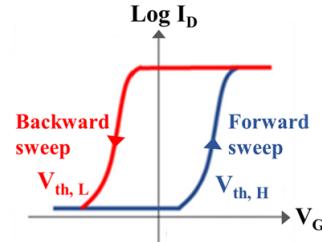

電記憶體元件包含鐵電隨機存取記憶體(Ferroelectric Random-Access memory, FeRAM)、鐵電場效電晶體(Ferroelectric Field Effect Transistor, FeFET)與鐵電穿隧接面(Ferroelectric Tunnel Junction, FTJ)如圖 1.6 所示，紅色與藍色箭頭代表極化穩定的兩種方向[19]。一、FeRAM 由一個電晶體與鐵電電容組成如圖 1.6(a)所示，在電晶體打開的狀態下，於鐵電電容上方施加一正電壓改變極化向下，讀取時在電容上施加負電壓使極化由下轉上，產生轉換電流(Switching current)如圖 1.6(a)下方紅線所示，相反地，若儲存在電容的極化是向上，讀取時施加負電壓，電流幾乎不會改變如圖 1.6(a)下方藍線所示，藉此判斷原本資料，值得注意的是，FeRAM 經過讀取後極化都會在同方向，為一種破壞性(Destructive)讀取，讀取完後需重新寫入新的資料。二、FeFET 將電晶體氧化層替換為鐵電材料，這裡以 n-type 電晶體為例，其元件示意圖如圖 1.7(b)所示，藉由在電晶體閘極施加正電壓或負電壓寫入不同極化狀態，舉例來說，施加一個正電壓使極化向下，靠近通道的氧化層有相對較多正電荷，吸引通道電子，電晶體通道較容易打開，因此臨界值電壓向負方向偏移，如圖 1.7(b)下方紅線所示，相反地，在閘極施加一個負電壓使極化向上，靠近通道的氧化層有相對較多負電荷，排斥通道電子，電晶體通道需要更大的電壓打開，臨界值電壓向正方向偏移，如圖 1.7(b)下方藍線所示，在相同電壓範圍下讀取到的電流不同，藉此判斷原本寫入的資料，讀取時並不會改變原本的極化，是非破壞性讀取，兩種狀態的臨界電壓差稱為記憶體視窗。三、FTJ 結構為上下金屬包覆鐵電材料

圖 1.6 (a)鐵電隨機存取記憶體(FeRAM)，(b)鐵電場效電晶體(FeFET)與(c)鐵電穿隧接面(FTJ)[19]。

如圖 1.6(c)所示，對於鐵電材料施加不同電壓，改變極化狀態，同時改變能障高度，不同能障高度對應到不同穿隧電阻(Tunneling Resistance, TER)，也對應到不同穿隧電流，舉例來說，在電容上方施加正電壓，使極化向下，有較小穿隧電阻，對應到較大穿隧電流，藉由讀取電流高低可以判斷原本寫入的資料，如圖 1.6(c)下方所示，也為非破壞性讀取，但是 FTJ 較低的電流密度限制了讀取資料的速度，但可以用於大量平行運算(Parrallel Processing)[19]。

FeFET 元件在 1960 年代提出，Moll 與 Tarui 發表鐵電材料硫酸三甘氨酸(triglycine sulfate, TGS)的剩餘極化特性可以控制半導體材料硫化鎘(cadmium sulfide, CdS)的空間電荷(Space charge)[20]，使元件電阻改變，而 Zuleeg 與 Wieder 發表鐵電材料場效特性可以用於改變電晶體臨界值電壓[21]，是 FeFET 最顯著的特性。1974 年，Wu 發表第一個 FeFET 元件採用金屬-鐵電-半導體(MFS)結構(圖 1.7(a))[22]，採用鐵電材料鈦酸鉍(bismuth titanate)薄膜製作在矽塊材上，這種結構的優點為與傳統平面金屬-氧化層半導體電晶體結構相同，不同之處為閘極氧化層替換成鐵電材料，但是 MFS 結構有鐵電材料與矽原子間擴散(inter-diffusion)問題[23][24]，影響 FeFET 的記憶體特性，因此在鐵電層與半導體材料間多加一層氧化層作為介面層(interfacial layer)，也稱為緩衝層(buffer layer)，形成金屬-鐵電-介電層-半導體(MFIS)結構(圖 1.7(b))，改善 MFS 結構所遇到問題。隨後，許多不同鈣鈦

圖 1.7 (a)MFS 結構與(b)MFIS 結構之 FeFET 元件示意圖[25]。

礦 (perovskite) 鐵電材料如鎵鈦酸鉛 (lead zirconate titanate, PZT) 與鉭酸鋨鈦 (strontium bismuth tantalate) 陸續應用於元件[25]，如 Sakai 等人發表採用 SBT 鐵電材料製作 FeFET[26]，展現記憶體視窗達 1.6 V，且耐久度(endurance)高於  $10^{12}$ 。但是部分鈣鈦礦材料含鉛具毒性，並且難以與矽整合，為了達到足夠大的記憶體電壓與低漏電，鈣鈦礦材料需厚於 100 nm[25][26]，不符元件微縮趨勢。

在 2011 年，Müller 等人提出二氧化鈽 ( $\text{HfO}_2$ ) 薄膜具有鐵電特性[27]，這種材料有望改善上述鈣鈦礦材料所遇到問題， $\text{HfO}_2$  可以作為高介電係數金屬 (high-k metal gate, HKMG) 的介電質[7]，展現與 CMOS 製程相容，此外， $\text{HfO}_2$  具有較大的矯頑電場 ( $\sim 1 \text{ MV cm}^{-1}$ ) 與相對鈣鈦礦材料低的介電係數 ( $k \sim 30$ )[7]，使  $\text{HfO}_2$  在數奈米厚度下，具與鈣鈦礦材料相近的記憶體視窗範圍與穩定的資料保存能力 (retention)，這些優點使  $\text{HfO}_2$  鐵電材料之 FeFET 迅速發展。 $\text{HfO}_2$  鐵電材料之 FeFET 發展圖如圖 1.8 所示，在 2011 年，Böscke 等人製作出首個  $\text{HfO}_2$  之 FeFET[28]，元件結構圖

圖 1.8  $\text{HfO}_2$  鐵電材料之 FeFET 發展演進圖[25]。

圖 1.9  $\text{HfO}_2$  鐵電材料 FeFET 之(a)元件結構圖與(b)  $I_D$ - $V_G$  電性量測結果[28]。

如圖 1.9(a)所示，採用 MFIS 結構， $I_D$ - $V_G$  電性量測結果如圖 1.9(b)所示，展現大約 1 V 記憶體視窗。隨後，在文獻[29]中，Müller 等人成功將 FeFET 整合至 28 nm HKMG 製程技術。在文獻[30]中，Mulaosmanovic 等人改變鐵電材料不同極化程度，證明 FeFET 可以讀取到多種狀態(multi-level)，具有成為多位元記憶體的潛力。後續將 FeFET 擴展到更大容量的記憶體陣列[31]，在先進的平面[32]與垂直技術中整合[33]，以及將 FeFET 與邏輯裝置整合在同一主動區[34]，提升 FeFET 在嵌入式非揮發記憶體(embedded NVM)應用中的關注度，與未來運用在類神經(neuromorphic)運算與記憶體內(logic-in-memory)運算領域展現潛力。綜合上述，利用二氧化鎵( $\text{HfO}_2$ )鐵電材料製作 FeFET 備受關注，因其與現代 CMOS 製程相容，具有高速度寫入，與低功耗的優點[32]，FeFET 是單電晶體(1T)記憶體元件，不需額外的電容元件，與傳統快閃記憶體相比架構更簡單，在晶片上的占用面積較小，有望運用於 NAND 快閃記憶體 3D 垂直堆疊結構，實現採用多晶矽通道的 3D 垂直 FeFET[33]。

表 1.1 不同記憶體的參數特性比較[35]。

| Technology           | CMOS Mainstream Memories |                   |                    |                    | Memristive Emerging Memories |                    |         |            |                  |

|----------------------|--------------------------|-------------------|--------------------|--------------------|------------------------------|--------------------|---------|------------|------------------|

|                      | NOR Flash                | NAND Flash        | RRAM               | PCM                | STT-MRAM                     | FeRAM              | FeFET   | SOT-MRAM   | Li-ion           |

| ON/OFF Ratio         | $10^4$                   | $10^4$            | $10\text{-}10^2$   | $10^2\text{-}10^4$ | 1.5-2                        | $10^2\text{-}10^3$ | 5-50    | 1.5-2      | $40\text{-}10^3$ |

| Multilevel operation | 2 bit                    | 4 bit             | 2 bit              | 2 bit              | 1 bit                        | 1 bit              | 5 bit   | 1 bit      | 10 bit           |

| Write voltage        | <10 V                    | >10 V             | <3V                | <3V                | <1.5 V                       | <3 V               | <5 V    | <1.5 V     | <1 V             |

| Write time           | 1-10 $\mu\text{s}$       | 0.1-1 ms          | <10 ns             | ~50 ns             | <10 ns                       | ~30 ns             | ~10 ns  | <10 ns     | <10 ns           |

| Read time            | ~50 ns                   | ~10 $\mu\text{s}$ | <10 ns             | <10 ns             | <10 ns                       | <10 ns             | ~10 ns  | <10 ns     | <10 ns           |

| Stand-by power       | Low                      | Low               | Low                | Low                | Low                          | Low                | Low     | Low        | Low              |

| Write energy (J/bit) | ~100 pJ                  | ~10 fJ            | 0.1-1 pJ           | 10 pJ              | ~100 fJ                      | ~100 fJ            | <1 fJ   | <100 fJ    | ~100 fJ          |

| Linearity            | Low                      | Low               | Low                | Low                | None                         | None               | Low     | None       | High             |

| Drift                | No                       | No                | Weak               | Yes                | No                           | No                 | No      | No         | No               |

| Integration density  | High                     | Very High         | High               | High               | High                         | Low                | High    | High       | Low              |

| Retention            | Long                     | Long              | Medium             | Long               | Medium                       | Long               | Long    | Medium     | -                |

| Endurance            | $10^5$                   | $10^4$            | $10^5\text{-}10^8$ | $10^6\text{-}10^9$ | $10^{15}$                    | $10^{10}$          | $>10^5$ | $>10^{15}$ | $>10^5$          |

不同記憶體的參數比較如表 1.1 所示[35]，FeFET 可以透過改變不同極化程度實現多位元(Multilevel)操作，其他優點包含快速的寫入與讀取速度、高記憶體密度、高保存時間(Retention)與高耐久度(Endurance)，具有取代快閃記憶體的潛力，並可在未來運用於記憶體內計算(In-Memory Computing)。FeFET 在元件尺寸微縮下，仍會遇到傳統半導體通道的限制，因此本論文將使用二維材料作為 FeFET 通道進行研究。

## 1.4 論文架構

本論文在第一章分別介紹二維材料與鐵電記憶體，二維材料在元件尺度為縮下仍保有良好電性，有望成為延續摩爾定律的半導體通道材料，鐵電電晶體是一種新穎的非揮發記憶體，具潛力取代傳統快閃記憶體，使用二維材料作為鐵電電晶體通道為本論文研究動機。在第二章回顧二硫化鉬電晶體相關文獻，並設計以二硫化鉬作為通道的場效電晶體製程流程，完成製程後進行電性量測分析，確認製程流程可行。在第三章使用四種不同堆疊方式的鐵電材料氧化鎵鋯(HZO)加上氧化鋁( $\text{Al}_2\text{O}_3$ )作為介電層，製作金屬-介電層-矽(MIS)電容結構進行極化量測，分析不同堆疊方式的鐵電特性，後續製作二維材料通道鐵電場效電晶體，分析鐵電極化以及缺陷對於電晶體電性造成的遲滯曲線。第四章統整全部實驗結果並做出結論，最後提出實驗可以改進的地方與未來可以研究的方向。

## 第 2 章 二硫化鉬場效電晶體

### 2.1 二硫化鉬場效電晶體文獻回顧

在過去十幾年，二硫化鉬(Molybdenum-di-sulphide, MoS<sub>2</sub>)場效電晶體被廣泛研究[36]，二硫化鉬材料特性結合積體電路技術製作電晶體，可以運用於醫療、感測、商用電子等多個領域，被認為是未來具有潛力可以取代矽的材料。過去曾有研究同是二維材料的石墨烯(Graphene)作為電晶體通道，但是石墨烯沒有能隙的特性，有較高的漏電流，導致較差的電流開關比，並不符合低功耗的要求。光致發光量測單層二硫化鉬能隙約為 1.9 eV[37]，參考文獻[38]中提到兩層至多層二硫化鉬能隙約在 1.87-1.83 eV 範圍，且隨二硫化鉬層數增加而下降，二硫化鉬的大能隙可有效抑制電晶體關閉時的漏電流，因此適合作為電晶體通道。

傳統的場效電晶體以矽作為通道，以 n-type 通道電晶體為例，使用 p-type 矽作為基板，隨著閘極電壓增加，當電流導通時操作於反轉區(Inversion)，此時半導體通道表面由 p-type 載子(電洞)反轉成 n-type 輽子(電子)。而二硫化鉬場效電晶體則是多數載子元件[36]，當電流導通時操作於累積區(Accumulation)，若要將電晶體關閉，則需要施加更負的電壓排開通道的電子。二硫化鉬電晶體結構與與矽電晶體相同具有源極、汲極與閘極，不同的是，通常直接使用高濃度摻雜的矽基板作為背閘極(Back-gate)或稱為底閘極(Bottom-gate)，元件結構如圖 2.1(a)所示，於基板上方成長氧化層後，轉移或是沉積二硫化鉬作為通道，以及鍍上金屬直接作為源極與汲極，不需要額外進行離子佈值，此時已具有電晶體特性，其結構與傳統矽電晶體上下相反，後續也可以再沉積氧化層並製作頂閘極(Top-gate)形成雙閘極(Dual-gate)

圖 2.1 (a)底閘極結構與(b)雙閘極結構(包含頂閘極與底閘極)之二硫化鉬場效電晶體結構示意圖。

圖 2.2 單層二硫化鉬作為通道的場效電晶體之(a)元件結構示意圖，(b)背閘極掃描  $I_D$ - $V_G$  量測結果與(c)頂閘極  $I_D$ - $V_G$  量測結果[39]。

[36]，元件結構如圖 2.1(b)所示，根據通道材料層數與閘極位置，可以將元件分類以進行比較。二硫化鉬電晶體有幾個優點，在材料厚度小於 5 nm 時仍保有高的載子遷移率，適合作為電晶體尺寸微縮趨勢下具有競爭力的選擇，有較低的關閉(Off)電流，以及高電流開關比(On/off ratio)與快速切換速度(high switching speed)[36]。

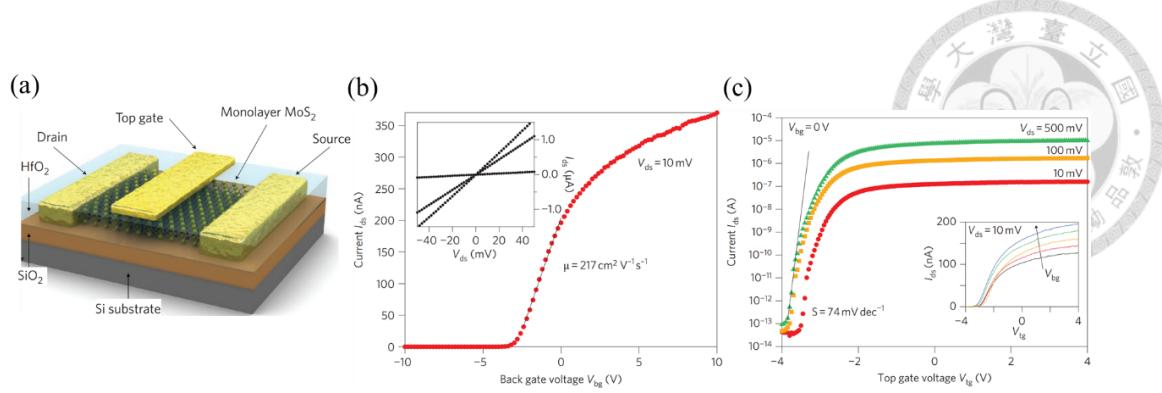

在 2011 年，Radisavljevic 等人首次發表以單層二硫化鉬作為通道的電晶體[39]，其元件結構如圖 2.2(a)所示，以高濃度摻雜矽基板作為閘極，在上方成長厚度為 270 nm 的二氧化矽( $\text{SiO}_2$ )作為氧化層，使用機械式剝離法撕出厚度約為 0.65 nm 的單層二硫化鉬並轉移至氧化層上，後續鍍上金作為源極與汲極，完成背閘極元件，後續再成長厚度為 30 nm 的二氧化鈦( $\text{HfO}_2$ )，最後製作頂閘極。在室溫下，背閘極掃描下的  $I_D$ - $V_G$  量測結果如圖 2.2(b)所示，由負電壓掃描到正電壓看到明顯的關閉電流與導通電流，展現如同典型 n-type 電晶體曲線，萃取場效載子遷移率高於 200

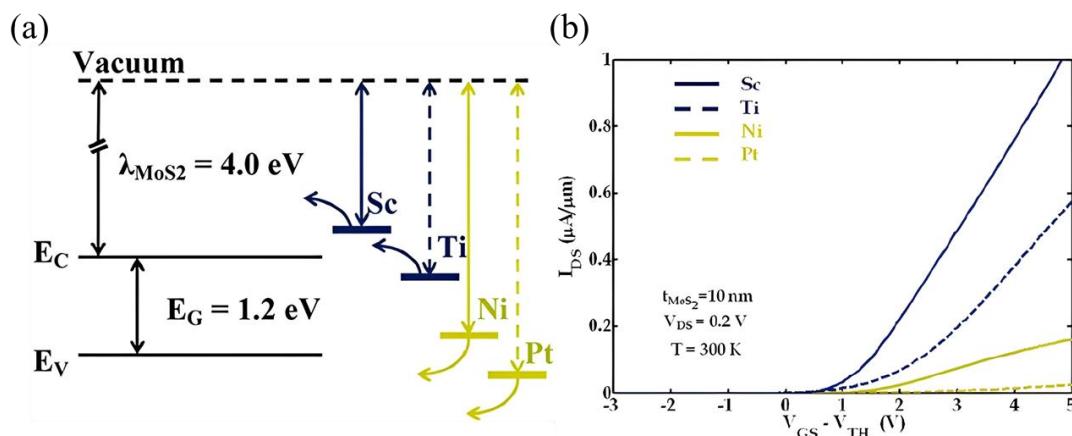

圖 2.3 (a)二硫化鉬與金屬釔(Sc)、鈦(Ti)、鎳(Ni)與鉑(Pt)能帶示意圖與(b)多層二硫化鉬背閘極電晶體改變不同接觸金屬之  $I_D$  對應  $V_{GS} - V_{TH}$  量測結果[42]。

$\text{cm}^2/\text{V}\cdot\text{s}$ 。將基板接地後，量測頂閘極掃描下的  $I_D$ - $V_G$  量測結果如圖 2.2(c)所示，在  $V_{DS}$  為 0.5 V 條件下，二硫化鉬電晶體展現高達  $10^8$  電流開關比，以及次臨界擺幅值低至 74 mV/dec。因為單層的二硫化鉬中電子有相對大的有效質量(Effective mass)，減少源極與汲極間穿隧，降低了次臨界擺幅值[17]。總結這篇文獻，單層二硫化鉬場效電晶體有良好電性，以及與矽薄膜(Silicon films)[40]或石墨烯奈米帶(Graphene nanoribbons)[41]相近的載子遷移率。

在過去論文中提到有幾個原因會限制二硫化鉬元件的表現，如源極與汲極金屬與二硫化鉬之間的接觸會影響電晶體電性，Das 等人比較了不同接觸金屬對於多層二硫化鉬背閘極電晶體的影響[42]，二硫化鉬與其他金屬的能帶圖示意圖如圖 2.3(a)所示，功函數越小的金屬做為接觸金屬之電晶體展現較大導通電流。二硫化鉬的電子親和力約為 4 eV，較小功函數的接觸金屬如銠，其功函數約為 3.5 eV，或是鈦，其功函數約為 4.3 eV，功函數較接近二硫化鉬導帶，金屬與二硫化鉬間有較小的能障，因此有較好的電晶體導通電流(圖 2.3(b))，適合做為接觸金屬，而較大功函數的金屬如鎳(功函數約為 5 eV)與鉑(功函數約為 5.9 eV)，與二硫化鉬有較大的能障，只能導通較小的電流。

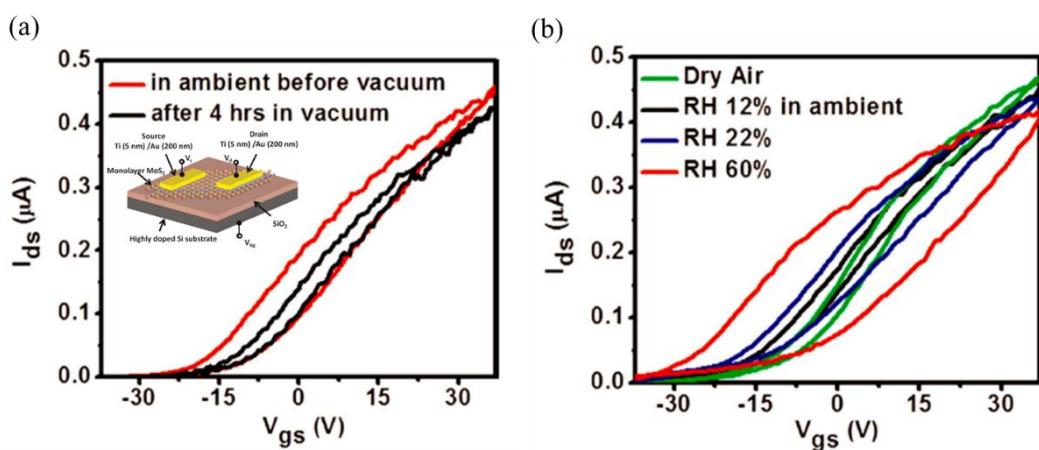

環境因素如濕度、氧氣和光照也會影響到電晶體特性，Late 等人比較在不同環境下對於單層二硫化鉬背閘極電晶體的影響[43]，首先，比較是否將元件放置於真空環境，電晶體之  $I_D$ - $V_G$  量測結果如圖 2.4(a)所示，將元件放置在真空環境中並於 90 °C 加熱 4 小時候量測，由圖中黑色曲線可以看出遲滯現象減小，造成遲滯現象的其中一個原因为環境中的水氣、氧氣吸附於二硫化鉬表面，使得量測時電子被

圖 2.4 (a)放置於真空 4 小時與未經過特別處理之二硫化鉬背閘極電晶體  $I_D$ - $V_G$  量測結果，圖中插圖為元件示意圖。(b)放置於在不同濕度下之  $I_D$ - $V_G$  量測結果[43]。

捕捉。接著，不同環境濕度下對電晶體的  $I_D$ - $V_G$  量測結果如圖 2.4(b)所示，將元件放置在不同濕度條件 30 分鐘後量測，放置於乾空氣中的元件量測結果為最小的遲滯曲線，隨著環境濕度增加，電晶體量測到的遲滯現象也會增加，原因為濕度導致缺陷密度更高，使得更多電子在量測過程中被缺陷捕獲，導致較大的遲滯，二硫化鉬電晶體適合放在真空或乾燥的環境下，欲比較環境以外不同條件元件時，應將元件放在相同環境下量測。

## 2.2 二硫化鉬材料分析

二硫化鉬的結構為一層鉬(Mo)原子被兩層硫(S)原子以共價鍵結構夾著如圖 2.5(a)所示，單層厚度約為 0.65 nm，塊材照片如圖 2.5(b)所示。已剝離過的二維材料在光學顯微鏡下的照片如圖 2.5(c)所示，照片中藍色碎片為二硫化鉬，灰黑色碎片為石墨烯，這些碎片貼在厚度 15 nm 的二氧化矽上，其中從左上、右上延伸出的白色直線為金。透過原子力顯微鏡掃描圖中紅色虛線的高低差結果如圖 2.5(d)所示，在這張圖中位於中間的二硫化鉬厚度為約 20 nm，而右方石墨烯厚度約為 57 nm。

圖 2.5 (a)二硫化鉬晶體結構側視圖[39]，(b)二硫化鉬塊材照片，(c)二硫化鉬與石墨烯光學顯微鏡照片(紅色虛線為剖面)與(d)二硫化鉬與石墨烯 AFM 掃描結果與剖面高度(沿紅色虛線)。

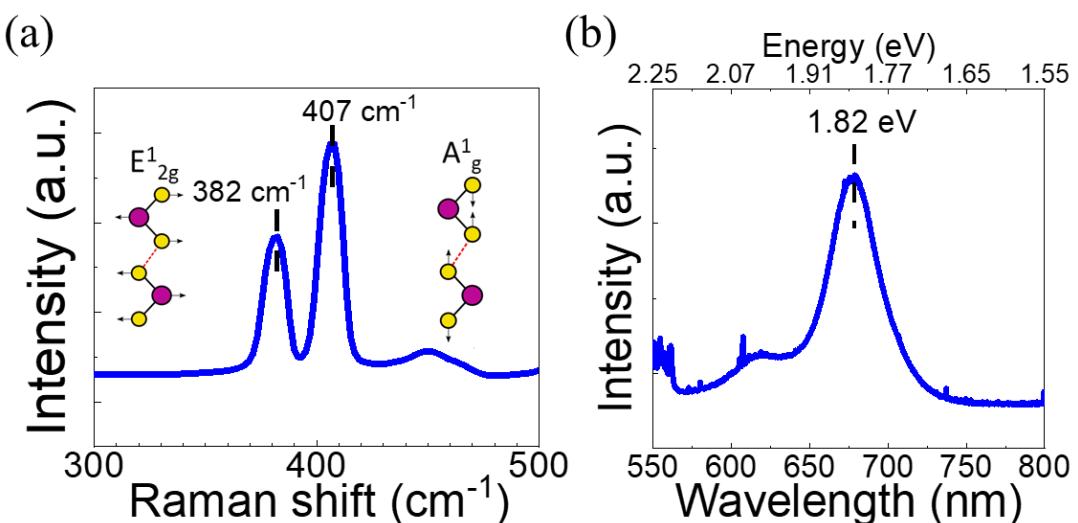

拉曼光譜(Raman Spectroscopy)是一種用來研究材料晶格振動模式的方法，當材料被特定波長的雷射光照射後，光子與聲子產生交互作用，使得光子能量改變，透過分析這些能量變化，稱為拉曼偏移(Raman shift)，可以知道晶格的振動模式。使用波長 532 nm 的綠光雷射打在二硫化鉬上的拉曼光譜結果如圖 2.6(a)所示，縱軸為強度，橫軸為拉曼偏移，圖中插圖紫色與黃色圓圈分別代表鉬原子與硫原子。光譜在拉曼偏移  $300\text{ cm}^{-1}$  到  $500\text{ cm}^{-1}$  範圍內出現兩個強度峰值， $382\text{ cm}^{-1}$  對應到平面(in-plane,  $E_{2g}^1$ )振動模態，源自於鉬原子或硫原子在平面內的振動行為，示意圖如圖 2.6(a)中左方所示； $407\text{ cm}^{-1}$  對應到垂直平面(out-of-plane,  $A_g^1$ )振動模態，由於二硫化鉬層與層間垂直於平面振動，示意圖如圖 2.6(a)中右方所示，出現強度峰值對應的拉曼偏移會因為二維材料層數不同而略有不同，實驗結果與文獻相符[44]。光致發光(Photoluminescence, PL)是一種非接觸與非破壞性的方法，用於探測材料的能隙，當材料被特定波長的光子如雷射光照射後，電子會被激發從價帶跳到導帶，隨後這些激發態的電子會與價帶中的電洞復合，並釋放出光子，這些光子的波長對應強度即為光致發光光譜，其峰值也對應到材料的能隙。單層二硫化鉬具有直接能隙，隨著層數增加，轉變為非直接能隙，並且價帶與導帶的距離變得更靠近[38]。使用波長 532 nm 的綠光雷射打在二硫化鉬上的光致發光結果如圖 2.6(b)所示，縱軸為強度，橫軸為波長，光譜上在波長 678 nm 出現強度峰值，對應到能隙大約為  $1.82\text{ eV}$ ，與文獻結果中多層二硫化鉬對應能隙相符[38][45]。

圖 2.6 (a)二硫化鉬拉曼光譜，圖中兩張插圖為振動模態示意圖[44]。(b)二硫化鉬光致發光光譜。

## 2.3 元件製作流程

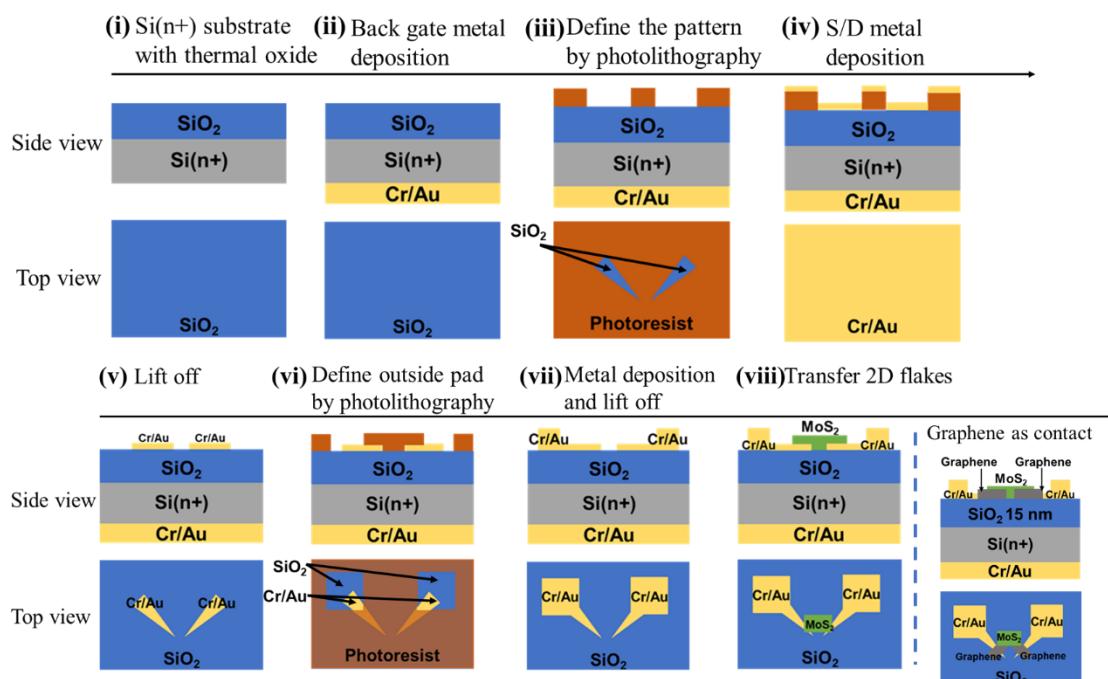

二維材料電晶體的常見製程為背閘極結構，閘極在元件底部與一般常見的電晶體相反，這種設計可以避免在二維材料上方製作閘極而造成可能的薄膜損傷，此外，可以先將汲極與源極金屬鍍好，最後貼上二維材料薄膜，避免薄膜接觸光阻與其他溶液。在本論文中，所有電晶體皆是背閘極結構，並利用金屬作為源極與汲極，而通道材料皆是使用二硫化鉬。元件製作流程如圖 2.7 所示，包含側視與俯視示意圖，步驟說明如下：(i) 使用高濃度磷摻雜的矽基板作為閘極，並且在上方透過乾式熱氧化法成長二氧化矽作為氧化層，(ii) 利用熱蒸鍍法在元件背部鍍上厚度為 20/200 nm 的鉻/金作為閘極的接觸金屬，(iii) 在元件正面旋塗光阻，並且曝光出內部連線的圖形後顯影，(iv) 利用熱蒸鍍法在元件正面鍍上厚度為 10/30 nm 的鉻/金作為源極與汲極，這裡鍍上較薄的金屬使其與平面高低差較小，利於最後二維材料薄片轉移至元件上，(v) 利用掀離法(Lift-off)去除多餘光阻與其上方金屬，僅留下內部連線金屬，(vi) 曝光出利於在探針台下針的較大塊圖形，同時連接已鍍好的內部連線金屬，(vii) 利用熱蒸鍍法在元件正面鍍上厚度為 20/150 nm 的鉻/金，這裡鍍上較厚的金屬是為了下針時不易將金屬戳破，並且使用掀離法留下鍍好金屬的圖形，(viii) 利用乾式轉移法將已剝離過的二維材料薄片轉移到已鍍好的金屬上，而這步

圖 2.7 二硫化鉬場效電晶體製程流程示意圖。

驟在後續將有更詳細的說明。

兩種常見的二硫化鉬製備方法為化學氣相沉積(CVD)與剝離法，CVD 利用化學反應在基板上直接生長薄膜，優點為可以精準控制薄膜厚度與可以大面積生長，適合未來量產，但可能受到前驅物選擇、基板粗糙度與生長溫度影響，進而導致二硫化鉬有較高的缺陷密度與應變。剝離法利用機械方式從塊狀晶體分離出薄膜，提供較好結晶品質和較低的缺陷密度，但受限於尺寸較小以及厚度難以控制[46]。本論文中，皆是採用剝離法，向廠商購買塊材後，使用 Scotch(品牌)膠帶剝離二維材料，並以固化的聚二甲基矽氧烷(PDMS)做為轉移媒介，PDMS 為一種橡膠狀彈性體具有表面黏附性，並且有光學透明性，適合在顯微鏡下對準下方樣品。

二維材料剝離與乾式轉移皆在手套箱中完成[47][48]，以減少大氣環境對二維材料薄膜的影響。機械式剝離法分離二硫化鉬的示意圖如圖 2.8(a)所示，其步驟說明如下:(i)將二硫化鉬塊材放在膠帶上，(ii)接著移開塊材，此時膠帶上面已經有殘留的二維材料(iii)將貼有二維材料部分膠帶對折，(iv)將膠帶黏接觸打開，並且重複步驟(iii)與(iv)五至六次，即完成二維材料剝離。實際照片如圖 2.8(b)所示，(i)為二硫化鉬塊材放在膠帶上，(ii)是將塊材拿起後殘留的二硫化鉬碎片，(iii)看到已剝離的二維材料碎片散布在膠帶上。

乾式轉移在本實驗室中手套箱內的轉移系統中完成，此系統目的將二維材料轉移至樣品的金屬圖形上，其中吸附二維材料的 PDMS 被貼在載玻片上以利轉移進行，系統的示意圖與實際照片如圖 2.9 所示，進行實驗時透過編號 1 顯微鏡由

圖 2.8 機械式剝離法分離二硫化鉬(a)流程示意圖與(b)實際照片。

圖 2.9 手套箱內轉移系統之(a)示意圖和(b)實際照片。

圖 2.10 透過 PDMS 轉移二硫化鉬之流程示意圖。

上往下看到載玻片和在編號 2 載台的樣品，其中載台中間有一真空吸引孔外接管線到幫浦以吸附樣品，編號 3 與 4 可以手動調整載台旋轉角度與高度，編號 5 為電控平台可以調整整個系統在平面上的移動，編號 6 為夾具可以夾住載玻片，編號 7 為控制載玻片在平面上前後左右的電控平台，編號 8 為調整載玻片高度的電控平台，編號 9 可以手動調整載玻片旋轉角度。

轉移二維材料至樣品表面流程如圖 2.10 所示，(i)將 PDMS 貼到已剝離好二維材料的膠帶上，(ii)吸附二維材料後抬起 PDMS，(iii)透過轉移系統將二維材料與樣品表面圖形對齊，圖中黃色圖案為元件表面圖形，(iv)下降載玻片高度使得 PDMS 與樣品表面貼合，(v)將 PDMS 緩慢抬起使得二維材料留在樣品上。

## 2.4 元件電性量測

使用 B1500A 半導體元件參數分析儀進行直流電性量測，將元件源極接地，於汲極施加正電壓，閘極電壓從施加於元件背面。這裡量測三個不同的電晶體，元件

示意圖如圖 2.11 所示，條件如下：元件 A(圖 2.11(a))的氧化層二氧化矽厚度 100 nm，石墨烯做為接觸金屬， $\text{MoS}_2$  厚度約為 55 nm；元件 B(圖 2.11(b))的氧化層二氧化矽厚度 15 nm，石墨烯做為接觸金屬， $\text{MoS}_2$  厚度約為 20 nm；元件 C(圖 2.11(c))的氧化層二氧化矽厚度 15 nm，沒有石墨烯作為接觸金屬， $\text{MoS}_2$  厚度約為 100 nm。元件 A 的  $I_D$ - $V_G$  曲線如圖 2.12(a)所示，縱軸為汲極電流，左邊黑色刻度為對數，右邊紅色刻度為線性，橫軸為背閘極電壓，圖中曲線由分別表示汲極電壓為 1 V、500 mV、200 mV、100 mV。由對數刻度可以看出此元件在  $V_{DS}$  為 1 V 時，電流開關比大於  $10^5$ (過驅電壓為 1.1 V)，次臨界擺幅的最小值約為 120 mV/dec。元件 B 的  $I_D$ - $V_G$  曲線如圖 2.12(b)所示，電晶體的電流開關比約為  $10^6$ ，而次臨界擺幅最小值約為 90 mV/dec。元件 C 的  $I_D$ - $V_G$  曲線如圖 2.12(c)所示，此電晶體的電流開關比約為  $10^5$ ，而次臨界擺幅最小值約為 150 mV/dec。

圖 2.11 二硫化銅電晶體之元件示意圖與光學顯微鏡照片。條件分別為：(a)元件 A，氧化層二氧化矽厚度 100 nm，石墨烯做為接觸金屬。(b)元件 B，氧化層二氧化矽厚度 15 nm，石墨烯做為接觸金屬。(c)元件 C，氧化層二氧化矽厚度 15 nm，沒有石墨烯作為接觸金屬。

圖 2.12 二硫化銅電晶體之  $I_D$ - $V_G$  量測結果。分別為：(a)元件 A，(b)元件 B 與(c)元件 C。

比較元件 A(二氧化矽厚度 100 nm)與元件 B(二氧化矽厚度 15 nm)的導通電流，如圖 2.13(a)中黑線與藍線所示，元件 B 的氧化層較薄，具有較大的電容，能在通道中較有效率地產生電荷，因此元件 B 有較大導通電流。元件 A 與元件 B 臨界電壓分別約為 -3.5 V 與 -4 V，根據過去文獻[49]的實驗與模擬結果，底閘極二硫化鉬電晶體的臨界電壓會隨二硫化鉬厚度的上升而下降，這是因為較厚的二硫化鉬擁有較大耗盡層(depletion layer)，需要施加更負的電壓將通道電子完全排開，當二硫化鉬厚度大於最大耗盡寬度(約為 60 nm)[49]，閘極電壓更難有效排開通道較上方電子，導致臨界電壓往負偏移更嚴重。在本實驗中，元件 A 二硫化鉬厚度為 55 nm 較元件 B(20 nm)厚，應該展現更負臨界電壓，但實際上元件 A 却展現較正的臨界電壓，因此，僅以二硫化鉬厚度無法完全解釋結果。若比較兩者的氧化層電容大小，可發現元件 A 的氧化層遠較元件 B 厚，其電容較小，因此需要較大的電壓[50]。接著，比較元件 B 與元件 C 的  $I_D$ - $V_G$  曲線，觀察到在較大電壓時，以 Graphene 做為接觸金屬的導通電流(On current)較大，不同元件的導通電流如圖 2.13(a)所示，在相同氧化層厚度(15 nm)下，Au 與 MoS<sub>2</sub> 因功函數差而形成蕭特基能障[51]，有較大的接觸電阻，而 Graphene 的功函數會隨施加電壓上升而減少，可以與 MoS<sub>2</sub> 形成歐姆接觸[52]，有較小的接觸電阻，提高導通電流。元件 B 與元件 C 臨界電壓皆約為 -3.5 V，兩者氧化層厚度相同，但元件 C 的二硫化鉬厚度約為 100 nm，遠大於元件 B 的 20 nm，理論上應展現較負臨界電壓，顯示氧化層的厚度為主要影響臨界電壓的因素。

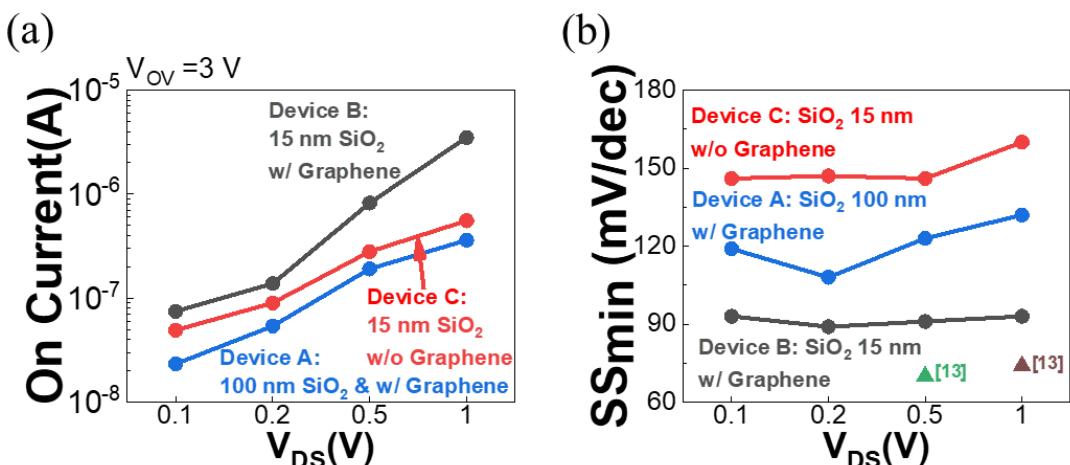

三個不同元件的次臨界擺幅最小值如圖 2.13(b)所示，縱軸為次臨界擺幅，橫

圖 2.13 (a)三種不同元件導通電流與(b)次臨界擺幅最小值。

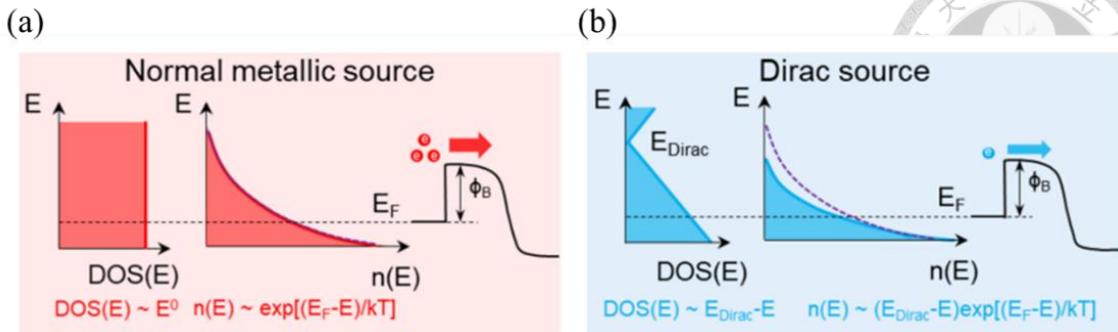

圖 2.14 利用(a)一般金屬或(b)狄拉克材料作為源極之狀態密度與波茲曼分布的載子數量示意圖 [54]。

軸為汲極電壓，首先比較元件 A 與元件 B(藍線與黑線)，兩個元件結構完全相同，僅氧化層厚度不同，由圖可以看出黑線在不同汲極電壓下，次臨界擺幅皆小於藍線，根據公式： $SS = \ln(10) \frac{kT}{q} \left(1 + \frac{C_D}{C_{ox}}\right)$ ，其中 k 為波茲曼常數，T 為溫度，q 為基本電荷帶電量， $C_D$  為空乏區電容， $C_{ox}$  為氧化層電容並可以寫成  $C_{ox} = \frac{\epsilon_{ox}}{t_{ox}}$ ， $\epsilon_{ox}$  為氧化層介電常數， $t_{ox}$  為氧化層厚度，因此在厚度變薄情況下， $C_{ox}$  值上升使得 SS 下降，對於較薄的氧化層，閘極對於通道有較好的控制。接著比較元件 B 與元件 C(黑線與紅線)，兩者差別為有無使用 Graphene 做為接觸金屬，使用 Graphene 最為接觸金屬有較低的 SS，其原因可能是 Graphene 為狄拉克(Dirac)材料[53]。電晶體中通道的載子通常是由金屬源極提供，狀態密度(Density of states)通常為一常數，源極的電子密度近似於波茲曼分布乘上狀態密度，其電子密度會在費米能階之上形成長的熱尾巴(Long thermal tail)，示意圖如圖 2.14(a)所示，限制了次臨界擺幅最小在  $(K_B T/q)(\ln 10)$ 。然而當金屬源是狄拉克材料時，狀態密度隨能量線性改變 ( $DOS(E) \sim E_{Dirac}-E$ )，減少電子密度在費米能階上的熱尾巴，示意圖如圖 2.14(b)所示，電子注入通道的分布更集中，以此達到較小的次臨界擺幅[54]。在文獻[47]中兩個二維材料電晶體元件 SS 低至 70 mV/dec(無使用 Gr 作為接觸， $MoS_2$  厚度約為 12 nm)與 74 mV/dec(使用 Gr 作為接觸， $MoS_2$  厚度約為 20 nm)，25 nm 二氧化矽作為閘極氧化層，有較好 SS 值可能原因為  $MoS_2$  厚度較薄，閘極控制通道能力較好。

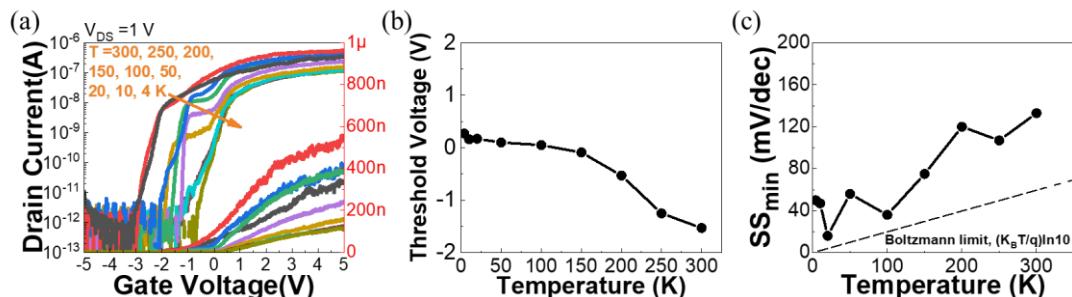

## 2.5 低溫量測

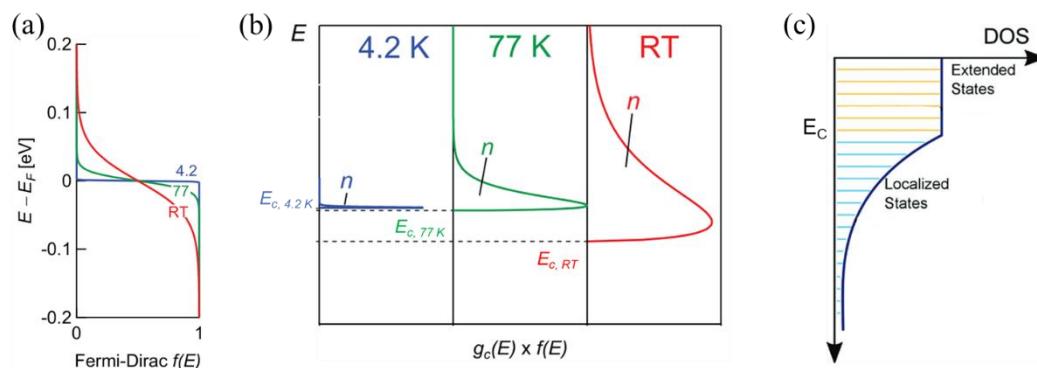

二硫化鉬電晶體變溫量測的  $I_D-V_G$  曲線如圖 2.15(a)所示，元件氧化層為 15 nm

二氧化矽，並無額外使用 Graphene 做為接觸金屬，溫度由 300 K 降至 4 K，由實驗結果看出，導通電流隨著溫度下降而下降，代表材料中的雜質(impurity)主導散射機制[55]，溫度較高時載子具有較高熱能，減弱雜質的影響，有較高的遷移率，與文獻[55][56]結果相符。電晶體臨界電壓對於溫度的關係如圖 2.15(b)所示，元件臨界電壓隨溫度下降而上升，與過去文獻結果相符，對於單層與多層二硫化鉬電晶體進行低溫量測[55]-[57]，皆有觀察到臨界電壓值隨溫度下降而上升，其原因為二硫化鉬載子濃度隨溫度下降而降低，在低溫時，若要達到臨界值，需要施加更大的電壓，使得導帶上電子數目與高溫時相同[56][57]。電子占據能階機率以費米-狄拉克(Fermi-Dirac)分布函數表示為  $F(E) = \frac{1}{1+exp[(E-E_F)/kT]}$ ，在不同溫度下的費米-狄拉克分布如圖 2.16(a)所示，隨著溫度下降，尤其是溫度低至 4 K 時，費米-狄拉克分布曲線越接近階梯函數，費米-狄拉克分布曲線乘以能量態密度得到載子濃度，在不同溫度下高於導帶的載子濃度示意圖如圖 2.16(b)所示，為了達到通道導通時相同數量的載子，需要更大電壓提高費米能階[58]，使更多載子到導帶，因此臨界電

圖 2.15 (a)二硫化鉬電晶體變溫量測之  $I_D-V_G$  曲線，(b)臨界電壓對於溫度關係圖與(c)次臨界擺幅對於溫度關係圖。

圖 2.16 (a)不同溫度下的費米-狄拉克分布[58]，(b)不同溫度下的載子密度[58]與(c)局域態示意圖[59]。

壓隨溫度下降而上升。次臨界擺幅最小值對於溫度的關係如圖 2.15(c)所示，次臨界擺幅最小值隨溫度下降而下降，次臨界擺幅定義為改變汲極電流一階次大小幅度所需閘極電壓[50]，次臨界擺幅公式： $SS = \frac{\partial V_G}{\partial [\log(I_D)]} = \frac{\partial V_G}{\partial \psi_s} \cdot \frac{\partial \psi_s}{\partial [\log(I_D)]} = \left(1 + \frac{C_D}{C_{ox}}\right) \cdot \frac{k_B T}{q} \ln(10)$ ， $\psi_s$ 為表面電位，可以將公式看成兩項相乘，第一項為閘極電壓對於表面電位控制能力，氧化層電容值越大，閘極控制通道能力越強，次臨界擺幅越小。第二項為表面電位改變汲極電流的幅度，若 $C_{ox}$ 遠大於 $C_D$ ，在室溫下次臨界擺幅最小值約為 60 mV/dec，根據公式次臨界擺幅值正比於溫度，隨著溫度降低，次臨界擺幅值越小，不同溫度下的費米-狄拉克分布如圖 2.16(a)所示，在室溫下形成長的熱帶尾(long thermal tail)，因熱激發的電子先進入導帶，使得電晶體通道慢慢打開，而在低溫下費米-狄拉克分布如階梯函數，絕大部分電子分布在費米能階之下，在導通時載子會集中注入通道，使得電晶體在一瞬間打開，有較好的次臨界擺幅最小值。在溫度小於 100 K 後，次臨界擺幅最小值沒有持續顯著地降低，可能是被缺陷所影響。若在半導體側存在缺陷，缺陷電容與空乏層電容為並聯模式，可以改寫次臨界擺幅公式： $SS = \ln(10) \frac{k_B T}{q} \left(1 + \frac{C_D + C_{it}}{C_{ox}}\right)$ [50]， $C_{it}$ 為缺陷電容，缺陷存在會惡化臨界值擺幅最小值，二硫化鉬電晶體中缺陷可能源自於二硫化鉬中的硫空缺(Sulfur vacancies)或是錯位缺陷(Antisite defects)[59]，這些缺陷在導帶邊緣以下，形成一個在導帶邊緣的局域態(Localized states)如圖 2.16(c)所示[59]，如同先前討論，高溫時，費米能階變化範圍離導帶較遠，此時能帶尾缺陷密度較低，較少缺陷被填入，不影響載子傳輸，次臨界擺幅主要由熱電壓決定，在低溫時，需要提高費米能階以導通電流，費米能階甚至需要高於導帶，此時有較大的缺陷密度並被填入，影響載子傳輸，為次臨界擺幅最小值在低溫時沒有持續下降的可能原因[47]。

## 2.6 結論

本章首先回顧了二硫化鉬電晶體的相關文獻，了解元件結構如何設計及其電性表現。再來，對於剝離的二硫化鉬碎片進行材料分析，由光致發光光譜結果看出能隙約為 1.82 eV，拉曼散射光譜結果看出晶格振動模式。接著，製作二硫化鉬電晶體，並介紹如何進行二維材料轉移，隨後進行電性量測，二硫化鉬直接與鉻/金接觸(無石墨烯連結)的元件，電流開關比約為  $10^5$ ，次臨界擺幅最小值約為 150

mV/dec；以石墨烯做為接觸金屬的元件，電流開關比可達  $10^6$ ，次臨界擺幅最小值約為 90 mV/dec，其原因可能與石墨烯為狄拉克(Dirac)材料有關。最後，對元件進行變溫量測，由實驗結果看出，臨界電壓隨著溫度降低而提高，由於費米-狄拉克分布在低溫時趨近一階梯函數，為了達到通道導通時相同數量的載子，需要更大電壓提高費米能階，使載子進入導帶。以及，臨界值擺幅(SS)整體趨勢隨溫度下降而下降，室溫時，費米-狄拉克分布有一熱帶尾，導通時使通道慢慢打開，而低溫時費米-狄拉克如階梯函數的分布，在導通時載子瞬間填入導帶，有較好的 SS，但低於 50 K 時，SS 不會下降並接近飽，可能與缺陷形成的局域態(Localized states)有關，惡化了臨界值擺幅。

## 第3章 二維鐵電場效電晶體

### 3.1 二維鐵電場效電晶體文獻回顧

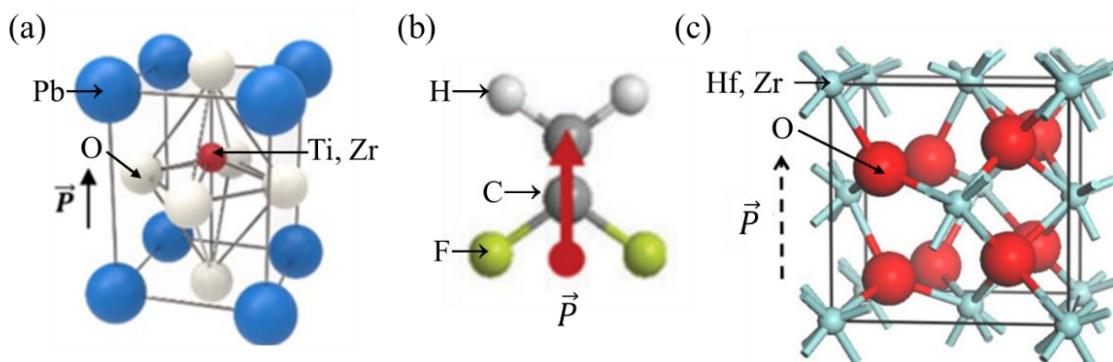

鐵電材料的極化現象源自於材料中的非中心對稱(Non-centrosymmetric)結構[27,60,61]，幾種常見的鐵電材料如 PZT(Lead Zirconate Titanate)、PVDF(Polyvinylidene difluoride)與 HZO(Hafnium zirconium oxide)皆是因為材料中有位移(Displaced)原子而產生極化現象。極化方向由原原子位移的位置決定，極化程度隨材料的特定相態或是外部條件有所不同[60]。PZT 的極化特性是因為 Zr 與 Ti 原子在鈣鈦礦結構有位移[60](圖 3.1(a))。PVDF 的極化特性是由於氫離子與氟離子具有電位差形成偶極(Dipole)，並在晶格結構中沿一個方向平行排列[61](圖 3.1(b))。HZO 的極化特性，在以  $\text{HfO}_2$  為基底的晶格受到 Zr 摻雜濃度、上與下電極所產生的應力影響，氧原子晶格的位移形成極化[27](圖 3.1(c))。這三個常見鐵電材料的參數如厚度範圍、沉積方式、矯頑電場(Coercive field)、極化強度(Polarization,  $2\text{Pr}$ )、介電常數、操作電壓與優缺點如表 3.1 所示。PZT 已是發展成熟的鐵電材料，具有高極化值、高介電常數和良好的工業應用性，缺點是材料厚度大、能隙較小、在高溫下不穩定以及鉛的環境毒性。PVDF 優點是易於合成、高彈性以及有良好的生物相容性，適合可穿戴設備與醫學應用，但是 PVDF 的熱穩定度差、厚度大並只有較小的極化值，作為記憶體元件時需要較大的操作電壓。以上原因限制了這兩種材料在現今技術發展的潛力，而 HZO 與半導體製程相容性以及並在較薄的材料厚度具有高極化值，成為鐵電材料發展的熱門選項，然而 HZO 的鐵電特性容易受到材料缺陷影響，是仍需解決的問題，接下來對於論文中使用的鐵電材料 HZO 做較詳細的說明。

圖 3.1 鐵電材料晶格結構示意圖：(a)PZT[60]，(b)PVDF[61]與(c)HZO[27]。

表 3.1 比較不同鐵電材料氧化層，包含 PZT、PVDF 與基於 HfO<sub>2</sub> 鐵電材料[60]。

|                                                 | Pb(ZrxTi <sub>1-x</sub> )O <sub>3</sub>                                                                                               | PVDF, P(VDF-TrFE)                                                                                                                   | HfO <sub>2</sub> -based ferroelectric                                                                           |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Layer Thickness (nm)                            | Insulator <sup>62,64</sup><br>10–340 <sup>149</sup><br>Solution process <sup>52–58</sup><br>(sol-gel process and wet chemical method) | Insulator <sup>40</sup><br>200~ <sup>69</sup><br>Solution process <sup>83–87</sup> (spray, inkjet printing, and roll to roll print) | Insulator <sup>41,127</sup><br>~10 <sup>149</sup><br>ALD <sup>29,41,127</sup>                                   |

| Coercive field $E_c$ (MV/cm)                    | 0.1 <sup>150</sup>                                                                                                                    | 0.5 <sup>150</sup>                                                                                                                  | 0.8–2 <sup>150</sup>                                                                                            |

| Polarization $2P_r$ ( $\mu$ C/cm <sup>2</sup> ) | 30–60 <sup>150</sup>                                                                                                                  | ~10 <sup>150</sup>                                                                                                                  | 30–60 <sup>150</sup>                                                                                            |

| Dielectric constant ( $\epsilon_F$ )            | ~200 <sup>149</sup>                                                                                                                   | ~12 <sup>153</sup>                                                                                                                  | ~30 <sup>149</sup>                                                                                              |

| Gate voltage range (V)                          | $\pm 20$ <sup>62</sup>                                                                                                                | $\pm 60$ <sup>62,69</sup>                                                                                                           | $\pm 3$ <sup>29,41,127</sup>                                                                                    |

| Advantage                                       | Easy synthesis <sup>52–58</sup> and high polarization <sup>154</sup>                                                                  | Easy synthesis <sup>83–87</sup> and flexibility <sup>87</sup>                                                                       | High industrial applicability, <sup>122</sup> high polarization, <sup>29</sup> and thin thickness <sup>29</sup> |

| Disadvantage                                    | Bulk scale layer, <sup>59–61</sup> environmental issues, <sup>48,50</sup> and low bandgap <sup>37,28,104–107</sup>                    | Thermal stability, <sup>62</sup> high power operation, <sup>52,69</sup> and low polarization <sup>150</sup>                         | High intrinsic defect <sup>46</sup>                                                                             |

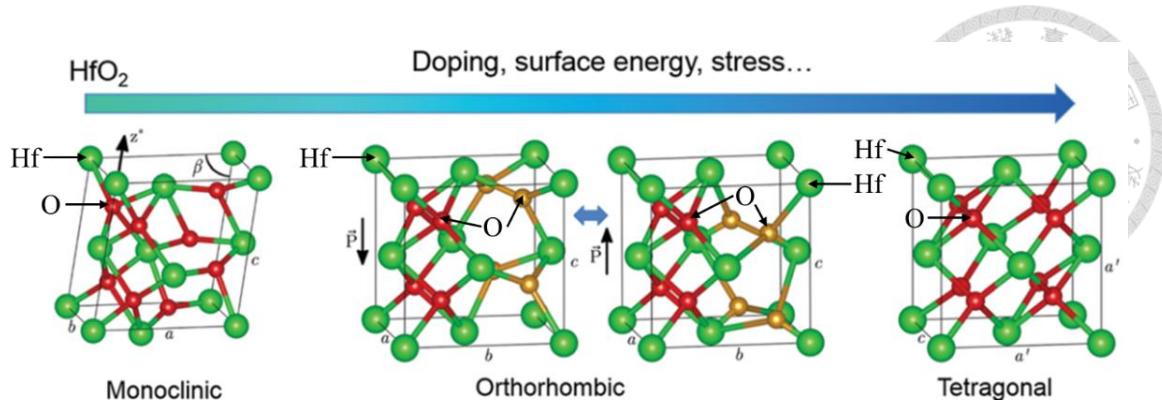

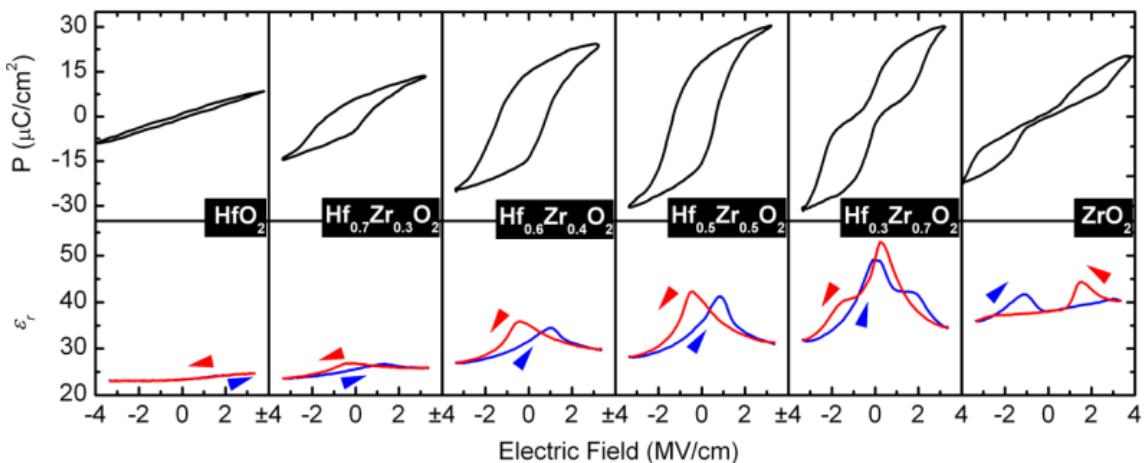

在 2011 年，透過摻雜 Si 的 HfO<sub>2</sub> 成為第一個螢石型(fluorite-type)氧化物被發現具有鐵電特性[27]，隨後，原子層沉積 HfO<sub>2</sub> 時摻雜其他材料如 Zr[62]、Y[63]與 Al[64]皆發現具有鐵電特性，而鐵電特性是源自於晶體中非中心對稱的正交晶相(Orthorhombic phase, o-phase)，在室溫下 HfO<sub>2</sub> 最穩定的晶相為單斜晶相(Monoclinic phase, m-phase)，在基於 HfO<sub>2</sub> 晶體摻雜其他原子並且退火(Annealing)，會形成正交晶相與四方晶相(Tetragonal phase, t-phase)，其晶相示意圖如圖 3.2 所示[65]，ALD 成長完的薄膜狀態為非晶態(Amorphous)，需要適當退火使薄膜結晶化(Crystallized)[66]。在 HfO<sub>2</sub> 中摻雜 Zr 為目前最被廣泛研究的鐵電薄膜，HfO<sub>2</sub> 與 ZrO<sub>2</sub> 都是二元氧化物，晶格結構相似，此外 Hf<sup>4+</sup> 與 Zr<sup>4+</sup> 的電子組態接近且半徑分別為 0.76 Å 和 0.78 Å，電負度也很接近，分別為 1.23 與 1.22，這些相似的特性使得 HfO<sub>2</sub> 與 ZrO<sub>2</sub> 可以形成穩定的連續固溶體，在不同比例下可混合形成單一晶體結構，而不分離為多個相[66]。Hf 與 Zr 做為二元氧化物可表示為 Hf<sub>x</sub>Zr<sub>1-x</sub>O<sub>2</sub>，不同比例下的 Hf 與 Zr 氧化物當作為金屬-絕緣層-金屬(MIM)結構中的介電層，其極化對應電場(P-E)的電性如圖 3.3 所示[67]，當 x=1 時晶體是 HfO<sub>2</sub>，晶格為 m-phase，表現順電性並沒有遲滯曲線。當 x=0.5 時代表 Hf 與 Zr 比例相同並表示為 Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>，以 HZO 簡稱，此時晶格為 o-phase 的特性最為顯著，展現出顯著的鐵電遲滯曲線，有最大的剩餘極化值。當 x=1 時晶體為 ZrO<sub>2</sub>，晶格為四方晶相，有兩個遲滯曲線展現反鐵電特性，不同的 Hf 與 Zr 比例會改變薄膜晶相，進而影響鐵電特性。

圖 3.2 在基於  $\text{HfO}_2$  薄膜中摻雜、改變表面位能與提供應力後，可能形成相變示意圖，包括單斜晶相(Monoclinic)、正交晶相(Orthorhombic)、四方晶相(Tetragonal)，圖中綠色圓圈代表 Hf 原子，紅色圓圈代表 O 原子，而金色圓圈標示為貢獻極化的 O 原子[65]。

圖 3.3 不同比例的  $\text{Hf}_x\text{Zr}_{1-x}\text{O}_2$  氧化層之金屬-氧化層-金屬結構電容極化-電場[67]。

在 HZO 鐵電相的形成過程如圖 3.4 所示[68]，對於垂直高度 9.2 nm 的 HZO 的 m-phase、t-phase 與 o-phase 三相轉變圖如圖 3.4(a)所示，縱軸為晶粒大小，橫軸為溫度，不同顏色的區域對應到不同相的熱力學穩定區，在綠色區域代表是 m-phase，括號文字代表第二穩定的相，如在溫度較高時，t-phase 是在 m-phase 中第二穩定的晶相，紅色虛線代表在 m-phase 中兩個第二穩定相的交界，在紅色區域代表的是 o-phase，藍色區域代表的是 t-phase。ALD 沉積完 HZO 薄膜的示意圖如圖 3.4(b)所示，此時 HZO 中大部分為無序的(amorphous)，紅色圈是半徑為 2 nm 的晶核(Crystalline nuclei)散布其中，對應的自由能圖如圖 3.4(c)所示，自由能最低的相為 o-phase。溫度升高後 HZO 薄膜的示意圖如圖 3.4(d)所示，此時晶粒開始生長，退火過程升溫時自由能圖如圖 3.4(e)所示，由於 t-phase 的熵在這三種相中相對較高[69]，隨著溫度升高，自由能會下降較多，因此 t-phase 變成自由能最低也是最穩定的相。退火達到最高溫時，在攝氏 600 度時維持大約一分鐘，薄膜中的晶粒的尺

寸變大如圖 3.4(f)所示，對應的自由能圖如圖 3.4(g)所示，因為晶界(grain boundary)面積與晶粒體積的比值下降，使得 m-phase 成為三相中自由能最低的相，但是從 t-phase 到 m-phase 的能量障礙太高，因此 t-phase 不會馬上轉移到 m-phase，除非將溫度提高且維持較久時間。降溫時 HZO 薄膜示意圖如圖 3.4(h)所示，大部分的晶粒轉變為 o-phase，對應的自由能圖如圖 3.4(i)所示，隨溫度下降 o-phase 再度變回自由能最低的相，t-phase 開始轉變到 o-phase，完成退火後薄膜示意圖如圖 3.4(j)所示，此時薄膜晶格中有最多的 o-phase，在自由能圖中是最穩定的相如圖 3.4(k)所示，上述說明了 HZO 薄膜經過退火後形成造成極化的晶相 o-phase。

圖 3.4 在不同退火階段垂直高度 9.2 nm  $\text{Hf}_{0.5}\text{Zr}_{0.5}\text{O}_2$  晶格與自由能變化示意圖，(a)三相圖，(b)沉積完薄膜示意圖與(c)三相自由能圖，(d)升溫時薄膜示意圖與(e)薄膜三相自由能圖，(f)達到最高溫時薄膜示意圖與(g)薄膜三相自由能圖，(h)降溫時薄膜示意圖與(i)薄膜三相自由能圖，(j)退火完薄膜示意圖與(k)薄膜三相自由能圖[68]。

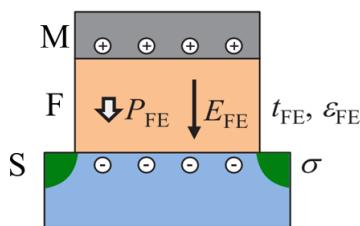

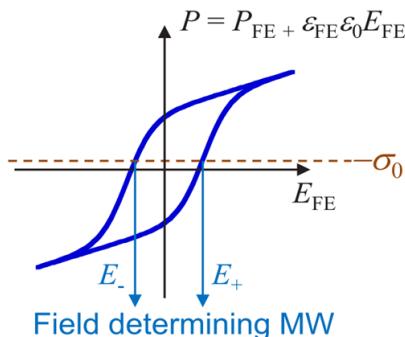

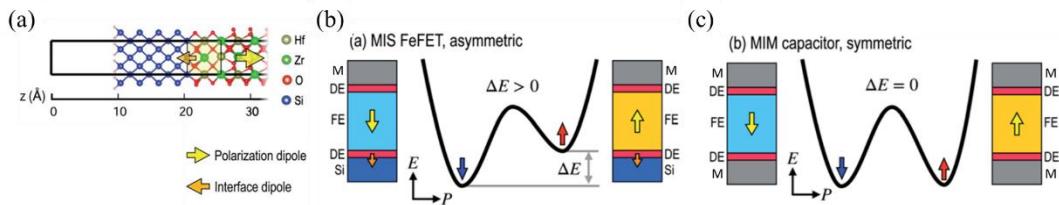

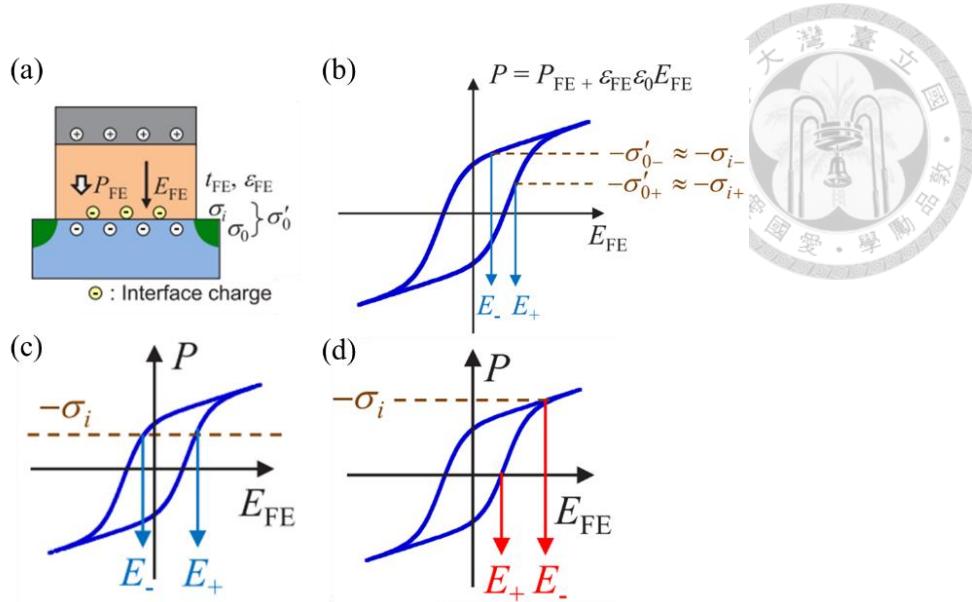

記憶體視窗(Memory window, MW)為衡量單一記憶體內，區分不同記憶狀態(Memory states)的能力，對於理想的金屬-鐵電-半導體(MFS)結構如圖 3.5(a)所示，鐵電場效電晶體的記憶體視窗可以寫成  $MW = V_{th,H} - V_{th,L}$ ， $V_{th,H}$  代表鐵電圖 3.5 電晶體由負往正掃較高的臨界電壓， $V_{th,L}$  代表鐵電電晶體由正往負回掃時有較低的臨界電壓(圖 3.5(b))，鐵電極化與半導體電荷密度關係如圖 3.5(c)所示[70]，從鐵電 P-E 曲線以圖形化方法判定臨界電壓下的操作電場，由  $P = -\sigma_0$  水平線交點決定， $\sigma_0$  為達到臨界電壓時半導體的電荷密度，負號來自於圖 3.5(a)中極化與電場方向向下， $E_+$  與  $E_-$  分別代表兩個臨界電壓分別對應的電場，將閘極上施加的電壓表示為 [70]：

$$MW = (E_+ t_{FE} + \Psi_S + \phi_{ms}) - (E_- t_{FE} + \Psi_S + \phi_{ms}),$$

$t_{FE}$  為鐵電層厚度， $E_+ t_{FE}$  代表氧化層的能量差， $\Psi_S$  為臨界電壓時半導體的表面電位， $\phi_{ms}$  為閘極金屬/半導體的功函數差，對於增強式(Enhancement mode)的傳統矽電晶體與耗盡式(Depletion mode)的二維材料電晶體接適用於此公式，電晶體來回掃時達到起始電壓的表面電位與金屬功函數差皆不變，因此記憶體視窗寫成  $MW = (E_+ - E_-)t_{FE}$ ，對於沒有缺陷的 MFS 結構，最大值  $MW \approx (E_{C+} - E_{C-})t_{FE}$ ，記憶體

(a) MFS structure FeFET

(b) I-V characteristics

(c) P-E characteristics

(d) MFIS structure FeFET

圖 3.5 (a)MFS 結構示意圖[70]，(b)FeFET  $I_D$ - $V_G$  曲線[71]，(c)圖解法判定臨界電壓下的操作電場，其中  $E_+$  與  $E_-$  分別代表兩個臨界電壓分別對應的電場， $\sigma_0$  為半導體在臨界電壓時的通道載子密度[70]，(d)MFIS 結構示意圖[70]。

視窗近似於  $2E_C t_{FE}$  等於  $2V_C$ 。有中間介電質(Interlayer dielectric)的結構如金屬-鐵電-介電質-半導體(MFIS)如圖 3.5(d)所示，相同地，記憶體視窗等於兩個臨界電壓差，層間介電質的跨壓可以寫成  $E_{IL} t_{IL} = -\sigma_0 t_{IL} / \varepsilon_{IL} \varepsilon_0$ ，記憶體視窗  $MW = (E_+ t_{FE} - \sigma_0 t_{IL} / \varepsilon_{IL} \varepsilon_0 + \Psi_S + \phi_{ms}) - (E_- t_{FE} - \sigma_0 t_{IL} / \varepsilon_{IL} \varepsilon_0 + \Psi_S + \phi_{ms}) = (E_+ - E_-) t_{FE}$ ，也適用於此記憶體視窗公式[70]。

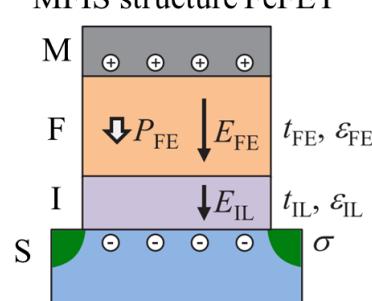

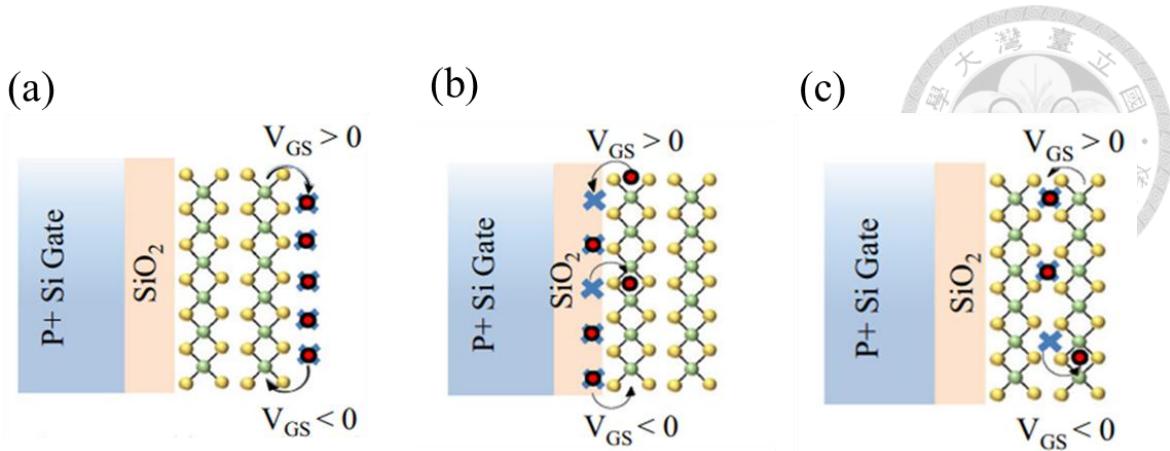

HZO 鐵電場效電晶體，因為與 CMOS 製程相容、可以快速讀寫與低功耗的潛力而受到關注，這些歸因於可以電場驅動 HZO 的鐵電性。然而基於矽通道的鐵電場效電晶體面臨幾項挑戰，包括：(1)因為超薄矽通道的低載子遷移率，導致存取速度緩慢，(2)因鐵電 HZO 絝緣層與矽通道間的低介電常數介面引起電荷捕捉的問題，使得可靠度下降，(3)在低介電常數介面的電壓限制了鐵電場效電晶體在低電壓操作的能力。為了解決矽作為通道材料所面臨的限制，有研究開始使用二硫化鉬作為通道材料，理論上，在數奈米厚度下仍具備高載子遷移率，此外，由於二硫化鉬表面並無懸浮鍵(Dangling bond)，有望實現較好的絕緣層/半導體介面[72]。對於二維材料作為通道的鐵電場效電晶體工作原理與一般鐵電場效電晶體相同[60]，背閘極

圖 3.6 (a)背閘極鐵電場效電晶體元件示意圖，(b)背閘極鐵電場效電晶體極化向上(朝向通道)示意圖與(c)背閘極鐵電場效電晶體極化向下示意圖[60]。

圖 3.7 閘極/鐵電氧化層/二硫化鉬能帶圖(a)鐵電極化方向朝向通道(低阻態)[73]，(b)鐵電極化方向朝向閘極(高阻態)[73]與(c) $I_D$ - $V_G$ 逆時針遲滯曲線示意圖[32]。

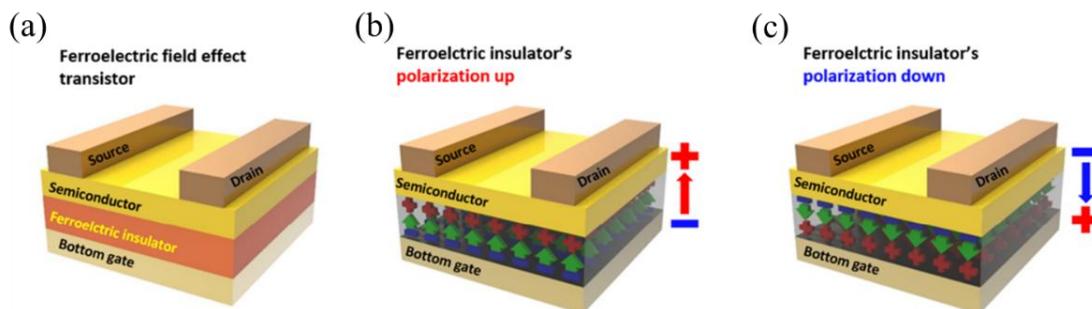

鐵電場效電晶體結構示意圖如圖 3.6(a)所示，與常見的電晶體結構上下顛倒，閘極在底部。對於電晶體施加足夠大的閘極偏壓，使鐵電層極化方向朝向通道(圖 3.6(b))，而對於電晶體施加足夠負的閘極偏壓，使鐵電極化方向朝向閘極(圖 3.6(c))。電晶體由負的電壓掃描至正電壓，能帶圖示意圖如圖 3.7(a)所示[73]，極化方向指向閘極，氧化層半導體側有相對多的負電荷，排斥半導體通道電子，因此要達到臨界電壓需要增加閘極偏壓，從正電壓回掃到負電壓時，能帶圖示意圖如圖 3.7(b)所示[73]，極化方向指向通道，氧化層半導體側有相對多的正電荷，吸引半導體通道電子，因此要達到回掃的臨界電壓需要加更負的閘極偏壓，從負電壓掃描至正電壓形成  $I_D-V_G$  逆時針遲滯曲線(圖 3.7(c))。

Zhang 等人製作以二硫化鉬作為通道的鐵電場效電晶體[74]，並以 HZO 作為鐵電絕緣層，其元件結構如圖 3.8(a)所示，使用高摻雜矽基板作為閘極，以原子層沉積厚度為 6 nm 的 HZO，並在上方額外成長厚度為 2 nm 的  $\text{Al}_2\text{O}_3$ ，隨後在氮氣環境下進行快速熱退火(Rapid thermal annealing)，源極/汲極使用鈦/金。其  $I_D-V_G$  量測結果如圖 3.8(b)所示，閘極電壓掃描範圍為-6.5~6.5 V 並回掃，記憶體視窗(Memory window)達到 4 V，並且電流開關比達到大約  $10^7$ 。

Wang 等人也製作以  $\text{MoS}_2$  作為通道的二維鐵電場效電晶體[75]，其元件結構由上到下為金屬-鐵電-金屬-介電層-半導體(MFMIS)(圖 3.9(a))，並且大部分由凡德瓦單晶材料構成，在半導體  $\text{MoS}_2$  上堆疊 h-BN 作為閘極介電層，後續堆疊石墨烯

圖 3.8 二硫化鉬鐵電場效電晶體(a)元件示意圖與(b)其  $I_D-V_G$  圖[74]。

圖 3.9 金屬-鐵電-金屬-介電層-半導體(MFMIS)結構堆疊之二硫化鉬鐵電場效電晶體(a)元件示意圖與(b)其  $I_d$ - $V_g$  圖[75]。

作為中間金屬，並以  $\text{CuInP}_2\text{S}_6$  (CIPS) 作為鐵電層，CIPS 是一種二維鐵電材料，由於分子中 Cu 與 In 形成位移(displacement)造成自發性極化[76]，這些凡德瓦材料優點為易於使用乾式轉移互相堆疊且沒有懸浮鍵，此外，在閘極堆疊中引入雙極性(bipolar)石墨烯，使 CIPS 鐵電極化得以補償(compensation)，有助於消除去極化場(depolarization field)，最後沉積 Cr/Au 金屬作為閘極與源極/汲極，完成製程。其元件  $I_d$ - $V_g$  電性量測結果如圖 3.9(b)所示，閘極電壓掃描範圍為-4~4 V 並回掃，記憶體視窗超過 3.7 V，電流開關比高於  $10^7$ 。

現今發展的二維鐵電場效電晶體基準(Benchmark)如圖 3.10 所示，縱軸是

圖 3.10 比較不同鐵電電晶體(方形框)與鐵電半導體電晶體(圓形框)[77]。

電晶體電流開關比，橫軸是記憶體視窗，圖中方形框代表鐵電電晶體使用鐵電氧化層如 HZO、PVDF、PZT 與 AlScN 等，並使用一般半導體二維材料如 MoS<sub>2</sub>、MoSe<sub>2</sub> 或是傳統半導體材料矽作為通道，而圓形框代表使用具有鐵電特性的二維半導體材料如  $\beta$ -InSe 與  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> 做為電晶體通道，由圖中最右上角可以看出使用鐵電二維材料 In<sub>2</sub>Se<sub>3</sub> 做為電晶體，有較好的記憶體視窗，並保有良好電流開關比，此外，對於傳統鐵電氧化層上使用二維半導體材料做為通道，與傳統通道 Si 相比，有機會達到較高的電流開關比，同時保有可比擬的記憶體視窗大小，本篇論文後續將第二章已成功製作的 MoS<sub>2</sub> 電晶體，把氧化層換為鐵電材料 HZO，製作二維材料鐵電電晶體。

### 3.2 元件製程流程

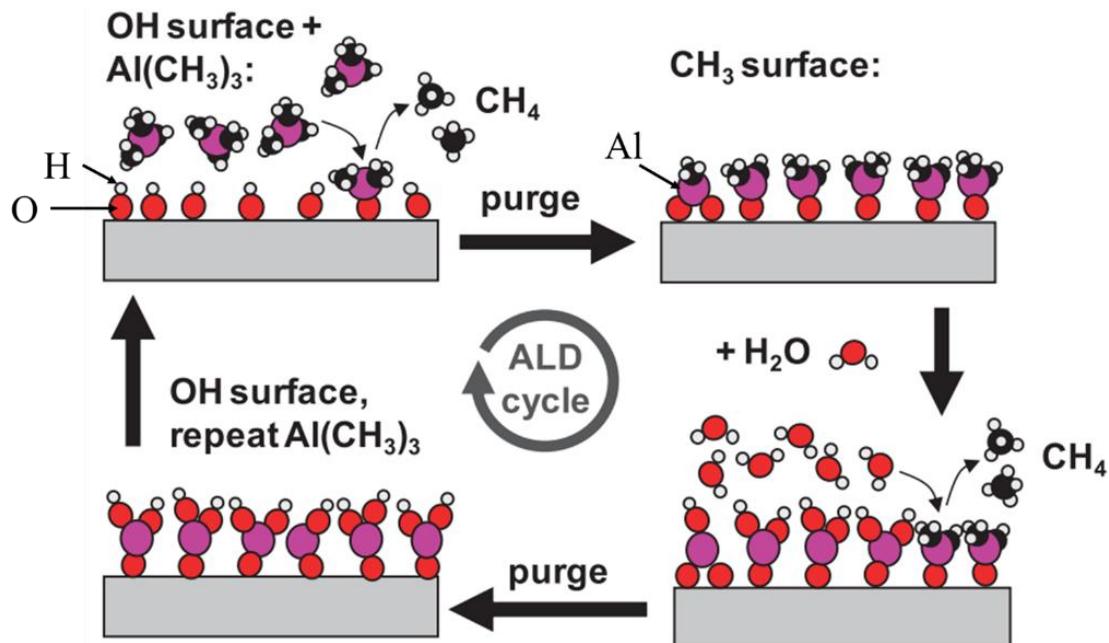

二維材料鐵電場效鐵晶體的製程流程示意圖如圖 3.11 所示，大部分製程流程與本文 2.3 節製作二硫化鉑電晶體相同，元件氧化層換成鐵電材料 HZO，此外，額外堆疊 Al<sub>2</sub>O<sub>3</sub> 以改善閘極漏電流[78]。本論文探討四種氧化層堆疊順序不同的鐵電電晶體，分別為 HZO(圖 3.11(a))、HZO/Al<sub>2</sub>O<sub>3</sub>(圖 3.11(b))、Al<sub>2</sub>O<sub>3</sub>/HZO/Al<sub>2</sub>O<sub>3</sub>(圖 3.11(c))以及 Al<sub>2</sub>O<sub>3</sub>/HZO(圖 3.11(d))。其製程步驟說明如下，(i)選用高摻雜磷的矽基板作為元件閘極，並在上方用原子層沉積法(ALD)成長 Al<sub>2</sub>O<sub>3</sub> 與 HZO，ALD 在溫度 250 °C 下進行，成長 Al<sub>2</sub>O<sub>3</sub> 所使用的前驅物為 H<sub>2</sub>O 與三甲基鋁(Trimethylaluminium, TMA)，ALD 循環示意圖如圖 3.12 所示[79]，使用順序為先通入 H<sub>2</sub>O 後再通入 TMA，鍍率約為 1 Å/cycle，依照目標厚度循環操作，舉例來說，1 nm 的 Al<sub>2</sub>O<sub>3</sub> 大約需要 10 個 cycle。成長 HZO 所使用前驅物為 H<sub>2</sub>O、四乙基甲基胺基鉻(Tetrakis(ethylmethylamino)hafnium, TEMAH)與四乙基甲基胺基鋯(Tetrakis(ethylmethylamino)zirconium, TEMAZ)，先通入 H<sub>2</sub>O 後再通入 TEMAH，再來，通入 H<sub>2</sub>O 後再通入 TEMAZ，形成 HfO<sub>2</sub> 與 ZrO<sub>2</sub> 交互堆疊，鍍率皆為 1 Å/cycle，也依照目標厚度按氣體順序循環操作。沉積完後在溫度攝氏 600 度與氮氣環境進行快速熱退火 30 秒，以形成 HZO 鐵電相。有部分元件在矽基板上，先用物理氣相沉積(PVD)成長 30 nm 氮化鈦，再進行原子層沉積與退火。(ii)鍍上元件背部金屬厚度 20/200 nm 鎔/金，作為閘極接觸金屬，(iii)在元件正面曝露出內部連線圖形後顯影，接著鍍上厚度 10/30 nm 鎔/金，再次曝露出大塊圖形以利於下針後顯影，接

著鍍上厚度 20/150 nm 鉻/金，(iv)在手套箱內的轉移系統進行，在源極/汲極貼上二硫化鉬完成電晶體。

圖 3.11 二維材料鐵電場效電晶體包含四種不同氧化層堆疊製程流程示意圖(a)氧化層為 HZO , (b) 氧化層為 HZO/Al<sub>2</sub>O<sub>3</sub> , (c) 氧化層為 Al<sub>2</sub>O<sub>3</sub>/HZO/Al<sub>2</sub>O<sub>3</sub> 與(d)氧化層為 Al<sub>2</sub>O<sub>3</sub>/HZO 。

圖 3.12 ALD 循環示意圖(以 Al<sub>2</sub>O<sub>3</sub> 為例)[79] 。

### 3.3 元件電性量測

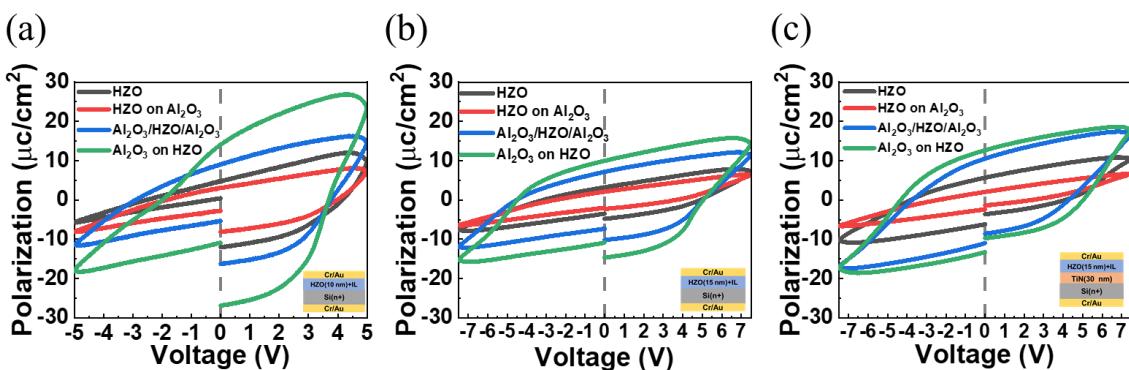

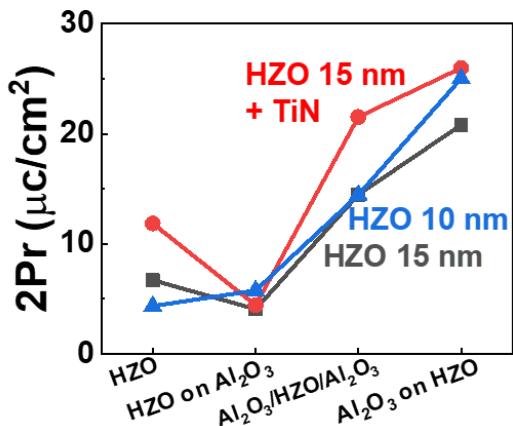

在製程流程進行至步驟(iii)完成後，元件結構由上到下為金屬-鐵電氧化層-高摻雜磷矽基板(MFS)的電容結構(圖 3.11)，可以進行極化值對於電壓(P-V)的量測，也可以測試電容是否有漏電。使用 Radiant Precision Premier II(鐵電材料測試儀)進行極化強度的測量，極化值公式  $P = \frac{Q}{Area} = \frac{CV}{Area}$ ，極化表示單位面積的電荷量，常用單位為  $\mu\text{C}/\text{cm}^2$ 。剩餘極化強度為衡量鐵電特性的參數，描述材料在外加電場移除之後，保留的極化值大小，常見的鐵電 P-V 關係圖為一遲滯曲線，當沒有電壓時( $V=0$ )，遲滯曲線在 y 軸(極化)上兩點的截距即為剩餘極化值，對於上電極與下電極對稱的電容，在沒有漏電情況下，正掃與回掃時的剩餘極化值相同，剩餘極化強度有時稱以  $2Pr$ ，而非對稱結構電容剩餘極化強度也可以  $2Pr$  表示，此時  $2Pr = Pr^+ - Pr^-$ 。四個不同氧化層堆疊的 MFS 結構電容的 P-V 量測結果如圖 3.13(a)所示，縱軸為極化強度，橫軸為施加的電壓，其中 HZO 的厚度皆為 10 nm，而單層  $\text{Al}_2\text{O}_3$  的厚度皆為 1 nm。在電壓範圍在-5 V 至 5 V 下量測極化值，灰黑線代表的元件是氧化層只有 HZO，在電壓為 0 時對應的剩餘極化值約為  $4.3 \mu\text{C}/\text{cm}^2$ ，紅線代表的元件是氧化層為 HZO 堆疊在  $\text{Al}_2\text{O}_3$  之上，剩餘極化值約為  $5.7 \mu\text{C}/\text{cm}^2$ ，藍色線代表的是氧化層為  $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$  堆疊，剩餘極化值約為  $14.5 \mu\text{C}/\text{cm}^2$ ，綠色線代表的是氧化層為  $\text{Al}_2\text{O}_3$  堆疊在 HZO 之上，剩餘極化值約為  $25.0 \mu\text{C}/\text{cm}^2$ 。不同氧化層的剩餘極化強度大小依序為  $\text{Al}_2\text{O}_3/\text{HZO}$ 、 $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$ 、 $\text{HZO}/\text{Al}_2\text{O}_3$  與 HZO。由實驗結果發現，在 HZO 上有覆蓋  $\text{Al}_2\text{O}_3$  的氧化層( $\text{Al}_2\text{O}_3/\text{HZO}$  與  $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$ )展現較大的剩餘極化值，而沒有  $\text{Al}_2\text{O}_3$  堆疊在 HZO 上方的元件

圖 3.13 金屬-鐵電層(+介面層)-矽(MF(+I)S)結構電容極化-電壓(P-V)量測結果，右下插圖為元件示意圖(a)HZO 厚度 10 nm·(b)HZO 厚度 15 nm 與(c)HZO 厚度 15 nm 並有額外一層 TiN 形成 MF(+I)M 結構。

(HZO/Al<sub>2</sub>O<sub>3</sub> 與 HZO)展現較小的剩餘極化值。

其可能原因為進行快速熱退火時，HZO 上需要有覆蓋層(Capping layer)以形成鐵電相，在製作金屬-鐵電層-金屬(MFM)結構電容時，頂部電極的存在，在退火時因上方電極熱膨脹係數較與 HZO 小，對 HZO 產生平面內拉伸應力，限制體積較大的單斜晶相(m-phase)成長[69][80]，使得亞穩態鐵電正交晶相(o-phase)含量增加，因此有較高的剩餘極化值，這種現象稱為覆蓋效應(Capping effect)或限制效應(Confinement Effect)[80](圖 3.14)，舉例來說，HZO 热膨胀係數為  $10.0 \times 10^{-6}/^{\circ}\text{C}$ [69]，CMOS 製程中常見的金屬 TiN 热膨胀係數約為  $9.1 \times 10^{-6}/^{\circ}\text{C}$ [81]，而對於退火時上方沒有覆蓋層提供應力的 HZO 僅有較小極化。在實驗中後續要製作成電晶體，鐵電層會與半導體通道直接接觸，若前面先使用金屬覆蓋層退火，後續則需移除該金屬覆蓋層，增加製程的複雜性與成本，也會影響到 HZO 薄膜的品質，有研究相同使用 Al<sub>2</sub>O<sub>3</sub> 薄膜作為覆蓋層[82]，以獲得 HZO 的鐵電特性，Al<sub>2</sub>O<sub>3</sub> 的熱膨脹係數為  $8.6 \times 10^{-6}/^{\circ}\text{C}$ [83]與 TiN 相近，能對下層的 HZO 薄膜在退火過程施加應力，形成鐵電正交晶，相較於金屬 TiN，對 HZO 電晶體提供較簡化的製程。Al<sub>2</sub>O<sub>3</sub>/HZO 與 Al<sub>2</sub>O<sub>3</sub>/HZO/Al<sub>2</sub>O<sub>3</sub> 兩種氧化層堆疊相比，上方皆有 Al<sub>2</sub>O<sub>3</sub> 做為覆蓋層，Al<sub>2</sub>O<sub>3</sub>/HZO/Al<sub>2</sub>O<sub>3</sub> 剩餘極化值較小原因可能為有兩層 Al<sub>2</sub>O<sub>3</sub>，較小的跨壓降於鐵電層 HZO，極化翻轉程度較小。

圖 3.14 鐵電 HZO 電容覆蓋效應(Capping effect)示意圖[80]。

HZO 的厚度為 15 nm，四種不同氧化層堆疊的 MFS 結構電容的 P-V 量測結果如圖 3.13(b)所示， $\text{Al}_2\text{O}_3$  的厚度為 1 nm，這裡施加的量測電壓為範圍在 -7.5 V 至 7.5 V，可使 HZO 厚度 15 nm 與厚度 10 nm 的電場相同，並在其他不同堆疊的電場較相近，以利後續比較。灰黑色線代表的是元件氧化層堆疊只有 HZO，剩餘極化值約為  $6.7 \mu\text{C}/\text{cm}^2$ ，紅線代表的元件是氧化層為 HZO 堆疊在  $\text{Al}_2\text{O}_3$  之上，剩餘極化值約為  $4.0 \mu\text{C}/\text{cm}^2$ ，藍色線代表的是氧化層為  $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$  堆疊，剩餘極化值約為  $14.5 \mu\text{C}/\text{cm}^2$ ，綠色線代表的是氧化層為  $\text{Al}_2\text{O}_3$  堆疊在 HZO 之上，剩餘極化值約為  $20.8 \mu\text{C}/\text{cm}^2$ ，由實驗結果看出，HZO 上方有覆蓋層  $\text{Al}_2\text{O}_3$  進行快速熱退火，有較好的剩餘極化值，對於厚度 10 nm 與 15 nm 的 HZO，退火時在 HZO 上方有覆蓋層皆有較好的鐵電特性。HZO 的厚度為 15 nm，先在矽基板成長 TiN，後續成長氧化層，四種不同氧化層堆疊的 MFS 結構電容的 P-V 量測結果如圖 3.13(c)所示，在施加電壓為 -7.5 V~7.5 V 下量測極化值，灰黑色線代表的是元件氧化層堆疊只有 HZO，剩餘極化值約為  $11.8 \mu\text{C}/\text{cm}^2$ ，紅線代表的元件是氧化層為 HZO 堆疊在氧化鋁之上，剩餘極化值約為  $4.4 \mu\text{C}/\text{cm}^2$ ，藍色線代表的是氧化層為氧化鋁/HZO/氧化鋁堆疊，剩餘極化值約為  $21.5 \mu\text{C}/\text{cm}^2$ ，綠色線代表的是氧化層為氧化鋁堆疊在 HZO 之上，剩餘極化值約為  $25.9 \mu\text{C}/\text{cm}^2$ 。

比較不同厚度 HZO 與是否有額外成長 TiN 的三組元件剩餘極化值如圖 3.15 所示，縱軸是剩餘極化強度，橫軸是四種不同堆疊結構，藍線代表的是 HZO 厚度 10 nm，灰黑線代表的是 HZO 厚度 15 nm，紅線代表的是 HZO 厚度 15 nm 並在氧化層底部有 TiN。比較藍線與灰黑線，10 nm 與 15 nm 厚度的 HZO，在相近的電場之下，在 4 種不同氧化層堆疊，剩餘極化值沒有太顯著的差異。接著，比較灰黑線與紅線，矽作為底部電極的量測結果與 TiN 作為底部電極是可比擬的，在氧化層下面多了一層 TiN，於 HZO、 $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$  與  $\text{Al}_2\text{O}_3/\text{HZO}$  這三種氧化層堆疊，提升剩餘極化值，可能原因為氧化層/金屬的表面較氧化層/矽的表面較好[84]，在矽與 HZO 介面會形成介面偶極(Interface dipole)，這是由於在介面矽原子的鍵結由共價鍵轉變為半離子鍵，舉例來說，矽從原本 +4 價改變至 +2 價，因此在矽與 HZO 表面產生一偶極，在 HZO 與矽之間存在一層氧化層，還是有介面偶極存在於氧化層/矽的表面，偶極方向由氧化層指向矽(圖 3.16(a))，橘色箭頭代表的是介面偶極方向，黃色箭頭代表的是鐵電層極化方向，對於 MIS 結構施加不同電場翻轉鐵電

圖 3.15 比較不同電容的剩餘極化值。

圖 3.16 (a)矽與氧化層間界面偶極示意圖，(b)對於 MIS 結構翻轉不同極化方向能量示意圖與(c)對於 MIM 結構翻轉不同極化方向能量示意圖[84]。

極化示意圖如圖 3.16(b)所示，因為多了氧化層/矽之間的界面偶極，對於改變兩個極化方向有不同的能量，進而影響到極化值改變的狀況，而對於 MIM 結構施加不同電場翻轉鐵電極化的示意圖如圖 3.16(c)所示，對於 MIM 結構沒有多餘的氧化層/矽界面產生偶極，對於兩個鐵電層翻轉極化的能量是對稱的。

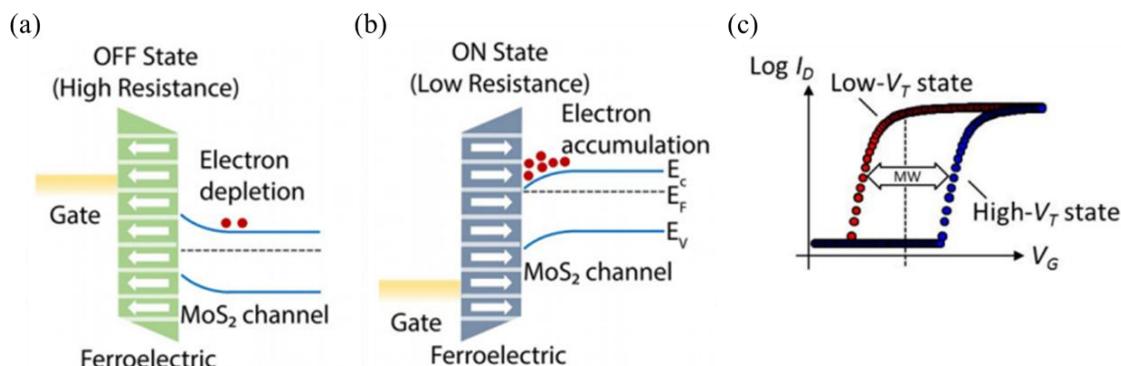

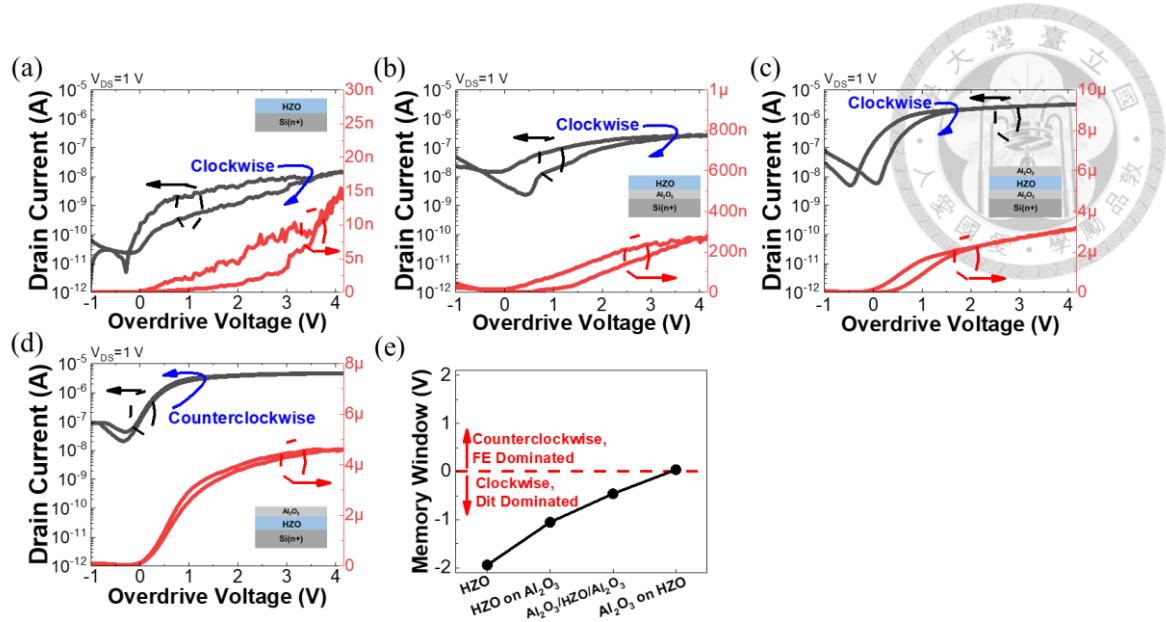

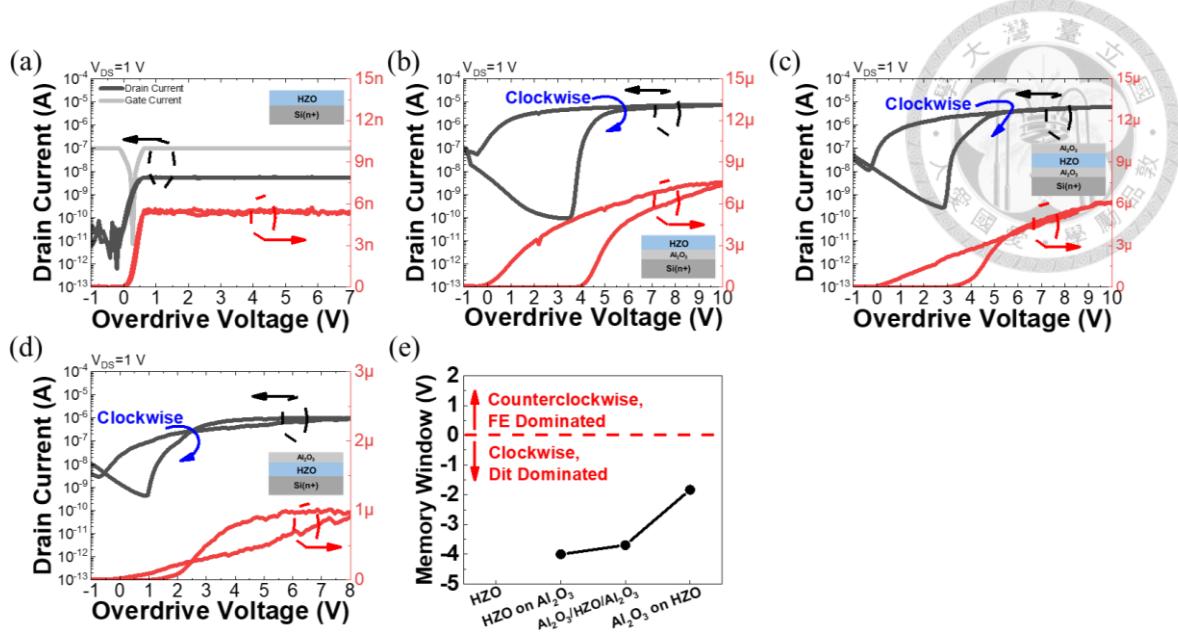

量測完電容之後，在元件的源極與汲極之間貼上二硫化鉬薄膜，完成電晶體製程，在閘極電壓範圍-5~5 V 下量測電晶體的  $I_D-V_{ov}$  曲線，HZO 厚度 10 nm 元件之  $I_D-V_{ov}$  量測結果如圖 3.17(a)-(d)所示，橫軸為過驅電壓(Overdrive voltage)，代表閘極電壓減掉臨界電壓，縱軸為汲極電流，左邊黑色刻度為對數，右邊紅色刻度為線性，鐵電電晶體記憶體視窗定義為  $MW = V_{th,H} - V_{th,L}$  也等於臨界電壓正掃減掉回掃，圖中藍色箭頭表示  $V_{th}$  正掃(閘極電壓由負往正)與回掃(閘極電壓由正往負)的方向，順時針代表是負的記憶體視窗，而逆時針代表正的記憶體視窗。電晶體氧化層只有 HZO 的元件之  $I_D-V_{ov}$  曲線如圖 3.17(a)所示，表現出順時針的遲滯曲線，記憶體視窗約為-1.94 V，電晶體氧化層為 HZO 對疊在  $\text{Al}_2\text{O}_3$  上之  $I_D-V_{ov}$  曲線如圖 3.17(b)所示，表現出順時針的遲滯曲線，記憶體視窗約為-1.05 V，電晶體氧化層為  $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$  堆疊之  $I_D-V_{ov}$  曲線如圖 3.17(c)所示，表現出順時針的遲滯曲線，

圖 3.17 HZO 厚度 10 nm 不同氧化層堆疊之鐵電電晶體  $I_D-V_{OV}$  曲線與總結，圖中插圖為氧化層堆疊示意圖(a)HZO，(b)HZO/ $\text{Al}_2\text{O}_3$ ，(c) $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$ ，(d) $\text{Al}_2\text{O}_3/\text{HZO}$ 。(e)記憶體視窗對應不同氧化層堆疊。

記憶體視窗約為 -0.46 V，電晶體氧化層為  $\text{Al}_2\text{O}_3$  堆疊在 HZO 上之  $I_D-V_{OV}$  曲線如圖 3.17(d)所示，表現出逆時針的遲滯曲線，記憶體視窗約為 0.04 V，記憶體視窗大小對應不同氧化層堆疊關係如圖 3.17(e)所示，大部分元件作為鐵電電晶體展現負的記憶體視窗，僅有  $\text{Al}_2\text{O}_3/\text{HZO}$  氧化層堆疊展現正的記憶體視窗。出現負的記憶體視窗可能原因為氧化層與半導體間存在界面缺陷，缺陷捕捉電荷(Charge trapping)造成正掃與回掃的介面電荷不同使得臨界電壓偏移[70]。考慮半導體與氧化層間有多餘的介面電荷(Interface charges) $\sigma_i$ 的 MFS 結構如圖 3.18(a)所示，多餘的介面電荷不會貢獻導通電流，用圖解方法判定臨界電壓下的操作電場，鐵電 P-V 遲滯曲線與多餘電荷 $\sigma_i$ 示意圖如圖 3.18(b)所示， $\sigma_{i+}$ 與 $\sigma_{i-}$ 分別代表正掃與回掃存在的介面多餘電荷，根據高斯定律 $P_{FE} + \varepsilon_{FE}\varepsilon_0 E_{FE} = -\sigma'_0$ ， $\varepsilon_{FE}$ 代表材料的介電常數， $\varepsilon_0$ 為真空介電常數，半導體側的電荷密度以 $-\sigma'_0$ 表示，等於半導體達到臨界電壓的電荷密度加多餘電荷 $\sigma'_0 = \sigma_0 + \sigma_i$ ， $\sigma_0$ 為達到臨界電壓時半導體的電荷密度，鐵電材料的極化約在  $1\sim100 \mu\text{C}/\text{cm}^2$ ，對於臨界值時的半導體表面電荷密度約為  $10^{-5}\sim10^{-2} \mu\text{C}/\text{cm}^2 (10^8\sim10^5 / \text{cm}^2)$ [70]，為了簡化計算，將半導體電荷密度近似於 0，因此公式右側可以只考慮多餘電荷 $P_{FE} + \varepsilon_{FE}\varepsilon_0 E_{FE} \approx -\sigma_i$ ，正掃時，遲滯曲線與半導體側的電荷密度 $\sigma_{i+}$ 交點對應的電場為 $E_+$ ，回掃時，遲滯曲線與半導體側的電荷密度 $\sigma_{i-}$ 交點對應的電場為 $E_-$ ，記憶體視窗  $MW = \Delta V_{th} = (E_+ - E_-)t_{FE}$ ，半導體側存在多餘

圖 3.18 (a)MFS 結構中存在介面電荷示意圖，(b)圖解法判定有介面電荷情況下於臨界電壓的操作電場，(c)有固定介面電荷情況下於臨界電壓的操作電場，(d)有非對稱介面電荷情況下於臨界電壓的操作電場[70]。

電荷會影響記憶體視窗大小。考慮半導體與氧化層間有多餘的介面電荷是一定值，不隨閘極電壓改變，鐵電 P-V 遲滯曲線與固定介面電荷  $\sigma_i$  示意圖如圖 3.18(c)所示，記憶體視窗  $MW = (E_+ - E_-)t_{FE}$  是正的，但是小於最大值  $2E_C t_{FE}$ 。接著考慮電晶體正掃與回掃被缺陷捕獲數量不同的不對稱行為，鐵電 P-V 遲滯曲線與較多的回掃介面電荷  $\sigma_i$  示意圖如圖 3.18(d)所示，為了方便討論，這裡將正掃時的介面電荷令為 0，回掃時有較多的介面電荷  $\sigma_i$ ，使得  $E_-$  較  $E_+$  正，在這種情況下，記憶體視窗  $MW = (E_+ - E_-)t_{FE} = V_+ - V_-$  變成負的，介面陷阱捕捉電子較嚴重時，舉例來說，在回掃時來不及釋放出缺陷的電荷密度數量大於  $P_r$ ，如圖 3.18(d)所示，對應到電晶體  $I_D-V_{OV}$  順時針遲滯現象，在相同電荷密度  $\sigma_{i-}$  下考慮一較大遲滯的 PV 曲線，即有較大的剩餘極化， $\sigma_{i-}$  與曲線的交點  $E_-$  會向左偏移，得到相對較正的記憶體視窗，實驗結果中氧化層堆疊  $\text{Al}_2\text{O}_3/\text{HZO}$  有較大的剩餘極化值，對應到電晶體有較正的鐵電記憶體視窗。

對於二硫化鉬作為通道的場效電晶體，有許多研究說明其電晶體  $I_D-V_G$  來回掃有順時針遲滯，或是稱為正的遲滯，形成順時針遲滯可能的原因包含量測環境中的水氣與氧氣(如圖 3.19(a))，存在於氧化層內並靠近半導體通道端的缺陷與位於氧化層/半導體界面的缺陷(如圖 3.19(b))，以及半導體通道本身存在的缺陷(如圖 3.19 (c))[85]。首先考慮量測環境的問題，對於二硫化鉬電晶體施加較大的閘極電

圖 3.19 缺陷存在於矽-氧化層-二硫化鉬示意圖(a)水氧被吸附在二硫化鉬表面，(b)於氧化層靠近半導體側與氧化層，(c)二硫化鉬本質缺陷[85]。

壓時，水和氧氣的分子會被吸引至二硫化鉬表面，並且從二硫化鉬中捕獲電子，在回掃時排開通道電子，導致從回掃時有較高的臨界電壓，施加較負的閘極電壓時則會將被捕獲的電子釋放，有較負的臨界電壓，導致順時針的遲滯。考慮缺陷存在於氧化層靠近半導體側與半導體/氧化層介面，如基於  $\text{HfO}_2$  材料的氧化層具有本質缺陷[86]，或是半導體通道內的本質缺陷，如硫空缺(Sulfur vacancies)[87]皆會造成遲滯，遲滯起因於這些陷阱捕捉與釋放電子的時間與閘極掃描時間是可比擬的[88]，並稱為慢缺陷(Slow trap)，假設這些缺陷的能量態位位於半導體禁帶能隙，缺陷可以與半導體交換電荷，缺陷被填入的狀態與電壓掃描的歷史有關，隨著閘極電壓的提高，缺陷會開始捕捉電子，若在回掃時被捕捉的電子釋放的速度較電壓改變慢，使得回掃時仍有較多的捕獲電荷，造成較大的臨界電壓，則會形成  $I_D-V_G$  曲線有順時針遲滯。

對於較厚的 HZO 電晶體元件，在閘極電壓範圍-7~7 V 下量測，HZO 15 nm 電晶體元件之  $I_D-V_{OV}$  量測結果如圖 3.20(a)-(d)所示，氧化層只有 HZO 的電晶體  $I_D-V_{OV}$  量測結果如圖 3.20(a)所示，灰黑色曲線與淡灰色曲線分別為汲極電流與閘極電流，皆對應到左邊對數刻度，由圖觀察到閘極電流大於汲極電流，並且閘極電流值已達量測所設限流，使得量測結果無法完全反映電晶體特性，在沒有添加額外氧化層的狀況下有較大的閘極漏電流。氧化層為 HZO 堆疊在  $\text{Al}_2\text{O}_3$  上的電晶體元件  $I_D-V_{OV}$  量測結果如圖 3.20(b)所示， $I_D-V_{OV}$  量測結果展現順時針遲滯，記憶體視窗約為-4.00 V，氧化層堆疊為  $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$  的電晶體元件  $I_D-V_{OV}$  量測結果如圖 3.20(c)所示， $I_D-V_{OV}$  量測結果展現順時針遲滯，記憶體視窗約為-3.59 V，氧化層堆

圖 3.20 HZO 厚度 15 nm 不同氧化層堆疊之鐵電電晶體  $I_D$ - $V_{OV}$  曲線與總結，圖中插圖為氧化層堆疊示意圖(a)HZO，(b)HZO/ $Al_2O_3$ ，(c) $Al_2O_3$ /HZO/ $Al_2O_3$ ，(d) $Al_2O_3$ /HZO。(e)記憶體視窗對應不同氧化層堆疊。

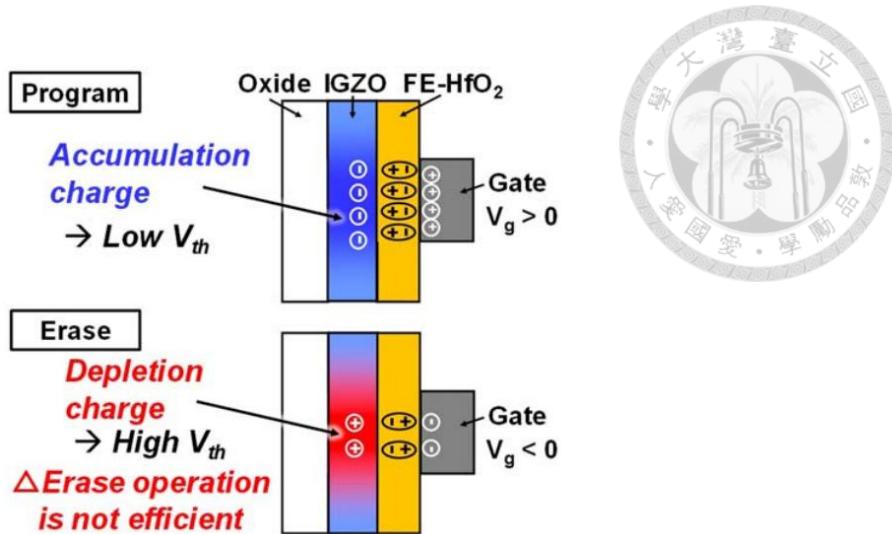

疊為  $Al_2O_3$ /HZO 的電晶體元件  $I_D$ - $V_{OV}$  量測結果如圖 3.20(d)所示， $I_D$ - $V_{OV}$  量測結果展現順時針遲滯，記憶體視窗約為 -1.83 V，在相同 HZO 15 nm 厚度下，此種堆疊展現最小的順時針遲滯，值得注意的是在  $V_{OV}$  範圍 2.5~8 V 下出現顯著的逆時針遲滯，意即這區間是由鐵電特性主導遲滯現象。記憶體視窗大小對應不同氧化層堆疊關係如圖 3.20(e)所示，相同地，具有相對較正的記憶體視窗電晶體元件的氧化層堆疊為  $Al_2O_3$ /HZO，對應到其電容最大的剩餘極化值。對於鐵電層 HZO 較厚的元件，展現相對於 10 nm HZO 較負的鐵電記憶體視窗，兩組元件掃描電壓範圍不一樣無法直接比較。假設不同厚度 HZO 在相同電場下有一樣的鐵電特性，且在量測電壓下剩餘極化值飽和，僅考慮缺陷捕捉電荷在不同電壓範圍下的不同行為，對於二硫化鉬電晶體，較大的閘極電壓掃描範圍會造成較大的順時針遲滯[88]，過去研究提出，缺陷與通道電子之間存在能障，電子需要能量跨越能障才會被缺陷捕獲，不同缺陷具有不同能障高度，對於二硫化鉬電晶體施加較大的閘極電壓，通道中電子能量較高可以跨越較大能障的缺陷，因此有較多的電子被缺陷捕獲成為介面電荷，回掃時較多介面電荷造成的順時針遲滯無法直接與鐵電造成的逆時針遲滯疊加[70]，但較多的介面電荷可以說明更負的鐵電記憶體視窗，以此解釋較厚的 HZO 在大電壓範圍量測，有更負鐵電記憶體視窗的可能原因。除了漏電的元件之外，其他三個元件有觀察到回掃的汲極電流曲線較陡峭(圖 3.20(b)-(d))，可能原因是在回

圖 3.21 沒有足夠電洞平衡極化示意圖[90]。

掃時鐵電極化方向改變，原本平衡極化的半導體側電荷被釋放出來，注入通道使得回掃的次臨界擺幅較好。此外，過去文獻[89]指出，鐵電電晶體的通道材料會影響鐵電層的極化行為，進而影響記憶體視窗大小。對於矽作為通道的鐵電電晶體為例，在正掃與反掃皆有足夠的電子與電洞平衡鐵電極化切換。然而，對於 n-型氮化鎵(GaN)作為通道鐵電電晶體則因電洞濃度極低，無法實現完整的極化切換。相同地，文獻[90]也提出氧化銦鎵鋅(IGZO)中缺少電洞，若作為鐵電電晶體通道，在閘極施加負偏壓時，沒有足夠電洞平衡鐵電極化(圖 3.21)，使得鐵電翻轉不完全。二硫化鉬作為 n-型無接面(junctionless)鐵電電晶體，記憶體視窗較小原因之一可能也是缺少電洞平衡極化，使鐵電翻轉不完全，缺陷電荷捕捉效應主導順時針遲滯行為。

而 HZO 15 nm 並額外增加 TiN 的電晶體元件之  $I_D-V_{ov}$  量測結果如圖 3.22(a)-(d)所示，氧化層只有 HZO 的電晶體  $I_D-V_{ov}$  量測結果如圖 3.22(a)所示， $I_D-V_{ov}$  量測結果展現順時針遲滯，記憶體視窗約為 -1.13 V，氧化層為 HZO 堆疊在  $\text{Al}_2\text{O}_3$  上的電晶體元件  $I_D-V_{ov}$  量測結果如圖 3.22(b)所示， $I_D-V_{ov}$  量測結果展現順時針遲滯，記憶體視窗約為 -4.32 V，氧化層堆疊為  $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$  的電晶體元件  $I_D-V_{ov}$  量測結果如圖 3.22(c)所示， $I_D-V_{ov}$  量測結果展現順時針遲滯，記憶體視窗約為 -1.52 V，氧化層堆疊為  $\text{Al}_2\text{O}_3/\text{HZO}$  的電晶體元件  $I_D-V_{ov}$  量測結果如圖 3.22(d)所示， $I_D-V_{ov}$  量測結果展現順時針遲滯，記憶體視窗約為 -0.79 V，記憶體視窗大小對應不同氧化層堆疊關係如圖 3.22(e)所示，相對較正的記憶體視窗電晶體元件的氧化層堆疊為  $\text{Al}_2\text{O}_3/\text{HZO}$ ，對應於其氧化層堆疊有較大的剩餘極化值。對於相同為 15 nm 厚度的 HZO，若在矽基板上先成長 TiN，在  $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$  與  $\text{Al}_2\text{O}_3/\text{HZO}$  兩種堆

圖 3.22 HZO 厚度 15 nm 不同氧化層堆疊加上額外 TiN 之鐵電電晶體  $I_D$ - $V_{OV}$  曲線與總結，圖中插圖為氧化層堆疊示意圖(a)HZO，(b)HZO/ $\text{Al}_2\text{O}_3$ ，(c) $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$ ，(d) $\text{Al}_2\text{O}_3/\text{HZO}$ 。(e)記憶體視窗對應不同氧化層堆疊。

疊電容皆有較大的剩餘極化值，對應電晶體展現相對較正的記憶體視窗，與其他兩組鐵電電晶體趨勢相同，若在這組元件中具相同多餘介面電荷密度  $\sigma_{i-}$  下，考慮一較大遲滯的 PV 曲線，即有較大的剩餘極化， $\sigma_{i-}$  與遲滯曲線的交點  $E_-$  會向左偏移，得到相對較正的記憶體視窗。

### 3.4 結論

本章首先回顧了鐵電材料與二維材料鐵電場效電晶體的相關文獻，了解元件結構如何設計，以及知道其操作機制。選用 HZO 作為鐵電材料，製作四種不同氧化層堆疊的 MFS 結構電容並量測鐵電 P-V 特性，包含 HZO、HZO/ $\text{Al}_2\text{O}_3$ 、 $\text{Al}_2\text{O}_3/\text{HZO}/\text{Al}_2\text{O}_3$  與  $\text{Al}_2\text{O}_3/\text{HZO}$ ，其中  $\text{Al}_2\text{O}_3/\text{HZO}$  堆疊電容展現最大剩餘極化值，在 HZO 上有  $\text{Al}_2\text{O}_3$  覆蓋層的兩種堆疊展現較好的鐵電特性，其原因為退火時  $\text{Al}_2\text{O}_3$  覆蓋層對 HZO 施加應力，使得鐵電相增加，稱為覆蓋效應(Capping effect)。此外，若先在矽基板上成長 TiN，則展現較好的剩餘極化值，代表 HZO/TiN 介面優於 HZO/Si 介面，其原因為 HZO/Si 可能產生介面偶極進而影響鐵電特性。後續製作二硫化鉬為通道的鐵電場效電晶體，HZO 10nm 且氧化層堆疊為  $\text{Al}_2\text{O}_3/\text{HZO}$  電晶體量測到逆時針遲滯，展現正的鐵電記憶體視窗，其他大部分元件的  $I_D$ - $V_{OV}$  曲線

則是量測到順時針遲滯，其原因為介面電荷在正掃與回掃的不對稱行為，若回掃時的在缺陷的介面電荷較多，使得回掃時的臨界電壓較正，可能造成順時針遲滯，對應到負的鐵電電晶體視窗，此外，對比是否在矽基板上成長 TiN 的電晶體，若有 TiN 展現相對較正的記憶體視窗。由本章結果可知，對於高摻雜矽作為背閘極的鐵電元件，額外覆蓋層  $\text{Al}_2\text{O}_3$  堆疊在鐵電層 HZO 之上是最佳的選擇。

## 第 4 章 結論與未來工作

### 4.1 結論

本論文研究二維材料鐵電場效電晶體，利用二硫化鉬作為半導體通道、氧化鋁作為鐵電層。首先，製作二硫化鉬電晶體，沈積二氧化矽作為氧化層以確認半導體製程流程可行，在實驗室已架設好的手套箱內進行二維材料機械式剝離，並將其轉移到元件圖案上，完成元件後進行電性量測，其電晶體具有良好電流開關比約為  $10^5$ ，而次臨界擺幅最小值約為  $150\text{ mV/dec}$ 。若額外使用石墨烯作為源極/汲極接觸金屬，電流開關比提升至約為  $10^6$ ，可能原因為石墨烯的功函數隨電壓上升而減少，與  $\text{MoS}_2$  形成較好的歐姆接觸，提高導通電流，此外，次臨界擺幅最小值降低至  $90\text{ mV/dec}$ ，可能是因為石墨烯是一種狄拉克材料，減少電子密度在費米能階之上的分佈，使電子注入通道更集中，達到較小的次臨界擺幅。後續進行變溫量測，電晶體的閾值電壓隨溫度下降而提升，在低溫下，費米-狄拉克分布在低溫時趨近階梯函數，需更大的電壓提高費米能階，達到與導通時相同的電子數量，而次臨界擺幅時隨溫度下降有下降的趨勢，室溫時，費米能階上有一因熱激發形成的熱帶尾，載子較分散進入導帶，使電晶體通道慢慢打開，而在低溫時，費米-狄拉克為一階梯函數，載子集中進入導帶，有較好的次臨界擺幅，但在溫度  $50\text{ K}$  後，次臨界擺幅並沒有明顯下降甚至惡化，可能與缺陷形成的局域態有關，使次臨界擺幅無法持續下降。

後續以前述之製程步驟製作二維鐵電場效電晶體，將電晶體氧化層改為鐵電氧化鋁，再轉移二維材料前，元件由上到下為一金屬-鐵電層(+介電層)-半導體結構，進行鐵電極化量測，由實驗結果發現，氧化層堆疊為氧化鋁在氧化鉻鋸上的元件，展現較大的剩餘極化值，在退火時有一覆蓋層在氧化鉻鋸上有助於形成鐵電相，並且在  $10\text{ nm}$  與  $15\text{ nm}$  厚度的氧化鉻鋸皆有看到此現象。轉移二維材料後完成製程，量測鐵電電晶體的遲滯曲線，僅有氧化層堆疊為氧化鋁在氧化鉻鋸上的電晶體展現逆時針遲滯，對應到正的鐵電記憶體視窗，而其他元件展現順時針曲線，其原因為缺陷造成介面電荷在正掃與回掃的不對稱行為，缺陷源自二硫化鉬本身與二硫化鉬/氧化層介面，若回掃時的被缺陷捕捉的介面電荷較多，使得回掃時的臨界電壓較正，得到順時針遲滯，對應到負的記憶體視窗。總結實驗結果，氧化鋁堆疊

在氧化鉻鋯上電容展現最大剩餘極化，其電晶體對應到較正的記憶體視窗。

## 4.2 未來工作

未來工作分為四個部分：

1. 電晶體採用後電極製程，在成長完氧化層後轉移二維材料，並用原子力顯微鏡掃描厚度，確認厚度相近後，再進行後續製程，以此減少元件間二維材料厚度差異。

2. 在二維材料上新增一絕緣層如氮化硼(h-BN)，減少環境中水氧吸附二維材料，改善環境對電性的影響。

3. 在 MFIS 結構中使用其他不同氧化層如二氧化鋯( $ZrO_2$ )與氧化鉻鋯堆疊，並比較哪種氧化層有助於提高鐵電特性。嘗試採用 MFMIS 結構，透過改變氧化層與鐵電層面積比值，增加鐵電層跨壓(減少介面層跨壓)，與 MFIS 結構相比，僅需要較小的操作電壓即可以達到相近的記憶體視窗，降低功耗與減少鐵電層漏電風險，此外，額外的浮動閘極可以儲存電荷，減少鐵電層介面缺陷捕獲行為，提升元件可靠度。

4. 使用脈衝(Pulse)電壓量測鐵電場效電晶體，以減少介面電荷捕捉效應影響。

## 參考文獻

-

- [1] G. E. Moore, "Cramming more components onto integrated circuits," *Proceedings of the IEEE*, vol. 86, no. 1, pp. 82–85, 1998.

- [2] G. E. Moore, "Progress in digital integrated electronics [Technical literature, Copyright 1975 IEEE. Reprinted, with permission. Technical Digest. International Electron Devices Meeting, IEEE, 1975, pp. 11-13.]," *IEEE Solid-State Circuits Society Newsletter*, vol. 11, no. 3, pp. 36–37, 2006.

- [3] K. S. Kim et al., "The future of two-dimensional semiconductors beyond Moore's law," *Nature Nanotechnology*, vol. 19, no. 7, pp. 895–906, 2024.

- [4] R.-H. Yan, A. Ourmazd, and K. F. Lee, "Scaling the Si MOSFET: from bulk to SOI to bulk," *IEEE Transactions on Electron Devices*, vol. 39, no. 7, pp. 1704–1710, 1992.

- [5] E. Pop, S. Sinha, and K. E. Goodson, "Heat generation and transport in nanometer-scale transistors," *Proceedings of the IEEE*, vol. 94, no. 8, pp. 1587–1601, 2006.

- [6] K. Rim et al., "Strained Si nMOSFETs for high performance CMOS technology," in *2001 Symposium on VLSI Technology. Digest of Technical Papers (IEEE Cat. No.01 CH37184)*, pp. 59–60, 2001.

- [7] K. Mistry et al., "A 45 nm logic technology with high-k+metal gate transistors, strained silicon, 9 Cu interconnect layers, 193 nm dry patterning, and 100 % Pb free packaging," *2007 IEEE International Electron Devices Meeting*, Washington, DC, USA, pp. 247–250, 2007.

- [8] S. Yamakawa et al., "Study of interface roughness dependence of electron mobility in Si inversion layers using the Monte Carlo method," *Journal of Applied Physics*, vol. 79, no. 2, pp. 911–916, 1996.

- [9] H.-H. S. Lee and K. Chakrabarty, "Test challenges for 3D integrated circuits," *IEEE Design & Test of Computers*, vol. 26, no. 5, pp. 26–35, 2009.

- [10] Y. Liu, X. Duan, H.-J. Shin, S. Park, Y. Huang, and X. Duan, "Promises and prospects of two-dimensional transistors," *Nature*, vol. 591, no. 7848, pp. 43–53, 2021.

- [11] C. Liu et al., "Two-dimensional materials for next-generation computing technologies," *Nature Nanotechnology*, vol. 15, no. 7, pp. 545–557, 2020.

- [12] P. Ajayan, P. Kim, and K. Banerjee, "Two-dimensional van der Waals materials,"

- Physics Today*, vol. 69, no. 9, pp. 38–44, 2016.

- [13] L. Cheng and Y. Liu, “What limits the intrinsic mobility of electrons and holes in two dimensional metal dichalcogenides?,” *Journal of the American Chemical Society*, vol. 140, no. 51, pp. 17895–17900, 2018.

- [14] H. Yu et al., “Waferscale growth and transfer of highlyoriented monolayer MoS<sub>2</sub> continuous films,” *ACS Nano*, vol. 11, no. 12, pp. 12001–12007, 2017.

- [15] L. Xie et al., “Graphene-contacted ultrashort channel monolayer MoS<sub>2</sub> transistors,” *Advanced Materials*, vol. 29, no. 37, p. 1702522, 2017.

- [16] Y. Liu et al., “Toward barrier free contact to molybdenum disulfide using graphene electrodes,” *Nano Letters*, vol. 15, no. 5, pp. 3030–3034, 2015.

- [17] W. Liu, D. Sarkar, J. Kang, W. Cao, and K. Banerjee, “Impact of contact on the operation and performance of back-gated monolayer MoS<sub>2</sub> field-effect-transistors,” *ACS Nano*, vol. 9, no. 8, pp. 7904–7912, 2015.

- [18] N. Izyumskaya, Y. I. Alivov, S. W. Cho, Hadis Morkoç, H. Lee, and Y. James Kang, “Processing, structure, properties, and applications of PZT thin films,” *Critical Reviews in Solid State and Materials Sciences*, vol. 32, no. 3–4, pp. 111–202, 2007.

- [19] T. Mikolajick et al., “Next generation ferroelectric materials for semiconductor process integration and their applications,” *Journal of Applied Physics*, vol. 129, no. 10, p. 100901, 2021.

- [20] J. L. Moll and Y. Tarui, “A new solid state memory resistor,” *IEEE Transactions on Electron Devices*, vol. 10, no. 5, p. 338, 1963.

- [21] R. Zuleeg and H. H. Wieder, “Effect of ferroelectric polarization on insulated-gate thin-film transistor parameters,” *Solid-State Electronics*, vol. 9, no. 6, pp. 657–661, 1966.

- [22] Shu-Yau Wu, “A new ferroelectric memory device, metal-ferroelectric-semiconductor transistor,” *IEEE Transactions on Electron Devices*, vol. 21, no. 8, pp. 499–504, 1974.

- [23] Yushi Shichi, S. Tanimoto, T. Goto, K. Kuroiwa, and Yasuo Tarui, “Interaction of PbTiO<sub>3</sub> films with Si substrate,” *Japanese Journal of Applied Physics*, vol. 33, no. 9S, pp. 5172–5172, 1994.

- [24] G. He, M. Liu, L. Q. Zhu, M. Chang, Q. Fang, and L. D. Zhang, “Effect of postdeposition annealing on the thermal stability and structural characteristics of sputtered HfO<sub>2</sub> films on Si (100),” *Surface Science*, vol. 576, no. 1–3, pp. 67–75,

2005.

- [25] H. Mulaosmanovic, E. T. Breyer, S. Dünkel, S. Beyer, T. Mikolajick, and S. Slesazeck, "Ferroelectric field-effect transistors based on HfO<sub>2</sub>: a review," *Nanotechnology*, vol. 32, no. 50, p. 502002, 2021.

- [26] S. Sakai and R. Ilangovan, "Metal–ferroelectric–insulator–semiconductor memory FET with long retention and high endurance," *IEEE Electron Device Letters*, vol. 25, no. 6, pp. 369–371, 2004.

- [27] T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger, "Ferroelectricity in hafnium oxide thin films," *Applied Physics Letters*, vol. 99, no. 10, p. 102903, 2011.

- [28] T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder and U. Böttger, "Ferroelectricity in hafnium oxide: CMOS compatible ferroelectric field effect transistors," *2011 International Electron Devices Meeting*, Washington, DC, USA, pp. 24.5.1-24.5.4, 2011.

- [29] J. Müller et al., "Ferroelectricity in HfO<sub>2</sub> enables nonvolatile data storage in 28 nm HKMG," *2012 Symposium on VLSI Technology (VLSIT)*, Honolulu, HI, USA, pp. 25-26, 2012.

- [30] H. Mulaosmanovic et al., "Evidence of single domain switching in hafnium oxide based FeFETs: enabler for multi-level FeFET memory cells," *2015 IEEE International Electron Devices Meeting (IEDM)*, Washington, DC, USA, pp. 26.8.1-26.8.3, 2015.

- [31] M. Trentzsch et al., "A 28nm HKMG super low power embedded NVM technology based on ferroelectric FETs," *2016 IEEE International Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, pp. 11.5.1-11.5.4, 2016.

- [32] S. Dünkel et al., "A FeFET based super-low-power ultra-fast embedded NVM technology for 22nm FDSOI and beyond," *2017 IEEE International Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, pp. 19.7.1-19.7.4, 2017.

- [33] K. Florent et al., "Vertical ferroelectric HfO<sub>2</sub> FET based on 3-D NAND architecture: towards dense low-power memory," *2018 IEEE International Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, pp. 2.5.1-2.5.4, 2018.

- [34] E. T. Breyer et al., "Ultra-dense co-integration of FeFETs and CMOS logic enabling very-fine grained logic-in-memory," *ESSDERC 2019 - 49th European Solid-State Device Research Conference (ESSDERC)*, Cracow, Poland, pp. 118–121, 2019.

- [35] V. Milo, G. Malavena, C. Monzio Compagnoni, and D. Ielmini, “Memristive and CMOS devices for neuromorphic computing,” *Materials*, vol. 13, no. 1, p. 166, 2020.

- [36] R. Mathew and J. Ajayan, “Material processing, performance and reliability of MoS<sub>2</sub> field effect transistor (FET) technology- A critical review,” *Materials Science in Semiconductor Processing*, vol. 160, p. 107397, 2023.

- [37] K. F. Mak, C. Lee, J. Hone, J. Shan, and T. F. Heinz, “Atomically thin MoS<sub>2</sub>: A new direct-gap semiconductor,” *Physical Review Letters*, vol. 105, no. 13, p. 136805, 2010.

- [38] S. Golovynskyi et al., “Exciton and trion in few-layer MoS<sub>2</sub>: thickness- and temperature-dependent photoluminescence,” *Applied Surface Science*, vol. 515, p. 146033, 2020.

- [39] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, “Single-layer MoS<sub>2</sub> transistors,” *Nature Nanotechnology*, vol. 6, no. 3, pp. 147–150, 2011.

- [40] L. Gomez, I. berg, and J. L. Hoyt, “Electron transport in strained-silicon directly on insulator ultrathin-body n-MOSFETs with body thickness ranging from 2 to 25 nm,” *IEEE Electron Device Letters*, vol. 28, no. 4, pp. 285–287, 2007.

- [41] X. Li, X. Wang, L. Zhang, S. Lee, and H. Dai, “Chemically derived, ultrasMOOTH graphene nanoribbon semiconductors,” *Science*, vol. 319, no. 5867, pp. 1229–1232, 2008.

- [42] S. Das, H.-Y. Chen, A. V. Penumatcha, and J. Appenzeller, “High performance multilayer MoS<sub>2</sub> transistors with scandium contacts,” *Nano Letters*, vol. 13, no. 1, pp. 100–105, 2012.

- [43] D. J. Late, B. Liu, S. Ramakrishna, V. P. Dravid, and R. Rao, “Hysteresis in single-layer MoS<sub>2</sub> field effect transistors,” *ACS Nano*, vol. 6, no. 6, pp. 5635–5641, 2012.

- [44] A. Molina-Sánchez, K. Hummer, and L. Wirtz, “Vibrational and optical properties of MoS<sub>2</sub> : from monolayer to bulk,” *Surface Science Reports*, vol. 70, no. 4, pp. 554–586, 2015.

- [45] J. Yan, C. Ma, P. Liu, and G. Yang, “Plasmon-induced energy transfer and photoluminescence manipulation in MoS<sub>2</sub> with a different number of layers,” *ACS Photonics*, vol. 4, no. 5, pp. 1092–1100, 2017.

- [46] E. Pollmann et al., “Apparent differences between single layer molybdenum disulphide fabricated via chemical vapour deposition and exfoliation,” *Nanotechnology*, vol. 31, no. 50, p. 505604, 2020.

- [47] R.-J. Wu, Effects of fabrication processes and measurement ambience on electron transport of tin disulfide, M.S. thesis, National Taiwan University, Taipei, Taiwan, 2023.

- [48] S.-C. Su, Fabrication of 2D/3D heterojunction tunnel field-effect transistors, M.S. thesis, National Taiwan University, Taipei, Taiwan, 2023.

- [49] Y. Zhang et al., "Thickness considerations of two-dimensional layered semiconductors for transistor applications," *Scientific Reports*, vol. 6, no. 1, p. 29615, 2016.

- [50] S. M. Sze, Y. Li, and K. K. Ng, *Physics of semiconductor devices*, John Wiley & Sons, 2021.

- [51] Lee, Young Tack, et al. "Graphene versus ohmic metal as source-drain electrode for MoS<sub>2</sub> nanosheet transistor channel." *Small*, vol. 10, no. 12, 2, pp. 2356–2361, 2014.

- [52] C.-S. C. Chien, H.-M. Chang, W.-T. Lee, M.-R. Tang, C.-H. Wu, and S.-C. Lee, "High performance MoS<sub>2</sub> TFT using graphene contact first process," *AIP Advances*, vol. 7, no. 8, p. 085018, 2017.

- [53] P. Wu and J. Appenzeller, "Explaining steep-slope switching in carbon nanotube Dirac-source field-effect transistors," *IEEE Transactions on Electron Devices*, vol. 69, no. 9, pp. 5270–5275, 2022.

- [54] Z. Tang et al., "A steep-slope MoS<sub>2</sub>/graphene dirac-source field-effect transistor with a large drive current," *Nano Letters*, vol. 21, no. 4, pp. 1758–1764, 2021.

- [55] S. Mengxing, X. Dan, S. Yilin, L. Weiwei, and R. Tianling, "The electrical performances of monolayer MoS<sub>2</sub>-based transistors under ultra-low temperature," *2018 IEEE 18th International Conference on Nanotechnology*, pp. 420–425, 2018.

- [56] X. Liu et al., "Low temperature carrier transport study of monolayer MoS<sub>2</sub> field effect transistors prepared by chemical vapor deposition under an atmospheric pressure," *Journal of Applied Physics*, vol. 118, no. 12, p. 124506, 2015.

- [57] F. Nan, K. Nagashio, and A. Toriumi, "Subthreshold transport in mono- and multilayered MoS<sub>2</sub> FETs," *Applied Physics Express*, vol. 8, no. 6, p. 065203, 2015.

- [58] C. Enz, A. Beckers and F. Jazaeri, "Cryo-CMOS compact modeling," *2020 IEEE International Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, pp. 25.3.1-25.3.4, 2020.

- [59] Z. Yu et al., "Analyzing the carrier mobility in transition-metal dichalcogenide MoS<sub>2</sub> field-effect transistors," *Advanced Functional Materials*, vol. 27, no. 19, p. 1604093,

2017.

- [60] Jae Young Kim, M. Choi, and Ho Won Jang, “Ferroelectric field effect transistors: progress and perspective,” *APL Materials*, vol. 9, no. 2, p. 021102, 2021

- [61] X. Chen, X. Han, and D. Zhou, “PVDF-based ferroelectric polymers in modern flexible electronics,” *Advanced Electronic Materials*, vol. 3, no. 5, p. 1600460, 2017.

- [62] J. Müller et al., “Ferroelectric  $Zr_{0.5}Hf_{0.5}O_2$  thin films for nonvolatile memory applications,” *Applied Physics Letters*, vol. 99, no. 11, p. 112901, 2011.

- [63] J. Müller et al., “Ferroelectricity in yttrium-doped hafnium oxide,” *Journal of Applied Physics*, vol. 110, no. 11, p. 114113, 2011.

- [64] S. Mueller et al., “Incipient ferroelectricity in Al-doped  $HfO_2$  thin films,” *Advanced Functional Materials*, vol. 22, no. 11, pp. 2412–2417, 2012.

- [65] M. H. Park et al., “A comprehensive study on the structural evolution of  $HfO_2$  thin films doped with various dopants,” *Journal of Materials Chemistry C*, vol. 5, no. 19, pp. 4677–4690, 2017.

- [66] U. Schroeder, Cheol Seong Hwang, and Hiroshi Funakubo, Ferroelectricity in doped hafnium oxide. Woodhead Publishing, 2019.

- [67] J. Müller et al., “Ferroelectricity in simple binary  $ZrO_2$  and  $HfO_2$ ,” *Nano Letters*, vol. 12, no. 8, pp. 4318–4323, 2012.

- [68] M. H. Park, Y. H. Lee, T. Mikolajick, U. Schroeder, and C. S. Hwang, “Thermodynamic and kinetic origins of ferroelectricity in fluorite structure oxides,” *Advanced Electronic Materials*, vol. 5, no. 3, p. 1800522, 2018.

- [69] M. H. Park et al., “Understanding the formation of the metastable ferroelectric phase in hafnia-zirconia solid solution thin films,” *Nanoscale*, vol. 10, no. 2, pp. 716–725, 2018.

- [70] K. Toprasertpong, M. Takenaka, and S. Takagi, “Memory window in ferroelectric field-effect transistors: analytical approach,” *IEEE Transactions on Electron Devices*, vol. 69, no. 12, pp. 7113–7119, 2022.

- [71] K. Yang et al., “Perspective on ferroelectric devices: lessons from interfacial chemistry,” *Chemistry of Materials*, vol. 35, no. 6, pp. 2219–2237, 2023

- [72] J. Xiang, Wen Hsin Chang, Takuya Saraya, T. Hiramoto, Toshifumi Irisawa, and M. Kobayashi, “Ultrathin  $MoS_2$ -channel FeFET memory with enhanced ferroelectricity in  $HfZrO_2$  and body-potential control,” *IEEE journal of the Electron Devices Society*,

- vol. 10, pp. 72–77, 2022.

- [73] P.-C. Shen, C. Lin, H. Wang, K. H. Teo, and J. Kong, “Ferroelectric memory field-effect transistors using CVD monolayer MoS<sub>2</sub> as resistive switching channel,” *Applied Physics Letters*, vol. 116, no. 3, p. 033501, 2020.