#### 國立臺灣大學電機資訊學院資訊工程學系

## 碩士論文

Department of Computer Science and Information Engineering

College of Electrical Engineering and Computer Science

National Taiwan University

Master's Thesis

vSECvma: 經優化與形式化驗證的 Arm 平台 Linux 核 心保護框架

vSECvma: An Optimized and Formally Verified Linux Kernel Protection Framework on Arm

鄭明淵

Beng Yen Teh

指導教授:黎士瑋博士

Advisor: Shih-Wei Li Ph.D.

中華民國 114 年 10 月

October, 2025

## 國立臺灣大學碩士學位論文口試委員會審定書

## MASTER'S THESIS ACCEPTANCE CERTIFICATE NATIONAL TAIWAN UNIVERSITY

vSECvma: 經優化與形式化驗證的 Arm 平台 Linux 核心保護框架

vSECvma: An Optimized and Formally Verified Linux Kernel Protection Framework on Arm

本論文係<u>鄭明淵</u>君(學號 R12922178)在國立臺灣大學資訊工程學系完成之碩士學位論文,於民國 114 年 10 月 08 日承下列考試委員審查通過及口試及格,特此證明。

The undersigned, appointed by the Department of Computer Science and Information Engineering on 8 October 2025 have examined a Master's thesis entitled above presented by THE, BENG-YEN (student ID: R12922178) candidate and hereby certify that it is worthy of acceptance.

第十译 (指導教授 Advisor) [中间]

系主任/所長 Director:

口試委員 Oral examination committee:

#### 致謝

在論文完成之際,首先要獻上我最誠摯的謝意,感謝所有在研究過程中給予我幫助、指導與支持的人。

由衷感謝我的指導教授黎士瑋老師,在整個研究過程中老師給予我無私的指導與支持。不僅在技術層面上提供了精闢的見解與建議,更在研究方向的選擇與論文的撰寫上給予我極大的啟發與鼓勵。老師嚴謹的學術態度與對研究的熱情,將持續成為我未來學術道路上的榜樣。

同時,我也誠摯感謝陳郁方老師在研究過程中所給予的指導與協助。陳老師 的建議與討論讓我對形式化驗證的研究內容有了更深入的理解,並對我思考問題 的方式帶來了莫大的啟發。

謹向本論文的口試委員:黎士瑋老師、陳郁方老師、林忠緯老師以及王超老師致以最深的謝意。感謝各位老師在百忙之中撥冗審閱本論文,並於口試過程中提供了實貴的建議與專業指導。老師們深入的提問與精闢的意見,不僅使本研究內容更加完整與嚴謹,也極大地拓展了我的研究視野與思考方向。

此外,我亦要特別感謝 Spoq 專案的作者們,感謝他們開放原始碼與相關資源,使我能夠在本研究中順利地運用 Spoq 進行形式化驗證。若無他們的傑出貢獻,本研究將難以順利完成。其中,尤其感謝 Jason Nieh、Xupeng Li 與 Xuheng Li, 他們慷慨分享專案工具的使用經驗與技術細節,對我理解 Spoq 的運作原理與

應用方法有極大的幫助。

同時,感謝 Joey Li 學長與黎老師促成了我們發表 SECvma 論文的機會,使我得以有機會參與學術研討會,拓展了我的研究視野與人脈網絡。在研究與開發過程中,這段交流與合作的歷程讓我獲益良多,充滿了挑戰與樂趣。

感謝所有與我共同討論、協助我解決研究問題,以及聆聽我的研究進度並給予實貴建議的同學與朋友們。特別感謝朋友馮朗軒、周健烽以及湯士弘同學,在研究過程中的切磋與陪伴。我也要感謝實驗室的夥伴們,感謝你們在研究與生活上的相互扶持與協助,讓這段求學旅程充滿意義與美好的回憶。

最後,也是最重要的,感謝我的家人。感謝您們一路以來的無私支持與鼓勵, 讓我在研究道路上得以心無旁慮、全心投入。謹向所有支持與幫助過我的人致以 最誠摯的謝意。

## 摘要

隨着單體式核心如 Linux 的規模與複雜度的不斷提升,其不僅造成了巨大的攻擊面,也引發了頻繁的安全性漏洞。雖然基於虛擬化的核心防護機制能透過硬體強制隔離提供強大的安全性,但它往往會帶來顯著的效能開銷,且僅僅是將信任邊界轉移到管理程式 (Hypervisor)。本論文提出 vSECvma,這是首個針對 Arm 架構、具備高效能且經過功能正確性形式化驗證的 Linux 核心防護框架。我們的工作證明了在強安全性、高效能與形式化保證之間能夠同時達成。在既有研究的基礎上,vSECvma 強化了安全性保證,並引入一系列新穎的最佳化技術,以緩解虛擬化方法所造成的效能負擔,從而維持 Linux 的效率與相容性。我們接著對系統核心進行功能正確性的形式化驗證。此驗證透過多重策略得以實現:重用來自SeKVM (經過形式化驗證的 KVM 管理程式)的已驗證元件;運用自動化驗證框架 Spoq;並將系統系統化地重構為更適合驗證的模型。本研究最終實現了首個能同時在 Arm 上提供強安全性與高效能,並具備功能正確性機器檢證證明的 Linux 核心防護框架。

關鍵字:作業系統,資訊安全,虛擬化,形式化驗證

#### **Abstract**

Monolithic kernels such as Linux have grown vastly in complexity, creating a large attack surface with frequent vulnerabilities. While virtualization-based kernel protection offers strong, hardware-enforced isolation, it often incurs significant performance overhead and merely shifts the trust boundary to the hypervisor. This thesis presents vSECvma, the first high-performance Linux kernel protection framework on Arm to be formally verified for functional correctness. Our work demonstrates that it is possible to achieve strong security, high performance, and formal assurance simultaneously. Building on prior work, vSECvma strengthens security guarantees and incorporates a suite of novel optimizations to mitigate the performance overhead of virtualization-based approaches, thereby retaining Linux's efficiency and compatibility. We then formally prove the functional correctness of its system's core. Our verification is made tractable through a multi-faceted strategy: reusing verified components from the SeKVM, a formally verified KVM-based hypervisor; leveraging Spoq, an automated verification framework; and systematically

restructuring the system into a verification-friendly model. Our work delivers the first framework for Linux on Arm that simultaneously achieves strong security and high performance, backed by a machine-checked proof of functional correctness.

Keywords: Operating Systems, Security, Virtualization, Formal Verification

## **Contents**

|               | P                                    | age  |

|---------------|--------------------------------------|------|

| 致謝            |                                      | iii  |

| 摘要            |                                      | V    |

| Abstract      |                                      | vii  |

| Contents      |                                      | ix   |

| List of Figur | res                                  | хi   |

| List of Table | es                                   | xiii |

| Chapter 1     | Introduction                         | 1    |

| Chapter 2     | Background                           | 5    |

| 2.1           | Formally Verified Systems            | 5    |

| 2.2           | Spoq                                 | 6    |

| 2.3           | Introduction to K-Int                | 10   |

| Chapter 3     | Threat Model And Assumptions         | 13   |

| Chapter 4     | Design                               | 15   |

| 4.1           | Security Enhancements                | 17   |

| 4.1.1         | System Register Protection           | 17   |

| 4.1.2         | Supervisor Mode Execution Prevention | 18   |

| 4.2           | Optimization                         | 20   |

|                        | 4.3                  | Adapting KPCore to Spoq Framework               | 23 |

|------------------------|----------------------|-------------------------------------------------|----|

|                        | 4.3.1                | Layered Design                                  | 28 |

| Chap                   | ter 5                | Verifying Functional Correctness of KPCore      | 33 |

|                        | 5.1                  | Abstract Machine Model Layer                    | 35 |

|                        | 5.2                  | Functional Correctness of Page Tables           | 35 |

|                        | 5.2.1                | Stage 2 Page Table Management                   | 36 |

|                        | 5.2.2                | Stage 1 Page Table Management                   | 40 |

|                        | 5.3                  | Functional Correctness of Secure Module Loading | 41 |

|                        | 5.4                  | Ensured Invariants and Correctness Guarantees   | 44 |

|                        | 5.5                  | Addressing Limitations of Spoq                  | 46 |

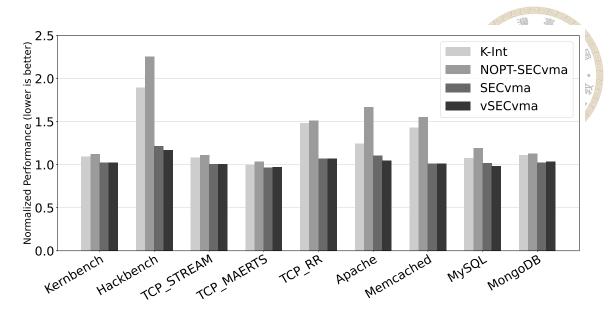

| Chapter 6              |                      | Evaluation                                      | 49 |

|                        | 6.1                  | Performance Evaluation                          | 52 |

|                        | 6.2                  | Bugs found in SECvma                            | 56 |

| Chapter 7 Related Work |                      | Related Work                                    | 61 |

| Chap                   | oter 8               | Limitations and Future Work                     | 65 |

| Chap                   | Chapter 9 Conclusion |                                                 | 67 |

| Refer                  | rences               |                                                 | 69 |

## **List of Figures**

| 4.1 | vSECvma System Architecture                                                | 16 |

|-----|----------------------------------------------------------------------------|----|

| 4.2 | Huge Page Optimization                                                     | 21 |

| 4.3 | Encapsulating raw pointers from higher-layers with a getter wrapper        | 25 |

| 4.4 | KPCore Layered Design. (1) Blue: Kernel Memory Protection. (2) Green:      |    |

|     | Secure Module Loading. (3) Red: System Register Protection. (4) Yel-       |    |

|     | low: Common/Helper/Machine Model Modules. (5) Grey and modules             |    |

|     | marked with *: SeKVM's existing modules [48] and the HACL crypto-          |    |

|     | graphic library [74]. † indicates the original implementations are fully   |    |

|     | reused without modification                                                | 32 |

| 5.1 | Security Components in KPCore                                              | 34 |

| 5.2 | Refinement relations used in the proof: (a) P1 and P2 enforces proper-     |    |

|     | ties (1) and (2); (b) P3 enforces property (3); and (c) lvXpt_rel connects |    |

|     | entries in the high-level flat map to their corresponding multi-level page |    |

|     | walks in the low-level specification. (b) and (c) indicate only the added  |    |

|     | relations for 1GB mappings, with other cases omitted for brevity           | 39 |

| 6.1 | Application Performance of Linux Host                                      | 54 |

хi

## **List of Tables**

| 4.1 | Virtual Memory System Registers                                      | 18 |

|-----|----------------------------------------------------------------------|----|

| 4.2 | Kernel Protection Hypercalls                                         | 31 |

| 6.1 | KPCore's Lines of Code                                               | 50 |

| 6.2 | Specification and proof generation by Spoq, with manual proof effort | 51 |

| 6.3 | Description of benchmark application                                 | 53 |

| 6.4 | Module Performance                                                   | 56 |

## **Chapter 1** Introduction

Monolithic OS kernels have become increasingly complex to meet the growing demands for functionality and performance. Linux, for example, is deployed across highly heterogeneous computing environments and has grown to tens of millions of lines of code. This complexity results in hundreds of new common vulnerabilities and exposures (CVEs) being reported each year [46], making the kernel a prime target for attackers. An attacker can exploit kernel vulnerabilities or install rootkits to gain full control over the system and unrestricted access to resources, thereby compromising user safety.

Virtualization-based kernel protection [8, 39, 52, 55, 58, 59, 61, 63, 71] has emerged as a practical and widely explored defense strategy. It leverages hardware virtualization features with a higher-privileged hypervisor to transparently monitor and restrict abnormal kernel behavior from outside the OS. Modern processors now provide virtualization support as a standard capability [64, 68, 69], including mechanisms such as nested page tables (NPTs) to enforce memory isolation between the host OS and guest virtual machines (VMs). The widespread availability of these features makes virtualization-based protection broadly deployable.

However, these approaches face two major challenges. First, establishing an additional protection layer at the hypervisor level often incurs non-trivial performance over-

1

head from frequent traps and hypervisor-mediated operations, while also lacking visibility into certain OS-level contexts. Second, although this reduces the security risks that stem from kernel vulnerabilities, it merely shifts the trust boundary to the hypervisor, whose own vulnerabilities remain a single point of failure that can compromise the entire system.

Formal verification offers a principled way to address the second challenge. By mathematically proving that system software is correctly implemented and satisfies desired security properties, formal methods provide strong security guarantees that go beyond conventional testing and eliminate broad classes of implementation flaws. Over the years, the field has seen significant advancements, with projects demonstrating the feasibility and benefits of this approach in verifying system software [24, 26, 49], such as OS kernels [30, 31, 38, 54] and hypervisors [15, 42, 47, 48, 66]. However, applying formal methods to complex systems remains immensely difficult. It requires deep understanding of low-level details, substantial expertise in formal methods, and often person-years of effort. The most fundamental and challenging part is proving functional correctness, which involves rigorously demonstrating that the implementation faithfully satisfies an abstract high-level specification. The specification represents the intended behavior of the software as formalized in its formal model. It can then serve as the foundation for establishing high-level security properties.

Building on these insights, we present vSECvma, the first high-performance Linux kernel protection framework that has been formally verified for functional correctness. vSECvma employs a virtualization-based approach to preserve Linux kernel code integrity throughout its lifetime, even against a powerful attacker who has already obtained kernel privileges, while retaining Linux's performance and compatibility. Our work addresses

the challenges of both optimization and verification in two steps.

We first design and implement SECvma [73], which builds on our prior work, K-Int [45]. K-Int is a virtualization-based kernel protection framework designed to enforce code integrity of the Linux kernel, prototyped on SeKVM [47, 48], a formally verified KVM-based hypervisor. Building on SeKVM, K-Int provides a strong security foundation for kernel protection while simplifying implementation efforts. However, K-Int has several limitations: it assumes critical system registers controlling the MMU remain benign, fails to prevent attacks such as ret2usr [37], and suffers from significant performance overheads due to nested paging. To address these shortcomings, SECvma strengthens security guarantees and introduces novel optimizations, such as huge-page support and optimized trap handling. Our evaluation shows that SECvma retains Linux performance and compatibility while maintaining kernel code integrity.

We next formally prove the functional correctness of SECvma's TCB. To make this large-scale effort feasible, we reuse verified components of SeKVM. For the novel and extended components introduced by SECvma, we adopt a modular verification strategy [32] and leverage Spoq [50], an automated verification framework that generates specifications and machine-checkable proofs from unmodified system software. However, SECvma's implementation contains complex semantics—nested loops, intricate control flow branches, and pervasive pointer manipulation—that exceed Spoq's direct capabilities. We address this by systematically restructuring SECvma into vSECvma, a verification-friendly model that preserves functionality while enabling automation. With these strategies, we successfully prove the correctness of the framework, generating a top-level specification formally captures the intended behavior of the implementation. Notably, our proof includes the most challenging and security-critical components: the paging and module loading

subsystems. In particular, the paging subsystem manages host nested page tables with hardware-defined semantics. We prove its correctness by adapting SeKVM's proven page-table abstraction methodology [48] and further extending the verified model to support 1GB pages in addition to the existing 4KB and 2MB granularities.

Our work makes the following contributions:

- We design and implement SECvma, a virtualization-based kernel protection framework that enforces Linux kernel code integrity throughout its lifetime. SECvma builds on the K-Int design, strengthens security guarantees, and introduces performance optimizations such as huge-page support and optimized trap handling, while preserving Linux's performance and compatibility.

- We formally prove the functional correctness of SECvma's TCB. We employ a modular approach that reuses verified components from SeKVM and retrofit new components into a verification-friendly model, vSECvma, enabling automated reasoning with the Spoq framework.

- We successfully verified two of the most complex and security-critical components:

the paging and module loading subsystems. Our work also extends the verified paging model to support 1GB huge pages.

4

### Chapter 2 Background

#### 2.1 Formally Verified Systems

To address the growing complexity of modern system software, which potentially introduces subtle bugs and security vulnerabilities, formal verification has emerged as a promising solution to ensure the correctness and reliability of system implementations. Formal verification employs mathematical techniques to prove that a system's implementation satisfies its formal specification, guaranteeing key properties like safety, integrity, or confidentiality under all specified conditions.

This potential has been realized in practice through a number of verified systems, such as microkernels and hypervisors. Pioneering examples include the seL4 microkernel [38], the first formally verified OS kernel, which leveraged the Isabelle/HOL theorem prover [56] to formally prove the functional correctness of its C code implementation. CertikOS [30, 31] builds a certified concurrent OS kernel using a layered verification methodology in Coq [4]. It leverages the CompCert verified C compiler [44] to extend its end-to-end correctness proofs reliably down to assembly level correctness. SeKVM [47, 48] retrofits a commodity multiprocessor KVM hypervisor and formally verifies its critical components that manage virtual machines (VMs) to ensure the integrity and confidentiality of VMs. Li et al. formally verified the correctness of SeKVM via mechanized

refinement proofs in Coq, building a low-level Arm machine model that captures page table management, TLB management, and a coherent cache hierarchy with cache-bypass support. Tao et al. [66] introduced the VRM framework and formally verified SeKVM, ensuring that proofs established under sequential consistency (SC) also hold on Arm's relaxed memory hardware.

#### 2.2 Spoq

Formal verification of complex system software is inherently difficult, particularly when dealing with low-level implementations in languages like C. Reasoning about intricate behaviors such as pointer arithmetic, type casting, low-level memory and register operations, and inline assembly code is inherently complex. Bridging the large semantic gap between low-level implementations and high-level formal specifications frequently requires developers to invest significant manual effort in writing specifications and proofs, which is difficult and error-prone. Any changes to the verified implementation can further invalidate existing proofs, imposing substantial engineering overhead for re-verification. These difficulties have motivated the development of verification frameworks [16, 18, 32, 34, 43, 50, 60, 65, 72] that aim to reduce manual effort and improve the scalability of formal verification.

Spoq [50] is an automated verification framework designed to generate machine-checkable proofs for system software. It significantly reduces the verification costs by automating the process of generating specifications and proofs directly from software implementations. Traditionally, specifications are manually written to describe the intended abstract behavior of a system and to capture the system's invariants. However, construct-

ing and maintaining such specifications for complex system requires substantial manual effort, and the process is prone to human error. In contrast, Spoq's specifications are implementation-driven. They are automatically derived from the system implementation, capturing most of its operational behavior. This approach greatly reduces manual modeling effort and the likelihood of human error, while still allowing developers to introduce additional abstract higher-level abstractions when reasoning about functional correctness or security properties. Unlike manually written specifications, Spoq-generated specifications faithfully capture the implementation's behavior. Consequently, any unintended behavior in the implementation will also be inherited by the generated specifications unless explicitly ruled out or constrained by separately proven invariants.

Spoq's verification process requires only minor code modifications and structural adjustments, guided by a principled methodology. To achieve large-scale automation, Spoq adopts a layering proof strategy based on Concurrent Certified Abstraction Layers (CCAL) [32]. It allows the decomposition of the complex verification process into multiple, independent layers, thereby simplifying the overall proof. Following the CCAL methodology, the system implementation is modularized into distinct layers, where each layer encapsulates a set of functions. Functions within these modules can be verified independently, yielding composable proofs. Each lower layer exposes a high-level, abstract interface to the layers above it, enabling higher layers to reason about functionality using these abstract interfaces, without being burdened by the intricate implementation details of the layers below. However, a key constraint of this approach is that functions within a layer are prohibited from invoking functions in the same or higher layers.

**Spoq's Layered Verification Workflow.** To scale and automate the verification process, a system's implementation is first refactored to conform to the layer structure

defined by CCALs. The developer provides Spoq with a configuration file describing this layer hierarchy. The workflow begins by translating the system implementation, typically written in C, into LLVM IR using the Clang compiler. Subsequently, Spoq's code analyzer transforms the LLVM IR into a Coq Abstract Syntax Tree (AST) representation, thereby eliminating the complexities of directly handling C semantics.

Following this, Spoq utilizes the provided configuration file to automatically generate a set of specifications and proofs for each defined layer. Based on the CCAL methodology, each proof module comprises three key components: a layer implementation, a low-level interface, and a high-level interface. To construct the proof for each module, Spoq introduces two fundamental types of refinement proofs for each function within the layer: the identical refinement and the lifting refinement. The former proves that the layer implementation built on top of the low-level interface correctly refines a low-level specification. The lifting refinement proves that this low-level specification ultimately refines the high-level specification with the refinement relation. The bottom layer serves as a machine model layer, which is a trusted layer that models low-level LLVM IR semantics, encompassing aspects such as register states, memory operations, and object pointers. Spoq provides a suite of Coq libraries to support these semantics as parsed from LLVM IR, simplifying the modeling of hardware and low-level software behaviors. The top-most layer culminates in a high-level specification of the entire system's intended behavior, which can then be used to formally prove critical properties, such as security invariants.

**Specifications and Proofs Generation.** Spoq automatically generates both specifications and proofs. To generate low-level specifications, Spoq performs a single-step transition from each instruction within the parsed Coq AST, progressively aggregating these individual instruction behaviors to form a comprehensive specification for the entire

function that is close to actual code behavior. Spoq then applies a set of transformation rules to systematically lift these low-level specifications to their corresponding high-level specifications, leveraging the Z3 SMT solver [25] to discharge symbolic execution obligations and perform mathematical simplifications. The high-level specifications are "self-contained", meaning they contain no calls to low-layer functions, as those calls are unfolded during the lifting process. Neither Spoq's libraries nor the generator needs to be trusted, as incorrect generation of specifications and proofs will be automatically detected and rejected by the Coq proof checker.

Spoq employs static proof strategies to generate proofs for each function, building them from generic and reusable templates. Distinct templates are used for functions with and without loops. For loop-free functions, Spoq applies a case analysis strategy to recursively decompose each conditional branch function into two sub-proofs, proving each execution path under a specific condition. For functions containing loops, Spoq applies an induction-based proof template. To assist in proving loop termination, the user is required to provide a "ranking function" in the configuration file. However, auto-generated proofs are not always sufficient, especially when dealing with complex functions that involve intricate branching, loop bodies with additional conditions, or early-exit constructs (e.g., break, continue). Such functions often span multiple basic blocks with complex control flow, making generic proof templates difficult to reason about. Even so, they provide a robust starting point. Although highly complex functions require manual refinement, most proofs can be completed with only minor user intervention or small adjustments to the proof template.

#### 2.3 Introduction to K-Int

Kernel integrity protection is a fundamental security property ensuring that the kernel code and critical data are not maliciously altered. Monolithic OS kernels, such as Linux, serve as the core component of an operating system, managing system resources and performing privileged tasks. Protecting their integrity is therefore essential to prevent full system compromise. One widely adopted defense strategy is to rely on a privileged system software, such as a hypervisor, cooperating with hardware features, to enforce robust protection even after the kernel's privileges have been breached.

K-Int [45] is a system that resides at the hypervisor level (EL2 on Arm) and leverages Arm Virtualization Extensions (VE) to enforce kernel code integrity. It aims to integrate with commodity hypervisors, reducing implementation effort while preserving essential hypervisor functionality, such as support for virtual machines. Currently, K-Int enforces several key protections, including **Kernel Code Integrity**, **Data Execution Prevention** (**DEP**), and **Kernel Page Table Protection**. It also supports **Loadable Kernel Modules** (**LKMs**), enabling users to install drivers as kernel extensions while prohibiting the installation of unauthorized modules.

Kernel Code Integrity and Data Execution Prevention. To enforce kernel code integrity and DEP, K-Int adopts the memory usage tracking mechanism that assigns a specific usage type to each memory page during system initialization (e.g., kernel code or kernel data). K-Int leverages Arm VE by enabling stage 2 paging for the host Linux. When the Linux host accesses memory via a virtual address (VA), the VA first translates to an intermediate physical address (IPA) through the Stage 1 Page Table (S1PT). This IPA is then translated to a physical address (PA) through the Stage 2 Page Table (S2PT), so

that the host cannot directly access physical memory. This allows K-Int to transparently interpose on all host memory accesses via host S2PT. K-Int handles S2 page faults from the host and employs identity mapping (where IPA is identical to PA), simplifying address management and minimizing TCB complexity. Based on the assigned memory usage type, K-Int enforces the appropriate S2 permissions (e.g., read-execute for kernel code, non-executable for kernel data) of mapped memory in host S2PT.

Kernel Page Table Protection. While K-Int effectively protects static kernel memory regions initialized during system boot, it also addresses threats stemming from dynamically allocated pages. The Linux kernel allocator allocates pages from the kernel heap, which can be subsequently used for various purposes such as S1PT pages, kernel data, or user memory. Since K-Int lacks specific knowledge of the intended use for these newly allocated pages (as they are not assigned a distinct usage type during runtime), these pages are granted full permissions in S2PT. An attacker could potentially perform page table manipulation attacks by tampering with S1PT entries, for example, by enabling Privileged Executable (PX) permissions, leading to arbitrary code execution attacks. To mitigate such threats, K-Int implements strict policies and write-protects the kernel page table (read-only in the S2PT). Any update to the kernel page table triggers a trap to K-Int, where the modification is validated against the predefined policies. These policies ensure that all non-executable memory pages mapped by the kernel are enforced as Privileged NoneXecute (PXN). Furthermore, they also ensure that kernel page mappings form a directed acyclic graph (DAG) structure and prevent attackers from altering existing mappings to arbitrary non-zero addresses. These enforcements are critical to prevent bypassing the protections enforced by K-Int.

Loadable Kernel Modules. To support loadable kernel modules, K-Int uses public-

key cryptography to ensure the integrity of loaded modules. It relies on a whitelist of valid signatures and keys, which are assumed to be securely sealed in secure storage before the kernel is compromised. In contrast to Linux's built-in module signing infrastructure [2], K-Int minimizes its TCB on handling module loading. It achieves this by delegating non-security-critical tasks like memory allocation to Linux, while retaining security-critical operations such as authentication and relocation within the K-Int. K-Int preserves Linux's functionality while ensuring that only authorized modules can be installed and executed.

K-Int's Limitations. Although K-Int effectively enforces kernel code integrity throughout its lifetime, it still relies on several trusted assumptions that introduce significant limitations and potential vulnerabilities. First, K-Int does not protect critical system registers, allowing an attacker to manipulate register values that control virtual memory and thereby bypass its protection. Second, K-Int does not provide protection for user page tables, leaving them vulnerable to direct manipulation. An attacker could exploit kernel vulnerabilities to alter user page table entries with elevated permissions, enabling attacks such as return-to-user (ret2usr [37]), where user code is executed with kernel privileges. Third, enabling stage 2 paging introduces significant runtime overhead due to additional page walks and increased pressure on the TLB cache, which is a hardware cache commonly employed across system architectures to accelerate page translation. Finally, K-Int's implementation is potentially vulnerable to flaws since it has not been formally verified.

# Chapter 3 Threat Model And Assumptions

We protect the code integrity of the Linux kernel. We assume the system is intially benign but may later be compromised by a remote attacker, including administrators with privileged remote access to the hardware. The attacker may exploit zero-day vulnerabilities in the Linux kernel to gain arbitrary memory write capabilities. Once compromised, the attacker can attempt to overwrite the existing kernel code, emit new code, or manipulate kernel page tables [6, 41] to modify the access permissions or page mapping in page table entries. The attacker may also control devices to perform arbitrary DMA operations or reprogram Arm system registers to manipulate the MMU. In addition, the attacker may install kernel rootkits or launch ret2usr attacks [37] to run malicious code with kernel privileges. Protection against data-only or code-reuse attacks is out of scope. Mechanisms to secure control flow integrity [22, 23, 29] or compartmentalization [51] could be employed to defend against these attacks. Denial of service attacks, side channels, and physical attacks against Linux are excluded from the threat model. We trust the Arm hardware platform, the machine model, the Clang/LLVM toolchain (including IR translation), the Spoq verification framework [50], and the Coq proof checker [4].

13

## Chapter 4 Design

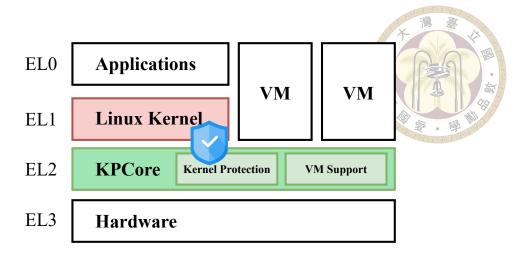

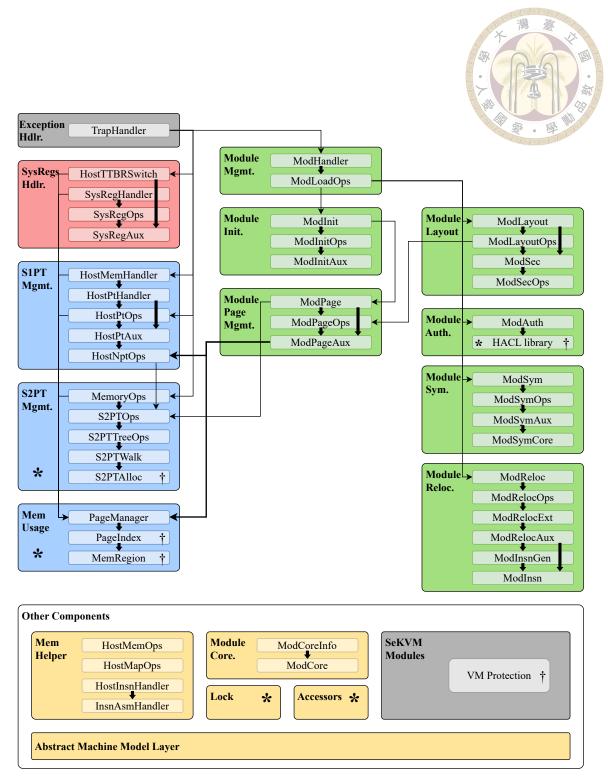

This chapter details the design of our system, which was developed in two primary stages: (1) **SECvma**, an optimized kernel protection framework, and (2) **vSECvma**, its formally verified model. Figure 4.1 illustrates the overall system architecture. KPCore serves as a trusted hypervisor core that enforces Linux kernel code integrity while preserving the functionality of commodity hypervisor such as virtual machine support.

SECvma extends K-Int, addressing its limitations and strengthening its security guarantees to ensure kernel code integrity. However, expanding security enforcement inherently adds runtime overhead. To overcome this, SECvma incorporates a suite of novel optimizations—such as mitigating nested paging overhead and reducing trap costs from register protection—aimed at preserving Linux's performance while upholding its protection guarantees.

The second stage is to formally verify SECvma's TCB (KPCore). Specifically, our primary goal is to prove its functional correctness, demonstrating that the implementation correctly refines a high-level formal specification. To manage the complexity of this task, we adopt modular verification based on the CCALs methodology, in which KPCore is decomposed into multiple independent, layered modules. Functions within these modules can be verified independently, yielding composable proofs that build towards verifying

Figure 4.1: vSECvma System Architecture

the entire TCB.

We build our prototype on the formally verified SeKVM hypervisor, which already employs the same layering strategy. This allows us to leverage SeKVM's existing proof efforts and focus on the novel and extended modules. For these new components, we use the Spoq framework to automate the generation of specifications and proofs. We introduce restructuring strategies to systematically transform SECvma into vSECvma to make the system amenable to automated verification. The final, composed proof establishes the TCB's functional correctness and yields a verified high-level specification, which serves as a trusted foundation for subsequently proving desired invariants. Spoq's specifications are implementation-driven, they will inherently reflect any unintended behaviors present in the code. Nevertheless, our framework still provides fundamental correctness guarantees built upon our machine model and several manually-written specifications. For example, we provide assertions in the machine model to enforce well-formedness conditions such as valid pointer dereferences, checks against out-of-bound memory accesses. In addition, we introduce data abstractions, such as representing S2PTs as well-formed tree structures that preserve essential properties. These guarantees will be formalized and detailed in the following discussion and in Chapter 5.

#### 4.1 Security Enhancements

KPCore, served as SECvma's TCB, builds upon the foundation of K-Int, providing essential kernel protections, such as data execution prevention, kernel code integrity enforcement, and kernel page table protection. It supports loadable kernel modules, enabling users to install authorized drivers as kernel extensions and execute driver code without kernel recompilation. As Section 2.3 mentioned, K-Int's design still relies on certain trusted assumptions that can potentially compromise kernel code integrity. The following sections describe the limitations that SECvma addresses, providing substantially stronger guarantees for maintaining kernel integrity.

#### 4.1.1 System Register Protection

K-Int assumes that system register values are benign. However, malicious manipulation of these registers can compromise kernel code integrity. For instance, an attacker could manipulate the value of the Arm register TTBR1\_EL1, which stores the base address of the kernel page table, to bypass K-Int's enforced kernel page table protection. SECvma addresses this vulnerability by employing a trap-and-emulate approach, preventing malicious manipulation of Arm's system registers that control virtual memory to compromise kernel code integrity.

SECvma categorizes these system registers into four categories shown in Table 4.1. SECvma enforces two policies: *ro-after-boot* and *write-check* against Linux's updates to these system registers. SECvma applies the *write-check* policy to Runtime-Updated Registers. SECvma enforces the *ro-after-boot* policy to registers in the rest of the three

| Category                   | Registers                        |

|----------------------------|----------------------------------|

| VMem Translation Registers | TCR_EL1, SCTLR_EL1, MAIR_EL1     |

| Hardware-Managed Register  | ESR_EL1                          |

| Misc Registers             | AFSR0_EL0, AFSR1_EL1, AMAIR_EL1, |

|                            | CONTEXTIDR_EL1                   |

| Runtime-Updated Registers  | FAR_EL1, TTBR0_EL1, TTBR1_EL1    |

Table 4.1: Virtual Memory System Registers

categories; the values of these registers either are predetermined by the OS kernel and remain unchanged after the kernel boot, or are only updated by hardware during runtime. KPCore enables the TVM bit from Arm's HCR\_EL2 register to trap every Linux's write to the registers in Table 4.1 to EL2. This allows KPCore to transparently interpose every register update and apply the appropriate protection strategies based on the register's category.

#### **4.1.2** Supervisor Mode Execution Prevention

K-Int write-protects the kernel page table and applies privileged non-executable (PXN) permissions to all non-executable memory pages to prevent malicious attackers from executing arbitrary code mapped by it. However, it lacks comprehensive protection for user page tables. A malicious attacker might manipulate user page table entries—for instance, by granting privileged executable (PX) permissions—and subsequently perform attacks such as return-to-user (ret2usr) attacks that execute arbitrary user code with kernel privileges. However, a significant challenge arises from the dynamic allocation of user page tables by the kernel allocator each time a new user process is created. Unlike the kernel page table, which is statically initialized at boot and shared across all processes, directly applying the same monitoring strategy to all user page table updates becomes infeasible with a dynamic kernel allocator. A naive approach would involve SECvma implementing its own page allocator for user page table allocation. However, this would significantly

increase the TCB complexity. Furthermore, directly write-protecting all user page tables would incur an excessive number of traps during frequent updates, leading to severe performance degradation.

To address these limitations, SECvma introduces a novel approach to monitor user page table updates, while incurring minimal trap overhead. To enforce Supervisor Mode Execution Prevention (SMEP) [27], SECvma write-protects the first-level user page tables and enforces the PXN bit, ensuring that all subsequent page table entries inherit PXN protection. Then, SECvma introduces two hypercalls to interpose Linux's user page table allocation and deallocation processes. When the kernel allocates the first-level user page table, it invokes the hypercall, causing a trap to SECvma. SECvma first verifies that the provided page is empty with no prior usage. It then assigns a new usage type (denoted as UPGD) to the page, explicitly marking it as a user page table.

It is known that when a user process is scheduled to run, the scheduler switches the active page table to that of the running process by modifying the TTBR0\_EL1 register. Through the mechanism introduced in Section 4.1.1, SECvma intercepts write accesses to TTBR0\_EL1. Upon such access, SECvma could validate that the target page table has a valid UPGDs identity assigned during the earlier allocation phase. As a result, the host kernel is compelled to invoke the SECvma hypercalls for legitimate page table setup. Otherwise, an invalid page table cannot be installed via TTBR0\_EL1 and used for execution. By doing so, SECvma achieves comprehensive supervisor mode execution prevention.

#### 4.2 Optimization

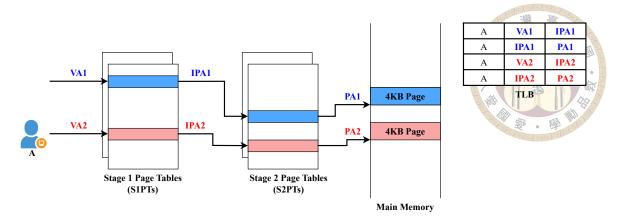

SECvma's design introduces performance overhead to enforce Linux kernel integrity throughout its runtime. SECvma adopts stage 2 paging and applies different permissions based on different memory usage types to protect kernel memory. To achieve memory access control at the finest granularity, SECvma uses the minimal (i.e., 4KB) translation granule in the host stage 2 page table (S2PT) by default. This approach incurs a significant performance slowdown due to the requirement for extra page walks and increased pressure on the TLB cache, as shown example in Figure 4.2a. Additionally, the system register protection also introduces significant overhead. The registers that are frequently runtime-updated by Linux can cause an excessive number of traps to KPCore for validation. We introduce optimizations to mitigate the trade-off caused by these approaches.

**Huge Page Optimization.** As illustrated in Figure 4.2b, we adopt huge page optimization to address the slowdown caused by S2 paging. However, this approach presents several challenges. First, to enforce precise memory access control on huge page mappings, we must ensure that all memory pages within a huge block share the same S2 permissions, thereby preventing unintended permission overlaps with different memory regions. Second, we need to minimize external fragmentation that could arise from the use of huge pages.

KPCore manages S2 mappings with different granularity sizes (e.g., Arm's 4KB, 2MB, and 1GB mappings), determined by the mapped region and its associated memory usage. To effectively apply these optimizations, we modified Linux's linker script to ensure all static memory within kernel binaries (i.e., kernel code and data) is loaded and aligned to 2MB regions during boot. This prevents kernel code and data from co-locating

(a) When stage 2 paging is enabled, both stage 1 (VA2 | IPA2) and stage 2 (IPA2 | PA2) translations are cached in TLB. Using 4KB mappings significant pressure on the TLB cache during runtime.

(b) VA1 and VA2 reside within the contiguous 2MB block (IPA) and share stage 2 permissions, SECvma maps both entries to a single 2MB S2 entry, reducing TLB pressure.

Figure 4.2: Huge Page Optimization.

within the same 2MB huge page, concurrently minimizing external fragmentation in these static areas.

By default, Linux allocates kernel pages from the kernel heap. We cannot directly map heap memory in the host S2PT with huge pages because 4KB pages with different S2 permissions could co-locate within the same huge page. To incorporate huge page optimization for dynamic kernel memory, we introduced a buddy memory allocator to Linux. This allocator is designed to provide 4KB-aligned pages from 2MB-aligned memory pools that are guaranteed to share the same permission in the host S2PT. For instance, the enlight-

ened Linux kernel can allocate page table pages from these specifically managed pools. When handling mapping traps to KPCore, KPCore can then apply the corresponding (e.g., read-only) permissions to these huge mappings.

We further extend huge page optimizations to support 1GB mappings. Currently, 1GB mappings are applied only to memory without specific usage types (i.e., user memory), with an explicit enforcement that no other memory pages with defined usages are co-located within the same 1GB region. These optimizations are transparent to Linux and do not change its page granularity, thus incurring no additional fragmentation or pressure during process creation and caching operations.

By enabling huge page optimizations, we introduce modifications to Linux, such as aligning static memory regions and creating specialized memory pools, with minimal impact on existing Linux's functionality. However, it is important to note that Linux itself may apply optimizations to the S1 mappings. SECvma supports S1 mapping optimizations performed by Linux but prevents attackers from tampering with huge page entries in the S1PTs that potentially lead to privilege escalation and bypass KPCore's preventions.

**System Register Optimization.** As previously discussed, KPCore employs a trapand-emulate mechanism to validate Linux's write accesses to system registers. We analyzed the usage patterns of these system registers across different scenarios and applied optimizations to reduce traps in two main contexts:

Batching System Register Updates: In scenarios where Linux performs multiple system register updates within a single process, KPCore introduces batching optimizations to consolidate these operations into a single hypercall. Rather than trapping and validating each update individually, KPCore validates all updates collectively upon handling the

doi:10.6342/NTU202504620

hypercall. For instance, during process context switches, Linux introduced three updates to replace the stage 1 user and kernel page tables (i.e., TTBR0\_EL1 and TTBR1\_EL1) of the next active process. By batching these updates, SECvma reduces the number of traps to KPCore from multiple individual traps to a single hypercall, reducing overhead during frequent context switches.

Replacing scratch registers: For specific mechanisms and scenarios, we observed that Linux may use system registers as scratchpads for temporary storage. To address the frequent traps caused by system register protection in these cases, we modified Linux to replace the use of such registers with alternative registers while ensuring the modifications do not compromise system behavior or security guarantees. For example, Linux's KPTI [21] implementation uses FAR\_EL1 as scratch registers during kernel/user mode switches [7]. Consequently, the writes to FAR\_EL1 result in traps to KPCore. To avoid the trap, we replaced the write to FAR\_EL1 with TPIDRRO\_EL0. This incurs no safety issue since Linux already uses TPIDRRO\_EL0 as a scratch register. To further guarantee security, before returning to userspace, KPCore zeros the value of TPIDRRO\_EL0 after use.

## 4.3 Adapting KPCore to Spoq Framework

SECvma is prototyped on SeKVM [47, 48], a formally verified KVM-based hypervisor for Arm. Spoq has also evaluated the correctness proofs of SeKVM through its open-source artifact [19]. We reuse and extend SeKVM's verified functionality, including S2PT management, exception handling, and memory usage mechanisms. Building on these components, we apply similar proof strategies to re-verify the extensions introduced by KPCore.

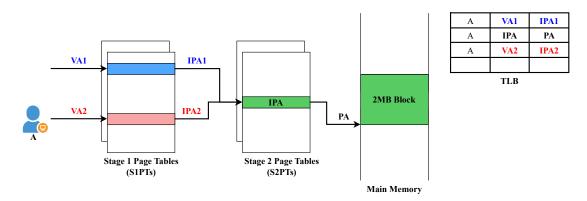

To adapt KPCore to Spoq framework, we first refactor its architecture into Spoq's layered verification model. In this model, functions in higher layers can only invoke functions in lower layers, and not vice versa. For example, the complex call patterns, such as recursion, are prohibited. Moreover, KPCore contains complex routines, such as kernel module loading, that are difficult to verify automatically. To manage these complexities, we applied several restructuring strategies, including encapsulating pointers, modularizing branches and loops, simplifying generated specifications through directives, and introducing manual data abstractions. These adaptations are essential for meeting the requirements of the Spoq framework and, just as importantly, for improving its performance in automatically generating complete specifications and composable proofs for every layer of KPCore.

Type-Aware Pointer Validation. In low-level systems like SECvma, memory pointers are extensively used to access and pass structured data. A key challenge is bridging the semantic gap between typed pointers preserved in the Coq AST and their representation in the machine model. Spoq provides Coq libraries for modeling low-level primitives such as object pointers as (base, ofs) pairs. However, Spoq's layering strategy introduces challenges when pointers are passed across different layers. If a pointer originates in the same or a lower layer, its source can be tracked and verified through the layer's exposed state and invariants. In contrast, when a pointer is passed from an upper layer, Spoq cannot assume what the pointer references. To ensure soundness, Spoq generates specifications using case analysis over all modeled object pointers and constructs conditional branches to check whether the (base, ofs) falls within a valid object footprint. If none of the cases match when the pointer source is revealed, the pointer evaluates to None in the specification, and any subsequent operations on it will raise a fault in Spoq, exposing a potential

Figure 4.3: Encapsulating raw pointers from higher-layers with a getter wrapper.

bug. While this approach ensures correctness, it leads to bloated specifications and slows down proof automation.

To address this, we encapsulate the pointers from upper layers within our machine model and mediate them through type-specific "getter" functions. As illustrated in Figure 4.3, a higher-layer function constructs a pointer \*M and passes it to a lower layer for further use. Since the low-level specification represents such pointers generically as Ptr, without type information, we introduce a getter get\_mod() to mediate these accesses. However, we cannot simply assume that the pointer is valid (\*M) and of the correct type (struct mod). It is unsafe, as an invalid pointer passed from the upper layer can cause the proof to succeed under a false assumption. Instead, we introduce assertions using the rely construct, previously leveraged in SeKVM's correctness verification with Spoq.

The rely construct is implemented in Coq as a pattern-matching expression (match ... with) that checks the validity of conditions. These assertions are automatically validated by Spoq through symbolic execution with the Z3 SMT solver during the generation of high-level specifications. If a condition evaluates to False, the specification for that execution path collapses to None, meaning that the subsequent function behavior is not executed. As a result, when an expected execution path incorrectly leads to None, it immediately exposes a potential bug in the implementation.

Modularizing Branches and Loops. In processes such as kernel module load-

ing, several functions exhibit intricate control flow, involving deeply nested branches and loops with non-trivial logic. These structures often lead to highly convoluted specifications generated by Spoq, potentially overwhelming its auto-generated proofs and necessitating manual intervention to complete the verification. To mitigate this, we refactored several functions by modularizing complex branches and loops. For example, as illustrated in Listing 1, we addressed functions with intricate branching and duplicated conditions by extracting the logic for dynamically constructing function arguments into dedicated getter functions. Instead of directly passing different arguments within each branch, we factored out argument construction into a separate get arg0 function. These getter functions calculate and return the necessary structured arguments, which are then passed to a unified function call. As a result, the switch-case structure becomes more concise to select the function to call, while the argument retrieval is encapsulated in a single function wrapper. Similarly, for loops with complex bodies, we encapsulated the loop's logic into multiple helper functions at a lower layer, so that we can significantly facilitate Spoq's auto-generated proof templates, allowing them to automatically prove the containing function with minimal manual effort.

```

switch (cond) {

case A:

funcA(a, ...)

case B:

funcB(b, ...)

case C:

funcB(c, ...)

case D:

funcA(b, ...)

...

}

arg0 = get_arg0(cond);

switch (cond) {

case A:

case D:

funcA(arg0, ...)

case C:

funcB(arg0, ...)

...

}

```

Listing 1: Modularizing complex branch logic.

**Simplifying Specifications for Scalable Proofs.** As previously discussed, the high-level specifications generated by Spoq are self-contained, derived by unfolding lower-layer specifications that contain no further calls to lower layers. However, for a large-scale

system like SECvma, these specifications often remain too complex to prove efficiently. This is because fully unfolding all low-level details can lead to a combinatorial explosion of states that overwhelm automated theorem provers. To manage this complexity, we employ two key, complementary strategies, depending on how a function is used across the system:

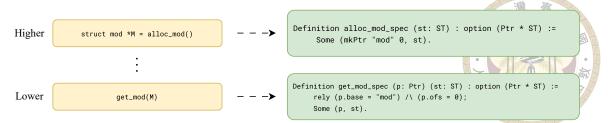

- Manual Abstract Specifications: For low-level and widely reused functions, such as general-purpose helpers that involve complex routines, we manually write abstract high-level specifications rather than relying solely on Spoq-generated ones. For example, stage 2 paging is widely used by higher-layer modules to enforce memory protection, yet its implementation involves intricate routines that traverse multi-level page tables to query or update entries. To manage this complexity, we manually define an abstract specification that captures the function's intended behavior and then construct refinement relations to formally prove that the low-level implementation correctly refines this specification. By doing so, we can focus on verifying essential properties without getting bogged down in implementation details. However, manually written specifications carry the inherent risk of containing errors by human efforts, which could compromise the soundness of the overall proof.

- Selective Use of NoUnfold: For higher-layer functions that are not helpers but instead provide relatively complete and self-contained functionality, we selectively apply the NoUnfold directive to prevent their high-level specifications from being automatically unfolded during proof construction. A prime example is the module loading process, which consists of sequential subprocesses like symbol resolution and relocation. Since each subprocess has been independently verified, operates

with minimal shared state, and exposes a well-defined interface, higher layers can safely invoke them as trusted, opaque operations without re-verifying their underlying implementation. This abstraction reduces proof size and complexity. To mitigate the risk of masking behaviors critical for system-wide reasoning, we apply NoUnfold conservatively and only when such structural properties are present.

These two approaches help us manage proof complexity in practice and were also applied in SeKVM's correctness proof. While each carries potential risks to soundness, we apply them conservatively and only when necessary, making them a practical compromise for reasoning about a full system implementation.

#### 4.3.1 Layered Design

Figure 4.4 illustrates the layered design of KPCore. Building on SeKVM, KPCore reuses and extends SeKVM's existing modules. It also introduces new modules to enforce kernel code integrity. The newly introduced modules are organized into three main security components: **Kernel Memory Protection**, **Secure Module Loading**, and **System Register Protection**. Each component is further decomposed into multiple layers, with each layer encapsulating a group of functions responsible for specific tasks. The top-layer module, TrapHandler, is responsible for handling exceptions and hypercalls (as summarized in Table 4.2) from the host kernel. It then dispatches these events by invoking the top-level interfaces exposed by the three primary security components.

**Kernel Memory Protection.** KPCore provides kernel memory protection through two key modules: HostMemHandler and MemoryOps. These modules are responsible for handling stage 2 permission faults and stage 2 page faults caused by the host, respectively.

Since KPCore write-protects the stage 1 page table to monitor updates by the Linux host, any write access to these page tables will trigger a permission fault trap to KPCore, which is captured by TrapHandler. TrapHandler then invokes HostMemHandler to process the fault. HostMemHandler retrieves relevant information from HostMemOps, a lower layer providing helper functions related to memory operations, such as fetching the faulting instruction, and the page table entry being written. Concurrently, it tracks the memory usage of the faulting address by invoking PageManager, determining whether it belongs to a kernel or user page table. According to the memory usage, it dispatches the request to the appropriate handler within HostPtHandler. HostPtHandler then interprets the operation performed by the host (i.e., mapping, unmapping, or updating a page table entry) and further delegates the task to functions in HostPtOps and HostPtAux. If the stage 1 page table operation is validated, HostNptOps is invoked to perform the corresponding stage 2 remapping, ensuring the nested page tables remain synchronized with the updated memory usage and its associated permissions. HostInsnHandler and HostInsnAsmHandler responsible to emulate the instructions issued by the host that caused the trap. Between this, HostMapOps is called by upper layers to perform map permission checks and updates as needed. To support user page table updates, KPCore introduces two hypercall handlers alloc elo pgd and free elo pgd in HostPtOps. These are triggered by TrapHandler when the host explicitly requests allocation or deallocation of user page tables.

When a stage 2 page fault occurs, MemoryOps is responsible for handling the fault. It first invokes PageManager and HostMapOps to track the memory usage of the faulting address, retrieving information to determine the final mapped permission and the mapping level. Subsequently, S2PTOps and S2PTTreeOps are triggered for handling stage 2 page table updates. During this process, S2PTWalk is used to traverse the stage 2 page table

across multiple levels. If any intermediate page table is missing, S2PTAlloc is responsible for managing the allocation for the stage 2 page table.

Secure Module Loading. KPCore exposes three hypercalls, mod auth, free init. and free\_module, to support dynamic kernel module loading. These hypercalls are invoked by the host kernel during module installation or removal, intercepted by TrapHandler, and dispatched to corresponding handlers in the ModHandler layer. To support secure module loading, KPCore adopts a layered design that divides the loading process into multiple stages. Each stage exposes a top-level interface, invoked by ModLoadOps, which coordinates a top-down approach across submodules responsible for specific tasks, including module initialization, authentication, and symbol resolution with relocation. The process begins with the ModInit\* layer, which collects and organizes essential metadata passed from the kernel. Next, similar to the Linux kernel, the ModLayout layer constructs the module's memory layout, such as handling text sections, read-only sections, and other segments. These sections are then stacked in preparation for signature verification. Then, ModAuth performs module authentication to the stacked module content. Once authorized, KPCore proceeds to the ModSym\* layer to resolve undefined symbols. Then, the ModReloc\* layer applies relocations to patch the module contents according to the resolved symbols. The lower-level module ModCore provides reusable utilities and helpers to support the various stages of this process. Meanwhile, ModCoreInfo stores persistent information about the loaded module, such as the address of its protected sections and its exported symbol table. ModPage\* manages both stage 1 and stage 2 page-level operations. For example, before authentication, KPCore write-protects the module pages to prevent any unauthorized access by the host. Only after the module is successfully authenticated does KPCore allow it to be installed and executed.

| <pre>mod_auth(info, list, size)</pre> | X XX |

|---------------------------------------|------|

| <pre>free_init(mod_id)</pre>          |      |

| <pre>free_module(mod_id)</pre>        |      |

| <pre>opt_switch_mm(ttbr0, asid)</pre> |      |

| alloc_el0_pgd(addr)                   |      |

| free_el0_pgd(addr)                    |      |

Table 4.2: Kernel Protection Hypercalls

System Register Protection. KPCore interposes on every host write to system registers listed in Table 4.1. SysRegHandler handles the fault and only permits writes to registers categorized as *Runtime-Updated Registers*, rejecting all other accesses. It then delegates to the corresponding register handlers defined in SysRegOps. SysRegOps invoke PageManager and SysRegAux to validate the written value and emulate the register update. As discussed in Section 4.2, KPCore also exposes a hypercall opt\_switch\_mm for batching register updates during process context switches. HostTTBRSwitch handles this hypercall, batching updates to the user and kernel page table base registers. All values are validated without compromising the functionality of context switches.

Figure 4.4: KPCore Layered Design. (1) Blue: Kernel Memory Protection. (2) Green: Secure Module Loading. (3) Red: System Register Protection. (4) Yellow: Common/Helper/Machine Model Modules. (5) Grey and modules marked with \*: SeKVM's existing modules [48] and the HACL cryptographic library [74]. † indicates the original implementations are fully reused without modification.

# Chapter 5 Verifying Functional Correctness of KPCore

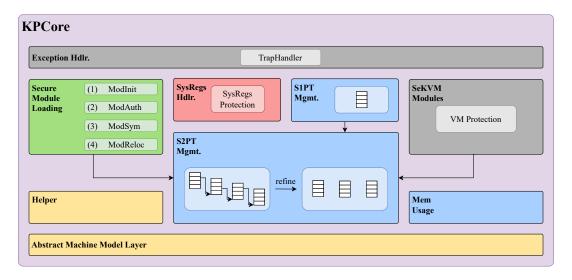

In this chapter, we present the methodologies used to prove the functional correctness of KPCore. Figure 5.1 illustrates the main security components of KPCore, including the paging subsystem, the module loading subsystem, the system register handler, and existing SeKVM modules for VM protection. These components were built on top of the abstract machine model. At the top layer, the exception handler served as the entry point to KPCore, handling faults and hypercalls and delegating them to the corresponding security components. Among these, the SeKVM modules dedicated to VM protection were reused without modification and were treated as trusted. We therefore focused our verification efforts on the remaining modules that are dedicated to host protection and proved their functional correctness.

In our implementation, we extended SeKVM's stage 2 page table (S2PT) management beyond the original 4 KB and 2 MB mappings to support 1 GB pages, along with additional permission configurations to enforce host memory protection. However, the hardware-defined semantics of multi-level page tables, when exposed to higher layers, could further complicate the specifications and dramatically increase the complexity of the proof. To simplify the proof, we proved the correctness of our extended S2PT man-

doi:10.6342/NTU202504620

agement by adapting SeKVM's page table abstraction strategy. Specifically, we showed that the multi-level page table, represented as a tree structure in the low-level specification, refines multiple flat maps in the high-level specification.

The module loading subsystem and stage 1 page table management (S1PT) were built on top of the S2PT management, leveraging its verified high-level abstract interface. We were therefore able to rely on this simplified abstraction and focus our verification efforts on proving the correctness of their main routines. We did not introduce additional data abstractions for S1PTs; instead we relied on Spoq to directly generate their specifications that capture the intended behavior of their functions, since S1PT component already reside at a higher layer and are not extensively used by other components. For the system register handler, the restructuring strategies described in Section 4.3 were sufficient for Spoq to generate specifications and proofs establishing functional correctness automatically.

In the remainder of this chapter, we describe our machine model layer (Section 5.1), the verification of the paging subsystem (Section 5.2) and the module loading subsystem (Section 5.3), the system invariants ensured by correctness proofs (Section 5.4), and the limitations we encountered when using Spoq (Section 5.5).

Figure 5.1: Security Components in KPCore

## 5.1 Abstract Machine Model Layer

The abstract machine model layer served as the trusted layer upon which all other modules were built. Following the methodology of Spoq, we modeled the low-level primitives essential for KPCore, such as memory load/store, register operations, and memory pointer accesses, using the Coq libraries provided by Spoq. To support CPU-local concurrency reasoning within our model, we incorporated key architectural ideas introduced by Spoq. This involved manually defining concurrency-related structures such as an event log and an oracle. This event-based approach, which was similar to methods used in prior work [31], enabled us to reason about multi-core execution by analyzing individual CPU behaviors, thereby laying the groundwork for composing these proofs to eventually verify global invariants under a sequential consistency memory model.

## 5.2 Functional Correctness of Page Tables

We formally verified the functional correctness of vSECvma's page table management. vSECvma's page table management architecture encompassed both stage 1 and stage 2 mappings. The former, residing in a higher layer, was built upon and leveraged the verified layer functions exposed by the S2PT modules. To handle S1PT fault traps from the host, KPCore validated and updated the S1PTs according to the policies described in Section 2.3 and Section 4.1.2, updating the corresponding S2 mapping when necessary. The S2PT management included walking the S2PT, allocating S2PT pages as needed, and mapping entries in S2PT at the specified level with appropriate permission configurations.

#### **5.2.1** Stage 2 Page Table Management

As discussed earlier, Spoq evaluated SeKVM's implementation and proved the functional correctness of its S2PT management. Building on this, we reused the S2PT management proof from Spoq's artifact and extended it to support new functionalities introduced by SECvma. Similar to SeKVM, we modeled the S2PT as a four-level hierarchical tree (i.e., pgd, pud, pmd, and pte) within the machine model layer. SeKVM ensured correct S2PT management and supported mappings with page sizes of 4KB and 2MB. To incorporate the performance optimizations in SECvma from Section 4.2, we extended this support to include 1GB mappings in the S2PT.

Modeling the S2PT as a tree structure made its specifications inherently complex. This complexity, in turn, made proving functional correctness more challenging. Adding 1 GB mappings further increased this challenge, especially when generating comprehensive proofs across the different layers. To simplify the proof, we followed SeKVM's approach: we proved that the multi-level page table, represented as a tree structure in the low-level specification, refines flat map representations in the high-level specifications, as shown in Figure 5.1. We reused the original refinement proof strategy. However, extending it to support 1GB mappings still posed challenges, especially in ensuring several properties within the refinement.

Listing 2 illustrates the high-level specification for handling S2 mappings, where the S2PT is represented as multiple abstract flat maps. In our machine model, npt serves as a lock-synchronized object that models the host S2PT. We abstract three flat maps (i.e., npt.lv1pt, npt.lv2pt, and npt.lv3pt) representing 1GB, 2MB, and 4KB mappings, respectively. All S2PT queries and updates in the low-level machine model ultimately

```

1 (* Allocate new page table pages from the npt.pool *)

2 Definition alloc_pt (npt : S2PT) : option S2PT := ...

(* Validity checks for overlapping mappings across different granularity lev

Definition is_valid_l1 (addr : Z) : Prop :=

forall (addr': Z), (addr[47:30] = addr'[47:30] ->

(npt.lv2pt # addr'[47:21] = None /\ npt.lv3pt # addr'[47:12] = None))

9 Definition s2pt_set (addr: Z) (level: Z) (pte: Z) (npt: S2PT) : option S2PT :=

let L1_index := addr[47:30] in

11

let L2_index := addr[47:21] in

12

let L3_index := addr[47:12] in

13

14

npt <- alloc_pt npt;</pre>

15

if level =? 1 then

16

rely (is_huge pte = true /\ is_valid_l1 addr);

Some (npt.lv1pt # L1_index <- pte) else</pre>

17

18

19

if level =? 2 then

rely (is_huge pte = true /\ is_valid_12 addr);

20

Some (npt.lv1pt # L2_index <- pte)

22

rely (is_valid_13 addr);

23

Some (npt.lv3pt # L3_index <- pte).

24

```

Listing 2: s2pt\_set models the operation for setting an S2PT entry. The function takes the intermediate physical address (addr), the target mapping level (level for 1GB, 2MB, or 4KB), the page table entry (pte) to be set, and the abstract object npt, which represents the host S2PT.

refine simple load/store operations on these flat maps, thereby simplifying higher-level proofs that reason about the S2PT. Each map is indexed by the specific range of the intermediate physical address and loads/stores the corresponding page table entry from/to the corresponding abstract map.

s2pt\_set. As shown in Listing 2, s2pt\_set (line 9) models the operation for setting an S2PT entry. It first invokes alloc\_pt (line 2, 15) to abstractly represent the allocation of necessary page table pages from npt.pool. Following this, s2pt\_set proceeds to handle the S2 mapping based on the target level. The function also includes rely assertions (line 17, 20, 23) that guarantee no overlapping mappings across different granularity levels (is\_valid\_lx). If the assertions fail, the function returns None without performing updates. In SeKVM, it is ensured that if a 2MB mapping exists, then no 4KB mappings exist within that same huge block. Likewise, by extending the support to 1GB mappings,

is\_valid\_11 enforced that neither 4KB nor 2MB mappings can exist within a 1GB-mapped region (line 5), and conversely, finer-grained mappings must not overlap with existing 1GB regions.

We constructed refinement relations to show that the multi-level page table refines the abstract flat maps. Several key properties are inherently validated by the refinement proof itself, ensuring that the structure is a well-formed tree and maintained in a hierarchical order. Within the refinement relations, the following properties are ensured: (1) each lower-level page table page is uniquely referenced by a single parent entry; (2) page tables allocated from the page pool are always free and empty; and (3) if a higher-level non-leaf entry exists, then there must have been, or currently exists, a corresponding next-level table entry or leaf entry. Property (1) rules out aliasing, i.e., where two distinct parent entries point to the same lower-level page table, which would cause unintended sharing of page table nodes. Property (2) guarantees that only a fresh page table can be inserted during allocation, meaning the page table has not already been referenced elsewhere. Properties (1) and (2) together ensure that the multi-level page table maintains a tree structure. Property (3) maintains hierarchical order: every non-leaf entry points only to the next lower-level page table or to a leaf entry, but not otherwise.

Listing 5.2 illustrates the refinement relations used to enforce these properties. To support 1GB mappings, we extended two additional refinement relations, as shown in Listing 5.2b and Listing 5.2c.

P1, P2. The P1 states that when an addr is accessed in npt.parent\_pool, the entry is either empty (val = 0) or allocated from the child pool. In the latter case, there exist a unique inverse mapping inv\_map that maps the page back to exactly one parent addr. The P2 states that unused pages in the child pool remain empty.

```

P1:

exists (inv_map: Z -> Z),

forall addr,

let val := npt.parent_pool[addr] in

let base := npt.child_pool_base in

let used := npt.child_pool_used in

val = 0 \/

(base <= val <= base + used * PAGE_SIZE) /\ (inv_map val = addr);

P2:

forall addr,

let base := npt.child_pool_base in

let used := npt.child_pool_used in

addr >= base + used * PAGE_SIZE -> npt.child_pool[addr] = 0;

```

#### (a) P1 and P2 relations.

```

P3: (* Omitted for brevity *)

P3_lv1:

forall pud,

is_tbl pud = true ->

exists addr' pmd' pte',

pgd_idx[addr] = pgd_idx[addr'] //

pud_idx[addr] = pud_idx[addr'] //

pmd' = npt.pmd # (pmd_idx[addr'] + pud) //

is_huge pmd' = true //

(is_tbl pmd' = true

// pte' = npt.pte # (pte_idx[addr'] + pmd')

// pte' <> 0);

```

#### (b) P3 relation.

```

lvXpt_rel: (* Omitted for brevity *)

lv1pt_rel:

let hnpt := (* S2PT in high spec *) in

let lnpt := (* S2PT in low spec*) in

forall addr pud,

hnpt.lv1pt # addr[47:30] = Some pud <->

let pgd := lnpt.pgd # (pgd_idx[addr] + lnpt.ttbr) in

pgd <> 0 /\ pud = lnpt.pud # (pud_idx[addr] + pgd)

/\ is_huge pud = true;

```

#### (c) lvXpt\_rel relation.

Listing 5.2: Refinement relations used in the proof: (a) **P1** and **P2** enforces properties (1) and (2); (b) **P3** enforces property (3); and (c) **lvXpt\_rel** connects entries in the high-level flat map to their corresponding multi-level page walks in the low-level specification. (b) and (c) indicate only the added relations for 1GB mappings, with other cases omitted for brevity.

**P3**, **P3\_lv1**. In the original proof, the P3 relation ensured that if a level-2 entry (pmd) was a table, it exclusively led to a valid pte leaf entry. With 1GB mapping support, however, a level-1 entry (pud) could reference either a huge page or another table. The P3\_lv1

relation captures this behavior: if a level-1 entry (pud) is a table (is\_tbl pud = true), then it must lead to either a 2MB huge block (is\_huge pmd' = true) or a valid level-3 page table (is\_tbl pmd' = true) that contains at least one valid 4KB page (pte' <> 0).

**lv1pt\_rel.** The lv1pt\_rel relation connects the high-level flat map to the low-level specification. Specifically, if a 1GB mapping exists at a given address in hnpt.lv1pt, then a level-by-level traversal in the low-level specification from the pgd to the pud must yield a pud entry marked as a 1GB huge block (is\_huge pud = true).

#### **5.2.2** Stage 1 Page Table Management

S1PT management was built upon the established and formally verified S2PT management layers, allowing S1PT operations to directly invoke the simplified high-level specifications exposed by the S2PT management as needed. By formally proving the functional correctness of S1PT management, we transformed its implementation into high-level specifications in Coq.

However, modeling the S1PT within the machine model layer, using the same tree-structural approach as S2PT, was challenging. First, KPCore did not manage memory pools for S1PT. Instead, these pages were dynamically allocated by the untrusted kernel allocator. As a result, KPCore had no control or visibility over how memory was allocated or reused, making it infeasible to enforce precise structural constraints in the same manner as S2PT. Second, the host kernel could also dynamically map memory using various granularities (e.g., 1GB, 2MB, or 4KB) at runtime, for example, to optimize performance or maintain memory efficiency. Unlike a static structure, S1PTs grew dynamically without

a fixed layout.

From a memory perspective, S1PT updates could be treated as reads or writes to arbitrary 8-byte-aligned physical memory addresses. Accordingly, we modeled S1PTs as a flat memory region (i.e., Map.t Z in Coq), where updates were interpreted as array modifications, similar to the high-level specifications of S2PTs, as illustrated in Figure 5.1. This simplified model allowed us to reason about the S1PTs as simple memory updates exposed to higher-level specifications. KPCore implements a lock for managing the write-protected S1PTs. This lock is required when handling permission fault traps from the host and during updates. Since the host cannot directly modify the protected page tables, we model S1PTs as lock-synchronized objects, with all updates performed under this lock to maintain consistency.

## 5.3 Functional Correctness of Secure Module Loading

SECvma adopted public-key cryptography to authenticate loaded kernel modules, ensuring that only authorized modules could be installed and executed. While SECvma's design migrated security-critical tasks from the kernel to KPCore, much of the inherent complexity of these operations was preserved within KPCore to maintain existing system properties and Linux features. This significantly increased the difficulty of formally proving the functional correctness of the module loading implementation.

We applied the design discussed in Section 4.3 to simplify the implementation and ultimately proved the functional correctness of secure module loading. By simplifications, we refer to modifications made to facilitate proof automation rather than changes to functionality. In the complex process of module loading, it was evident that it comprised many

independent tasks with limited interdependencies regarding their properties. To manage this complexity, we decomposed the module loading process into distinct sub-processes, each fulfilling a specific role. We identified functions that represented independent tasks or were not common helper routines, then applied "Hint NoUnfold" directive to simplify Spoq's generated high-level specifications. This allowed higher-layer modules to call these functions directly instead of unfolding the exposed abstract high-level interface, as discussed earlier. The module loading routine was decomposed into three key stages:

(1) Module Initialization, (2) Module Authentication, and (3) Symbol Resolution and Relocation.

Module Initialization. This stage consists of two main tasks: (1) memory remapping and (2) parsing and preparing module loading information. The kernel module is an

ELF file that contains an ELF header and a section header table describing the module's

layout and metadata, followed by the main contents such as code and data sections. Since