國立臺灣大學電機資訊學院光電工程學研究所

碩士論文

Graduate Institute of Photonics and Optoelectronics

College of Electrical Engineering and Computer Science

National Taiwan University

Master's Thesis

氧化鋯與氧化鎵穿隧奈米結構載子傳輸分析

Carrier Transport Analyses of  $\text{ZrO}_x/\text{GaO}_x$  Tunneling

Nanostructure

林柏宇

Bo-Yu Lin

指導教授：彭隆瀚 博士

Advisor: Lung-Han Peng, Ph.D.

中華民國 114 年 6 月

June, 2025

國立臺灣大學碩士學位論文

口試委員會審定書

MASTER'S THESIS ACCEPTANCE CERTIFICATE

NATIONAL TAIWAN UNIVERSITY

氧化鋯與氧化鎵穿隧奈米結構之載子傳輸分析

Carrier Transport Analyses of ZrO<sub>x</sub>/GaO<sub>x</sub> Tunneling

Nanostructure

本論文係林柏宇君（學號 R11941091）在國立臺灣大學光電工程

學研究所完成之碩士學位論文，於民國 114 年 6 月 26 日承下列考試委

員審查通過及口試及格，特此證明

The undersigned, appointed by the Graduate Institute of Photonics and Optoelectronics, on 26 June 2025 have examined a Master's thesis entitled above presented by BO-YU LIN (student ID: R11941091) candidate and hereby certify that it is worthy of acceptance.

口試委員 Oral examination committee:

(指導教授 Advisor)

彭隆漪 李致貴 葉有庭

王維新

吳育任

所長 Director: \_\_\_\_\_

# 摘要

本研究製作以氧化鋯( $ZrO_2$ )與氧化鎵( $Ga_2O_3$ )為主體之穿隧奈米結構(Tunneling Nanostructure)元件，並於非對稱雙能障量子井結構(Double Barrier Quantum Well, DBQW)中，探討載子穿隧傳輸機制與電性特徵。採用垂直堆疊之多層結構，將氧化鋯、氧化鎵與氧化銦錫(Indium Tin Oxide, ITO)等薄膜組成主體，並以氧化鎵包覆側壁，以有效抑制側向漏電流並提升垂直導電特性。元件製程採用濕蝕刻技術，成功製作最小直徑為5微米之元件，並於皮安培(pA)電流等級下觀察到階梯狀之穿隧電流特徵。

本研究展示準束縛態能階對齊條件下之穿隧行為；然而於陷阱密度較高之元件中，則觀察到其導電特性主要受到陷阱輔助穿隧(Trap-Assisted Tunneling, TAT)機制影響，與穿隧特性表現存在顯著差異。為深入探討傳輸行為，吾人應用熱發射(Thermionic Emission)理論評估材料介面間之能障高度，並以轉移矩陣法(Transfer Matrix Method, TMM)建立穿透係數模型，模擬其於不同電場條件下之變化，據以進行理論與實驗之對應分析與驗證。

# Abstract

This study presents a tunneling nanostructure device, primarily composed of zirconium oxide ( $ZrO_2$ ) and gallium oxide ( $Ga_2O_3$ ), and implemented in an asymmetric double barrier quantum well (DBQW) structure, to analyze carrier tunneling transport mechanisms and electrical characteristics. The device adopts a vertically stacked multilayer architecture comprising  $ZrO_2$ ,  $Ga_2O_3$ , and indium tin oxide (ITO) thin films. Sidewalls passivation with  $Ga_2O_3$  effectively suppresses lateral leakage currents and enhances vertical conduction. Utilizing wet etching techniques, devices with a minimum diameter of  $5\text{ }\mu\text{m}$  were successfully fabricated, exhibiting step-like tunneling current features at the picoampere (pA) level.

The observed stepwise current behavior is attributed to tunneling under aligned quasi-bound state conditions. However, in devices with higher trap densities, conduction characteristics were predominantly governed by trap-assisted tunneling (TAT), deviating significantly from ideal tunneling behavior. To further elucidate the transport mechanisms, thermionic emission theory was employed to extract interfacial barrier heights, and a transmission coefficient model was developed using the transfer matrix method (TMM) to simulate field-dependent variations. Theoretical analyses were correlated with experimental results for comprehensive validation.

# 目次

|                                           |      |

|-------------------------------------------|------|

| 摘要.....                                   | I    |

| Abstract .....                            | II   |

| 目次.....                                   | III  |

| 圖次.....                                   | V    |

| 表次.....                                   | VIII |

| 第一章 緒論.....                               | 1    |

| 1.1 簡介 .....                              | 1    |

| 1.2 研究動機與目的 .....                         | 4    |

| 1.3 論文內容概述 .....                          | 5    |

| 第二章 氧化鎵／氧化鋯穿隧二極體之理論介紹 .....               | 7    |

| 2.1 氧化鎵與氧化鋯材料特性 .....                     | 7    |

| 2.2 薄膜導電電流機制 (Conduction mechanisms)..... | 14   |

| 2.3 共振穿隧式二極體之理論介紹 .....                   | 18   |

| 第三章 雙能障之穿隧奈米結構製作 .....                    | 26   |

| 3.1 滅鍍技術 .....                            | 26   |

| 3.2 微影製程與濕蝕刻技術 .....                      | 28   |

| 3.3 樣品設計 .....                            | 29   |

| 3.4 穿隧奈米結構製程流程 .....                      | 31   |

|                             |    |

|-----------------------------|----|

| 第四章 穿隧奈米結構元件電性量測與模擬結果 ..... | 38 |

| 4.1 電流電壓量測系統簡介 .....        | 38 |

| 4.2 材料介面能障高度分析 .....        | 39 |

| 4.3 穿隧奈米結構電性分析與穿透係數擬合 ..... | 48 |

| 4.4 電場方向之陷阱輔助穿隧行為分析 .....   | 56 |

| 第五章 結論與未來展望 .....           | 67 |

| 5.1 結論 .....                | 67 |

| 5.2 未來展望 .....              | 69 |

| 參考文獻.....                   | 72 |

| 補充資料.....                   | 75 |

# 圖次

|                                                                   |    |

|-------------------------------------------------------------------|----|

| 圖 1.1 處理器性能演變，包含電晶體數量、核心數量、功耗、CPU 時脈、快取記憶體速度 <sup>[1]</sup> ..... | 2  |

| 圖 1.2 不同元件在相同的高電壓/高電流下之功耗比較 <sup>[9]</sup> .....                  | 4  |

| 圖 2.1 不同基板溫度對氧化鋁薄膜之影響 <sup>[11]</sup> .....                       | 7  |

| 圖 2.2 (a) 氩氣與氧氣比例 0% 之氧化鋁薄膜 (b) 氩氣與氧氣比例 20% 之氧化鋁薄膜 .....          | 9  |

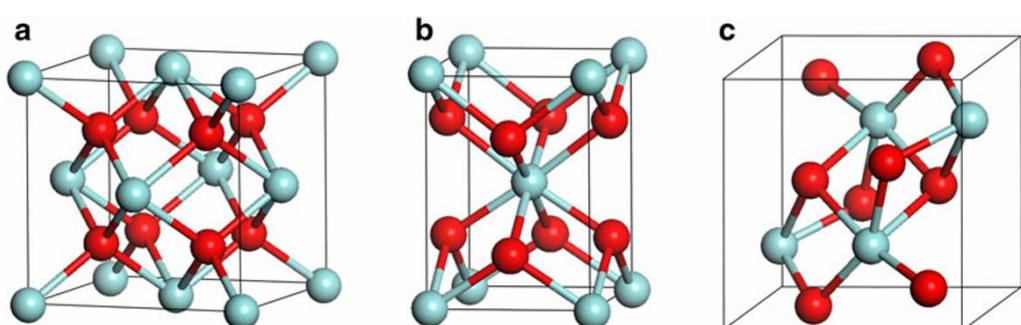

| 圖 2.3 氧化鋯不同晶相結構(a)立方相(b)四方相(c)單斜相 <sup>[13]</sup> .....           | 10 |

| 圖 2.4 非晶相氧化鋯在室溫下之極化-電場特性 <sup>[14]</sup> .....                    | 11 |

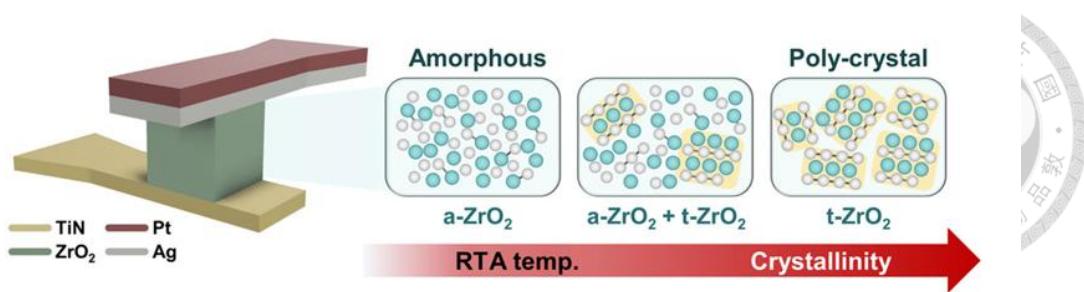

| 圖 2.5 快速熱退火形成多晶相之氧化鋯 .....                                        | 12 |

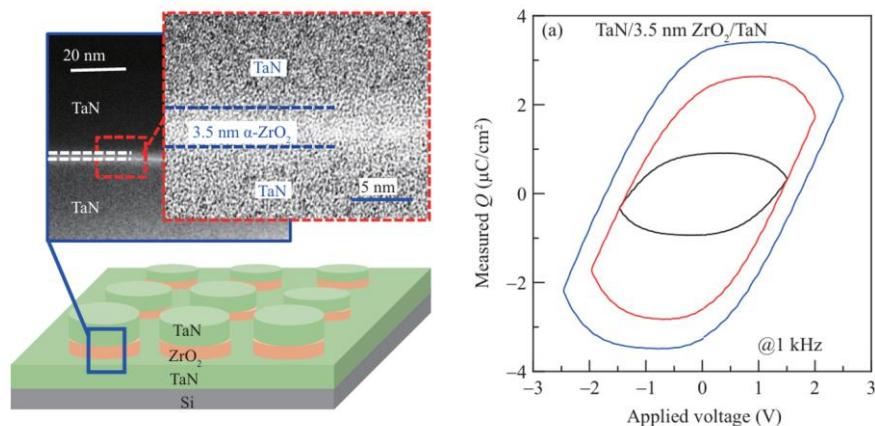

| 圖 2.6 (a)元件結構示意圖 (b)氧化鋯對稱結構之電流-電壓特性 .....                         | 12 |

| 圖 2.7 (a)低氧氣比例之氧化鋯薄膜 (b)高氧氣比例之氧化鋯薄膜 ...                           | 13 |

| 圖 2.8 薄膜導電電流機制 <sup>[17]</sup> .....                              | 15 |

| 圖 2.9 金屬/絕緣層/半導體在熱發射效應之能階圖 <sup>[16]</sup> .....                  | 17 |

| 圖 2.10 陷阱輔助穿隧機制示意圖 <sup>[18]</sup> .....                          | 18 |

| 圖 2.11 共振穿隧二極體原理示意圖 <sup>[20]</sup> .....                         | 20 |

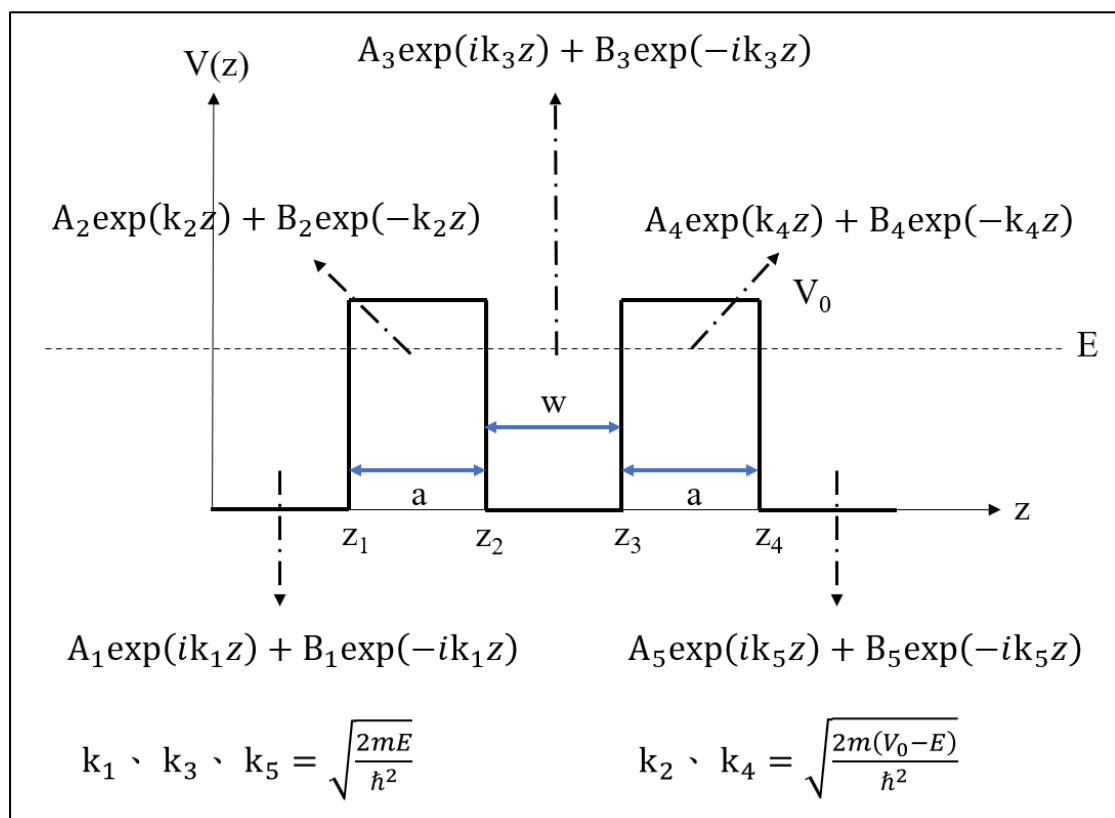

| 圖 2.12 電子波函數在單一能障結構中每個區域之一般解 .....                                | 22 |

| 圖 2.13 電子波函數在雙能障量子井結構中每個區域之一般解 .....                              | 24 |

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| 圖 3.1 磁控射頻濺鍍機原理示意圖 <sup>[22]</sup> .....                                                          | 27 |

| 圖 3.2 絶緣層包覆元件電流比較 .....                                                                           | 30 |

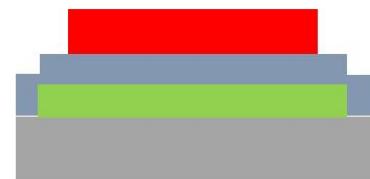

| 圖 3.3 底層金屬鎔製程流程 .....                                                                             | 32 |

| 圖 3.4 蝕刻絕緣層製程流程 .....                                                                             | 34 |

| 圖 3.5 蝏刻微米孔洞製程流程 .....                                                                            | 35 |

| 圖 3.6 濺鍍微米柱製程流程 .....                                                                             | 36 |

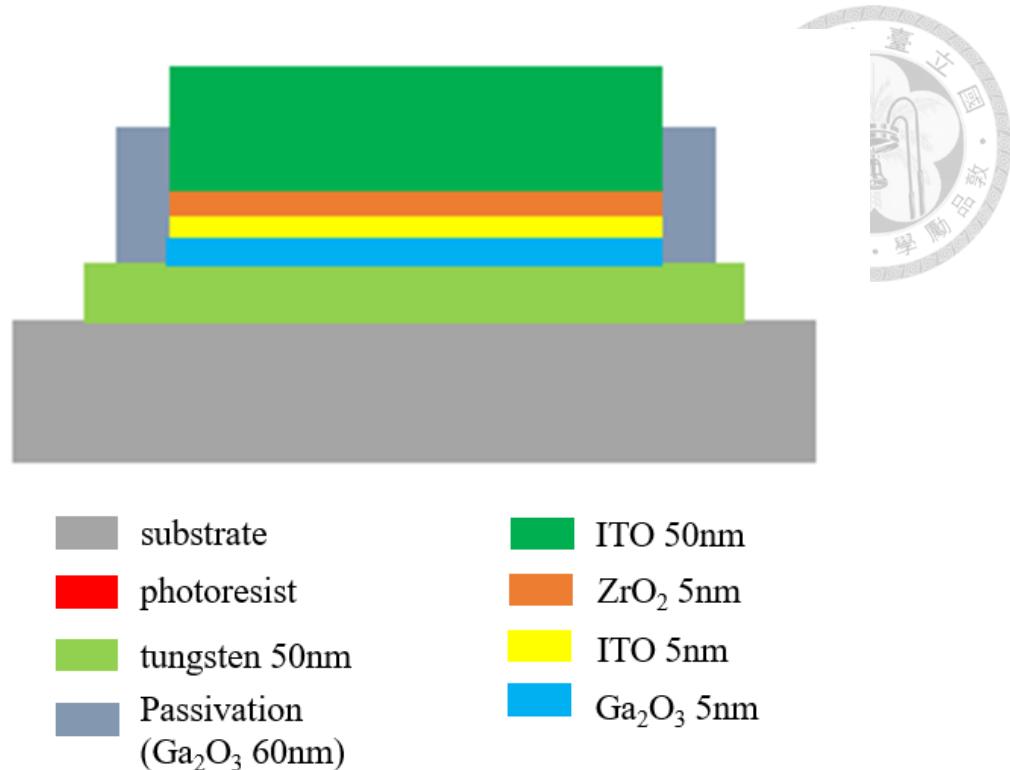

| 圖 3.7 氧化鎵/氧化鋯穿隧奈米結構元件示意圖 .....                                                                    | 37 |

| 圖 4.1 直流電性量測實驗儀器架構圖 .....                                                                         | 38 |

| 圖 4.2 萃取能障高度流程示意圖 .....                                                                           | 40 |

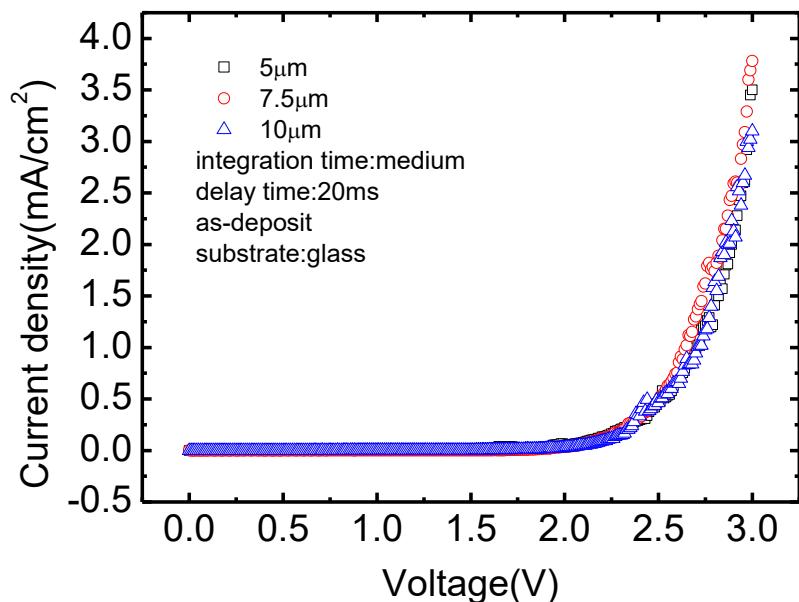

| 圖 4.3 W/ZrO <sub>2</sub> /W 結構之電壓 電流密度結果 .....                                                    | 41 |

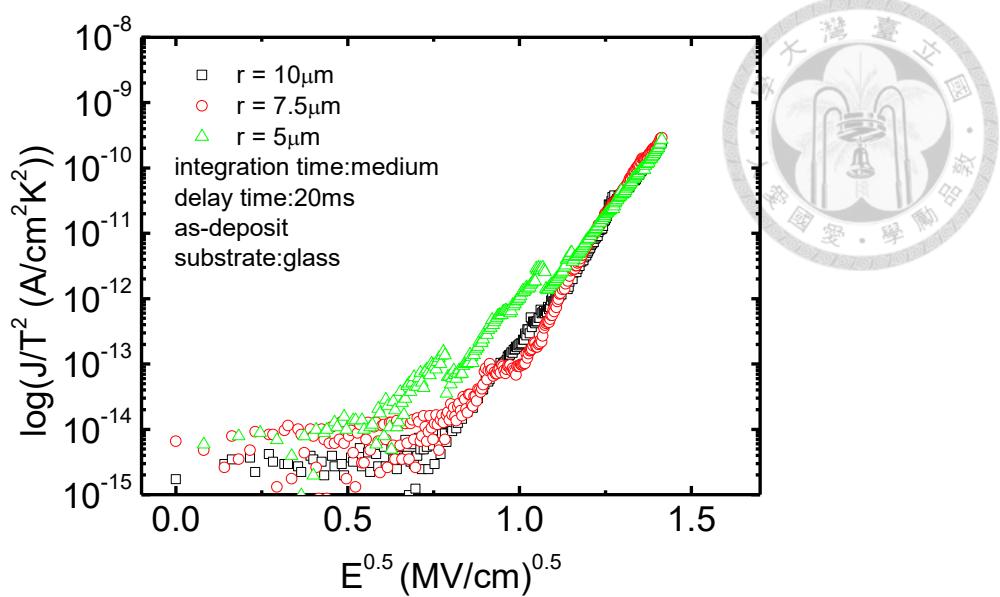

| 圖 4.4 W/ZrO <sub>2</sub> /W 結構之 log(J/T <sup>2</sup> )對 E <sup>0.5</sup> 特性圖 .....                | 42 |

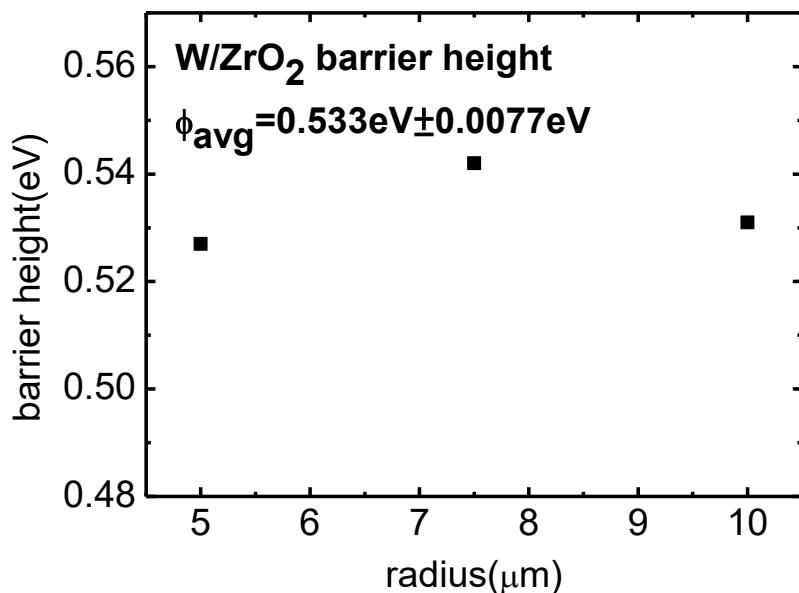

| 圖 4.5 W/ZrO <sub>2</sub> 能障高度與元件半徑之關係 .....                                                       | 42 |

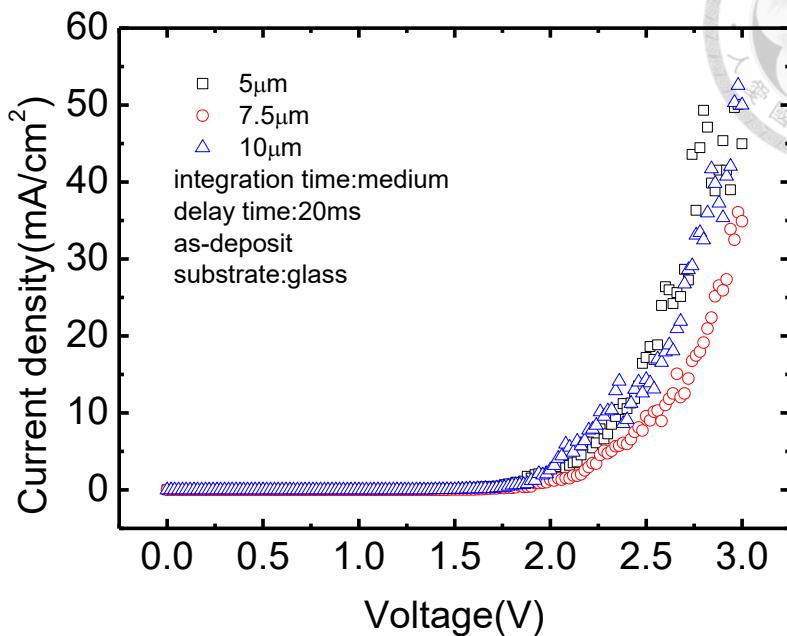

| 圖 4.6 ITO /ZrO <sub>2</sub> /ITO 結構之電壓 電流量測結果 .....                                               | 43 |

| 圖 4.7 ITO /ZrO <sub>2</sub> /ITO 結構之 log(J/T <sup>2</sup> )對 E <sup>0.5</sup> 特性圖 .....           | 43 |

| 圖 4.8 ITO/ZrO <sub>2</sub> 能障高度與元件半徑之關係 .....                                                     | 44 |

| 圖 4.9 W/Ga <sub>2</sub> O <sub>3</sub> /W 結構之電壓 電流密度量測結果 .....                                    | 44 |

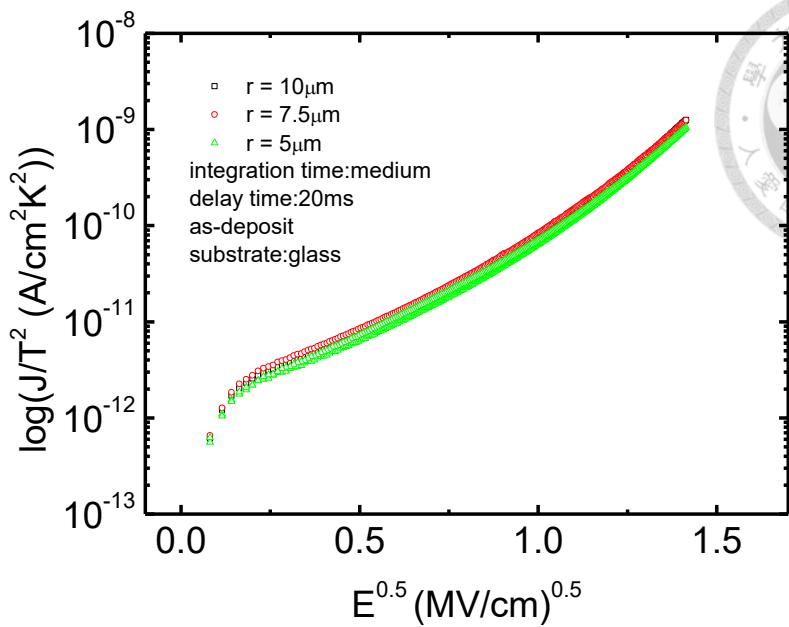

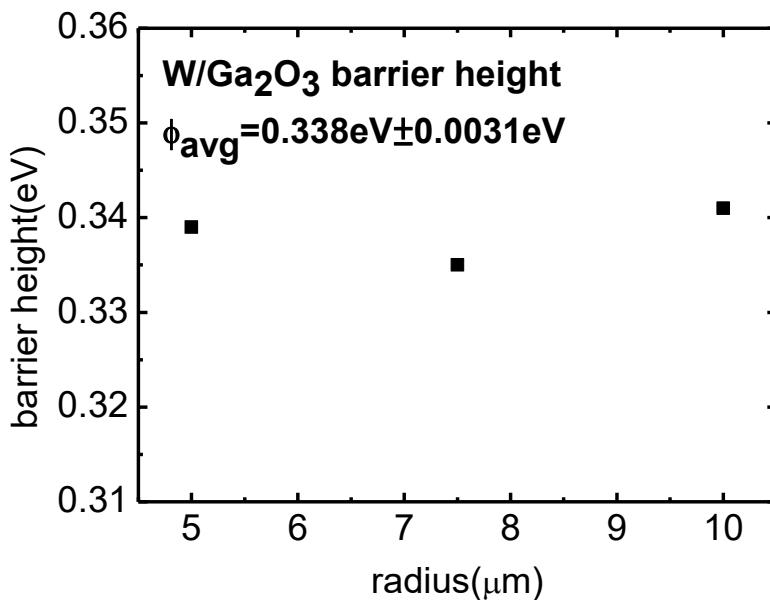

| 圖 4.10 W/Ga <sub>2</sub> O <sub>3</sub> /W 結構之 log(J/T <sup>2</sup> )對 E <sup>0.5</sup> 特性圖 ..... | 45 |

| 圖 4.11 W/ Ga <sub>2</sub> O <sub>3</sub> 能障高度與元件半徑之關係 .....                                       | 45 |

| 圖 4.12 ITO/ Ga <sub>2</sub> O <sub>3</sub> /ITO 結構之電壓 電流密度量測結果 .....                              | 46 |

|                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------|----|

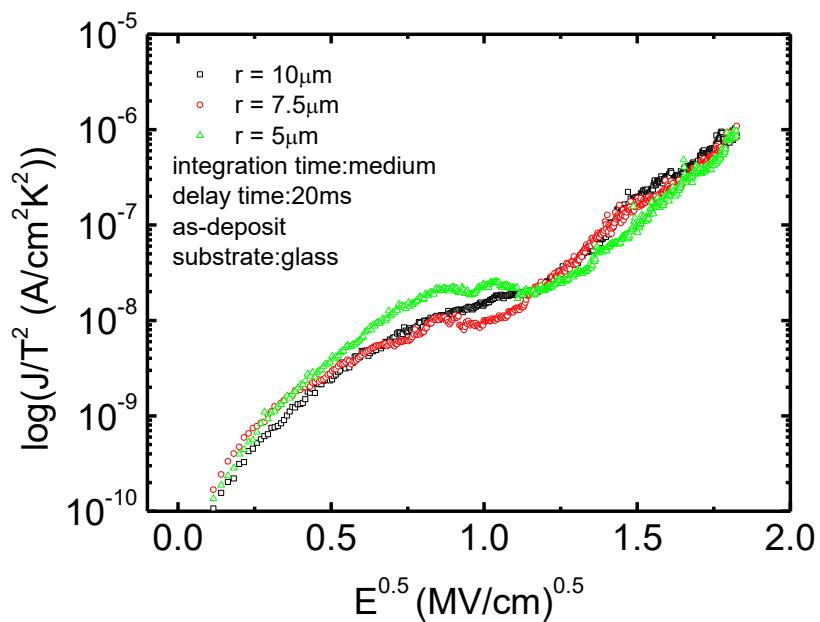

| 圖 4.13 ITO/ Ga <sub>2</sub> O <sub>3</sub> /ITO 結構之 log(J/T <sup>2</sup> )對 E <sup>0.5</sup> 特性圖 ..... | 46 |

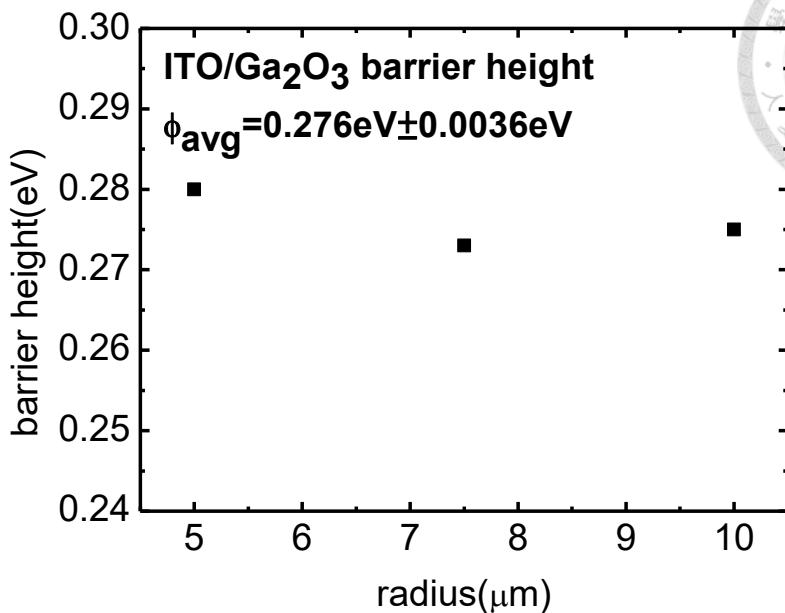

| 圖 4.14 ITO/ Ga <sub>2</sub> O <sub>3</sub> 能障高度與元件半徑之關係.....                                           | 47 |

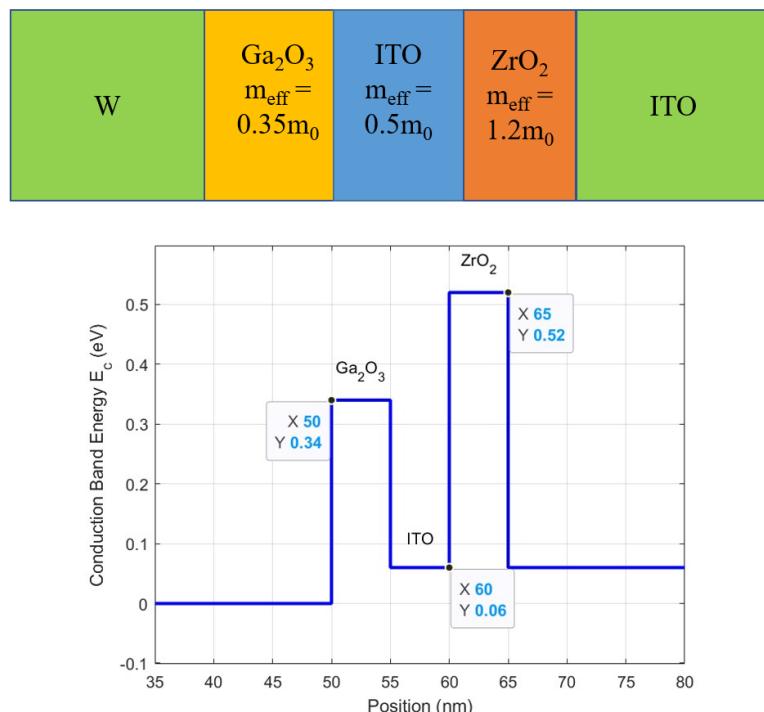

| 圖 4.15 雙能障量子井擬合模型 .....                                                                                | 49 |

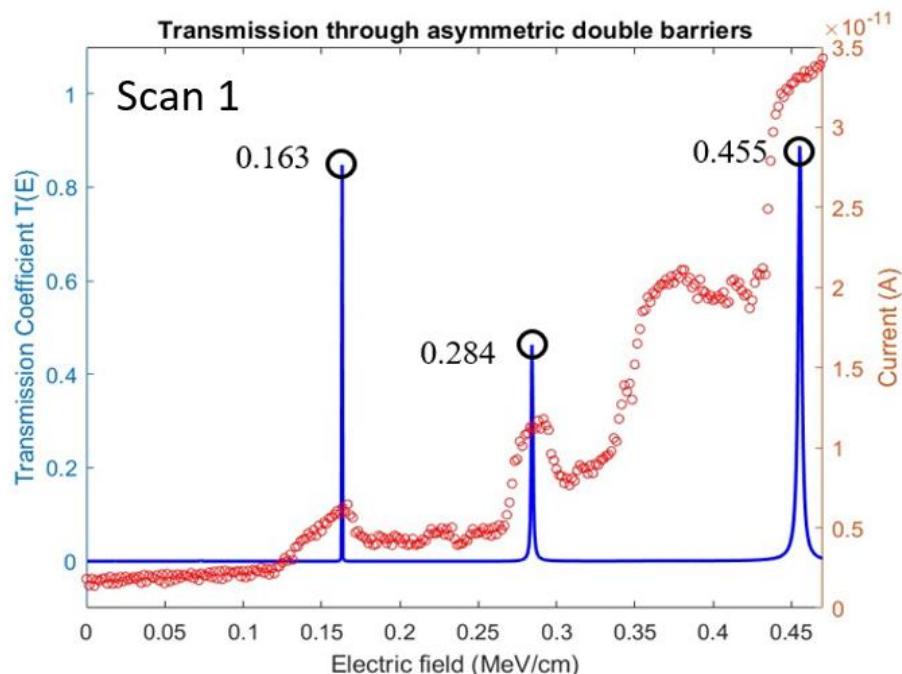

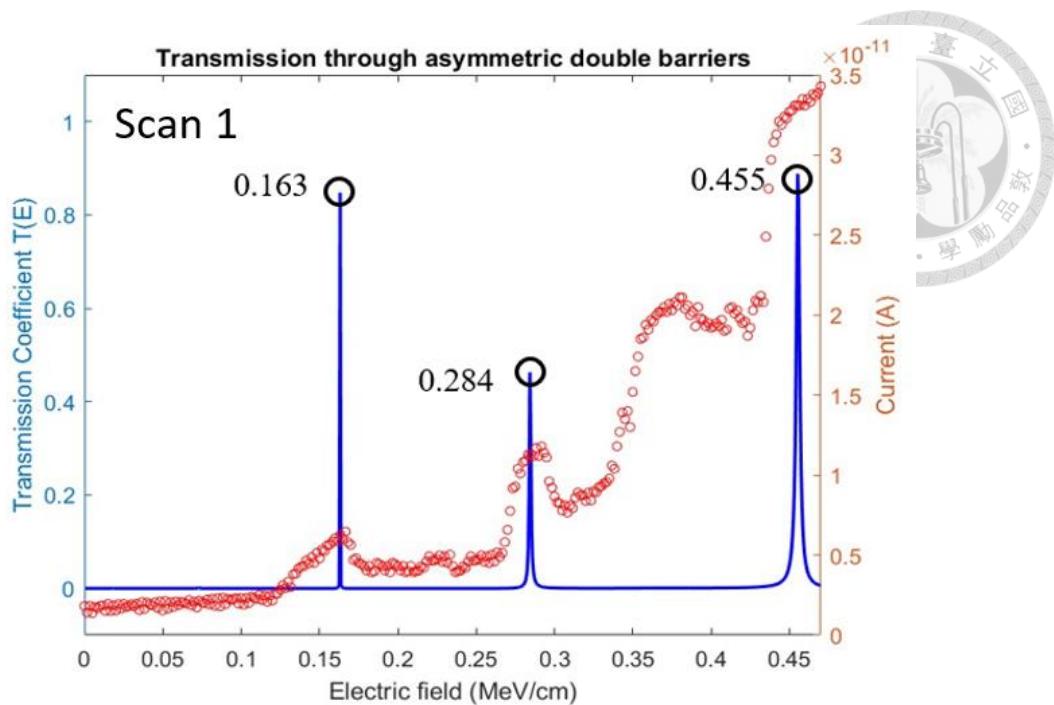

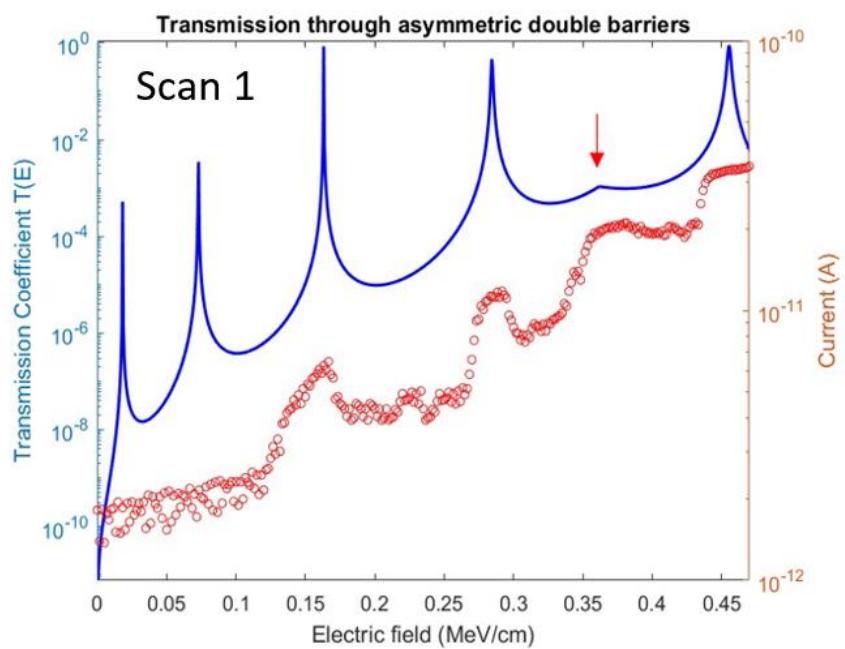

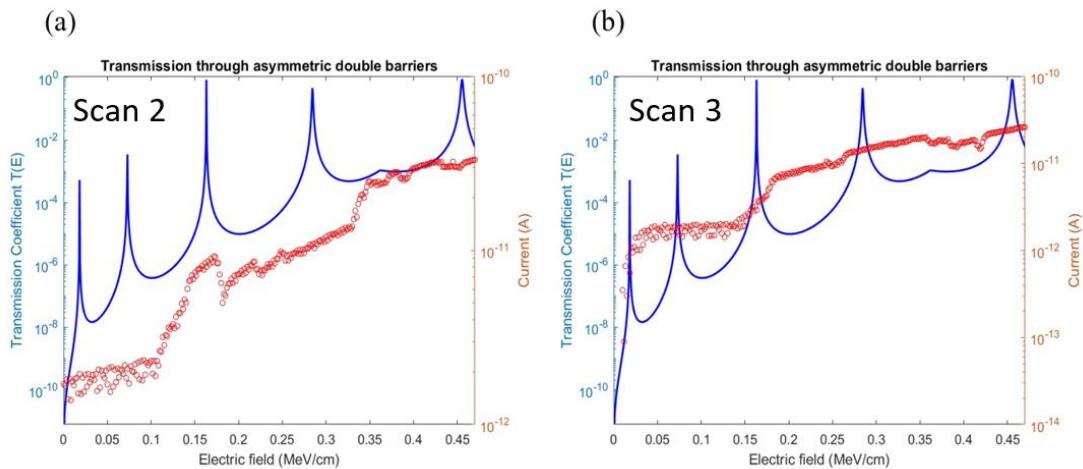

| 圖 4.16 首次掃描實驗數據與穿透係數模擬計算對比(線性) .....                                                                   | 53 |

| 圖 4.17 穿透係數模擬計算結果與實驗數據對比(對數) .....                                                                     | 53 |

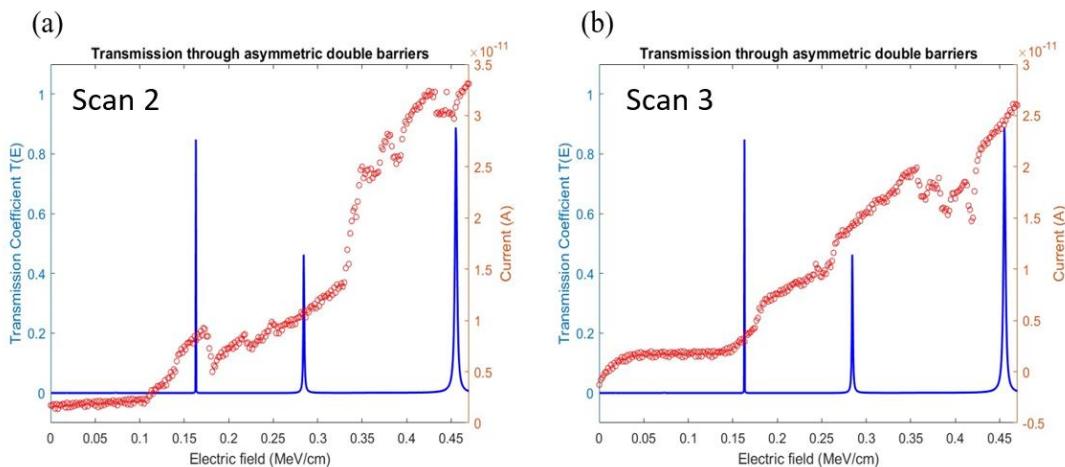

| 圖 4.18 連續掃描元件後穿透係數與實驗數據對比(線性) .....                                                                    | 54 |

| 圖 4.19 連續掃描元件後穿透係數與實驗數據對比(對數) .....                                                                    | 55 |

| 圖 4.20 (a)電場由 ITO 至 W (b)電場由 W 至 ITO .....                                                             | 56 |

| 圖 4.21 連續掃描元件對電流特性之影響 .....                                                                            | 58 |

| 圖 4.22 不同起始電壓與雙向掃描之電流特性 .....                                                                          | 59 |

| 圖 4.23 順向偏壓掃描結果分為三個區域分析 .....                                                                          | 60 |

| 圖 4.24 不同掃描速率下滿足電容充放電特徵 .....                                                                          | 61 |

| 圖 4.25 比較不同外加電場方向對電流特性的影響 .....                                                                        | 62 |

| 圖 4.26 漑鍍機製作多層膜時發生介面混合現象 <sup>[24]</sup> .....                                                         | 64 |

| 圖 4.27 比較穿隧效應與陷阱輔助機制下元件特性 .....                                                                        | 65 |

| 圖 4.28 連續掃描穿隧奈米結構 .....                                                                                | 66 |

# 表次

|                             |    |

|-----------------------------|----|

| 表 2.1 不同濺鍍條件下氧化鋂薄膜比較 .....  | 9  |

| 表 2.2 不同濺鍍條件下氧化鋯薄膜比較 .....  | 13 |

| 表 4.1 能障高度分析之實驗參數 .....     | 41 |

| 表 4.2 材料介面能障高度分析結果 .....    | 47 |

| 表 4.3 非對稱雙能障量子結構之模擬參數 ..... | 50 |

# 第一章 緒論

## 1.1 簡介

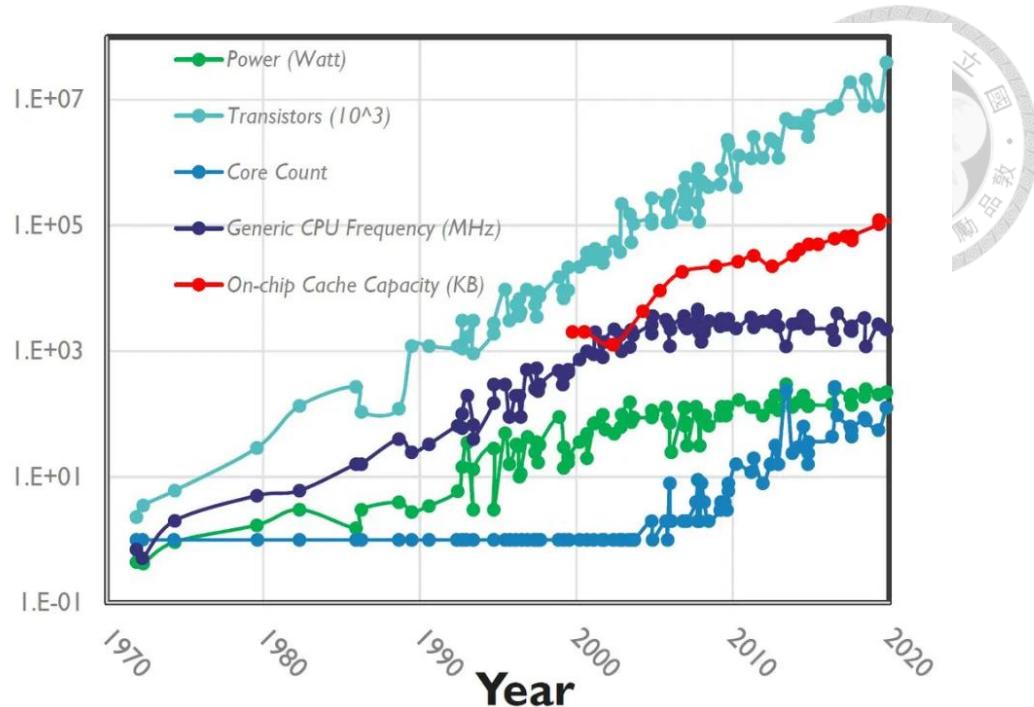

傳統半導體技術長期依賴提升時脈頻率 (CPU Clock Frequency) 作為主要手段。然而自 2000 年後，處理器時脈受到功耗與散熱限制，無法再如以往持續進步。圖 1.1 顯示，自 1970 年至今，雖然電晶體數量與快取記憶體容量仍維持指數成長，但處理器時脈頻率已於 2005 年後趨於飽和，取而代之的是多核心設計與封裝整合的推進。同時功耗曲線顯著上升，傳統以提升時脈換取效能的策略已面臨功耗瓶頸與散熱限制等物理極限，成為限制高速裝置發展的主要瓶頸。為突破此限制，具備非傳統導電機制的元件架構逐漸受到重視。共振穿隧式二極體( Resonant Tunneling Diode, RTD )利用量子力學中的穿隧效應與準束縛態 (quasi-bound state) 對齊時，電子穿隧的機率會顯著增加，在特定偏壓條件下能產生負微分電阻 (Negative Differential Resistance, NDR) 特性可用來實現兆赫 (Terahertz , THz) 級頻寬，因而受到廣泛的關注，並可應用於高頻振盪器、感測器與記憶元件等領域。

圖 1.1 處理器性能演變，包含電晶體數量、核心數量、功耗、CPU 時脈、快取記憶體速度<sup>[1]</sup>

共振穿隧二極體的發展可追溯至 1958 年 Leo Esaki 發表的穿隧二極體 (tunnel diode)<sup>[2]</sup>，首次觀察到電子透過摻雜 p - n 接面產生穿隧電流，並奠定量子穿隧應用的基礎。1973 年 Tsu 與 Esaki 提出雙能障量子井 (Double Barrier Quantum Well, DBQW) 結構理論<sup>[3]</sup>，當電子注入能量與量子井能階對齊時，會發生共振式穿隧效應相較於傳統穿隧二極體依賴單一能障，雙能障結構利用量子井中的離散能階，進一步提升穿隧選擇性與共振效應。在接續第二章節中有更詳細的理論說明。

目前為止，室溫下的共振穿隧特性與負微分電阻現象大多數在矽基板<sup>[4]</sup>或 III - V 族化合物半導體中實現<sup>[5]</sup>。Shaojun Lin 等人在 2020 年的文研究中顯示<sup>[6]</sup>第三代半導體，如 III 族氮化物 (GaN, AlN, InN) 因其高崩潰電場、載子遷移速度快與寬可調直接能隙特性，有望提供較傳統 GaAs/AlAs 材料之共振穿隧二極體更好的共振可調性。

此外，Zhijun Ma 在 2022 年的研究中，成功製作以鈣鈦礦結構氧化物結構 (BaTiO<sub>3</sub>/SrRuO<sub>3</sub>/BaTiO<sub>3</sub>) 為基礎之室溫鐵電共振穿隧二極體，在量子井中，可在室溫下實現穩定的鐵電調控共振穿隧效應以及負微分電阻行為<sup>[7]</sup>。另一研究則在 LSMO/BTO/LSMO 多鐵性穿隧中發現低於 100K 下的電導量子振盪，因氧空缺而穩定下來的電子氣 (electron gas) 被侷限在該畴壁 (domain wall) 內<sup>[8]</sup>。

綜觀近十年來之研究趨勢，無論是基於 III-V 族氮化物材料，亦或是鐵電性氧化物結構，共振穿隧二極體元件的發展正朝向結合可切換極化的鐵電材料，使其作為能障或量子井，進而在室溫操作條件下實現可調變的穿隧電流與共振條件，此類設計不僅能提高元件功能的可控性與穩定性，亦有望實現具備非揮發記憶特性與高能量效率的新型電子元件架構，拓展其在高速記憶體及未來低功耗奈米電子元件中的應用潛能。

## 1.2 研究動機與目的

隨著元件微縮與高速化發展趨勢，傳統基於 III-V 族化合物之共振穿隧二極體 (Resonant Tunneling Diode, RTD) 雖具兆赫級頻寬與負微分電阻特性，然其高成本、晶圓尺寸受限與製程難度，限制其在大規模整合應用上的發展潛力。此外實現共振穿隧二極體所需之極薄量子井與高品質介面，也大幅提高了材料與製程的複雜性。

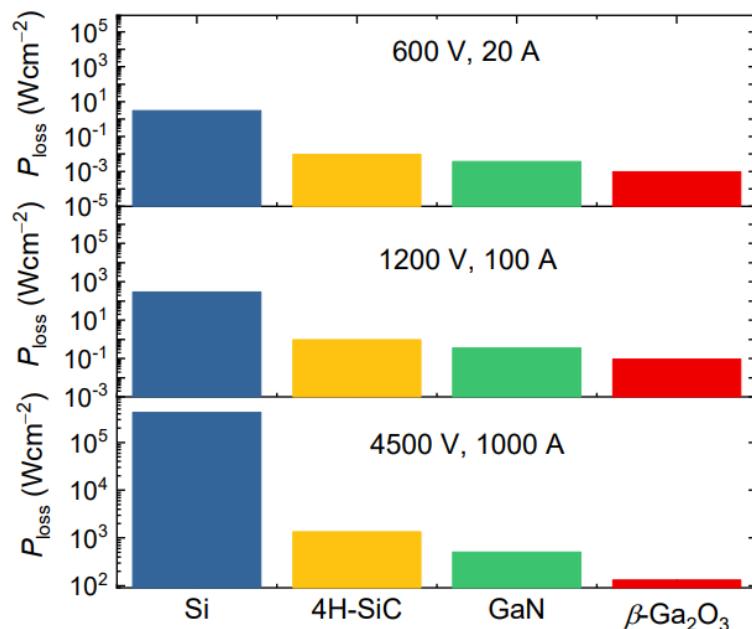

近年來，氧化鎵( $\text{Ga}_2\text{O}_3$ )因其寬能隙、高崩潰電場與豐富陷阱能階的特性，被大量應用於高功率元件<sup>[9]</sup>，鐵電材料則因其可逆自發極化效應與低功耗等優勢，被廣泛應用於記憶體當中。

圖 1.2 不同元件在相同的高電壓/高電流下之功耗比較<sup>[9]</sup>

本研究設計異質氧化物結構之垂直式穿隧奈米結構元件 (W/Ga<sub>2</sub>O<sub>3</sub>/ITO/ZrO<sub>2</sub>/ITO)，透過中間層氧化銦錫作為量子井，並結合氧化鋇與氧化鋯的高能障特性，製作可實現準束縛態的雙能障結構。預期能觀察穿隧電流、負微分電阻特徵，並探討電場方向、掃描速率與陷阱輔助穿隧對導電行為的影響。

本研究之目的：設計並製作 pA 等級電流元件並具雙能障與量子井的氧化物穿隧奈米結構結構；估算介面能障高度，分析載子注入與穿隧行為；分析遲滯與非對稱導通行為、陷阱輔助穿隧之參與機制；以轉移矩陣法模擬穿透係數，與實驗量測進行對照；拓展其於未來高速、低功耗記憶體與感測元件的應用潛能。

### 1.3 論文內容概述

本研究針對一新穎異質結構之穿隧奈米結構 (Tunneling Nanostructure) 進行設計、製作與分析。該元件採用高介電常數之氧化鋯 (ZrO<sub>2</sub>) 與具備高崩潰電壓及寬能隙特性的氧化鋇 (Ga<sub>2</sub>O<sub>3</sub>) 作為雙重能障材料，形成非對稱能障結構，並於微米柱周圍以高電阻絕緣層包覆，有效抑制側向漏電行為。

本研究結合實驗與理論模擬，透過直流電性量測觀察元件之傳輸特性與陷阱效應對導電行為之影響，並以 MATLAB 撰寫程式，模擬異質雙能障結構中電子穿透係數之變化，進一步分析其穿隧條件。

本論文共分為五個章節。第一章為緒論，說明研究背景、動機與論文內容架構。

第二章介紹本研究所使用之氧化鋯與氧化鎵材料特性，並以原子力顯微鏡( Atomic Force Microscopy, AFM )分析薄膜表面均勻度。接著說明薄膜導電傳輸機制與共振穿隧二極體之理論基礎。

第三章敘述穿隧奈米結構之製程流程與元件結構設計，涵蓋黃光微影、濕蝕刻技術、表面清潔步驟與微米柱孔洞製作方法。

第四章為元件直流電性分析與實驗結果討論，內容包含量測系統架構介紹、元件尺寸與各層材料能障高度分析、載子傳輸機制探討，以及模擬與實驗結果之比對。

第五章總結研究成果，並提出未來潛在的改良方向與研究展望。

## 第二章 氧化鎵／氧化鋯穿隧二極體之理論介紹

### 2.1 氧化鎵與氧化鋯材料特性

#### 氧化鎵 ( $\text{Ga}_2\text{O}_3$ )

氧化鎵( $\text{Ga}_2\text{O}_3$ )為一種寬能隙材料，被廣泛運用於光電二極體、發光體、電子開關與氣體感測器等多種裝置，1952 年首次被 RUSTEM ROY 等人提出氧化鎵具有五種多晶型態<sup>[10]</sup>，透過不同的生長條件而形成，包括 $\alpha$ 、 $\beta$ 、 $\gamma$ 、 $\delta$ 、 $\varepsilon$ 相多晶型態，其中又以 $\beta - \text{Ga}_2\text{O}_3$ 最為穩定。 $\beta - \text{Ga}_2\text{O}_3$ 屬單斜晶系，為所有晶相中最穩定的結構，具有優異的熱與化學穩定性，且熔點高達  $1780^\circ\text{C}$ 。 $\beta - \text{Ga}_2\text{O}_3$ 的晶格常數分別為  $a = 12.2140\text{ \AA}$ 、 $b = 3.0371\text{ \AA}$ 、 $c = 5.7981\text{ \AA}$ ， $\beta$ 角為  $103.83^\circ$ 。在製程中，其他晶相的氧化鎵可透過熱處理轉變為較穩定的 $\beta$ 相。

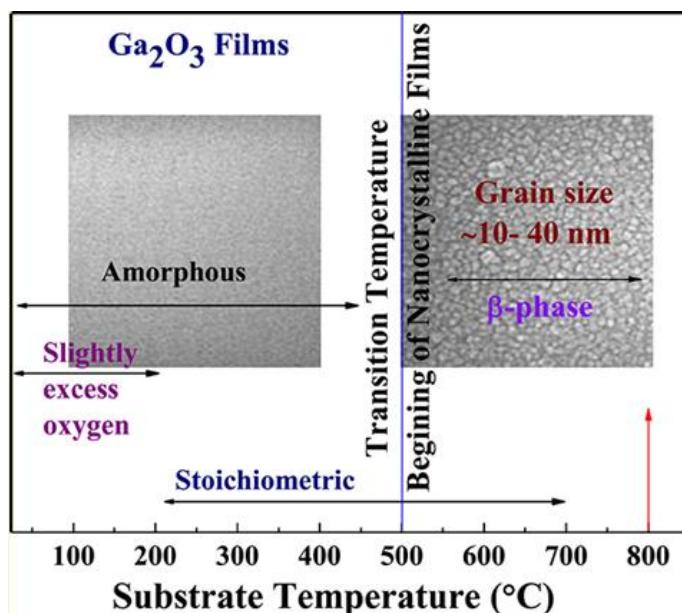

圖 2.1 不同基板溫度對氧化鎵薄膜之影響<sup>[11]</sup>

由於結晶相的氧化鎵薄膜通常具有較高的表面粗糙度，這些特性不利於形成共振結構。共振穿隧二極體（Resonant Tunneling Diode, RTD）元件對薄膜的結構均勻性要求極高，需具備高度平整且連續的薄膜，以確保量子穿隧效應能有效發生。因此，本研究於實驗設計上，透過調整濺鍍過程中的氧氣比例，藉以抑制不規則薄膜結晶，同時降低表面粗糙度，進而提升薄膜的平整性與均勻性，以利後續共振結構的製作。

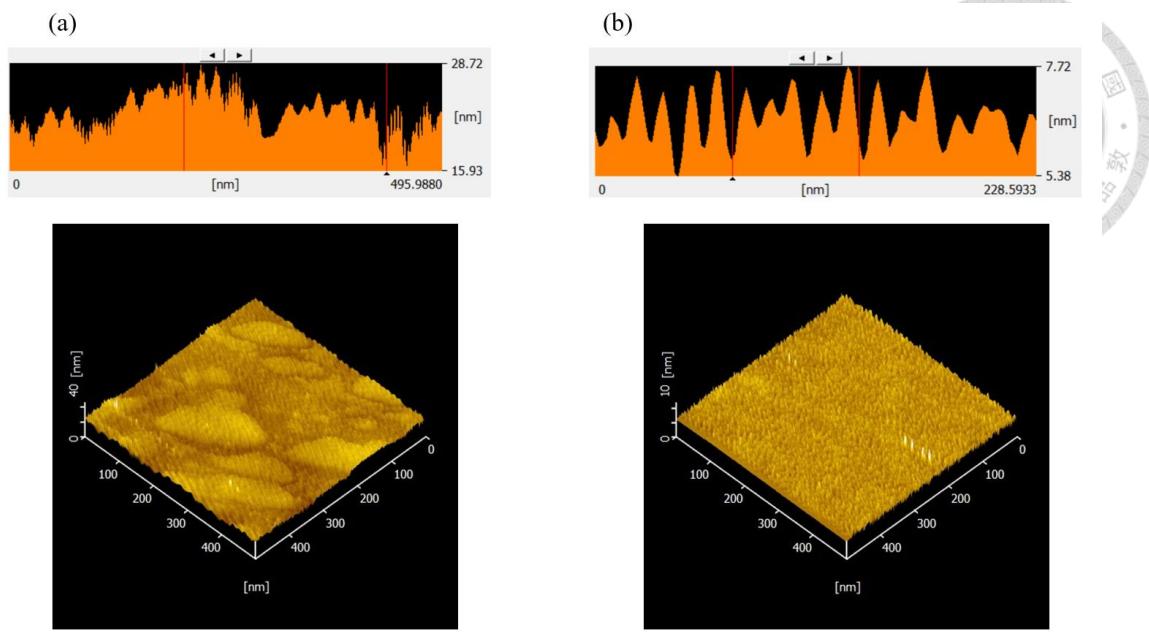

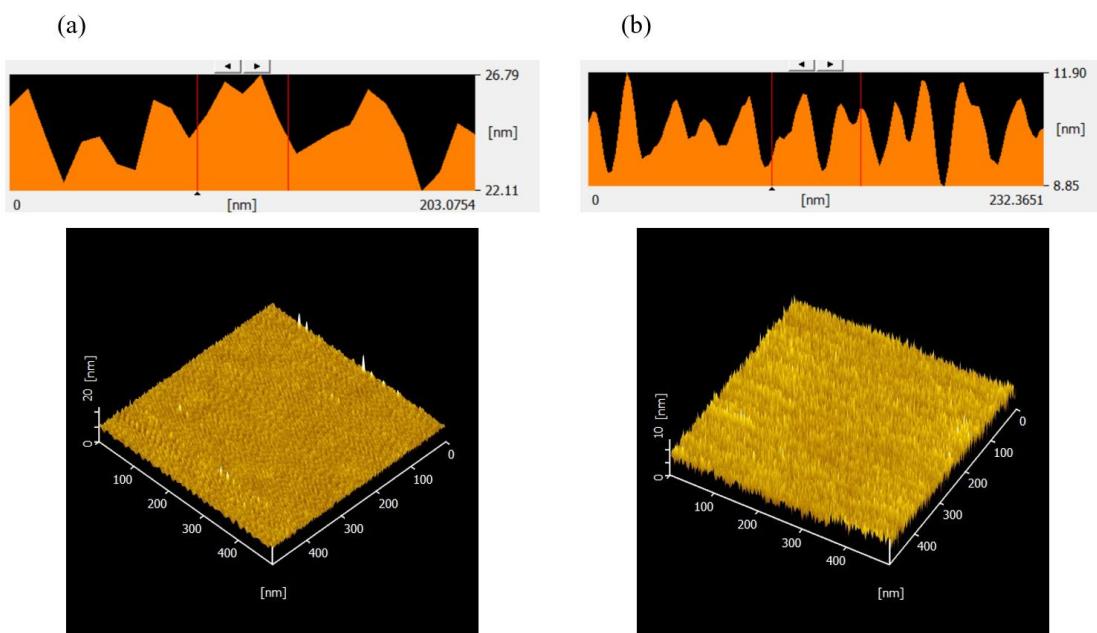

因此進一步調控濺鍍參數對薄膜表面形貌之影響，利用原子力顯微鏡（Atomic Force Microscopy, AFM）對不同濺鍍條件下之氧化鎵薄膜進行表面掃描，掃描範圍為 500 奈米，圖 2.2 (a) 通入氬氣與氧氣比例 0% 之氧化鎵，(b) 通入氬氣與氧氣比例 20% 氧化鎵薄膜之原子力顯微鏡影像。由結果可觀察到，在未通氧條件下，薄膜表面呈現明顯且不規則的結晶顆粒，導致粗糙度提升；而通入氧氣後，薄膜表面顯得更加平坦與均勻。

對原子力顯微鏡影像進行均方根粗糙度分析（root mean square roughness, RMS），可得知通入氧氣條件下薄膜之均方根粗糙度（表 2.1）明顯低於未通入氧氣者，進一步證實氧氣比例調整有助於改善薄膜表面品質。

圖 2.2 (a) 氣氣與氧氣比例 0% 之氧化鎵薄膜 (b) 氣氣與氧氣比例

20% 之氧化鎵薄膜

表 2.1 不同濺鍍條件下氧化鎵薄膜比較

| 濺鍍條件                               | 表面平均粗糙度<br>Ra (nm) | 均方根粗糙度<br>RMS (nm) | 最大高度差<br>Peak-to-Valley (nm) |

|------------------------------------|--------------------|--------------------|------------------------------|

| (a) $\frac{O_2}{Ar+O_2}$ (%) = 0%  | 1.82               | 2.32               | 46.2                         |

| (b) $\frac{O_2}{Ar+O_2}$ (%) = 20% | 0.57               | 0.73               | 12.4                         |

在化學性質方面，氧化鎵表現出兩性氧化物( amphoteric oxide )的特性，能夠同時與酸與鹼反應<sup>[12]</sup>。氧化鎵在濃硝酸(  $HNO_3$  )、濃鹽酸(  $HCl$  )等強酸環境中可被蝕刻，且在高溫條件下，使用氫氧化鉀(  $KOH$  )等強鹼亦能加速其溶解。酸性環境下，氫離子(  $H^+$  )攻擊  $Ga-O$  鍵，促

使  $\text{Ga}^{3+}$ 離子溶出；而在鹼性環境中， $\text{OH}^-$ 離子則促使氧化鎵轉化為可溶性的氫氧複合物(如 $[\text{Ga}(\text{OH})_4]^-$ )，兩者皆能有效蝕刻氧化鎵薄膜。

基於氧化鎵具備兩性蝕刻行為的特性，本研究後續製程將採用鹼性顯影液(MF-319)及稀鹽酸作為蝕刻溶液，完成圖案定義與元件微結構製作。顯影主要用於光阻圖案的形成及初步蝕刻，而稀鹽酸則作為最後確認完整蝕刻氧化鎵薄膜的蝕刻液。

### 氧化鋯 ( $\text{ZrO}_2$ )

氧化鋯屬於過渡金屬氧化物之一，且為寬能隙材料具有高介電常數，因此被認為是取代二氧化矽( $\text{SiO}_2$ )作為電介質閘極材料的潛力材料。氧化鋯在不同溫度條件下會呈現不同的晶體結構，如圖 2.3，由左而右分別為立方相(cubic)、四方相(tetragonal)和單斜相(monoclinic)。

圖 2.3 氧化鋯不同晶相結構(a)立方相(b)四方相(c)單斜相<sup>[13]</sup>

在室溫下所沉積的氧化鋯薄膜通常呈現非晶結構，由於缺乏非中心對稱晶格排列，因此不具備可反轉的自發極化（spontaneous polarization），而不被認為有鐵電的特性。然而，根據 2023 年 Liu 等人研究<sup>[14]</sup>中，即使是非晶態的氧化鋯薄膜，在金屬/絕緣體/金屬（MIM）結構中仍觀察到類似鐵電材料的遲滯特性（hysteresis），此現象被歸因於可移動離子（mobile ions）的移動行為，所產生與鐵電材料相似的鐵電行為。

圖 2.4 非晶相氧化鋯在室溫下之極化-電場特性<sup>[14]</sup>

另外，根據 2025 年 Lee 等人之研究<sup>[15]</sup>，透過快速熱退火（Rapid Thermal Anneal, RTA）可使非晶態氧化鋯轉變為四方晶相（tetragonal phase）。此一結晶化有助於降低電子於晶格中的散射，進而提升薄膜品質。未來可以嘗試此退火技術製備高品質結晶相氧化鋯，作為穿隧二極體中之能障材料。

圖 2.5 快速熱退火形成多晶相之氧化鋯 [15]

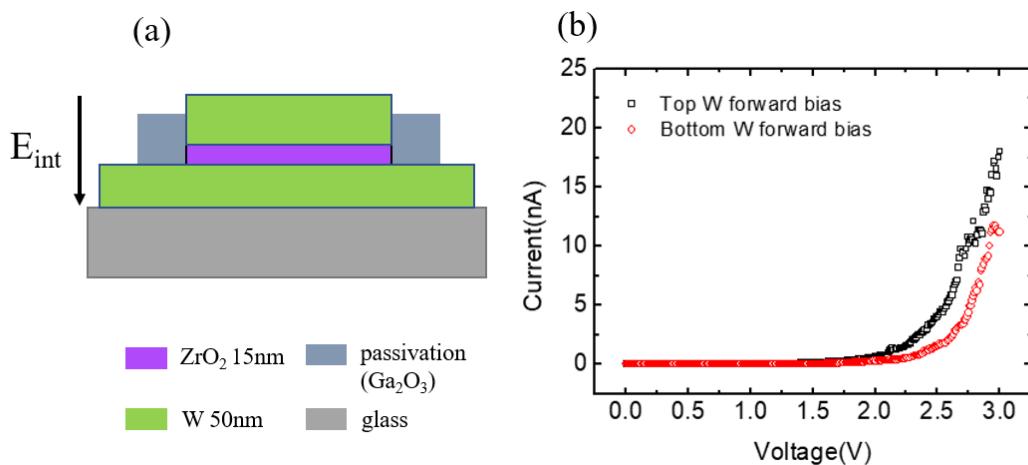

為驗證氧化鋯在元件內部自帶的電場方向，吾人進一步設計簡化之元件結構，圖 2.6(a)為元件示意圖(並非實際比例)，以金屬鎢為上下電極、氧化鋯為氧化層之結構，分別對上下電極施加偏壓，圖 2.6(b)量測之電流-電壓曲線（黑色為上電極鎢施加正偏壓，紅色為下電極鎢施加正偏壓），可由電流-電壓曲線不對稱性來推論在對稱結構下之內建電場方向。此分析將有助於第四章中對元件物理行為與電性特徵的深入討論。

圖 2.6 (a)元件結構示意圖 (b)氧化鋯對稱結構之電流-電壓特性

## 氧化鋯薄膜同樣以原子力顯微鏡( Atomic Force Microscopy, AFM )

進行表面形貌分析。實驗結果顯示，圖 2.7(a) 通入氮氣與氧氣比例 1.25% 與圖 2.7(b) 通入氮氣與氧氣比例 20% 條件下，其表面粗糙度差異不明顯，顯示氧氣流量對薄膜平整性之影響有限(表 2.2 )。因此，後續製程中選擇以通入低氧氣比例進行氧化鋯薄膜製作。

圖 2.7 (a)低氧氣比例之氧化鋯薄膜 (b)高氧氣比例之氧化鋯薄膜

表 2.2 不同濺鍍條件下氧化鋯薄膜比較

| 濺鍍條件                                   | 表面平均粗糙度<br>Ra (nm) | 均方根粗糙度<br>RMS (nm) | 最大高度差<br>Peak-to-Valley (nm) |

|----------------------------------------|--------------------|--------------------|------------------------------|

| (a) $\frac{O_2}{Ar+O_2} (\%) = 1.25\%$ | 0.71               | 0.89               | 23                           |

| (b) $\frac{O_2}{Ar+O_2} (\%) = 0\%$    | 1.2                | 1.62               | 14.2                         |

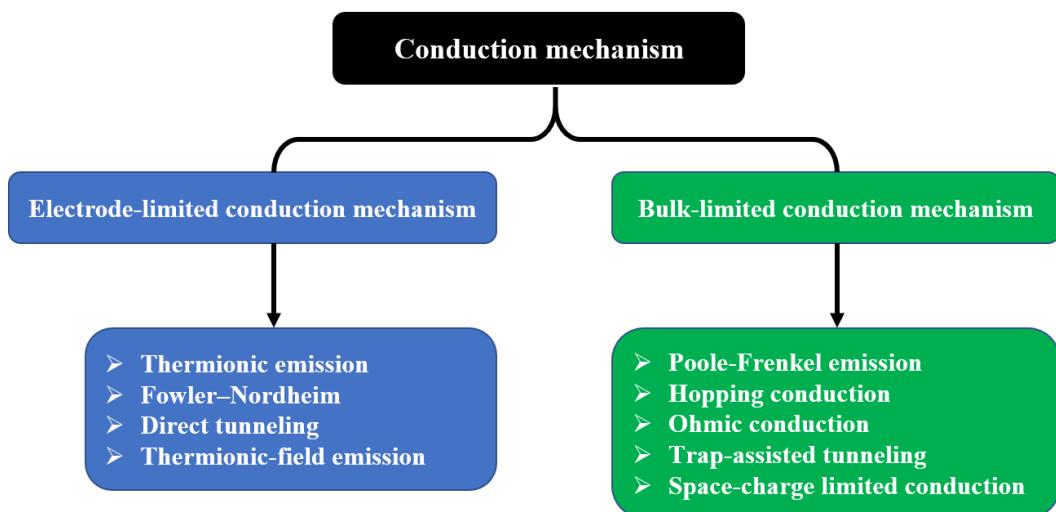

## 2.2 薄膜導電電流機制 (Conduction mechanisms)

在氧化物薄膜的導電行為中，導電機制可概分為電極限制型 (electrode-limited) 與本體限制型 (bulk-limited) 兩大類。前者的導電特性主要受限於金屬與介電質之間的介面能障；而後者與介電層本身的陷阱態 (trap states) 與陷阱分佈密切相關<sup>[16]</sup>。

其中，電極-介電質接面限制機制包括：(1) 热發射 (Thermionic emission) (2) Fowler-Nordheim (Fowler-Nordheim tunneling) (3) 直接穿隧 (Direct tunneling) 以及 (4) 热場發射 (Thermionic-field emission)。

本體限制機制則涵蓋：(1) Poole-Frenkel emission (2) 跳躍傳輸 (Hopping conduction) (3) 歐姆傳導 (Ohmic conduction) (4) 陷阱輔助穿隧 (Trap-assisted tunneling) 以及 (5) 空間電荷限制傳導 (Space-charge limited conduction)。

在本研究第四章中，吾人首先採用金屬/氧化層/金屬之對稱結構進行直流電性分析，進一步探討各層材料間之能障高度。考量穿隧效應對能障判讀之干擾，吾人使用氧化層厚度均為 15 奈米，藉此避免因氧化層過薄而產生直接穿隧，導致能障分析產生誤差。

在此厚膜結構下，載子傳輸主要受限於金屬與氧化層接面能障。因此，吾人將以熱發射效應 (thermionic emission) 作為主要導電機制進行討論。

然而，於穿隧奈米結構元件量測中，吾人亦觀察到非理想遲滯現象，推測為材料內部陷阱態（trap states）參與傳輸所致。此現象符合陷阱輔助穿隧（Trap-Assisted Tunneling, TAT）之典型行為。為更深入理解元件中可能共存之傳輸機制，以下將分別介紹熱發射效應與陷阱輔助穿隧效應之物理原理與對應數學模型，作為後續電性分析。

圖 2.8 薄膜導電電流機制<sup>[17]</sup>

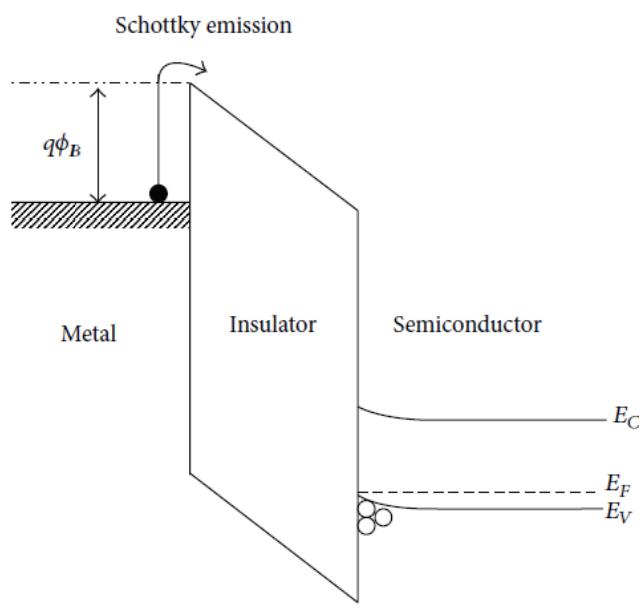

### 熱發射效應 (Thermionic emission)

熱發射效應，載子在外加電場作用下，獲得足夠熱能跨越金屬與介電質接面的能障，進而產生導通電流，如圖 2.9 所示。由於該機制對熱激發高度敏感，因此其電流對溫度變化具有高度依賴性。此機制主要受限於金屬與半導體或氧化物接面處的能障高度，故歸類為電極-介電質界面限制型導電機制（electrode-dielectric interface

limited conduction mechanism) , 热發射效應常見於高電阻態下的導

電行為，其電流如以下公式<sup>[16]</sup>。

$$J = A^* T^2 \exp \left[ \frac{-q(\phi_B - \sqrt{qE/4\pi\epsilon})}{kT} \right] \quad (2.1)$$

其中  $A^* = \frac{4\pi q m^* k^2}{h^3} = 120 \left( \frac{m^*}{m_0} \right)$  為 Richardson 常數， $m^*$  為電子在氧化層的等效質量， $k$  為 Boltzmann 常數， $T$  為絕對溫度， $h$  為 Planck 常數， $E$  為加在氧化層的電場， $\phi_B$  為介面能障高度， $\epsilon$  為氧化層的介電常數。

電流密度定義為：

$$J = \frac{I_{measure}}{\pi r^2} \quad (2.2)$$

其中  $I_{measure}$  為量測電流， $r$  為元件半徑， $J$  為電流密度。

電場定義為：

$$E = \frac{V_{measure}}{d_{oxide}} \quad (2.3)$$

$V_{measure}$  為量測時所施加電壓， $d_{oxide}$  為氧化層厚度。

電流密度與電場  $\ln J$  v.s  $\sqrt{E}$  關係，電流密度和溫度的關係

$\ln(\frac{J}{T^2})$  v.s  $\frac{1}{T}$  作圖呈線性關係。

圖 2.9 金屬/絕緣層/半導體在熱發射效應之能階圖<sup>[16]</sup>

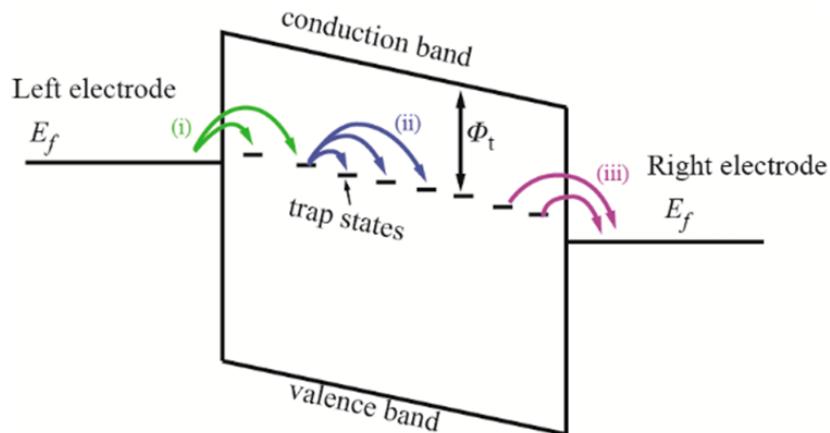

### 陷阱輔助穿隧 Trap-Assisted-Tunneling ( TAT )

陷阱輔助穿隧機制與直接穿隧不同，可以分為兩個步驟傳輸的機制。在此機制中，載子會先被陷阱或氧空缺捕捉，接著穿越能障至另一個陷阱，然後再重複穿隧至下一個陷阱，以此類推。透過多次的陷阱穿隧過程，載子最終能穿越整個氧化層，而每一次穿隧所跨越的距離只是氧化物厚度的一小部分。

圖 2.10 傳輸行為可以分為三個步驟，(i) 從一側電極穿隧進入陷阱態 ( trap states ) ; (ii) 電子在陷阱與陷阱之間穿隧遷移 ; (iii) 最後從陷阱穿隧至另一側電極。下列公式省略氧化層內部多個陷阱穿隧，只考慮單一陷阱位置。其電流如以下公式：

$$J = A \exp \left[ -\frac{8\pi\sqrt{2qm^*}}{3hE} \phi_t^{\frac{3}{2}} \right] \quad (2.4)$$

其中  $m^*$  為電子在氧化層的等效質量， $h$  為 Planck 常數， $\Phi_t$  為陷阱能階， $E$  為加在氧化層的電場。

電流密度與電場關係  $\ln(J) \text{ v.s. } \frac{1}{E}$  作圖呈線性關係。

圖 2.10 陷阱輔助穿隧機制示意圖<sup>[18]</sup>

## 2.3 共振穿隧式二極體之理論介紹

在這小節中，將介紹共振穿隧二極體 (Resonant Tunneling Diodes, RTD) 的物理機制，包括雙能障量子井結構 (Double Barrier Quantum Well, DBQW) 、載子傳輸過程、電流–電壓 (Current–Voltage) 特性與穿透係數 (Transmission Coefficient) 推導。

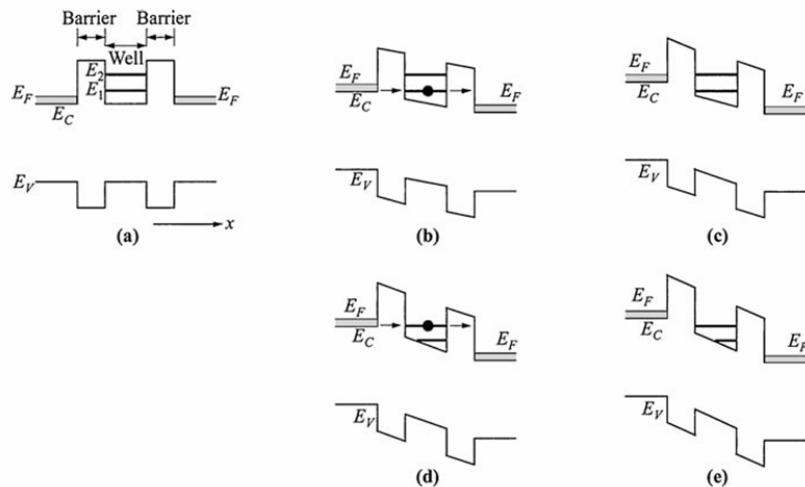

共振穿隧效應 (Resonant Tunneling Effect) 最早於 1970 年由 Esaki 和 Tsu 提出<sup>[19]</sup>，其原理建立在不同材料間導電帶 (conduction band) 與價電帶 (valence band) 能階的不連續性所造成的能障差異，

形成雙能障量子井結構，並結合兩端高濃度摻雜的半導體接觸區域，分別作為射極（陰極）與集極（陽極）。

圖 2.11 為共振穿隧二極體原理的示意圖，其概念基於電子波的量子力學行為。根據量子力學理論，當量子井的寬度接近電子德布羅意波長 (de Broglie wavelength) 時，電子的動能會產生量子化效應，使得量子井中能量呈現離散的能階分布，而不再是連續態。

達成共振條件所需的最小能量，如下式<sup>[20]</sup>:

$$E_n = \frac{h^2 n^2}{8m^* W^2}, \quad n = 1, 2, 3, \dots \dots \quad (2.5)$$

其中  $h$  為普朗克常數； $m^*$  為有效質量； $W$  為量子井寬度。

入射自由電子能量則由外加偏壓調節，如下式:

$$E_F = E_c + \frac{\hbar^2 k^2}{2m^*} \quad (2.6)$$

其中  $E_c$  為射極電子能量， $\hbar = \frac{h}{2\pi}$ ， $k$  為電子動量。

圖 2.11 共振穿隧二極體原理示意圖<sup>[20]</sup>

圖 2.11-(a) 顯示在無外加電場條件下，量子井中依據井深與寬度，可能形成一至數個離散能階，此時能帶水平分佈，元件處於平衡狀態。由於射極的費米能階低於量子井中第一個準束縛態 ( $E_F < E_1$ )，因此電子穿隧機率極低，電流近乎為零。

圖 2.11-(b) 當元件兩端施加電場時，左側射極的電子依據費米-狄拉克分佈 (Fermi-Dirac distribution) 展開，導電帶與價電帶因外

加電場而彎曲，使得能帶傾斜。當入射電子的能量與量子井中能階對準 ( $E_F = E_1$ ) 時，達到共振條件，穿隧機率提升，電流急劇上升。

圖 2.11-(c) 當電場持續增加，射極中自由電子能量高於量子井中的能階 ( $E_F > E_1$ )，失去共振條件，穿隧機率下降，導致流經元件的電流減少，進入負微分電阻 (Negative Differential Resistance, NDR) 區段。

### 穿透係數

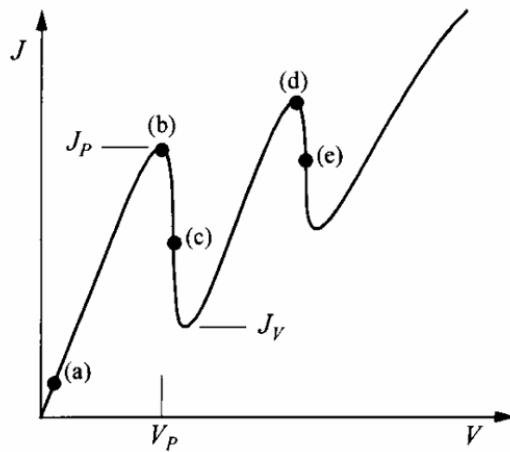

在進行雙能障量子井 (Double-Barrier Quantum Well, DBQW) 穿透係數計算前，需先探討單一能障 (Single Barrier) 結構中的電子穿隧行為。單一能障模型不僅是量子穿隧效應的基礎，更是建立多層異質結構 (如超晶格、多重量子井與共振穿隧二極體) 中電子傳輸理論之基礎，對於後續雙能障結構的模擬計算具關鍵意義。

## 單一能障( Single Barrier )

圖 2.12 電子波函數在單一能障結構中每個區域之一般解

在量子力學中，描述電子在一維中分佈行為的薛丁格方程式為：

$$\left[ \frac{d^2}{dz^2} + \frac{2m}{\hbar^2} (E - V(z)) \right] \Psi(z) = 0 \quad (2.7)$$

其中， $V(z)$ 為能障高度為常數，則式(2.7)的一般解為：

$$\Psi(z) = A \exp(ikz) + B \exp(-ikz) \quad (2.8)$$

$$E - V(z) = \frac{\hbar^2 k^2}{2m} \quad (2.9)$$

其中， $A$ 、 $B$  為波向量  $k$  的係數。

電子波函數滿足邊界條件：

$$\psi(z^-) = \psi(z^+) \quad (2.10)$$

式(2.10)表示波函數連續

$$\frac{1}{m_1} \frac{d\psi}{dz} \Big|_{z-} = \frac{1}{m_2} \frac{d\psi}{dz} \Big|_{z+} \quad (2.11)$$

式(2.11)表示電流密度的連續，其中  $m_1$ 、 $m_2$  為不同材料之等效質量，利用轉移矩陣法 ( Transfer Matrix Method, TMM )，可將單一能障之波函數寫成：

$$\begin{bmatrix} A_1 \\ B_1 \end{bmatrix} = M_1 \begin{bmatrix} A_2 \\ B_2 \end{bmatrix} \quad (2.12)$$

同理，

$$\begin{bmatrix} A_2 \\ B_2 \end{bmatrix} = M_2 \begin{bmatrix} A_3 \\ B_3 \end{bmatrix} \quad (2.13)$$

其中， $M_1$ 、 $M_2$  分別在介面  $z_1$ 、 $z_2$  之  $2 \times 2$  矩陣， $k$  為波向量， $A$ 、 $B$  為常數。

矩陣  $M$  可以表示成<sup>[21]</sup>：

$$M = \frac{1}{2k_1 m_2} \begin{bmatrix} C \exp[i(k_1 - k_2)z_1] & D \exp[-i(k_2 + k_1)z_1] \\ D \exp[i(k_2 + k_1)z_1] & C \exp[-i(k_2 - k_1)z_1] \end{bmatrix} \quad (2.14)$$

其中， $C = k_1 m_2 + k_2 m_1$ ， $D = k_1 m_2 - k_2 m_1$ 。

則穿透係數表示為<sup>[21]</sup>：

$$T_{1B} = \left| \frac{A_3}{A_1} \right|^2 = \frac{4E(V_0 - E)}{V_0^2 \sinh^2 k_2 a + 4E(V_0 - E)} \quad (2.15)$$

反射係數表示為<sup>[21]</sup>：

$$R_{1B} = \left| \frac{B_1}{A_1} \right|^2 = \frac{V_0^2 \sinh^2 k_2 a}{V_0^2 \sinh^2 k_2 a + 4E(V_0 - E)} \quad (2.16)$$

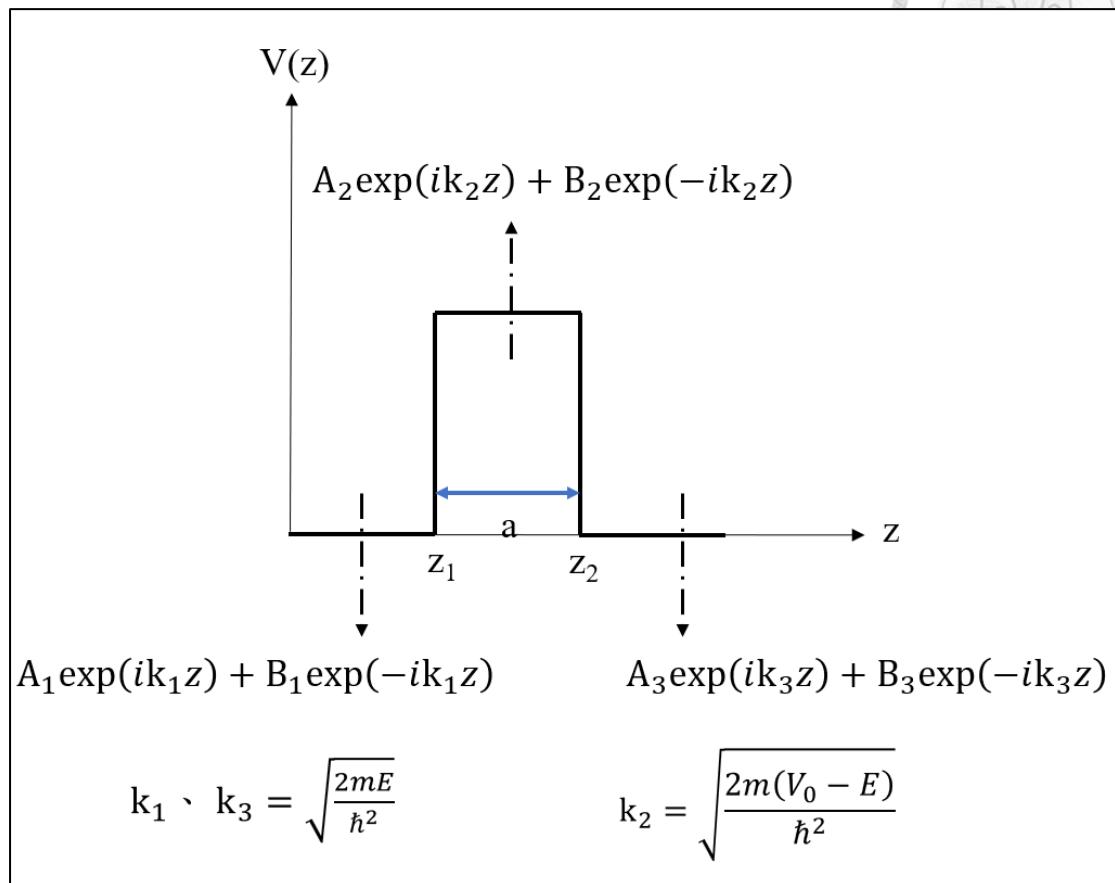

## 雙能障量子井 (Double Barrier Quantum Well)

根據上述單一能障之分析概念，雙能障量子井 (Double-Barrier Quantum Well, DBQW) 結構中各區域的波函數亦可由一維薛丁格方程式解得其一般解。其波函數形式如圖 2.13 所示，涵蓋五個區域，分別對應於入射區、兩個位障區、量子井區與透射區，並以對應係數  $A_i$ 、 $B_i$  表示。

圖 2.13 電子波函數在雙能障量子井結構中每個區域之一般解

電子波函數滿足邊界條件

$$\Psi(z^-) = \Psi(z^+) \quad (2.17)$$

(2.17)表示波函數連續

$$\frac{1}{m_1} \frac{d\Psi}{dz} \Big|_{z-} = \frac{1}{m_2} \frac{d\Psi}{dz} \Big|_{z+} \quad (2.18)$$

(2.18)表示電流密度的連續，其中  $m_1$ 、 $m_2$  為不同材料之等效質量。

利用轉移矩陣法 (Transfer Matrix Method, TMM)，可將波函數表示

成：

$$\begin{bmatrix} A_1 \\ B_1 \end{bmatrix} = M_1 M_2 M_3 M_4 \begin{bmatrix} A_5 \\ B_5 \end{bmatrix} \quad (2.19)$$

結構最右端不再具有異質接面，因此電子波函數在該區域不會發生

反射，即係數  $B_5$  為零。穿透係數表示成<sup>[21]</sup>：

$$T_{2B} = \left| \frac{A_5}{A_1} \right|^2 = \left[ 1 + \frac{4R_{1B}}{T_{1B}^2} \sin^2(k_1 W - \theta) \right]^{-1} \quad (2.20)$$

其中，式(2.16)之  $R_{1B}$ 、式(2.15)之  $T_{1B}$ ，為單一能障之反射係數與穿透係數。

$\theta$  定義為<sup>[21]</sup>：

$$\tan \theta = \frac{2k_1 k_2 \cosh k_2 a}{(k_1^2 - k_2^2) \sinh k_2 a} \quad (2.21)$$

### 第三章 雙能障之穿隧奈米結構製作

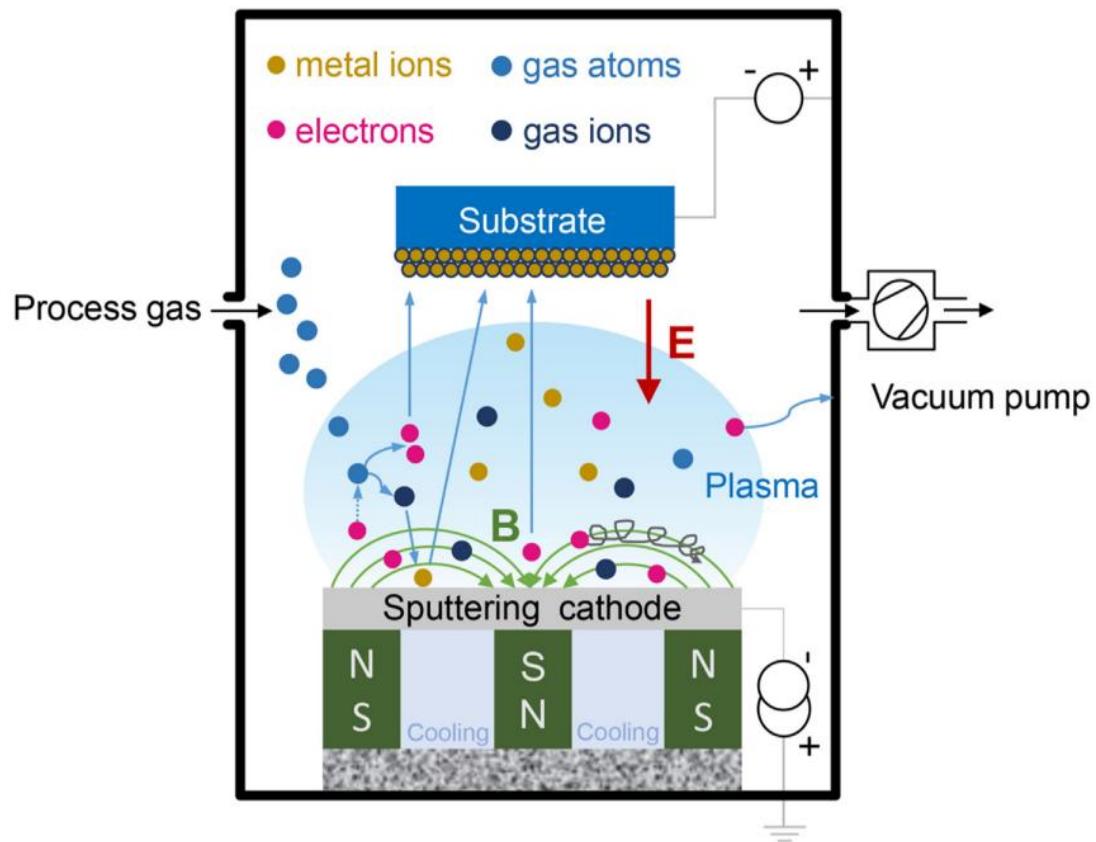

#### 3.1 滅鍍技術

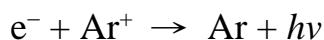

濺鍍 (Sputtering) 是一種物理氣相沉積 (Physical vapor deposition, PVD) 技術，主要在高真空環境下進行。通入少量惰性氣體（通常為氮氣），並於靶材與基板之間施加高電壓，形成電場。腔體內的陰極會釋放出少量自由電子，這些電子在電場的加速下與氮氣原子發生碰撞，進而使氮氣原子電離，產生帶正電的氮離子。這些氮離子在電場的驅動下加速撞擊靶材，將靶材表面的原子擊出，並在基板上沉積，形成薄膜，如下式：

為了提升濺鍍過程中的反應效率，在靶材底部設置磁鐵，藉由磁場來限制自由電子的運動路徑，使電子在靶材上方區域來回運動，增加其與氮氣原子碰撞的機率，進而提高等離子體密度與氮離子產生效率。在此過程中，部分電子與氮離子也可能發生複合反應並釋放能量，表現為腔體內等離子體的微弱發光，但對濺鍍效率的影響有限，如下式：

上述能量釋放的過程會以光與熱的形式呈現，這種現象稱為輝光放電。因此，透過觀察等離子體所發出的光的顏色與亮度，便可初步

判斷反應是否正常進行，以及腔體內氣體成分是否正確。在濺鍍過程中，產生的帶正電氣離子會被加速並轟擊位於陰極的靶材，使靶材表面原子因動能衝擊而脫離，進一步濺射至基板表面並沉積，最終形成薄膜。示意圖如下圖所示：

圖 3.1 磁控射頻濺鍍機原理示意圖<sup>[22]</sup>

濺鍍技術主要可分為直流濺鍍 (DC Sputtering) 與射頻濺鍍 (RF Sputtering) 兩種類型。直流濺鍍系統中所施加的電壓為固定方向，當帶正電的氣離子持續轟擊靶材表面時，若靶材為絕緣材料，表面正電荷將逐漸累積，導致電場被中和，進而使電漿熄滅並終止濺鍍反應。因此，直流濺鍍僅適用於導電性良好的金屬靶材。相較之下，射頻濺

鍍採用交流電場，電壓方向會隨時間變化，使絕緣靶材表面的電荷無法持續累積，從而穩定維持等離子體，適用於金屬與絕緣材料的濺鍍。在實際元件製程中，吾人採用射頻濺鍍於基板上濺鍍二氧化鋯、氧化銦錫、氧化鋻等材料，並利用直流濺鍍鎔金屬作為電極。

### 3.2 微影製程與濕蝕刻技術

微影製程 (Photolithography) 為現代半導體製程中不可或缺之核心技術，其目的為將設計完成之元件圖案精確轉印至基板上的功能薄膜層。本研究採用正光阻 (S1813) 進行圖形定義，並以旋轉塗佈 (Spin Coating) 方式將感光材料均勻塗佈於基板表面，形成均勻的光阻。為確保製程與膜厚一致性，光阻塗佈前將 S1813 光阻靜置於室溫環境中 10 分鐘，以減少溫度對黏度與塗佈均勻度之影響。旋轉塗佈過程採兩階段進行：先以每分鐘 1000 轉 (1000 rpm) 預旋塗 10 秒，隨後以每分鐘 4500 轉 (4500 rpm) 旋塗 30 秒以達成均勻薄膜。塗佈完成後，進行軟烘 (Soft Bake)，於 120 °C 下加熱 1 分鐘以去除殘留溶劑，提升光阻膜之附著性與熱穩定性。考量本研究需製作尺寸小於 10 微米的微米柱結構，選擇濕蝕刻 (Wet Etching) 作為主要圖形轉移方式。相較於掀離法 (Lift-off)，濕蝕刻在圖形解析度、邊緣定義以及蝕刻深度控制方面具有更高之準確性與穩定性。

製程中，先於基板上沉積所需材料層（如金屬或氧化物），再透過微影製程將圖形轉印至材料表面，最後以高選擇性之蝕刻液進行濕式蝕刻處理。

為抑制過度側向腐蝕 (Lateral Etching) 造成之圖形失真與結構崩塌，針對光阻厚度與蝕刻液配方進行優化調整。於本研究中，使用稀鹽酸作為蝕刻液，調配比例為去離子水與濃鹽酸 (HCl) 之體積比 5:1，以降低蝕刻速率、提升控制精度，同時減少對下層金屬層可能產生之腐蝕損傷。

### 3.3 樣品設計

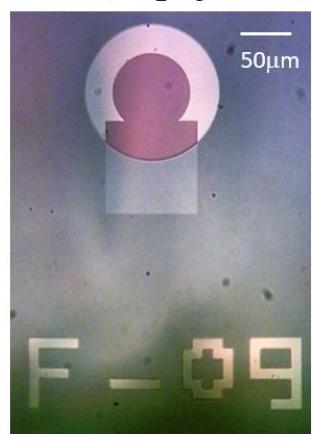

為實現具穿隧特性之穿隧奈米結構，吾人採用氧化鎵作為包覆微米柱結構之材料、設計微米小孔圖形之光罩，並透過微影製程定義圓柱形圖案。

此光罩圖案設計考量包括：

#### (1) 微米柱直徑設定：

元件最小直徑設定為 3 微米，盡可能將元件面積縮小，可以大幅度降低電流，有助於觀察穿隧主導之量子傳輸現象。

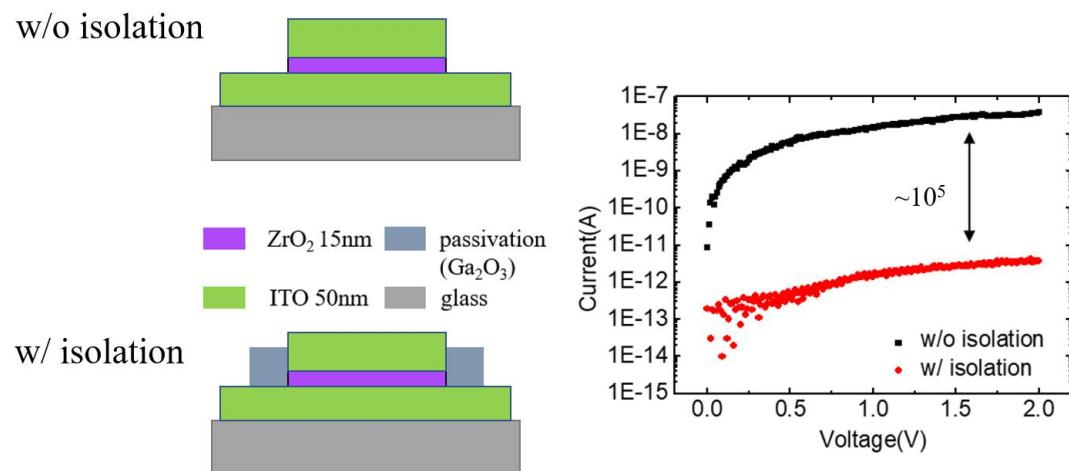

## (2) 絶緣包覆設計：

微米柱周圍採用高電阻氧化鎔進行包覆，形成柱狀絕緣結構，根據吾人先前之實驗結果（如圖 3.2 所示），比較未包覆與包覆絕緣層之元件可觀察到明顯電性差異。於相同偏壓條件下，包覆絕緣層之元件其漏電流量降低約五個數量級，約為未包覆結構的  $10^{-5}$  倍。此結果證實絕緣層能有效隔絕橫向載子傳輸路徑，提升縱向通道中電場控制與導通。

圖 3.2 絶緣層包覆元件電流比較

## 3.4 穿隧奈米結構製程流程

### 基本清洗

1. 將樣品浸泡於  $85^{\circ}\text{C}$  的丙酮中，並使用超音波震盪清洗 5 分鐘，以有效去除表面之有機雜質。

2. 再將樣品泡入甲醇中，以超音波震盪器震洗 5 分鐘，去除丙酮殘留。

3. 接著以去離子水 (Deionized water, DI water) 沖洗，去除甲醇殘留，再以氮氣槍吹乾，以上完成對有機物的清潔。

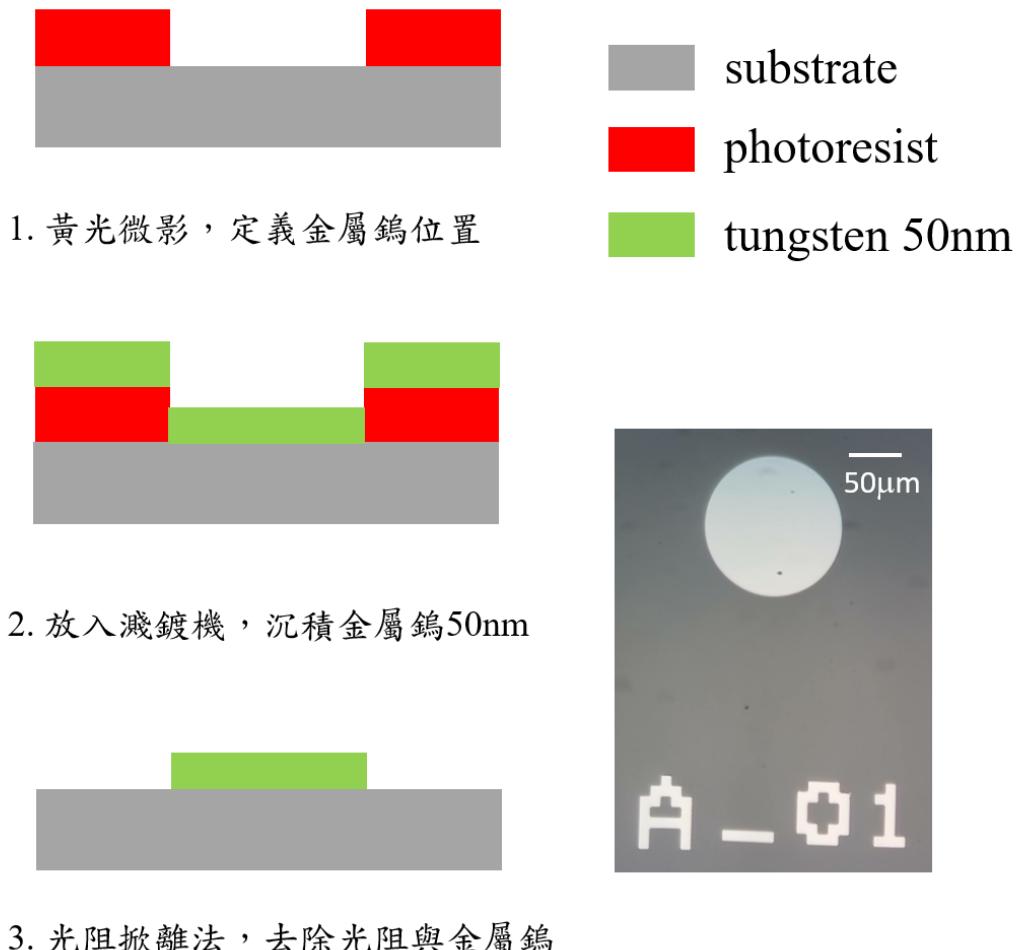

### 金屬製作

在垂直式穿隧二極體 (Resonant Tunneling Diode, RTD) 製作過程中，需於元件底部製作導電電極，作為載子傳輸的接觸端。本研究選用鎢 (Tungsten, W) 作為下電極材料，主要考量其具備高熔點、低電阻率以及優異的化學穩定性，同時提供穩定的導電特性。

1. 在石英基板滴上正光阻 (S1813)，並透過旋轉塗佈 (spin coating) 進行光阻塗佈。首先以每分鐘 1000 轉預旋塗 10 秒，使光阻均勻鋪展於基板表面；隨後以每分鐘 4500 轉旋塗 30 秒，再將樣品放上加熱台以  $120^{\circ}\text{C}$  加熱 60 秒，增加光阻鍵結，以形成厚度均勻且附著良好的光阻。

2. 曝光 7 秒，定義下電極位置，使用顯影液(MF-319)進行顯影，並用去離子水沖洗後，氮氣槍吹乾。

3. 迅速放入直流濺鍍機中( DC-sputter )，濺鍍金屬鎢，厚度約為 50 奈米。

4. 將樣品浸入丙酮中，利用光阻掀離法 ( lift-off ) 去除區域上殘留的 S1813 光阻與覆蓋其上的金屬薄膜。掀離完成後，進一步以甲醇與去離子水進行清洗，以去除表面有機殘留物，最後以氮氣槍吹乾樣品，完成電極圖案。

圖 3.3 底層金屬鎢製程流程

## 微米柱隔離

製作低電流特性之微米柱元件時，若元件不隔離，側壁會造成嚴重的漏電流，影響元件電壓-電流特性，亦會造成元件製作完成後，水氣的直接進入，進而導致元件特性改變。

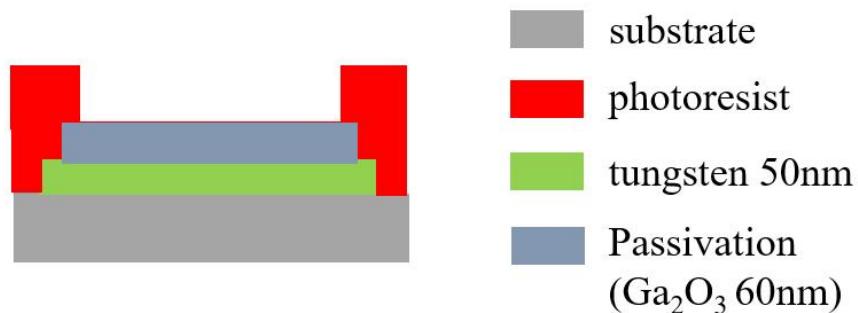

1. 首先，在製作好金屬鎢的石英基板上濺鍍一層厚度約 60 奈米的絕緣薄膜，作為後續微米柱結構的包覆層。本研究選用氧化鎢 ( $\text{Ga}_2\text{O}_3$ ) 作為絕緣層材料。

2. 將已沉積氧化鎢 ( $\text{Ga}_2\text{O}_3$ ) 薄膜之石英基板滴上正光阻 (S1813)，並透過旋轉塗佈進行光阻塗佈。首先以每分鐘 1000 轉預旋塗 10 秒，使光阻均勻鋪展於基板表面；隨後以每分鐘 4500 轉旋塗 30 秒，再將樣品放上加熱台以  $120^\circ\text{C}$  加熱 60 秒，增加光阻鍵結，以形成厚度均勻且附著良好的光阻。

3. 曝光 7 秒，定義絕緣層位置，放入顯影液約 55 秒，進行顯影與蝕刻氧化鎢，並用去離子水沖洗後，氮氣槍吹乾。

4. 為確保可以蝕刻至底層金屬鎢，再將樣品放入以去離子水與氯化氫 ( $\text{HCl}$ ) 5:1 之溶液 60 秒，最後以去離子水沖洗後，氮氣槍吹乾。

4. 放入濺鍍機，沉積60nm氧化鎵

5. 黃光微影，定義絕緣層位置

6. 顯影液(MF-319)進行顯影與蝕刻

再放入稀鹽酸，確保蝕刻完全

7. 丙酮去除表面光阻

■ substrate

■ photoresist

■ tungsten 50nm

■ passivation

( $\text{Ga}_2\text{O}_3$  60nm)

圖 3.4 蝕刻絕緣層製程流程

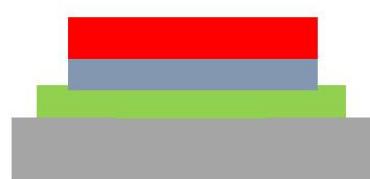

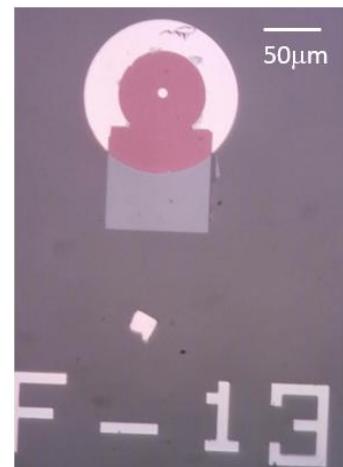

### 蝕刻微米柱孔洞

透過蝕刻形成孔洞，使微米柱結構能完整嵌入絕緣層之中，不僅可以有效保護元件，降低外部水氣或污染物進入，進而提升元件的穩定性與可靠性。

1. 將已蝕刻出絕緣層圖形的樣品滴上正光阻(S1813)，以每分鐘 1000 轉預旋塗 10 秒，再以每分鐘 4500 轉旋塗 30 秒，再將樣品放上加熱台以  $120^\circ\text{C}$  加熱 60 秒。

2. 曝光 7 秒，定義微米柱位置，放入顯影液約 45 秒，進行顯影與蝕刻氧化鎔，形成出不同尺寸孔洞，並用去離子水沖洗後，氮氣槍吹乾。

3. 再將樣品放入以去離子水與氯化氫(HCl)5:1 之溶液，確保蝕刻完全，最後以去離子水沖洗後，氮氣槍吹乾。

8. 黃光微影，定義微米柱位置

9. 顯影液(MF-319)進行顯影與蝕刻

再放入稀鹽酸，確保蝕刻完全

圖 3.5 蝕刻微米孔洞製程流程

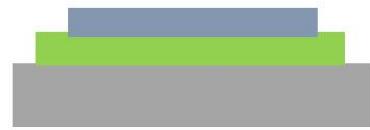

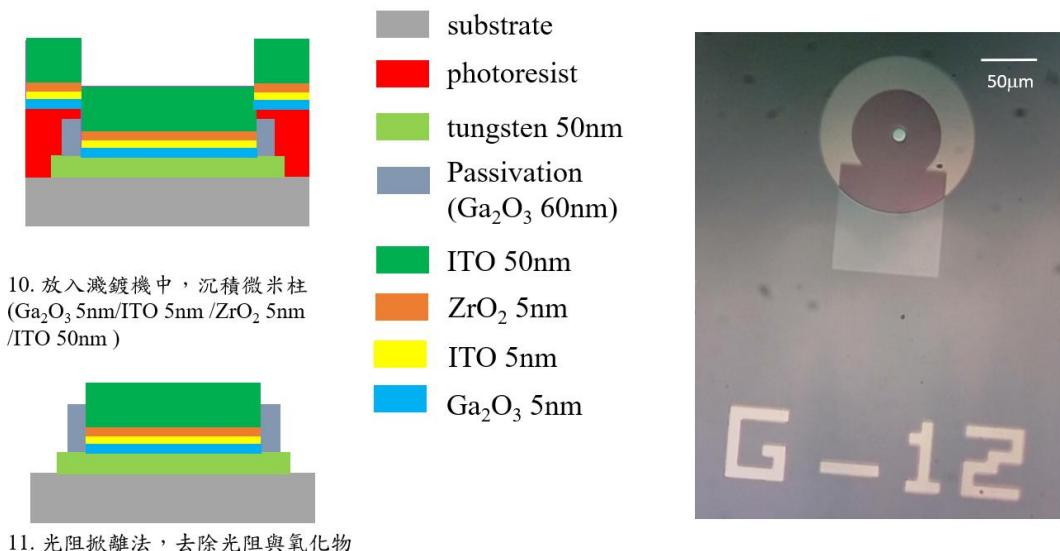

## 製作微米柱

1. 在確認蝕刻至金屬鎢後，放入磁控射頻濺鍍機中 (RF-sputter)，生長微米柱結構，氧化鎔/氧化銦錫/二氧化鋯/氧化銦錫，厚度約  $\text{Ga}_2\text{O}_3$  /ITO / $\text{ZrO}_2$  /ITO ( 5/5/50nm ) 。

2. 將樣品浸入丙酮中，利用光阻掀離法 (lift-off) 去除區域上殘留的 S1813 光阻與覆蓋其上的氧化物薄膜。掀離完成後，進一步以甲醇與去離子水進行清洗，以去除表面有機殘留物，最後以氮氣槍吹乾樣品，完成微米柱製作。

圖 3.6 濺鍍微米柱製程流程

最終成功製作出以金屬鎢作為底電極，並由氧化鎔( $\text{Ga}_2\text{O}_3$ )包覆元件四周的穿隧奈米結構，其元件結構示意圖如圖 3.7 所示。

圖 3.7 氧化鎗/氧化鋯穿隧奈米結構元件示意圖

## 第四章 穿隧奈米結構元件電性量測與模擬結果

### 4.1 電流電壓量測系統簡介

完成氧化鎵/氧化鋁雙能障穿隧奈米結構元件製作後，本章將進行直流電性（DC）量測，藉由電流-電壓特性分析，探討元件之傳輸行為與電性特徵。首先將介紹本研究使用量測系統，接著詳述量測之結果與相關討論。

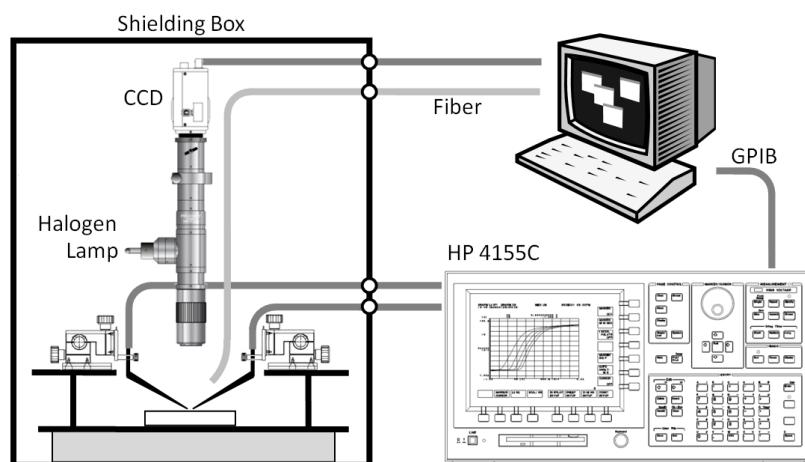

圖 4.1 顯示本研究量測穿隧奈米結構元件直流電性之實驗儀器架構。量測系統中，電腦透過通用介面匯流排（General Purpose Interface Bus, GPIB）控制半導體參數分析儀（Semiconductor Parameter Analyzer, HP 4155C），以進行元件的電流-電壓特性量測。量測過程中，數據透過介面匯流排即時回傳至電腦儲存分析。此外，整個量測系統置於接地之屏蔽箱（Shielding Box）內，以有效隔絕外界電磁雜訊干擾，確保量測數據之準確性與穩定性。

圖 4.1 直流電性量測實驗儀器架構圖

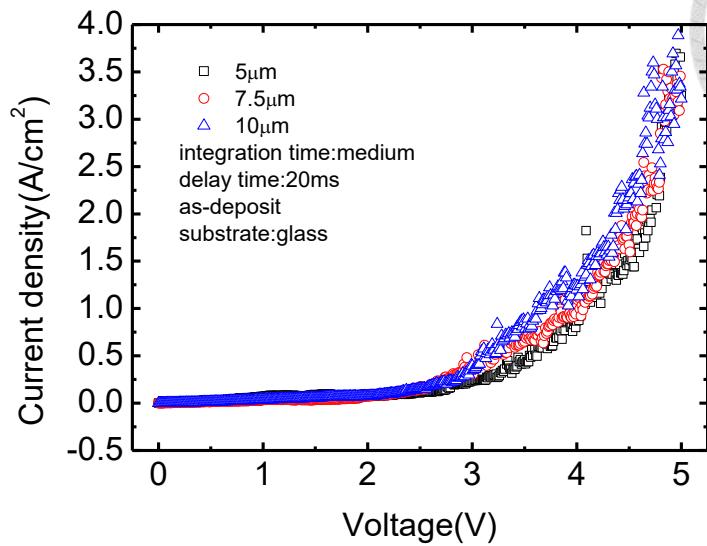

## 4.2 材料介面能障高度分析

為釐清穿隧奈米結構中各層氧化物與金屬之間的能帶高度，吾人分別製作以下兩類樣品：

(1)  $\text{ZrO}_2$  為中間氧化層之金屬/氧化物/金屬結構

(2)  $\text{Ga}_2\text{O}_3$  為中間氧化層之金屬/氧化物/金屬結構

上下電極分別選用氧化銻錫 (Indium Tin Oxide, ITO) 與金屬鎢進行搭配，估算出各層相異材料之能障高度。

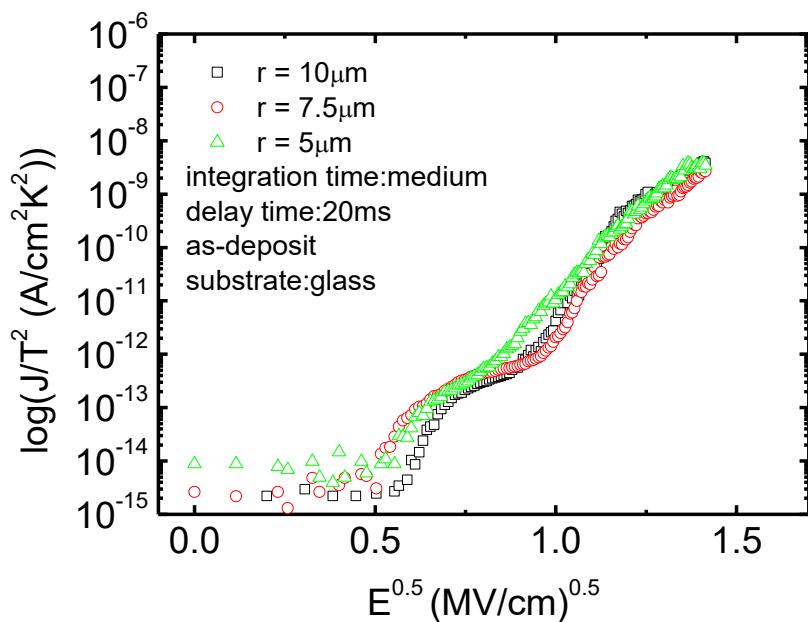

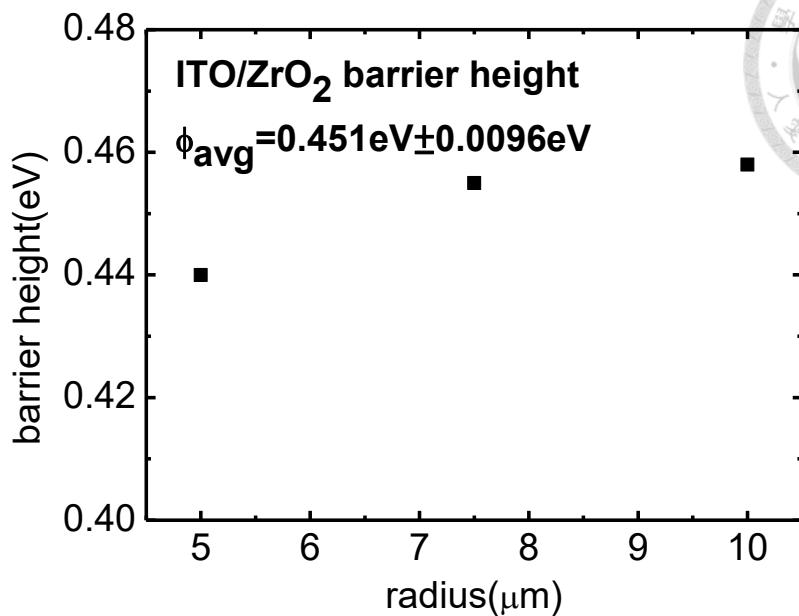

吾人分別量測半徑為 5 微米、7.5 微米與 10 微米之微米柱結構，進行電流-電壓特性分析。電壓掃描範圍為 0 至 3V 再從 3V 至 0V， $\text{ITO}/\text{Ga}_2\text{O}_3$  樣品掃描範圍為 0 至 5V，延遲時間均設定為 20 毫秒，積分時間設定為中等 (medium)。為排除尺寸差異對電流大小的影響，將量測所得之電流值以微米柱橫截面積進行正規化，轉換為電流密度 (current density)，公式如下：

$$J = \frac{I_{measure}}{\pi r^2} \quad (4.1)$$

其中  $I_{measure}$  為量測電流， $r$  為元件半徑， $J$  為電流密度。

電場定義為：

$$E = \frac{V_{measure}}{d_{oxide}} \quad (4.2)$$

$V_{measure}$  為量測時所施加電壓， $d_{oxide}$  為氧化層厚度。

分析結果顯示，不同尺寸之微米柱在相同偏壓條件下展現相同之電流密度特性，排除微米柱的尺寸變化對元件整體電性的影響，元件特性主要由材料及結構本質決定。

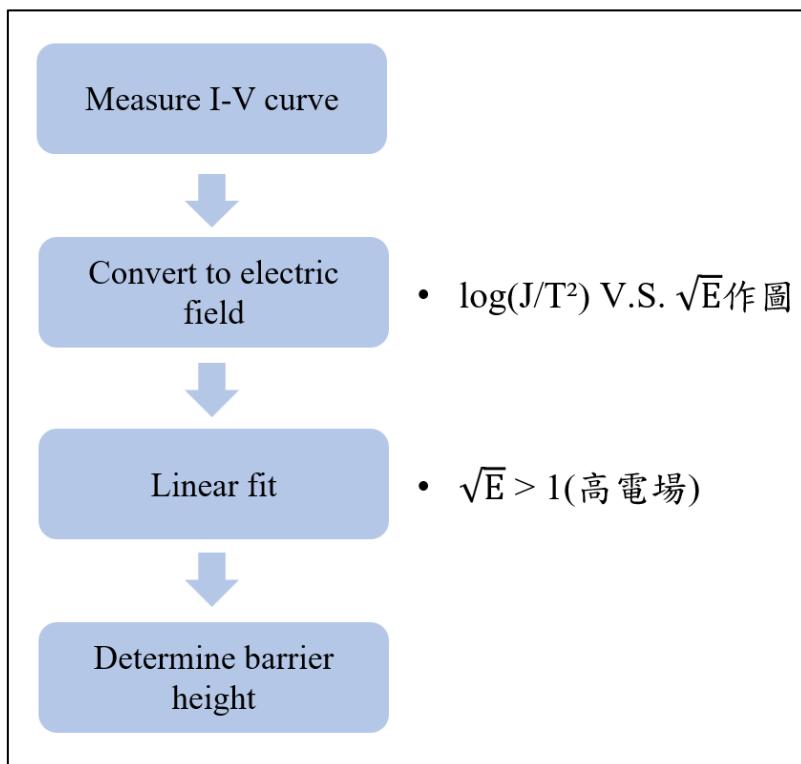

根據第二章介紹之熱發射理論公式，式(2.1)。

$$J = A^* T^2 \exp \left[ \frac{-q(\phi_B - \sqrt{qE/4\pi\epsilon})}{kT} \right]$$

將量測結果繪製為  $\log(J/T^2)$  相對於  $E^{0.5}$  作圖，應呈線性關係。針對高電場區域( $E^{0.5} > 1$ )進行線性擬合<sup>[23]</sup>，由擬合曲線之截距，即可進一步萃取出金屬與氧化層介面之能障高度（barrier height）。

圖 4.2 萃取能障高度流程示意圖

表 4.1 能障高度分析之實驗參數

|                          | $\text{ZrO}_2$ | $\text{Ga}_2\text{O}_3$ |

|--------------------------|----------------|-------------------------|

| 厚度(d)                    | 15nm           | 15nm                    |

| 等效質量( $m_{\text{eff}}$ ) | $1.2m_0$       | $0.35m_0$               |

| 溫度                       | 300K           | 300K                    |

**W/ZrO<sub>2</sub>/W ( 50/15/50nm )**

圖 4.3 W/ZrO<sub>2</sub>/W 結構之電壓-電流密度結果

圖 4.4 W/ZrO<sub>2</sub>/W 結構之 log(J/T<sup>2</sup>)對 E<sup>0.5</sup> 特性圖

圖 4.5 W/ZrO<sub>2</sub> 能障高度與元件半徑之關係

## ITO /ZrO<sub>2</sub>/ITO ( 50/15/50nm )

圖 4.6 ITO /ZrO<sub>2</sub> /ITO 結構之電壓-電流量測結果

圖 4.7 ITO /ZrO<sub>2</sub> /ITO 結構之  $\log(J/T^2)$  對  $E^{0.5}$  特性圖

圖 4.8 ITO/ZrO<sub>2</sub>能障高度與元件半徑之關係

#### W/Ga<sub>2</sub>O<sub>3</sub>/W ( 50/15/50nm )

圖 4.9 W/Ga<sub>2</sub>O<sub>3</sub>/W 結構之電壓-電流密度量測結果

圖 4.10 W/Ga<sub>2</sub>O<sub>3</sub>/W 結構之 log(J/T<sup>2</sup>)對 E<sup>0.5</sup> 特性圖

圖 4.11 W/ Ga<sub>2</sub>O<sub>3</sub>能障高度與元件半徑之關係

## ITO/ $\text{Ga}_2\text{O}_3$ /ITO ( 50/15/50nm )

圖 4.12 ITO/  $\text{Ga}_2\text{O}_3$ /ITO 結構之電壓-電流密度量測結果

圖 4.13 ITO/  $\text{Ga}_2\text{O}_3$ /ITO 結構之  $\log(J/T^2)$  對  $E^{0.5}$  特性圖

圖 4.14 ITO/  $\text{Ga}_2\text{O}_3$  能障高度與元件半徑之關係

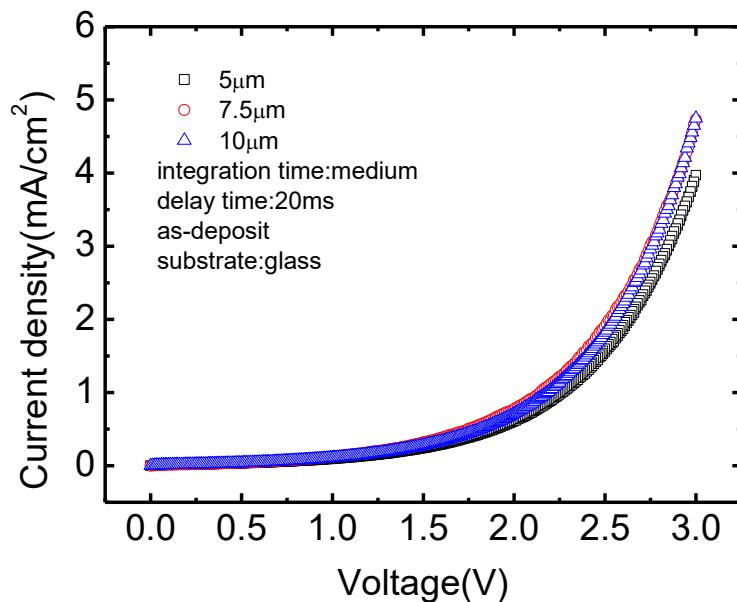

最後將結果整理，如表 4.2。

表 4.2 材料介面能障高度分析結果

Parameter:

(1)  $\text{ZrO}_2$  ,  $m^*/m_0 = 1.2$  ,  $d = 15\text{nm}$  ,  $T = 300\text{K}$

(2)  $\text{Ga}_2\text{O}_3$  ,  $m^*/m_0 = 0.35$  ,  $d = 15\text{nm}$  ,  $T = 300\text{K}$

ITO ,  $d = 50\text{nm}$  ; W ,  $d = 50\text{nm}$

|                | W/ZrO <sub>2</sub> | ITO/ ZrO <sub>2</sub> | W/Ga <sub>2</sub> O <sub>3</sub> | ITO/ Ga <sub>2</sub> O <sub>3</sub> |

|----------------|--------------------|-----------------------|----------------------------------|-------------------------------------|

| Barrier height | 0.527 eV           | 0.451 eV              | 0.338 eV                         | 0.276 eV                            |

### 4.3 穿隧奈米結構電性分析與穿透係數擬合

為了解穿隧通道形成條件，吾人以轉移矩陣法建構穿透係數模型，並以 MATLAB 撰寫程式進行數值計算，分析非對稱雙能障量子井結構中之穿隧行為。

在 4.2 節中，吾人透過不同金屬與氧化層結構，萃取出各層材料間之介面能障高度，進一步釐清本研究所製作之穿隧奈米結構元件的能帶排列與結構特性。模擬模型為雙能障量子井結構，元件製程堆疊順序如圖 4.15。

進行實驗與模擬結果之疊圖比較時，吾人需將實驗電流掃描的偏壓值轉換為對應電場。實驗部分之電壓掃描範圍為 0 至 6 V 再從 6V 至 0V，在連續量測過程中，每組量測數據(Scan 1、Scan 2、Scan 3)皆間隔五分鐘後再次量測。延遲時間設定為 20 毫秒，積分時間設定為中等 (medium)。對應之電場以元件氧化層厚度進行換算，作為電場橫軸(單位為 MeV/cm)。此一方法採用「平均電場」近似，旨在提供模擬與實驗可比對之橫軸基準。以下列公式表示：

$$E = \frac{V_{\text{measure}}}{d_{\text{DB}} + d_{\text{QW}}} \quad (4.3)$$

其中  $V_{\text{measure}}$  為外加電壓， $d_{\text{DB}}$  為雙能障寬度， $d_{\text{QW}}$  為量子井寬度。

模擬部分針對穿隧結構（即量子井與雙能障結構）進行穿透係數之計算，因此其橫軸所對應之電場值則以結構厚度為分母計算。以下列公式表示：

$$E = \frac{\Phi_B}{q \cdot (d_{DB} + d_{QW})} \quad (4.4)$$

其中  $\Phi_B$  為能障高度， $d_{DB}$  為雙能障寬度， $d_{QW}$  為量子井寬度。

上述處理方式隱含假設元件內部電場沿厚度方向呈近似線性分佈；然而，實際上由於不同材料層之介電常數差異，將導致電位於各層中分佈不均，進而使電場在垂直方向上產生不均勻性。為簡化模擬計算與比對分析，吾人於模擬中採用平均電場近似，作為穿透係數與實驗結果之對應依據。

圖 4.15 雙能障量子井擬合模型

表 4.3 非對稱雙能障量子結構之模擬參數

|                          | $\text{ZrO}_2$      | ITO      | $\text{Ga}_2\text{O}_3$    |

|--------------------------|---------------------|----------|----------------------------|

| 厚度(d)                    | 1.2nm               | 5.6nm    | 2.6nm                      |

| 等效質量( $m_{\text{eff}}$ ) | $1.2m_0$            | $0.5m_0$ | $0.35m_0$                  |

|                          | ITO/ $\text{ZrO}_2$ |          | W/ $\text{Ga}_2\text{O}_3$ |

| 能障高度( $\phi_B$ )         | 0.451eV             |          | 0.338eV                    |

圖 4.16 顯示本研究所設計之非對稱雙能障結構中，穿透係數模擬結果與實驗電流量測數據之對比分析，紅色資料點為實驗量測電流，藍線則是以轉移矩陣法建立模型計算之穿透係數。在實驗中可觀察到多個電流峰值與負微分電阻現象，顯示其行為有別於典型共振穿隧二極體常見之單一共振峰特性。推測在非對稱雙能障量子井結構中，入射

電子能量於不同電場條件下與多組準束縛態能階發生能量對齊，形成多組穿隧電流，進而產生階梯狀電流特徵。在模擬結果中，於 0.163、0.284 與 0.455 MeV/cm 等電場強度下可明顯觀察到穿透係數之尖峰，對應於實驗中所觀測到的電流峰值，顯示在該些電場條件下，電子具有較高之穿隧機率。然而，在約 0.38 MeV/cm 處亦可觀察到額外電流峰值，在線性座標下之穿透係數模擬結果未呈現對應尖峰。進一步將模擬結果轉換為對數座標後，可於相同電場位置發現微弱之穿透係數提升(圖 4.17 紅色箭頭)，推測可能為準束縛態能階與入射能量未完全對齊所致，或受限於結構中存在缺陷態與介面混合所引起之能障擾動，使得模擬與實驗略有偏移。

在有限深量子井中，波函數於井外會發生穿透並呈指數衰減，且當電子能量趨近井外位能高度 ( $V_0$ ) 時，井內電子的行為逐漸趨近於自由粒子，亦意味著能階分布趨於連續。然而在圖 4.17 中可以觀察到，隨著入射電子能量的增加，所出現的穿透係數峰值間隔反而增大，與前述結果相反。此現象的原因在於，於雙能障量子井中，隨著入射電子能量提升，其德布羅意波長 (de Broglie wavelength) 變短，可表示為：

$$\lambda = \frac{h}{p} = \frac{h}{\sqrt{2m^*E}} \quad (4.5)$$

其中  $\lambda$  為德布羅意波長  $h$  為普朗克常數， $E$  表示為入射電子能量。

滿足駐波條件：

$$kL_w = n\pi, \quad n = 1, 2, 3 \dots \quad (4.6)$$

$$k = \frac{\sqrt{2m^*E}}{\hbar} \quad (4.7)$$

其中  $k$  為電子波數， $L_w$  為量子井寬度。

將電子波數( $k$ )代入式(4.7)，可得：

$$\frac{\sqrt{2m^*E}}{\hbar} L_w = n\pi \quad (4.8)$$

則在第  $n$  個能階可以表示為：

$$E_n = \frac{n^2\pi^2\hbar^2}{2m^*L^2}, \quad n = 1, 2, 3 \dots \quad (4.9)$$

相鄰能階間距 $\Delta E$ 可以表示成：

$$\Delta E = \frac{(2n+1)\pi^2\hbar^2}{2m^*L^2}, \quad n = 1, 2, 3 \dots \quad (4.10)$$

因此當量子數  $n$  越大，相鄰能階的間距也隨之增大，對應於穿透係數

曲線中共振峰值的間隔亦逐漸變寬。

圖 4.16 首次掃描實驗數據與穿透係數模擬計算對比(線性)

圖 4.17 穿透係數模擬計算結果與實驗數據對比(對數)

圖 4.18 為相同元件經重複掃描後之量測結果。可見雖穿透係數尖峰位置與首次掃描一致，但在  $0.284 \text{ MeV/cm}$  之實驗電流峰值已被掩蓋，僅在  $0.163$  與  $0.455 \text{ MeV/cm}$  附近仍可觀察到明顯電流峰值。此現象推測可能與材料缺陷累積、陷阱態填充、或能障結構之變化等因素相關，使元件於經歷多次高電場掃描後傳輸機制改變，使部分原有穿隧條件無法再現。

圖 4.18 連續掃描元件後穿透係數與實驗數據對比(線性)

圖 4.19 採用對數繪製模擬與實驗資料，可觀察到多組由模擬預測之準束縛態能階所對應之穿透係數。然而，在實驗量測中，僅在部分電場區間觀察到明顯的電流峰值，其餘低穿透係數對應之共振態則未能穩定呈現，可能原因為元件之穿隧電流極低，已接近儀器量測極限，或因元件陷阱、載子散射機制等導致共振路徑不穩定。然而，在經歷多次高偏壓掃描後，元件最終損壞。此現象突顯出本研究元件仍

處於開發初期階段，未來須進一步優化材料品質與堆疊結構穩定性，

以提升共振特性之重現性與可靠度。

圖 4.19 連續掃描元件後穿透係數與實驗數據對比(對數)

整體而言，本模擬結果成功對應穿隧共振發生位置，並與元件首次掃描之實驗數據具有良好一致性，顯示建立之模型具有解釋共振條件的能力。雖然隨著掃描次數增加，實驗結果逐漸衰退，顯示共振穿隧特徵難以穩定重現，反映出材料品質與製程均勻性對元件穩定性及穿隧效應再現性具有關鍵影響。

基於上述觀察，下一小節將進一步分析當共振條件不成立時，元件所呈現之導電行為與潛在傳輸機制，作為後續理解與改善之基礎。

#### 4.4 電場方向之陷阱輔助穿隧行為分析

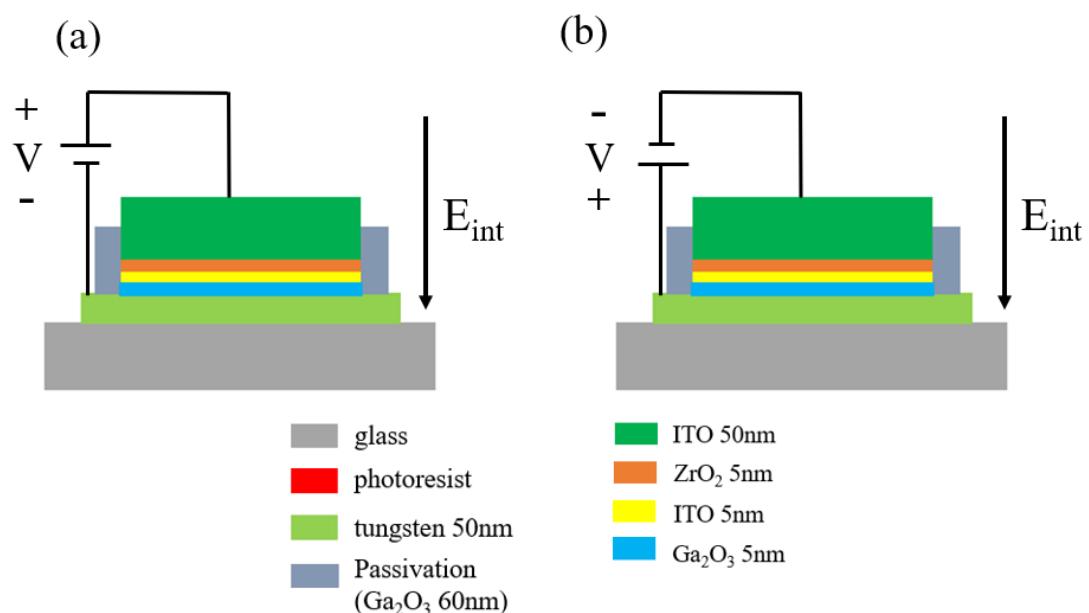

在分別確認氧化鋯、氧化鎵與金屬鎬、氧化銅錫間的能障高度後，接續進行共振穿隧二極體元件之直流電性特性分析。量測方式分為，圖 4.20(a)電場由上至下( ITO 至 W )，與圖 4.20(b)電場由下至上( W 至 ITO )。

圖 4.20 (a)電場由 ITO 至 W (b)電場由 W 至 ITO

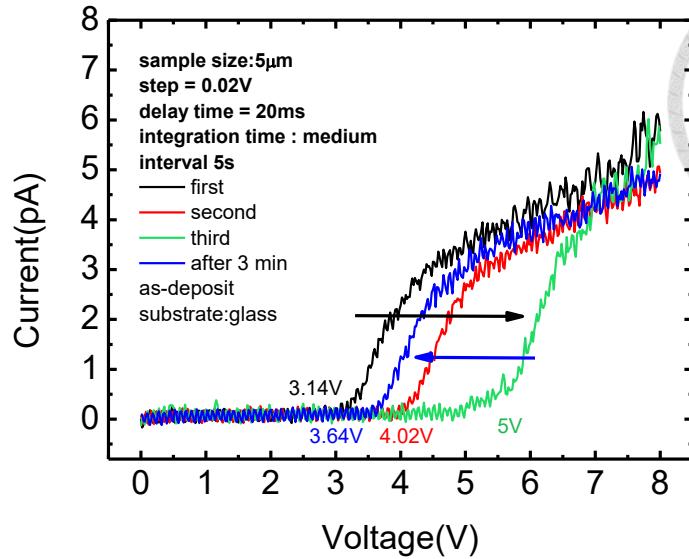

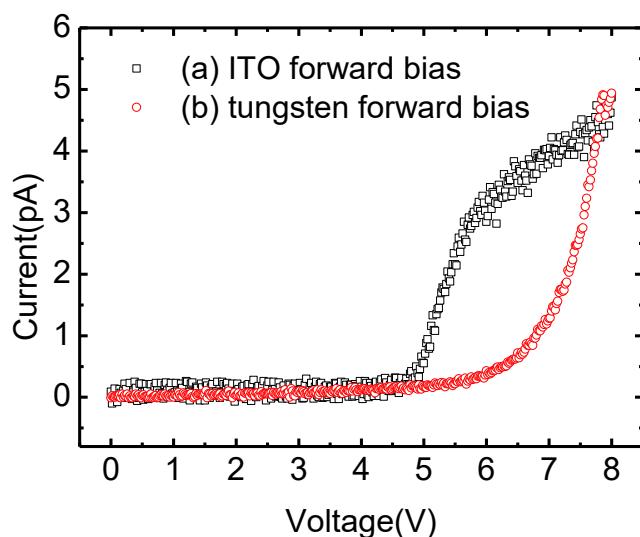

##### (a) 電場由上至下( ITO 至 W )，外加電場方向與內電場同向

實驗部分之電壓掃描範圍為 0 至 8 V 再從 8V 至 0V，在連續量測過程中，每組量測數據(黑、紅、綠線)皆間隔五秒後再次量測。延遲時間設定為 20 毫秒，積分時間設定為中等 (medium)。圖 4.21 電場由上至下，首次掃描時，此時外加電場方向與內電場同向，電子在較低偏壓下由底層鎬電極注入，氧化層中仍存在大量未被占據的陷阱

態，因此，迅速填滿陷阱並由陷阱態穿隧至氧化銦錫，形成導電路徑，

對應首次掃描之導通電壓約為 3.14 V。

隨著掃描次數增加，氧化層中的陷阱逐漸被電子佔據，導致有效的陷阱密度下降，電子傳輸過程中需跨越更長的穿隧距離或具備更高的能量才能離開陷阱態，進而造成導通電壓逐漸上升至約 3.64 V、4.02 V，在第三次掃描時，氧化層內部的陷阱態已趨於飽和，導致陷阱輔助穿隧路徑受限，電流無法有效導通。當偏壓提升至約 5V 時，電子才能獲得足夠能量，直接跨越能障或進行熱激發傳輸，進而產生明顯導通電流。(圖 4.21 黑色箭頭)

當樣品靜置三分鐘後再次掃描，導通電壓回降至約 3.64 V(圖 4.21 藍色箭頭)，顯示部分陷阱經歷電子釋放，可重新再被電子佔據穿隧至氧化銦錫。此結果證實氧化層內部陷阱不僅參與導電過程，其佔據與釋放行為亦會隨時間發生改變，顯著影響後續掃描的電流特性。

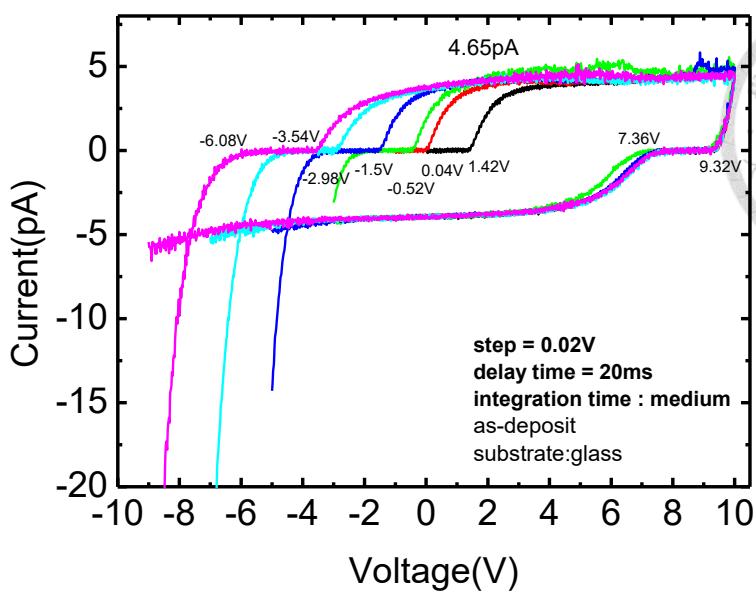

圖 4.21 連續掃描元件對電流特性之影響

為進一步探討元件陷阱態與元件間之特性關係，吾人嘗試於不同起始偏壓，量測電流-電壓特性，對共振穿隧二極體元件進行雙向掃描測試，圖 4.22 第一組掃描範圍設定為 0 至 10V( 黑線 )，並在達 10V 後再掃回 0V，在連續量測過程中，每組量測數據皆間隔五分鐘後再次量測。延遲時間設定為 20 毫秒，積分時間設定為中等 ( medium )。同一組曲線之正負掃描以相同顏色表示。為觀察掃描起始點對元件特性的影響，逐次改變起始偏壓，依序為 0V、-1V、-3V、-5V、-7V 與-9V。隨起始偏壓越往負值移動，整體電流-電壓曲線向負電壓方向平移，對應的導通電壓亦逐漸向負偏壓方向偏移。

圖 4.22 不同起始電壓與雙向掃描之電流特性

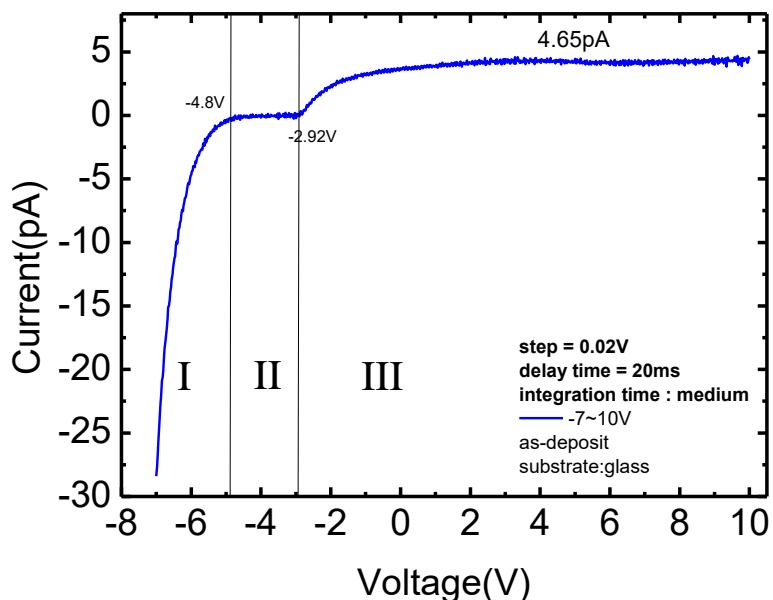

吾人為探討此一物理現象，將順向掃描之電流-電壓圖分割為三個區域進行討論(如圖 4.23)。

區域 I (  $-7V \sim -4.8V$  ):在高電場下，能帶傾斜程度大，電子可獲得足夠能量直接跨越界面能障，形成導通電流，在此區域藉由熱發射效應而形成的導電行為。隨著電場降低，入射電子能量減弱，進入下一區域。

區域 II (  $-4.8V \sim -2.92V$  ):外加偏壓已不足以使電子直接跨越能障，此時電子轉而進入氧化層中之陷阱態後，再穿隧至鄰近陷阱，逐漸填滿陷阱態。該階段導電機制由陷阱輔助穿隧 ( Trap-Assisted Tunneling, TAT ) 主導，當陷阱逐漸被電子填滿，穿隧通道逐步建立。

區域 III ( $>-2.92V$ ): 當氧化層中多數深能階陷阱已被電子佔據後，穿隧傳輸通道穩定形成，電子可連續透過陷阱穿隧機制傳遞至另一側電極，整體電流趨於飽和值，約為  $4.65\text{pA}$ 。

其中，在外加偏壓為  $0\text{V}$  時，仍可觀察到穩定電流產生，推測為材料內部存在內建電場 (built-in field)，使電子可在無外加電壓下透過陷阱輔助穿隧 (Trap-Assisted Tunneling, TAT) 機制傳輸至對側電極，因此可以觀察到穩定的電流。

圖 4.23 順向偏壓掃描結果分為三個區域分析

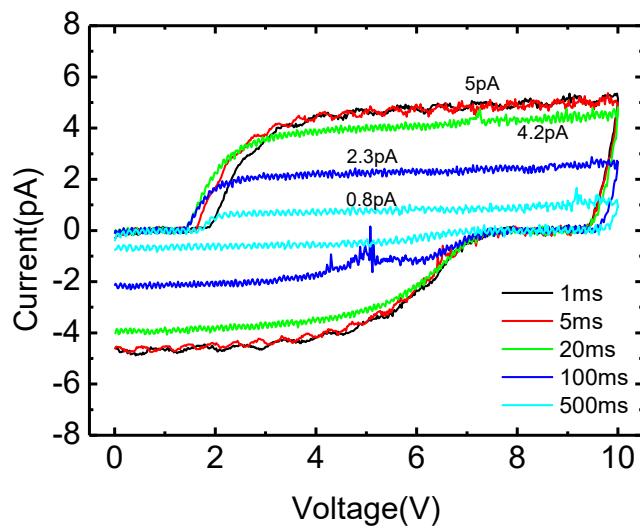

圖 4.24 為確認元件電流飽和行為是否受限於載子注入速率或電場誘發陷阱釋放，透過調整 HP 4155C 之延遲時間 (delay time)，探討不同掃描速率 ( $\text{dV/dt}$ ) 對電流-電壓曲線之影響。

半導體參數分析儀(HP 4155C)量測範圍為 100 pA 電流，並將積分時間設定為中等 (Medium) 時。根據儀器操作手冊，PLC (Power Line Cycle) 設為 10，因此在延遲時間 (Delay Time) 設定為 0 時，量測周期約為 0.1667 秒。

$$\text{掃描速率 (sweep rate)} = 10\text{PLC} + \text{延遲時間 (Delay Time)}$$

從圖 4.24 可觀察到，元件導通電流隨著延遲時間的變化而改變。由於延遲時間亦影響掃描速率，掃描速率越快 ( $dV/dt$  大)，導通電流相對大；反之，延遲時間越長，掃描速率越慢 ( $dV/dt$  小)，導通電流小。因此，導通電流大小與延遲時間呈正相關。

滿足電容器電流公式：

$$\frac{dQ}{dt} = I = C \frac{dV}{dt} \quad (4.11)$$

圖 4.24 不同掃描速率下滿足電容充放電特徵

(b) 電場由下至上(W 至 ITO)，外加電場方向與內電場反向

圖 4.25 比較當外加電場方向改變，分別由氧化銻錫或鎢施加電場時，所造成之導通電流差異。根據圖 2.6 所示之內建電場方向，當外加電場與內建電場方向相反時，導致能帶傾斜程度減緩，抑制電子注入與穿隧行為。特別是在低偏壓時，電子能量不足以直接跨越介面能障，難以提供有效之陷阱輔助傳輸路徑，導致整體穿隧機率下降。

實驗結果顯示，當由下方鎢電極外加電場（即外加場與內建場方向相反）時，元件直至約 6.8 V 才開始顯著導通，呈現二極體的電流特性。相對地，當由上方氧化銻錫施加偏壓時，在較低偏壓下即觀察到較大的導通電流，顯示外加電場順應內建電場方向有助於促進陷阱填充與穿隧形成。

圖 4.25 比較不同外加電場方向對電流特性的影響

綜合上述結果，材料本身所產生之內電場方向，將導致外加電場方向對載子傳輸機制產生顯著影響。當外加電場方向與內建電場一致時，元件主要呈現陷阱輔助穿隧行為；反之，當電場方向與內建場相反時，則展現典型的二極體導通特性。

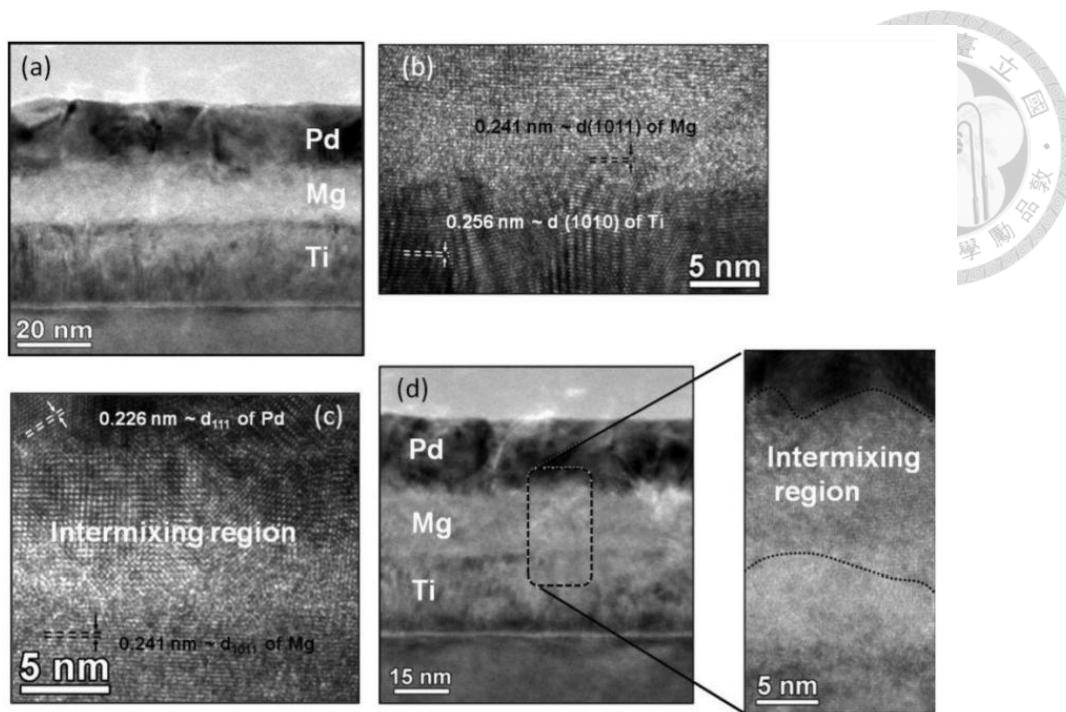

推測本研究中部分元件無法觀察到明顯共振穿隧電流特徵的原因，可能與濺鍍製程所導致之結構缺陷有關。於多層結構沉積過程中，介面易發生成核不均與薄膜間元素交互擴散，進而形成介面混合區（intermixing region）。圖 4.26 引自文獻<sup>[24]</sup>，展示以射頻濺鍍沉積之多層薄膜介面處，觀察到顯著的原子混合現象。介面混合區將導致能障與量子井之介面模糊，削弱準束縛態的侷限能力與能量選擇性，進而破壞理想共振條件的建立。此結構缺陷使得載子傳輸行為趨於連續，難以呈現階梯狀電流與負微分電阻等共振穿隧特徵，而轉由陷阱輔助穿隧（trap-assisted tunneling, TAT）機制主導。

圖 4.26 滅鍍機製作多層膜時發生介面混合現象<sup>[24]</sup>

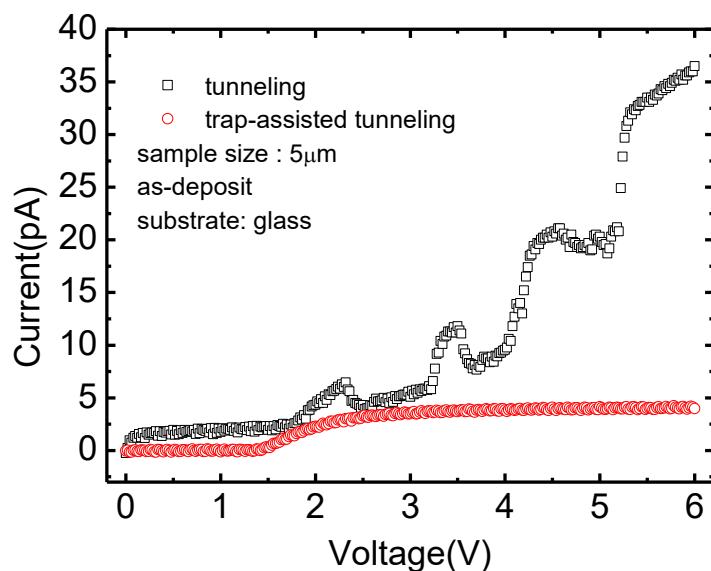

在 4.3 節中，已指出當多層薄膜於滅鍍製程中產生介面混合現象時，元件中之電子傳輸機制將主要受到陷阱輔助穿隧（Trap-Assisted Tunneling, TAT）效應主導。然而，若量子井結構中之入射電子能量與準束縛態對齊，則有機會觀察到共振穿隧二極體（Resonant Tunneling Diode, RTD）所特有之階梯狀電流特徵與負微分電阻（Negative Differential Resistance, NDR）行為。

圖 4.27 比較兩種不同穿隧機制下之電流特徵。實驗中，若因製程因素導致多層薄膜間出現成核不均、結構中斷或介面不連續等現象，可能使元件整體表現趨近於電容性結構，進而使載子傳輸機制主要受到陷阱輔助穿隧（Trap-Assisted Tunneling, TAT）所主導。在此類元件

中，缺乏明確之準束縛態與能量選擇性通道，導致穿隧行為趨於連續，對應之電流特徵亦僅呈現緩慢上升之趨勢，無明顯階梯狀變化。相較之下，於共振穿隧主導之元件中，則可觀察到多個電流共振峰與階梯狀導通特徵，顯示入射載子於特定電場強度下對齊準束縛能階時具有較高穿隧機率，呈現明確之能量選擇性傳輸行為。

圖 4.27 比較穿隧效應與陷阱輔助機制下元件特性

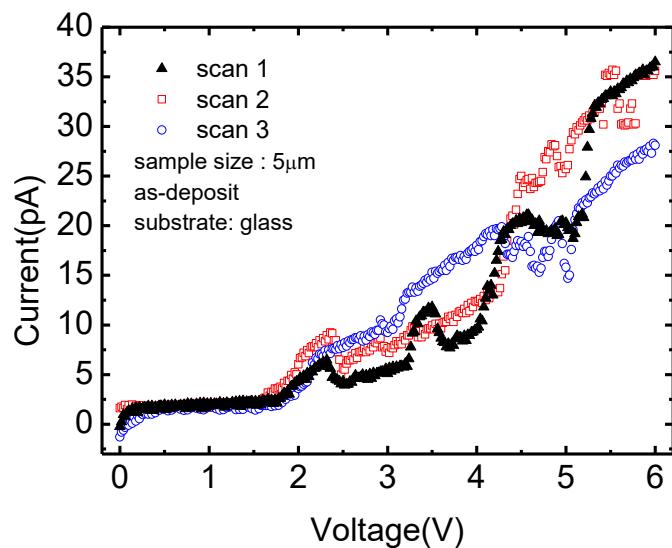

圖 4.28 在成功量測到共振穿隧特性後，透過連續掃描可進一步觀察其穩定性與再現性。於首次掃描中，在電壓約 2.32 V、3.5 V、4.56 V 與 5.36V，因入射能量與量子井中多組準束縛態對齊，電流急速上升，所產生多組電流峰值。然而，在連續掃描後，僅剩約 2.32V、5.36V 處仍保有較明顯之電流峰值，其他峰值則顯著衰退，顯示共振

穿隧現象在材料條件具備下可被驗證，唯其再現性與穩定性仍需進一步討論。

圖 4.28 連續掃描穿隧奈米結構

## 第五章 結論與未來展望

### 5.1 結論

本研究針對異質氧化物堆疊結構所構成之奈米穿隧二極體進行製作、電性分析與傳輸機制驗證。首先，重新設計元件結構，並以高電阻氧化鎵( $\text{Ga}_2\text{O}_3$ )作為絕緣層包覆微米柱側壁，成功製作具皮安培( $\text{pA}$ )等級電流之垂直導電元件。初步以單一氧化層與上下金屬電極構成對稱結構，並藉由熱發射理論(Thermionic Emission)分析材料間介面之能障高度，以還原元件能帶結構。

進一步，針對直徑  $5\text{ }\mu\text{m}$  之微米柱元件進行直流電性量測，透過掃描速率與電場方向調控，釐清載子於多層氧化物堆疊結構中之傳輸行為。量測中觀察到遲滯與非對稱電流特徵，並以陷阱輔助穿隧(Trap-Assisted Tunneling, TAT)機制進行理論解釋。針對以濺鍍方式沉積之氧化物薄膜，進行製程優化，改善濺鍍過程中可能造成之介面混合與結構缺陷等問題。經優化後之元件成功呈現階梯狀電流響應，顯示載子於特定電場下可能對齊準束縛態，產生共振穿隧效應。

本研究亦整合介面能障高度與材料有效質量參數，建立穿透係數模擬模型，並以 MATLAB 撰寫程式進行計算，對比模擬結果與實驗資料，驗證本元件結構之穿隧主導傳輸行為。進一步比較共振穿隧與陷阱輔助穿隧兩種導電機制可知，於室溫濺鍍製程下，薄膜間之介面

混合 (intermixing region) 常導致高陷阱密度，使得載子傾向透過陷阱態進行躍遷，抑制準束縛態之形成與能量對齊條件之建立，進而降低共振穿隧特徵電流之出現。唯有當陷阱密度低且能障與量子井結構設計得當時，方能有效觀察共振穿隧行為與負微分電阻等典型特徵。儘管本元件於多次高電場量測後發生劣化、特性逐漸喪失，導致部分行為無法重現，然而本研究結果已成功驗證氧化物異質結構具實現共振穿隧之潛力，並為未來氧化物基穿隧元件的設計與製程開發提供有價值之參考方向。

## 5.2 未來展望

本研究在穿隧奈米結構下，成功觀察到像是二維能態密度特徵的階梯狀電流，顯示載子於量子井中可能存在準束縛態，驗證異質氧化物結構中具備共振穿隧潛力。然而，在實驗過程中面臨挑戰，影響元件之可重現性與穩定性。吾人認為尚有幾項問題需克服與改善：

### 1. 簡化結構：

在元件初期開發階段，觀察到載子於多層氧化物結構中會產生暫態效應，且量測結果易受操作手法差異影響而產生變化。為進一步了解元件特性，後續將先製作單層氧化物結構的元件，以簡化結構並降低干擾因素。

### 2. 原子層沉積技術：

採用射頻濺鍍機於室溫條件下進行材料沉積時，除難以精準控制薄膜厚度外，其膜層均勻性亦較差，易導致薄膜間介面產生混合現象，進而形成非理想介面結構並伴隨大量陷阱態，造成載子傳輸過程中之散射行為。從本研究所建立之穿透係數模擬結果可觀察到，各層材料厚度對穿透機率具有顯著影響，反映出薄膜厚度控制與介面品質於穿隧型元件中之關鍵性。

### 3. 元件面積:

使用濺鍍機作為主要製程工具，則需盡可能所小元件面積，並利用濺鍍機中高溫生長技術，使單位小孔能平坦化且為高品質結晶狀態。

### 4. 材料選擇:

未來研究可進一步導入具備鐵電性質之材料，例如採用氧化鈰鋯 ( $\text{HfZrO}$ ) 薄膜，透過氧化鈰與氧化鋯之共濺鍍製程形成雙能障量子井結構，藉此引入額外極化場，模擬鐵電極化效應對載子輸運行為之影響，期望提升穿隧效率與能帶調控能力。此外，現階段所採用之氧化銦錫 (ITO) 雖具有良好導電性，惟其導電性過高，可能不利於量子井中載子之侷限效果。鑑於此，未來可考慮以氧化鋅 ( $\text{ZnO}$ ) 作為替代材料。氧化鋅可於約  $500^\circ\text{C}$  退火後形成高品質結晶結構，兼具適度導電性與載子侷限能力，為更具潛力之量子井材料。

### 5. 高溫製程:

室溫濺鍍條件下，氧化物薄膜容易產生氧空缺與結構性陷阱，導致陷阱態密度升高，使得元件的導電行為以陷阱輔助穿隧機制為主，進而遮蔽原欲觀察之穿隧電流特徵。此結果顯示，材料中陷阱態的有效控制對於共振條件的建立具有關鍵性影響。因此，未來可考慮導入高溫製程以促進薄膜結晶化，降低陷阱密度，進一步提升共振效應，重現元件特性。

展望未來，期盼透過改善各層材料之結晶品質、精準控制薄膜厚度、優化高溫製程技術、以及選用更適當的材料，進一步提升元件良率與可重現性。同時，亦可結合外加磁場與低溫量測條件，探討元件中潛在之二維量子傳輸現象，拓展其在先進奈米電子元件與量子功能應用上的發展潛力。

## 參考文獻

- <sup>1</sup> <https://www.eetimes.eu/scaling-the-scaling-wall-to-future-compute-systems/>

- <sup>2</sup> Leo Esaki, "New Phenomenon in Narrow Germanium p-n Junctions," *Physical Review*. **109**, 603 (1958).

- <sup>3</sup> L. L. Chang et al., "Resonant tunneling in semiconductor double barriers," *Applied Physics Letters*. **24**, 593 (1974).

- <sup>4</sup> Anisha Ramesh et al., "High 5.2 peak-to-valley current ratio in Si/SiGe resonant interband tunnel diodes grown by chemical vapor deposition," *Applied Physics Letters*. **100**, 092104 (2012).

- <sup>5</sup> Michael Feiginov et al., "Operation of resonant-tunneling diodes with strong back injection from the collector at frequencies up to 1.46 THz," *Applied Physics Letters*. **104**, 243509 (2014).

- <sup>6</sup> Shaojun Lin et al., "III-nitrides based resonant tunneling diodes," *Journal of Physics D: Applied Physics*. **53**, 253002 (2020).

- <sup>7</sup> Zhijun Ma et al., "A Room-Temperature Ferroelectric Resonant Tunneling Diode," *Advanced Materials*. **34**, 2205359 (2022).

- <sup>8</sup> Gabriel Sanchez-Santolino et al., "Resonant electron tunnelling assisted by charged domain walls in multiferroic tunnel junctions," *Nature Nanotechnology*. **12**, 655 (2017).

- <sup>9</sup> Maolin Zhang et al., " $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-Based Power Devices: A Concise Review," *Crystals*. **12**, 406 (2022).

- <sup>10</sup> Rustum Roy et al., "Polymorphism of Ga<sub>2</sub>O<sub>3</sub> and the System Ga<sub>2</sub>O<sub>3</sub>—H<sub>2</sub>O," *Journal of the American Chemical Society*. **74**, 719 (1952).

<sup>11</sup> S. Sampath Kumar et al., "Structure, Morphology, and Optical Properties of Amorphous and Nanocrystalline Gallium Oxide Thin Films," The Journal of Physical Chemistry C. **117**, 4194 (2013).

<sup>12</sup> Hsien-Chih Huang et al., "Wet etch, dry etch, and MacEtch of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>: A review of characteristics and mechanism," Journal of Materials Research. **36**, 4756 (2021).

<sup>13</sup> Yong Han and Junfa Zhu, "ChemInform Abstract: Surface Science Studies on the Zirconia-Based Model Catalysts," Topics in Catalysis. **56**, 15 (2013).

<sup>14</sup> Huan Liu et al., "Ferroelectric-like behaviors of metal-insulator-metal with amorphous dielectrics," Science China Information Sciences. **66**, 200410 (2023).

<sup>15</sup> Dae Kyu Lee et al., "Crystallinity-controlled volatility tuning of ZrO<sub>2</sub> memristor for physical reservoir computing," InfoMat. **7**, e12635 (2025).

<sup>16</sup> Fu-Chien Chiu, "A Review on Conduction Mechanisms in Dielectric Films," Advances in Materials Science and Engineering. **7**, 578168 (2014).

<sup>17</sup> 張彥凱, "摻雜氧化鋅之三族氮化物電阻式記憶體," 光電工程學研究所, 國立臺灣大學 (2017).

<sup>18</sup> Carsten Funck and Stephan Menzel, "Comprehensive Model of Electron Conduction in Oxide-Based Memristive Devices," ACS Applied Electronic Materials. **3**, 3674 (2021).

<sup>19</sup> L. Esaki and R. Tsu, "Superlattice and Negative Differential Conductivity in Semiconductors," IBM Journal of Research and Development. **14**, 61 (1970).

<sup>20</sup> Kwok K. Ng and S.M. Sze, "Tunnel Devices," in Physics of Semiconductor Devices, 2006.

<sup>21</sup> Jasprit Singh, "The Tunneling Problem," in Quantum Mechanics, 1996.

<sup>22</sup> Yang Deng et al., "Physical vapor deposition technology for coated cutting tools: A review," Ceramics International. **46**, 18373 (2020).

<sup>23</sup> Fu-Chien Chiu et al., "Electron conduction mechanism and band diagram of sputter-deposited Al / ZrO<sub>2</sub> / Si structure," Journal of Applied Physics. **97**, 034506 (2005).

<sup>24</sup> Luca Pasquini, "The Effects of Nanostructure on the Hydrogen Sorption Properties of Magnesium-Based Metallic Compounds: A Review," Crystals. **8**, 106 (2018).

## 補充資料

### 雙能障量子井穿透係數計算程式

```

clc ; clear ; close all

filePath1 = "C:\Users\Samuel\OneDrive - 國立臺灣大學\桌面\raw data 3.xlsx";

data1 = readtable(filePath1);

excel_energy = data1{:, 1};

excel_current = (data1{:, 2}) ;

% Physical constants

q = 1.602e-19; % elementary charge (C)

hbar = 1.0546e-34; % reduced Planck constant (J s)

hbar2 = hbar^2;

m0 = 9.1095e-31; % free electron mass (kg)

% Material parameters

meff_well = 0.5; % effective mass ratio in well region ITO

meff_barrier1 = 0.35; % effective mass ratio in first barrier Ga2O3

meff_barrier2 = 1.2; % effective mass ratio in second barrier ZrO2

% Convert to absolute masses

m_well = meff_well * m0;

m_barrier1 = meff_barrier1 * m0;

m_barrier2 = meff_barrier2 * m0;

% Barrier parameters

V1 = 0.34; % Ga2O3 first barrier height (eV)

V2 = 0.46; % ZrO2 second barrier height (eV)

Db1 = 2.6e-9; % Ga2O3 first barrier thickness (m)

Db2 = 1.2e-9; % ZrO2 second barrier thickness (m)

Dw = 5.6e-9; % ITO quantum well thickness (m)

d = (Db1 + Db2 + Dw)*100 % m 換 cm

excel_electric_field = excel_energy/(120e-7)/1000000 % [MeV/cm]

% Max barrier height for energy range calculation

Vmax = 0.52;

```

```

% Parameters for energy range

M = 1000; % number of energy steps

t_d = zeros(M-1, 1); % transmission coefficient

% Energy range (0 to max barrier height)

E_d = linspace(Vmax/M, Vmax-Vmax/M, M-1);

% Calculate transmission for each energy

for i = 1:M-1

T = calculate_transfer_matrix(E_d(i), V1, V2, Db1, Db2, Dw, m_well,

m_barrier1, m_well, m_barrier2, m_well, hbar2, q

% Calculate transmission coefficient from the transfer matrix

t_d(i) = 1 / (abs(T(1,1))^2);

end

figure;

yyaxis left;

plot(E_d/d/1000000, t_d, 'b-', 'LineWidth', 1.5, 'DisplayName', 'Simulated

Transmission');

title('Transmission through asymmetric double barriers');

ylabel('Transmission Coefficient T(E)');

xlabel('Electric field (MeV/cm)');

ylim([-0.1, 1.1]);

xlim([0, 0.47])

yyaxis right;

plot(excel_electric_field, excel_current, 'ro', 'MarkerSize', 4, 'DisplayName',

'Experimental Current');

ylabel('Current (A)');

figure;

yyaxis left;

semilogy(E_d/d/1000000, t_d, 'b-', 'LineWidth', 1.5, 'DisplayName', 'Simulated

Transmission');

title('Transmission through asymmetric double barriers');

ylabel('log(Transmission Coefficient T(E))');

xlabel('Electric field (MeV/cm)');

ylim([-0.1, 1.1]);

xlim([0, 0.47])

yyaxis right;

```

```

semilogy(excel_electric_field, excel_current, 'ro', 'MarkerSize', 4,

'DisplayName', 'Experimental Current');

ylabel('Current (A)');

%%

function T = calculate_transfer_matrix(E, V1, V2, Db1, Db2, Dw, m_incident,

m_barrier1, m_well, m_barrier2, m_transmit, hbar2, q)

% Calculate wave vectors

k0_squared = 2 * m_incident * E * q / hbar2;           % in region I (incident)

k0 = sqrt(k0_squared);

k1_squared = 2 * m_barrier1 * (V1 - E) * q / hbar2;   % in region II (barrier 1)

if E > V1

k1 = sqrt(k1_squared);

else

k1 = 1i * sqrt(abs(k1_squared));

end

k2_squared = 2 * m_well * E * q / hbar2;                % in region III (well)

k2 = sqrt(k2_squared);

k3_squared = 2 * m_barrier2 * (V2 - E) * q / hbar2;   % in region IV (barrier 2)

if E > V2

k3 = sqrt(k3_squared);

else

k3 = 1i * sqrt(abs(k3_squared));

end

k4_squared = 2 * m_transmit * E * q / hbar2;           % in region V

k4 = sqrt(k4_squared);

M01 = [0.5*(1 + k0*m_barrier1/(k1*m_incident)), 0.5*(1 -

k0*m_barrier1/(k1*m_incident));

0.5*(1 - k0*m_barrier1/(k1*m_incident)), 0.5*(1 +

k0*m_barrier1/(k1*m_incident))];

```

$M12 = [0.5*(1 + k1*m_well/(k2*m_barrier1)), 0.5*(1 - k1*m_well/(k2*m_barrier1)),$

$0.5*(1 - k1*m_well/(k2*m_barrier1)), 0.5*(1 + k1*m_well/(k2*m_barrier1))];$

$M23 = [0.5*(1 + k2*m_barrier2/(k3*m_well)), 0.5*(1 - k2*m_barrier2/(k3*m_well)),$

$0.5*(1 - k2*m_barrier2/(k3*m_well)), 0.5*(1 + k2*m_barrier2/(k3*m_well))];$

$M34 = [0.5*(1 + k3*m_transmit/(k4*m_barrier2)), 0.5*(1 - k3*m_transmit/(k4*m_barrier2)),$

$0.5*(1 - k3*m_transmit/(k4*m_barrier2)), 0.5*(1 + k3*m_transmit/(k4*m_barrier2))];$

% Propagation matrices

$P1 = [\exp(-1i*k1*Db1), 0;$

$0, \exp(1i*k1*Db1)];$

$P2 = [\exp(-1i*k2*Dw), 0;$

$0, \exp(1i*k2*Dw)];$

$P3 = [\exp(-1i*k3*Db2), 0;$

$0, \exp(1i*k3*Db2)];$

% Total transfer matrix

$T = M01 * P1 * M12 * P2 * M23 * P3 * M34;$

end