國立臺灣大學電機資訊學院電子工程學研究所

碩士論文

Graduate Institute of Electronics Engineering

College of Electrical Engineering and Computer Science

National Taiwan University

Master's Thesis

銻（錫）金氧化半場效電晶體的低溫電子傳輸特性

Electron Transport in Ge(Sn) Metal-Oxide-Semiconductor Field-

Effect Transistors at Cryogenic Temperatures

陳彥洋

Yen-Yang Chen

指導教授：李峻賓 教授

Advisor: Prof. Jiun-Yun Li

中華民國 114 年 7 月

July, 2025

國立臺灣大學碩士學位論文

口試委員會審定書

**MASTER'S THESIS ACCEPTANCE CERTIFICATE**

**NATIONAL TAIWAN UNIVERSITY**

## 鎵（錫）金氧半場效電晶體的低溫電子傳輸特性

# Electron Transport in Ge(Sn) Metal-Oxide-Semiconductor Field-Effect Transistors at Cryogenic Temperatures

本論文係陳彥洋 (R11943087) 在國立臺灣大學電子工程學研究所完成之碩士學位論文，於民國 114 年 06 月 27 日承下列考試委員審查通過及口試及格，特此證明。

The undersigned, appointed by the Graduate Institute of Electronics Engineering on 27 June 2025 have examined a Master's Thesis entitled above presented by Yen-Yang Chen (R11943087) candidate and hereby certify that it is worthy of acceptance.

口試委員 Oral examination committee:

王文慶

(指導教授 Advisor)

林浩惟 (指導教授 Advisor) 張書維 罷廣禮

系（所、學位學程）主管 Director: 江介宏

## 謝誌

感謝指導教授李峻賈教授七年來的教導，讓我從原本懵懂的大學部專題生，蛻變成為通過論文口試的碩士生。您對於學術品質的要求，以及做學問態度的堅持，建立了一個示範，讓我在完成學業的過程中，認識到做研究該有的精神。這一路走來經歷的磨練與考驗、穿越的深山與低谷，逐漸地讓我體會到，真正的光芒，只會在幽暗中顯現。您培養了我探究現象背後物理成因的能力，而我則發現，洞悉事物的道理，竟能毫無理由地帶給我源源不絕的樂趣，支持我在挫折當中，逆勢而行。學術探究之於我，似乎就是幽暗中的那一盞光芒。

能擁有這樣的體悟，還必須感謝父母二十五餘年來的養育，讓我無後顧之憂地唸書，直到考進臺大，並完成研究所學位。您們開明的教育方式，撐出了自由探索的空間，允許我依憑心之所向，走上屬於我自己的道路。在我剛踏入 QEL、處於懵懂階段時，很慶幸能有機會向嘉澤、韋志、凱瑩、宗穎、大劉、志力、睿濬、士傑、宸曉、瑋哲、蘇遙、俞叡、祥順等學長姐學習，打下製程、量測與分析的基礎。在研究上遇到困難時，幸虧有哲豪、俊瑋、昱呈、陳恩、顓慈、偉翔、旻叡、菩家、閻宇、則瑋、昊謙等好同學的互相幫助，才能夠順利地解決問題、推展實驗的進度。我特別感謝士傑學長的照顧，願意在我還很菜的時候，不厭其煩地回答我一個又一個的問題，並且在我碩士生涯的中後期、對未來迷茫時，和我一起討論人生的方向，以及下一步的規劃。我也特別感謝昱呈同學，和我一起討論如何突破研究上的瓶頸，以及各式各樣的物理問題，因為你的洞見與優秀的分析能力，與你對談，我總是收穫滿滿。而當我心情低落的時候，只要跟旻叡聊上幾句話，鬱悶就會立刻一掃而空。謝謝你神奇的魔力，還有對於儀器知識、產業發展及各種情報的分享，讓我的碩士生涯變得更豐富、更順利。

此外，我還想要感謝一路以來陪伴我的朋友們。謝謝岩壁大隊的旻珊、品函、馬丁跟愷蔓，每次跟你們聚餐，總能夠開懷大笑，把所有的煩惱拋在腦後。謝謝胖子團的小白、亮姊、卡比跟禮仲，每次見面，都有聊不完的話題，和你們做朋友，我獲得好多个快樂。謝謝欣哲、宣皓、鈺軒和嘉祥，在大學部修課時，一起討論作業的解法、準備考試，一起顧好 GPA，讓未來申請博士班更加順利。我特別感謝小白，能夠一起分享生活遇到的大小事，和各種對於人事物的想法，許多被人批評為

想太多的煩惱，都能夠在對談時被提出來討論，光是這一點，就已經達成深深的療癒。我也特別感謝欣哲，能夠一起討論投資策略、分享人生的價值觀，你清晰的思路，總能在一問一答之間，直指問題的核心，使答案自然浮現。我也感激能夠與你談論形而上的哲學問題，不為錢財、不計功名，只為了滿足好奇心。你獨到的觀點，總能激盪出許多火花，把我們對於事物的認知，往更本質、更全面的方向拓展。最後，我要特別感謝瑞智，在我做研究感到最痛苦的時候，不斷地告訴我，我可以。如果不是你，也許我還是可以從幽暗中走出來，不過那盞珍貴的光芒，大概會因為過度耗損，而永遠的熄滅了。

陳彥洋 謹誌於

2025 年 7 月 25 日

## 中文摘要

鍺錫 (GeSn) 合金因其具備直接能隙、高載子遷移率，以及與矽積體電路技術的相容性，在光電與電子應用領域中引起廣泛關注。儘管已有諸多研究展示出高性能的鍺錫元件，關於鍺錫由間接能隙轉變為直接能隙之機制，仍未獲得完整的理解。過往相關的實驗研究多半聚焦於光學特性，對於電性方面的探究則相對稀少。因此，本論文旨在探討鍺錫由間接能隙轉變為直接能隙對於電子傳輸特性造成的影響。

本研究使用化學氣相沉積 (CVD) 技術，成長高品質且應變鬆弛的鍺磊晶結構及錫原子比例分別為 4.5% 與 10.5% 的鍺錫磊晶結構。隨後製備鍺 (錫) n 型金氧半場效電晶體 (n-MOSFETs)，並於 300 K 至 4 K 的溫度範圍內進行電性特性分析。在 300 K 時，隨著錫原子比例增加，元件的關閉電流上升而開態電流下降，推測原因分別為接面漏電流的增加與合金散射效應的加劇。在所有元件中，於積累區與空乏區皆觀察到異常高的閘極-通道電容，其成因為接面在交流訊號的驅動下提供了大量的多數載子 (電洞)。本文提出一種方法，未來可用於校正關閉電流對閘極電容和等效遷移率的影響，適合應用於能隙小、遷移率高的電晶體，如鍺錫、砷化銦 (InAs) 及銻化銦 (InSb) n 型金氧半場效電晶體。當溫度自 300 K 降低至 4 K 時，隨著接面漏電流受到抑制，所有元件的關閉電流皆呈現單調遞減。然而，開態電流隨溫度的變化則呈現出較為複雜的行為。為便於分析，本研究採用分裂電容-電壓方法，以分離開態電流對電子濃度與遷移率的依賴性。在強反轉區中，閘極-通道電容對溫度的微幅變化，可歸因於反轉層電子在交流訊號驅動下的供應對溫度的變化。最後，本研究探討了電子的等效遷移率。隨著錫原子比例提升至 10.5%，遷移率隨溫度變化的趨勢由原先的單調遞減，轉變為在 100 K 至 20 K 之間出現異常上升的行為。此現象可歸因於直接能隙  $Ge_{0.895}Sn_{0.105}$  元件中的遷移率提升，此提升係由隨著溫度降低， $\Gamma$  谷中電子數量的增加所致。根據傳輸特性的結果可推論，鍺錫材料中由間接能隙轉變為直接能隙的轉換範圍，發生於錫原子比例介於 4.5% 與 10.5% 之間。

**關鍵字：**鍺錫、金氧半場效電晶體、間接能隙至直接能隙的轉變、電子遷移率、小訊號模型

# ABSTRACT

Germanium-tin (GeSn) alloys have attracted great attention for both optoelectronic and electronic applications due to their direct-bandgap characteristics, high carrier mobility, and compatibility with Si VLSI technology. While numerous studies have demonstrated high-performance GeSn devices, the understanding of indirect-to-direct bandgap transition in GeSn remains incomplete. Previous experimental studies have predominantly focused on optical aspects, with limited electrical data available. This thesis investigates the impact of the indirect-to-direct bandgap transition on electron transport properties in GeSn.

High-quality, strain-relaxed Ge,  $\text{Ge}_{0.955}\text{Sn}_{0.045}$ , and  $\text{Ge}_{0.895}\text{Sn}_{0.105}$  epitaxial structures are grown using chemical vapor deposition. Ge(Sn) n-type metal-oxide-semiconductor field-effect transistors (n-MOSFETs) are fabricated and characterized at temperatures of 300 K to 4 K. At 300 K, the off-state current increases and the on-state current decreases with the Sn fraction due to enhanced junction leakage and alloy scattering, respectively. Abnormally high gate-to-channel capacitance is observed in the accumulation and depletion regimes across all devices due to a large supply of majority carriers (holes) through the junctions in response to the AC signals. A method is proposed for future calibration of the off-state leakage effect on  $C_{\text{GC}}$ , and consequently, mobility extraction, which can be applied to small-bandgap, high-mobility transistors such as GeSn, InAs, and InSb n-MOSFETs. As the temperature decreases from 300 K to 4 K, the off-state current decreases monotonically across all devices due to the suppressed junction leakage. The on-state current, however, exhibits a complex trend with temperature. To facilitate analysis, the dependence of on-state current on both electron density and mobility is decoupled using a split C-V method. The slight temperature dependence of gate-to-

channel capacitance in the strong inversion regime is a result of the temperature-dependent supply of inverted electrons in response to the AC signals. Lastly, the electron effective mobility is investigated. As the Sn fraction increases up to 10.5 at%, the trend of mobility over temperature transitioned from a monotonic decrease to one exhibiting an anomalous upturn between 100 K and 20 K. This is attributed to the mobility enhancement in the direct-bandgap  $\text{Ge}_{0.895}\text{Sn}_{0.105}$  device due to an increased electron population in the  $\Gamma$ -valley as the temperature decreases. Based on the transport results, the indirect-to-direct bandgap transition in GeSn is identified to occur between Sn fractions of 4.5 at% and 10.5 at%.

**Keywords:** germanium-tin (GeSn), metal-oxide-semiconductor field-effect transistor (MOSFET), indirect-to-direct bandgap transition, electron mobility, small-signal model

# CONTENTS

|                                                                            |           |

|----------------------------------------------------------------------------|-----------|

| 口試委員會審定書 .....                                                             | i         |

| 謝誌 .....                                                                   | ii        |

| 中文摘要 .....                                                                 | iv        |

| ABSTRACT .....                                                             | v         |

| CONTENTS .....                                                             | vii       |

| LIST OF FIGURES .....                                                      | x         |

| LIST OF TABLES .....                                                       | xxi       |

| <b>Chapter 1 Introduction.....</b>                                         | <b>1</b>  |

| 1.1 Motivation.....                                                        | 1         |

| 1.2 Tunable Band Structure of GeSn.....                                    | 3         |

| 1.3 Thesis Outline .....                                                   | 9         |

| <b>Chapter 2 Fabrication and Characterization of Ge(Sn) n-MOSFETs.....</b> | <b>10</b> |

| 2.1 Introduction.....                                                      | 10        |

| 2.1.1 Planar GeSn n-MOSFETs .....                                          | 11        |

| 2.1.2 Mesa GeSn n-MOSFETs .....                                            | 12        |

| 2.1.3 Surface-Capped GeSn n-MOSFETs.....                                   | 13        |

| 2.2 Experiment.....                                                        | 15        |

| 2.2.1 Material Growth and Analysis .....                                   | 15        |

| 2.2.2 Device Fabrication .....                                             | 20        |

| 2.2.3 Device Characterization .....                                        | 22        |

| 2.3 Room-Temperature Device Characteristics .....                          | 27        |

| 2.3.1 Transfer I-V Characteristics .....                                   | 28        |

|                                                                                     |                                                                |            |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------|------------|

| 2.3.2                                                                               | Split C-V Characteristics.....                                 | 34         |

| 2.3.3                                                                               | Split G-V Characteristics .....                                | 50.        |

| 2.3.4                                                                               | $\mu_{\text{eff}}\text{-}N_{\text{inv}}$ Characteristics ..... | 56         |

| 2.4                                                                                 | Summary.....                                                   | 59         |

| <b>Chapter 3 Electron Transport Properties in Ge(Sn) n-MOSFETs .....</b>            |                                                                | <b>60</b>  |

| 3.1                                                                                 | Introduction.....                                              | 60         |

| 3.2                                                                                 | Cryogenic Device Characteristics.....                          | 63         |

| 3.2.1                                                                               | Transfer I-V Characteristics .....                             | 63         |

| 3.2.2                                                                               | Split C-V Characteristics.....                                 | 67         |

| 3.3                                                                                 | Electron Mobility in Ge(Sn) n-MOSFETs.....                     | 78         |

| 3.3.1                                                                               | Effective Mobility vs. Inversion Carrier Density .....         | 78         |

| 3.3.2                                                                               | Effective Mobility vs. Temperature.....                        | 80         |

| 3.4                                                                                 | Summary.....                                                   | 86         |

| <b>Chapter 4 Conclusion and Future Work.....</b>                                    |                                                                | <b>87</b>  |

| 4.1                                                                                 | Conclusion .....                                               | 87         |

| 4.2                                                                                 | Future Work .....                                              | 89         |

| <b>REFERENCES .....</b>                                                             |                                                                | <b>91</b>  |

| <b>Appendix A Derivation of the Circuit Capacitance of Small-Signal Models.....</b> |                                                                | <b>103</b> |

| A.1                                                                                 | Accumulation Regime ( $V_{\text{ov}} = -2$ V).....             | 103        |

| A.2                                                                                 | Depletion Regime ( $V_{\text{ov}} \sim -0.5$ V).....           | 108        |

| A.3                                                                                 | Strong Inversion Regime ( $V_{\text{ov}} = 2$ V).....          | 110        |

| <b>Appendix B Scattering Mechanisms in n-MOSFETs.....</b>                           |                                                                | <b>115</b> |

| B.1                                                                                 | Overview.....                                                  | 115        |

| B.2                                                                                 | Surface Roughness Scattering .....                             | 117        |

| B.2.1                                                                               | The Physical Mechanism .....                                   | 117        |

|       |                                   |      |

|-------|-----------------------------------|------|

| B.2.2 | The Temperature Dependence.....   | 118  |

| B.2.3 | The Density Dependence .....      | 118. |

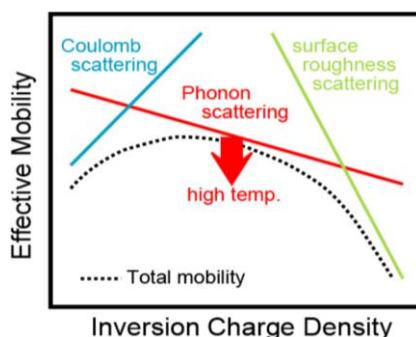

| B.3   | Phonon and Alloy Scattering ..... | 119  |

| B.3.1 | The Physical Mechanism .....      | 119  |

| B.3.2 | The Temperature Dependence.....   | 119  |

| B.3.3 | The Density Dependence .....      | 120  |

| B.4   | Coulomb Scattering .....          | 120  |

| B.4.1 | The Physical Mechanism .....      | 121  |

| B.4.2 | The Temperature Dependence.....   | 121  |

| B.4.3 | The Density Dependence .....      | 125  |

|       | PUBLICATION LIST .....            | 127  |

# LIST OF FIGURES

|                                                                                                                                                                                                                                                                                                                      |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Fig. 1-1 Bandgap energy vs. lattice constant of the SiGe and GeSn alloy systems as well as direct-bandgap III-V compound semiconductors [1].                                                                                                                                                                         | 1 |

| Fig. 1-2 Bulk mobility of electron and hole in group-IV and III-V compound semiconductors [6].                                                                                                                                                                                                                       | 2 |

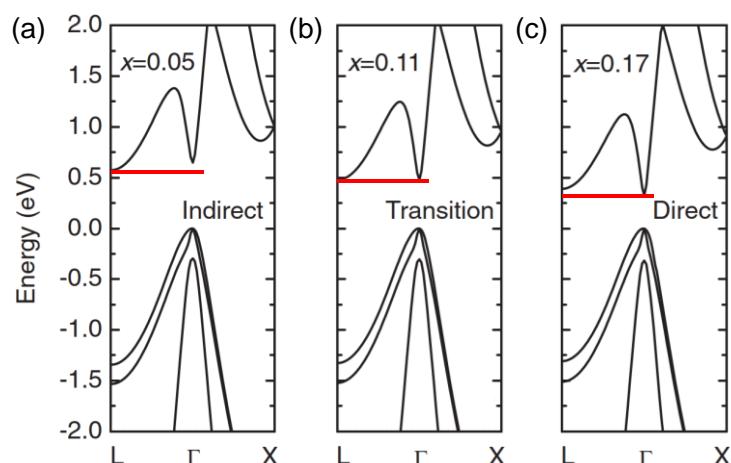

| Fig. 1-3 Simulated band structures of strain-relaxed GeSn alloys with Sn fractions of (a) 5%, (b) 11%, and (c) 17% [17].                                                                                                                                                                                             | 3 |

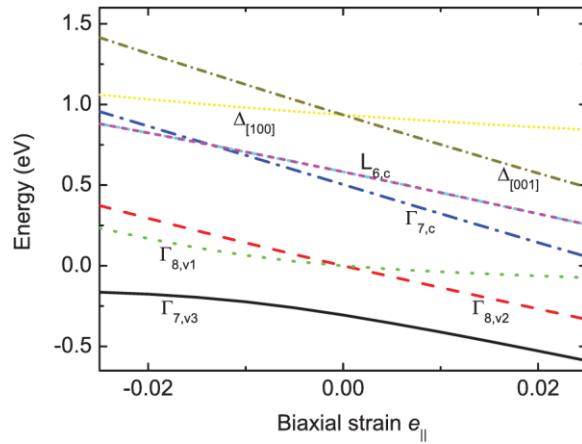

| Fig. 1-4 Relative energy shifts of the band edges at various symmetry points of $\text{Ge}_{0.90}\text{Sn}_{0.10}$ vs. in-plane biaxial strain along the (001) plane [18].                                                                                                                                           | 4 |

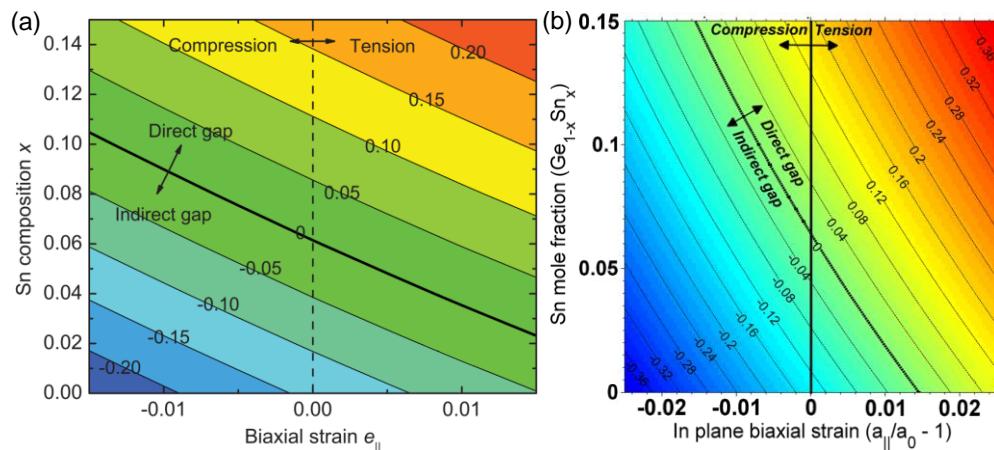

| Fig. 1-5 Contour maps of calculated energy separation between the L- and $\Gamma$ -valley vs. Sn fraction and in-plane biaxial strain along the (001) plane reported in (a) [18] and (b) [19].                                                                                                                       | 4 |

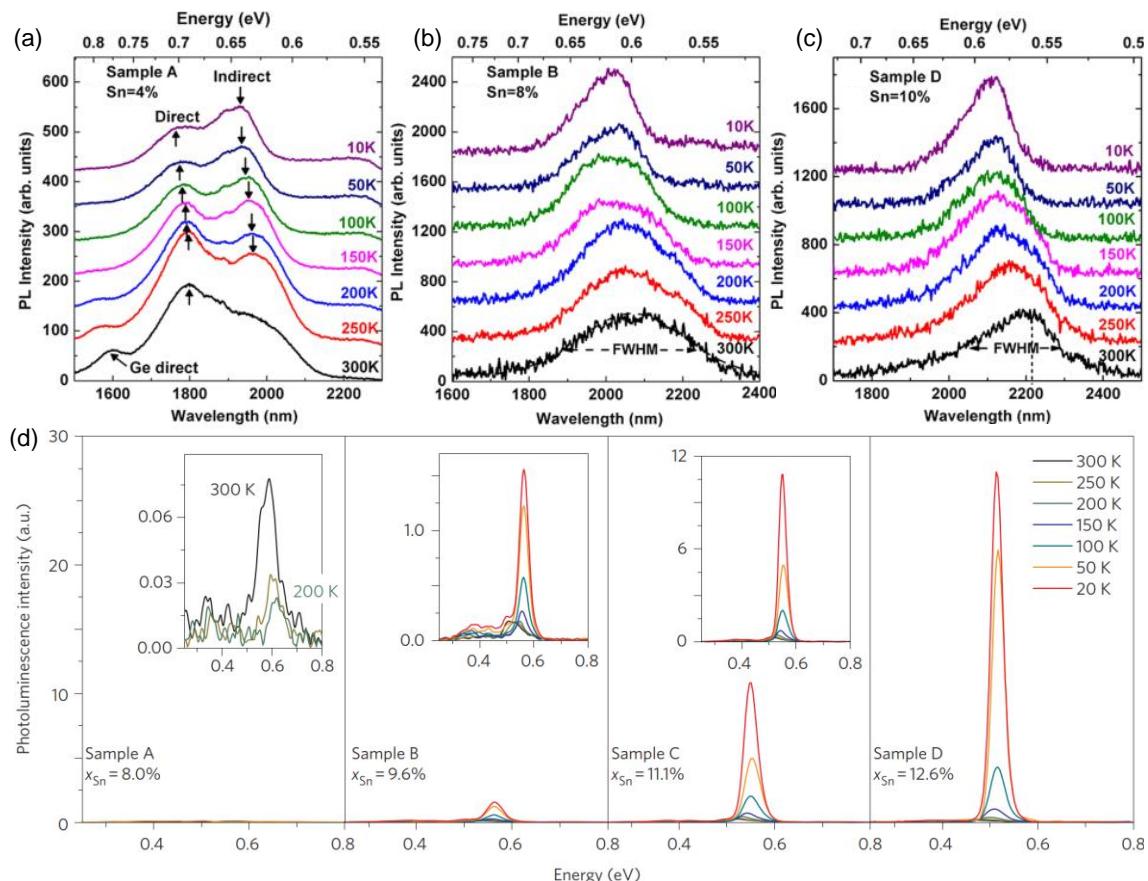

| Fig. 1-6 Temperature dependent photoluminescence (PL) spectra of the GeSn alloys with Sn fractions of (a)-(c) 4 – 10 at% [15] and (d) 8.0% – 12.6% [2]. The insets in (d) show zoomed portions of the spectra.                                                                                                       | 5 |

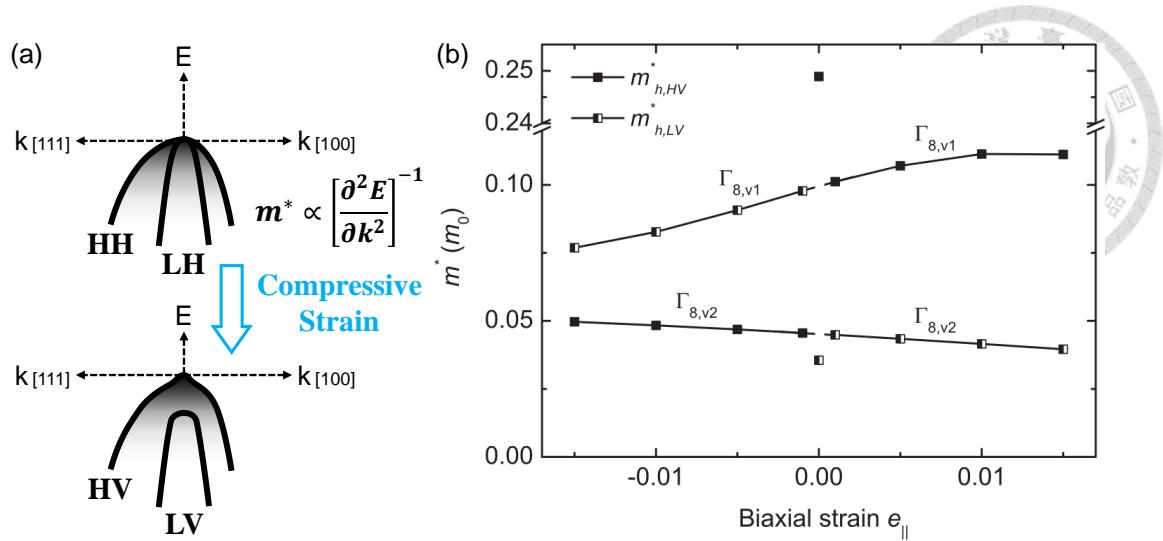

| Fig. 1-7 (a) Schematics of the band structure showing the hole mobility enhancement in GeSn alloys. (b) Simulated hole effective masses of the higher valence ( $m_{h,HV}^*$ ) and lower valence ( $m_{h,LV}^*$ ) bands of $\text{Ge}_{0.9}\text{Sn}_{0.1}$ vs. in-plane biaxial strain along [100] direction [18].  | 7 |

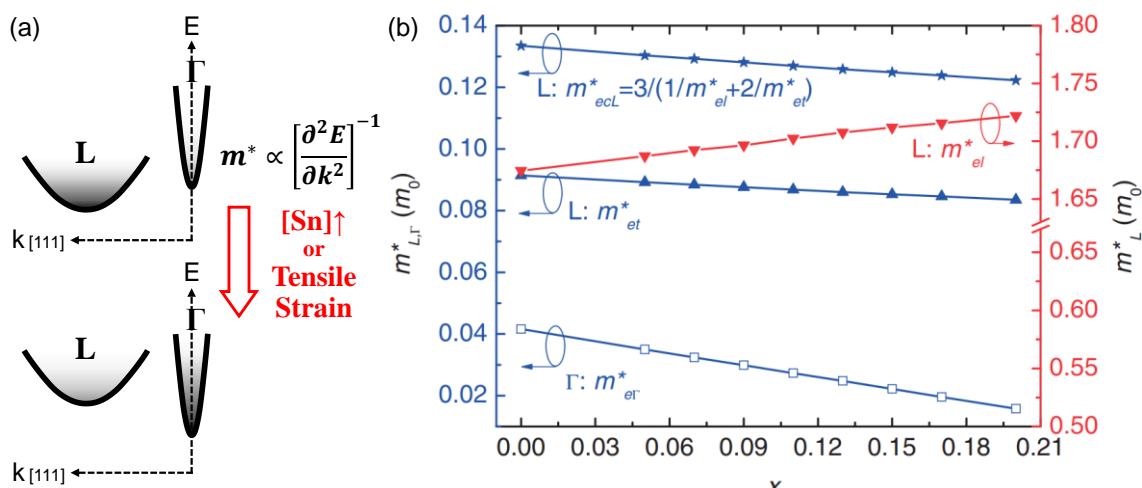

| Fig. 1-8 (a) Schematics of the band structure showing the electron mobility enhancement in GeSn alloys. (b) Simulated conductivity effective masses of electron in the L-valley ( $m_{eL}^*$ ) and $\Gamma$ -valley ( $m_{e\Gamma}^*$ ) of strain-relaxed $\text{Ge}_{1-x}\text{Sn}_x$ alloys vs. Sn content x [17]. | 7 |

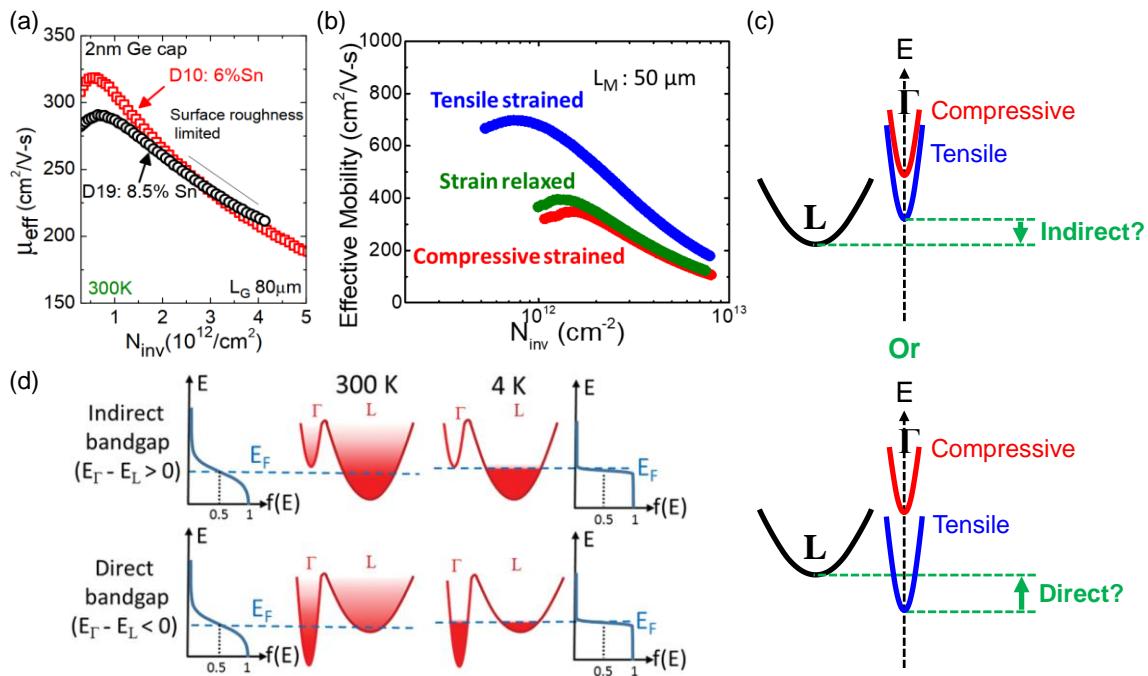

| Fig. 1-9 Electron effective mobility ( $\mu_{\text{eff}}$ ) vs. inversion carrier density ( $N_{\text{inv}}$ ) of GeSn n-                                                                                                                                                                                            |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| MOSFETs (a) with different Sn fractions (compressive-strained) [21] and (b) different strain conditions ( $[Sn] = 4\%$ ) [11]. (c) Schematics of band structures of compressive and tensile-strained GeSn in (b). (d) Schematics of electron population in the L- and $\Gamma$ -valleys of indirect-bandgap and direct-bandgap GeSn at 300 K and 4 K [12]. .....                                                                                                                         | 8  |

| Fig. 2-1 (a) Device structure, (b) transfer I-V characteristics, (c) normalized gate-to-channel capacitance ( $C_{GC}$ ) vs. gate voltage, and (d) effective mobility ( $\mu_{eff}$ ) vs. inversion carrier density ( $N_{inv}$ ) of the planar $Ge_{0.955}Sn_{0.045}$ n-MOSFET [22]. .....                                                                                                                                                                                              | 11 |

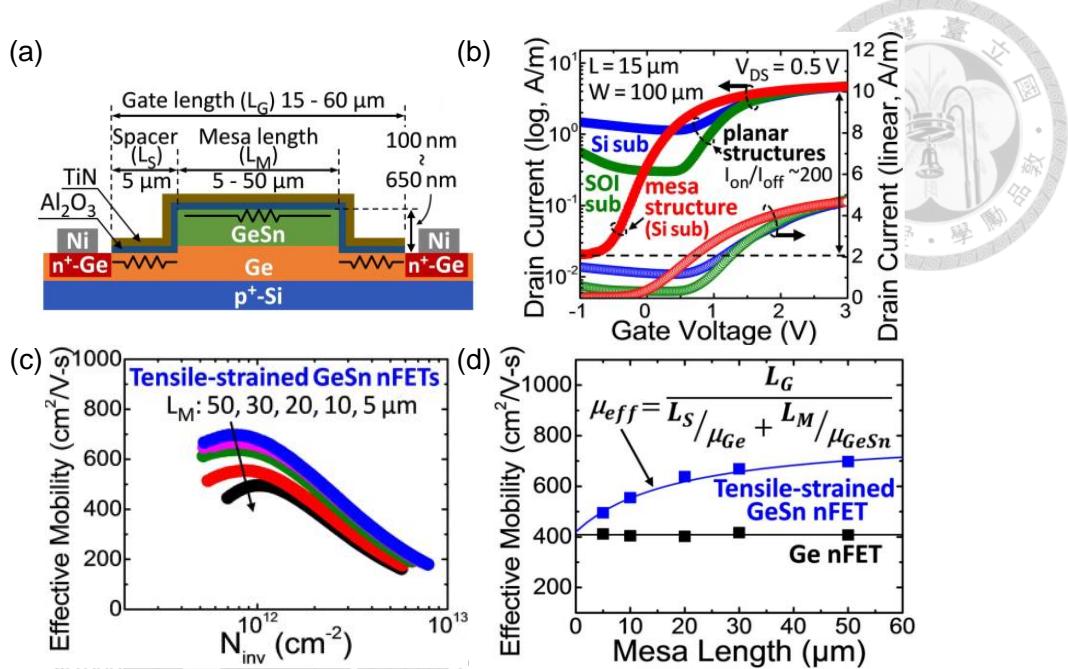

| Fig. 2-2 (a) Device structure of the mesa GeSn n-MOSFETs [11]. (b) Transfer I-V characteristics of the planar (on Si and SOI substrates) and mesa $Ge_{0.96}Sn_{0.04}$ n-MOSFETs [11]. (c) Effective mobility ( $\mu_{eff}$ ) vs. inversion carrier density ( $N_{inv}$ ) of the tensile-strained $Ge_{0.96}Sn_{0.04}$ n-MOSFETs with various mesa lengths ( $L_M$ ) [11]. (d) $\mu_{eff}$ vs. $L_M$ of the Ge n-MOSFETs and tensile-strained $Ge_{0.96}Sn_{0.04}$ n-MOSFETs [11]. ..... | 13 |

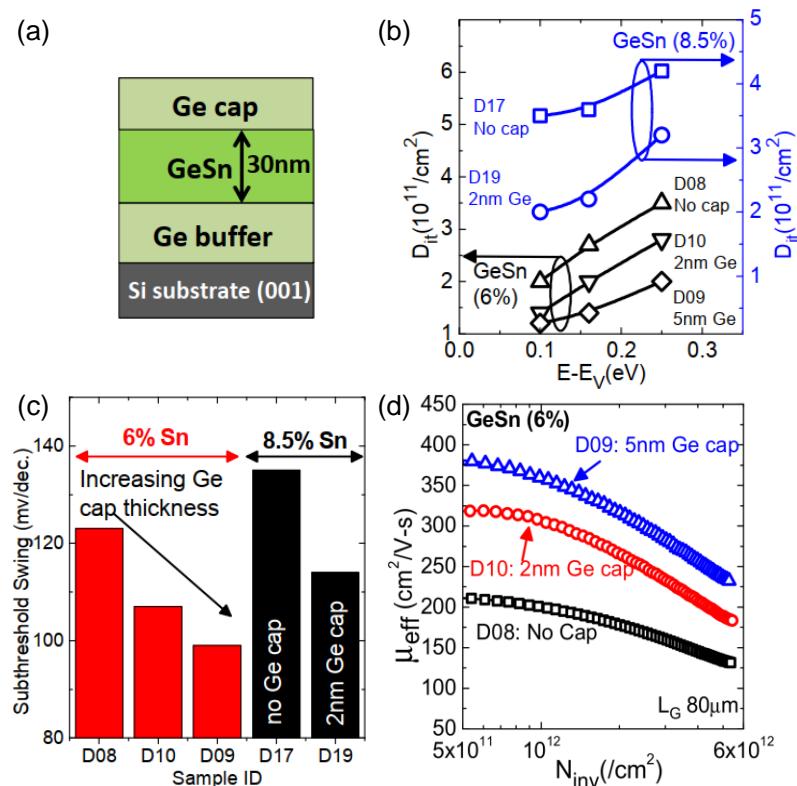

| Fig. 2-3 (a) Epitaxial structure, (b) interface trap density ( $D_{it}$ ) vs. energy ( $E-E_V$ ), (c) subthreshold swing, and (d) $\mu_{eff}$ vs. $N_{inv}$ of the planar $Ge_{0.94}Sn_{0.06}$ and $Ge_{0.915}Sn_{0.085}$ n-MOSFETs with or without a Ge cap [21]. .....                                                                                                                                                                                                                 | 14 |

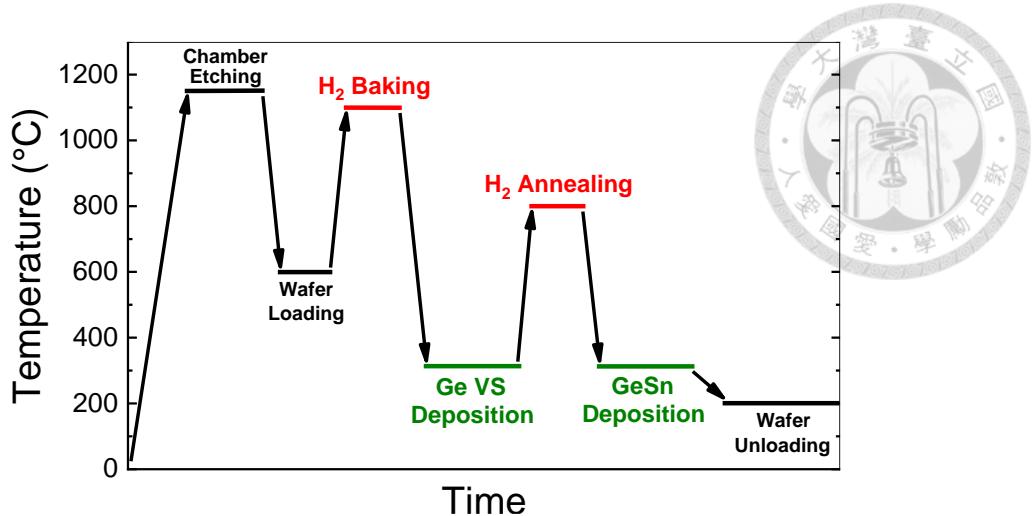

| Fig. 2-4 A schematic of the deposition process of Ge(Sn) epitaxial structures. ....                                                                                                                                                                                                                                                                                                                                                                                                      | 16 |

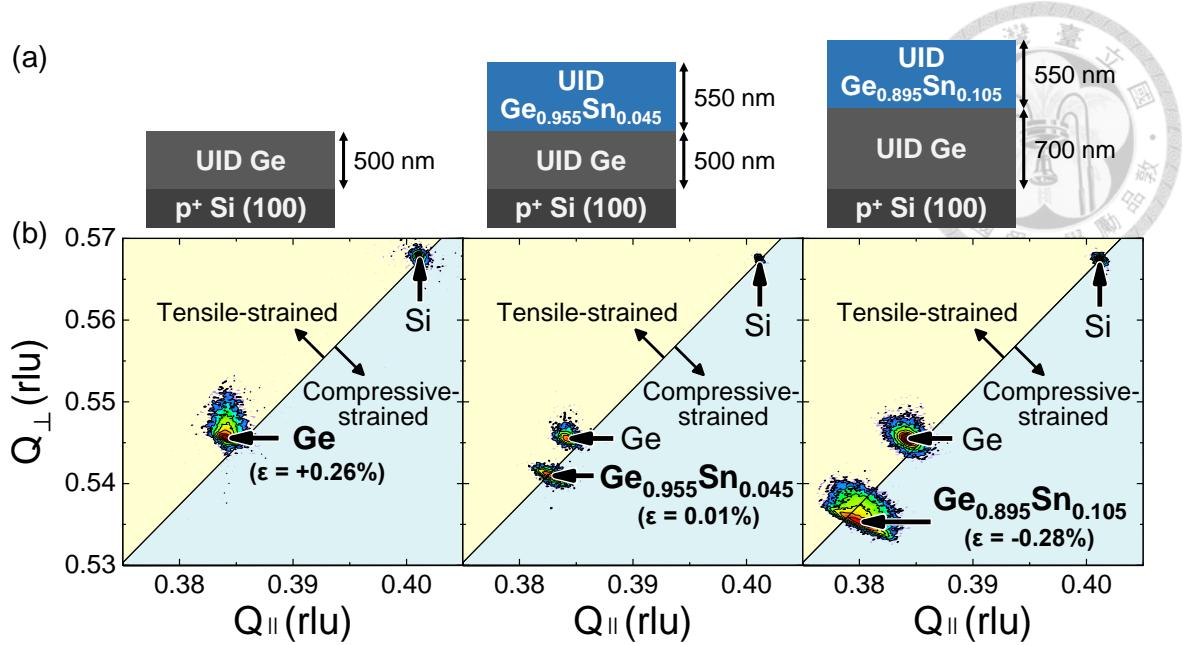

| Fig. 2-5 (a) Epitaxial structures of the Ge, $Ge_{0.955}Sn_{0.045}$ , and $Ge_{0.895}Sn_{0.105}$ films and (b) the corresponding (224) high-resolution reciprocal space mapping (HRRSM) contours.....                                                                                                                                                                                                                                                                                    | 17 |

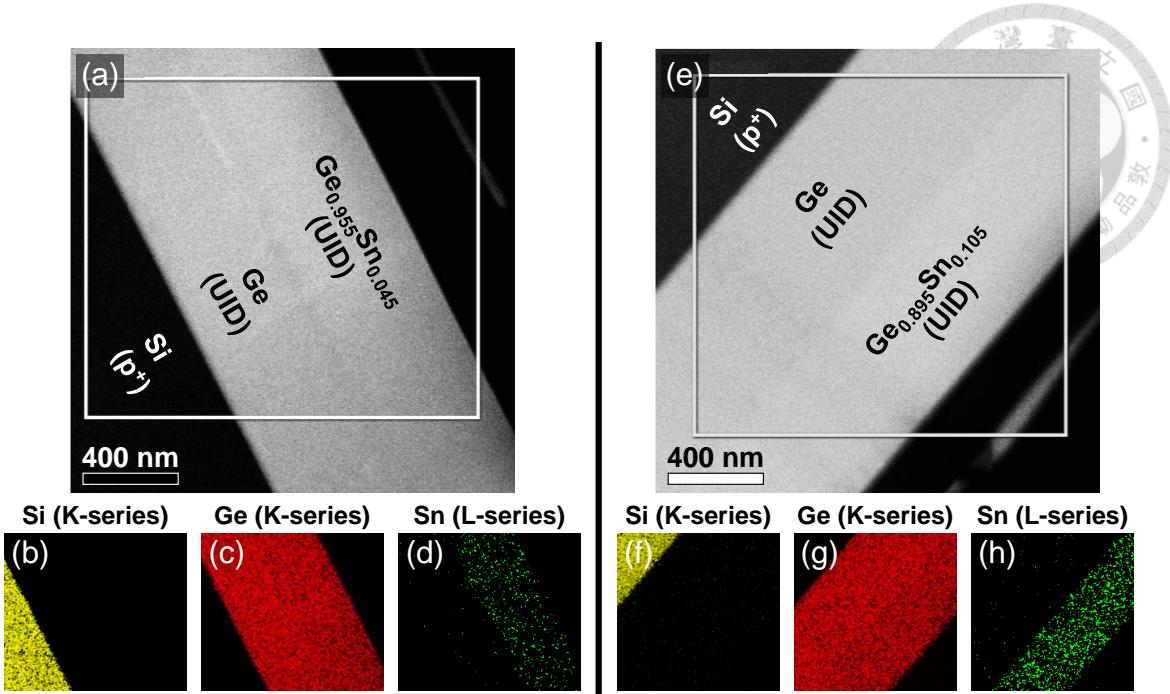

| Fig. 2-6 Scanning electron microscope (SEM) images by backscattered electrons (BSEs) of the (a) $Ge_{0.955}Sn_{0.045}$ and (e) $Ge_{0.895}Sn_{0.105}$ epitaxial structures. Energy-dispersive X-ray spectroscopy (EDXS) mapping of the white squares in (a)                                                                                                                                                                                                                              |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| and (e) showing (b)(f) Si, (c)(g) Ge, and (d)(h) Sn atom distributions. ....                                                                                                                                                                                                                                                                                                                                                                 | 18 |

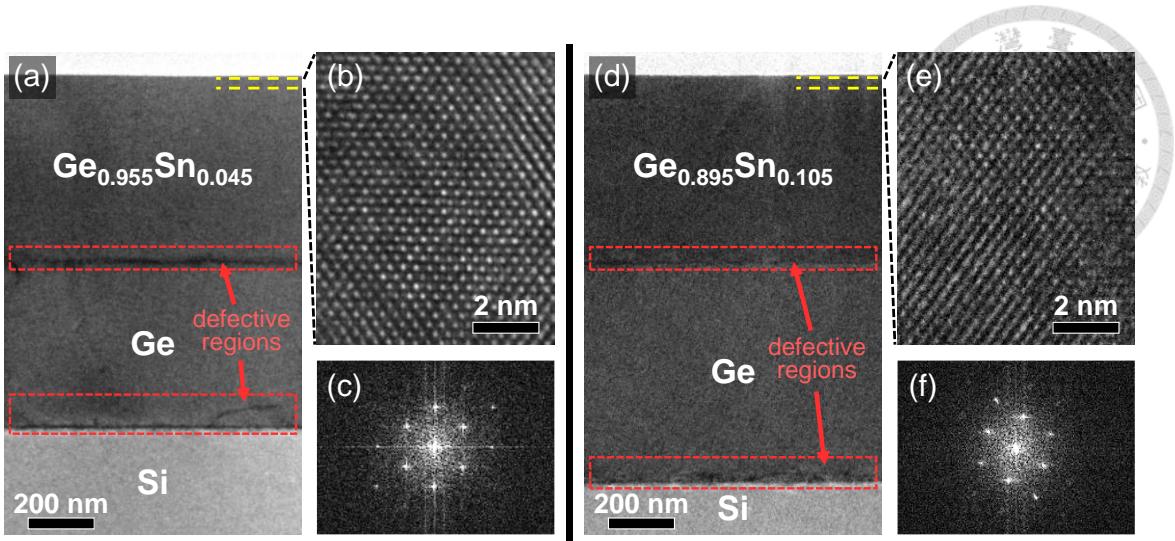

| Fig. 2-7 (a)(d) Cross-sectional high-resolution transmission electron microscope (HRTEM) images, (b)(e) the near-surface cross-sectional HRTEM images, and (c)(f) the near-surface spot diffraction pattern of the $Ge_{0.955}Sn_{0.045}$ and $Ge_{0.895}Sn_{0.105}$ epitaxial structures. ....                                                                                                                                              | 19 |

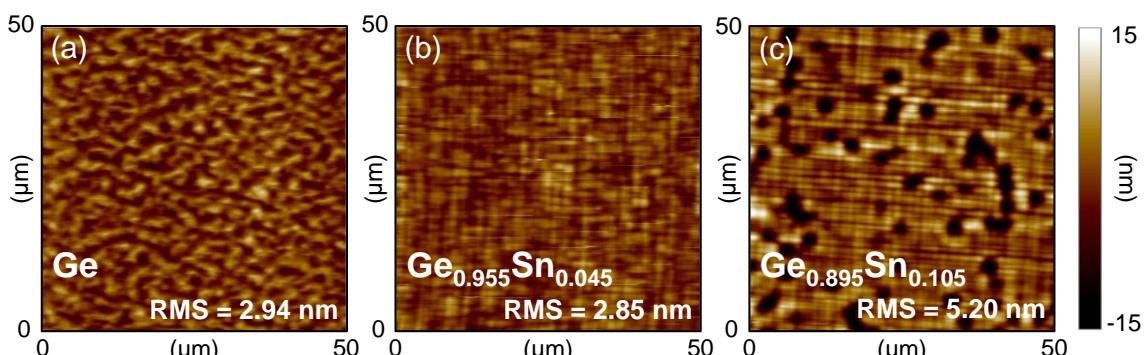

| Fig. 2-8 Atomic force microscope (AFM) images of the surface of the (a) Ge, (b) $Ge_{0.955}Sn_{0.045}$ , and (c) $Ge_{0.895}Sn_{0.105}$ epitaxial structures. ....                                                                                                                                                                                                                                                                           | 19 |

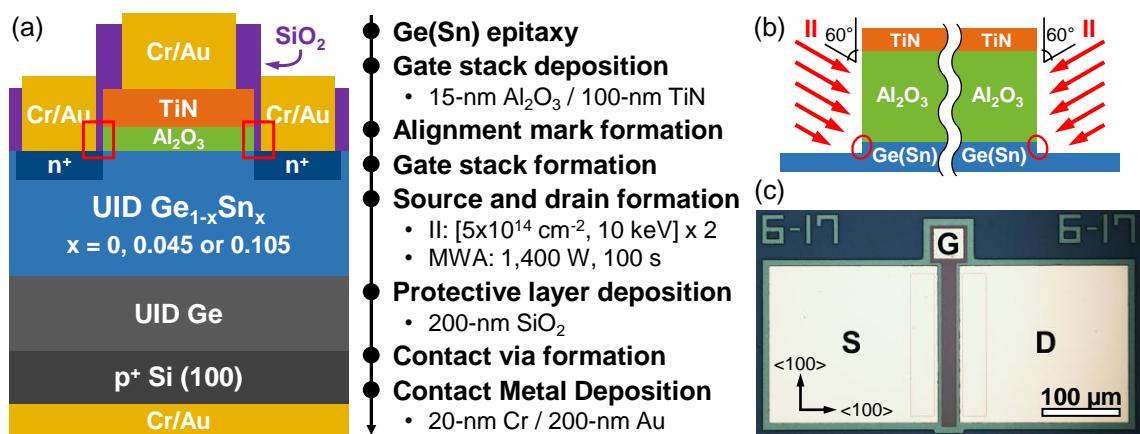

| Fig. 2-9 (a) A schematic of the device structure and the process flow of Ge(Sn) n-MOSFETs. (b) Enlarged portions of the red squares in (a) showing the angle of the 2-steps ion implantation (II). (c) An optical microscope (OM) image of a Ge(Sn) n-MOSFET. Crystallography directions $<100>$ are labeled.....                                                                                                                            | 20 |

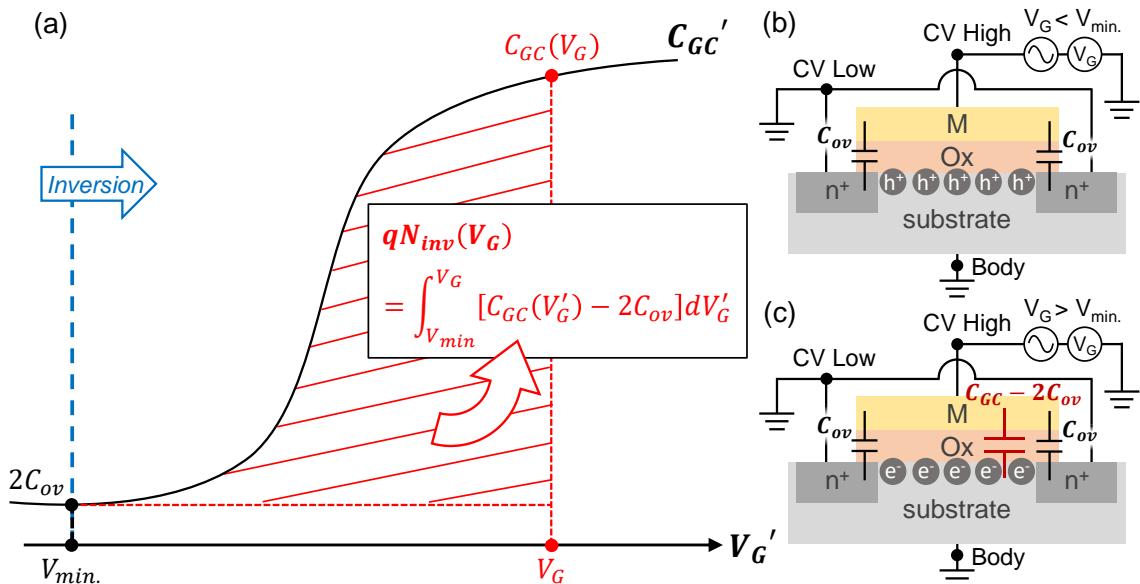

| Fig. 2-10 (a) A schematic of the normalized gate-to-channel capacitance ( $C_{GC}$ ) vs. gate voltage ( $V_G$ ) of an n-MOSFET as well as the derivation of inversion carrier density ( $N_{inv}$ ) and effective mobility ( $\mu_{eff}$ ). Schematics of the biasing configuration and capacitance components measured in (b) the accumulation or depletion regime ( $V_G < V_{min}$ ) and (c) the inversion regime ( $V_G > V_{min}$ ). 22 |    |

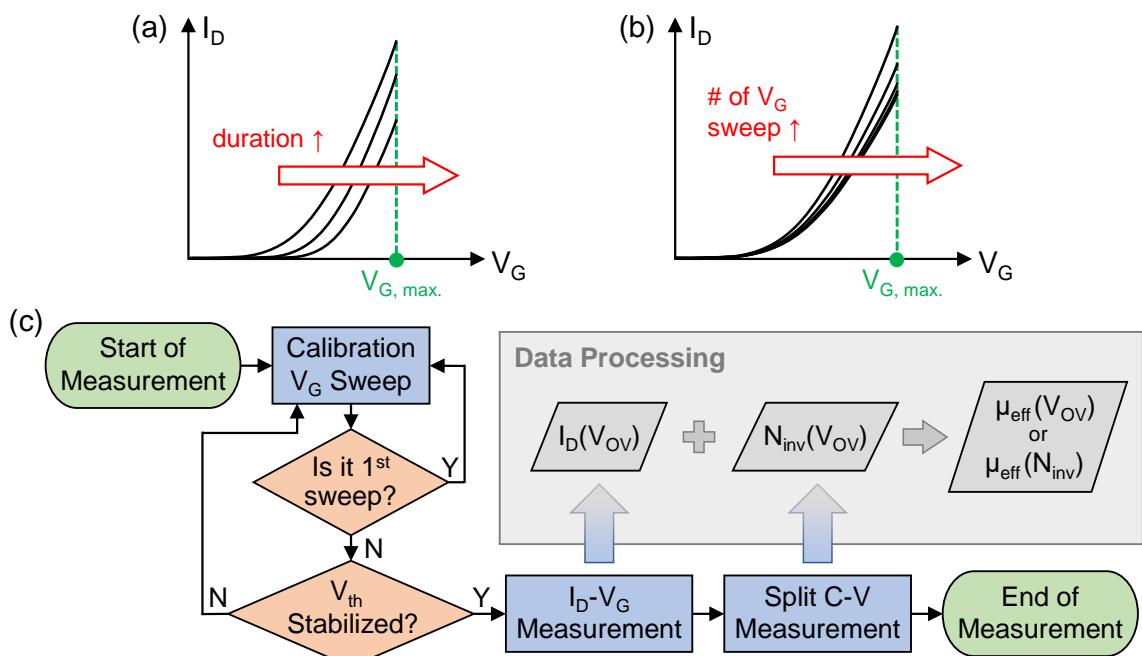

| Fig. 2-11 Schematics of $V_{th}$ shift caused by the increase of (a) $V_G$ sweep durations and (b) the number of $V_G$ sweeps. (c) A schematic of the standard measurement procedure. ....                                                                                                                                                                                                                                                   | 25 |

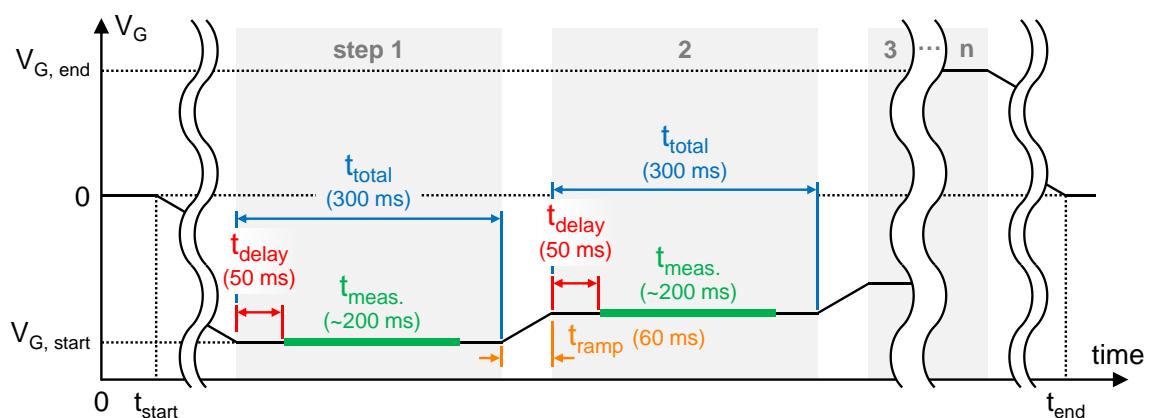

| Fig. 2-12 A schematic of the timing of each $V_G$ step during a single measurement. ....                                                                                                                                                                                                                                                                                                                                                     | 26 |

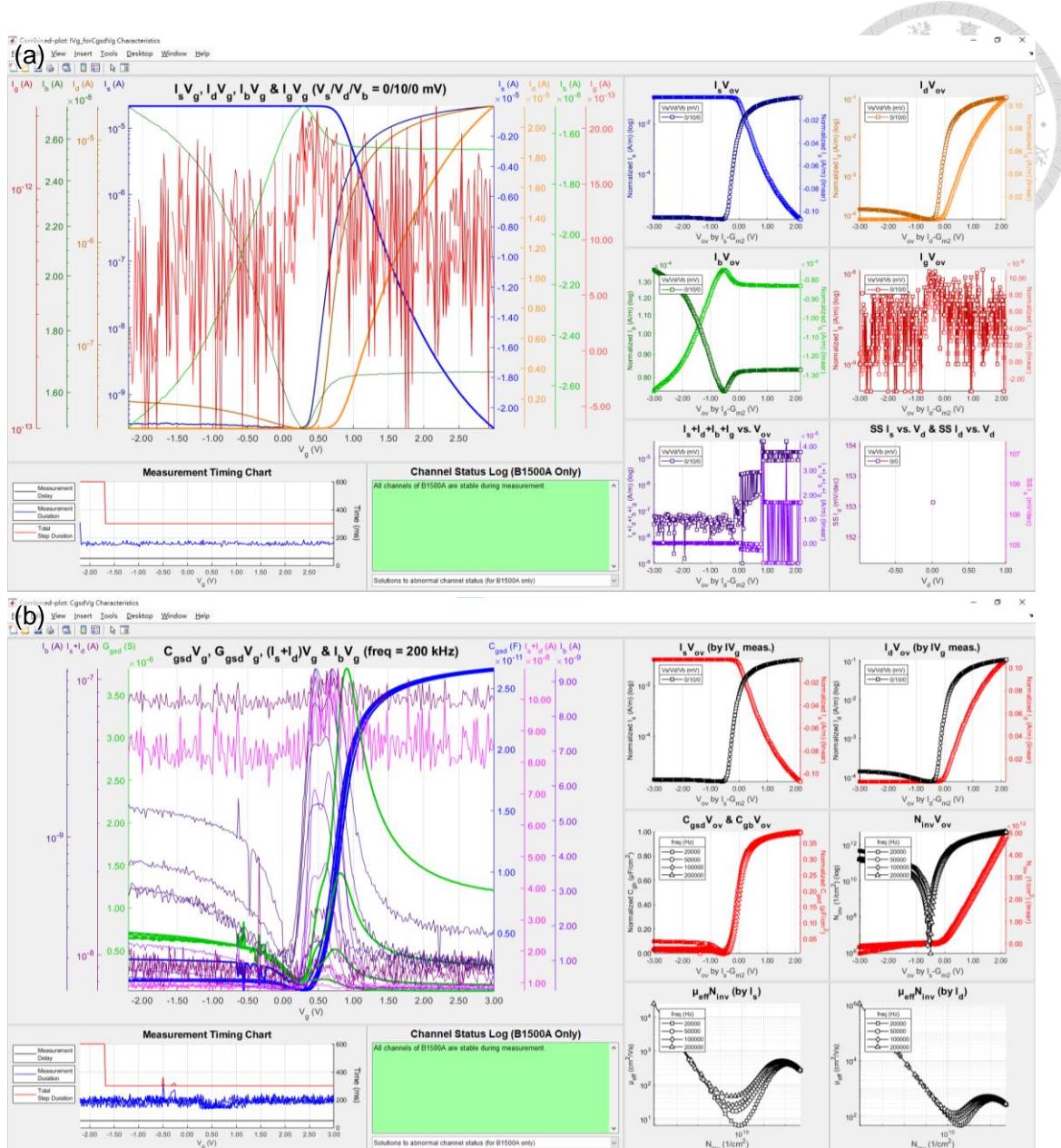

| Fig. 2-13 Screenshots of the monitoring panel of the MATLAB® program during the (a) transfer I-V and (b) split C-V measurement of the Ge n-MOSFET at 250 K. ....                                                                                                                                                                                                                                                                             | 27 |

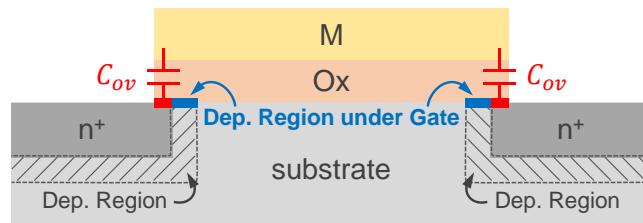

| Fig. 2-14 A schematic showing the reduction of channel area due to the junction depletion regions under the gate region.....                                                                                                                                                                                                                                                                                                                 | 28 |

|                                                                                                                                                                                                                                           |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

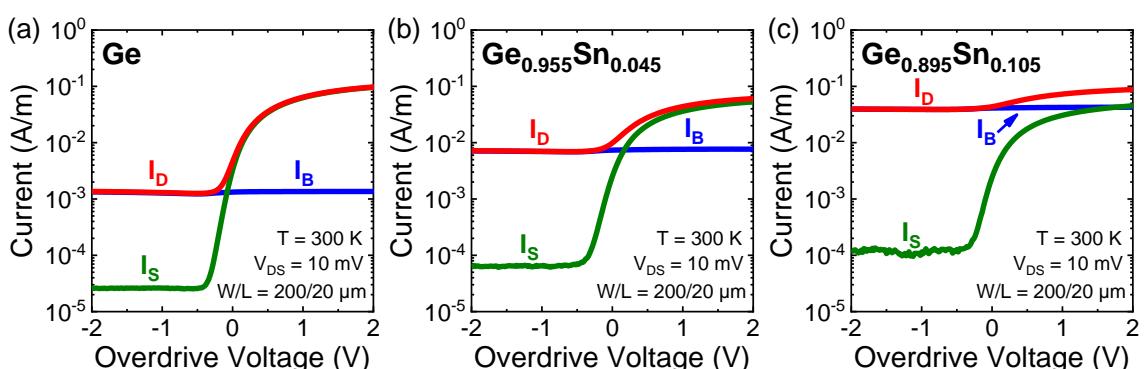

| Fig. 2-15 Normalized drain current ( $I_D$ ), source current ( $I_S$ ), and body current ( $I_B$ ) vs. overdrive voltage ( $V_{ov}$ ) of the (a) Ge, (b) $Ge_{0.955}Sn_{0.045}$ , and (c) $Ge_{0.895}Sn_{0.105}$ n-MOSFETs at 300 K ..... | 29 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                          |    |

|----------------------------------------------------------------------------------------------------------|----|

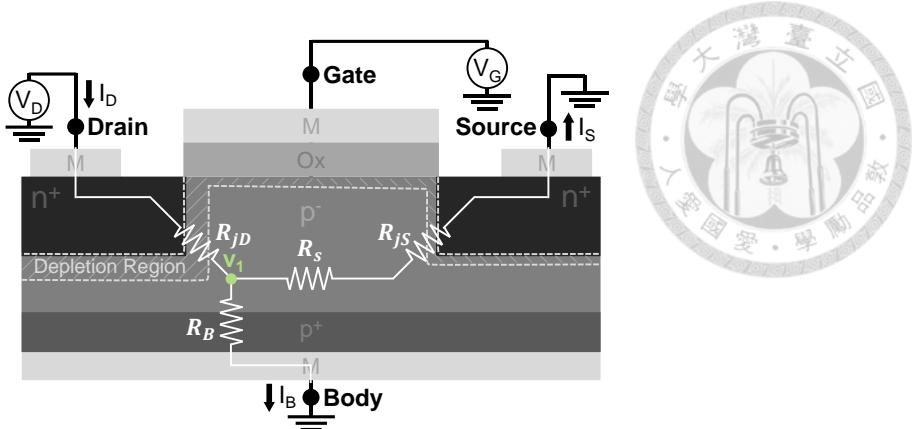

| Fig. 2-16 Schematics showing the polarity of current at each terminal and the internal resistances ..... | 30 |

|----------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                                                                                                                    |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

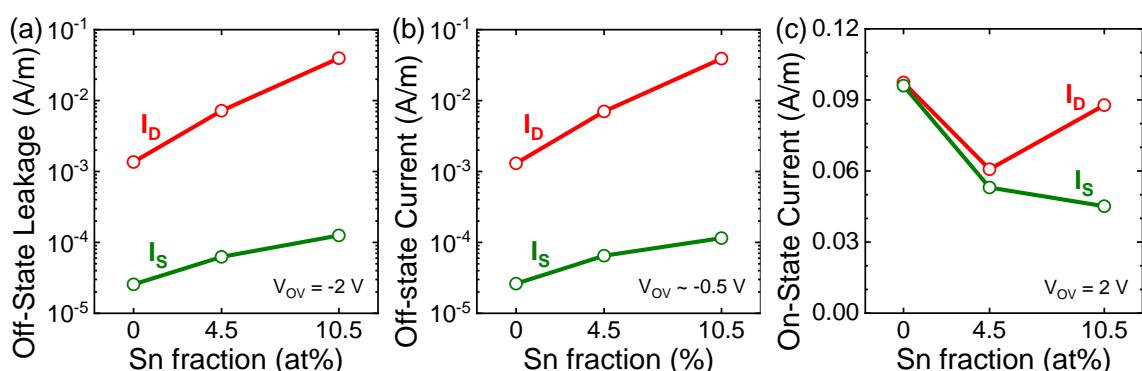

| Fig. 2-17 (a) The off-state leakage at $V_{ov} = -2$ V ( $I_{OFF*}$ ), (b) off-state current ( $I_{OFF}$ , $I_S$ or $I_D$ at $V_{ov} \sim -0.5$ V), and (c) on-state current ( $I_{ON}$ , $I_S$ or $I_D$ at $V_{ov} = 2$ V) vs. Sn fraction of the Ge(Sn) n-MOSFETs at 300 K ..... | 30 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                      |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2-18 The (a) on-off current ratio ( $I_{ON}/I_{OFF}$ ) and (b) minimum subthreshold swing ( $SS_{min}$ ) vs. Sn fraction of the Ge(Sn) n-MOSFETs at 300 K ..... | 31 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                                                                                                                                                        |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

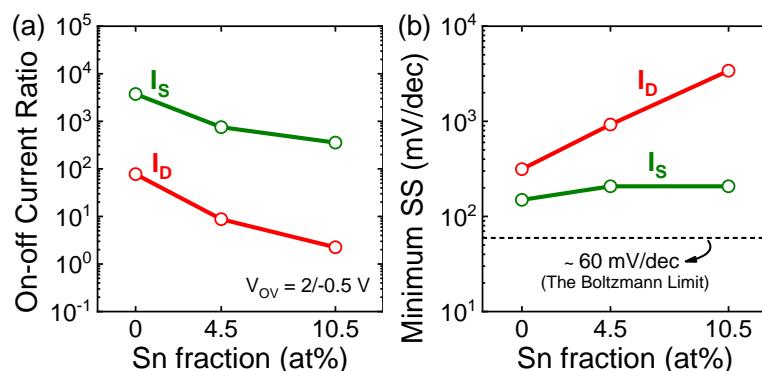

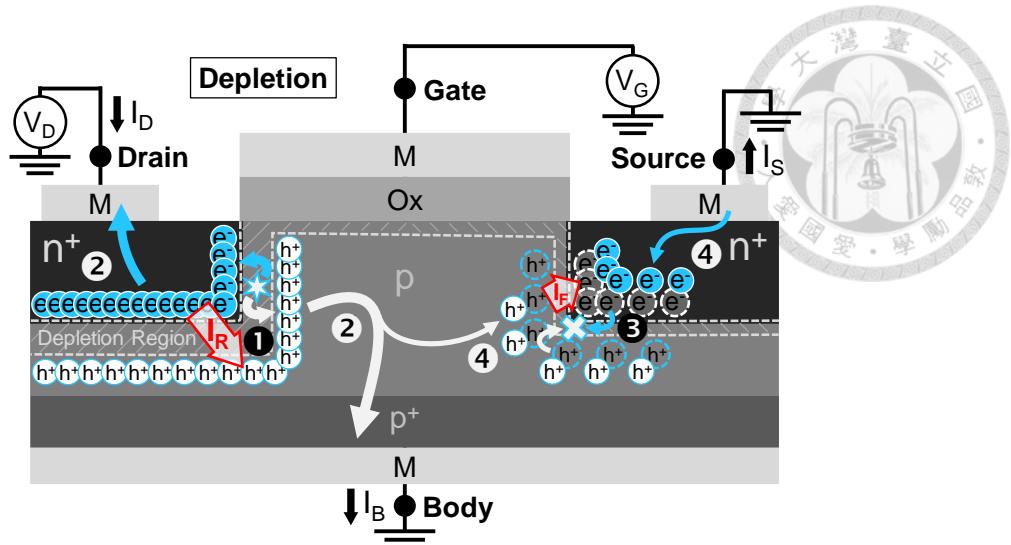

| Fig. 2-19 Schematics of the DC carrier transport mechanisms in the Ge(Sn) n-MOSFETs during the transfer I-V measurements in the accumulation regime ( $V_{ov} = -2$ V). Excess/Deficient carriers are represented by solid/hollow circles; electron/hole/total currents are represented by blue/white/red arrows ..... | 32 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2-20 Schematics of the DC carrier transport mechanisms in the Ge(Sn) n-MOSFETs during the transfer I-V measurements in the depletion regime ( $V_{ov} \sim -0.5$ V). ..... | 34 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                  |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2-21 Schematics of the DC carrier transport mechanisms in the Ge(Sn) n-MOSFETs during the transfer I-V measurements in the strong inversion regime ( $V_{ov} = 2$ V). ..... | 34 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                                                                      |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

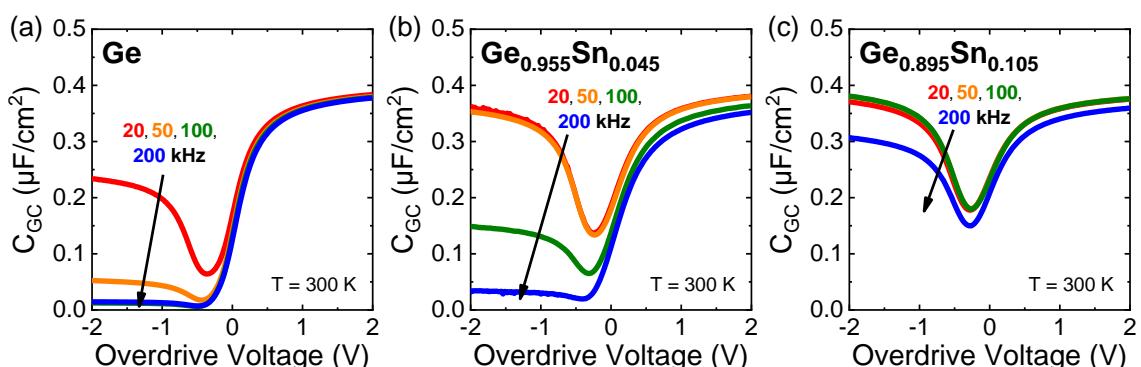

| Fig. 2-22 Normalized gate-to-channel capacitance ( $C_{GC}$ ) of the (a) Ge, (b) $Ge_{0.955}Sn_{0.045}$ , and (c) $Ge_{0.895}Sn_{0.105}$ n-MOSFETs vs. $V_{ov}$ measured with frequencies of 20, 50, 100, and 200 kHz at 300 K ..... | 35 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

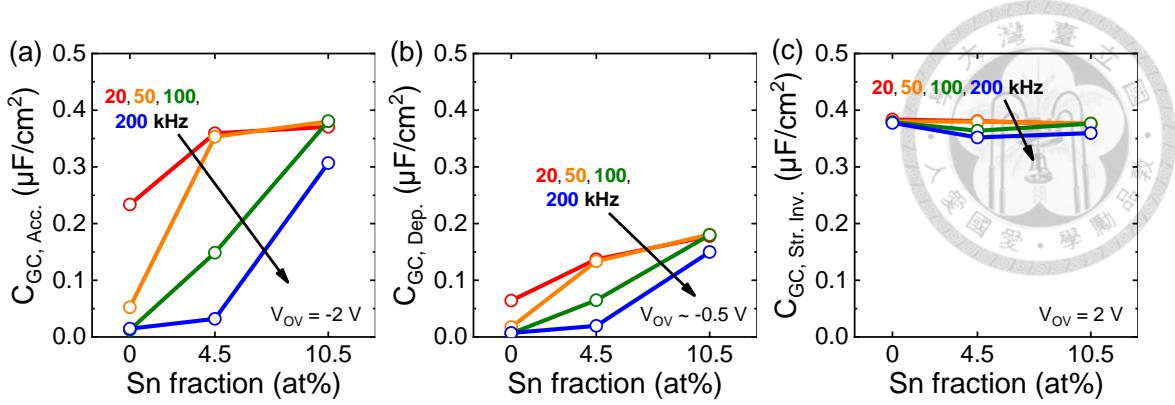

|                                                                                                                                                                  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fig. 2-23 $C_{GC}$ vs. Sn fraction in the (a) accumulation, (b) depletion, and (c) strong inversion regimes of the Ge(Sn) n-MOSFETs measured with frequencies of |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 20, 50, 100, and 200 kHz at 300 K .....                                                                                                                                                                                                                                                                                                                                                                            | 36 |

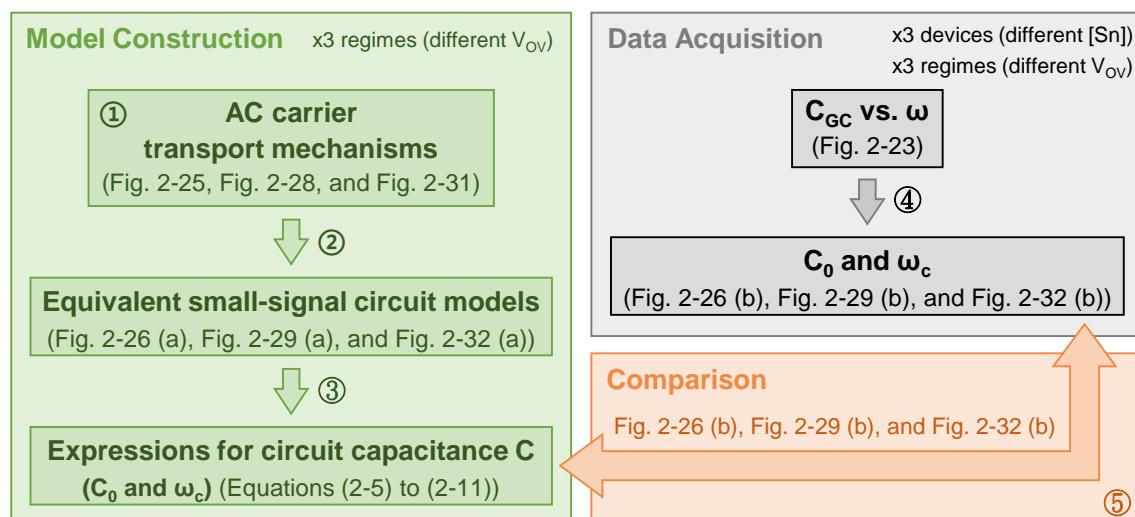

| Fig. 2-24 A schematic of the validation process of the split C-V characteristics.....                                                                                                                                                                                                                                                                                                                              | 37 |

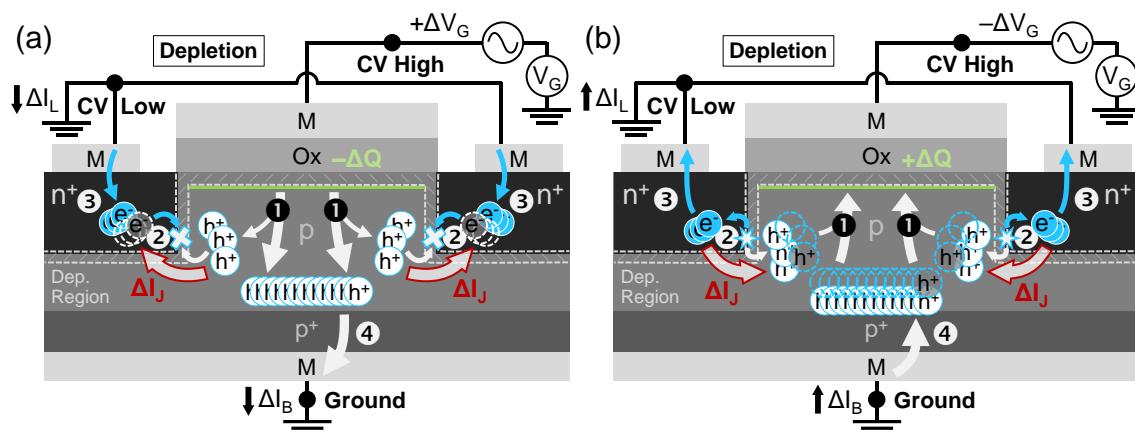

| Fig. 2-25 Schematics of the AC carrier transport mechanisms in the Ge(Sn) n-MOSFETs<br>during the (a) positive and (b) negative half of an AC cycle of the split C-V<br>measurements in the accumulation regime. Differential (AC) excess/deficient<br>carriers are represented by the solid/hollow circles, while differential (AC)<br>electron/hole/total currents are represented by blue/white/red arrows..... | 38 |

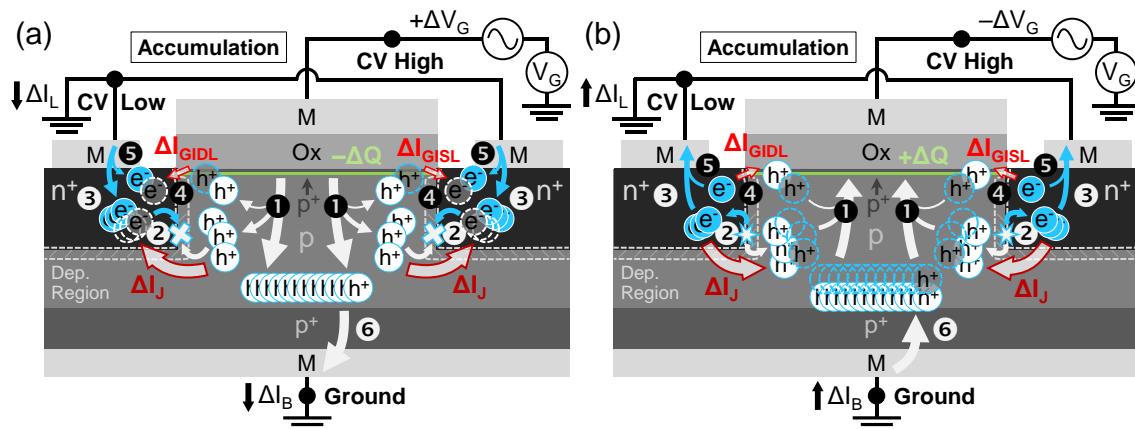

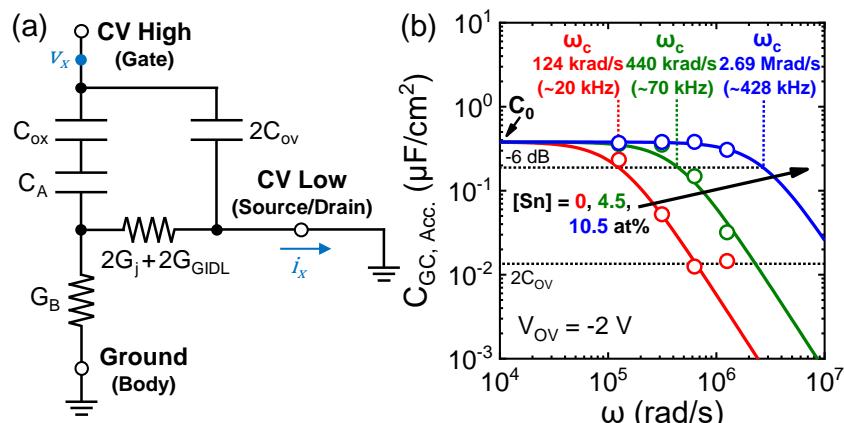

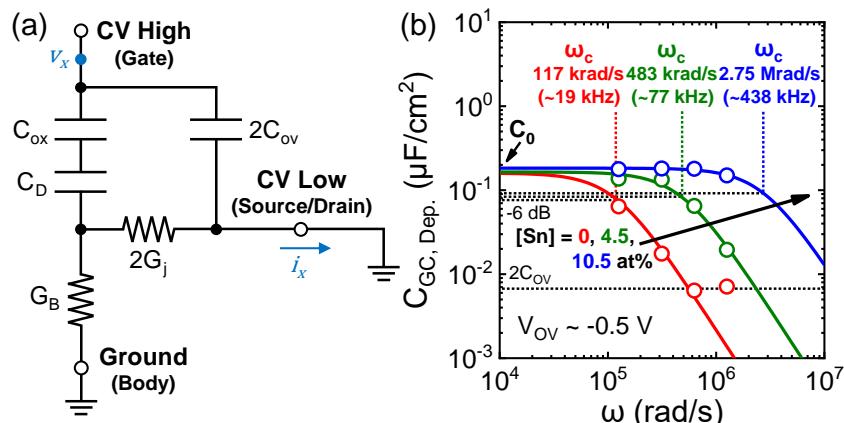

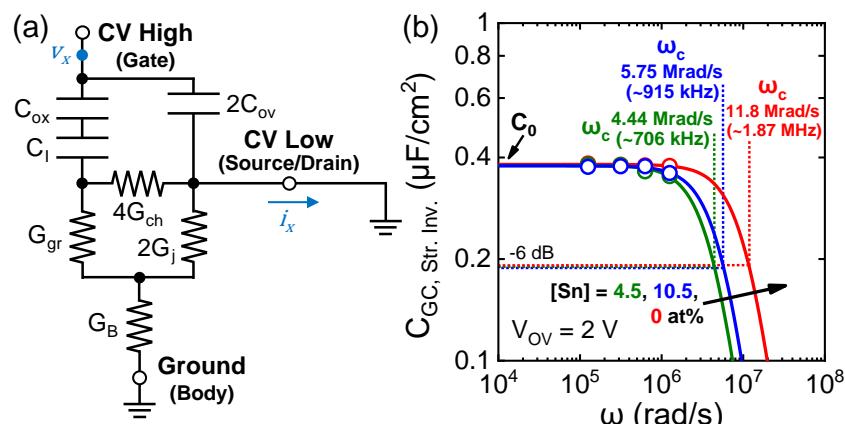

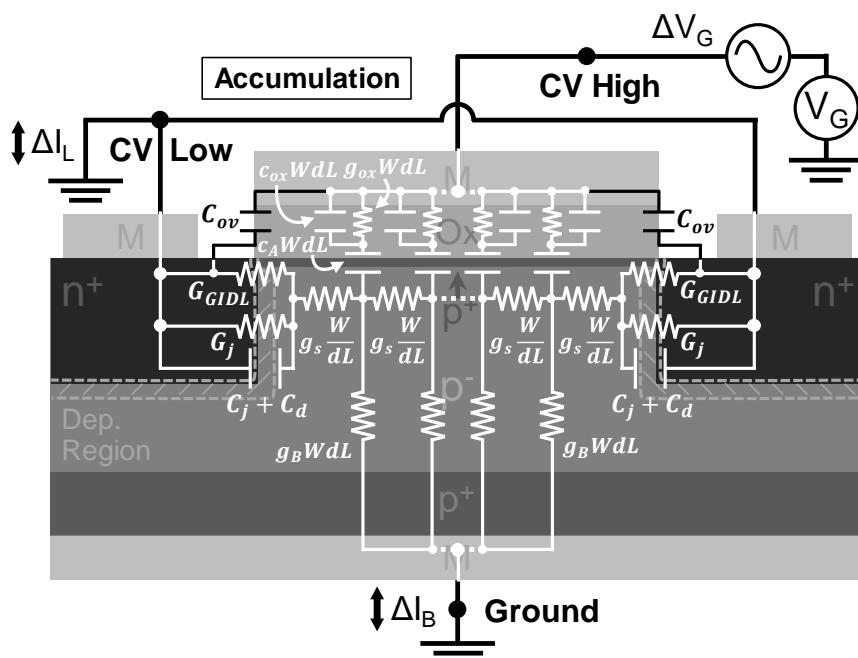

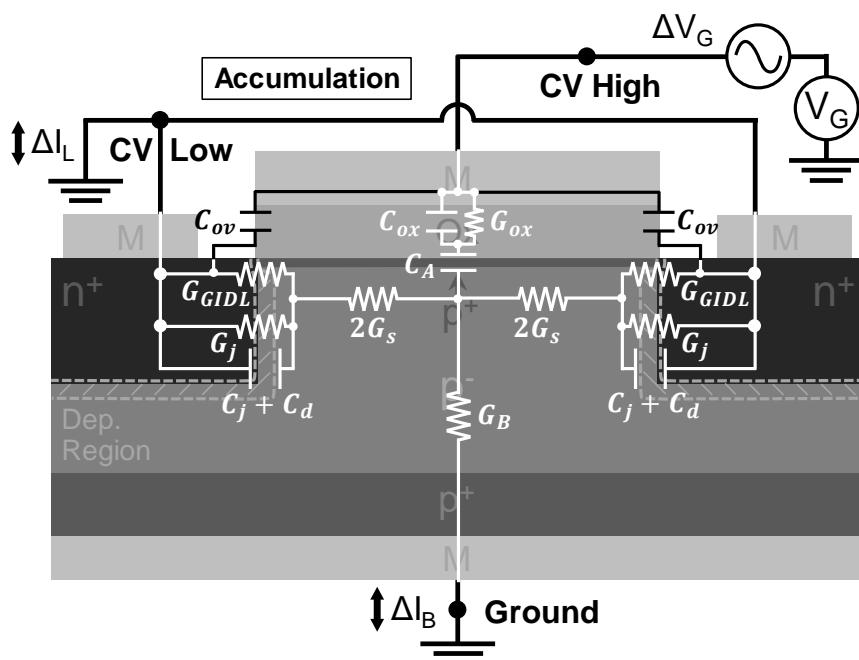

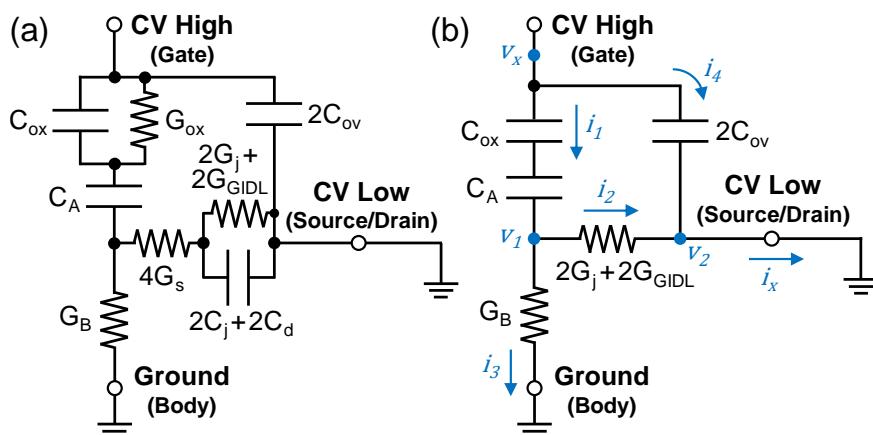

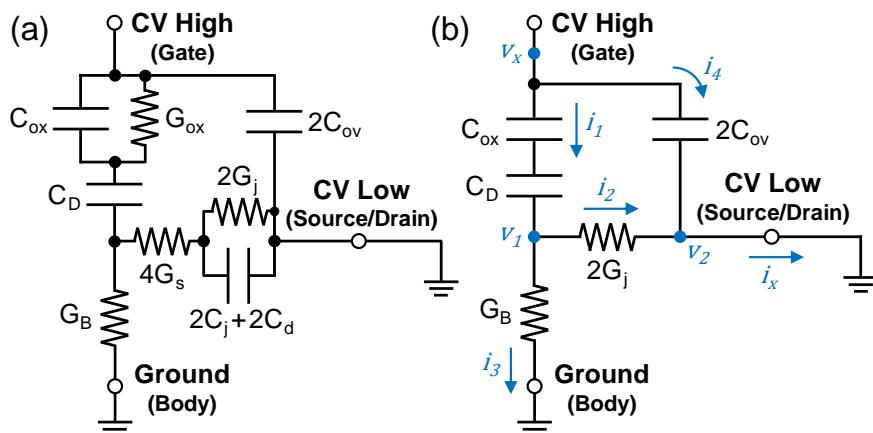

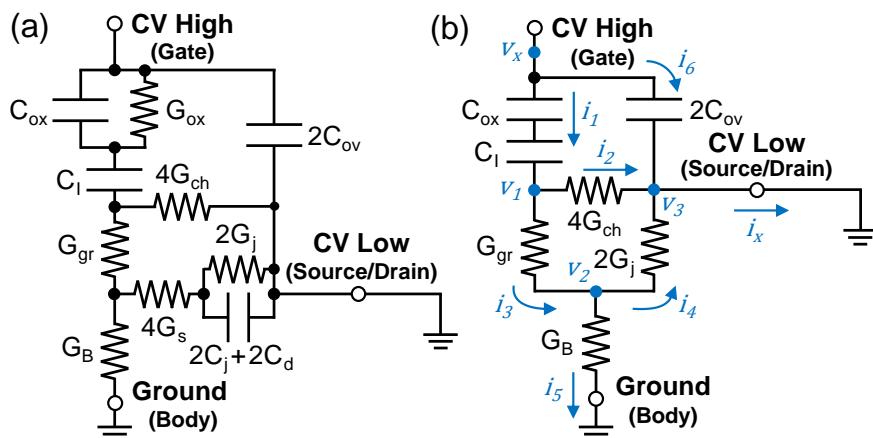

| Fig. 2-26 (a) An equivalent small-signal circuit model of the Ge(Sn) n-MOSFETs biased<br>in the accumulation regime. (b) $C_{GC}$ vs. angular frequency $\omega$ (replotted from<br>Fig. 2-23 (a)) and the fitted curves. ....                                                                                                                                                                                     | 40 |

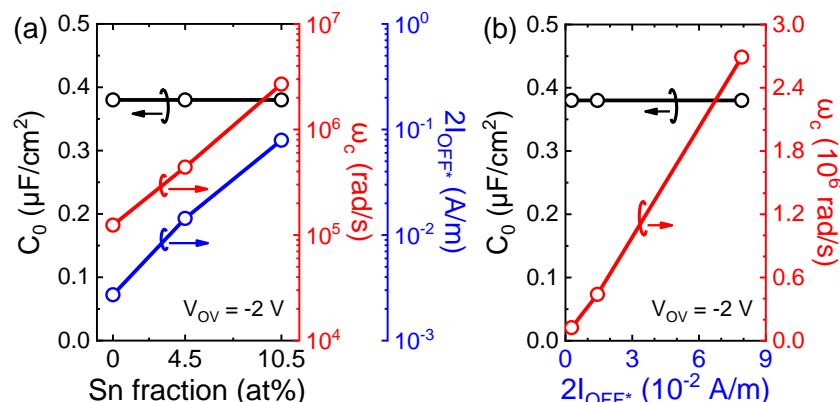

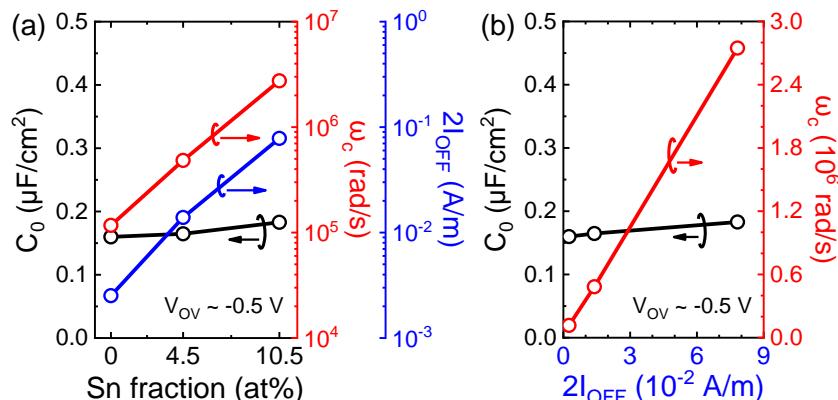

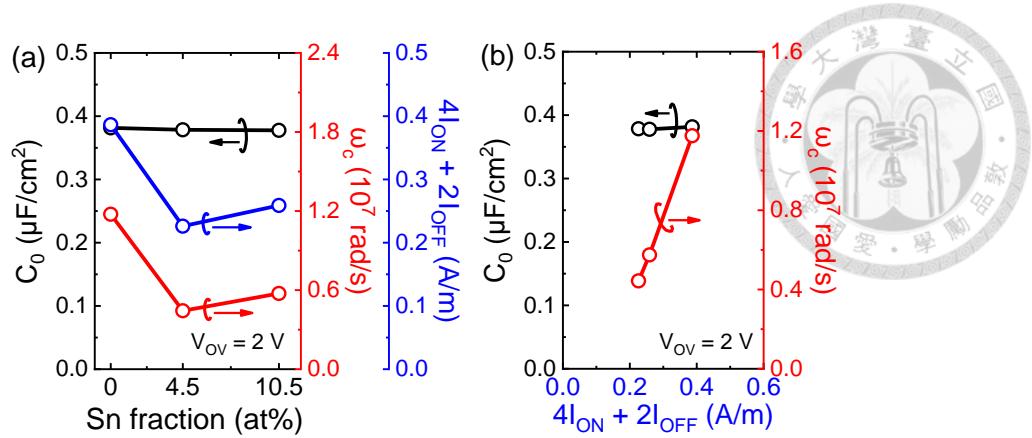

| Fig. 2-27 (a) Fitting parameters $C_0$ and $\omega_c$ (used in Fig. 2-26 (b)) as well as $2I_{OFF^*}$<br>(excerpted from Fig. 2-17 (a)) vs. Sn fraction. (b) $C_0$ and $\omega_c$ (from (a)) vs.<br>$2I_{OFF^*}$ (from (a)).....                                                                                                                                                                                   | 42 |

| Fig. 2-28 Schematics of the AC carrier transport mechanisms in the Ge(Sn) n-MOSFETs<br>during the (a) positive and (b) negative half of an AC cycle of the split C-V<br>measurements in the depletion regime. ....                                                                                                                                                                                                 | 43 |

| Fig. 2-29 (a) An equivalent small-signal circuit model of the Ge(Sn) n-MOSFETs biased<br>in the depletion regime. (b) $C_{GC}$ vs. angular frequency $\omega$ (replotted from Fig.<br>2-23 (b)) and the fitted curves. ....                                                                                                                                                                                        | 44 |

| Fig. 2-30 (a) Fitting parameters $C_0$ and $\omega_c$ (used in Fig. 2-29 (b)) as well as $2I_{OFF}$<br>(excerpted from Fig. 2-17 (b)) vs. Sn fraction. (b) $C_0$ and $\omega_c$ (from (a)) vs.<br>$2I_{OFF}$ (from (a)). ....                                                                                                                                                                                      | 45 |

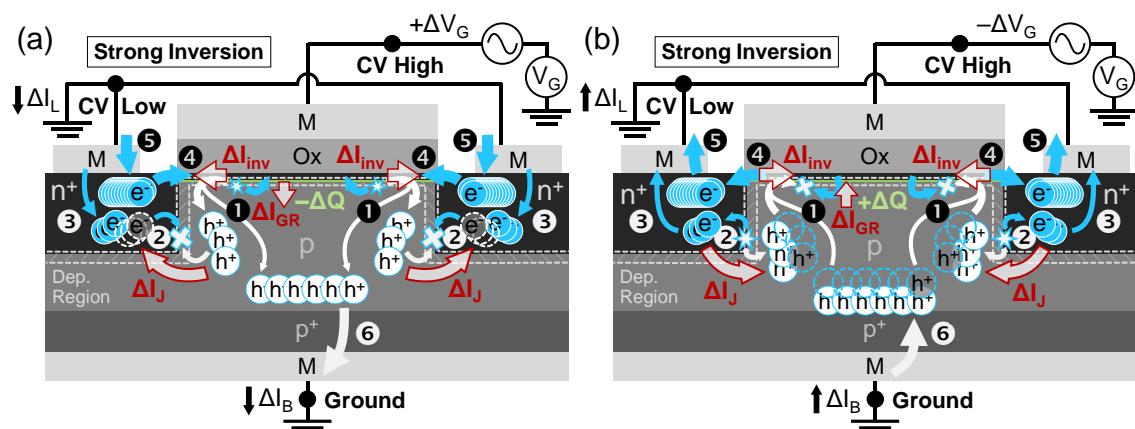

| Fig. 2-31 Schematics of the AC carrier transport mechanisms in the Ge(Sn) n-MOSFETs<br>during the (a) positive and (b) negative half of an AC cycle of the split C-V<br>measurements in the strong inversion regime. ....                                                                                                                                                                                          | 46 |

|                                                                                                                                                                                                                                                                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2-32 (a) An equivalent small-signal circuit model of the Ge(Sn) n-MOSFETs biased in the strong inversion regime. (b) $C_{GC}$ vs. angular frequency $\omega$ (replotted from Fig. 2-23 (c)) and the fitted curves.....                                                                                                                            | 47 |

| Fig. 2-33 (a) Fitting parameters $C_0$ and $\omega_c$ (used in Fig. 2-32 (b)) as well as $4I_{ON} + 2I_{OFF}$ (excerpted from Fig. 2-17 (b) and (c)) vs. Sn fraction. (b) $C_0$ and $\omega_c$ (from (a)) vs. $4I_{ON} + 2I_{OFF}$ (from (a)). .....                                                                                                   | 49 |

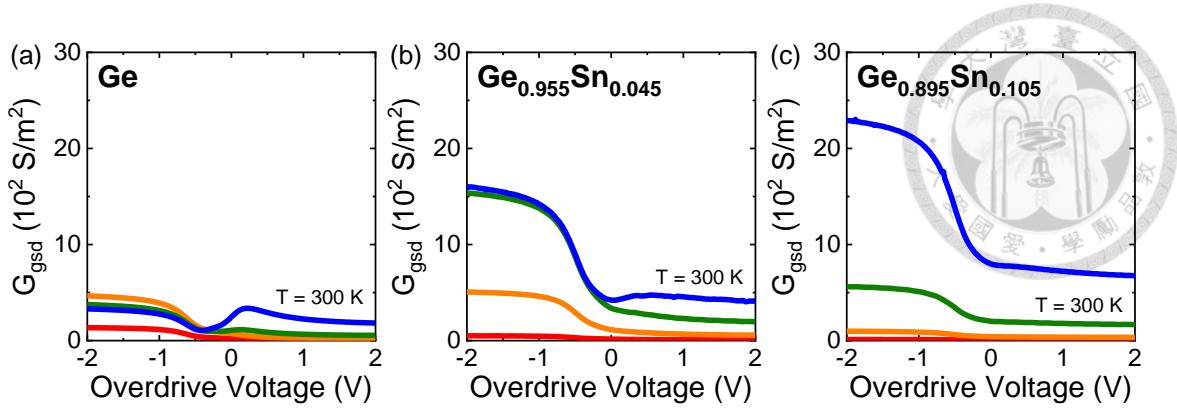

| Fig. 2-34 Normalized gate-to-source-drain conductance ( $G_{gsd}$ ) of the (a) Ge, (b) $Ge_{0.955}Sn_{0.045}$ , and (c) $Ge_{0.895}Sn_{0.105}$ n-MOSFETs vs. $V_{OV}$ measured with frequencies of 20, 50, 100, and 200 kHz at 300 K. .....                                                                                                            | 51 |

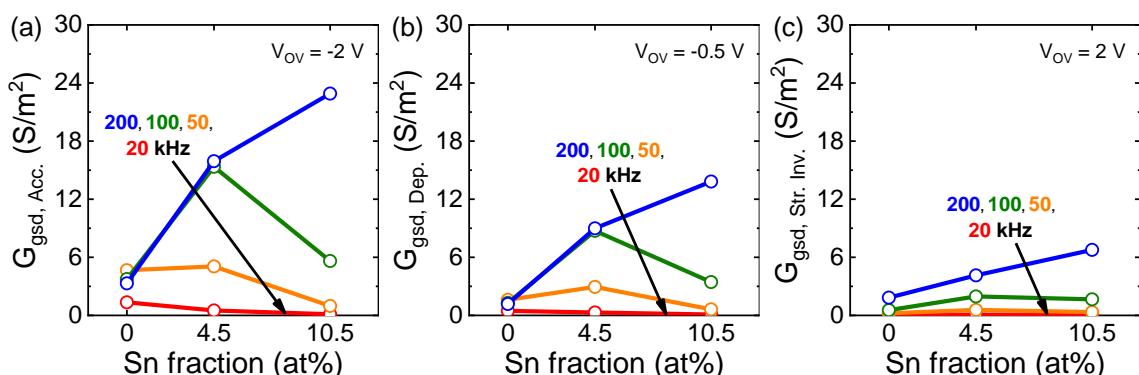

| Fig. 2-35 $G_{gsd}$ vs. Sn fraction in the (a) accumulation, (b) depletion, and (c) strong inversion regimes of the Ge(Sn) n-MOSFETs measured with frequencies of 20, 50, 100, and 200 kHz at 300 K. .....                                                                                                                                             | 51 |

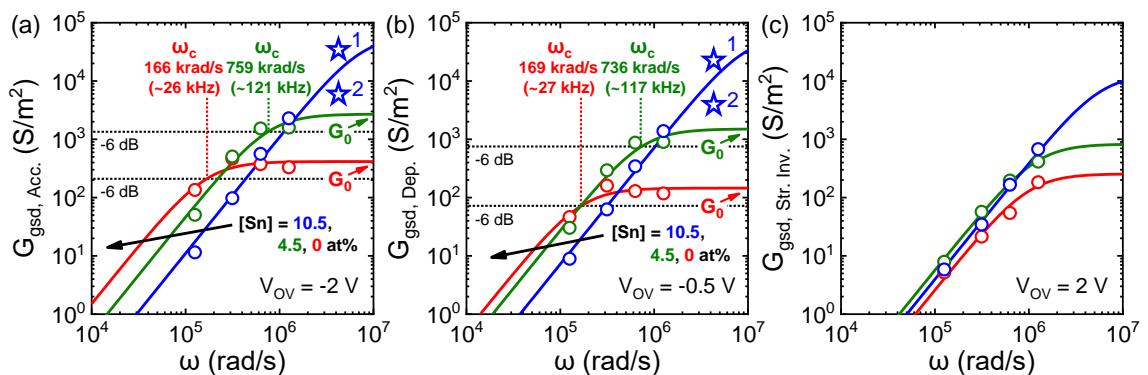

| Fig. 2-36 $G_{gsd}$ vs. angular frequency $\omega$ in the (a) accumulation (replotted from Fig. 2-35 (a)), (b) depletion (replotted from Fig. 2-35 (b)), and (c) strong inversion regimes (replotted from Fig. 2-35 (c)) along with the fitted curves. The blue stars represent the next possible high-frequency data. .....                           | 53 |

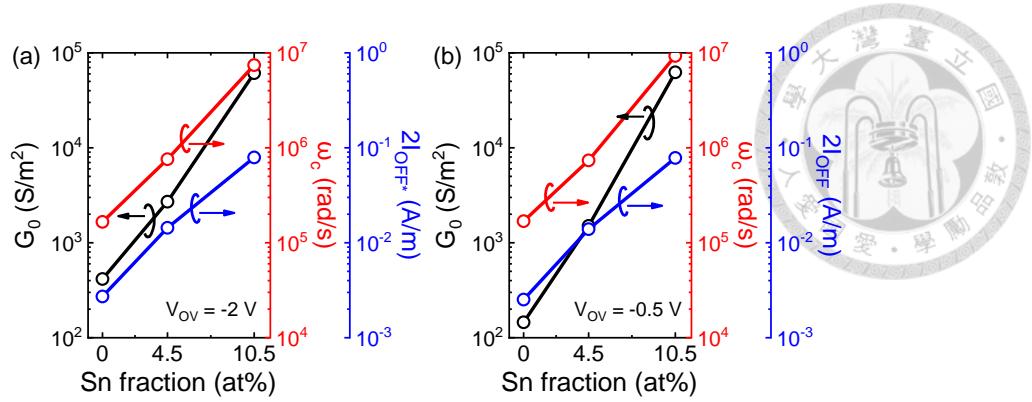

| Fig. 2-37 (a) Fitting parameters $G_0$ and $\omega_c$ (used in Fig. 2-36 (a)) as well as $2I_{OFF}^*$ (excerpted from Fig. 2-17 (a)) vs. Sn fraction in the accumulation regime. (b) Fitting parameters $G_0$ and $\omega_c$ (used in Fig. 2-36 (b)) as well as $2I_{OFF}$ (excerpted from Fig. 2-17 (b)) vs. Sn fraction in the depletion regime..... | 54 |

| Fig. 2-38 (a) $G_0$ and $\omega_c$ vs. $2I_{OFF}^*$ in the accumulation regime. (b) $G_0$ and $\omega_c$ vs. $2I_{OFF}$ in the depletion regime. .....                                                                                                                                                                                                 | 54 |

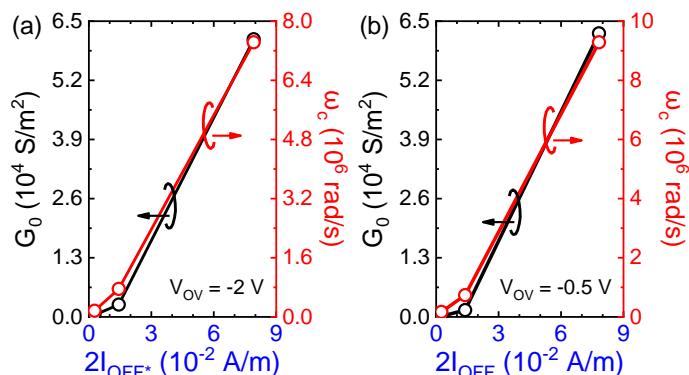

| Fig. 2-39 Effective mobility ( $\mu_{eff}$ ) vs. inversion carrier density ( $N_{inv}$ ) of the (a) Ge, (b) $Ge_{0.955}Sn_{0.045}$ , and (c) $Ge_{0.895}Sn_{0.105}$ n-MOSFETs measured at frequencies of 20, 50, 100, and 200 kHz at 300 K. .....                                                                                                      | 56 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

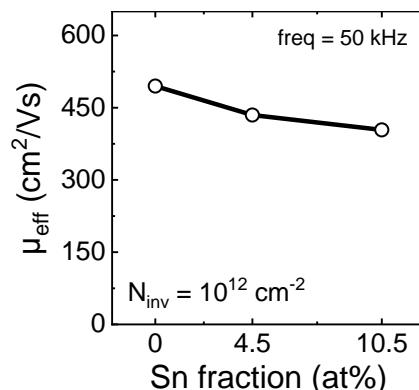

| Fig. 2-40 $\mu_{\text{eff}}$ (extracted from $I_s$ and $C_{\text{GC}}$ at 50 kHz) vs. Sn fraction at a fixed $N_{\text{inv}}$ of $10^{12}$ $\text{cm}^{-2}$ at 300 K .....                                                                                                                                                                                                                                                                                | 58 |

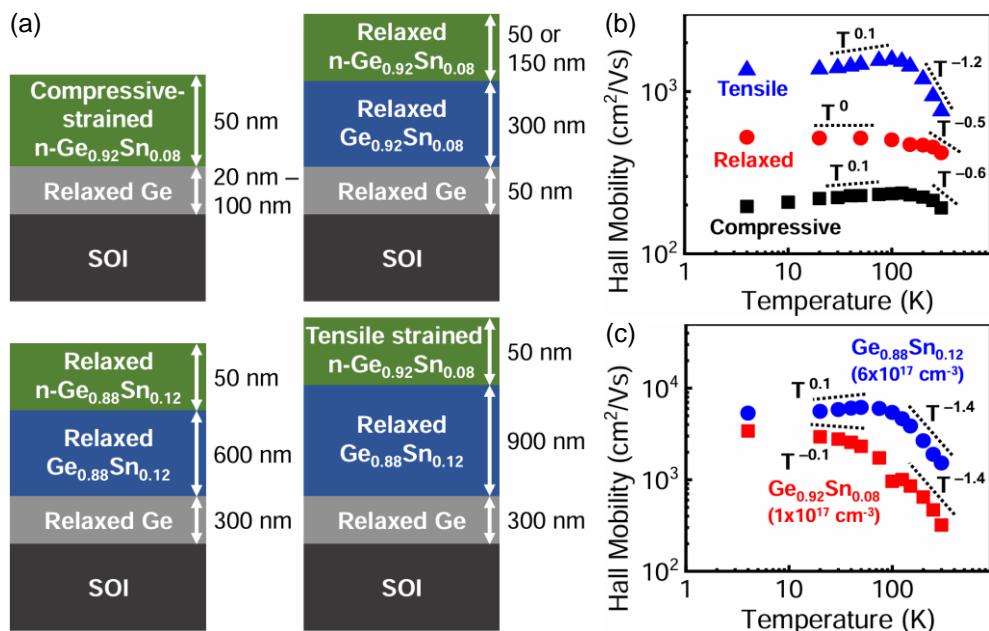

| Fig. 3-1 (a) Epitaxial structures of the $\text{Ge}_{0.92}\text{Sn}_{0.08}$ and $\text{Ge}_{0.88}\text{Sn}_{0.12}$ films under different strain conditions. Hall mobility vs. temperature of (b) $\text{Ge}_{0.92}\text{Sn}_{0.08}$ films under different strain conditions as well as (c) strain-relaxed $\text{Ge}_{0.92}\text{Sn}_{0.08}$ and $\text{Ge}_{0.88}\text{Sn}_{0.12}$ films [9] .....                                                       | 60 |

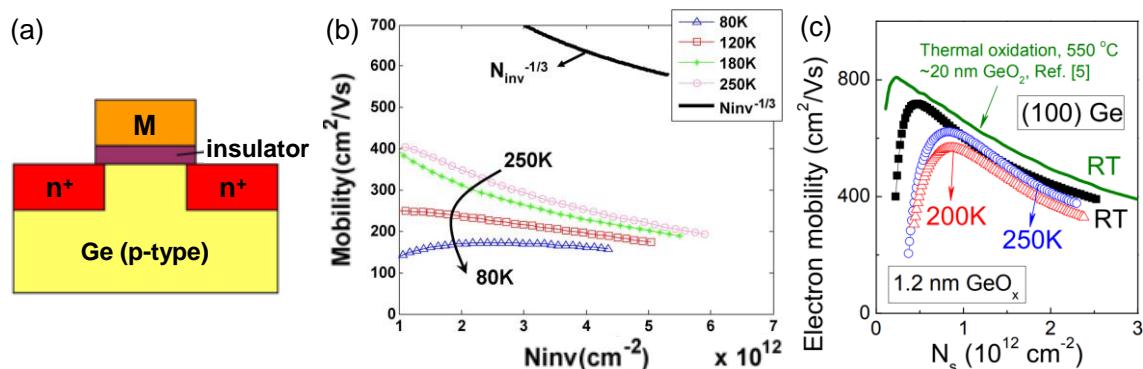

| Fig. 3-2 (a) Device structure of a Ge n-MOSFET with its effective electron mobility vs. inversion carrier density ( $N_{\text{inv}}$ or $N_s$ ) at various temperatures reported in (b) [79] and (c) [33] .....                                                                                                                                                                                                                                           | 61 |

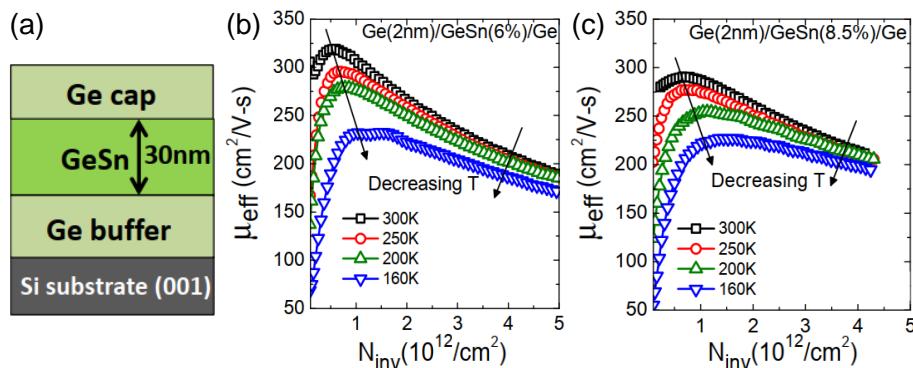

| Fig. 3-3 (a) Epitaxial structure of the GeSn capped with a thin Ge layer. Effective electron mobility ( $\mu_{\text{eff}}$ ) vs. inversion carrier density ( $N_{\text{inv}}$ ) of the (b) $\text{Ge}_{0.94}\text{Sn}_{0.06}$ and (c) $\text{Ge}_{0.915}\text{Sn}_{0.085}$ n-MOSFETs (with a 2-nm Ge capping layer) at various temperatures [21] .....                                                                                                    | 62 |

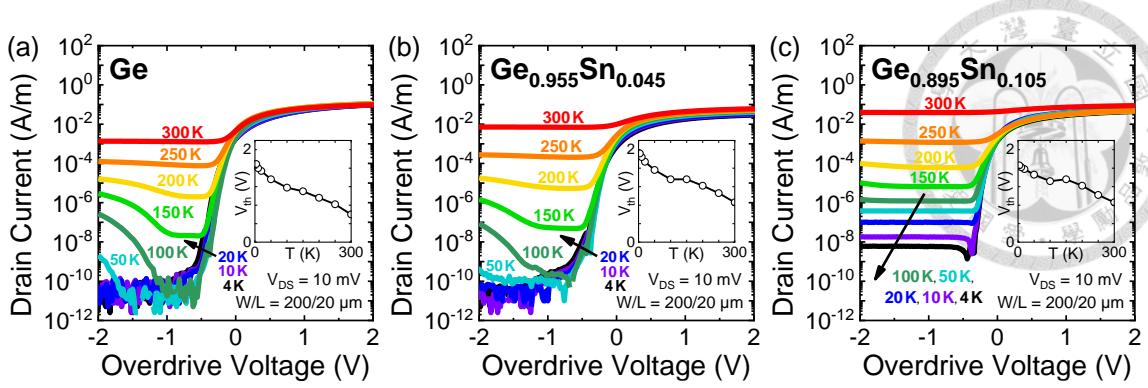

| Fig. 3-4 Normalized drain current ( $I_D$ ) vs. overdrive voltage ( $V_{\text{ov}}$ ) of the (a) Ge, (b) $\text{Ge}_{0.955}\text{Sn}_{0.045}$ , and (c) $\text{Ge}_{0.895}\text{Sn}_{0.105}$ n-MOSFETs from 300 K to 4 K. Threshold voltage ( $V_{\text{th}}$ ) vs. temperature (T) of the Ge, $\text{Ge}_{0.955}\text{Sn}_{0.045}$ , and $\text{Ge}_{0.895}\text{Sn}_{0.105}$ n-MOSFETs are shown in the insets of (a), (b), and (c), respectively ..... | 64 |

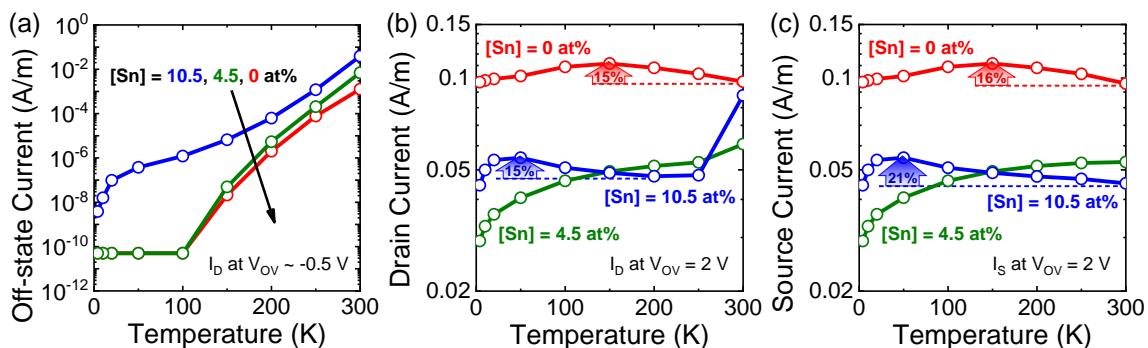

| Fig. 3-5 (a) Off-state current ( $I_{\text{OFF}}$ , $I_D$ at $V_{\text{ov}} \sim -0.5$ V), (b) on-state drain current ( $I_{\text{ON},D}$ , $I_D$ at $V_{\text{ov}} = 2$ V), and (c) on-state source current ( $I_{\text{ON},S}$ , $I_s$ at $V_{\text{ov}} = 2$ V) vs. temperature of the Ge(Sn) n-MOSFETs .....                                                                                                                                          | 65 |

| Fig. 3-6 (a) On-off current ratio ( $I_{\text{ON}}/I_{\text{OFF}}$ ), minimum subthreshold swing ( $SS_{\text{min}}$ ) extracted from (b) $I_D$ - $V_{\text{ov}}$ curves (Fig. 3-4) and (c) $I_s$ - $V_{\text{ov}}$ curves (not shown) vs. temperature of the Ge(Sn) n-MOSFETs .....                                                                                                                                                                      | 66 |

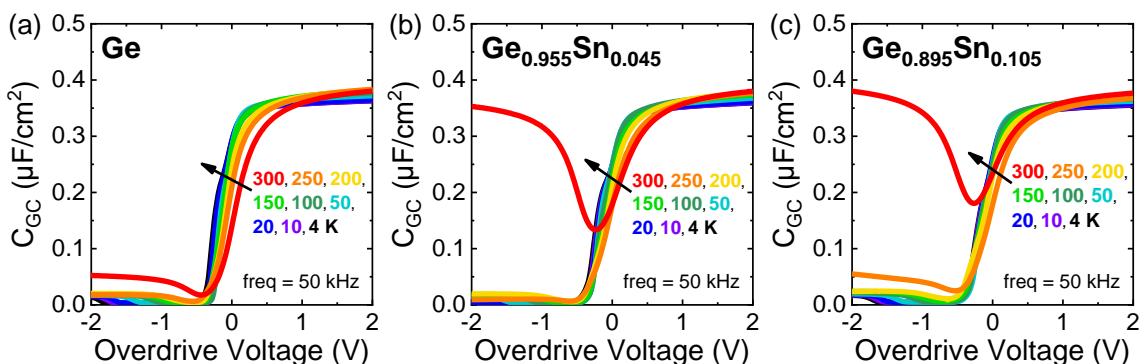

| Fig. 3-7 Normalized gate-to-channel capacitance ( $C_{\text{GC}}$ ) vs. $V_{\text{ov}}$ of the (a) Ge, (b)                                                                                                                                                                                                                                                                                                                                                |    |

|                                                                                                                                                                                                                                                                                                                          |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Ge <sub>0.955</sub> Sn <sub>0.045</sub> , and (c) Ge <sub>0.895</sub> Sn <sub>0.105</sub> n-MOSFETs measured with frequencies of 50 kHz from 300 K to 4 K.....                                                                                                                                                           | 67 |

| Fig. 3-8 $C_{GC}$ vs. temperature in the (a) accumulation ( $V_{ov} = -2$ V), (b) depletion ( $V_{ov} \approx -0.5$ V), and (c) strong inversion ( $V_{ov} = 2$ V) regimes of the Ge(Sn) n-MOSFETs measured with frequencies of 50 kHz. ....                                                                             | 68 |

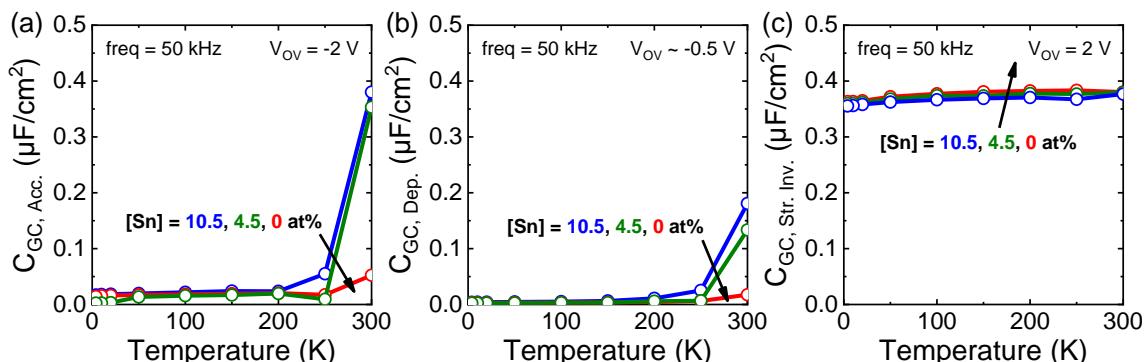

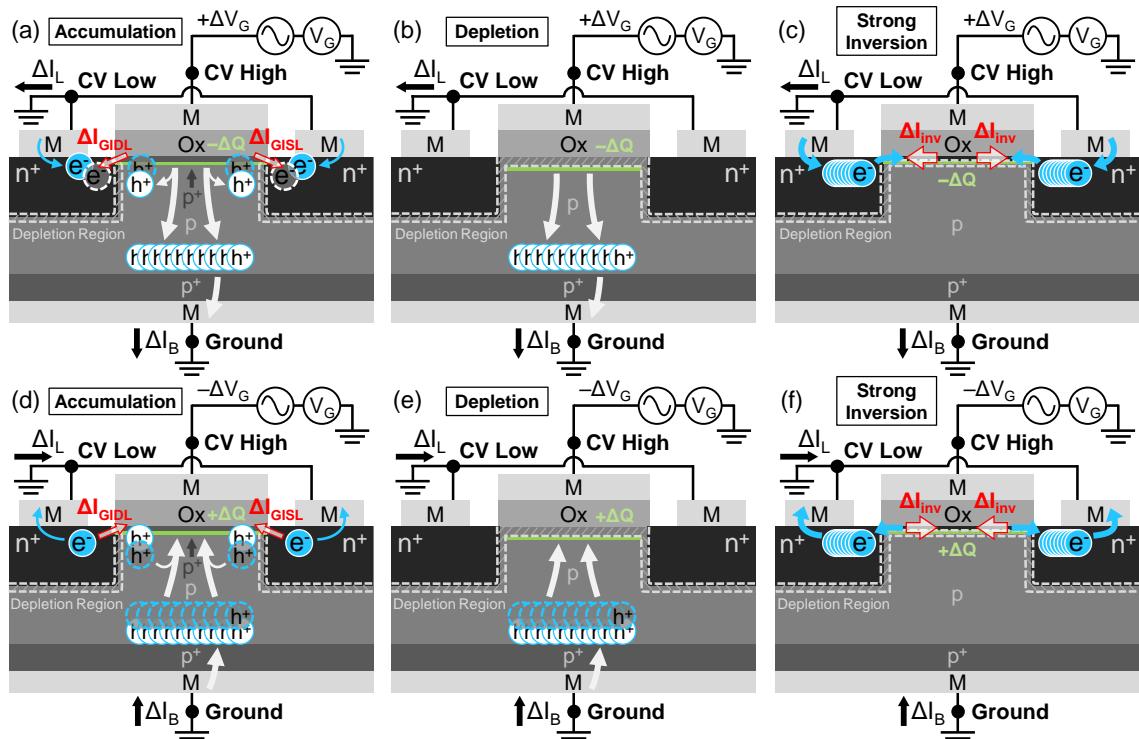

| Fig. 3-9 Schematics showing the AC carrier transport mechanisms in the Ge(Sn) n-MOSFETs during the positive/negative half of an AC cycle of the split C-V measurements in the (a/d) accumulation, (b/e) depletion, and (c/f) strong inversion regimes at the lowest temperature of 4 K. ....                             | 69 |

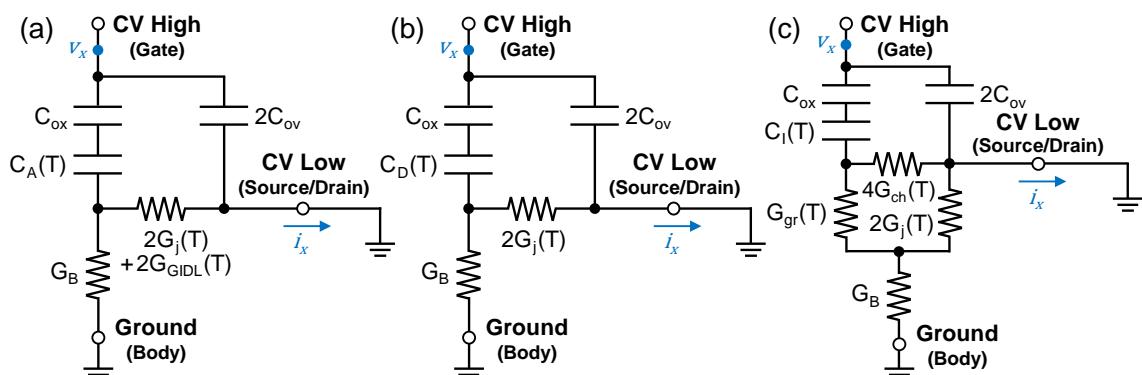

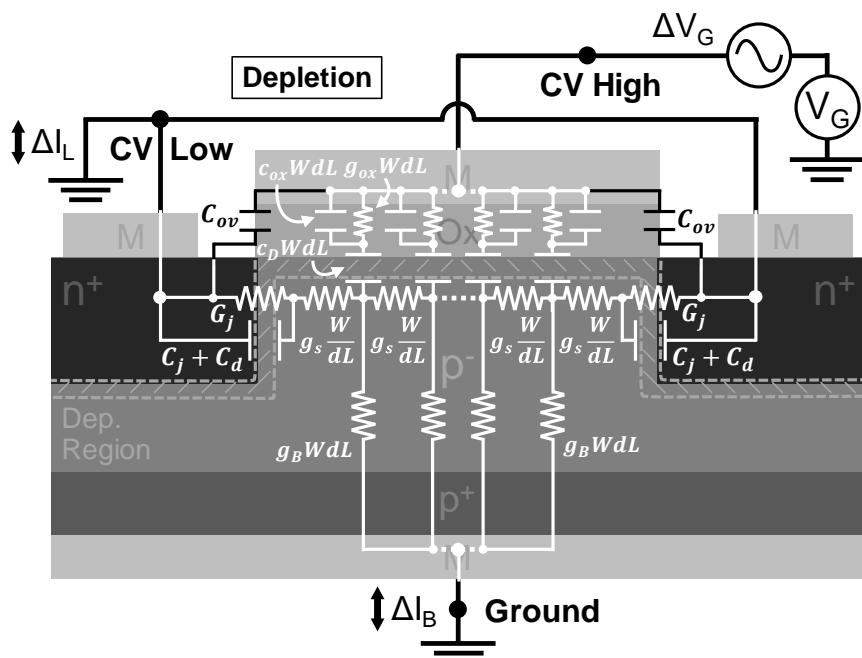

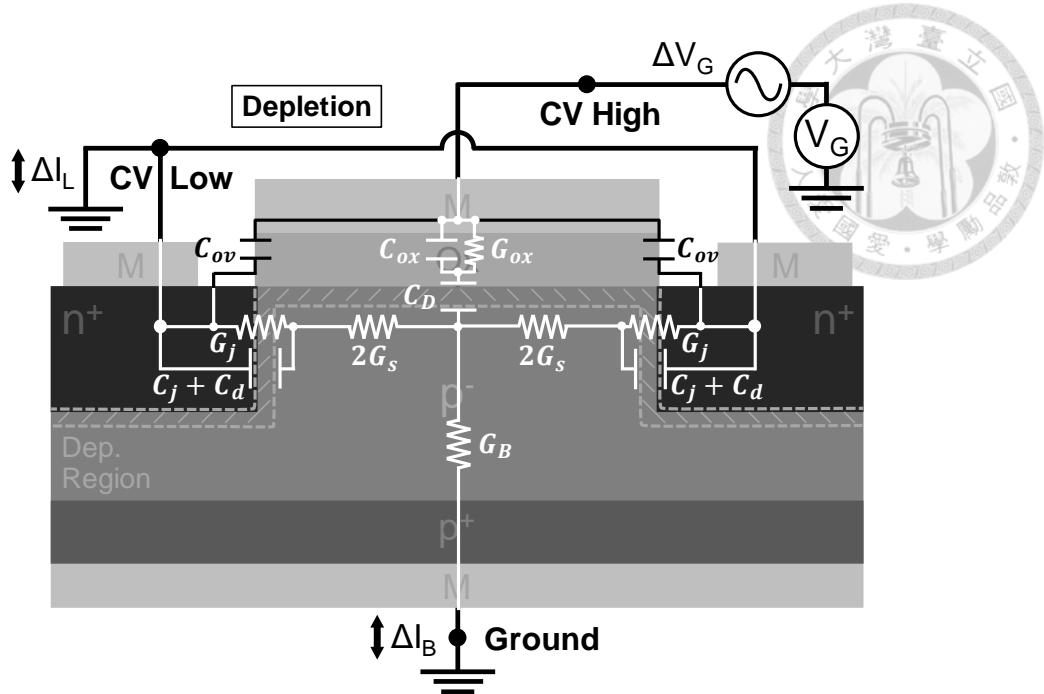

| Fig. 3-10 Equivalent small-signal circuit models of the Ge(Sn) n-MOSFETs biased in the (a) accumulation, (b) depletion, and (c) strong inversion regimes at temperatures ranging from 300 K to 4 K. ....                                                                                                                 | 70 |

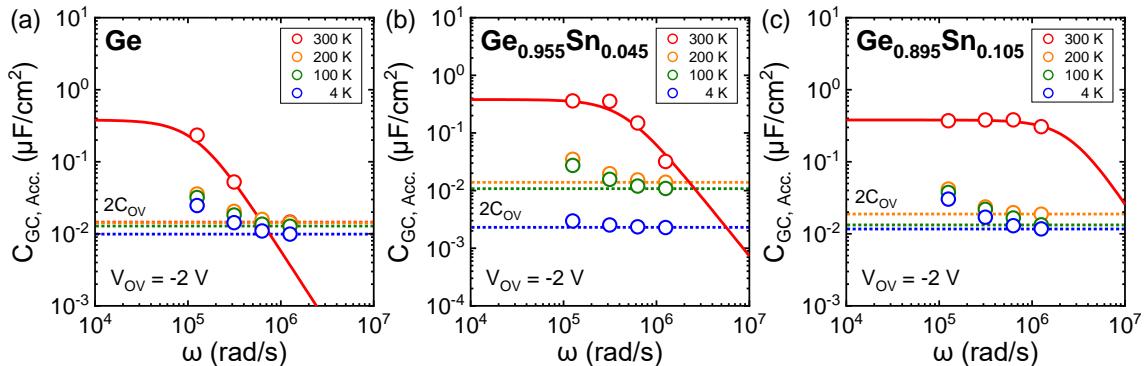

| Fig. 3-11 $C_{GC}$ vs. angular frequency $\omega$ (replotted from Fig. 3-8 (a) and data measured at other frequencies, not shown) of the (a) Ge, (b) Ge <sub>0.955</sub> Sn <sub>0.045</sub> , and (c) Ge <sub>0.895</sub> Sn <sub>0.105</sub> n-MOSFETs in the accumulation regime at 300 K, 200 K, 100 K and 4 K. .... | 71 |

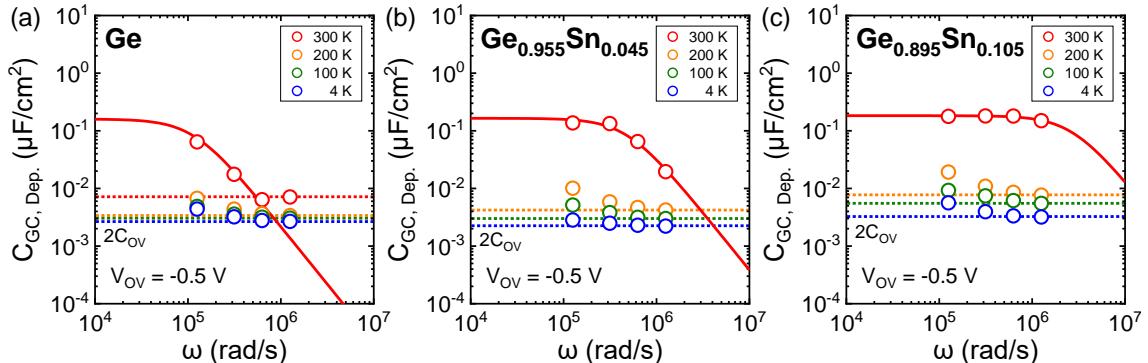

| Fig. 3-12 $C_{GC}$ vs. angular frequency $\omega$ (replotted from Fig. 3-8 (b) and data measured at other frequencies, not shown) of the (a) Ge, (b) Ge <sub>0.955</sub> Sn <sub>0.045</sub> , and (c) Ge <sub>0.895</sub> Sn <sub>0.105</sub> n-MOSFETs in the depletion regime at 300 K, 200 K, 100 K and 4 K. ....    | 73 |

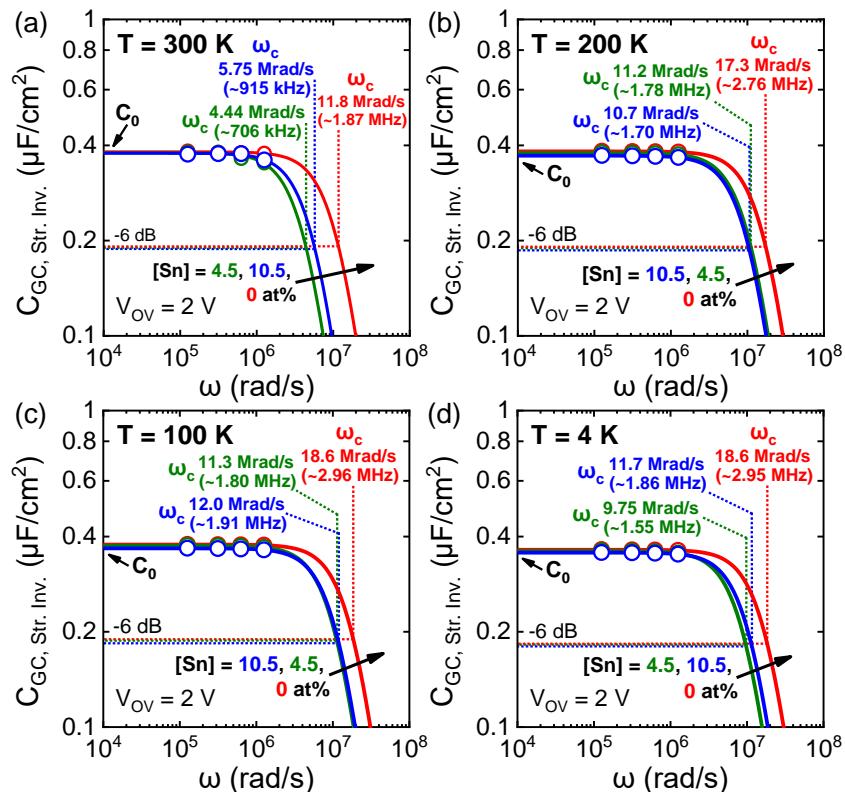

| Fig. 3-13 $C_{GC}$ vs. angular frequency $\omega$ (replotted from Fig. 3-8 (c) and data measured at other frequencies, not shown) of the Ge(Sn) n-MOSFETs in the strong inversion regime at (a) 300 K, (b) 200 K, (c) 100 K, and (d) 4 K. ....                                                                           | 75 |

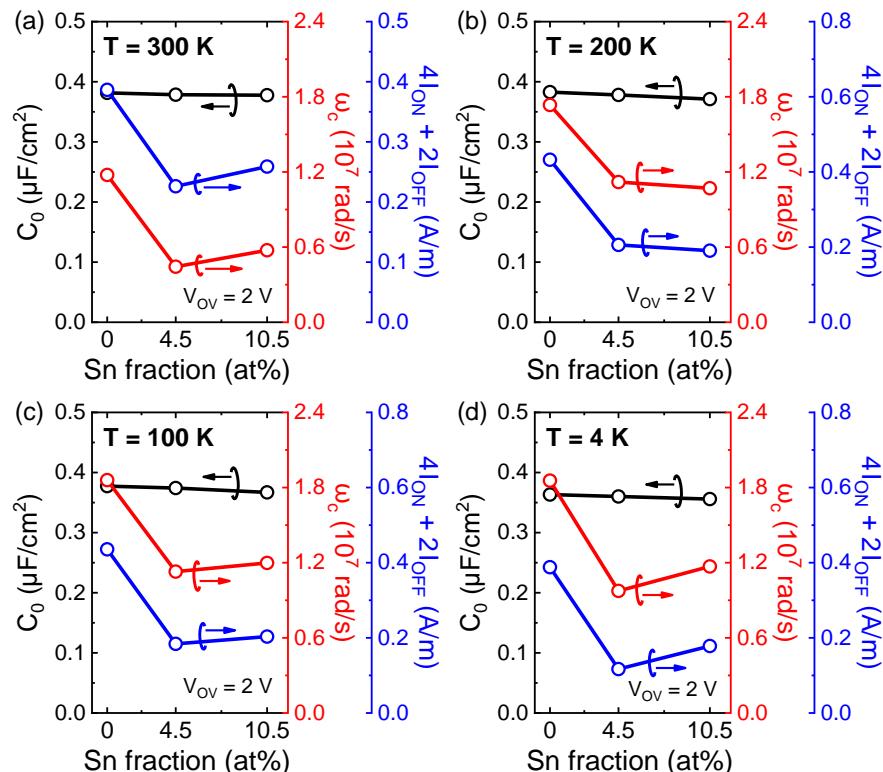

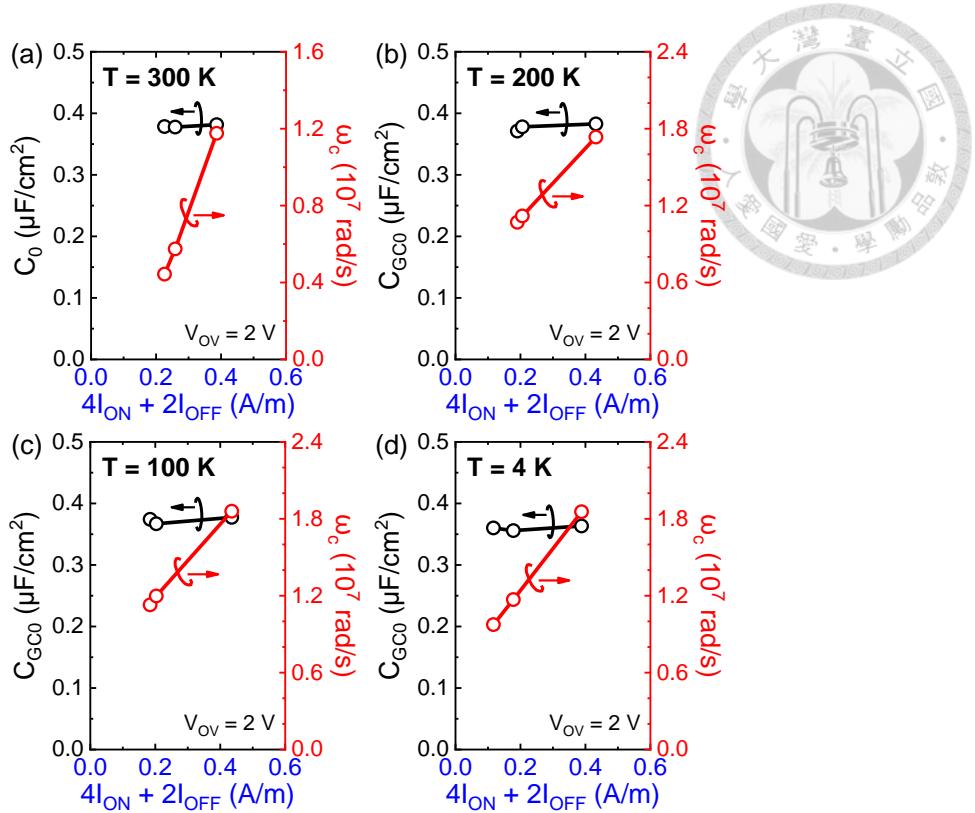

| Fig. 3-14 Fitting parameters $C_0$ and $\omega_c$ (used in Fig. 3-13) as well as $4I_{ON} + 2I_{OFF}$ (excerpted from Fig. 3-5 (a) and (c)) vs. Sn fraction at (a) 300 K, (b) 200 K,                                                                                                                                     |    |

(c) 100 K, and (d) 4 K. (b)  $C_0$  and  $\omega_c$  (from (a)) vs.  $4I_{ON} + 2I_{OFF}$  (from (a)).

76

Fig. 3-15 Fitting parameters  $C_0$  and  $\omega_c$  (used in Fig. 3-13) as well as  $4I_{ON} + 2I_{OFF}$  (excerpted from Fig. 3-5 (a) and (c)) vs. Sn fraction at (a) 300 K, (b) 200 K, (c) 100 K, and (d) 4 K. (b)  $C_0$  and  $\omega_c$  (from (a)) vs.  $4I_{ON} + 2I_{OFF}$  (from (a)).

77

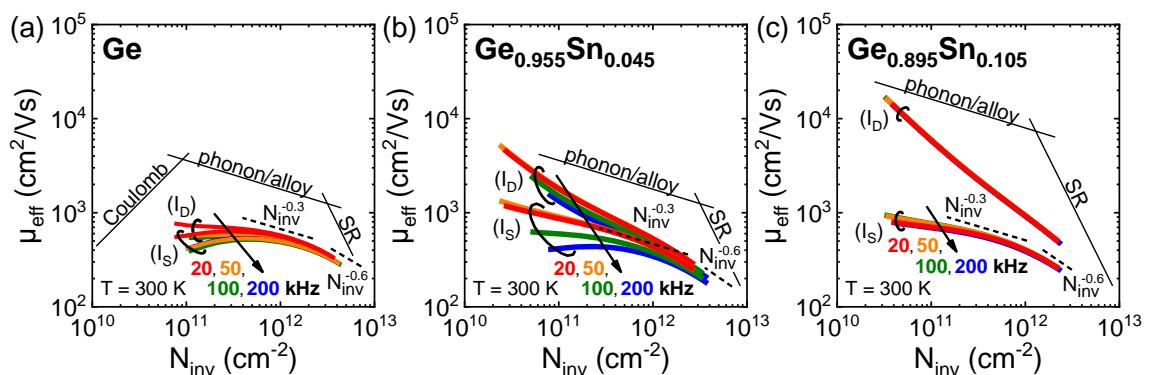

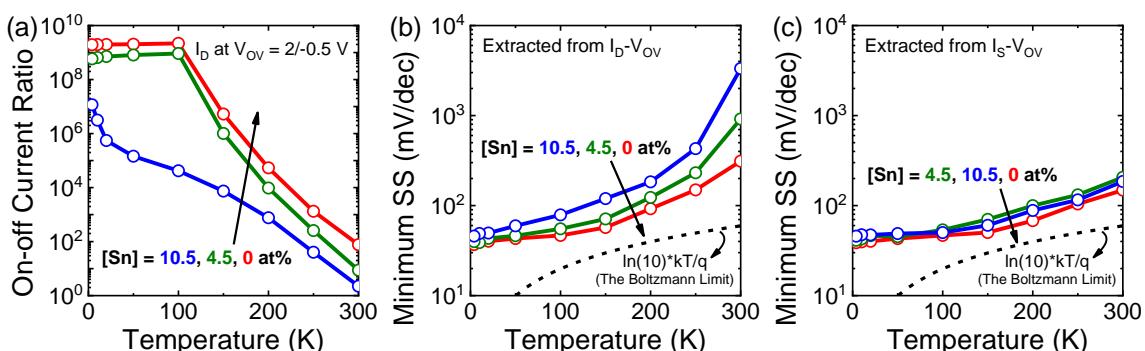

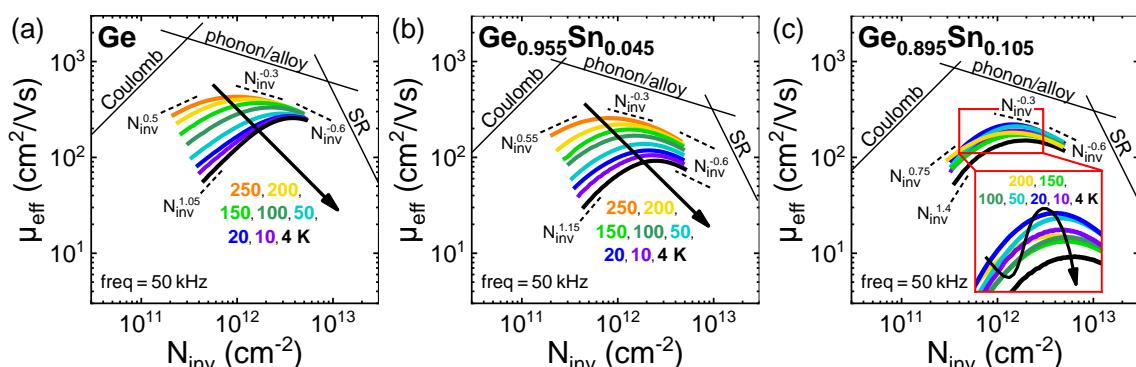

Fig. 3-16 Effective mobility ( $\mu_{eff}$ ) vs. inversion carrier density ( $N_{inv}$ ) of the (a) Ge, (c)  $Ge_{0.955}Sn_{0.045}$ , and (e)  $Ge_{0.895}Sn_{0.105}$  n-MOSFETs (extracted from  $I_D$  (Fig. 3-4) and  $C_{GC}$  at 50 kHz (Fig. 3-7)).....79

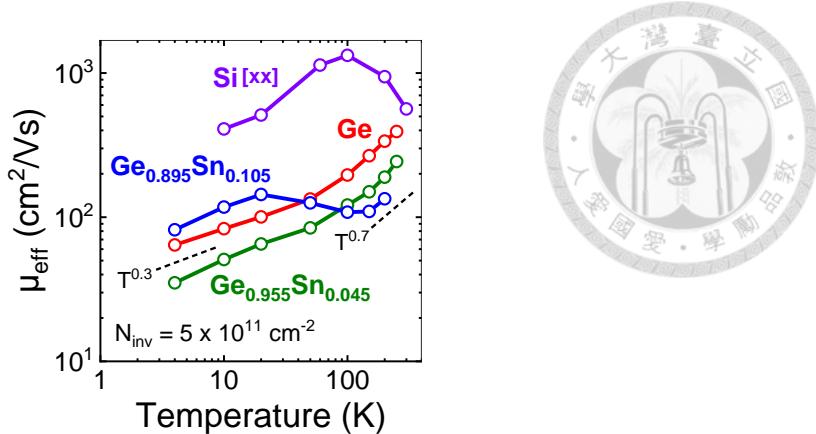

Fig. 3-17  $\mu_{eff}$  vs. temperature of the Si [31] and Ge(Sn) n-MOSFETs (extracted from Fig. 3-16) in the low-density regime ( $N_{inv} = 5 \times 10^{11} \text{ cm}^{-2}$ ).....81

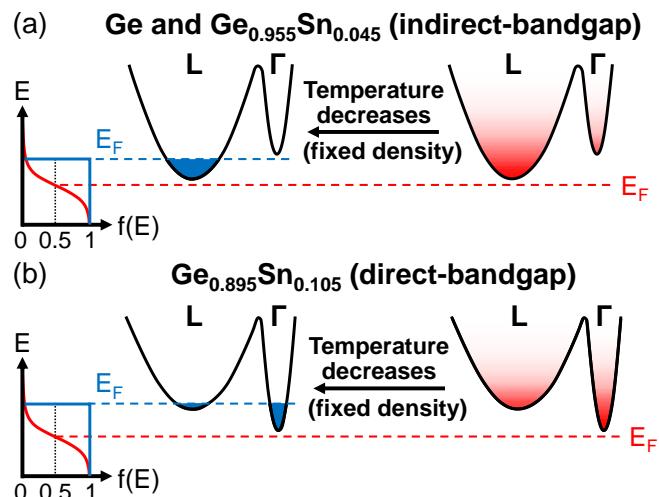

Fig. 3-18 The variation of electron population in the  $\Gamma$ - and L-valley with temperature in (a) indirect-bandgap and (b) direct-bandgap Ge(Sn) alloys under a fixed electron density [12].....82

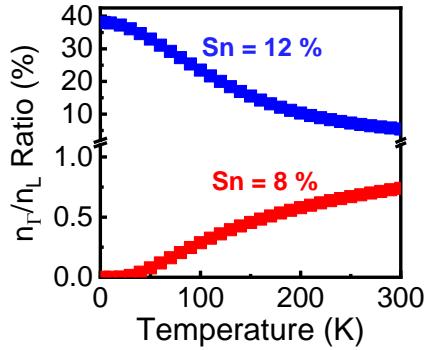

Fig. 3-19 Calculated electron population ratio in the  $\Gamma$ -valley relative to that in the L-valley ( $n_\Gamma/n_L$ ) of the strain-relaxed n- $Ge_{0.92}Sn_{0.08}$  and n- $Ge_{0.88}Sn_{0.12}$  films [9].

.....84

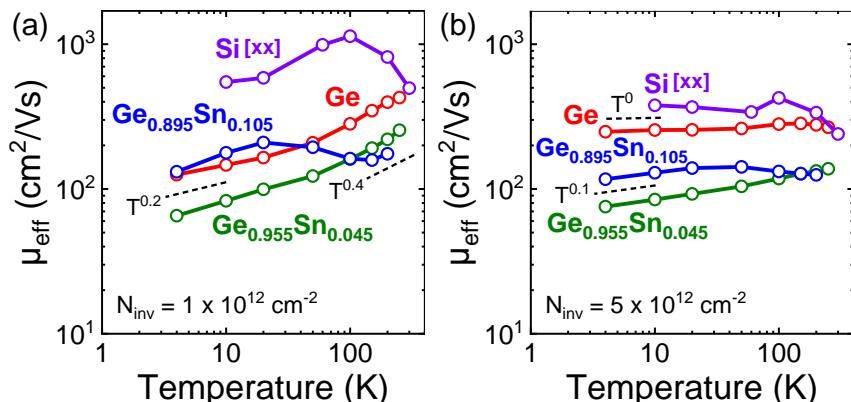

Fig. 3-20  $\mu_{eff}$  vs. temperature of the Si [31] and Ge(Sn) n-MOSFETs (extracted from Fig. 3-16) in the (a) intermediate-density ( $N_{inv} = 1 \times 10^{12} \text{ cm}^{-2}$ ) and (b) high-density regimes ( $N_{inv} = 5 \times 10^{12} \text{ cm}^{-2}$ ).....84

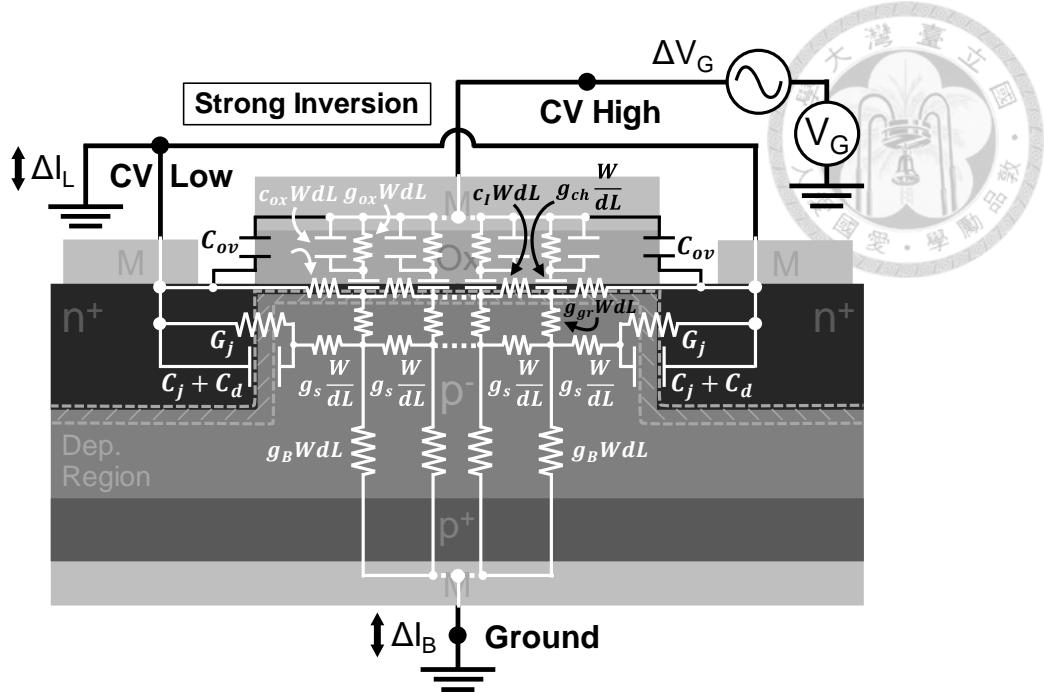

Fig. A-1 The distributed small-signal circuit model of the Ge(Sn) n-MOSFETs biased in the accumulation regime ( $V_{ov} = -2 \text{ V}$ ) during split C-V measurement....103

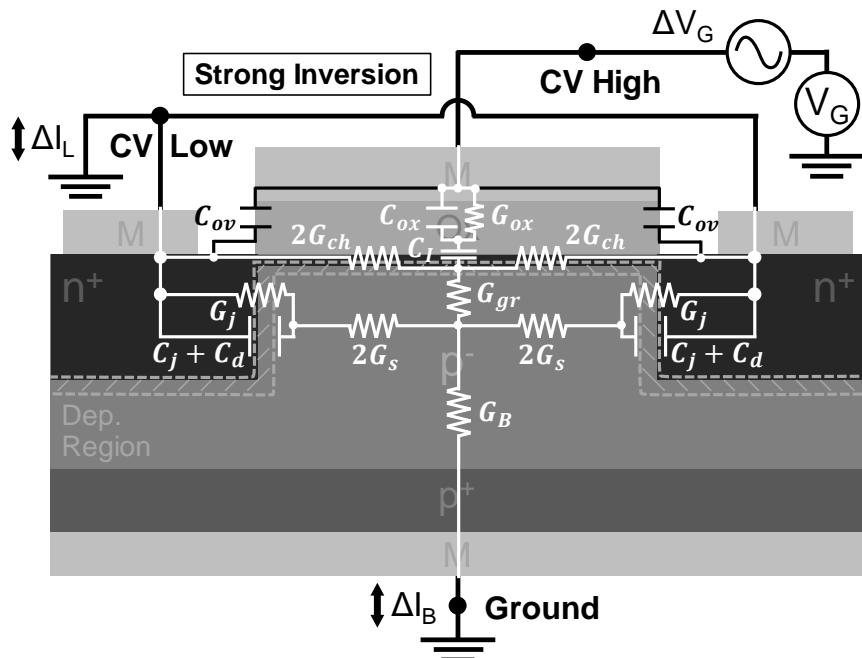

Fig. A-2 The lumped small-signal circuit model derived from Fig. A-1.....104

Fig. A-3 The (a) complete and (b) simplified equivalent small-signal circuit model derived from Fig. A-2.....105

|                                                                                                                                                                                                                                                                                                                                                 |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. A-4 The distributed small-signal circuit model of the Ge(Sn) n-MOSFETs biased in the depletion regime ( $V_{ov} \sim -0.5$ V) during split C-V measurement.....                                                                                                                                                                            | 108 |

| Fig. A-5 The lumped small-signal circuit model derived from Fig. A-4.....                                                                                                                                                                                                                                                                       | 109 |

| Fig. A-6 The (a) complete and (b) simplified equivalent small-signal circuit model derived from Fig. A-5.....                                                                                                                                                                                                                                   | 109 |

| Fig. A-7 The distributed small-signal circuit model of the Ge(Sn) n-MOSFETs biased in the strong inversion regime ( $V_{ov} = 2$ V) during split C-V measurement. .                                                                                                                                                                             | 111 |

| Fig. A-8 The lumped small-signal circuit model derived from Fig. A-7.....                                                                                                                                                                                                                                                                       | 111 |

| Fig. A-9 The (a) complete and (b) simplified equivalent small-signal circuit model derived from Fig. A-8.....                                                                                                                                                                                                                                   | 112 |

| Fig. B-1 A schematic showing the relationships between the total mobility and different mobility branches corresponding to various scattering mechanisms [100].                                                                                                                                                                                 | 116 |

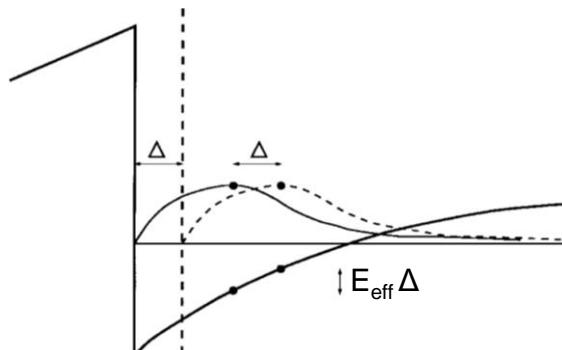

| Fig. B-2 A schematic showing the effect of the change in surface position ( $\Delta$ ) on the electron wavefunction, where the potential energy at the centroid is varied by $E_{eff}\Delta$ [101]......                                                                                                                                        | 117 |

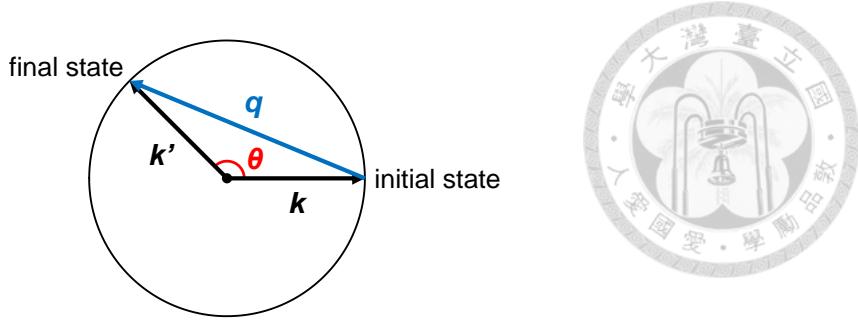

| Fig. B-3 A schematic showing the geometrical relationships between the wavevector before scattering ( $\mathbf{k}$ ) and after scattering ( $\mathbf{k}' = \mathbf{k} + \mathbf{q}$ ). The magnitude of $\mathbf{k}$ and $\mathbf{k}'$ are identical since Coulomb scattering is an elastic (energy-conserving) scattering process [102]. ..... | 122 |

| Fig. B-4 A schematic showing the geometrical relationships between the charged impurity ( $e^+$ ) and 2DEG. .....                                                                                                                                                                                                                               | 123 |

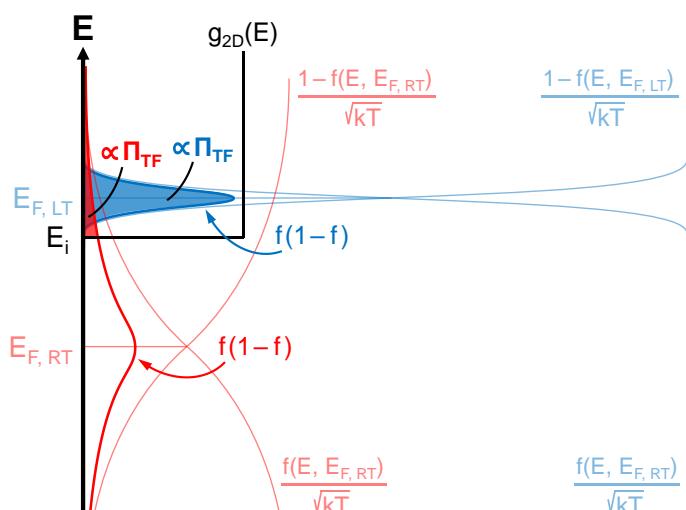

| Fig. B-5 A schematic showing the relationship between the polarizability $\Pi_{TF}$ and the joint Fermi-Dirac distribution $f(E, E_F)[(1 - f(E, E_F))]/kT$ at a fixed electron density at room temperature and low temperature. .....                                                                                                           | 124 |

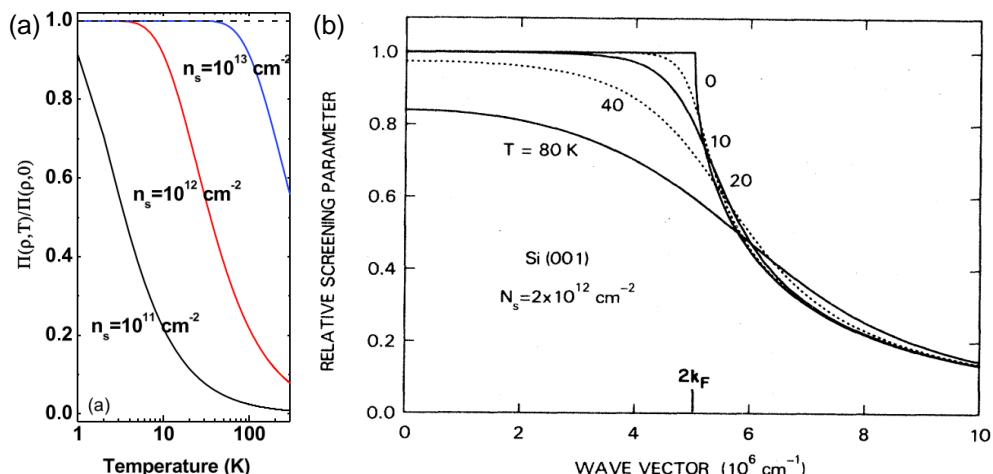

Fig. B-6 Relative screening parameter (polarizability  $\Pi_{TF}$ ) vs. (a) temperature at various 2DEG densities [88] and (b) the scattering wavevector  $|\mathbf{q}|$  at various temperatures [106].....125

## LIST OF TABLES

Table 2-1  $G_0$  and  $\omega_c$  of Equation (2-13).  $\alpha$  is defined as  $[1 + (G_B + 2G_J)/G_{gr}]^{-1}$  ..... 52

Table B-1 The power of density ( $\alpha$ ) and temperature ( $\gamma$ ) dependence of 2DEG mobility

$\mu_{n,2D}$  ..... 116

# Chapter 1 Introduction

## 1.1 Motivation

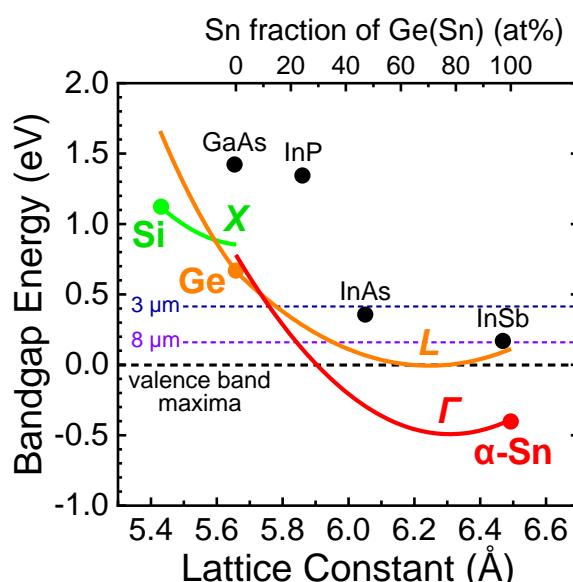

Germanium-tin (GeSn) alloys hold great promise for optical and electrical device applications owing to their direct-bandgap characteristics [2] and small carrier effective masses [3]. In addition, the compatibility with Si VLSI technologies makes GeSn alloys a competitive platform for the monolithic integration of optoelectronics and nanoelectronics, offering a cost-effective alternative to III-V compound semiconductors [4]. Among the group-IV semiconductors, bandgap transitions between indirect valleys (X and L) as well as between indirect and direct valleys (L and  $\Gamma$ ) have been predicted in the SiGe and GeSn alloy systems, respectively [1] (Fig. 1-1). When the Sn fraction exceeds 10 at%, GeSn undergoes an indirect-to-direct bandgap transition [1]. Due to their small bandgap energy, direct-bandgap GeSn alloys span the mid-wave infrared (3 – 8  $\mu\text{m}$ ) and far-wave infrared (8 – 14  $\mu\text{m}$ ) spectrums [1]. The combination of both properties enable high-performance infrared photonic applications, such as GeSn-based lasers [2] and

Fig. 1-1 Bandgap energy vs. lattice constant of the SiGe and GeSn alloy systems as well as direct-bandgap III-V compound semiconductors [1].

photodetectors [5].

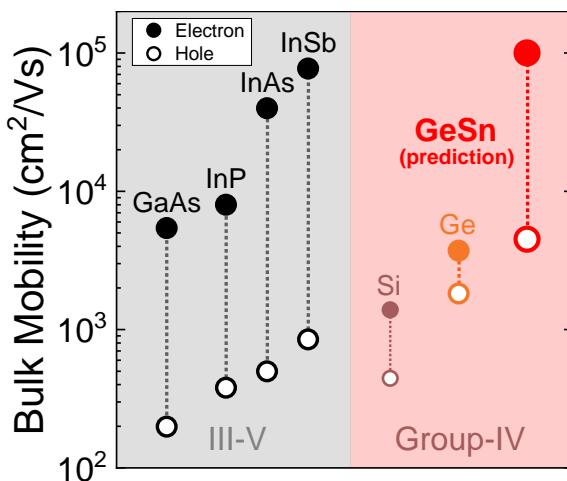

GeSn alloys also exhibit high carrier mobility. Traditionally, III-V compound semiconductors offer significantly higher electron mobility ( $\sim 70,000 \text{ cm}^2/\text{Vs}$  [6]) compared to that of Si and Ge ( $\sim 1,400$  and  $3,900 \text{ cm}^2/\text{Vs}$ , respectively [6]) (Fig. 1-2). However, the hole mobility in III-V materials is merely comparable to that in Si and significantly lower than that in Ge. Therefore, a heterogeneous group III-V/Ge complementary metal-oxide-semiconductor (CMOS) was proposed as a new transistor architecture to leverage their respective carrier mobility advantages [6]. Nevertheless, the integration of III-V materials with Ge remains a challenge, and GeSn alloys emerge as one of the alternative material platforms that offers a monolithic solution [4]. By incorporating Sn atoms into Ge, the hole mobility is greatly enhanced ( $\sim 4,500 \text{ cm}^2/\text{Vs}$ ) [7]. On the other hand, in direct-bandgap GeSn, electron mobility comparable to that of III-V materials ( $\sim 100,000 \text{ cm}^2/\text{Vs}$  [8]) have been predicted thanks to a large electron population in the  $\Gamma$ -valley, where the electron effective mass is very small [9]. The superior carrier mobilities and direct-bandgap characteristics in GeSn enable high-performance GeSn-based electronic devices, such as metal-oxide-semiconductor field-effect transistors (MOSFETs) [10, 11], tunneling diodes [12], and tunneling FETs (TFETs) [13, 14].

Fig. 1-2 Bulk mobility of electron and hole in group-IV and III-V compound semiconductors [6].

Despite extensive works of direct-bandgap GeSn in optoelectronic and electronic applications, the indirect-to-direct bandgap transition in GeSn is not yet fully understood. Previous experimental investigations have primarily focused on optical aspects [2, 15, 16], with very few electrical studies reported [9]. Therefore, in this work, the transport properties in Ge(Sn) n-type metal-oxide-semiconductor field-effect transistors (n-MOSFETs) were investigated. The temperature dependence of mobility changes substantially as the Sn fraction increases up to 10.5 at%, which is attributed to enhanced  $\Gamma$ -valley electron transport resulting from an indirect-to-direct bandgap transition in GeSn.

## 1.2 Tunable Band Structure of GeSn

By incorporating Sn atoms into Ge crystals, the bandgap energies of both the indirect valleys (e.g., X and L) and the direct valley (e.g.,  $\Gamma$ ) in GeSn decrease due to the increased lattice constant [7]. In addition to the reduction in bandgap energy, the strong spin-orbit coupling in Sn atoms raises the energy of the entire conduction band except for that at the  $\Gamma$ -point [7]. The combined effect of Sn incorporation is a more pronounced reduction in the bandgap energy of the direct  $\Gamma$ -valley compared to the other indirect valleys. There-

Fig. 1-3 Simulated band structures of strain-relaxed GeSn alloys with Sn fractions of (a) 5%, (b) 11%, and (c) 17% [17].

fore, by increasing the Sn fraction, an indirect-to-direct bandgap transition in GeSn can be achieved (Fig. 1-3). Another way to achieve the indirect-to-direct bandgap transition in GeSn is to apply in-plane biaxial strain. As the tensile (positive) strain increases, the energy of the conduction band edge at the  $\Gamma$ -point ( $\Gamma_{7,c}$ ) decreases faster than that at the L-point ( $L_{6,c}$ ), thereby resulting in a less energetic  $\Gamma$ -valley compared to the L-valley [18] (Fig. 1-4). The effect of Sn incorporation and strain on the “directness” of GeSn alloys are summarized in the contour maps showing the energy separation between the two valleys, where an indirect-to-direct transition in unstrained GeSn alloys occurs at a Sn frac-

Fig. 1-4 Relative energy shifts of the band edges at various symmetry points of  $\text{Ge}_{0.90}\text{Sn}_{0.10}$  vs. in-plane biaxial strain along the (001) plane [18].

Fig. 1-5 Contour maps of calculated energy separation between the L- and  $\Gamma$ -valley vs. Sn fraction and in-plane biaxial strain along the (001) plane reported in (a) [18] and (b) [19].

tion of around 6 – 7 at% (Fig. 1-5).

The transition of GeSn alloys from an indirect-bandgap to a direct-bandgap material is clearly observed in the temperature-dependent photoluminescence (PL) spectra (Fig. 1-6). At room temperature, the PL spectrum of  $\text{Ge}_{0.96}\text{Sn}_{0.04}$  exhibits only one peak, which is attributed to stronger radiative recombination from the direct  $\Gamma$ -valley compared to the indirect L-valley [15] (Fig. 1-6 (a)). As the temperature decreases, the single peak splits into two distinct peaks. This is attributed to the indirect bandgap nature of  $\text{Ge}_{0.96}\text{Sn}_{0.04}$ , which suppresses the thermal excitation of electrons to the direct  $\Gamma$ -valley at low temperatures and enhances radiative recombination from the indirect L-valley [20]. However, as the Sn fraction increases to 8 at% or 10 at%, only one peak is observed in the PL spectra, irrespective of temperature (Fig. 1-6 (b) and (c)). This is attributed to the indirect-to-direct

Fig. 1-6 Temperature dependent photoluminescence (PL) spectra of the GeSn alloys with Sn fractions of (a)-(c) 4 – 10 at% [15] and (d) 8.0% – 12.6% [2]. The insets in (d) show zoomed portions of the spectra.

bandgap transition in GeSn, bringing the energy of the  $\Gamma$ -valley closer to or lower than that of the L-valley [15]. As a result, radiative recombination is dominated by that from the direct  $\Gamma$ -valley at all temperatures.

The indirect-to-direct bandgap transition in GeSn is also observed from the temperature-dependent PL intensity (Fig. 1-6 (d)). As the temperature decreases, the PL intensity of  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  decreases monotonically, implying that  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  is an indirect-bandgap material. This is because at low temperatures, electrons in  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  condense to the L-valley, where radiative recombination is significantly less efficient in comparison to that in the direct  $\Gamma$ -valley [2]. With Sn fractions of 9.6 at% and above, the PL intensity increases as the temperature decreases, and this enhancement becomes more pronounced with increasing Sn content. This is attributed to the indirect-to-direct transition in GeSn alloys, which brings the energy of the direct  $\Gamma$ -valley closer to or lower than that of the L-valley and results in an increased electron population in the  $\Gamma$ -valley, where radiative recombination is significantly more efficient than that in the indirect L-valley [2].

By applying in-plane biaxial compressive strain to GeSn alloys, the hole mobility is enhanced (Fig. 1-7 (a)). This is because the compressive strain breaks the symmetry of the group-IV diamond structure, thereby lifting the degeneracy of the heavy-hole (HH) and light-hole (LH) bands and splitting them into higher valence (HV) and lower valence (LV) bands [18]. As a result, more holes occupy the HV band, which is deformed and has a much-reduced effective mass compared to the degenerate HH band (Fig. 1-7 (b)). Furthermore, interband scattering is reduced due to the lifting of the  $\Gamma$ -point degeneracy, which further contributes to the enhancement of hole mobility in compressively strained GeSn [7]. In contrast, by increasing the Sn fraction and/or applying in-plane biaxial tensile strain to GeSn alloys, the electron mobility is enhanced (Fig. 1-8 (a)). This is because both Sn alloying and tensile strain increase the cell volume, which results in a faster

Fig. 1-7 (a) Schematics of the band structure showing the hole mobility enhancement in GeSn alloys. (b) Simulated hole effective masses of the higher valence ( $m^*_{h,HV}$ ) and lower valence ( $m^*_{h,LV}$ ) bands of Ge<sub>0.9</sub>Sn<sub>0.1</sub> vs. in-plane biaxial strain along [100] direction [18].

reduction in the direct  $\Gamma$ -gap compared to the indirect L-gap [7]. As a result, more electrons occupy the  $\Gamma$ -valley, where the effective mass is much smaller than that of the L-valley (Fig. 1-8 (b)). Besides, the conductivity effective masses in both the L-valley and  $\Gamma$ -valley decrease with increasing Sn fraction, which might possibly lead to the enhancement of electron mobility in GeSn alloys with high Sn contents [17] (Fig. 1-8 (b)).

Fig. 1-8 (a) Schematics of the band structure showing the electron mobility enhancement in GeSn alloys. (b) Simulated conductivity effective masses of electron in the L-valley ( $m^*_{elL}$ ) and  $\Gamma$ -valley ( $m^*_{e\Gamma}$ ) of strain-relaxed Ge<sub>1-x</sub>Sn<sub>x</sub> alloys vs. Sn content x [17].

The variation of electron mobility with the Sn fraction and tensile strain has been investigated in GeSn n-MOSFETs. Unexpectedly, the electron effective mobility does not increase as the Sn fraction increases from 6 at% to 8.5 at% (Fig. 1-9 (a)). This could be attributed to an enhanced alloy scattering with increasing Sn fraction [21]. By contrast, a significant enhancement in electron mobility is achieved by applying tensile strain while keeping the Sn fraction constant (Fig. 1-9 (b)). This is because the tensile strain increases the electron population in the  $\Gamma$ -valley, while the fixed Sn content ensures a constant alloy scattering intensity [11].

To investigate the effect of indirect-to-direct bandgap transition on the electrical transport properties in GeSn, a temperature-dependent mobility characterization is required. This is because the room-temperature data in Fig. 1-9 (b) only indicate that the  $\Gamma$ -valley lies lower in tensile-strained GeSn compared to compressively strained GeSn, but

Fig. 1-9 Electron effective mobility ( $\mu_{\text{eff}}$ ) vs. inversion carrier density ( $N_{\text{inv}}$ ) of GeSn n-MOSFETs (a) with different Sn fractions (compressive-strained) [21] and (b) different strain conditions ( $[\text{Sn}] = 4\%$ ) [11]. (c) Schematics of band structures of compressive and tensile-strained GeSn in (b). (d) Schematics of electron population in the L- and  $\Gamma$ -valleys of indirect-bandgap and direct-bandgap GeSn at 300 K and 4 K [12].

do not confirm a transition to a direct bandgap GeSn (Fig. 1-9 (c)). Thanks to the suppressed Fermi-tail at low temperatures, electrons condense to different valleys depending on the indirect-bandgap or direct-bandgap nature of GeSn (Fig. 1-9 (d)). Due to the big difference in the electron effective masses between the  $\Gamma$ -valley and L-valley (Fig. 1-8 (b)), a distinct characteristic in the temperature-dependent of the effective mobility is expected when an indirect-to-direct bandgap transition in GeSn occurs. These will be explored in this work.

### 1.3 Thesis Outline

In this thesis, transport properties in GeSn n-MOSFET with a Sn fraction up to 10.5 at% are investigated from 300 K to 4 K. In Chapter 2, GeSn epitaxial growth, n-MOSFET fabrication, and the measurement methodology are introduced. Then, room-temperature device characteristics are investigated. Equivalent small-signal circuit models are proposed to explain the anomalous I-V and C-V results due to high off-state leakages. In Chapter 3, cryogenic device characteristics are investigated. Then, electron mobility and density are extracted using the split C-V method. As the Sn fraction increases, a drastic change in the temperature-dependence of mobility is observed. This is explained by the *dual-valley electron transport* and is attributed to the effect of indirect-to-direct bandgap transition in GeSn. Finally, the conclusions and future works of this thesis are given in Chapter 4.

# Chapter 2 Fabrication and Characterization of Ge(Sn) n-MOSFETs

GeSn alloys are promising for electronic applications due to their small carrier effective masses [3]. When compressive strain is applied on GeSn, the valence band is deformed, which reduces the effective mass of the heavy-hole band [18]. Furthermore, the compressive strain lifts the degeneracy at the  $\Gamma$ -point, which increases hole occupancy in the deformed heavy-hole band and further enhances hole mobility [18]. On the other hand, when tensile strain is applied on GeSn or the Sn fraction is increased, the  $\Gamma$ -valley is lowered relative to the L-valley [19]. This increases the electron population in the  $\Gamma$ -valley and enhances electron mobility, because the effective mass in the  $\Gamma$ -valley is much smaller than that in the L-valley [9]. The high carrier mobilities enable high-performance GeSn-based CMOS applications, making it a promising candidate for next-generation channel materials for transistors [4].

## 2.1 Introduction

Ge(Sn) n-type metal-oxide-semiconductor field-effect transistors (n-MOSFETs) with various architectures, such as planar [22], mesa [11], tri-gate (FinFET) [23], and gate-all-around (GAAFET) [24], have been reported. Ge(Sn) n-FinFETs and n-GAAFETs excel in device performance due to their excellent capability for gate control [23, 24], making them ideal candidates to further extend Moore's Law. To investigate electron transport in Ge(Sn) n-MOSFETs, it is necessary to characterize the dependence of electron mobility on electron density, which is commonly practiced using a split C-V method [25]. This method, however, cannot be applied to the FinFET or GAAFET since the gate capacitance is too small for a C-V meter to detect reliably. Ge(Sn) planar and mesa n-

MOSFETs are preferred for the split C-V method due to their large gate-to-channel areas [11, 22], with examples of successful mobility extraction summarized below.

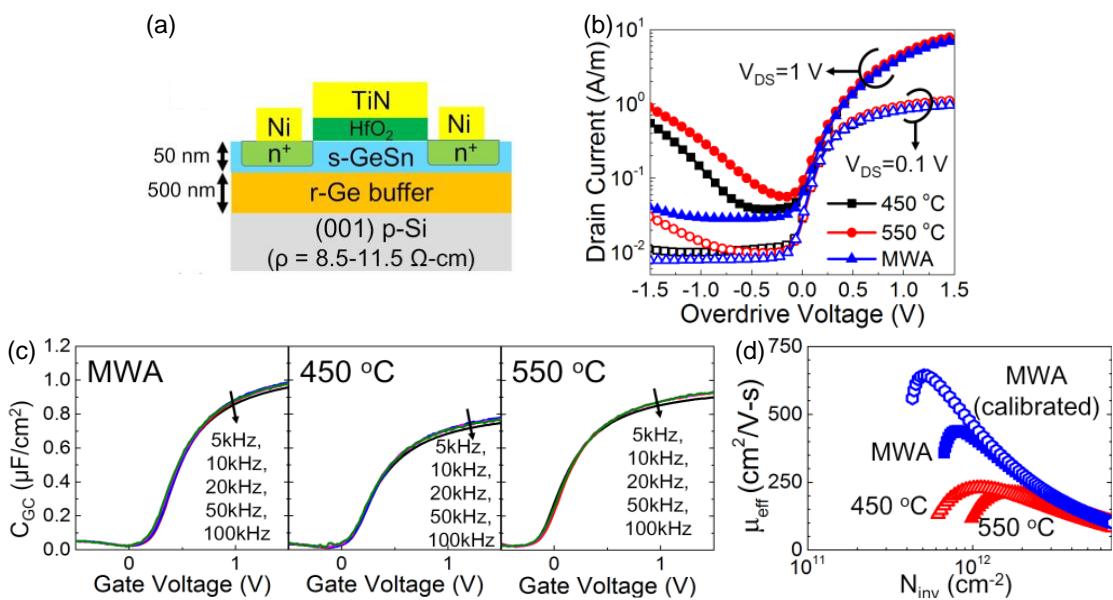

### 2.1.1 Planar GeSn n-MOSFETs

Prior to the deposition of GeSn layers, a Ge epitaxial layer is grown on a Si substrate and subjected to in-situ hydrogen annealing to form a strain-relaxed, defect-free virtual substrate [26, 27]. This facilitates the subsequent growth of a fully strained GeSn active layer and preserves the film quality by reducing the defect formation associated with strain relaxation [28]. The device structure is shown in Fig. 2-1 (a). In transfer I-V curves, clear transistor characteristics with an on-off current ratio ( $I_{ON}/I_{OFF}$ ) of approximately  $10^2$  is observed (Fig. 2-1 (b)). In the microwave-annealed (MWA) device, the off-state current ( $I_{OFF}$ ) is lower and the gate-induced drain leakage is less pronounced than in the rapid thermal annealed (RTA) devices (Fig. 2-1 (b)) thanks to the much suppressed dopant diffusion during the MWA process [22]. In addition, the on-state gate-to-channel capacitance

Fig. 2-1 (a) Device structure, (b) transfer I-V characteristics, (c) normalized gate-to-channel capacitance ( $C_{GC}$ ) vs. gate voltage, and (d) effective mobility ( $\mu_{eff}$ ) vs. inversion carrier density ( $N_{inv}$ ) of the planar Ge<sub>0.955</sub>Sn<sub>0.045</sub> n-MOSFET [22].

( $C_{GC}$  at gate voltage = 1.5 V) is higher for the MWA device (Fig. 2-1 (c)), indicating that the quality of gate stack and oxide/semiconductor interface are better preserved by MWA [22], as evidenced by the higher effective mobility ( $\mu_{eff}$ ) of the MWA device (Fig. 2-1 (d)).

These results show that MWA is a better dopant activation method compared to RTA for GeSn n-MOSFETs. It's worth noting that the electron transport occurs exclusively within the  $Ge_{0.955}Sn_{0.045}$  layer, because the inversion channel only spans a few nanometers near the surface (Fig. 2-1 (a)) [29, 30]. Consequently, the  $\mu_{eff}$  reflects only the transport properties in  $Ge_{0.955}Sn_{0.045}$  channel, which is very different from the cases discussed below.

### 2.1.2 Mesa GeSn n-MOSFETs

Mesa GeSn n-MOSFETs are identical to the planar devices (Fig. 2-1 (a)), except that the source and drain are “recessed”, i.e., formed in a wider-bandgap layer (Ge) beneath the channel ( $Ge_{0.96}Sn_{0.04}$ ) (Fig. 2-2 (a)), to reduce off-state current ( $I_{OFF}$ ) [11]. In transfer I-V characteristics, an on-off current ratio ( $I_{ON}/I_{OFF}$ ) of approximately 200 is observed for the mesa structure, which is larger than those for the planar structures ( $\sim 10$  for Si substrates and  $\sim 5$  for SOI substrates) (Fig. 2-2 (b)). Given that the on-state current ( $I_{ON}$ , drain current at gate voltage = 3 V) is similar for both structures (Fig. 2-2 (b)), the higher  $I_{ON}/I_{OFF}$  is attributed to a lower  $I_{OFF}$  in the mesa structure thanks to its “recessed” source and drain (formed on a wider-bandgap Ge layer) [11]. The  $I_{OFF}$  is higher in the planar structures because their junctions are formed on a narrower-bandgap  $Ge_{0.96}Sn_{0.04}$  layer [11]. These results show that the mesa structure is excellent for suppressing  $I_{OFF}$  while taking advantage of the high channel mobility in the  $Ge_{0.96}Sn_{0.04}$  layer.

As the mesa length ( $L_M$ ) increases, the effective mobility increases accordingly (Fig. 2-2 (c)). This is attributed to an increasing contribution from the high-mobility, tensile-strained  $Ge_{0.96}Sn_{0.04}$  layer, because the total mobility ( $\mu_{eff}$ ) is consisted of contributions

Fig. 2-2 (a) Device structure of the mesa GeSn n-MOSFETs [11]. (b) Transfer I-V characteristics of the planar (on Si and SOI substrates) and mesa  $\text{Ge}_{0.96}\text{Sn}_{0.04}$  n-MOSFETs [11]. (c) Effective mobility ( $\mu_{\text{eff}}$ ) vs. inversion carrier density ( $N_{\text{inv}}$ ) of the tensile-strained  $\text{Ge}_{0.96}\text{Sn}_{0.04}$  n-MOSFETs with various mesa lengths ( $L_M$ ) [11]. (d)  $\mu_{\text{eff}}$  vs.  $L_M$  of the Ge n-MOSFETs and tensile-strained  $\text{Ge}_{0.96}\text{Sn}_{0.04}$  n-MOSFETs [11].

from both the recessed source and drain regions ( $\mu_{\text{Ge}}$ ) and the mesa region ( $\mu_{\text{GeSn}}$ ) (Fig. 2-2 (a)) [11], as evidenced by the well-fitted curves to the data extracted from Fig. 2-2 (c) (Fig. 2-2 (d)). Consequently, the effective mobility does not reflect the “pure” electron transport in the  $\text{Ge}_{0.96}\text{Sn}_{0.04}$  layer. Instead, it reflects a combination of transport in both the “recessed” Ge channel and the  $\text{Ge}_{0.96}\text{Sn}_{0.04}$  channel. The “pure” electron mobility in the  $\text{Ge}_{0.96}\text{Sn}_{0.04}$  channel can only be approximated by either making  $L_M$  much larger than the spacer length ( $L_S$ ) or extracting the parameter  $\mu_{\text{GeSn}}$  from the equation in Fig. 2-2 (d) via parametric fitting [11]. As a result, the planar structure is preferred over the mesa structure for extracting the “pure” GeSn mobility.

### 2.1.3 Surface-Capped GeSn n-MOSFETs

Surface-capped GeSn n-MOSFETs are identical to the planar ones (Fig. 2-1 (a)),

except that the GeSn channel is capped with Ge (Fig. 2-3 (a)) [21]. Lower interface trap density ( $D_{it}$ ) is observed for samples capped with a thicker Ge layer (Fig. 2-3 (b)), which translates into a steeper subthreshold-swing (SS) (Fig. 2-3 (c)) and a higher effective mobility ( $\mu_{eff}$ ) (Fig. 2-3 (d)) due to a lower interface trap capacitance [31] and fewer Coulomb scatterers at the oxide/semiconductor interface [10, 32, 33], respectively. These results indicate that the surface-capped structure is excellent for improving SS and  $\mu_{eff}$ . Nevertheless, it's worth noting that a significant portion of electron transport occurs in the Ge capping layer, even if it is as thin as 2 nm. This is because the conduction band offset between Ge and GeSn (either with a Sn fraction of 6 at% or 8.5 at%) is negligible compared to the thermal energy at room temperature ( $\sim 25$  meV) [34], and the electron distribution in the inversion channel only spans a few nanometers near the surface [29, 30]. Consequently, the  $\mu_{eff}$  does not reflect the “pure” electron transport in the  $Ge_{0.94}Sn_{0.06}$  or

Fig. 2-3 (a) Epitaxial structure, (b) interface trap density ( $D_{it}$ ) vs. energy ( $E-E_V$ ), (c) subthreshold swing, and (d)  $\mu_{eff}$  vs.  $N_{inv}$  of the planar  $Ge_{0.94}Sn_{0.06}$  and  $Ge_{0.915}Sn_{0.085}$  n-MOSFETs with or without a Ge cap [21].

$\text{Ge}_{0.915}\text{Sn}_{0.085}$  layer. Instead, it reflects a combination of transport in both the Ge layer and the GeSn layer. Since it is difficult to eliminate the contribution of the Ge layer to the  $\mu_{\text{eff}}$ , the planar structure is preferred over the surface-capped structure for extracting the “pure” GeSn mobility.

## 2.2 Experiment

### 2.2.1 Material Growth and Analysis