國立臺灣大學電資學院電子工程研究所

碩士論文

Graduate Institute of Electronics Engineering

College of Electrical Engineering and Computer Science

National Taiwan University

Master Thesis

微縮閘極線寬之 SiC 基板 HEMT 的電性研究

與三層光阻法開發 T 型閘極

Investigation of Electrical Characteristics in Scaled-

Gate-Length HEMTs on SiC Substrates and

Development of a Three-Layer Photoresist Technique for

T-Gate Fabrication

蔡駿杰

Chun-Chieh Tsai

指導教授：管傑雄 博士、

林致廷 博士、蘇文生 博士

Advisor : Chieh-Hsiung Kuan, Ph.D. 、

Chih-Ting Lin, Ph.D. 、 Vin-Cent Su, Ph.D.

中華民國 112 年 7 月

July 2023

# 口試委員審定書

國立臺灣大學碩士學位論文

口試委員會審定書

MASTER'S THESIS ACCEPTANCE CERTIFICATE

NATIONAL TAIWAN UNIVERSITY

微縮閘極線寬之 SiC 基板 HEMT 的電性研究

與三層光阻法開發 T 型閘極

Investigation of Electrical Characteristics in Scaled-Gate-Length HEMTs

on SiC Substrates and Development of a Three-Layer Photoresist

Technique for T-Gate Fabrication

本論文係蔡駿杰(R10943137)在國立臺灣大學電子工程學研究所完成

之碩士學位論文，於民國 112 年 7 月 21 日承下列考試委員審查通過及

口試及格，特此證明。

The undersigned, appointed by the Department / Institute of Electronics Engineering on 21/07/2023

have examined a Master's thesis entitled above presented by Chun-Chieh Tsai (R10943137)

candidate and hereby certify that it is worthy of acceptance.

口試委員 Oral examination committee:

(管傑雄) 林汲江 蘇文生

(指導教授 Advisor) (Advisor) (Advisor)

朱富強 江介宏 林建江

系主任/所長 Director: \_\_\_\_\_

## 致謝

時光飛逝，轉眼間已經到了碩班生活的最後一哩路，回首在台大的這兩年，真的經歷了很多事也學習成長許多，在完成研究的過程中遇到了很多問題，更是讓我覺得能完成此研究多不容易，真的非常感謝研究路上獲得的幫忙。

最要感謝的就是教授們，首先是我的指導老師管傑雄教授，管老師一直強調健康學習，常常叮囑我們在研究之餘一定要運動保持身體健康，甚至會演示氣功來教我們，而且管老師提供我們一個自由的學習環境，讓我們可以負擔不重的專心完成我們的研究，每周也都會請大家吃飯，來更了解實驗室同學們的近況，真的非常感謝管老師這兩年的諄諄教誨，老師說的話我會銘記在心，願老師在天之靈可以安息。再來要感謝的就是蘇文生教授，在指導眾多學生之餘，還要費心力來指導我們，關注我們的研究進度，並給予我們實驗上的建議，甚至在台大的機台陸續停機維修時，給予我跟嶧喆去 TSRI 做實驗的資源，才能完成這份研究，真的非常感謝蘇老師的教導與幫助。第三個要感謝的就是林致廷教授，在管老師逝世後，願意擔任我們的新指導教授及口試委員，真的很感謝林老師的幫忙，讓我們可以順利處理後續相關事宜。

感謝我的女友 Mina，在碩二下這半年真的壓力很大而且常常早出晚歸的做實驗，感謝你一路的陪伴與鼓勵，也願意聽我訴苦發牢騷，在我心情不好時會逗我開心，沒有你的陪伴我可能會常常處在低潮情緒，真的很感謝你的陪伴與支持，祝你未來一年也能順利完成自己的研究。

再來要感謝 HEMT 組的育誠學長及翰霆學長，非常感謝兩位學長在我碩一時的教導，讓我能熟悉機台及了解 HEMT 這個題目，尤其是育誠學長，常常跟著他做實驗到半夜，一起聊天玩遊戲，我非常懷念跟著學長一起做事的那段時光；也感謝宣翰學長教導我操作 Ebeam，及討論實驗的改良，祝你能趕快發表 paper 完成博士學業；還要感謝同屆的同學嶧喆，常一起吃飯討論實驗的問題，甚至一起去 TSRI 做實驗互相鼓勵，祝你未來也能順順利利；最後是三位碩一的學弟昱

尚、鈺祥與晨璋，感謝他們在實驗上的配合與幫忙，尤其是昱尚鈺祥這半年幫了我非常多，祝三位在新實驗室都能順利完成碩班學業。

再來感謝其他實驗室成員，特別感謝冠彬學長，這兩年幫了我許多忙及解惑很多問題，甚至常常給予鼓勵，讓我在低落時總能感到溫暖，實驗室很多事情也都勞煩他處理，真的非常感謝冠彬學長，辛苦了，祝你博士學業順利！感謝同屆的同學人豪、博鈞、書平、舒婷、宇岑，在大家都在辛苦的研究過程中，互相鼓勵加油打氣，都讓我能更加打起精神，各位都辛苦了，祝各位工作順利！也感謝學弟們穎宇、紹耘、寬程、鴻亦、達禎，一起打遊戲打球很開心，祝你們在新實驗室都能好好完成碩士學業。

感謝在 TSRI 做實驗時的幫忙，四位蘇老師的學生文昇、彥良、廷宇、博文及在 TSRI 當研究員的伯維學長還有岱穎學長，這份研究的完成真的非常感謝你們的幫忙，才可以順利將實驗完成，也很感謝伯維學長給的建議及解惑，真的獲益良多；在量測時也真的感謝岱穎學長的教學，讓我們可以順利量測。

感謝一些我的朋友們在研究過程中給予的幫助，謝謝品嘉讓我在新竹做實驗時借我機車及供我住宿；謝謝致成常來找我聊天吃飯玩遊戲，也會分享許多新奇的故事，還有借我微波工程的書籍學習；謝謝國倫教我如何量測高頻參數及解答微波工程的問題。謝謝你們的幫忙，祝大家都能鴻圖大展。

最後要感謝的就是我的家人們，提供我生活上的資源及精神上的鼓勵與支持，這半年由於做研究的關係鮮少回家，真的很抱歉沒能常伴你們，期許自己日後能好好報答你們，不讓你們失望。

總而言之，這份研究真的仰賴了許多人的幫忙，過程中遇到許多問題更能深切體會完成研究的艱辛，感謝一路上獲得的恩惠，感謝伴我成長的所有人事物。最後特別感謝台大土地公廟及交大土地公廟神明們的保佑，讓我能安心及順利完成研究，大恩大德沒齒難忘，我一定會好好的回報。

## 中文摘要

氮化鎵屬於第三代半導體，具備了寬能隙、高電子遷移率、高載子傳輸速度與高崩潰電場等特性，而以氮化鋁鎵/氮化鎵為材料的高電子遷移率電晶體，在氮化鋁鎵及氮化鎵接面處會有極化反應的產生，進而生成高濃度的二維電子氣(Two-dimensional electron gas, 2DEG)，使得此電晶體能在高頻及高功率元件中有良好的特性表現及發展空間。

本論文採用以碳化矽(SiC)基板為底搭配氮化鎵磊晶層而成之試片，研究微縮閘極線寬對高電子遷移率電晶體之影響，且將該製作之元件進行電性量測及分析。此外，本論文並於矽基板上利用三層光阻( ZEP(1:1)/LOR/ZEP(1:1) )之 T 型閘極技術與角標對準優化技術製作出小閘極線寬。利用角標對準優化技術，讓實驗之二次對準良率提高，再加上三層光阻( ZEP(1:1)/LOR/ZEP(1:1) )定義出 T 型的閘極，並使用電子束微影技術成功開發出閘極線寬(T 型閘極的, T-foot,)78.5 奈米的元件，最後利用簡化後的公式，進行高頻特性參數的估算及比較。

關鍵字：T 型閘極、碳化矽基板、電子束微影技術、高電子遷移率電晶體、高頻

# Abstract

Gallium nitride (GaN) belongs to the third generation of semiconductors, possessing characteristics such as a wide bandgap, high electron mobility, high carrier velocity, and high breakdown electric field. High electron mobility transistors (HEMTs) using AlGaN/GaN as the material exhibit polarization effects at the AlGaN/GaN interface, resulting in the generation of a high-density two-dimensional electron gas (2DEG). This enables the HEMTs to exhibit excellent performance and development potential in high-frequency and high-power devices.

This study utilizes silicon carbide (SiC) substrates with GaN epitaxial layers to investigate the effect of gate width reduction on HEMTs, and to perform electrical measurements and analyses on the fabricated devices. Additionally, this work employs a T-gate fabrication technique using three layers of resist (ZEP(1:1) / LOR / ZEP(1:1)) and an alignment optimization technique on silicon substrates to produce smaller gate widths. By utilizing the alignment optimization technique, the secondary alignment yield of the experiment is improved. Moreover, a T-shaped gate was defined using a three-layer photoresist (ZEP(1:1)/LOR/ZEP(1:1)), and the electron beam lithography technique was successfully employed to develop devices with a gate width (T-foot, the foot of the T-shaped gate) of 78.5 nanometers. Finally, a simplified formula is used to estimate and compare high-frequency characteristic parameters.

Keywords : T-gate, SiC substrate, EBL, HEMTs, High frequency

# 目錄

|                                                                    |      |

|--------------------------------------------------------------------|------|

| 口試委員審定書.....                                                       | I    |

| 致謝.....                                                            | II   |

| 中文摘要.....                                                          | IV   |

| Abstract.....                                                      | V    |

| 目錄.....                                                            | VI   |

| 圖目錄.....                                                           | VIII |

| 表目錄.....                                                           | XI   |

| 第一章 緒論.....                                                        | 1    |

| 1.1    前言 .....                                                    | 1    |

| 1.2    研究動機.....                                                   | 2    |

| 1.3    論文架構.....                                                   | 4    |

| 第二章 理論基礎.....                                                      | 5    |

| 2.1    氮化鎵(GaN) .....                                              | 5    |

| 2.2    氮化鋁鎵/氮化鎵之異質結構特性 .....                                       | 6    |

| 2.2.1    自發極化(Spontaneous polarization) .....                      | 6    |

| 2.2.2    壓電極化(Piezoelectric polarization) .....                    | 7    |

| 2.2.3    二維電子氣(Two-Dimensional Electron Gas, 2DEG) .....           | 9    |

| 2.3    半導體與金屬接面.....                                               | 10   |

| 2.3.1    歐姆接觸(Ohmic contact) .....                                 | 11   |

| 2.3.2    蕭特基接觸(Schottky contact) .....                             | 12   |

| 2.3.3    傳輸線模型原理(Transfer Length Method, TLM) .....                | 12   |

| 2.4    碳化矽(SiC).....                                               | 13   |

| 2.5    高頻理論.....                                                   | 14   |

| 2.5.1    雙埠網路(Two-port network) .....                              | 14   |

| 2.5.2    開路短路襯墊去嵌化(open short pad de-embedding) .....              | 18   |

| 2.5.3    電流增益截止頻率(current gain cutoff frequency, <i>fT</i> ).....  | 19   |

| 2.5.4    功率增益截止頻率(power gain cutoff frequency, <i>fmax</i> ) ..... | 20   |

| 第三章 實驗儀器介紹.....                                                    | 21   |

| 3.1    微影技術(Lithography) .....                                     | 21   |

|            |                                                                                |    |

|------------|--------------------------------------------------------------------------------|----|

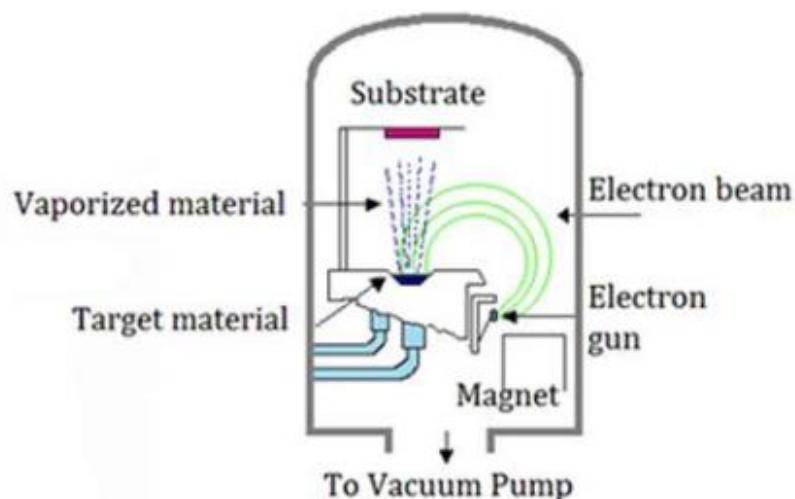

| 3.2        | 電子束蒸鍍機(Electron Beam Evaporator, E-gun) .....                                  | 23 |

| 3.3        | 快速升溫熱退火(Rapid Thermal Anneal, RTA) .....                                       | 24 |

| 3.4        | 反應式離子蝕刻機 (Reactive Ion Etching, RIE) .....                                     | 24 |

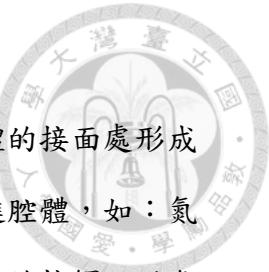

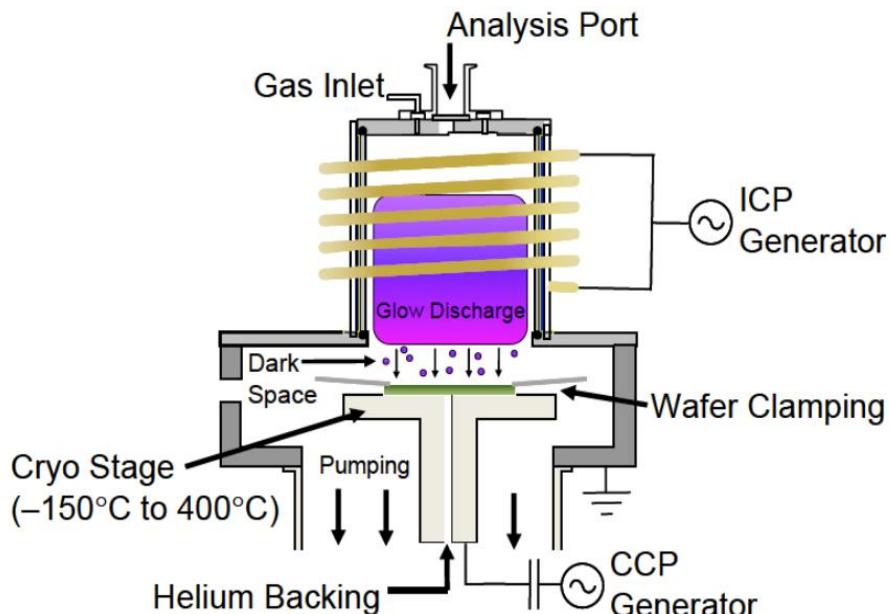

| 3.5        | 感應耦合電漿反應式離子蝕刻機(Inductively Coupled Plasma Reactive Ion Etching, ICP-RIE) ..... | 25 |

| 3.6        | 電漿輔助化學氣相沉積(Plasma-Enhanced Chemical Vapor Deposition, PECVD) .....             | 26 |

| 3.7        | 掃描式電子顯微鏡(Scanning Electron Microscope, SEM) .....                              | 27 |

| 3.8        | 聚焦離子束顯微鏡(Focused Ion Beam, FIB).....                                           | 28 |

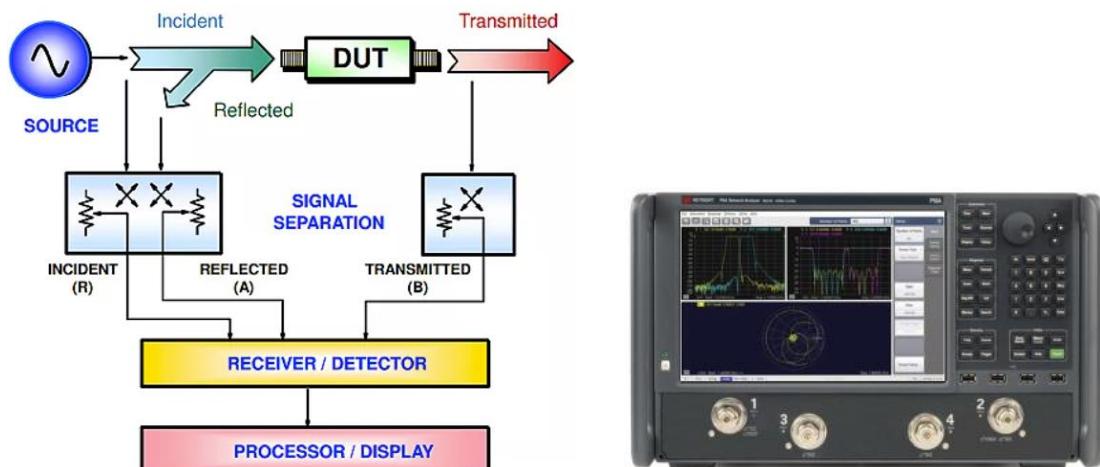

| 3.9        | 網路分析儀(Network Analyzer) .....                                                  | 29 |

| 第四章        | 實驗設計與製程.....                                                                   | 30 |

| 4.1        | 文獻回顧.....                                                                      | 30 |

| 4.1.1      | 縮小閘極線寬( $Lg$ )用以提升元件特性[28] .....                                               | 30 |

| 4.1.2      | T型閘極[3, 29, 30] .....                                                          | 31 |

| 4.2        | 元件設計 .....                                                                     | 32 |

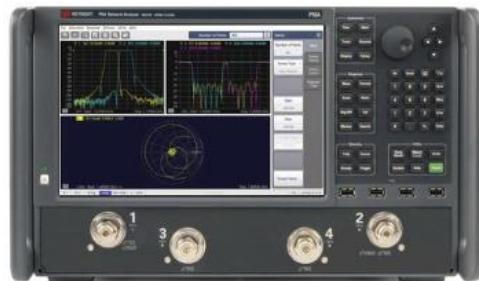

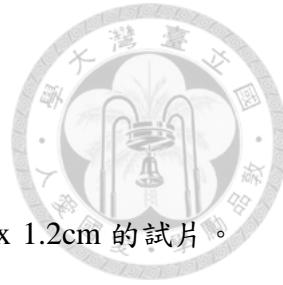

| 4.2.1      | 元件基板磊晶結構及特性.....                                                               | 32 |

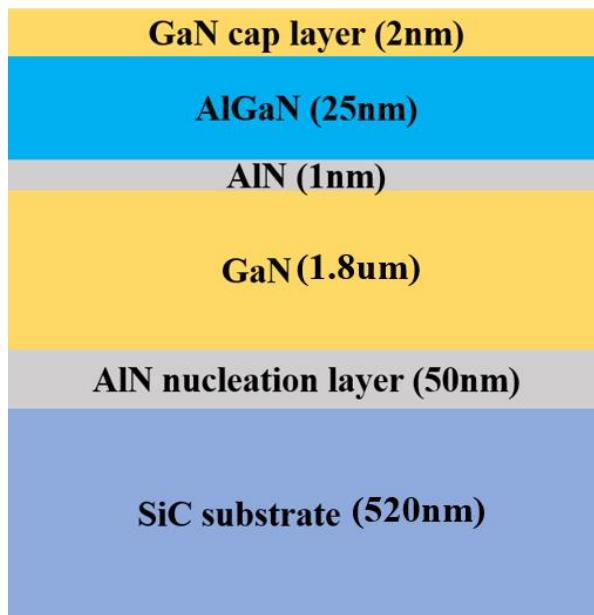

| 4.2.2      | 光罩設計.....                                                                      | 32 |

| 4.3        | 元件製程 .....                                                                     | 34 |

| 第五章        | 實驗結果與分析.....                                                                   | 44 |

| 5.1        | 直流量測 .....                                                                     | 44 |

| 5.2        | T型閘極 .....                                                                     | 48 |

| 5.3        | $fT$ 與 $fmax$ 估算 .....                                                         | 51 |

| 第六章        | 結論與未來展望 .....                                                                  | 54 |

| 參考文獻 ..... |                                                                                | 55 |

# 圖 目 錄

|                                                  |    |

|--------------------------------------------------|----|

| 圖 1-1 氮化鎗功率元件市場分析[2].....                        | 2  |

| 圖 1-2 (a)傳統閘極 (b) T 型閘極[3].....                  | 3  |

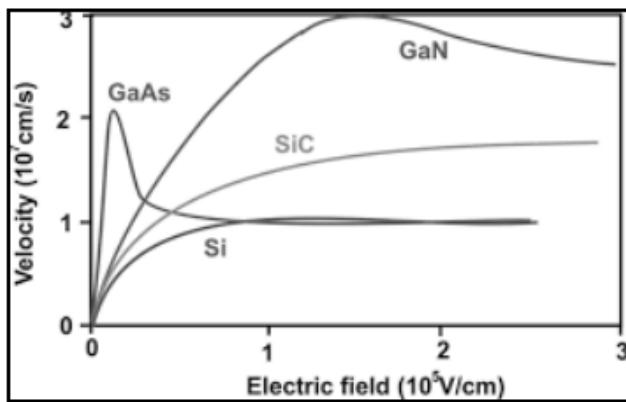

| 圖 2-1 不同半導體材料的電子飽和速度與電場之關係圖[5].....              | 6  |

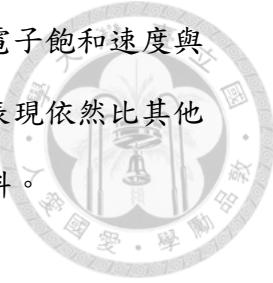

| 圖 2-2 (a)烏采結構 (b) GaN 原子排列結構圖[6, 7] .....        | 7  |

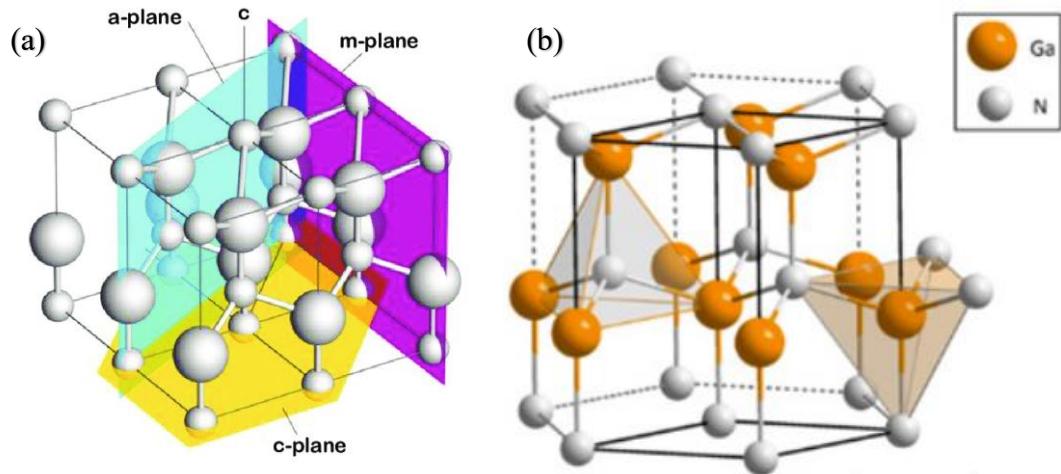

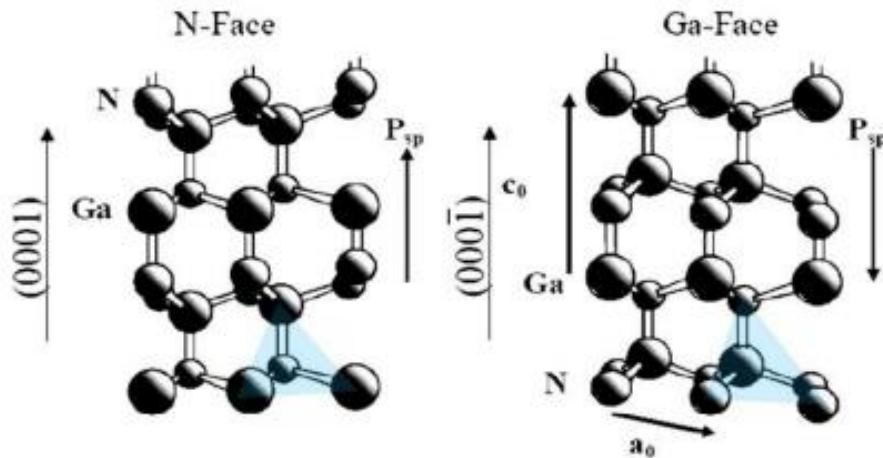

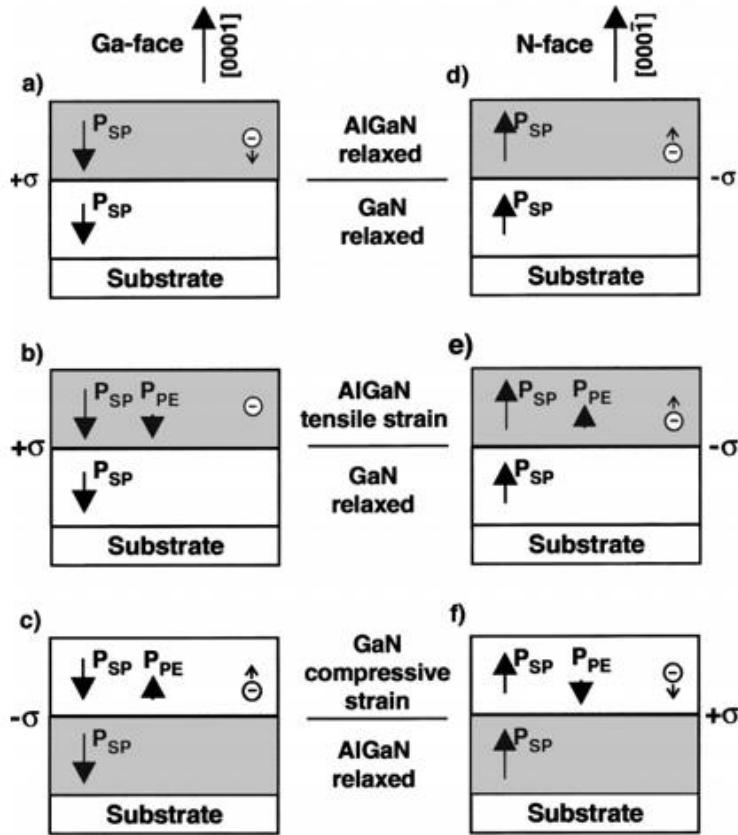

| 圖 2-3 N-face 與 Ga-face 示意圖[8] .....              | 7  |

| 圖 2-4 不同磊晶順序於不同終結面所對應之極化方向[8].....               | 9  |

| 圖 2-5 二維電子氣形成示意圖[9].....                         | 10 |

| 圖 2-6 極化效應形成量子井之能帶示意圖[10].....                   | 10 |

| 圖 2-7 歐姆接觸能帶示意圖(由 a 至 d) [11] .....              | 11 |

| 圖 2-8 薦特基接觸能帶圖[12].....                          | 12 |

| 圖 2-9 TLM 原理示意圖[13] .....                        | 13 |

| 圖 2-10 碳化矽常見的原子堆疊結構[14].....                     | 14 |

| 圖 2-11 N 埠網路示意圖[16].....                         | 17 |

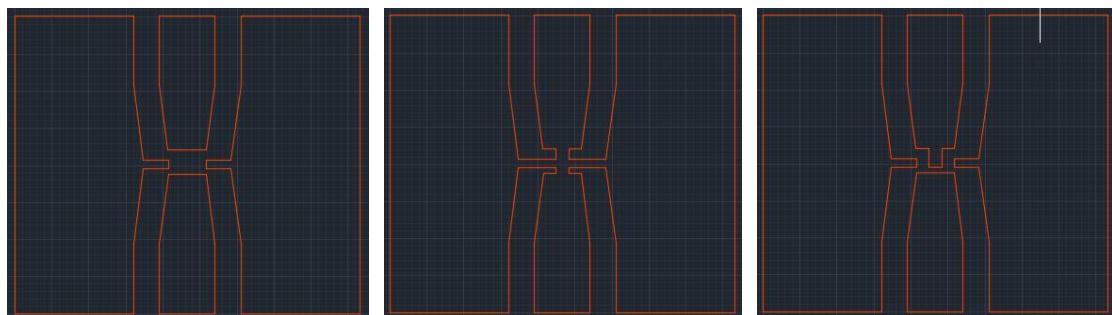

| 圖 2-12 開路襯墊(左)、短路襯墊(中)、待測元件(右) .....             | 18 |

| 圖 2-13 (a)開路襯墊模型 (b)短路襯墊模型 (c)待測元件襯墊模型[17] ..... | 18 |

| 圖 2-14 $fT$ 與 $fmax$ 量測結果示意圖[18].....            | 20 |

| 圖 3-1 光學微影技術之曝光示意圖[19].....                      | 22 |

| 圖 3-2 電子束微影技術之曝光示意圖[20].....                     | 22 |

| 圖 3-3 電子束蒸鍍機系統[21].....                          | 23 |

| 圖 3-4 RIE 系統[6] .....                            | 24 |

| 圖 3-5 ICP-RIE 系統[22].....                        | 25 |

| 圖 3-6 (左)等向性蝕刻 (右)非等向性蝕刻[23] .....               | 25 |

| 圖 3-7 PECVD 系統[24] .....                         | 26 |

| 圖 3-8 SEM 系統[25] .....                           | 27 |

| 圖 3-9 FIB 系統[26] .....                           | 28 |

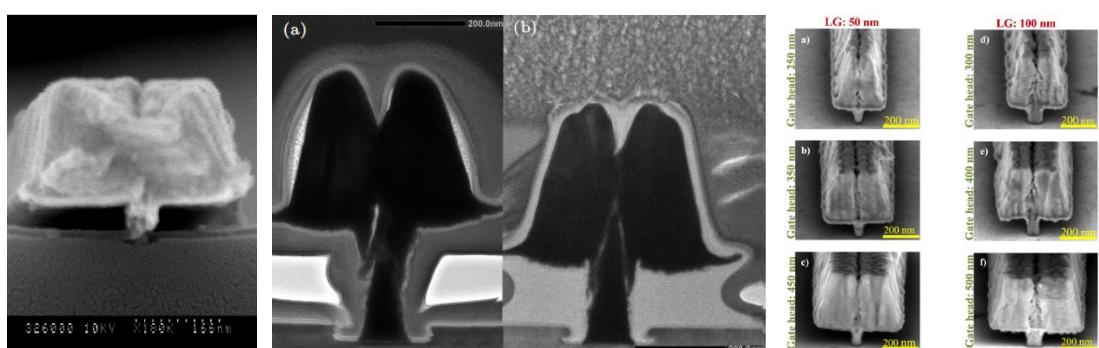

| 圖 3-10 以離子束切割之 T 型閘極.....                        | 28 |

| 圖 3-11 網路分析儀運作原理[27].....                        | 29 |

|                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------|----|

| 圖 3-12 網路分析儀[27].....                                                                                        | 29 |

| 圖 4-1 文獻元件結構[28].....                                                                                        | 30 |

| 圖 4-2 文獻元件量測結果[28].....                                                                                      | 30 |

| 圖 4-3 各參考文獻之 T 型閘極成品圖(左 1[3]、左 2[29]、右 1[30]).....                                                           | 31 |

| 圖 4-4 元件基板磊晶結構 .....                                                                                         | 32 |

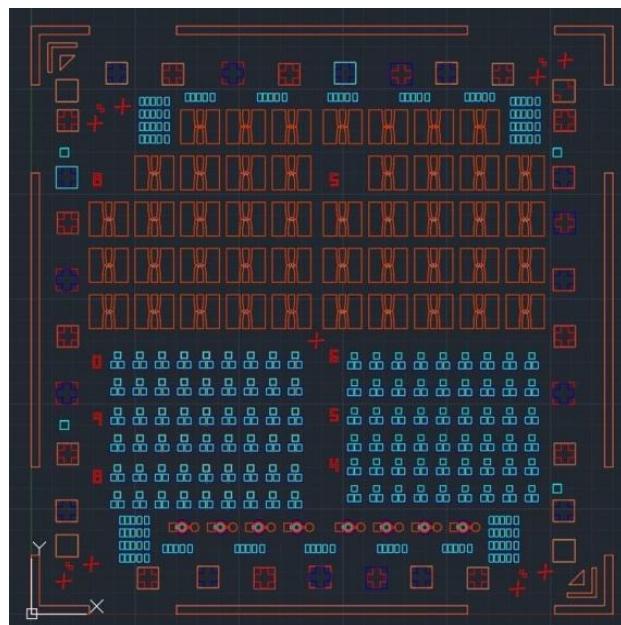

| 圖 4-5 Autocad 元件設計圖 (a)角標 (b)直流元件 (c)高頻元件 .....                                                              | 33 |

| 圖 4-6 光罩設計圖 .....                                                                                            | 33 |

| 圖 4-7 Clean 示意圖 .....                                                                                        | 34 |

| 圖 4-8 定義電子束角標及歐姆接觸示意圖 .....                                                                                  | 36 |

| 圖 4-9 元件隔離示意圖 .....                                                                                          | 37 |

| 圖 4-10 定義 T 型閘極與蕭特基接觸示意圖 .....                                                                               | 38 |

| 圖 4-11 定義 T 型閘極與蕭特基接觸之流程圖 (a)塗佈第一層光阻 (b)曝光及顯影 T-foot (c)塗佈第二、三層光阻 (d)曝光及顯影 T-head (e)鍍金屬 Ni/Au (f)掀離金屬 ..... | 40 |

| 圖 4-12 沉積鈍化層示意圖 .....                                                                                        | 41 |

| 圖 4-13 電極金屬洞通孔示意圖 .....                                                                                      | 42 |

| 圖 5-1 TLM 量測結果 .....                                                                                         | 44 |

| 圖 5-2 調整後的元件製程順序 .....                                                                                       | 45 |

| 圖 5-3 元件設計圖(單位為 um) .....                                                                                    | 46 |

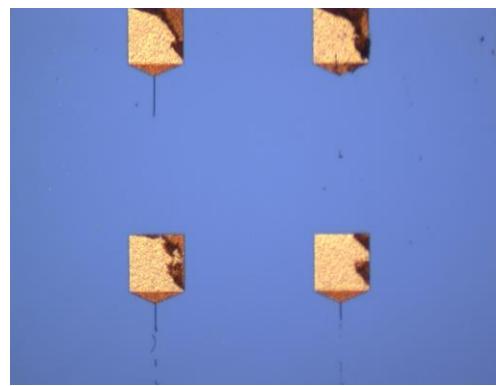

| 圖 5-4 元件 OM 圖 .....                                                                                          | 46 |

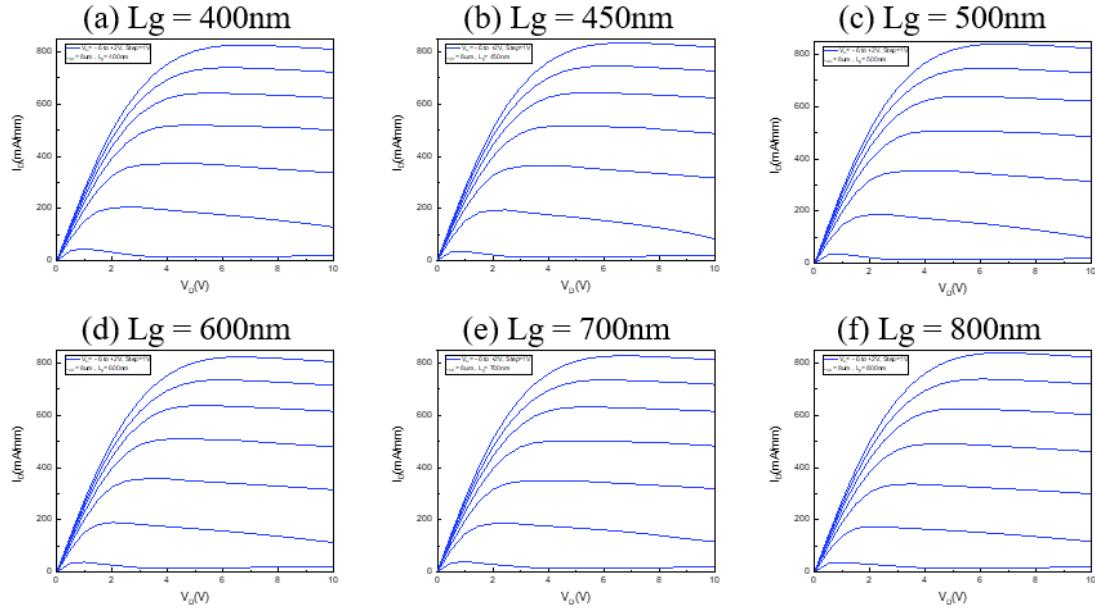

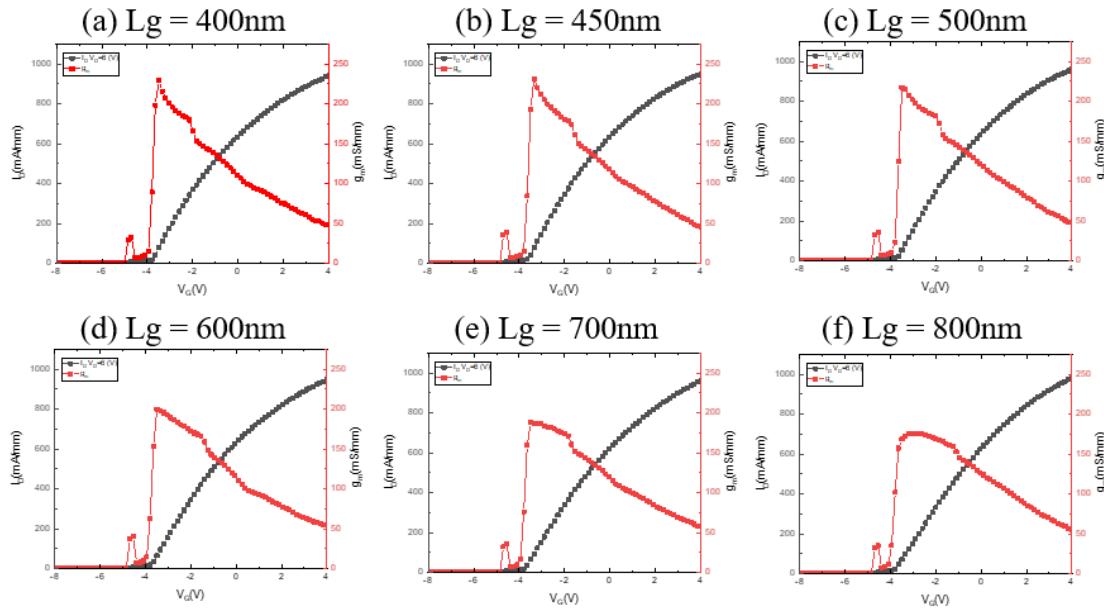

| 圖 5-5 元件 $I_D$ - $V_D$ 圖 .....                                                                               | 47 |

| 圖 5-6 元件 $I_D$ - $V_G$ 圖 .....                                                                               | 47 |

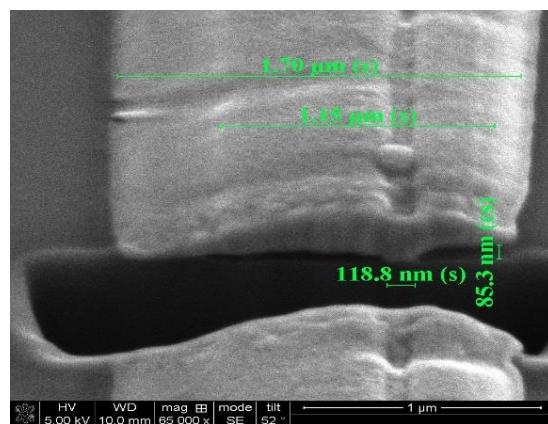

| 圖 5-7 Sample 1 FIB .....                                                                                     | 49 |

| 圖 5-8 Sample 2 OM .....                                                                                      | 49 |

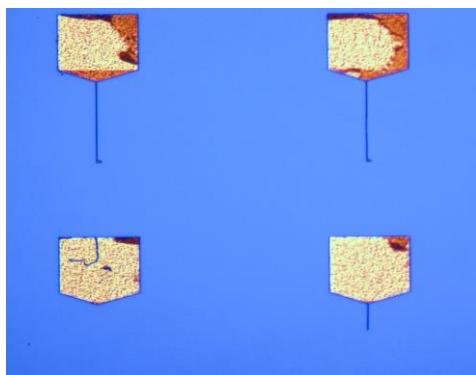

| 圖 5-9 Sample 3 OM .....                                                                                      | 50 |

| 圖 5-10 Sample 4 OM .....                                                                                     | 50 |

| 圖 5-11 Sample 5 FIB .....                                                                                    | 50 |

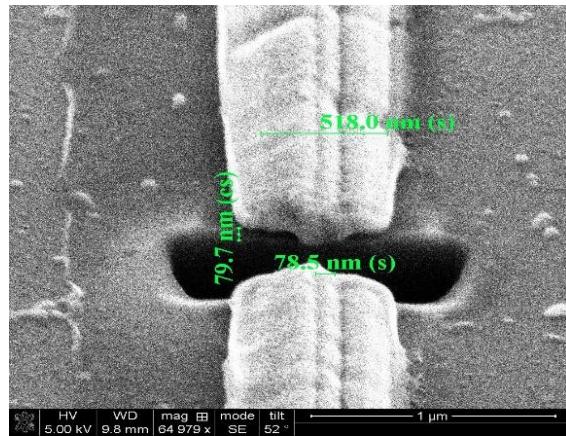

| 圖 5-12 Sample 6 FIB .....                                                                                    | 51 |

| 圖 5-13 傳統線閘極結構示意圖 .....                                                                                      | 52 |

圖 5-14 T 型閘極結構示意圖 ..... 52

## 表目錄

|                                      |    |

|--------------------------------------|----|

| 表 1-1 半導體材料特性[1].....                | 1  |

| 表 2-1 常見半導體材料的特性比較 .....             | 5  |

| 表 2-2 砂基板、碳化矽基板與藍寶石基板與氮化鎗磊晶之比較 ..... | 14 |

| 表 5-1 本研究與參考文獻之電性比較 .....            | 48 |

| 表 5-2 估算結果 .....                     | 53 |

# 第一章 緒論

## 1.1 前言

隨著科技進步，5G 世代的來臨，對於半導體產業的需求日漸增加，為了因應科技的發展，半導體產業也不斷在改良製程及使用不同材料，第一代半導體為矽(Si)半導體，但隨著摩爾定律(Moore's Law)的趨勢，元件尺寸須不斷微縮，於相同面積的晶片中，每 24 個月電晶體數目要增加一倍，這使得矽製程被迫受限於物理極限且其製程成本相對較為昂貴，因此須尋求新材料來補足矽製程的不足。第二代半導體以砷化鎵(GaAs)、磷化銦(InP)為主，因其較高的電子遷移率及直接能隙的特性，比起矽半導體更適合應用在無線通訊及光電元件上，不過雖擁有較高的電子遷移率，但第二代半導體其崩潰電場及能隙無法滿足現今高功率及高頻元件的需求，因此出現第三代半導體，以寬能矽的碳化矽(SiC)與氮化鎵(GaN)為代表，第三代半導體的寬能隙、高崩潰電場及高電子遷移率等特性，如表 1-1 所示[1]，更適合發展於高頻及高功率元件上。

表 1-1 半導體材料特性[1]

|                                                 | Si   | 4H-SiC | GaN  |

|-------------------------------------------------|------|--------|------|

| Bandgap $E_g$ /eV                               | 1.12 | 3.25   | 3.4  |

| Dielectric constant $k$                         | 11.8 | 9.7    | 9    |

| Breakdown field $E_{br}$ /(MV/cm)               | 0.3  | 2.5    | 3.3  |

| Thermal conductivity $\lambda$ /(W/cm·K)        | 1.5  | 4.9    | 2.3  |

| Electron mobility $\mu$ /(cm <sup>2</sup> /V·s) | 1500 | 1000   | 1250 |

| BFOM $k\mu E_{br}^3$                            | 1    | 317.1  | 846  |

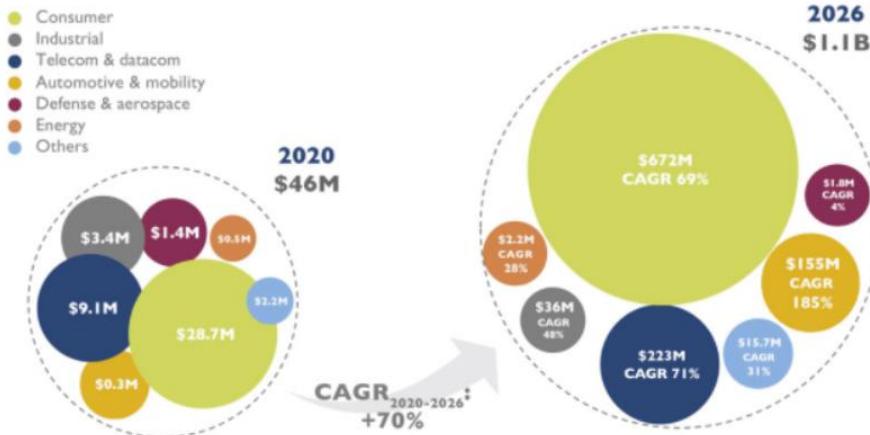

氮化鎵高電子遷移率電晶體因上述優點使得此電晶體能廣泛應用在諸多領域之中，舉例來說：高電子遷移率及高飽和速度的特性讓氮化鎵高電子遷移率電晶體適合應用於高頻放大器，像現在正在發展的 5G 領域、衛星通信、等；耐高溫高電壓的特性，也讓氮化鎵高電子遷移率電晶體適合應用於高溫環境及高功率元件之中，例如：車用電子元件、航太工業等。於市場分析調查中，氮化鎵功率元件主要被應用於通訊、軍事及手機產品等等，更於 2020 年時氮化鎵功率

元件整體營收達到 460 萬，而預期到了 2026 年時整體營收可達 1.1 億，且複合年成長率(CAGR)達到 70%，如圖 1-1 所示[2]，由此可發現氮化鎵元件所具備可觀的未來發展性。

## 2020-2026 power GaN market forecast split by application

(Source: GaN Power 2021: Epitaxy, Devices, Applications and Technology Trends report, Yale Développement, 2021)

圖 1-1 氮化鎵功率元件市場分析[2]

## 1.2 研究動機

為了判斷所製作元件的高頻特性表現，有兩個重要參數可以做為評判的指標，這兩個參數分別是電流增益截止頻率(current gain cutoff frequency,  $f_T$ )以及功率增益截止頻率(power gain cutoff frequency,  $f_{max}$ )，而這兩個參數於小訊號模型中可以推導得到公式如下所示：

$$f_T = \frac{g_m}{2\pi[(C_{gs}+C_{gd})(1+\frac{R_s+R_d}{R_{ds}})+g_m C_{gd}(R_s+R_d)]} \quad (式 1-1)$$

$$f_{max} = \frac{f_T}{2[\pi f_T C_{gd}(R_s+R_g+R_{gs}+2\pi L_g)+G_{ds}(R_s+R_g+R_{gs}+\pi f_T L_s)]} \quad (式 1-2)$$

其中電流增益截止頻率  $f_T$  又能近似成：

$$f_T \approx \frac{g_m}{2\pi C_{gs}} = \frac{v_{sat}}{2\pi L_g} \quad (式 1-3)$$

由上式可知，若要提升電流增益截止頻率  $f_T$  可以藉由兩個方式來達成，第一個

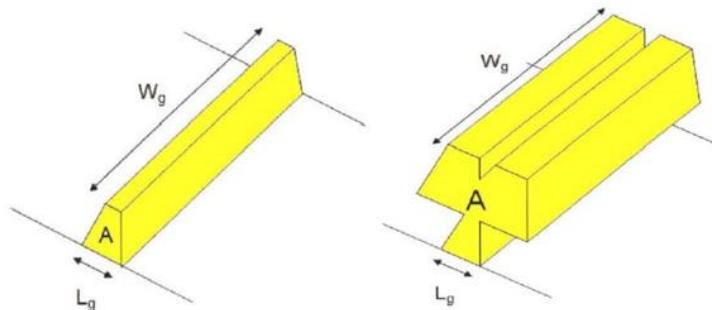

是提升轉導值( $g_m$ )，第二個是降低閘極線寬(gate length,  $L_g$ )，其中閘極線寬 $L_g$ 微縮能夠使得元件的通道電阻被有效降低，進而提高飽和電流與轉導值( $g_m$ )，但當閘極線寬 $L_g$ 縮越小時，其相應之閘極電阻(gate resistance,  $R_g$ )會隨之上升，由功率增益截止頻率 $f_{max}$ 的公式可以發現，若閘極電阻 $R_g$ 上升則會造成功率增益截止頻率 $f_{max}$ 下降，為了能夠同時提升電流增益截止頻率 $f_T$ 與不讓功率增益截止頻率 $f_{max}$ 下降，即同時讓閘極線寬 $L_g$ 與閘極電阻 $R_g$ 降低，T型閘極(T-gate)的技術被開發出來用來製作高頻元件，由於T型閘極具有較大的橫截面積，如圖 1-2 所示[3]，能有效降低閘極電阻 $R_g$ ，同時T型閘極也能製作較小的閘極線寬 $L_g$ ，如此一來即可確保電流增益截止頻率 $f_T$ 與功率增益截止頻率 $f_{max}$ 都有良好的表現。

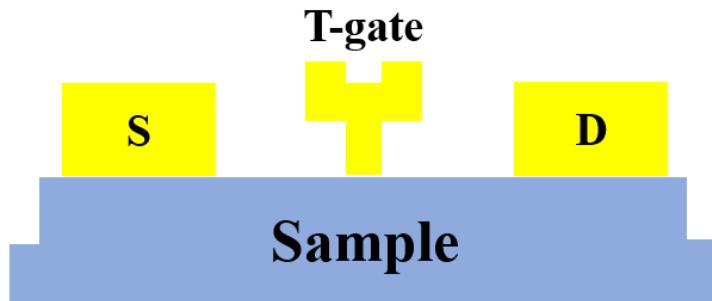

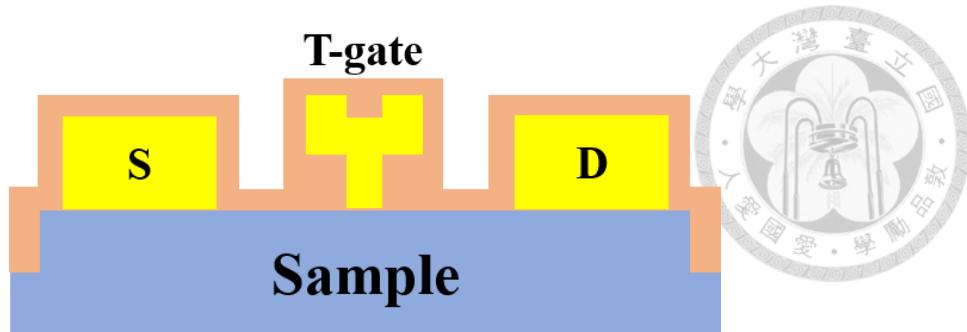

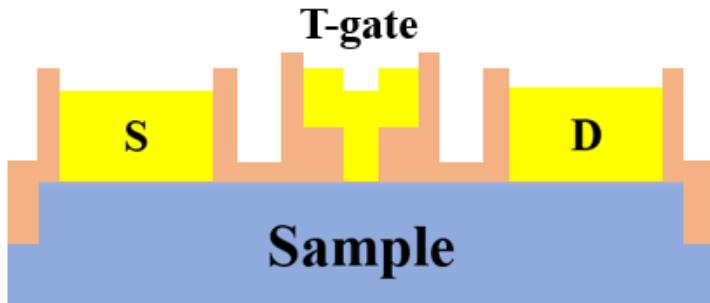

圖 1-2 (a)傳統閘極 (b) T型閘極[3]

為了能讓高頻 GSG 探針(ground signal ground probe)成功將訊號輸入元件當中來量測 HEMT 元件的 S 參數(S-parameter)，此實驗將元件設計成二指結構(two finger)，以及另外設計三種金屬襯墊，包含開路襯墊(open pad)、短路襯墊(short pad)及去嵌化襯墊(de-embedding pad)，其中利用去嵌化襯墊可以去除開路襯墊與短路襯墊上的寄生參數，並萃取獲得所製作元件的本質參數。最後藉由建立開路襯墊、短路襯墊與元件的小訊號模型進行模擬，並與量測結果相擬合來分析製作出的 T-gate HEMT 元件之高頻特性。

### 1.3 論文架構

本論文撰寫架構分為以下六個章節，分別是緒論、理論基礎、實驗儀器介紹、實驗設計與製程、實驗結果與分析、結論與未來展望，各章節內容敘述如下：

第一章 緒論：

簡介第一代半導體到第三代半導體之特性與發展，及現今半導體產業之趨勢與氮化鎵材料之市場價值，並說明本篇論文之研究動機及架構。

第二章 理論基礎：

介紹氮化鋁鎵/氮化鎵此種異質結構及二維電子氣(2DEG)生成機制，且說明金屬歐姆接觸、蕭特基接觸還有歐姆接觸的量測方法，介紹碳化矽的材料特性，並藉由微波工程之內容嘗試推導分析高頻量測相關公式。

第三章 實驗儀器介紹：

介紹實驗所用之機台及其儀器操作原理。

第四章 實驗設計與製程：

簡介T型閘極相關文獻，並說明此研究之元件設計、製程步驟與量測方式。

第五章 實驗結果與分析：

用FIB剖面圖印證三層光阻法製作T型閘極之可行性，並利用公式估算其高頻特性參數；元件在直流特性方面利用電流電壓曲線獲取相應之最大飽和電流、漏電流、轉導值與電流開關比，並探討閘極線寬微縮之特性變化。

第六章 結論與未來展望：

對此篇論文之實驗結果做總結，並提出可以改良的方向與未來預期可達之目標。

## 第二章 理論基礎

### 2.1 氮化鎗(GaN)

在科技越來越發達的時代，需要更加追求訊號傳輸能更快速且無延遲，因此對於高頻及高功率元件的需求及研究日漸增加，且相應技術的開發也越來越重要。以氮化鎗(GaN)為主體的 III-V 族化合物半導體材料，不僅能彌補第一代半導體-矽(Si)於物理限制造成的技術瓶頸，且具備更高的載子傳輸速度，更適合作為通道材料來製作更高性能的元件，因此被稱之為第三代半導體。其中氮化鎗具備寬能隙、高崩潰電場及高電子遷移率等特性，因此更是常被用來製作高頻及高功率元件的材料，其可應用範圍及具備的市場發展潛力於 1.1 章提過，這裡就不再贅述重提。常見的半導體材料特性如表 2-1 所示[4]，可以發現氮化鎗相較於其他材料的優異特性表現。

表 2-1 常見半導體材料的特性比較[4]

Table 1. Physical properties of Si, GaAs, SiC, GaN, and diamond.

| Materials | $E_g$<br>(eV) | $\epsilon$ | $\mu_n$<br>( $\text{cm}^2/\text{V}\cdot\text{s}$ ) | $E_c$<br>( $\text{MV}/\text{cm}$ ) | $V_{\text{sat}}$<br>( $10^7\text{cm}/\text{s}$ ) | Total<br>Dislocation ( $\text{cm}^2$ ) | Thermal<br>Conductivity<br>( $\text{W}/\text{m}\cdot\text{K}$ ) |

|-----------|---------------|------------|----------------------------------------------------|------------------------------------|--------------------------------------------------|----------------------------------------|-----------------------------------------------------------------|

| Si        | 1.12          | 11.8       | 1350                                               | 0.3                                | 1                                                | -                                      | 145                                                             |

| GaAs      | 1.42          | 13.1       | 8500                                               | 0.4                                | 2                                                | -                                      | 50                                                              |

| 4H-SiC    | 3.26          | 10         | 720                                                | 2.0                                | 2                                                | $>10^2$                                | 370                                                             |

| GaN       | 3.44          | 9          | 1250                                               | 3.3                                | 2.5                                              | $>10^5$                                | 253                                                             |

| Diamond   | 5.5           | 5.7        | 2000                                               | 13.0                               | 1.5                                              | $>10^4$                                | 2290                                                            |

$E_g$  energy bandgap;  $\epsilon$ , relative dielectric constant;  $\mu_n$ , electron mobility;  $E_c$ , critical electric field;  $V_{\text{sat}}$ , saturation velocity

對於是否適合作為高頻與高功率元件，可以比較不同材料的電子遷移率(Electron mobility)作為考量，電子遷移率越高表示其造成的電阻越小，因此導電度也會越高，進而使功耗降低且具有較高的電流承載負荷能力，且其傳輸時間也會越小，因而可以提高元件的轉換開關速度。圖 2-1 為不同半導體材料的電子飽和速度與電場的關係圖[5]，根據表 2-1 及圖 2-1 可以發現矽的表現與其他材料相比略顯不足；接著可以發現身為第二代半導體的代表材料-砷化鎗，雖具有較高的電子飽和速度與電子遷移率，但隨著電場增加，其電子飽和速度會

急遽降低，甚至表現比矽材料更差；而氮化鎗材料不僅具備高電子飽和速度與高電子遷移率，雖在高電場環境時電子飽和速度會略降，但其表現依然比其他材料更為優異，因此更適合作為高頻與高功率元件的半導體材料。

圖 2-1 不同半導體材料的電子飽和速度與電場之關係圖[5]

## 2.2 氮化鋁鎗/氮化鎗之異質結構特性

氮化鋁鎗與氮化鎗具備不同的晶格常數與能隙，因此在這兩個材料的接面處會產生兩種極化反應，分別是因氮化鋁鎗與氮化鎗的組成架構所形成的自發極化(Spontaneous polarization)效應與因晶格常數不匹配所形成之壓電極化(Piezoelectric polarization)效應。除了上述兩種極化反應，由於氮化鋁鎗與氮化鎗的能隙相差極大，因此在其接面處會有因極化反應形成之二維電子氣(2DEG)，以下將詳細介紹此異質結構接面的三個特性。

### 2.2.1 自發極化(Spontaneous polarization)

自發極化效應(Spontaneous polarization)的原理是由於材料中的結構造成電荷分布不均所導致，當材料的原子排列結構非中心對稱時，於結構中的正負電荷分布不均形成內部電場，使得在無外加電場時，此內部電場的形成造成材料於結構中自發產生極化現象。

氮原子與大部分 IIIA 元素形成鍵結時會具有強離子性，原因是因兩者具差異較大的電負度，且氮化鎗晶體為了達到平衡，大多會生成扭曲的結構，而非完整烏采結構(Wurtzite)，如圖 2-2 所示[6, 7]，氮化鎗晶體因此扭曲結構使得內

部電荷分布不均與強離子性，使晶體會產生由晶體表面指向基板方向的極化反應，即為自發極化效應。氮化鎵晶體中的氮原子與鎵原子呈現六方最密堆積(Hexagonal Close-Packed, HCP)結構，其中又會因磊晶方式不同，進而分別生成以氮原子為主(N-face)或以鎵原子為主(Ga-face)的終結面，如圖 2-3 所示[8]。

圖 2-2 (a)烏采結構 (b) GaN 原子排列結構圖[6, 7]

圖 2-3 N-face 與 Ga-face 示意圖[8]

## 2.2.2 壓電極化(Piezoelectric polarization)

在氮化鋁鎵與氮化鎵磊晶結構中的壓電極化(Piezoelectric polarization)效應是由於兩種材料於接面處，氮化鋁鎵的部分鋁原子會取代氮化鎵的鎵原子，而鋁原子與鎵原子不同的電負度造成晶格產生形變，進而導致晶格內部電荷分布不均形成內部電場，並引發極化效應的產生，此現象即稱之為壓電極化效應。

此效應可以看出材料在受應力或壓力時，所產生極化效應的能力，並可以透過壓電常數的公式來描述：

· 壓電極化公式：

$$P_{PE} = e_{33} \cdot \epsilon_Z + e_{31}(\epsilon_x + \epsilon_y) \quad (\text{式 2-1})$$

其中  $e_{33}$  與  $e_{31}$  皆為壓電極化常數(Piezoelectric coefficients)、 $\epsilon_Z$ 為朝向 c 軸之

應力且可表示為  $\frac{(c-c_0)}{c_0}$ 、 $\epsilon_x$ 為朝向 a 軸之應力且  $\epsilon_x = \epsilon_y = \frac{(a-a_0)}{a_0}$  ( $\epsilon_x$ 與  $\epsilon_y$ 同向)

，其中  $c_0$  與  $a_0$  皆為晶格不受任何應力時的晶格常數，而  $c$  與  $a$  皆為晶格受應力作用後的晶格常數。

· 六方最密堆積結構中 a 軸與 c 軸間的晶格常數關係式：

$$\frac{(c-c_0)}{c_0} = -2 \times \frac{c_{13}}{c_{33}} \times \frac{(a-a_0)}{a_0} \quad (\text{式 2-2})$$

其中  $c_{13}$  與  $c_{33}$  皆為彈性係數(Elastic constant)。

將式 2-2 帶入式 2-1 可推得下式 2-3，此式即可表示於 c 軸上的壓電極化大小：

$$P_{PE} = 2 \frac{(a-a_0)}{a_0} \cdot \left( e_{31} - \frac{(e_{33}-c_{13})}{c_{33}} \right) \quad (\text{式 2-3})$$

以  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  磚晶於 GaN 上的異質結構為例，其相應晶格常數之關係式如下：

$$a\text{Al}_x\text{Ga}_{1-x}\text{N} = a\text{AlN}_x + a\text{GaN}_{1-x} \quad (\text{式 2-4})$$

其中  $\chi$  為含鋁量、 $a\text{Al}_x\text{Ga}_{1-x}\text{N}$  為不同鋁含量的氮化鋁鎵之晶格常數、 $a\text{AlN}$  為氮化鋁之晶格常數、 $a\text{GaN}$  為氮化鎵之晶格常數。其異質接面處所受應力的平面分量可以下式 2-5 表示：

$$\epsilon_x = \epsilon_y = \frac{a\text{GaN} - a\text{AlGaN}}{a\text{AlGaN}} \quad (\text{式 2-5})$$

由  $\epsilon_x = \epsilon_y$  數值的正負可以將極化產生的應力分為伸張應力(Tensile strain)與壓縮應力(Compress strain)，當數值為正時表示氮化鎵的晶格常數比氮化鋁鎵的晶格常數要大，因此磚晶層所受到的應力稱之為伸張應力；反之，則稱之為壓縮應力。

異質結構中相異材料所引起的極化效應為自發極化與壓電極化之總和，而

極化效應的方向會受材料磊晶成長的順序所影響，由圖 2-4[8]可發現，若是氮化鎵磊晶於氮化鋁鎵之上，其相應的自發極化方向與壓電極化方向相異，整體極化能力較低；反之，若氮化鋁鎵成長於氮化鎵之上，其相應的自發極化方向與壓電極化方向相同，因此可以得到較高的極化能力。

圖 2-4 不同磊晶順序於不同終結面所對應之極化方向[8]

### 2.2.3 二維電子氣(Two-Dimensional Electron Gas, 2DEG)

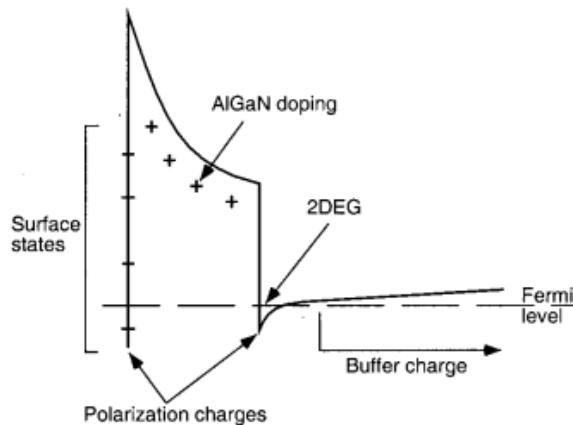

二維電子氣最常見於異質結構中，相異材料具有不同晶格參數造成晶格不匹配，且具有不同能隙形成能帶差異，為了保持費米能階(Fermi Level)連續及電中性，進而產生能帶彎曲或偏移的現象，以氮化鋁鎵與氮化鎵的異質接面為例，除了上述兩個情形皆具備，同時也有極化效應的產生，使其接面處生成空間電荷，且氮化鎵的導電帶(Ec)在接面處會彎曲，形成倒三角形量子井(Quantum Well)，而因極化效應生成的空間電荷會在此量子井中累積，進而形成二維電子氣，如圖 2-5 所示[9]。

二維電子氣的濃度受極化效應所影響，若極化效應越強則會於接面處生成較深的量子井，因此能累積更多空間電荷形成更高濃度的二維電子氣，如圖 2-6 所示[10]，不過受平面限制，僅能於平面中運動傳輸。與一般常見的電晶(如：MOSFET)相比，二維電子氣具有更高的電子傳輸速度與電子遷移率，因此具有二維電子氣的異質結構適合作為電晶體之基板材料。

圖 2-5 二維電子氣形成示意圖[9]

圖 2-6 極化效應形成量子井之能帶示意圖[10]

## 2.3 半導體與金屬接面

電晶體的製程中，常見的部分即是半導體與金屬的異質接面，此接面的好壞能直接影響元件製成後的特性表現，而此接面會有兩種不同的金屬與半導體接觸面性質，分別是供應電晶體的載子傳輸且接觸電阻較低的歐姆接觸(Ohmic contact)與具整流特性並能控制通道電流的蕭特基接觸(Schottky contact)，此章節

會分別詳細介紹上述的兩種接觸面性質及歐姆接觸之量測方式。

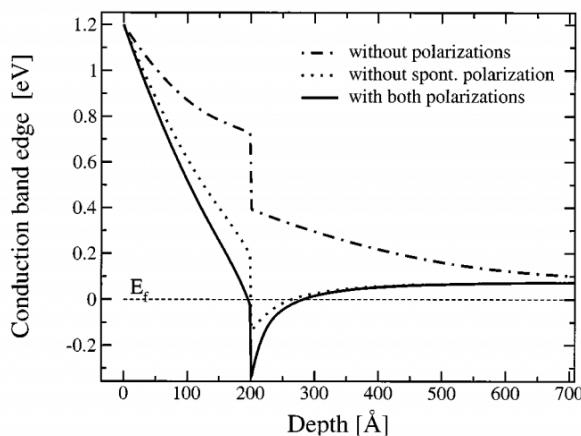

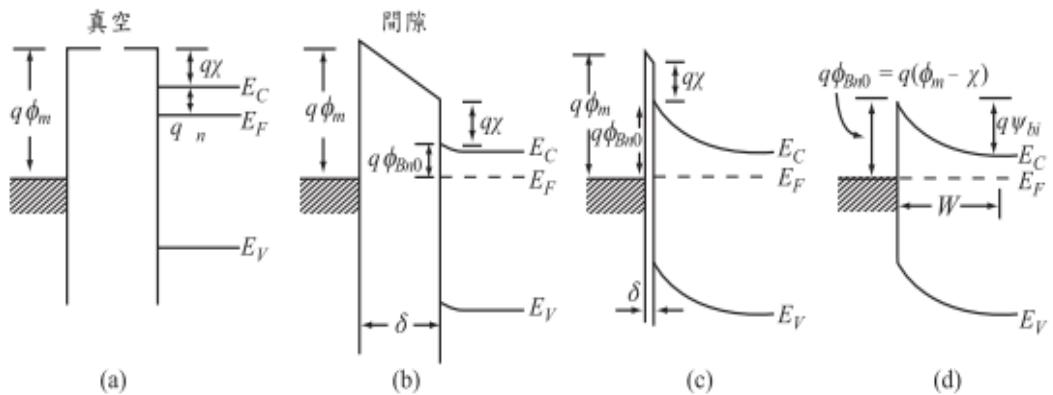

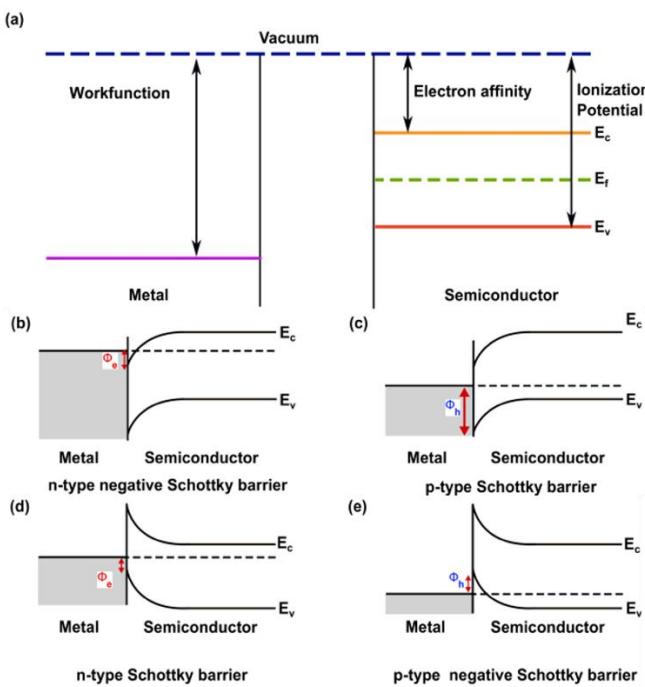

### 2.3.1 歐姆接觸(Ohmic contact)

歐姆接觸的目的是實現良好的電子電動傳導且降低接觸電阻，通過金屬與半導體材料不同的能階接觸，形成能帶連續區域，使得於此區域中的電子能自由穿越此接面，如圖 2-7 所示[11]。其中接觸電阻越趨近於零則越接近理想的歐姆接觸，元件的操作效率就會越好且於接面產生的損耗越小。

圖 2-7 歐姆接觸能帶示意圖(由 a 至 d) [11]

我們可以透過一些措施來使得歐姆接觸品質更佳，如：使用適當比例的金屬材料、提高半導體的參雜濃度、、、等，這些優化歐姆接觸的措施可以提高導電性且降低接觸電阻，進而實現優良的歐姆接觸。常見的氮化鋁鎵/氮化鎵高電子遷移率電晶體通常採用鈦(Ti)/鋁(Al)/鎳(Ni)/金(Au)不同比例的四種金屬並配合快速升溫熱退火來實現歐姆接觸，其中鈦(Ti)於高溫時會與氮化鋁鎵的氮原子作用形成氮化鈦(TiN)，使氮化鋁鎵結構中形成氮原子空缺，而此高濃度的氮原子空缺能降低空乏區寬度，與參雜高濃度的 n-GaN 有相似效果，能助於形成歐姆接觸；鋁(Al)因其具備較低的功函數，可用來進行能障位置的調整；第三層為阻擋層，用來避免不同金屬產生交互作用影響歐姆接觸的品質，因此會選擇高熔點的金屬來作為阻擋層材料，如：鎳(Ni)、鉑(Mo)；金(Au)具有高導電性且不易氧化，因此適合作為最上層材料的選擇及作為接觸電極。製作好歐姆接觸後會進行快速升溫熱退火製程，使其原子得以重新排列讓架構更穩固，也可

獲得品質較佳的歐姆接觸。

### 2.3.2 蕭特基接觸(Schottky contact)

蕭特基接觸常見於半導體材料與高導電性且具較高功函數金屬的接面處，由於高功函數的金屬與半導體接觸面會形成一不連續能帶( $\Phi_m > \Phi_s$ )，稱之為障壁電位(Schottky barrier)，如圖 2-8 所示[12]，此障壁電位會限制電子的傳輸進而達到整流的作用，而閘極的功用為控制汲極與源極間的流通電流，因此蕭特基接觸適合用來製作元件之閘極。此外，由於具有障壁電位，因此蕭特基接觸需要施加足夠大的電壓才能使元件導通，若選擇具有越高的功函數金屬作為接觸材料，其能隙與半導體材料差距越大則會形成更大的障壁電位，因而能提高閘極控制能力且同時降低閘極漏電流的產生。

圖 2-8 蕭特基接觸能帶圖[12]

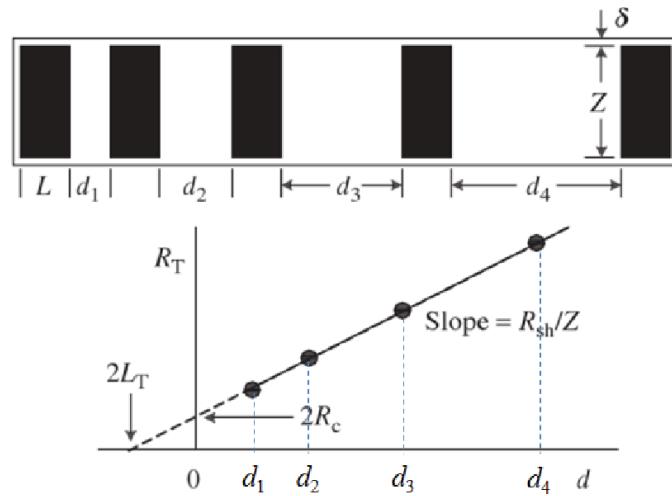

### 2.3.3 傳輸線模型原理(Transfer Length Method, TLM)

為了得知該金屬與半導體形成的歐姆接觸品質好壞，須利用傳輸線模型理論(TLM)進行量測，其原理為設計數個不同間距的金屬襯墊，間距分別為  $d_1$ 、 $d_2$ 、 $d_3$ 、 $d_4$ ，金屬襯墊之寬度為  $Z$ ，量測後可獲得各間距金屬襯墊的總電阻  $R_T$

。將金屬襯墊的不同間隔距離與總電阻 $R_T$ 繪製其關係圖，縱軸為 $R_T$ 橫軸為距離，並可以得到一趨勢線，最佳狀態為呈現一斜直線，如圖 2-9 所示[13]，因此可以將此斜直線用線性方程式表達：

$$R_T = 2R_c + R_{semi} = 2R_c + \frac{R_s d}{Z} \approx \frac{2R_s L_T}{Z} + \frac{R_s d}{Z} = \frac{R_s}{Z} (d + L_T) \quad (式 2-6)$$

其中 $R_T$ 為總電阻、 $d$ 為各金屬襯墊間距、 $R_s$ 為片電阻、 $R_c$ 為接觸電阻、 $R_{semi}$

為半導體內部電阻。由式 2-6 可知縱軸 $R_T$ 的截距為 $2R_c$ 且斜率為 $\frac{R_s}{Z}$ 。

圖 2-9 TLM 原理示意圖[13]

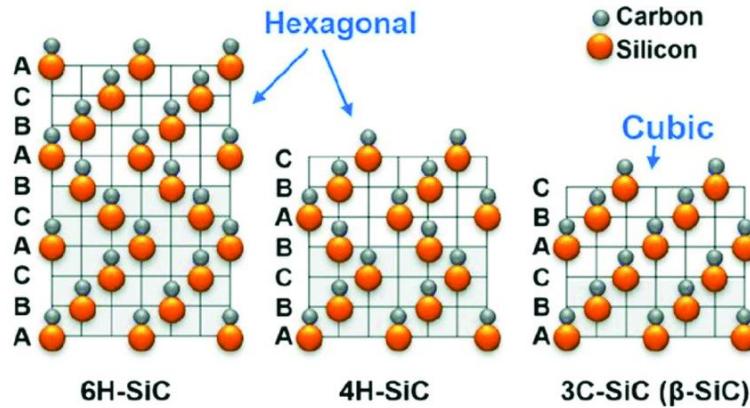

## 2.4 碳化矽(SiC)

碳化矽(SiC)與氮化鎵(GaN)同屬第三代半導體，具有寬能隙、高電子遷移率極高飽和速度等優點。碳化矽有多種晶格結構，依其結構型態可分為立方晶系(Cubic)、六方晶系(Hexagonal)、菱形晶系(Rhombohedral)等等，再根據堆疊結構和排列順序之差異，能再細分為不同型態，如：3C、4H、6H，其中英文表示晶體結構型態，數字則表示堆疊的週期排列個數，如圖 2-10 所示[14]。過去本實驗室採用的元件基板材料為藍寶石(Sapphire)，其成本較低因而被廣泛使用於製作元件，以磊晶氮化鎵為例(表 2-2[15])，藍寶石與氮化鎵的晶格常數高度不匹配，磊晶後之結構較為不穩定，而碳化矽雖然成本較高，但其與氮化鎵晶格常數不匹配度低很多，且其具有較高的導熱性，使得製作出來的元件能負

荷更高壓及更高溫的環境，因此本研究之元件基板選用碳化矽材料作為基板。

圖 2-10 碳化矽常見的原子堆疊結構[14]

表 2-2 砂基板、碳化矽基板與藍寶石基板與氮化鎗磊晶之比較[15]

| Substrate | Lattice mismatch | Epilayer crystal quality | Thermal conductivity | Large wafer size | Cost |

|-----------|------------------|--------------------------|----------------------|------------------|------|

| GaN       | 0%               | ✓✓                       | Δ                    | ✗                | ✗    |

| Sapphire  | 13.6%            | Δ                        | ✗                    | Δ                | ✓    |

| SiC       | 3.6%             | ✓                        | ✓                    | Δ                | Δ    |

| Si        | 16.9%            | Δ                        | Δ                    | ✓                | ✓✓   |

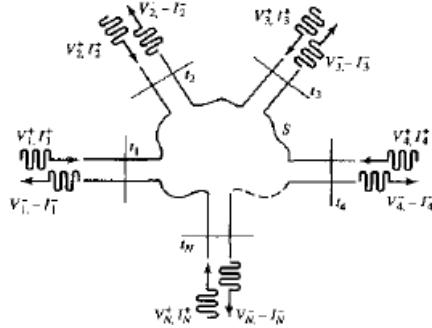

## 2.5 高頻理論

本研究所製作的 T 型閘極目的是用來提升元件的高頻特性，因此需要進行高頻量測來檢測其特性，此章節會介紹高頻量測原理-雙埠網路(Two-port network)及兩個用來判定高頻特性好壞的參數，分別是電流增益截止頻率(current gain cutoff frequency,  $f_T$ )與功率增益截止頻率(power gain cutoff frequency,  $f_{max}$ )。

### 2.5.1 雙埠網路(Two-port network)

雙埠網路是一種用來描述與分析待測電路或待測元件行為的電路系統，此系統具有兩個輸入端及兩個輸出端，其中一個輸入端加一個輸出端會形成一個埠。雙埠網路可視為一個「黑盒」，在不考慮其內部行為或特性的情況下，接收來自輸入端的訊號並將其轉換為相應之輸出訊號於輸出端匯出，即獲得不同的特性參數，以此

來描述待測電路或待測元件之特性行為，主要有四種變量可以組成不同特性參數，分別是：輸入電壓( $V_1$ )、輸出電壓( $V_2$ )、輸入電流( $I_1$ )及輸出電流( $I_2$ )，而可描述待測電路或待測元件行為的特性參數有許多種，不過由於這些參數的導出條件是在各種電路在短路及開路時的線性疊加，因此只可用來描述線性電路，以下將介紹常見用來描述分析高頻特性的三種參數，分別是  $Z$  參數、 $Y$  參數與  $S$  參數，其中這些參數之間也有其相應的轉換關係，此章節亦會說明其轉換關係。

#### • $Z$ 參數( $Z$ -parameter)

此參數為阻抗參數，亦稱為開路阻抗參數，原因是在計算此參數時須滿足下式條件  $I_n = 0$  (其中  $n$  表示經過各個端口的輸入電流與輸出電流)。由於此特性參數用來描述阻抗，因此輸出電壓與輸入電流及  $Z$  參數矩陣會滿足以下矩陣方程：

$$[V] = [Z] [I] \quad (\text{式 2-7})$$

這些參數矩陣皆為方陣，其大小取決於為採用的是  $N$  埠網路，本研究用的是雙埠網路，因此其矩陣大小為  $2 \times 2$ ，並可表示成下列矩陣方程：

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} Z_{11} & Z_{12} \\ Z_{21} & Z_{22} \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix} \quad (\text{式 2-8})$$

再將此矩陣方程展開成下列方程組：

$$\begin{cases} V_1 = Z_{11}I_1 + Z_{12}I_2 \\ V_2 = Z_{21}I_1 + Z_{22}I_2 \end{cases} \quad (\text{式 2-9})$$

最後為了導出各個  $Z$  參數，需假設其中一端為開路，表示此開路端的訊號不會造成額外的散射或穿透，滿足條件後即可獲得各個  $Z$  參數，如下所示：

$$\begin{cases} Z_{11} = \frac{V_1}{I_1} | I_2=0 \\ Z_{12} = \frac{V_1}{I_2} | I_1=0 \\ Z_{21} = \frac{V_2}{I_1} | I_2=0 \\ Z_{22} = \frac{V_2}{I_2} | I_1=0 \end{cases} \quad (\text{式 2-10})$$

#### • $Y$ 參數( $Y$ -parameter)

此參數為導納參數，亦稱為短路導納參數，原因是在計算此參數時須滿足下式的條件： $V_n = 0$  (其中  $n$  表示經過各個端口的輸入電壓與輸出電壓)。由於此特性參數用來描述導納，因此輸出電流與輸入電壓及  $Y$  參數矩陣會滿足以下矩陣方程：

$$[I] = [Y] [V] \quad (\text{式 2-11})$$

由於採用的是雙埠網路，因此其矩陣大小為  $2 \times 2$ ，並可表示成下列矩陣方程：

$$\begin{bmatrix} I_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} Y_{11} & Y_{12} \\ Y_{21} & Y_{22} \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix} \quad (\text{式 2-12})$$

再將此矩陣方程展開成下列方程組：

$$\begin{cases} I_1 = Y_{11}V_1 + Y_{12}V_2 \\ I_2 = Y_{21}V_1 + Y_{22}V_2 \end{cases} \quad (式 2-13)$$

最後為了導出各個 Y 參數，需假設其中一端為短路，表示此短路端的訊號不會造成額外的散射或穿透，滿足條件後即可獲得各個 Y 參數，如下所示：

$$\begin{cases} Y_{11} = \frac{I_1}{V_1} | V_2=0 \\ Y_{12} = \frac{I_1}{V_2} | V_1=0 \\ Y_{21} = \frac{I_2}{V_1} | V_2=0 \\ Y_{22} = \frac{I_2}{V_2} | V_1=0 \end{cases} \quad (式 2-14)$$

#### • S 參數(S-parameter)

上述兩種特性參數皆由經過埠的電壓及電流所定義而得，而 S 參數則是由埠的反射波來定義，因此這個特性參數是用來描述待測電路或待測元件的訊號散射和傳輸特性，且會滿足下列矩陣方程：

$$\begin{cases} [V^-] = [S] [V^+] \\ [I^-] = [S] [I^+] \end{cases} \quad (式 2-15)$$

負號表示訊號的反射波，正號表示的是訊號的入射波，由於採用的是雙埠網路，因此其矩陣大小為  $2 \times 2$ ，其中以 a 表示經過埠之訊號的入射波，而 b 表示經過埠之訊號的反射波並以下列矩陣方程表示：

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix} \quad (式 2-16)$$

再將此矩陣方程展開成下列方程組：

$$\begin{cases} b_1 = S_{11}a_1 + S_{12}a_2 \\ b_2 = S_{21}a_1 + S_{22}a_2 \end{cases} \quad (式 2-17)$$

最後為了導出各個 Z 參數，需假設其中一端為匹配，表示此匹配端的訊號不會造成額外的散射或穿透，滿足條件後即可獲得各個 Z 參數，如下所示：

$$\begin{cases} S_{11} = \frac{b_1}{a_1} | a_2=0 \\ S_{12} = \frac{b_1}{a_2} | a_1=0 \\ S_{21} = \frac{b_2}{a_1} | a_2=0 \\ S_{22} = \frac{b_2}{a_2} | a_1=0 \end{cases} \quad (式 2-18)$$

得知 S 參數後，可以使我們對待測電路或待測元件能進行更精確的分析，如：

阻抗匹配，並對其進行優化改良，因此需要了解 Z 參數與 Y 參數各自與 S 參數的轉換關係，以便於後續量測分析，以下將以矩陣方程式試著將其轉換關係推導出來：

圖 2-11 N 埠網路示意圖[16]

為了方便計算推導各特性參數之間的轉換關係，需要假設  $Z_n = 1$  (表示各個埠皆為阻抗匹配，不會有額外的訊號散射或穿透影響其他參數的計算)，因此各個埠的電壓及電流數值會相等，即  $V_n = I_n$ ，條件假設成立後即可開始進行各特性參數轉換之推導。

首先由圖 2-11 可知各個埠的總電壓與總電流可由下列方程組表示：

$$\begin{cases} V_n = V_n^+ + V_n^- \dots (1) \\ I_n = I_n^+ - I_n^- \dots (2) \end{cases} \quad (\text{式 2-19})$$

由於  $V_n = I_n$ ，所以(2)可以進一步表示為  $I_n = I_n^+ - I_n^- = V_n^+ - V_n^- \dots (3)$

#### • Z 參數轉 S 參數

將(3)代入 Z 參數的矩陣表示式  $[V] = [Z] [I]$ ，可得下式：

$$[Z][I] = [Z][V^+] - [Z][V^-] = [V] = [V^+] + [V^-] \quad (\text{式 2-20})$$

將式 2-20 進行移項處理後可得：

$$([Z] + [U])[V^-] = ([Z] - [U])[V^+] \quad (\text{式 2-21})$$

其中  $[U]$  為單位矩陣，此時再將式 2-21 與 S 參數的矩陣表示式  $[V^-] = [S][V^+]$  相比較並進行移項處理即可獲得 Z 參數與 S 參數的關係：

$$[S] = ([Z] + [U])^{-1}([Z] - [U]) \quad (\text{式 2-22})$$

#### • Y 參數轉 S 參數

同理，將式 2-19 的(1)代入 Y 參數的矩陣表示式  $[I] = [Y] [V]$ ，可得下式：

$$[Y][V] = [Y][V^+] + [Y][V^-] = [I] = [V^+] - [V^-] \quad (\text{式 2-23})$$

將式 2-20 進行移項處理後可得：

$$([Y] - [U])[V^+] = -([Y] + [U])[V^-] \quad (\text{式 2-24})$$

其中  $[U]$  為單位矩陣，此時再將式 2-21 與 S 參數的矩陣表示式  $[V^-] = [S] [V^+]$  相比較並進行移項處理即可獲得 Z 參數與 S 參數的關係：

$$[S] = ([Y] + [U])^{-1}([U] - [Y]) \quad (\text{式 2-25})$$

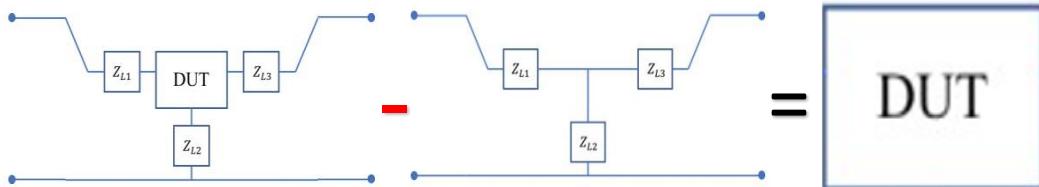

## 2.5.2 開路短路襯墊去嵌化(open short pad de-embedding)

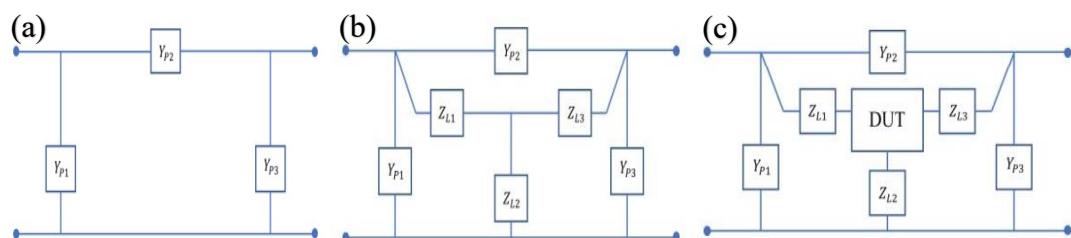

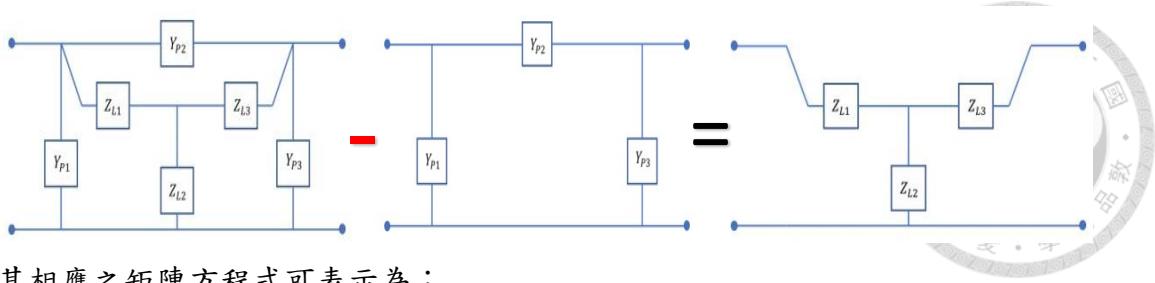

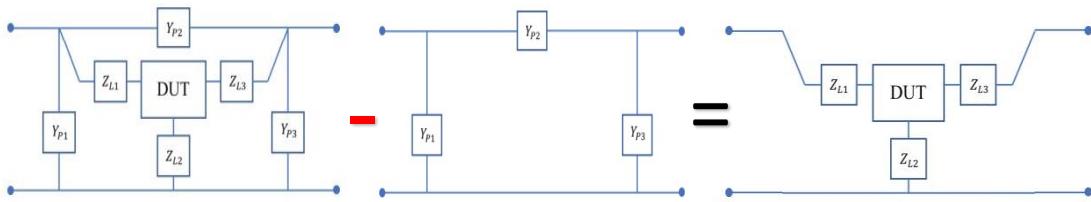

於高頻量測時，需考慮金屬襯墊的寄生參數，包含並聯及串聯阻抗，因此有人提出開路短路襯墊去嵌化(open short pad de-embedding)，藉由設計三種不同金屬襯墊並將其互相進行去嵌化，以此來獲得待測電路或待測元件更為精準的高頻特性參數。三種金屬襯墊之設計如圖 2-12 所示且其相應之電路模型如圖 2-13 所示[17]：

圖 2-12 開路襯墊(左)、短路襯墊(中)、待測元件(右)

圖 2-13 (a)開路襯墊模型 (b)短路襯墊模型 (c)待測元件襯墊模型[17]

接著利用示意圖及相應之矩陣方程式來推倒獲得待測元件的高頻特性參數，首先將短路襯墊模型進行開路襯墊去嵌化：

其相應之矩陣方程式可表示為：

$$[Y]_{short} - [Y]_{open} = [Z]_{short}^{-1} \quad (\text{式 2-26})$$

接著再將待測元件襯墊電路進行開路襯墊去嵌化：

其相應之矩陣方程式可表示為：

$$[Y]_{measurement} - [Y]_{open} = [Z]_{measurement}^{-1} \quad (\text{式 2-27})$$

最後將式 2-27 與式 2-26 相減即可獲得待測元件之高頻特性參數：

其相應之矩陣方程式可表示為：

$$([Y]_{measurement} - [Y]_{open})^{-1} - ([Y]_{short} - [Y]_{open})^{-1} = [Z]_{DUT} \quad (\text{式 2-28})$$

其中  $[Y]_{measurement}$  為待測元件襯墊的 Y 參數， $[Y]_{open}$  為開路襯墊的 Y 參數， $[Y]_{short}$  為短路襯墊之 Y 參數， $[Z]_{DUT}$  為元件本質 Z 參數， $[Z]_{short}^{-1}$  為短路襯墊進行開路去嵌化之後剩餘之 Z 參數， $[Z]_{measurement}^{-1}$  為待測元件襯墊進行開路去嵌化之後剩餘之 Z 參數。由式 2-28 與式 2-21 即可獲得待測元件的本質 S 參數 ( $[Z]_{DUT} \Leftrightarrow [S]_{DUT}$ )。

### 2.5.3 電流增益截止頻率(current gain cutoff frequency, $f_T$ )

其定義為元件輸出端短路時，電流增益( $h21$ )會隨著頻率上升而逐漸下降，

當其值降至 1 或增益為 0 dB 時，此時的頻率即為電流增益截止頻率( $f_T$ )，公式如下所示：

$$h_{21} = \frac{-2S_{21}}{(1-S_{11})(1+S_{22})+S_{12}S_{21}} \quad (式 2-29)$$

### 2.5.4 功率增益截止頻率(power gain cutoff frequency, $f_{max}$ )

當元件的輸入端與輸出端皆為阻抗匹配時，可達到最大有效增益(Maximum Available Gain, MAG)，其公式如下所示：

$$G_{a\_MAX} = \frac{|S_{21}|}{|S_{12}|} (K - \sqrt{K^2 - 1}) \quad (式 2-30)$$

其中  $K$  為穩定係數(Stability factor)，若  $K$  大於 1 則表示此時原件為無條件穩定；反之，若  $K$  小於 1 則表示此件為有條件穩定，如果此時元件輸入端及輸出端沒有達到匹配，會使得元件容易出現震盪，其公式如下所示：

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 - |S_{11}S_{22} - S_{12}S_{21}|^2}{2|S_{12}S_{21}|^2} \quad (式 2-31)$$

而功率增益截止頻率( $f_{max}$ )的定義為當頻率增加時，最大有效增益(MAG)降為 1 或增益為 0 dB 時的頻率即為所求。

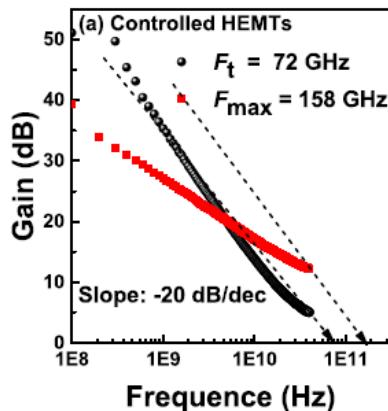

圖 2-14  $f_T$  與  $f_{max}$  量測結果示意圖[18]

### 第三章 實驗儀器介紹

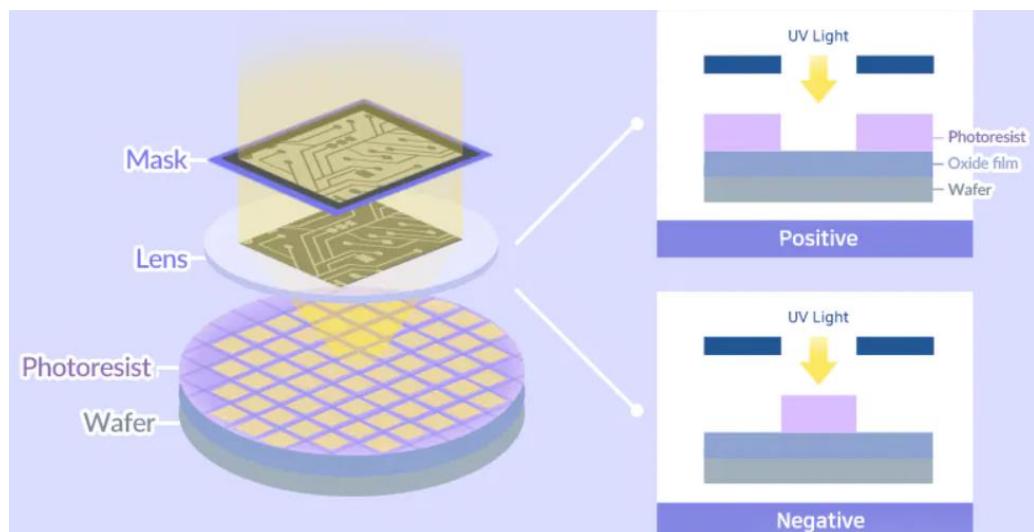

#### 3.1 微影技術(Lithography)

微影技術在半導體製程中採用易於與光反應的化學物質-光阻(photoresist)與光進行交互作用來達成定義元件圖形之目的，因應不同的曝光方式區分為兩種，分別是光學微影技術(Optical Lithography)與電子束微影技術(E-beam Lithography)。

光學微影技術需要先設計好定義圖形之光罩，其中光罩的圖形區又區分成金屬區與非金屬區，如圖 3-1[19]所示。金屬區的目的是阻擋光通過，使被金屬區遮擋住的光阻不會與光進行化學反應，因此在顯影過後會留下金屬區的圖形；反之，非金屬區的光阻會與光產生交互作用，使得此區光阻在顯影過程中會被溶解帶離樣品。由於光學微影技術的圖形定義是用光來達成，而此光源的波長是固定的，因此當元件圖形隨尺寸縮小時，會有當光源通過圖形時產生繞射現象進而造成圖形曝光後不夠銳利的問題出現，為解決此問題來製作更微縮的圖形尺寸，解析度是一個用來參考的指標，而解析度的公式可以根據瑞里準則(Rayleigh Criterion)來獲得，如式 3-1 所示：

$$R = K \frac{\lambda}{NA} \quad (式 3-1)$$

其中  $R$  為解析角度(通常以弧度表示)、 $K$  為系統常數、 $\lambda$  為光源波長、 $NA$  為數值孔徑。解析角度  $R$  越小則解析度越高，由此可知當光源波長越小時會得到較佳的解析度，因此可以採用波長更小的光源來進行微影用以改善圖形曝光後不夠銳利的問題，然而常用於光學微影技術的汞燈曝光機，其最佳解析度為 0.25 微米，已不足以應用於奈米等級的圖形尺寸，所以採用電子束微影技術來達成奈米尺寸圖形之微影。

本實驗室的電子束微影技術使用的是 ELS-7000 機台，將加速電壓設定於 100kv 下操作，並利用場效應(Field Emission)與熱電子(Thermionic)來產生電子

束，其波長約為  $1.2 \times 10^{-12} \text{m}$ ，而汞燈的波長約為  $3 \sim 4 \times 10^{-9} \text{m}$ ，因此可以獲得比汞燈曝光機更佳的解析度，也更利於製作奈米尺寸的圖形。此 ELS-7000 機台的系統包含高真空系統、用以供應電子的電子槍(Electron Gun)、用來控制電子束聚焦的電磁透鏡組(Condenser Lens)與用來輸入圖檔且連接至機台的電腦。電子束微影技術需注意樣品導電度，若過低會造成電荷累積進而影響曝光品質，不過此微影技術不需準備光罩，而是可以利用產生的高能量電子束直接在塗好光阻的樣品上繪製出元件圖形，如圖 3-2[20]所示。

圖 3-1 光學微影技術之曝光示意圖[19]

圖 3-2 電子束微影技術之曝光示意圖[20]

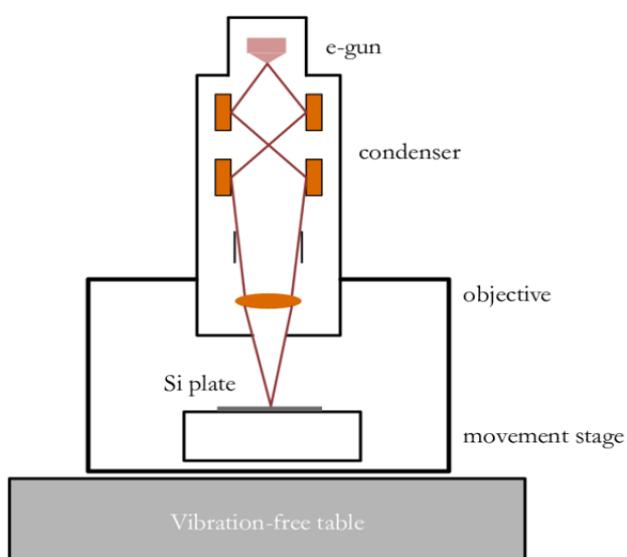

## 3.2 電子束蒸鍍機(Electron Beam Evaporator, E-gun)

為了達成歐姆接觸、蕭特基接觸及製作成連結用的導線，需要在半導體元件的電極端沉積金屬，沉積的方式分為化學氣相沉積(Chemical Vapor Deposition, CVD)與物理氣相沉積(Physical Vapor Deposition, PVD)兩種，其中 CVD 是利用化學反應在樣品表面沉積金屬塗層，通常在高溫和高真空條件下，將金屬前驅體氣體與反應氣體引入反應室，進行氣相反應生成金屬沉積物；PVD 包括蒸鍍(Evaporation)和濺鍍(Sputtering)，蒸鍍是將金屬靶材加熱到高溫，使其蒸發並沉積在樣品上，而濺鍍則是通過將金屬靶材置於離子輔助的高真空中，利用離子轟擊使其從靶材表面解離並沉積在樣品上，在半導體製程中常用的方式是物理氣相沉積的蒸鍍法，而蒸鍍的方式又分成熱蒸鍍法(Thermal Evaporator)與電子束蒸鍍法(Electron Beam Evaporator)，E-gun 即為後者的方式，首先加熱鎢絲使其激發並游離出電子，再利用環形線圈所形成的磁場控制電子束的方向，使電子束集中於金屬靶材上進行加熱讓金屬呈現熔融態，最後蒸發並沉積於樣品表面，如圖 3-3 所示[21]。本研究在實驗過程中皆操作於高真空狀態(約  $4 \times 10^{-5}$  Torr)，以避免蒸鍍時金屬靶材氧化造成蒸鍍出的金屬品質下降，且在蒸鍍過程中，可以藉由膜厚偵測器偵測當下的鍍率及已沉積之金屬厚度，達到對沉積速度與蒸鍍品質之控管，避免沉積速度過快造成厚度不均勻或晶格結構不穩定。

圖 3-3 電子束蒸鍍機系統[21]

### 3.3 快速升溫熱退火(Rapid Thermal Anneal, RTA)

經過蒸鍍後金屬沉積在樣品的元件處，為了在金屬及半導體的接面處形成歐姆接觸，需要利用快速升溫熱退火製程，藉由通入惰性氣體進腔體，如：氮氣，不僅不易與元件產生反應，也能減少元件與氧氣或其他雜質的接觸，避免元件材料氧化或被污染，將樣品於短時間內快速升溫，升溫至目標溫度後將其置於此溫度一段時間，促使金屬及半導體材料間的原子得以進行晶格結構重新排列與修復，強化金屬與半導體材料接面處進而形成較優的歐姆接觸，完成保溫後系統會快速冷卻，防止在退火過程中再次產生缺陷造成晶格結構不穩。

### 3.4 反應式離子蝕刻機 (Reactive Ion Etching, RIE)

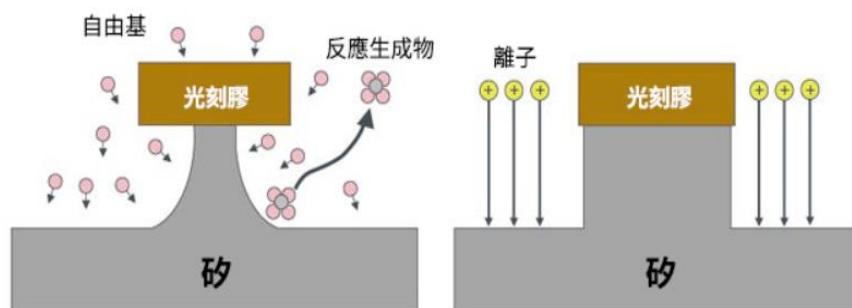

蝕刻製程分為兩類，分別是濕式蝕刻(Wet Etching)與乾式蝕刻(Dry Etching)，濕式蝕刻會將樣品放置於化學溶液中，使材料與化學溶液產生反應藉此達成蝕刻；乾式蝕刻又分成化學蝕刻、物理蝕刻與反應式離子蝕刻，化學蝕刻利用電漿激發蝕刻氣體離子，使其擴散並與樣品的待蝕刻部分產生反應，最後藉由機台的抽氣系統帶離樣品達成蝕刻，能達到等向性蝕刻且具有較高的選擇比；物理蝕刻則是利用離子對樣品表面進行轟擊，也因此易造成樣品表面被破壞產生缺陷，此種蝕刻方式具備高度非等向性及低選擇比；反應式離子蝕刻將上述兩種蝕刻方式結合，利用電漿激發蝕刻氣體離子，並與樣品產生化學反應，再藉由離子物理轟擊，加速破壞鍵結及幫助剝離待蝕刻物質，在半導體製程中也被廣泛使用來達成蝕刻的目的，如圖 3-4 所示[6]。

圖 3-4 RIE 系統[6]

### 3.5 感應耦合電漿反應式離子蝕刻機 (Inductively Coupled Plasma Reactive Ion Etching, ICP-RIE)

感應耦合電漿反應式離子蝕刻 (Inductively Coupled Plasma) 屬於反應式離子蝕刻的一種，此蝕刻方式與反應式離子蝕刻相異處在於後者是利用高頻電場將蝕刻氣體離子化去進行蝕刻作用，而前者則是透過施加高頻電場及射頻功率產生電漿耦合之等離子體，再利用電感耦合的能量將蝕刻氣體離子化，並藉由電場加速離子撞擊樣品表面進行蝕刻，如圖 3-5 所示[22]，且由於離子的能量較高及高度非等向性，使其能達成垂直的非等向性蝕刻。此外，透過調整不同種的反應氣體和比例，從而實現高選擇比的蝕刻，避免損害其他樣品材料。

圖 3-5 ICP-RIE 系統[22]

圖 3-6 (左)等向性蝕刻 (右)非等向性蝕刻[23]

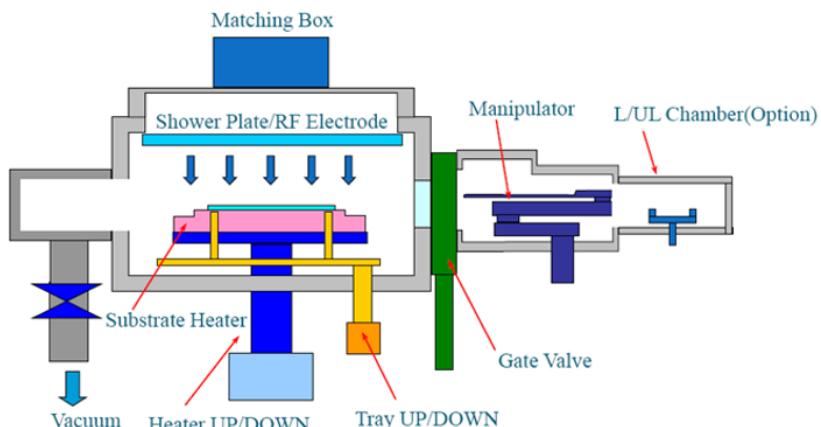

## 3.6 電漿輔助化學氣相沉積(Plasma-Enhanced Chemical Vapor Deposition, PECVD)

沉積方式主要分為物理氣相沉積(Physical Vapor Deposition, PVD)及化學氣相沉積(Chemical Vapor Deposition, CVD)兩種，於 3.2 章中已有兩個方式的原理介紹，這章節將不再贅述，其中 CVD 主要被應用在高純度固態材料的成長，而電漿輔助化學氣相沉積(Plasma-Enhanced Chemical Vapor Deposition, PECVD)即屬於 CVD 的一種。PECVD 操作時會先將蝕刻室內的氣體壓力調整到適當的範圍，並於蝕刻室施加高頻電場使其產生電漿，從而形成等離子體，其中等離子體中的電子會因為高頻電場的激發而能量增加，這些高能量的電子會碰撞並激發蝕刻氣體分子，將它們轉化為活性種類並於樣品表面進行化學反應，而在表面吸附的過程中，活性種類和蝕刻氣體分子會於樣品表面結合，形成具揮發性的中間產物並生成薄膜，且中間產物會持續在樣品表面反應和結合，進而形成沉積層，並隨時間增加而增厚，如圖 3-7 所示[24]，其中沉積層的成長速率會受到沉積氣體濃度、沉積溫度、沉積時間和等離子體密度等參數的影響，且可以通過調整蝕刻氣體的種類及比例、高頻功率、氣體壓力和溫度等參數來控制薄膜的品質。此外，由於電漿會助長電子撞擊氣體分子來提高活化能，因此反應所需之熱預算(Thermal Budget)能被有效降低。基於此法具備較高的沉積速率、能在較低溫中操作且沉積之薄膜品質較優等優點而被廣泛使用。

圖 3-7 PECVD 系統[24]

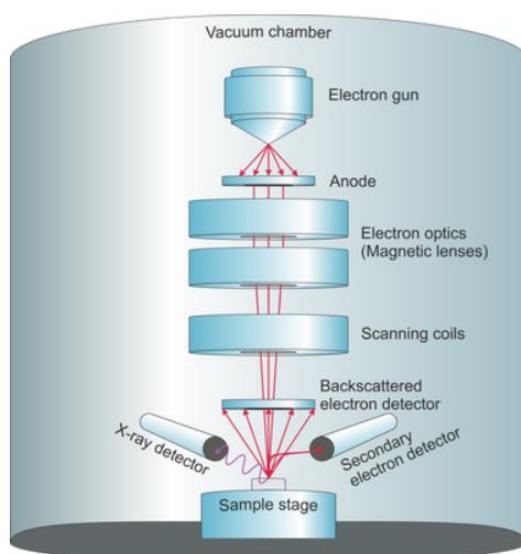

## 3.7 掃描式電子顯微鏡(Scanning Electron Microscope, SEM)

傳統的光學顯微鏡使用可見光作為光源，透過光學透鏡系統對光進行聚焦及放大，且利用這也導致光的穿透或反射來觀察樣品，這也導致光學顯微鏡的解析度會被光的波長所侷限，而半導體製程中的元件大多為微米、奈米等級，使用光學顯微鏡會沒辦法清楚觀察樣品圖形，因此採用以電子束取代可見光源的掃描式電子顯微鏡(Scanning Electron Microscope, SEM)即可解決光學顯微鏡的光繞射極限之問題。SEM 的主要組成架構為電子槍(Electron Gun)、電磁透鏡系統(Electromagnetic Lens System)與成像系統(Imaging System)，藉由電子槍發射電子束，並利用高壓電場加速射入電磁透鏡系統進行控制和聚焦，被聚焦縮小過後的電子束接著會投射在待觀察的樣品上，待測樣品被電子束擊中後會激發多種訊號，如：二次電子(Secondary Electron)、背向散射電子(Backscattered Electron)……等，偵測系統主要掃描及辨識二次電子及背向散射電子的訊號，經過分析處理並產生同步影像，即可觀察微米、奈米等級尺寸之元件圖形，如圖 3-8[25]所示，其中成像的解析度除了會受所偵測到的訊號強度影響，待測樣品本身的基板導電度也會影響成像結果，基板的導電度越高則成像結果越清晰；反之，基板的導電度越低則越容易於表面累積電荷，進而影響成像品質。

圖 3-8 SEM 系統[25]

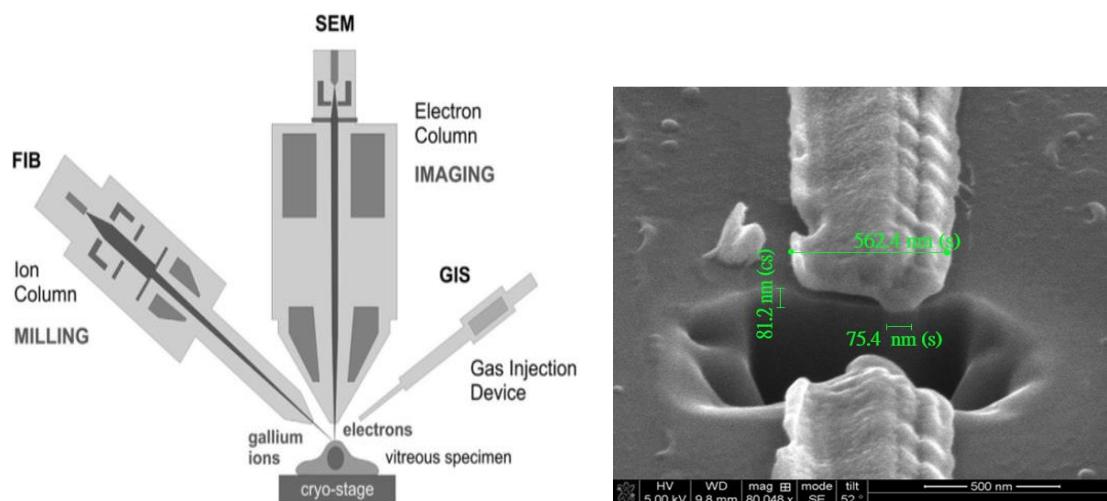

### 3.8 聚焦離子束顯微鏡(Focused Ion Beam, FIB)

聚焦離子束顯微鏡(Focused Ion Beam, FIB)主要組成架構為離子源(Ion Source)、電磁透鏡系統(Electromagnetic Lens System)與成像系統(Imaging System)，利用離子源發射高能量離子束進電磁透鏡系統，用以進行控制及聚焦離子束，接著投射至待測樣品上，此時會像 SEM 一樣激發多種訊號，偵測系統再對這些訊號進行分析並產生即時影像，如圖 3-9 所示[26]，而本研究中也利用 FIB 的離子束對元件的閘極進行切割確認 T 型閘極的形狀及尺寸，如圖 3-10 所示。

聚焦離子束顯微鏡具有高空間解析度(能夠觀察奈米等級的結構且獲得高精度的成像)、多功能性(除了高解析度成像，利用離子束的高能量和高定位精度可以對待測物件進行細微切割、沉積、離子注入和探針測量等操作)、低損傷檢測(由於使用低電流和高能量的離子束，相較於電子束或光學顯微鏡等其他成像技術，對樣品產生的損傷較小)與三維成像(通過切割可以獲得高解析度的三維圖像，包含橫截面圖及體積等資訊，可以更全面的分析所製作出的樣品)等優點，因此在奈米尺寸等級的元件觀察量測及生物學研究中被廣泛使用。

圖 3-9 FIB 系統[26]

圖 3-10 以離子束切割之 T 型閘極

## 3.9 網路分析儀(Network Analyzer)

我們需要 S-parameter 來進行高頻量測分析，因此會使用網路分析儀 (Network Analyzer) 來測得 S-parameter，其常用於測量電路或元件的電性和頻率響應，也常被用來進行分析和測量射頻和微波電路的傳輸特性、通訊系統、等。

網路分析儀的基本原理是通過將待測試電路或元件樣品連接儀器，將特定信號輸入至待測試物件中，即可量測並輸出待測試物件具備的電性和頻域表現，如圖 3-11 所示[27]，可以獲得包含傳輸增益(Transmission Gain)、傳輸相位(Transmission Phase)、頻率響應(Frequency response)、反射損耗(Reflection loss)等特性資訊。網路分析儀可以進行不同模式的分析測量，如：時域分析模式與頻域分析模式，其中時域分析模式可以觀察出信號與時間的關係，而頻域分析模式則用來觀察信號在頻率上的表現，利用這些不同模式所測得之結果可以幫助我們更快速理解和評估電路或元件的性能。

圖 3-11 網路分析儀運作原理[27]

圖 3-12 網路分析儀[27]

## 第四章 實驗設計與製程

### 4.1 文獻回顧

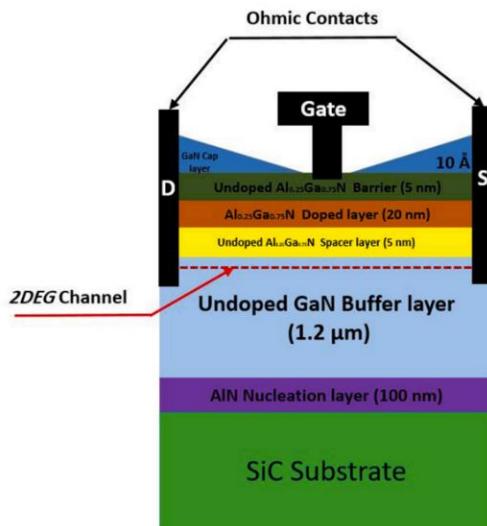

#### 4.1.1 縮小閘極線寬( $L_g$ )用以提升元件特性[28]

該參考文獻中，當元件的通道長度不變時，藉由閘極長度的縮短與在汲極和源極多加一層  $10\text{\AA}$  的保護層，如圖 4-1 所示，使元件之通道電阻降低，進而提升元件的轉導值( $g_m$ )與最大飽和電流( $I_{dmax}$ )。該參考文獻設計且比較了五組不同閘極線寬( $L_g$ )的 HEMT 元件，分別為 2 微米、1 微米、0.5 微米、0.25 微米及 0.15 微米，於量測結果中可發現當閘極線寬( $L_g$ )越小時，則其表現之特性越好，元件的轉導值( $g_m$ )會從  $228.6(\text{mA/mm})$  提升至  $259.8(\text{mA/mm})$ ，且最大飽和電流( $I_{dmax}$ )也從  $1.17(\text{A/mm})$  提升至  $1.36(\text{A/mm})$ ，如圖 4-2 所示。

圖 4-1 文獻元件結構[28]

圖 4-2 文獻元件量測結果[28]

#### 4.1.2 T型閘極[3, 29, 30]

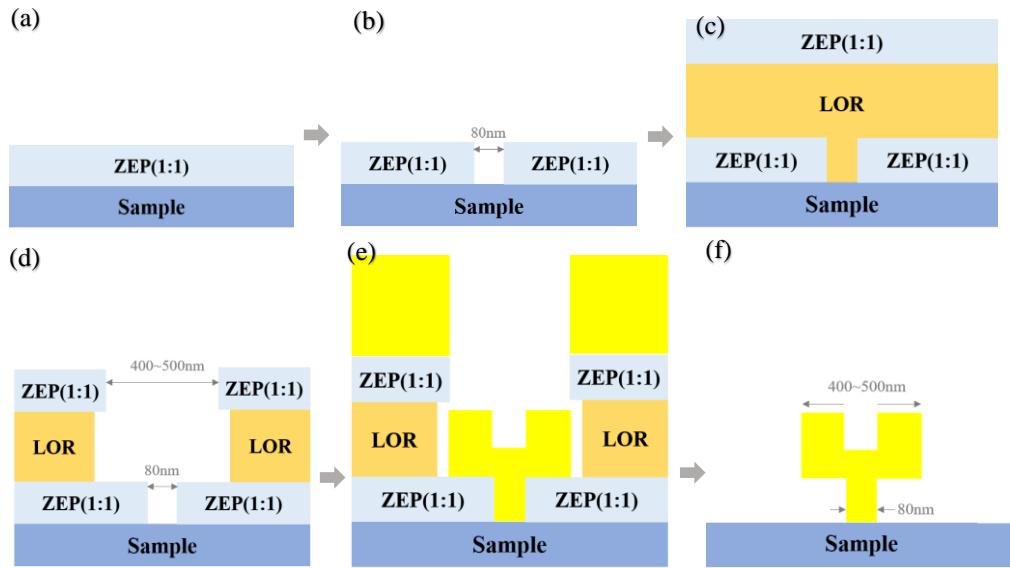

高電子遷移率電晶體(HEMT)因其氮化鋁鎵及氮化鎵異質結構所生成的二維電子氣(2DEG)具備高載子傳輸速度及高載子濃度，因此適合作為高頻及高功率元件。於高頻領域中，為了使高電子遷移率電晶體能夠有更好的電流增益截止頻率( $f_T$ )與功率增益截止頻率( $f_{max}$ )表現，從傳統的線閘極(Line gate)進而改良開發出T型閘極(T-gate)，而使用多層光阻來定義T型閘極形狀的做法即是常見的製作T型閘極方法之一，其原理是利用不同光阻有不同的光敏感度或是對不同層的相同光阻使用不同曝光劑量(Dose time)，進而顯影出不同線寬之圖形以此達成T型的形狀定義。文獻[32]於2005年即用PMMA/LOR/UVIII製作出下層閘極線寬(gate length of T-foot,  $L_{fg}$ )為30奈米的HEMT元件，如圖4-3(左1)所示；文獻[33]於2020年提出了兩組以ZEP520A/PMGI/ZEP520A製作的T型閘極HEMT元件，其下層閘極線寬( $L_{fg}$ )皆為120奈米而各自的閘極高度為165奈米與250奈米，並各自具有 $f_T$ 為240GHz、 $f_{max}$ 為370GHz與 $f_T$ 為270GHz、 $f_{max}$ 為460GHz的表現，如圖4-3(左2)所示；文獻[33]於2023年提出使用PMMA/LOR/CSAR三層光阻製作出下層閘極線寬( $L_{fg}$ )分別為50及100奈米，且上層閘極線寬(gate length of T-head,  $L_{hd}$ )為250~500奈米的六組T型閘極元件，如圖4-3(右1)所示。根據參考文獻可知，三層光阻法用來製作T型閘極是常見且同時能製作出小線寬閘極的方法，而本研究使用ZEP520A(1:1)/LOR/ZEP520A(1:1)來製作T型閘極HEMT元件，於第五章介紹本研究之成果圖。

圖4-3 各參考文獻之T型閘極成品圖(左1[3]、左2[29]、右1[30])

## 4.2 元件設計

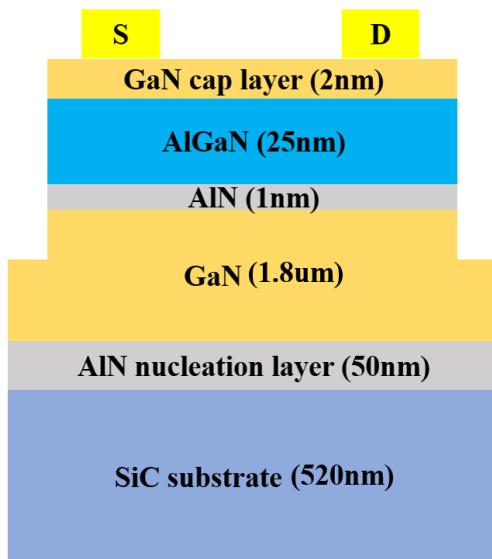

### 4.2.1 元件基板磊晶結構及特性

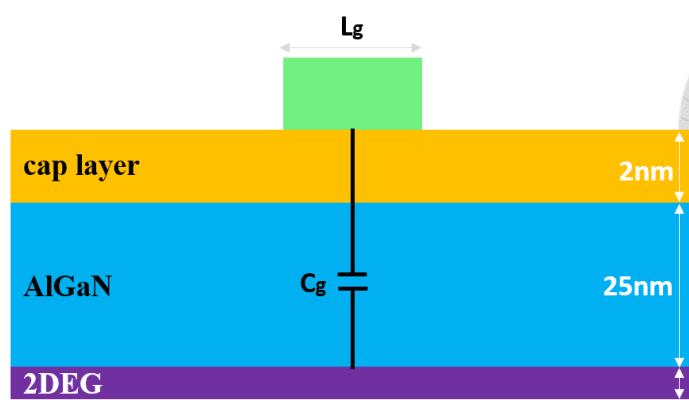

本研究採用之四吋晶片，將其送至廠商雷射切割成 1.2cm x 1.2cm 的試片。該晶圓的基板材料為碳化矽(SiC)，利用有機金屬化學氣相沉積(Metal-organic Chemical Vapor Deposition, MOCVD)往上進行磊晶，首先於碳化矽基板上沉積 50 奈米的氮化鋁(AlN)作為核層(Nucleation Layer)，再往上成長 1.8 微米未經參雜的氮化鎗(GaN)，接著沉積一層氮化鋁的空間層(Spacing Layer)，此層的用意為增加氮化鋁鎗(AlGaN)與氮化鎗(GaN)形成的異質結構間的載子穩定度，所以選擇具有較高能障的氮化鋁來作為此層材料。接著成長一層 25 奈米的氮化鋁鎗(Al<sub>0.25</sub>Ga<sub>0.75</sub>N)作為障蔽層(Barrier Layer)，最後沉積一層 2 奈米的氮化鎗作為覆蓋層，目的是為了避免因氮化鋁鎗與空氣接觸而氧化導致元件性能不佳，整體元件基板磊晶結構如圖 4-4 所示。

圖 4-4 元件基板磊晶結構

### 4.2.2 光罩設計

本研究根據不同道的 T 型閘極氮化鋁鎗/氮化鎗高電子遷移率電晶體製程，利用 Autocad 此軟體進行元件尺寸及圖形的設計，會用到光罩的製程大致可分為

六道製程，分別是定義電子束角標與歐姆接觸(E-beam alignment mark and Ohmic contact)、元件隔離(Mesa Isolation)、定義 T 型閘極與蕭特基接觸(T-gate and Schottky contact)、沉積鈍化層(Passivation)、電極金屬洞通孔(Via hole)及製作金屬襯墊(Metal pad)，於下個小章節 4.3 中會有各道製程的詳細說明。角標的圖形設計成十字型，如圖 4-5(a)所示，其目的是為了確保角標正中心沒有重疊以免曝光顯影後的角標過大影響後續二次對準的精準度；為定義出 T 型閘極(T-gate)，將其分為上下層閘極(T-head and T-foot)且採用 bottom-up 的製作方式進行實驗，並將上下層閘極依比例設計為 5~6:1 左右，下層閘極(T-foot)之線寬( $L_{fg}$ )設計為 80 奈米，上層閘極(T-head)之線寬( $L_{hg}$ )設計為 400~500 奈米。

圖 4-5 Autocad 元件設計圖 (a)角標 (b)直流元件 (c)高頻元件

圖 4-6 光罩設計圖

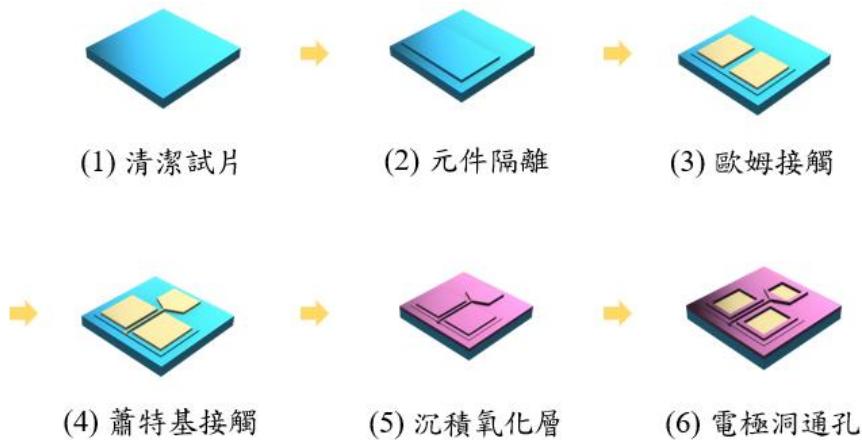

## 4.3 元件製程

本章節會說明本研究的 T 型閘極高電子遷移率電晶體元件之製作流程，大致分為以下七個部分：

1. 試片表面清潔(Clean)

2. 定義電子束角標與歐姆接觸(E-beam alignment mark and Ohmic contact)

3. 元件隔離(Mesa Isolation)

4. 定義 T 型閘極與蕭特基接觸(T-gate and Schottky contact)

5. 沉積鈍化層(Passivation)

6. 電極金屬洞通孔(Via hole)

7. 製作金屬襯墊(Metal pad)

接下來會依實驗流程步驟詳細介紹。

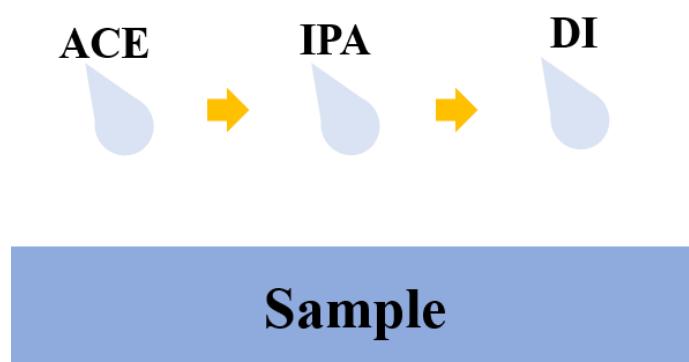

### 1. 試片表面清潔(Clean)：

為了保持實驗元件的製作品質，有效清潔試片表面的灰塵及雜質即為重要的第一步驟，本實驗將實驗之試片依序放入丙酮(Acetone, ACE)、異丙醇(Isopropyl Alcohol, IPA)及去離子水(DI water)的溶液中，並利用超音波震洗器各別震洗 5 分鐘，接著使用氮氣槍吹除試片上的多餘水氣，最後再將試片置於 110°C 的烤盤(Hot plate)上烤乾 1 分鐘以此確保試片上無水氣殘留，如圖 4-7 所示。

圖 4-7 Clean 示意圖

### 2. 定義電子束角標與歐姆接觸(E-beam alignment mark and Ohmic contact)：

本實驗中採用實驗室的電子束微影系統(E-beam Lithography)進行電子束角

標及歐姆接觸之定義，分為光阻塗佈(PR Coating)、電子束微影(E-beam Lithography)、顯影(Development)、蒸鍍及掀離金屬(Metal deposition and lift off)、快速升溫熱退火(Rapid Thermal Anneal, RTA)五個步驟。

- (1) 光阻塗佈(PR Coating)：首先將清潔完的乾燥試片放置於光阻旋轉塗佈機(Spin Coater)上，於試片上先滴上第一層光阻 LOR5B，其旋轉塗佈參數為 1000 rpm 初轉 10 秒，接著提升轉速至 4000 rpm 末轉 40 秒，塗佈完成後再靜置於 180°C 的烤盤(Hot plate)烤乾 3 分鐘；LOR5B 烤乾後接著再將試片放置於光阻旋轉塗佈機並塗上第二層光阻 ZEP520A(1:1)，其旋轉塗佈參數為 500 rpm 初轉 5 秒，接著提升轉速至 5000 rpm 末轉 1 分 30 秒，塗佈完成後再靜置於 180°C 的烤盤烤乾 3 分鐘，烤乾的用意為去除光阻內部水分以此增強其鍵結，至此即完成光阻塗佈。

- (2) 電子束微影(E-beam Lithography)：將塗佈好光阻的試片放入 ELS-7000 進行電子束微影，並於電腦中開啟設計好之元件圖檔且依實驗需求設定好適當的曝光劑量(Dose time)，使經過電子束微影系統曝光之圖形尺寸能與設計好之元件圖形尺寸相符，若曝光劑量太少則會造成電子束強度不夠擊穿光阻，造成顯影後圖形不明顯甚至沒有圖形，反之若曝光劑量設定太大，則可能造成曝光後的圖形線寬過大與設計之線寬不符。

- (3) 顯影(Development)：待 ELS-7000 電子束微影系統繪製完成後，會將試片依序放入 ZED-N50 及 MF-319 進行顯影的動作，首先將試片浸入 ZED-N50 顯影液 5 分鐘，將上層 ZEP520A(1:1)光阻顯影，再依序泡入異丙醇(IPA)與去離子水(DI water)去除殘餘的 ZED-N50，並使用氮氣槍吹除表面水氣，接著將試片浸入 MF-319 顯影液中 2 秒用來顯影下層光阻 LOR5B，再泡入去離子水(DI water)去除殘餘 MF-319，並使用氮氣槍吹除殘餘水氣，最後將試片置於 110°C 的烤盤上烤乾 1 分鐘確保無水氣殘留。

- (4) 蒸鍍及掀離金屬(Metal deposition and lift off)：將顯影過後的試片放入電

子束蒸鍍機(E-gun)中，並依序進行四種金屬鈦(Ti)/鋁(Al)/鎳(Ni)/金(Au)的蒸鍍，其各別的蒸鍍厚度為 20/100/40/50 奈米，在蒸鍍過程需仔細調控電子束電流的增加及減少，以免鍍率變化過快影響蒸鍍品質。蒸鍍完成過後，將試片浸入 ZDMAC 中進行金屬掀離，並可以將其置於 60°C 的烤盤及使用滴管輔助掀離，接著將試片依序泡入異丙醇(IPA)與去離子水(DI water)去除殘餘的 ZDMAC，最後使用氮氣槍吹除試片表面的殘餘水氣。

(5) 快速升溫熱退火(Rapid Thermal Anneal, RTA)：將掀離後之試片置於高溫熱退火機台腔體中，並通入氮氣( $N_2$ )避免金屬氧化影響電性表現，將系統升溫到 840°C 且維持於此溫度 120 秒，再待其降溫過後取出試片，即完成定義電子束角標及歐姆接觸的製程，如圖 4-8 所示。

圖 4-8 定義電子束角標及歐姆接觸示意圖

### 3. 元件隔離(Mesa Isolation)：

元件隔離(Mesa Isolation)的目的是確保基板上的各個元件之二維電子氣(2DEG)不會相互影響，進而造成漏電流的生成影響所製作元件的特性，共可分為光阻塗佈(PR Coating)、黃光微影(Lithography)、顯影(Development)、蝕刻(Etching)四個步驟。

(1) 光阻塗佈(PR Coating)：首先將快速熱退火完的試片放置於光阻旋轉塗佈機(Spin Coater)上，於試片上滴上光阻 S1813，其旋轉塗佈參數為 1000 rpm 初轉 10 秒，接著提升轉速至 4000 rpm 末轉 30 秒，塗佈完成後先用沾取丙酮(ACE)的棉棒進行殘餘光阻去邊的動作，確保試片周遭(如：四個角)較厚的光阻被去除利於後續黃光微影的進行，再靜置於 110°C 的烤

盤(Hot plate)烤乾 1 分鐘。

- (2) 黃光微影(Lithography)：將塗佈好 S1813 的試片置於曝光機的載台，並將試片與所設計之光罩進行貼合，若塗佈 S1813 後未先用沾有丙酮(ACE)的棉棒進行去邊，會造成貼合困難導致圖形歪掉，接著以 Soft Contact 模式將試片曝光 20 秒即完成此步驟。

- (3) 顯影(Development)：曝光後將試片取出並浸入 MF-319 顯影液中 14 秒，再泡入去離子水中去除殘餘的 MF-319，接著使用氮氣槍吹除水氣並將試片置於 110°C 的烤盤上烤乾 1 分鐘。

- (4) 蝕刻(Etching)：將顯影過後的試片放入感應耦合電漿反應式離子蝕刻機(ICP-RIE)，並通入蝕刻氣體氯氣( $\text{Cl}_2$ )與三氯化硼( $\text{BCl}_3$ )，將試片的元件周遭蝕刻 120 奈米的深度，蝕刻完成後將試片浸泡於加熱至 90°C 的丙酮中 5 分鐘用以去除光阻 S1813，接著依序泡入異丙醇與去離子水去除丙酮，不過由於進行乾蝕刻時會導致光阻變質，若單用丙酮無法達到完全去除殘餘光阻的作用，因此會再使用反應式離子蝕刻機(RIE)以去除殘餘光阻，至此即完成元件隔離，如圖 4-9 所示。

圖 4-9 元件隔離示意圖

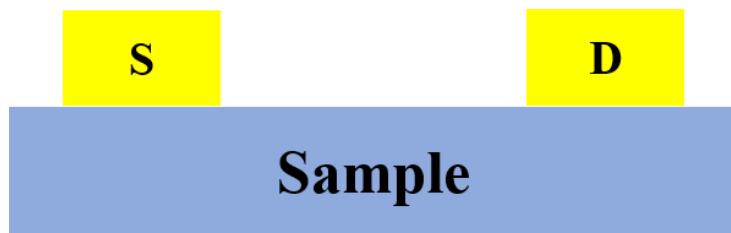

4. 定義 T 型閘極與蕭特基接觸(T-gate and Schottky contact)：

該步驟採用電子束微影技術進行二次對準，使得閘極可以落於汲極與源極中間，若是製作傳統線閘極(Line gate)只需用一層或兩層光阻並使用 ELS-7000 機台即可達成線閘極的圖形定義，而本研究中為了定義 T 型閘極，使用了三層光阻 ZEP520A(1:1)/LOR5B/ZEP520A(1:1)來達成圖形定義，且本研究採用 bottom-up 的製作方式，先定義好下層(T-foot)再製作上層(T-head)，利用上下層使用不同曝光劑量及線寬設計，以此達成 T 型之圖型定義，並於圖形定義完成後進行顯影及金屬蒸鍍製作蕭特基接觸，如圖 4-10 所示。製程總共可分為上下層光阻塗佈(PR Coating)、兩次電子束微影(E-beam Lithography)、兩次顯影(Development)、蒸鍍及掀離金屬(Metal deposition and lift off) 7 個步驟，此道製程之流程如圖 4-11 所示。

圖 4-10 定義 T 型閘極與蕭特基接觸示意圖

- (1) 下層光阻塗佈(T-foot PR Coating)：將元件隔離(Mesa Isolation)完成的試片放置於光阻旋轉塗佈機(Spin Coater)上，於試片上滴上第一層光阻 ZEP520A(1:1)，其旋轉塗佈參數為 500 rpm 初轉 5 秒，接著提升轉速至 5000 rpm 末轉 1 分 30 秒，塗佈完成後再靜置於 180°C 的烤盤烤乾 3 分鐘。

- (2) 電子束微影(E-beam Lithography)：將塗佈好第一層層光阻的試片放入 ELS-7000 進行電子束微影，並於電腦中開啟設計好之元件圖檔且依實驗需求設定好適當的曝光劑量(Dose time)，接著須對準於第一道製程中所製作好的角標(Alignment)，確保下層(T-foot)閘極圖形位置與設計圖檔相同。

(3) 顯影(Development)：繪製完成後，將試片放入 ZED-N50 進行顯影 5 分鐘，再依序泡入異丙醇(IPA)與去離子水(DI water)去除殘餘的 ZED-N50，並使用氮氣槍吹除表面水氣，最後將試片置於 110°C 的烤盤上烤乾 1 分鐘確保無水氣殘留。

(4) 上層光阻塗佈(T-head PR Coating)：此步驟會使用兩層光阻，分別是 LOR5B 與 ZEP520A(1:1)，LOR5B 的用途是墊高，使得在掀離時金屬不會隨著光阻被帶走。首先將顯影完第一層光阻的試片放置於光阻旋轉塗佈機(Spin Coater)上，於試片上滴上第二層光阻 LOR5B，其旋轉塗佈參數為 1000 rpm 初轉 10 秒，接著提升轉速至 4000 rpm 末轉 40 秒，塗佈完成後再靜置於 180°C 的烤盤(Hot plate)烤乾 3 分鐘；LOR5B 烤乾後接著再將試片放置於光阻旋轉塗佈機並塗上第三層光阻 ZEP520A(1:1)，其旋轉塗佈參數為 500 rpm 初轉 5 秒，接著提升轉速至 5000 rpm 末轉 1 分 30 秒，塗佈完成後再靜置於 180°C 的烤盤烤乾 3 分鐘。

(5) 電子束微影(E-beam Lithography)：將塗佈好第二及第三層層光阻的試片放入 ELS-7000 進行電子束微影，並於電腦中開啟設計好之元件圖檔且依實驗需求設定好適當的曝光劑量(Dose time)，接著須對準於第一道製程中所製作好的角標(Alignment)，確保上層(T-foot)閘極圖形位置與設計圖檔相同。

(6) 顯影(Development)：繪製完成後，將試片依序放入 ZED-N50 及 MF-319 進行顯影的動作，首先將試片浸入 ZED-N50 顯影液 5 分鐘，將第三層 ZEP520A(1:1)光阻顯影，再依序泡入異丙醇(IPA)與去離子水(DI water)去除殘餘的 ZED-N50，並使用氮氣槍吹除表面水氣，接著將試片浸入 MF-319 顯影液中 2 秒用來顯影第二層光阻 LOR5B，再泡入去離子水(DI water)去除殘餘 MF-319，並使用氮氣槍吹除殘餘水氣，最後將試片置於 110°C 的烤盤上烤乾 1 分鐘確保無水氣殘留。

(7) 蒸鍍及掀離金屬(Metal deposition and lift off)：將顯影過後的試片放入電子束蒸鍍機(E-gun)中，並依序進行兩種金屬鎳(Ni)/金(Au)的蒸鍍，其各自的蒸鍍厚度為 30/80 奈米，在蒸鍍過程需仔細調控電子束電流的增加及減少，以免鍍率變化過快影響蒸鍍品質。蒸鍍完成過後，將試片浸入 ZDMAC 中進行金屬掀離，並可以將其置於 60°C 的烤盤及使用滴管輔助掀離，接著將試片依序泡入異丙醇(IPA)與去離子水(DI water)去除殘餘的 ZDMAC，最後使用氮氣槍吹除試片表面的殘餘水氣。

圖 4-11 定義 T 型閘極與蕭特基接觸之流程圖 (a)塗佈第一層光阻 (b)曝光及顯影 T-foot (c)塗佈第二、三層光阻 (d)曝光及顯影 T-head (e)鍍金屬 Ni/Au (f)掀離金屬

##### 5. 沉積鈍化層(Passivation)：

鈍化層(Passivation)的目的是保護元件不受外在環境所影響而導致元件特性表現不佳，於本研究中使用電漿輔助化學氣相沉積(PECVD)系統，在定義好 T 型閘極與蕭特基接觸後的元件表面沉積約 250 奈米的 SiN 作為鈍化層，如圖 4-12 所示。

圖 4-12 沉積鈍化層示意圖

#### 6. 電極金屬洞通孔(Via hole)：

元件在鈍化層沉積完成後會處於絕緣狀態，為了利於進行下探針量測，須於電極處(汲極(Drain)、源極(Source)、閘極(Gate))上方將其蝕刻開通。其實驗步驟可分為光阻塗佈(PR Coating)、黃光微影(Lithography)、顯影(Development)、蝕刻(Etching)四個。

(1) 光阻塗佈(PR Coating)：首先將沉積完鈍化層的試片放置於光阻旋轉塗佈機(Spin Coater)上，於試片上滴上光阻 S1813，其旋轉塗佈參數為 1000 rpm 初轉 10 秒，接著提升轉速至 4000 rpm 末轉 30 秒，塗佈完成後先用沾取丙酮(ACE)的棉棒進行殘餘光阻去邊的動作，確保試片周遭(如：四個角)較厚的光阻被去除利於後續黃光微影的進行，再靜置於 110°C 的烤盤(Hot plate)烤乾 1 分鐘。

(2) 黃光微影(Lithography)：利用此步驟定義出欲下針區域之圖型，將塗佈好 S1813 的試片置於曝光機的載台，並將試片與所設計之光罩進行貼合，若塗佈 S1813 後未先用沾有丙酮(ACE)的棉棒進行去邊，會造成貼合困難導致圖形歪掉，接著以 Soft Contact 模式將試片曝光 20 秒即完成此步驟。

(3) 顯影(Development)：曝光後將試片取出並浸入 MF-319 顯影液中 14 秒，再泡入去離子水中去除殘餘的 MF-319，接著使用氮氣槍吹除水氣並將試片置於 110°C 的烤盤上烤乾 1 分鐘。

(4) 蝕刻(Etching)：將顯影過後的試片放入反應式離子蝕刻機(RIE)且通入四

氟化碳( $CF_4$ )用以蝕刻鈍化層的  $SiN$ ，蝕刻完成後將試片浸泡於加熱至  $90^{\circ}C$  的丙酮中 5 分鐘用以去除光阻 S1813，接著依序泡入異丙醇與去離子水去除丙酮，並用氮氣槍吹除水氣即完成電極金屬洞蝕刻，如圖 4-13 所示。

圖 4-13 電極金屬洞通孔示意圖

#### 7. 製作金屬襯墊(Metal pad)：

金屬襯墊(Metal pad)是為了高頻量測下探針所用，分別有開路襯墊(Open pad)、短路襯墊(Short pad)及待測元件襯墊(Device Under Test pad, DUT pad)。本研究使用黃光微影技術來定義各個襯墊之圖型，可分為光阻塗佈(PR Coating)、黃光微影(Lithography)、顯影(Development)、蒸鍍及掀離金屬(Metal deposition and lift off)四個步驟。

(1) 光阻塗佈(PR Coating)：首先將完成通孔(Via)的試片放置於光阻旋轉塗佈機(Spin Coater)上，於試片上滴上第一層光阻 LOR5B，其旋轉塗佈參數為  $1000\text{ rpm}$  初轉 3 秒，接著提升轉速至  $4000\text{ rpm}$  末轉 40 秒，塗佈完成後再靜置於  $180^{\circ}C$  的烤盤烤乾 3 分鐘，接著塗佈第二層光阻 S1813，其旋轉塗佈參數為  $1000\text{ rpm}$  初轉 10 秒，接著提升轉速至  $4000\text{ rpm}$  末轉 30 秒，塗佈完成後先用沾取丙酮(ACE)的棉棒進行殘餘光阻去邊的動作，確保試片周遭(如：四個角)較厚的光阻被去除利於後續黃光微影的進行，再靜置於  $110^{\circ}C$  的烤盤(Hot plate)烤乾 1 分鐘。

(2) 黃光微影(Lithography)：定義出各個襯墊之圖型，將塗佈好兩層光阻的試片置於曝光機的載台，並將試片與所設計之光罩進行貼合，若塗佈 S1813

後未先用沾有丙酮(ACE)的棉棒進行去邊，會造成貼合困難導致圖形歪掉，接著以 Soft Contact 模式將試片曝光 20 秒即完成此步驟。

(3) 顯影(Development)：曝光後將試片取出並浸入 MF-319 顯影液中 18 秒，再泡入去離子水中去除殘餘的 MF-319，接著使用氮氣槍吹除水氣，並使用反應式離子蝕刻機(RIE)通入氧氣( $O_2$ )將殘餘光阻完全去除，最後將試片置於 110°C 的烤盤上烤乾 1 分鐘。

(4) 蒸鍍及掀離金屬(Metal deposition and lift off)：將顯影過後的試片放入電子束蒸鍍機(E-gun)中，並依序進行兩種金屬鈦(Ti)/金(Au)的蒸鍍，其各自的蒸鍍厚度為 15/400 奈米，在蒸鍍過程需仔細調控電子束電流的增加及減少，以免鍍率變化過快影響蒸鍍品質。蒸鍍完成過後，將試片浸入 ZDMAC 中進行金屬掀離，並可以將其置於 60°C 的烤盤及使用滴管輔助掀離，接著將試片依序泡入異丙醇(IPA)與去離子水(DI water)去除殘餘的 ZDMAC，最後使用氮氣槍吹除試片表面的殘餘水氣。至此即完成整套 T 型閘極高電子遷移率電晶體元件之製作流程。

## 第五章 實驗結果與分析

### 5.1 直流量測

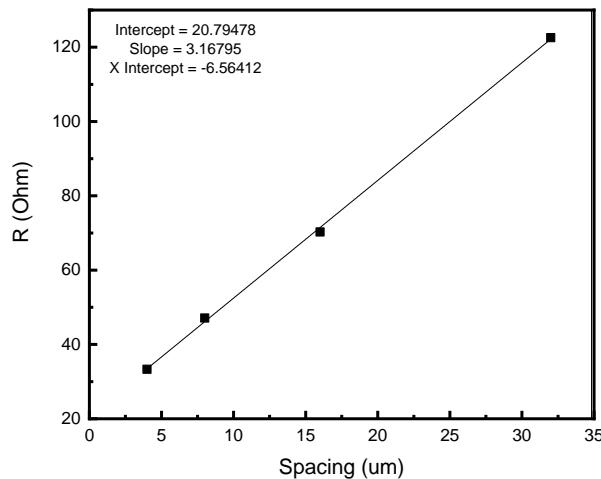

良好的歐姆接觸品質可以改善元件的特性表現，因此在完成整體元件製作前，會在元件完成元件隔離(Mesa isolation)後先進行 TLM 電性量測，確保歐姆接觸的品質，將量測到的接觸電阻  $R_G$  及片電阻  $R_S$  與過去實驗數據相比，其表現相近甚至更低即表示歐姆接觸品質是良好的，再進行後續閘極的製作。本研究的元件進行 TLM 量測之結果如圖 5-1 所示，計算後可得到此元件之接觸電阻  $R_C=1.04 \Omega/\text{mm}$  且片電阻  $R_S=316.795 \Omega/\text{mm}$ 。

圖 5-1 TLM 量測結果

整體元件製作完成後，在直流量測中可以藉由一些參數來判定元件的特性表現，本研究以下列幾個參數來做為直流特性表現之依據：

- **轉導值(Transconductance,  $g_m$ )**

此參數表示輸入端電壓與輸出端電流的轉換能力，當元件的轉導值越大則元件也可達更高的操作速度，其定義如下所示：

$$g_m = \frac{\partial I_D}{\partial V_{GS}} \text{ (mS/mm)}$$

- **臨限電壓(Threshold voltage,  $V_{th}$ )**

當閘極偏壓持續上升時，元件會從截止區進入飽和區，於  $I_D-V_G$  圖中，汲極電流一開始會平緩增加而後會出現一個轉折點，使其急劇上升，此轉折點所對應之閘極電壓極為臨限電壓，表示須外加閘極偏壓至此電壓值以上元件才會導通。除了觀察  $I_D-V_G$  圖來得到臨限電壓，也能藉由最大轉導值所對應之閘極電壓，再將此閘極電壓值對應到汲極電流，並於 x 軸作一切線，此切點即為臨限電壓。

### • 電流開關比(Current on/off ratio)

此參數是用來判斷元件自身電流開關程度，若其值越大則表示元件所具備的切換能力越好；反之，其值越低則元件的切換能力越差。其定義如下所示：

$$\frac{I_{on}}{I_{off}} = \frac{I_{max}}{I_{min}}$$

- 次臨界擺幅(Subthreshold Swing, S.S)

此參數用來描述閘極對通道的控制能力，元件在一定量之閘極電壓時，其相對增加多少量之汲極電流，也表示元件之開關速度，其定義如下所示：

$$S.S = \frac{dV_G}{d\log I_{DS}} \text{ (mV/dec)}$$

由於機台維修的關係，後續元件是在台灣半導體研究中心(TSRI)進行製作，因此製程有稍作修改微調，以下是調整後的製作流程：

圖 5-2 調整後的元件製程順序

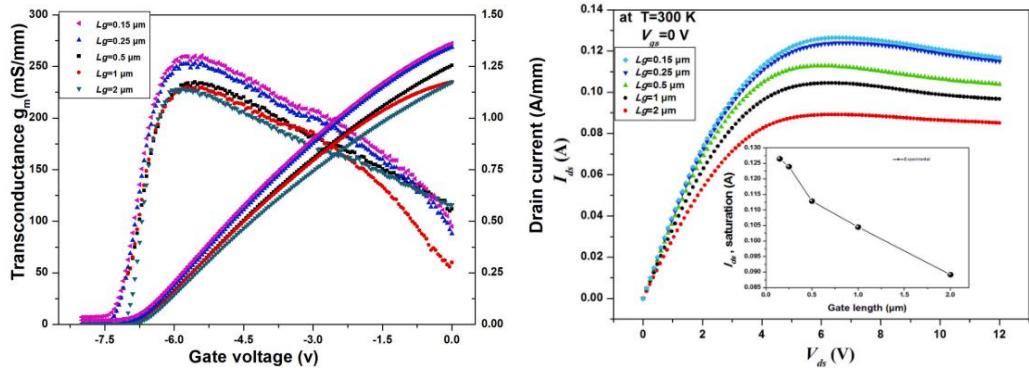

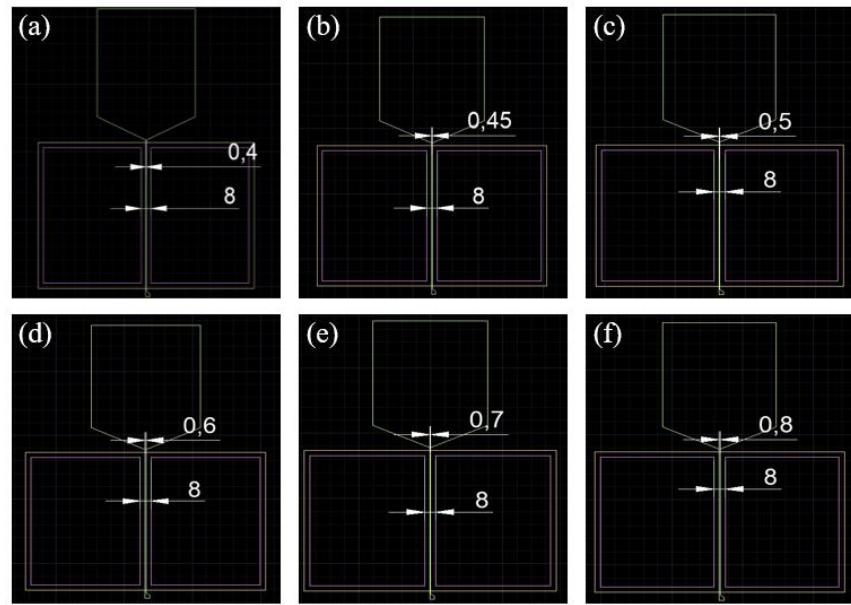

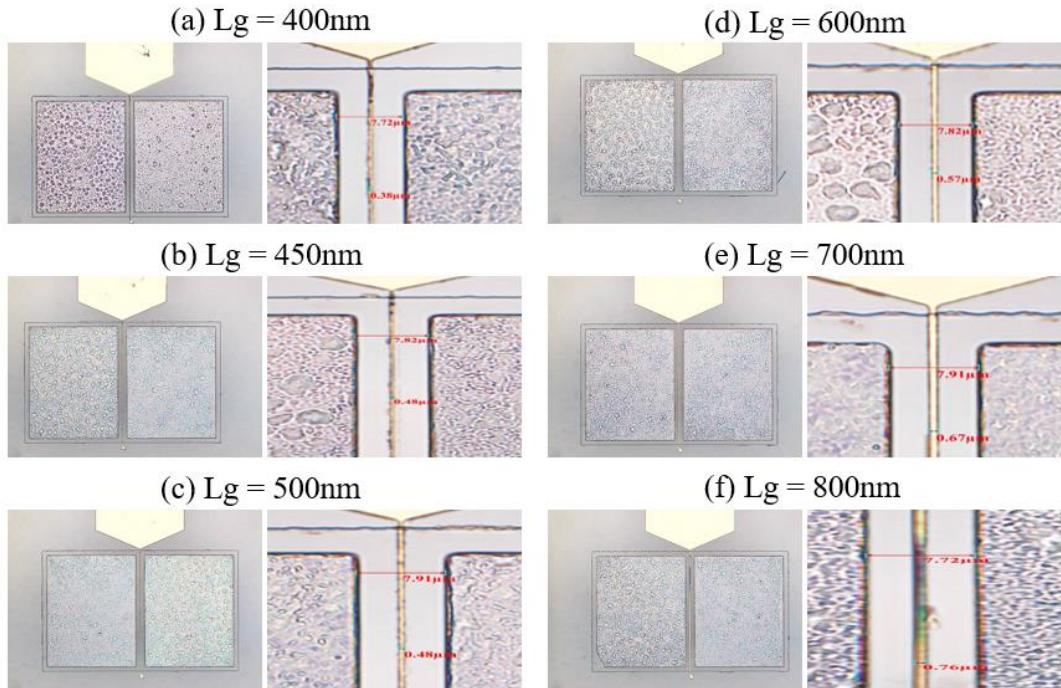

由文獻可知，縮小閘極線寬( $L_g$ )可以提升元件特性表現，為探討不同長度的閘極線寬的直流特性變化，我們固定源極與汲極的距離為 8um，並設計了以下六

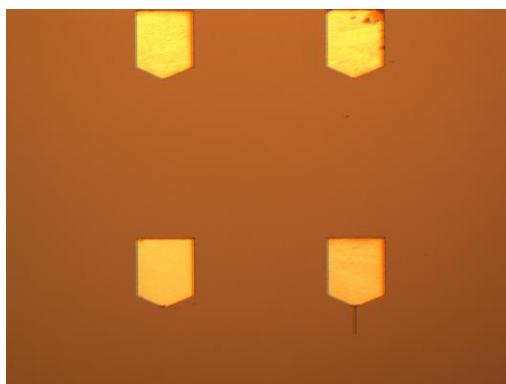

種大小的閘極線寬，分別是 400nm、450nm、500nm、600nm、700nm、800nm，其 Autocad 設計圖如 5-3 所示，所製作出的元件 OM 如圖 5-4 所示：

圖 5-3 元件設計圖(單位為 um)

圖 5-4 元件 OM 圖

量測結果如圖 5-5 及圖 5-6 所示，六個不同閘極線寬的元件的  $I_{Dmax}$  數值相近(約為 830mA/mm)，並無因閘極線寬縮小而變大，猜測其原因應該是汲極與源及距離較大( $LSD=8\mu m$ )，因此閘極線寬的縮小對其產生的影響甚小；不過轉導值

(gm)有隨著線寬縮小從 175.58(mS/mm)增加至 229.08(mS/mm)，且次臨界斜率(Subthreshold Swing, S.S)也隨著閘極線寬縮小從 859.47(mV/dec)降至 562.7(mV/dec)，由這兩項數據可發現閘極線寬縮小時，閘極具備更佳的控制能力，實驗結果也與參考文獻相符。

圖 5-5 元件  $I_D$ - $V_D$  圖

圖 5-6 元件  $I_D$ - $V_G$  圖

最後將本研究結果與近幾年氮化鋁鎵/氮化鎵高電子遷移率電晶體的文獻做

比較，如表 5-1 所示。由結果可發現即使本研究元件的  $L_{DS}$  與  $L_g$  都比參考文獻大，不過特性表現卻沒有比較不佳，甚至能與之相近，若能再縮短  $L_{DS}$  與  $L_g$ ，其特性應該會更加優異。不過也有能再提升的部分，如： $V_{th}$ ，相較其他參考文獻而言，本研究的元件之  $V_{th}$  略高，若能將此現象改善，製作出的元件特性表現也會更好。

表 5-1 本研究與參考文獻之電性比較

| Gate length (nm)        | $L_{DS}$ (um) | $I_{Dmax}$ (mA/mm) | $V_{th}$ (V) | $gm$ (mS/mm) | $R_{on}$ ( $\Omega$ *mm) | S.S (mV/dec) | On/off Ratio (order) |

|-------------------------|---------------|--------------------|--------------|--------------|--------------------------|--------------|----------------------|

| 400                     | 8             | 826.39             | -3.83        | 229.08       | 3.54                     | 562.7        | 5                    |

| 450                     |               | 834.84             | -3.79        | 231.37       | 3.49                     | 567.49       | 5                    |

| 500                     |               | 840.64             | -3.81        | 217.29       | 3.43                     | 619.37       | 5                    |

| 600                     |               | 824.17             | -3.85        | 199.89       | 3.51                     | 693.18       | 5                    |

| 700                     |               | 828.66             | -3.87        | 187.77       | 3.46                     | 754.82       | 4                    |

| 800                     |               | 839.82             | -3.91        | 175.58       | 3.54                     | 859.47       | 5                    |

| Previous Work 200nm[31] | 3             | 862                | -4.69        | 165          | 2.84                     | --           | 6                    |

| 250nm[28]               | 4             | 1250               | -7           | 250          | --                       | --           | --                   |

| 264nm[32]               | 2             | 1010               | -4.52        | 291          | 2.45                     | 199          | 6                    |

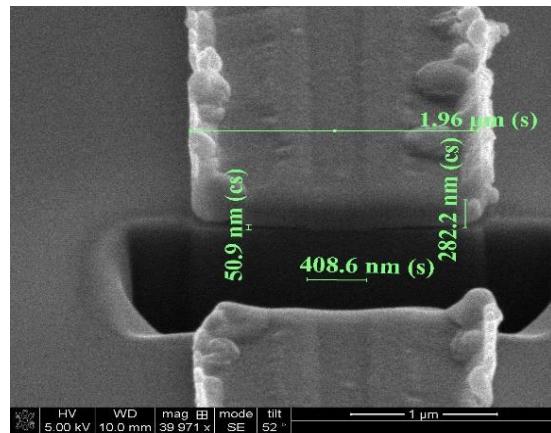

## 5.2 T 型閘極

在參考文獻過後，首先須確定所選用之三層光阻是否能達成 T 型的形狀定義，因此先設計一組較大線寬( $L_{fg}=400$  nm /  $L_{hg}=2$  um)的 T 型閘極來證明其可行性，在經過多組參數改良之後證明了所選用的三層光阻(ZEP520A(1:1)/LOR5B/

ZEP520A)可以達成 T 型的形狀定義，如圖 5-7 所示，其  $L_{fg}=408.6 \text{ nm}$ ， $L_{hg}=1.96 \mu\text{m}$ 。

圖 5-7 Sample 1 FIB

在確定此三層光阻法可以成功做出 T 型閘極後，我們開始對其線寬進行微縮及增高 T-foot，我們將最下層光組換為 ZEP520A 而上面兩層光組不變，預期其所定義出來的 T-foot 高度為 300 nm 且線寬設計為  $L_{fg}=200 \text{ nm}$  /  $L_{hg}=800 \text{ nm}$ ，在後續實際進行實驗後，會發現常有掀離金屬過後大部分的元件都被掀離的情形出現，如圖 5-8 所示：

圖 5-8 Sample 2 OM

推測由於下層的 ZEP520A 因為厚度較厚，需要使用更大曝光劑量的電子束才能擊穿光阻，接著將實驗使用的曝光計量提高後，其成果雖有改善但仍不如預期，且有發現線寬變大的情形出現，如圖 5-9 所示：

圖 5-9 Sample 3 OM

由上圖來看，推測下層有些許殘餘光阻，因此在製程中加入一道使用 RIE 來去除殘餘光阻，雖然情況亦有改善但良率不如預期，如圖 5-10 所示：

圖 5-10 Sample 4 OM

根據上述三種情形分析，若下層光組改為 ZEP520A，會需要提高曝光劑量但同時會造成線寬變大，且是否有打 RIE 的樣品皆呈現良率不佳的情形，因此選擇原本的 ZEP520A(1:1)作為最下層光阻，並重新設計線寬( $L_{fg}=100\text{ nm} / L_{hg}=800\text{ nm}$ )及作曝光劑量調整，實驗結果為  $L_{fg}=118.8\text{ nm} / L_{hg}=1.7\text{ um}$ ，如下圖所示：

圖 5-11 Sample 5 FIB

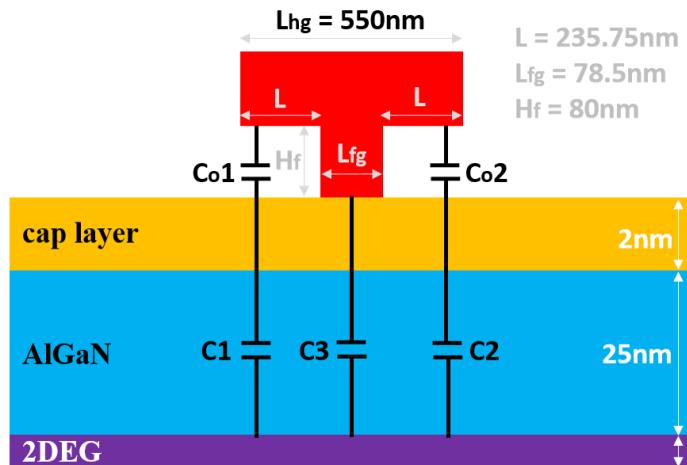

由於 T-head 越大則表示  $L_{SG}$  與  $L_{GD}$  會越接近，依據平行板電容公式  $C = \varepsilon \frac{A}{d}$ ，其中  $d$  為兩個平行板之間的距離，在平行板面積  $A$  不變時，若距離越接近則其相應之電容值會越大，表示寄生電容效應越明顯進而影響整體元件特性表現，因此我們同時將 T-head 與 T-foot 的線寬進行微縮，設計為  $L_{fg}=100\text{ nm}$  /  $L_{hg}=500\text{ nm}$ ，其實驗結果為  $L_{fg}=78.5\text{ nm}$  /  $L_{hg}=\text{約 } 550\text{ nm}$ 。

圖 5-12 Sample 6 FIB

由上圖可發現將上下層都使用 ZEP520A(1:1)來製作 T 型閘極的良率較高且能同時達到線寬微縮之效果。

### 5.3 $f_T$ 與 $f_{max}$ 估算

藉由開發出來的 T 型閘極與本研究的元件與過去實驗室做的元件，將其進行較為理想化的高頻特性參數估算。首先，本研究的元件與過去實驗室做的元件皆為傳統線閘極，其相應之結構如圖 5-13，T 型閘極的結構如圖 5-14 所示，在進行估算前先確立一些參數，由於閘極只改變線寬，因此閘極寬度  $W$  皆相同為 100um，本研究之元件以  $L_g=400\text{nm}$  做代表，過去實驗室所做的元件閘極線寬為 200nm，T 型閘極以圖 5-12 作為代表，接下來開始進行  $C_g$  的估算：

圖 5-13 傳統線閘極結構示意圖

$$C_g = \epsilon_{AlGaN} \times \frac{W \times L_g}{27(nm)} \quad (式 5-1)$$

由式 5-1 可推得  $C_g(L_g=200nm) = 0.65 \text{ fF}$  及  $C_g(L_g=400nm) = 1.31 \text{ fF}$

圖 5-14 T 型閘極結構示意圖

T 型閘極的  $C_g$  較為複雜，先進行參數的代換：

$$\begin{cases} C_{g1} = \frac{C_{o1}C_1}{C_{o1} + C_1} \\ C_{g2} = \frac{C_{o2}C_2}{C_{o2} + C_2} \end{cases} \quad (式 5-2)$$

其中  $C_{o1} = C_{o2} = \epsilon_{Air} \times \frac{W \times L}{80(nm)}$  及  $C_1 = C_2 = \epsilon_{AlGaN} \times \frac{W \times L}{27(nm)}$

由此可將 T 型閘極的閘極電容表示為  $C_g = C_{g1} + C_3 + C_{g2}$ ，並可推出  $C_g(T\text{-gate}) = 0.31 \text{ fF}$ 。

在推出個別閘極電容後，將這些數值代入簡化後的 $f_T$ 與 $f_{max}$ 公式：

$$\begin{cases} f_T \approx \frac{gm}{2\pi C_g} \\ f_{max} = \sqrt{\frac{f_T}{8\pi R_g C_g}} \end{cases}$$

(式 5-3)

代入計算過後可得表 5-2：

表 5-2 估算結果

|                | Lg=200nm | Lg=400nm | T-gate |         |      |

|----------------|----------|----------|--------|---------|------|

| gm(mS/mm)      | 160      | 229      | 160    | 229     | 300  |

| Cg(fF)         | 0.65     | 1.31     |        | 0.31    |      |

| Rg( $\Omega$ ) | 122      | 61       |        | 22.1818 |      |

| fT(GHz)        | 388      | 278      | 827    | 1184    | 1551 |

| fmax(GHz)      | 139      | 118      | 694    | 831     | 959  |

由於 T 型閘極的元件尚未量測其直流特性，因此假設三種情形來估算其高頻表現，分別是與 Lg=200nm 的元件轉導值相同、與 Lg=400nm 的元件轉導值相同及轉導值比前兩者都大，由估算結果可發現 T 型閘極的元件表現確實比傳統線閘極的元件更好，這個結果也與我們的研究動機相符，不過若能進行量測可獲得更為精確的結果。

## 第六章 結論與未來展望

本論文藉由微縮閘極線寬及採用 SiC 基板，成功提升元件性能，雖然通道長度較大，但與實驗室過去所做的藍寶石基板 HEMT 研究及參考文獻相比，其特性沒有比較遜色，反而若能更加進行尺寸微縮，其特性表現會更好。

本研究也成功採用三層光阻 ZEP520A(1:1)/LOR5B/ZEP520A(1:1)成功製作出 T 型閘極，線寬從  $L_{fg}=408.6\text{ nm}$  及  $L_{hg}=1.96\text{ um}$  微縮至  $L_{fg}=78.5\text{ nm}$  且  $L_{hg}=\text{約}550\text{ nm}$ ，藉由不同曝光劑量達成上下層線寬的定義，由結果也可發現三層光阻可製作出不同大小的 T 型閘極，因此若要更加提升元件特性，能再將線寬更加微縮；若考慮寄生電容效應，則必須考慮上層閘極線寬的影響，當其線寬越大時則與汲極及源極距離更短，其寄生電容會越大，因此可以固定下層閘極線寬，設計不同大小的上層閘極線寬，並個別對其進行元件特性量測與分析，找出最適當的上下層線寬比來達到更佳的特性表現。另外，本研究在實驗過程中亦有發現三層光阻法採用 bottom-up 的製作方式會使得下層線寬被定義出來後，於後續製作上層閘極製程時，會有殘餘 LOR 的情形影響金屬掀離，所以若採用 top-down 的方式即可避免此情形發生，甚至可以在製作閘極前先成長一層氧化層，將閘極形狀定義於此氧化層取代三層光阻法的第一層光阻，不但能提升 T 型閘極的穩定性，同時也能減少寄生電容效應的影響。

## 參考文獻

-

- [1] M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, "Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) metal-semiconductor field-effect transistors on single-crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (010) substrates," *Applied Physics Letters*, vol. 100, no. 1, 2012.

- [2] Y. Développement, "GaN Power 2021: Epitaxy, Devices, Applications and Technology Trends report," 2021.

- [3] Y.-C. Wan, "Fabrication and Characterization of AlInGaN/GaN Millimeter Wave Power Transistors," 2020.

- [4] Y. Sun *et al.*, "Review of the recent progress on GaN-based vertical power Schottky barrier diodes (SBDs)," *Electronics*, vol. 8, no. 5, p. 575, 2019.

- [5] T. Liu, S. Chen, and P. Wang, "Analysis on the application, development, and future prospects of Gallium Nitride (GaN)," presented at the 2020 International Conference on Optoelectronic Materials and Devices, 2021.

- [6] J. N. Burghartz, Ed. *Ultra-thin Chip Technology and Applications*. 2016.

- [7] E. T.-e. PE. "What is a GaN Transistor?" (accessed).

- [8] O. Ambacher *et al.*, "Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures," *Journal of applied physics*, vol. 87, no. 1, pp. 334-344, 2000.

- [9] J. P. Ibbetson, P. T. Fini, K. D. Ness, S. P. DenBaars, J. S. Speck, and U. K. Mishra, "Polarization effects, surface states, and the source of electrons in AlGaN/GaN heterostructure field effect transistors," *Applied Physics Letters*, vol. 77, no. 2, pp. 250-252, 2000, doi: 10.1063/1.126940.

- [10] F. Sacconi, A. D. Carlo, P. Lugli, and Hadis Morkoç, Fellow, and IEEE, "Spontaneous and Piezoelectric Polarization Effects on the Output Characteristics of AlGaN/GaN Heterojunction Modulation Doped FETs," 2001.

- [11] Y.-W. Chen, "Study of Ohmic Contact to p-type AlGaN," 2006.

- [12] A. Zahin, "Schottky Barrier Heights at Two-Dimensional Metallic and Semiconducting Transition-Metal Dichalcogenide Interfaces," 2017.

- [13] P. Zhang, "Effects of surface roughness on electrical contact, RF heating and field enhancement," University of Michigan, 2012.

- [14] C. Langpoklakpam *et al.*, "Review of silicon carbide processing for power MOSFET," *Crystals*, vol. 12, no. 2, p. 245, 2022.

- [15] Z.-F. Huang and T.-F. Zhang, "Overview of GaN Based Power Device," 2014.

- [16] D. M. Pozar, *Microwave Engineering*, 3 ed. 2004.

- [17] S.-Y. Lo, "Integrating Aluminum Nitride Film Buffer Layer and Surface Passivation Layer Technology in the Production of T-gate High Electron

- Mobility Transistors and High Frequency Analysis," 2020.

- [18] Y. Zhang *et al.*, "Millimeter-wave AlGaN/GaN HEMTs with 43.6% power-added-efficiency at 40 GHz fabricated by atomic layer etching gate recess," *IEEE Electron Device Letters*, vol. 41, no. 5, pp. 701-704, 2020.

- [19] Samsung. "Printing circuits onto wafers: 'Photoresist'." (accessed).

- [20] M. Lyubomirskiy, "High energy X-ray inline interferometry based on refractive optics," 2016.

- [21] K. University, "Electron-Beam Evaporation," ed.

- [22] L. Vigen, "Etching AlGaN alloys using ICP-RIE," ed, 2019.

- [23] R. CO. "MEMS." (accessed).

- [24] Wise-Creative. "ULVAC CC-200 PECVD 化學氣相沈積." (accessed).

- [25] S. S. o. A. S. Adlershof. "Scanning-electron microscopy." (accessed).

- [26] K. L. House, L. Pan, D. M. O'Carroll, and S. Xu, "Applications of scanning electron microscopy and focused ion beam milling in dental research," *European Journal of Oral Sciences*, vol. 130, no. 2, p. e12853, 2022.

- [27] KEYSIGHT. "Network Analyzer." (accessed).

- [28] S. Saadaoui, O. Fathallah, and H. Maaref, "Effects of gate length on GaN HEMT performance at room temperature," *Journal of Physics and Chemistry of Solids*, vol. 161, 2022, doi: 10.1016/j.jpcs.2021.110418.

- [29] Z.-H. Tong, P. Ding, Y.-B. Su, D.-H. Wang, and Z. Jin, "Influences of increasing gate stem height on DC and RF performances of InAlAs/InGaAs InP-based HEMTs\*," *Chinese Physics B*, vol. 30, no. 1, 2021, doi: 10.1088/1674-1056/abb30d.

- [30] K. Karami *et al.*, "Robust sub-100 nm T-Gate fabrication process using multi-step development," *Micro and Nano Engineering*, vol. 19, 2023, doi: 10.1016/j.mne.2023.100211.

- [31] Y.-C. Liu, "Investigation of Gate-Length Downscaling of AlGaN/GaN HEMT by Alignment Mark Improvement," 2022.

- [32] L.-C. Chang, K.-C. Hsu, Y.-T. Ho, W.-C. Tzeng, Y.-L. Ho, and C.-H. Wu, "High  $f_{max}$  L G product of AlGaN/GaN HEMTs on Silicon with thick rectangular gate," *IEEE Journal of the Electron Devices Society*, vol. 8, pp. 481-484, 2020.