國立臺灣大學工學院機械工程學系

碩士論文

Department of Mechanical Engineering

College of Engineering

National Taiwan University

Master Thesis

應用結構函數於功率放大器元件之 PCB 分層

最佳熱通孔設計

Using structure function to optimize the design of thermal

vias in PCB for power amplifier

劉啟玄

Chi-Hsuan Liu

指導教授：孫珍理 博士

Advisor: Chen-li Sun, Ph.D.

中華民國 112 年 7 月

July 2023

國立臺灣大學碩士學位論文

口試委員會審定書

MASTER'S THESIS ACCEPTANCE CERTIFICATE

NATIONAL TAIWAN UNIVERSITY

應用結構函數於功率放大器元件之 PCB 分層最佳熱通孔設計

Using structure function to optimize the design of thermal

vias in PCB for power amplifier

本論文係劉啟玄(R10522101)在國立臺灣大學機械工程學系完成之碩士學位論文，於民國 112 年 07 月 26 日承下列考試委員審查通過及口試及格，特此證明。

The undersigned, appointed by the Department / Institute of Mechanical Engineering

on 26/07/2023 have examined a Master's thesis entitled above presented by Chi-Hsuan Liu

(R10522101) candidate and hereby certify that it is worthy of acceptance.

口試委員 Oral examination committee:

孫玲玲

(指導教授 Advisor)

劉慈祥

黃美娟

系主任/所長 Director:

林許群

## 誌謝

首先感謝孫珍理老師的指導，總是能在我遇到瓶頸的時候給予最確切的建議，而在每一次與廠商的開會時總能讓我學習到專業的知識，甚至是待人處事的技巧，更是讓我由衷欽佩。也非常感謝老師在百忙之中仍細心的幫我修改論文，這兩年在老師身上真的學到了非常多，也希望未來的自己能夠成為像老師一樣的人。

最感謝爸爸跟媽媽在我求學路上的支持，從來不會給我學業上的壓力，也讓我不需要煩惱生活上的支出，每一次在經歷低潮的時候總會有你們傳來的電話跟訊息關心，讓我可以有繼續前進的動力，很幸運能成為你們的小孩。謝謝兩位姐姐，讓我壓力大的時候可以有人傳梗圖發洩情緒，以及謝謝你們分享自己過來人的經驗，都讓我也能繼續努力做研究。

謝謝淳民、逸軒及聖捷，很高興能夠跟你們一起度過碩士的這兩年，那些一起成長、一起抱怨、一起度過碩士這兩年的每個日子我都會謹記在心，也祝福你們在未來能夠一帆風順。謝謝學長穎希、泓宇、家弘及育誠的教導，學弟妹明諺、其安、神瑋及子淇在各個方面的幫助，祝福你們做研究時一切順利。謝謝成大的朋友們易玄、志霖、敬桓、立渝還有餘之，每一次的午餐約會都是讓我打起精神繼續前進的動力，特別謝謝易玄一直以來的陪伴。謝謝振儀跟羽球少年團，在我剛到台北時帶我熟悉環境，跟我一起玩遍台北。謝謝 Gummy B 的音樂陪伴我度過每個寫論文的夜晚。最後，謝謝文瑄，沒有你的陪伴我一個人沒辦法撐過這段日子。

## 摘要

本研究建構一暫態熱特性測試平台，透過電晶體的順向電壓與溫度呈線性關係的特性，估測功率放大器在關掉電源後的暫態溫度響應，以獲得結構函數，準確表徵元件封裝內不同分層之熱阻與熱容。此外，我們亦以數值模擬搭配結構函數，探討功率放大器的 PCB 基板中熱通孔的設計對整體散熱之影響。

實驗結果顯示，PCB 基板含有 13 個熱通孔的功率放大器樣品其熱阻值與僅有 4 個熱通孔時相比大幅降低 65.9%，由  $9.55\text{ }^{\circ}\text{C W}^{-1}$  降低至  $3.25\text{ }^{\circ}\text{C W}^{-1}$ 。13 個熱通孔的樣品所造成之最高結溫為  $41.5\text{ }^{\circ}\text{C}$ ，與 4 個熱通孔的最高結溫  $48.5\text{ }^{\circ}\text{C}$ 相比降低了 14.4%，並可減少 39.1% 熱量由晶片結接面傳遞至 PCB 底部的熱傳時間。熱通孔的增加有效增加熱傳效率，減少了元件在高溫損壞的可能。

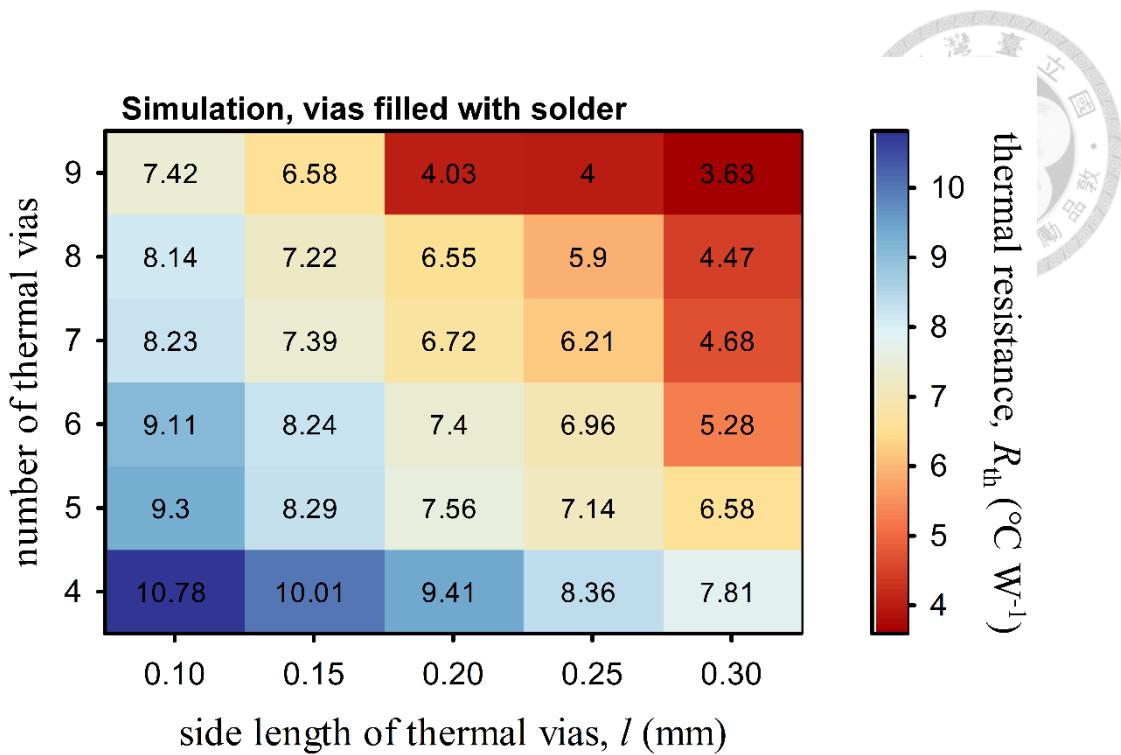

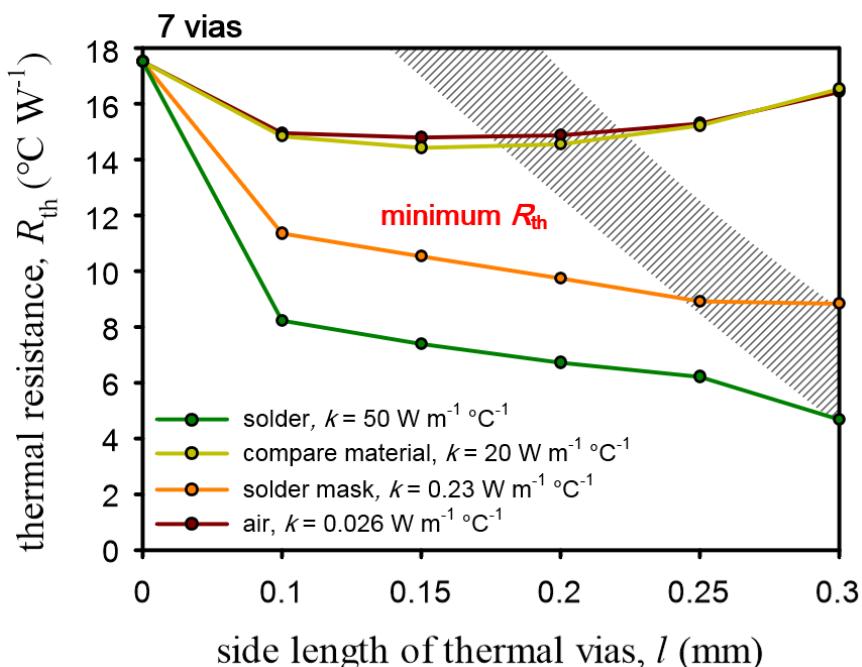

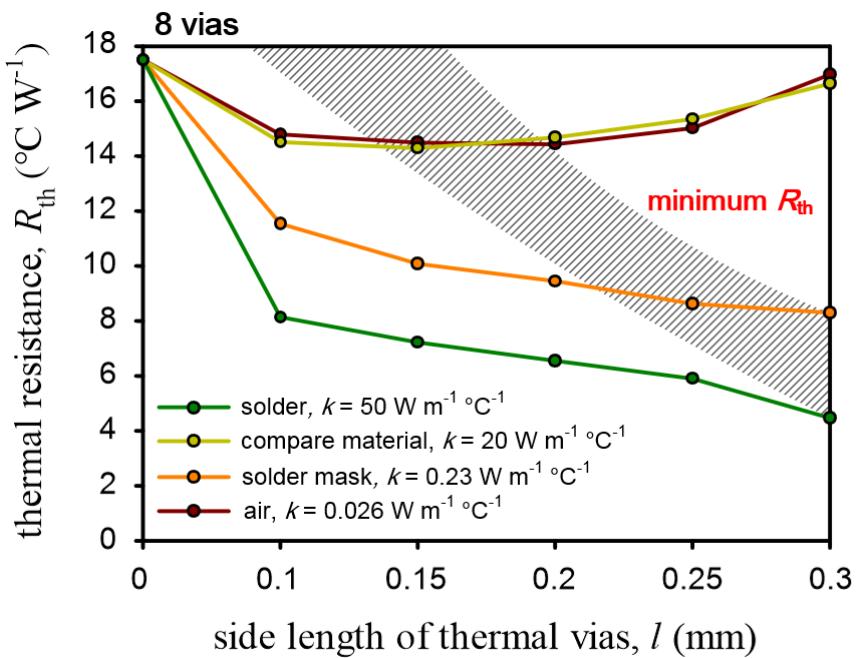

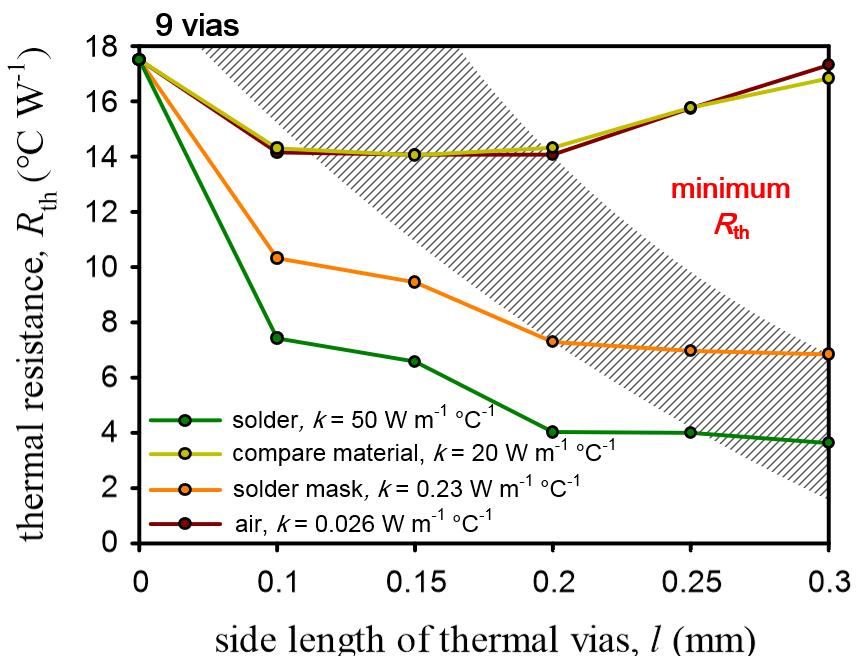

此外，我們發現 PCB 層的熱阻受到熱通孔填充物材料的熱傳導係數影響甚劇。使用熱傳導係數較大的焊料時，熱通孔數量以及尺寸的增加都有助於降低 PCB 基板的熱阻，在 9 個熱通孔、尺寸  $0.3\text{ mm}$  的組合下有最低的熱阻值  $3.63\text{ }^{\circ}\text{C W}^{-1}$ 。若使用熱傳導係數較小的空氣或防焊漆進行填充時，則分別在 9 個熱通孔、尺寸  $0.2\text{ mm}$  及  $0.15\text{ mm}$  有最小的 PCB 分層熱阻  $14.07\text{ }^{\circ}\text{C W}^{-1}$  與  $14.05\text{ }^{\circ}\text{C W}^{-1}$ 。填充物的熱傳導係數下降，則最佳熱通孔尺寸降低，因為熱通孔的尺寸太大，反而會受到填充物的熱傳導係數影響，熱通孔內填充物所占的面積增加，熱阻不降反升。

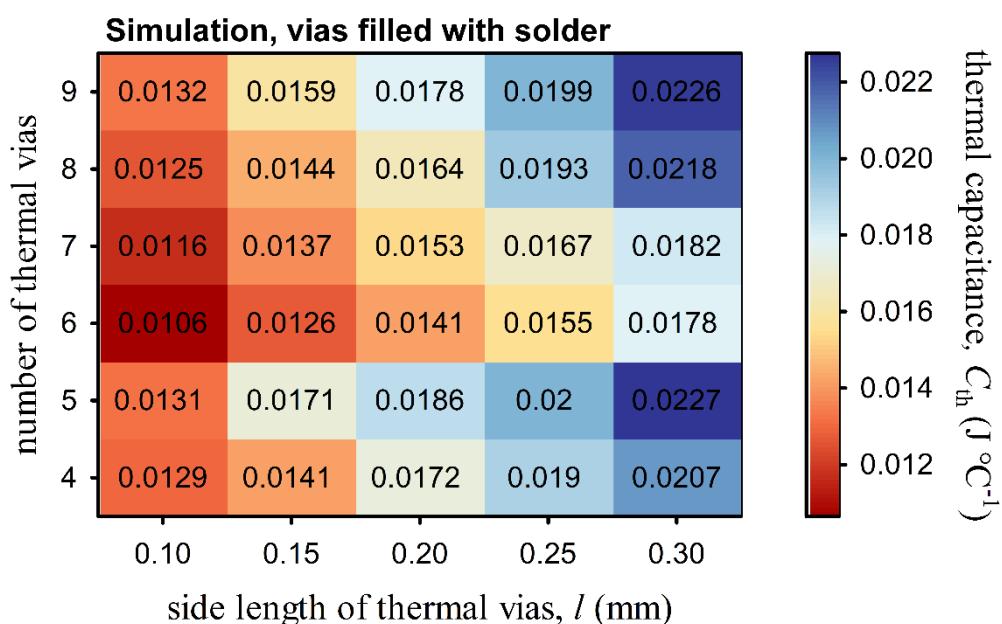

PCB 基板熱容的變化主要可以填充物的比熱分為兩種情形，當熱通孔使用的填充材料比熱為小於 FR4 材料的焊料時，若熱通孔數量大於 6 個，因為熱通孔占整體 PCB 面積較大，則填充物的比熱主導 PCB 層之熱容，使得 PCB 層熱容相較 6 個熱通孔以下的樣品皆明顯降低。當熱通孔數量少於 6 個時，PCB 分層的熱容反而受到熱阻的影響，填充物為焊料時熱通孔尺寸增加會降低 PCB 热阻，在特徵時

間改變不大的情況下，PCB 整體熱容有較大值。我們也發現填充物為焊料時，PCB 分層熱容的增加能夠使 PCB 基板中溫度的分布較為平均，較不會出現局部熱點。若熱通孔填充材料的比熱大於 FR4 材料，即填充物為空氣與防焊漆時，不論熱通孔的數量，PCB 層的熱容僅受 PCB 層的熱阻主宰，熱通孔小於尺寸約 0.2 mm 的大小時，PCB 層的熱阻隨尺寸增加而下降，則 PCB 分層的熱容會隨尺寸增加而上升。

在本研究中，我們成功以結構函數深入瞭解 PCB 基板中熱通孔的設計對於熱網絡的影響，將有助於未來優化功率放大器的熱傳表現。

關鍵字：結構函數、熱通孔、暫態熱響應、熱阻、熱容

## Abstract

This study uses the structure function to investigate the impacts of filler materials and design of thermal vias of the PCB substrate on the thermal networks of a power amplifier. A test platform is constructed to measure the transient temperature response, from which the structure function is derived.

We find that the thermal conductivity of the filler material significantly affects the thermal resistance of PCB substrates. When thermal vias are filled with high thermal conductivity materials such as solder, increasing its number and size helps to reduce the thermal resistance of the PCB layer. However, when the thermal conductivity of the filler material is lower (air or solder mask), there exists an optimal via size. Thermal vias that are too large can lead to a higher thermal resistance of the PCB layer.

On the other hand, the variation of the thermal capacitance of the PCB layer is more complicated. When the specific heat of the filler material is lower than that of FR4, the thermal capacitance of the PCB layer is controlled by its thermal resistance for a number of thermal vias less than 6. Since the characteristic time remains on the same order for the PCB layer, by reduction of the thermal resistance filling with solder, leads to the increase in the thermal capacitance for the PCB layer. Higher thermal capacitance can promote a more uniform temperature distribution within the substrate and reduce local hotspots. However, when the number of thermal vias exceeds 6, the thermal capacitance of the PCB layer is dominated by the specific heat of the filler material; the thermal capacitance decreases accordingly with the increase in the size of the thermal vias. For a filler material with higher specific heat, such as air or solder mask, the thermal

capacitance of the PCB layer is solely determined by its thermal resistance. When the thermal vias are larger than about 0.2 mm, the lower thermal conductivities of air or solder mask increase the thermal resistance of the PCB and decrease the thermal capacitance of the PCB layer.

Keywords: structure function, thermal vias, transient thermal response, thermal resistance, thermal capacitance

# 目錄

|                           |      |

|---------------------------|------|

| 摘要 .....                  | iii  |

| Abstract .....            | v    |

| 目錄 .....                  | vii  |

| 符號索引 .....                | x    |

| 表目錄 .....                 | xii  |

| 圖目錄 .....                 | xiii |

| 第一章 導論 .....              | 1    |

| 1.1 前言 .....              | 1    |

| 1.2 文獻回顧 .....            | 2    |

| 1.2.1 結溫量測方法 .....        | 2    |

| 1.2.2 暫態熱阻與結構函數 .....     | 3    |

| 1.2.3 反卷積網絡識別 .....       | 4    |

| 1.2.4 Cauer 網絡模型轉換 .....  | 4    |

| 1.2.5 結構函數校正 .....        | 5    |

| 1.2.6 热通孔對熱阻之影響 .....     | 6    |

| 1.3 研究目的 .....            | 6    |

| 第二章 實驗架構與不確定性分析 .....     | 7    |

| 2.1 實驗架構 .....            | 7    |

| 2.1.1 溫控平台與加壓治具 .....     | 7    |

| 2.1.2 精密電源供應與電壓量測系統 ..... | 9    |

| 2.2 溫度敏感電性參數校正 .....      | 10   |

| 2.2.1 順向電壓與結溫理論 .....     | 10   |

| 2.2.2 校正實驗程序 .....        | 12   |

| 2.2.3 校正線性擬合 .....        | 12   |

| 2.3 結構函數理論 .....          | 13   |

| 2.3.1 反卷積網絡識別 .....       | 13   |

|                           |     |

|---------------------------|-----|

| 2.3.2 貝氏反卷積理論 .....       | 16  |

| 2.3.3 Cauer 热網絡模型 .....   | 18. |

| 2.4 量測與分析程序 .....         | 21  |

| 2.4.1 降溫曲線量測 .....        | 21  |

| 2.4.2 實驗數據分析 .....        | 20  |

| 2.4.3 資料縮減及延伸 .....       | 22  |

| 2.4.4 平滑降溫曲線 .....        | 22  |

| 2.4.5 模擬校正與最佳參數 .....     | 23  |

| 2.5 不確定性分析 .....          | 24  |

| 2.5.1 順向電壓量測之不確定性 .....   | 25  |

| 2.5.2 溫控平台溫度量測之不確定性 ..... | 26  |

| 2.5.3 結溫之不確定性 .....       | 26  |

| 2.5.4 加熱功率之不確定性 .....     | 28  |

| 2.5.5 热阻之不確定性 .....       | 28  |

| 第三章 實驗結果與討論 .....         | 30  |

| 3.1 實驗功率放大器樣品 .....       | 30  |

| 3.1.1 暫態熱阻變化 .....        | 30  |

| 3.1.2 結構函數 .....          | 31  |

| 3.2 模擬不同填充物之熱通孔 .....     | 33  |

| 3.2.1 填充焊料之熱通孔 .....      | 33  |

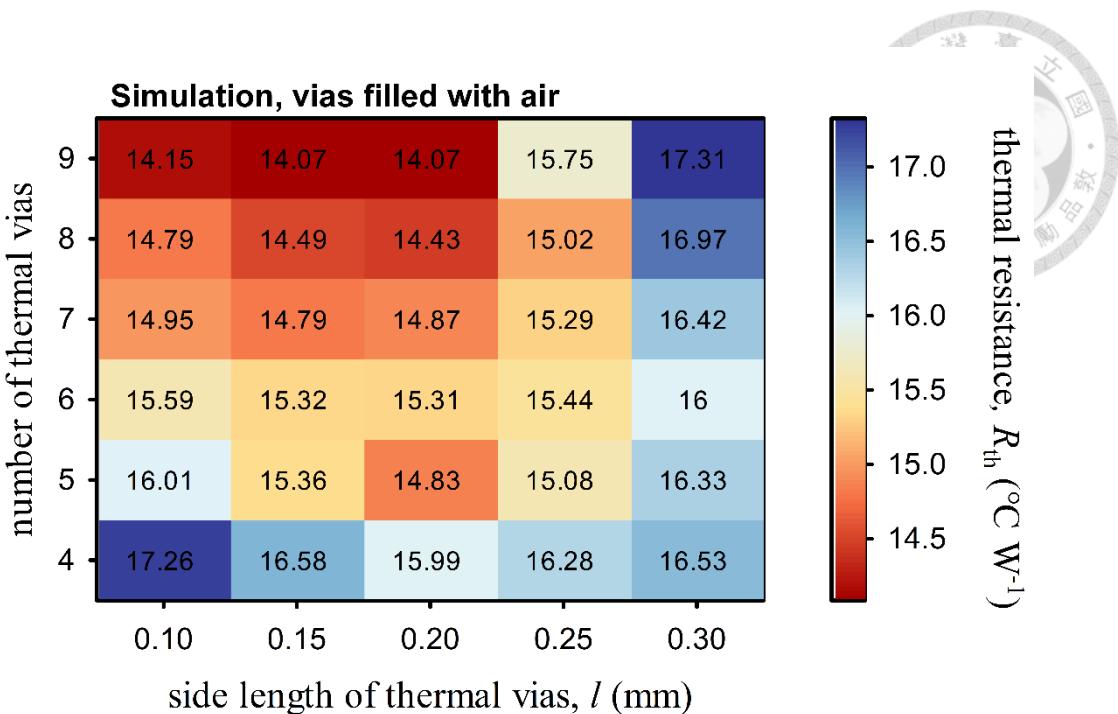

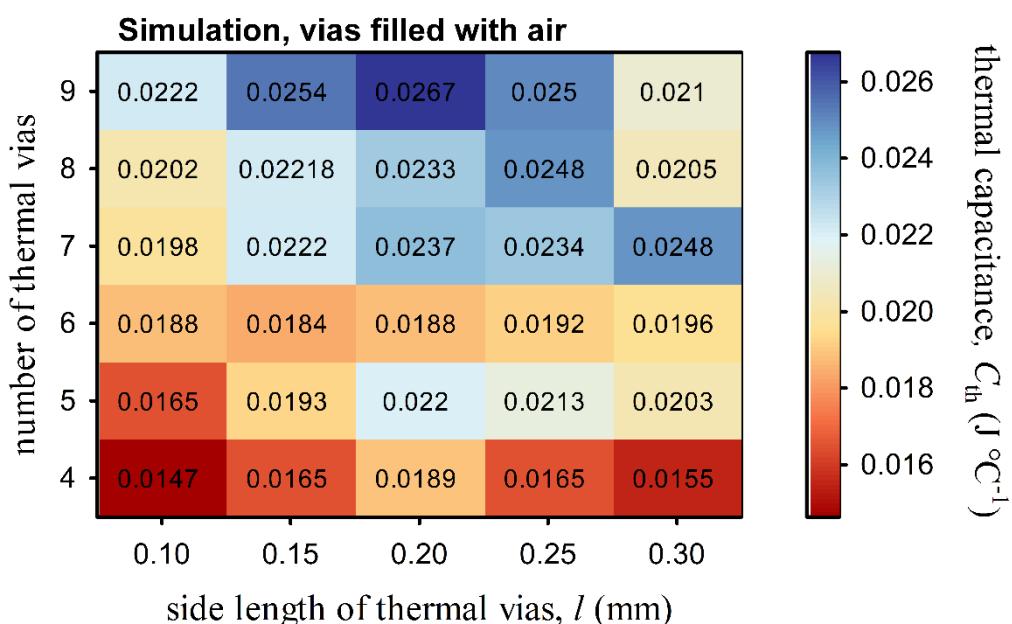

| 3.2.2 無填充物之熱通孔 .....      | 38  |

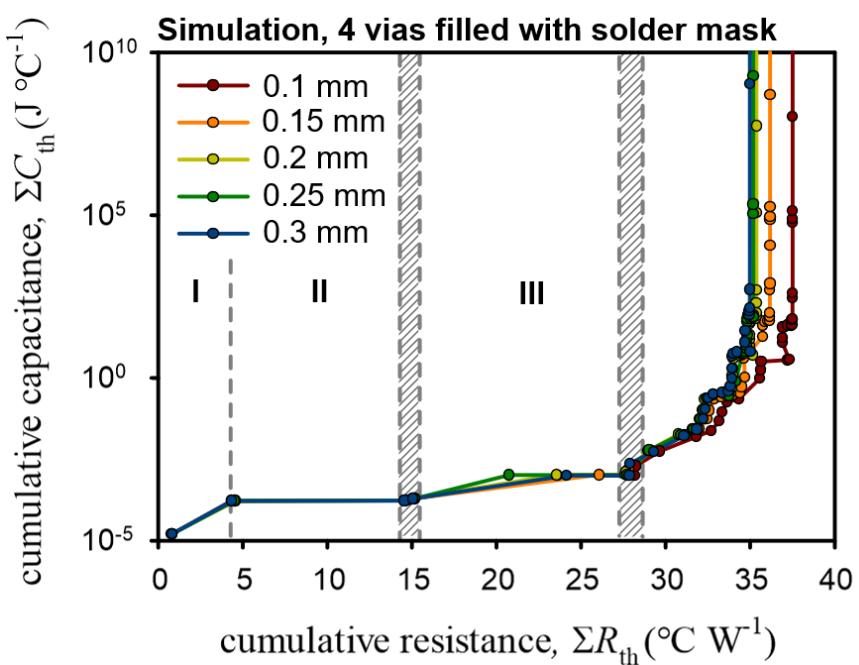

| 3.2.3 填充防焊漆之熱通孔 .....     | 41  |

| 3.3 不同填充物之熱通孔比較 .....     | 45  |

| 3.3.1 热阻比較 .....          | 45  |

| 3.3.2 热容比較 .....          | 47  |

| 第四章 結論與建議 .....           | 49  |

| 4.1 結論 .....              | 49  |

| 4.2 建議 .....              | 50  |

|            |     |

|------------|-----|

| 參考文獻 ..... | 52  |

| 附錄 .....   | 56. |

## 符號索引

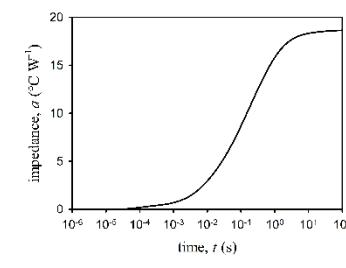

$a$  暫態阻抗 transient impedance ( $^{\circ}\text{C W}^{-1}$ )

$C_{\text{th}}$  热容 thermal capacitance ( $\text{J } ^{\circ}\text{C}^{-1}$ )

$c_p$  比热 specific heat ( $\text{J kg}^{-1} \text{ K}^{-1}$ )

$d$  分母係數 denominator coefficient

$E_g$  能隙 energy gap (eV)

$I$  電流 current (A)

$K_{\text{TSEP}}$  溫度敏感電性參數 temperature sensitive electrical parameters

( $^{\circ}\text{C V}^{-1}$ )

$k$  热傳導係數 thermal conductivity ( $\text{W m}^{-1} \text{ K}^{-1}$ )

$k_B$  波茲曼常數 Boltzmann constant ( $\text{m}^2 \text{ kg s}^{-2} \text{ K}^{-1}$ )

$l$  热通孔邊長 thermal via side length (mm)

$n$  分子係數 numerator coefficient

$P$  機率 probability

$P_{\text{heat}}$  加熱功率 heating power (W)

$q$  基本電荷 elementary charge (C)

$R_{\text{th}}$  热阻 thermal resistance ( $^{\circ}\text{C W}^{-1}$ )

$s$  複數頻率 complex frequency (Hz)

$T$  溫度 temperature ( $^{\circ}\text{C}$ )

$t$  時間 time (s)

$V$  電壓 voltage (V)

$\Psi$  體積 volume ( $\text{m}^3$ )

|       |                                     |

|-------|-------------------------------------|

| $V_0$ | 電壓截距 voltage intercept (V)          |

| $w_z$ | 權重函數 weight function                |

| $Y$   | 導納 admittance ( $\Omega^{-1}$ )     |

| $z$   | 自然對數時間 natural logarithmic time     |

| $Z$   | 複數阻抗 complex impedance ( $\Omega$ ) |

### 希臘符號

|          |                                            |

|----------|--------------------------------------------|

| $\zeta$  | 自然對數時間常數 natural logarithmic time constant |

| $\rho$   | 密度 density ( $\text{kg m}^{-3}$ )          |

| $\sigma$ | 標準差 standard deviation                     |

| $\tau$   | 時間常數 time constant (s)                     |

### 符號下標

|          |                                     |

|----------|-------------------------------------|

| f        | 順向條件 forward condition              |

| j        | 結接面 junction                        |

| pn       | p-n 結 p-n junction                  |

| rand     | 隨機 random                           |

| sat      | 飽和條件 saturated condition            |

| sink     | 恆溫熱沉 constant temperature heat sink |

| sys      | 系統 system                           |

| th       | 熱條件 thermal condition               |

| $\Sigma$ | 累積值 cumulative value                |

### 符號上標

|   |                     |

|---|---------------------|

| n | 迭代次數 iteration time |

|---|---------------------|

# 表目錄

## 第二章附表

|                                   |    |

|-----------------------------------|----|

| 表 2.1 樣品之材料性質參數 [35, 39, 40]..... | 56 |

|-----------------------------------|----|

## 第三章附表

|                           |    |

|---------------------------|----|

| 表 3.1 功率放大器樣品實驗量測結果 ..... | 56 |

|---------------------------|----|

|                             |    |

|-----------------------------|----|

| 表 3.2 功率放大器樣品實驗分層熱阻結果 ..... | 56 |

|-----------------------------|----|

|                              |    |

|------------------------------|----|

| 表 3.3 功率放大器樣品校正後分層熱容結果 ..... | 57 |

|------------------------------|----|

|                                                               |    |

|---------------------------------------------------------------|----|

| 表 3.4 功率放大器樣品 PCB 層熱阻模擬與實驗比較結果 ( $l = 0.2 \text{ mm}$ ) ..... | 57 |

|---------------------------------------------------------------|----|

|                                   |    |

|-----------------------------------|----|

| 表 3.5 填充焊料之熱通孔樣品 PCB 分層模擬結果 ..... | 58 |

|-----------------------------------|----|

|                                |    |

|--------------------------------|----|

| 表 3.6 填充焊料之熱通孔樣品晶片分層模擬結果 ..... | 59 |

|--------------------------------|----|

## 圖目錄

### 第二章附圖

|                                                                 |    |

|-----------------------------------------------------------------|----|

| 圖 2.1 實驗架構示意圖 .....                                             | 60 |

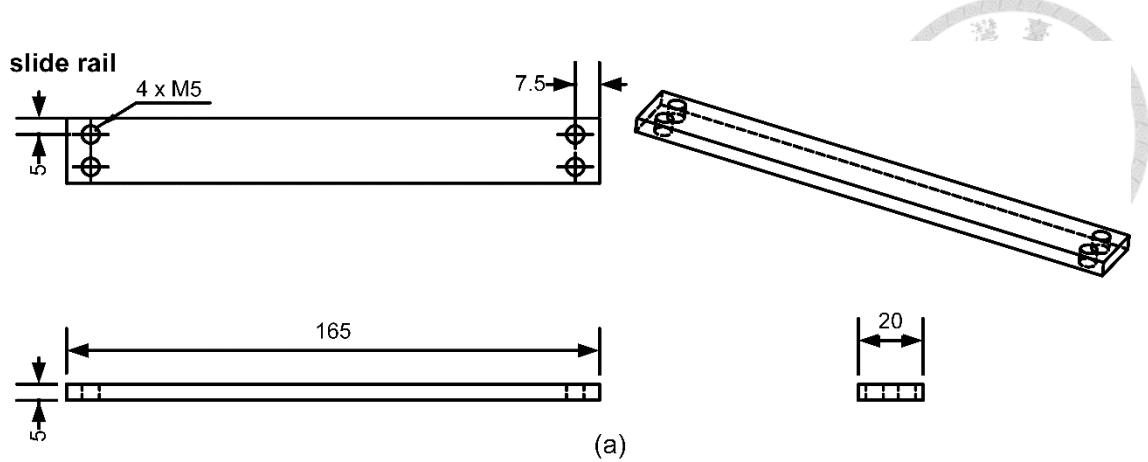

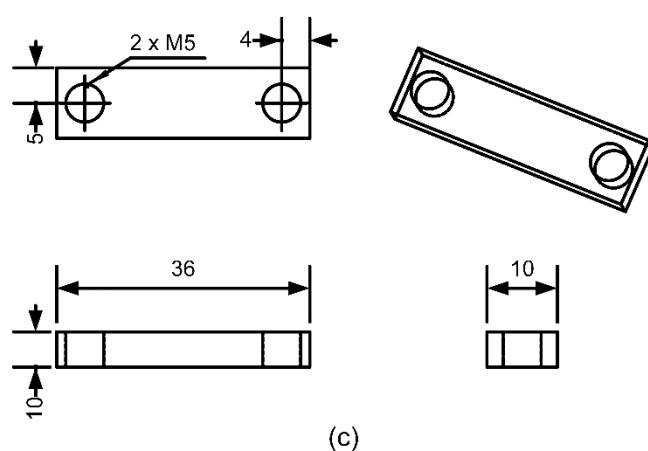

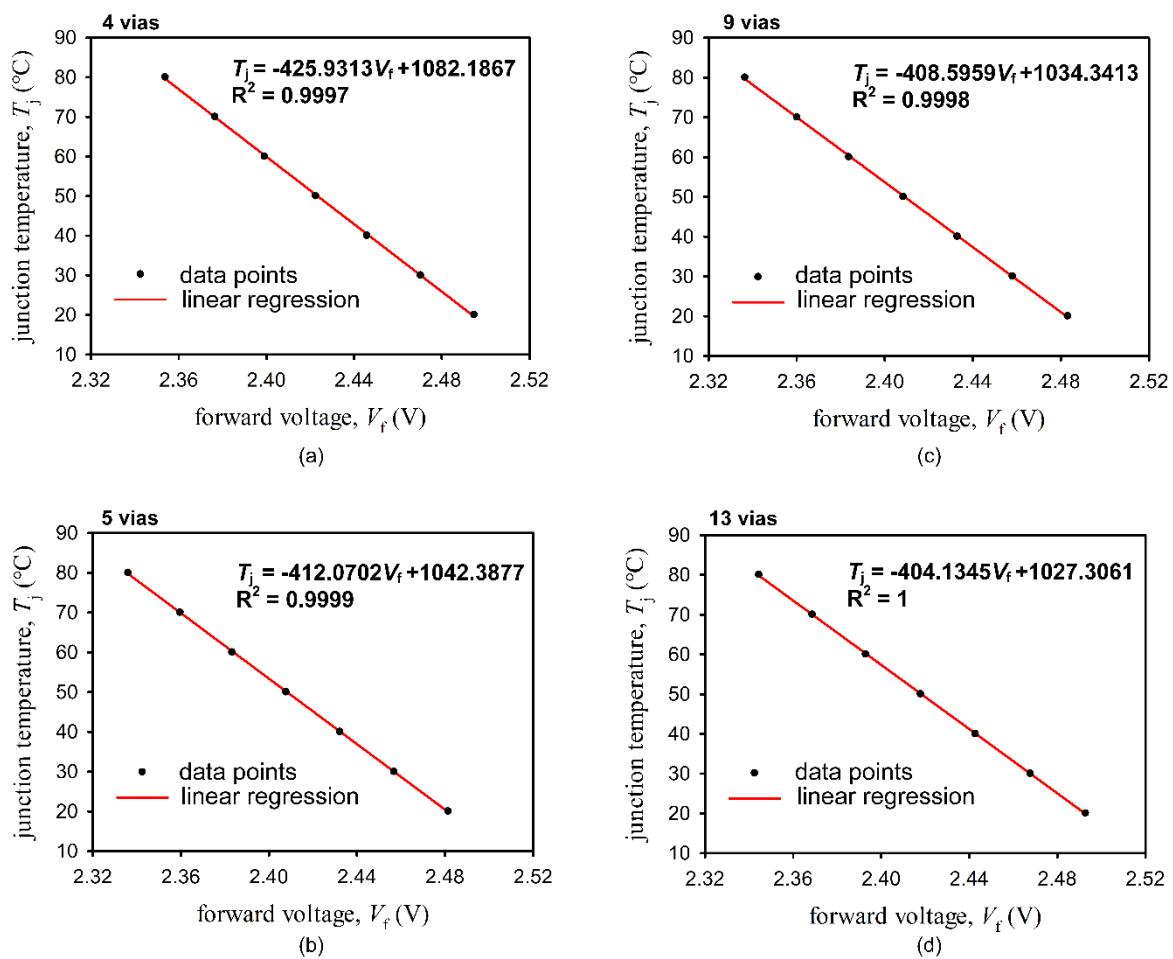

| 圖 2.2 冷卻塊尺寸 (unit: mm).....                                     | 61 |

| 圖 2.3 冷卻槽尺寸 (unit: mm).....                                     | 62 |

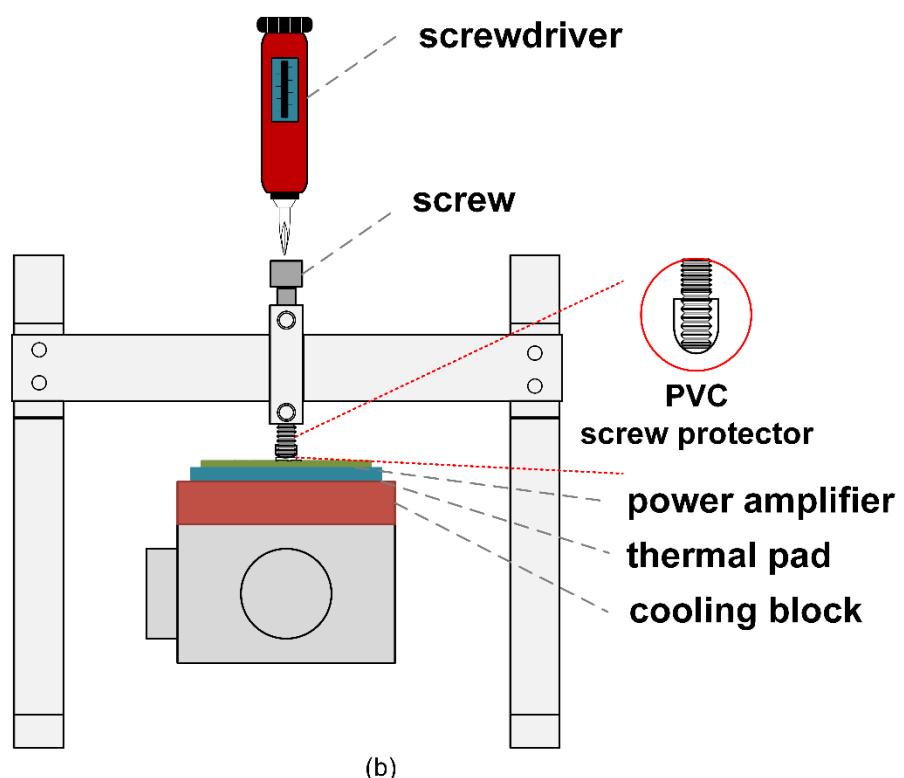

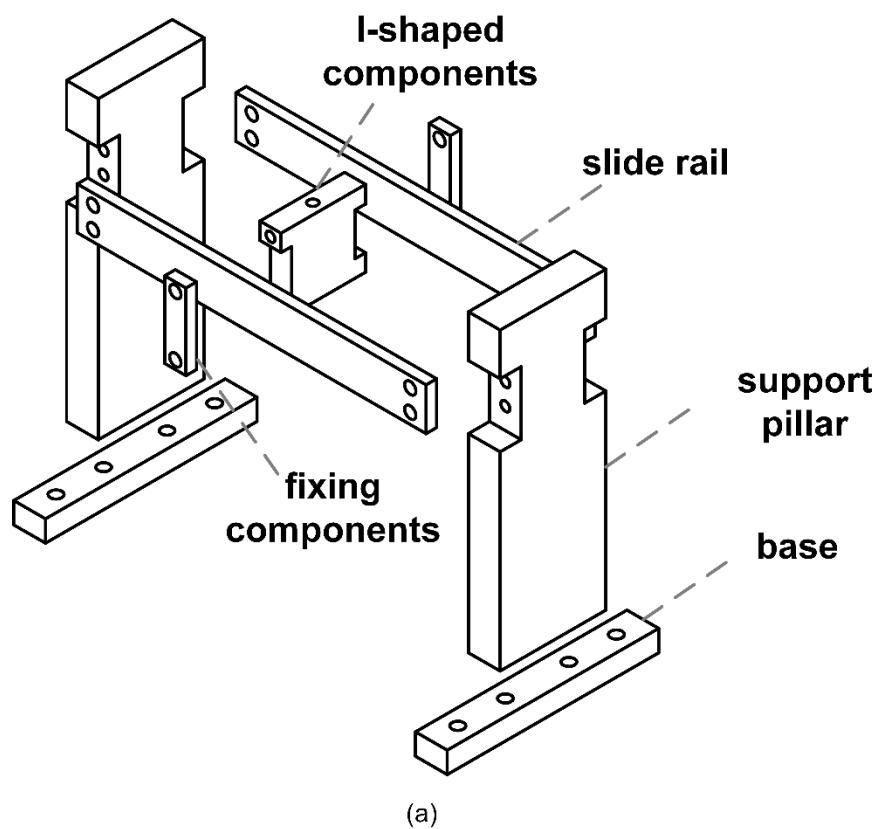

| 圖 2.4 (a) 加壓治具爆炸圖 (b) 組裝示意圖 (未依實際比例作圖) .....                    | 63 |

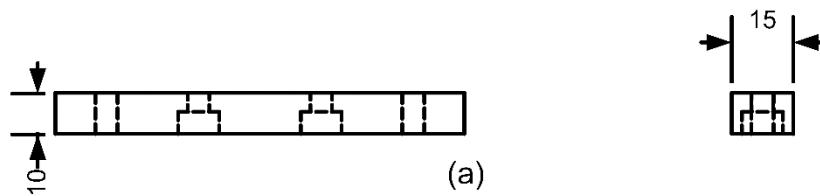

| 圖 2.5 加壓治具 (a) 底座 (b) 側邊支撐柱 尺寸 (unit: mm).....                  | 64 |

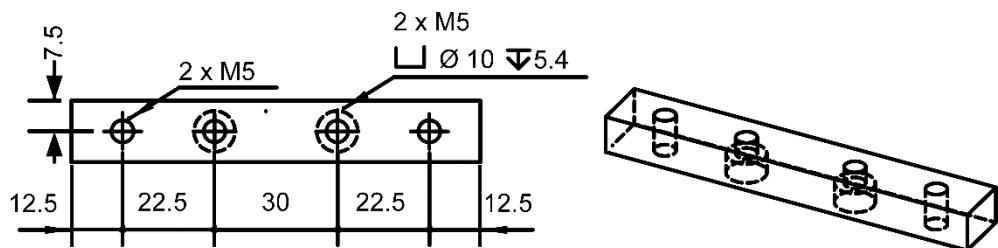

| 圖 2.6 加壓治具 (a) 滑軌 (b) 工字型組件 (c) 固定零件 尺寸 (unit: mm) .....        | 65 |

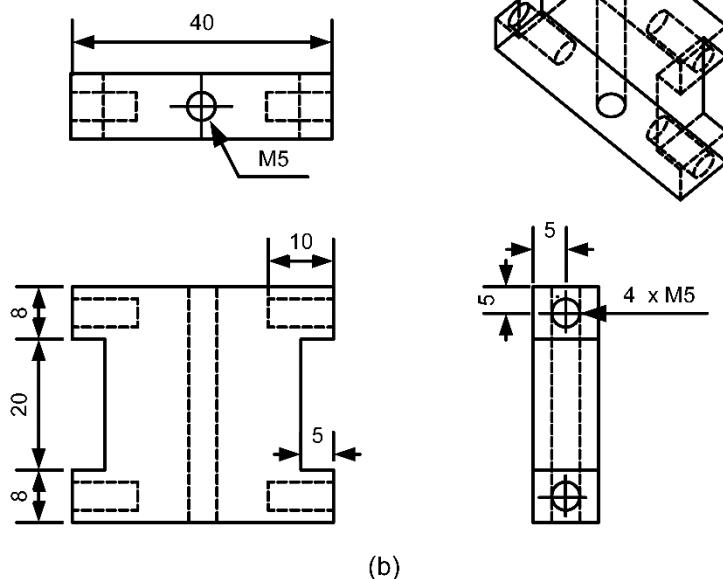

| 圖 2.7 热通孔數目 (a) 4 個 (b) 5 個 (c) 9 個 (d) 13 個 樣品溫度敏感電性參數校正 ..... | 66 |

| 圖 2.8 热模型與等效熱網絡示意圖 .....                                        | 67 |

| 圖 2.9 (a) N 層 Foster 網絡 (b) 離散時間常數波譜 (c) 連續時間常數波譜 示意圖 .....     | 67 |

| 圖 2.10 貝氏反卷積迭代次數最佳化作圖 .....                                     | 68 |

| 圖 2.11 (a) N 層 Cauer 網絡 (b) 累積結構函數 示意圖 .....                    | 68 |

| 圖 2.12 結構函數計算流程圖 .....                                          | 69 |

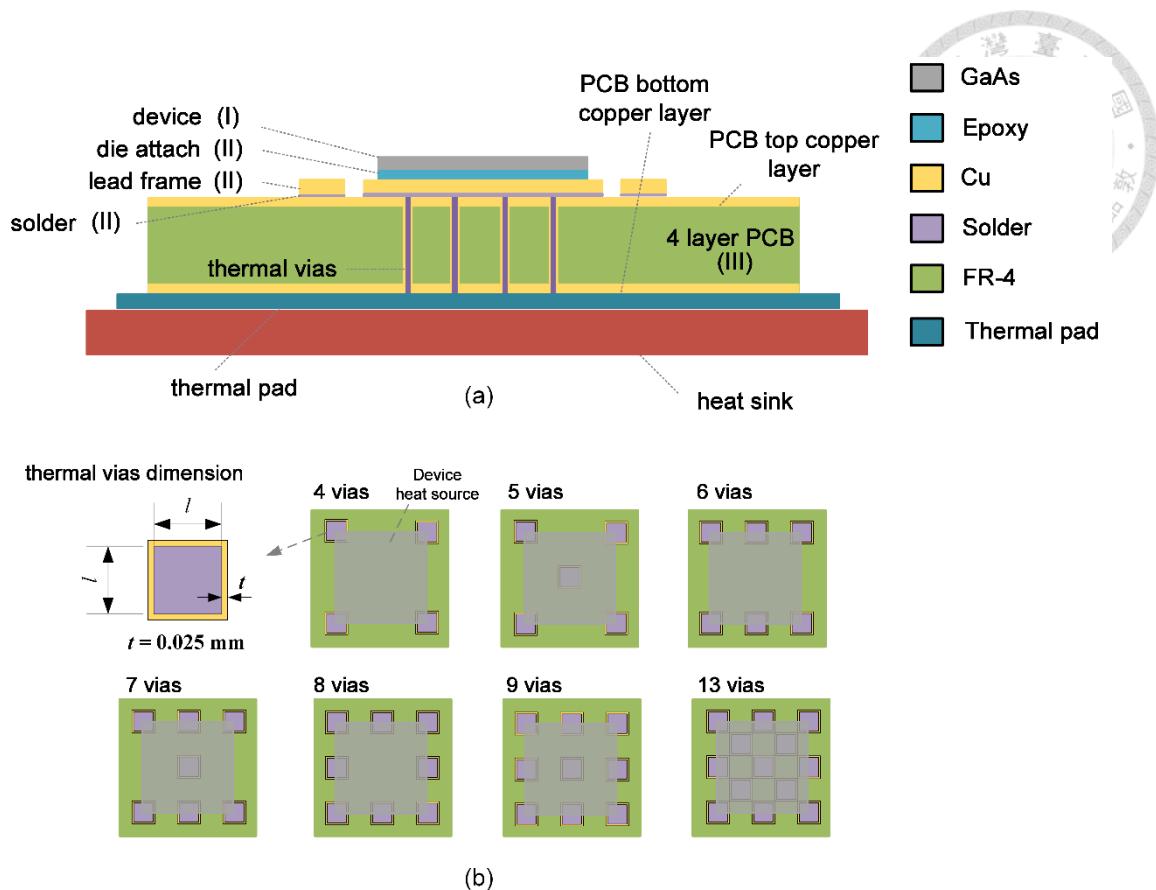

| 圖 2.13 (a) 模擬模型分層 (b) 热通孔尺寸與排列 示意圖 (未依實際比例作圖) .....             | 70 |

### 第三章附圖

|                                                           |    |

|-----------------------------------------------------------|----|

| 圖 3.1 热通孔數目 (a) 4 (b) 5 (c) 9 (d) 13 功率放大器樣品暫態阻抗變化圖 ..... | 71 |

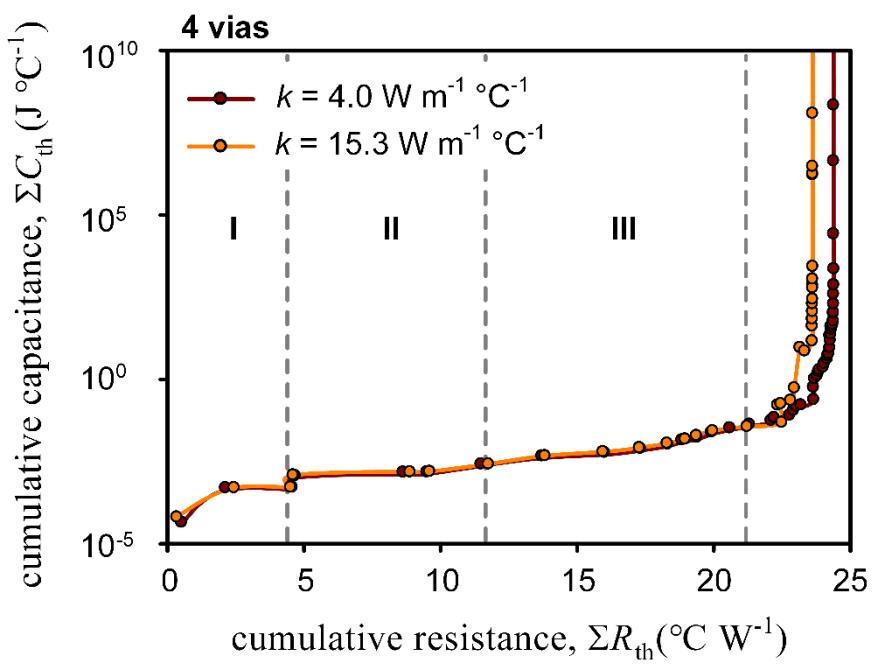

| 圖 3.2 功率放大器 4 個熱通孔數目樣品之實驗與模擬結構函數圖 .....                   | 72 |

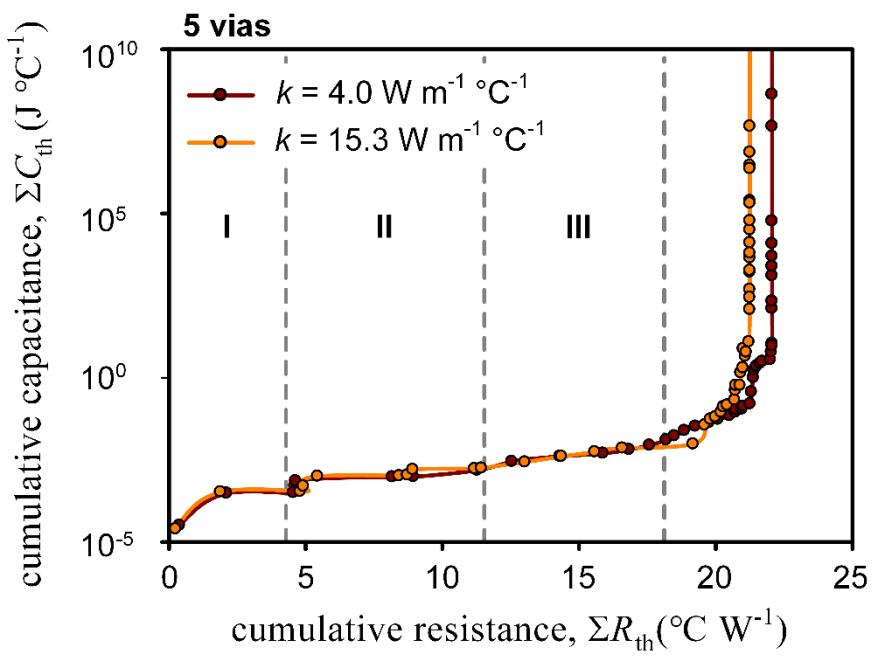

| 圖 3.3 功率放大器 5 個熱通孔數目樣品之實驗與模擬結構函數圖 .....                   | 72 |

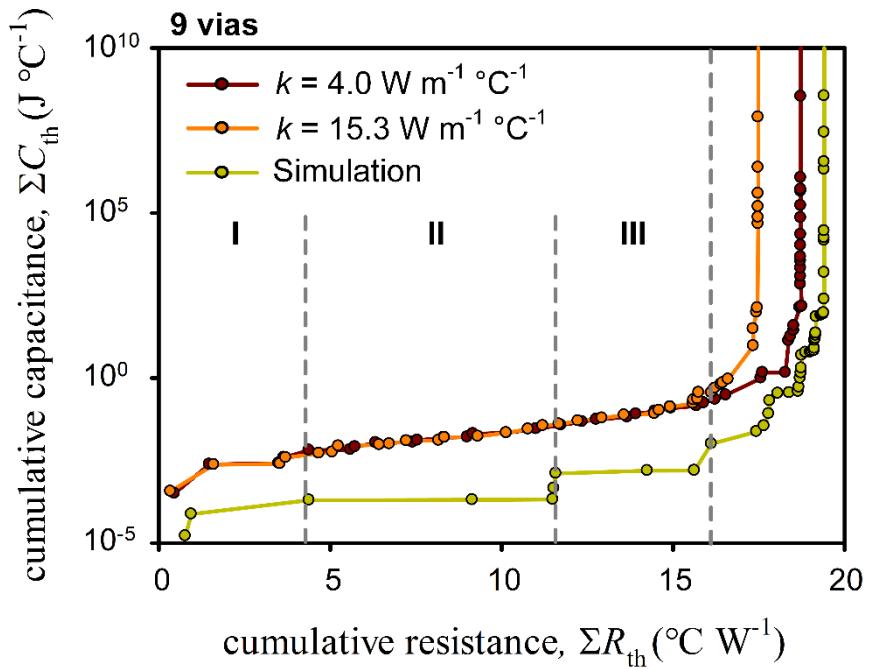

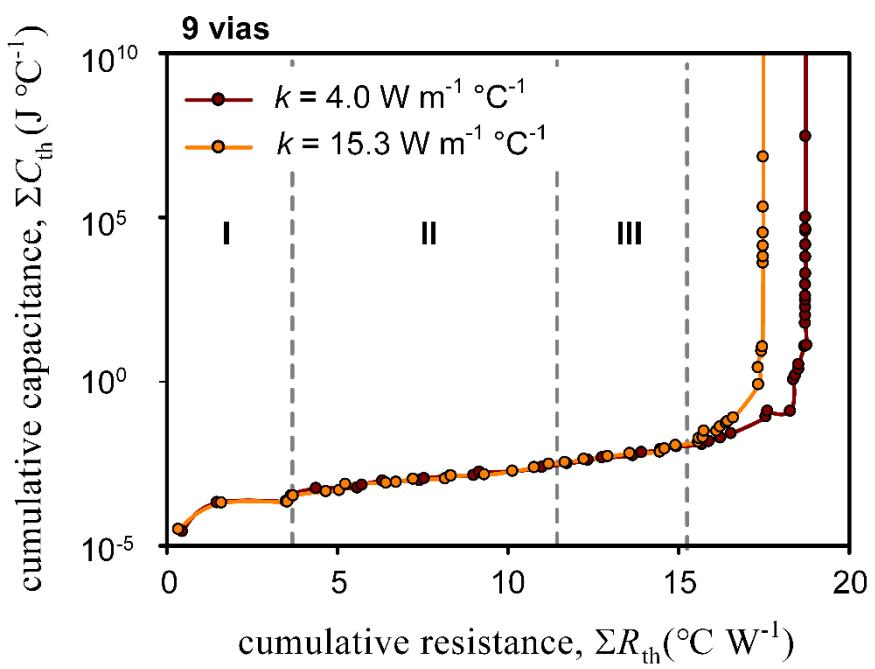

| 圖 3.4 功率放大器 9 個熱通孔數目樣品之實驗與模擬結構函數圖 .....                   | 73 |

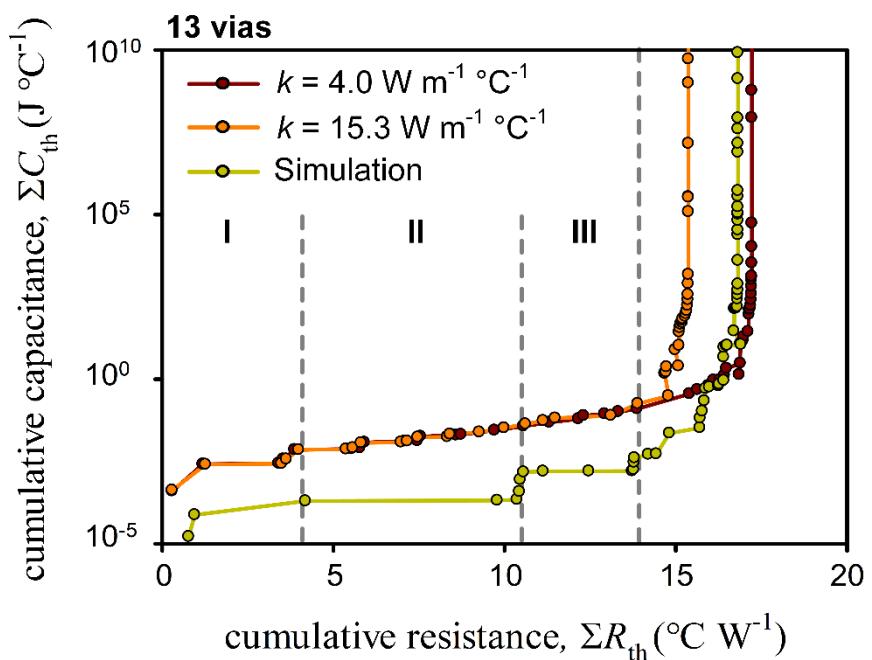

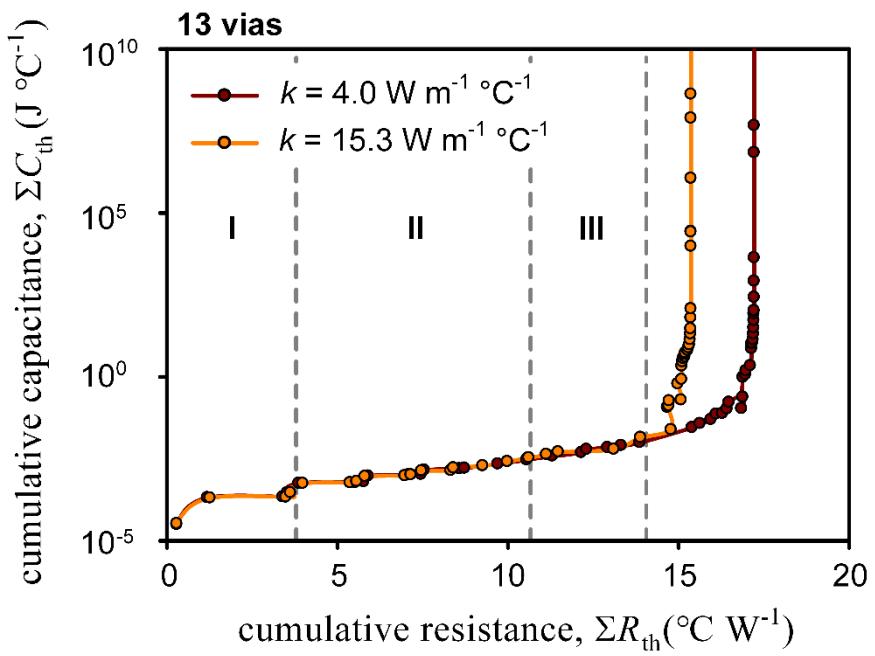

| 圖 3.5 功率放大器 13 個熱通孔數目樣品之實驗與模擬結構函數圖 .....                  | 73 |

|                                           |    |

|-------------------------------------------|----|

| 圖 3.6 功率放大器 4 個熱通孔數目樣品之結構函數圖 (已平移) .....  | 74 |

| 圖 3.7 功率放大器 5 個熱通孔數目樣品之結構函數圖 (已平移) .....  | 74 |

| 圖 3.8 功率放大器 9 個熱通孔數目樣品之結構函數圖 (已平移) .....  | 75 |

| 圖 3.9 功率放大器 13 個熱通孔數目樣品之結構函數圖 (已平移) ..... | 75 |

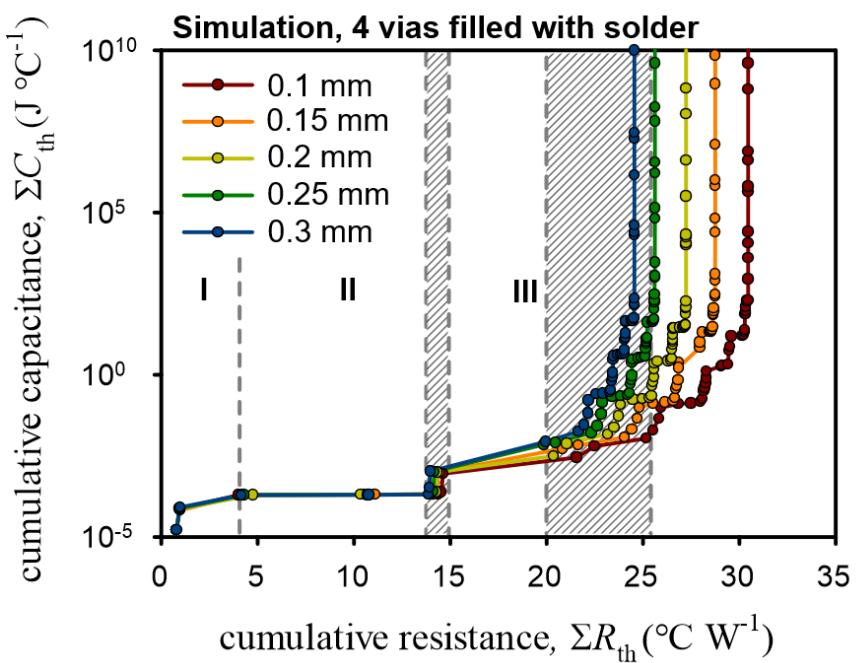

| 圖 3.10 4 個熱通孔不同尺寸之結構函數比較 (solder).....    | 76 |

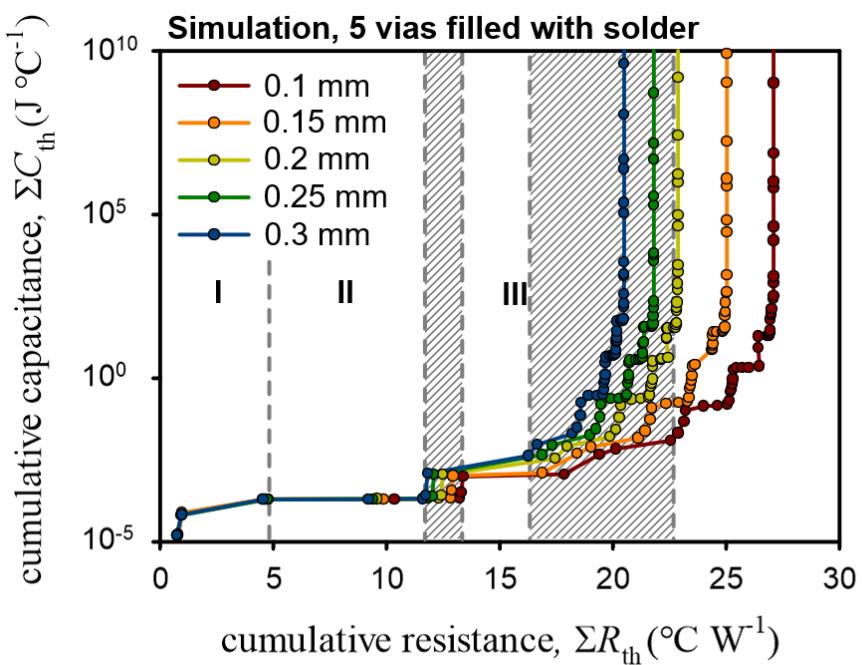

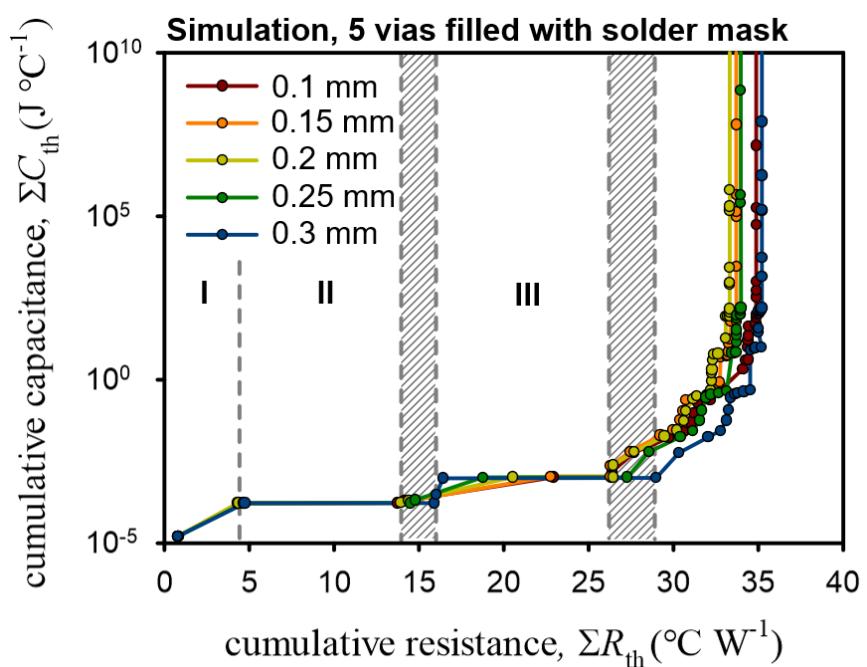

| 圖 3.11 5 個熱通孔不同尺寸之結構函數比較 (solder).....    | 76 |

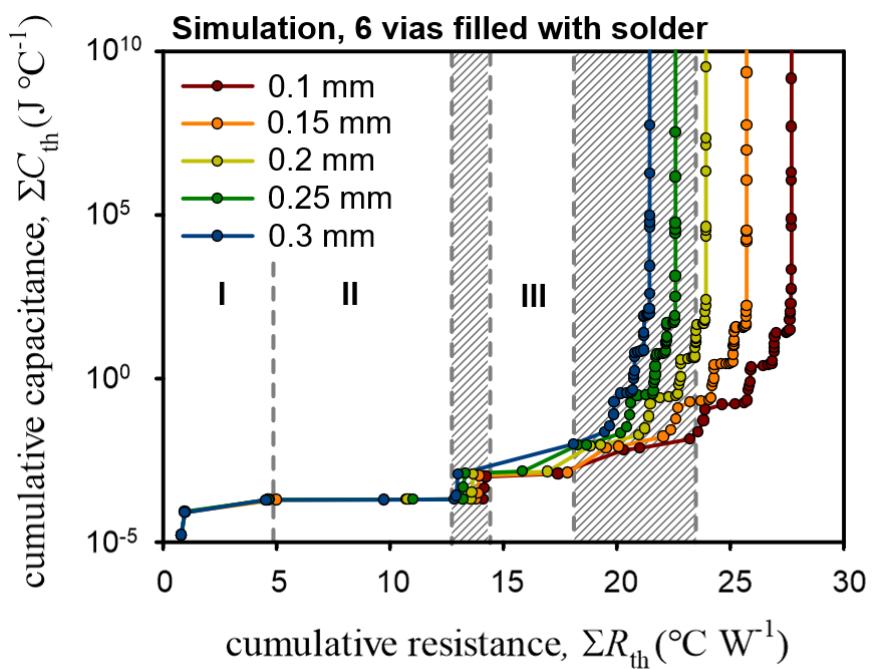

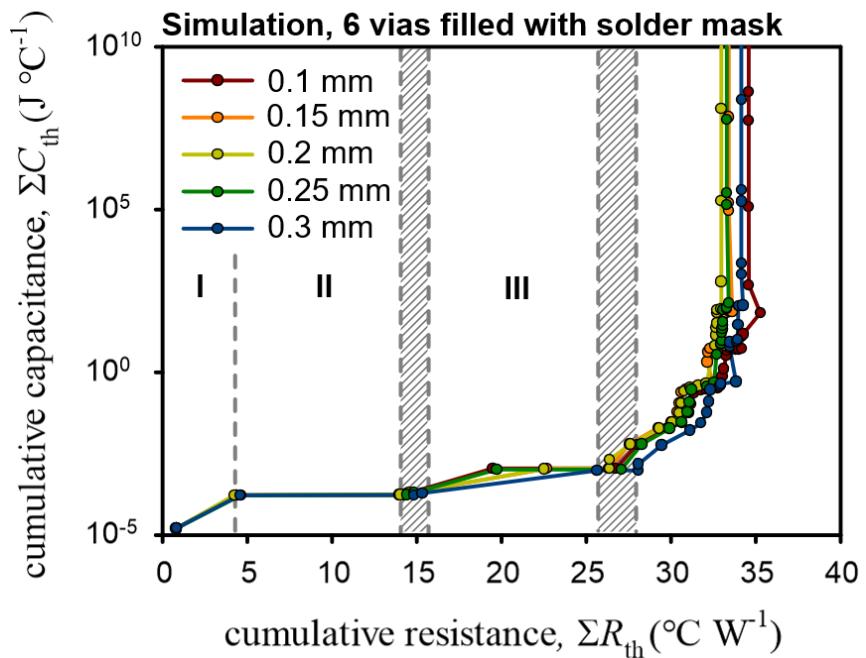

| 圖 3.12 6 個熱通孔不同尺寸之結構函數比較 (solder).....    | 77 |

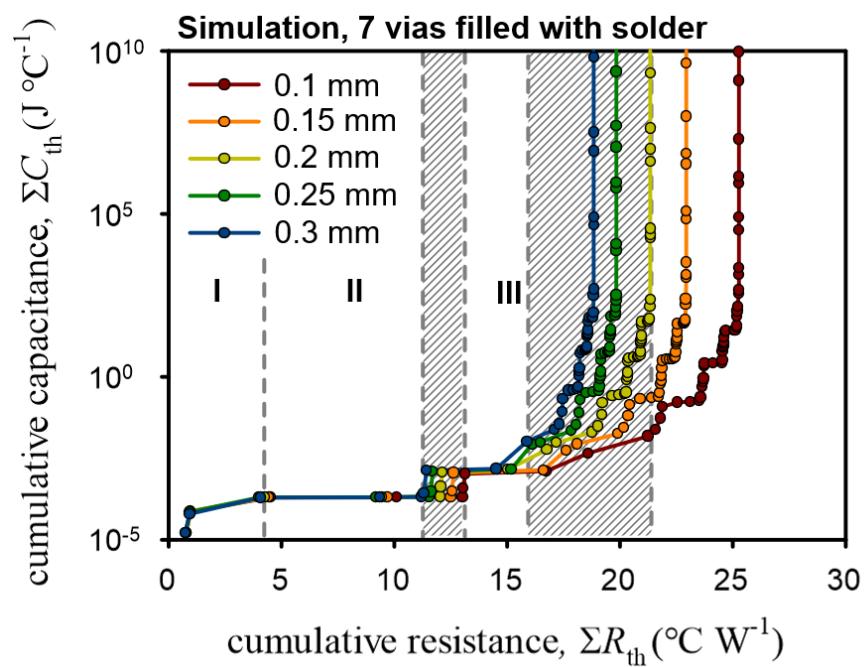

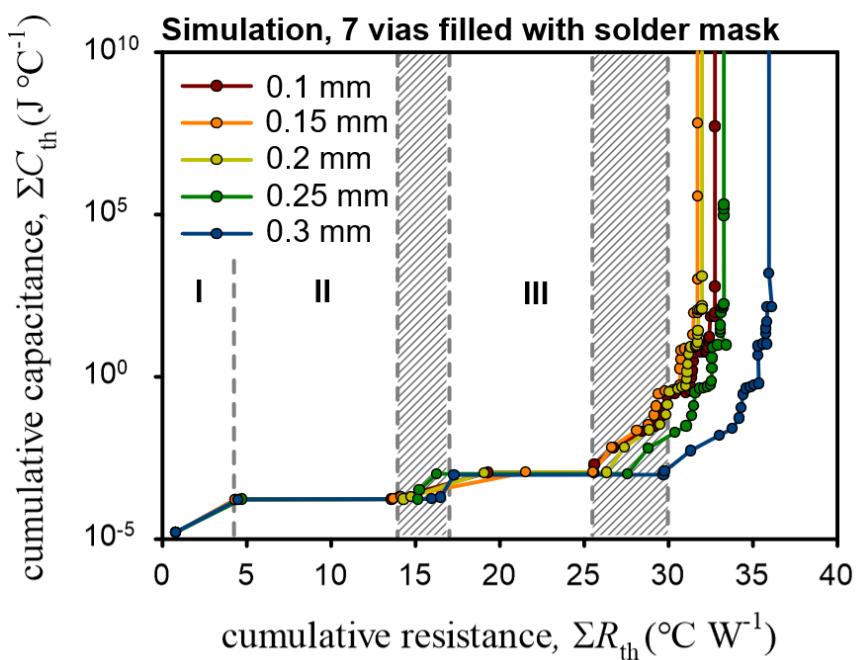

| 圖 3.13 7 個熱通孔不同尺寸之結構函數比較 (solder).....    | 77 |

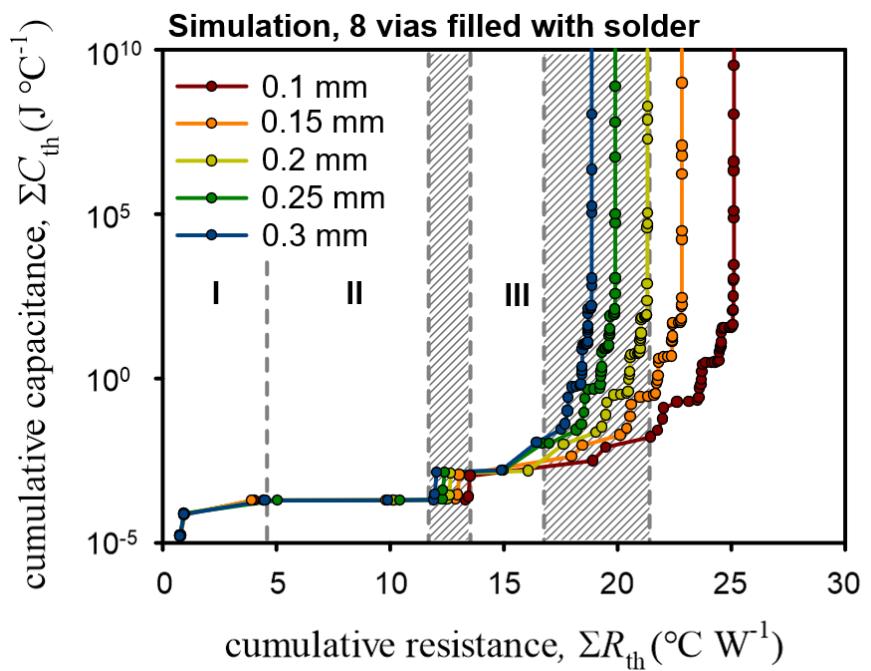

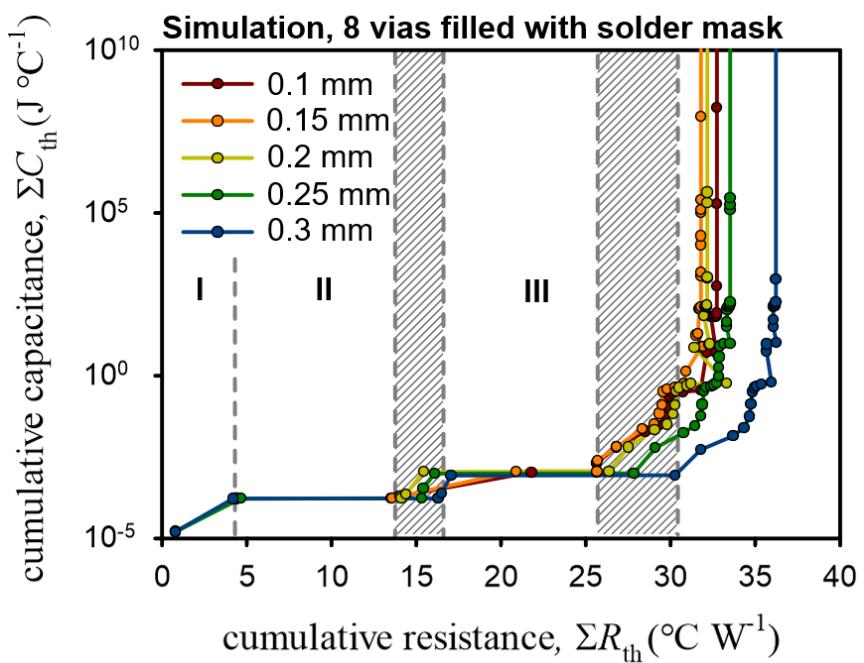

| 圖 3.14 8 個熱通孔不同尺寸之結構函數比較 (solder).....    | 78 |

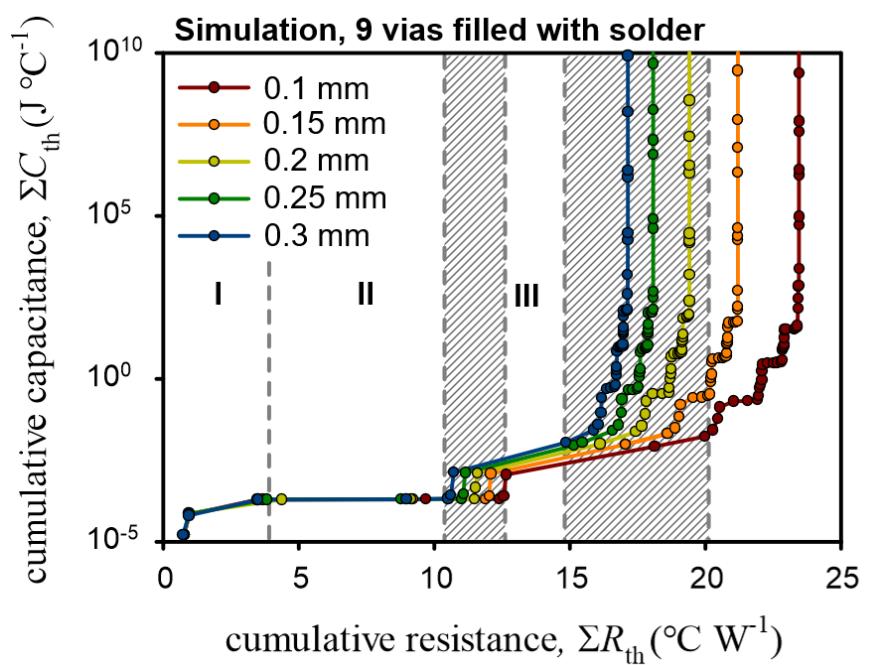

| 圖 3.15 9 個熱通孔不同尺寸之結構函數比較 (solder).....    | 78 |

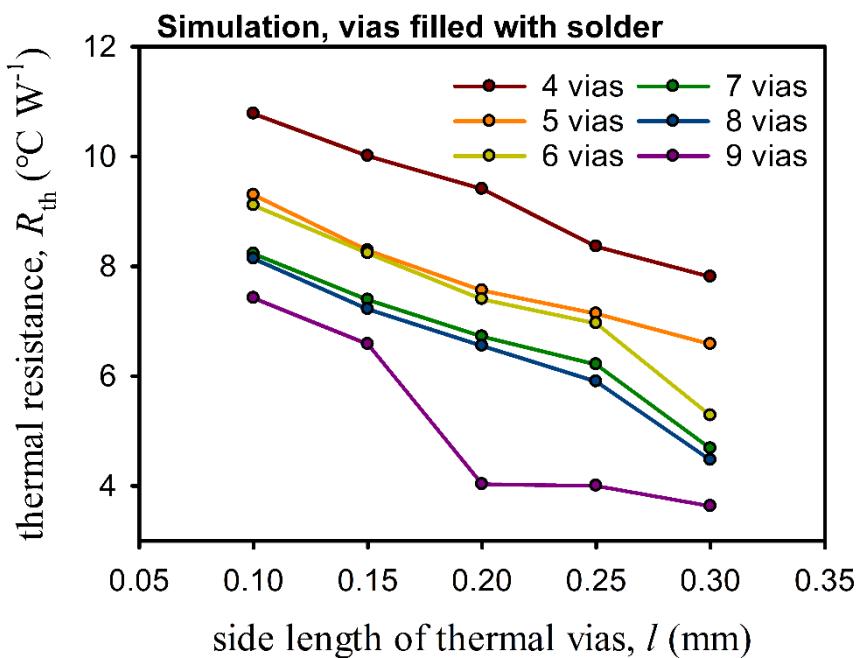

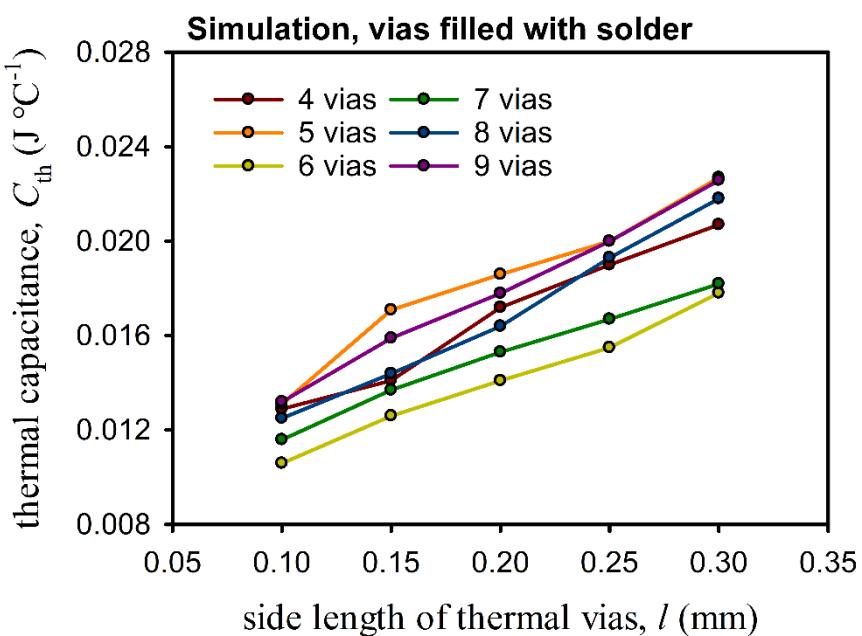

| 圖 3.16 不同熱通孔尺寸之 PCB 層熱阻比較 (solder).....   | 79 |

| 圖 3.17 不同熱通孔尺寸之 PCB 層熱容比較 (solder).....   | 79 |

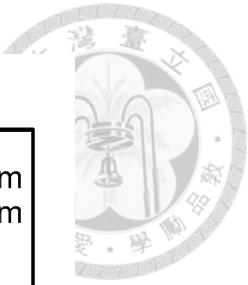

| 圖 3.18 不同熱通孔數目之 PCB 層熱阻比較 (solder).....   | 80 |

| 圖 3.19 不同熱通孔數目之 PCB 層熱容比較 (solder).....   | 80 |

| 圖 3.20 PCB 層之熱阻數值熱圖 (solder).....         | 81 |

| 圖 3.21 PCB 層之熱容數值熱圖 (solder).....         | 81 |

| 圖 3.22 4 個熱通孔不同尺寸之結構函數比較 (air).....       | 82 |

| 圖 3.23 5 個熱通孔不同尺寸之結構函數比較 (air).....       | 82 |

| 圖 3.24 6 個熱通孔不同尺寸之結構函數比較 (air).....       | 83 |

| 圖 3.25 7 個熱通孔不同尺寸之結構函數比較 (air).....       | 83 |

| 圖 3.26 8 個熱通孔不同尺寸之結構函數比較 (air).....       | 84 |

| 圖 3.27 9 個熱通孔不同尺寸之結構函數比較 (air).....       | 84 |

|                                              |    |

|----------------------------------------------|----|

| 圖 3.28 不同熱通孔尺寸之 PCB 層熱阻比較 (air).....         | 85 |

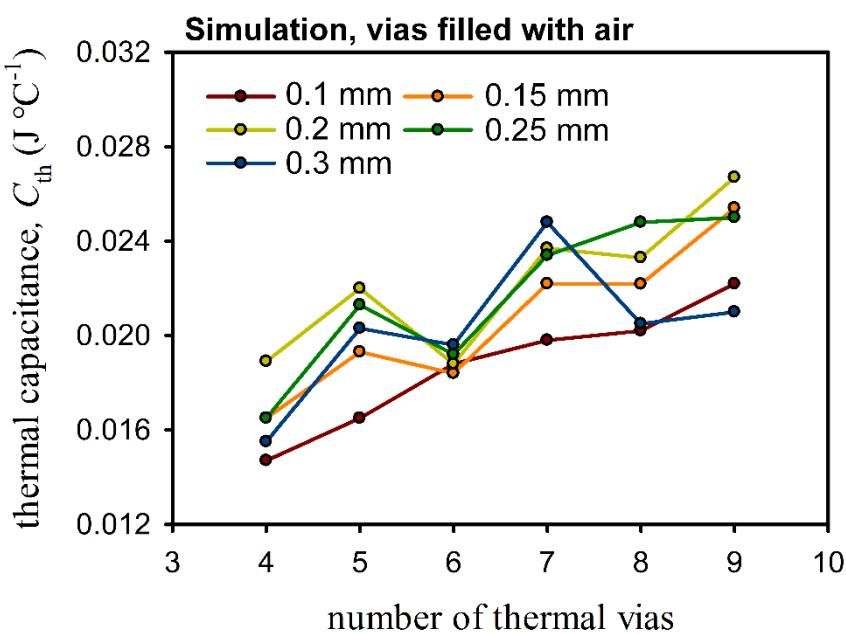

| 圖 3.29 不同熱通孔尺寸之 PCB 層熱容比較 (air).....         | 85 |

| 圖 3.30 不同熱通孔數目之 PCB 層熱阻比較 (air).....         | 86 |

| 圖 3.31 不同熱通孔數目之 PCB 層熱容比較 (air).....         | 86 |

| 圖 3.32 PCB 層之熱阻數值熱圖 (air) .....              | 87 |

| 圖 3.33 PCB 層之熱容數值熱圖 (air) .....              | 87 |

| 圖 3.34 4 個熱通孔不同尺寸之結構函數比較 (solder mask) ..... | 88 |

| 圖 3.35 5 個熱通孔不同尺寸之結構函數比較 (solder mask) ..... | 88 |

| 圖 3.36 6 個熱通孔不同尺寸之結構函數比較 (solder mask) ..... | 89 |

| 圖 3.37 7 個熱通孔不同尺寸之結構函數比較 (solder mask) ..... | 89 |

| 圖 3.38 8 個熱通孔不同尺寸之結構函數比較 (solder mask) ..... | 90 |

| 圖 3.39 9 個熱通孔不同尺寸之結構函數比較 (solder mask) ..... | 90 |

| 圖 3.40 不同熱通孔尺寸之 PCB 層熱阻比較 (solder mask)..... | 91 |

| 圖 3.41 不同熱通孔尺寸之 PCB 層熱容比較 (solder mask)..... | 91 |

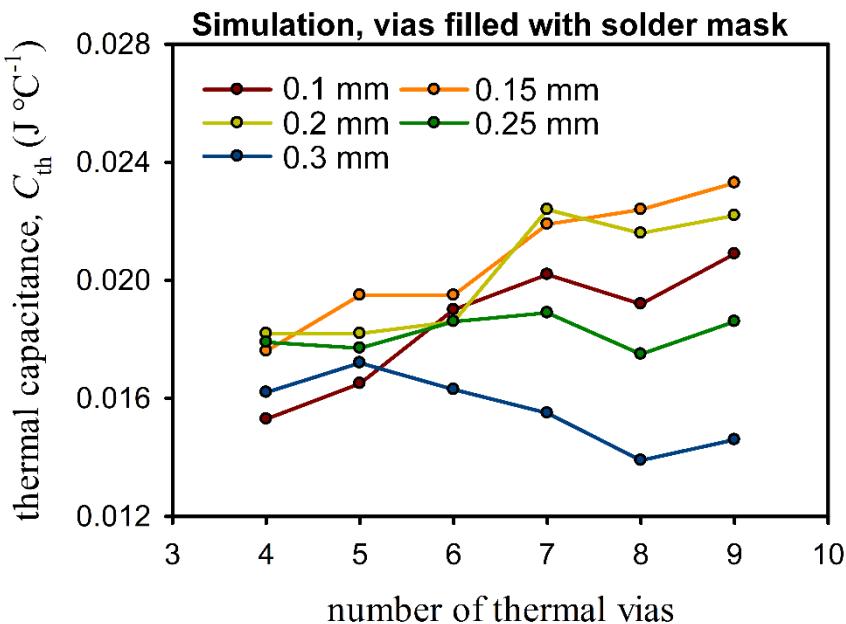

| 圖 3.42 不同熱通孔數目之 PCB 層熱阻比較 (solder mask)..... | 92 |

| 圖 3.43 不同熱通孔數目之 PCB 層熱容比較 (solder mask)..... | 92 |

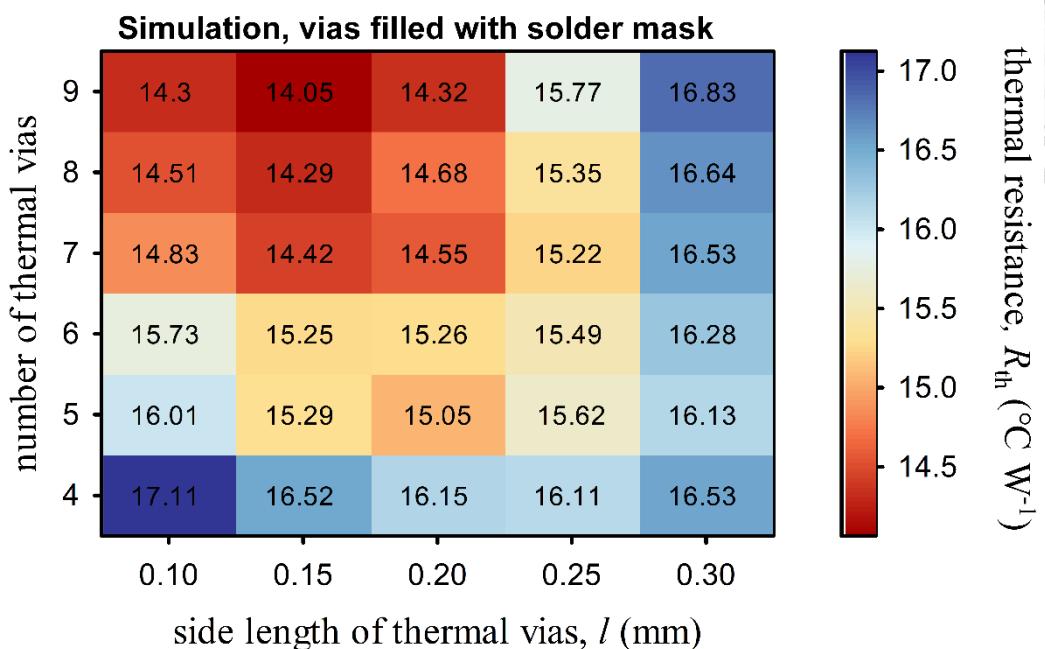

| 圖 3.44 PCB 層之熱阻數值熱圖 (solder mask).....       | 93 |

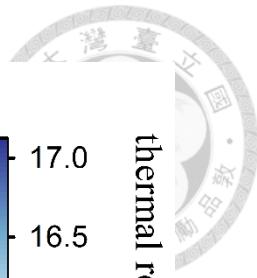

| 圖 3.45 PCB 層之熱容數值熱圖 (solder mask).....       | 93 |

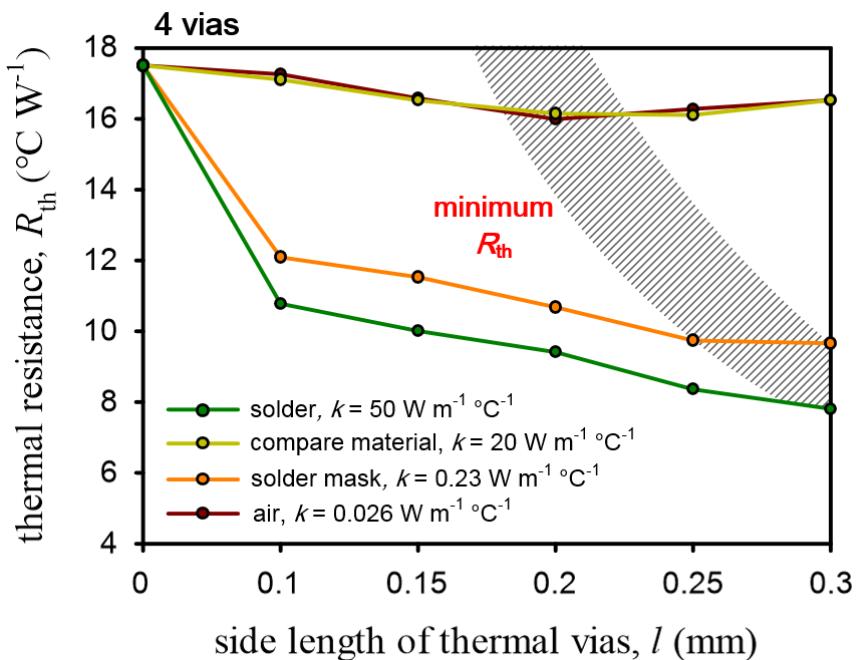

| 圖 3.46 4 個熱通孔不同熱傳導係數之填充物 PCB 層熱阻比較.....      | 94 |

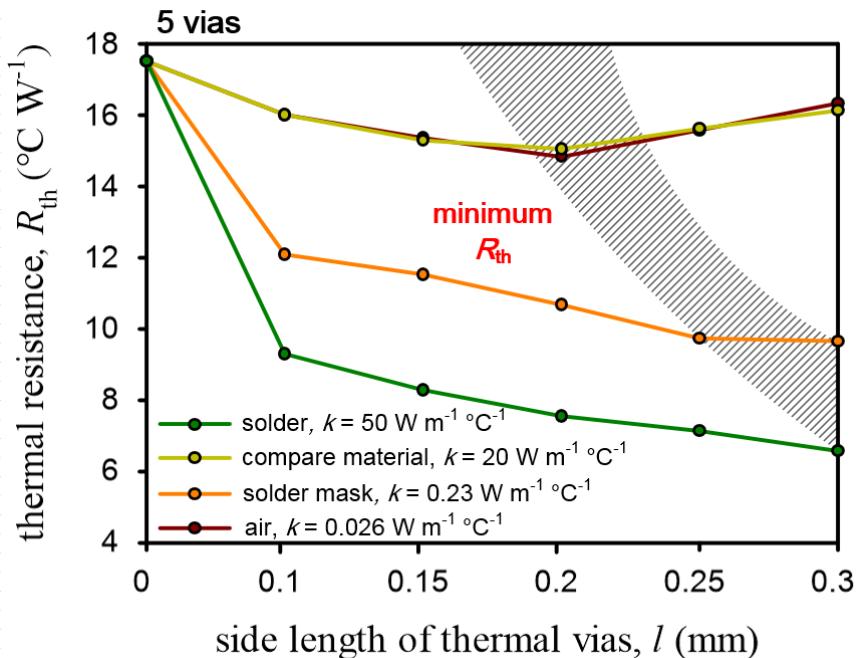

| 圖 3.47 5 個熱通孔不同熱傳導係數之填充物 PCB 層熱阻比較.....      | 94 |

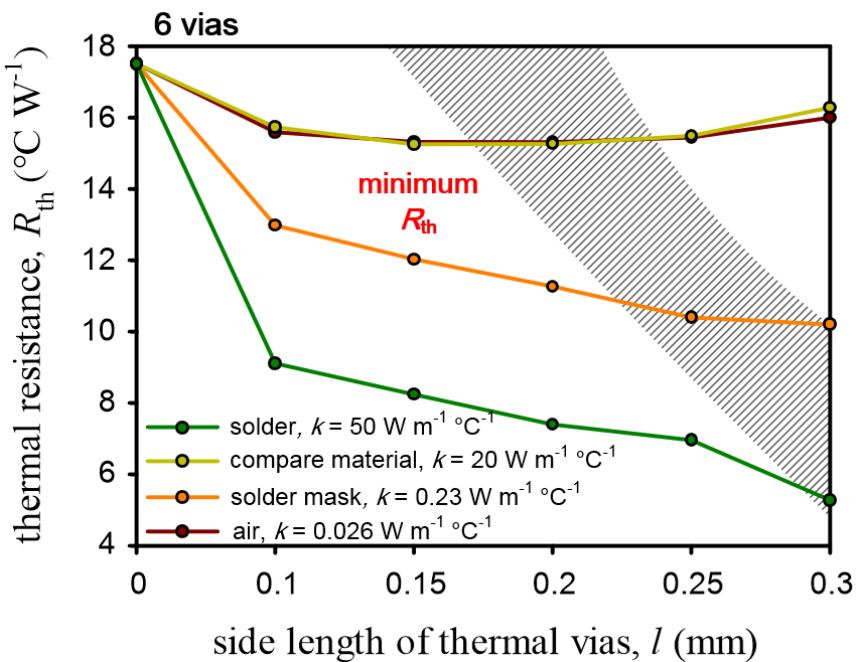

| 圖 3.48 6 個熱通孔不同熱傳導係數之填充物 PCB 層熱阻比較.....      | 95 |

| 圖 3.49 7 個熱通孔不同熱傳導係數之填充物 PCB 層熱阻比較.....      | 95 |

|                                         |    |

|-----------------------------------------|----|

| 圖 3.50 8 個熱通孔不同熱傳導係數之填充物 PCB 層熱阻比較..... | 96 |

| 圖 3.51 9 個熱通孔不同熱傳導係數之填充物 PCB 層熱阻比較..... | 96 |

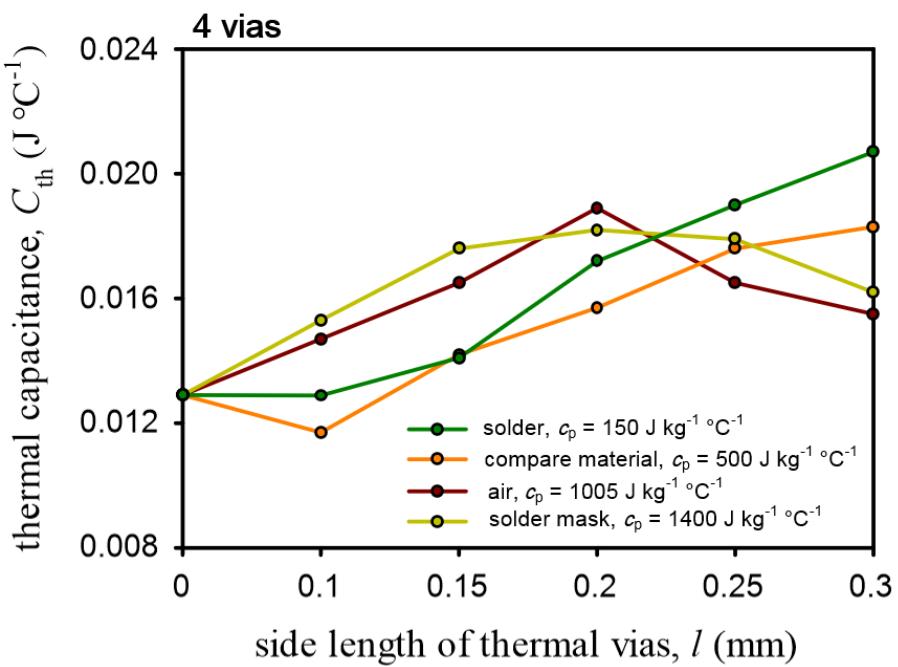

| 圖 3.52 4 個熱通孔不同比熱之填充物 PCB 層熱容比較 .....   | 97 |

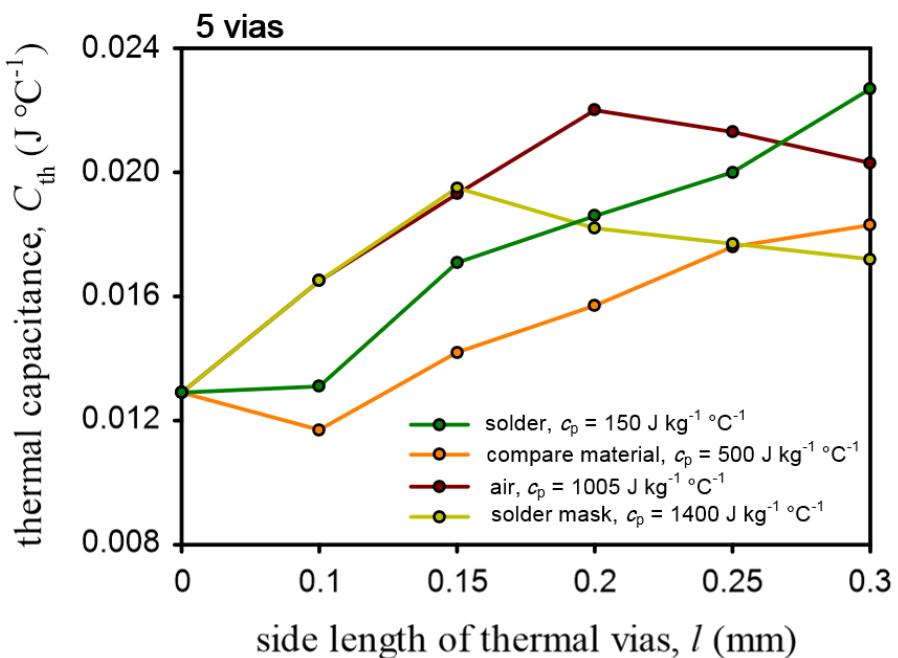

| 圖 3.53 5 個熱通孔不同比熱之填充物 PCB 層熱容比較 .....   | 97 |

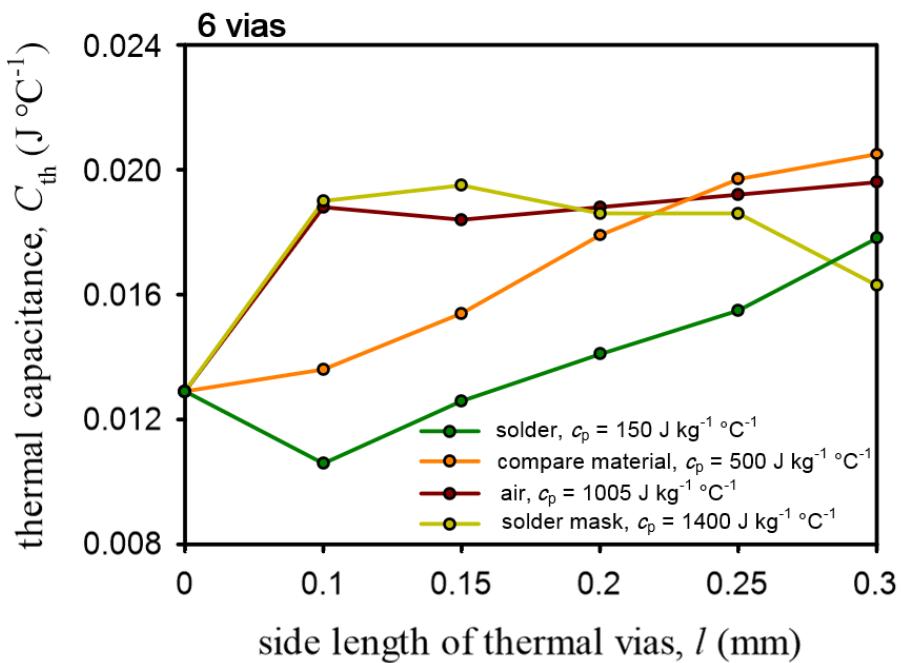

| 圖 3.54 6 個熱通孔不同比熱之填充物 PCB 層熱容比較 .....   | 98 |

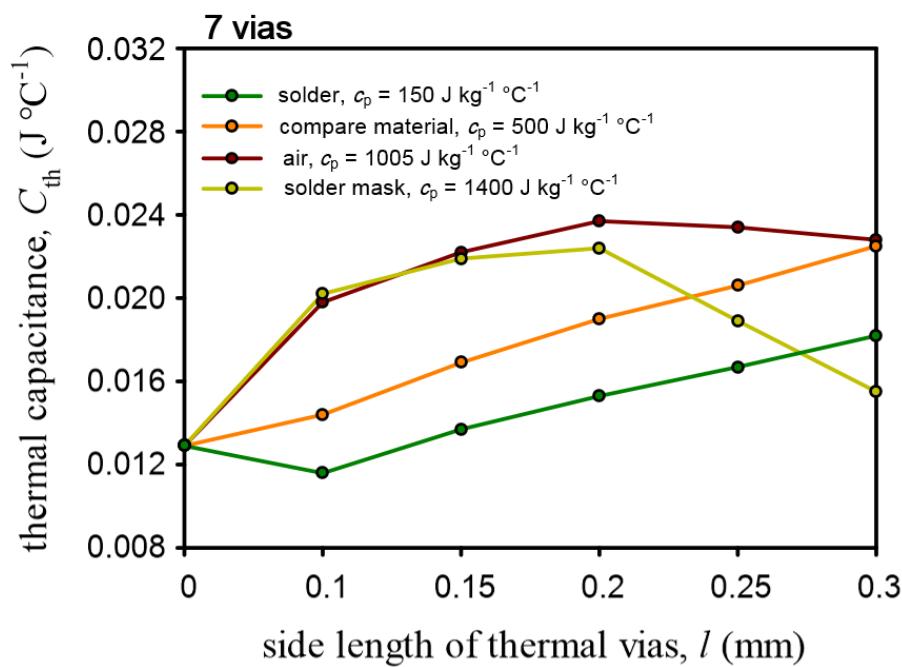

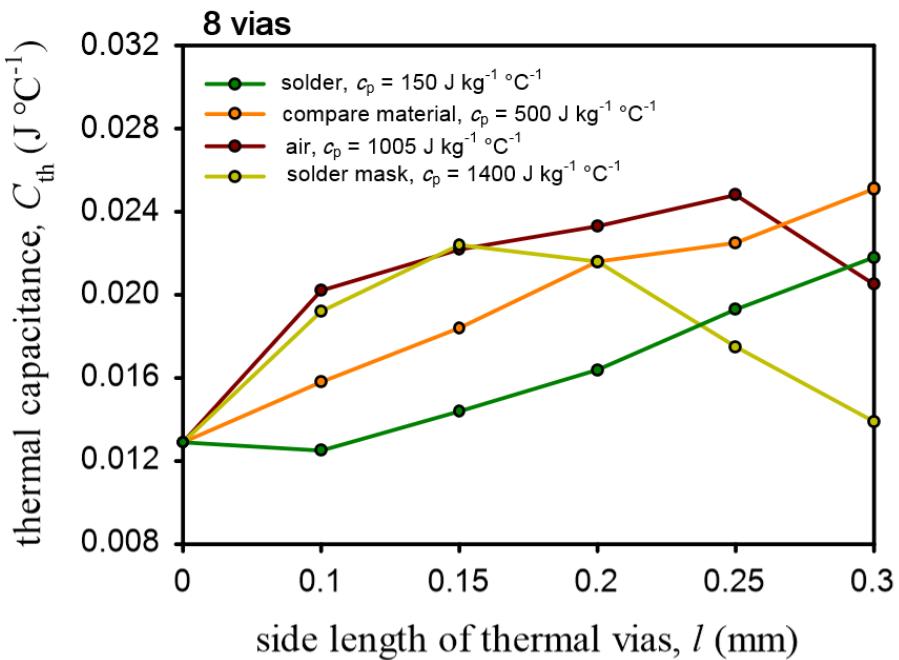

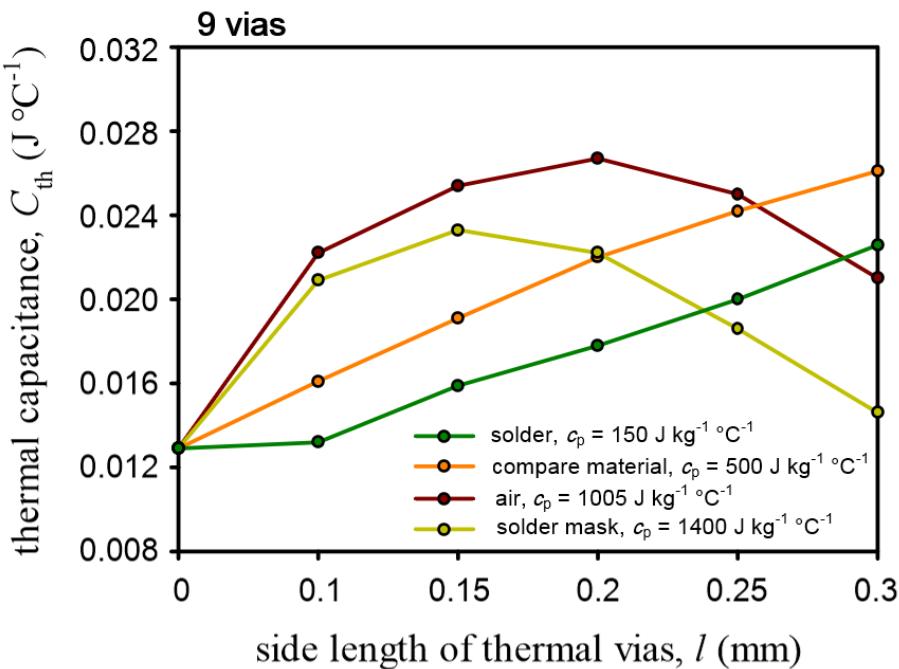

| 圖 3.55 7 個熱通孔不同比熱之填充物 PCB 層熱容比較 .....   | 98 |

| 圖 3.56 8 個熱通孔不同比熱之填充物 PCB 層熱容比較 .....   | 99 |

| 圖 3.57 9 個熱通孔不同比熱之填充物 PCB 層熱容比較 .....   | 99 |

# 第一章 導論

## 1.1 前言

近年來無線通訊於 5G 通訊、Wi-Fi 無線網路、智慧家庭產品及物聯網等應用迅速成長，功率放大器 (power amplifier, PA) 為無線傳輸發射模組中的重要元件，且技術需求的增加使功率密度大幅增加[1]。在高頻與電壓操作條件下砷化鎵 (gallium arsenide, GaAs) 功率放大器的結溫 (junction temperature) 大幅增加，進而影響放大器之轉換效率，因此改善半導體封裝中熱傳遞路徑熱阻值較大的材料層，解決結溫過高所致之影響已成為重要的課題[2, 3]。傳統穩態熱阻的量測方法僅能得到單一整體阻值，無法得知詳細熱傳路徑中的瓶頸，結構函數 (structure function) 則以一維暫態熱傳導模型將，並以熱網絡模型 (thermal network) 的方式將熱傳遞細節完整提取熱傳遞細節完整提取。若能透過改變熱阻值較大的材料層設計，即可使結溫熱源迅速且均勻地傳遞至指定散熱區域。

功率放大器元件的封裝熱阻僅與材料與其幾何形狀相關，外在的散熱條件不影響分層熱阻與熱容的大小，因此結接面至封裝層或 PCB 層 (printed circuit board) 的熱阻被作為衡量熱量消散的能力指標。獲取結接面至 PCB 板的熱阻常使用的方法為雙介面測試法 (dual interface test)，使用不同熱傳導係數 (thermal conductivity) 的導熱墊 (thermal pad) 與 PCB 板接觸，改變穩態下的總熱阻，使阻抗曲線在導熱片接觸層產生明顯差異，曲線中分離的起始點即為接觸面，可用以獲取結接面至 PCB 板的總熱阻[4]。

在積體電路 (integrated circuit, IC) 封裝中，導熱通孔 (thermal via) 可應用於含有兩層以上之 PCB，將熱量經由熱通孔傳導至 PCB 另一面之銅層上，增加功率

放大器的散熱能力，對於相同尺寸的導熱通孔，熱通孔數量與尺寸的增加可有效降低整體熱阻[5]。因此本研究使用雙介面測試法，利用結構函數解析 IC 封裝中各分層材料的熱阻與熱容，搭配數值模擬與市售 IC 封裝暫態熱特性測試的儀器 T3ster [6] 代測結果驗證，並探討不同熱通孔的 PCB 分層所造成之熱傳影響，藉以獲得最佳化之封裝結構與熱通孔設計，作為優化散熱之參考依據。

## 1.2 文獻回顧

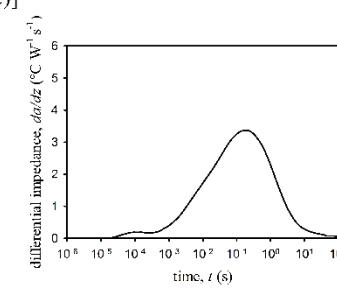

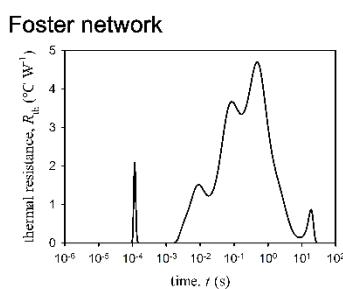

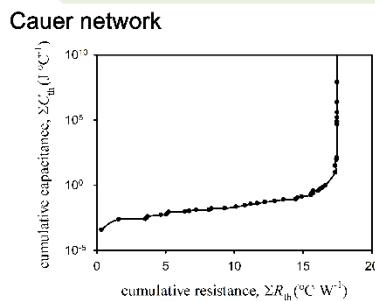

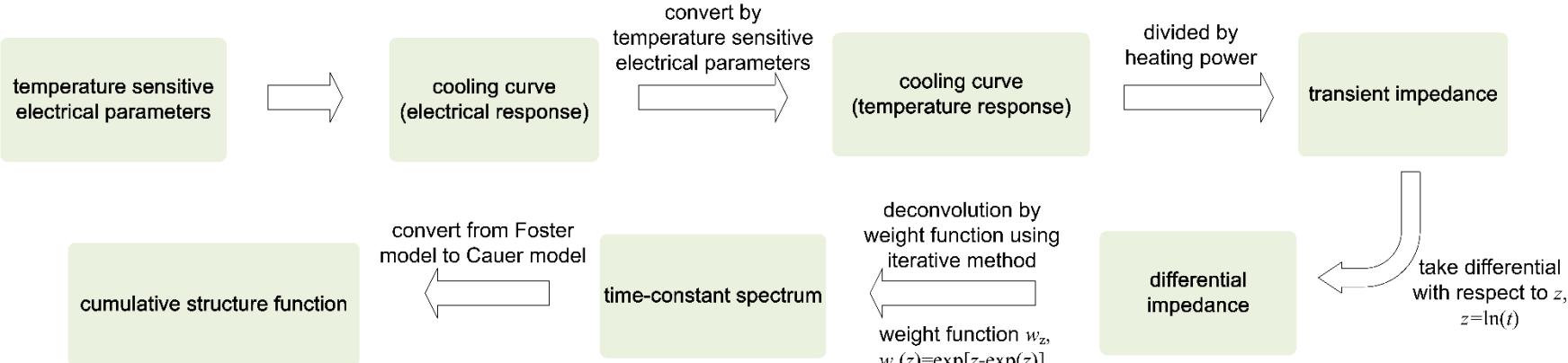

結構函數的獲取過程包含結溫的量測，將實驗量測得到的結溫與加熱功率相除得到暫態熱阻，並以數值微分 (numerical differentiation) 得到暫態熱阻在自然對數時間域的微分結果，利用反卷積 (deconvolution) 將暫態熱阻的微分轉換為時間常數波譜 (time-constant spectrum)，時間常數波譜的熱阻即為 Foster 热網絡模型，最後將 Foster 热網絡模型轉換為 Cauer 热網絡模型，並將 Cauer RC 對加總後即為結構函數。

從上述可知，結構函數的結果準確度主要受量測方法與演算法過程優化的影响，獲取結構函數牽涉微分與其他複雜的計算過程，錯誤的量測方法與計算過程將導致誤差傳播與放大，進而影響結果。因此本節將針對以下部分進行文獻回顧：結溫量測方法、暫態熱阻與結構函數、反卷積網絡識別法、Cauer 網絡模型轉換對結果之影響與結構函數透過模擬之校正，並進行熱通孔對熱阻影響之文獻回顧。

### 1.2.1 結溫量測方法

傳統的量測方法如熱電偶 (thermocouple)、紅外線熱像儀 (infrared thermal imager) 與其他接觸式或光學式量測方法僅能獲取封裝表面的溫度，並無法取得發熱半導體元件內部的正確結溫[7]。Xi 與 Schubert [8] 利用電晶體順向電壓 (forward

voltage) 與溫度之間的線性關係，以實驗控制環境溫度方式量測順向電壓，驗證 GaN 電晶體之結溫變化。Sathik 等人[9] 整理了絕緣柵雙極晶體管 (insulated gate bipolar transistor, IGBT) 的多種溫度敏感電性參數 (temperature sensitive electrical parameters, TSEP)，利用順向電壓、閥值電壓、飽和電流等參數進行結溫的量測，其中以高線性度的順向電壓量測法最為簡單，且電壓僅為溫度之函數，不受其他參數影響。Blackburn 與 Berning[10] 提出將功率電晶體以等效以二極體的方式量測順向電壓，在實驗流程中使用控制溫度之熱沉 (heat sink) 調整環境溫度並記錄電壓，所供給之量測電流以不影響整體溫度的毫安培等級為主，實驗中為確保熱沉與待測樣品間的熱平衡，每個溫度點的量測時間都為 15 分鐘以上。

### 1.2.2 暫態熱阻與結構函數

Diebold 與 Luft [11] 提出利用暫態熱阻來量化半導體元件元件的散熱能力，並以解析解計算不同封裝材料及尺寸的阻抗與其對應之散熱時間尺度，將結溫控制在安全使用範圍的極限。Jakopovic 等人[12] 以實驗量測金屬氧化物半導體場效電晶體 (metal oxide semiconductor field effect transistor, MOSFET) 與 IGBT 的暫態熱阻，發現量測結溫的方式應選擇較穩定的降溫過程而非升溫過程，並以暫態熱阻建構一簡單的熱網絡模型。

Székely[13, 14] 首次提出結構函數的概念，從數學方法中利用反卷積網絡識別 (network identification by deconvolution, NID)，將時間域或頻率域之暫態熱阻響應進行資料處理，以獲得晶片至環境之熱結構的時間常數波譜，並進一步轉換成以一維結構分層來描述三維物理結構的熱傳導路徑，生成階梯熱網絡模型 (ladder network) 來應用於電路模擬中，納入熱電耦合效應以增加模擬之正確性。Székely [15] 亦對電晶體進行暫態量測以提取結構函數，並利用解析解確認實驗結果的正

確性與可行性。

### 1.2.3 反卷積網絡識別

為獲取正確的結構函數，演算法的過程中必須先獲得正確的離散時間常數波譜，而時間常數波譜為微分暫態熱阻與權重函數 (weight function) 進行反卷積 (deconvolution) 之結果，反卷積的計算過程為影響結果正確性最重要的因素。Székely[16] 以傅立葉轉換 (Fourier transform) 將時間域的資料轉換至頻率域，並進行計算以獲得時間常數波譜，然而此方法對實驗原始數據的雜訊干擾相當敏感，須將數據以 Fermi-Dirac 濾波器搭配合適的參數進行調整，才得以獲得正確的時間常數波譜[4]。Kennett 等人[17] 從貝氏定理 (Bayes' theorem) 發展出以條件機率計算之反卷積法，利用迭代方式所得的結果恆為正值，符合實際現象中熱阻恆為正的情況且能減少雜訊對結果的影響，使用上更為容易且正確。Dey 等人[18] 探討迭代的次數與結果的正確性，發現迭代次數的增加以緩慢的速度收斂至正確的結果並再次發散，因此提出一收斂的停止迭代標準。Bissuel 等人[19] 探討迭代次數對時間常數的影響，並以不同迭代次數比較波譜的結果，發現迭代次數須至少為數萬次才得以獲得在電子封裝散熱行為中有明顯意義的時間常數。Dupuis 等人[20] 將反卷積所得到的熱阻值與時間常數，相除後獲得熱容值，以反卷積所得的熱阻與熱容重建暫態熱阻抗響應，並與實驗所得結果以及解析解之暫態阻抗比較，確認貝氏反卷積的正確性及可行性。

### 1.2.4 Cauer 網絡模型轉換

Foster 網絡為一理想的熱傳遞模型，熱流從輸入端輸入的同時以相同大小的熱流離開網絡的輸出端，並不符合實際現象中熱流從晶片傳遞至冷卻熱沉會有一特

徵時間常數 (characteristic time constant) 的延遲[21]。Cauer 網絡模型是透過各分層逐一傳遞熱量，熱量經過特徵時間的延遲後傳遞至熱沉，能夠描述實際的物理現象。但 Cauer 網絡模型的獲取較 Foster 網絡更複雜，在廠商提供的數據資料中的熱阻模型常以 Foster 參數表示，需另外透過 Foster 與 Cauer 模型間的轉換，獲得符合物理現象的完整描述[22, 23]。Foster 與 Cauer 模型的轉換牽涉上百個 RC 對的計算，越多對的數量所獲得的分層熱阻與熱容有較高的分辨率，因此在轉換過程中對數值計算的精度與計算時間需求，以一般計算軟體所使用之雙精度浮點數計算小於 15 對之 Foster RC 模型的轉換效果很好，但增加至上百個 RC 對的轉換時，則需使用多精度運算，可利用多精度運算庫 (GNU multiple precision arithmetic library, GMP) 以拓展算術精度，得到更精確的分層熱網絡模型資訊[4, 24]。

### 1.2.5 結構函數校正

Kim 與 Yoon[25] 在實驗中由於時間量測上的限制，使訊號在時間尺度較小時沒有數據，因此 Kim 與 Yoon 透過模擬結果代入暫態阻抗曲線在時間尺度較小的值，此方法所獲得之熱阻僅與數值解結果相差 3.8%，故確認了此方法的可行性。Ouyang 等人[26] 以模擬提取覆晶球柵陣列 (flip-chip ball grid array, FCBGA) 之封裝的暫態熱阻，利用模擬所獲得之結構函數，以校正因實驗量測限制或誤差所造成之實驗結果；由於廠商所提供之熱介面材料 (thermal interface material, TIM) 的材料熱力性質經常與實際情形有誤差，且熱介面材料與封裝間的實際尺寸難以確認，因此將實驗與模擬所得之結構函數進行相互迭代校正，以獲得最貼近實際情況之熱網絡模型。Bornoff 與 Vass-Varnai[27] 同樣利用模擬結果校正結構函數，對各分層個別進行模擬參數的調整再與實驗結果比較，並特別在晶片級之時間常數進行微調校準，以提高時間尺度在  $10^{-5}$  s 以下的熱阻與熱容精度。

### 1.2.6 热通孔對熱阻之影響

Beng 等人[28] 對環氧樹脂玻璃纖維 FR-4 (flame resistance-4) 材料之 PCB 板以模擬方式研究不同熱通孔形狀及數量對熱阻的影響，熱通孔可透過鍍銅的高熱傳導係數來增加垂直方向熱傳，鍍銅與傳統 FR-4 材料的熱傳導係數相比約大 1200 倍，藉由熱通孔的數量增加可使更多熱量擴散至 FR-4 底部而提升散熱效率。結果顯示，存在一最佳之熱通孔數量可以最大限度減少 FR-4 PCB 之熱阻約  $8 \text{ }^{\circ}\text{C W}^{-1}$ ，但過多熱通孔數量對於降低結溫並沒有幫助。Texas Instruments [29] 之應用報告書亦提出一設計熱通孔數量之最佳值，以兩層與四層 PCB 板為例，熱通孔數量在增加至一定數量後即不能改善熱阻值，若晶片面積為  $6.45 \text{ mm}^2$  至  $32.25 \text{ mm}^2$ ，則以 5 至 9 個熱通孔為最佳設計，而較大的晶片則可以使用較多的熱通孔。

## 1.3 研究目的

基於以上的文獻回顧，在本研究中我們將建構一暫態熱特性量測平台，包含恆溫熱沉、電壓與電流供應器及暫態資料擷取器，對功率放大器產品進行溫度敏感參數的校正、暫態溫度響應量測。從降溫曲線經反卷積網絡識別得到結構函數，即可轉換為熱阻與熱容關係，從中識別 IC 封裝不同分層的物理特性。接續以數值模擬獲得  $10^{-5} \text{ s}$  以下之結果，進一步針對不同熱通孔的填充物、數量及尺寸進行數值模擬，並同樣透過結構函數獲得分層的熱阻與熱容。實驗方法與結果將有助於瞭解功率放大器晶片封裝與設計對熱特性的影響，並進一步將熱模型用於後續設計上的改良。

## 第二章 實驗架構與不確定性分析

### 2.1 實驗架構

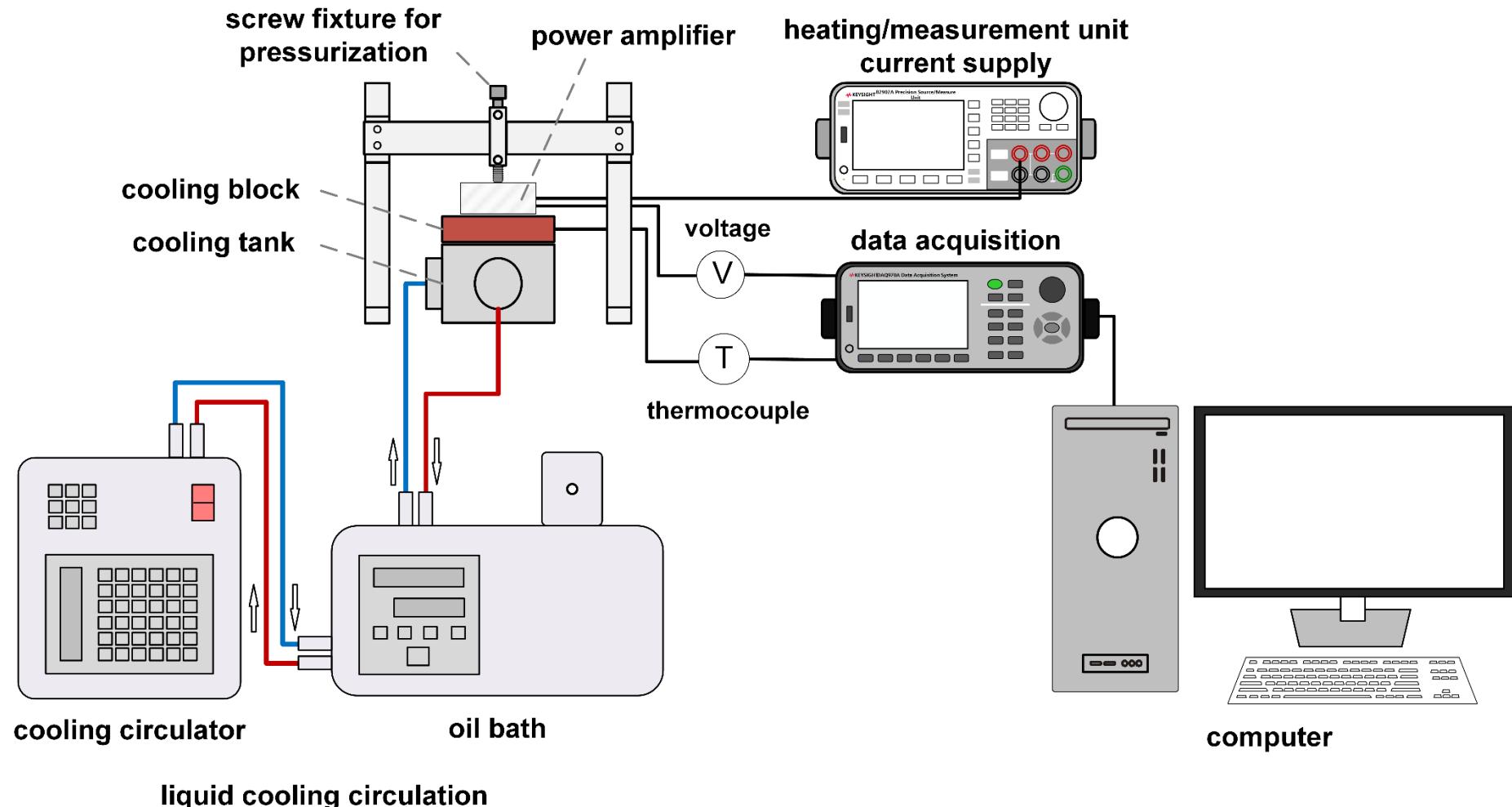

本研究之實驗架構如圖 2.1 所示，主要可分為兩大部份：溫控平台與加壓治具、高精度電源供應與電壓量測系統。實驗首先進行順向電壓與溫度的校正，利用溫控平台中的加熱系統與冷卻系統控制整體環境溫度，將待測之功率放大器晶片與不同熱傳導係數的導熱墊，放置在溫控水冷平台上方，以加壓治具固定，並給予一感應電流 (sensing current)，記錄不同環境溫度下順向電壓的變化。接續給予感應電流與加熱電流 (heating current)，當順向電壓到達穩態後關閉加熱電流，以資料擷取器紀錄順向電壓隨時間的變化。待實驗完成後，將結果進行後續資料處理以獲得所需之熱阻與熱容關係。

#### 2.1.1 溫控平台與加壓治具

為了要分辨熱傳遞至 PCB 與溫控平台接觸面時，在暫態阻抗曲線中對應的熱阻值，在此實驗使用不同熱傳導係數的導熱墊，使阻抗曲線在導熱片接觸層產生明顯差異，曲線中分離的起始點即為 PCB 與溫控平台之間的接觸面。實驗中所使用之兩種導熱墊分別為熱傳導係數 (thermal conductivity) 為  $4.0 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  之矽膠導熱墊 (thermal pad, TIF<sup>TM</sup>100-40-10F, Ziitek) 與熱傳導係數為  $15.6 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  之矽膠導熱墊 (thermal pad, TPY-NDPB-9020-R1, Cooler Master)，導熱墊尺寸長 30 mm、寬 30 mm、厚 2 mm，且為應用於電子產品之高絕緣材質，並以三用電錶確認晶片與溫控平台接觸面未接通。在加壓後，會導致矽膠導熱墊變形，因此在每次實驗進行前須檢查導熱墊與 PCB 是否正常貼合，確保實驗的準確性。

本研究使用恆溫水冷裝置作為實驗之溫控平台，溫控平台由紅銅 (C1020) 製

成之冷卻塊、鋁合金 (6061) 製成之冷卻槽、恆溫油浴器 (oil bath, B501, FIRSTEK)、低溫循環水槽 (cooling circulator, B402H, FIRSTEK) 所組成，內循環之工作流體為水。透過恆溫油浴器供給穩定的水溫，其溫度操作範圍為 RT+5~200°C，恆溫油浴器無製冷效果，因此低於室溫之冷水需使用低溫循環水槽進行冷卻。校正順向電壓與溫度實驗中，設定恆溫油浴器溫度範圍為 20°C 至 80°C，以 10°C 為間隔調整設定溫度；降溫曲線實驗中設定製冷水槽溫度於 20°C，透過乳膠軟管將冷水送至恆溫油浴器，恆溫油浴器溫度則設定為 25°C，提供功率放大器晶片強制一維熱傳導之冷卻。恆溫油浴器中設有一沉水幫浦，以固定的體積流率將冷卻水供給至冷卻槽，並將循環水導入恆溫油浴器中完成循環。

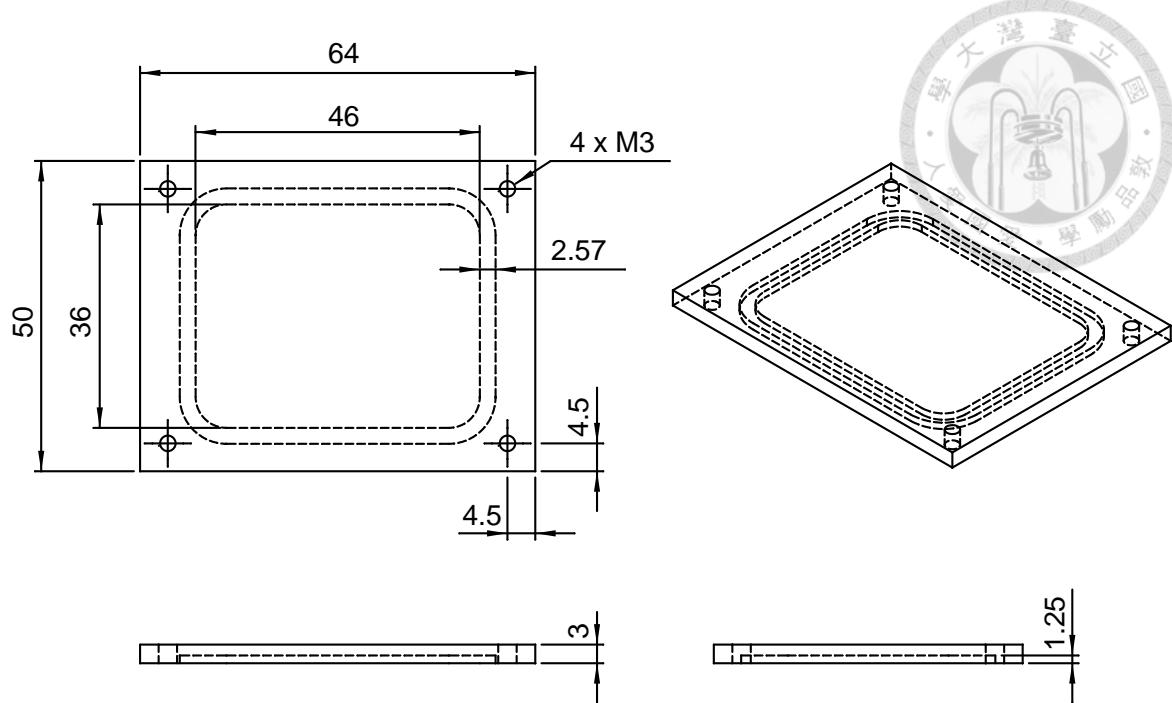

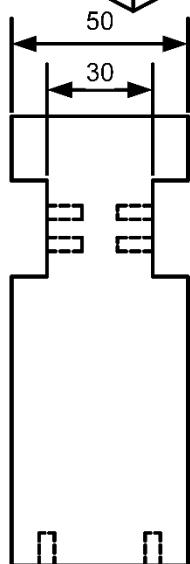

冷卻塊尺寸如圖 2.2 所示，為使功率放大器晶片與溫控平台簡化為垂直方向上的一維熱傳導，冷卻塊使用熱傳導係數為  $391 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  長 64 mm、寬 50 mm、厚 3mm 之紅銅塊，符合 JEDEC standard No.51-14[4] 所規範之冷卻塊材料選擇與厚度規範。為防止冷卻水外漏，冷卻塊底部銑有一寬 2.57 mm、深 1.25 mm 溝槽以放置 O 型環，並於四角落加工直徑 3 mm 螺紋孔，用於與下述之冷卻槽連接。

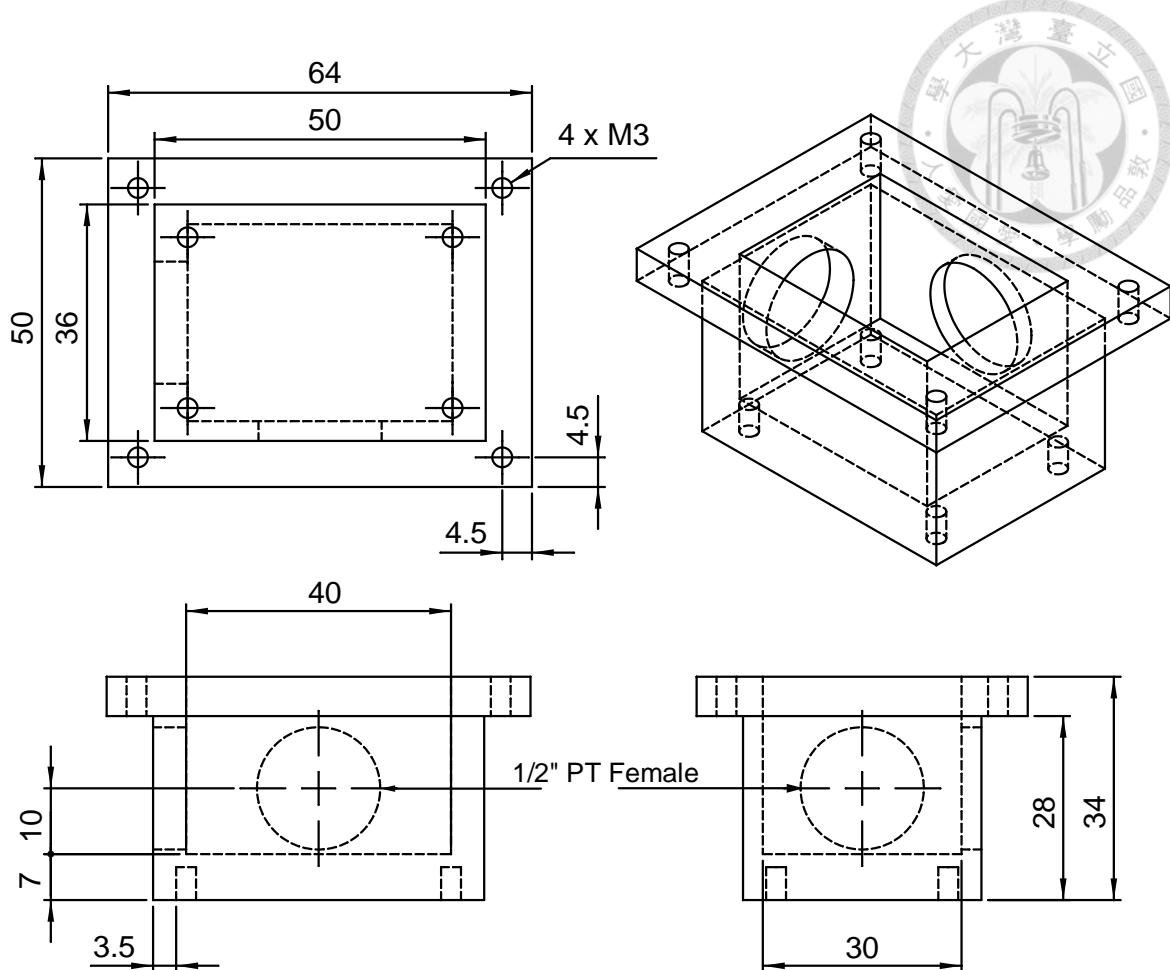

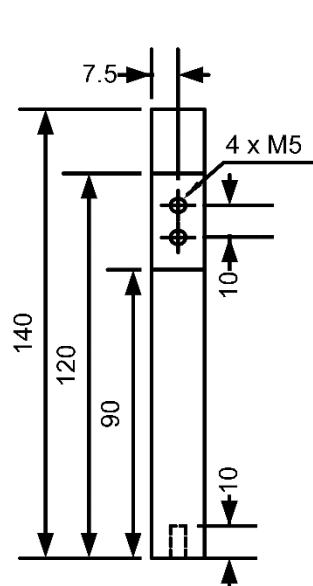

冷卻槽尺寸如圖 2.3 所示，長 64 mm、寬 50 mm、高 34 mm 的冷卻槽為鋁合金所製成，並在中心銑有一長 40 mm、寬 30 mm 之長方形空腔，用來存放恆溫水，四角落加工有直徑 3 mm 螺紋孔，用來與冷卻塊連接，相鄰之兩側面攻有 1/2" PT Female 的管牙，用來連接乳膠軟管至恆溫油浴器作為穩定水溫之入水口與出水口。

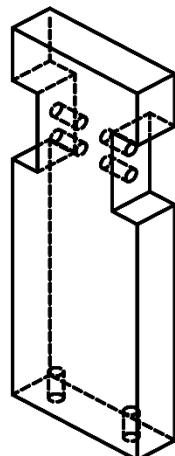

加壓治具的爆炸圖與組裝使用方法如圖 2.4 所示，每一個組件皆由鋁合金 (6061) 所製成，圖 2.5 (a) 為底座的尺寸圖，底座長 100 mm、寬 15 mm、厚 10 mm，底部銑有兩個沉頭直徑 10 mm、深度 5.4 mm，螺紋直徑 5 mm 的沉頭孔，以及兩個直徑 5 mm 螺紋孔，用以與側邊支撐柱組裝。圖 2.5 (b) 為側邊支撐柱的尺寸圖，

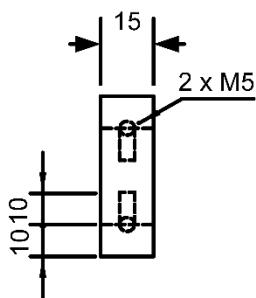

支撐柱長 50 mm、寬 15 mm、高 140 mm，在支撐柱兩側銑有長 30 mm、深度 5 mm 的凹槽，並在凹槽內各加工有兩個直徑 5 mm 螺紋孔，用來與滑軌組裝。滑軌尺寸圖如圖 2.6(a) 所示，滑軌長 165 mm、寬 20 mm、厚 5 mm，並在四角落加工直徑 5 mm 螺紋孔，與上述的支撐柱連接。兩滑軌中間有一工字型之組件可調整夾持螺絲至所需夾持位置，工字型組件與固定用零件尺寸如圖 2.6(b)(c) 所示，工字型正中間加工有直徑 5 mm 螺紋貫穿孔，能夠鎖入螺絲作為夾持工具。工字型組件四角落各有直徑 5 mm 的螺紋孔，連接固定用零件以固定夾持位置。依據所需使用長度為 70 mm、直徑 5 mm 的螺絲作為夾持工具，夾持力的控制則使用扭力板手 (adjustable torque screwdriver, QDRIVER4NM, Snap On)，設定扭矩為 5 N cm，以減少導熱墊與 PCB 的接觸熱阻。為避免夾持螺絲與功率放大器晶片之間的熱傳遞以及對晶片之損傷，螺絲頂端使用市售熱傳導係數低的 PVC 螺絲保護套 (polyvinyl chloride screw protector) 保護，使用方法如圖 2.4(b) 所示。

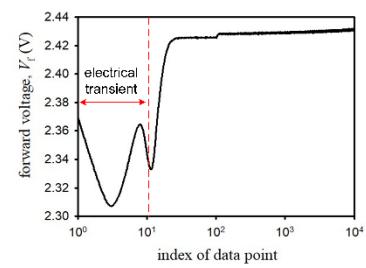

### 2.1.2 精密電源供應與電壓量測系統

結構函數的提取受到原始數據的雜訊與正確性影響甚劇，實驗中功率放大器的順向電壓訊號需穩定且減少雜訊，因此使用精密型電源量測供給設備 (precision source/measure unit, B2902A, Keysight) 來提供雙通道的固定電流源，加熱電流施予 300 mA，感應電流施予 25 mA。電壓的擷取則使用資料擷取器 (data acquisition system, DAQ970A, Keysight) 與 20 通道多工器模組 (20-channel multiplexer module, DAQM901A, Keysight)，將正負極單芯線一端鎖入多工器模組的通道，把多工器模組放入資料擷取器之插槽，正負極單芯線的另一端分別與待測之功率放大器晶片正負極相互接觸並連接。資料擷取器中設定 6.5 位數之數位電表 (digital multimeter, DMM) 為電壓量測模式，並調整量測電壓範圍為 10 V，為獲得溫度敏感參數，電

壓量測的取樣頻率 1 Hz，取樣時間 10 s，並將 10 筆電壓資料取平均，作為該溫度點之順向電壓；降溫曲線之實驗量測取樣頻率設為 20000 Hz、取樣時間 50 s，並將電壓隨時間的變化以 csv 檔案存入 USB 進行後續資料處理。

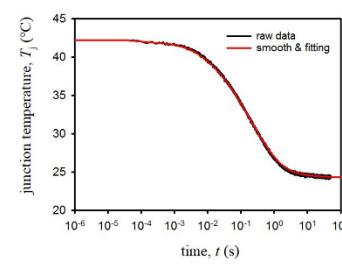

## 2.2 溫度敏感電性參數校正

傳統利用熱電偶或熱像儀的溫度量測方式並無法獲得正確的結溫變化，結溫的正確獲取以順向電壓法最為準確且方便，因此本節將接續以 Shockley equation 公式得到順向電壓與結溫之間的關係，並說明溫度敏感電性參數校正實驗的程序。

### 2.2.1 順向電壓與結溫理論

對於任何 p-n 接面 (p-n junction) 的半導體元件之順向電壓都與溫度呈線性關係，兩參數之間的關係基於 Shockley equation 可表示如式 (2.1) 所示 [30]：

$$I_{pn} = I_{sat} \left[ \exp\left(\frac{qV_f}{k_B T_j}\right) - 1 \right] \quad (2.1)$$

其中  $I_{pn}$  為 p-n 結接面理想電流， $q$  為電子基本電荷 ( $q=1.6\times10^{-19}$  C)， $k_B$  為波茲曼常數 ( $k_B=1.38\times10^{-23}$  J °C<sup>-1</sup>)， $V_f$  為順向電壓， $T_j$  為結溫溫度， $I_{sat}$  為飽和電流 (saturation current)， $I_{sat}$  如式 (2.2) 所示：

$$I_{sat} = I_0 T_j^\gamma \exp\left(-\frac{E_g}{k_B T_j}\right) \quad (2.2)$$

其中  $I_0$  與  $\gamma$  皆為與溫度無關之常數， $E_g$  為半導體材料之能隙。

假設  $I_{pn} \gg I_{sat}$ ，式 (2.1) 可以改寫為：

$$I_{pn} = I_{sat} \exp\left(\frac{qV_f}{k_B T_j}\right) \quad (2.3)$$

將式 (2.2) 與式 (2.3) 整理後可得順向電壓的關係式，如式 (2.4) 所示：

$$V_f = \frac{E_g}{q} + \frac{k_B T_j}{q} \ln \left( \frac{I_{pn}}{I_0} \cdot \frac{1}{T_j^\gamma} \right) \quad (2.4)$$

在固定 p-n 接面電流  $I_{pn}$  的條件下，若將式 (2.4) 對結溫  $T_j$  進行偏微分，則可得

式 (2.5)：

$$\left[ \frac{\partial V_f}{\partial T_j} \right]_{I_{pn}} = -\gamma \frac{k_B}{q} + \frac{\left( V_f - \frac{E_g}{q} \right)}{T_j} \quad (2.5)$$

式 (2.5) 等號左側為順向電壓隨結溫變化的關係，即溫度敏感電性參數  $K_{TSEP}$  的倒數，將式 (2.5) 左右兩側移項並整理後可得：

$$V_f = T_j \left( \frac{1}{K_{TSEP}} + \gamma \frac{k_B}{q} \right) + \frac{E_g}{q} \quad (2.6)$$

式 (2.6) 中，順向電壓對溫度的關係在大範圍的溫度變化下僅有很小的非線性影響，因此對於實際應用常近似為一線性方程式，並可表示為：

$$V_f = \frac{1}{K_{TSEP}} \cdot T_j + C \quad (2.7)$$

其中  $C$  為一常數，而為了方便後續計算將電壓轉換為結溫，將式 (2.7) 整理，把結溫移至等號左側，並整理如式 (2.8) 所示：

$$T_j = K_{TSEP} V_f + T_0 \quad (2.8)$$

其中斜率  $K_{TSEP}$  恒為一負值，結溫的升高會使順向電壓降低， $T_0$  為隨感應電流變化之截距。欲獲得  $K_{TSEP}$  與  $T_0$ ，我們可控制溫控平台的溫度下，給定一感應電流得到該溫度下的順向電壓，即可得到順向電壓與結溫的校正曲線，由於  $K_{TSEP}$  與  $T_0$  隨不同樣品有所差異，因此每一實驗樣品都需要進行  $T_j$  與  $V_f$  之校正。

### 2.2.2 校正實驗程序

電性參數的校準，透過量測不同環境溫度下功率放大器樣品之順向電壓，以獲得溫度敏感電性參數，實驗流程如下所述：

1. 將待測之功率放大器樣品與導熱片放置於溫控平台之冷卻塊上，並以加壓治具以扭力板手設定扭矩為 5 N cm，夾持功率放大器樣品於冷卻塊上，如圖 2.4(b) 所示。功率放大器樣品的輸入端與接地端 (ground) 則分別以單芯線連接資料擷取器。

2. 設定溫控平台溫度為 20°C，在冷卻塊上方放置 T 型熱電偶 (thermocouple wire, TT-T-36-SLE-100, Omega) [31]，並開啟精密型電源量測供給設備，給予功率放大器樣品一固定電壓 5 V，以資料擷取器檢查溫度與電壓訊號是否正確。

3. 利用精密型電源量測供給設備，給予固定在溫控平台上的待測功率放大器樣品 25 mA 的量測電流，待溫控平台溫度及順向電壓穩定後，每秒量測一次順向電壓，記錄 10 s 後將 10 組順向電壓資料點進行平均，即為此溫度下的順向電壓值。

4. 改變溫控平台溫度，以 10°C 為間隔增加溫度，重複以上步驟進行實驗至溫控平台溫度 80°C。

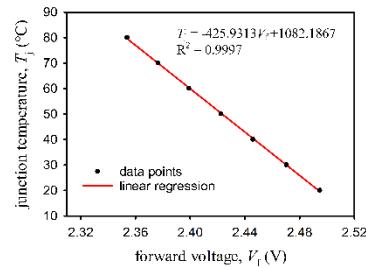

### 2.2.3 校正線性擬合

將校正實驗程序中，固定溫控平台溫度下所測得之 10 組順向電壓資料點進行平均，做為該固定溫度下的平均順向電壓  $V_f$ ，如式 (2.9) 所示：

$$V_f = \frac{1}{10} \sum_{i=1}^{10} V_{f,i} \quad (2.9)$$

其中  $V_{f,i}$  為第  $i$  秒之順向電壓。

利用控制溫控平台溫度下所獲得的平均順向電壓進行線性迴歸 (linear regression)，以最小平方法 (least squares method) 獲得擬合方程式與決定係數 (coefficient of determination) 確認擬合程度，擬合的線性方程式如式 (2.10) 所示：

$$T_j = K_{TSEP} \cdot V_f + T_0 \quad (2.10)$$

其中斜率  $K_{TSEP}$  即為校正所得之溫度敏感電性參數，並可由決定係數  $R^2$  確認擬合程度。本研究所使用的功率放大器樣品的溫度敏感電性參數校準結果如圖 2.7 所示，從  $R^2$  值可知，功率放大器樣品的結溫對電壓的線性擬合程度高。獲得溫度敏感電性參數後，即可以所得之線性方程式得到在特定順向電壓下所對應之結溫，並用以獲得功率放大器樣品的降溫曲線。

## 2.3 結構函數理論

本節將描述結構函數的理論，藉暫態熱阻以數學方式的描述轉換為結構函數，並從實驗獲得暫態熱阻，接續以數值計算方式推算功率放大器晶片之熱網絡模型。

### 2.3.1 反卷積網絡識別

熱阻抗定義為兩等溫面之間的溫度差與熱功率之比值，在熱平衡狀態下熱阻抗即為熱阻，暫態熱阻與到達穩態前兩等溫面之間溫差隨時間的變化有關，熱通量從結接面向外傳遞至溫控水冷裝置的路徑上，受不同層的形狀與材料性質之影響，暫態熱阻可以表示如式 (2.11) 所示：

$$a_{th,j-sink}(t) = \frac{T_j(t) - T_{sink}}{P_{heat}} \quad (2.11)$$

其中  $T_j(t)$  為結溫隨時間之變化， $T_{sink}$  為溫控環境之溫度， $P_{heat}$  為加熱功率。

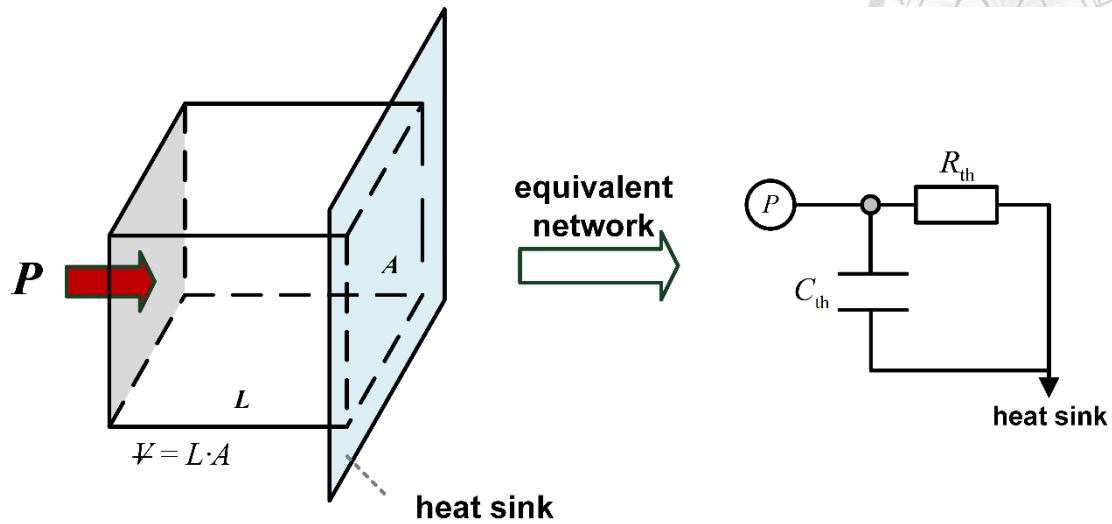

考慮一四面側壁皆為絕熱的長方體，在右方的表面與等溫的熱沉接觸，如圖

2.8 所示，等效熱網絡模型中可簡化為一個熱容與一個熱阻，當給定一固定熱功率時，表面的溫度隨時間之響應可以表示如式 (2.12)所示：

$$T(t) = P_{\text{heat}} \cdot R_{\text{th}} \cdot \left[ 1 - \exp\left(\frac{-t}{\tau}\right) \right] \quad (2.12)$$

其中  $P_{\text{heat}}$  為加熱功率， $R_{\text{th}}$  為熱阻， $\tau$  為熱網絡模型之時間常數 ( $\tau=R_{\text{th}} \cdot C_{\text{th}}$ )，而此時熱阻與熱容的解析解可表示為式 (2.13)與式 (2.14)：

$$R_{\text{th}} = \frac{L}{k \cdot A} \quad (2.13)$$

$$C_{\text{th}} = \rho \cdot V \cdot c_p \quad (2.14)$$

其中  $L$  為材料之邊長長度， $k$  為材料之熱傳導係數， $A$  為材料截面積， $\rho$  為材料密度， $V$  為材料體積， $c_p$  為材料之比熱。

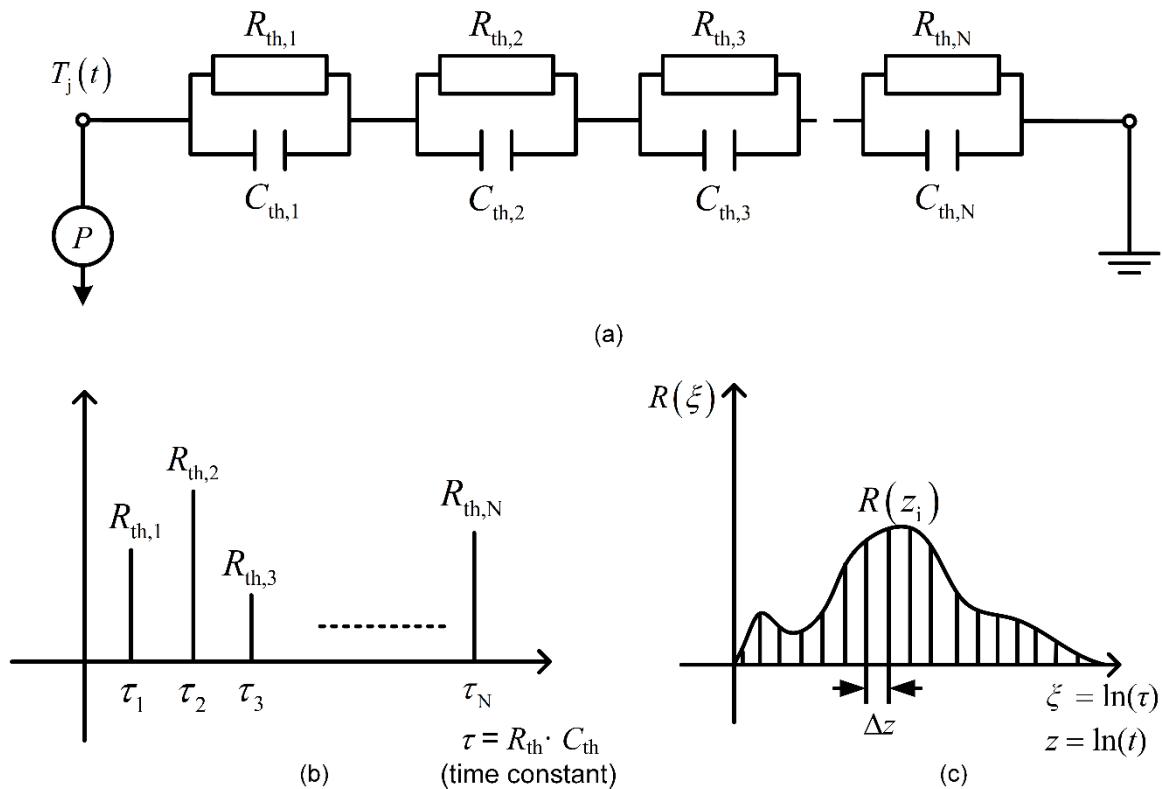

若有  $N$  層材質的長方體相連，則熱網絡模型可簡化為  $N$  個熱阻與熱容的串聯網絡，並以時間常數波譜表示，如圖 2.9 (a)與圖 2.9 (b)所示，溫度隨時間之響應則可以表示為式 (2.15)所示：

$$T(t) = P_{\text{heat}} \cdot \sum_{i=1}^N R_{\text{th},i} \cdot \left[ 1 - \exp\left(\frac{-t}{\tau_i}\right) \right] \quad (2.15)$$

其中  $P_{\text{heat}}$  為加熱功率， $R_{\text{th},i}$  為第  $i$  個熱阻， $\tau_i$  為第  $i$  個時間常數。

得到溫度響應後，則暫態熱阻可以表示為式 (2.16)：

$$a(t) = \sum_{i=1}^N R_{\text{th},i} \cdot \left[ 1 - \exp\left(\frac{-t}{\tau_i}\right) \right] \quad (2.16)$$

對於實際熱網絡模型為連續的時間常數波譜，當  $i$  趨近於無限，離散的 RC 热時間常數可替換為連續模型，實際的暫態熱阻響應可以積分形式表示，如式 (2.17) 所示：

$$a(t) = \int_0^\infty R_{\text{th}}(\tau) \left[ 1 - \exp\left(\frac{-t}{\tau}\right) \right] d\tau \quad (2.17)$$

其中  $R(\tau)$  為時間常數之熱阻波譜。為了能夠精確表達時間常數之波譜，將線性時間尺度轉換為對數時間尺度 (logarithmic time-scale)，如式 (2.18) 與式 (2.19) 所示：

$$z = \ln(t) \quad (2.18)$$

$$\xi = \ln(\tau) \quad (2.19)$$

轉換後連續的時間常數波譜如圖 2.9 (c) 所示。將式 (2.17) 利用式 (2.18) 與式 (2.19) 轉換後，再以  $z = \ln(t)$  進行微分，可得式 (2.20)：

$$\frac{d}{dz} a(z) = \int_0^\infty R_{\text{th}}(\xi) \left\{ \exp[z - \xi - \exp(z - \xi)] \right\} d\xi \quad (2.20)$$

在此，導入一權重函數  $w_z(z) = \exp[z - \exp(z)]$ ，則式 (2.20) 可轉換為式 (2.21)：

$$\frac{d}{dz} a(z) = \int_0^\infty R_{\text{th}}(\xi) w_z(z - \xi) d\xi \quad (2.21)$$

式 (2.21) 中等號右側為一卷積積分 (convolution integral)，因此式 (2.21) 可表示為：

$$\frac{d}{dz} a(z) = R_{\text{th}}(z) \otimes w_z(z) \quad (2.22)$$

其中  $\otimes$  為卷積運算符號，卷積運算將  $R_{\text{th}}(z)$  在權重函數  $w_z(z)$  的寬度範圍內進行平均值運算。

由於式 (2.22) 中暫態熱阻響應  $da(z)/dz$  可藉由實驗量測獲得，權重函數也為一已知函數，故時間常數波譜之熱阻可藉由反卷積方式獲得，如式 (2.23) 所示：

$$R_{\text{th}}(z) = \frac{d}{dz} a(z) \otimes^{-1} w_z(z) \quad (2.23)$$

藉由上述方法，時間常數波譜能以反卷積方式，得到如圖 2.9 (c) 中多個以  $\Delta z$  為時間寬度的 RC 热網絡模型，並呈現熱傳路徑上網絡的熱阻和熱容分布函數，其中串聯之 Foster 網絡的熱阻  $R_{\text{th}}$  與熱容  $C_{\text{th}}$  可表示為式 (2.24)：

$$\begin{cases} R_{\text{th,Foster}} = R_{\text{th}}(z) \cdot \Delta z \\ C_{\text{th,Foster}} = \frac{\exp(z)}{R_{\text{th}}} \end{cases} \quad (2.24)$$

對連續的時間常數波譜，以 $\Delta z$  為間隔取出之離散 RC 模型即為 Foster 热網絡模型，時間寬度 $\Delta z$  越小所獲得的 Foster 热網絡 RC 對數越多。

### 2.3.2 貝氏反卷積理論

處理反卷積最常使用的兩種方法為頻率域反卷積法與貝氏反卷積法 (Bayes' deconvolution)，貝氏反卷積法基於迭代方法，可避免使用頻率域因去除雜訊的困難，所造成提取時間常數波譜的錯誤，迭代次數造成的計算速度問題也可透過優化程式碼來解決。貝氏反卷積法基於貝氏定理，即一事件之事後機率 (posterior probability) 為兩個前置發生事件的結果，事件發生之條件機率密度可表示為式 (2.25)：

$$P(A|B) = \frac{P(B|A) \cdot P(A)}{P(B)} \quad (2.25)$$

其中  $P(A)$  為事前機率 (priori probability)， $P(A|B)$  為取決於 B 事件發生的事後機率，若能確定事前機率則能推得事後機率。在此，將時間常數波譜的熱阻值與暫態阻抗微分的關係代入式 (2.25) 中，如式 (2.26) 所示：

$$P(R_{th,i} | a_k') = \frac{P(a_k' | R_{th,i}) \cdot P(R_{th,i})}{\sum_j P(a_k' | R_{th,j}) \cdot P(R_{th,j})} = \frac{P(a_k' | R_{th,i}) \cdot P(R_{th,i})}{\sum_j P(a_k' | R_{th,j}) \cdot P(R_{th,j})} \quad (2.26)$$

其中  $R_{th,i}$  與  $a_k'$  分別為離散之時間常數波譜熱阻值與暫態阻抗的微分，時間常數波譜與暫態阻抗微分的關係可假設為式 (2.27)：

$$P(R_{th,i}) = \sum_k P(R_{th,i} | a_k') \cdot P(a_k') \quad (2.27)$$

將式 (2.26) 代入式 (2.27)，可得式 (2.28)：

$$P(R_{th,i}) = \sum_k \frac{P(a'_k | R_{th,i}) \cdot P(R_{th,i}) \cdot P(a'_k)}{\sum_j P(a'_k | R_{th,j}) \cdot P(R_{th,j})} \quad (2.28)$$

由於在式 (2.28) 中  $R_{th,i}$  出現在等號兩側，因此需透過迭代法求得估計之期望解  $P^n(R_{th,i})$ ，其中  $n$  為迭代次數，如式 (2.29) 所示：

$$P^{n+1}(R_{th,i}) = P^n(R_{th,i}) \sum_k \frac{P(a'_k | R_{th,i}) \cdot P(a'_k)}{\sum_j P(a'_k | R_{th,j}) \cdot P(R_{th,j})} \quad (2.29)$$

貝氏假定 (Bayes' postulate) 指出對事前機率未知時，可以假設每種情況發生的機率是相等的，並在獲得正確的發生機率後，更新先前的假設。在時間常數波譜中， $P^0(R_{th,i})$  為一未知的機率，權重函數  $w_z$  為時間常數波譜的分散算子 (dispersive operator)，權重函數使  $P^0(R_{th,i})$  落在  $P(a'_k)$  的範圍之間，因此將初始猜測值假設為  $P(a'_k)$  為一合理的初步估計值，並在迭代後更新先前的假設。

在機率恆為正的情況下，每一個事件發生的機率為一守恆的過程，可將式 (2.29) 中的每一項表示為式 (2.30) 至式 (2.32)：

$$P(R_{th,i}) = \frac{R_{th,i}}{R_{th}} \quad (2.30)$$

$$P(a'_k) = \frac{a'_k}{a'} \quad (2.31)$$

$$P(a'_k | R_{th,i}) = \frac{w_{ki}}{w} \quad (2.32)$$

將式 (2.30) 至式 (2.32) 代入式 (2.29)，可得式 (2.33)：

$$R_{th,i}^{n+1} = R_{th,i}^n \sum_k \frac{w_{ki} a'_k}{\sum_j w_{kj} R_{th,j}} \quad (2.33)$$

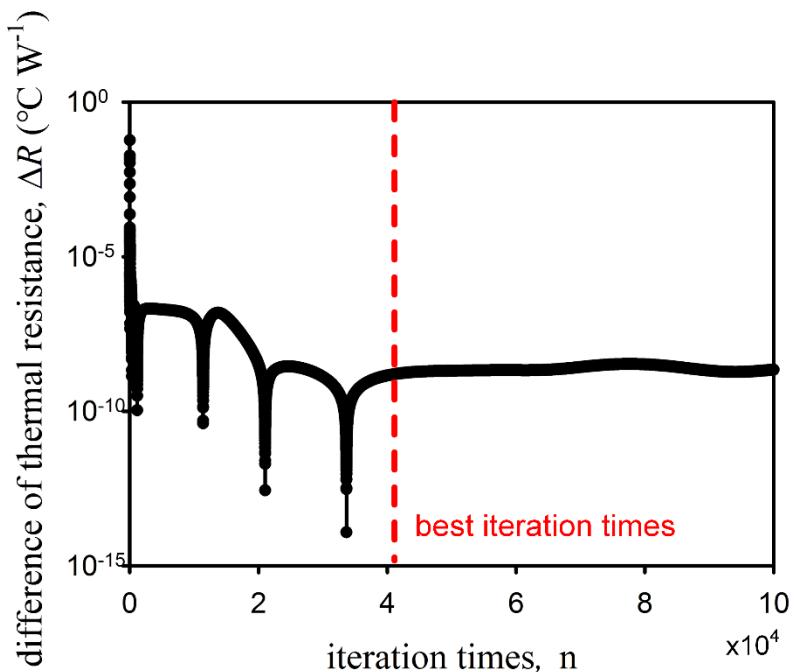

式 (2.33) 即為利用迭代之貝氏反卷積法，迭代次數的最佳化可避免數值的發

散，最佳化收斂次數之判斷公式如式 (2.34)所示：

$$\Delta R = \left[ \frac{\sum_z R^{n+1}(z) - R^n(z)}{\sum_z R^n(z)} \right] \quad (2.34)$$

若兩次迭代的 Foster 網絡熱阻差值趨於穩定，則為最佳迭代次數，如圖 2.10 所示。經反卷積得到 Foster 網絡後，需透過 Foster 與 Cauer 網絡轉換，將熱阻與熱容網絡轉換為有物理意義之熱網絡模型，轉換過程如下一小節所示。

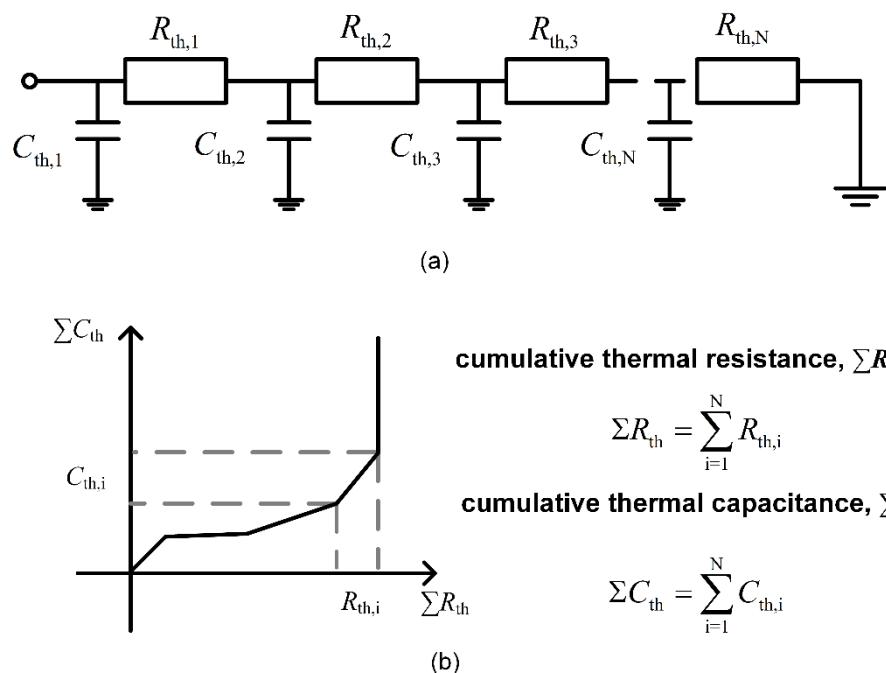

### 2.3.3 Cauer 热網絡模型

Cauer RC 網絡是 RC 單端口的等效階梯網絡物理模型，實驗所獲得之 Foster 網絡與 Cauer 網絡的轉換步驟如下所示：

考慮 N 階 Foster RC 網絡模型之複數阻抗 (complex impedance) 可以表示如式 (2.35)所示：

$$Z(s) = \sum_{i=1}^N \frac{R_i}{1+sR_iC_i} \quad (2.35)$$

其中  $s$  為複數頻率 (complex frequency)， $R_i$  與  $C_i$  分別為 Foster 網絡之 RC 對。

將式 (2.35)中的連加運算展開後，可將複數阻抗表示為兩多項式相除，如式 (2.36)所示：

$$Z(s) = \frac{n_0 + n_1s + n_2s^2 + \dots + n_{N-1}s^{N-1}}{d_0 + d_1s + d_2s^2 + \dots + d_Ns^N} \quad (2.36)$$

其中  $n$  與  $d$  分別為分子與分母的多項式中的係數，且均為實數。若要取出第一個串聯熱容，可將羅必達法則 (L'Hôpital's rule) 使用在式 (2.36)上，假設  $s$  趨近無限時，導納 (admittance)  $Y(s)$  可被近似為式 (2.37)：

$$Y(s) = \frac{1}{Z(s)} \equiv \frac{d_N}{n_{N-1}} s = C_1 s$$

其中  $C_1$  即為第一個 Cauer 模型的熱容，可表示如式 (2.38) 所示：

$$C_1 = \frac{d_N}{n_{N-1}} \quad (2.38)$$

新的導納  $Y^*(s)$  即為原先之導納減去已提取出之串聯熱容，如式 (2.39) 所示：

$$\begin{aligned} Y^*(s) &= Y(s) - C_1 s = \frac{d_0 + d_1 s + d_2 s^2 + \cdots + d_N s^N}{n_0 + n_1 s + n_2 s^2 + \cdots + n_{N-1} s^{N-1}} - \frac{d_N}{n_{N-1}} s \\ &= \frac{d_0^* + d_1^* s + d_2^* s^2 + \cdots + d_{N-1}^* s^{N-1}}{n_0^* + n_1^* s + n_2^* s^2 + \cdots + n_{N-1}^* s^{N-1}} \end{aligned} \quad (2.39)$$

接續要取出第一個串聯熱阻，同樣可利用羅必達法則，假設  $s$  趨近無限時，則阻抗  $Z^*(s)$  可被近似表示為式 (2.40)：

$$Z^*(s) = \frac{1}{Y^*(s)} \equiv \frac{n_{N-1}^*}{d_{N-1}^*} = R_1 \quad (2.40)$$

新的阻抗  $Z^{**}(s)$  即為原先之阻抗減去已提取出之串聯熱阻，如式 (2.41) 所示：

$$\begin{aligned} Z^{**}(s) &= Z^*(s) - R_1 = \frac{n_0^* + n_1^* s + n_2^* s^2 + \cdots + n_{N-1}^* s^{N-1}}{d_0^* + d_1^* s + d_2^* s^2 + \cdots + d_{N-1}^* s^{N-1}} - \frac{n_{N-1}^*}{d_{N-1}^*} \\ &= \frac{n_0^{**} + n_1^{**} s + n_2^{**} s^2 + \cdots + n_{N-2}^{**} s^{N-2}}{d_0^{**} + d_1^{**} s + d_2^{**} s^2 + \cdots + d_{N-1}^{**} s^{N-1}} \end{aligned} \quad (2.41)$$

重複以上步驟即可獲得  $R_i$  與  $C_i$ ，將 Foster RC 網絡轉換為 Cauer RC 網絡。而累積結構函數 (cumulative structure function) 即為 Cauer RC 網絡的  $R$  值與  $C$  值各自連加，累積熱阻  $\sum R_{th}$  與累積熱容  $\sum C_{th}$  可以表示為式 (2.42) 及式 (2.43)：

$$\Sigma R_{th}(i) = \sum_{i=1}^N R_{th,i} \quad (2.42)$$

$$\Sigma C_{th}(i) = \sum_{i=1}^N C_{th,i} \quad (2.43)$$

Cauer 網絡模型與結構函數的示意圖如圖 2.11 所示，藉結構函數即可獲得待測樣品之分層的熱阻與熱容。

#### 2.3.4 實驗數據分析

本研究利用自行撰寫之 Matlab[32] 程式與 C++ 程式進行後續處理與運算，程序說明如下：

1. 將 2.4.1 小節量測的一百萬筆順向電壓值中，電性暫態響應的電壓資料刪除，本實驗中將電壓開始單調遞增 (monotonically increasing) 作為電壓暫態響應結束的判斷依據。將順向電壓值，以校正過後之溫度敏感電性參數值轉換為溫度變化值。

2. 轉換後之溫度資料點因受接續計算大小的限制，以及電晶體溫度變化的時間尺度，需對資料進行縮減與延伸，且反卷積的資料需去除雜訊，因此對降溫曲線進行平滑處理，詳細方法將在 2.4.3 小節與 2.4.4 小節說明。

3. 將溫度除以加熱功率計算暫態阻抗後，將時間轉換為自然對數時間，計算暫態阻抗在自然對數時間的離散暫態阻抗微分值。將微分結果與權重函數代入貝氏反卷積公式中，設定初始迭代次數為十萬次，執行程式獲得如式 (2.34) 所示之最佳迭代次數，並以新迭代次數重新執行程式，得到時間常數波譜，此波譜即為 Foster 網絡的熱阻值。

4. 將時間常數波譜結果以時間常數與熱阻相除後獲得熱容，熱阻與熱容結果輸出成 csv 檔，以利後續處理。

5. 開啟 Dev-C++ [33] 以 GMP 函式庫自行撰寫之程式，執行 Foster 與 Cauer 轉換，將 csv 檔輸入程式執行，得到轉換完成的 Cauer 網絡模型並輸出成 csv 檔。

6. 以 Matlab 程式將 Cauer 網絡累加並作圖，即為累積結構函數。

以下小節將針對前述步驟中的數據分析進行更詳盡的介紹。

## 2.4 量測與分析程序

結構函數的計算過程流程圖如圖 2.12 所示，首先利用溫度敏感電性參數將順向電壓的降溫曲線轉換為溫度的資料點，再與加熱功率相除得到暫態阻抗，接續將暫態阻抗對自然對數時間進行數值微分，並以反卷積得到時間常數波譜，即為 Foster 的 RC 網絡，最後轉換成 Cauer 的 RC 網絡並連加後即為累積結構函數。實驗的量測流程與資料的處理方法將於本節進行詳細的說明。

### 2.4.1 降溫曲線量測

為得知暫態熱阻的變化，需要對待測之功率放大器所有電晶體的電路進行降溫曲線的量測，實驗流程如下所述：

1. 將待測之功率放大器樣品與導熱片放置於溫控平台之冷卻塊上，並以加壓治具以扭力板手設定扭矩為  $5\text{ N cm}$ ，夾持功率放大器樣品於冷卻塊上，如圖 2.4(b) 所示。

2. 設定溫控平台溫度為  $25^\circ\text{C}$ ，在冷卻塊上方放置 T 型熱電偶，監測溫控平台溫度保持穩定。

3. 開啟精密型電源量測供給設備，以定電流方式，第一通道設定感應電流  $25\text{ mA}$ 、第二通道設定加熱電流  $300\text{ mA}$ ，並以資料擷取器擷取電壓訊號，確認加熱至順向電壓穩定後即為系統達到穩態，而順向電壓穩定之標準定義為  $\Delta V_f < 1\text{ mV}$ ，當測得之順向電壓小於此範圍則視為穩態。

4. 以資料擷取器設定取樣頻率  $20\text{ kHz}$ ，在關閉加熱功率後，擷取一百萬筆順向電壓資料，擷取時間共  $50\text{ s}$ 。

#### 2.4.2 資料縮減及延伸

由於資料擷取器的量測時間間距設定為固定值，原始的電壓資料數量高達一百萬筆，在獲得降溫曲線後，計算數值微分與反卷積時會超過電腦記憶體的大小，因此在對數時間域中，我們必須以等時間間距對資料先進行縮減。本研究中從時間數量級為  $10^{-6} \sim 10^2$  s 的範圍，每個時間量級取出 100 個資料點，若該時間數量級中溫度資料點少於 100，則不進行縮減，最後得到共 900 個資料點。

在量測順向電壓時，資料擷取器的擷取間距設定為  $50\text{ }\mu\text{s}$ ，然而電晶體構成的元件暫態溫度變化最短時間尺度約為  $1\text{ }\mu\text{s}$ ，且完整的降溫曲線範圍通常需冷卻至  $100\text{ s}$ ；另外電晶體在溫度變化時有一電壓的暫態響應，此暫態響應使電壓值不穩定，在實際溫度響應前有一電壓的起伏，需透過外插將不穩定資料點補齊。綜合以上兩點，須利用鄰近插值法 (nearest interpolant) 將溫度資料點延伸，延伸實驗中小於  $50\text{ }\mu\text{s}$  的資料至  $1\text{ }\mu\text{s}$ ，以及延伸大於  $50\text{ s}$  的資料至  $100\text{ s}$ ，鄰近插值法新的插值是最近的原始樣本點的值，因此延伸值為一固定值。延伸後在時間範圍中以對數時間域等間距取出 300 個資料點，以進行後續計算。

#### 2.4.3 平滑降溫曲線

獲得結構函數的過程需經過數值微分與反卷積計算，原始溫度資料內的雜訊會在數值計算時受到放大，造成結果的錯誤，因此必須對原始降溫曲線的溫度資料進行平滑處理，減少原始資料的雜訊所造成的誤差。其平滑處理採用移動平均法 (moving average) [34]，移動平均法公式如式 (2.44) 所示：

$$V_{i,\text{smooth}} = \frac{1}{n} \sum_{j=(n-1)/2}^{(n-1)/2} V_{i+j} \quad (2.44)$$

其中  $V_{i,\text{smooth}}$  為平滑後的資料點， $n$  為濾波窗寬且恆為奇數，可針對不同實驗調整

不同的  $n$  值，本實驗中  $n$  選擇為資料點總數的 5%，避免使資料的變化趨勢過度平滑，並將雜訊消除。

原始資料點內的雜訊經平滑後可完全消除，並保留一定之降溫趨勢，即可確保正確性並進行後續資料處理。

#### 2.4.4 模擬校正與最佳參數

由於本研究實驗器材限制，無法得到  $10^{-5}$  s 以下之電壓變化，故使用套裝軟體 Ansys Icepak [35] 模擬功率放大器待測樣品在不同熱通孔數量下之暫態阻抗。另外，本研究中以模擬改變熱通孔中材料、數目與尺寸三個參數，將模擬結果轉換為結構函數，分析不同參數對熱阻與熱容的影響。

首先將功率放大器的 CAD 檔匯入 Icepak，詳細之結構與材料如圖 2.13 (a) 所示。環境溫度設定為  $25^{\circ}\text{C}$ ，各物體使用之材料性質特性如表 2.1 所示。設定功率放大器中發熱源的發熱功率，並將 PCB 底部設為  $25^{\circ}\text{C}$  的恆溫表面，模擬實際溫控平台。接續對不同區域之網格分別進行設定，設定準則以該物體最大邊長的 25% 作為該物體的最大網格尺寸，如電晶體最長邊長為  $3.2\ \mu\text{m}$ ，其網格尺寸設定為  $0.8\ \mu\text{m}$ ，而邊長為  $0.2\ \text{mm}$  的熱通孔，其網格尺寸設定為  $0.05\ \text{mm}$ ，以相同方式對不同尺寸的元件設置不同網格大小，以確保各尺寸之零件皆能夠創建網格並計算，且不需要將整個模型的網格都設定成最小網格尺寸，能有效減少網格數量。為減少計算時間並保留適當之資訊量使求解過程收斂，暫態模擬之計算時間步長 (time step) 以分段常數 (piecewise constant) 進行設定，時間  $10^{-6}\sim10^2\ \text{s}$  之間，每一時間量級所使用之時間步長皆與該量級相當，如  $1\sim10\ \text{s}$  即設定  $1\ \text{s}$  作為時間步長，最大迭代次數設定為 20 次，殘值收斂標準設定為  $10^{-7}$ ，環境選擇層流模型，忽略輻射與焦耳熱影響。

實驗樣品之熱通孔尺寸為邊長 0.2 mm 之正方形，將實驗所得的結構函數中晶片層的熱容結果，利用模擬相同條件的熱通孔尺寸與數量得到模擬的結構函數，使實驗與模擬結構函數兩者晶片層的熱容部分相互重合，並以平移後的實驗結構函數，替換原先所得的各分層熱容資料。接續設定不同熱通孔尺寸與數量，熱通孔尺寸與排列如圖 2.13 (b)所示，分別為邊長 0.1 mm、0.15 mm、0.2 mm、0.25 mm 與 0.3 mm，並替換熱通孔填充材料，分別為焊料 (soldering)、空氣、防焊漆 (solder mask) 以及額外增加一個比較用的材料，將模擬所得的暫態熱阻轉換為結構函數，分析結構函數中熱阻與熱容的變化，並找到一最佳之熱通孔設計。

## 2.5 不確定性分析

實驗過程中存在許多因素而導致實驗量測以及分析結果有誤差，因此本節透過不確定性分析估算實驗誤差，以驗證實驗結果之可靠性。實驗的誤差主要可分為系統誤差 (systematic errors) 以及隨機誤差 (random errors) 兩種。系統誤差取決於實驗設備本身精確度，可透過實驗前校正儀器以降低誤差；隨機誤差則為實驗操作的手法或其他不可預期之因素所導致，可藉由重複量測以降低其影響。整體實驗之量測誤差、系統誤差以及隨機誤差的關係如式 (2.45) 所示：

$$\delta z = \left( \delta z_{\text{sys}}^2 + \delta z_{\text{rand}}^2 \right)^{1/2} \quad (2.45)$$

其中  $\delta z$  為整體量測誤差， $\delta z_{\text{sys}}$  為系統誤差， $\delta z_{\text{rand}}$  為隨機誤差。若以相對形式表示整體量測誤差的關係則如式 (2.46) 所示：

$$\frac{\delta z}{z} = \left[ \left( \frac{\delta z_{\text{sys}}}{z} \right)^2 + \left( \frac{\delta z_{\text{rand}}}{z} \right)^2 \right]^{1/2} \quad (2.46)$$

實驗量測或計算受到各獨立變數的影響，即  $Z = f(z_1, z_2, \dots, z_n)$ ，其中  $Z$  代表實驗測量之物理量， $z_1, z_2, \dots, z_n$  為影響  $Z$  之各獨立變數。考量誤差傳遞 (error

propagation) 的影響， $Z$  的相對誤差如式 (2.47) 所示：

$$\frac{\delta Z}{Z} = \left[ \sum_{i=1}^n \left( \frac{\partial Z}{\partial z_i} \cdot \frac{\delta z_i}{Z} \right)^2 \right]^{1/2} \quad (2.47)$$

其中  $\delta Z/Z$  為  $Z$  之相對誤差， $\delta z_i$  為各獨立變數之誤差。

$Z$  的相對隨機誤差則如式 (2.48) 所示：

$$\frac{\delta Z_{\text{rand}}}{Z} = \frac{\sigma_Z}{n^{1/2}} \frac{1}{Z} \quad (2.48)$$

其中  $\delta Z_{\text{rand}}/Z$  為  $Z$  的相對隨機誤差， $\sigma_Z$  為變數在量測  $n$  次後的標準差 (standard deviation)。

本節接續將討論並計算實驗中各量測值之不確定性。

### 2.5.1 順向電壓量測之不確定性

本實驗使用資料擷取器量測順向電壓，順向電壓之不確定性如式 (2.49) 所示：

$$\delta V_f = \left( \delta V_{f,\text{sys}}^2 + \delta V_{f,\text{rand}}^2 \right)^{1/2} \quad (2.49)$$

其中量測電壓範圍區間為 2.3 V~2.5 V，以資料擷取器之技術規格書 [36] 對應直流電壓範圍 10 V 之系統誤差為讀值之  $\pm 0.003\%$  以及直流電壓範圍之  $\pm 0.0004\%$  總和，故系統誤差為  $\delta V_{f,\text{sys}} = \pm 1 \times 10^{-4}$  V。在溫度敏感電性參數的校正實驗中，設定資料擷取器的取樣頻率為 1 Hz，取樣時間 10 s，量測實驗樣品的穩態順向電壓，可得隨機誤差如式 (2.50)：

$$\delta V_{f,\text{rand}} = \frac{\sigma_{V_f}}{\sqrt{n}} \quad (2.50)$$

其中  $n = 10$ ，計算得到量測溫度敏感電性參數中的校正實驗中，順向電壓的隨機誤差為  $\delta V_{f,\text{rand}} = \pm 5 \times 10^{-5} \sim 9 \times 10^{-5}$  V，分別將  $\delta V_{f,\text{sys}}$  與  $\delta V_{f,\text{rand}}$  代入式 (2.49) 中，其中隨機誤差皆遠小於系統誤差，因此可得到溫度敏感電性參數校正與降溫曲線實

驗中，順向電壓的量測誤差為  $\delta V_f = \pm 1 \times 10^{-4}$  V，而順向電壓  $V_f$  之相對誤差為  $\delta V_f/V_f = \pm 4 \times 10^{-3}\%$ 。

降溫曲線量測實驗中，對量測點的順向電壓進行平滑，以 2.4.4 小節敘述之方式，將該資料點前後共 15 個資料點進行平均，以平滑後的資料點進行隨機誤差的計算，得到最大的順向電壓標準差為  $\sigma_{V_f} = 0.87$  V，代入式 (2.50) 計算，其中  $n = 15$ ，得到降溫曲線的隨機誤差  $\delta V_{f,rand} = \pm 2 \times 10^{-3}$  V，將隨機誤差與系統誤差代入式 (2.49)，可以得到降溫曲線量測實驗中平滑後的順向電壓誤差為  $\delta V_f = \pm 2 \times 10^{-3}$  V，而平滑後的順向電壓相對誤差為  $\delta V_f/V_f = \pm 8.1\sim8.2\%$ 。

### 2.5.2 溫控平台溫度量測之不確定性

本研究使用 T 型熱電偶量測溫控平台溫度，不確定性如式 (2.51) 所示：

$$\delta T = \left( \delta T_{sys}^2 + \delta T_{rand}^2 \right)^{1/2} \quad (2.51)$$

其中 T 型熱電偶的系統誤差為  $\delta T_{sys} = \pm 1.0^\circ\text{C}$ ，而溫度量測之隨機誤差  $\delta T_{rand}$ ，以取樣頻率 0.2 Hz，取樣時間 25 s，量測實驗設定範圍之恆溫穩態溫度  $20\sim80^\circ\text{C}$ ，以式 (2.48) 計算，其中  $n = 5$ ，得到溫度量測之隨機誤差  $\delta T_{rand} = \pm 0.02\sim0.04^\circ\text{C}$ 。分別將  $\delta T_{sys}$  與  $\delta T_{rand}$  代入式 (2.50)，計算得到溫度的誤差為  $\delta T = \pm 1.0^\circ\text{C}$ 。故溫控平台恆溫之穩態溫度之相對誤差為  $\delta T/T = \pm 1.25\sim5\%$ 。

### 2.5.3 結溫之不確定性

實驗數據處理之線性擬合方程式，利用 N 個已知量測值  $(x_1, y_1), (x_2, y_2)$  至  $(x_N, y_N)$  以最小平方法構成一擬合的直線方程式  $y = A + Bx$ ，測量值之間的未知量則以代入直線方程式獲得數值，其中截距 A 與斜率 B 的計算方法如式 (2.52) 及式 (2.53) 所示：

$$A = \frac{\sum x_i^2 \sum y_i - \sum x_i \sum x_i y_i}{N \sum x_i^2 - (\sum x_i)^2} \quad (2.52)$$

$$B = \frac{N \sum x_i y_i - \sum x_i \sum y_i}{N \sum x_i^2 - (\sum x_i)^2} \quad (2.53)$$

將溫控平台溫度由 20 調整至 80°C，每次增加 10°C，在固定溫度下所量測之順向電壓值，以最小平方法進行線性擬合，得到  $x$  與  $y$  之直線方程式  $T_j = A + BV_f$ ，則結溫之不確定性  $\delta T_j = f(A, B, V_f)$ ，由誤差傳遞公式計算， $T_j$  的不確定性，如式(2.54)所示：

$$\begin{aligned} \delta T_j &= \left[ \left( \frac{\partial T_j}{\partial A} \delta A \right)^2 + \left( \frac{\partial T_j}{\partial B} \delta B \right)^2 + \left( \frac{\partial T_j}{\partial V_f} \delta V_f \right)^2 \right]^{1/2} \\ &= \left[ (\delta A)^2 + (V_f \delta B)^2 + (B \delta V_f)^2 \right]^{1/2} \end{aligned} \quad (2.54)$$

首先計算結溫量測值的不確定性  $\sigma_{T_j}$ ，可由式 (2.55) 計算：

$$\sigma_{T_j} = \left[ \frac{1}{N-2} \sum_{i=1}^N (T_{j,i} - A - BV_{f,i})^2 \right]^{1/2} \quad (2.55)$$

其中  $N$  為以最小平方法擬合時所使用的量測點總數，在本實驗中  $N=7$ ，將不同功率放大器樣品量測的結溫與順向電壓資料點，以及各自樣品所擬合出的截距  $A$  與斜率  $B$  代入，得到結溫量測值的不確定性  $\sigma_{T_j} = \pm 0.16 \sim 0.2^\circ\text{C}$ 。

將結溫量測值的不確定性代入  $A$  與  $B$  的不確定性計算，如式 (2.56) 及式 (2.57) 所示：

$$\delta A = \sigma_{T_j} \sqrt{\frac{\sum_{i=1}^N V_{f,i}^2}{N \sum_{i=1}^N V_{f,i}^2 - (\sum_{i=1}^N V_{f,i})^2}} \quad (2.56)$$

$$\delta B = \sigma_{T_j} \left( \frac{N}{N \sum_{i=1}^N V_{f,i}^2 - \left( \sum_{i=1}^N V_{f,i} \right)^2} \right)^{1/2} \quad (2.57)$$

把不同功率放大器樣品量測的順向電壓資料點以及  $\sigma_{T_j}$  代入，可以得到截距 A 的不確定性  $\delta A = 3 \sim 3.89^\circ\text{C}$ ，而斜率 B 的不確定性  $\delta B = 1.24 \sim 1.6^\circ\text{C V}^{-1}$ 。將計算所得的結果代入式 (2.54)，得到結溫之不確定性  $\delta T_j = \pm 4.18 \sim 5.58^\circ\text{C}$ ，因此結溫之相對不確定性為  $\delta T_j / T_j = \pm 6.9 \sim 20.9\%$ 。

#### 2.5.4 加熱功率之不確定性

精密電源供應器輸出之功率為電壓及電流的函數，即  $P_{\text{heat}} = P_{\text{heat}}(I, V)$ ，因此加熱功率之相對不確定性如式 (2.54) 所示：

$$\frac{\delta P_{\text{heat}}}{P_{\text{heat}}} = \left[ \left( \frac{\partial P_{\text{heat}}}{\partial I} \frac{\delta I}{P_{\text{heat}}} \right)^2 + \left( \frac{\partial P_{\text{heat}}}{\partial V} \frac{\delta V}{P_{\text{heat}}} \right)^2 \right]^{1/2} = \left[ \left( \frac{\delta I}{I} \right)^2 + \left( \frac{\delta V}{V} \right)^2 \right]^{1/2} \quad (2.58)$$

本實驗電壓範圍為 3.5~3.8 V，電流供應為定電流 0.3 A，即  $P_{\text{heat}} = 1.05 \sim 1.14$  W。以精密電源供應器之技術規格書 [37] 對應之電壓誤差為讀值之  $\pm(0.015\%+5$  mV)，故電壓之誤差為  $\delta V = \pm 5 \times 10^{-3}$  V，而電流誤差為讀值之  $\pm(0.03\%+1.5$  mA)，故電流之誤差為  $\delta I = \pm 1 \times 10^{-3}$  A。將計算結果代入式 (2.58)，可得到  $\delta P_{\text{heat}} = \pm 4 \times 10^{-3}$  W，因此加熱功率  $P_{\text{heat}}$  之相對不確定性  $\delta P_{\text{heat}} / P_{\text{heat}} = \pm 0.3\%$ 。

#### 2.5.5 热阻之不确定度

由式 (2.11) 可知热阻  $a_{\text{th}} = a_{\text{th}}(T_j, T_{\text{sink}}, P_{\text{heat}})$ ，因此热阻不确定度如式 (2.59) 所示：

(2.59)

$$\begin{aligned}\frac{\delta a_{\text{th}}}{a_{\text{th}}} &= \left[ \left( \frac{\partial a_{\text{th}}}{\partial T_j} \frac{\delta T_j}{a_{\text{th}}} \right)^2 + \left( \frac{\partial a_{\text{th}}}{\partial T_{\text{sink}}} \frac{\delta T_{\text{sink}}}{a_{\text{th}}} \right)^2 + \left( \frac{\partial a_{\text{th}}}{\partial P_{\text{heat}}} \frac{\delta P_{\text{heat}}}{a_{\text{th}}} \right)^2 \right]^{1/2} \\ &= \left[ \left( \frac{\delta T_j}{(T_j - T_{\text{sink}})} \right)^2 + \left( -\frac{\delta T_{\text{sink}}}{(T_j - T_{\text{sink}})} \right)^2 + \left( \frac{-\delta P_{\text{heat}}}{P_{\text{heat}}} \right)^2 \right]^{1/2}\end{aligned}$$

將 2.5.2 節~2.5.4 節討論結果代入，得到暫態熱阻不確定性  $\delta a_{\text{th}} < 4.03 \text{ }^{\circ}\text{C W}^{-1}$ ，當加熱功率施加與關閉至穩態時有最大與最小之不確定性，而對應之暫態熱阻相對不確定性  $\delta a_{\text{th}} / a_{\text{th}}$  最大值為 19%。

## 第三章 實驗結果與討論

本章將針對實驗結果，探討不同功率放大器樣品的 PCB 上熱通孔數目對其熱傳遞行為的影響，比較結構函數中熱阻與熱容的變化情形；主要探討參數為熱通孔填充物、熱通孔數量以及熱通孔的大小。

### 3.1 實驗功率放大器樣品

#### 3.1.1 暫態熱阻變化

本研究中對功率放大器的 PCB 上不同熱通孔數目，藉由實驗所獲得之量測結果如表 3.1 所示，將降溫曲線中達到穩態的溫度定義為最高結溫，從表中可以看到在熱通孔邊長同為 0.2 mm 下，最高的結溫隨熱通孔數量的增加而降低，其中 4 個與 5 個熱通孔兩者最高結溫分別為 48.5°C 及 45.7°C，最高結溫相差 2.8°C，下降約 5.7%；5 個與 9 個熱通孔之間最高結溫亦相差 2.8°C，下降約 6.1%，而 9 個與 13 個熱通孔之間相差 1.4°C，溫度下降幅度 3.2%。從樣品的整體熱阻也可見到 4 與 5 個熱通孔之間熱阻差為  $2.31 \text{ }^{\circ}\text{C W}^{-1}$ ，5 與 9 個熱通孔熱阻差為  $3.32 \text{ }^{\circ}\text{C W}^{-1}$ ，9 與 13 個熱通孔的熱阻相差約  $1 \text{ }^{\circ}\text{C W}^{-1}$ ，因此可推斷隨著熱通孔數量增加，熱阻能夠有效降低。

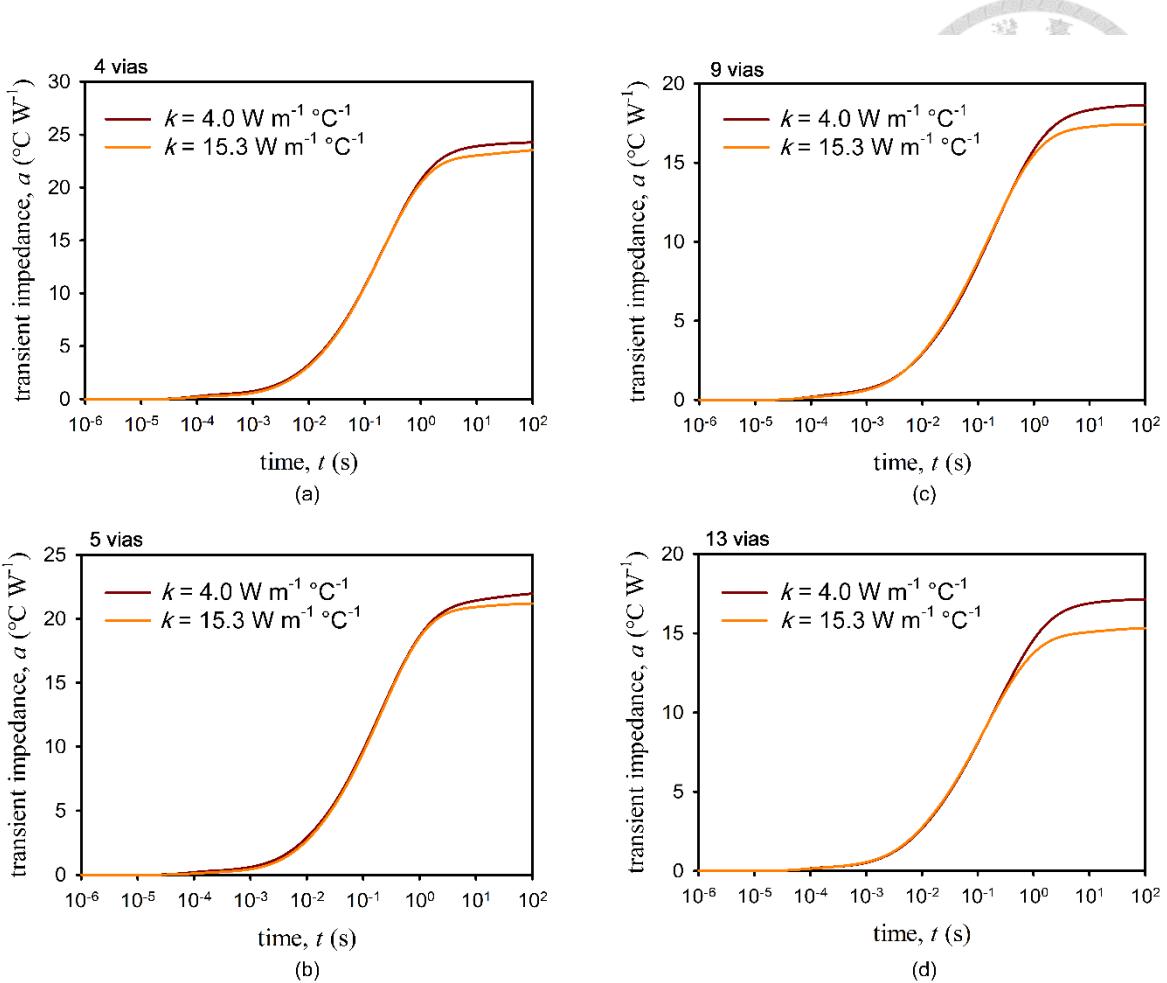

圖 3.1 為各功率放大器樣品在使用不同熱傳導係數的導熱墊下所量測之暫態阻抗變化圖，總阻抗在 4 個熱通孔時有一最大阻抗  $24.28 \text{ }^{\circ}\text{C W}^{-1}$ ，而 13 個熱通孔時有最小阻抗值  $17.15 \text{ }^{\circ}\text{C W}^{-1}$ ，阻抗隨著熱通孔數量的增加有大幅的降低。另外從圖 3.1 中可見，在時間  $10^{-1} \text{ s}$  之前使用不同熱傳導係數的導熱墊對於暫態阻抗變化曲線沒有影響，但在時間約大於  $10^{-1} \text{ s}$  後開始出現明顯的分歧，此分歧的時間尺度

即為熱傳遞至 PCB 板與導熱墊接觸的位置所需花費的時間。在分歧點後，使用熱傳導係數為  $4.0 \text{ W m}^{-1}\text{C}^{-1}$  的導熱墊，整體熱阻抗皆明顯大於使用熱傳導係數為  $15.3 \text{ W m}^{-1}\text{C}^{-1}$  的導熱墊的阻抗結果。

欲獲得更詳細在不同分層的熱阻與熱容資訊，則須以結構函數進行討論，如 3.1.2 節所示。

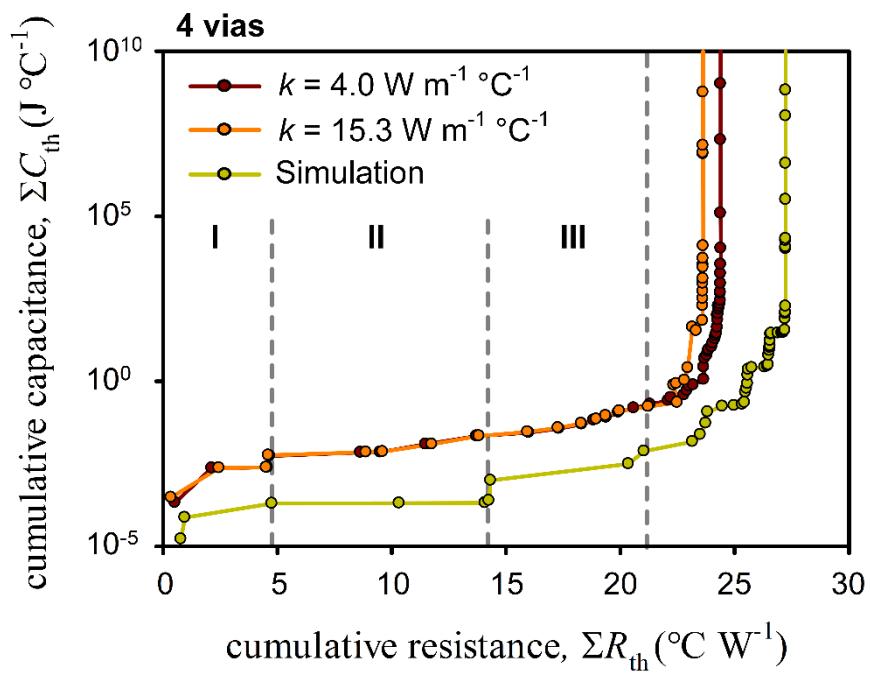

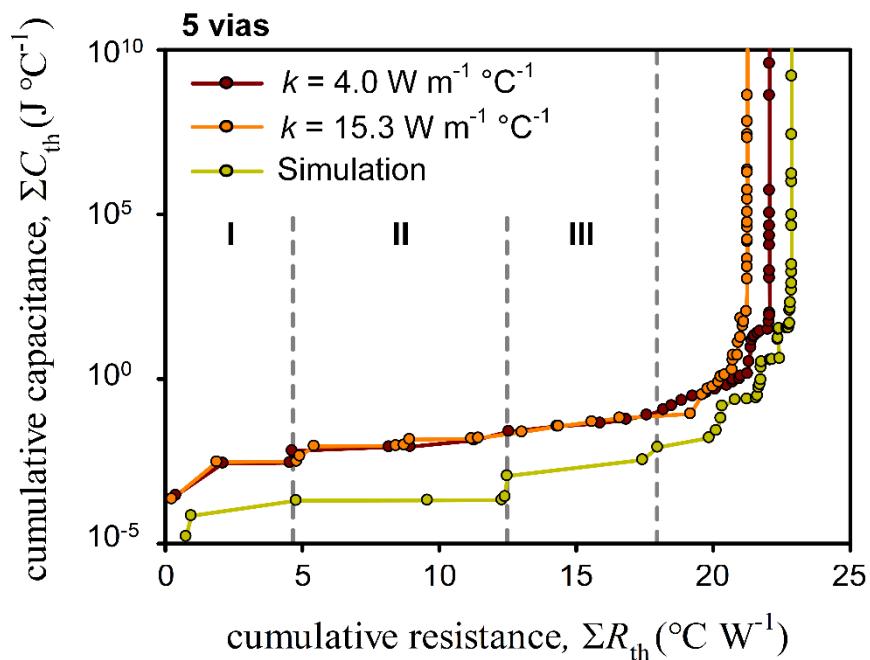

### 3.1.2 結構函數

圖 3.2 至圖 3.5 分別為功率放大器樣品的 PCB 上四種不同熱通孔數量的實驗與模擬所獲得之結構函數，從圖中可發現，實驗結果所得到的結構函數與模擬所獲得的結構函數比較，熱容的數值有約  $10^1$  的平移，主要原因為實驗受設備中最小量測時間的限制，無法得到時間在  $10^{-6} \text{ s}$  之結果，需要透過模擬獲得  $10^{-6} \text{ s}$  的資訊來平移結構函數，將熱容的結果校正為正確數值。我們在相同熱阻的情況下，將實驗的結構函數向下垂直平移，將實驗的結構函數之晶片層熱容平移至與模擬所得之結構函數的晶片層熱容完全吻合，此時實驗結構函數晶片層的熱容即為校正後的熱容結果，圖 3.6 至圖 3.9 即為平移後之結構函數圖。

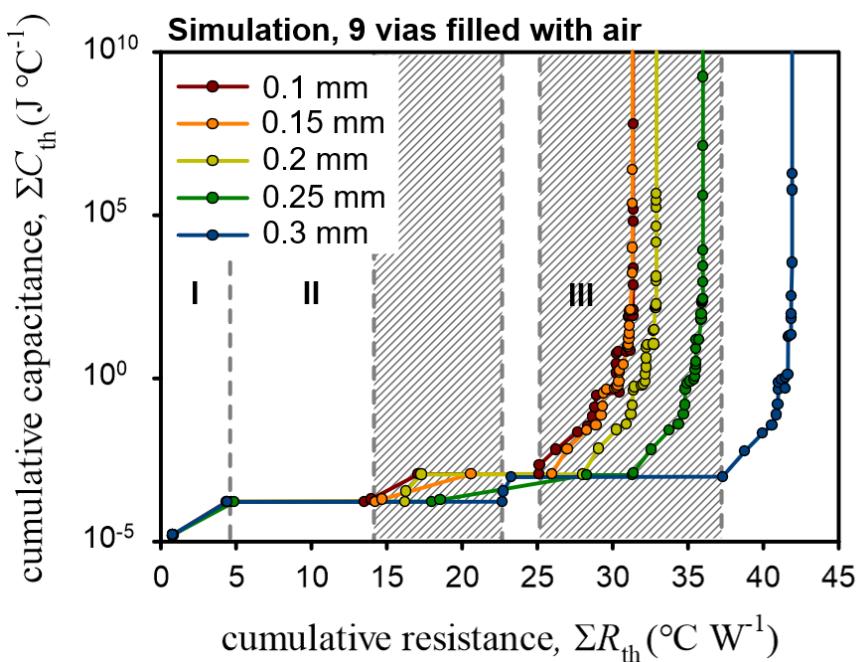

圖 3.6 至圖 3.9 中平移後的結構函數可劃分為三個分層，分別是分層 I：晶片層，分層 II：晶片接著劑、導線架及焊料層，分層 III：PCB 層。表 3.2 與表 3.3 整理了熱通孔邊長為  $0.2 \text{ mm}$ ，不同分層的熱阻及熱容實驗結果與 T3ster 代測結果之比較。四個功率放大器樣品在分層 I 的晶片層熱阻並沒有太大的差異，約為  $4.3 \sim 4.6 \text{ }^\circ\text{C W}^{-1}$  之間，晶片層的熱容校正後約為  $1.2 \times 10^{-4} \sim 1.6 \times 10^{-4} \text{ J }^\circ\text{C}^{-1}$ ，由 T3ster 代測之晶片層熱阻為  $4.55 \text{ }^\circ\text{C W}^{-1}$ ，與實驗量測之誤差最大僅  $6.3\%$ ，代測之熱容為  $1.4 \times 10^{-4} \text{ J }^\circ\text{C}^{-1}$ ，與實驗量測之結果亦沒有明顯的誤差。

分層 II 為晶片接著劑、導線架層及焊料層，三者因厚度以及製程上的影響，較

難以在結構函數區別各自材料之獨立分層。在此分層的整體熱阻中，最大值為 4 個熱通孔的  $7.18\text{ }^{\circ}\text{C W}^{-1}$ ，隨著熱通孔數量的增加此分層的熱阻逐漸降低，5 個熱通孔時為  $6.71\text{ }^{\circ}\text{C W}^{-1}$ 、9 個熱通孔之  $6.59\text{ }^{\circ}\text{C W}^{-1}$  以及最小的熱阻值則為 13 個熱通孔的  $5.91\text{ }^{\circ}\text{C W}^{-1}$ ，此分層熱阻的差異主要受到熱通孔的數量多寡影響，熱通孔與晶片接著劑接觸將熱量由發熱源傳導至熱通孔底部，因此熱通孔數量增加，熱量傳遞截面積增加，進而使熱阻有些微降低；校正後的分層熱容約為  $8.5 \times 10^{-3} \sim 9.3 \times 10^{-3}\text{ J }^{\circ}\text{C}^{-1}$ ，沒有明顯的差異與變化趨勢。T3ster 代測之分層 II 热阻為  $6.58\text{ }^{\circ}\text{C W}^{-1}$ ，對應實驗量測中 9 個熱通孔的樣品，兩者熱阻幾乎相同，而代測之熱容為  $9.19 \times 10^{-3}\text{ J }^{\circ}\text{C}^{-1}$ ，與實驗量測之誤差也僅有 1.7%。

分層 III 為含有熱通孔之 PCB 分層，熱通孔中的填充物為焊料，使用的焊料為 Sn63/Pb37 材料，此分層的熱阻受到熱通孔的數量主宰變化較為明顯，4 個熱通孔之分層熱阻為  $9.55\text{ }^{\circ}\text{C W}^{-1}$ 、5 個熱通孔之分層熱阻為  $7.15\text{ }^{\circ}\text{C W}^{-1}$ ，兩個樣品唯一差異為 5 個熱通孔的功率放大器樣品中，多了一個位於熱源正下方的中心熱通孔，使得熱阻在此分層大幅下降 25.1%。而 9 個熱通孔的功率放大器樣品，其熱通孔的分布近乎完全覆蓋熱源的表面，使其分層的熱阻降低至僅有  $3.65\text{ }^{\circ}\text{C W}^{-1}$ 。13 個熱通孔之分層熱阻則為  $3.25\text{ }^{\circ}\text{C W}^{-1}$ ，與 9 個熱通孔相比並沒有明顯的熱阻下降，多餘的 4 個熱通孔並沒有對熱傳有明顯的效益。從整體 PCB 分層的熱容數值可知，當填充物為焊料時，熱容隨熱通孔的數目增加而有些許的上升，並從熱通孔的排列方式可知，在 PCB 上有中心熱通孔的功率放大器樣品中，都能更有效降低其熱阻以及增加熱容，詳細的排列方式對熱阻與熱容的影響將於 3.2 節中討論。

在分層 III 後即為導熱墊接觸層與溫控平台，使用兩個不同熱傳導係數的導熱墊所得到的結構函數曲線，出現分離點的位置即為功率放大器樣品 PCB 板的最下

層，而熱容的數值有明顯之垂直向上大幅提升處即為溫控平台區域。利用分層 I 至分層 III 之熱阻總合值，對應圖 3.1 的時間軸，可以獲得表 3.1 中熱量由發熱源傳遞至 PCB 底部所需的时间。4 個熱通孔熱流從晶片層至 PCB 層底部所經歷的時間為 1.21 s，而 13 個熱通孔所需時間為 0.73 s，速度明顯加快 39.1%，此熱傳時間的縮短能夠更有效率地將熱量帶離功率放大器晶片，證明熱通孔數量的增加能有效幫助晶片層的熱量傳遞至 PCB 底部。

表 3.4 為實驗與模擬所得 PCB 分層的熱阻比較，從結果可以得知，實驗與模擬之間的誤差並不明顯，最大誤差僅為 9 個熱通孔的 9.4%，可以藉此驗證實驗中結構函數的正確性。而透過以上對熱阻、熱容及熱傳遞時間的推論，含有中心熱通孔且熱通孔數量較多的 9 個熱通孔功率放大器樣品有一最佳散熱設計，超過 9 個熱通孔後的 13 個熱通孔在 PCB 層熱阻降低幅度並不明顯，且多餘的熱通孔會增加 PCB 上佈線的困難以及製造成本的增加，導致功率放大器發生信號衰減與功率耗損的可能性。而僅有 5 個熱通孔的功率放大器樣品，雖然相較於 4 個熱通孔的樣品已經在 PCB 層有明顯的熱阻減少，但仍遠大於 9 個熱通孔的樣品。從熱容結果也可以得知，9 個熱通孔的 PCB 層熱容相較於 5 個與 4 個熱通孔的功率放大器樣品也有變大，表示熱量在 PCB 層傳遞時能在垂直方向有更良好的分散與儲存，減少熱量堆積於結接面或特定位置的情形出現。

### 3.2 模擬不同填充物之熱通孔

#### 3.2.1 填充焊料之熱通孔

此小節所使用之熱通孔填充的焊料與前一節中實驗的功率放大器樣品所使用的填充熱通孔材料相同，皆為 Sn63/Pb37 材料，其熱傳導係數為  $50 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$ ，而

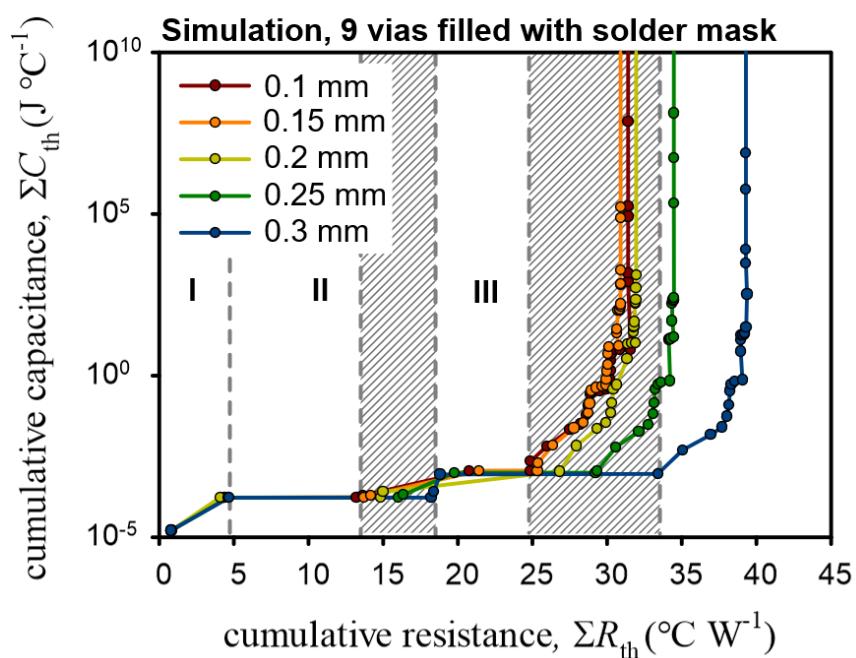

比熱為  $150 \text{ J kg}^{-1} \text{ }^{\circ}\text{C}^{-1}$ 。圖 3.10 至圖 3.15 為熱通孔不同尺寸下，填充焊料的熱通孔數目從 4 個增加至 9 個之模擬結構函數，從結構函數中同樣可以得到分層 I：晶片層，分層 II：晶片接著劑、導線架及焊料層，分層 III：PCB 層。圖中的斜線區域為分層 II 與分層 III 受不同熱通孔數量影響所產生之差異。分層 I 晶片層的熱阻與熱容因為設計相同，因此不隨熱通孔的尺寸變化而有差異；分層 II 中，熱通孔尺寸的增加使分層 II 與熱通孔的接觸面積增加，進而讓分層 II 的熱阻隨熱通孔尺寸的增加有些微降低。

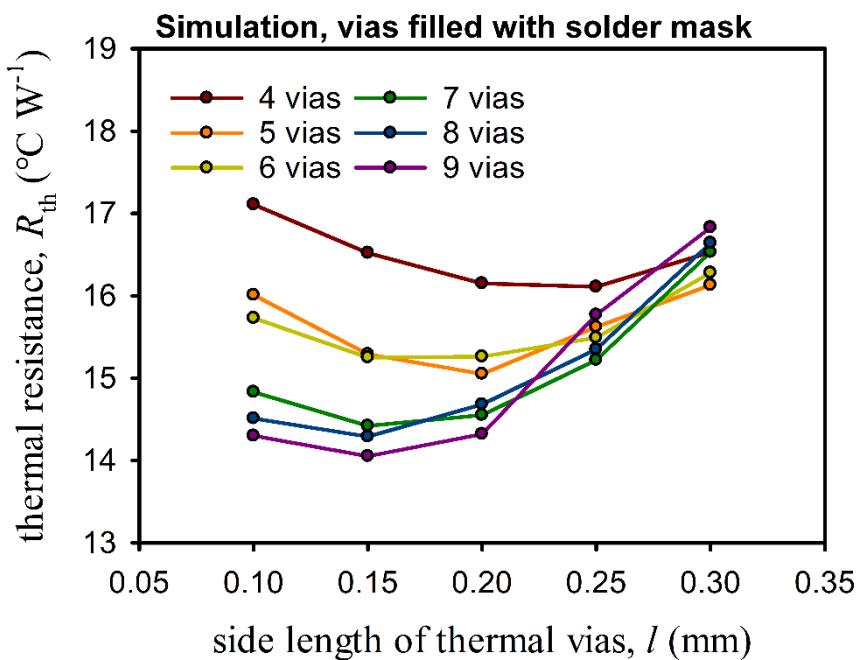

在 4 個熱通孔的模擬中，隨著熱通孔尺寸從 0.1 mm 增加至 0.3 mm，PCB 層熱阻從  $10.78 \text{ }^{\circ}\text{C W}^{-1}$  降低至  $7.81 \text{ }^{\circ}\text{C W}^{-1}$ ，大幅降低 27.5%；熱容則從  $1.29 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$  增加至  $2.07 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$ ，提升了 60.4%。圖 3.11 為 5 個熱通孔的模擬結構函數，熱通孔尺寸從 0.1 mm 增加至 0.3 mm 時，PCB 層熱阻從  $9.3 \text{ }^{\circ}\text{C W}^{-1}$  降低至  $6.58 \text{ }^{\circ}\text{C W}^{-1}$ ，降低 29.2%；PCB 層熱容則從  $1.31 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$  增加至  $2.27 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$ ，提升了 73.2%。從圖 3.11 的結構函數可以發現，相較於 4 個熱通孔的結構函數，含有中心熱通孔的 5 個熱通孔樣品中，區域 II 熱阻在熱通孔的尺寸變大後有較明顯的熱阻降低，這主要是因為位於發熱源正下方的熱通孔，能有效提升晶片層與 PCB 底層之間的熱傳效果，增加熱量的傳遞至 PCB 底部散熱，使其有較低的熱阻值，驗證了中心熱通孔對熱傳遞的效益影響較大。由圖 3.16 所整理的熱阻變化可以得知，在 4 個熱通孔與 5 個熱通孔的模擬結果中，熱阻隨尺寸的變化趨勢近乎相同，為一接近線性的遞減，推論在熱通孔數目較少時，尺寸對於熱阻的影響並不那麼明顯。

圖 3.12 為 6 個熱通孔在不同邊長尺寸下之模擬結構函數，熱通孔尺寸從 0.1 mm 增加至 0.3 mm，PCB 層熱阻從  $9.11 \text{ }^{\circ}\text{C W}^{-1}$  降低至  $5.28 \text{ }^{\circ}\text{C W}^{-1}$ ，減少了約 42%；PCB 層熱容則從  $1.06 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$  增加至  $1.78 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$ ，提升了 67.9%。從圖 3.16

可以觀察到，當熱通孔尺寸小於 0.2 mm 時，整體熱阻與 5 個熱通孔的熱阻近乎相同，主要原因為缺少了中心熱通孔的散熱，因此雖然熱通孔的數量增加，但位置的擺放使其熱阻值反而增加；而在尺寸大於 0.2 mm 後，熱通孔的尺寸增加使得填充物對熱阻的影響變大，特別在 0.25 mm 增加至 0.3 mm 時，6 個熱通孔的熱阻值明顯大幅下降。

圖 3.13 與圖 3.14 分別為 7 個與 8 個熱通孔在不同邊長尺寸下之模擬結構函數，熱通孔尺寸從 0.1 mm 增加至 0.3 mm，7 個熱通孔的功率放大器樣品中 PCB 層熱阻從  $8.23\text{ }^{\circ}\text{C W}^{-1}$  降低至  $4.68\text{ }^{\circ}\text{C W}^{-1}$ ，減少了 43%；PCB 層熱容則從  $1.16 \times 10^{-2}\text{ J }^{\circ}\text{C}^{-1}$  增加至  $1.82 \times 10^{-2}\text{ J }^{\circ}\text{C}^{-1}$ ，提升了 67.9%。8 個熱通孔 PCB 層熱阻則從  $8.14\text{ }^{\circ}\text{C W}^{-1}$  降低至  $4.47\text{ }^{\circ}\text{C W}^{-1}$ ，減少了 45%；PCB 層熱容從  $1.25 \times 10^{-2}\text{ J }^{\circ}\text{C}^{-1}$  增加至  $2.18 \times 10^{-2}\text{ J }^{\circ}\text{C}^{-1}$ ，提升了 42.6%。從圖 3.16 中可見，7 個熱通孔及 8 個熱通孔隨著尺寸的增加，熱阻的變化趨勢與 6 個熱通孔相同，均在尺寸大於 0.25 mm 後，熱阻值隨尺寸增加而大幅下降。

圖 3.15 為 9 個熱通孔在不同邊長尺寸下之模擬結構函數，熱通孔尺寸從 0.1 mm 增加至 0.3 mm，PCB 層熱阻從  $7.42\text{ }^{\circ}\text{C W}^{-1}$  降低至  $3.63\text{ }^{\circ}\text{C W}^{-1}$ ，熱阻值減少了約 50%；PCB 層熱容則從  $1.32 \times 10^{-2}\text{ J }^{\circ}\text{C}^{-1}$  增加至  $2.26 \times 10^{-2}\text{ J }^{\circ}\text{C}^{-1}$ ，提升了 41.5%。特別的是，從圖 3.16 中可以看到，在 9 個熱通孔的尺寸大於 0.15 mm 後，因中心熱通孔以及熱通孔已經遍佈晶片發熱源的範圍，受到熱通孔的面積增加以及填充物的熱傳導係數較低的影響，熱阻有明顯的大幅降低，且尺寸對熱阻的影響在熱通孔尺寸超過 0.2 mm 後因為面積已經幾乎覆蓋熱源，因此熱阻並不會隨尺寸的繼續增加而有降低。

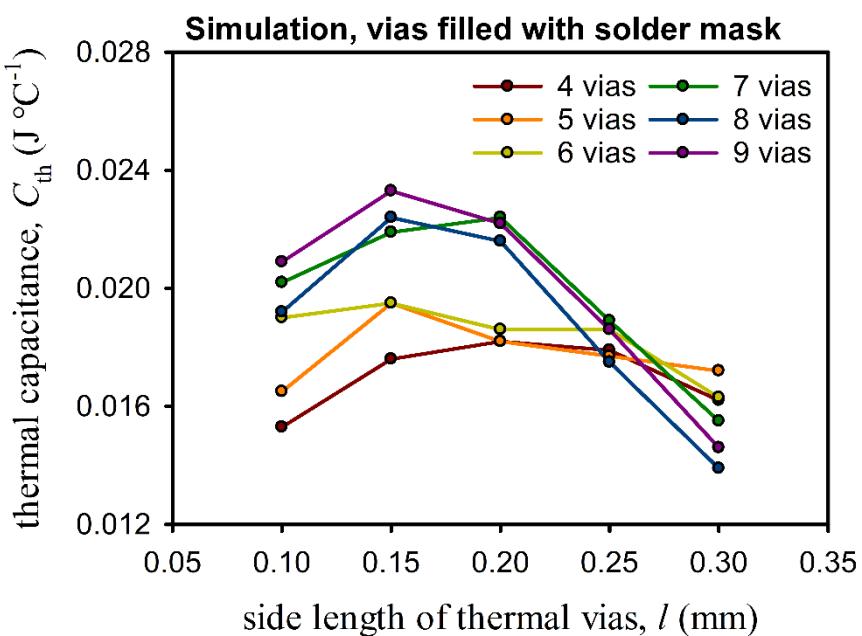

圖 3.17 為填充焊料的熱通孔隨尺寸增加的 PCB 層熱容變化，從圖中可見到

不同數目的熱通孔在尺寸增加時，熱容的變化趨勢一致，都是隨尺寸增加而提升。

從表 2.1 中材料性質可以看到，雖然填充熱通孔的焊料比熱相較 PCB 板的 FR4 材料為低，但熱通孔尺寸加大後，熱通孔有助於熱量以垂直方向傳遞，可更快速地將晶片層產生的熱量垂直傳遞分散於 PCB 垂直方向其他位置，使得整體 PCB 層的熱容反而有上升的趨勢。

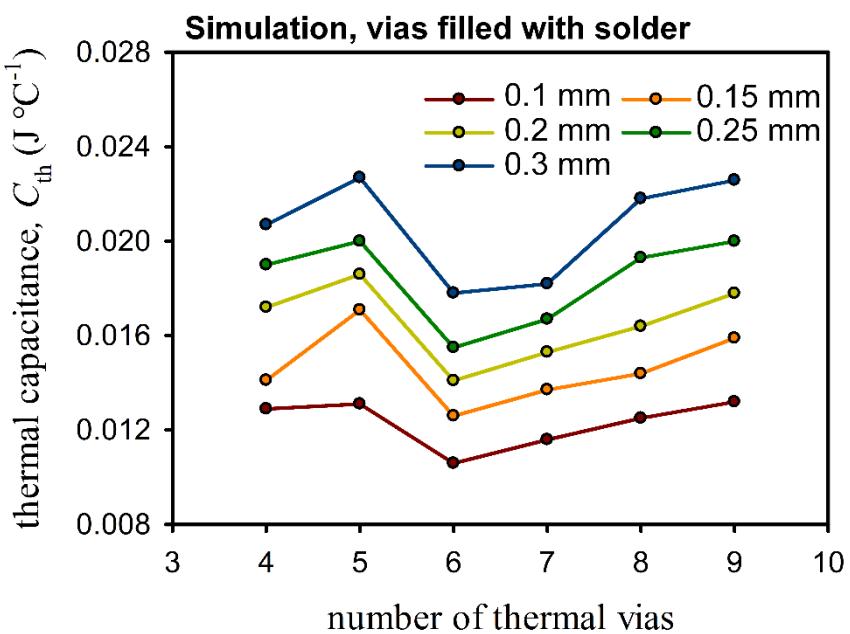

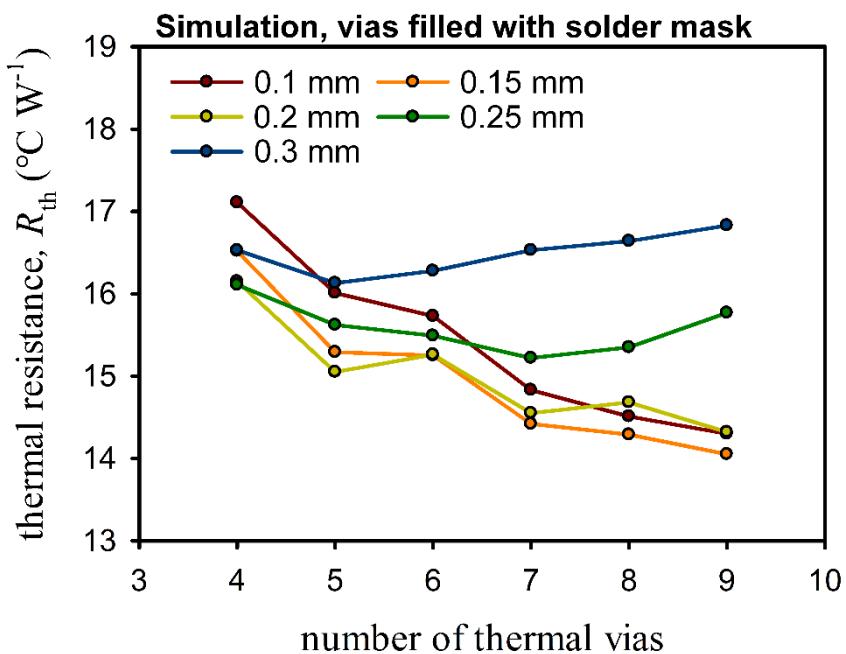

不同熱通孔數目與排列對熱阻的影響比較如圖 3.18 所示，尺寸 0.1 mm 及 0.15 mm 的熱阻變化呈現相同趨勢，在有中心熱通孔的 5 個、7 個及 9 個熱通孔樣品中，熱阻都有明顯的下降。而在尺寸 0.2 mm 及 0.25 mm 時，9 個熱通孔前熱阻的變化趨勢並沒有差異，唯有在數量增加至 9 個熱通孔時，熱阻出現一劇烈的下降，此時的熱通孔近乎完全涵蓋了 PCB 與功率放大器晶片層熱源之間的接觸面積，使得熱量能夠完全透過熱通孔往 PCB 底部傳遞。在尺寸 0.3 mm 後，熱通孔的數目與中心熱通孔的有無已經幾乎不影響熱阻的變化，而是隨熱通孔的數量增加熱阻接近一線性的遞減，並沒有出現因為熱通孔的排列方式，而發生特別顯著的熱阻變化。

不同熱通孔數目與排列對熱容的影響比較如圖 3.19 所示，在不同尺寸下熱容隨熱通孔數目的增加有幾乎相同的趨勢，在 6 個熱通孔時皆有最低之熱容值，其原因是受到熱通孔排列影響，如圖 2.13 (b) 所示，相較於 4 個熱通孔與 5 個熱通孔，中上方與中下方的兩個熱通孔的增加並沒有提升 PCB 層的熱容量，且相較 4 個熱通孔反而受到填充熱通孔的焊料比熱相較 FR4 材料的比熱低的影響，因而有下降的趨勢；大於 6 個熱通孔後的熱容變化，主要受到中心熱通孔的增加以及熱通孔數量的增加，使得熱容有些許的提升，但因為仍存在中上方與中下方的兩個熱通孔，使得在各尺寸下 5 個熱通孔因為中心熱通孔的存在與熱通孔的排列方式，而有最高之熱容值。

圖 3.20 與圖 3.21 為填充焊料的熱通孔，不同熱通孔數量與熱通孔尺寸的熱阻值分布圖與熱容值分布圖，圖中顏色為深藍色的區域，為樣品中 PCB 層模擬所得熱阻與熱容較大處。在 PCB 热通孔填充焊料的樣品中，模擬熱阻值在熱通孔數較少、熱通孔尺寸較小的樣品有熱阻較大以及熱容較小的趨勢；而熱通孔數量增加、熱通孔尺寸越大的樣品則其熱阻降低，熱容數值越大。從上述討論可以得知，當填充物為焊料時，以熱通孔數量越多、熱通孔尺寸越大為最佳之設計，可以大幅減少 PCB 分層的熱阻並增加熱容，熱容的提升能有效提供熱量儲存的能力，並且分散熱量減少局部熱點可能導致的功率放大器損壞。

從表 3.5 所整理的 PCB 分層模擬之溫度與其在空間上溫度分布的標準差  $\sigma$  及變異係數 CV (coefficient of variance) 可以得知，對應圖 3.19 的熱容變化，當熱通孔尺寸為 0.1 mm 時，含有最大熱容值的 4 個及 5 個熱通孔其溫度分布的標準差及變異數明顯相較於其他樣品小，表示在 PCB 分層中的溫度分布較為均勻，且熱容最小值的 6 個熱通孔也有最大的標準差及變異數；而熱通孔尺寸為 0.3 mm 時，整體的標準差及變異數皆小於 0.1 mm 的結果，且 6 個熱通孔時的結果仍為所有樣品之最大值，以上結果皆證明熱容值越大，對於 PCB 層中熱量的分散效果佳，減少了熱量的不均勻分布。

表 3.5 及表 3.6 亦整理了填充焊料的熱通孔之模擬結果中 PCB 分層與晶片分層溫度變化的特徵時間  $\tau$ ，特徵時間為分層溫度的變化到達穩態之 63.2% 所需時間，而 PCB 分層的特徵時間隨著熱通孔大小增加，以及熱通孔數量增加而特徵時間明顯縮短，此結果與 PCB 分層之熱阻與熱容相乘之變化結果相同，PCB 分層之熱阻與熱容相乘結果同樣隨著熱通孔大小增加以及熱通孔數量增加而下降。若以圖 3.18 及圖 3.19 之熱阻與熱容結果觀察，特徵時間的變化與熱阻變化趨勢相同，表

示 PCB 分層的特徵時間變化為熱阻主宰，與熱容的關聯較低。特別的是，晶片層的尺寸及材料皆相同，其晶片層的熱阻與熱容相乘結果並不隨 PCB 層熱通孔的變化而有改變，然而表 3.6 中的晶片層溫度變化特徵時間依然隨著 PCB 層的熱通孔數量增加以及尺寸越大而越短，且結溫也隨之下降，表示 PCB 分層的改變連帶影響其他分層的溫度變化。

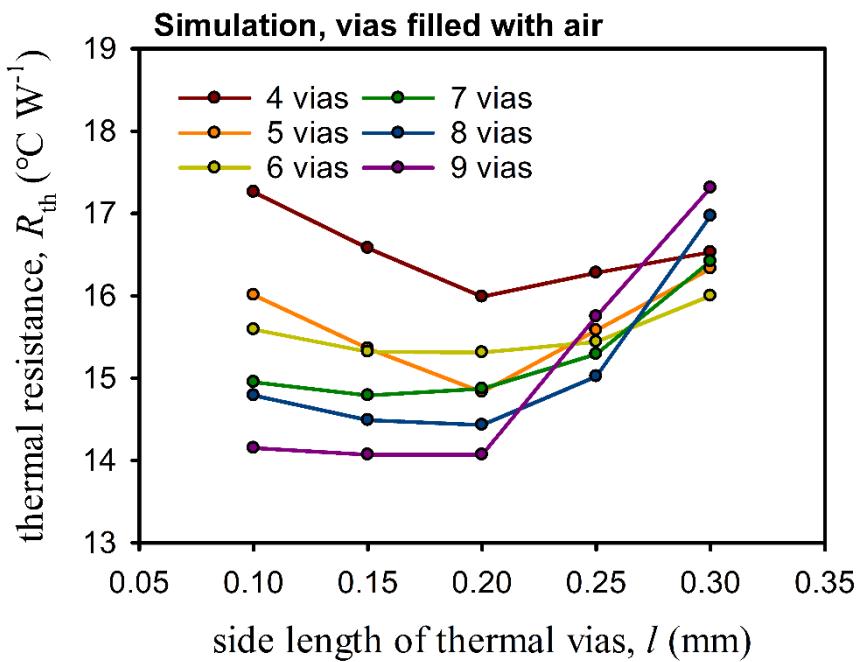

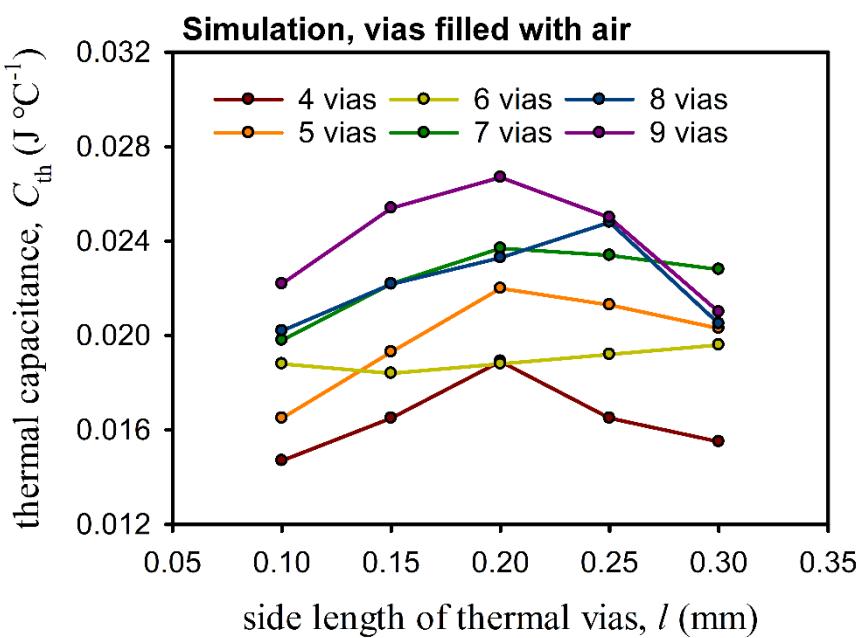

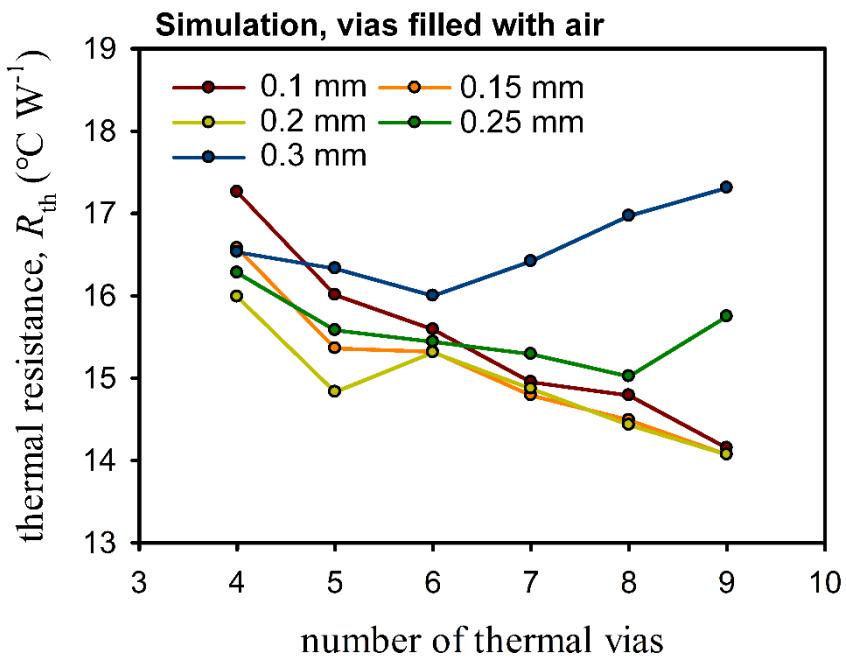

### 3.2.2 填充空氣之熱通孔

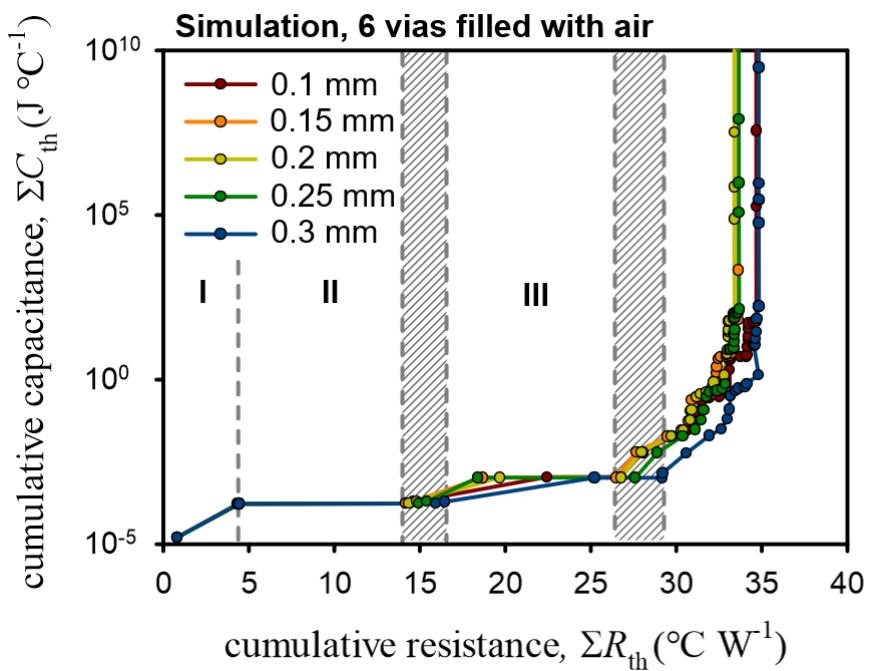

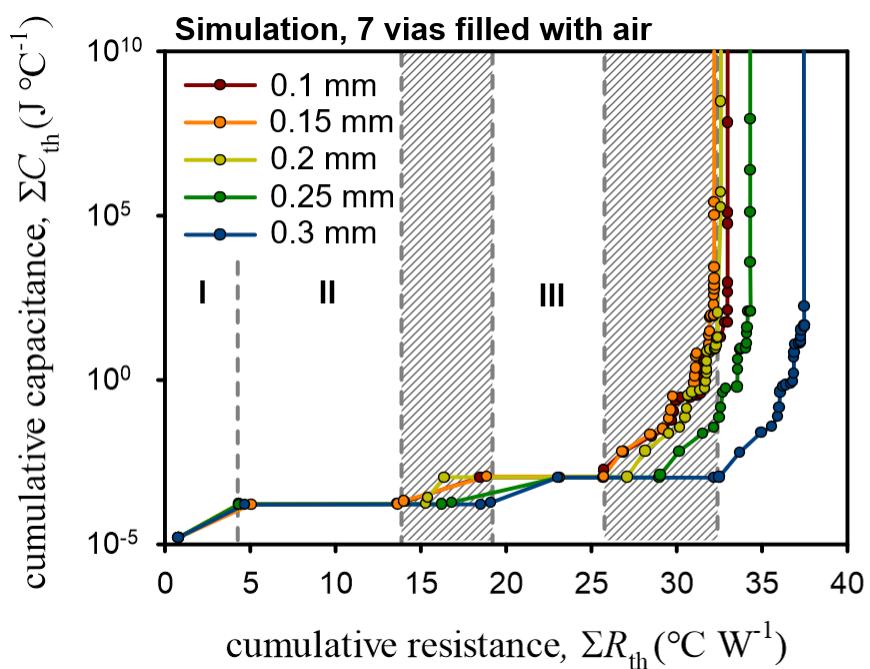

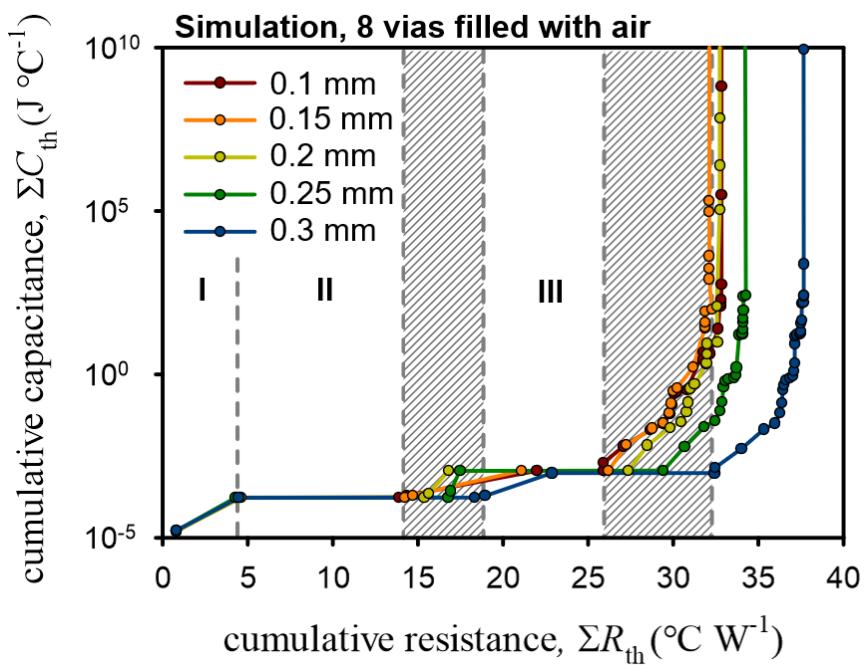

圖 3.22 到圖 3.27 為熱通孔中填充物為空氣的模擬結構函數圖，斜線區域同樣為分層 II 與分層 III 受不同熱通孔數量影響所產生之差異。與前一小節中填充焊料的熱通孔所得到的結構函數相比，整體的熱阻有一明顯的增加，主要原因因為無填充物的熱通孔之間傳遞熱量的介質為空氣，雖然熱通孔的側壁有鋪銅，但由表 2.1 的材料性質可以得知，空氣的熱傳導係數較焊料小了兩個數量級，使熱量傳遞至分層 II 之後，較難以藉由熱通孔傳遞至 PCB 底部，使得熱量堆積在分層 I 的晶片層，結溫大幅上升，擴大晶片層與溫控平台之間的溫差，整體熱阻因而有較明顯的提升。

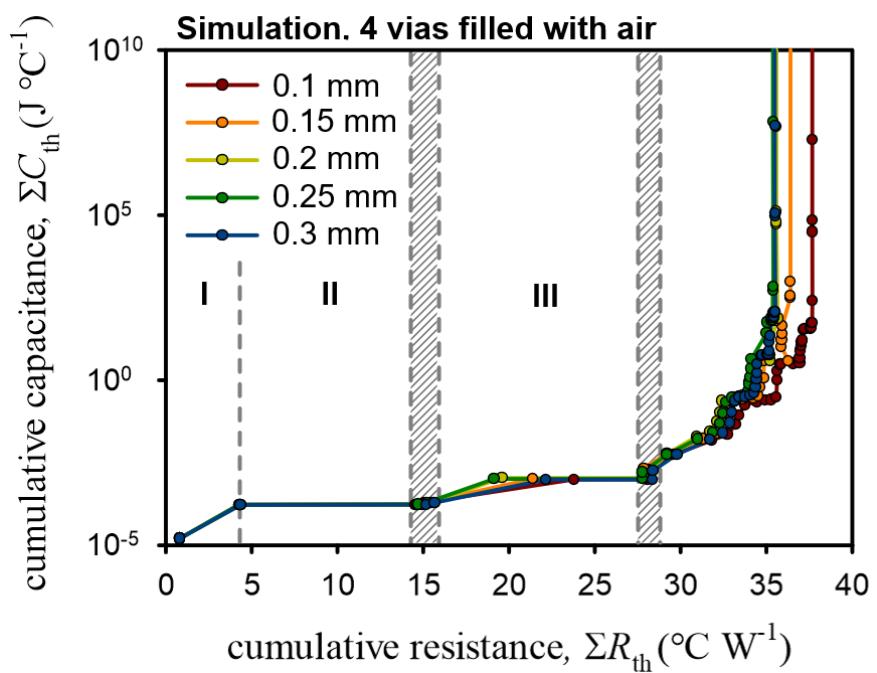

圖 3.22 為 4 個無填充物的熱通孔模擬結構函數，隨著熱通孔尺寸的變化，PCB 層熱阻從 0.1 mm 的  $17.26 \text{ }^{\circ}\text{C W}^{-1}$  降低至 0.2 mm 的  $15.99 \text{ }^{\circ}\text{C W}^{-1}$ ，而後熱阻又開始隨著熱通孔的尺寸增加而增加，並在 0.3 mm 時增加至  $16.53 \text{ }^{\circ}\text{C W}^{-1}$ ，從圖 3.28 中熱阻的比較可見，PCB 熱阻的變化與填充焊料時的情況並不相同，熱阻在熱通孔尺寸小於 0.2 mm 時會受到熱通孔側壁的銅影響使得整體 PCB 熱阻降低，然而當熱通孔尺寸增加至 0.2 mm 後，受到空氣的熱傳導係數非常小的影響，反而出現熱阻隨尺寸增加而提升的情況，且越大的熱通孔因為空氣越多，PCB 分層的熱阻值也隨之增加。分層的熱容則與熱阻有類似的變化趨勢，從圖 3.29 中熱容隨尺寸的變化可見，在尺寸小於 0.2 mm 時，熱容從 0.1 mm 的  $1.47 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$  增加至 0.2 mm

時的熱容為  $1.89 \times 10^{-2} \text{ J } ^\circ\text{C}^{-1}$ ，而在熱通孔尺寸超過 0.2 mm 後熱容開始下降，並在 0.3 mm 時降低為  $1.55 \times 10^{-2} \text{ J } ^\circ\text{C}^{-1}$ ，此時熱容的變化並不只受空氣的比熱影響，熱阻對熱容的影響更為明顯，熱阻在熱通孔尺寸 0.2 mm 後上升，使得熱量較難以傳遞至 PCB 垂直方向分散儲存，因此整體 PCB 分層的熱容下降，較容易出現局部熱點的情形。

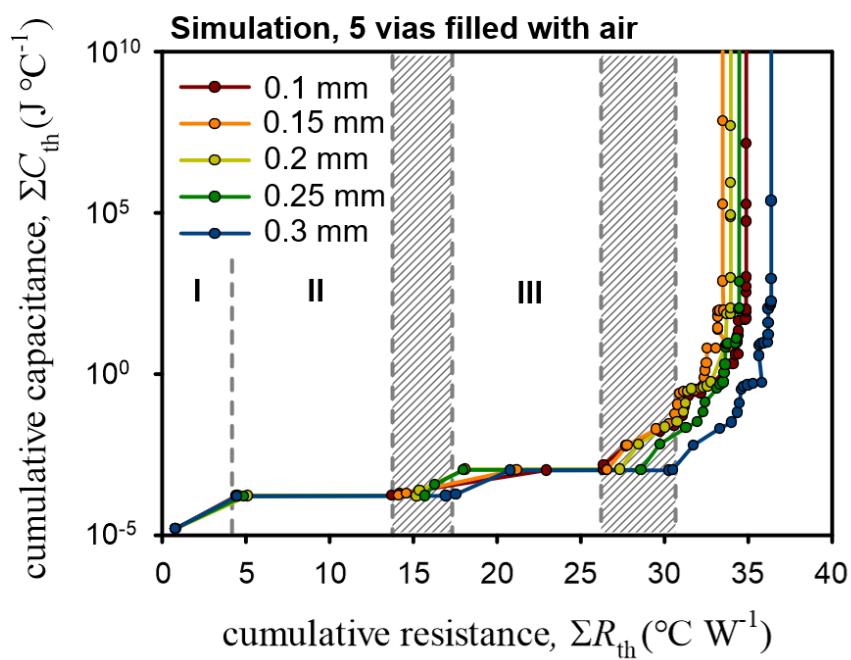

圖 3.23 為 5 個無填充物的熱通孔模擬結構函數，從圖 3.28 整理的熱阻值可以看見，5 個熱通孔的 PCB 層熱阻變化與 4 個熱通孔的變化趨勢類似，同樣在 0.2 mm 有一轉折點，小於 0.2 mm 時熱阻隨尺寸的增加而下降，從尺寸 0.1 mm 的熱阻值  $16.01 \text{ } ^\circ\text{C W}^{-1}$ ，下降至 0.2 mm 的轉折點時熱阻值為  $14.83 \text{ } ^\circ\text{C W}^{-1}$ 。在大於 0.2 mm 後，因為中心熱通孔的存在，使得熱阻增加的幅度更為明顯，在熱通孔 0.3 mm 時的熱阻  $16.33 \text{ } ^\circ\text{C W}^{-1}$  甚至相比 0.1 mm 時的熱阻值還要大，主要是受到熱通孔尺寸大、填充物的空氣含量也較多，因此熱量透過熱通孔的傳遞能力明顯降低。PCB 層熱容由圖 3.29 中可以得知，在尺寸小於 0.2 mm 時，熱容從  $1.65 \times 10^{-2} \text{ J } ^\circ\text{C}^{-1}$  增加至  $2.2 \times 10^{-2} \text{ J } ^\circ\text{C}^{-1}$ ，熱通孔尺寸超過 0.2 mm 後，熱容開始下降，變化的趨勢與原因與 4 個熱通孔的情形相同。

6 個熱通孔的模擬結構函數如圖 3.24 所示，整理的熱阻與熱容從圖 3.28 與圖 3.29 可以得知，熱阻以及熱容不隨尺寸的增加而有改變，在圖中近乎呈現一水平線，同樣可用以說明相較於 4 個與 5 個熱通孔的 PCB 層，增加的中間上方與中間下方的兩個熱通孔對於熱量的傳遞並沒有提供太大的幫助。

7 個熱通孔隨尺寸變化的模擬結構函數如圖 3.25 所示，與 6 個熱通孔相比增加一個中心熱通孔，這一個中心熱通孔使得在熱通孔尺寸 0.3 mm 之前，因為中心熱通孔側壁的銅使得熱傳導較佳，熱阻都小於 6 個熱通孔的熱阻值，但在 0.3 mm

時，因為熱通孔中的空氣含量過多，空氣的熱傳導係數極差使得中心熱通孔的增加反而令熱阻較大。變化趨勢由圖 3.28 中可見，與 4 個熱通孔、5 個熱通孔的樣品相同，在 0.2 mm 時出現明顯轉折，小於 0.2 mm 的 PCB 層熱阻幾乎持平或僅有些微的下降；而在大於 0.2 mm 後的熱阻值，從熱阻值  $14.87 \text{ }^{\circ}\text{C W}^{-1}$ ，0.3 mm 時劇烈增加到  $16.42 \text{ }^{\circ}\text{C W}^{-1}$ ，大幅上升 10.4%。由圖 3.33 可以觀察 7 個熱通孔熱容隨尺寸的變化情形，同樣在 0.2 mm 時有最大熱容  $2.37 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$ ，並隨著尺寸的增加而熱容開始下降，變化的趨勢與原因與 4 個、5 個熱通孔的情形相同。

8 個與 9 個熱通孔模擬所得的結構函數如圖 3.26 與圖 3.27 所示，兩者因為熱通孔的面積已經涵蓋功率放大器晶片發熱源的範圍，因此從圖 3.28 中可以觀察到，在熱通孔尺寸小於 0.2 mm 時，PCB 層熱阻並沒有隨著尺寸的增加而有下降，而是維持相近的熱阻值。特別在 0.2 mm 後，受到熱通孔內空氣接觸面積的增加，熱阻開始大幅上升，8 個熱通孔的熱阻從 0.2 mm 的  $14.43 \text{ }^{\circ}\text{C W}^{-1}$ ，0.3 mm 增加到  $16.97 \text{ }^{\circ}\text{C W}^{-1}$ ，上升了 17.6%；9 個熱通孔時熱阻的增加幅度更為明顯，從 0.2 mm 的  $14.07 \text{ }^{\circ}\text{C W}^{-1}$ ，0.3 mm 時增加到所有模擬的功率放大器樣品中最大的 PCB 層熱阻值  $17.31 \text{ }^{\circ}\text{C W}^{-1}$ ，增加了 23%。從圖 3.29 中可以見到熱容的變化，9 個熱通孔的樣品同樣在 0.2 mm 之後有一明顯的下降，特別在 9 個熱通孔的尺寸從 0.2 mm 增加至 0.3 mm 時，熱容從  $2.67 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$  減少至  $2.1 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$ ，但 9 個熱通孔因為整體的熱通孔數量最多，使得熱容值在熱通孔尺寸 0.3 mm 前，受到空氣的比熱較大的影響，PCB 分層的熱容仍是所有樣品中最大的；熱通孔尺寸 0.3 mm 時則因為熱阻較大的影響，使得熱量不易傳遞至 PCB 垂直的方向分散與儲存，因此有熱容的明顯降低。

將結構函數中的 PCB 層熱阻對熱通孔數目作圖，從圖 3.30 热阻的變化可以看出，當尺寸為 0.1 mm 時，含有中心熱通孔的 5、7 及 9 個熱通孔的排列方式，

使熱阻相較於沒有中心熱通孔的 4、6 及 8 個熱通孔有較明顯的下降，熱阻與熱通孔的數量呈現起伏變化；尺寸為 0.15 mm 及 0.2 mm 時，當熱通孔數量大於 6 個熱通孔，熱阻開始隨熱通孔的數量增加而下降，中心熱通孔的影響並不明顯；當尺寸大於 0.25 mm 時，熱阻受到熱通孔的尺寸影響較大，特別在尺寸 0.3 mm 下， 6 個熱通孔後熱阻都隨著熱通孔的數量增加而大幅上升。

PCB 層的熱容對熱通孔數目變化從圖 3.31 可見，在尺寸 0.1 mm 時，熱容隨著熱通孔的數量增加而上升，與中心熱通孔的有無並沒有太明顯的關聯，主因為熱通孔尺寸 0.1 mm 時，熱通孔內空氣的接觸面積小，熱阻較小使得熱量得以因為熱通孔的增加而更好的均勻分散儲存至整體 PCB，熱容因此上升。隨著尺寸增加後，0.15 mm 至 0.3 mm 的熱容變化的方式大致相同，含有中心熱通孔的 5 個、7 個以及 9 個熱通孔的功率放大器樣品中，PCB 層熱容都會相較於沒有中心熱通孔的功率放大器樣品還要來得大，原因同樣為受到中心熱通孔的增加，熱阻的降低讓熱量能均勻分散儲存，因此圖 3.31 中會呈現如波浪狀的熱容變化。

從上述的討論，以及圖 3.32 與圖 3.33 中 PCB 層的熱阻與熱容分布圖可以得知，當熱通孔填充物為空氣時，熱通孔數目增加及尺寸加大、熱通孔數目減少及尺寸縮小，皆會使得 PCB 層熱阻變大、熱容會降低，而導致整體熱傳效益變差。另外，含有中心熱通孔的樣品在小尺寸的熱通孔時，雖然能降低熱阻並增加熱容，但效果並不顯著，反而是熱通孔大於 0.2 mm 時，中心熱通孔的存在會大幅增加熱阻值。因此當熱通孔中填充物為空氣時，熱通孔設計會以增加熱通孔數量且選擇適當尺寸的方向設計為佳。

### 3.2.3 填充防焊漆之熱通孔

在電路的應用中，為了避免產生漏氣 (air leakage) 或者靠近 PCB 板的電子零

件發生短路，在不增加成本的方式下，經常以防焊漆填補熱通孔，確保電子元件的正常運作[38]。圖 3.34 至圖 3.39 為功率放大器樣品熱通孔填充防焊漆的結構函數，從區域 I 至區域 III 的熱阻值可以觀察到，每一區域的熱阻與填充物為空氣的功率放大器樣品之結構函數幾乎相同，特別的是，從表 2.1 中可知空氣與防焊漆的熱傳導係數相差一個數量級，然而熱傳導係數的差別並沒有對 PCB 層的熱阻產生明顯的影響，而比熱也僅有些微的差異，因此分層的熱容也相差不大。

4 個熱通孔在不同尺寸的結構函數如圖 3.34 所示，從圖 3.40 整理的 PCB 層熱阻值變化可以知道，熱阻從熱通孔尺寸 0.1 mm 增加至 0.25 mm 皆有些許的降低，而尺寸增加至 0.25 mm 時熱阻出現轉折開始上升，主要原因與填充空氣之熱通孔相同，熱通孔尺寸小於 0.25 mm 時會受到熱通孔填充物為防焊漆與側壁之鋪銅層的影響使得整體 PCB 热阻降低，然而當熱通孔尺寸增加至 0.25 mm 後，受到防焊漆的熱傳導係數非常小的影響，反而出現熱阻隨尺寸增加而提升的情況，且越大的熱通孔因為防焊漆的接觸面積越大，PCB 分層的熱阻值也隨之增加，但整體的熱阻仍沒有劇烈的變化，皆在  $16\text{--}17 \text{ }^{\circ}\text{C W}^{-1}$  之間。從 3.2.2 小節的結果與以上的推論得知，防焊漆的熱傳導係數較空氣大一個數量級，因此轉折之熱通孔尺寸相較填充物為空氣的熱通孔尺寸為 0.2 mm，填充防焊漆的轉折熱通孔尺寸增加為 0.25 mm。熱容的變化同樣呈現隨著尺寸增加先上升後下降的變化，原因亦與填充空氣之熱通孔相同，此時熱容的變化並不只受防焊漆的比熱影響，熱阻對熱容的影響更為明顯，熱阻在熱通孔尺寸 0.25 mm 後上升，使得熱量較難以傳遞至 PCB 垂直方向分散儲存，因此整體 PCB 分層的熱容下降，從 0.1 mm 的  $1.53 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$  增加至 0.2 mm 的  $1.82 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$ ，而後下降至 0.3 mm 的  $1.62 \times 10^{-2} \text{ J }^{\circ}\text{C}^{-1}$ ，變化的趨勢如圖 3.41 所示。

圖 3.35 與圖 3.36 為 5 個與 6 個熱通孔的結構函數，兩者結構函數上在分層 II 的差異受到中心熱通孔的影響，5 個熱通孔在分層 II 受不同熱通孔數量影響所產生的差異較大，與 3.2.1 小節討論的情況相同。從圖 3.40 中可見，在 5 個以及 6 個填充防焊漆的熱通孔下，熱通孔的尺寸增加至  $0.15 \sim 0.2$  mm 時熱阻有一個轉折點，在轉折點之前的熱阻會隨著尺寸的增加而有降低，而在轉折點之後的熱阻卻有較明顯的上升，此一現象的發生同樣受到防焊漆的熱傳導係數較小所影響。5 個熱通孔時尺寸從 0.2 mm 的 PCB 層熱阻  $15.05 \text{ } ^\circ\text{C W}^{-1}$ ，到 0.3 mm 時的熱阻增加為  $16.13 \text{ } ^\circ\text{C W}^{-1}$ ，增加 7.7%；6 個熱通孔的熱阻在 0.3 mm 時的熱阻為  $16.28 \text{ } ^\circ\text{C W}^{-1}$ ，超過 5 個熱通孔 0.3 mm 時的熱阻，在  $0.25 \text{ mm} \sim 0.3 \text{ mm}$  之間出現一分岔點。從圖 3.41 整理的尺寸對於熱容的影響可見，5 個熱通孔與 6 個熱通孔同樣在 0.15 mm 時有熱容的最大值  $1.95 \times 10^{-2} \text{ J } ^\circ\text{C}^{-1}$ ，隨後開始隨著尺寸增加下降，而 6 個熱通孔在 0.3 mm 時的熱容，低於 5 個熱通孔在 0.3 mm 時的熱容，此情形與熱阻的變化相似，主要都是受到在 0.3 mm 時熱通孔所覆蓋的面積較大，含有中心熱通孔的 PCB 層因此有較低的熱阻，固有相較於 6 個熱通孔時較大的熱容值。

熱通孔數量為 7 個、8 個及 9 個的模擬結構函數如圖 3.37 至圖 3.39 所示，從圖 3.40 整理的 PCB 層熱阻可以得知，當熱通孔數量增加至 7 個後，熱通孔的轉折尺寸為 0.15 mm，超過轉折的尺寸後三者的熱阻開始大幅上升，三者從 0.15 mm 增加至 0.3 mm 分別有 13.6%、13.5% 以及 17.5% 的熱阻值增加，9 個熱通孔在 0.3 mm 時的 PCB 層熱阻值為  $16.83 \text{ } ^\circ\text{C W}^{-1}$ ，與其他尺寸同樣是 0.3 mm 的熱阻相比都還要大，主要是因為受到填充防焊漆的熱傳導係數影響所致。熱容的變化如圖 3.41 中可見，與熱阻的變化相似，在熱通孔尺寸大於 0.15 mm 後，熱容開始有陡峭的下滑，三者從 0.2 mm 增加至 0.3 mm 時熱容的下降幅度分別有 30.8%、35.6% 及 34.2%。

從熱阻與熱容的變化可以得知，在 7、8 及 9 個熱通孔時，熱通孔尺寸的增加對於 PCB 層的總體面積占比較大，使得熱通孔填充物防焊漆的接觸面積占比增加，因此熱阻在超過 0.15 mm 後開始大幅上升，而熱容則因為熱量在 PCB 垂直方向傳遞較為困難，而導致熱量無法均勻分散與儲存，熱容也隨之大幅下降。

以熱通孔的數量與排列探討 PCB 層熱阻與熱容的變化，結果如圖 3.42 與圖 3.43 所示。在尺寸小於 0.2 mm 時，整體的熱阻隨著熱通孔數量的增加而呈現下降的趨勢，但以排列位置觀察，含有中心熱通孔的 5 個、7 個以及 9 個熱通孔的功率放大器樣品 PCB 層熱阻會有較明顯下降。尺寸超過 0.2 mm 之後，並不受到熱通孔排列的影響，而是隨著數量增加，熱通孔內防焊漆的接觸面積增加，使得熱通孔數量的增加，熱阻不減反增。熱容的變化同樣與熱阻相似，尺寸 0.1 mm、0.15 mm 及 0.2 mm 的熱容趨勢是隨著熱通孔數量增加而上升，並在含有中心熱通孔時熱容會相較沒有中心熱通孔的樣品增加，而尺寸 0.25 mm 及 0.3 mm 時的熱容，則是隨著熱通孔數量增加而持平或下降，且中心熱通孔的存在對熱容沒有明顯影響。

綜合本小節的討論與圖 3.44 及圖 3.45 的熱阻與熱容數值分布圖可以得知，熱通孔填充物為防焊漆時，會出現兩種對散熱較差的設計，第一種為熱通孔數量少且尺寸小，第二個為熱通孔數量多且尺寸大，前者因為一定數量的熱通孔側壁仍有銅層幫助散熱，因此當熱通孔的數量少或尺寸小時對於熱量傳遞不利；而後者則受到熱通孔填充材料為防焊漆，防焊漆的熱傳導係數小，使得熱通孔數量多或尺寸增加時，填充物的接觸面積增加，熱阻也會隨之增加。因此當填充物為防焊漆時，設計將以熱通孔數量 9 個且熱通孔的尺寸約 0.15 mm ~ 0.2 mm 為佳，可以得到最小的熱阻值與最大的熱容值，幫助熱量傳遞並散熱。

Shen 等人[5] 對填充空氣與填充防焊漆的熱通孔以解析解計算 PCB 分層的熱

阻，結果顯示因為兩者填充物的熱傳導係數較小，在熱通孔尺寸小於約 0.25 mm 時熱阻會隨著熱通孔尺寸增加而下降，但熱通孔尺寸大於 0.25 mm 後的熱阻開始隨著尺寸增加而上升，與本實驗所得之結果相同，填充物為空氣與防焊漆時有一最佳的熱通孔數量及尺寸，超過最佳設計的數量或尺寸反而會使得熱阻上升。

### 3.3 不同填充物之熱通孔比較

本節將對 PCB 中熱通孔填充不同填充物所造成熱行為的影響進行討論。

#### 3.3.1 热阻比較

圖 3.46 至圖 3.51 為 4 個至 9 個熱通孔下，不同熱傳導係數的填充物隨著熱通孔尺寸變化的比較，其中熱傳導係數由小到大分別為  $k = 2.6 \times 10^{-2} \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  之無填充物的空氣、 $k = 2.3 \times 10^{-1} \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  之防焊漆填充物、 $k = 5 \times 10^1 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  之焊料填充物。為了觀察不同熱傳導係數所造成的 PCB 層熱阻變化，增加一個比較材料，並設定熱傳導係數為  $k = 2 \times 10^1 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  進行模擬，並同樣得到結構函數後將 PCB 層的熱阻與熱容提取出來。從圖 3.46 至圖 3.51 中可見， $k = 2.6 \times 10^{-2} \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  與  $k = 2.3 \times 10^{-1} \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  的填充物雖然在熱傳導係數上差了一個數量級，但 PCB 層的熱阻幾乎沒有差別，而在填充物增加至  $k = 2 \times 10^1 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  時，相較於前兩者熱阻有一大幅的降低，推測熱阻的降低並非與熱傳導係數的增加呈現線性關係，而是呈現與熱傳導係數的對數關係減少，主要的原因為整體 PCB 層的熱阻為熱通孔的熱阻以及 FR4 材料的熱阻，兩者進行並聯所得之結果，因此改變熱通孔填充物的熱傳導係數時，PCB 分層的整體熱阻才會以接近對數關係減少。

將不同熱傳導係數的結果中，出現最低熱阻值的區間劃分出一塊 PCB 層熱阻最小值的區域，如圖 3.46 至圖 3.51 中斜線區域所示。此一區域可提供在使用不同

熱通孔填充物時的尺寸建議，在範圍內所選取之熱通孔的尺寸將獲得最小值熱阻，熱量能夠有效的傳遞。

從圖 3.46 及圖 3.47 的 4 個及 5 個熱通孔最小熱阻區域可見，當填充物為空氣及防焊漆，即熱傳導係數較小的填充材料時，所對應的最佳熱通孔尺寸約在 0.2 mm 附近，並隨著使用的填充材料熱傳導係數越小而最佳尺寸越小，尺寸超過範圍的熱通孔反而會使得熱阻提升；而隨著熱傳導係數增加後，填充物為焊料或  $k = 2 \times 10^1 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  的材料時，熱通孔的尺寸增加可有效降低熱阻，使得最佳尺寸的範圍增加至 0.25 mm~0.3 mm 之間。另外，從圖 3.47 中可以觀察到 5 個熱通孔在  $k = 2 \times 10^1 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  及  $k = 5 \times 10^1 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  兩者的熱阻值差異明顯較 4 個熱通孔大，主要是因為中心熱通孔的存在，對於使用不同熱傳導係數填充物時的靈敏度提高。

圖 3.48 為 6 個熱通孔使用不同熱傳導係數的填充物熱阻比較，最小值的熱阻區間同樣隨著填充物的熱傳導係數增加而對應之熱通孔尺寸增加，與 4 個及 5 個熱通孔比較最大的差別在於，在  $k = 2 \times 10^1 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  及  $k = 5 \times 10^1 \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  之間的熱阻差異更為明顯，使用不同熱傳導係數填充物時的靈敏度隨著熱通孔數量的增加更為提高。

7 個、8 個以及 9 個的熱阻變化如圖 3.49、圖 3.50 及圖 3.51 所示，在填充物的熱傳導係數為  $k = 2.6 \times 10^{-2} \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  及  $k = 2.3 \times 10^{-1} \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  的情況下，最佳熱通孔尺寸變小，如圖 3.50 及圖 3.51 中在熱傳導係數小於  $k = 2.6 \times 10^{-2} \text{ W m}^{-1} \text{ }^{\circ}\text{C}^{-1}$  時，可容許的熱通孔設計尺寸約為 0.1 mm 至 0.2 mm，主要是因為填充物的熱傳導係數低時，增加熱通孔的尺寸會使得填充物的接觸面積增加，會使得熱阻變大，因此建議的設計尺寸下降。隨著填充物的熱傳導係數增加，尺寸的增加使填充物對熱

傳的影響增加，最小熱阻的區域隨熱傳導係數的增加，最佳熱通孔的設計尺寸也會變大。

綜合以上討論，以熱阻作為最佳的熱通孔設計之依據進行總結，PCB 層熱阻受到填充物的熱傳導係數影響最為明顯，填充物熱傳導係數較小時，隨著熱通孔數量增加，所容許之最佳熱通孔尺寸也會變小，以減少熱通孔內填充物與其他分層的接觸面積；使用熱傳導係數較大的填充物時，熱通孔尺寸以  $0.2\text{ mm} \sim 0.3\text{ mm}$  為最佳設計，繼續增加熱通孔尺寸對熱阻的降低並不明顯，反而會增加製造成本與電性上的問題。

### 3.3.2 热容比較

圖 3.52 至圖 3.57 為不同填充物的熱通孔之熱容比較，其中比熱由大到小分別為  $c_p = 1.4 \times 10^3 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  之防焊漆填充物、 $c_p = 1.005 \times 10^3 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  之空氣填充物、 $c_p = 1.5 \times 10^2 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  之焊料填充物，而  $c_p = 5 \times 10^2 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  則對應熱傳導係數為  $20 \text{ W m}^{-1} \text{ }^\circ\text{C}^{-1}$  用以比較的填充材料。PCB 分層的熱容增加可以提供更多的熱量儲存能力，有助於熱量的分布均勻，減少局部熱點的形成，有助於提高元件的工作溫度以及減少因為高溫而造成之功率放大器效能降低。

從圖 3.52 至圖 3.57 中可見，當填充物比熱為  $1.4 \times 10^3 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  的防焊漆及  $1.005 \times 10^3 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  的空氣時，在熱通孔為較小的尺寸時，填充物比熱為主導 PCB 層熱容的因素，熱通孔尺寸增加而熱容隨之有所提升，但超過一定大小的尺寸後，熱容反而開始下降，不同熱通孔數的最大尺寸有所不同，但都約為  $0.15\text{ mm} \sim 0.2\text{ mm}$  之間，超過此熱通孔大小後熱容即開始下降。此現象與熱阻的變化相關，這兩種填充物的熱阻變化是隨著尺寸增加到一定大小時出現轉折點，熱阻開始隨著尺寸增加而上升，因此推測在小尺寸時垂直熱阻較小，熱量在 PCB 層的垂直傳遞速

度增加，使熱量不僅是在接近晶片層的表面儲存，而是於 PCB 垂直方向分散，使得整體熱容增加，反之當垂直熱阻增加時，則整體 PCB 的熱容降低。

在熱通孔小尺寸時，比熱為  $5 \times 10^2 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  的比較用填充物以及  $1.5 \times 10^2 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  焊料填充物之 PCB 層熱容雖然低於比熱較大的兩種填充物，但其熱容隨著尺寸而持續增加，主要也與熱阻的變化相關，兩種填充物的 PCB 分層熱阻都是隨著尺寸增加而降低，與前述的原因相同，熱阻降低時熱容增加，因此熱容才會隨著尺寸而持續增加，並在熱通孔尺寸約  $0.25 \text{ mm} \sim 0.3 \text{ mm}$  時，比熱較小的填充物 PCB 分層熱容反而大於前段所述的比熱較大的填充物樣品 PCB 層熱容。

特別的是，比較兩種小比熱的填充物 PCB 層熱容結果時，當僅有 4 個與 5 個熱通孔，因為熱通孔數量少，填充物的比熱對熱容影響較低，比熱為  $1.5 \times 10^2 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  對應的熱傳導係數為  $5 \times 10^1 \text{ W m}^{-1} \text{ }^\circ\text{C}^{-1}$ ，其擁有四種填充物的熱阻最小值，因此垂直熱量傳遞速度增加，整體熱容相較於填充物比熱為  $5 \times 10^2 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  的結果更大，PCB 層的熱容變化為熱阻較小時則熱容較大。而熱通孔數量增加至 6 個以上，熱通孔中填充物的比熱性質對 PCB 分層的熱容影響增加，受到熱阻的影響降低，因此比熱為  $5 \times 10^2 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  的整體 PCB 熱容皆大於  $1.5 \times 10^2 \text{ J kg}^{-1} \text{ }^\circ\text{C}^{-1}$  的熱容。

綜合熱容的討論結果，熱容的變化不僅需考慮填充物的比熱，熱阻對其影響甚劇，受到 PCB 在縱向與橫向的熱傳差異，垂直熱阻值較大時整體 PCB 熱容通常會較小，反之則有較大的熱容值。唯一的例外為使用的材料比熱值較小時，需考慮熱通孔數量及比熱兩個因素的影響，熱通孔數量較少時受到熱阻的影響較明顯，熱阻較低者熱容有較大值，並且熱容隨尺寸增加而上升；熱通孔數量增加到一定數量後，僅需考慮熱通孔中填充物的比熱大小，隨填充物比熱的增加而有較大的 PCB 層熱容，並且熱容同樣隨熱通孔尺寸的增加而上升。

## 第四章 結論與建議

本研究建構一暫態熱特性量測平台，對不同 PCB 分層上熱通孔設計之功率放大器樣品進行暫態量測，以結構函數探討 PCB 分層的熱阻與熱容變化。此外，亦利用數值模擬，對實驗結果進行驗證，並透過模擬更改熱通孔的填充材料、數量及尺寸，探討不同的熱通孔設計對於功率放大器 PCB 分層熱網絡的影響。茲將結論與建議分述如下：

### 4.1 結論

1. 實驗中功率放大器在 PCB 層為 13 個熱通孔時有最小分層熱阻值  $3.25\text{ }^{\circ}\text{C W}^{-1}$ ，而 4 個熱通孔之 PCB 分層熱阻為  $9.55\text{ }^{\circ}\text{C W}^{-1}$ ，兩者相比熱阻有效降低 65.9%；PCB 層 13 個熱通孔的功率放大器樣品，熱從晶片層傳遞至 PCB 底部所需時間，相較 4 個熱通孔的時間減少 39.1%，且最高結溫降低  $7\text{ }^{\circ}\text{C}$ ，代表在 PCB 分層的熱通孔數量增加下，熱量能夠更有效率地從結接面傳遞至 PCB 底部。

2. 填充焊料的熱通孔在 PCB 分層為 9 個熱通孔、尺寸  $0.3\text{ mm}$  時因為填充物熱傳導係數較大的優勢，與熱通孔相同填充焊料的其他樣品相比，有 PCB 分層熱阻最小值  $3.63\text{ }^{\circ}\text{C W}^{-1}$ ；熱容則因為垂直熱阻的降低，熱量在 PCB 分層中有較佳的分散，並在特徵時間變化不大的情況下，而有最大的熱容  $2.26 \times 10^{-2}\text{ J }^{\circ}\text{C}^{-1}$ ，熱容的增加讓 PCB 層中溫度分布更加均勻。特別的是，PCB 層以及晶片層的溫度特徵時間受到 PCB 層的熱阻主宰，與熱容的變化無明顯關係，且特徵時間皆隨著 PCB 層熱阻減少而縮短。

3. 热通孔填充物為熱傳導係數較小的空氣與防焊漆填充物時，熱通孔在大於一

定尺寸後受到填充物的熱傳導係數影響使熱阻增加，並讓熱容受到熱阻的影響而下降，因此設計時選擇熱通孔數量多，且尺寸適當大小為佳。填充物為空氣時以 9 個熱通孔、尺寸 0.2 mm 有熱阻最小值  $14.07\text{ }^{\circ}\text{C W}^{-1}$  及最大的熱容  $2.67 \times 10^{-2}\text{ J }^{\circ}\text{C}^{-1}$ ，填充物為防焊漆時以 9 個熱通孔、尺寸 0.15 mm 有熱阻最小值  $14.05\text{ }^{\circ}\text{C W}^{-1}$  及最大的熱容  $2.33 \times 10^{-2}\text{ J }^{\circ}\text{C}^{-1}$ 。

4. 热通孔填充物的熱傳導係數為影響 PCB 分層熱阻的主要因素，當使用的填充物為空氣與防焊漆，即熱傳導係數低於一定值時，熱阻有一最佳設計的尺寸，繼續增加熱通孔尺寸反而會使得填充物的面積增加，而造成熱阻上升；使用熱傳導係數為較大的焊料時，熱阻則隨熱通孔的尺寸增加而持續降低。

5. 热通孔填充物為比熱小於 FR4 材料的焊料時，可以分為兩種情形，若熱通孔數量大於 6 個時，填充物的比熱為影響 PCB 層之熱容的主要因素，因為熱通孔占整體 PCB 面積較大，使得 PCB 層熱容相較 6 個熱通孔以下的樣品皆明顯降低；在熱通孔數量少於 6 個的情況下，PCB 層熱阻的大小為主要影響熱容的因素，熱阻降低使熱量能夠分散於 PCB 分層中，在特徵時間變化不大下，PCB 層熱容因此有較大值。而填充物為比熱較大的空氣或防焊漆時，PCB 層熱阻的大小為主要影響熱容的因素，熱通孔小於尺寸約 0.2 mm 時，PCB 分層的熱阻會隨著尺寸增加而下降，分層熱容會隨之增加，當熱通孔尺寸大於 0.2 mm 後則因為熱阻上升而有較小的熱容值。

## 4.2 建議

1. 由於本實驗中順向電壓量測所使用之資料擷取器的最小量測時間限制，無法量測到  $1\text{ }\mu\text{s}$  時間尺度的電壓變化，使得結構函數中的熱容數量級並不準確，

需要透過數值模擬進行額外的校正。若在未來能使用如 T3ster<sup>®</sup>的設備，量測時間尺度為 1  $\mu$ s 的資料擷取器，獲得精確的電壓變化，將更有助於了解結構函數中分層的熱容變化。

2. 本研究所使用的程式碼仍需跨平台使用 Matlab 與 C++進行計算，若能將程式碼進行整合，將有助於使用的便利性。

3. 本研究中實際量測的功率放大器樣品僅更改熱通孔的數量，其他結果皆以模擬進行驗證，若能實際替換熱通孔的材料，亦或是更改其他分層的設計，例如更換晶片黏接材料等，基於本實驗的手法，將有助於更全面的了解功率放大器的散熱優化設計方向。

## 參考文獻

- [1] K. Hoo Teo, Y. Zhang, N. Chowdhury, S. Rakheja, R. Ma, Q. Xie, E. Yagyu, K. Yamanaka, K. Li and T. Palacios, "Emerging GaN technologies for power, RF, digital, and quantum computing applications: Recent advances and prospects," *Journal of Applied Physics*, vol. 130, no. 16, 2021, doi: 10.1063/5.0061555.

- [2] M. Mahalingam, "RF power amplifier thermal design," in *Handbook of RF and Microwave Power Amplifiers*, J. L. B. Walker, Ed., USA: Cambridge University Press, 2011, pp. 411-445.

- [3] T. Kang, Y. Ye, Y. Jia, Y. Kong and B. Jiao, "Enhanced thermal management of GaN power amplifier electronics with micro-pin fin heat sinks," *Electronics*, vol. 9, no. 11, doi: 10.3390/electronics9111778

- [4] *Transient dual interface test method for the measurement of the thermal resistance junction-to-case of semiconductor devices with heat flow through a single path*, JEDEC Standards 51-14, 2010.

- [5] Y. Shen, H. Wang, F. Blaabjerg, H. Zhao and T. Long, "Thermal modeling and design optimization of PCB vias and pads," *IEEE Transactions on Power Electronics*, vol. 35, no. 1, pp. 882-900, 2020, doi: 10.1109/TPEL.2019.2915029.

- [6] Simcenter Micred T3STER, Siemens, 2023. [Online]. Available: <https://plm.sw.siemens.com/en-US/simcenter/physical-testing/t3ster/>

- [7] D. L. Blackburn, "Temperature measurements of semiconductor devices - a review," in *Proceedings of. Twentieth Annual IEEE Semiconductor Thermal Measurement and Management Symposium*, San Jose, CA, USA, March 11, 2004, pp. 70-80, doi: 10.1109/STHERM.2004.1291304.

- [8] Y. Xi and E. F. Schubert, "Junction-temperature measurement in GaN ultraviolet light-emitting diodes using diode forward voltage method," *International Journal of High Speed Electronics and Systems*, vol. 14, no. 03, pp. 708-713, 2004, doi: 10.1142/S0129156404002715.

- [9] M. H. M. Sathik, J. Pou, S. Prasanth, V. Muthu, R. Simanjorang and A. K. Gupta, "Comparison of IGBT junction temperature measurement and estimation methods-a review," in *Proceedings of. 2017 Asian Conference on Energy, Power and Transportation Electrification*, Oct. 24-26, 2017, pp. 1-8, doi: 10.1109/ACEPT.2017.8168600.

- [10] D. L. Blackburn and D. W. Berning, "Power MOSFET temperature measurements," in *Proceedings of. 1982 IEEE Power Electronics Specialists conference*, Cambridge, MA, USA, June 14-17, 1982, pp. 400-407, doi: 10.1109/PESC.1982.7072436.

- [11] E. J. Diebold and W. Luft, "Transient thermal impedance of semiconductor

- devices," *Transactions of the American Institute of Electrical Engineers, Part I: Communication and Electronics*, vol. 79, no. 6, pp. 719-726, 1961, doi: 10.1109/TCE.1961.6373039.

- [12] Z. Jakopovic, Z. Bencic and F. Kolonic, "Important properties of transient thermal impedance for MOS-gated power semiconductors," in *Proceedings of. ISIE '99. Proceedings of the IEEE International Symposium on Industrial Electronics*, July 12-16, 1999, vol. 2, pp. 574-578, doi: 10.1109/ISIE.1999.798675.

- [13] V. Székely, "A new evaluation method of thermal transient measurement results," *Microelectronics Journal*, vol. 28, no. 3, pp. 277-292, 1997, doi: 10.1016/S0026-2692(96)00031-6.

- [14] V. Székely, "THERMODEL: a tool for compact dynamic thermal model generation," *Microelectronics Journal*, vol. 29, no. 4, pp. 257-267, 1998, doi: 10.1016/S0026-2692(97)00065-7.

- [15] V. Székely, "Enhancing reliability with thermal transient testing," *Microelectronics Reliability*, vol. 42, no. 4, pp. 629-640, 2002, doi: 10.1016/S0026-2714(02)00028-8.

- [16] V. Székely, "Identification of RC networks by deconvolution: chances and limits," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 45, no. 3, pp. 244-258, 1998, doi: 10.1109/81.662698.

- [17] T. J. Kennett, W. V. Prestwich and A. Robertson, "Bayesian deconvolution I: Convergent properties," *Nuclear Instruments and Methods*, vol. 151, no. 1, pp. 285-292, 1978, doi: 10.1016/0029-554X(78)90502-5.

- [18] N. Dey, L. Blanc-Feraud, C. Zimmer, P. Roux, Z. Kam, J.-C. Olivo-Marin and J. Zerubia, "3D microscopy deconvolution using Richardson-Lucy algorithm with total variation regularization," *Microscopy research and technique*, vol. 69, pp. 260-6, 2006, doi: 10.1002/jemt.20294.

- [19] V. Bissuel, E. Monier-Vinard, Q. Dupuis, O. Daniel, N. Laraqi and J. G. Bauzin, "Application of stochastic deconvolution methods to improve the identification of complex BCI multi-port thermal RC networks," in *Proceedings of. 2020 19th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (iTherm)*, Orlando, FL, USA, July 21-23, 2020, pp. 236-243, doi: 10.1109/iTherm45881.2020.9190341.

- [20] Q. Dupuis, V. Bissuel, N. Laraqi, J. G. Bauzin and O. Daniel, "A Bayesian deconvolution application to calibrate multi-port RC network representation of electronic packages," in *Proceedings of. 2021 20th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (iTherm)*, San Diego, CA, USA, June 1-4, 2021, pp. 139-144, doi: 10.1109/iTherm51669.2021.9503278.

- [21] Y. C. Gerstenmaier, W. Kiffe and G. Wachutka, "Combination of thermal subsystems by use of rapid circuit transformation and extended two-port theory," *Microelectronics Journal*, vol. 40, no. 1, pp. 26-34, 2009, doi: 10.1016/j.mejo.2008.09.002.

- [22] Y. C. Gerstenmaier and G. Wachutka, "Rigorous model and network for transient thermal problems," *Microelectronics Journal*, vol. 33, no. 9, pp. 719-725, 2002, doi: 10.1016/S0026-2692(02)00055-1.

- [23] L. Weinberg, *Network Analysis and Synthesis*. New York, NY, USA: McGraw-Hill, 1962.

- [24] V. Székely and T. Van Bien, "Fine structure of heat flow path in semiconductor devices: A measurement and identification method," *Solid-State Electronics*, vol. 31, no. 9, pp. 1363-1368, 1988, doi: 10.1016/0038-1101(88)90099-8.

- [25] M.-K. Kim and S. Yoon, "Thermal impedance characterization using optical measurement assisted by multi-physics simulation for multi-chip SiC MOSFET module," *Micromachines*, vol. 11, p. 1060, 11/30 2020, doi: 10.3390/mi11121060.

- [26] E. Ouyang, W. He, Y. Jeong, M. Chae, S. Gu, G. Kim and B. Ahn, "Thermal characterization and simulation of a fcBGA-H device," *International Symposium on Microelectronics*, vol. 2012, no. 1, pp. 809-817, 2012, doi: 10.4071/isom-2012-WP22.

- [27] R. Bornoff and A. Vass-Varnai, "A detailed IC package numerical model calibration methodology," in *Proceedings of. 29th IEEE Semiconductor Thermal Measurement and Management Symposium*, San Jose, CA, USA, March 17-21, 2013, pp. 65-70, doi: 10.1109/SEMI-THERM.2013.6526807.

- [28] A. L. Y. Beng, G. S. Hong and M. Devarajan, "Optimization of thermal vias for thermal resistance in FR-4 PCBs," in *Proceedings of. Fifth Asia Symposium on Quality Electronic Design (ASQED 2013)*, Penang, Malaysia, Aug. 26-28, 2013, pp. 345-349, doi: 10.1109/ASQED.2013.6643611.

- [29] PowerPAD™ thermally enhanced package, Texas Instruments, 1997. [Online]. Available: <https://www.ti.com/lit/an/slma002h/slma002h.pdf?ts=1675407389140>

- [30] M. T. Thompson, *Intuitive Analog Circuit Design*, second ed. Boston: Newnes, 2014, pp. 53-86.

- [31] Revised thermocouple reference tables, Omega Engineering, Inc., 2023. [Online]. Available: [https://assets.omega.com/pdf/tables\\_and\\_graphs/thermocouple-type-t-fahrenheit.pdf](https://assets.omega.com/pdf/tables_and_graphs/thermocouple-type-t-fahrenheit.pdf)

- [32] MATLAB. (2023). MathWorks. [Online]. Available: <https://www.mathworks.com/products/matlab.html>

- [33] Dev-C++. (2022). Bloodshed Software. [Online]. Available: [bloodshed.net](http://bloodshed.net)

- [34] S. W. Smith, *The Scientist and Engineer's Guide to Digital Signal Processing*, 2nd

- ed. California, CA, USA: California Technical Publishing, 1999, pp. 277-284.

- [35] *Ansys Icepak*. (2023). Ansys, Inc. [Online]. Available: <https://www.ansys.com/zh-tw/products/electronics/ansys-icepak>

- [36] Keysight DAQ970A data acquisition system user's guide, Keysight Technologies, 2020. [Online]. Available: <https://www.keysight.com/tw/zh/assets/9018-04738/user-manuals/9018-04738.pdf>

- [37] Keysight B2900A series precision source/measure unit, Keysight Technologies, 2020. [Online]. Available: <https://www.keysight.com/tw/zh/assets/7018-02794/data-sheets/5990-7009.pdf>

- [38] A. S. Cura, "Enhancement of thermal performance in QFN assembly with respect to solder coverage and thermal via design," M.S., State University of New York at Binghamton, United States, 2011

- [39] MatWeb, "Material property data." Available: <https://www.matweb.com/search/QuickText.aspx>

- [40] S. Cho and J. Lee, "Heat dissipation of printed circuit board by the high thermal conductivity of photo-imageable solder resist," *Electronic Materials Letters*, vol. 6, pp. 167-172, 2010, doi: 10.3365/eml.2010.12.167.

## 附錄

表 2.1 樣品之材料性質參數 [35, 39, 40]

| Material            | Physical properties             |                                              |                                                 |

|---------------------|---------------------------------|----------------------------------------------|-------------------------------------------------|

|                     | $\rho$<br>(kg m <sup>-3</sup> ) | $k$<br>(W m <sup>-1</sup> °C <sup>-1</sup> ) | $c_p$<br>(J kg <sup>-1</sup> °C <sup>-1</sup> ) |

| Cu                  | 19300                           | 385                                          | 385                                             |

| Epoxy               | 700                             | 2.5                                          | 500                                             |