國立臺灣大學電機資訊學院電子工程學研究所

碩士論文

Graduate Institute of Electronics Engineering

College of Electrical Engineering and Computer Science

National Taiwan University

Master Thesis

銻錫合金之電子傳輸特性與能帶結構模擬

Electron Transport and Simulation of Band Structures

of GeSn Alloys

田凱瑩

Kai-Ying Tien

指導教授：李峻霄 教授

Advisor: Professor Jiun-Yun Li

中華民國 111 年 6 月

June, 2022

# 誌謝

首先要感謝李峻賓教授從專題開始總共四年的諄諄教誨，從一開始引領我們閱讀文獻的方式、做投影片的方式、報告的方式、做研究的心態，也讓我在對未來迷惘的時候可以暫時停下腳步好好地思考，以及成全我的人生選擇。謝謝陳敏璋教授、廖洺漢教授和李敏鴻教授在口試時的鼓勵與犀利提問，讓我了解自己在基礎知識上的不足以及可以更深入討論的部分。

謝謝 QEL 的夥伴們：幫忙長晶和時常協助我的研究的家佑學長、教我電晶體製程的莊嚴學長、教我做模擬的柏元學長、和我一起架設 4K 系統還有幫我多次代工的宗穎、在剛進實驗室初期和我相互扶持的承育、和我教學相長的彥洋、時常揪我吃飯一起大聊音樂動漫和心路歷程的燿均學長、分享許多 QEL 生存法則的韋志學長、引領我進入 QEL 的俞叡學長、盡心盡力辛苦的無塵室助教子茗學長、祥順學長和志力，以及嘉澤學長、志穎學長、奕潔、驛凌、士傑、蘇遙、宸峽、睿濬、瑋哲一起在實驗室奮鬥、聊八卦、講幹話，祝福各位都能早日畢業！

還要感謝交響打擊們：通通、家蓉、冠宏、裴新、昌彥、柏儒，團練時的 UNO、彩排後台的各種桌遊和團練後的宵夜時間是我研究所生涯中少數可以開懷大笑的時光，跟你們在一起就會覺得延畢的我不孤單（笑），祝福還沒畢業的人都早日畢業，脫離「還沒」地獄！

謝謝材料小圈圈：姜寧、Coco、佳韋、鈺宸、吉瑞、老大、昱晴，不管是一起修日文課、追動漫當個阿宅，或是翹班去攀岩、抱怨實驗的點滴，都是我研究生活中很重要的調劑。

謝謝靖雅當我的垃圾桶，聽我抱怨實驗上的不順心，在我半夜崩潰大哭的時候陪我聊天。最後要謝謝我的父母，雖然一天到晚說我是米蟲、問我怎麼還沒畢業，但還是刀子嘴豆腐心地把我當公主養，讓我無後顧之憂地完成學位。

## 摘要

近年來，鍺錫材料越來越受到關注，這是由於鍺錫合金在錫濃度高於 6~11% 時有機會轉變為直接能隙材料，除了能應用於高效能的光電元件，鍺錫同時擁有高電子與電洞遷移率，且可與現今的積體電路技術相容，因此極具潛力成為下一代場效電晶體(MOSFET)的通道(channel)材料。為了有效利用直接能隙鍺錫的優點，已有許多文獻探討其光電特性，然而對於其電特性的相關研究較少，因此，本論文將利用變溫霍爾量測與數值賈勢法計算深入研究鍺錫的能隙與電特性。

我們以減壓化學氣相沉積法製備含有錫比例為 8%、12% 的壓縮應變、鬆弛、拉伸應變之內摻雜鍺錫磊晶，並將磊晶製作成霍爾棒元件進行變溫霍爾量測，探討錫比例與應變對於鍺錫的電子遷移率之影響。在 8% 鍺錫中，以拉伸應變鍺錫的遷移率最高，壓縮應變鍺錫的遷移率最低；在鬆弛鍺錫中，以高錫比例的 12% 鍺錫之遷移率較高，推測原因為施加拉伸應變或提高錫比例有助於讓鍺錫由間接能隙轉變為直接能隙，使具有較小等效質量的  $\Gamma$  電子的比例增加。

為了驗證實驗結果，在論文的第二部分使用 Sentaurus TCAD 套件以數值賈勢法模擬鍺錫能帶結構，並計算 L 谷與  $\Gamma$  谷的等效電子質量與電子於兩谷中的分布比例，以研究錫比例與應變對電子分布情形的影響。在錫比例 0% 至 20% 的無應變鍺錫中，L 點的等效質量約為  $\Gamma$  點的 15~40 倍。不同應變條件中，拉伸應變鍺錫之  $\Gamma$  電子最多，而不同錫比例的鍺錫中，12% 鍺錫的  $\Gamma$  電子較多，因此預期其電子遷移率較高，此結果與實驗數據吻合。

**關鍵字：**鍺錫合金、直接能隙、間接能隙、電子遷移率、數值賈勢法

# Abstract

Germanium-tin (GeSn) alloys have attracted much attention recently because of its direct-bandgap characteristics for high-performance optoelectronic devices. Furthermore, GeSn is very promising for the next-generation channel material MOSFET applications due to its high electron and hole mobilities and compatibility with Si VLSI technology. Despite the potential of direct-bandgap GeSn, there are few experimental results about electrical transport reported while much optical data is available. Therefore, the band structures and electrical properties of GeSn were investigated in this thesis.

In this thesis, electron transport properties in epitaxial GeSn films under different strain conditions such as compressive-strain, strain-relaxation, and tensile-strain are investigated. The epitaxial films are epitaxially grown by reduced pressure chemical vapor deposition and the Sn fractions are 8 and 12 %. Hall bar devices are fabricated and characterized at 4 ~ 300 K. Among all strain conditions, the electron mobility of tensile-strained GeSn is the highest. For strain-relaxed GeSn, the electron mobility is higher as the Sn fraction increases. Both could be attributed to a higher electron population in the  $\Gamma$  valley, where electrons have a lower effective mass and high mobility. Applying tensile stress on GeSn films or increasing the Sn fraction reduces the energy difference between the  $\Gamma$  valley and the L valley. As a result, more electrons populate in the  $\Gamma$  valley, leading to a higher mobility due to the smaller effective mass.

To characterize the electron transport properties in n-GeSn, we perform TCAD simulation of GeSn band structures. Effective masses and electron populations at  $\Gamma$  and L valleys are calculated. With Sn fractions of 0 ~ 20 %, the effective mass at the L valley is 15 ~ 40 times larger than that at the  $\Gamma$  valley. Among all strain conditions, tensile-strained GeSn shows the highest electron populations in the  $\Gamma$  valley. Moreover, for strain-relaxed GeSn, the electron population in the  $\Gamma$  valley increases as the Sn fraction increases. Both simulation results support the experimental data.

**Keywords:** germanium-tin (GeSn), direct bandgap, indirect bandgap, electron mobility, empirical pseudopotential method (EPM)

# 目錄

|                                |           |

|--------------------------------|-----------|

| 口試委員會審定書 .....                 | #         |

| 誌謝 .....                       | i         |

| 摘要 .....                       | ii        |

| Abstract.....                  | iii       |

| 目錄 .....                       | v         |

| 圖目錄 .....                      | vii       |

| 表目錄 .....                      | x         |

| <b>第 1 章 引言.....</b>           | <b>1</b>  |

| 1.1 研究動機——鍺錫半導體 .....          | 1         |

| 1.2 文獻回顧 .....                 | 3         |

| 1.2.1 鍺錫之直接能隙與間接能隙 .....       | 3         |

| 1.2.2 鍳錫之電子遷移率 .....           | 6         |

| 1.3 論文架構 .....                 | 9         |

| <b>第 2 章 內摻雜鍺錫之電子傳輸特性.....</b> | <b>10</b> |

| 2.1 簡介 .....                   | 10        |

| 2.2 實驗方法與量測 .....              | 12        |

| 2.2.1 鍳錫薄膜磊晶結構與分析 .....        | 12        |

| 2.2.2 霍爾量測原理簡介 .....           | 16        |

| 2.3 霍爾棒元件製作及電性量測 .....         | 18        |

| 2.4 結論 .....                   | 26        |

| <b>第 3 章 鍳錫之能帶結構模擬.....</b>    | <b>27</b> |

| 3.1 數值贊勢法原理與參數選定 .....         | 27        |

| 3.1.1 NL-EPM 理論簡介 .....        | 28        |

| 3.1.2 NL-EPM 之參數選定 .....       | 31        |

| 3.2 鍳錫能帶結構模擬 .....             | 33        |

|              |                     |           |

|--------------|---------------------|-----------|

| 3.3          | 結論 .....            | 41        |

| <b>第 4 章</b> | <b>結論及未來工作.....</b> | <b>42</b> |

| 4.1          | 結論 .....            | 42        |

| 4.2          | 未來工作 .....          | 43        |

|              | 參考文獻 .....          | 44        |

|              | 相關發表 .....          | 48        |

# 圖目錄

|                                                                                                                                                                   |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 圖 1.1 摩爾定律演進圖[1]。 .....                                                                                                                                           | 1  |

| 圖 1.2 2020 年發表之國際元件與系統發展藍圖，指出鎵將可能取代矽成為未來邏輯元件的通道材料[2]。 .....                                                                                                       | 2  |

| 圖 1.3 常見半導體的載子遷移率，實心點為電子遷移率，空心點為電洞遷移率[3]。 .....                                                                                                                   | 2  |

| 圖 1.4 (a)直接能隙與間接能隙對錫濃度的關係圖[12]，(b)直接( $\Gamma$ valley)與間接能隙(L valley)對錫濃度的關係圖[13]，(c)間接(EgL)與直接能隙(Eg $\Gamma$ )大小隨錫比例之變化[6]。 .....                                | 3  |

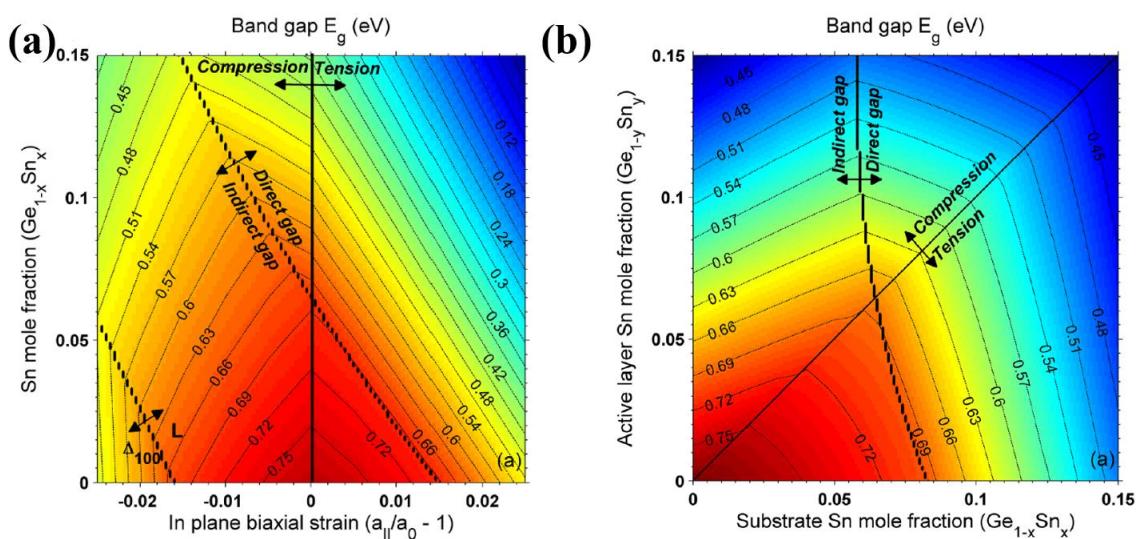

| 圖 1.5 (a)各種錫比例與應變條件下之鎵錫能隙大小，並標示其間接-直接能隙轉變的邊界，(b)鎵錫主動層(Ge <sub>1-y</sub> Sn <sub>y</sub> )中鎵錫能隙大小，隨其本身錫比例與鎵錫緩衝層(Ge <sub>1-x</sub> Sn <sub>x</sub> )比例的變化[5]。 ..... | 4  |

| 圖 1.6 (a)錫比例 4% 與 (b)錫比例 9% 之鎵錫薄膜之變溫光致發光頻譜[15]。 .....                                                                                                             | 5  |

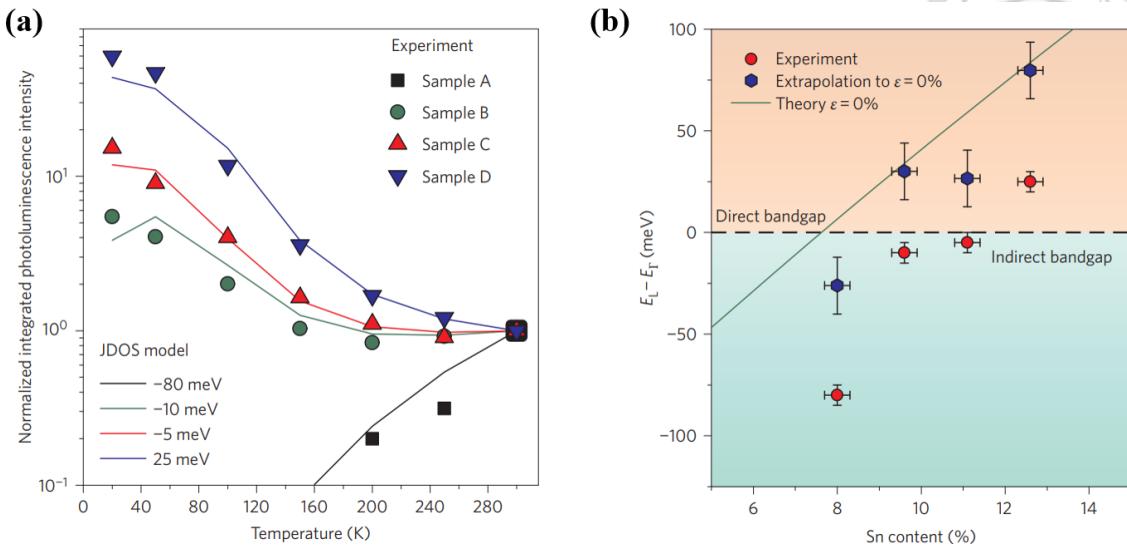

| 圖 1.7 (a)模擬與實際量測的發光頻譜的總強度隨溫度的變化，不同曲線為改變 L- $\Gamma$ 谷之間的能量差，(b) L- $\Gamma$ 谷之間的能量差隨錫比例的變化，考慮實際樣品中的應變大小，並推測無應變下的狀況[11]。 .....                                     | 6  |

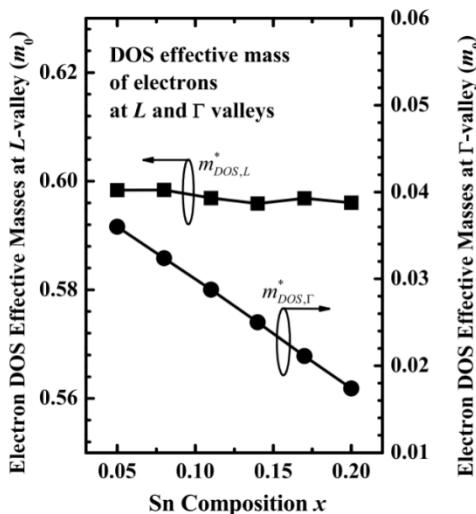

| 圖 1.8 鎵錫電子在 L 谷與 $\Gamma$ 谷的等效質量隨錫比例之變化，且 $\Gamma$ 谷的等效質量遠小於 L 谷[16]。 .....                                                                                       | 7  |

| 圖 1.9 (a)室溫下鬆弛 GeSn 的 $\Gamma$ 電子數量與電子遷移率，(b)不同應變條件下的 GeSn 電子遷移率[8]。 .....                                                                                        | 8  |

| 圖 1.10 (a)錫比例為 4 % 之拉伸應變、鬆弛與壓縮應變鎵錫 nMOSFET 之等效遷移率[17]，(b)錫比例為 6 % 與 8.5 % 之鎵錫 nMOSFET 之等效遷移率[18]。 ....                                                            | 8  |

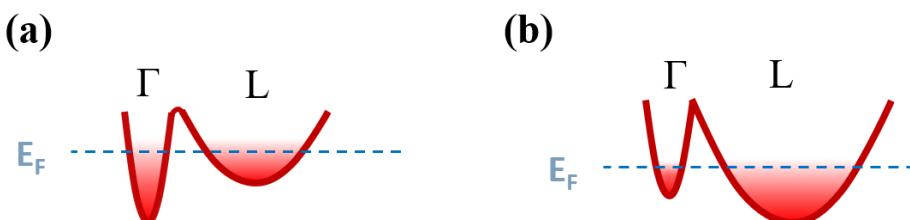

| 圖 2.1 (a)直接能隙鎵錫與(b)間接能隙中電子分布示意圖。 .....                                                                                                                            | 10 |

| 圖 2.2 以增加錫比例或施加拉伸應變之方式使鎵錫由間接能隙轉變為直接能隙[4]。 .....                                                                                                                   | 11 |

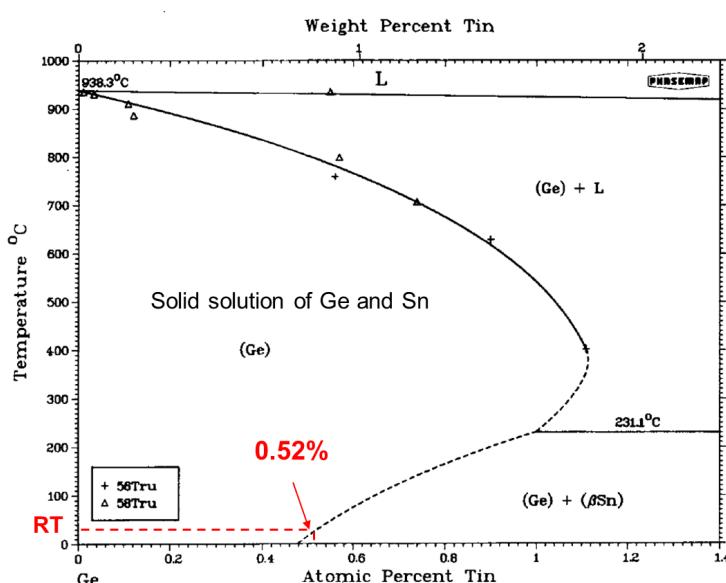

| 圖 2.3 鎵錫合金相圖[21]。 .....                                                                                                                                           | 12 |

|                                                                                                                                                                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

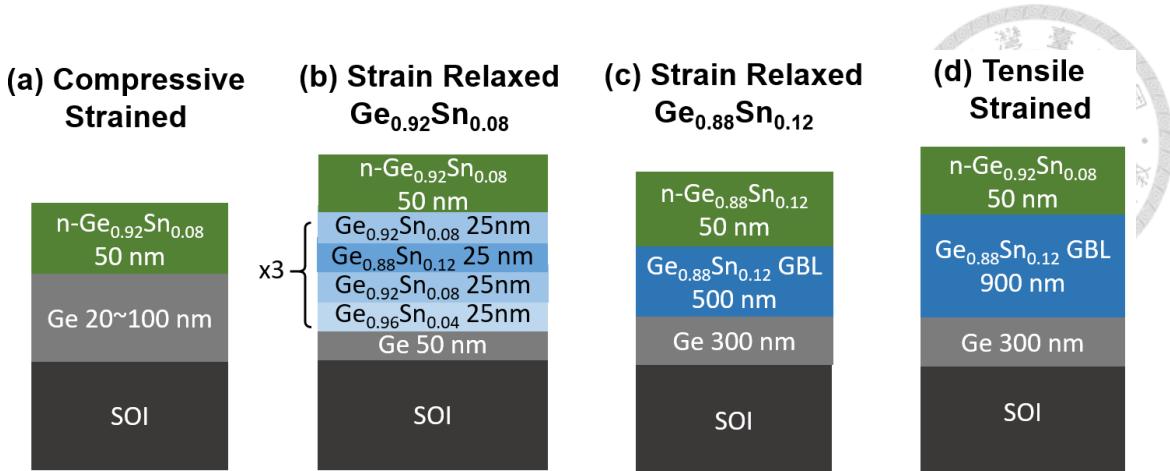

| 圖 2.4 (a)壓縮應變、(b)應變鬆弛 $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 、(c)應變鬆弛 $\text{Ge}_{0.88}\text{Sn}_{0.12}$ 與(d)拉伸應變內摻雜鍺錫磊晶結構示意圖。 .....                                                                                                              | 13 |

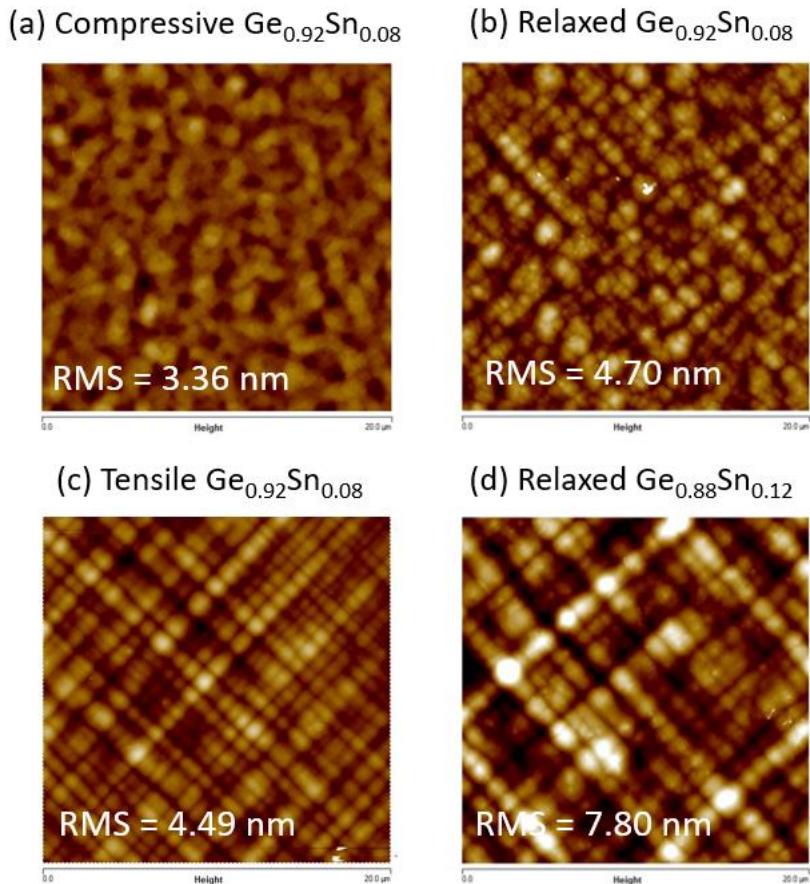

| 圖 2.5 (a)壓縮應變、(b)鬆弛、(c)拉伸應變 $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 與(d)鬆弛 $\text{Ge}_{0.88}\text{Sn}_{0.12}$ 之合金表面之 AFM 影像。 .....                                                                                                                 | 14 |

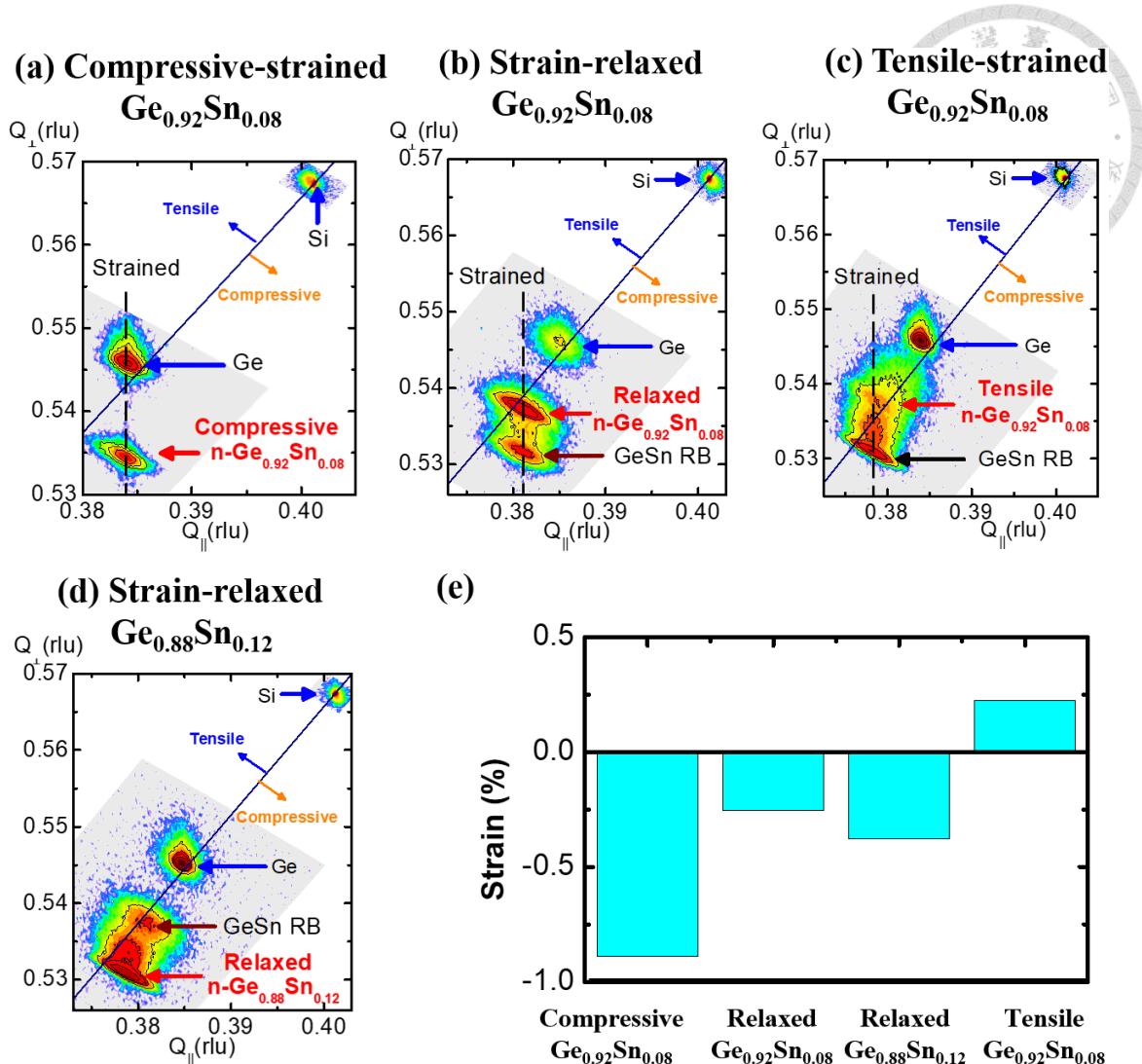

| 圖 2.6 (a)壓縮應變、(b)鬆弛、(c)拉伸應變 $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 與(d)鬆弛 $\text{Ge}_{0.88}\text{Sn}_{0.12}$ 之(224)晶格面之 RSM 分析結果，(e)由 RSM 結果計算之雙軸向應變量。 .....                                                                                      | 15 |

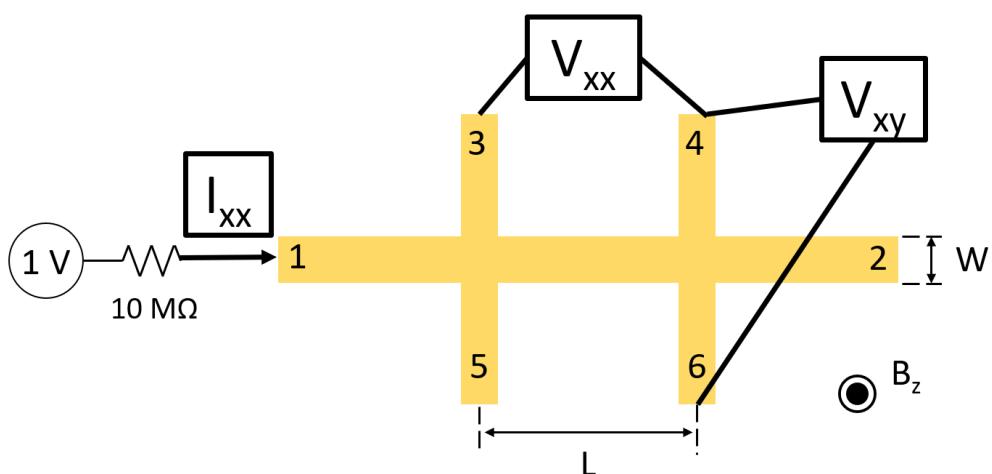

| 圖 2.7 霍爾量測設置示意圖。 .....                                                                                                                                                                                                                        | 16 |

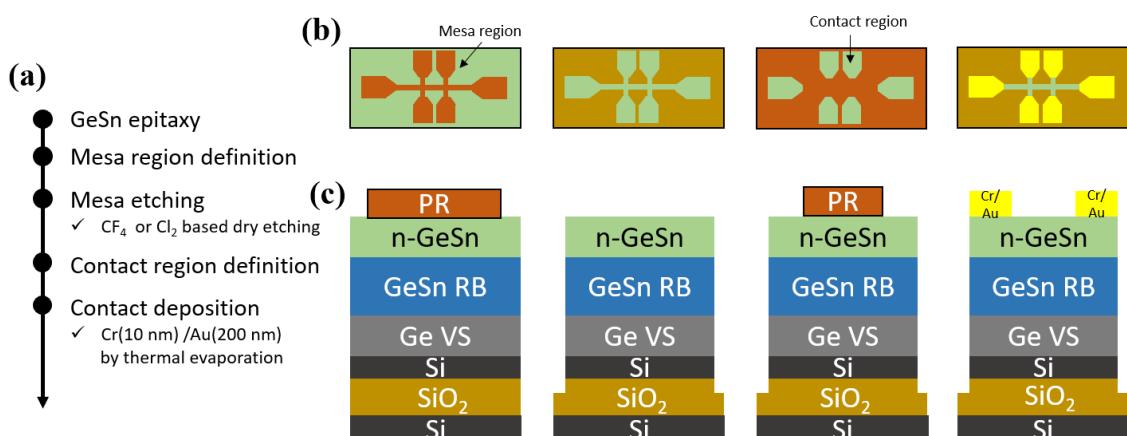

| 圖 2.8 霍爾棒元件製程之(a)流程解說、(b)俯視圖與(c)側視圖。 .....                                                                                                                                                                                                    | 18 |

| 圖 2.9 雙層傳導示意圖。圖中白色箭頭為內摻雜鍺錫中電子流通路徑，黑色箭頭為鍺錫與鍺緩衝層中電洞流通路徑。 .....                                                                                                                                                                                  | 19 |

| 圖 2.10 (a)拉伸應變 $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 之原始霍爾濃度(空心)與經過雙層傳導校正後之霍爾濃度(實心)(b)拉伸應變 $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 之原始霍爾遷移率(空心)與經過雙層傳導校正後之霍爾遷移率(實心)。 .....                                                                            | 20 |

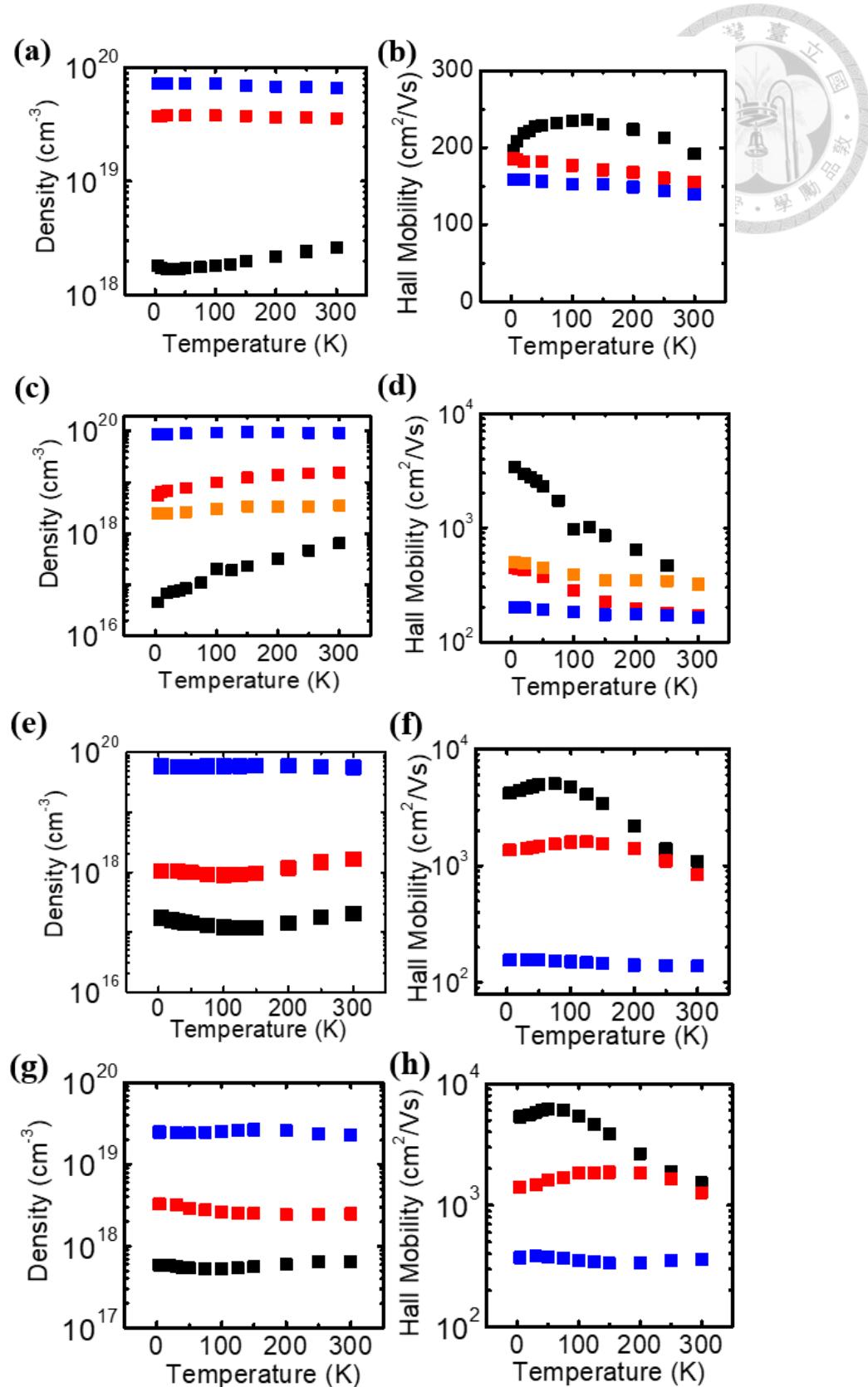

| 圖 2.11 (a)壓縮應變、(c)鬆弛、(e)拉伸應變 $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 與(g) 鬆弛 $\text{Ge}_{0.88}\text{Sn}_{0.12}$ 之電子濃度與溫度關係圖，(b)壓縮應變、(d)鬆弛、(f)拉伸應變 $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 與(h)鬆弛 $\text{Ge}_{0.88}\text{Sn}_{0.12}$ 之電子遷移率與溫度關係圖。 ..... | 21 |

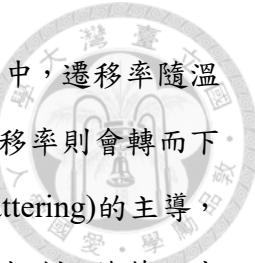

| 圖 2.12 (a)拉伸應變、鬆弛與壓縮應變 $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 之電子遷移率比較圖，摻雜濃度皆為 $2 \times 10^{18} \text{ cm}^{-3}$ ，(b)間接能隙與直接能隙鍺錫在室溫與低溫的電子分布情形示意圖。 .....                                                                                          | 23 |

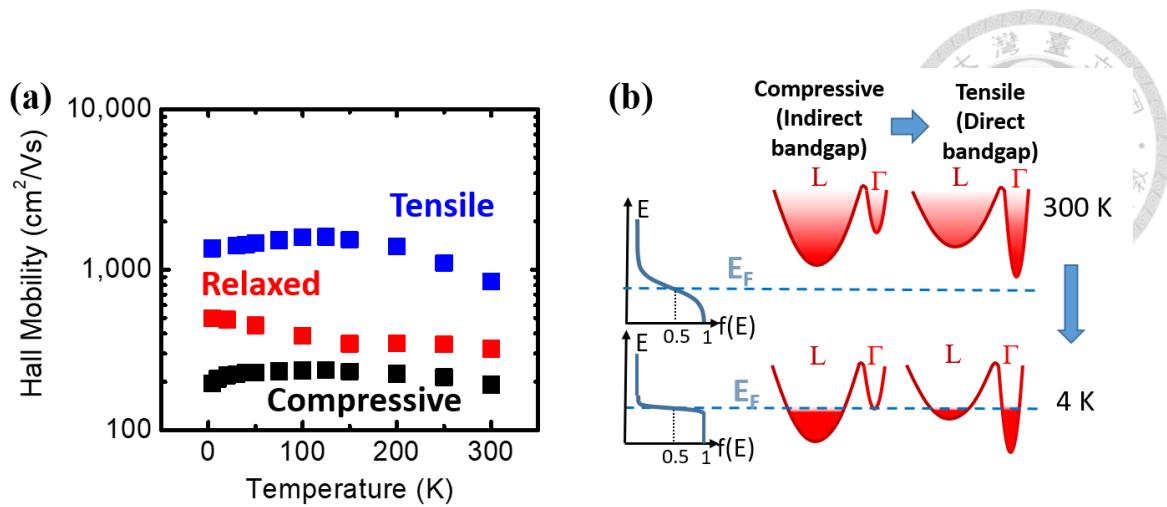

| 圖 2.13 (a)錫比例 8 %與錫比例 12 %之鬆弛鍺錫之電子遷移率比較圖，(b)間接能隙與直接能隙鍺錫在室溫與低溫的電子分布情形示意圖。 .....                                                                                                                                                                | 24 |

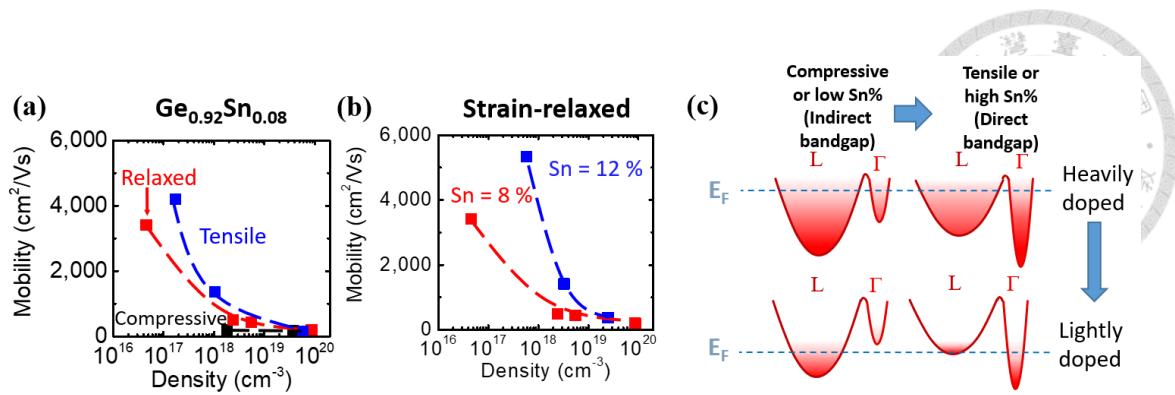

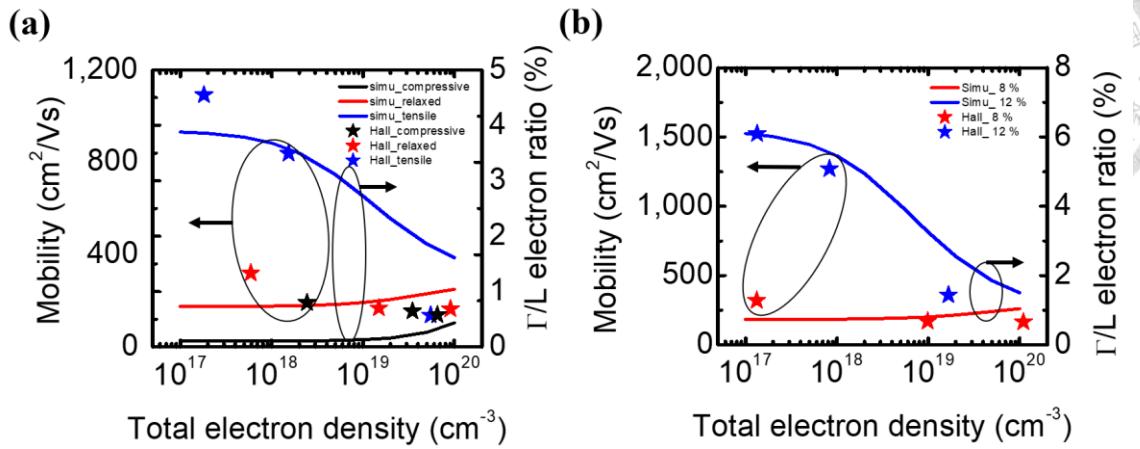

| 圖 2.14 (a)不同應變條件之 $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 在 4 K 下的電子遷移率隨電子濃度之變化，(b)不同錫比例之鬆弛鍺錫在 4 K 下的電子遷移率隨電子濃度之變化，(c)間接能隙與直接能隙鍺錫在重摻雜與輕摻雜條件下的電子分布情形示意圖。 .....                                                                                      | 25 |

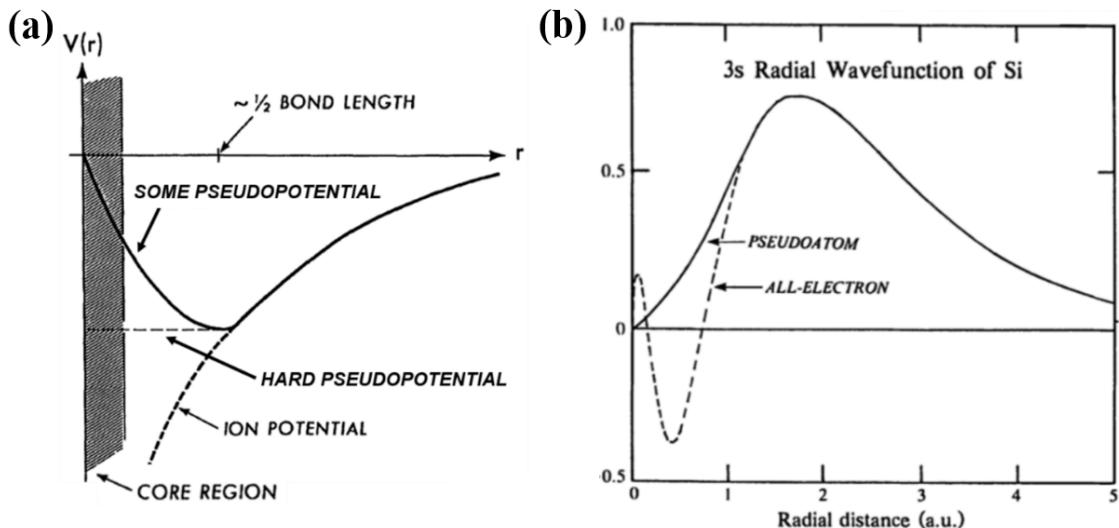

| 圖 3.1 (a)單一原子之離子位能(短虛線)及贊勢(長虛線和實線)在空間中之變化示意圖[25]，(b)矽之價電子波函數(all-electron)和贊勢波函數(pseudoatom)在空間                                                                                                                                               |    |

|                                                                                                                                                                                                                                                      |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 之變化示意圖[25]。                                                                                                                                                                                                                                          | 28 |

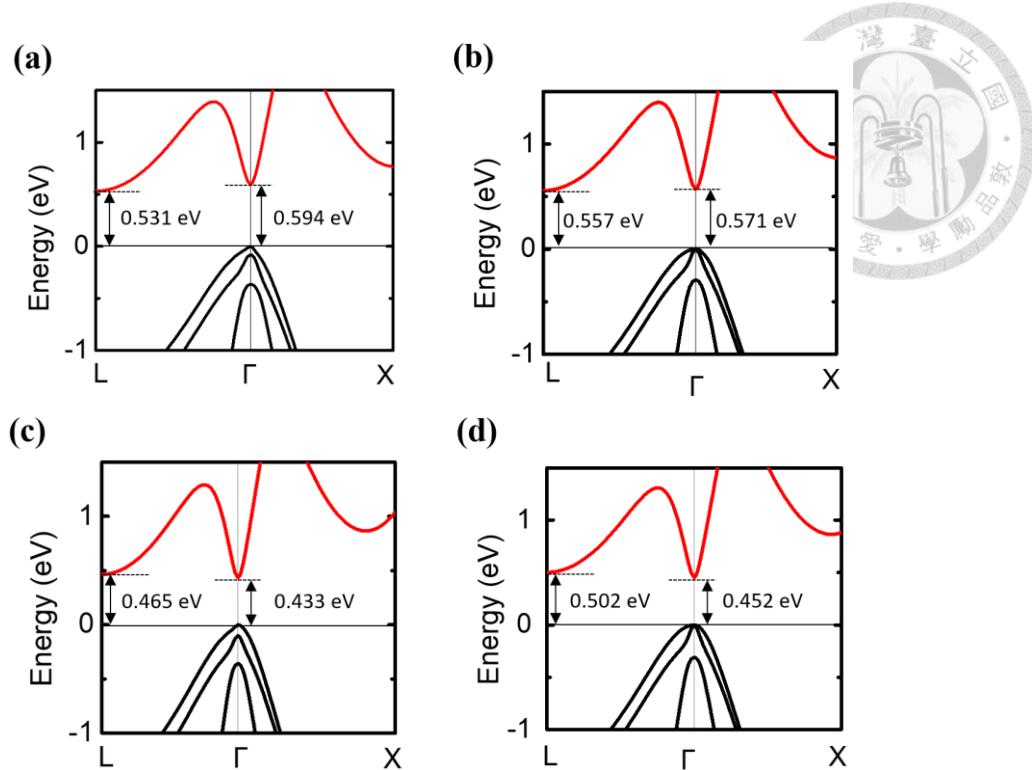

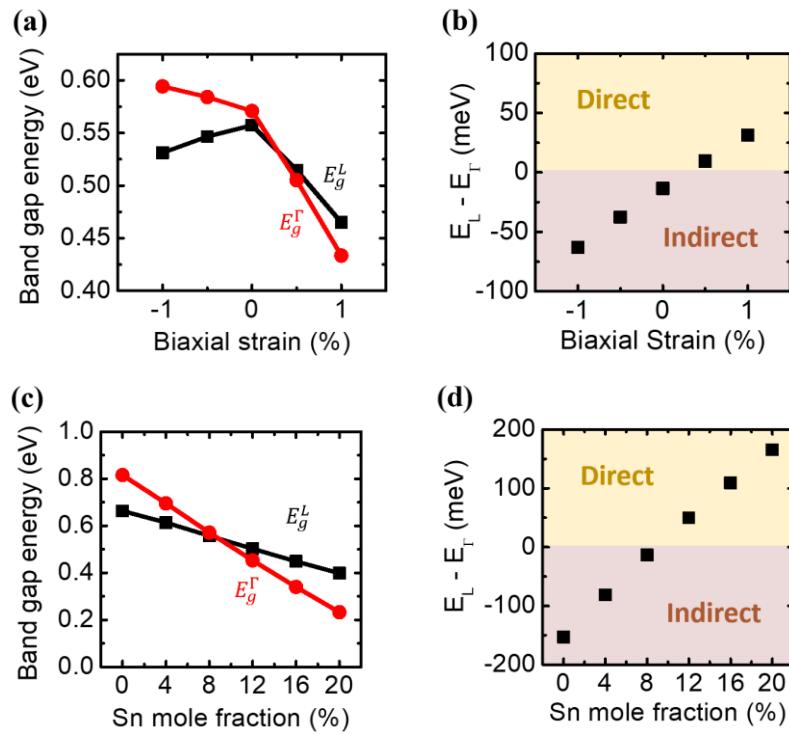

| 圖 3.2 (a)壓縮應變( $\varepsilon = -1\%$ )、(b)鬆弛( $\varepsilon = 0$ )、(c)拉伸應變( $\varepsilon = +1\%$ ) $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 與<br>(d)鬆弛( $\varepsilon = 0$ ) $\text{Ge}_{0.88}\text{Sn}_{0.12}$ 之能帶結構模擬結果。                                    | 34 |

| 圖 3.3 (a) $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 之直接與間接能隙隨雙軸向應變的變化，(b)鬆弛鍺錫之直接<br>與間接能隙隨錫比例的變化，(c) $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 之間接與直接能隙差值隨雙軸<br>向應變的變化，(d) 鬆弛鍺錫之間接與直接能隙差值隨錫比例的變化。 ...                                                              | 34 |

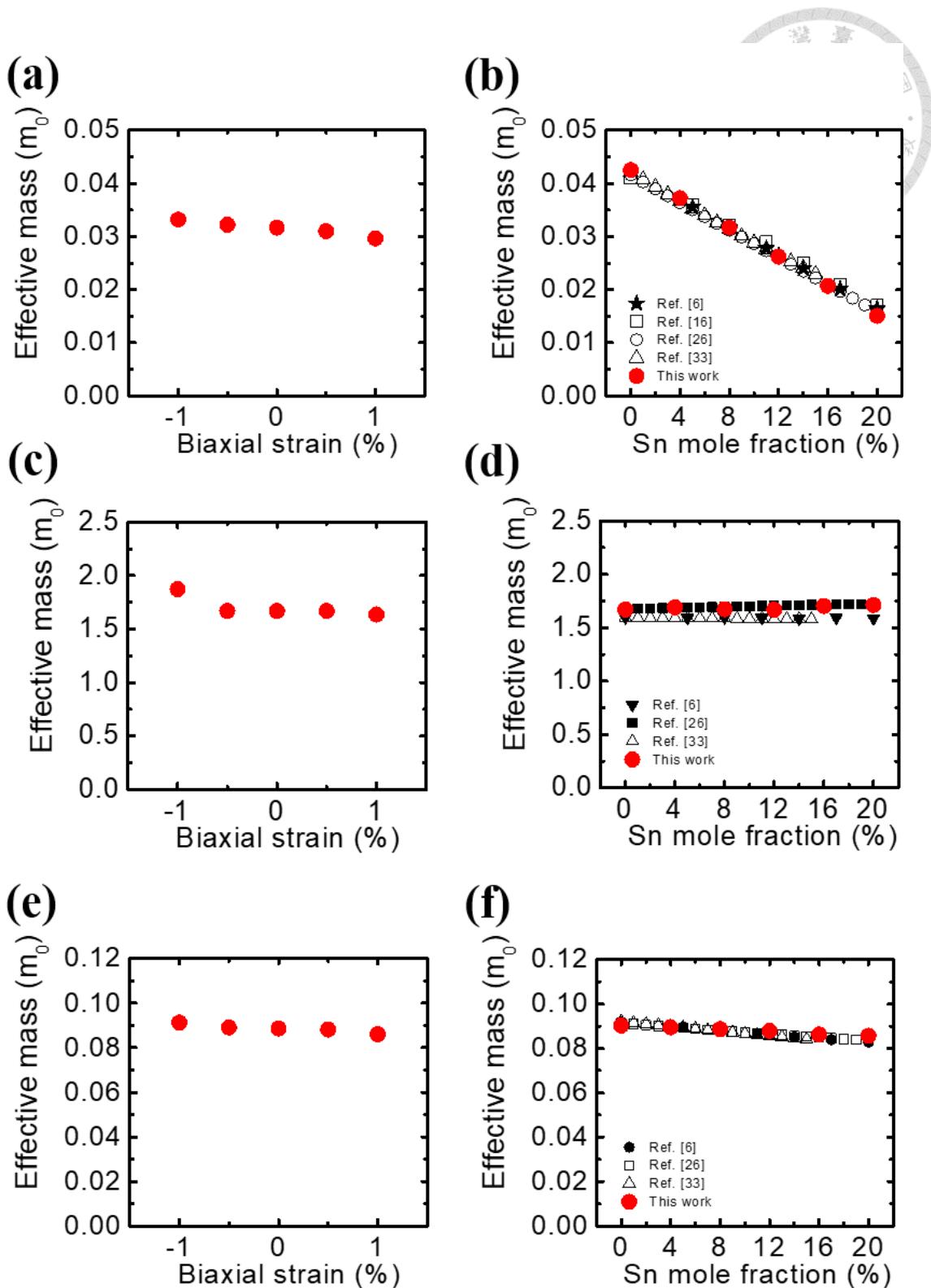

| 圖 3.4 不同應變條件下， $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 之(a) $\Gamma$ 電子、(c) L 電子之縱向和(e) L 電子之<br>橫向等效質量模擬結果。不同錫比例之無應變鬆弛鍺錫之(b) $\Gamma$ 電子、(d) L<br>電子之縱向和(f) L 電子之橫向等效質量模擬結果。 ....                                                                        | 36 |

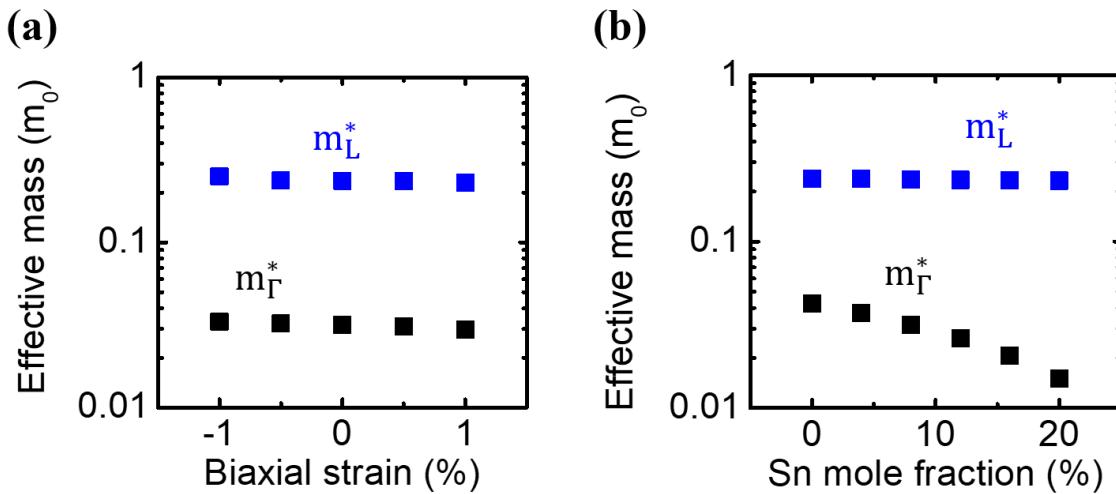

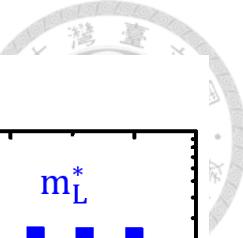

| 圖 3.5 (a)不同應變條件下， $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 之 $\Gamma$ 電子與 L 電子之能態密度等效質量比<br>較圖。(b)不同錫比例之無應變鬆弛鍺錫之 $\Gamma$ 電子與 L 電子之能態密度等效<br>質量比較圖。 ....                                                                                                   | 37 |

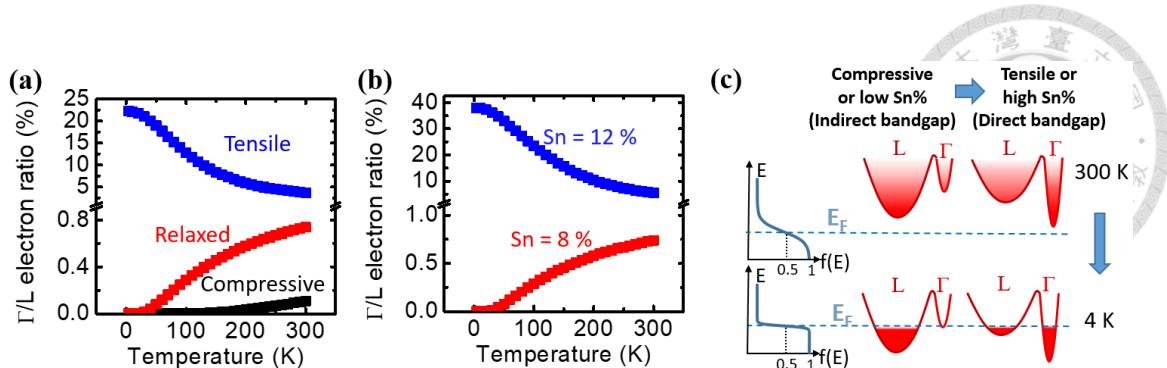

| 圖 3.6 (a)壓縮應變( $\varepsilon = -1\%$ )、無應變( $\varepsilon = 0$ )與拉伸應變( $\varepsilon = +1\%$ ) $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 中 $\Gamma$ 電<br>子與 L 電子比例隨溫度之變化，(b)不同錫比例的無應變鍺錫中 $\Gamma$ 電子與 L<br>電子比例隨溫度之變化，(c)間接能隙與直接能隙鍺錫在室溫與低溫的電子<br>分布情形示意圖。 .... | 38 |

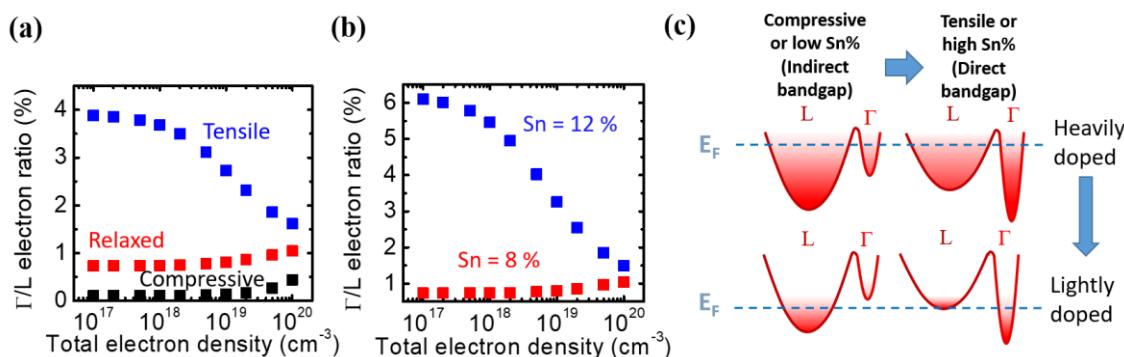

| 圖 3.7 (a)室溫下不同應變條件下的 $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 中 $\Gamma$ 電子與 L 電子比例隨總電子密<br>度之變化，(b)室溫下不同錫比例的鬆弛鍺錫中 $\Gamma$ 電子與 L 電子比例隨總電<br>子密度之變化，(c)間接能隙與直接能隙鍺錫在重摻雜與輕摻雜條件下的電<br>子分布情形示意圖。 ....                                                          | 39 |

| 圖 3.8 (a)室溫下不同應變條件下的 $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 與(b)室溫下不同錫比例的鬆弛鍺錫<br>之 $\Gamma/L$ 電子比例(實線)與電子遷移率(星號)隨電子濃度之變化。 ....                                                                                                                           | 40 |

## 表目錄

|                                                     |    |

|-----------------------------------------------------|----|

| 表 3.1 EPM 模擬所使用鉻與 $\alpha$ -錫之局域與非局域賡勢參數[14]。 ..... | 32 |

| 表 3.2 EPM 模擬所使用鉻與 $\alpha$ -錫之其他參數[4][14]。 .....    | 32 |

# 第1章 引言

## 1.1 研究動機——鎵錫半導體

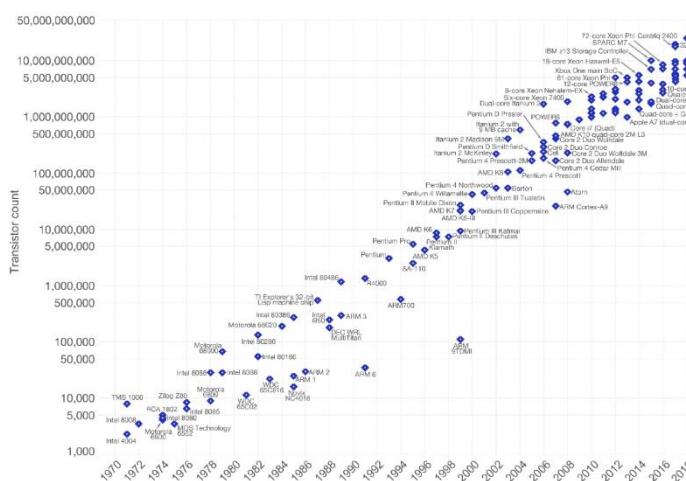

自 1960 年代以來，積體電路的發展大致按照摩爾定律(Moore's law)的預測演進(圖 1.1)，積體電路上可容納的電晶體數目，約每隔兩年增加一倍，晶片效能的提高促進了電子資訊產業的蓬勃發展。然而當電晶體的尺寸微縮至 10 nm 以下時，量子穿隧效應使得電晶體的漏電流問題加劇，功耗提升阻止了電晶體進一步的微縮。為了持續提升電晶體的效能而開發出許多新技術，例如鰭式電晶體(FinFET)和環閘極(gate-all-around, GAA)等立體結構的電晶體，利用包覆性更高的閘極結構抑制漏電流。除了改變電晶體結構，國際半導體技術發展藍圖也預測未來的通道材料，將會換成比矽具有更高載子遷移率的材料如鎵(圖 1.2)。

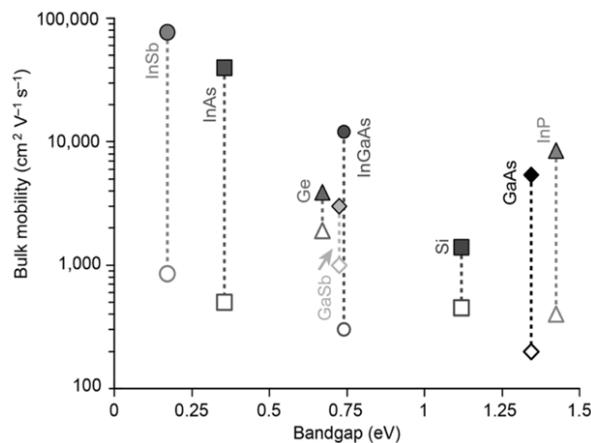

四族鎵除了擁有高載子遷移率外，相比於三五族材料更具有兩項優勢：其一，同時擁有較矽高的電子與電洞遷移率，因此適合應用在互補式金氧半(complementary metal-oxide-semiconductor, CMOS)電晶體的製程上，三五族雖擁有高電子遷移率，其電洞遷移率只與矽相近(圖 1.3)；其二，由於鎵之物理化學特性與矽相似，鎵電晶體所需的製程與現今的矽基製程相容性高，能大幅減少更改製程的時間與金錢成本，且在氧化層介面、源/汲極電阻等特性比三五族半導體表現更佳。

圖 1.1 摩爾定律演進圖[1]。

| YEAR OF PRODUCTION                                          | 2020                      | 2022                               | 2025                               | 2028                                                     | 2031                                                 | 2034                                 |

|-------------------------------------------------------------|---------------------------|------------------------------------|------------------------------------|----------------------------------------------------------|------------------------------------------------------|--------------------------------------|

| <i>Logic industry "Node Range" Labeling (nm)</i>            | G48M36                    | G45M24                             | G42M20                             | G40M16                                                   | G38M16T2                                             | G38M16T4                             |

| <i>IDM-Foundry node labeling</i>                            | "5"                       | "3"                                | "2.1"                              | "1.5"                                                    | "1.0 eq"                                             | "0.7 eq"                             |

| <i>Logic device structure options</i>                       | i7-f5                     | i5-f3                              | i3-f2.1                            | i2.1-f1.5                                                | i1.5e-f1.0e                                          | i1.0e-f0.7e                          |

| <i>Mainstream device for logic</i>                          | FinFET                    | finFET                             | LGAA                               | LGAA                                                     | LGAA-3D                                              | LGAA-3D                              |

| <b>LOGIC TECHNOLOGY ANCHORS</b>                             |                           |                                    |                                    |                                                          |                                                      |                                      |

| <i>Patterning technology inflection for Mx interconnect</i> | 193i, EUV DP              | 193i, EUV DP                       | 193i, EUV DP                       | 193i, High-NA EUV                                        | 193i, High-NA EUV                                    | 193i, High-NA EUV                    |

| <i>Beyond-CMOS as complimentary to mainstream CMOS</i>      | -                         | -                                  | -                                  | 2D Device, FeFET                                         | 2D Device, FeFFT                                     | 2D Device, FeFFT                     |

| <b>Channel material technology inflection</b>               | SiGe25%                   | SiGe50%                            | SiGe50%                            | Ge, 2D Mat                                               | Ge, 2D Mat                                           | Ge, 2D Mat                           |

| <i>Process technology inflection</i>                        | Conformal Doping, Contact | Channel, RMG                       | Lateral/Atomic Etch                | Non-Cu Mx                                                | 3D VLSI                                              | 3D VLSI                              |

| <i>Stacking generation inflection</i>                       | 2D                        | 3D-stacking: W2W, D2W Mem-on-Logic | 3D-stacking: W2W, D2W Mem-on-Logic | 3D-stacking, Fine-pitch stacking, P-over-N, Mem-on-Logic | 3D-stacking, 3D VLSI: Mem-on-Logic with Interconnect | 3D-stacking, 3D VLSI: Logic-on-Logic |

圖 1.2 2020 年發表之國際元件與系統發展藍圖，指出鍺將可能取代矽成為未來邏輯元件的通道材料[2]。

圖 1.3 常見半導體的載子遷移率，實心點為電子遷移率，空心點為電洞遷移率[3]。

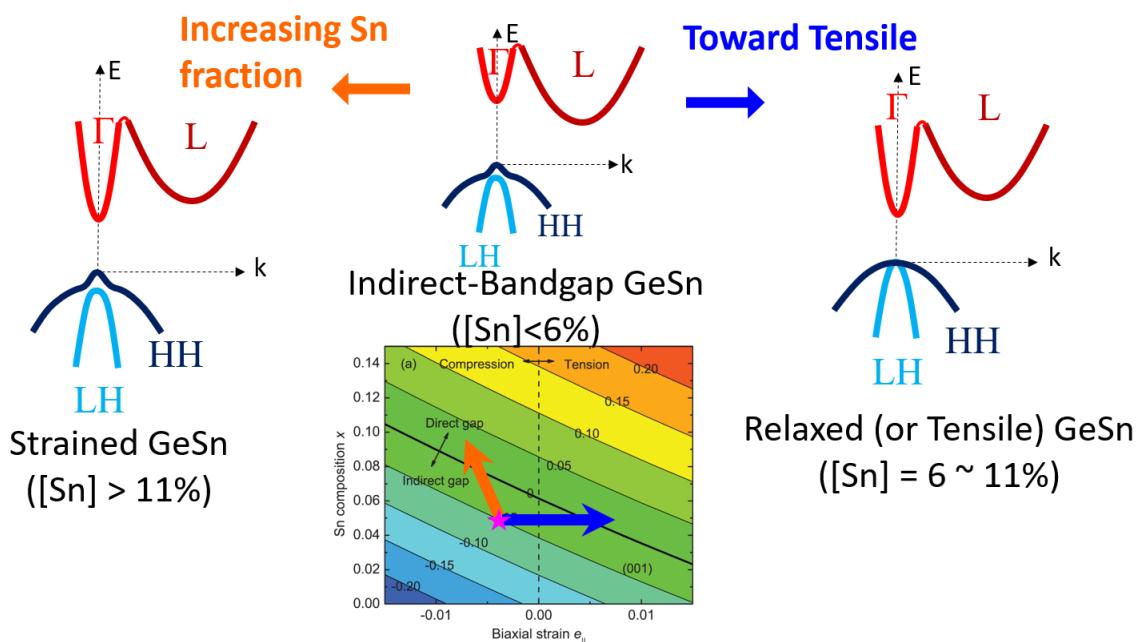

如同矽半導體，鍺半導體為間接能隙材料，因此不像具有直接能隙的三五族材料適合製作光電元件，然而鍺的直接能隙只比間接能隙大約 140 meV，可以透過施加拉伸應變[4][5]或加入錫[4][5][6]使其成為直接能隙材料，有利於光子的吸收與釋放，大大拓展在光電領域上的應用；此外，鍺錫合金可與現有的矽半導體製程整合。除了可應用於光電元件的優點之外，鍺錫合金在電性上的表現更勝於純鍺，由於鍺錫的晶格常數較純鍺大，與鍺形成異質結構時會產生壓縮應變，使電洞的等效質量下降，進而增加鍺錫的電洞遷移率[7]；另一方面，當鍺錫合金變成直接能隙材料時，其電子等效質量可大幅降低，使鍺錫具有極高的電子遷移率，經計算在錫比例等於 12.5 %時，其電子遷移率可達  $70,000 \text{ cm}^2/\text{Vs}$ [8]。

直接能隙鎵錫的應用廣泛，不僅在光學上能夠製作發光二極體[9]、光偵測器[10]、光激發雷射[11]等，在電學上也很有潛力成為電晶體中的下一代通道材料。然而，鎵錫材料之間接-直接能隙轉變條件目前皆以光學特性作為判斷標準，例如：光致發光頻譜，利用雷射光激發半導體材料產生額外的電子與電洞，使其於能隙邊緣複合發光，發出與能隙之能量大小相當的光子，藉此量測半導體的能隙大小。目前對於直接能隙鎵錫的電特性仍未完全掌握，因此，本論文將從實驗與理論兩方面深入研究鎵錫的能隙與電特性。

## 1.2 文獻回顧

### 1.2.1 鎵錫之直接能隙與間接能隙

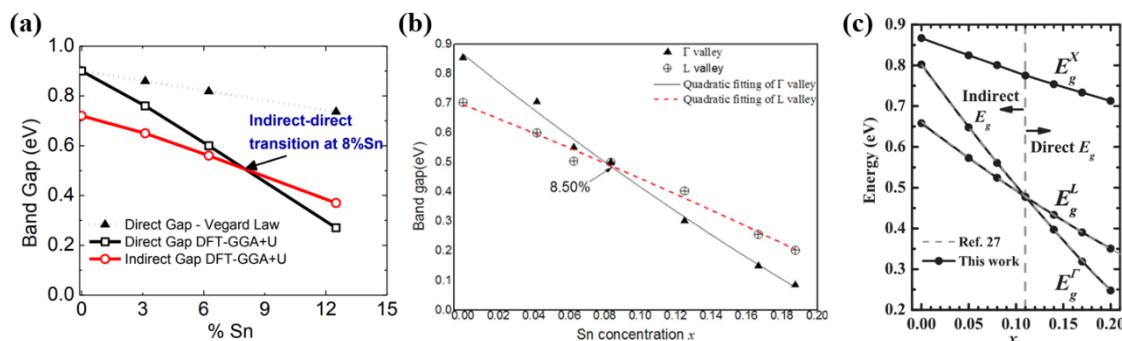

為了研究鎵錫的能隙與載子質量等特性，許多人針對鎵錫的能帶結構進行模擬，其中主要有兩種方法：第一原理計算(first principle calculation)與數值殼勢法(empirical pseudopotential method, EPM)。第一原理的優點為計算過程中不需要實驗數據，因此適合用於研究新材料。文獻[12]使用密度泛函理論模擬不同錫比例的鎵錫之能帶結構，隨著錫比例增加，直接能隙( $\Gamma$  谷)與間接能隙(L 谷)的大小均下降，由於直接能隙的下降幅度較大，在錫比例約 8 %時，直接與間接能隙出現交叉點(圖 1.4 (a))，使鎵錫合金從間接能隙材料轉為直接能隙材料。文獻[13]同樣使用密度泛函理論進行模擬，間接-直接能隙轉換發生在錫濃度為 8.5 % (圖 1.4 (b))。

圖 1.4 (a)直接能隙與間接能隙對錫濃度的關係圖[12]，(b)直接( $\Gamma$  valley)與間接能隙(L valley)對錫濃度的關係圖[13]，(c)間接( $E_g^L$ )與直接能隙( $E_g^\Gamma$ )大小隨錫比例之變化[6]。

儘管第一原理可以不依靠實驗數據，然而其計算方式涉及原子層級，在多原子計算時耗費大量時間，為了改善這項問題，許多文獻以數值賡勢法計算鎗錫的能帶結構。文獻[6]利用數值賡勢法模擬不同錫比例下的能帶結構，錫比例為 5 % 時的鎗錫材料之間接能隙較直接能隙小，隨著錫比例增加，直接能隙與間接能隙逐漸變小，且在錫比例超過 11 % 後鎗錫將轉變為直接能隙材料(圖 1.4 (c))。然而根據選用參數的不同，不同研究團隊間算出的轉變點會有些許的差異，如文獻[14]中轉變點為 10 % 錫、文獻[4]中轉變點為 6 % 錫，在無應變、完全鬆弛(fully relaxed)的條件下，鎗錫轉變點大致上的範圍為 6~11 %。

在實際材料中，鎗錫會受基材或結構的影響而受到不同的應力，尤其在磊晶的鎗錫薄膜中，應變條件會受到下方緩衝層與本身厚度的影響，因此不同應變條件對於鎗錫能帶結構的影響也是重要的參數。文獻[5]中模擬各種錫比例與應變條件下的能隙大小(圖 1.5)，並算出各條件下的轉變點，隨著壓縮應變增加( $\epsilon = a_{\parallel}/a_0 - 1 < 0$ )，轉變點之錫比例會增加；反之，若增加拉伸應變( $\epsilon > 0$ )，則鎗錫在較低的錫比例就能轉變為直接能隙。該團隊也計算出在不同錫比例的鎗錫緩衝層上，鎗錫薄膜的應變條件與對應之能隙大小(圖 1.5 (b))，對於相同錫比例的鎗錫主動薄膜層，緩衝層的錫比例越高將產生更多的拉伸應變，使之更容易轉變成直接能隙材料。

圖 1.5 (a)各種錫比例與應變條件下之鎗錫能隙大小，並標示其間接-直接能隙轉變的邊界，(b)鎗錫主動層( $Ge_{1-y}Sn_y$ )中鎗錫能隙大小，隨其本身錫比例與鎗錫緩衝層( $Ge_{1-x}Sn_x$ )比例的變化[5]。

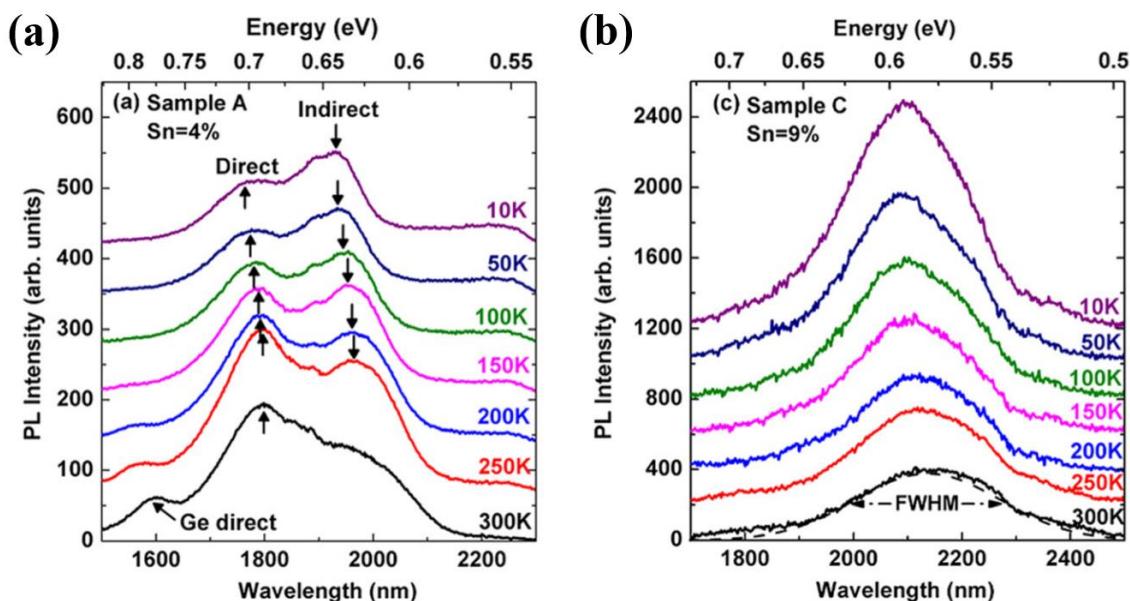

除了能帶結構模擬，實驗上可透過光致發光頻譜瞭解鍺錫的能帶特性。文獻[15]利用變溫光致發光頻譜研究不同錫比例的鍺錫(圖 1.6)，在錫比例為 4 % 的間接能隙鍺錫頻譜中(圖 1.6 (a))，可同時觀察到直接與間接能隙發光，低溫下受激發的電子大多累積於能量較低的間接 L 谷並與電洞複合發光；隨溫度增加，較多電子可分佈在較高能量的直接  $\Gamma$  谷並與電洞複合發光，因直接複合發光的效率遠高於間接複合發光，只需少量電子就能在頻譜中觀察到直接複合發光的訊號，因此可從變溫頻譜中觀察到發光機制轉變的現象。隨著錫比例增加(圖 1.6 (b))，鍺錫逐漸轉變為直接能隙材料，低溫下受激發的電子大多累積於能量較低的  $\Gamma$  谷，而高溫時即使累積在 L 谷中的電子增加，由於直接能隙的放光效率較高，因此不論溫度高低皆以直接  $\Gamma$  谷與電洞複合發光為主，發光機制轉變的現象逐漸消失，頻譜中只會出現一個發光訊號，可以此做為判斷間接-直接能隙轉換的依據。然而頻譜中的半高寬過大，不易判斷位置相近、強度差異大的兩個峰值，為此，文獻[11]利用發光頻譜的總強度隨溫度的變化作為判斷依據(圖 1.7)，對於直接能隙鍺錫， $\Gamma$  電子數量會隨著溫度降低而增加，因此頻譜的強度會增加，而在間接能隙鍺錫中則會有相反的趨勢，由於直接與間接能隙的放光效率不同，無法只憑強度增減判斷其為直接或間接能隙鍺錫，還需搭配擬合計算才能得到較明確的間接-直接能隙轉換條

圖 1.6 (a)錫比例 4% 與 (b)錫比例 9% 之鍺錫薄膜之變溫光致發光頻譜[15]。

圖 1.7 (a)模擬與實際量測的發光頻譜的總強度隨溫度的變化，不同曲線為改變 L- $\Gamma$  谷之間的能量差，(b) L- $\Gamma$  谷之間的能量差隨錫比例的變化，考慮實際樣品中的應變大小，並推測無應變下的狀況[11]。

件，其計算出的轉換點在無應變條件下約為 9%，而實際材料中因受到部份的壓縮應變使轉換點增加至約 12%。

### 1.2.2 鋒錫之電子遷移率

目前已有許多文獻利用模擬預測鋒錫的間接-直接能隙的轉變條件，然而利用光電實驗仍無法準確地確定轉變點，因此我們期望從電性的角度去研究鋒錫的能隙特性。文獻[16]以數值贊勢法模擬不同錫比例下的鋒錫能帶結構，並以拋物線近似計算 L 谷與  $\Gamma$  谷的等效電子質量(圖 1.8)，模擬結果指出電子在  $\Gamma$  谷的等效質量遠小於 L 谷，使得  $\Gamma$  電子擁有較高的遷移率，因此可以推斷當鋒錫轉變為直接能隙的半導體時，其電子會在能量較低的  $\Gamma$  谷傳輸，而使電子遷移率明顯地增加。文獻[8]使用  $k \cdot p$  方法模擬鋒錫的能帶結構與等效載子質量，並計算電子在  $\Gamma$  谷與 L 谷的分布比例，進一步地考慮雜質散射、谷間散射(inter-valley scattering)等散射機制後計算出鋒錫的電子遷移率。隨著錫比例增加， $\Gamma$  谷的能量逐漸低於 L 谷，鋒錫轉變為直接能隙材料，累積在  $\Gamma$  谷的電子比例提高，使得鋒錫的整體平均電子

圖 1.8 鋒錫電子在 L 谷與  $\Gamma$  谷的等效質量隨錫比例之變化，且  $\Gamma$  谷的等效質量遠小於 L 谷[16]。

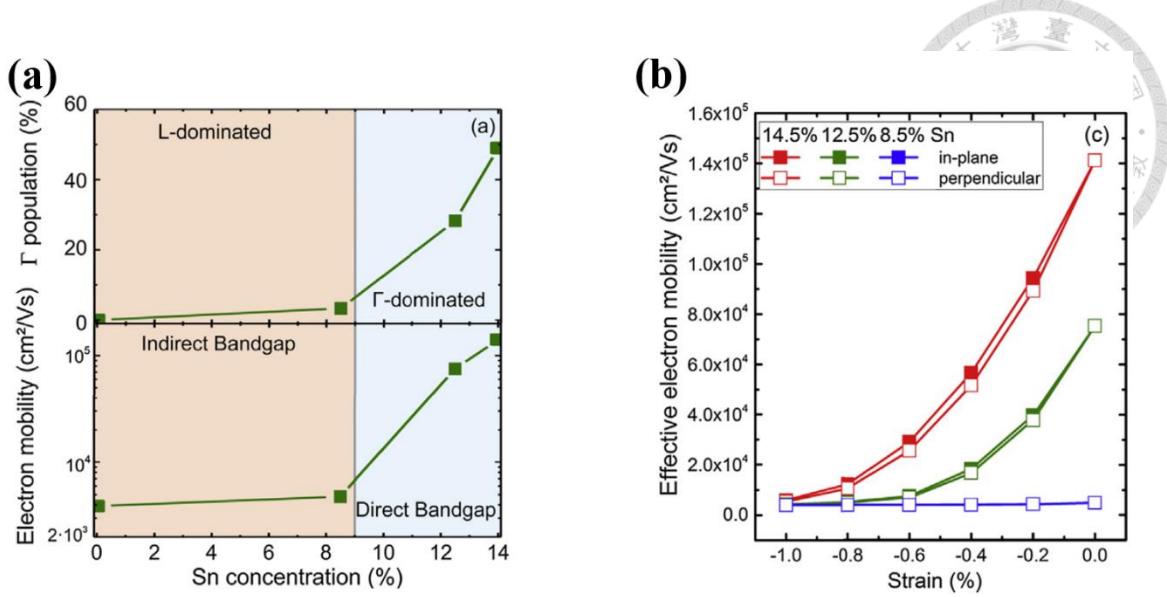

遷移率能夠大幅地提升(圖 1.9 (a))。而對鋒錫施加拉伸應力或減少壓縮應力，使鋒錫在較低錫比例就發生間接-直接能隙的轉變，也會因為前述的原因使平均電子遷移率提升(圖 1.9 (b))。

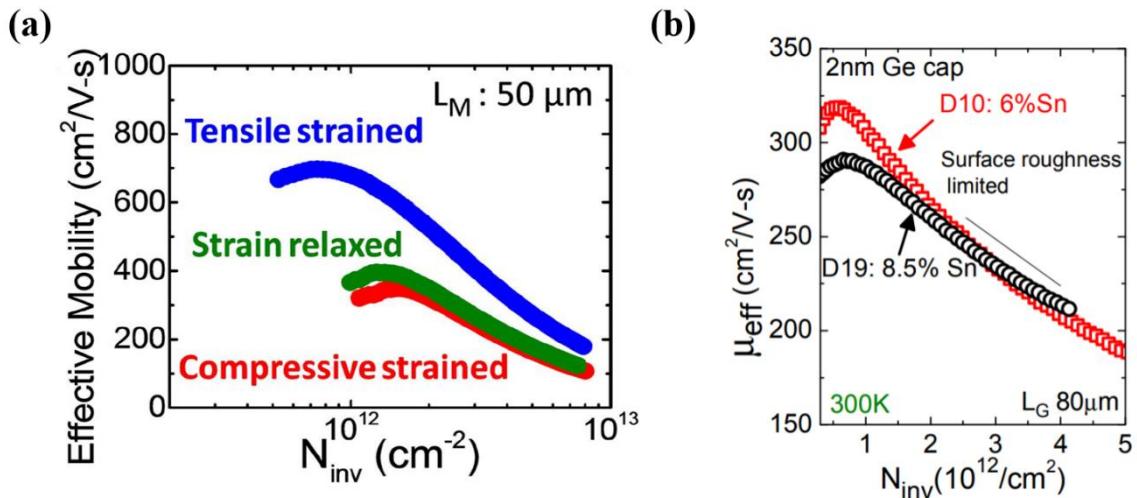

實驗上，關於鋒錫電子遷移率的研究多著重在 n 型電晶體的等效遷移率(effective mobility)。文獻[17]以減壓化學氣相沉積法(reduced pressure chemical vapor deposition)沉積錫比例為 4 %且含有不同應變條件的鋒錫磊晶薄膜並製作 n 型電晶體，利用分離式電容-電壓法(split C-V method)進行室溫量測，萃取電晶體的等效遷移率，研究結果顯示對鋒錫施加拉伸應變能夠大幅提升元件中的電子遷移率(圖 1.10 (a))，與模擬結果相符。然而電晶體的等效遷移率容易受到表面粗糙散射、氧化層界面缺陷密度等因素影響，文獻[18]以錫比例為 6 %與 8.5 %的鋒錫磊晶薄膜製作 n 型電晶體，然而等效遷移率並未如模擬預期的隨錫比例增加而增加(圖 1.10 (b))。因此，本論文將重點放在塊材鋒錫，探討錫比例與應變對於室溫及低溫電子遷移率的影響，以期能對鋒錫合金的材料特性有更全面的了解。

圖 1.9 (a)室溫下鬆弛 GeSn 的  $\Gamma$  電子數量與電子遷移率，(b)不同應變條件下的 GeSn 電子遷移率[8]。

圖 1.10 (a)錫比例為 4 %之拉伸應變、鬆弛與壓縮應變鍺錫 nMOSFET 之等效遷移率[17]，(b)錫比例為 6 %與 8.5 %之鍺錫 nMOSFET 之等效遷移率[18]。

### 1.3 論文架構

第二章將介紹直接能隙與間接能隙鎵錫的特性，並說明能隙與電子遷移率之間的關係，接著介紹鎵錫合金磊晶方法及結構參數，並利用原子力顯微鏡(atomic force microscope, AFM)與倒空間映射(Reciprocal Space Mapping, RSM)等技術對鎵錫薄膜進行材料分析，確認其中的錫比例以及應變狀況。接著介紹霍爾量測的基本原理，並製作元件進行室溫至 4 K 的霍爾量測，萃取出電子濃度與遷移率，研究錫比例與應變對於鎵錫的電子遷移率之影響。

第三章將介紹數值賈勢法的原理，並使用 Sentaurus TCAD 套件以非局域數值賈勢法模擬鎵錫之能帶結構，並計算在直接能隙的  $\Gamma$  點與間接能隙的 L 點之等效電子質量與電子分布情形，進一步探討鎵錫之直接能隙特性與電子遷移率之關係，並與第二章的實驗結果進行比較。最後在第四章總結論文，並提出未來可進行的研究方向。

## 第 2 章 內摻雜鎵錫之電子傳輸特性

### 2.1 簡介

相較於傳統的半導體材料矽，鎵具有更高的電子及電洞遷移率[3]，且同為四族的鎵與傳統矽製程相容性高，因此很有潛力成為互補式金氧半場效電晶體中的下一代通道材料。鎵半導體擁有間接能隙的特性，其導帶的能量最低點位於 L 點，然而直接能隙的  $\Gamma$  點只比 L 點高約 140 meV，可以透過加入錫或拉伸應變使鎵轉變為直接能隙材料[4]，此一特性的轉變會使鎵錫半導體中的電子分布情形產生變化，如圖 2.1 所示，在直接能隙的鎵或鎵錫中，導帶的最低點位於  $\Gamma$  點，因此電子分布於  $\Gamma$  谷中較 L 谷多；反之，在間接能隙的鎵錫材料中，導帶的最低點位於 L 點，因此分布於 L 谷中的電子較  $\Gamma$  谷多。

在 L 谷與  $\Gamma$  谷中，電子具有不同的等效質量，由於在室溫下電子可同時分布於兩谷中，鎵錫的電子傳導必須考慮雙層傳導效應。假設  $\Gamma$  電子的濃度為  $n_\Gamma$  且遷移率為  $\mu_\Gamma$ ，L 電子的濃度為  $n_L$  且遷移率為  $\mu_L$ ，此時整體的電子濃度與遷移率可以下列加權平均式表示[19]：

$$n = \frac{(n_\Gamma \mu_\Gamma + n_L \mu_L)^2}{n_\Gamma \mu_\Gamma^2 + n_L \mu_L^2} \quad (\text{式 2.1})$$

$$\mu = \frac{n_\Gamma \mu_\Gamma^2 + n_L \mu_L^2}{n_\Gamma \mu_\Gamma + n_L \mu_L} \quad (\text{式 2.2})$$

由於  $\Gamma$  電子的等效質量遠小於 L 電子，使得  $\Gamma$  電子擁有較高的遷移率[8]，因此在  $\Gamma$  電子比例較高的直接能隙鎵錫中，等效電子遷移率將會大幅地提升。

圖 2.1 (a)直接能隙鎵錫與(b)間接能隙中電子分布示意圖。

根據文獻[4]的模擬結果(圖 2.2)，有兩種方式可得到直接能隙鎗錫材料。一為透過在鎗中摻雜錫，隨著錫的比例增加， $\Gamma$  點與 L 點的能量差減少，並在錫比例超過 6~11 %後轉變為直接能隙[4][6][14]，然而在增加錫比例的同時，晶格中的壓縮應變量也會增加，使得鎗錫趨向間接能隙[5]。而另一種方式為施加拉伸應變，拉伸應變同樣能減少  $\Gamma$  點與 L 點的能量差，因此可以使鎗錫在較低的錫比例就轉變為直接能隙材料。本研究將分別針對兩種方式進行實驗與分析。

在本章中，我們先介紹含有不同錫比例與應變條件的鎗錫合金磊晶特性及結構參數，並針對磊晶成長後的鎗錫薄膜進行材料分析，如原子力顯微鏡 atomic force microscope, AFM)來確認薄膜表面的品質，並進一步利用倒空間映射(Reciprocal Space Mapping, RSM)圖形確認鎗錫薄膜中的錫比例以及應變狀況。接著介紹霍爾量測的基本原理，並製作元件進行室溫至 4 K 的霍爾量測，萃取出電子濃度與遷移率，以研究錫比例與應變對於鎗錫的電子遷移率之影響。

圖 2.2 以增加錫比例或施加拉伸應變之方式使鎗錫由間接能隙轉變為直接能隙[4]。

## 2.2 實驗方法與量測

### 2.2.1 鋒錫薄膜磊晶結構與分析

我們以減壓化學氣相沉積法(reduced pressure chemical vapor deposition, RPCVD)成長鋨與鋨錫磊晶層，並以二鋨烷(digermane, Ge<sub>2</sub>H<sub>6</sub>)與四氯化錫(tin tetrachloride, SnCl<sub>4</sub>)作為前驅物，以及磷化氫(phosphine, PH<sub>3</sub>)作為n型摻雜氣體。由鋨錫合金相圖(圖 2.3)中可以得知，即使是在錫溶解度最高的400 °C，錫的固體溶解度也僅有1.1%，因此在成長高濃度錫的鋨錫合金時，必須於非平衡狀態下成長。此外在較高的磊晶溫度下，鋨錫合金的穩定狀態容易被破壞使錫析出[20]，因此必須在低溫條件下(< 450 °C)才能成長出穩定的高濃度鋨錫合金[20]。

我們使用絕緣層上矽(silicon on insulator, SOI)的8吋晶圓進行薄膜磊晶成長，以避免較厚的矽基板產生雙層導通效應，進而影響量測結果。首先在320 °C成長一層鋨作為緩衝層(buffer layer)，接著成長三種不同應變條件下的內摻雜鋨錫合金，分別為壓縮應變(compressive strained)、應變鬆弛(strain relaxed)和拉伸應變(tensile strained)結構(圖 2.4)。在壓縮應變結構中，50 nm厚且錫比例約8%的內(in situ)摻雜鋨錫合金薄膜直接成長於鋨緩衝層上(圖 2.4(a))。而鬆弛、拉伸應變結構相對於

圖 2.3 鋨錫合金相圖[21]。

圖 2.4 (a)壓縮應變、(b)應變鬆弛  $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 、(c)應變鬆弛  $\text{Ge}_{0.88}\text{Sn}_{0.12}$  與(d)拉伸應變內摻雜鍺錫磊晶結構示意圖。

壓縮應變結構不同之處，在於內摻雜鍺錫與鍺緩衝層之間多了一層無摻雜鍺錫作為應變鬆弛緩衝層。鍺錫緩衝層分為兩種，一種為漸變緩衝層(graded buffer layer, GBL)，隨著厚度增加逐漸增加錫的濃度至最終所需的比例；另一種為超晶格結構(superlattice)，以最終所需錫比例為 8 %的鬆弛鍺錫緩衝層而言，我們採用 4 %、8 %、12 %、8 %為一個週期，總共成長三個週期，在 8 %內摻雜鬆弛鍺錫結構中即是採用此方式成長緩衝層(圖 2.4 (b))，而在 8 %拉伸應變與 12 %鬆弛內摻雜鍺錫結構中(圖 2.4 (c)(d))，由於所需要的緩衝層之錫比例為 12 %，且我們目前的磊晶技術尚無法穩定成長出超晶格中所需要的錫比例為 16 %的鍺錫層，因此採取漸變緩衝層的方式成長。在內摻雜鍺錫磊晶層中，雜質摻雜濃度為  $1 \times 10^{16} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 。

完成鍺錫薄膜磊晶後，我們利用原子力顯微鏡 atomic force microscope, AFM)進行磊晶薄膜表面分析(圖 2.5)，表面平均粗糙度(rms)約為 3 ~ 7 nm，其中在鬆弛鍺錫中可以觀察到由於應變鬆弛而產生的交叉線(cross-hatch)紋路(圖 2.5 (b)(d))。完成材料表面分析後，我們進一步針對鍺錫合金的成分比例與應變特性進行分析，我們進行(224)晶格面之倒空間映射(reciprocal space mapping, RSM)分析，並以應變值  $\varepsilon$  做為應變程度之度量，定義如下：

$$\varepsilon = \frac{a_{\parallel} - a_0}{a_0} \quad (\text{式 2.3})$$

圖 2.5 (a)壓縮應變、(b)鬆弛、(c)拉伸應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  與(d)鬆弛  $\text{Ge}_{0.88}\text{Sn}_{0.12}$  之合金表面之 AFM 影像。

其中  $a_0$  為材料無應變下之晶格常數， $a_{\parallel}$ 為垂直於長晶方向之晶格常數。RSM 分析結果如圖 2.6 所示，在壓縮應變結構中有矽、鍺緩衝層、內摻雜鍺錫三個訊號峰值，且鍺錫與鍺緩衝層位於同一垂直線上(即兩者的  $Q_{\parallel}$  座標相同)，代表兩層薄膜在平面上之晶格常數相同，顯示鍺錫薄膜完全應變於鍺薄膜上。在 8 % 鬆弛鍺錫中，由於緩衝層是採用超晶格結構，可以看到圖上多了 12 % 鍺錫緩衝層的訊號，又內摻雜鍺錫與鍺錫緩衝層位於同一垂直線上，且與矽訊號位於同一條深藍色斜線上，代表內摻雜鍺錫完全應變於鍺錫緩衝層上且應變條件接近完全鬆弛。在拉伸應變結構中，可以看到鍺比例漸變至約 15 % 的鍺錫緩衝層訊號，且內摻雜鍺錫之訊號落於深藍色完全鬆弛斜線以上，顯示其應變條件為拉伸應變。在 12 % 鬆弛鍺錫中，同樣出現鍺錫漸變緩衝層的訊號，且內摻雜鍺錫接近完全鬆弛。以線性內插之方式

圖 2.6(a)壓縮應變、(b)鬆弛、(c)拉伸應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  與(d)鬆弛  $\text{Ge}_{0.88}\text{Sn}_{0.12}$  之(224)晶格面之 RSM 分析結果，(e)由 RSM 結果計算之雙軸向應變量。

由鍺和錫之參數計算鍺錫之晶格常數和卜松比(Poisson ratio)，再由圖中鍺錫訊號峰之座標位置，可得壓縮應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 、應變鬆弛  $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 、應變鬆弛  $\text{Ge}_{0.88}\text{Sn}_{0.12}$  與拉伸應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  內摻雜鍺錫層之錫比例分別為 8.2 %、8.2 %、14.8 %與 9.7 %，且應變值分別為 -0.89 %、-0.25 %、-0.37 %與 +0.25 %。

## 2.2.2 霍爾量測原理簡介

我們使用霍爾量測(Hall measurement)方法測定在銻錫薄膜中的載子濃度與遷移率。此方法是由霍爾(Edwin H. Hall)在 1879 年所發明，目前仍然被廣泛地利用於半導體中摻雜載子種類與濃度的量測。霍爾量測的原理可參考圖 2.7 的示意圖，將電流從待測物體的腳位 1 導入至腳位 2，並施加垂直於樣品平面的磁場  $\vec{B} = B_z$ ，根據帶電粒子在電磁場中受到的勞侖茲力：

$$\vec{F} = q(\vec{E} + \vec{v} \times \vec{B}) \quad (\text{式 2.4})$$

待測物中的帶電粒子受到作用力而聚集至樣品的兩側形成電場  $\vec{E}$ ，其中  $\vec{F}$  為粒子受到的作用力， $q$  為粒子的帶電量， $\vec{v}$  為粒子的速度。平衡時垂直載子運動方向的電場與磁場對載子產生的作用力之合力為零，因此式 2.4 可以寫成：

$$\vec{F} = 0 = q(E_{xy} + v_{xx} \times B_z) \Rightarrow E_{xy} = -v_{xx} \times B_z \quad (\text{式 2.5})$$

橫向電場  $E_{xy}$  可以從霍爾電壓  $V_H = V_{xy} = E_{xy}w$  得到，其中  $w$  為待測物的寬。而速度  $v_{xx}$  可以電流

$$I_{xx} = qv_{xx}nwt \Rightarrow v_{xx} = \frac{I_{xx}}{qnwt} \quad (\text{式 2.6})$$

表示，其中  $n$  為載子濃度， $t$  為待測物的厚度。把橫向電場  $E_{xy}$  與速度  $v_{xx}$  代換至

圖 2.7 霍爾量測設置示意圖。

式 2.5 可得

$$\frac{V_H}{w} = -\frac{I_{xx}}{qnwt} B_z \quad (\text{式 2.7})$$

移項整理後可以得到

$$nt = -\frac{I_{xx}}{qV_H} B_z = n_{Hall} \quad (\text{式 2.8})$$

其中  $n$  為單位體積內的載子個數，將它乘上待測物的厚度  $t$  可以得到面濃度  $n_{Hall}$ 。而在實際的量測中為了排除因待測物不完美，而導致在沒有外加磁場  $B_z$  的情況下產生霍爾電壓  $V_H$  不為零的壓差，因此在取二維載子濃度時會對式 2.8 取微分得到：

$$n_{Hall} = -\frac{I_{xx}}{q} \frac{1}{dV_H/dB_z} \quad (\text{式 2.9})$$

之後量測霍爾電壓  $V_H$ ，並透過與磁場  $B_z$  的關係就能從式 2.9 得到待測物中的載子種類與濃度。而載子的遷移率可以從平行運動方向的電流電壓關係得到：

$$v_{xx} = \mu E_{xx} \quad (\text{式 2.10})$$

將速度  $v_{xx}$  與電場  $E_{xx}$  用電流  $I_{xx}$  與電壓  $V_{xx}$  代換可以得到：

$$\frac{I_{xx}}{qn_{Hall}w} = \mu \frac{V_{xx}}{L} \quad (\text{式 2.11})$$

其中  $L$  為待測物的長度，移項整理後可以得到：

$$\mu = \frac{I_{xx}}{qn_{Hall}V_{xx}} \frac{L}{w} \quad (\text{式 2.12})$$

由式 2.9 得到載子濃度後就可以利用式 2.12 測量電位  $V_{xx}$  後進一步求得載子遷移率。

## 2.3 霍爾棒元件製作及電性量測

為了進行內摻雜鍺錫之霍爾量測，我們製作霍爾棒元件，元件製作流程可分為兩部分：霍爾棒平台(Hall bar mesa)製作與電極製作(圖 2.8)。首先，我們將磊晶完成的 8 吋晶圓以鑽石刀切出  $1.5 \times 1.0\text{ cm}$  之破片，接著進行有機溶劑清洗：依序以丙酮、異丙醇經超音波震洗 5 min 並以氮氣槍吹乾，接著塗佈 AZ 5214 光阻後進行軟烤( $95^\circ\text{C}$ 、90 s)以穩定光阻，接著以光學微影(photolithography)定義霍爾棒平台形狀，利用 AZ 300 MIF 顯影約 40 秒，最後硬烤光阻( $120^\circ\text{C}$ 、5 min)以保護光阻不會於後續蝕刻製程遭到破壞。使用 RIE(reactive-ion etching)在腔體壓力 4 Pa 及 RF 功率 100 W 下，通入流量分別為 30 sccm 與 10 sccm 之氣體  $\text{CF}_4$  與  $\text{O}_2$  蝕刻樣品至氧化層部分，以達到元件隔離的作用。最後為電極製作：先以前述有機溶劑清洗後，進行預烤再塗佈光阻，軟烤後以光學微影定義出金屬電極區域，接著利用熱蒸鍍法將 10/200 nm 之鉻/金薄膜作為元件的金屬電極，鍍膜完成後將樣品浸泡於丙酮至少 1 hr，以掀離法(lift-off)移除電極定義區外之金屬薄膜。元件製作完成後，我們將元件置於 4 K 低溫系統，利用鎖向(Lock-in)放大技術進行低頻( $10 \sim 15\text{ Hz}$ )霍爾量測，其中使用的電流大小為 100 nA，磁場上限為 0.5 T。

在霍爾棒元件中，除了最上層的摻雜鍺錫層，鍺錫或鍺緩衝層也是可能的導通路徑，雖然緩衝層在磊晶過程中沒有摻雜其他原子，然而鍺或鍺錫中的缺陷可能產生電洞[22]，因此我們必須考慮雙層導通效應(圖 2.9)。假設內摻雜鍺錫層的厚度為

圖 2.8 霍爾棒元件製程之(a)流程解說、(b)俯視圖與(c)側視圖。

圖 2.9 雙層傳導示意圖。圖中白色箭頭為內摻雜鍺錫中電子流通路徑，黑色箭頭為鍺錫與鍺緩衝層中電洞流通路徑。

$d_1$  且導電度為  $\sigma_1$ ，鍺加上鍺錫緩衝層的厚度為  $d_2$  且導電度為  $\sigma_2$ ，則整體的霍爾係數可以表示為：

$$R_H = \frac{d[(R_{H1}\sigma_1^2 d_1 + R_{H2}\sigma_2^2 d_2) + R_{H1}\sigma_1^2 R_{H2}\sigma_2^2 (R_{H1}d_2 + R_{H2}d_1)B^2]}{(\sigma_1 d_1 + \sigma_2 d_2)^2 + \sigma_1^2 \sigma_2^2 (R_{H1}d_2 + R_{H2}d_1)^2 B^2} \quad (\text{式 2.13})$$

假設外加磁場很小，式 2.13 可以改寫為：

$$R_H = \frac{d(R_{H1}\sigma_1^2 d_1 + R_{H2}\sigma_2^2 d_2)}{(\sigma_1 d_1 + \sigma_2 d_2)^2} = R_{H1} \frac{d_1}{d} \left( \frac{\sigma_1}{\sigma} \right)^2 + R_{H2} \frac{d_2}{d} \left( \frac{\sigma_2}{\sigma} \right)^2 \quad (\text{式 2.14})$$

其中  $d = d_1 + d_2$ ，導電度  $\sigma = d_1\sigma_1/d + d_2\sigma_2/d$ ， $R_{H1}$  與  $R_{H2}$  分別為內摻雜鍺錫層與緩衝層的霍爾係數，內摻雜鍺錫層中主要載子為電子，而緩衝層的主要載子為電洞，因此可以表示為：

$$R_{H1} = -\frac{1}{qn_1} \quad (\text{式 2.15})$$

$$R_{H2} = \frac{1}{qp_2} \quad (\text{式 2.16})$$

其中  $q$  為基本電荷。從式 2.14 可知，緩衝層的厚度越厚，對於量測的結果影響越大，因此對於應變鬆弛和拉伸應變等緩衝層較厚的磊晶結構，必須使用上述的式子去分析，扣除緩衝層的傳導效應，才能得到內摻雜鍺錫層正確的電子濃度與遷移率。

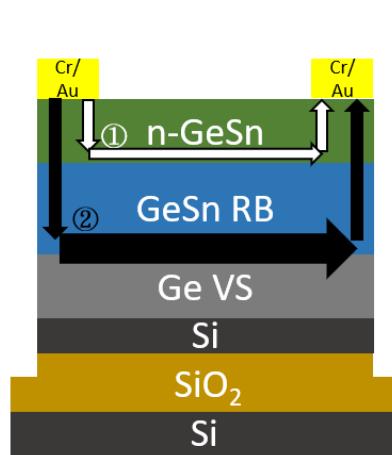

拉伸應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  之電子霍爾濃度與遷移率相對溫度的關係圖(圖 2.10)，黑、紅、藍色的點分別代表低、中、高三種摻雜濃度的樣品，空心為霍爾量測量得之原始值，實心則為考慮雙層傳導並利用式 2.14 校正排除緩衝層傳導後所得之值。

圖 2.10 (a)拉伸應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  之原始霍爾濃度(空心)與經過雙層傳導校正後之霍爾濃度(實心)(b)拉伸應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  之原始霍爾遷移率(空心)與經過雙層傳導校正後之霍爾遷移率(實心)。

在所有樣品中，校正後之電子濃度均較校正前低，而電子遷移率經過校正後相對校正前高，且濃度與遷移率在校正前後的差異在高溫、低摻雜濃度的樣品中最為明顯，主要是由於摻雜濃度低的樣品其摻雜鍺錫層導電度較低，造成在量測時緩衝層的傳導效應較明顯；而隨著溫度降低，緩衝層的載子凍結(freeze-out)，因此樣品中的傳導以內摻雜鍺錫層的電子為主。

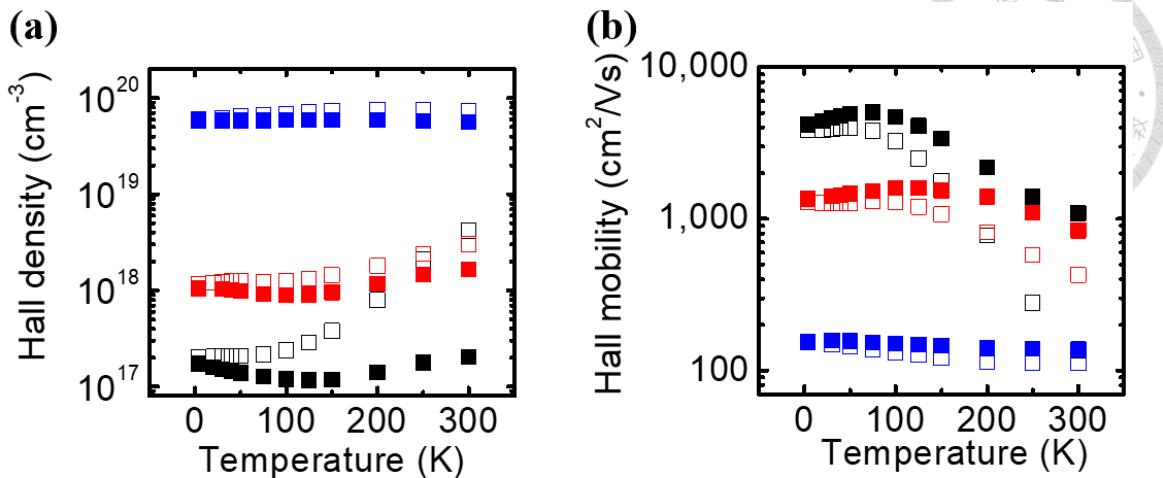

經雙層傳導校正後的電子濃度與遷移率對溫度的關係圖如圖 2.11 所示，其中壓縮應變、拉伸應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  與鬆弛  $\text{Ge}_{0.88}\text{Sn}_{0.12}$  鍺錫各包含三種摻雜濃度的樣品，而鬆弛  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  則有四種摻雜濃度。從圖中可知，電子濃度幾乎不隨溫度而變，只有在最低摻雜濃度的鬆弛  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  中電子濃度隨溫度降低而減少，鍺的電子等效能態密度(effective density of states)約為  $1 \times 10^{19} \text{ cm}^{-3}$ ，隨著錫比例增加，鍺錫的等效電子質量降低，若轉變為直接能隙鍺錫， $\Gamma$  谷的等效質量只有 L 谷的約 0.067 倍，將大幅減少等效能態密度，因此摻雜濃度約在  $10^{17} \sim 10^{18} \text{ cm}^{-3}$  以上的鍺錫即可達到退化態摻雜(degenerate doping)，而在此濃度以下的鍺錫則會出現低溫載子凍結的現象。在所有錫比例與應變條件的鍺錫中，電子遷移率均隨濃度增加而減少，此現象可以歸因於雜質散射(impurity scattering)。而電子遷移率隨溫度的變化依摻雜濃度高低呈現不同的趨勢：在重摻雜鍺錫中，遷移率幾乎不隨溫度變化，

圖 2.11 (a)壓縮應變、(c)鬆弛、(e)拉伸應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  與(g) 鬆弛  $\text{Ge}_{0.88}\text{Sn}_{0.12}$  之電子濃度與溫度關係圖，(b)壓縮應變、(d)鬆弛、(f)拉伸應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  與(h)鬆弛  $\text{Ge}_{0.88}\text{Sn}_{0.12}$  之電子遷移率與溫度關係圖。

主要是因為受到雜質散射的抑制；相對而言，在低摻雜濃度的鎵錫中，遷移率隨溫度上升先微幅增加，溫度上升至約 50~100 K 後，繼續升高溫度遷移率則會轉而下降，在這個過程中遷移率先後受到雜質散射與聲子散射(phonon scattering)的主導，在低溫時，電子受到來自游離雜質的庫倫作用力影響，遷移率受到抑制，隨著溫度升高，電子獲得較多動能克服雜質的庫倫力，遷移率因此上升；隨著溫度持續升高，晶格振動加劇使得聲子散射開始抑制遷移率，因此可以看到遷移率大幅下降。

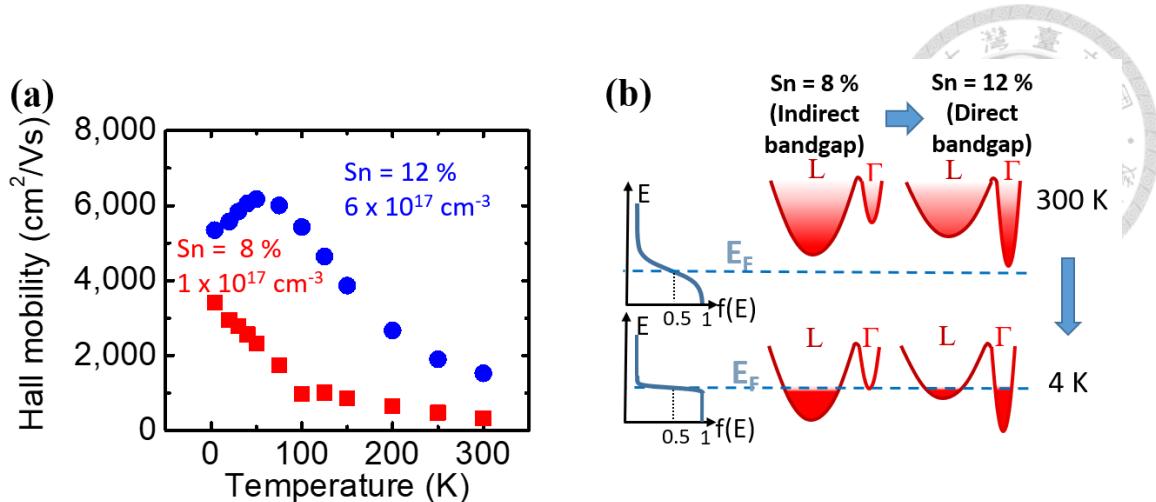

為了探討應變對於鎵錫電子遷移率的影響，我們從錫比例為 8% 的拉伸應變、鬆弛、壓縮應變鎵錫中挑選摻雜濃度接近 ( $\sim 2 \times 10^{18} \text{ cm}^{-3}$ ) 的樣品做比較，以排除雜質散射對遷移率的影響。隨著溫度上升，拉伸與壓縮應變鎵錫先後受到雜質散射減弱和聲子散射增強的影響，電子遷移率呈現先升後降的趨勢(圖 2.12(a))，在大約 100 K 時達到高峰；鬆弛鎵錫的遷移率則是隨著溫度上升而持續下降，有可能是谷間散射抑制了遷移率[8]。低溫下，電子會聚集在能量較低的單一谷中，因此  $\Gamma$ -L 谷之間的谷間散射較弱，高溫時，電子會同時分布在兩能帶中，谷間散射因而增強[8]。鬆弛鎵錫之  $\Gamma$  谷與 L 谷的能量接近，因此谷間散射較強，使得遷移率隨著溫度上升而下降；另一方面，在拉伸和壓縮應變鎵錫中此現象較不明顯，推測是由於  $\Gamma$  谷和 L 谷的能量差距較大（拉伸鎵錫為直接能隙材料，壓縮鎵錫為間接能隙材料），因此可以忽略谷間散射的影響。不同應變條件的 8% 鎵錫中，拉伸應變鎵錫擁有最高的電子遷移率，最大值發生在 125 K 的  $1,600 \text{ cm}^2/\text{Vs}$ ，其次為鬆弛鎵錫，最高遷移率為 4 K 時的  $500 \text{ cm}^2/\text{Vs}$ ，而壓縮應變鎵錫的遷移率最低，在整個溫度範圍中大約維持在  $200 \text{ cm}^2/\text{Vs}$ 。根據文獻的模擬預期[4][5][14]，施加拉伸應變能夠使鎵錫由間接能隙逐漸轉變成直接能隙，反之，施加壓縮應變會使得鎵錫更趨向間接能隙，因此在電子濃度相同的情況下，拉伸應變鎵錫中的  $\Gamma$  電子比例較壓縮應變鎵錫高(圖 2.12(b))，使得電子遷移率提升。值得注意的是，拉伸與壓縮應變鎵錫的電子遷移率之差距在低溫時較室溫時更為顯著，其原因除了低溫下聲子散射減少，我們認為主要是因為拉伸應變鎵錫在低溫時較多電子分佈於  $\Gamma$  谷中。高溫時費米尾端(Fermi tail)延伸至較高的能量，使電子能克服直接與間接能帶的能量差，因此即使  $\Gamma$  谷的能量較低，在 L 谷中也會有電子存在，使得整體遷移率較低；相對而言，低

圖 2.12 (a)拉伸應變、鬆弛與壓縮應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  之電子遷移率比較圖，摻雜濃度皆為  $2 \times 10^{18} \text{ cm}^{-3}$ ，(b)間接能隙與直接能隙鍺錫在室溫與低溫的電子分布情形示意圖。

溫下能克服直接與間接能帶能量差的電子大幅減少，電子大部分聚集在較低的能量帶中，因此直接能隙的拉伸應變鍺錫之  $\Gamma$  電子佔比增加，使得遷移率上升。在下一章將會有詳細的能帶計算證實霍爾實驗的量測結果。

接著針對錫比例對於鍺錫電子遷移率的影響進行分析，我們從錫比例為 8 % 與 12 % 的鬆弛鍺錫挑選摻雜濃度相近的樣品進行比較。從圖 2.13(a)的結果可以得知，12 % 鍺錫的電子遷移率在 4 ~ 300 K 範圍中都較 8 % 鍺錫高，最大值發生在 50 K 的  $6,170 \text{ cm}^2/\text{Vs}$ ，遠大於 8 % 鍺錫在 4 K 時的  $3,410 \text{ cm}^2/\text{Vs}$ 。根據文獻[4][5][6][14]的模擬預期，雖然 8 % 鬆弛鍺錫是否為直接能隙尚無定論，不過普遍認為增加錫比例至超過 11 % 後會轉變為直接能隙，因此在電子濃度相近的情況下，12 % 鍺錫具有較多的  $\Gamma$  電子，使得整體電子遷移率較 8 % 鍺錫高。此外，8 % 與 12 % 鍺錫都呈現隨溫度降低遷移率升高的趨勢，如前段所述，高溫時電子能夠克服 L 谷與  $\Gamma$  谷之間的能量差而分布於兩谷中，低溫時電子則聚集在能量較低的谷中，因此對於直接能隙而言，降溫後低能量的  $\Gamma$  谷中電子增多，整體電子遷移率上升；相反地，對於間接能隙而言，降溫後高能量的  $\Gamma$  谷中電子減少，整體電子遷移率下降。雖然 8 % 與 12 % 鍺錫的遷移率都出現降溫後上升的趨勢，然而與溫度有關影響遷移率的要素還有聲子散射、雜質散射等複雜的機制，因此我們仍無法完全確

圖 2.13 (a)錫比例 8 %與錫比例 12 %之鬆弛鍺錫之電子遷移率比較圖，(b)間接能隙與直接能隙鍺錫在室溫與低溫的電子分布情形示意圖。

定其為直接能隙或間接能隙。不過含有錫比例較高的 12 %鍺錫其雜質濃度較高，原本應產生較強的雜質散射而使遷移率降低，量測結果反而顯示其遷移率較 8 %鍺錫高，因此我們認為這是由於 12 %鍺錫較 8 %鍺錫更為接近直接能隙的緣故。

如前段所述，高溫時電子能克服 L 谷與  $\Gamma$  谷的能量差分布於兩谷中，較不容易區別直接能隙與間接能隙的差異，因此我們選取各樣品在 4 K 時的遷移率對濃度作圖，探討錫比例與應變對於能隙以及遷移率的影響。從圖 2.14(a)可知，在不同應變條件的 8 %鍺錫中，拉伸應變鍺錫在相同電子濃度下的電子遷移率最高，其次為鬆弛鍺錫；圖 2.14(b)則顯示應變鬆弛的鍺錫中，12 %鍺錫呈現較高的電子遷移率，皆與前兩段的討論結果相同：拉伸應變與增加錫比例有助於鍺錫轉變為直接能隙，並且提升電子遷移率。此外，拉伸應變與 12 %鬆弛鍺錫皆呈現遷移率隨濃度下降而顯著上升的趨勢，其原因除了雜質散射的減少之外，我們認為也和  $\Gamma$  電子與 L 電子的分布比例相關(圖 2.14 (c))，電子濃度較低時，電子大多分布於低能量的  $\Gamma$  谷中，隨著電子濃度增加，低能階填滿後電子依序往高能階填，因此 L 谷中也有電子存在， $\Gamma$  電子的比例下降使得遷移率隨之降低。相對來說，間接能隙鍺錫的 L 谷能量較低，隨著電子濃度的增加， $\Gamma$  電子的佔比反而上升，然而在 8 %壓縮應變鍺錫中並沒有觀察到遷移率隨濃度增加而上升的趨勢，我們推測可能的原因有兩個：其一是摻雜濃度的增加連帶使得雜質散射變得更強烈，因而抑制遷移率

圖 2.14 (a)不同應變條件之  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  在 4 K 下的電子遷移率隨電子濃度之變化，

(b)不同錫比例之鬆弛錫在 4 K 下的電子遷移率隨電子濃度之變化，(c)間接能隙

與直接能隙錫在重摻雜與輕摻雜條件下的電子分布情形示意圖。

的提升；其二是由於電子在 L 谷中的等效質量遠大於  $\Gamma$  谷，因此在 L 谷中的能階密度(density of states)也遠大於  $\Gamma$  谷，即使  $\Gamma$  電子的比例增加也是微不足道，對於遷移率的影響微乎其微。

## 2.4 結論

直接能隙鍺錫由於等效電子質量較小的  $\Gamma$  谷之能量較低， $\Gamma$  電子的比例較高，因此其電子遷移率會比間接能隙鍺錫之電子高，而文獻的模擬結果指出施加拉伸應變或提高錫比例能夠獲得直接能隙鍺錫。本章以實驗探討錫比例與應變對於鍺錫的電子遷移率之影響，並製作霍爾棒元件研究變溫下(4~300 K)的鍺錫薄膜導特性。我們以減壓化學氣相沉積法製備含有錫比例為 8 %、12 %的壓縮應變、鬆弛、拉伸應變之內摻雜鍺錫磊晶，並且以 AFM 分析磊晶之表面粗糙度，以及 RSM 分析鍺錫薄膜之錫濃度和應變大小，得到壓縮應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 、應變鬆弛  $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 、應變鬆弛  $\text{Ge}_{0.88}\text{Sn}_{0.12}$  與拉伸應變  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  內摻雜鍺錫層之錫比例分別為 8.2 %、8.2 %、14.8 %與 9.7 %，且應變值分別為 -0.89 %、-0.25 %、-0.37 %與 +0.25 %。

為進行電性分析，我們將磊晶製作成霍爾棒元件，經過雙層傳導校正後之電子濃度幾乎不隨溫度變化，而電子遷移率在重摻雜鍺錫中幾乎不隨溫度變化，主因為受到雜質散射的抑制；而低摻雜鍺錫則受到聲子散射主導，電子遷移率隨溫度降低而先升後降。為探討應變與錫比例對鍺錫的電子遷移率之影響並排除雜質散射的干擾，我們以電子濃度相近的樣品做比較，得知在 8 %鍺錫中以拉伸應變鍺錫的遷移率最高，壓縮應變鍺錫的遷移率最低，而在鬆弛鍺錫中以高錫比例的 12 %鍺錫之遷移率較高，顯示施加拉伸應變或提高錫比例有助於讓鍺錫由間接能隙轉變為直接能隙，其中由於低溫時能克服直接與間接能帶能量差的電子大幅減少，因此遷移率的差距更為明顯。我們也觀察 4 K 下遷移率隨濃度變化的趨勢，發現在較接近直接能隙的拉伸應變或高錫比例鍺錫中，遷移率隨濃度下降明顯地上升，推測原因為雜質散射減弱與  $\Gamma$  電子的比例增加。

## 第3章 鋒錫之能帶結構模擬

為瞭解鋰錫半導體的直接能隙與間接能隙特性，近年來越來越多研究專注於鋰錫材料的能帶結構模擬上，例如：第一原理計算(first principle calculation)、緊束縛方法(tight binding method, TBM)及數值賡勢法(empirical pseudopotential method, EPM)等。第一原理計算在多原子計算時需要耗費大量時間，且經常低估材料的能隙，尤其在鋰錫等能隙較小的材料中更為嚴重[6]；緊束縛法計算出的鋰錫間接-直接能隙轉變發生在錫比例超過 20 %時，與實驗數據不符[23]，而數值賡勢法(empirical pseudopotential method, EPM)可以避免這些問題[4]。在本章節中，我們使用 Sentaurus TCAD 套件[24]，以數值賡勢法模擬塊材鋰錫之能帶結構，並計算在直接能隙的  $\Gamma$  點與間接能隙的 L 點之等效電子質量與電子能量分布情形，進一步探討鋰錫之直接能隙特性與電子遷移率之關係。

### 3.1 數值賡勢法原理與參數選定

數值賡勢法的概念是將電子區分為內層核電子與最外層的價電子，並將原子核與核電子產生的總位能以一等效位能取代，將原本的多電子問題（核電子+價電子）簡化為只需考慮價電子的單電子問題，大幅降低計算的複雜度。此一等效位能是由人為給定，使其計算結果符合以第一原理計算得到的位能或實驗數據，與實際的等效位能不盡相同，因此被稱為賡勢位能。由於此賡勢位能不具唯一性[25]，如何設計此一等效位能以符合實驗數據便成了核心問題。目前已有許多使用 EPM 計算矽、鋰、矽鋰以及鋰錫能帶結構的文獻[4][5][6][26]，其中可分為兩種方法：局域 EPM(local EPM, L-EPM) 以及非局域 EPM (nonlocal EPM, NL-EPM)。相較於 L-EPM, NL-EPM 額外考慮角動量對賡勢之影響，並且被認為較 L-EPM 準確[27]。本節將介紹本論文用於計算鋰錫能帶結構的 NL-EPM 理論，以及 Sentaurus TCAD 套件中 NL-EPM 所需的各項參數之物理意義，並說明鋰錫合金之參數的內插方法。

### 3.1.1 NL-EPM 理論簡介

令內層核電子與最外層價電子之波函數分別為 $|c\rangle$  和 $|\Psi\rangle$ ，由於核電子不參與鍵結，因此 $|c\rangle$ 與單原子內的電子波函數近似。根據包立不相容原理(Pauli exclusion principle)，特徵波函數間彼此正交，因此可將 $|\Psi\rangle$ 以 $|c\rangle$ 和任意一組不在 $|c\rangle$ 空間中的波函數 $|\varphi\rangle$ 透過格瑞姆-史密正交化 (Gram-Schmidt orthogonalization)表示：

$$|\Psi\rangle = |\varphi\rangle - \sum_c |c\rangle < c | \varphi > \quad (\text{式 3.1})$$

代入薛丁格方程式並進行化簡：

$$H|\Psi\rangle = E|\Psi\rangle \quad (\text{式 3.2})$$

$$(H - \sum_c H |c\rangle < c |) |\varphi\rangle = E (|\varphi\rangle - \sum_c |c\rangle < c | \varphi >) \quad (\text{式 3.3})$$

$$(H + \sum_c (E - E_c) |c\rangle < c |) |\varphi\rangle = (H + V_R) |\varphi\rangle = E |\varphi\rangle \quad (\text{式 3.4})$$

其中 $H = \frac{p^2}{2m} + H_{SO} + V_C$ ， $H_{SO}$ 為自旋-軌道耦合之 Hamiltonian， $V_C$ 為原子核產生的週期性位能， $E$ 、 $E_c$ 分別為 $|\varphi\rangle$ 、 $|c\rangle$ 之能量， $V_R$ 為核電子與價電子之間的等效位能，由於 $E > E_c$ ，表示核電子和價電子之間的作用為排斥力。 $V = V_C + V_R$ 即為價電子感受到的總等效位能，也就是贊勢(pseudopotential)，而 $|\varphi\rangle$ 即為其贊勢波函

圖 3.1 (a)單一原子之離子位能(短虛線)及贊勢(長虛線和實線)在空間中之變化示意圖[25]，(b)矽之價電子波函數(all-electron)和贊勢波函數(pseudoatom)在空間之變化示意圖[25]。

數(pseudowavefunction)。原子核的庫倫吸引力被核電子的排斥力部分抵銷，因此  $V_R$  相比於  $V$  較平緩，如圖 3.1(a)所示，原子核造成之離子位能在  $r \rightarrow 0$  處發散，而 費勢則平穩地趨近於有限值，也因此使得費勢波函數  $|\phi\rangle$  在接近原子核處較價電子 波函數  $|\Psi\rangle$  平緩而不會震盪，如圖 3.1 (b)所示。在進行能帶結構計算時，我們所關 注的是價電子的能量  $E$ ，而此能量同時為式 3.2 與式 3.4 之解，因此我們可以費勢 取代原子核位能，求解較簡單的式 3.4 得到價電子能量。

費勢運算子(pseudopotential operator)可以表示為局域費勢運算子(local operator) 與非局域費勢運算子(nonlocal operator)之和。局域運算子是指當該運算子  $A$  作用 於某函數  $f$  上時，滿足以下關係式：

$$Af = a(\vec{r})f(\vec{r}) \quad (\text{式 3.5})$$

意即此運算子作用於函數上的效應  $a(\vec{r})$  只與  $\vec{r}$  處的資訊有關，若不滿足式 3.5 則為 非局域運算子[28]。L-EPM 僅考慮局域費勢，而 NL-EPM 則額外考慮非局域費勢 和角動量對等效位能的修正。文獻[27]指出若使用 L-EPM 計算鎗和  $\alpha$ -錫之能帶結 構，會使得導帶的極值點大小與在  $k$  空間中的位置和實驗結果不符，因此我們選 擇使用 NL-EPM 模擬鎗錫的能帶結構。

晶體中的費勢  $V$  可以視為單原子的費勢  $V_{\text{atom}}$  與晶體結構的卷積運算 (convolution)結果，化簡後可以表示為

$$V = S(\vec{q})\hat{V}_{\text{atom}} = S(\vec{q})[\hat{V}_{\text{atom},L}(\vec{q}) + \hat{V}_{\text{atom},NL}] \quad (\text{式 3.6})$$

其中  $\vec{q}$  為倒晶格向量， $S(\vec{q})$  為結構因子(structure factor)， $\hat{V}_{\text{atom}}$  為  $V_{\text{atom}}$  的傅立葉轉換 並稱之為費勢形式因子(pseudopotential form factor)，並可以進一步展開為局域項  $\hat{V}_{\text{atom},L}(\vec{q})$  和非局域項  $\hat{V}_{\text{atom},NL}$ ，其中局域項只與倒晶格向量  $\vec{q}$  有關，因此只須給定  $\vec{q}$  即可決定  $\hat{V}_{\text{atom},L}$ 。由於  $V$  在空間中的變化平緩，經過傅立葉變換後之  $\hat{V}_{\text{atom},L}(\vec{q})$  在 倒空間中隨  $\vec{q}$  增加而快速遞減至 0，因此通常會選擇一個  $q_{\text{cut-off}}$  使  $\|q\| > q_{\text{cut-off}}$  時 之  $\hat{V} = 0$ ，以加快運算速度， $\|q_{\text{cut-off}}\|$  通常選定在  $\sqrt{11}\frac{2\pi}{a_0}$  處[29]，其中  $a_0$  為晶格常 數。在鑽石結構中，在  $\|q\| \leq q_{\text{cut-off}}$  的範圍內只有  $\{111\}$ 、 $\{222\}$  和  $\{311\}$  之結構因 子不為 0[29]，因此只須考慮  $\|q\| \in \{\sqrt{3}\frac{2\pi}{a_0}, \sqrt{8}\frac{2\pi}{a_0}, \sqrt{11}\frac{2\pi}{a_0}\}$  三組晶格點的費勢值  $V_3$ 、

$V_8$  與  $V_{11}$  便能決定整個局域賡勢。

為了使計算結果更接近實驗數據，必須考慮非局域賡勢  $V_{NL}$  對賡勢的修正。

$V_{NL}$  具有以下形式[27]

$$V_{NL} = \sum_{l=1}^{\infty} A_l(E) f_l(\vec{r}) P_l \quad (\text{式 3.7})$$

$A_l(E)$  為此位能井深， $f_l(\vec{r})$  為角量子數  $l$  之核電子產生的位能， $P_l$  為角量子數  $l$  之角動量投影。在文獻[27]和 Sentaurus TCAD 套件[24]中皆忽略  $l = 1$  的核電子對賡勢位能的效應，即  $A_1(E) = 0$ 。而  $l \geq 3$  的部分因強度較弱，在文獻[24][27]中同樣被忽略。對於  $l = 0$  和  $2$ ， $A_l(E)$  具有以下形式

$$A_0(E) = \alpha_0 + \beta_0 [k(k + q) - k_F^2] \quad (\text{式 3.8})$$

$$A_2(E) = \alpha_2 \quad (\text{式 3.9})$$

其中  $\alpha_0$  和  $\alpha_2$  分別為  $l = 0$  和  $2$  時的位能井深， $\beta_0$  為  $l = 0$  時位能井深和能量相關的修正項， $k_F = \sqrt[3]{\frac{3\pi N_{val}}{\Omega_{cell}}}$  為費米波向量， $\Omega_{cell}$  為單位晶胞體積， $N_{val}$  為單位晶胞內總價電子數。 $f_l(\vec{r})$  在 Sentaurus TCAD 中有階梯函數(step function)和高斯函數(Gaussian function)兩種形式：

$$\text{階梯函數 : } f_l(\vec{r}) = \begin{cases} 1, & r \leq R_l \\ 0, & r > R_l \end{cases} \quad (\text{式 3.10})$$

$$\text{高斯函數 : } f_l(\vec{r}) = e^{-\frac{r^2}{R_l^2}} \quad (\text{式 3.11})$$

兩種形式的  $f_l(\vec{r})$  皆需要給定一參數  $R_l$ 。因此決定非局域賡勢所需要的參數為  $\alpha_0$ 、 $\alpha_2$ 、 $\beta_0$  及  $R_l$ 。在材料受到應變後，各方向的晶格常數與倒晶格常數改變，使得結構因子不為 0 的倒晶格點不再是  $\{111\}$ 、 $\{222\}$  和  $\{311\}$ ，局域賡勢也必須以新的倒晶格位置計算。因此為了得知應變如何改變晶格常數，在計算應變錫的能帶結構時還必須使用到剛度係數(stiffness coefficient) $C_{11}$ 、 $C_{12}$ 、 $C_{44}$  以及內應力參數(internal strain parameter)  $\zeta$  共四項參數。

### 3.1.2 NL-EPM 之參數選定

我們利用 Sentaurus TCAD 套件中的 NL-EPM 計算塊材鉭錫的能帶結構，所使用的鉭與  $\alpha$ -錫之賡勢參數取自文獻[14]，應變參數則取自文獻[4]，如表 3.1、表 3.2 所示。針對不同錫濃度的鉭錫，使用虛擬晶格近似(virtual crystal approximation, VCA) 對大部分參數進行線性內插，少數例外為晶格常數、單一原子體積和局域賡勢形式因子值，因這些參數有較 VCA 更為準確的內插方式：

- i. 晶格常數考慮二次修正項(bowing parameter)，對於錫濃度  $x$  之鉭錫，其晶格常數 $a_{Ge_{1-x}Sn_x}$ 可以式 3.12 計算：

$$a_{Ge_{1-x}Sn_x} = (1 - x)a_{Ge} + xa_{Sn} - (1 - x)x \cdot b \quad (\text{式 3.12})$$

其中  $a_{Ge}$ 、 $a_{Sn}$  分別為鉭、錫之晶格常數， $b = -0.166[5]$ 。

- ii. 單一原子體積 $\Omega$ 由晶格常數計算而得。鑽石結構中單位晶格的原子數為 8，因此 $\Omega_{Ge_{1-x}Sn_x} = a_{Ge_{1-x}Sn_x}^3 / 8$ 。

- iii. 因鉭和  $\alpha$ -錫的晶格常數相差較大，會產生成分失序(compositional disorder)進而對賡勢值造成影響[4]因此必須採用修正型虛擬晶格近似(modified virtual crystal approximation, modified VCA)來計算鉭錫合金的賡勢值[4][5][30]，其具有以下形式

$$\begin{aligned} V_{Ge_{1-x}Sn_x}(q) &= (1 - x) \frac{\Omega_{Ge}}{\Omega_{Ge_{1-x}Sn_x}} V_{Ge}(q) + x \frac{\Omega_{Sn}}{\Omega_{Ge_{1-x}Sn_x}} V_{Sn}(q) \\ &\quad - Px(1 - x) \frac{\Omega_{Sn}V_{Sn} - \Omega_{Ge}V_{Ge}(q)}{\Omega_{Ge_{1-x}Sn_x}} \end{aligned} \quad (\text{式 3.13})$$

其中  $q$  為倒晶格空間向量， $\Omega_{Ge}$ 、 $\Omega_{Sn}$  為鉭和  $\alpha$ -錫之單一原子體積， $V_{Ge}(q)$ 、 $V_{Sn}(q)$  為鉭和錫之賡勢值， $P$  為擬合參數，用於調整賡勢值使模擬出的能帶結構符合能隙實驗值。根據文獻[31]的擬合結果，選用  $P = -0.3$  進行本論文中的能帶結構模擬。

表 3.1 EPM 模擬所使用鉻與  $\alpha$ -錫之局域與非局域賈勢參數[14]。

| 參數           | 單位               | 鉻數值     | $\alpha$ -錫數值 | 物理意義                                 |

|--------------|------------------|---------|---------------|--------------------------------------|

| $V_3$        | $R_y$            | -0.2378 | -0.21         | $q = \sqrt{3}(2\pi/a_0)$ 處之局域賈勢形式因子  |

| $V_8$        | $R_y$            | 0.02852 | 0.02359       | $q = \sqrt{8}(2\pi/a_0)$ 處之局域賈勢形式因子  |

| $V_{11}$     | $R_y$            | 0.0469  | 0.01737       | $q = \sqrt{11}(2\pi/a_0)$ 處之局域賈勢形式因子 |

| $a_0$        | $R_y$            | 0.0     | 0.0           | 角量子數 $l=0$ 之非局域位能井深度                 |

| $a_2$        | $R_y$            | 0.309   | 0.71          | 角量子數 $l=2$ 之非局域位能井深度                 |

| $\beta_0$    | 1                | 0.0     | 0.365         | 角量子數 $l=0$ 之修正項                      |

| $R_0$        | $\text{\AA}$     | 0.0     | 1.0           | 角量子數 $l=0$ 之非局域位能井寬度                 |

| $R_2$        | $\text{\AA}$     | 1.2788  | 1.453         | 角量子數 $l=2$ 之非局域位能井寬度                 |

| $\mu_{LS}$   | $R_y$            | 0.00093 | 0.00225       | 自旋-軌道耦合強度                            |

| $\zeta_{LS}$ | 1/Bohr<br>Radius | 5.34    | 3.97          | 核電子屏蔽自旋-軌道耦合之程度                      |

表 3.2 EPM 模擬所使用鉻與  $\alpha$ -錫之其他參數[4][14]。

| 參數       | 單位                   | 鉻數值     | $\alpha$ -錫數值 | 物理意義       |

|----------|----------------------|---------|---------------|------------|

| $a_0$    | $\text{\AA}$         | 5.650   | 6.489         | 鬆弛條件下之晶格常數 |

| $\Omega$ | $\text{\AA}$         | 22.5453 | 34.1541       | 晶格中單位原子體積  |

| $C_{11}$ | $10^{11} \text{ Pa}$ | 1.287   | 0.690         | 剛度係數       |

| $C_{12}$ | $10^{11} \text{ Pa}$ | 0.477   | 0.293         | 剛度係數       |

| $C_{44}$ | $10^{11} \text{ Pa}$ | 0.667   | 0.362         | 剛度係數       |

| $\zeta$  | 1                    | 0.440   | 0.548         | 內應力參數      |

## 3.2 鋒錫能帶結構模擬

我們利用 NL-EPM 計算不同應變條件與錫比例的鋒錫能帶結構，以驗證前一章的實驗結果。能帶結構模擬結果如圖 3.2 所示，施加拉伸應變能減少間接與直接能隙的差值，在拉伸應變( $\epsilon = +1\%$ )、無應變鬆弛( $\epsilon = 0$ )與壓縮應變( $\epsilon = -1\%$ )的 8 %鋒錫中，間接與直接能隙的差值( $E_g^L - E_g^\Gamma$ )分別為 32 meV、-14 meV 與-63 meV，只有拉伸應變鋒錫為直接能隙材料，壓縮應變與無應變鋒錫均為間接能隙材料。對於錫比例較高的無應變 12 %鋒錫，模擬結果顯示其能隙差值為 50 meV，相較於無應變 8 %鋒錫直接能隙的特性更為顯著，顯示增加錫比例有助於使鋒錫由間接轉變為直接能隙材料，與文獻之結果相符。圖 3.3(a)為錫比例為 8 %的鋒錫之能隙隨雙軸向應變的變化圖，其中正應變代表材料受到拉伸應力，負應變代表材料受到壓縮應力。8 %鋒錫在鬆弛狀態時為間接能隙材料，對鋒錫施加拉伸應力後，直接能隙與間接能隙均隨應變增加而下降，又以直接能隙的下降幅度較大，因此在拉伸應變超過約 0.3 %後，鋒錫轉變為直接能隙材料(圖 3.3 (b))。相對地，若是對鋒錫施加壓縮應力，直接能隙的能量會隨著應變增加而上升，間接能隙的能量卻隨應變增加而下降，使間接與直接能隙的能量差距增加，因此施加壓縮應力使鋒錫更趨向間接能隙材料。圖 3.3 (c)為無應變鋒錫之能隙隨錫比例的變化圖，直接與間接能隙均隨著錫比例的增加而減少，其中又以直接能隙的減少幅度較大，因此在錫比例超過約 9 %時，鋒錫由間接能隙轉變為直接能隙材料(圖 3.3 (d))，在文獻[6]中此值為 11 %，在文獻[4]中此值為 6 %，而在文獻[14]中此值為 10 %，三篇文獻均使用 EPM 計算鋒錫能帶結構，然而因參數選用不同在模擬結果產生分歧，我們的模擬結果與文獻[14]最接近，推測是因為使用的參數選自該文獻，而結果的些微差異可能原因為我們使用 modified VCA，而該文獻則使用 VCA 直接以線性內插計算鋒錫合金的參數。

圖 3.2 (a)壓縮應變( $\varepsilon = -1\%$ )、(b)鬆弛( $\varepsilon = 0$ )、(c)拉伸應變( $\varepsilon = +1\%$ )  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  與

(d)鬆弛( $\varepsilon = 0$ ) $\text{Ge}_{0.88}\text{Sn}_{0.12}$  之能帶結構模擬結果。

圖 3.3 (a) $\text{Ge}_{0.92}\text{Sn}_{0.08}$  之直接與間接能隙隨雙軸向應變的變化，(b)鬆弛錫錫之直接

與間接能隙隨錫比例的變化，(c)  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  之間接與直接能隙差值隨雙軸向應變

的變化，(d) 鬆弛錫錫之間接與直接能隙差值隨錫比例的變化。

為了計算電子於 L 谷與  $\Gamma$  谷的分布情形，必須取得電子的能態密度等效質量 (density of states effective mass)，因此我們從塊材鍺錫的能帶結構模擬結果，以拋物線近似萃取  $\Gamma$  點與 L 點的等效電子質量

$$m_e^* = \hbar^2 \left( \frac{\partial^2 E}{\partial k^2} \right)^{-1} \quad (\text{式 3.14})$$

其中鍺錫在 L 點處的等效電子質量由於晶體結構的非對稱性，可以分成與<111>方向平行的縱向等效質量  $m_{e,l}^*$  (longitudinal effective mass) 以及垂直於<111>方向的橫向等效質量  $m_{e,t}^*$  (transverse effective mass)。 $\Gamma$  點與 L 點的能態密度等效質量可以進一步以式 3.15 與式 3.16 計算得到[16]：

$$m_{DOS,\Gamma}^* = m_{e,\Gamma}^* \quad (\text{式 3.15})$$

$$m_{DOS,L}^* = (m_{e,t}^*)^{2/3} \cdot (m_{e,l}^*)^{1/3} \quad (\text{式 3.16})$$

圖 3.4 為不同應變條件與錫比例的鍺錫之等效電子質量模擬結果。隨著應變條件由壓縮轉變為拉伸， $\Gamma$  電子與 L 點的縱向及橫向等效電子質量均微幅下降(圖 3.4 (a)(c)(e))， $\Gamma$  電子與 L 電子的縱向等效質量在 1 % 拉伸應變鍺錫中，相較於在 1 % 壓縮應變鍺錫中減少約 10 %，L 電子的橫向等效質量則減少約 5 %。而在不同錫比例的無應變鍺錫中， $\Gamma$  電子的等效質量隨錫比例的增加呈現明顯下降趨勢(圖 3.4 (b))，從錫比例 0 % 至 20 %，等效質量約減少了 60 %；相對而言，L 電子的橫向與縱向等效質量在錫比例 0 ~ 20 % 的範圍內幾乎不變(圖 3.4 (d)(f))。與同樣使用 EPM 模擬鍺錫能帶結構的文獻[6][16][26][32]比較， $\Gamma$  電子的等效質量在錫比例 4 % 至 12 % 範圍內與文獻數值接近，平均誤差在 2 % 內，而在純鍺與錫比例超過 12 % 後平均誤差約為 10 %，L 電子的橫向與縱向等效質量的平均誤差則分別在 4 % 與 8 % 內，整體而言，我們的等效質量隨錫濃度變化之趨勢和文獻結果相符，驗證了我們 NL-EPM 模擬的可靠性。圖 3.5 為電子在  $\Gamma$  點與 L 點的能態密度等效質量比較圖。在 8 % 鍺錫中， $\Gamma$  點與 L 點的能態密度等效質量在應變條件從 -1 % 至 1 % 的範圍內變化不大(圖 3.5 (a))，L 點的質量約為  $\Gamma$  點的 8 倍。而對於無應變鍺錫(圖 3.5 (b))，由於 L 點的等效質量幾乎不隨錫比例改變， $\Gamma$  點的等效質量卻隨錫比例增加而下降，因此從錫比例 0 % 至 20 %，L 點的能態密度等效質量從  $\Gamma$  點的 6 倍上升至 15 倍。由於等效質量越大，遷移率就越小，因此從模擬結果可以預期電子在 L 點的

圖 3.4 不同應變條件下， $\text{Ge}_{0.92}\text{Sn}_{0.08}$  之(a)  $\Gamma$  電子、(c) L 電子之縱向和(e) L 電子之橫向等效質量模擬結果。不同錫比例之無應變鬆弛錫之(b)  $\Gamma$  電子、(d) L 電子之縱向和(f) L 電子之橫向等效質量模擬結果。

圖 3.5 (a)不同應變條件下， $\text{Ge}_{0.92}\text{Sn}_{0.08}$  之  $\Gamma$  電子與 L 電子之能態密度等效質量比較圖。(b)不同錫比例之無應變鬆弛錫之  $\Gamma$  電子與 L 電子之能態密度等效質量比較圖。

遷移率較  $\Gamma$  點低，且隨著錫比例增加，遷移率的差距越大。

為了驗證我們於前一章所提出的電子遷移率與直接、間接能隙的關係，我們進一步計算電子於 L 谷與  $\Gamma$  谷中的分布情形。假設能帶的完美拋物線性，即等效質量不隨能量 E 而變，L 谷與  $\Gamma$  谷中的電子濃度 n 可分別以式 3.17 計算

$$n = \int_{E_C}^{\infty} g(E) \times f(E) dE \\ = \int_{E_C}^{\infty} \frac{M_C \sqrt{2} m_{\text{DOS}}^{3/2} \sqrt{E-E_C}}{\pi^2 \hbar^3} \times \frac{1}{1 + \exp(\frac{E-E_F}{kT})} dE \quad (\text{式 3.17})$$

其中由於我們是計算塊材錫之電子濃度，因此  $g(E)$  為三維的能態密度公式， $f(E)$  為費米-狄拉克分布函數， $M_C$  為傳導帶中等效最低點的數量，此值在  $\Gamma$  點為 1，在 L 點為 4[16]， $E_C$  為傳導帶在 L 點或  $\Gamma$  點的值。圖 3.6 為 4 ~ 300 K 下不同應變條件與錫比例之錫之  $\Gamma$  電子與 L 電子的數量比例( $n_\Gamma/n_L$ )比較圖，由前一章的霍爾量測結果可知，電子濃度幾乎不隨溫度而變，因此在計算不同溫度下的  $\Gamma/L$  電子比例時固定總電子濃度為  $n_L + n_\Gamma = 1 \times 10^{18} \text{ cm}^{-3}$ ，以模擬低摻雜濃度的錫塊材。圖 3.6 (a) 為拉伸應變( $\varepsilon = +1\%$ )、無應變鬆弛( $\varepsilon = 0$ )與壓縮應變( $\varepsilon = -1\%$ )的 8% 錫之  $\Gamma/L$  電子比例比較圖，間接能隙材料的無應變與壓縮應變錫之  $\Gamma/L$  電子比例隨溫

圖 3.6 (a)壓縮應變( $\varepsilon = -1\%$ )、無應變( $\varepsilon = 0$ )與拉伸應變( $\varepsilon = +1\%$ ) $\text{Ge}_{0.92}\text{Sn}_{0.08}$ 中  $\Gamma$  電子與 L 電子比例隨溫度之變化，(b)不同錫比例的無應變鍺錫中  $\Gamma$  電子與 L 電子比例隨溫度之變化，(c)間接能隙與直接能隙鍺錫在室溫與低溫的電子分布情形示意圖。

度下降而降低，而直接能隙材料的拉伸應變鍺錫的  $\Gamma/L$  電子比例隨溫度下降而增加，且在  $4 \sim 300\text{ K}$  溫度範圍中，拉伸應變鍺錫的  $\Gamma/L$  電子比例最高，其次為無應變鍺錫，壓縮應變鍺錫的比例最低，其原因可以圖 3.6(c)解釋。高溫時電子能克服  $\Gamma$  谷與 L 谷的能量差，因此不論在直接能隙或間接能隙鍺錫中， $\Gamma$  谷與 L 谷中都有電子存在，三種應變條件的鍺錫之  $\Gamma/L$  電子比例差異較小；而低溫下的電子無法克服  $\Gamma$  谷與 L 谷的能量差，大部分聚集在較低的谷中，因此屬於直接能隙材料的拉伸應變鍺錫之  $\Gamma$  電子佔比增加，而屬於間接能隙材料的無應變與壓縮應變鍺錫之  $\Gamma$  電子佔比減少。值得注意的是，即使在  $\Gamma$  電子比例最高的拉伸應變鍺錫中， $\Gamma$  電子的數量大約也只有 L 電子的四分之一，L 電子依然佔多數，這是由於 L 電子的能態密度等效質量較大，使得與等效質量呈 1.5 次方正比的能態密度約為  $\Gamma$  電子的 90 倍，因此在直接能隙與間接能隙相近的情況下，分布於 L 谷中的電子數量會遠大於  $\Gamma$  谷。圖 3.6(b)為無應變鬆弛的 8 % 與 12 % 鍺錫之  $\Gamma/L$  電子比例比較圖，間接能隙材料的 8 % 鍳錫的  $\Gamma/L$  電子比例隨溫度下降而降低，而直接能隙材料的 12 % 鍳錫的  $\Gamma/L$  電子比例隨溫度下降而增加，且 12 % 鍳錫在  $4 \sim 300\text{ K}$  溫度範圍中， $\Gamma$  電子的比例均較 8 % 鍳錫高，其原因同樣可以圖 3.6(c)解釋，電子隨著溫度降低而聚集至低能量的谷中，使得直接能隙的 12 % 鍳錫中  $\Gamma$  電子佔比上升，對於間接能隙的 8 % 鍳錫則有相反的趨勢。根據 EPM 的等效質量模擬，L 電子的質量較大，

其遷移率較  $\Gamma$  電子低，因此在不考慮其他散射機制的情況下，鉭錫中的  $\Gamma/L$  電子比例越高，平均電子遷移率就越高。將模擬結果與前一章的霍爾量測結果(圖 2.12、圖 2.13)進行比較，可以發現拉伸應變鉭錫由於具有較高的  $\Gamma$  電子比例，電子遷移率較相同錫比例的無應變和壓縮應變鉭錫高，同理，12 %無應變鉭錫相比於錫比例較低的 8 %鉭錫擁有較多的  $\Gamma$  電子以及較高的遷移率。而模擬結果與實驗結果不同之處，在對於間接能隙鉭錫的遷移率隨溫度變化的趨勢，模擬顯示  $\Gamma$  電子隨溫度降低而減少，遷移率應隨之降低，然而霍爾量測結果卻顯示隨著溫度降低，遷移率維持不變或甚至不降反升，可能的原因為模擬並未考慮電子的散射機制，例如會抑制高溫時遷移率的聲子散射，因此無法完美預測溫度對遷移率的影響。

除了溫度對  $\Gamma/L$  電子分布的影響，我們也針對不同摻雜濃度的鉭錫進行模擬計算。圖 3.7 為 300 K 下電子濃度在  $10^{17}$  至  $10^{20} \text{ cm}^{-3}$  的鉭錫之  $\Gamma/L$  電子比例模擬結果，在不同應變條件與錫比例的鉭錫中，無應變與壓縮應變的 8 %鉭錫之  $\Gamma$  電子比例隨著摻雜濃度提升而增加(圖 3.7 (a))，而拉伸應變 8 %鉭錫(圖 3.7 (a))與無應變 12 %鉭錫(圖 3.7 (b))的  $\Gamma$  電子比例隨摻雜濃度提升而下降，其原因可以圖 3.7 (c)解釋：電子濃度低時，電子大多分布於低能量的谷中，隨著電子濃度增加，低能階填滿後電子依序往高能階填，因此  $\Gamma$  谷與 L 谷中均有電子存在。對直接能隙鉭

圖 3.7 (a)室溫下不同應變條件下的  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  中  $\Gamma$  電子與 L 電子比例隨總電子密度之變化，(b)室溫下不同錫比例的鬆弛鉭錫中  $\Gamma$  電子與 L 電子比例隨總電子密度之變化，(c)間接能隙與直接能隙鉭錫在重摻雜與輕摻雜條件下的電子分布情形示意圖。

圖 3.8 (a)室溫下不同應變條件下的  $\text{Ge}_{0.92}\text{Sn}_{0.08}$  與(b)室溫下不同錫比例的鬆弛鍺錫之  $\Gamma/L$  電子比例(實線)與電子遷移率(星號)隨電子濃度之變化。

錫而言，電子濃度越高會使  $\Gamma$  電子的比例下降，反之，對間接能隙鍺錫而言，隨著電子濃度的增加， $\Gamma$  電子的佔比上升。與第二章之實驗數據相比，不同之處在於無應變與壓縮應變的 8 %鍺錫隨電子濃度的變化(圖 3.8)，雖然模擬結果預期  $\Gamma$  電子的比例隨著電子濃度增加，遷移率應該相對應地增加，然而在實驗結果上，壓縮應變鍺錫的遷移率幾乎不變，無應變鍺錫的遷移率甚至反而降低，推測原因為雜質散射抑制了遷移率，電子濃度越高代表摻雜的濃度也越高，從電子濃度  $10^{17}$  至  $10^{20} \text{ cm}^{-3}$ ，雜質濃度大幅提升，然而  $\Gamma$  電子只有微幅增加且只有  $L$  電子數量的約 1 %，因此推測是散射機制抵銷了  $\Gamma$  電子增加的效應，使得遷移率不見提升。在不同應變條件中，以拉伸應變鍺錫的  $\Gamma$  電子比例最高，最低的為壓縮應變鍺錫，因此可以預期拉伸應變鍺錫擁有最高的電子遷移率，此結果與實驗相符(圖 3.8(a))；在不同錫比例的鍺錫中，12 %鍺錫的  $\Gamma$  電子比例較高，而我們的實驗數據也證實高錫比例的鍺錫具有較高的電子遷移率(圖 3.8(b))。

### 3.3 結論

本章使用 Sentaurus TCAD 套件以 NL-EPM 模擬塊材鉭錫之能帶結構，萃取 L 點與  $\Gamma$  點的等效電子質量，並計算不同應變條件與錫比例的鉭錫在 4~300 K 溫度下，電子於 L 谷與  $\Gamma$  谷中的分布情形。能帶結構的模擬結果顯示隨著錫比例增加，直接與間接能隙減少，並且在錫比例超過 9 % 時鉭錫轉變為直接能隙材料，與大多數文獻之模擬結果接近，顯示我們的模擬套件的可信度。利用拋物線近似萃取在  $\Gamma$  點與 L 點的能態密度等效質量， $\Gamma$  點的等效質量隨錫比例增加而減少，L 點則幾乎不受影響， $\Gamma$  點與 L 點的等效質量也幾乎不隨應變而變，在錫比例 0 % 至 20 % 的無應變鉭錫中，L 點的等效質量約為  $\Gamma$  點的 15~40 倍，因此預期  $\Gamma$  點的電子遷移率較 L 點高。計算鉭錫在不同溫度與摻雜濃度下的  $\Gamma$  電子與 L 電子之比例並與第二章之實驗數據相比，我們發現具有直接能隙特性的鉭錫之  $\Gamma$  電子隨著溫度和濃度的降低而增加，因此拉伸應變與高錫比例的 12 % 鉭錫之電子遷移率相對應地增加。不同應變條件中，拉伸應變鉭錫之  $\Gamma$  電子最多，而不同錫比例的鉭錫中，12 % 鉭錫的  $\Gamma$  電子較多，因此預期其電子遷移率較高，此結果與實驗數據相符。

## 第 4 章 結論及未來工作

### 4.1 結論

本論文以實驗與理論計算探討不同應變條件與錫比例下的鍺錫之能帶結構與電子傳導特性。第二章以霍爾量測實驗探討錫比例與應變對於鍺錫的電子遷移率之影響，製作元件研究 4~300 K 的鍺錫薄膜傳導特性。以減壓化學氣相沉積法製備含有錫比例為 8%、12% 的壓縮應變、鬆弛、拉伸應變之內摻雜鍺錫磊晶，並以 AFM 分析磊晶之表面粗糙度，以及 RSM 分析鍺錫薄膜之錫濃度和應變大小，得到錫濃度與預期值相近，壓縮應變  $Ge_{0.92}Sn_{0.08}$ 、應變鬆弛  $Ge_{0.92}Sn_{0.08}$ 、應變鬆弛  $Ge_{0.88}Sn_{0.12}$  與拉伸應變  $Ge_{0.92}Sn_{0.08}$  內摻雜鍺錫層之應變值分別為 -0.89%、-0.25%、-0.37% 與 +0.25%。將鍺錫磊晶圓製作成霍爾棒元件並進行變溫霍爾量測，經過雙層傳導校正後，發現電子遷移率受到聲子散射主導，隨溫度降低而先升後降。為探討應變與錫比例對鍺錫的電子遷移率之影響並排除雜質散射的干擾，以電子濃度相近的樣品做比較，在 8% 鍺錫中以拉伸應變鍺錫的遷移率最高，壓縮應變鍺錫的遷移率最低，而在鬆弛鍺錫中以高錫比例的 12% 鍺錫之遷移率較高，顯示施加拉伸應變或提高錫比例有助於讓鍺錫由間接能隙轉變為直接能隙，其中由於低溫時能克服直接與間接能帶能量差的電子大幅減少，因此遷移率的差距更為明顯。我們也觀察 4 K 下遷移率隨濃度變化的趨勢，發現在較接近直接能隙的拉伸應變或高錫比例鍺錫中，遷移率隨濃度下降明顯地上升，推測原因為雜質散射減弱與  $\Gamma$  電子的比例增加。

第三章使用 Sentaurus TCAD 套件以 NL-EPM 模擬塊材鍺錫之能帶結構，萃取 L 點與  $\Gamma$  點的等效電子質量，並計算不同應變條件與錫比例的鍺錫在 4~300 K 溫度下，電子於 L 能帶與  $\Gamma$  能帶中的分布情形。能帶結構的模擬結果顯示隨著錫比例增加，直接與間接能隙減少，並且在錫比例超過 9% 時鍺錫轉變為直接能隙材料。利用拋物線近似萃取在  $\Gamma$  點與 L 點的能態密度等效質量，在錫比例 0% 至 20% 的無應變鍺錫中，L 點的等效質量約為  $\Gamma$  點的 15~40 倍，因此預期  $\Gamma$  點的電子遷移率較 L 點高。計算鍺錫在不同溫度與摻雜濃度下的  $\Gamma$  電子與 L 電子之比例並與第二章之實驗數據相比，發現具有直接能隙特性的鍺錫之  $\Gamma$  電子隨著溫度和濃度的

降低而增加，因此拉伸應變與高錫比例的 12 %錫錫之電子遷移率相對應地增加。不同應變條件中，拉伸應變錫錫之  $\Gamma$  電子最多，而不同錫比例的錫錫中，12 %錫錫的  $\Gamma$  電子較多，因此預期其電子遷移率較高，此結果與實驗數據相符。

## 4.2 未來工作

未來的工作項目可分為三個部分：

1. 考慮雜質散射、聲子散射、谷間散射等多種散射機制[8]，搭配以 EPM 計算出之  $\Gamma/L$  電子分布情形，計算錫錫之電子遷移率，更深入探討錫錫的能隙與電性之關係。

2. 製作不同應變條件與錫比例的錫錫 nMOSFET[17]，進行 4 ~ 300 K 的電性量測並萃取等效遷移率，與塊材錫錫的量測結果比較。

3. 製作 p 型內摻雜錫錫磊晶，進行 4 ~ 300 K 的霍爾量測，探討應變與錫比例對塊材錫錫的電洞遷移率之影響。

## 參考文獻

- [1] Jeff Desjardins, “Visualizing Moore’s law in action (1971-2019),” available: [www.visualcapitalist.com/visualizing-moores-law-in-action-1971-2019/](http://www.visualcapitalist.com/visualizing-moores-law-in-action-1971-2019/), 2019.

- [2] L. S. Wilson, “International roadmap for devices and systems™ 2020 edition: More Moore,” 2020.

- [3] C. Yadav, “Compact modeling of capacitance and current in silicon and III - V transistors,” Ph.D. dissertation, Indian Institute of Technology Kanpur, India, 2016.

- [4] L. Liu, R. Liang, J. Wang, and J. Xu, “Enhanced carrier mobility and direct tunneling probability of biaxially strained  $\text{Ge}_{1-x}\text{Sn}_x$  alloys for field-effect transistors applications,” *Journal of Applied Physics*, vol. 117, no. 18, p. 184501, 2015.

- [5] S. Gupta, B. Magyari-Köpe, Y. Nishi, and K. C. Saraswat, “Achieving direct band gap in germanium through integration of Sn alloying and external strain,” *Journal of Applied Physics*, vol. 113, no. 7, p. 073707, 2013.

- [6] K. L. Low, Y. Yang, G. Han, W. Fan, and Y.-C. Yeo, “Electronic band structure and effective mass parameters of  $\text{Ge}_{1-x}\text{Sn}_x$  alloys,” *Journal of Applied Physics*, vol. 112, no.10, p. 103715, 2012.

- [7] J. D. Sau and M. L. Cohen, “Possibility of increased mobility in Ge-Sn alloy system,” *Physical Review B*, vol. 75, no. 4, p. 045208, 2007.

- [8] C. Schulte-Braucks *et al.*, “Process modules for GeSn nanoelectronics with high Sn-contents,” *Solid-State Electronics*, vol. 128, p. 54, 2017.

- [9] W. Du *et al.*, “Room-temperature electroluminescence from Ge/ $\text{Ge}_{1-x}\text{Sn}_x$ /Ge diodes on Si substrates,” *Applied Physics Letters*, vol. 104, no. 24, p. 241110, 2014.

- [10] B. R. Conley *et al.*, “Si based GeSn photoconductors with a 1.63 A/W peak responsivity and a 2.4  $\mu\text{m}$  long-wavelength cutoff,” *Applied Physics Letters*, vol. 105, no. 22, p. 221117, 2014.

- [11] S. Wirths *et al.*, “Lasing in direct-bandgap GeSn alloy grown on Si,” *Nature*

*Photonics*, vol. 9, no. 2, p. 88, 2015.

- [12] S. Gupta, “Germanium-tin (GeSn) technology,” Ph.D. dissertation, Stanford University, USA, 2013.

- [13] W. Huang, B. Cheng, C. Xue, and Z. Liu, “Comparative studies of band structures for biaxial (100)-, (110)-, and (111)-strained GeSn: A first-principles calculation with GGA+U approach,” *Journal of Applied Physics*, vol. 118, no. 16, p. 165704, 2015.

- [14] S. Sant and A. Schenk, “Pseudopotential calculations of strained-GeSn/SiGeSn hetero-structures,” *Applied Physics Letters*, vol. 105, no. 16, p. 162101, 2014.

- [15] S. A. Ghetmiri *et al.*, “Direct-bandgap GeSn grown on silicon with 2230 nm photoluminescence,” *Applied Physics Letters*, vol. 105, no. 15, p. 151109, 2014.

- [16] Y. Yang *et al.*, “Germanium-tin n-channel tunneling field-effect transistor: Device physics and simulation study,” *Journal of Applied Physics*, vol. 113, no. 19, p. 194507, 2013.

- [17] Y. Chuang, C.-Y. Liu, G.-L. Luo, and J.-Y. Li, “Electron mobility enhancement in GeSn n-channel MOSFETs by tensile strain,” *IEEE Electron Device Letters*, vol. 42, no. 1, p. 10, 2021.

- [18] S. Gupta *et al.*, “Towards high mobility GeSn channel nMOSFETs: Improved surface passivation using novel ozone oxidation method,” *2012 International Electron Devices Meeting*, p. 16.2.1, 2012.

- [19] D. K. Schroder, *Semiconductor material and device characterization*, John Wiley & Sons, 2015.

- [20] H. Li, Y. X. Cui, K. Y. Wu, W. K. Tseng, H. H. Cheng, and H. Chen, “Strain relaxation and Sn segregation in GeSn epilayers under thermal treatment,” *Applied Physics Letters*, vol. 102, no. 251907, p. 1, 2013.

- [21] T. T. Tran, “Synthesis of germanium-tin alloys by ion implantation and pulsed laser melting: Towards a group IV direct band gap semiconductor,” Ph.D. dissertation,

The Australian National University, Australia, 2017.

- [22] W. Takeuchi, T. Asano, Y. Inuzuka, M. Sakashita, O. Nakatsuka, and S. Zaima, “Characterization of shallow- and deep-level defects in undoped  $\text{Ge}_{1-x}\text{Sn}_x$  epitaxial layers by electrical measurements,” *ECS Journal of Solid State Science and Technology*, vol. 5, no. 4, p. P3082, 2015.

- [23] D. W. Jenkins and J. D. Dow, “Electronic properties of metastable  $\text{Ge}_x\text{Sn}_{1-x}$  alloys”, *Physical Review B*, vol. 36, no. 15, p. 7994, 1987.

- [24] Synopsys Inc., *Sentaurus Device Monte Carlo User Guide*, Version 2018.06, 2018.

- [25] M. L. Cohen and J. R. Chelikowsky, *Electronic Structure and Optical Properties of Semiconductors*, Springer Science & Business Media, 2012.

- [26] L. Liu, R. Liang, J. Wang, and J. Xu, “Investigation on the effective mass of  $\text{Ge}_{1-x}\text{Sn}_x$  alloys and the transferred-electron effect,” *Applied Physics Express*, vol. 8, no. 3, p. 031301, 2015.

- [27] J. R. Chelikowsky and M. L. Cohen, “Nonlocal pseudopotential calculations for the electronic structure of eleven diamond and zinc-blende semiconductors,” *Physical Review B*, vol. 14, no. 2, p. 556, 1976.

- [28] M. L. Cohen and V. Heine, “The fitting of pseudopotentials to experimental data and their subsequent application,” *Solid State Physics*, vol. 24, p. 37, 1970.

- [29] P. Y. Yu and M. Cardona, *Fundamentals of Semiconductors*, Springer, 1996.

- [30] S. J. Lee, T. S. Kwon, K. Nahm, and C. K. Kim, “Band structure of ternary compound semiconductors beyond the virtual crystal approximation,” *Journal of Physics: Condensed Matter*, vol. 2, no. 14, p. 3253, 1990.

- [31] P.-Y. Chiu, “Magneto-transport and effective mass of two-dimensional hole gases in Ge and GeSn quantum wells,” M.S. thesis, Nation Taiwan University, Taiwan, 2020.

- [32] S.-Q. Liu and S.-T. Yen, “Extraction of eight-band  $k \cdot p$  parameters from empirical pseudopotentials for GeSn,” *Journal of Applied Physics*, vol. 125, no. 24, p. 245701,

2019.

## 相關發表

### 會議論文：

1. K.-Y. Tien, C.-Y. Liu, P.-Y. Chiu, Y. Chuang, H.-S. Kao, and J.-Y. Li, “Electron Mobility Enhancement in n-GeSn Epitaxial Layers by Tensile Strain,” *2021 International Conference on Solid State Devices and Materials*, Japan(virtual), Sep. 6 – 9, 2021.

2. C.-Y. Liu, Y. Chuang, C.-T. Tai, H.-S. Kao, K.-Y. Tien, J.-Y. Li, “High-performance GeSn Electronic Devices and spin-orbit coupling in GeSn/Ge heterostructures,” *2021 IEEE Photonics Society Summer Topicals Meeting Series (SUM)*, Cabo San Lucas, Mexico, July 19-21, 2021.

3. C.-Y. Lin, K.-Y. Tien, C.-Y. Liu, Y. Chuang, C.-T. Chu, P.-Y. Chiu, J.-Y. Li, “Weak antilocalization (WAL) effects in p-GeSn epilayers,” *2019 International Electron Devices and Materials Symposium (IEDMS)*, New Taipei, Taiwan, Oct. 24 – 25, 2019.

### 期刊論文：

1. C.-Y. Liu, K.-Y. Tien, P.-Y. Chiu, Y.-J. Wu, Y. Chuang, H.-S. Kao, and J.-Y. Li, “Room-Temperature Negative Differential Resistance and High Tunneling Current Density in GeSn Esaki Diodes,” *Advanced Materials*, vol. 34, no. 41, p. 2203888, 2022.

2. Y. Chuang, C.-Y. Liu, H.-S. Kao, K.-Y. Tien, G.-L. Luo, and J.-Y. Li, “Schottky barrier height modulation of metal/n-GeSn contacts featuring low contact resistivity by in situ chemical vapor deposition doping and NiGeSn alloy formation,” *ACS Applied Electronic Materials*, vol. 3, no. 3, pp. 1334-1340, 2021.