國立臺灣大學電機資訊學院電信工程學研究所

# 博士論文

Graduate Institute of Communication Engineering College of Electrical Engineering & Computer Science National Taiwan University Doctoral Dissertation

毫米波除頻器及相移器之研究

Research on Millimeter-Wave Frequency Dividers and Phase Shifters

林毓軒

Yu-Hsuan Lin

指導教授:王暉 博士

Advisor: Huei Wang, Ph.D.

中華民國 107 年 2 月

February, 2018

# 國立臺灣大學(碩)博士學位論文 口試委員會審定書

## 毫米波除頻器及相移器之研究

# Research on Millimeter-Wave Frequency Dividers and Phase Shifters

本論文係林毓軒君(F99942093)在國立臺灣大學電信工程學研 究所完成之碩(博)士學位論文,於民國106年12月29日承下列考 試委員審查通過及口試及格,特此證明

口試委員:

(簽名) (指導教授) 家行 (簽名) 所 長

誌謝

漫長的碩博士生涯即將隨著此本論文的完成而結束。能夠完成這本論文,我 要感謝我的指導教授王暉老師。王老師提供相當豐富的資源和合作計畫,提供了 學生學習機會和實現自己研究想法。同時也感謝王老師非常有耐心地幫我批改了 幾篇國際期刊及會議論文,使我的英文在文法和邏輯上更為流暢。此外王老師的 工作態度、效率以及精準的判斷力讓學生欽佩不已。也感謝各位口試委員在百忙 之中抽空檢閱本論文的口試委員黃天偉教授、呂良鴻教授、陳怡然教授、邱煥凱 教授、盧信嘉教授、林坤佑教授、蔡作敏教授、蔡政翰教授,謝謝您們的建議與 幫助使本論文更加完備。

感謝郭京霖學長引導我進入射頻及毫米波電路設計領域,從第一次洗板子至 第一次晶片下線、量測和第一次國際會議論文的撰寫都是在學長的幫助下完成。 感謝高瑞智學長在研究上的討論以及建議,即使學長畢業後還是不厭其煩的解答 我各式各樣的問題,在期刊論文的修改也給予我很大的幫助。感謝楊弘源學長在 Satcom 計畫奠定良好的基礎,在我接手後又幫忙協助各種棘手的問題。謝謝碩士 班同屆的秉翰、信強、鼎傑和元鴻,和你們一同趕電路下線一同出遊的時光十分 懷念。元鴻更是博士班的同屆戰友,謝謝你一同為了實驗室而努力,平時研究上 的討論也讓我獲益良多。謝謝各位王老師實驗室的博士班同學吳依靜、王雲杉、 陳俊年,有了你們的幫忙才能讓實驗室順利運作。謝謝黃派的人豪、茗航、文傑、 杰穎、宜賢平時的幫忙,一起聊天打屁的時光相當愉快。還有謝謝電信所助理淑

i

貞、惠美平時在公務上的協助。也謝謝歷屆王派學弟妹在計畫上的幫助、處理雜 事以及幫助我實現研究上的想法。

能夠順利取得博士學位,最感謝爸爸、媽媽和姊姊的照顧。因為有你們的全力支持與鼓勵使我可以無後顧之憂的專注在研究上並完成博士論文。再次感謝在完成論文上幫助我的人們。

毓軒 2018.2

## 中文摘要

本論文主要分為兩部分,分別是毫米波寬頻除頻器和毫米波低相位移和振幅誤差之相移器。

第一部分是有關毫米波寬頻除頻器的研究。除頻器是鎖相迴路中的關鍵電路 之一,在毫米波頻段的米勒除頻器(Miller frequency divider)和注入鎖定式除頻器 (Injection-locked frequency divider)廣泛的被使用,然而和低頻率的除頻器相比頻寬 受到相當大的限制,因此本論文提出兩個方法,用來改善兩種毫米波除頻器的頻 寬。第一個除頻器是操作在 60GHz 且使用 65 奈米 CMOS 製程製作的米勒除頻器。 此除頻器使用了弱反轉區(weak inversion region)偏壓的混頻器使其能達到 57%的 鎖定比例頻寬(35.7 至 64.2 GHz),而且功耗僅 1.6 毫瓦。第二個除頻器是使用分裂 式變壓器耦合振盪器(split transformer-coupled oscillator)的注入鎖定式除頻器。使用 了此架構的注入鎖定式除頻器可以增加操作頻率和鎖定頻寬且不會增加額外晶片 面積及功率消耗。此注入鎖定式除頻器在不需要額外調控機制下達到 25.4%的鎖定 比例頻寬(75.1 至 97 GHz),且在 0.7V 供給電壓下有 2.45 毫瓦的功率消耗。

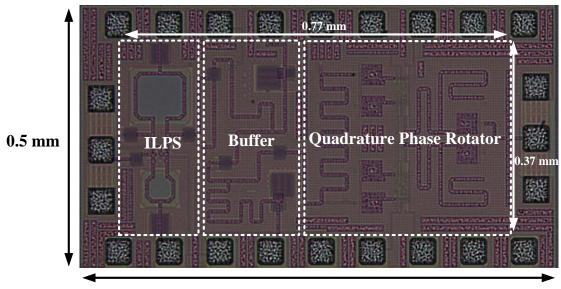

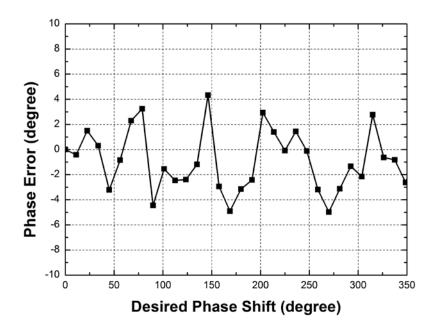

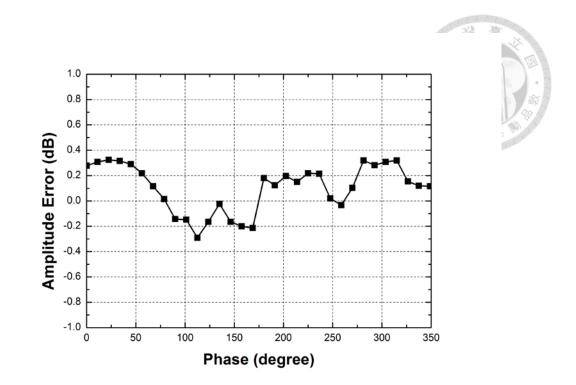

第二部分是有關應用在 60GHz 相位陣列的毫米波低相位移和振幅誤差之相移 器設計。相移器為相位陣列(phased array)系統中的關鍵元件,本論文中,設計了一 種低相位移和振幅誤差的四相位旋轉器由四相位產生器和相位選擇器所組成,用 以搭配射頻(RF)端和本地振盪源(LO)端相移器,使這兩個相移器皆能達到 360 度的 相移而且具有低相位移和振幅誤差的特性。射頻端相移器是基於開關式相移器所 設計,是全被動的架構且達到四位元的數位式控制。此相移器最大均方根振幅誤 差為 0.5dB,最大的均方根相位誤差為 5 度。另一個本地震盪源端相移器使採用注入鎖定式架構,此相移器達最大震幅誤差為±0.3 dB,最大相為誤差為 5 度。具有-10 B dBm 的輸出功率和 18 毫瓦的功率消耗。

關鍵字:互補式金氧半場效電金體、除頻器、變壓器、振盪器、注入鎖定、相移

器

## ABSTRACT

This dissertation consists of two main parts, the first part is design of wide bandwidth millimeter-wave (MMW) frequency divider, and the second part is about 60 GHz phase shifter with low phase and amplitude error.

In the first part, two MMW frequency dividers for MMW PLL are presented. The first frequency divider is 60 GHz Miller divider demonstrated in 65 nm CMOS. The Miller divider achieves 57% input locking range from 35.7 to 64.2 GHz with power consumption of 1.6 mW owing to using weak inversion bias mixer. The second frequency divider is a W-band injection-locked frequency divider (ILFD) fabricated in 90 nm CMOS, The STCO (split transformer-coupled oscillator) technique is proposed and utilized in ILFD and the operation frequency and locking range of the proposed ILFD can be increased without extra chip area and power consumption. The input locking range is 25.4% from 75.1 to 97 GHz at 0-dBm input power without any frequency tuning mechanism. The dc power consumption is 2.45 mW with a 0.7-V supply voltage.

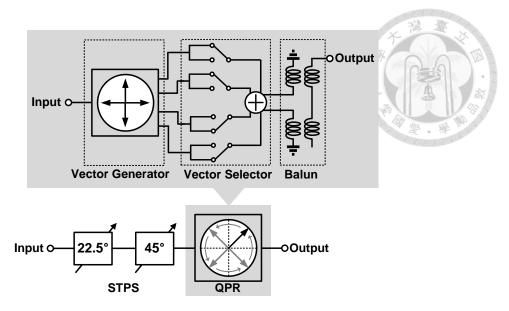

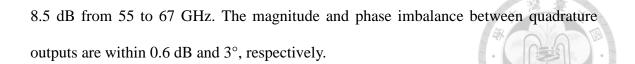

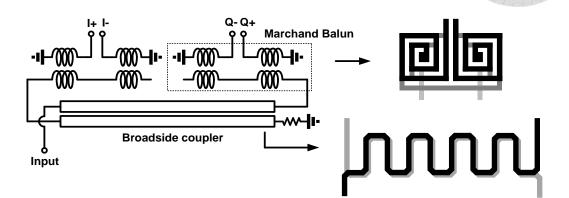

The second part is about phase shifter design for 60 GHz phased array system. A RF phase shifter and a LO phase shifter are presented and fabricated in 90 nm CMOS. The quadrature phase rotator (QPR) included vector generator and vector selector is proposed and applied in both phase shifter to achieve 360° phase shift with low phase and amplitude error. The proposed RF phase shifter based on STPS (switch type phase shifter) is all passive and fully digital control with 4 bit resolution. It demonstrates the maximum RMS amplitude error of 0.5 dB and phase error of 5°. Another proposed LO phase shifter based on ILPS (injection-locked phase shifter) exhibits the maximum am-

plitude error of  $\pm 0.3$  dB and phase error of 5°. The output power of the proposed LO phase shifter is -10 dBm with 18 mW dc consumption.

Index Terms - CMOS, frequency divider, oscillator, phased array, phase shifter.

## **CONTENTS**

|           |        | CONTENTS                                        | A COLONE            |

|-----------|--------|-------------------------------------------------|---------------------|

| 誌謝        |        |                                                 |                     |

| 中文摘要      |        |                                                 | iii                 |

| ABSTRA    | СТ     |                                                 | v                   |

| CONTEN    | TS     |                                                 | vii                 |

| LIST OF   | FIGURI | ES                                              | X                   |

| LIST OF ' | TABLE  | S                                               | XV                  |

| Chapter 1 | 1 Int  | troduction                                      |                     |

| 1.1       | Back   | ground and Motivation                           | 1                   |

| 1.2       | Litera | ature Survey                                    |                     |

|           | 1.2.1  | MMW frequency dividers                          |                     |

|           | 1.2.2  | MMW phase shifters                              | 6                   |

| 1.3       | Contr  | ributions                                       | 9                   |

| 1.4       | Disse  | ertation Organization                           |                     |

| Chapter 2 | 2 Mi   | illimeter-wave Frequency Divider Design         |                     |

| 2.1       | Over   | view of Frequency Divider                       |                     |

|           | 2.1.1  | Static Frequency Divider [6], [7]               |                     |

|           | 2.1.2  | Miller Frequency Divider [34], [35]             |                     |

|           | 2.1.3  | Injection-Locked Frequency Divider [36], [37]   |                     |

| 2.2       | 35.7-  | -64.2 GHz low power Miller Divider with Weak In | version Mixer in 65 |

|           | nm C   | MOS                                             |                     |

|           | 2.2.1  | Introduction of MMW Miller Divider              |                     |

|           | 2.2.2  | Circuit Design                                  |                     |

|         | 2.2   | 2.2.1 Weak Inversion Biasing mixer          |          |

|---------|-------|---------------------------------------------|----------|

|         | 2.2   | 2.2.2 Bandwidth of Miller Divider with BPF  |          |

|         | 2.2   | 2.2.3 Proposed Miller Divider               |          |

|         | 2.2.3 | Measurement Results                         |          |

|         | 2.2.4 | Discussion                                  |          |

| 2.3     | W-ba  | and Injection-Locked Frequency Divider Usin | ng Split |

|         | Trans | sformer-Coupled Oscillator Technique        |          |

|         | 2.3.1 | Introduction of MMW ILFD                    |          |

|         | 2.3.2 | Split Transformer-Coupled Oscillator        |          |

|         | 2.3   | 3.2.1 Oscillation Frequency                 |          |

|         | 2.3   | 3.2.2 Oscillation Condition                 |          |

|         | 2.3.3 | Analysis of ILFD                            |          |

|         | 2.3   | 3.3.1 Locking Range Analysis                |          |

|         | 2.3   | 3.3.2 Injection Transistor                  |          |

|         | 2.3.4 | Circuit Design                              |          |

|         | 2.3.5 | Measurement Results                         | 59       |

| 2.4     | Sum   | mary                                        |          |

| Chapter | 3 Mi  | illimeter-wave Phase Shifter Design         |          |

| 3.1     | Intro | duction of Phased Array [52], [53]          | 67       |

| 3.2     | Phase | ed Array Architectures                      | 68       |

| 3.3     | Over  | view of Phase Shifter                       | 71       |

|         | 3.3.1 | Transmission Line Phase Shifter [16]        |          |

|         | 3.3.2 | Reflection Type Phase Shifter [17]          |          |

|         | 3.3.3 | Vector Sum Phase Shifter [21]viii           |          |

|           | 3.3.4  | Switch Type Phase Shifter [25]                      |

|-----------|--------|-----------------------------------------------------|

|           | 3.3.5  | Injection-Locked Phase Shifter [30]75               |

| 3.4       | Four   | Bit RF Phase Shifter for 60-GHz RF Phased Array     |

|           | 3.4.1  | Introduction                                        |

|           | 3.4.2  | Architecture                                        |

|           | 3.4.3  | Switch Type Phase Shifter                           |

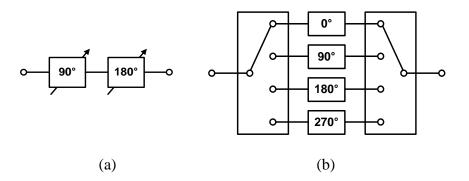

|           | 3.4.4  | Quadrature Phase Rotator (QPR)                      |

|           | 3.4    | .4.1 Vector Generator                               |

|           | 3.4    | .4.2 Vector Selector                                |

|           | 3.4.5  | Measurement Results                                 |

| 3.5       | Inject | ion-Locked Phase Shifter for 60-GHz LO Phased Array |

|           | 3.5.1  | Introduction                                        |

|           | 3.5.2  | Phase shift of ILPS                                 |

|           | 3.5.3  | Circuit Design                                      |

|           | 3.5.4  | Measurement Results                                 |

| 3.6       | Sumn   | nary                                                |

| Chapter 4 | 4 Co   | nclusion                                            |

| Reference | s      |                                                     |

|           |        |                                                     |

# LIST OF FIGURES

|            | LIST OF FIGURES                                                               |

|------------|-------------------------------------------------------------------------------|

| Fig. 1.1.  | The frequency allocation for MMW application1                                 |

| Fig. 1.2.  | Block diagram of conventional PLL                                             |

| Fig. 2.1.  | (a) Static frequency divider, and (b) its time domain waveform13              |

| Fig. 2.2.  | D-latch of current mode logic (CML)13                                         |

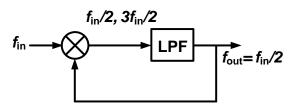

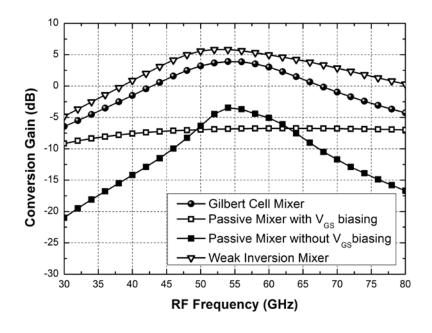

| Fig. 2.3.  | The model of Miller frequency divider15                                       |

| Fig. 2.4.  | Bipolar Miller divider                                                        |

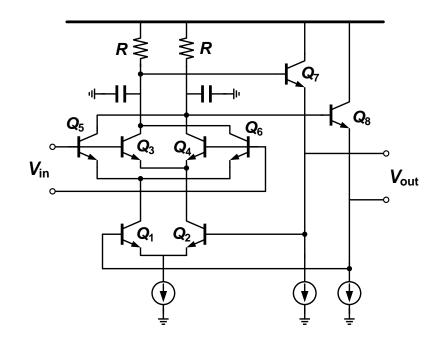

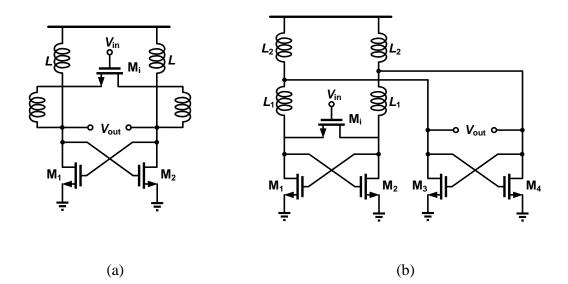

| Fig. 2.5.  | (a) RF-port feedback Miller divider. (b) LO-port feedback Miller divider16    |

| Fig. 2.6.  | Oscillator under injection locking                                            |

| Fig. 2.7.  | (a) Conventional ILFD. (b) Equivalent circuit                                 |

| Fig. 2.8.  | Modified ILFD with (a) shunt peaking inductor (b) direct injection20          |

| Fig. 2.9.  | (a) Block diagram of Miller divider, (b) conventional Gilbert cell mixer, (c) |

|            | passive mixer, and (d) weak inversion biasing mixer23                         |

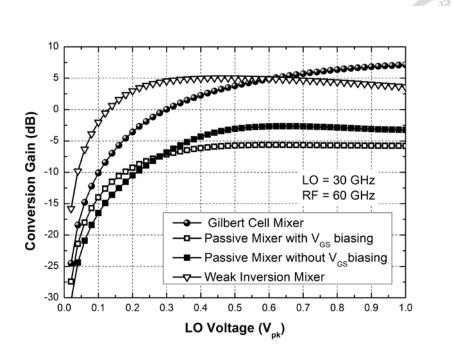

| Fig. 2.10. | Simulated (a) conversion gain versus LO voltage, and (b) conversion gain      |

|            | versus input frequency of each mixers                                         |

| Fig. 2.11. | Miller divider with BPF as RLC tank27                                         |

| Fig. 2.12. | Proposed Miller divider based on weak inversion mixer                         |

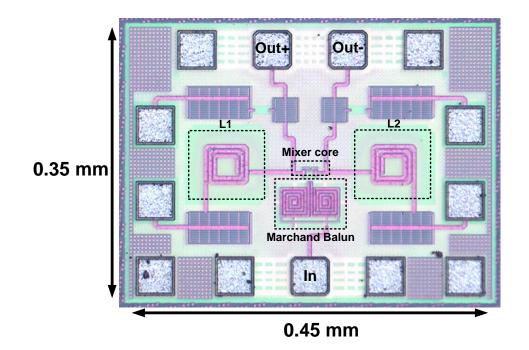

| Fig. 2.13. | Chip photo of proposed Miller divider                                         |

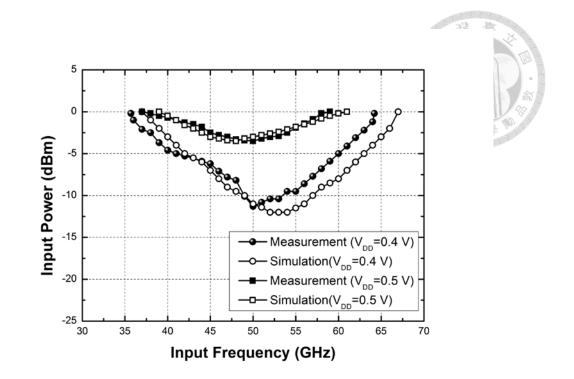

| Fig. 2.14. | Simulated and measured sensitivity curve of proposed Miller divider31         |

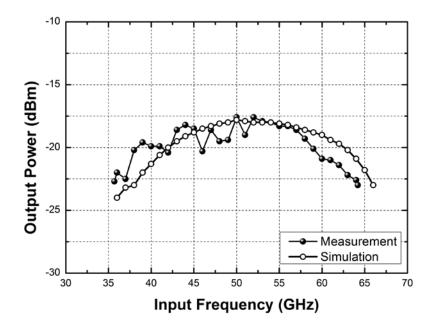

| Fig. 2.15. | Simulated and measured output power of proposed Miller divider at             |

|            | injection power of 0 dBm                                                      |

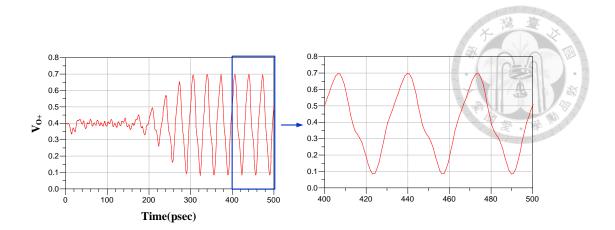

| Fig. 2.16. | Simulated transient response of $V_{0+}$ with 0 dBm input power               |

| Fig. 2.17. | ILFD with (a) inductor peaking technique and (b) distributed LC structure 36  |

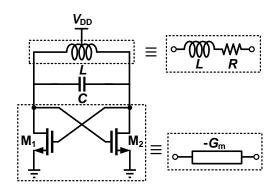

| Fig. 2.18. | Conventional cross-coupled oscillator                                                  |

|------------|----------------------------------------------------------------------------------------|

| Fig. 2.19. | Proposed split transformer coupled oscillator (STCO)                                   |

| Fig. 2.20. | Equivalent circuit of STCO42                                                           |

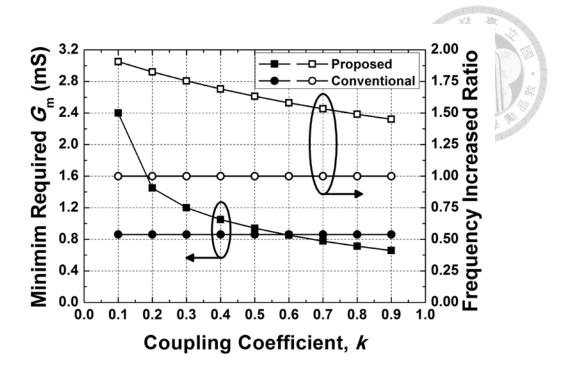

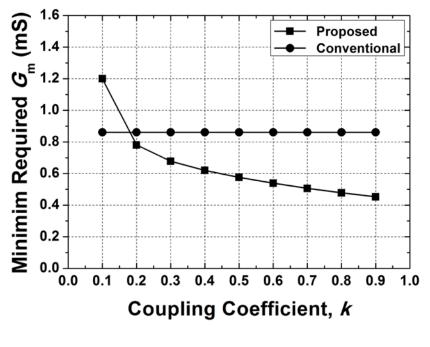

| Fig. 2.21. | Calculated (a) Minimum required $G_m$ and frequency increasing ratio versus            |

|            | transformer coupling coefficient, $k$ , and (b) minimum required Gm versus             |

|            | transformer coupling coefficient under the same oscillation frequency43                |

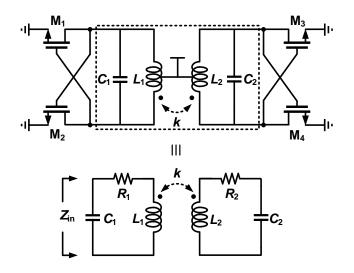

| Fig. 2.22. | (a) ILFD with direct injection and (b) its equivalent circuit model45                  |

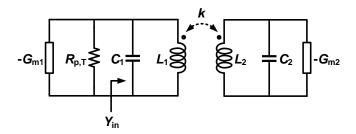

| Fig. 2.23. | The proposed ILFD realized by STCO and (b) its equivalent circuit model.50             |

| Fig. 2.24. | Split transformer and its equivalent circuit model                                     |

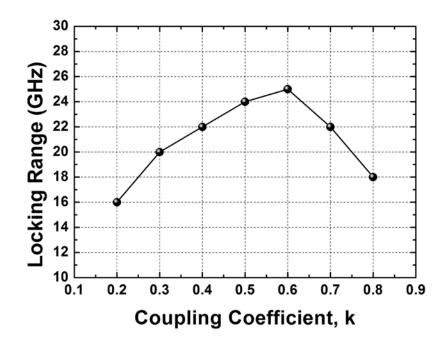

| Fig. 2.25. | Simulated locking range versus different coupling coefficient, k                       |

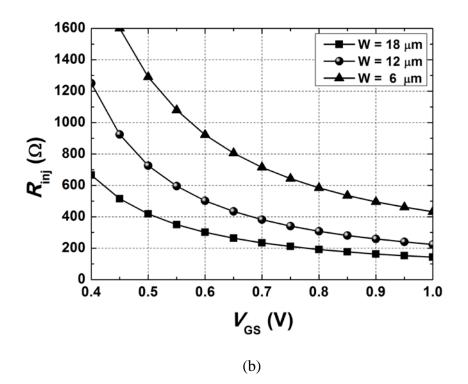

| Fig. 2.26. | Simulated (a) $\alpha_{inj}$ and (b) $R_{inj}$ of injection transistor versus $V_{GS}$ |

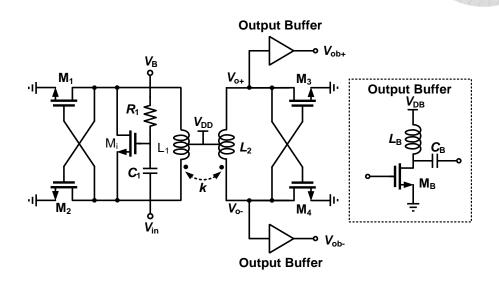

| Fig. 2.27. | The complete circuit schematic of proposed ILFD55                                      |

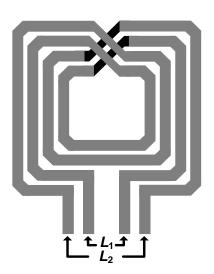

| Fig. 2.28. | Layout of transformer                                                                  |

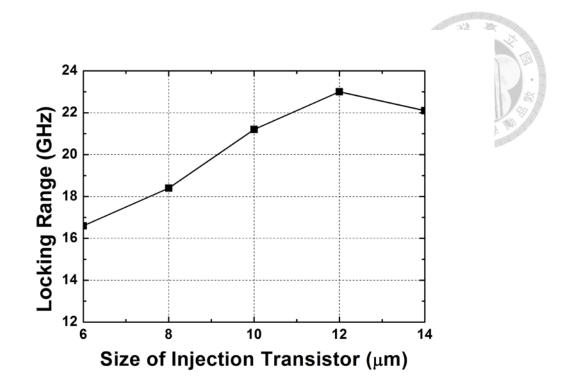

| Fig. 2.29. | Simulated locking range of proposed ILFD versus size of injection transistor,          |

|            | with $V_{\rm GS} = 0.6$ V                                                              |

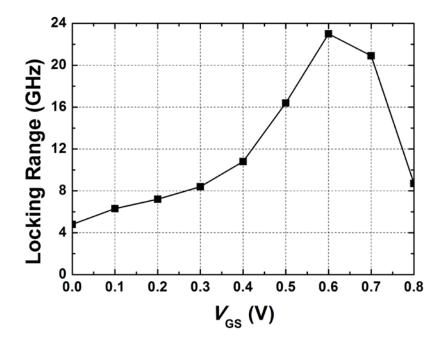

| Fig. 2.30. | Simulated locking range of proposed ILFD versus $V_{GS}$ of injection transistor,      |

|            | with injection transistor size of 12 $\mu$ m                                           |

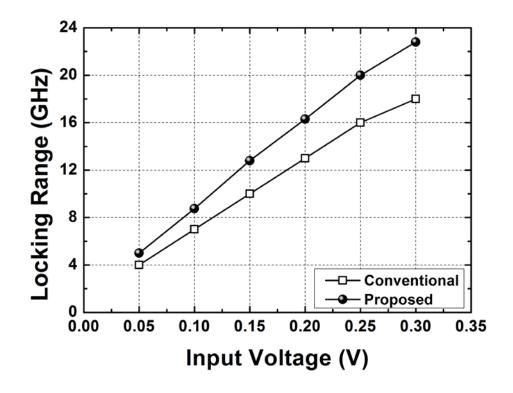

| Fig. 2.31. | Simulated locking range of the conventional and proposed ILFD58                        |

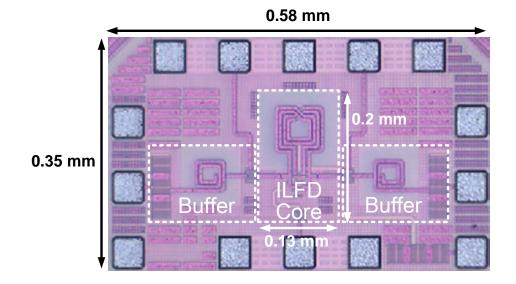

| Fig. 2.32. | Chip photo of proposed ILFD                                                            |

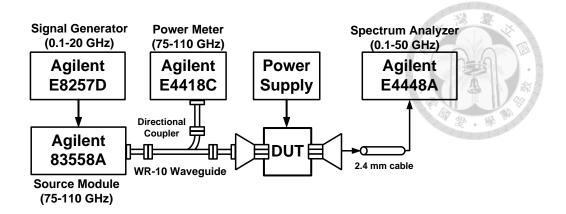

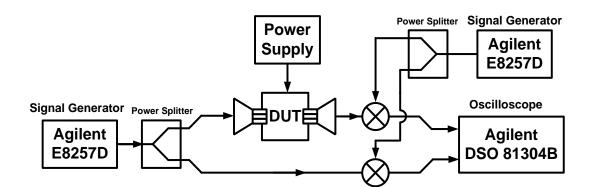

| Fig. 2.33. | The measurement setup for proposed ILFD60                                              |

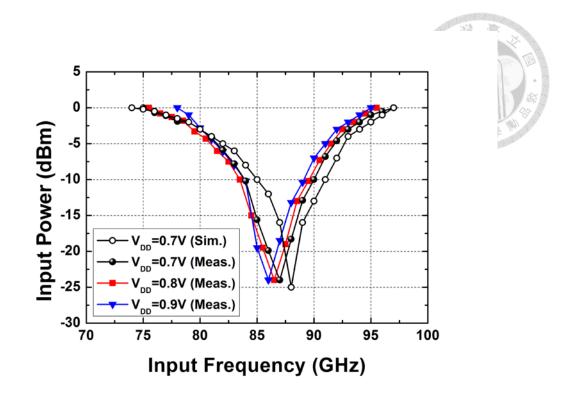

| Fig. 2.34. | Measured and simulated input sensitivity curves of proposed ILFD with                  |

|            | different supply voltage61                                                             |

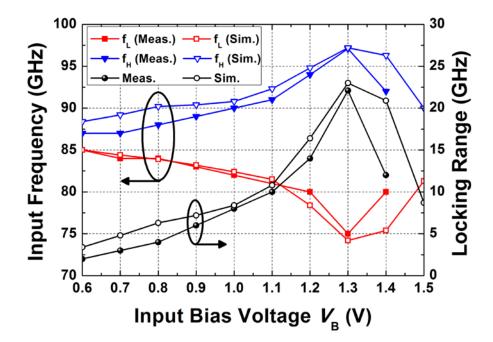

| Fig. 2.35. | Measured and simulated locking range versus input bias voltage $V_{\rm B}$ 61          |

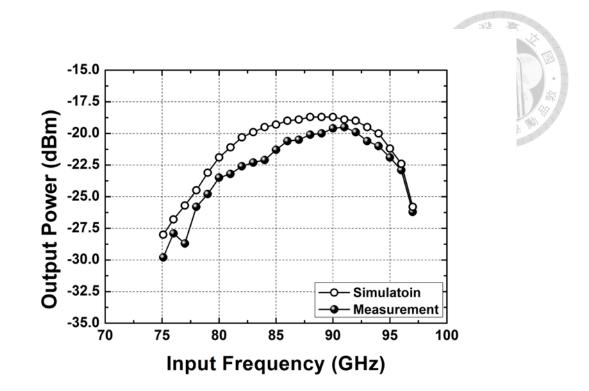

| Fig. 2.36.   | Measured and simulated output power of proposed ILFD62                            |

|--------------|-----------------------------------------------------------------------------------|

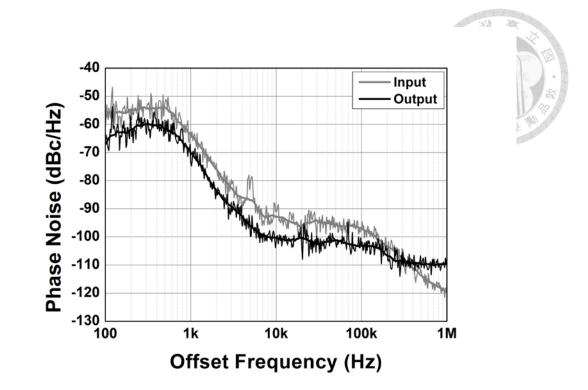

| Fig. 2.39.   | Measured phase noise of input signal and output signal                            |

| Fig. 2.38.   | Designed 50 GHz Miller divider as next stage divider in 90 nm CMOS65              |

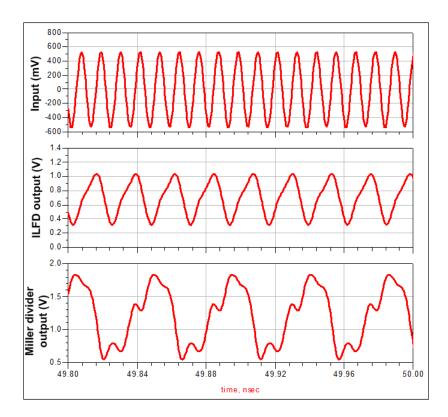

| Fig. 2.39. S | Simulated input and each divider output waveform                                  |

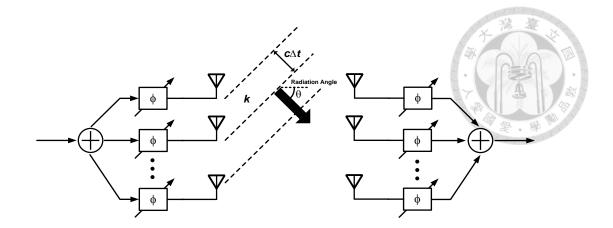

| Fig. 3.1.    | <i>N</i> -element phased array transmitter and receiver                           |

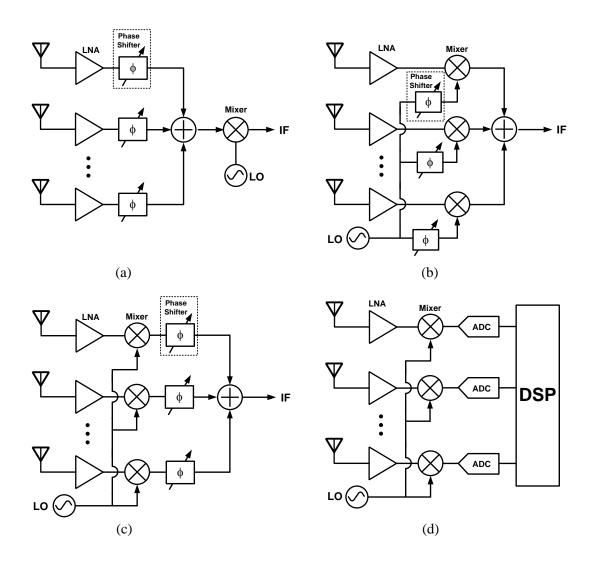

| Fig. 3.2.    | Different phased array architecture: (a) RF phase shifting. (b) LO phase          |

|              | shifting. (c) IF phase shifting. (d) Digital phase shifting69                     |

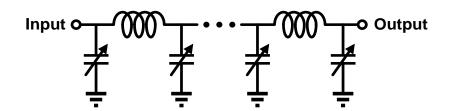

| Fig. 3.3.    | Transmission line phase shifter [16]71                                            |

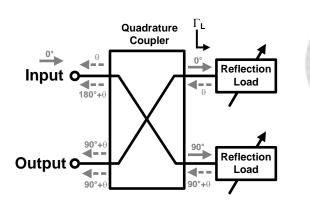

| Fig. 3.4.    | Reflection type phase shifter [17]73                                              |

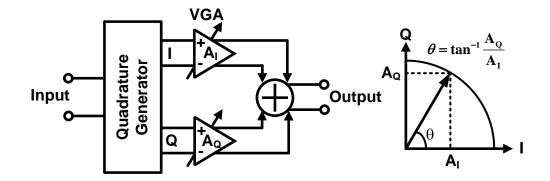

| Fig. 3.5.    | Vector sum phase shifter [21]73                                                   |

| Fig. 3.6.    | (a) The switch type phase shifter [25], and (b) multi-stage switch type phase     |

|              | shifter75                                                                         |

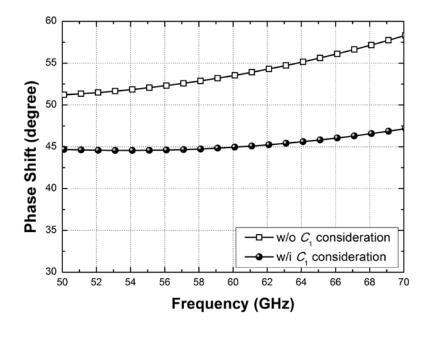

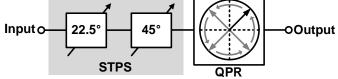

| Fig. 3.7.    | Block diagram of proposed 4 bit RF phase shifter77                                |

| Fig. 3.8.    | (a) $\pi$ -type LPF-based STPS. (b) Equivalent circuit when $V_c = 0$ V. (c)      |

|              | Equivalent circuit when $V_c = 1.2$ V                                             |

| Fig. 3.9.    | (a) T-type LPF-based STPS. (b) Equivalent circuit when $V_c = 0$ V. (c)           |

|              | Equivalent circuit when $V_c = 1.2$ V. (d) Modified equivalent circuit when $V_c$ |

|              | = 0 V                                                                             |

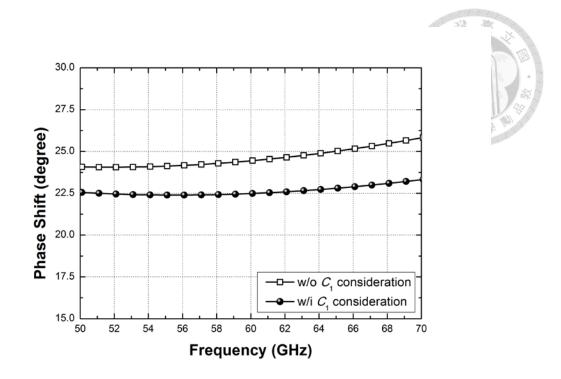

| Fig. 3.10.   | Simulated phase shift of (a) 22.5° and (b) 45° STPS with and without $C_1$        |

|              | consideration                                                                     |

| Fig. 3.11.   | Schematic of 2 stages STPS                                                        |

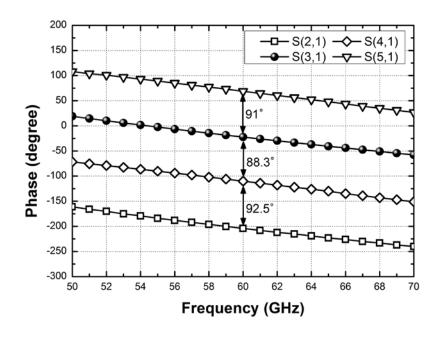

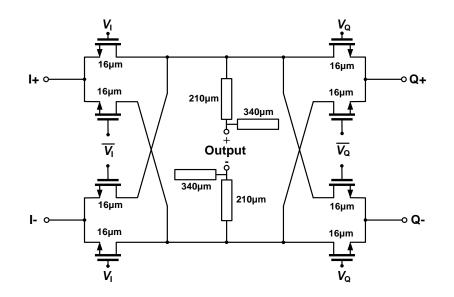

| Fig. 3.12.   | Block diagram of (a) series STPS and (b) parallel STPS85                          |

| Fig. 3.13.   | Proposed quadrature phase rotator (QPR)                                           |

| Fig. 3.14. | Schematic of vector generator                                                                         |

|------------|-------------------------------------------------------------------------------------------------------|

| Fig. 3.15. | 3D view of vector generator in full EM simulator                                                      |

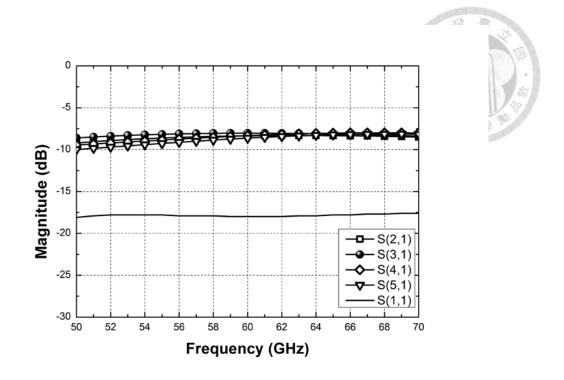

| Fig. 3.16. | Simulated (a) magnitude and (b) phase response of the vector generator88                              |

| Fig. 3.17. | Schematic of proposed vector selector                                                                 |

| Fig. 3.18. | Equivalent circuit of vector selector at 4 phase selection (a) first phase, (b)                       |

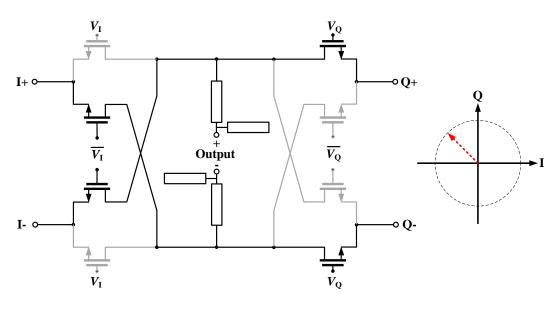

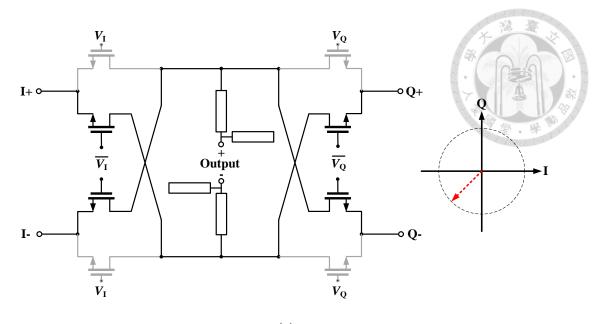

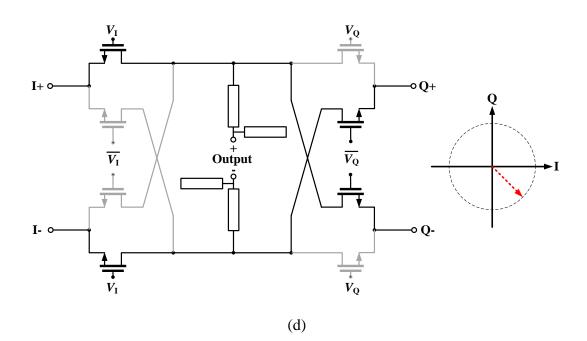

|            | second phase, (c) third phase, and (d) fourth phase91                                                 |

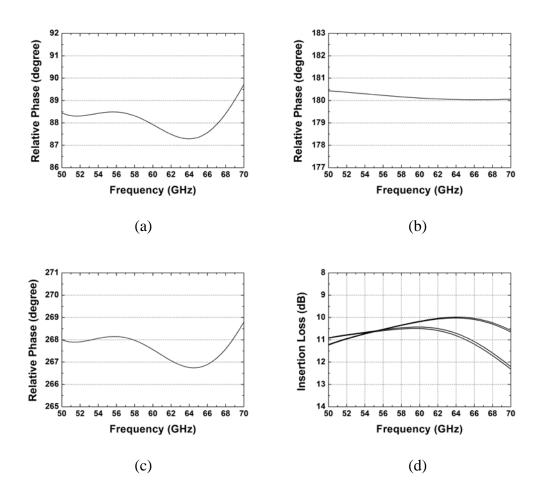

| Fig. 3.19. | Simulated relative phase of QPR: (a) $90^{\circ}$ (b) $180^{\circ}$ (c) $270^{\circ}$ . (d) Simulated |

|            | insertion loss of QPR92                                                                               |

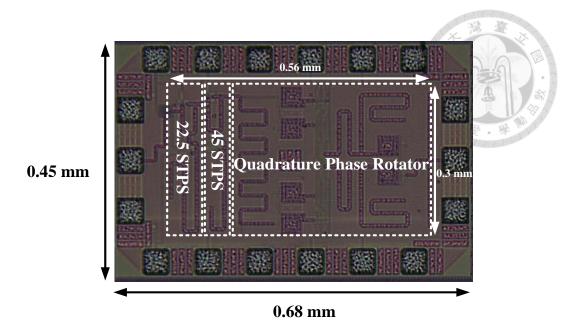

| Fig. 3.20. | Chip photo of 4 bit passive RF phase shifter94                                                        |

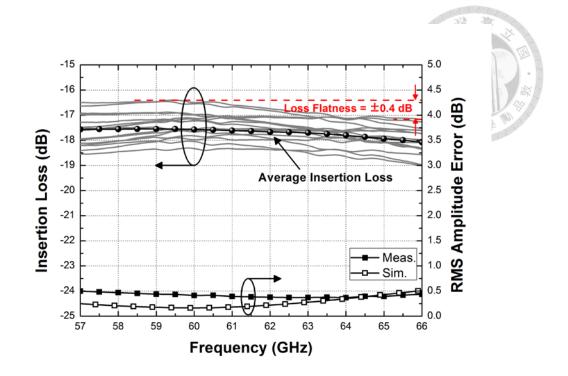

| Fig. 3.21. | Measured insertion loss $(S_{21})$ of 16 phase states and RMS amplitude error.95                      |

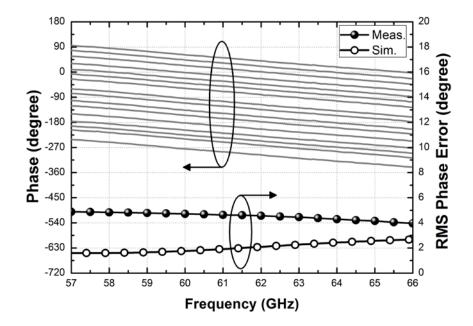

| Fig. 3.22. | Measured phase of 16 phase states and RMS phase error                                                 |

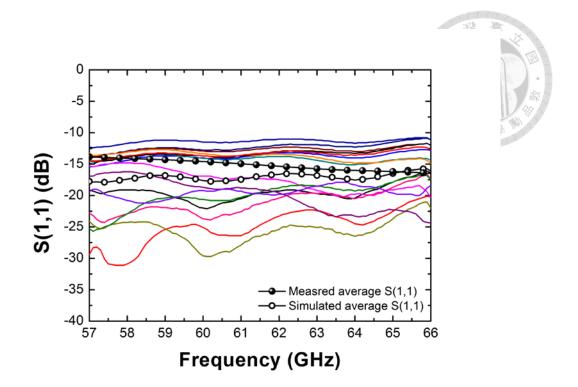

| Fig. 3.23. | Measured input return loss of 16 phase states96                                                       |

| Fig. 3.24. | Measured output return loss of 16 phase states                                                        |

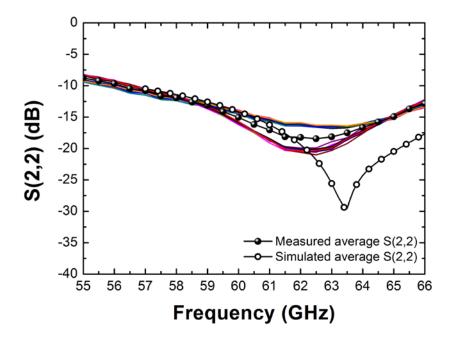

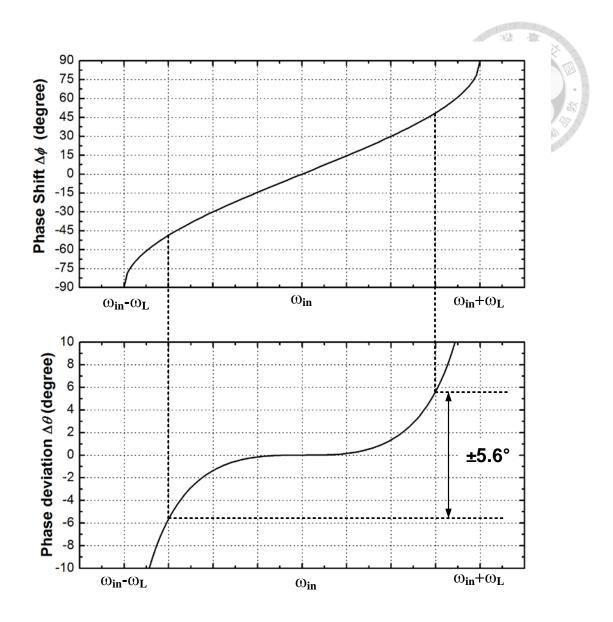

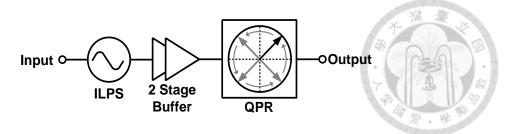

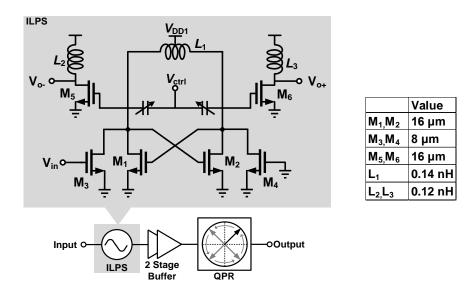

| Fig. 3.25. | Plot of the phase shift and phase deviation versus $\omega_{in}$                                      |

| Fig. 3.26. | Block diagram of proposed LO phase shifter                                                            |

| Fig. 3.27. | Schematic of ILPS                                                                                     |

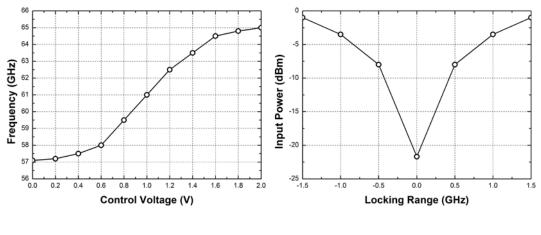

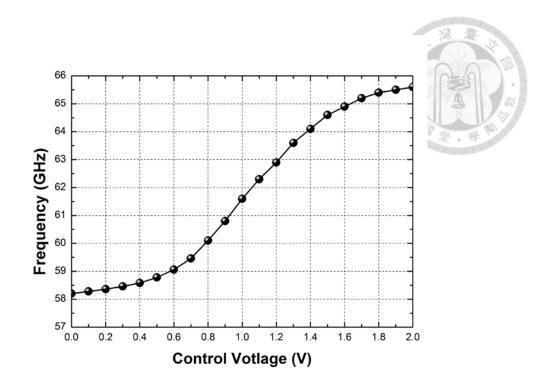

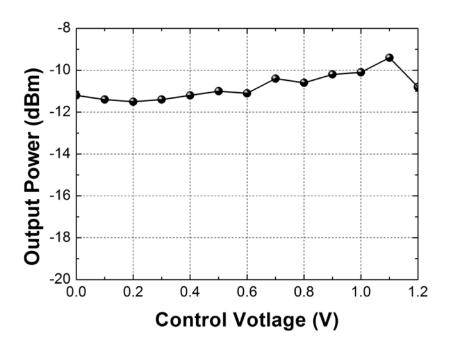

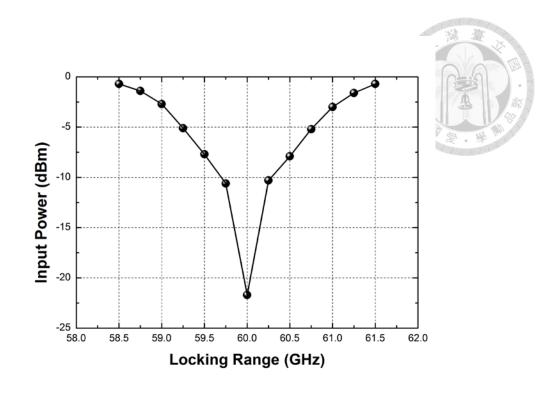

| Fig. 3.28. | (a) Simulated free-running tuning range of ILO. (b) Simultedd locking range                           |

|            | as ILO locked by input signal                                                                         |

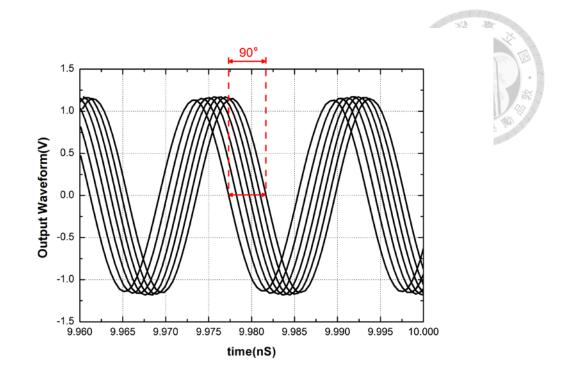

| Fig. 3.29. | Simulated output waveform of ILPS103                                                                  |

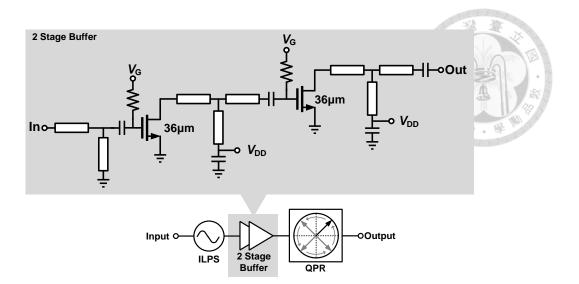

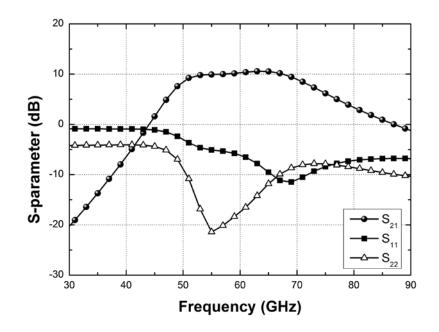

| Fig. 3.30. | Schematic of buffer amplifier                                                                         |

| Fig. 3.31. | Simulated S-parameter of buffer amplifier104                                                          |

| Fig. 3.32. | Chip photo of proposed LO phase shifter105                                                            |

|            | 1010101010                                                               |

|------------|--------------------------------------------------------------------------|

| Fig. 3.33. | (a) Measured free-running tuning range of ILO. (b) Measured output power |

|            | of ILO(c) Measured locking range as ILO locked by input signal107        |

| Fig. 3.34. | Test setup for phase shift measurement                                   |

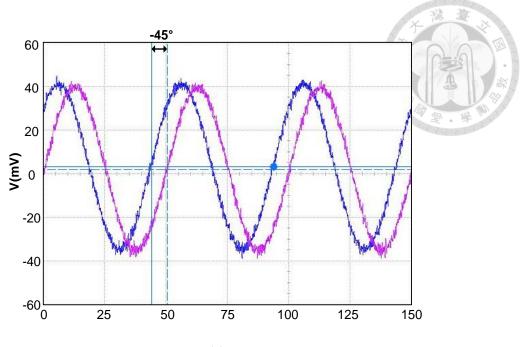

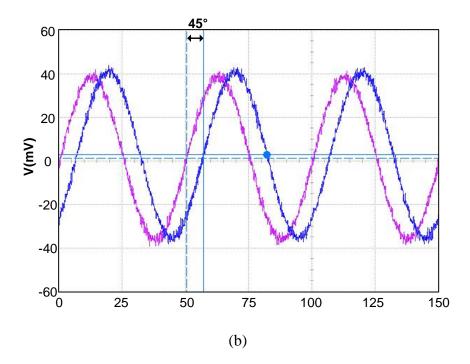

| Fig. 3.35. | Measured output waveform of proposed ILPS. (a) -45°. (b) 45°109          |

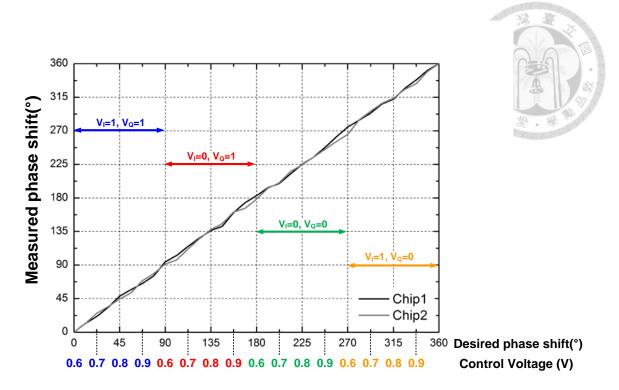

| Fig. 3.36. | Measured phase shift of proposed ILPS110                                 |

| Fig. 3.37. | Measured phase error of proposed ILPS                                    |

| Fig. 3.38. | Measured amplitude error of proposed ILPS111                             |

# LIST OF TABLES

|            | LIST OF TABLES                                                  |

|------------|-----------------------------------------------------------------|

| Table 1.1. | Summary of reported MMW frequency divider                       |

| Table 1.2. | Summary of reported MMW phase shifter                           |

| Table 2.1. | Comparison of Published MMW Miller dividers                     |

| Table 2.2. | Comparison of Published MMW ILFDs and proposed Miller divider32 |

| Table 2.3. | Design parameters of proposed ILFD55                            |

| Table 2.4. | Comparison of published millimeter wave frequency dividers64    |

| Table 3.1. | Comparison of 4 type phased array architecture70                |

| Table 3.2. | Calculated design parameters for STPS84                         |

| Table 3.3. | Comparison of published MMW RF phase shifters97                 |

| Table 3.4. | Comparison of published MMW LO phase shifters                   |

## **Chapter 1** Introduction

### **1.1 Background and Motivation**

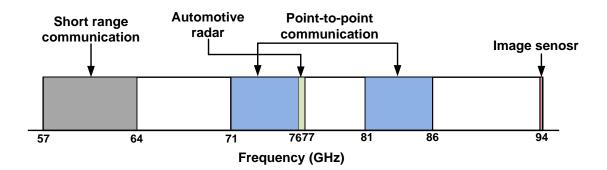

As modern CMOS technology continuous to scale down, millimeter wave (MMW) wireless systems have drawn lots of attention. Recently, MMW frequency band have been allocated for different wireless application, as shown in Fig. 1.1. The 57 to 64 GHz unlicensed band have been released for short range communication [1]. According to IEEE 802.15.3c standard [2], the band around 60 GHz can be divided into four 2.16 GHz channels. It is capable of achieving data rate of 3.5Gbps/Ch in QPSK modulation and 7 Gbps/ch in 16 QAM modulation. Besides, 71-76/81-86 GHz licensed band are reserved for point-to-point communication [3]. Total of 10 GHz bandwidth can be utilized in E-band for high capacity link. In addition to wireless communication application, 77 GHz and 94 GHz are planned for automotive anti-collision radar and image sensor, respectively [4]-[5].

Fig. 1.1. The frequency allocation for MMW application.

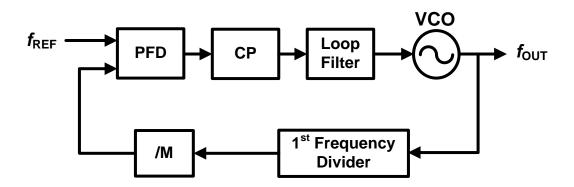

In MMW wireless system, the Phase lock loop (PLL) is a key building block to provide local oscillator source. Fig. 1.2 shows the block diagram conventional PLL which included a phase frequency detector (PFD), a charge pump (CP), a loop filter, a voltage-controlled oscillator (VCO) and frequency dividers. The most challenge components of MMW PLL are VCO and frequency divider. The VCO in CMOS process can operate in very high frequency, but frequency tuning range, phase noise, power consumption, and output power are still the design issue. On the other hand, the CMOS frequency divider such as Miller divider and injection-locked frequency divider (ILFD) can operate in MMW frequency easily. However, the bandwidth is narrow compared with frequency divider at low frequency. Besides, the bandwidth of frequency divider should be designed much wider than tuning range of VCO due to process-voltage-temperature (PVT) variation. In this dissertation, two wide bandwidth MMW frequency dividers with low power consumption are proposed for low power MMW PLL design.

Fig. 1.2. Block diagram of conventional PLL.

Since the free space loss in MMW frequency is tremendously higher than that in microwave frequency and the output power provided by power amplifier is lower, the radiation region is limited. Phased array system which is a multi-channel transceiver is developed to solve this problem. It can increase the output power and system sensitivity by combining the coherent signal in space. Also, the radiation beam can be steered by changing the phase in each channel. Phased array systems require phase shifter to control the phase in each channel path. However, there are several design challenges such as loss, phase error, amplitude error, and phase resolution. This dissertation proposes two architectures of phase shifter for two type of phased array system to solve these issues.

### **1.2 Literature Survey**

#### 1.2.1 MMW frequency dividers

In MMW PLL, the design of first-stage frequency divider is as critical as VCO since PLL require reliable tracking and lower power consumption. For MMW frequency, static frequency divider, Miller frequency divider, and ILFD are widely applied in MMW PLLs.

Static frequency divider has wide bandwidth performance. It can work at MMW frequency by using current mode logic (CML) topology. A wide bandwidth frequency divider demonstrates operation frequency from 5 to 66 GHz [6]. To reach higher frequency, another static frequency divider in W-band frequency has been presented [7]. However, the power consumption increases tremendously with increasing operation frequency. Also the bandwidth is constrained in high operation frequency. Miller divider is mixer-based frequency divider can operate at MMW frequency easily with moderate bandwidth and power consumption. Two Miller dividers operated in V-band have been reported [8], [9]. The two Miller dividers are applied the techniques of current bleeding

and transformer injection, respectively. The power consumption is much lower than static frequency divider. Nevertheless, the maximum operation frequency is still limit. Among all frequency divider, ILFD has the highest operation frequency and the lowest power consumption. Three ILFD have been demonstrated in V-band and W-band frequencies with quite low power consumption, but their bandwidth is narrower [10]-[12]. In order to enhance the operation bandwidth, the ILFD with dual-mixing technique has been proposed [13]. The locking range is improved significantly with additional power consumption. The other methods to improve the locking range without extra power consumption are distributed LC structure and inductor peaking technique [14], [15]. Both the methods require multiple inductors and result in large chip area.

Table 1.1 summarizes the comparison of reported MMW frequency divider. Although Miller dividers consume much lower power consumption than that of CML divider, the operation bandwidth is still limited. On the contrary, thanks to certain techniques proposed and applied in ILFD, the bandwidth is extend significantly. The ILFD shows the great potential for MMW PLL integration.

| _    |                 |          |                             |                    |                         |                        |                         | 018  |

|------|-----------------|----------|-----------------------------|--------------------|-------------------------|------------------------|-------------------------|------|

| Ref. | Process         | Topology | Input<br>Frequency<br>(GHz) | Bandwidth<br>(GHz) | Input<br>Power<br>(dBm) | V <sub>DD</sub><br>(V) | P <sub>DC</sub><br>(mW) | FOM  |

| [6]  | 90 nm<br>CMOS   | CML      | 5-66                        | 51<br>(171%)       | 0                       | 1.4                    | 44.6                    | 1.14 |

| [7]  | 65 nm<br>CMOS   | CML      | 76-94.4                     | 18.4<br>(21.6%)    | 0                       | 2.4                    | 64.9                    | 0.28 |

| [8]  | 0.13 μm<br>CMOS | Miller   | 56.5-72.2                   | 15.7<br>(24.4%)    | 0                       | 1                      | 4.65                    | 3.37 |

| [9]  | 0.13 μm<br>CMOS | Miller   | 57-72                       | 15<br>(23.2%)      | 0                       | 0.8                    | 5                       | 3    |

| [10] | 65 nm<br>CMOS   | ILFD     | 82-94.1                     | 12.1<br>(13.7%)    | 0                       | 0.56                   | 3.92                    | 3.09 |

| [11] | 0.13 μm<br>CMOS | ILFD     | 67.2-75.4                   | 8.2<br>(11.5%)     | 0                       | 1                      | 4.4                     | 1.86 |

| [12] | 90 nm<br>CMOS   | ILFD     | 85.5-96.2                   | 10.7<br>(11.7%)    | 0                       | 1.2                    | 3.5                     | 3.06 |

| [13] | 90 nm<br>CMOS   | ILFD     | 51-74                       | 23<br>(36.8%)      | 0                       | 0.5                    | 3                       | 7.67 |

| [14] | 65 nm<br>CMOS   | ILFD     | 107.9-128.<br>8             | 20.9<br>(17.7%)    | -2                      | 1.1                    | 6.27                    | 3.33 |

| [15] | 65 nm<br>CMOS   | ILFD     | 53.4-79.4                   | 26<br>(39.2)       | 0                       | `0.8                   | 2.9                     | 8.97 |

Table 1.1. Summary of reported MMW frequency divider

#### 1.2.2 MMW phase shifters

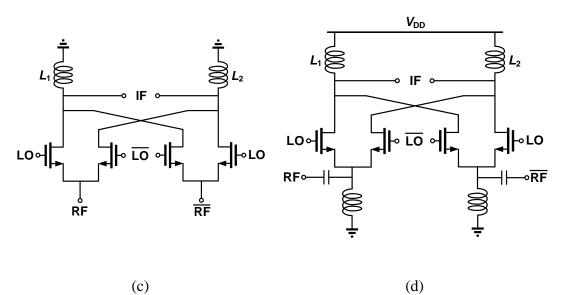

Several topologies of phase shifter have been utilized in phased array system. The transmission line phase shifter (TLPS) is simple way to achieve continuous phase shift but the phase shift range is narrow [16]. Wider phase shift can be obtained by adding more stages of TLPS, but insertion loss will be degraded. Therefore, TLPS is seldom used in MMW frequency. Another way to perform wider continuous phase shift is reflection type phase shifter (RTPS), but phase shift range is limited by reflection load [17]. The phase shift range can be enhanced by modifying reflection load. However, wider phase tuning cause higher reflective loss variation. Several MMW RTPSs have been published in silicon process [18]-[20]. Single RTPS can cover 180° phase shift but suffer from high loss variation [18]. Casacading multiple RTPSs can achieve similar phase shift and reduce the loss variation [19], [20]. To reach full 360° phase shift, vector sum phase shifter (VSPS) is proposed. This phase shifter provides continuous phase shift by synthesizing quadrature signals [21]. By adjusting each path signal gain level, the arbitrary phase shift can be obtained. Among all VSPS, quadrature phase generator is a key component to generate accurate quadrature signal. Quadrature all-pass filter (QAF) consisted of lumped inductors and capacitors is used as quadrature phase generator in VSPS [21],[22]. However, in MMW frequency, the bandwidth of QAF is limited. Owing to the operation frequency extended to MMW region, a few microwave passive component technique can implemented in CMOS process, such as 90° coupler and left hand transmission line. Those are applied in VSPS for quadrature signal generation and achieve good phase and amplitude accuracy [23], [24]. Nevertheless, VSPS require more building block which cause higher power consumption and larger chip area.

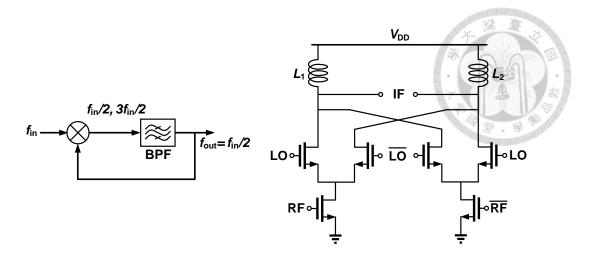

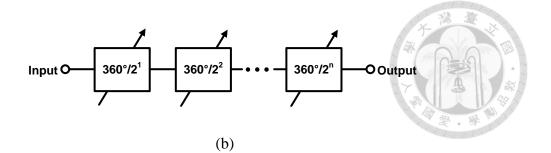

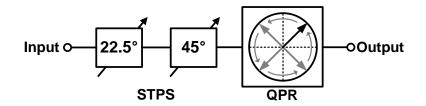

In addition to continuous tuning phase shifter, the discrete phase shift control can be achieved by switch type phase shifter (STPS) [25]. Phase shift in STPS can be controlled by digital signal without digital-to-analog converter (DAC). It is more convenient than other topology and save DC power of DAC. Traditional STPS is utilized switching low pass and high pass network to obtain certain phase shift. However, the chip size is larger due to low pass and high pass network. Also, the parasitic resistance of switch cause high loss. Two type of low pass filter (LPF) based STPS have been proposed to reduce the chip size and loss by reduce the passive component and number of switch [25], [26]. Nonetheless, both the above STPS cannot cover more than 90° phase shift. The great advantage of STPS is that *N*-bit digital control 360° phase shifter can be easily implemented by series connecting *N*-stage STPS [25]-[29].

Recently, injection-locked phenomenon has been used for achieving phase shift and it is suitable to use in LO path phased array [30] due to the low power consumption. However, the drawback is the narrow phase tuning range limited by injection-locked mechanism. Several injection-locked phase shifters (ILPSs) cascading with multiplier have been proposed to multiply phase shift tuning range [31]-[33].

Table 1.2 summarizes the performance of reported MMW phase shifter. All kind of phase shifters can be applied in phased array system depends on different system requirement. Among all phase shifter, Only STPS can work without dc power and extra DAC. Therefore, STPS is the better choice for large scale phased array transceiver.

|      | Tab             | le 1.2. Sum | nmary of       | reported       | MMW phase sh        | ifter 7           |                         |

|------|-----------------|-------------|----------------|----------------|---------------------|-------------------|-------------------------|

| Ref. | Process         | Topology    | Freq.<br>(GHz) | Phase<br>Range | Resolution          | Insertion<br>Loss | P <sub>DC</sub><br>(mW) |

| [18] | 0.13 μm<br>SiGe | RTPS        | 57-64          | 180            | Continuous          | 4.2-7.8           | 0                       |

| [19] | 65 nm<br>CMOS   | RTPS        | 55-65          | 180            | Continuous          | 5-8.3             | 0                       |

| [20] | 0.12 μm<br>SiGe | RTPS        | 57-66          | 200            | Continuous          | 6.3-8.2           | 0                       |

| [22] | 90 nm<br>CMOS   | VSPS        | 40-67          | 360            | 22.5<br>(Extra DAC) | 5-9               | 23                      |

| [23] | 90 nm<br>CMOS   | VSPS        | 57-64          | 360            | 22.5<br>(Extra DAC) | 3.4-7.2           | 34                      |

| [24] | 90 nm<br>CMOS   | VSPS        | 57-66          | 360            | 22.5<br>(Extra DAC) | 2.2-5             | 15.6                    |

| [27] | 90 nm<br>CMOS   | STPS        | 57-64          | 360            | 11.25               | 11.6-18           | 0                       |

| [28] | 0.13 μm<br>SiGe | STPS        | 67-82          | 360            | 22.5                | 15.5-23           | 0                       |

| [29] | 65 nm<br>CMOS   | STPS        | 75-85          | 360            | 22.5                | 22.9-27           | 0                       |

| [31] | 65 nm<br>CMOS   | ILPS        | 43-50          | ±90            | 22.5<br>(Extra DAC) | -                 | 85*                     |

| [32] | 90 nm<br>SiGe   | ILPS        | 57-61          | ±80            | Continuous          | -                 | 117**                   |

| [33] | 90 nm<br>SiGe   | ILPS        | 62-73          | ±300           | Continuous          | -                 | 236*                    |

\* 4 element arrays

\*\* 2 element arrays

### **1.3 Contributions**

In this dissertation, two MMW frequency dividers were demonstrated with wide locking range for MMW low power PLL applications. Besides, two MMW phase shifters with low phase and amplitude error are presented for 60 GHz phased array. The major contributions in this dissertation are described briefly as follows.

First, a 35.7 to 64.2 GHz Miller divider with weak inversion mixer is presented. Conventional Miller divider using Gilbert cell mixer have narrow bandwidth. Even though a few techniques are proposed, the fractional bandwidth is smaller than 25%. To enhance the locking range of divider and save power consumption, a Miller divider based on weak inversion mixer is proposed. Unlike conventional Miller divider, the weak inversion mixer is applied in proposed Miller divider due to its low dc power and low LO driving power. Much wider bandwidth and smaller dc power can be obtained in proposed Miller divider. The proposed Miller divider is implemented in 65 nm CMOS and exhibits 57% locking range from 35.7 to 64.2 GHz at an input power of 0 dBm while consuming 1.6-mW dc power at 0.4 V supply voltage. Compared to the previously reported CMOS MMW frequency dividers, the proposed divider achieves the widest fractional bandwidth without any frequency tuning mechanism.

For higher frequency operation, a W-band injection-locked frequency divider (ILFD) with low power and wide locking range is demonstrated. Split transformer-coupled oscillator (STCO) technique is proposed to enhance the operation frequency and relieve the oscillation condition. Besides, the STCO applied in ILFD can enhance the locking range without increasing chip area and dc power consumption. On the other hand, the optimum bias and the size of injection transistor are chosen to achieve wider locking range. The detail analysis and design procedure of proposed ILFD are described in this dissertation. The proposed ILFD is implemented in 90-nm CMOS and exhibits 25.4% locking range from 75.1 to 99 GHz at an input power of 0 dBm without any tuning mechanism. The core dc power consumption is 2.45 mW with a supply voltage of 0.7 V and the core chip size is  $0.13 \times 0.2 \text{ mm}^2$ .

In second part, two 60 GHz phase shifters with low phase and amplitude error for the beam-forming systems are presented. Among different phased array architectures, RF and LO phased array are widely used in wireless application. Therefore, the proposed phase shifters are designed for RF and LO phased arrays, respectively. The quadrature phase rotator (QPR) which consists of a vector generator and a vector selector is used in two phase shifters to achieve 360° phase shift. The QPR also contribute low phase and amplitude error with small chip size. Two phase shifters are designed and fabricated in 90-nm CMOS process. The first phase shifter is RF phase shifter used LPF based STPS to obtain zero power consumption and full digital control. The modified design equations are derived to acquire more accurate phase response. Based on the derived equations, this RF phase shifter realizes 22.5° resolution and 360° phase range with the quadrature phase rotator (QPR). The measured insertion loss is 17.5 dB with loss flatness of  $\pm 0.4$ dB, and the measured RMS phase and amplitude error are  $< 5^{\circ}$  and 0.5 dB, respectively, from 57-66 GHz. The second phase shifter is LO phase shifter based on ILPS for low power and high linear phase tuning range. Different from previous reported works [31]-[33], the proposed LO phase shifter composed of an ILPS cascade with QPR. With the QPR, the ILPS overcomes the weakness of low phase tuning range. The measured amplitude variation is within 0.3 dB, and maximum phase error is 5° at 60 GHz.

### **1.4 Dissertation Organization**

This dissertation is organized as follow:

In chapter 2, the brief introduction of different kinds of frequency divider operated in MMW frequency is given first. Then, section 2.2 present a 60 GHz Miller divider with weak inversion mixer in 65 nm CMOS. In section 2.3, a wide locking range ILFD using split transformer coupled oscillator (STCO) is proposed. The detail analysis of proposed STCO and ILFD are included in this section. The summary of two MMW frequency dividers is shown in the end of this chapter.

In chapter 3, at first, the brief introduction of phased array system and different phased array architecture are described. Also different types of phase shifters are also mentioned. Then, two phase shifters with low phase and amplitude error are presented in section 3.4 and 3.5, respectively. This two phase shifters are designed with QPR and can be applied in RF and LO phased array system, respectively. The design methods and measurement results are presented in both phase shifters and summary are shown in the end of this chapter.

Finally, a brief conclusion of this dissertation will be given in chapter 4.

## Chapter 2 Millimeter-wave Frequency Divider Design

### 2.1 Overview of Frequency Divider

### 2.1.1 Static Frequency Divider [6], [7]

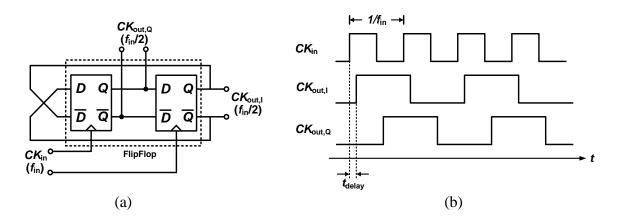

As shown in Fig. 2.2(a), a static frequency divider includes a flip-flop constructed by two latches in a negative feedback loop. This circuit works by continuously toggling the output state after every rising edge of clock. The mechanism effectively causes the output to toggle between one and zero at a half period of the input clock. Therefore, the frequency division is obtained. By driving differential input clock, the output quadrature output signals at half of the input frequency are provided by the two latches, as shown in Fig. 2.1(b). Since the latches can save the data permanently, the static frequency dividers can operate at very low frequency, and also have wide bandwidth performance. However, there is time delay between input and output, the maximum operation frequency is limit.

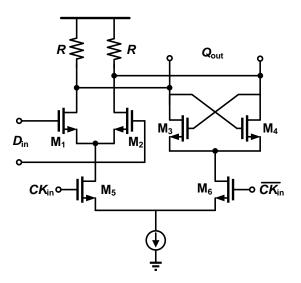

At low frequency, true single phase clocking (TSPC) latches are adopted in static frequency divider, due to its compact size, and no static power consumption. The rail-to-rail clock swings are required for correct operation. Also, it does not provide quadrature output. For high speed operation, the latch is implemented by current mode logic (CML), as shown in Fig. 2.2. This circuit is controlled by the clocked pair,  $M_{5-6}$ . It samples the input through input pair,  $M_{1-2}$ , and holds the data by cross-coupled pair  $M_{3-4}$ as long as the loop gain of cross-coupled pair exceeds unity. Since the propagation delay of CML is smaller than TSPC, the CML can achieve higher speed. Although CML frequency divider can operate at MMW region [6], [7], the tradeoff is requiring more power consumption to compensate the degradation of loop gain at high operation frequency. Another way to increase the operation frequency without extra power consumption is using inductor peaking technique. However, it has drawbacks of narrower bandwidth and larger area.

Fig. 2.1. (a) Static frequency divider, and (b) its time domain waveform.

Fig. 2.2. D-latch of current mode logic (CML)

### 2.1.2 Miller Frequency Divider [34], [35]

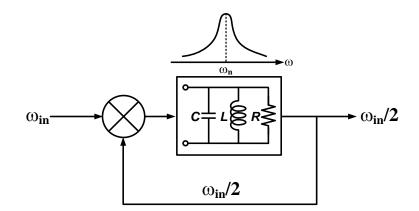

The Miller divider, or so-called regenerative divider, is originally proposed by Miller in 1939 [34] as shown in Fig. 2.3. The conventional Miller divider consists of a mixer and a low-pass filter (LPF) in a feedback loop. The mechanism is based on mixing the output and input signal and the result is applied to low-pass filter (LPF). The up-conversion signal is suppressed by LPF, and the divide-by-two signal is regenerated at output. Since the device parasitic capacitance can be absorb as part of LPF, Miller divider can achieve higher speed than static frequency divider. Besides, the phase and gain condition need to be satisfied. To realize the Miller divider with enough phase shift, the emitter follower is used in the Miller divider with BJT process as shown in Fig. 2.4 [35]. This topology is difficult to implement in CMOS process due to its low transconductance in a source follower configuration and low voltage headroom. To solve this problem, the Miller divider with inductive load has been proposed [35]. A band-pass filter (BPF) formed by LC-tank replaces the original LPF to suppress the high-order harmonic and ensure the loop gain at  $f_{in}/2$  continually exceeds unity. Also, the BPF provide enough phase shift to achieve phase condition. Hence, the Miller divider in CMOS process can operate at MMW frequency.

Base on the difference of feedback path, the Miller divider with inductive load has two configurations. The output port could either feedback to the RF-port or LO-port of the mixer, as shown in Fig. 2.5. The RF-port feedback Miller divider needs extra capacitors to isolate the DC bias. The more parasitic capacitance may degrade the operation frequency and the loop gain. Therefore, the LO-port feedback Miller divider is more preferable in MMW frequency.

Fig. 2.3. The model of Miller frequency divider

Fig. 2.4. Bipolar Miller divider

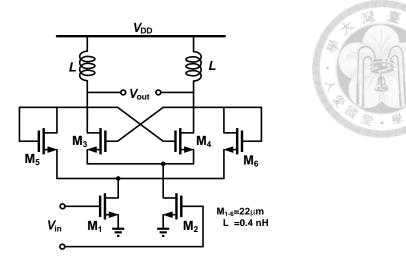

$V_{DD}$  L  $V_{out}$   $(f_{in}/2)$   $M_3$   $M_5$   $M_4$   $M_6$   $V_{in}$   $M_1$  =  $M_2$  $M_2$

(b)

Fig. 2.5. (a) RF-port feedback Miller divider. (b) LO-port feedback Miller divider

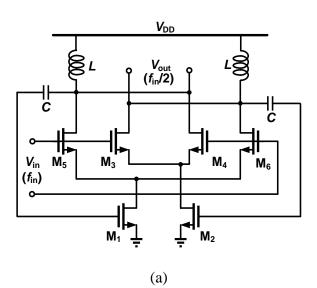

### 2.1.3 Injection-Locked Frequency Divider [36], [37]

Injection locking is a phenomenon which can be observed in all kinds of oscillators. When an oscillator is injected by an external signal which is close to the free-running frequency of the oscillator, the oscillation frequency of oscillator is changed to identical frequency of injection signal, i.e. the oscillator is locked by external signal, and the phenomenon is known as injection locking. Consider the oscillator provides differential output, as the external signal which is approximately twice the oscillator's free-running frequency inject into the common-mode point and make the oscillator locked, the frequency division is achieved. Among all kinds of frequency dividers, ILFD reaches the highest operation frequency among all frequency divider topology.

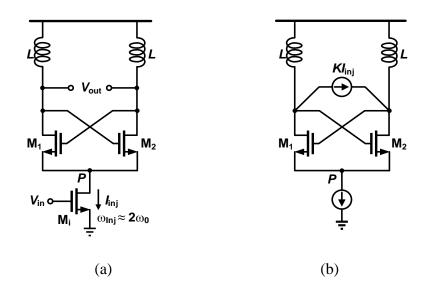

The phenomenon of injection locking can be explained by adding an external sinusoidal current  $I_{inj}$  to a conventional cross-coupled oscillator as shown in Fig. 2.6(a). Additional phase shift  $\phi_0$  caused by  $I_{inj}$  is inserted in the loop. The oscillator can no longer oscillate at  $\omega_0$  because the total phase shift at this frequency departs from 360° by  $\phi_0$ . The oscillation frequency must change to injection frequency  $\omega_{inj}$ . At frequency of  $\omega_{inj}$ , the phase shift contributed by  $I_{inj}$ ,  $I_{osc}$  (the oscillation current) and  $I_{tank}$  (current through LC tank) need to sustain a certain phase difference, meaning that the total phase shift maintain 360° From above description, the injection locking only occur at the frequency near  $\omega_0$  and the locking range is limited. As the matter of fact, the locking range was analytically derived as [37], [38]

$$\Delta \omega = \frac{\omega_0}{Q} \frac{I_{inj}}{I_{osc}} \frac{1}{\sqrt{1 - \frac{I_{inj}^2}{I_{osc}^2}}}$$

(2.1)

where Q is the quality factor of the LC tank. As a special case, if  $I_{inj} \ll I_{osc}$ , can be degenerated to

$$\Delta \omega = \frac{\omega_0}{Q} \frac{I_{inj}}{I_{osc}}$$

Fig. 2.6. Oscillator under injection locking.

Fig. 2.7. (a) Conventional ILFD. (b) Equivalent circuit.

(2.2)

The injection locking technique can be easily applied in frequency dividers. Fig. 2.7(a) shows conventional injection-locked frequency divider. The input signal injected through tail current transistor is twice the LC tank resonance frequency. The cross-coupled pair M<sub>1</sub> and M<sub>2</sub> form a mixer that down-converts  $\omega_{nj}$  into  $\omega_{nj} - \omega_0$  (up-converted component is suppressed by LC tank). A current of  $I_{inj}$  at  $\omega_{inj}$  into node *P* is equivalent to a current of  $KI_{inj}$  at  $\omega_{inj} - \omega_0$  into LC tank, as depicted in Fig. 2.7(b). If M<sub>1</sub> and M<sub>2</sub> can be switched on and off fully with enough voltage swing at  $V_{out}$ , then *K* is equal to  $2/\pi$ , and the locking range of ILFD can be written as

$$\Delta \omega = \frac{\omega_0}{Q} \frac{2}{\pi} \frac{I_{inj}}{I_{osc}}.$$

(2.3)

Referred to the input, the locking range is twice this value:

$$\Delta \omega = \frac{\omega_0}{Q} \frac{4}{\pi} \frac{I_{inj}}{I_{asc}}$$

(2.4)

A few techniques can be applied in ILFD to enhance the locking range of conventional ILFD in Fig. 2.7(a). To increase the injection current  $I_{inj}$ , the size of M<sub>i</sub> is chosen large, causing large parasitic capacitance at node *P*. At high frequency, part of injection current pass though the capacitor to ground, and decrease the locking range. A modified ILFD with shunt peaking inductor *L*s to resonate the parasitic capacitor  $C_p$  is shown in Fig. 2.8(a) [39]. Although the locking range is improved, the extra inductor requires more area. The other modified ILFD in Fig. 2.8(b) is proposed to enhance the injection efficiency [40]. Because the injection current is directly injected to LC-tank, the injection efficiency is not degraded without extra inductor. Therefore, the ILFD with direct injection is widely utilized in high frequency CMOS PLL design.

Fig. 2.8. Modified ILFD with (a) shunt peaking inductor (b) direct injection.

# 2.2 35.7–64.2 GHz low power Miller Divider with Weak Inversion Mixer in 65 nm CMOS

# 2.2.1 Introduction of MMW Miller Divider

The millimeter wave (MMW) communication system has been developed rapidly due to the unlicensed band around 60 GHz. These systems require a phase lock loop (PLL) to provide local oscillator (LO) source for frequency conversion. The PLL needs a frequency divider to connect with voltage control oscillator (VCO) operated at high frequency, and the power consumption and locking range must be considered carefully. Due to the process variation, the bandwidth of divider is better to be several times wider than the tuning range of VCO. Therefore, a wide bandwidth with low power frequency divider is desired.

Static current mode logic (CML) frequency divider, injection lock frequency divider (ILFD) and Miller frequency divider are widely used in high speed PLL and synthesizer. The Miller divider has wider frequency response than ILFD with moderate power consumption. Therefore, the Miller divider is suitable for high frequency divider.

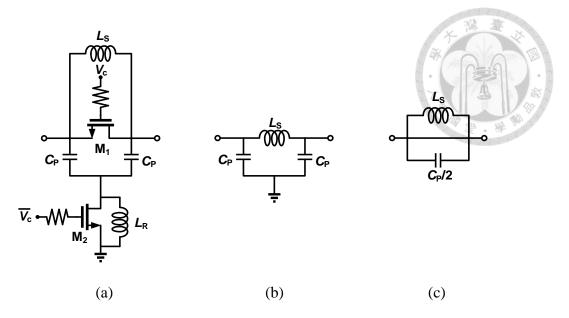

To implement Miller divider in CMOS process, the BPF is required. The block diagram of Miller divider with BPF is shown in Fig. 2.9(a). The mechanism is based on mixing the output and input signal and the result is filtered by BPF to get the divide-by-two signal. In the most cases, the Gilbert cell mixer shown in Fig. 2.9(b) is chosen in Miller divider design due to the simple implementation. However, the locking range is limited by the conversion gain (CG) of mixer, BPF response and parasitic effect of mixer. To solve these problems, transformer injection [8] and current bleeding [9] are proposed. These two techniques improve the CG of mixer and achieve wider locking range. Nevertheless, the improvements are limited, and it takes extra chip area and power consumption. Another effective way to enhance the bandwidth of Miller divider is using the band-switched Miller divider [41]. To select suitable band automatically, the additional calibration circuit is required. It can increase the operation frequency significantly. However, it also suffers from the large chip size and high dc power. In this section, a Miller divider with weak inversion biasing mixer is presented. By using the weak inversion mixer as mixer core of Miller divider, this divider achieves the locking range of 57 % from 35.7 to 64.2 GHz at 0-dBm injection power with low power consumption of 1.6 mW.

# 2.2.2 Circuit Design

Most of the Miller dividers include a mixer with good performance. Usually, these mixers have high CG, wide frequency response and low dc power. In previous reported work [8], [9], [35], Gilbert cell mixer is chosen as mixer core in Miller divider design. However, a conventional Gilbert cell mixer (Fig. 1(b)) consumes high dc power, and requires high voltage power supply for stack transistor topology. Passive mixer shown in Fig. 2.9(c), which can be operated without dc power; nevertheless, it still needs buffer amplifier for CG. To obtain sufficient CG with low dc power and low voltage supply, the weak inversion mixer is proposed and shown in Fig. 2.9(d) [42]. This mixer has advantage over other mixer, and is suitable as mixer core of Miller divider.

(a)

(c)

Fig. 2.9. (a) Block diagram of Miller divider, (b) conventional Gilbert cell mixer, (c) passive mixer, and (d) weak inversion biasing mixer

#### 2.2.2.1 Weak Inversion Biasing mixer

The mixer with weak inversion bias technique is attractive because of its low LO power and low dc power. Traditional Gilbert cell mixer is operated in strong inversion region ( $V_{\text{GS}} > V_{\text{TH}}$ ). In the weak inversion region, the gate-source  $V_{\text{GS}}$  is lower than threshold voltage  $V_{\text{TH}}$ , and the  $i_{\text{DS}}$  vs  $V_{\text{GS}}$  of MOS transistor is exponential dependence rather than square-law characteristics [42]. At this bias condition, the LO voltage swing requirement is relatively low.

Fig. 2.10(a) shows the simulated mixer conversion gain with different type mixers (Fig. 2.9(b), (c), (d)) at MMW frequency in 65 nm CMOS. Each mixer has the same device size (18  $\mu$ m gate width) and inductor value with equal quality factor for a fair comparison. The only difference is bias condition. As can be observed, no matter with or without  $V_{GS}$  biasing, the conventional passive mixer has the lowest gain even in high LO voltage swing. A traditional Gilbert cell mixer in typical bias point has the highest gain in high LO voltage. Owing to operating in MMW, the gain provided by transconductance stage of Gilbert cell mixer is limited. By adopting the weak inversion bias in weak inversion mixer, this mixer improves conversion gain in low LO voltage region. The simulated mixer conversion gain versus input RF frequency is shown in Fig. 2.10(b). The weak inversion mixer exhibits better frequency response than others at low LO voltage. Moreover, this mixer consumes lower dc power than traditional Gilbert cell mixer.

(a)

(b)

Fig. 2.10. Simulated (a) conversion gain versus LO voltage, and (b) conversion gain versus input frequency of each mixers

#### 2.2.2.2 Bandwidth of Miller Divider with BPF

The block diagram of Miller divider with BPF is shown in Fig. 2.11. Considering the mixer is ideal, and BPF is simple parallel RLC network. The impedance of RLC tank can be expressed as

$$Z_{\text{tank}} = \frac{\frac{j\omega_n \omega}{Q}R}{\omega_n^2 + \frac{j\omega_n \omega}{Q} - \omega^2}$$

(2.5)

where  $\omega_n = 1/\sqrt{LC}$  and  $Q = \omega RC$ . As the switch pairs of mixer are fully switching, the conversion gain of mixer is equal to  $(2/\pi)g_m$  multiplying by impedance of RLC tank, where  $g_m$  is the transconductance of transconductor stage of mixer. Also, the loop gain is equal to conversion gain of mixer, and to divide successfully, the loop gain at  $\omega_{in}/2$  has to excess unity at  $\omega_{in}/2$ , the condition can be written as

$$\frac{2}{\pi}g_{m}\left|\frac{\frac{j\omega_{n}\omega_{in}}{2Q}R}{\omega_{n}^{2}+\frac{j\omega_{n}\omega_{in}}{2Q}-\frac{\omega_{in}^{2}}{4}}\right| \ge 1$$

(2.6)

$$\frac{2}{\pi}g_{m}R\frac{\frac{\omega_{n}\omega_{in}}{2Q}}{\sqrt{\left(\omega_{n}^{2}-\frac{\omega_{in}^{2}}{4}\right)^{2}+\frac{\omega_{n}^{2}\omega_{in}^{2}}{4Q^{2}}}} \ge 1$$

(2.7)

Obviously, the peak loop gain is  $(2/\pi)g_mR$  at  $\omega_{in} = \omega_n/2$ , and (2.7) can rewritten as

$$\frac{2}{\pi}g_{m}R \ge \sqrt{1 + \frac{\left(1 - \frac{\omega_{in}^{2}}{4\omega_{n}^{2}}\right)^{2}}{\frac{1}{4Q^{2}}\frac{\omega_{in}^{2}}{\omega_{n}^{2}}}}$$

(2.8)

For  $\Delta \omega = \left| \omega_{\rm in} - 2\omega_{\rm n} \right| \ll 2\omega_{\rm n}$ , we have

$$1 - \frac{\omega_{\text{in}}^2}{4\omega_{\text{n}}^2} = \frac{(2\omega_{\text{n}} + \omega_{\text{in}})(2\omega_{\text{n}} - \omega_{\text{in}})}{4\omega_{\text{n}}^2}$$

$$\approx \frac{4\omega_{\text{n}}(2\omega_{\text{n}} - \omega_{\text{in}})}{4\omega_{\text{n}}^2}$$

$$\approx \frac{\Delta\omega}{\omega_{\text{n}}}$$

Therefore, the denominator under the square root in (2.8) can be reduced to  $(Q\Delta\omega/\omega_n)^2$ , resulting in

$$\frac{2}{\pi}g_{m}R \ge \sqrt{1 + \left(\frac{Q\Delta\omega}{\omega_{n}}\right)^{2}}$$

(2.10)

Then,

$$\Delta \omega = \frac{\omega_{\rm n}}{Q} \left[ \left( \frac{2}{\pi} g_{\rm m} R \right)^2 - 1 \right] \approx \frac{\omega_{\rm n}}{Q} \left( \frac{2}{\pi} g_{\rm m} R \right)^2 \tag{2.11}$$

Let  $CG = 2g_m R/\pi$ , (2.11) can be written as

$$\Delta \omega \approx \frac{\omega_{\rm n}}{Q} (CG)^2 \tag{2.12}$$

Fig. 2.11. Miller divider with BPF as RLC tank.

(2.9)

#### 2.2.2.3 Proposed Miller Divider

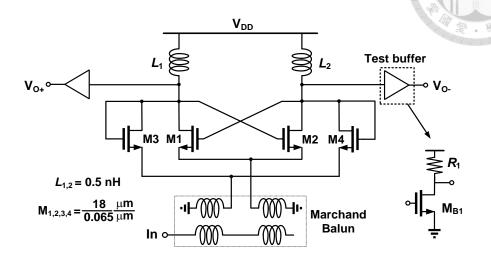

The operation frequency range of Miller divider with LC tank as the load was derived as (2.12). From (2.12), the operation frequency range is proportional to 1/Q and CG. It can be observed that increasing the CG of mixer is effective to improve the locking range of Miller divider. Generally, CG is equal to  $2g_{\rm m}R/\pi$  and independent of LO voltage [35], and it is true when LO voltage is high enough. However, as long as LO voltage is not sufficient, CG is lower with lower LO voltage. As shown in Fig. 2.10(a), CG is dependent on LO voltage. From the principle of Miller divider, the mixer output port is fed back to LO port to mix with the divide-by-two signal. For low dc operation, the swing of output signals is small. As above mentioned, the weak inversion mixer has higher gain at low LO input. Also, based on Fig. 2.10(b), the weak inversion mixer has better frequency response. Therefore, the Miller divider with this mixer has a wider locking range than others. The proposed Miller divider is shown in Fig. 2.12.  $M_1$ - $M_4$ form the mixer core with weak inversion bias, and IF port is connected to LO port directly to form feedback loop. The gate and drain node share the same voltage source, since the performance does not improve by separating the bias. The size of transistor is selected appropriately to construct desired BPF center frequency with inductors  $L_1$  and  $L_2$ . Instead of the RF choke, the Marchand balun is utilized to construct current coupling and differential signal between input and divider core; also, the required supply voltage will be decreased. Besides, the input matching network is not needed because the impedance looking into the source of MOS transistor is close to the output impedance of the Marchand balun. For measurement requirement, the common source amplifier used as test buffer to isolate the load of instruments, otherwise the BPF response will be influenced. To save the chip area, the load is realized by a resistor rather than an inductor.

Fig. 2.12. Proposed Miller divider based on weak inversion mixer.

# 2.2.3 Measurement Results

The proposed Miller divider is implemented in 65-nm CMOS general process. The chip microphotograph is shown in Fig. 2.13 with a die size of  $0.35 \times 0.45 \text{ mm}^2$ , including DC and RF pads. This divider is measured via on-wafer probing. The input is generated by a signal generator Agilent E8257D, and the output signal is captured by spectrum analyzer Agilent E4448A. This frequency divider operates at 0.4-V supply voltage and consumes 1.6 mW. The measured and simulated input sensitivity curve is shown in Fig. 2.14. It indicates that no self-oscillation is observed. The measured input locking range is from 35.7 to 64.2 GHz (57%) without frequency tuning. The measured sensitivity curve with supply voltage of 0.5 V is also shown in Fig. 2.14. The locking range is limited because the bias region is not in weak inversion region. The simulated and measured output powers are shown in Fig. 2.15. The tendency of the measured output

power is similar to the simulation and it varies from -23 to -17 dBm. For phase noise measurement, as the input frequency is 50 GHz with input power of 0 dBm, the measured output phase noise is -106 dBc/Hz, which is better than input phase noise of -100 dBc/Hz at 100-kHz offset, and consistent with the theoretical value. Table 2.1 summarizes the performance of previously reported MMW Miller divider in CMOS process. Due to the weak inversion mixer, the proposed Miller divider has the widest locking range at 0-dBm input power among the previous reported MIW ILFD, as summarized in Table 2.2. Compared with other published MMW ILFD, the proposed Miller divider has the lowest power consumption. This circuit also demonstrates the highest locking range and highest FOM [13] compared with others in MMW range.

Fig. 2.13. Chip photo of proposed Miller divider.

Fig. 2.14. Simulated and measured sensitivity curve of proposed Miller divider.

Fig. 2.15. Simulated and measured output power of proposed Miller divider at injection power of 0 dBm.

|                              |       | [35]   | [8]       | [9]    | This Work |

|------------------------------|-------|--------|-----------|--------|-----------|

| Technology                   |       | 0.18µm | 0.13 μm   | 0.13µm | 65 nm     |

|                              |       | CMOS   | CMOS      | CMOS   | CMOS      |

| Topology                     |       | Miller | Miller    | Miller | Miller    |

| Input Frequency (GHz)        |       | 38-41  | 56.5-72.2 | 57-72  | 35.7-64.2 |

| Locking Range                | (GHz) | 3      | 15.7      | 15     | 28.5      |

|                              | (%)   | 7.6%   | 24.4%     | 23.2%  | 57%       |

| Input Power (dBm)            |       | 3      | 0         | 0      | 0         |

| V <sub>DD</sub> (V)          |       | 2.5    | 1         | 0.8    | 0.4       |

| P <sub>DC</sub> (mW)         |       | 16.8   | 4.65      | 5      | 1.6       |

| FOM (GHz/mW)                 |       | 0.18   | 3.37      | 3      | 17.81     |

| Chip Size (mm <sup>2</sup> ) |       | 0.35   | 0.42      | *0.007 | 0.156     |

Table 2.1. Comparison of Published MMW Miller dividers

\* core area only

Table 2.2. Comparison of Published MMW ILFDs and proposed Miller divider

|                              |       | [43]    | [44]    | [13]  | [15]      | This Work |

|------------------------------|-------|---------|---------|-------|-----------|-----------|

| Technology                   |       | 0.18 µm | 65nm    | 90nm  | 65nm      | 65 nm     |

|                              |       | CMOS    | CMOS    | CMOS  | CMOS      | CMOS      |

| Topology                     |       | ILFD    | ILFD    | ILFD  | ILFD      | Miller    |

| Input Frequency (GHz)        |       | 37.5-49 | 53.7-72 | 51-74 | 53.4-79.4 | 35.7-64.2 |

| Locking Range                | (GHz) | 11.5    | 23      | 18.3  | 26        | 28.5      |

|                              | (%)   | 26.6%   | 36.8%   | 29%   | 39.2%     | 57%       |

| Input Power (dBm)            |       | 0       | 0       | 0     | 0         | 0         |

| $V_{DD}(V)$                  |       | 1       | 0.8     | 0.5   | 0.8       | 0.4       |

| $P_{DC}(mW)$                 |       | 6       | 1.9     | 3     | 2.9       | 1.6       |

| FOM (GHz/mW)                 |       | 1.92    | 9.63    | 7.67  | 8.97      | 17.81     |

| Chip Size (mm <sup>2</sup> ) |       | 0.428   | *0.023  | 0.136 | *0.126    | 0.156     |

\* core area only

#### 2.2.4 Discussions

There are several issues to be further discussed. The measured locking range is sensitive to supply voltage  $V_{DD}$  due to the bias condition. Although this circuit still can operate below 0.4-V supply voltage, the performance is degraded. As MOS is biased in weak inversion region, the relation for the transcondance of MOS ( $g_m$ ) vs  $V_{GS}$  is exponential dependence like  $i_D$  vs  $V_{GS}$ . Hence, Miller divider with larger  $V_{DD}$  has wider locking range as biasing in weak inversion region. However, as  $V_{DD}$  larger than 0.45 V, the MOS is not biased in weak inversion region, which causes smaller CG. Therefore, bandwidth is limited and it has been demonstrated in measurement (Fig. 2.14).

Furthermore, due to no self-oscillation, this Miller divider cannot operate at low input power. In order to drive Miller divider with low input power, Miller divider need to be designed with self-oscillation which can be obtained by increasing the device size  $M_1$  and  $M_2$  since  $M_1$ ,  $M_2$  and the inductor ( $L_1$  and  $L_2$ ) form a cross-coupled oscillator. However, it will consume more dc power.

For output power measurement, since the power was measured from output buffer, the resistive-load buffer cannot provide enough power. However, in real application, the resistive-load buffer is not required. The voltage swing at Miller divider output is enough to drive next stage divider. Unfortunately, the voltage swing is not easy to measure in MMW region. Hence, the simulated output peak-to-peak voltage > 0.6 V is provided as shown in Fig. 2.16, and this is large enough to drive the next frequency divider chain.

Fig. 2.16. Simulated transient response of  $V_{\rm o^+}$  with 0 dBm input power.

# 2.3 W-band Injection-Locked Frequency Divider Using Split Transformer-Coupled Oscillator Technique

# 2.3.1 Introduction of MMW ILFD

With rapid progress in modern CMOS technology, the MMW applications have obtained lots of attention, such as 77 GHz automotive radars, 94 GHz image sensors, and point to point communications. These systems require a PLL to provide signal source or local oscillator (LO) source for frequency conversion. For the MMW PLLs, the main blocks are the VCO and frequency divider. The design challenges of MMW VCOs are the frequency tuning range, phase noise, and power consumption. For the frequency dividers, the first stage divider is a critical block since its operation frequency has to cover the frequency tuning range of VCOs. In addition, low power consumption is also an important issue for high frequency PLLs.

Static CML frequency dividers [6], [7], Miller frequency dividers [8], [9], [35] and ILFD [10]-[15], [39], [40], [43]-[47] are widely used in high speed PLLs. CML divider has the widest locking range and small size, but it suffers from high dc power consumption and lower operation frequency. Miller divider can operate at higher frequency with lower power consumption than CML divider, however, the locking range is still narrow. Among all the high frequency dividers, ILFD has the highest operation frequency and the lowest dc power consumption, but with the narrowest locking range. Nevertheless, ILFD still has potential for MMW low power PLLs.

The principle of ILFD has been described in section 2.1.3, the ILFD with direct injection have the wider locking range and much wider used in MMW PLL. Several

techniques have been proposed to improve the locking range of ILFD with direct injection. The inductor peaking is one of the useful techniques as shown in Fig. 2.17(a) [15], [43]. By inserting the inductors in injection transistor, the locking range can be enhanced by boosting its transconductance. Another method to improve locking range is using distributed LC structures illustrated in Fig. 2.17(b) [14], [45]. The parasitic capacitance is separated by distributed LC network to obtain higher operation frequency and wider locking range. However, these techniques require multiple inductors, and occupy larger chip areas as well as the design complexity of integration with the VCO.

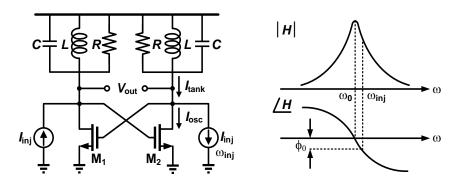

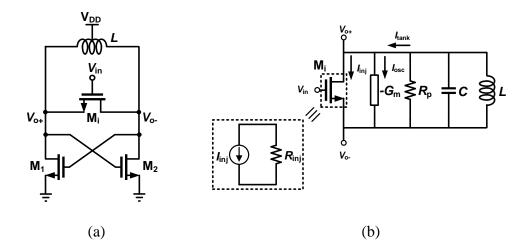

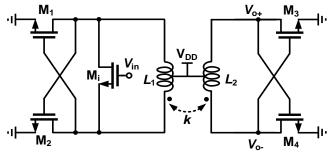

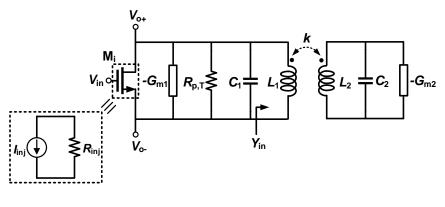

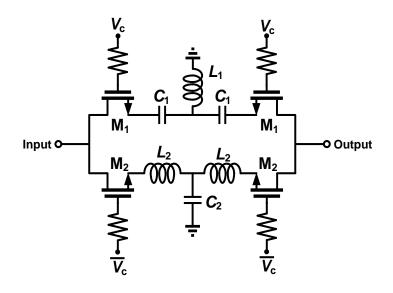

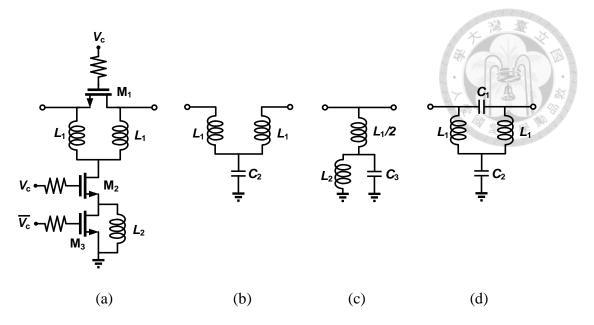

In this section, a W-band divide-by-two ILFD with split transformer-coupled oscillator (STCO) is proposed to enhance the locking range of ILFD without additional inductors. Also, with splitting cross-coupled transistor and splitting transformer, the operation frequency is increased and oscillation condition can be easily satisfied without sacrificing dc power consumption.

Fig. 2.17. ILFD with (a) inductor peaking technique and (b) distributed LC structure

# 2.3.2 Split Transformer-Coupled Oscillator

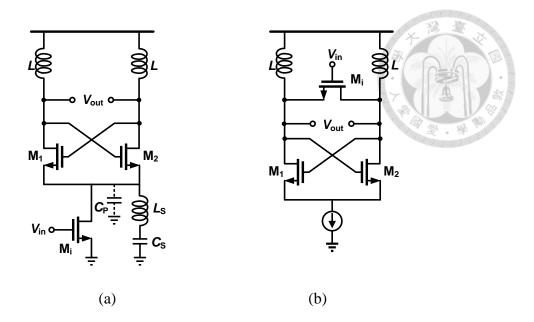

Transformer-coupled oscillators have been proposed to achieve wide tuning range with low phase noise [48], [49]. The idea is utilizing multiple coupled oscillators which are controlled by switch to realize multi-band operation. In this design, the transformer couples two split cross-coupled pair transistors to increase the oscillation frequency and eases the oscillation condition.

#### 2.3.2.1 Oscillation Frequency

A conventional LC oscillator and its equivalent model are shown in Fig. 2.18. The oscillation frequency is expressed as  $\omega_0 = 1/\sqrt{LC}$ , where *L* is the total inductance and *C* is the total parasitic capacitance contributed by MOS transistors and *L*.

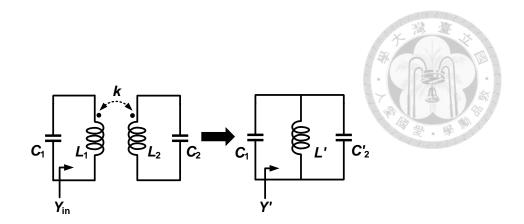

The proposed STCO is shown in Fig. 2.19. The original inductor L is decomposed to two inductors  $L_1$  and  $L_2$ , and a transformer with coupling coefficient k is constructed by the two inductors. The original cross-coupled pair transistor is split into two pairs of cross-coupled pair transistor. The equivalent model of STCO is also shown in Fig. 2.  $C_1$  and  $C_2$  are parasitic capacitance on two sides of transistor and inductor. The parasitic resistors of the transformer are  $R_1$  and  $R_2$ . The input impedance of transformer can be derived as.

$$Z_{in}(s) = \frac{s^{3}(1-k^{2})L_{1}L_{2}C_{2} + s^{2}(L_{1}R_{2} + L_{2}R_{1})C_{2} + s(L_{1} + R_{1}R_{2}C_{2}) + R_{1}}{s^{4}(1-k^{2})L_{1}L_{2}C_{1}C_{2} + s^{3}(L_{1}R_{2} + L_{2}R_{1})C_{1}C_{2} + s^{2}(L_{1}C_{1} + L_{2}C_{2} + R_{1}R_{2}C_{1}C_{2}) + s(R_{1}C_{1} + R_{2}C_{2}) + 1}$$

$$(2.13)$$

By setting imaginary part of the denominator to zero, the oscillation frequency is calculated as

$$\omega_{\rm L,H} = \sqrt{\frac{L_1C_1 + L_2C_2 \pm \sqrt{(L_1C_1 + L_2C_2)^2 - 4(1 - k^2)L_1L_2C_1C_2}}{2(1 - k^2)L_1L_2C_1C_2}}$$

By splitting transformer-coupled oscillator, the total inductance and capacitance of split transformer-coupled oscillator are equal to the conventional cross-coupled oscillator ( $L = L_1 + L_2$ ,  $C = C_1 + C_2$ ). Because of the symmetric architecture, we assume  $L_1 = L_2 = L/2$ , and  $C_1 = C_2 = C/2$ , then the oscillation frequency can be rewritten as

$$\omega_{\rm L} = \frac{2}{\sqrt{(1+k)LC}} = \frac{2}{\sqrt{(1+k)}} \omega_0$$

(2.15a)

(2.14)

$$\omega_{\rm H} = \frac{2}{\sqrt{(1-k)LC}} = \frac{2}{\sqrt{(1-k)}} \,\omega_0 \tag{2.15b}$$

Note that STCO has two oscillation frequencies. Usually, it only operates at low frequency because the currents in two inductors,  $L_1$  and  $L_2$ , are in phase. For higher frequency, the currents are out of phase, causing larger inductor loss. The frequency increasing ratio is defined as  $\omega_L/\omega_0$ . For a special case of k = 1, the oscillation frequency,  $\omega_L = \sqrt{2}\omega_0 \approx 1.414\omega_0$ , i.e., the frequency at least increase 41.4%, and the increasing ratio is higher than distributed LC-oscillator [14]. From (2.8a), it also shows that the oscillation frequency can be increased by reducing *k*. However, once  $\omega_L$  is increased by reducing *k*,  $\omega_H$  is decreased. The lower *k* makes the two oscillation frequency close to each other. The higher oscillation frequency mode cannot be eliminated easily and thus, the two tone oscillations may occur in STCO simultaneously. Hence, the ILFD may not divide to correct frequency by this phenomenon. Also, the oscillation condition can be influenced by *k*, which will be discussed in the next paragraph.

Fig. 2.18. Conventional cross-coupled oscillator.

Fig. 2.19. Proposed split transformer coupled oscillator (STCO).

#### 2.3.2.2 Oscillation Condition

To satisfy the oscillation condition of oscillator, the cross-coupled pair transistors must provide enough negative conductance,  $-G_m$ , to compensate the loss of LC-tank. Assuming the series resistance of inductor dominates the total loss of LC-tank, the equivalent parallel resistance of LC-tank is equal to  $R_p \approx Q\sqrt{L/C}$ , where  $Q = \omega L/R$  is the quality factor of inductor. As a result, the oscillation condition of conventional LC oscillator can be expressed as

$$G_{\rm m} Q \sqrt{\frac{L}{C}} > 1 \tag{2.16}$$

Considering a conventional LC oscillator operated at 40 GHz as an example, *L* is 0.3 nH with Q = 15, and the total parasitic capacitor *C* is 50 fF. By (2.16), the minimum required  $G_{\rm m}$  is equal to 0.86 mS. The oscillation condition of STCO can be derived by using the equivalent circuit model in Fig. 2.20. The equivalent parallel resistance of transformer  $R_{\rm p,T}$  in two frequency modes can be calculated from (2.13) as

$$R_{\rm p,T}(\omega_{\rm L}) = \operatorname{Re}[Z_{\rm in}(\omega_{\rm L})] \approx \frac{Q(1+k)}{2} \sqrt{\frac{(1+k)L}{C}}$$

(2.17a)

$$R_{\rm p,T}(\omega_{\rm H}) = {\rm Re}[Z_{\rm in}(\omega_{\rm H})] \approx \frac{Q(1-k)}{2} \sqrt{\frac{(1-k)L}{C}}$$

(2.17b)

The negative transconductance  $-G_{m2}$  which is transformed by transformer can be represented as Re[ $Y_{in}$ ], and is derived as

$$\operatorname{Re}[Y_{\text{in}}(\omega)] = \frac{-k^2 G_{\text{m2}}}{\frac{\omega^4 L^2 C^2 (k^2 - 1)^2}{16} + \frac{\omega^2 L C (k^2 - 1)}{2} + \frac{\omega^2 L^2 G_{\text{m2}}^2 (k^2 - 1)^2}{4}}$$

(2.18)

Then, the total equivalent transconductance,  $G_{m,eq}$ , is given as

$$G_{\rm m,eq}(\omega) = G_{\rm m1} + \left| \text{Re}[Y_{\rm in}(\omega)] \right|$$

Setting  $G_{m1} = G_{m2} = G_m/2$  due to the symmetry of splitting cross-coupled pair transistor, the  $G_{m,eq}$  in low and high oscillation frequency can be expressed as

$$G_{\rm m,eq}(\omega_{\rm L}) = \frac{G_{\rm m}}{2} + \frac{1}{2} \frac{k^2 G_{\rm m}}{k^2 + (k+1)(k-1)^2 \frac{L}{C} G_{\rm m}^2}$$

(2.20a)

(2.19)

and

$$G_{\rm m,eq}(\omega_{\rm H}) = \frac{G_{\rm m}}{2} + \frac{1}{2} \frac{k^2 G_{\rm m}}{k^2 + (k+1)^2 (k-1) \frac{L}{C} G_{\rm m}^2}.$$

(2.20b)

Accordingly, to ensure the oscillation occurs at the lower frequency, the following condition need to be satisfied.

$$G_{\rm m,eq}(\omega_{\rm L})R_{\rm p,T}(\omega_{\rm L}) > 1$$

(2.21a)

$$G_{\rm m,eq}(\omega_{\rm H})R_{\rm p,T}(\omega_{\rm H}) < 1.$$

(2.21b)

Otherwise, concurrent dual mode oscillation may occur. As mentioned before, choosing higher k can avoid this phenomenon easily because the higher k leads to higher loss of transformer in high frequency from (2.17b). In addition, this condition also can be achieved by choosing appropriate  $G_m$  value. Considering STCO only operated in the lower frequency mode, the minimum required  $G_m$  of STCO can be found in (2.21a). Fig. 2.21(a) shows the minimum required  $G_m$  and frequency increasing ratio versus different k. STCO has higher oscillation frequency for all k value, and requires less  $G_m$  as k is higher than 0.6. To make a fair comparison, the frequency increasing ratio is normalized to unity by changing the inductor value of STCO with the same total transistor size as conventional LC oscillator (constant total  $G_m$  and capacitance). The minimum required  $G_{\rm m}$  versus different *k* under the same oscillation frequency is shown in Fig. 2.21(b). It can be observed that the minimum required  $G_{\rm m}$  for proposed STCO is lower than conventional LC-oscillator when *k* is larger than 0.2, and the higher *k* will further relieve the oscillation condition.

Fig. 2.20. Equivalent circuit of STCO

(a)

(b)

Fig. 2.21. Calculated (a) Minimum required  $G_m$  and frequency increasing ratio versus transformer coupling coefficient, k, and (b) minimum required Gm versus transformer coupling coefficient under the same oscillation frequency.

### 2.3.3 Analysis of ILFD

#### 2.3.3.1 Locking Range Analysis

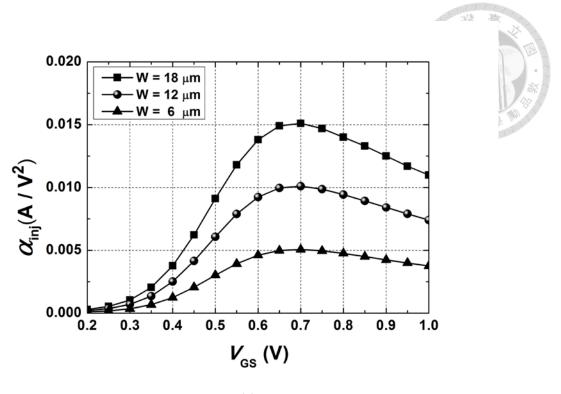

The schematic and equivalent circuit model of divide-by-two ILFD with direct injection are shown in Fig. 2.22(a) and (b). This ILFD is realized by conventional-LC oscillator, and the injection transistor, M<sub>i</sub> is connected to LC-tank directly. Before injecting signal, the output frequency of the ILFD is free-running oscillation frequency  $\omega_0$ . When input frequency  $\omega \approx 2\omega_0$  is injected into the injection transistor, the output frequency is locked to half of input frequency  $\omega$ . The injection transistor can be modeled as an injection current source,  $i_{inj}(t)$ , controlled by input and output voltage, and a parasitic resistor,  $R_{inj}$ . The input voltage  $v_{in}(t)$  is  $V_i \cos(2\omega t + \phi)$ , and the differential output voltage  $v_{0+}(t)$  and  $v_{0-}(t)$  are  $\pm (V_0/2)\cos\omega t$ , where  $V_i$  and  $V_o$  are the magnitudes of input and output voltage, respectively, and  $\phi$  is the phase shift between input and output voltage.  $i_{inj}(t)$  is derived by multiplying input and output voltage as

$$i_{\rm ini}(t) = \alpha_{\rm ini} V_{\rm i} \cdot V_{\rm o} \cos(2\omega t + \phi) \cos \omega t \tag{2.22}$$

where  $\alpha_{inj}$  is the mixing factor which depends on device size and bias voltage. Assuming that the frequency components far from resonant frequency  $\omega_0$  are filtered by LC-tank, (2.22) can be simplified as

$$i_{\rm ini}(t) = \alpha_{\rm ini} V_{\rm i} \cdot V_{\rm o}(\cos\phi\cos\omega t - \sin\phi\sin\omega t)$$

(2.23)

Using complex exponential to replace sines and cosines, so the injection current can be expressed by phasor form as

$$I_{\rm inj} = I_{\rm inj,i} + I_{\rm inj,q} = \alpha_{\rm inj} V_{\rm i} \cdot V_{\rm o}(\cos\phi - j \cdot \sin\phi)$$

(2.24)

where  $I_{inj,i}$  and  $I_{inj,q}$  are in-phase and quadrature-phase current, respectively. The locking range of ILFD is determined by phase [37] and gain condition [15], [14]. The phase condition means that the phase of total input current should be equal to the phase of current through LC-tank when ILFD is locked and stable oscillation is maintained.

Fig. 2.22. (a) ILFD with direct injection and (b) its equivalent circuit model.