國立臺灣大學電機資訊學院電子工程學研究所

博士論文

Graduate Institute of Electronics Engineering

College of Electrical Engineering & Computer Science

National Taiwan University

Doctoral dissertation

三維電晶體之自發熱效應及

三維積體電路穿矽連通柱之應變/應力

**Self-heating Effects in 3D Transistors and

Strain/Stress of 3D-IC TSV**

顏智洋

Jhih-Yang Yan

指導教授：劉致為 博士

Advisor: Chee Wee Liu, Ph.D.

中華民國 107 年 7 月

July, 2018

國立臺灣大學博士學位論文

口試委員會審定書

三維電晶體之自發熱效應及

三維積體電路穿矽連通柱之應變/應力

Self-heating Effects in 3D Transistors

and Strain/Stress of 3D-IC TSV

本論文係顏智洋君 (F01943063) 在國立臺灣大學電子工程學研究所完成之博士學位論文，於民國 107 年 7 月 21 日承下列考試委員審查通過及口試及格，特此證明

口試委員：

劉政彥

林吉慶 (指導教授)

張書遠

李政彥

陳敏遠

系主任、所長

林楚軒

廖詒漢

張序慶

高國興

李政彥

# **Self-heating Effects in 3D Transistors and Strain/Stress of 3D-IC TSV**

By

**Jhih-Yang Yan**

## **Dissertation**

Submitted in partial fulfillment of the requirement

for the degree of Doctor of Philosophy

in Electronics Engineering

at National Taiwan University

Taipei, Taiwan, R.O.C.

July 2018

Approved by :

Chih-Lun Jhih-Yang Yan Chu-Hsuan Lin

Shu-Tung Chang Ming-Han Liao Wish Yu Lin

Wen-Hui Lee Ming-Jang Chen Kuo-Hsing Kao

Advised by :

Approved by Director :

Chee-wei Wu

An-Yen Wu

# Related Publication (相關論文發表)

## A: Journal Paper (學術期刊論文)

1. Jhih-Yang Yan, Sun-Rong Jan, Yi-Chung Huang, Huang-Siang Lan, Y.-H. Huang, Bigchoug Hung, K.-T. Chan, Michael Huang, M.-T. Yang and C. W. Liu, “Asymmetric Keep-out Zone of Through-Silicon Via using 28nm Technology Node”, *IEEE Electron Device Letter*, Vol. 36, No. 9, pp. 938-940, 2015.

2. S.-T. Fan, J.-Y. Yan, D.-C. Lai, C. W. Liu, “The hysteresis-free negative capacitance field effect transistors using non-linear poly capacitance,” *Solid-State Electronics*, Volume 122, Pages 13-17, 2016.

3. I-Hsieh Wong, Yen-Ting Chen, Jhih-Yang Yan, Huang-Jhih Ciou, Yu-Sheng Chen and C. W. Liu, “Fabrication and Low Temperature Characterization of Ge (110) and (100) p-MOSFETs” *IEEE Transactions on Electron Devices*, Vol. 61, No. 6, pp. 2215, 2014.

## B: Conference Paper (學術會議論文)

1. Jhih-Yang Yan, Chia-Che Chung, Sun-Rong Jan, H. H. Lin, W. K. Wan, M.-T. Yang, and C. W. Liu, "Comprehensive Thermal SPICE Modeling of FinFETs and BEOL with Layout Flexibility Considering Frequency Dependent Thermal Time Constant, 3D Heat Flows, Boundary/Alloy Scattering, and Interfacial Thermal Resistance with Circuit Level Reliability Evaluation," accepted by *Symposium on VLSI Technology (VLSI-Technology), Honolulu, Hawaii, June 18-22, 2018*.

2. Jhih-Yang Yan, Sun-Rong Jan, Yu-Jiun Peng, H. H. Lin, W. K. Wan, Y.-H. Huang, Bigchoug Hung, K.-T. Chan, Michael Huang, M.-T. Yang, and C. W. Liu, “Thermal Resistance Modeling of Back-end Interconnect and Intrinsic FinFETs, and Transient Simulation of Inverters with Capacitive Loading Effects,” p.898-

3. I-Hsieh Wong, Fang-Liang Lu, Shih-Hsien Huang, Hung-Yu Ye, Chun-Ti Lu, Jhih-Yang Yan, Yu-Cheng Shen, Yu-Jiun Peng, Huang-Siang Lan, and C. W. Liu, "High Performance Ge Junctionless Gate-all-around NFETs with Simultaneous  $I_{on}=1235$   $\mu A/\mu m$  at  $V_{ov}=V_{DS}=1V$ ,  $SS=95$  mV/dec, high  $I_{on}/I_{off}=2E6$ , and Reduced Noise Power Density using S/D Dopant Recovery by Selective Laser Annealing," *p.842-845, International Electron Devices Meeting (IEDM), 2016.*

4. C. W. Liu, Jhih-Yang Yan, and Sun-Rong Jan, "Modeling and Simulation of TSV Induced Keep-out Zone Using Silicon Data," 13th International Conference on Solid-State Integrated Circuit & Technology (ICSICT 2016), Hangzhou, China, Oct. 25-28, 2016.

5. Jhih-Yang Yan, Sun-Rong Jan, Yi-Chung Huang, Huang-Siang Lan, C. W. Liu, Y.-H. Huang, Bigchoug Hung, K.-T. Chan, Michael Huang, and M.-T. Yang, "Compact Modeling and Simulation of TSV with Experimental Verification," *International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA)*, Hsinchu, Taiwan, 2016.

6. Jhih-Yang Yan, Pin-Shiang Chen, Jiun-Ian Pai, Wen-Wei Hsu and C. W. Liu, "The Incorporation of Electromagnetic Effects on Through Silicon Vias in TCAD Simulation" International Semiconductor Device Research Symposium, 2013.

7. I-Hsieh Wong, Yen-Ting Chen, Huang-Jhih Ciou, Yu-Sheng Chen, Jhih-Yang Yan and C.W. Liu, "Mobility Strain Response and Low Temperature Characterization of Ge p-MOSFETs," 71st Annual Device Research Conference.

## C: Patents (專利)

1. **Jhih-Yang Yan**, C. W. Liu, and Der-Chuan Lai, “Semiconductor device and transistor,” (US 9,679,893 B2).

2. **Jhih-Yang Yan**, Samuel C. Pan, C. W. Liu, Hung-Yu Yeh, and Da-zhi Zhang, “Three-Dimensional Transistor and Methods of Manufacturing Thereof,” (US 9,627,411 B2).

3. **Jhih-Yang Yan**, Fang-Liang Lu, and Chee Wee Liu, “Highly thermally conductive via structure in MEOL and BEOL for integrated circuits, and intradevice highly thermally conductive trench structure for multi-channel devices,” (application in progress).

4. **Jhih-Yang Yan**, Yu-Jiun Peng, H. H. Lin, and Chee Wee Liu, “Thermal via0s to cool down multi-channel devices,” (application in progress).

## 誌謝

於台大電子所求學的六年轉瞬已過，從碩士班一年級帶著衝勁卻不知前路有何物，到如今取得博士學位在相關領域嘗試貢獻己力，是得眾位師長、同儕、朋友、家人及合作單位的協助與鼓勵。感謝指導教授 劉致為老師在研究所期間的指導、包容及身教，舉凡：引導研究方向、指正思考邏輯、精確論文著述及訓練報告口條等皆使我裨益匪淺；您更多次於國外研討會中鞭策我在每日會後深入閱讀文獻、隔天與會發問及踴躍於報告結束後與國外學者討論交流研究成果，讓我的研究能與國外團隊之成果比肩。感謝口試委員：張廖貴術教授、林吉聰教授、李敏鴻教授、陳敏璋教授、張書通教授、廖洺漢教授、林楚軒教授以及高國興教授撥冗批閱論文初稿，並在口試時提供建議及方向。

感謝指導過我的學長們：孫宏彰、許文璋，在我碩一時於文獻蒐集、投影片製作及與合作公司彙報進度等方面給予幫助，使我能步上軌道迅速適應研究室生活。感謝在電二 514 那兩年多的時光，陳彥廷學長及翁翊軒學長讓我視野寬廣，於最前沿半導體元件及材料有更深刻的認識，並在生活中多了許多美好的回憶。感謝研究主題合作的同學及學弟：白君彥、黃奕中、賴德全及彭裕鈞，對於研究主題相關模擬上的幫助讓研究進度能順利推進；特別感謝彭裕鈞學弟，在我想法、直覺最豐富的兩年內，於實作上分擔許多壓力，我們才能將諸多假說及發想一一驗證並發表。感謝詹孫戎學長在應力應變模擬軟體上的教導，讓我免去許多不必要的嘗試。

感謝貫串博班研究生涯合作計畫的聯發科 PTD 部門的各位長官，在每個月的月報中，您們總針對我的研究進度以業界觀點提出問題、給予討論及必要的回饋支持。謝謝科技部與台積電-台大聯合研發中心的支持，使我在博士學位就讀期間專心致志，毋須為生活四處奔波。

最後要感謝我的父母對於我無條件的支持與愛護，我的求學期間與您們周遭所知、所遇的年輕人相比是如此的漫長，辛苦您們耐心的等待及一路陪伴。

## 摘要

本篇論文之目的為對三維電晶體之自發熱效應及三維積體電路穿矽連通柱造成之截止區提出模型並驗證。三維電晶體相比平面電晶體能提供更好的電性表現，然而單位面積功率的提高、材料的低熱導率皆使元件操作溫度升高，而元件溫度升高將導致元件表現衰退及可靠度問題，因此需要有準確的模型及驗證方法，才能監控三維電晶體中的自發熱行為；三維積體電路比起平面系統單晶片有許多優點：更大的頻寬、更短的導線長度、更高的製程選擇靈活度等，然而其所使用之穿矽連通柱於周遭矽晶圓上造成額外的應變將影響元件表現，因此需要有準確的截止區模型作為電路設計的參考。

在自然對流的狀況下，空氣與散熱表面的邊界需考慮一極大的額外熱阻，此熱阻並在晶片面朝上及晶片面朝下時造成元件散熱路徑的不同。為了能準確描述元件的本質自發熱行為，吾人藉由提出之「二階偽等溫面模型」精準的計算後段繞線熱阻，方得以於晶片面朝下及晶片面朝上的條件分別由總熱阻中萃取出鰭式電晶體的本質熱阻。由於鰭式電晶體具備一垂直非對稱結構，在晶片面朝上時，鰭式電晶體有比起晶片面朝下時更大的本質熱阻。藉由電熱模擬軟體，本篇論文指出因矽鋅源/汲極的低熱導係數，在一反向器中，p型元件比起n型元件有更高的操作溫度。反向器中的溫度高低及高溫持續時間可藉由輸出負載電容及元件電流大小來調變。吾人並指出當以交流訊號驅動反向器後，殘存於元件通道中及第一層金屬導線上的溫度比起操作時溫度皆過低，導致量測困難，以至於利用此溫度作為可靠度評估指標可能高估生命期。

本篇論文提出具分佈式熱阻熱容網路之「以積體電路為重點的模擬程式所建立的熱模型」(thermal SPICE)，以解決現有之雙時間常數及單時間常數模型皆無法準確預估交流元件的自發熱效應的問題。在鰭式電晶體中，熱時間常數並非單一數值，而是與輸入頻率成線性相關。邊界散射、合金散射及介面熱阻皆會提高溫度，並皆被本篇論文提出之 thermal SPICE 納入考量。藉由模組化鰭、金屬

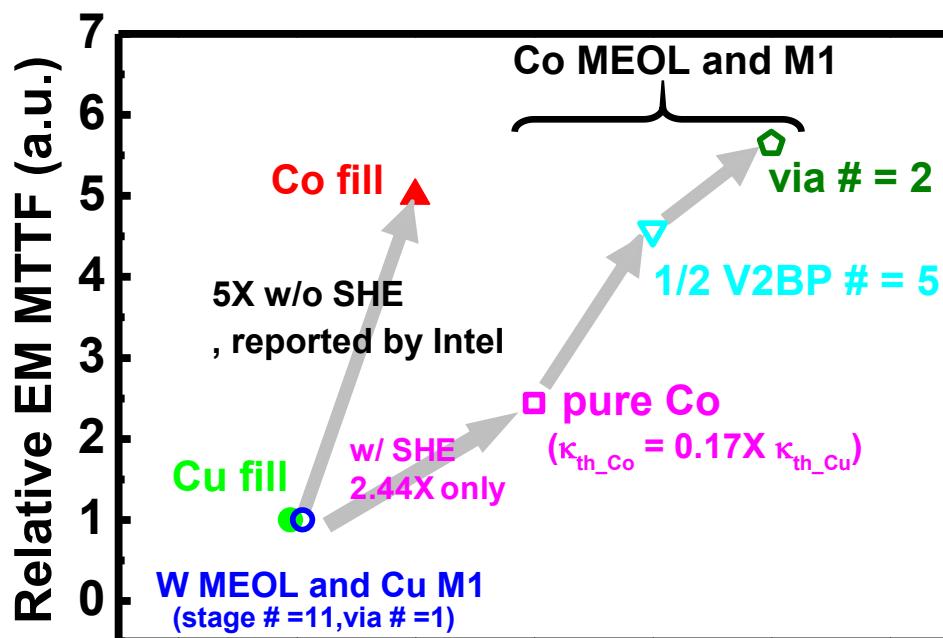

導線以及絕緣層，此熱模型具有元件布局及連線的彈性。於美商英特爾(intel)最先進的鰭式電晶體技術文獻指出，其將採用以鈷製成之導線，因鈷導線具有比銅導線長達 5 倍的電致遷移生命期，然而，當使用本論文提出之 thermal SPICE 對於環型震盪器進行模擬可發現，因鈷導線的熱傳導係數較低，以所得之鈷導線溫度進行理論投射，其電致遷移生命期在考慮金屬導線溫度上升的情況下對銅導線的優勢將減少至僅剩 2.44 倍。吾人發現模擬出之溫度可藉由額外擺放於環形震盪器上的第二層連通柱而降低。藉著第二層連通柱達成較低的鈷金屬溫度，可使得鈷導線比起原情況下的銅導線有 5.56 倍的電致遷移生命期。後段繞線及多鰭鰭式電晶體的熱阻可分別藉由加入額外的熱連通柱及額外的第零層連通柱來降低。

後段繞線完成後才製作之穿矽連通柱在附近的元件中施加額外的應變。本篇論文中於十二吋晶圓上量測 28 奈米節點元件因穿矽連通柱造成的導通電流變異。在此條件下，穿矽連通柱的應力場受到後段繞線絕緣層的影響，吾人觀察到非對稱之應力場並提出其模型。有別於先前的文獻，由於徑向應力及切線應力絕對值大小並不相同，穿矽連通柱造成的截止區並不對稱。藉由量測結果及三維有限元素分析模擬，吾人提出並驗證了一非對稱截止區模型。並推測因為內建應力大小的不同，n 型元件與 p 型元件被發現有大小相近的截止區。

關鍵字：自發熱效應、熱阻模型、鰭式電晶體、後段繞線、以積體電路為重點的模擬程式所建立的熱模型、穿矽連通柱、非對稱截止區

# Abstract

The purpose of this dissertation is to model the self-heating effect in 3D transistors and the keep-out zone of 3D-IC TSVs. 3D transistors provide better electrostatic as compared to planar transistors. However, the junction temperature increases in 3D transistors due to the increased power density and low thermal conductivity of materials. The high junction temperature degrades device performance and reliability. Accurate self-heating effect modeling can help to monitor the junction temperature for lifetime prediction. 3D-IC has the larger bandwidth, shorter interconnect length, and is more cost effective than 2D SoC. However, the through-silicon vias (TSVs) induce additional strain in nearby Si substrate. The strain field leads to the performance variation in the transistors neighboring to the TSV. Precise keep-out zone (KOZ) modeling is important for the circuit design.

With the accurate modeling of the thermal resistance of back-end-of-line (BEOL) by two-step pseudo isothermal plane, the intrinsic thermal resistances of FinFETs are extracted with face-down and face-up configurations. The intrinsic thermal resistance is affected by the direction of heat flow, and it is higher for the face-up configuration than the face-down configuration. The free convection of the air leads to a large thermal resistance. Due to the low thermal conductivity of SiGe S/D, the maximum temperature of pFET is found higher than nFET in an inverter. The output capacitive loading and

the current of the inverter can control the maximum temperature and the high temperature duration. With AC input, the temperature in M1 layer and the residual temperature in the channel are found too low as compared to the real device temperature.

Using the temperature on metal line as the  $T_j$  indicator may overestimate the reliability lifetime.

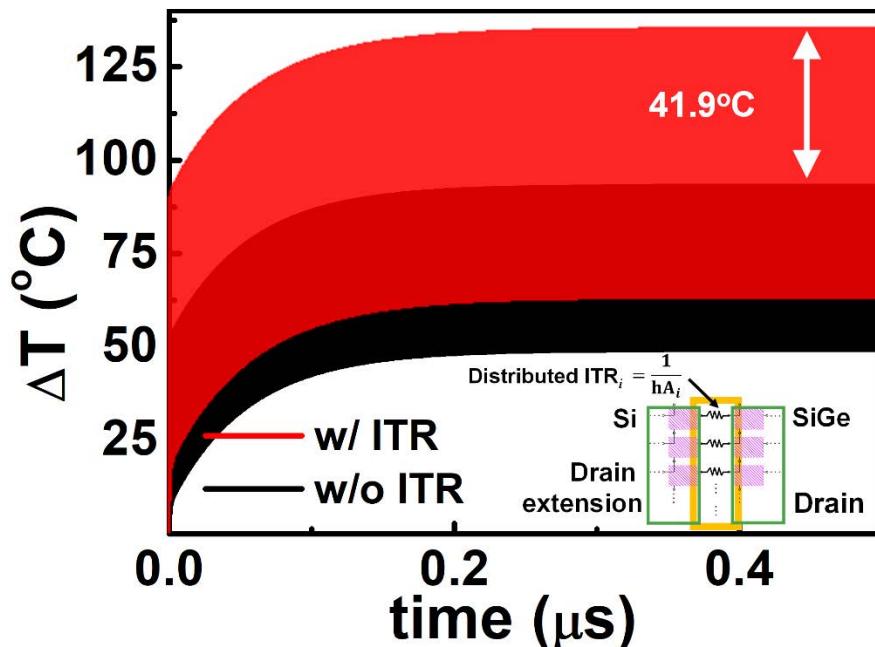

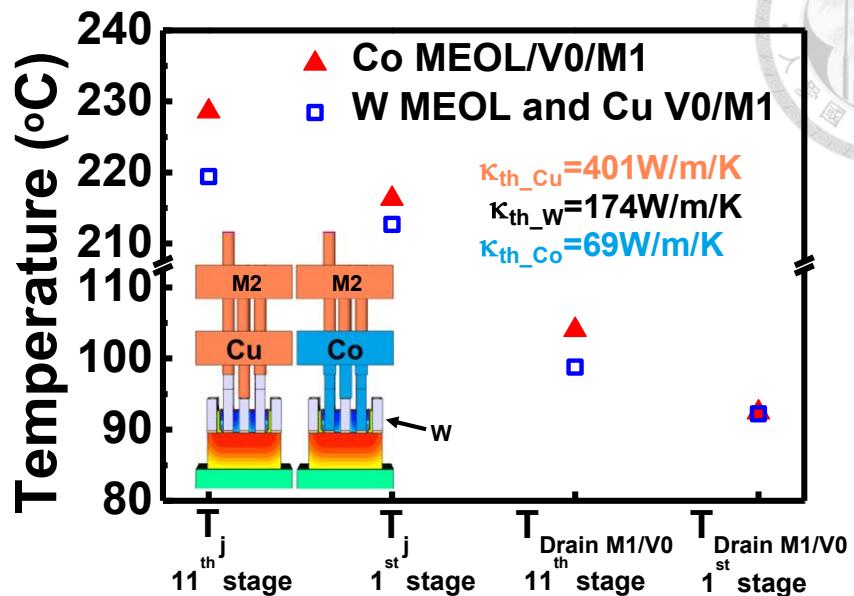

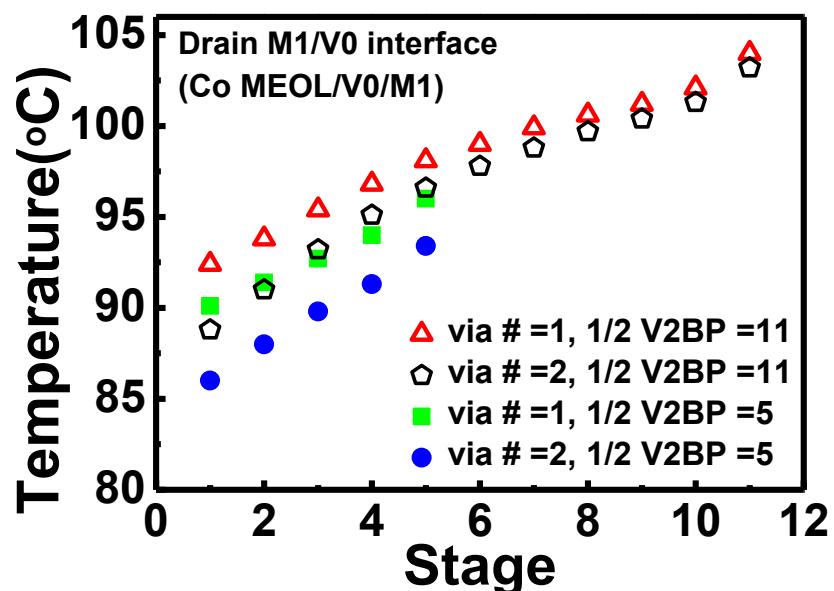

Two  $\tau_c$  and one  $\tau_c$  models failed to predict accurate AC self-heating results, and a thermal SPICE modeling with distributed  $R_{th}$ - $C_{th}$  network is proposed in this dissertation. In FinFETs, the thermal time constant of the hotspot is linearly dependent to input frequency instead of a constant. Boundary scattering, alloy scattering, and interfacial thermal resistance raise the temperature and are included in the SPICE. The device layout and interconnect routing flexibilities are achieved by using modularized components of fins, metals, and IMDs. The reported intrinsic electromigration improvement of Co interconnect (5X) could be countervailed (5X→2.44X) by the increasing  $T_{metal}$  with the projection of Black's theory.  $T_j$  (FinFET) and  $T_{metal}$  are lowered by placing additional V2 on the power line of a ring oscillator. The predicted EM MTTF of Co interconnect with the lowered  $T_{metal}$  by V2 insertion is ~5.65X of W/Cu interconnect. The  $R_{th,BEOL}$  and  $R_{th0,FinFET}$  can be reduced by adding thermal via in the BEOL and increasing via0s on the multi-fin FinFETs, respectively.

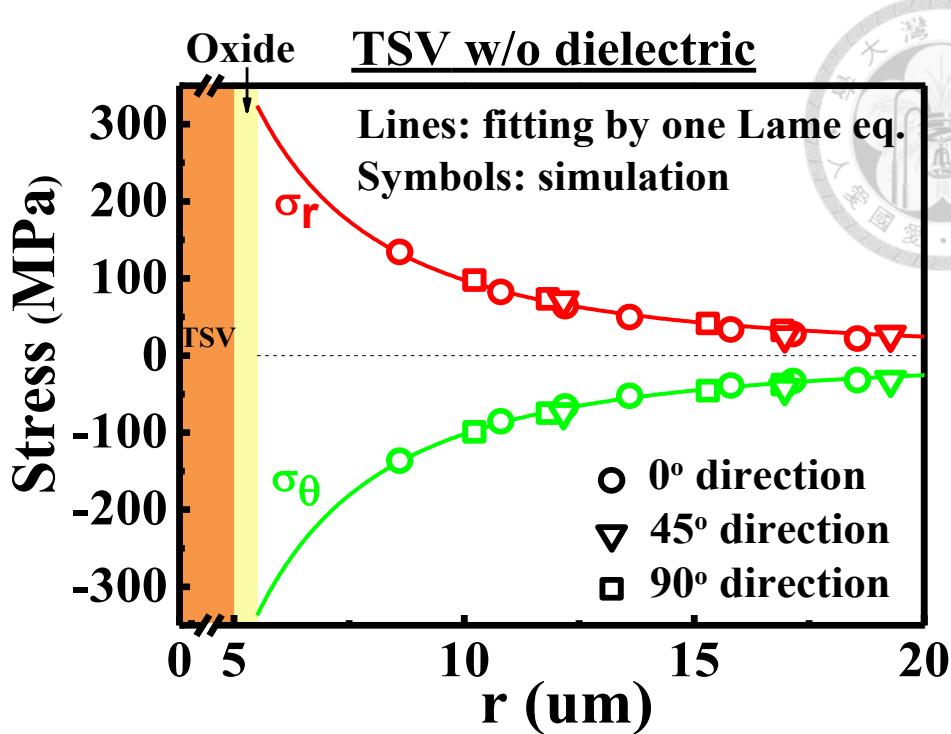

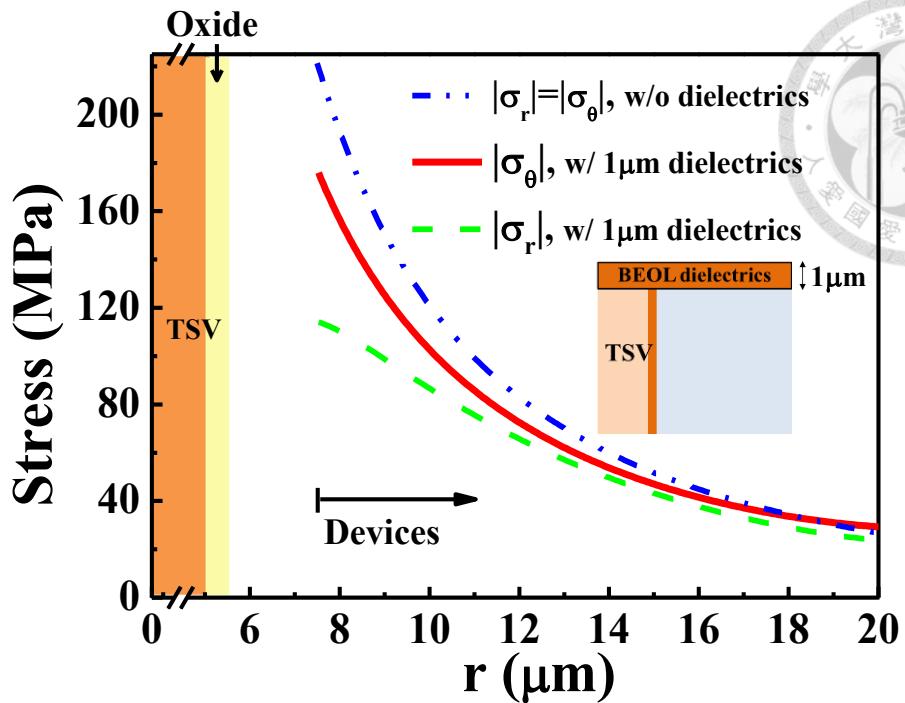

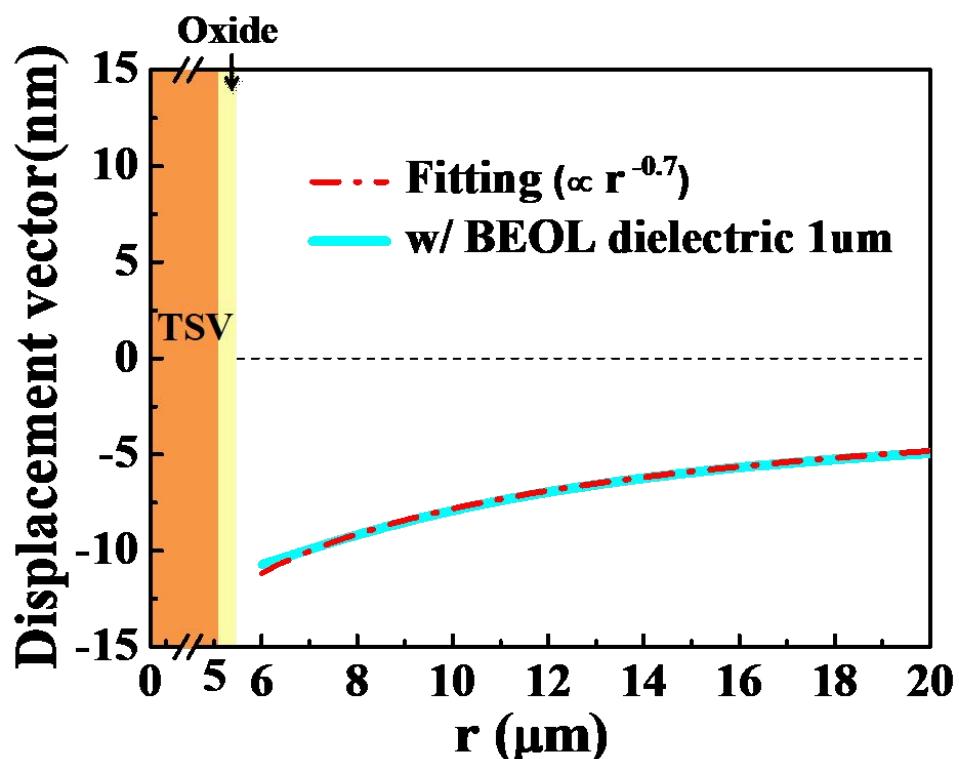

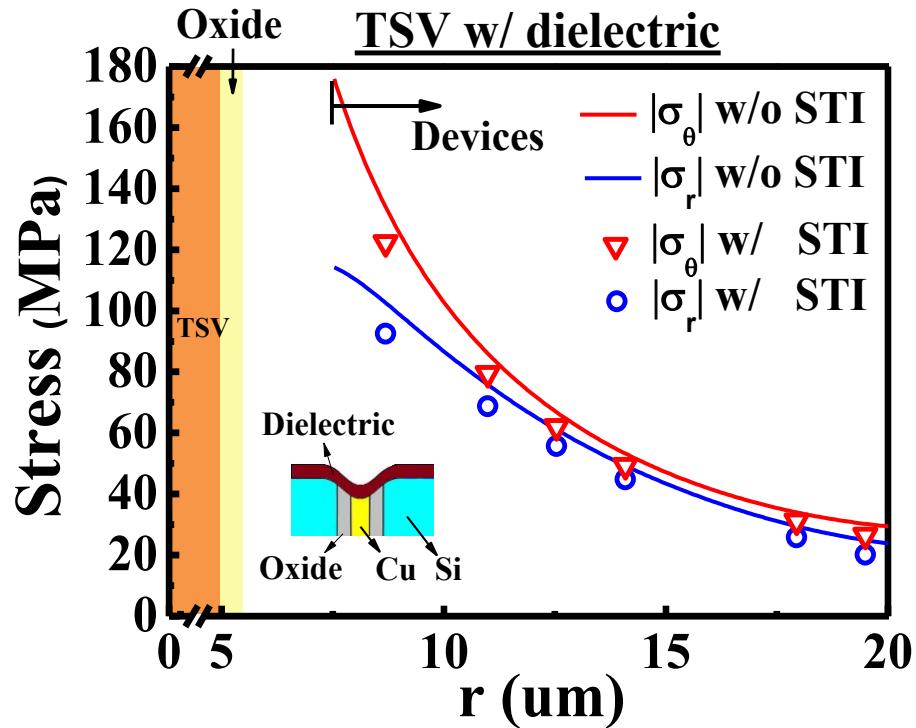

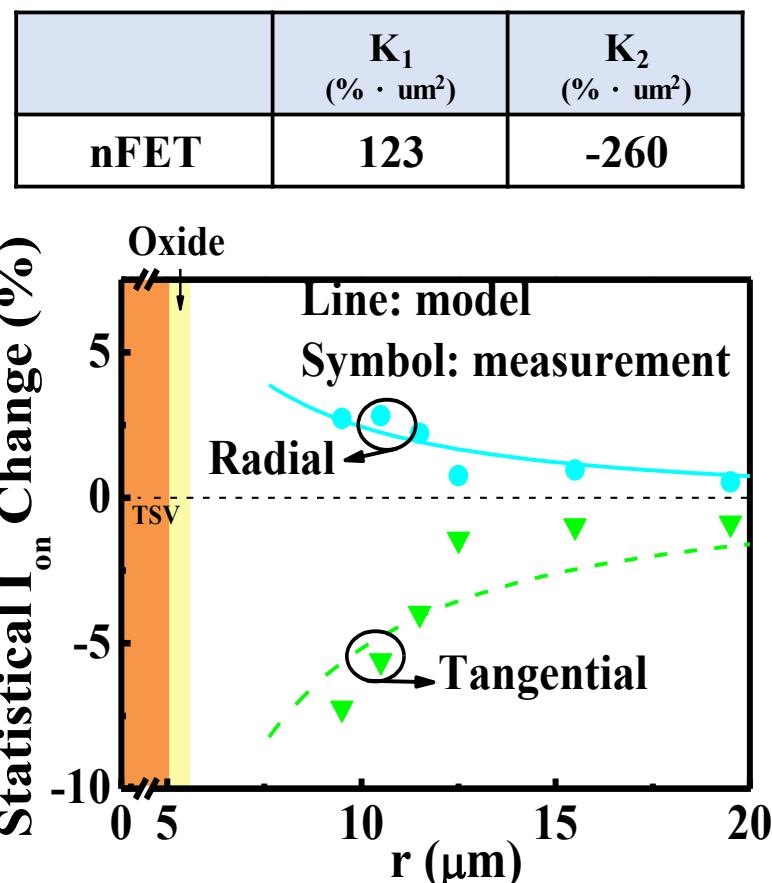

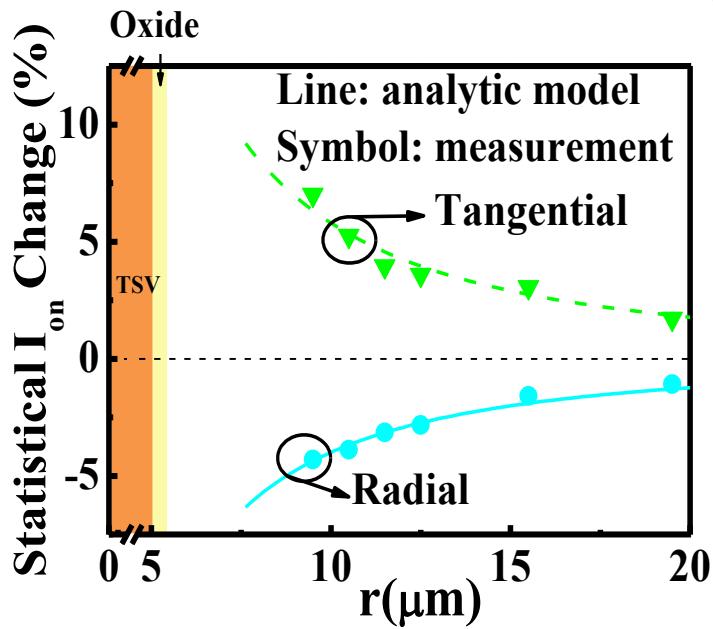

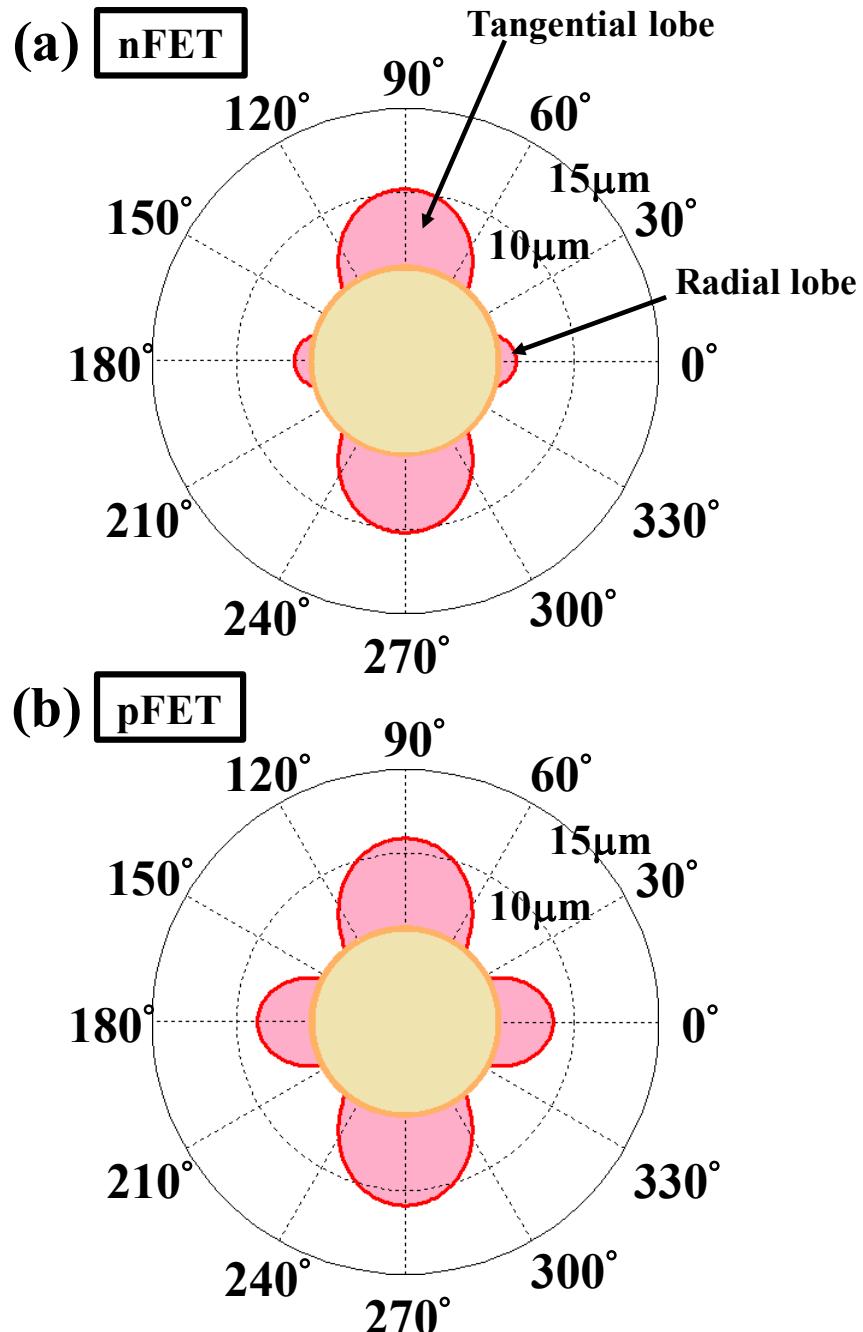

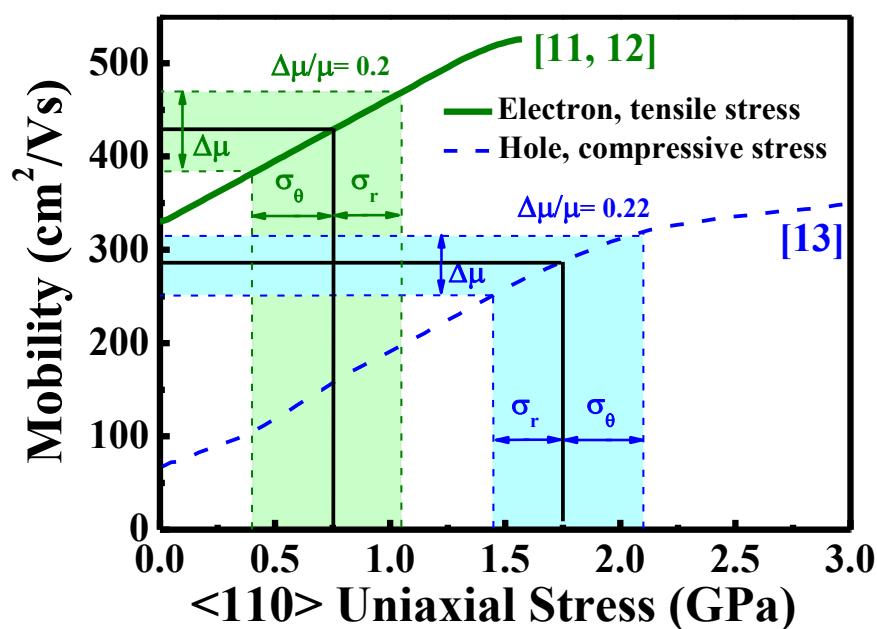

The via-last TSV induced additional strain in nearby devices. The  $I_{on}$  variation is

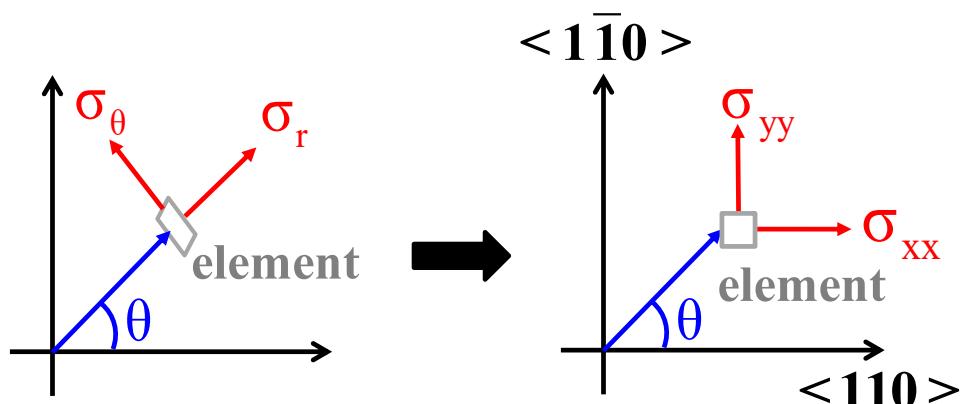

measured using 28nm node devices across 12 inch wafers. The stress field of TSV is affected by the BEOL dielectrics, and an asymmetric stress field is observed and modeled. The absolute value of radial stress ( $|\sigma_r|$ ) does not equal to that of tangential stress ( $|\sigma_\theta|$ ) and leads to the asymmetric KOZ, different from previously reported. With the help of experiment data and 3D finite element analysis (FEA) simulation, a modified KOZ model with the asymmetric radial and tangential stress field is proposed, fitted, and verified. Different internal stress in device channel leads to comparable KOZ size for nFETs and pFETs.

Keywords: Self-heating effect, thermal resistance modeling, FinFET, BEOL, thermal SPICE modeling, through-silicon via, asymmetric keep-out zone.

# Table of Contents

|                                                                                              |           |

|----------------------------------------------------------------------------------------------|-----------|

| <b>Chapter 1 Introduction .....</b>                                                          | <b>1</b>  |

| 1.1 Motivation.....                                                                          | 1         |

| 1.2 Dissertation Organization .....                                                          | 3         |

| 1.3 References.....                                                                          | 6         |

| <b>Chapter 2 Thermal Resistance Modeling of Intrinsic FinFETs and Back-end-of-line .....</b> | <b>10</b> |

| 2.1 Introduction.....                                                                        | 10        |

| 2.2 Electro-thermal Simulation and Boundary Conditions.....                                  | 12        |

| 2.2.1 FinFET Structure and Simulation Settings .....                                         | 12        |

| 2.2.2 Conventional Measurement and Flip-chip Packaging .....                                 | 14        |

| 2.3 Thermal Resistance Modeling of BEOL.....                                                 | 17        |

| 2.3.1 Thermal Resistance Circuit.....                                                        | 17        |

| 2.3.2 Two-step Pseudo Isothermal Plane Modeling .....                                        | 19        |

| 2.4 Thermal Resistance Modeling of FinFET.....                                               | 23        |

| 2.4.1 Intrinsic Thermal Resistance of FinFET .....                                           | 23        |

| 2.4.2 Layout and Geometry Dependence of Intrinsic Thermal Resistance .....                   | 25        |

| 2.5 Summary .....                                                                            | 29        |

| 2.6 References.....                                                                          | 30        |

## Chapter 3 Transient Thermal Simulation of Inverters with Capacitive Loading Effects ..... 33

|                                                                 |    |

|-----------------------------------------------------------------|----|

| 3.1 Introduction.....                                           | 33 |

| 3.2 Self-heating Effect in FinFETs with Transient Input .....   | 34 |

| 3.3 Electrical Characteristics of the Inverter.....             | 34 |

| 3.4 Self-heating and Output Loading Effect in Inverters.....    | 37 |

| 3.4.1 Output Capacitive Loading Effects on $T_j$ .....          | 39 |

| 3.4.2 Drive Current, $T_j$ , and High Temperature Duration..... | 40 |

| 3.4.3 Layout Size Effects of Inverters .....                    | 40 |

| 3.5 SHE of Inverters with AC input.....                         | 43 |

| 3.5.1 Temperature Distribution on M1 Layer.....                 | 43 |

| 3.5.2 Residual Temperature in the Channel.....                  | 45 |

| 3.6 Summary .....                                               | 46 |

| 3.7 References.....                                             | 47 |

## Chapter 4 Comprehensive Thermal SPICE Modeling of FinFETs and Back-end-of-line ..... 48

|                                                                |    |

|----------------------------------------------------------------|----|

| 4.1 Introduction.....                                          | 48 |

| 4.2 Frequency Dependent Thermal Time Constant in FinFETs ..... | 49 |

| 4.2.1 Issues of Lumped $R_{th}$ - $C_{th}$ models.....         | 49 |

| 4.2.2 Thermal time constant of scaled FinFETs .....            | 51 |

|                                                               |    |

|---------------------------------------------------------------|----|

| 4.3 Thermal SPICE Modeling of FinFETs .....                   | 52 |

| 4.3.1 Equivalent Circuit Models in SPICE .....                | 52 |

| 4.3.2 Modularized Fin and Power Distribution Matrix.....      | 55 |

| 4.4 DC Validation of Thermal SPICE Model .....                | 58 |

| 4.4.1 Distributed $R_{th}$ Verification .....                 | 58 |

| 4.4.2 Temperature on MEOL.....                                | 59 |

| 4.4.3 Layout Flexibility of Thermal SPICE Model .....         | 60 |

| 4.5 Including Interfacial Thermal Resistance into SPICE ..... | 61 |

| 4.6 Summary .....                                             | 62 |

| 4.7 References.....                                           | 63 |

## **Chapter 5 Circuit Level Reliability Evaluation of Ring Oscillators using 10nm FinFETs .....** 66

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| 5.1 Introduction.....                                                            | 66 |

| 5.2 AC Validation of Thermal SPICE Model and ITR Effects on Temperature .....    | 67 |

| 5.3 Transient Self-heating Effects in FinFETs .....                              | 69 |

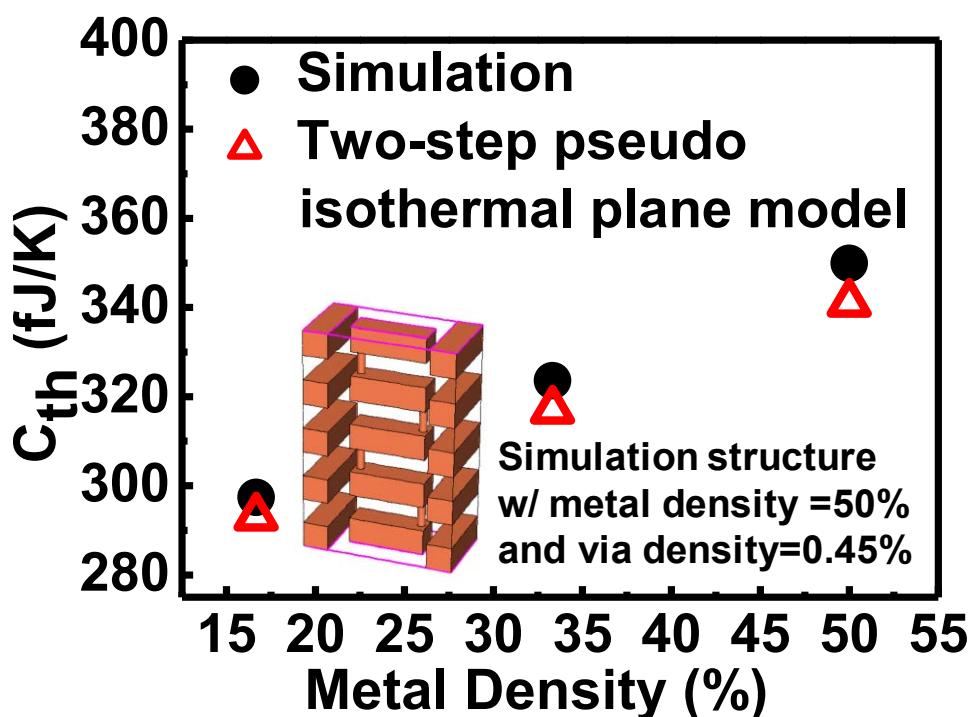

| 5.3.1 Thermal Capacitance Modeling of BEOL .....                                 | 69 |

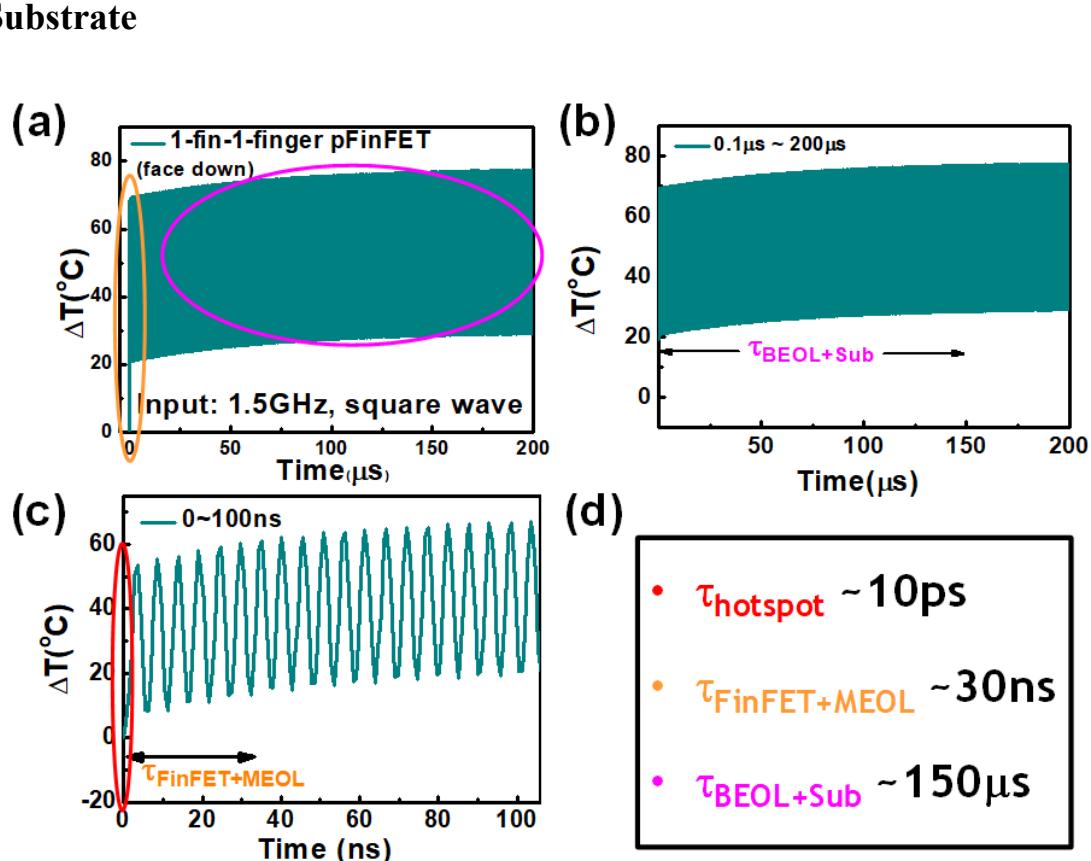

| 5.3.2 Thermal Time Constants in FinFET, MEOL, BEOL, and Substrate.....           | 71 |

| 5.4 Transient Self-heating Effects on Ring Oscillator .....                      | 72 |

| 5.5 Cobalt Interconnect and Electro-migration Mean Time to Failure Prediction .. | 75 |

| 5.6 Innovations to Improve Heat Dissipation of Device and BEOL .....             | 78 |

| 5.6.1 Additional Via0 to Lower Intrinsic Thermal Resistance .....                | 78 |

|                                                     |    |

|-----------------------------------------------------|----|

| 5.6.2 Highly Thermally Conductive Via in BEOL ..... | 80 |

| 5.7 Summary .....                                   | 83 |

| 5.8 References .....                                | 84 |

## **Chapter 6 Asymmetric Keep-out Zone Modeling of Through-Silicon Via with Experimental Verification.....85**

|                                                         |    |

|---------------------------------------------------------|----|

| 6.1 Introduction .....                                  | 85 |

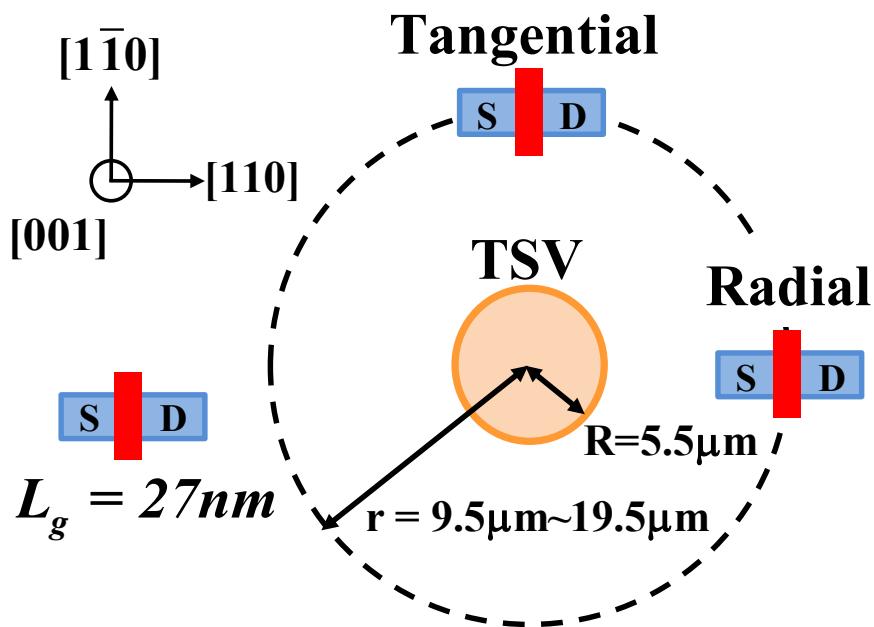

| 6.2 TSV and Device Layout.....                          | 86 |

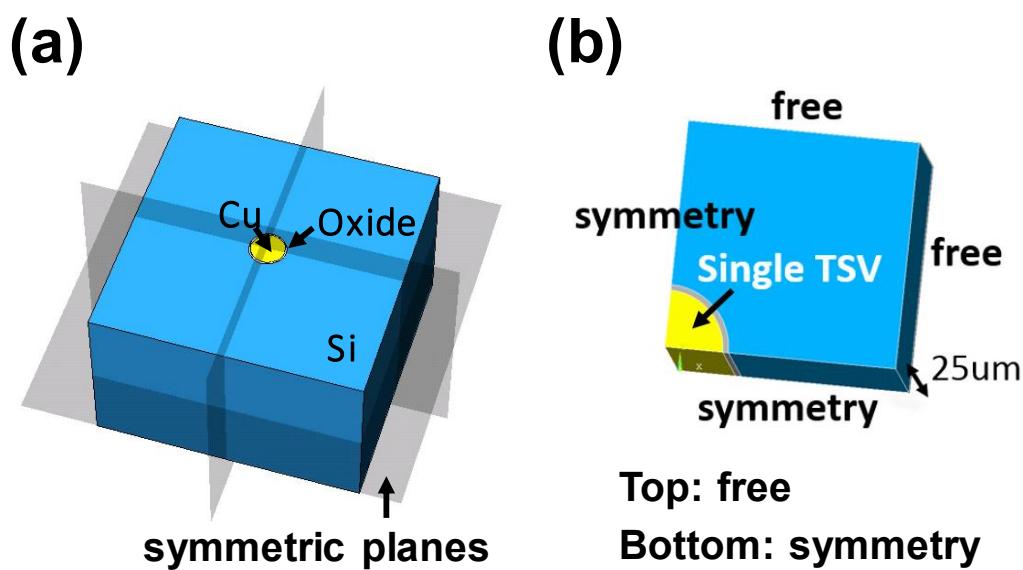

| 6.3 3D Finite-element Analysis Simulation.....          | 87 |

| 6.3.1 Simulation Settings .....                         | 87 |

| 6.3.2 STI Pattern Effects.....                          | 89 |

| 6.4 Modeling of Stress Field on Silicon Surface .....   | 90 |

| 6.4.1 BEOL Dielectric Effects on the Stress Field ..... | 90 |

| 6.4.2 Modeling the asymmetric stress field .....        | 91 |

| 6.5 Asymmetric Keep-out Zone of Via-last TSV .....      | 93 |

| 6.5.1 Analytic Model of KOZ.....                        | 93 |

| 6.5.2 KOZs of nFET and pFET .....                       | 95 |

| 6.6 Summary .....                                       | 99 |

| 6.7 Reference .....                                     | 99 |

## **Chapter 7 Summary and Future Work.....103**

|                   |     |

|-------------------|-----|

| 7.1 Summary ..... | 103 |

|-------------------|-----|

# List of Figures

|                                                                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

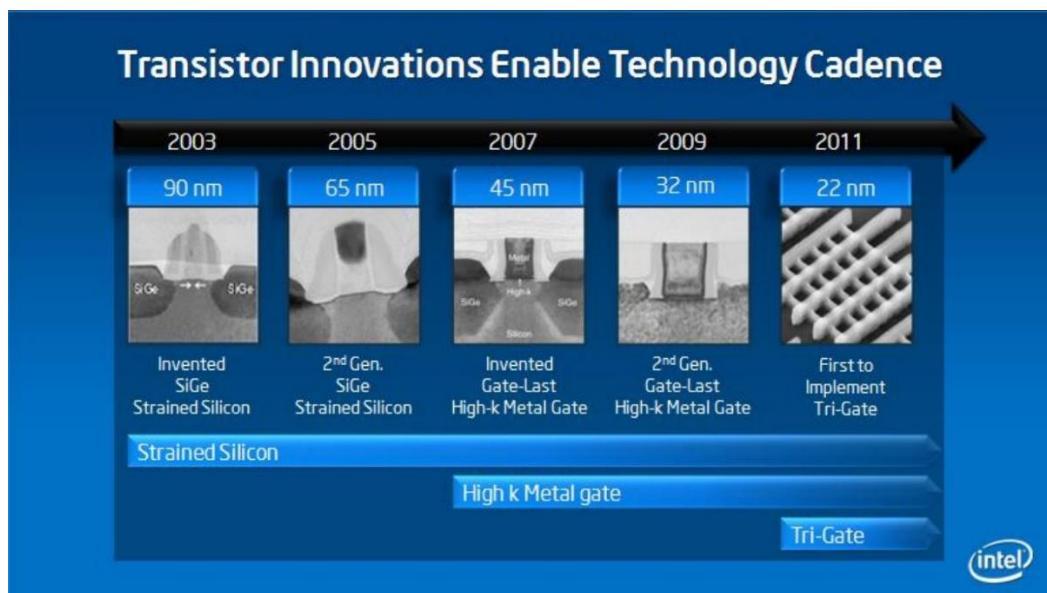

| <b>Fig. 1. 1</b> Transistor performance boosters since 90nm node (Source: Intel Corp.) .....                                                           | 2  |

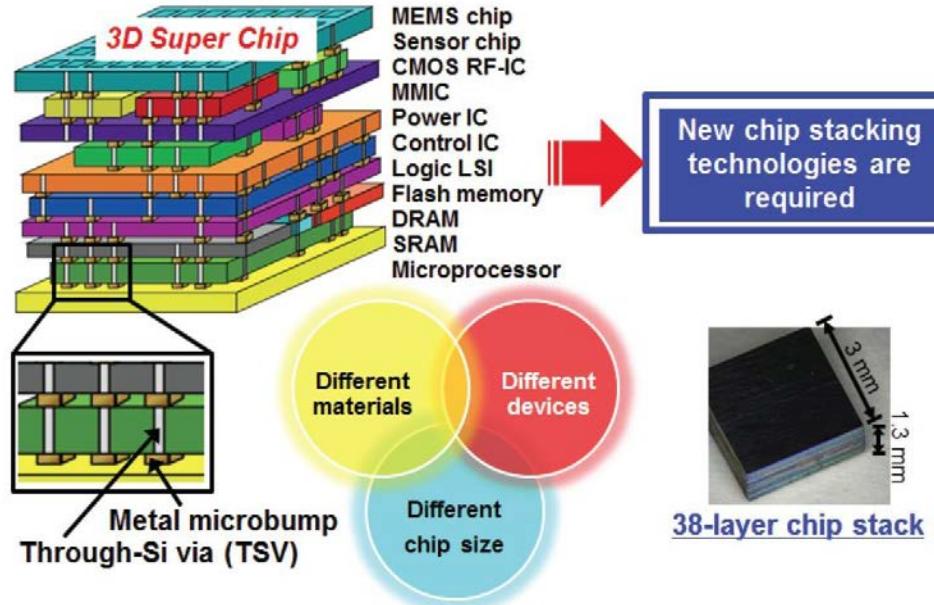

| <b>Fig. 1. 2</b> 3D Super chip by TSV [1.11] .....                                                                                                     | 3  |

| <b>Fig. 2. 1 (a)</b> FinFET structure and thermal resistances of BEOL and substrate, .....                                                             | 13 |

| <b>Fig. 2. 2</b> Heat dissipation paths in <b>(a)</b> conventional measurement (face-up) and <b>(b)</b> flip-chip packaging (face-down).....           | 16 |

| <b>Fig. 2. 3</b> Simulation structure, boundary condition, and thermal resistances of <b>(a)</b> face-up and <b>(b)</b> face-down configurations ..... | 17 |

| <b>Fig. 2. 4</b> Thermal resistance circuit of device, BEOL, substrate, and free convection                                                            | 18 |

| <b>Fig. 2. 5</b> Simulated temperature contour in BEOL .....                                                                                           | 19 |

| <b>Fig. 2. 6</b> Two-step pseudo isothermal plane modeling of $R_{th, BEOL}$ with the corrected IMD thickness .....                                    | 20 |

| <b>Fig. 2. 7</b> Simulation structure and settings for $R_{th, BEOL}$ extraction .....                                                                 | 21 |

| <b>Fig. 2. 8</b> Comparison of $R_{th, BEOL}$ models with simulation results .....                                                                     | 22 |

| <b>Fig. 2. 9</b> Thermal resistance of the entire device and a single channel .....                                                                    | 23 |

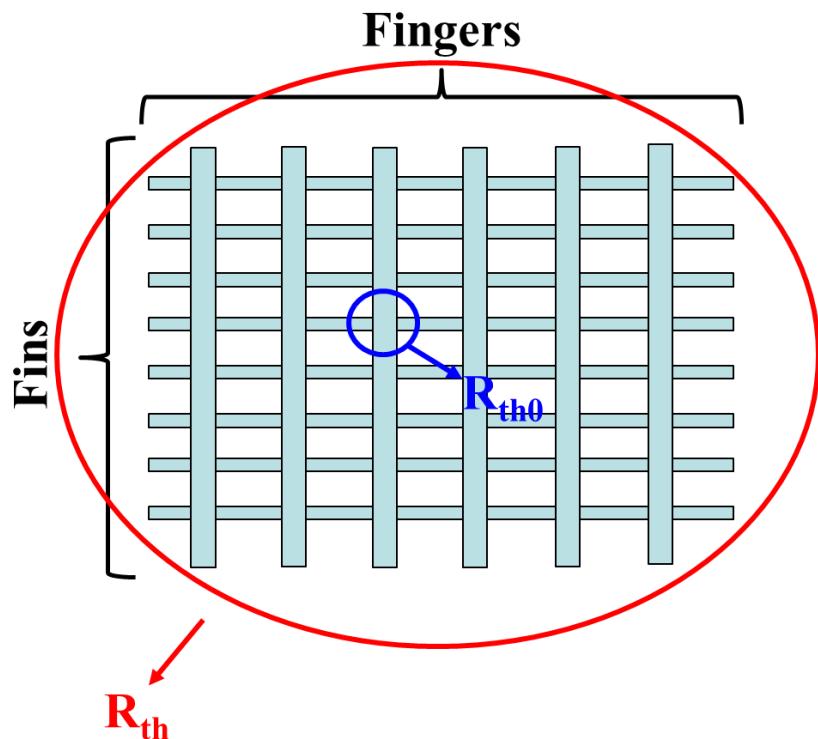

| <b>Fig. 2. 10 (a)</b> $R_{th0, total}$ and <b>(b)</b> $R_{th0, device}$ with different substrate thickness.....                                        | 24 |

| <b>Fig. 2. 11</b> $R_{th0, device}$ fitting as a function of fin number for face-up and face-down configurations .....                                 | 27 |

| <b>Fig. 2. 12</b> $R_{th0, device}$ fitting as a function of finger number for face-up and face-down configurations .....                              | 27 |

| <b>Fig. 2. 13</b> $R_{th0, device}$ fitting as a function of fin height for face-up and face-down configurations .....                                 | 28 |

| <b>Fig. 3. 1 (a)</b> Cross-sectional temperature distribution and <b>(b)</b> transient $T_j$ response with different input pulse width .....           | 35 |

| <b>Fig. 3. 2 (a)</b> Measured input and output voltage of an inverter and <b>(b)</b> the transient                                                     |    |

|                                                                                                                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| responses of output current and simulated $T_j$ of the inverter .....                                                                                                                                        | 36 |

| <b>Fig. 3. 3</b> Simulation structure of the inverter with face-down configuration .....                                                                                                                     | 37 |

| <b>Fig. 3. 4</b> Cross-sectional temperature distribution in the inverter .....                                                                                                                              | 38 |

| <b>Fig. 3. 5</b> Transient responses of input power and the $T_{max}$ in the inverter .....                                                                                                                  | 38 |

| <b>Fig. 3. 6</b> The device temperature of inverters with different $C_{load}$ .....                                                                                                                         | 39 |

| <b>Fig. 3. 7</b> $T_{max}$ of an inverter (2-fin-1-finger n/pFinFETs) with different $I_{on}$ , and <b>(b)</b> the temperature evolution .....                                                               | 41 |

| <b>Fig. 3. 8</b> $T_{max}$ vs finger number with <b>(a)</b> the capacitive loading of 5fF and <b>(b)</b> the capacitive loading proportional to layout size .....                                            | 42 |

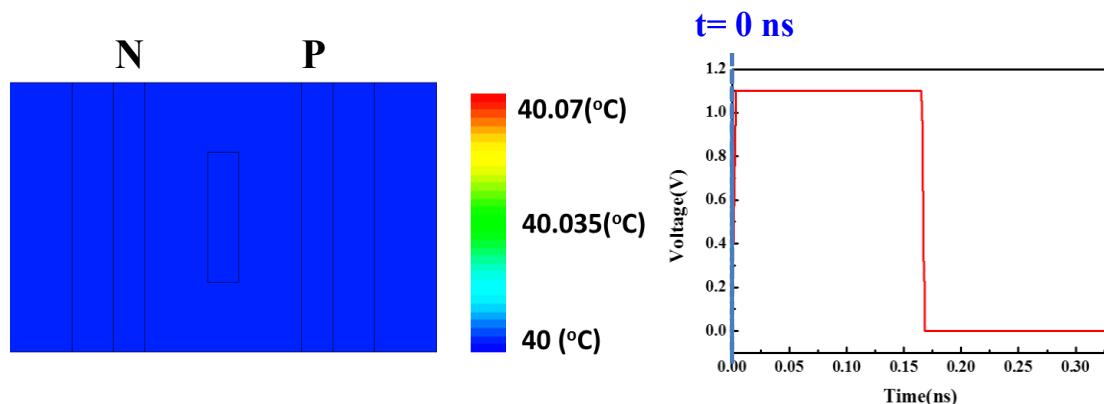

| <b>Fig. 3. 9</b> Snap shot on the M1 layer at $t= 0$ ns .....                                                                                                                                                | 43 |

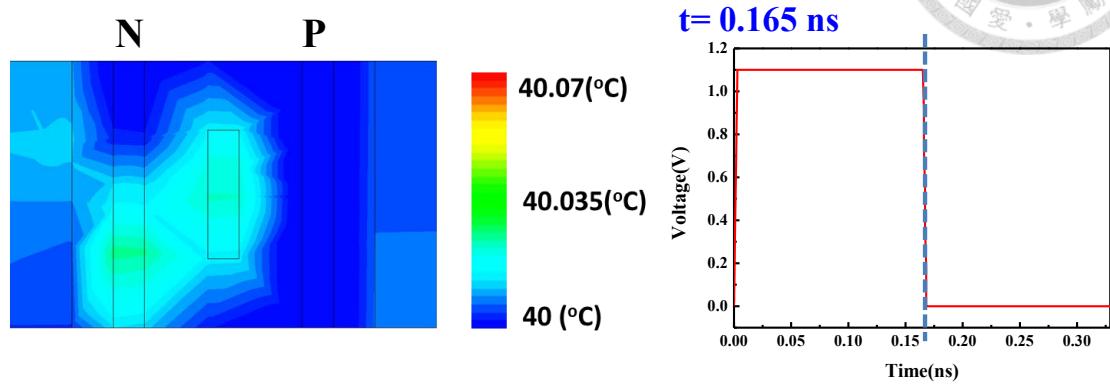

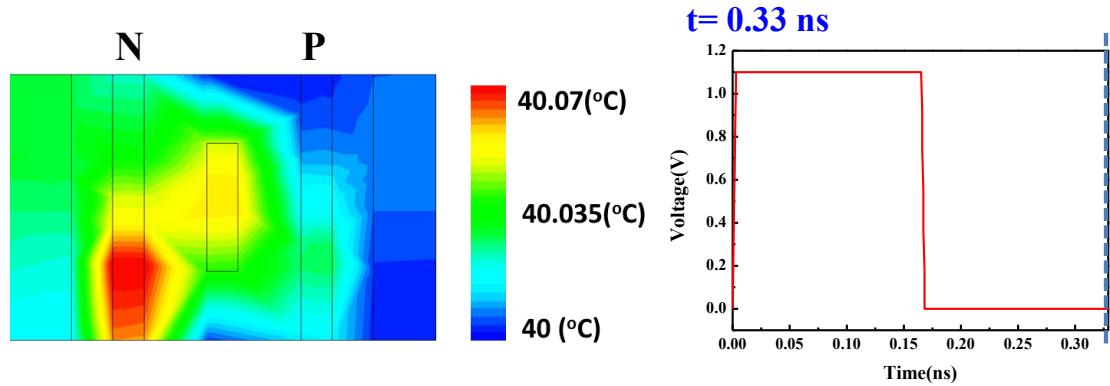

| <b>Fig. 3. 10</b> Snap shot on the M1 layer at $t= 0.165$ ns .....                                                                                                                                           | 44 |

| <b>Fig. 3. 11</b> Snap shot on the M1 layer at $t= 0.33$ ns .....                                                                                                                                            | 44 |

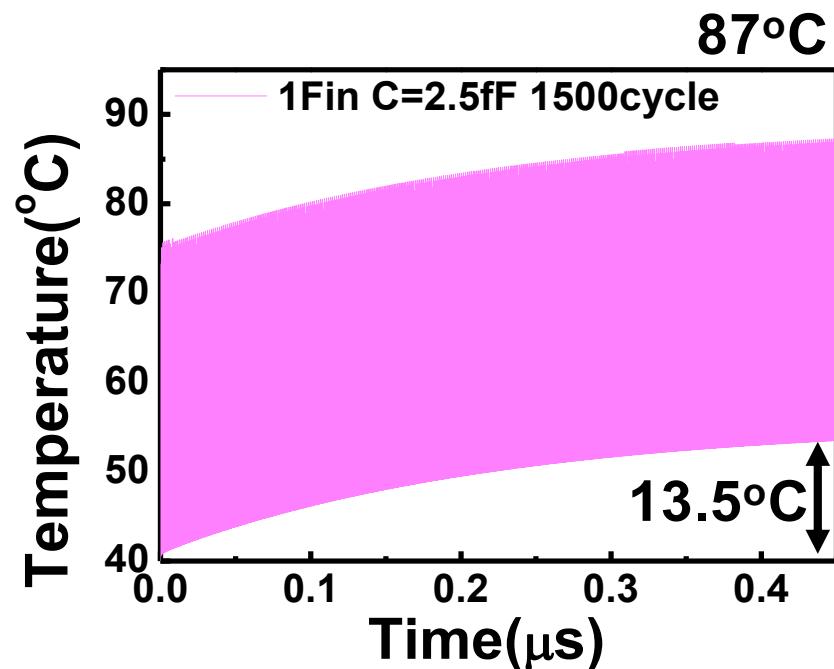

| <b>Fig. 3. 12</b> Residual temperature in the channel of an inverter with $C_{load} = 2.5$ fF after 1500 cycles.....                                                                                         | 45 |

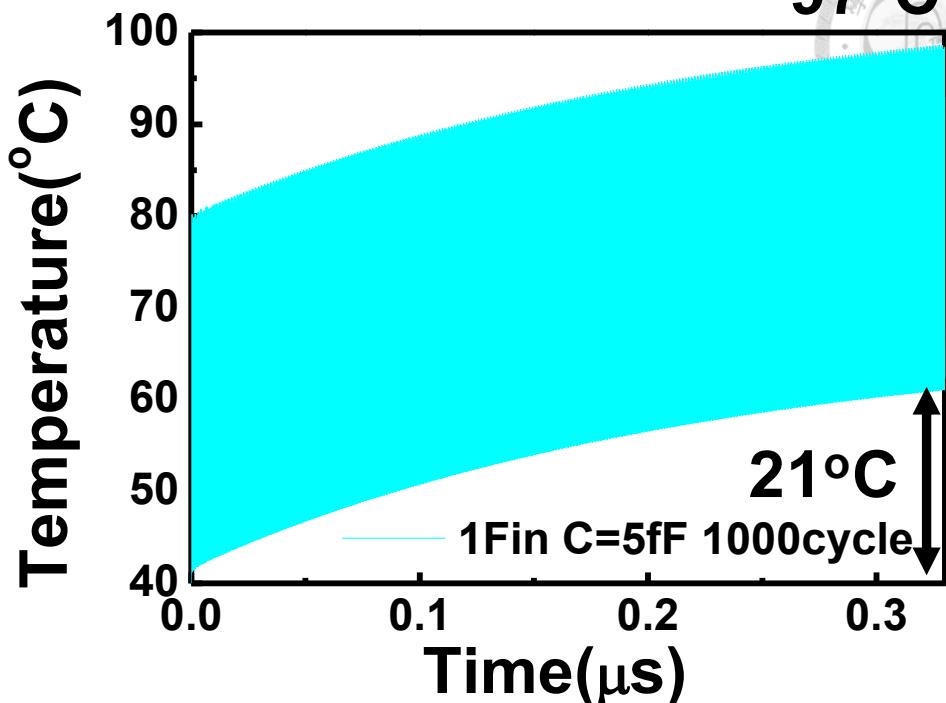

| <b>Fig. 3. 13</b> Residual temperature in the channel of an inverter with $C_{load} = 5$ fF after 1000 cycles.....                                                                                           | 46 |

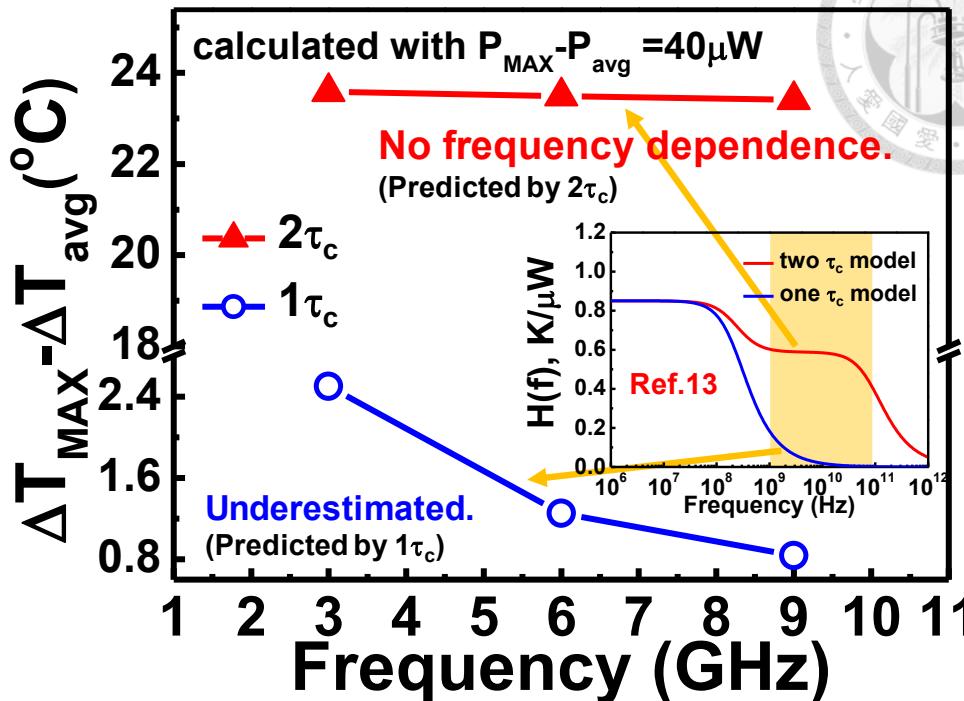

| <b>Fig. 4. 1</b> $\Delta T_{MAX}-\Delta T_{avg}$ calculated by $H(f)$ (differential $R_{th}$ ) times $(P_{MAX}-P_{avg})$ versus frequency. <b>(inset)</b> $H(f)$ of a FinFET by lumped $R_{th}-C_{th}$ ..... | 50 |

| <b>Fig. 4. 2</b> AC thermal response of a 14nm FinFET <b>(inset)</b> AC response in one period                                                                                                               | 50 |

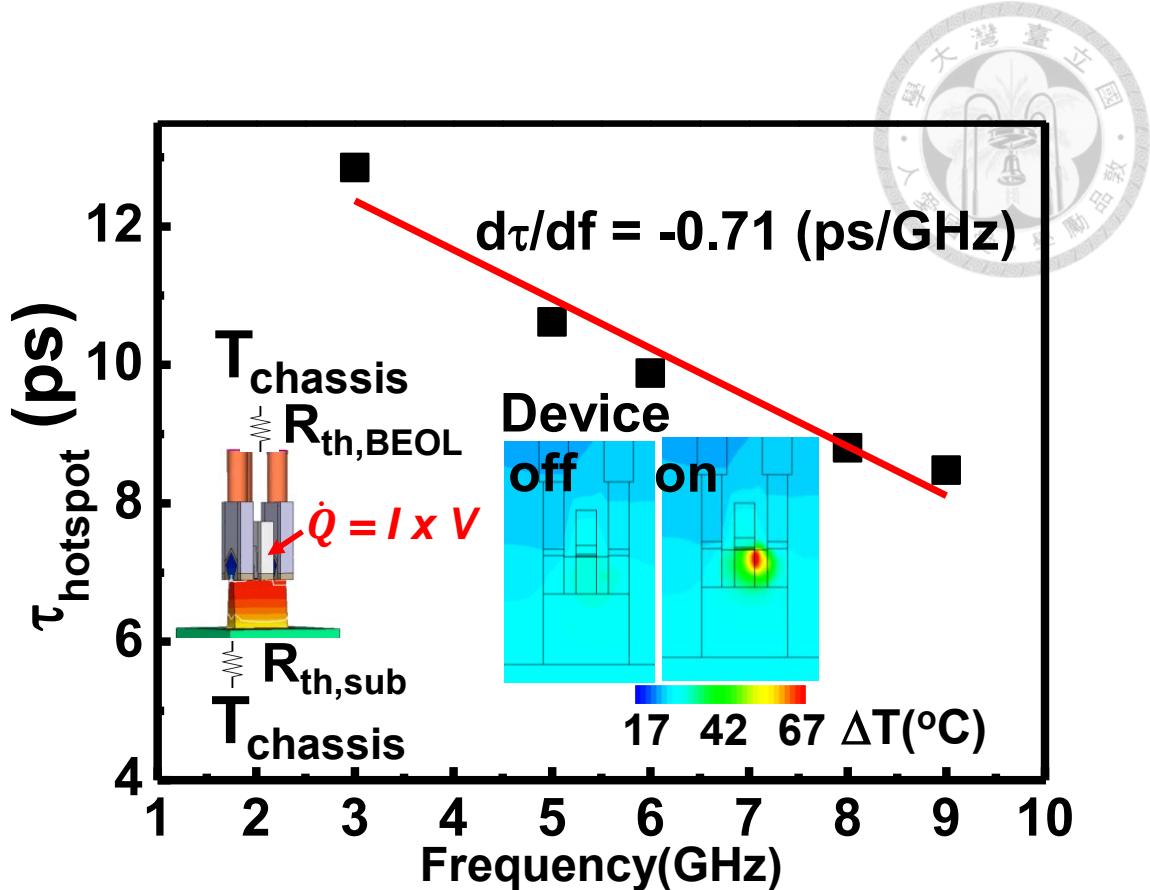

| <b>Fig. 4. 3</b> $\tau_{hotspot}$ versus input frequency. <b>(inset)</b> Simulated FinFET with corresponding thermal resistances and the localized hotspot in AC simulation.....                             | 52 |

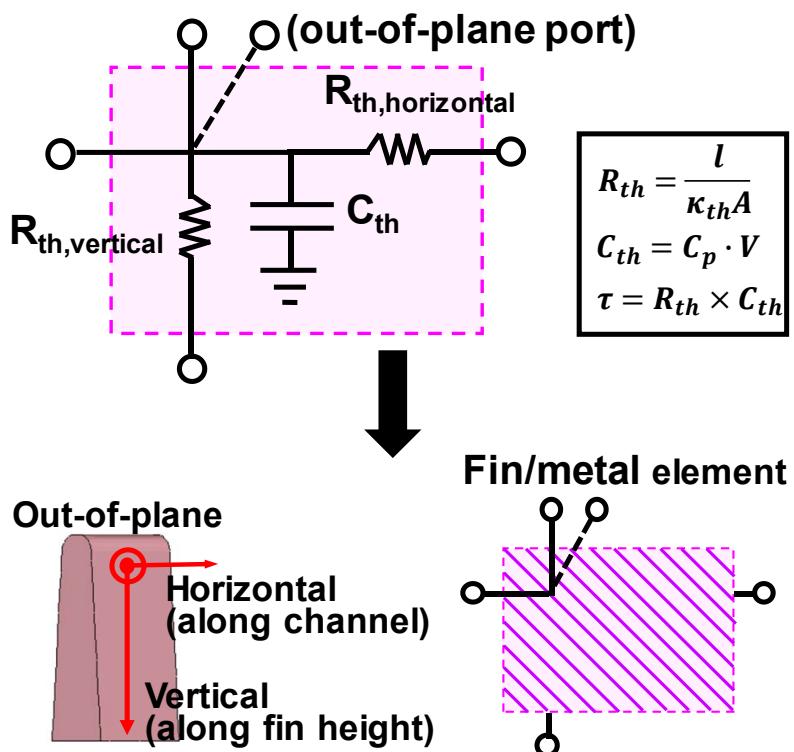

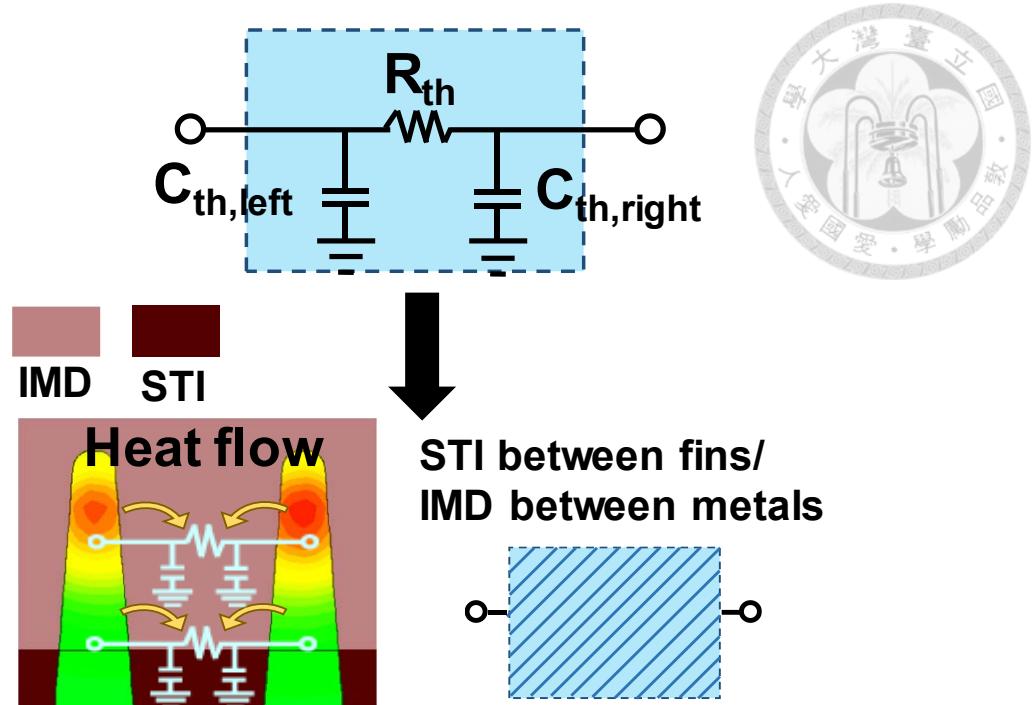

| <b>Fig. 4. 4</b> Equivalent circuit models and simplified color symbols of fin or metal .....                                                                                                                | 53 |

| <b>Fig. 4. 5</b> Equivalent circuit models and simplified color symbols of STI between fins or IMD between metals.....                                                                                       | 54 |

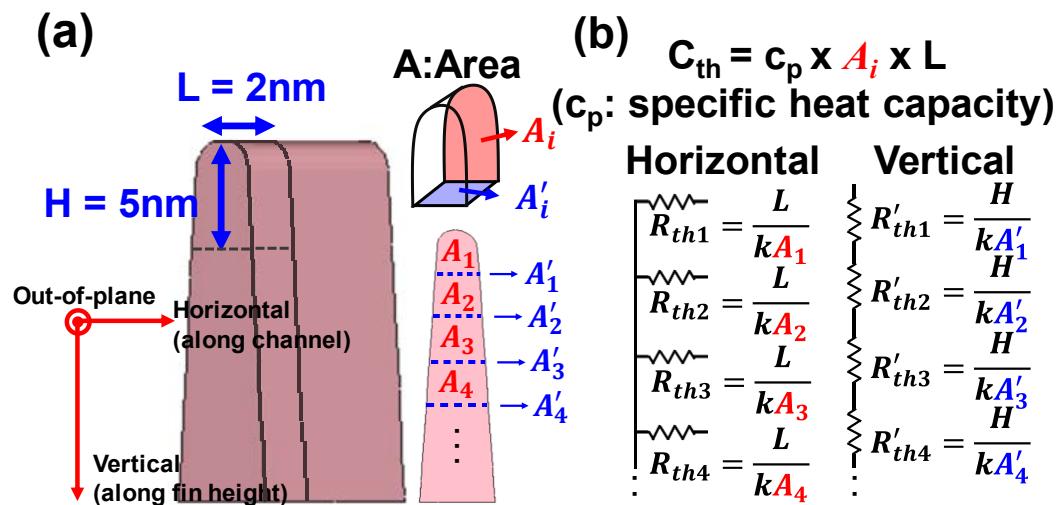

| <b>Fig. 4. 6</b> <b>(a)</b> Element size in a FinFET channel and <b>(b)</b> the thermal capacitance, horizontal, and vertical thermal resistances to form a distributed $R_{th}-C_{th}$ model .....          | 54 |

|                                                                                                                                                                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                         |    |

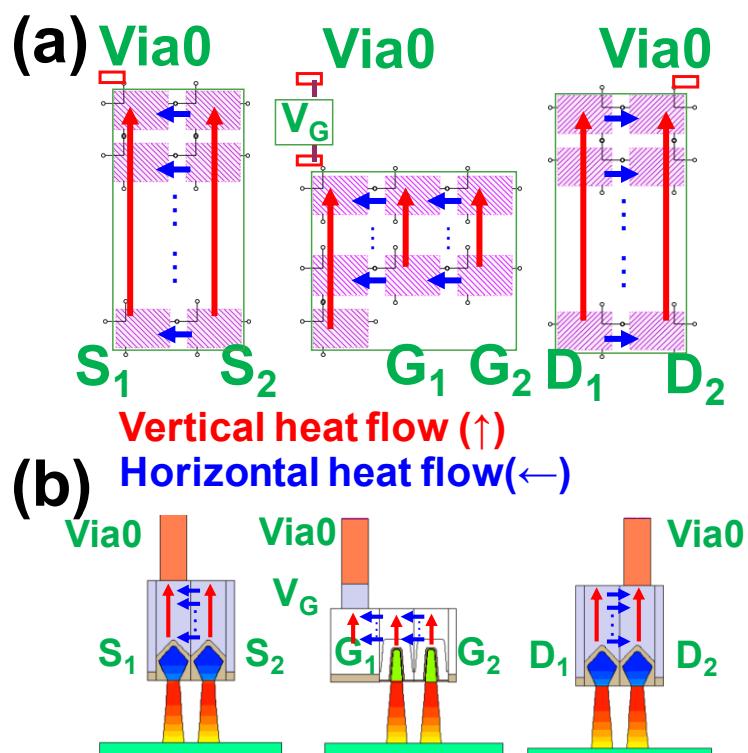

| <b>Fig. 4. 7 (a)</b> SPICE modules of source, gate, and drain as well as corresponding MEOLs, and <b>(b)</b> TCAD counterparts .....                                                                                                                       | 55 |

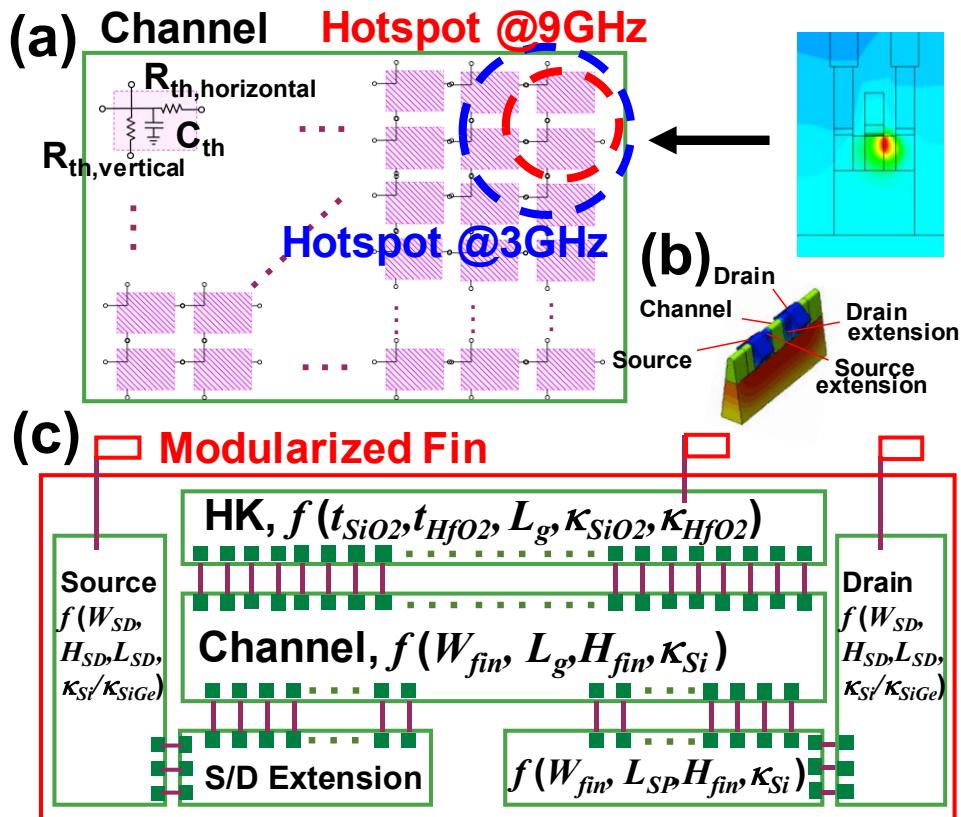

| <b>Fig. 4. 8 (a)</b> $R_{th}$ - $C_{th}$ network of channel region with schematically drawn hotspot at 3GHz and 9GHz <b>(b)</b> Geometry of fin including the SiGe S/D, and <b>(c)</b> the geometry based modularized fin .....                            | 56 |

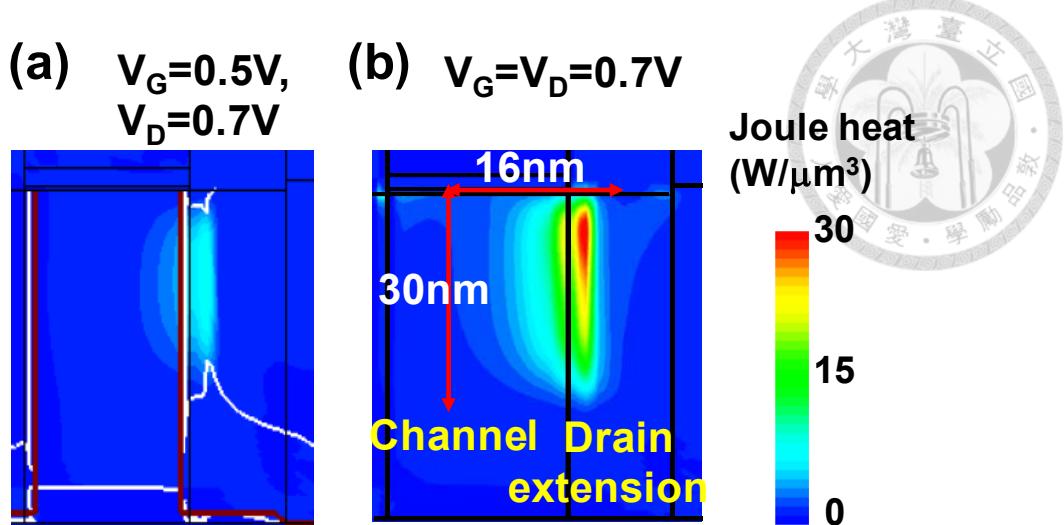

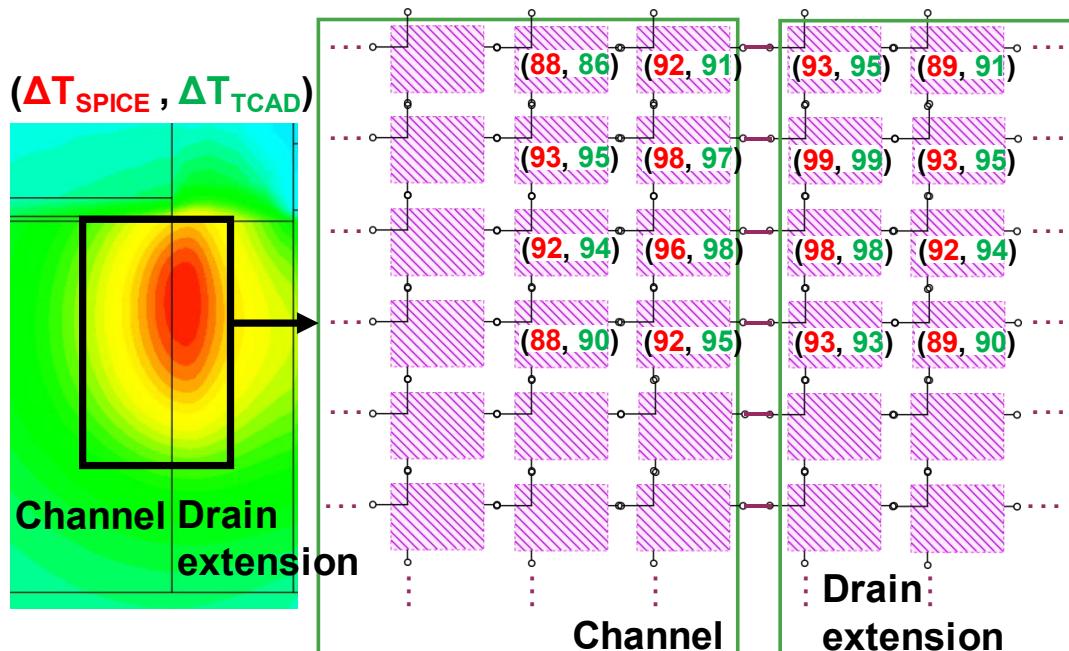

| <b>Fig. 4. 9</b> Joule heat distribution by TCAD at <b>(a)</b> $V_G=0.5V$ and $V_D=0.7V$ , and <b>(b)</b> $V_G=V_D=0.7V$ .....                                                                                                                             | 57 |

| <b>Fig. 4. 10</b> Nodal temperature near the hot spot with the comparison between SPICE and TCAD.....                                                                                                                                                      | 58 |

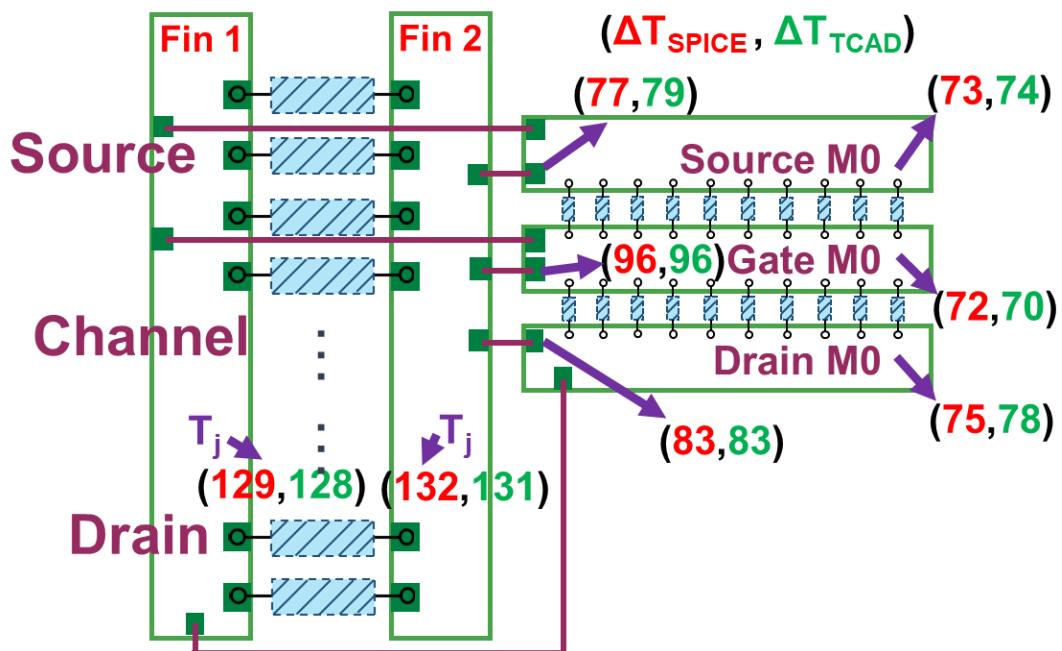

| <b>Fig. 4. 11</b> Nodal temperature on MEOL in the complete SPICE model with the comparison of TCAD.....                                                                                                                                                   | 59 |

| <b>Fig. 4. 12</b> SPICE and TCAD yielding the similar $R_{th0,FinFET}$ with the same fitting equation for face-down configuration.....                                                                                                                     | 60 |

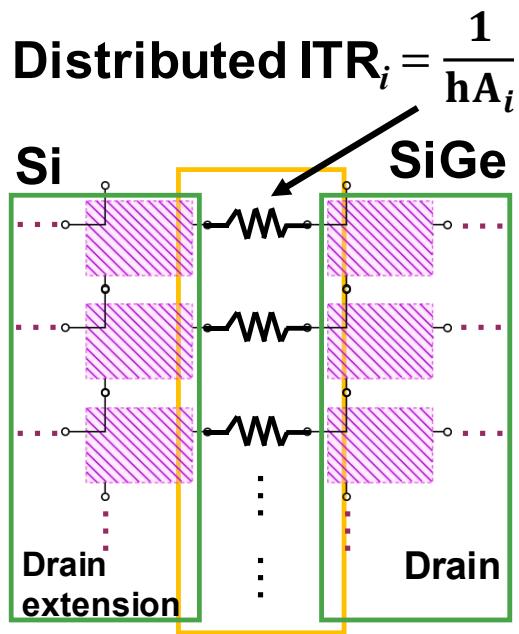

| <b>Fig. 4. 13</b> Distributed interfacial thermal resistance between two different materials in SPICE model.....                                                                                                                                           | 62 |

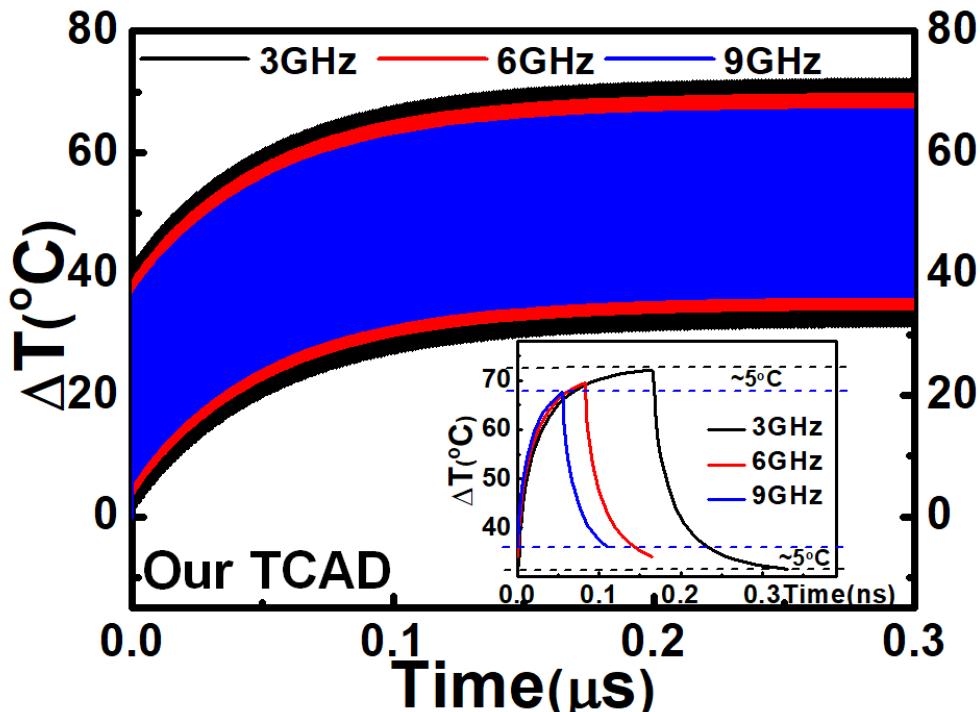

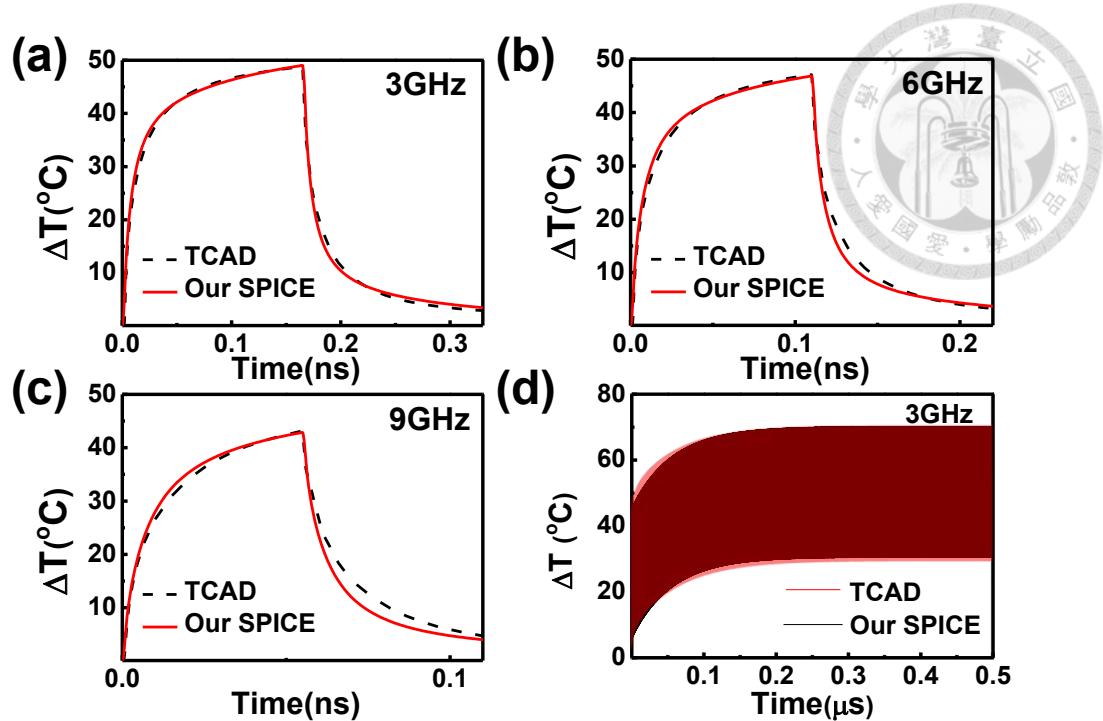

| <b>Fig. 5. 1</b> Transient $T_j$ of a 1-fin-1finger pFinFET in the first period with 0.7V square wave input at <b>(a)</b> 3GHz, <b>(b)</b> 6GHz, <b>(c)</b> 9GHz, and <b>(d)</b> envelope of transient $T_j$ evolution at 3GHz by TCAD and our SPICE ..... | 68 |

| <b>Fig. 5. 2</b> Envelope of transient $T_j$ evolution at 3GHz with and without ITR in the SPICE model.....                                                                                                                                                | 68 |

| <b>Fig. 5. 3</b> $R_{th}$ - $C_{th}$ circuit of the FinFET, MEOL, BEOL, and substrate .....                                                                                                                                                                | 69 |

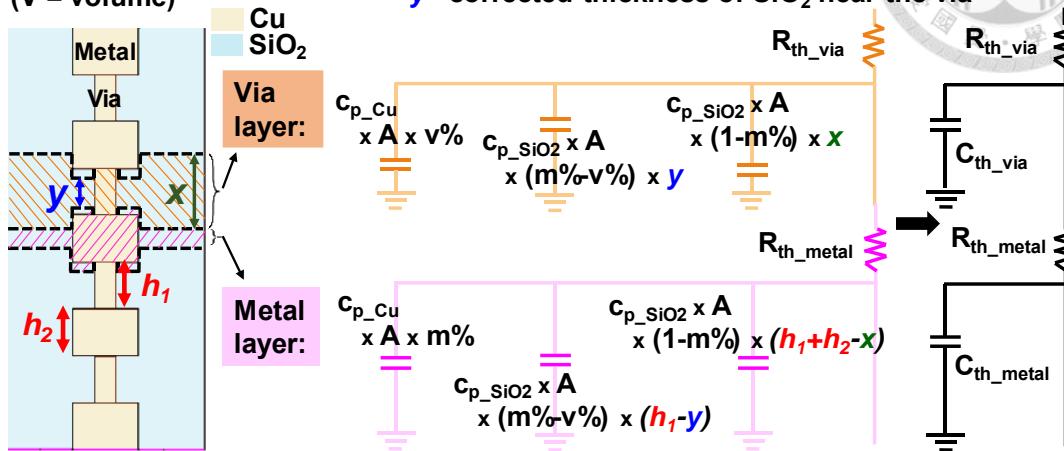

| <b>Fig. 5. 4</b> Extended two-step pseudo isothermal plane model of $R_{th,BEOL}$ and $C_{th,BEOL}$ with the corrected thicknesses of $SiO_2$ .....                                                                                                        | 70 |

| <b>Fig. 5. 5</b> Modeling $C_{th,BEOL}$ with the comparison of simulation results.....                                                                                                                                                                     | 70 |

| <b>Fig. 5. 6 (a)</b> Envelope of transient $T_j$ evolution at 1.5GHz including the BEOL and substrate to extract thermal time constants of <b>(b)</b> BEOL+substrate <b>(c)</b> hotspot and                                                                |    |

|                                                                                                                                                                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FinFET. <b>(d)</b> Summarized thermal time constants .....                                                                                                                                                                                                                      | 71 |

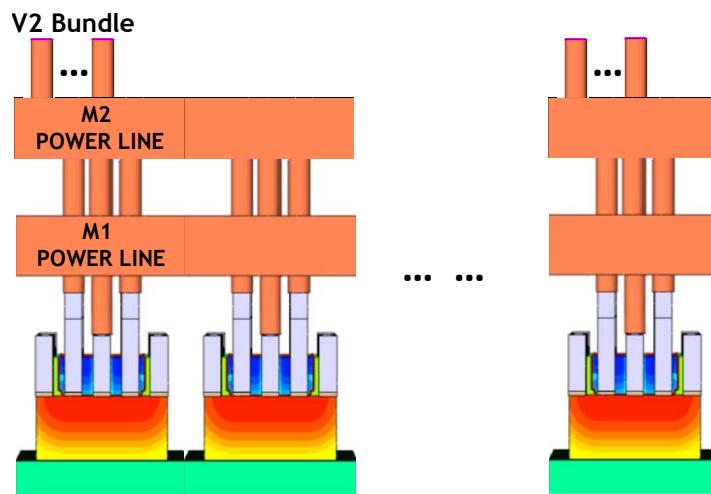

| <b>Fig. 5. 7</b> RO with stacked metal line and V2 bundle .....                                                                                                                                                                                                                 | 72 |

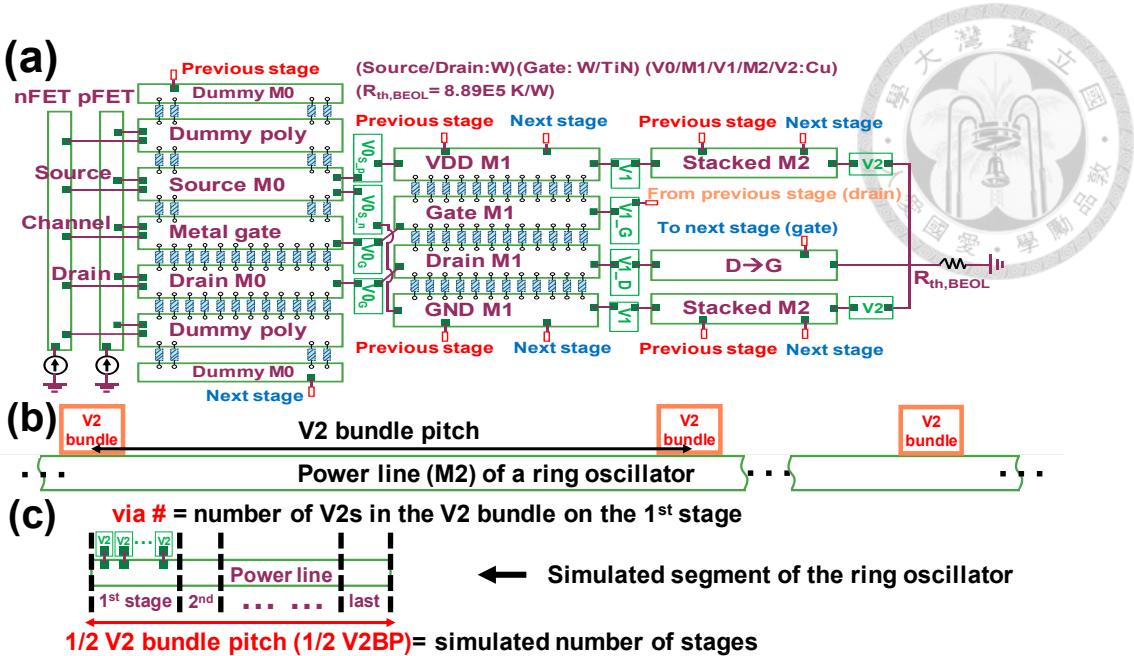

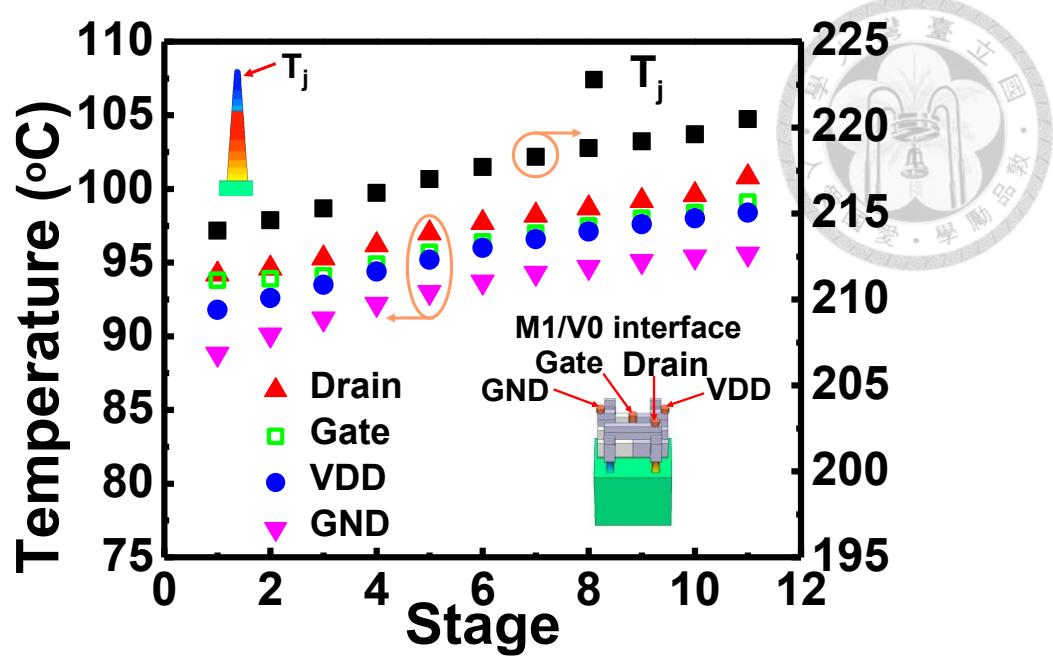

| <b>Fig. 5. 8 (a)</b> One stage of the ring oscillator with stacked power line, <b>(b)</b> the V2 bundles on the power line of a ring oscillator, and <b>(c)</b> simulated segment of the ring oscillator and the definitions of via # and 1/2 V2 bundle pitch (1/2 V2BP). ..... | 73 |

| <b>Fig. 5. 9</b> $T_j$ and the temperature at M1/V0 interfaces for a segment of the RO with 1/2 V2BP of 11 and via # of 1 .....                                                                                                                                                 | 74 |

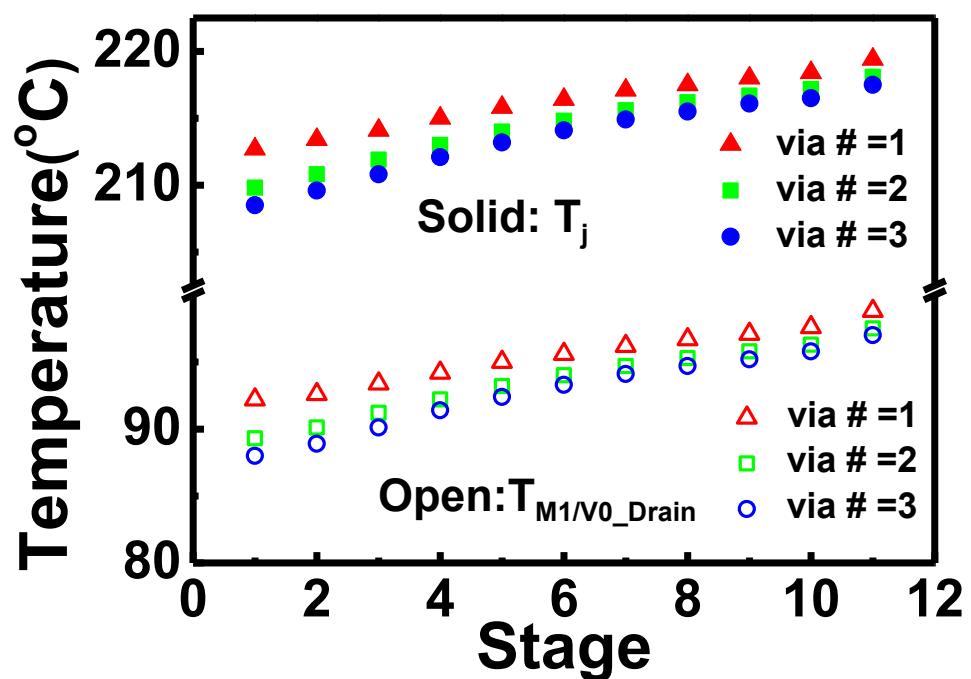

| <b>Fig. 5. 10</b> $T_j$ and the temperature at drain M1/V0 interface for a segment of the RO with 1/2 V2BP of 11 and different via numbers.....                                                                                                                                 | 74 |

| <b>Fig. 5. 11</b> Comparison of $T_j$ and the temperature at drain M1/V0 interface for pure Co or W MEOL and Cu M1 .....                                                                                                                                                        | 76 |

| <b>Fig. 5. 12</b> Temperature at drain M1/V0 interface for segments of the ROs using Co MEOL and M1 with different stage numbers and via numbers.....                                                                                                                           | 76 |

| <b>Fig. 5. 13</b> EM MTTF prediction based on different designs as compared to Cu technology.....                                                                                                                                                                               | 77 |

| <b>Fig. 5. 14</b> Top view of multi-fin FinFETs (a) remain three via0s and (b) adding additional via0s .....                                                                                                                                                                    | 78 |

| <b>Fig. 5. 15</b> Reduced $R_{th0,FinFET}$ with the increasing fin # by additional via0s.....                                                                                                                                                                                   | 79 |

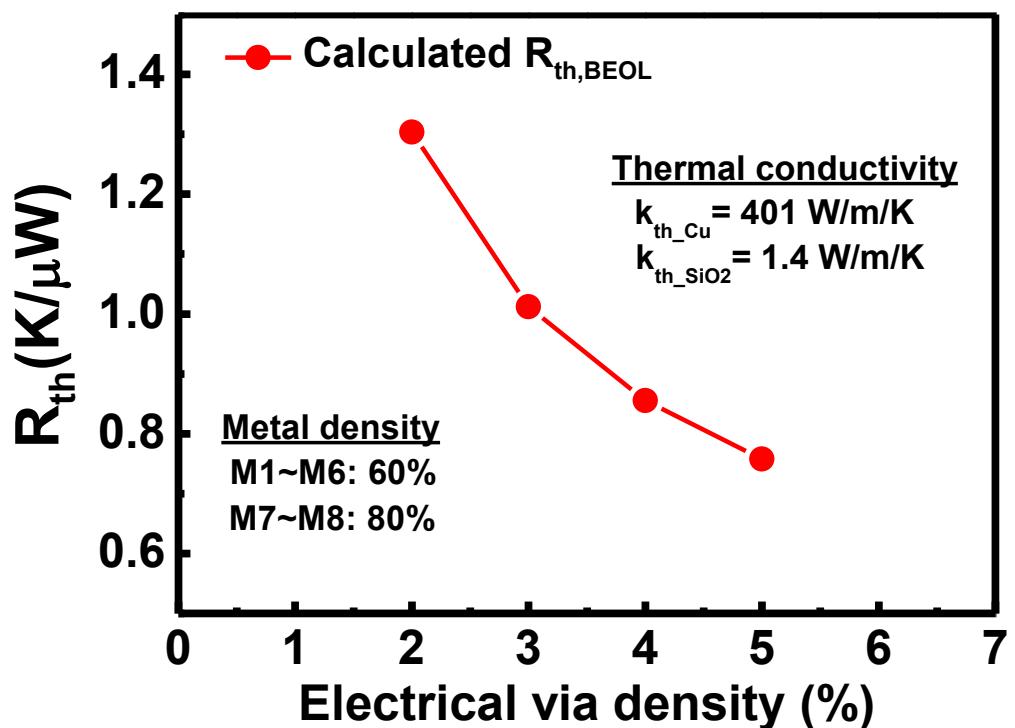

| <b>Fig. 5. 16</b> $R_{th,BEOL}$ with different via densities .....                                                                                                                                                                                                              | 80 |

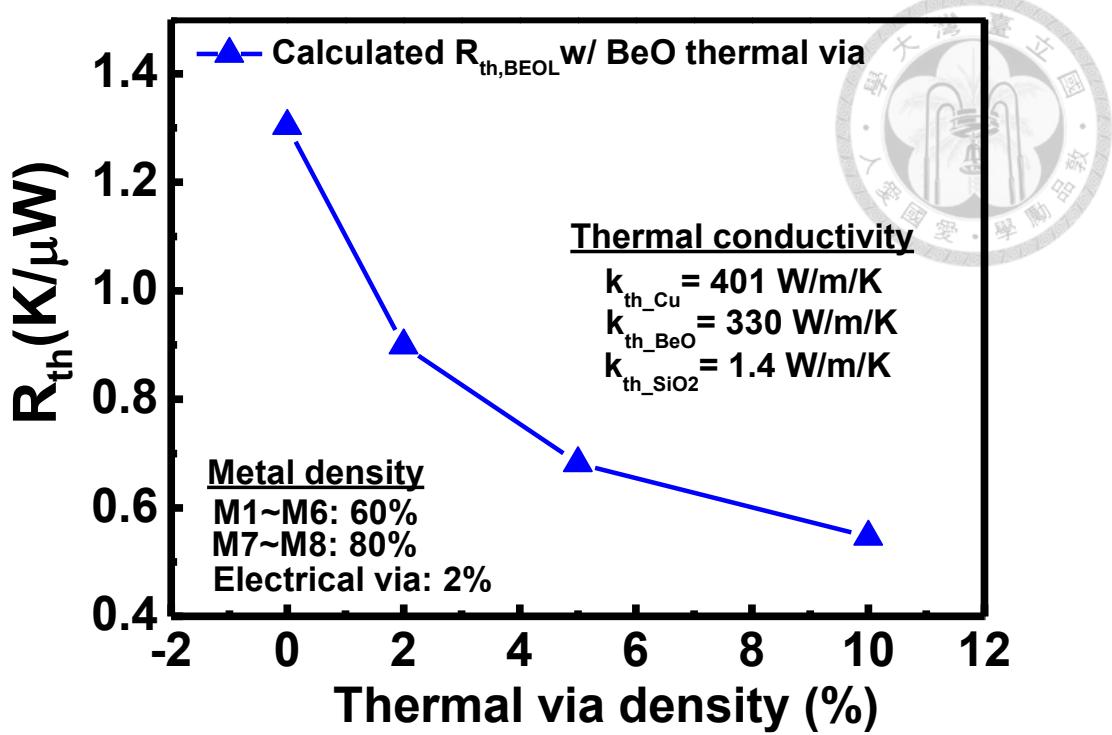

| <b>Fig. 5. 17</b> $R_{th,BEOL}$ with different thermal via densities .....                                                                                                                                                                                                      | 82 |

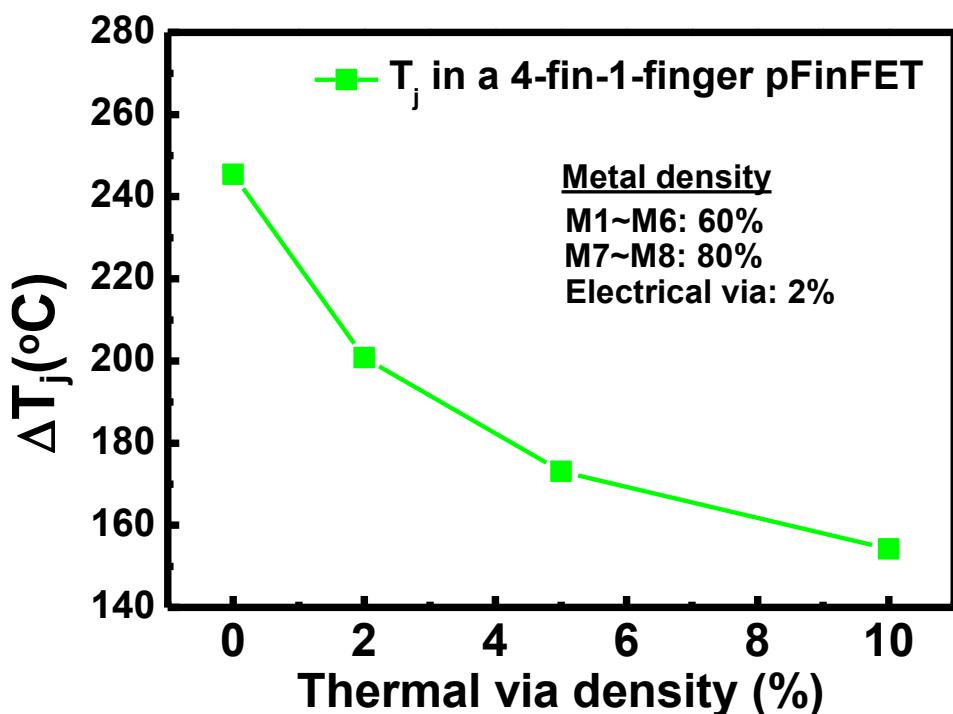

| <b>Fig. 5. 18</b> Reduced $T_j$ with increasing thermal via densities .....                                                                                                                                                                                                     | 82 |

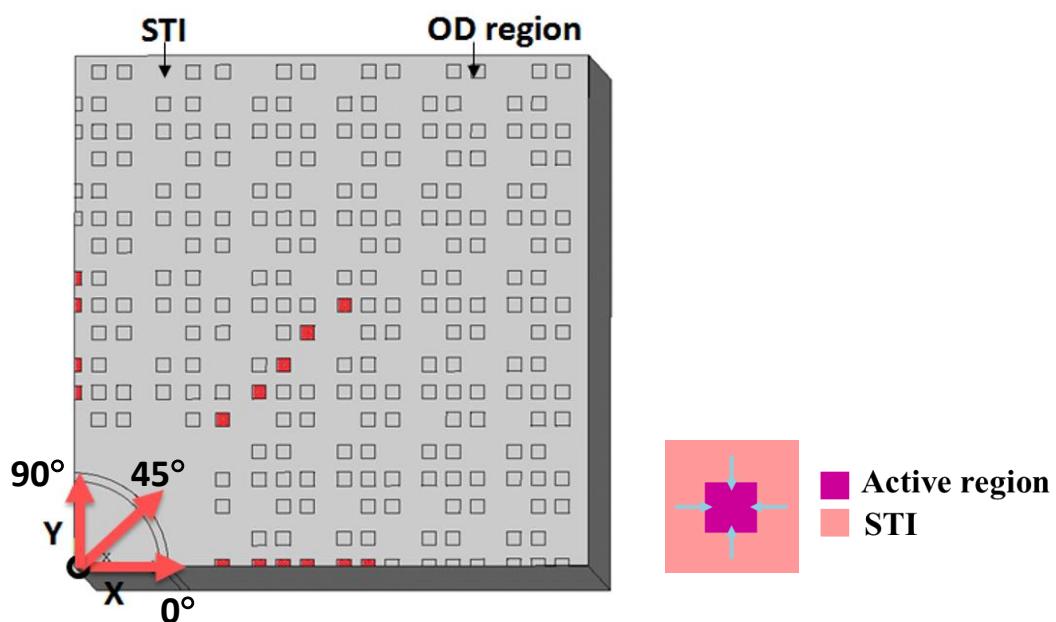

| <b>Fig. 6. 1</b> TSV and device placement.....                                                                                                                                                                                                                                  | 86 |

| <b>Fig. 6. 2</b> Side view of TSV and device, and area ratio of active region .....                                                                                                                                                                                             | 87 |

| <b>Fig. 6. 3 (a)</b> Structure of single TSV with symmetric planes <b>(b)</b> simplified simulation structure with regard to the symmetric planes .....                                                                                                                         | 88 |

| <b>Fig. 6. 4</b> STI pattern and devices in different direction .....                                                                                                                                                                                                           | 89 |

|                                                                                                                                                                              |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Fig. 6. 5</b> Simulated stress in devices which induced by a TSV w/ STI pattern but w/o the BEOL dielectrics .....                                                        | 90 |

| <b>Fig. 6. 6</b> The asymmetric stress field by BEOL dielectrics (inset) simulated TSV with the BEOL dielectric .....                                                        | 91 |

| <b>Fig. 6. 7</b> Simulated displacement vector of a TSV with 1 $\mu$ m BEOL dielectrics .....                                                                                | 92 |

| <b>Fig. 6. 8</b> STI effect on the asymmetric stress field .....                                                                                                             | 93 |

| <b>Fig. 6. 9</b> Coordinate transformations into Cartesian coordinates .....                                                                                                 | 94 |

| <b>Fig. 6. 10</b> Fitted K <sub>1</sub> , K <sub>2</sub> values with measured I <sub>on</sub> of nFETs .....                                                                 | 95 |

| <b>Fig. 6. 11</b> Fitted K <sub>1</sub> , K <sub>2</sub> values with measured I <sub>on</sub> of pFETs .....                                                                 | 96 |

| <b>Fig. 6. 12</b> Graphical expression of (a) nFET KOZ and (b) pFET KOZ .....                                                                                                | 97 |

| <b>Fig. 6. 13</b> Electron and hole mobility versus <110>uniaxial stress with E <sub>eff</sub> = 0.7MV/cm. The internal stress is conceptually drawn for nFET and pFET ..... | 98 |

# List of Tables

|                                                                                             |    |

|---------------------------------------------------------------------------------------------|----|

| <b>Table 2. 1</b> 14nm FinFET Parameters [2.6] .....                                        | 14 |

| <b>Table 2. 2</b> Thermal conductivities of materials .....                                 | 14 |

| <b>Table 2. 3</b> BEOL metal densities and specific thermal resistivity.....                | 22 |

| <b>Table 4. 1</b> Extracted nodal power distribution for SPICE .....                        | 57 |

| <b>Table 4. 2</b> Interfacial thermal conductivity at material interface.....               | 61 |

| <b>Table 5. 1</b> Thermal conductivity and coefficient of thermal expansion of materials .. | 81 |

| <b>Table 6. 1</b> Material properties used in Ansys. .....                                  | 88 |

| <b>Table 6. 2</b> Piezoresistances from zero internal stress condition [6.10] .....         | 98 |

# Chapter 1 Introduction

---

## 1.1 Motivation

The improvements in device Performance, Power, Area, and Cost (**PPAC**) were delivered by classic Dennard scaling over the past few decades. However, the Dennard scaling met the limitation at about 15 years ago, and the performance of transistors started to be boosted by transistor innovations (**Fig. 1. 1**) instead of simply shrinking. Strained Si was introduced by SiGe stressor and contact-etching-stop-layer (CESL) for pFETs and nFETs, respectively, at 90nm node. High-k metal gate was proposed to lower the gate leakage by the large physical thickness as compared to the SiO<sub>2</sub> with the same EOT at 45nm node. Since 2012, 3D transistors (Si FinFETs [1.1]) and 3D-ICs (Integrated Fan-out, InFO [1.2]) have become the mainstream of semiconductor industry in commercial products to overcome the short channel effects and to achieve low cost and small form factor, respectively. Nowadays, Reliability (R) issues are eye-catching in advanced technology nodes, and to meet the requirements of **PPACR** simultaneously has become a must.

Thermal management is getting critical in ultra-scaled 3D transistors due to the increasing device density, the confined device geometry, and the high thermal resistivity of some materials. High temperature in the channel induced by self-heating

effect (SHE) is reported not only to degrade the device performance [1.3]-[1.5] but also to poison the reliability due to accelerated channel hot-carrier degradation [1.6]-[1.8], bias-temperature instability [1.9], and time-dependent dielectric breakdown [1.10].

Therefore, precise device temperature is essential for accurate reliability lifetime projection.

**Fig. 1. 1** Transistor performance boosters since 90nm node (Source: Intel Corp.)

While InFO serves as a cost effective option of 3D-IC for the application processor in mobile devices, **Fig. 1. 2** shows the 3D super chip by using the through-silicon vias (TSVs) to connect the vertical stacked chips for heterogeneous integration such as RF, photonics, memories, and logics, etc, which is a promising choice for high-end 3D-IC applications. However, the stress field induced by TSVs due to the mismatch of materials' coefficients of thermal expansion (CTEs) add additional strain in the transistors, which changes the device current. Accurate keep-out zone (KOZ) modeling

is needed for circuit design to avoid the performance variation.

**Fig. 1. 2** 3D Super chip by TSV [1.11]

In this dissertation, the SHE in scaled FinFETs and the stress field induced by via-last TSVs are simulated and modeled.

## 1.2 Dissertation Organization

The objections of this dissertation are to provide the temperature mapping both in transistors and the BEOL with the modeling of the SHE in scaled FinFETs both for DC and AC inputs, and to predict the proximity effects of via-last TSVs on nearby devices by the proposed KOZ model with experimental verifications.

In chapter 2, the SHE of FinFETs is simulated using TCAD based on the structure of Intel 14nm FinFETs considering the reduced thermal conductivities of materials suffering from alloy scattering and boundary scattering due to confined geometry.

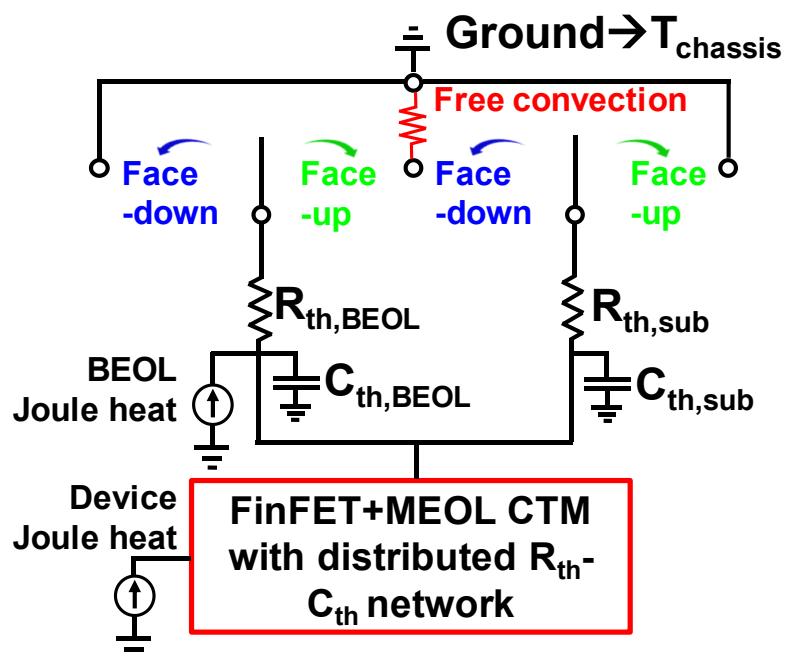

Thermal resistance ( $R_{th}$ ) circuit consist of the FinFET, the BEOL, and the substrate is schematically drawn. Non-flat isothermal plane is observed in the BEOL. A two-step pseudo isothermal plane for BEOL  $R_{th}$  modeling is proposed and verified by the simulation results. Method of enhancing the heat dissipation is demonstrated. The direction of heat flow is affected by the large thermal resistance of the free convection of air ( $R_{th,convection}$ ). The intrinsic thermal resistances of a single channel ( $R_{th0,device}$ ) in the multi-fin FinFETs are extracted from the overall  $R_{th}$ . The  $R_{th0,device}$  is dependent on FinFET layout, geometry, and thermal boundary condition.

In chapter 3, the transient junction temperature ( $T_j$ ) response in an inverter with capacitive loading is simulated by mix-mode electro-thermal TCAD simulation. The cooling time is decided by the volume of hot spot in device channel. The capacitive loading of the inverter in the real circuit is calculated by the output current experimentally. The low thermal conductivity of SiGe S/D leads to the higher  $T_j$  in pFETs than in nFETs. The temperature in back-end interconnect and the dependence of device temperature on the output loading are investigated with AC input. The residual  $T_j$  and the temperature on M1 are found too low to reflect the real device temperature, which may lead to an underestimation of device temperature with transient AC input during measurements.

In chapter 4, thermal SPICE Modeling of FinFETs and BEOL with distributed  $R_{th}$ -

$C_{th}$  network is demonstrated. The thermal time constant of the hotspot ( $\tau_{hotspot}$ ) in scaled FinFETs is found to be frequency dependent instead of being a constant. Guideline for determining the grid size is reported using fitted slope of the frequency dependence of  $\tau_{hotspot}$ . The discretized fin is modeled with device geometry and material thermal conductivity. The completely modularized fin is connected to the middle-end-of-line (MEOL) and inter-metal dielectric (IMD) to form a FinFET.  $R_{th0,device}$  values of the multi-fin FinFETs implemented using our modularized model are verified by the TCAD simulation results to ensure the layout flexibility of the model. Interfacial thermal resistance can be considered in the thermal SPICE model, different from the device simulation.

In chapter 5, the validity of the thermal SPICE model with AC input is ensured by the similar results with device simulation. The  $C_{th,BEOL}$  is calculated by the extended two-step pseudo isothermal plane model with identical correction factors for the non-flat isothermal plane in BEOL.  $\tau_{hotspot}$ ,  $\tau_{FinFET+MEOL}$ , and  $\tau_{BEOL+Sub}$  are extracted from the envelope of transient  $T_j$  evolution by the time when  $\Delta T_j$  increases to  $1-e^{-1}$  of the final value. A ring oscillator (RO) with stacked power line and V2 bundles is assembled using our modularized SPICE model. Nodal temperatures at the V0/M1 interface are extracted for BEOL reliability evaluation. The effect of Co incorporation on BEOL EM MTTF considering its low thermal conductivity as compared to Cu and W is

demonstrated. The EM MTTF can be improved by the layout design of BEOL.

In chapter 6, the performance variation caused by the stress field near a through-silicon via (TSV) is measured using 28nm node devices across 12-inch wafers. The TSV is fabricated by a via-last process. The back-end-of-line (BEOL) dielectrics on TSV cause the asymmetric stress field, i.e., the absolute value of radial stress ( $|\sigma_r|$ ) does not equal to that of tangential stress ( $|\sigma_\theta|$ ) on silicon and leads to the asymmetric keep-out zone (KOZ), different from previously reported. A modified KOZ model with the asymmetric radial and tangential stress field is proposed and verified by 3D finite element analysis (FEA) simulation and experiment data. The physics behind the asymmetry is also described. Comparable KOZ size for nFETs and pFETs is observed.

Finally, chapter 7 summarizes the conclusions and the contributions of this work. The further improvements of thermal SPICE model of scaled FinFET and circuit level reliability evaluation are discussed in the future work.

### 1.3 References

- [1.1] C. Auth, C. Allen, A. Blattner, D. Bergstrom, M. Brazier, M. Bost, M. Buehler, V. Chikarmane, T. Ghani, T. Glassman, R. Grover, W. Han, D. Hanken, M. Hattendorf, P. Hentges, R. Heussner, J. Hicks, D. Ingerly, P. Jain, S. Jaloviar, R. James, D. Jones, J. Jopling, S. Joshi, C. Kenyon, H. Liu, R. McFadden, B. McIntyre, J. Neirynck, C. Parker, L. Pipes, I. Post, S. Pradhan, M. Prince, S.

Ramey, T. Reynolds, J. Roesler, J. Sandford, J. Seiple, P. Smith, C. Thomas, D.

Towner, T. Troeger, C. Weber, P. Yashar, K. Zawadzki, K. Mistry, "A 22nm

high performance and lowpower CMOS technology featuring fully-depleted tri-

gate transistors, self-aligned contacts and high density MIM capacitors," in *Proc.*

*Symposium on VLSI Technology*, June 2012, pp. 131-132.

[1.2] Christianto C. Liu, Shuo-Mao Chen, Feng-Wei Kuo, Huan-Neng Chen, En-

Hsiang Yeh, Cheng-Chieh Hsieh, Li-Hsien Huang, Ming-Yen Chiu, John Yeh,

Tsung-Shu Lin, Tzu-Jin Yeh, Shang-Yun Hou, Jui-Pin Hung, Jing-Cheng Lin,

Chewn-Pu Jou, Chuei-Tang Wang, Shin-Puu Jeng, Douglas C.H. Yu, "High-

performance integrated fan-out wafer level packaging (InFO-WLP):

Technology and system integration," in *IEEE IEDM Tech. Dig.*, Dec. 2012, pp.

14.1.1-14.1.4.

[1.3] Liping Wang, Andrew R. Brown, Mihail Nedjalkov, Craig Alexander, Binjie

Cheng, Campbell Millar, and Asen Asenov, "Impact of self-heating on the

statistical variability in bulk and SOI FinFETs," *IEEE Transactions on Electron*

*Devices*, Vol. 62, No. 7, July 2015, pp. 2106-2112.

[1.4] E. Bury, B. Kaczer, P. Roussel, R. Ritzenthaler, K. Raleva, D. Vasileska, and G.

Groeseneken, "Experimental validation of self-heating simulations and

projections for transistors in deeply scaled nodes," *Reliability Physics*

[1.5] E. Bury, B. Kaczer, J. Mitard, N. Collaert, N.S. Khatami, Z. Aksamija, D. Vasileska, K. Raleva, L. Witters, G. Hellings, D. Linten, G. Groeseneken, and A. Thean, "Characterization of self-heating in high-mobility Ge FinFET pMOS devices," in *Proc. Symposium on VLSI Technology*, June 2015, pp. T60–T61.

[1.6] Hai Jiang, Xiaoyan Liu, Nuo Xu, Yandong He, Gang Du, and Xing Zhang, "Investigation of self-heating effect on hot carrier degradation in multiple-Fin SOI FinFETs," *Electron Device Letters, IEEE* 36.12 (2015): pp.1258-1260.

[1.7] Steven Mittl and Fernando Guarín, " Self-Heating and Its Implications on Hot Carrier Reliability Evaluations," *Reliability Physics Symposium (IRPS), 2015 IEEE International*, pp. 4A.4.1-4A.4.4.

[1.8] A. Laurent, X. Garros, S. Barraud, G. Mariniello, G. Reimbold, D. Roy, E. Vincent, and G. Ghibaudo, "Hot Carrier Degradation in Nanowire Transistors: Physical mechanisms, Width dependence and Impact of Self-Heating," in *Proc. Symposium on VLSI Technology*, June 2016, pp. T48–T49.

[1.9] S. E. Liu, J. S. Wang, Y. R. Lu, D. S. Huang, C. F. Huang, W. H. Hsieh, J. H. Lee, Y. S. Tsai, J. R. Shih, Y.-H. Lee, and K. Wu, "Self-heating effect in FinFETs and its impact on device reliability characterization," *Reliability Physics Symposium (IRPS), 2014 IEEE International*, pp. 4A.4.1-4A.4.4.

[1.10] S. Mei, N. Raghavan, M. Bosman, D. Linten, G. Groeseneken, N. Horiguchi,

and K.L. Pey, "New understanding of dielectric breakdown in advanced FinFET

devices – physical, electrical, statistical and multiphysics study," in *IEEE IEDM*

*Tech. Dig.*, Dec. 2016, pp. 15.5.1-15.5.4.

[1.11] Mitsumasa Koyanagi, " Heterogeneous 3D Integration - Technology Enabler

toward Future Super-Chip," in *IEEE IEDM Tech. Dig.*, Dec. 2013, pp. 1.2.1-

1.2.8.

# Chapter 2 Thermal Resistance Modeling of Intrinsic FinFETs and Back-end-of-line

---

## 2.1 Introduction

Self-heating (SH) in scaled FinFET circuits retards the performance, degrades device reliability, and accelerates the electro-migration (EM) in back-end-of-line (BEOL). Temperature mapping with high accuracy is essential for precise reliability lifetime prediction.

Several methods have been reported for SHE measuring:

1. *Resistance thermometry structure* [2.1],[2.2]: the electrical resistance changes of the device metal gate and the M1 metal are measured. However, the extracted temperature is the average temperature of the entire metal line, and the junction temperature ( $T_j$ ) projection needs to be carefully calibrated by device simulation.

2. *Heater-sensor structure* [2.2]: changes in the electrical properties of the nearby device are measured. In this case, the  $T_j$  of device under test (DUT) is not measured directly. The estimate  $T_j$  of DUT could be affected by device layouts and boundary condition. Device simulation is also needed for the  $T_j$  projection.

3. *Thermoreflectance image* [2.3]: it images the top surface temperature of transistors. However, the different boundary condition and heat dissipation path

between conventional measurement and flip-chip packaging will lead to the  $T_j$  difference between measurement and real circuit. These two configurations will be discussed in 2.2.2.

*4. Scanning Thermal Microscopy* [2.4]: the local temperature of the top surface of the sample is measured by a nanoscale sharp tip through the mechanical contact. This method suffers from the similar boundary condition issue as thermoreflectance image does.

Moreover, it has been reported that none of the existing SHE measurement methods can provide precise AC response of spatial and temporal temperatures, which are essential for accurate reliability lifetime projection in circuit level. Therefore, device simulation is the only way to know the exact temperature distribution and time evolution in the channel. Device simulation of the SHE in FinFET was reported [2.3],[2.5], but the difference between measurement and real circuit was not considered, and the intrinsic thermal resistance was not decoupled.

In this chapter, a two-step pseudo isothermal plane model of the thermal resistance of BEOL ( $R_{th,BEOL}$ ) is proposed and verified by numerical simulation. With  $R_{th,BEOL}$ , the intrinsic thermal resistance of FinFET ( $R_{th,device}$ ) is decoupled from the thermal resistance circuit. The dependence of intrinsic thermal resistance of a single channel in FinFETs ( $R_{th0,device}$ ) on the device geometry and layout are discussed.

## 2.2 Electro-thermal Simulation and Boundary Conditions

### 2.2.1 FinFET Structure and Simulation Settings

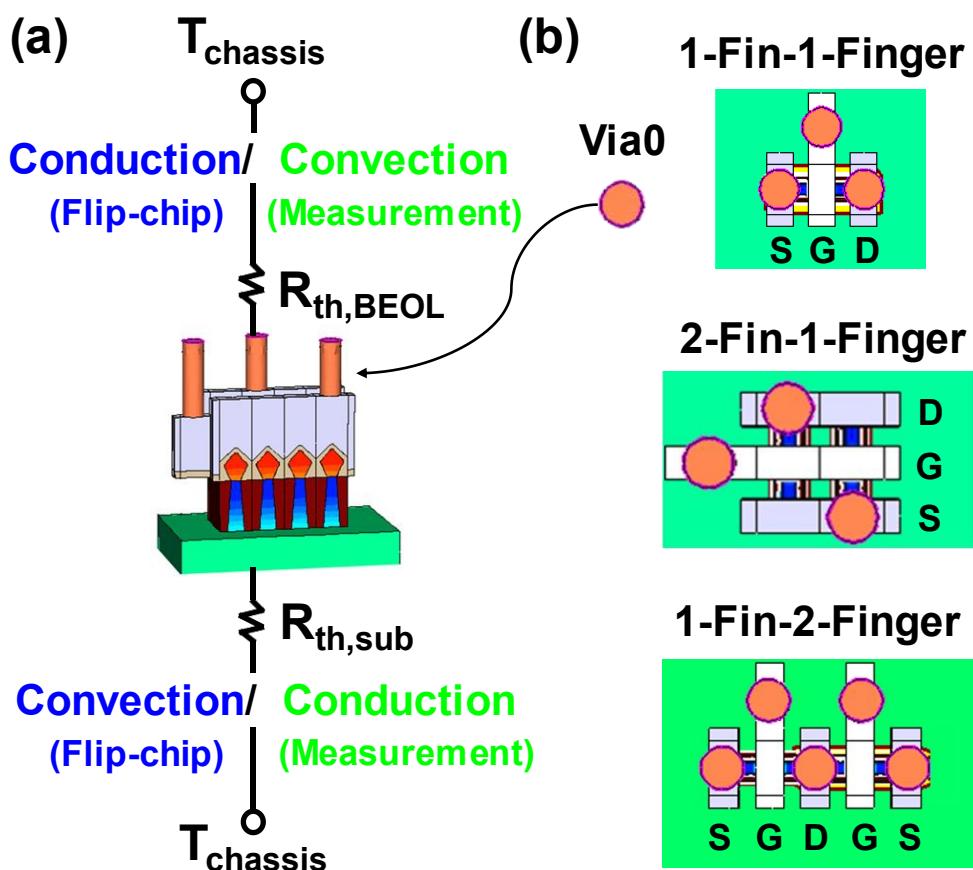

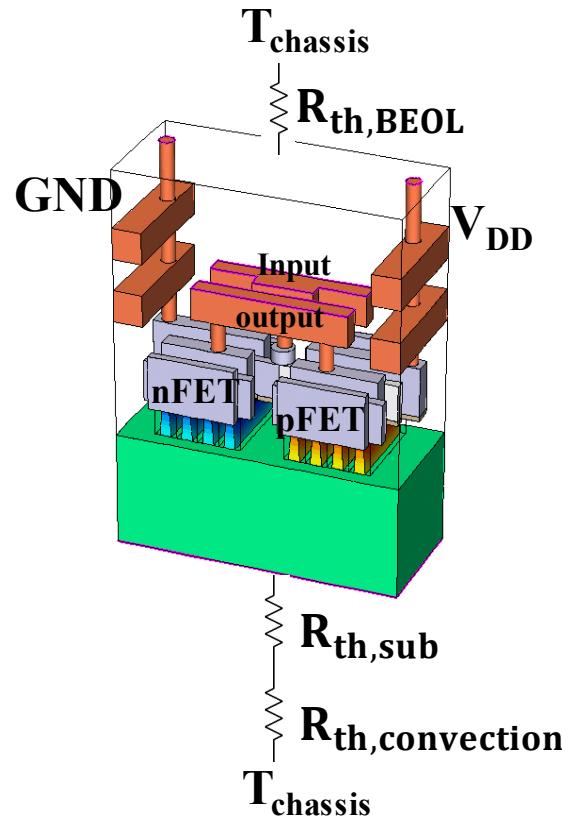

The simulation structure is composed of the FinFET, S/D contacts, gate metal, via0s, and part of the Si substrate with the thickness of 250nm. (**Fig. 2. 1**). Diamond shape S/D structure and the taper fin are considered according to the cross-sectional TEM images. **Table 2. 1** shows the geometry parameters which follow the reported 14nm FinFET technology by intel [2.6]. The bottom side of FinFETs is connected to the chassis temperature ( $T_{chassis}$ ) by the thermal resistance of Si substrate ( $R_{th,sub}$ ) and the via0s are connected to  $T_{chassis}$  through  $R_{th,BEOL}$  (**Fig. 2. 1 (a)**). The  $T_{chassis}$  is assumed to be 40°C. The four sidewalls of simulation structure are set adiabatic to represent the boundary condition in the hot spot of a chip (no heat flux between two turned on device).

Top views of FinFETs with 1-fin-1-finger, 2-fin-1-finger, and 1-fin-2-finger are shown in **Fig. 2. 1 (b)**. The tungsten M0 of source and drain, TiN metal gate, and copper via0s are implemented in the structure. The extension of metal gate is considered following the design rule.

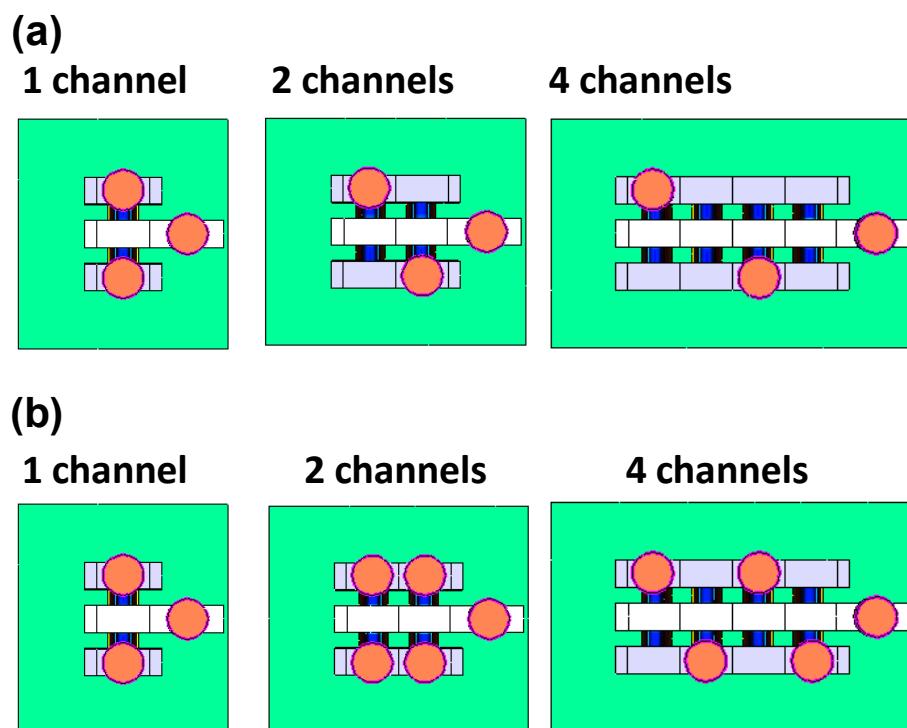

Note that in multi-fin FinFETs, e.g. the 2-fin-1-finger device, the number of via0s remains three as compared to the 1-fin-1-finger device. On the other hand, the number of via0s increases with the increasing finger number in multi-finger FinFETs. For example, there are five via0s for the 1-fin-2-finger device.

Thermal conductivities of materials used in the simulation are shown in **Table 2**.

2. It is reported [2.7],[2.8] that the thermal conductivity of SiGe S/D and silicon fin are lower than that of bulk Si due to alloy scattering and boundary scattering, respectively.

**Fig. 2. 1** (a) FinFET structure and thermal resistances of BEOL and substrate, and (b) device layouts

**Table 2. 1** 14nm FinFET Parameters [2.6]

|                                         |        |                    |                    |

|-----------------------------------------|--------|--------------------|--------------------|

| Gate length ( $L_g$ )                   | 22 nm  | Contact poly pitch | 70 nm              |

| Fin height ( $H_{fin}$ )                | 40 nm  | $I_D$              | 42 ( $\mu A/fin$ ) |

| Average fin width<br>( $W_{fin, avg}$ ) | ~10 nm | $V_{DD}$           | 0.7 V              |

| Fin pitch (FP)                          | 42nm   |                    |                    |

**Table 2. 2** Thermal conductivities of materials

| Material         | $\kappa_{th}$<br>( $Wm^{-1}K^{-1}$ ) | Material | $\kappa_{th}$<br>( $WM^{-1}K^{-1}$ ) |

|------------------|--------------------------------------|----------|--------------------------------------|

| Si (bulk)        | 148                                  | Tungsten | 174                                  |

| <b>Si (10nm)</b> | <b>13</b>                            | TiN      | 19.2                                 |

| $SiO_2$          | 1.4                                  | Copper   | 401                                  |

| <b>SiGe</b>      | <b>2</b>                             |          |                                      |

### 2.2.2 Conventional Measurement and Flip-chip Packaging

In the common SHE measurements, the samples are placed face-up on the stage and only the devices under test are turned on. On the other hand, the ICs such as the application processors (AP) in mobile phones are usually packaged in the face-down

configuration (flip-chip), and many devices are turned on.

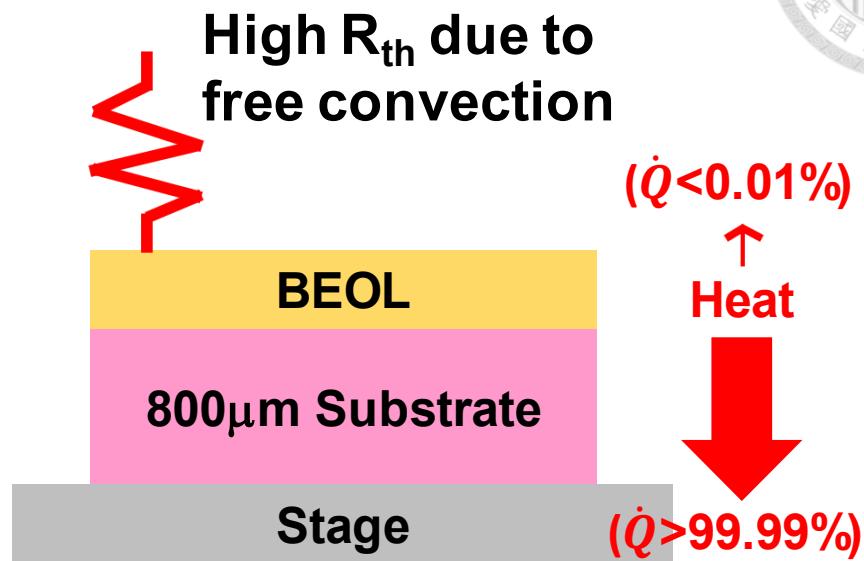

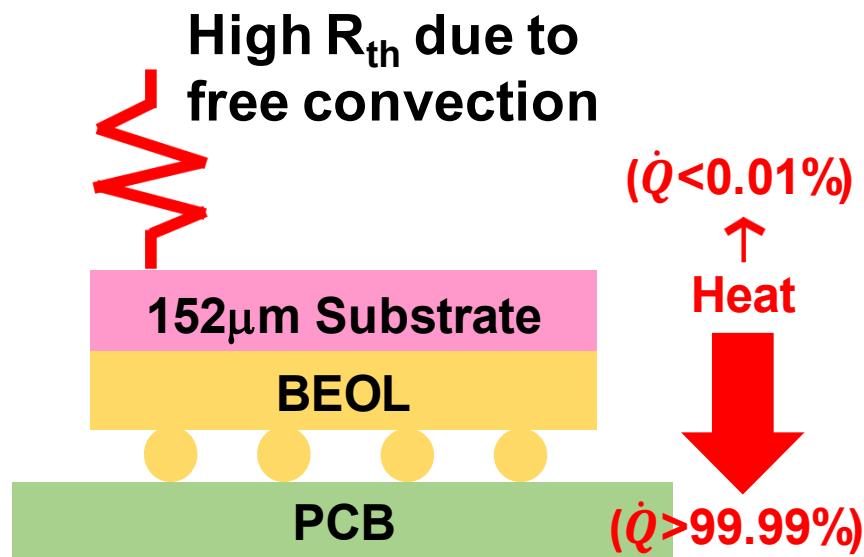

Dissipating the heat through the free convection of the air is way less efficient than the conduction [2.9], and leads to an additional thermal resistance ( $R_{th,convection}$ ) at the boundary. The  $R_{th,convection}$  is much larger than  $R_{th,BEOL}$  and  $R_{th,Sub}$ . Most of the heat ( $>99.99\%$ ) dissipates by conducting through the Si substrate to the stage for face-up configuration (**Fig. 2. 2 (a)**). For the face-down configuration, most of the heat dissipates by conducting through the BEOL mounted on PCB using  $\mu$ -bumps (**Fig. 2. 2 (b)**).

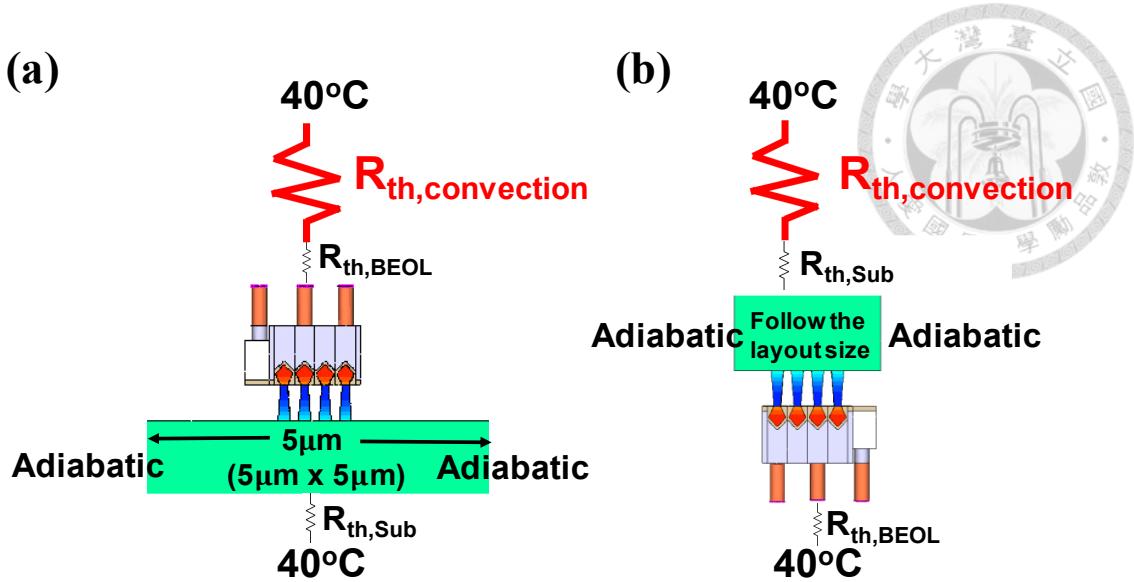

With  $T_{chassis} = 40^\circ\text{C}$ , the four sidewalls of simulated FinFETs are set to be adiabatic (no heat flux between two on devices). For face-up configuration, the FinFETs are connected to the calculated  $R_{th,Sub}$  for the area size of  $5\mu\text{m} \times 5\mu\text{m}$  through the substrate side to represent the single turned on device during the measurement (**Fig. 2. 3 (a)**). For face-down configuration, the FinFETs are connected to the modeled  $R_{th,BEOL}$  with the device layout size through the via0s, just as the hotspot in the circuit of a flip-chip packaged die (**Fig. 2. 3 (b)**).

## (a) Face-up configuration

## (b) Face-down configuration

Fig. 2. 2 Heat dissipation paths in (a) conventional measurement (face-up) and (b) flip-chip packaging (face-down)

**Fig. 2.3** Simulation structure, boundary condition, and thermal resistances of (a) face-up and (b) face-down configurations

## 2.3 Thermal Resistance Modeling of BEOL

### 2.3.1 Thermal Resistance Circuit

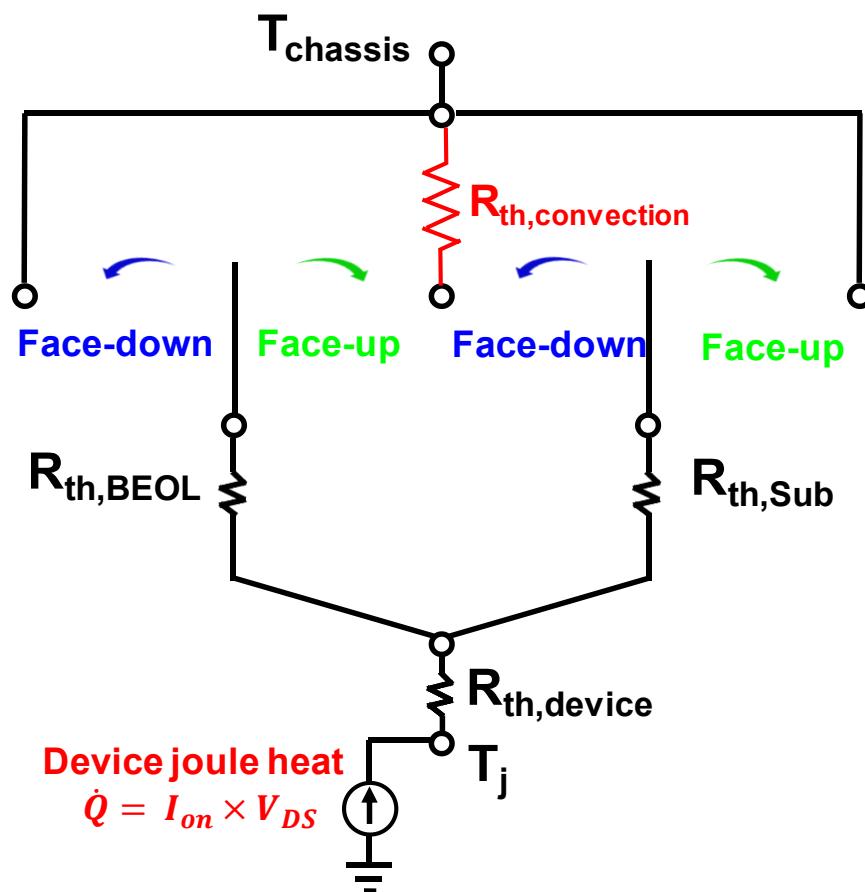

The thermal resistance circuit is schematically drawn for both face-up and face-down configurations (Fig. 2.4). The total thermal resistance ( $R_{th,total}$ ) can be calculated by:

$$R_{th,total} = \frac{T_j - T_{chassis}}{\dot{Q}} \quad (2.1)$$

, where

$$\dot{Q} = I_{on} \times V_{DS} \quad (2.2)$$

is the Joule heat of device.

The corresponding intrinsic thermal resistance of device ( $R_{th,device}$ ) can be

decoupled from the  $R_{th, total}$  by:

$$R_{th, device} = R_{th, total} - [(R_{th, BEOL} + R_{th, convection}) // R_{th, Sub}] \quad (2.3)$$

, and

$$R_{th, device} = R_{th, total} - [R_{th, BEOL} // (R_{th, Sub} + R_{th, convection})] \quad (2.4)$$

for face-up and face-down configurations, respectively.

**Fig. 2. 4** Thermal resistance circuit of device, BEOL, substrate, and free convection

While  $R_{th,Sub}$  can be simply calculated by:

$$R_{th,Sub} = \frac{1}{k_{th,Si \text{ (bulk)}}} \cdot \frac{\text{thickness}}{\text{area}} \quad (2.5)$$

precise  $R_{th,BEOL}$  modeling is needed to extract the  $R_{th,device}$  from the thermal resistance circuit based on equation (2.3) and (2.4).

### 2.3.2 Two-step Pseudo Isothermal Plane Modeling

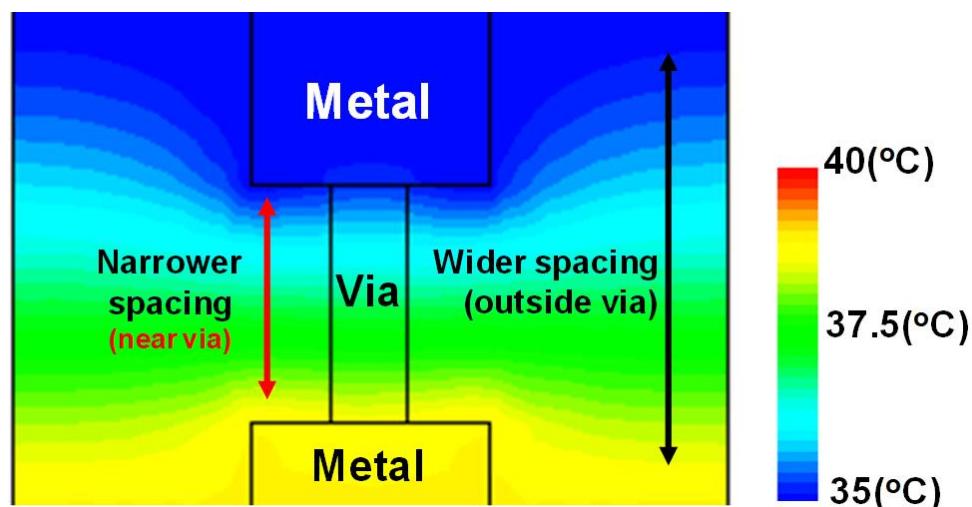

**Fig. 2. 5** shows the isothermal plane in the simulated BEOL structure. Both of the thicknesses of via layer and metal layer are 100nm. The metal line and via are made of Cu, and the IMD is assumed pure  $\text{SiO}_2$ . Non-flat isothermal plane in BEOL is observed, different from the physical structure. The spacing between isothermal plane in  $\text{SiO}_2$  outside the via is wider than near the via due to the thermal conductivity difference between metal and dielectric.

**Fig. 2. 5** Simulated temperature contour in BEOL

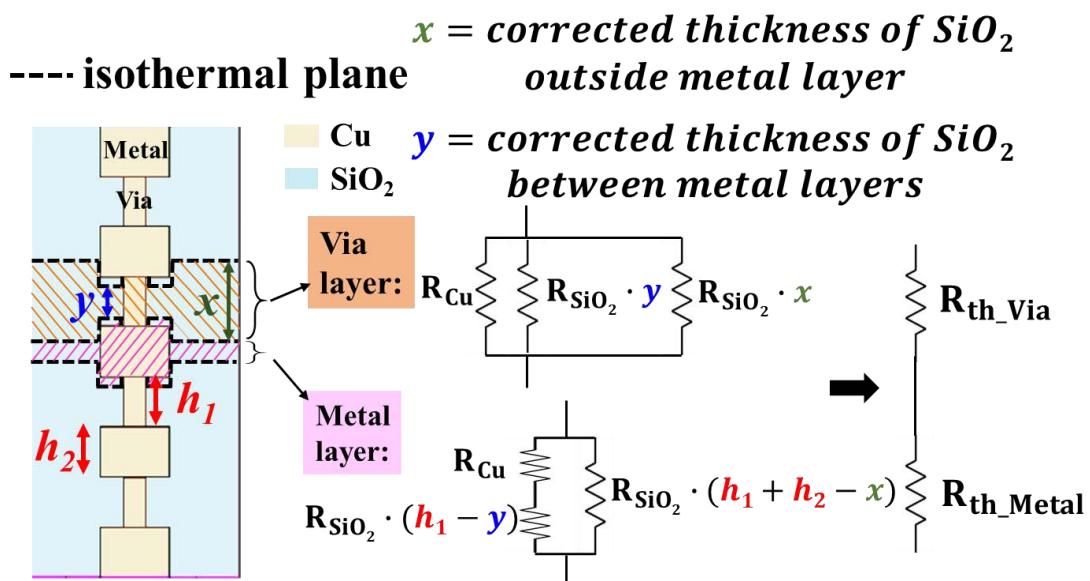

A two-step pseudo isothermal plane model with the corrected oxide thicknesses  $x$  and  $y$  for  $\text{SiO}_2$  outside the metal layers and  $\text{SiO}_2$  between the metal layers, respectively,

is proposed based on the simulation results (**Fig. 2. 6**). With the physical thickness of via layer ( $h_1$ ) and metal layer ( $h_2$ ), thermal resistances are calculated layer by layer based on the via densities and metal densities. In via layers, the thermal resistance is:

$$R_{th,via} = R_{Cu}/R_{SiO_2 \text{ between metal layers}}/R_{SiO_2 \text{ outside the metal layers}} \quad (2.6)$$

In metal layers, the thermal resistance is:

$$R_{th,metal} = (R_{Cu} + R_{SiO_2 \text{ between metal layers}})/R_{SiO_2 \text{ outside the metal layers}} \quad (2.7)$$

The total  $R_{th,BEOL}$  is the series of all  $R_{th,via}$  and  $R_{th,metal}$ .

**Fig. 2. 6** Two-step pseudo isothermal plane modeling of  $R_{th,BEOL}$  with the corrected IMD thickness

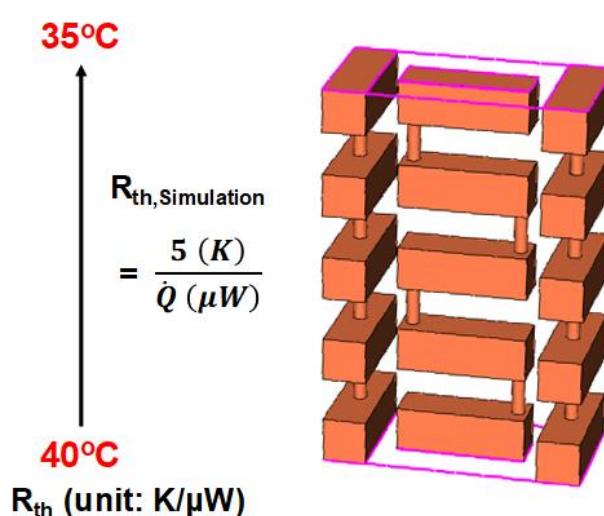

To verify the proposed model, BEOL structures (**Fig. 2. 7**) consist of five metal layers with different via densities are simulated. The top contact and the bottom contact

are set to be at 35°C and 40°C, respectively. The thermal resistance is calculated by the temperature difference (5°C) and the simulated heat flow through the contacts. There are some dummy metals in the BEOL in real products, which has also been considered using parts of none connected metals in the cases with low via density (<1%).

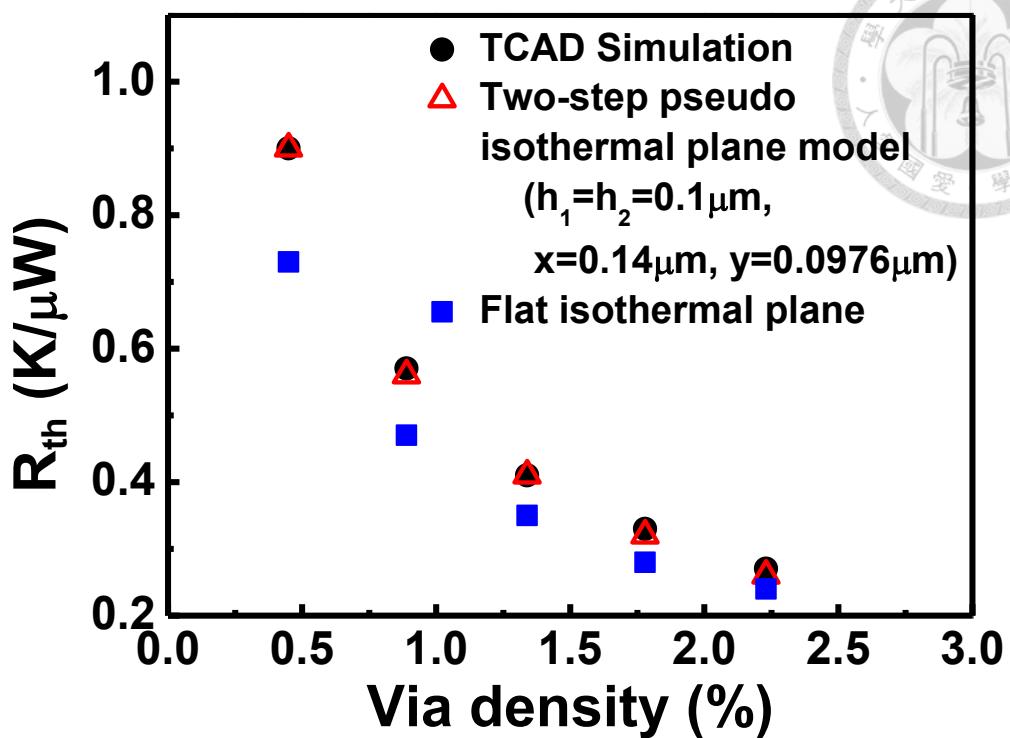

The two-step pseudo isothermal model with  $h_1=h_2=1\mu\text{m}$ ,  $x=0.14\mu\text{m}$ , and  $y=0.098\mu\text{m}$  is verified by the simulation results (Fig. 2. 8). The model can provide accurate  $R_{\text{th,BEOL}}$  as compared to the flat isothermal plane model.

With the  $R_{\text{th,BEOL}}$  model, the specific thermal resistivities ( $\rho$ , thermal resistance per unit area) are calculated for both BEOL using listed metal density and Si substrate, and compared to the free convection (Table 2. 3). The  $\rho_{\text{th,convection}}$  is over five orders of magnitude larger than  $\rho_{\text{th,BEOL}}$  and  $\rho_{\text{th,sub}}$ .

**Fig. 2. 7** Simulation structure and settings for  $R_{\text{th,BEOL}}$  extraction

**Fig. 2.8** Comparison of  $R_{th,BEOL}$  models with simulation results

**Table 2.3** BEOL metal densities and specific thermal resistivity

| BEOL metal densities                                |        |

|-----------------------------------------------------|--------|

| Via layers                                          | 5%     |

| M1~M6                                               | 60%    |

| M7 and M8                                           | 80%    |

| Specific thermal resistivity (K•μm <sup>2</sup> /W) |        |

| $\rho_{th,BEOL}$                                    | 4.8E4  |

| $\rho_{th,sub}$ (152μm)                             | 1.0E6  |

| $\rho_{th,sub}$ (800μm)                             | 5.4E6  |

| $\rho_{th,convection}$                              | 2.0E11 |

## 2.4 Thermal Resistance Modeling of FinFET

### 2.4.1 Intrinsic Thermal Resistance of FinFET

The intrinsic thermal resistance of the entire device  $R_{th,device}$  decreases with the increasing device layout due to the enlarged heat dissipation area. To evaluate the SHE in FinFETs with different layout size, the intrinsic thermal resistance of a single channel ( $R_{th0,device}$ ) should be used for the convenience (Fig. 2. 9). Given the  $R_{th,device}$  value of a multi-fin or multi-finger FinFET, the  $R_{th0,device}$  of a single channel is obtained as:

$$R_{th0,device} = R_{th,device} \times (\text{fin \#}) \times (\text{finger \#}) \quad (2.8)$$

**Fig. 2. 9** Thermal resistance of the entire device and a single channel

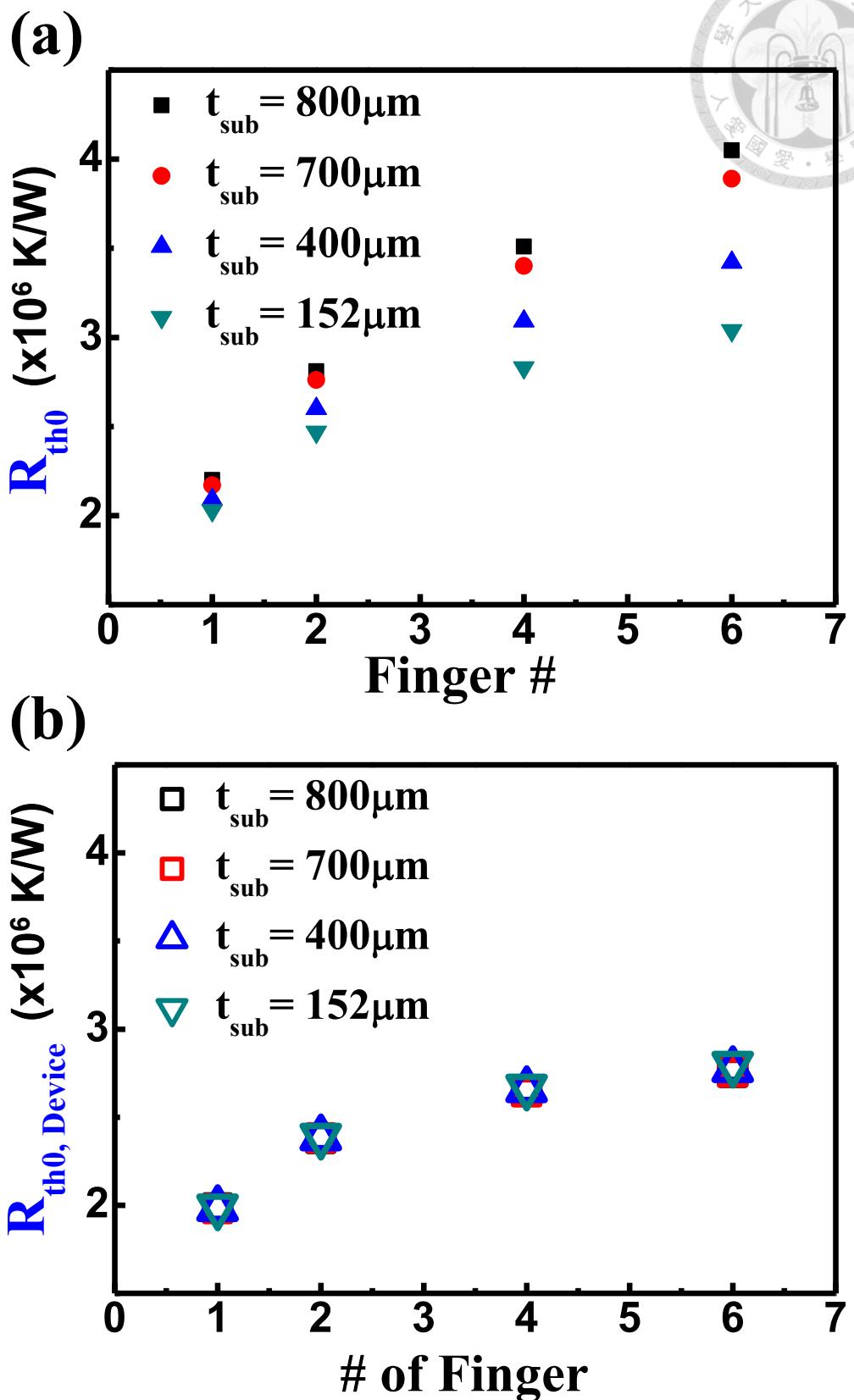

Fig. 2. 10 (a)  $R_{th0,\text{total}}$  and (b)  $R_{th0,\text{device}}$  with different substrate thickness

It is important to extract the  $R_{th0,device}$  from the  $R_{th0,total}$ . The typical substrate thickness of a Si wafer is about 800  $\mu\text{m}$ . However, to achieve small form factor of the mobile phone, the AP dies are usually thinned down to 6 mils (152  $\mu\text{m}$ ). The simulated

$R_{th0,total}$  under face-up configuration is observed to be highly dependent on the substrate thickness (**Fig. 2. 10 (a)**). Using the measured or simulated  $R_{th0,total}$  with the substrate thickness of 800  $\mu\text{m}$  could overestimate the device  $T_j$  after the thin down process.

The  $R_{th0,device}$  is decoupled using equation (2.3), and shows no substrate thickness dependence (**Fig. 2. 10 (b)**). It is the intrinsic characteristic of the device and would not be affected by substrate or BEOL.

## 2.4.2 Layout and Geometry Dependence of Intrinsic Thermal Resistance

The device  $T_j$  can be predicted by the following equation:

$$T_j - T_{chassis} = R_{th} \times \dot{Q}_{total} = R_{th0} \times \dot{Q}_{single\ channel} \quad (2.9)$$

, where  $\dot{Q}_{total}$  is total power of the device and  $\dot{Q}_{single\ channel}$  is power of a channel.

To see the layout and geometry dependence of SHE in FinFETs,  $R_{th0,device}$  is extracted and fitted for both face-up and face-down configurations.

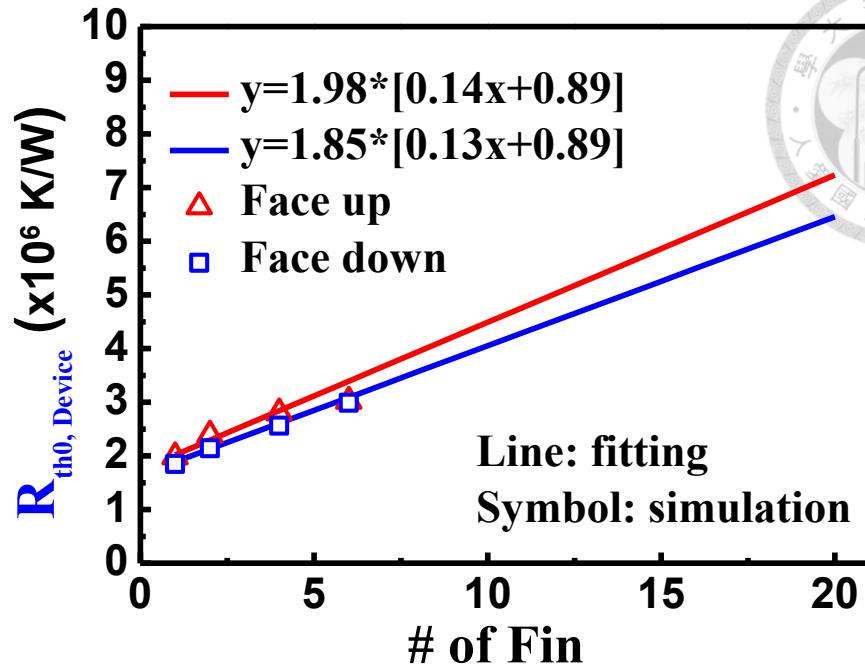

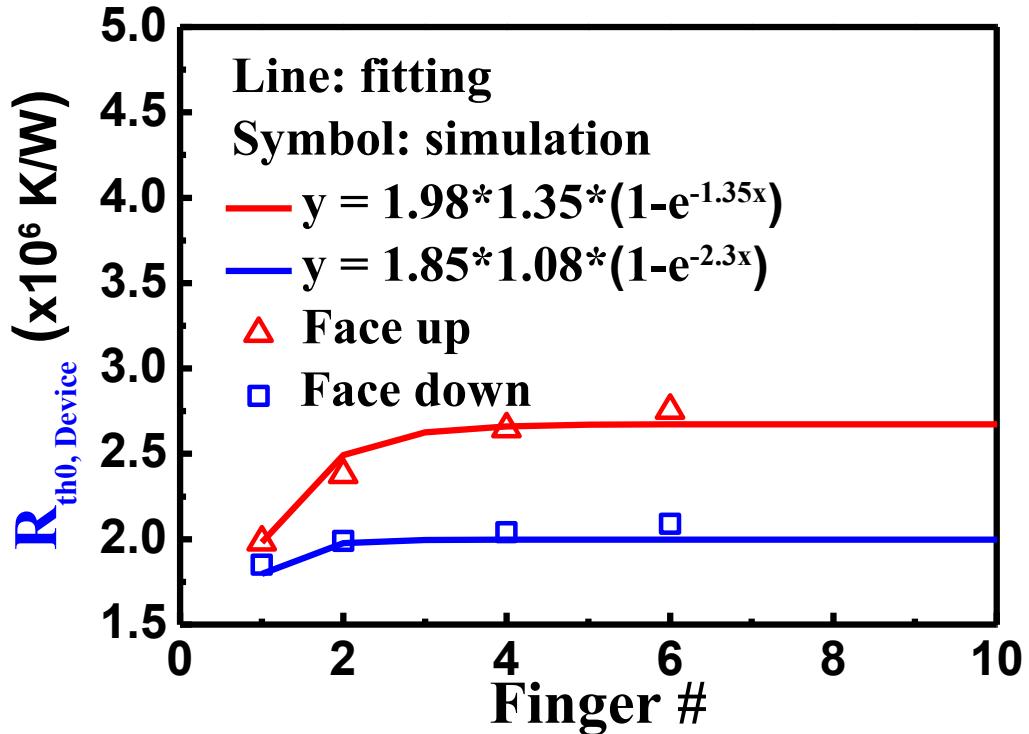

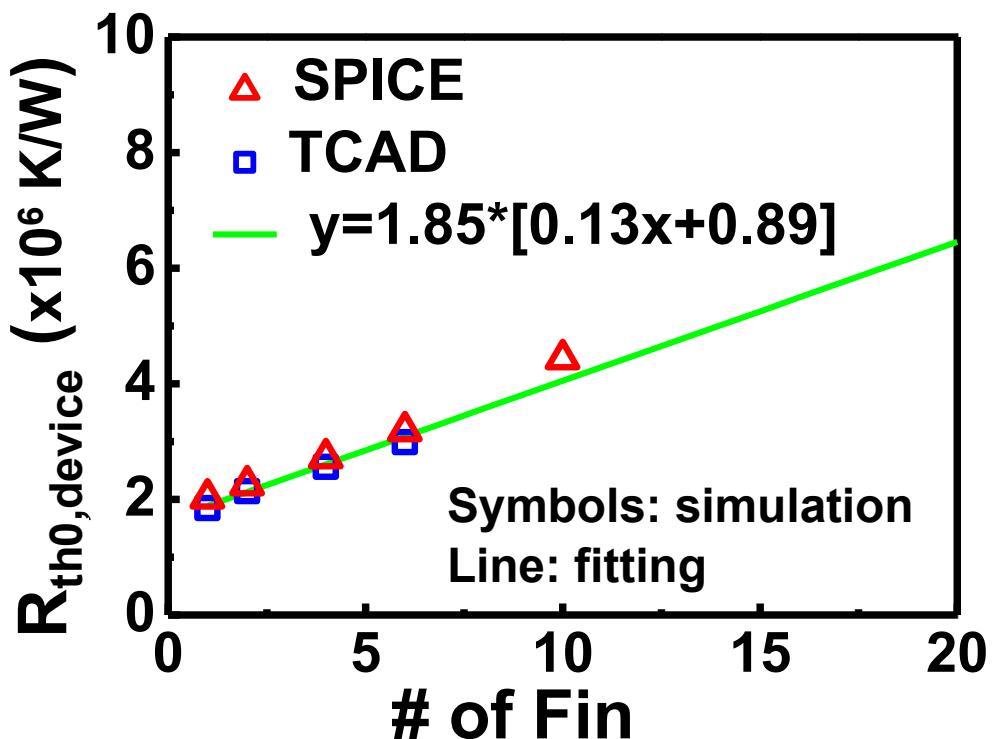

The  $R_{th0,FinFET}$  is observed to be linearly dependent on the fin number (**Fig. 2. 11**) and can be fitted by:

$$R_{th0,FinFET} = 1.98 \times [0.13(fin \#) + 0.87] \left( \frac{K}{\mu W} \right) \quad (2.10)$$

, and

$$R_{th0,FinFET} = 1.85 \times [0.13(fin \#) + 0.89] \left( \frac{K}{\mu W} \right) \quad (2.11)$$

for face-up and face-down configurations, respectively

On the contrary, the  $R_{th0,FinFET}$  saturates as the number of finger increases (**Fig. 2.**

**12**) and is fitted by:

$$R_{th0,FinFET} = 1.98 \times [1.35(1 - e^{-1.35 \times (finger \#)})] \left( \frac{K}{\mu W} \right) \quad (2.12)$$

, and

$$R_{th0,FinFET} = 1.85 \times [1.08(1 - e^{-2.30 \times (finger \#)})] \left( \frac{K}{\mu W} \right) \quad (2.13)$$

for face-up and face-down configurations, respectively.

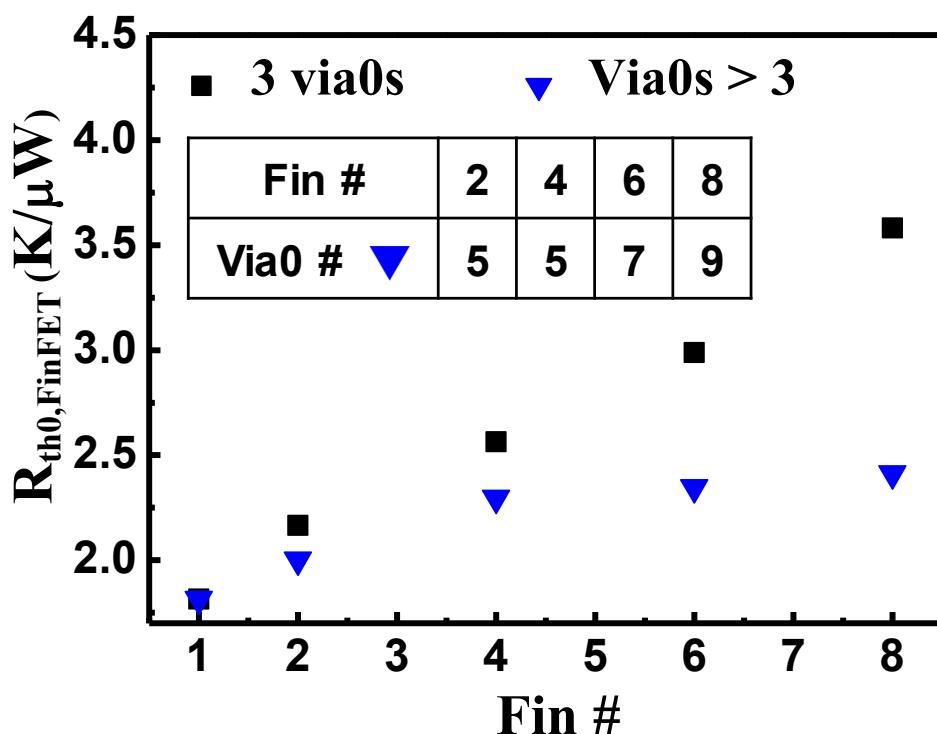

The difference trends of  $R_{th0,FinFET}$  with increasing number of fin and increasing number of finger is due to the number of via0 on the FinFETs. As fin number increases, the number of via0 remains three. For fixed three via0s, the  $R_{th0,FinFET}$  increases linearly with the increasing total area. On the other hand, the number of via0 increases with the increasing finger number. The enhanced heat dissipating ability by additional via0s makes  $R_{th0,FinFET}$  to saturate.

The results reveals that adding additional via0s can ease SHE, and will be further discussed in chapter 6.

Fig. 2. 11  $R_{th0,device}$  fitting as a function of fin number for face-up and face-down

configurations

Fig. 2. 12  $R_{th0,device}$  fitting as a function of finger number for face-up and face-down

configurations

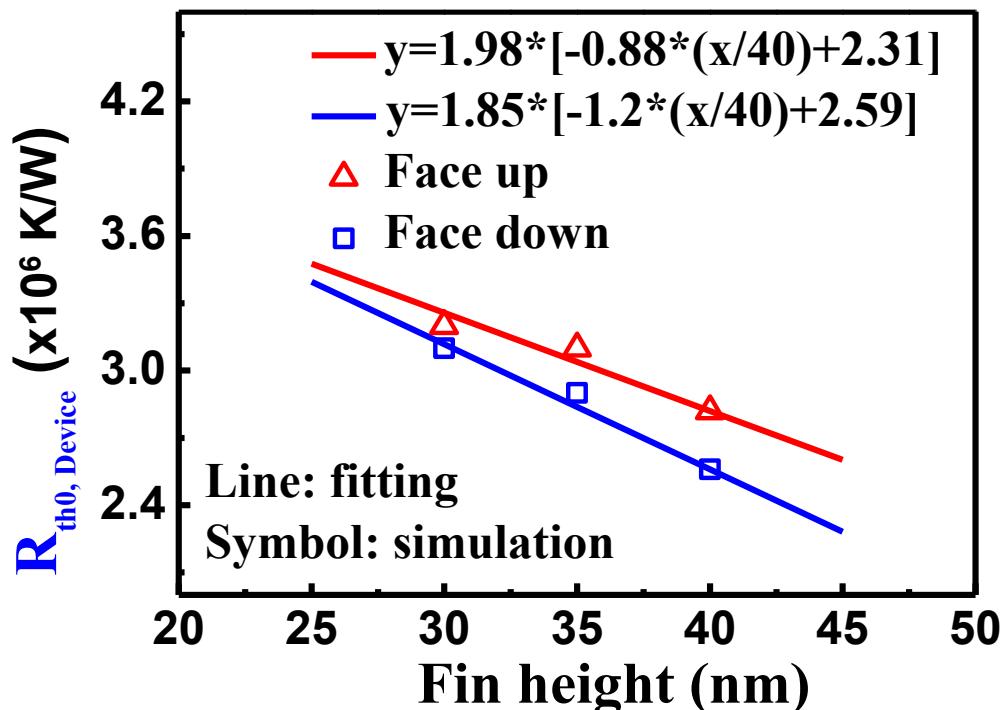

The contact area of metal gate increases with the increasing fin height, leading to the decreasing  $R_{th0,FinFET}$  in both cases.

The fitted  $R_{th0,FinFET}$  are:

$$R_{th0,FinFET} = 1.98 \times \left[ -0.88 \left( \frac{H_{fin}}{40nm} \right) + 2.31 \right] \left( \frac{K}{\mu W} \right) \quad (2.14)$$

, and

$$R_{th0,FinFET} = 1.85 \times \left[ -1.2 \left( \frac{H_{fin}}{40nm} \right) + 2.59 \right] \left( \frac{K}{\mu W} \right) \quad (2.15)$$

for face-up and face-down configurations, respectively.

**Fig. 2. 13**  $R_{th0,device}$  fitting as a function of fin height for face-up and face-down configurations

The summarized final equations are:

Face-up:

$$R_{th0,device} = 1.98 \times [0.13(fin \#) + 0.87] \times [1.35(1 - e^{-1.35 \times (finger \#)})] \times \\ [-0.88 \left( \frac{H_{fin}}{40nm} \right) + 2.31] \left( \frac{K}{\mu W} \right) \quad (2.16)$$

Face-down:

$$R_{th0,device} = 1.85 \times [0.13(fin \#) + 0.89] \times [1.08(1 - e^{-2.30 \times (finger \#)})] \times \\ [-1.2 \left( \frac{H_{fin}}{40nm} \right) + 2.59] \left( \frac{K}{\mu W} \right) \quad (2.17)$$

The face-down configuration has a lower  $R_{th0,device}$  because the FinFET is not a vertically zygomorphic structure. With face-down, the heat flux flows through the via0s which have a smaller thermal resistivity as compared to the channel stopper and STI of the FinFET.

## 2.5 Summary

In this chapter, the intrinsic thermal resistance of 14nm FinFETs is simulated using TCAD and extracted from the thermal resistance circuit. To decouple the  $R_{th0,FinFET}$ , accurate thermal resistance of BEOL is essential. A two-step pseudo isothermal plane model is used to calculate the  $R_{th,BEOL}$  based on the non-flat isothermal plane in the BEOL observed in the simulation results. The extracted  $R_{th0,FinFET}$  has no substrate thickness dependence and is the intrinsic characteristic of FinFETs.

The free convection of air has a large thermal resistance and should be considered for both face-up (conventional measurement, heat flow from the channel to substrate) and face-down (flip-chip, heat flow from the channel to metal contact) configurations.

The FinFET is not a vertically zygomorphic structure and the heat flow direction affects  $R_{th0,FinFET}$ . The layout and geometry dependence of  $R_{th0,FinFET}$  is summarized by fitted equations. The face-up  $R_{th0,FinFET}$  is higher than face-down  $R_{th0,FinFET}$ .

Device temperature with arbitrary BEOL metal density can be predicted by the proposed  $R_{th0,device}$  and  $R_{th,BEOL}$  model. The  $R_{th0,device}$  model can also be adopted in the circuit simulation for IC design.

## 2.6 References

[2.1] C.W. Chang, S.E. Liu, B.L. Lin, C.C. Chiu, Y.-H. Lee, and K. Wu, " Thermal Behavior of Self-heating Effect in FinFET Devices Acting on Back-end Interconnects," *Reliability Physics Symposium (IRPS), 2015 IEEE International*, pp. 2F.6.1- 2F.6.5.

[2.2] E. Bury, B. Kaczer, D. Linten, L. Witters, H. Mertens, N. Waldron, X. Zhou, N. Collaert, N. Horiguchi, A. Spessot, and G. Groeseneken, " Self-heating in FinFET and GAA-NW using Si, Ge and III/V channels," in *IEEE IEDM Tech. Dig.*, Dec. 2016, pp. 15.6.1-15.6.4.

[2.3] Muhammad Abdul Wahab, SangHoon Shin, and Muhammad Ashraful Alam, "3D modeling of spatio-temporal heat-transport in III-V gate-all-around transistors allows accurate estimation and optimization of nanowire temperature, " *IEEE Transactions on Electron Devices*. Vol.62, No.11, Nov. 2015, pp.3595-3604.

[2.4] F. Menges, F. Motzfeld, H. Schmid, P. Mensch, M. Dittberner, S. Karg, H. Riel, and B. Gotsmann, " Local thermometry of self-heated nanoscale devices," in *IEEE IEDM Tech. Dig.*, Dec. 2016, pp. 15.8.1-15.8.4.

[2.5] D. Jang, E. Bury, R. Ritzenthaler, M. Garcia Bardon, T. Chiarella, K. Miyaguchi, P. Raghavan, A. Mocuta, G. Groeseneken, A. Mercha, D. Verkest, and A. Thean, " Self-heating on bulk FinFET from 14nm down to 7nm node," in *IEEE IEDM Tech. Dig.*, Dec. 2015, pp. 11.6.1-11.6.4.

[2.6] S. Natarajan, M. Agostinelli, S. Akbar, M. Bost, A. Bowonder, V. Chikarmane, S. Chouksey, A. Dasgupta, K. Fischer, Q. Fu, T. Ghani, M. Giles, S. Govindaraju, R. Grover, W. Han, D. Hanken, E. Haralson, M. Haran, M. Heckscher, R. Heussner, P. Jain, R. James, R. Jhaveri, I. Jin, H. Kam, E. Karl, C. Kenyon, M. Liu, Y. Luo, R. Mehandru, S. Morarka, L. Neiberg, P. Packan, A. Paliwal, C. Parker, P. Patel, R. Patel, C. Pelto, L. Pipes, P. Plekhanov, M. Prince, S. Rajamani, J. Sandford, B. Sell, S. Sivakumar, P. Smith, B. Song, K.

Tone, T. Troeger, J. Wiedemer, M. Yang, K. Zhang, " A 14nm logic technology featuring 2<sup>nd</sup>-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 $\mu\text{m}^2$  SRAM cell size," in *IEEE IEDM Tech. Dig.*, Dec. 2014, pp. 3.7.1-3.7.4.

[2.7] Ramez Cheaito, John C. Duda, Thomas E. Beechem, Khalid Hattar, Jon F. Ihlefeld, Douglas L. Medlin, Mark A. Rodriguez, Michael J. Campion, Edward S. Piekos, and Patrick E. Hopkins, " Experimental investigation of size effects on the thermal conductivity of silicon-germanium alloy thin films," *Physical Review Letters*, 109, 195901, 2012.

[2.8] Changwook Jeong, Supriyo Datta, and Mark Lundstrom, " Thermal conductivity of bulk and thin-film silicon: A Landauer approach," *Journal of Applied Physics*, 111.9, 093708, 2012.

[2.9] Hazim B. Awbi, " Calculation of convective heat transfer coefficients of room surfaces for natural convection," *Energy and Building*, 28. 2, 1998, pp. 219-227.

# Chapter 3 Transient Thermal Simulation of Inverters with Capacitive Loading Effects

## 3.1 Introduction

AC self-heating effect in scaled FinFET circuits retards the performance, i.e. dark silicon. It was reported that about 20% of the chip area will be dark at 22nm node and more than 50% of the chip cannot be utilized for technology nodes beyond 10nm [3.1]. Circuit level thermal management and self-heating aware design rules are the keys to achieve robust circuit design.

In chapter 2, we've pointed out that the embedded SH measurements such as resistance thermometry structure [3.2],[3.3] and heater-sensor structure [3.3] can only provide the average temperature near the DUT instead of device  $T_j$ , and the precision of temperature is suffering from the difference of boundary condition between face-up and face-down configurations. To monitor DC SHE in scaled FinFETs, the intrinsic thermal resistance ( $R_{th0,FinFET}$ ) model is proposed in chapter 2.

In this chapter, transient SHE in FinFETs and inverters will be investigated using TCAD simulation. Capacitive loading effects of the inverter on  $T_j$  and the temperature distribution in the metal layer of an inverter are investigated with AC input.

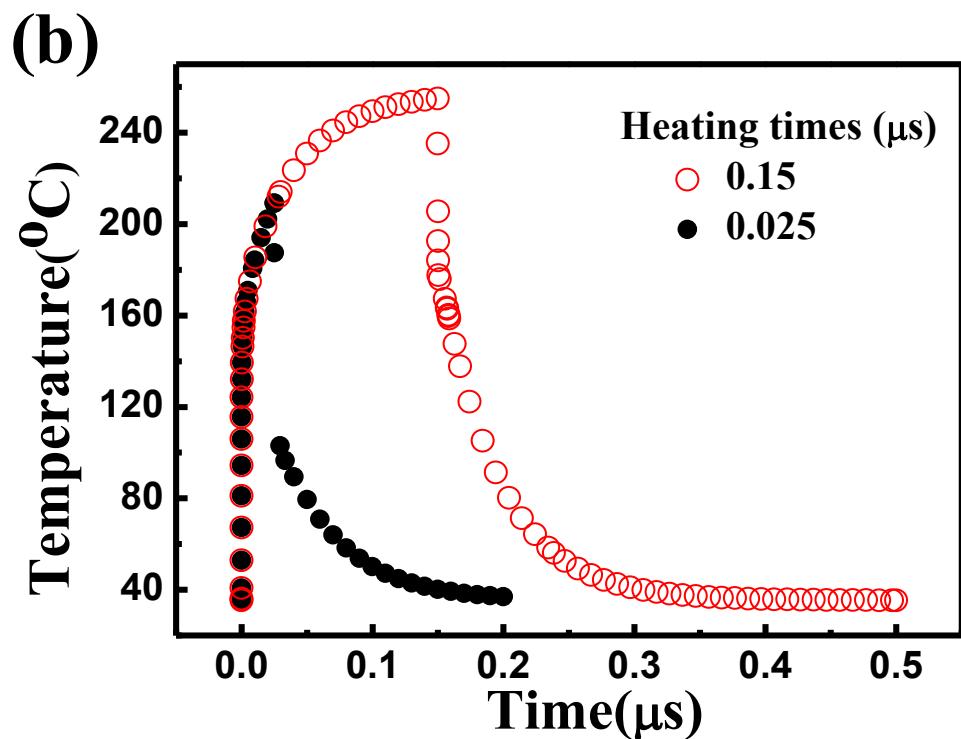

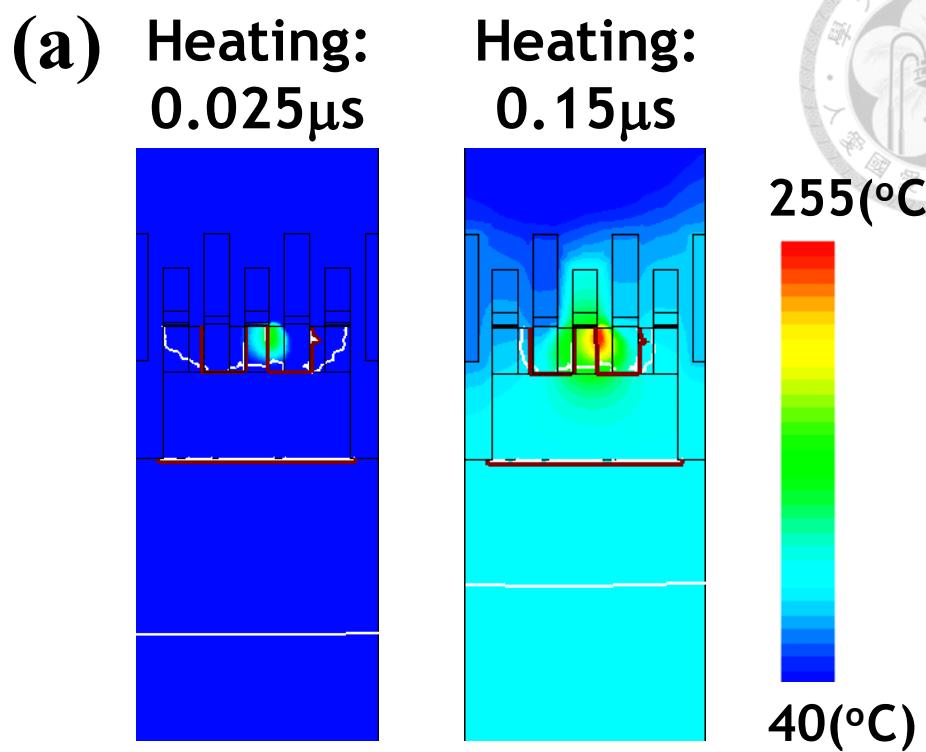

### 3.2 Self-heating Effect in FinFETs with Transient Input

The transient SHE in scaled FinFET is simulated by transient input with different pulse width. **Fig. 3. 1 (a)** shows the simulated cross-sectional temperature contour with different heating times. It is observed that different heating times lead to different hot volumes. With the pulse width of 25ns, the hotspot is localized in the drain extension. It could be even more difficult to measure the SHE with transient input than DC input. The high temperature region extends to the substrate and MEOL with the pulse width of 150ns.

The Cooling time relates to the heat dissipating ability ( $R_{th}$ ), and thermal capacitance ( $C_{th}$ ). The  $C_{th}$  is proportional to the hot volume in the device. As a result, the short heating time (small hot volume) leads to short cooling time (**Fig. 3. 1 (b)**).

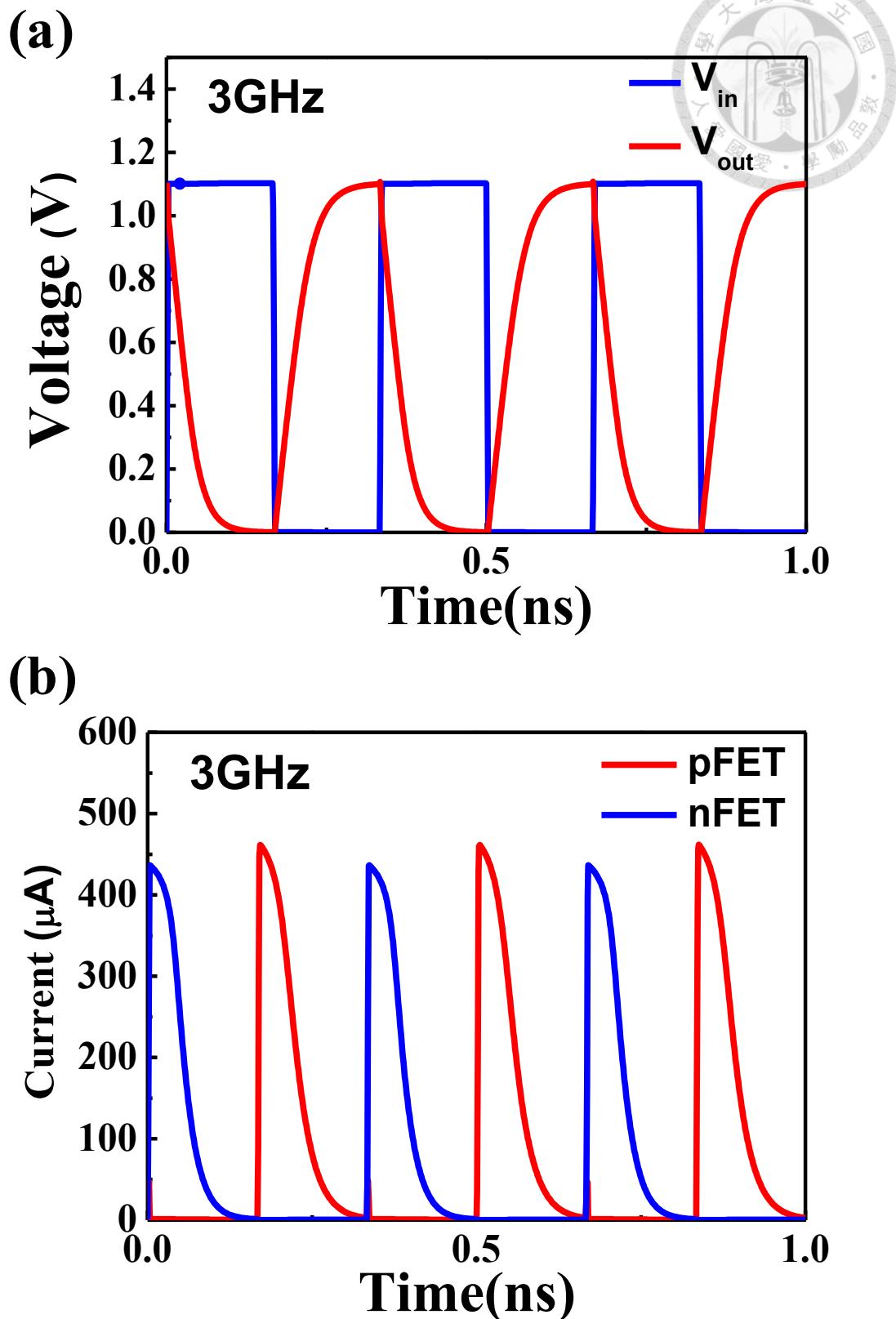

### 3.3 Electrical Characteristics of the Inverter

Capacitive loading is essential for the mix-mode electro-thermal simulation. An inverter consists of a four-fin-one-finger nFinFET and a four-fin-one-finger pFinFET is experimentally measured by a square wave input with the frequency of 3GHz and the amplitude of 1.1V (**Fig. 3. 2 (a)**). The corresponding output voltage and output current of are shown in **Fig. 3. 2 (a)** and **(b)**, respectively.

Fig. 3. 1 (a) Cross-sectional temperature distribution and (b) transient  $T_j$  response

with different input pulse width

**Fig. 3.2 (a)** Measured input and output voltage of an inverter and **(b)** the transient

responses of output current and simulated  $T_j$  of the inverter

The amount of charge/discharge is obtained by integrate the output current in a period:

$$Q = \int I(t) \times dt = 2.38E - 14(C) \quad (3.1)$$

The output capacitive loading is calculated by:

$$C_{load} = \frac{Q}{V} = \frac{2.38E-14}{1.1} = 2.164E - 14 = 21.64 \text{ (fF)} \quad (3.2)$$

### 3.4 Self-heating and Output Loading Effect in Inverters

The transient response of the  $T_j$  in the inverter consist of 4-fin-1-finger n/pFinFETs with output capacitance of 21.64 fF is investigated by mix-mode TCAD simulation.

**Fig. 3. 3** Simulation structure of the inverter with face-down configuration

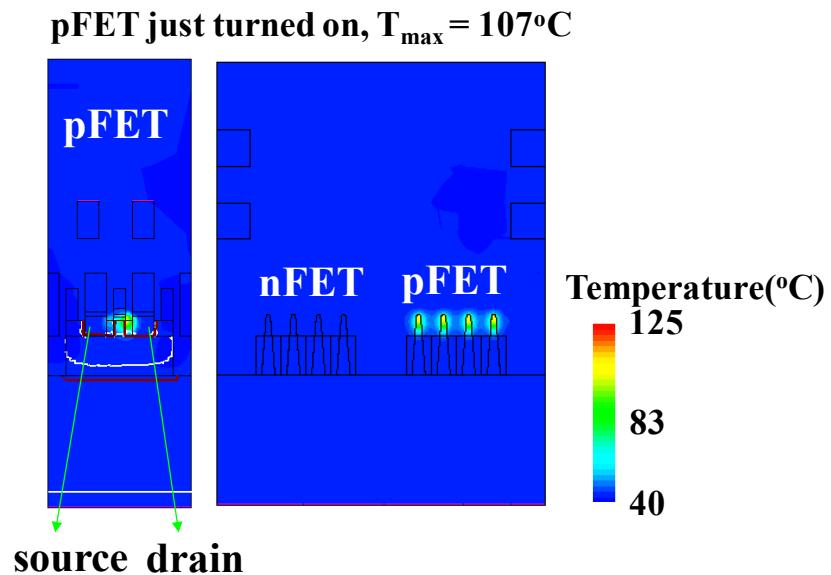

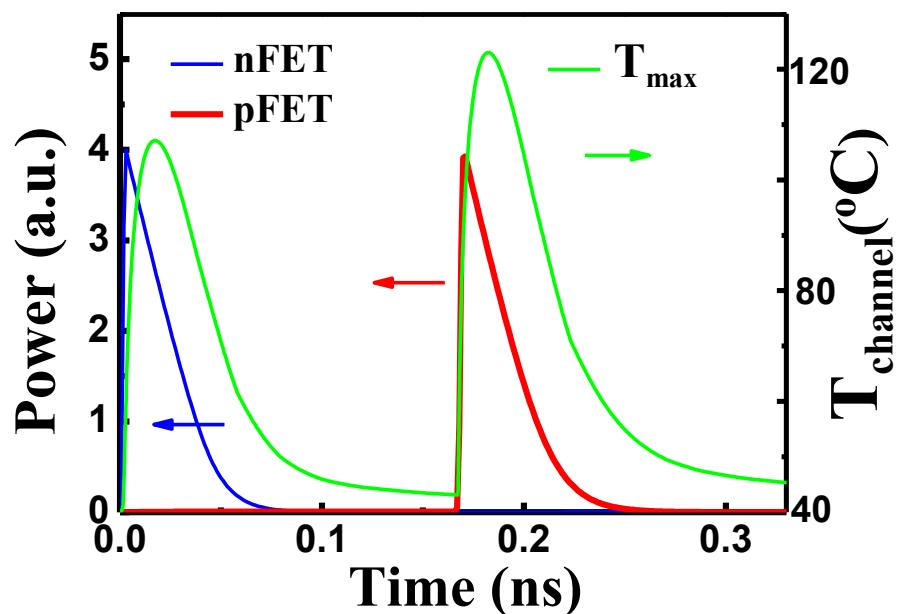

The simulation structure is shown in **Fig. 3. 3**, and the simulated  $T_{\max}$  in the inverter is located at the channel of turned on device (**Fig. 3. 4**). Due to the low thermal conductivity of SiGe S/D, the highest temperature during transient input is with pFET turned on (**Fig. 3. 5**).

**Fig. 3. 4** Cross-sectional temperature distribution in the inverter

**Fig. 3. 5** Transient responses of input power and the  $T_{\max}$  in the inverter

### 3.4.1 Output Capacitive Loading Effects on $T_j$

**Fig. 3. 6** The device temperature of inverters with different  $C_{load}$

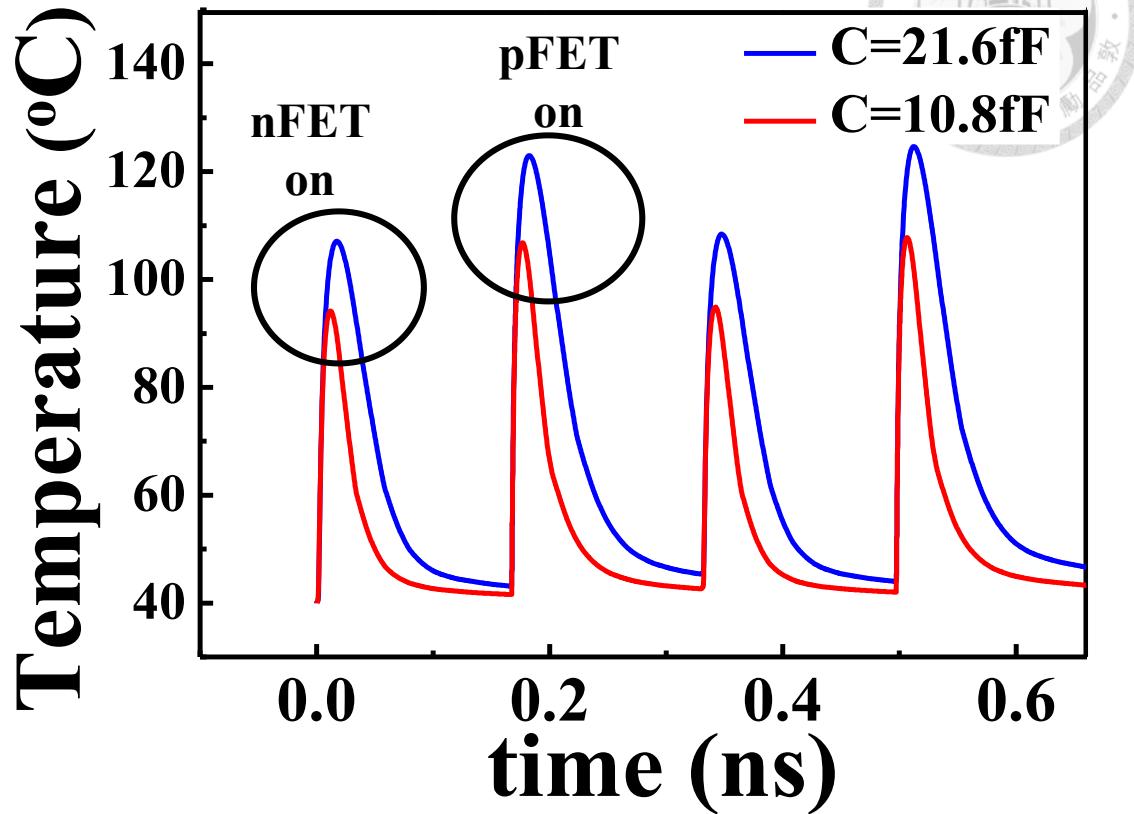

Inverters with 4-fin-1-finger n/pFinFETs are simulated with different capacitive loadings under 3GHz square wave input. **Fig. 3. 6** shows the simulated transient temperature response. With the low output capacitance of 10.8fF, both the  $T_{max}$  and the high temperature duration decreases due to the reduction of charge and discharge time. Lowering the parasitic capacitance could help to gain benefits not only from reducing the latency but also from lowering the temperature to maintain the performance and improve the reliability.

### 3.4.2 Drive Current, $T_j$ , and High Temperature Duration

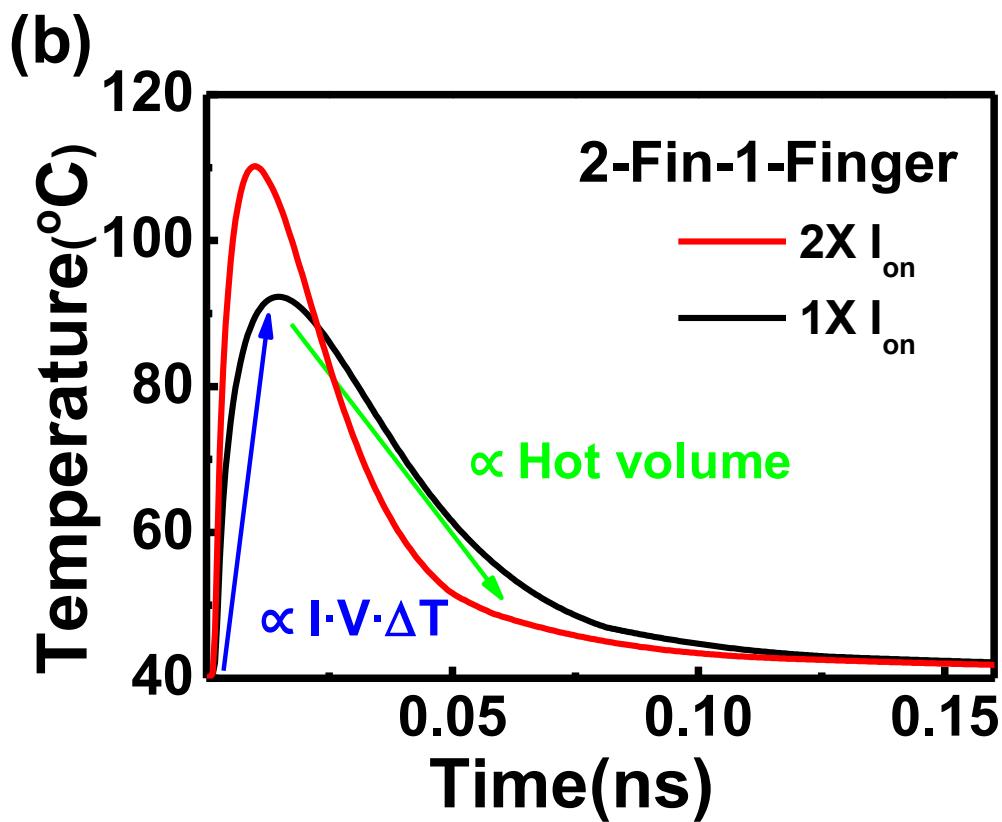

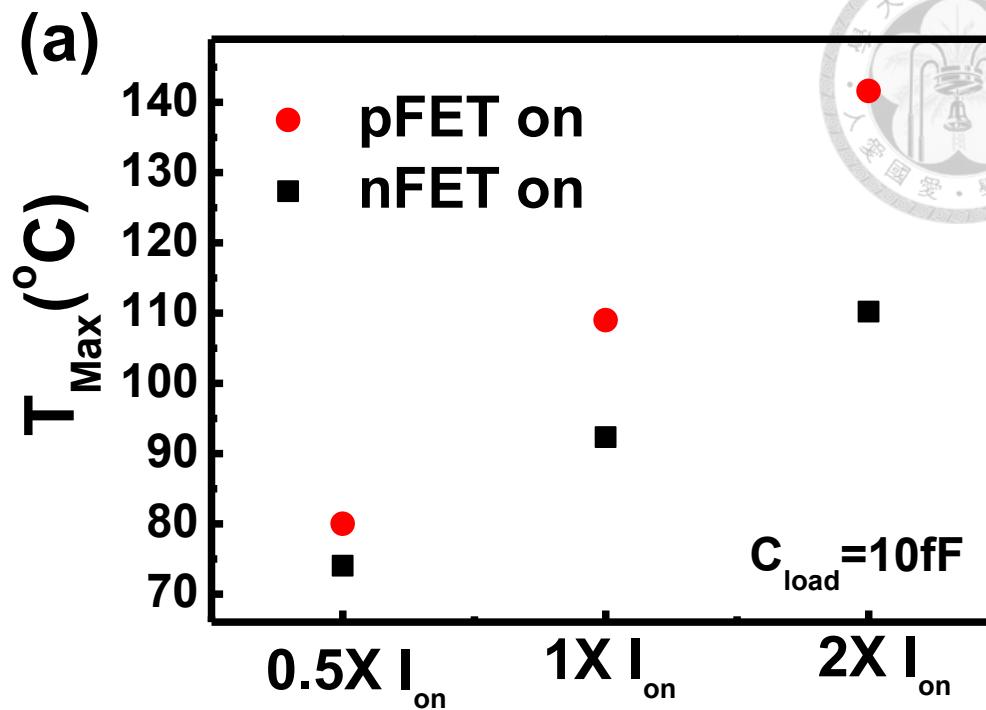

$T_{max}$  in an inverter consists of 2-fin-1-finger n/pFinFETs with the capacitive loading of 10fF is simulated with different  $I_{on}$  by intentionally changing the channel mobility.

Increasing  $T_{max}$  is found with the increasing  $I_{on}$  due to the increased Joule heating (Fig. 3. 7 (a)). The degradation mechanisms could be accelerated by the increased temperature. However, the degradations are also proportional to the duration of stress condition. Decreasing  $I_{on}$  can help decreasing the Joule heating and  $T_{max}$ , but the charge time is extended which results in an increased hot volume and longer high temperature duration (Fig. 3. 7 (b)). The drive current of the inverter affects not only the Joule heat but also the time for charge/discharge, and should be designed carefully from the aspect of reliability.

### 3.4.3 Layout Size Effects of Inverters

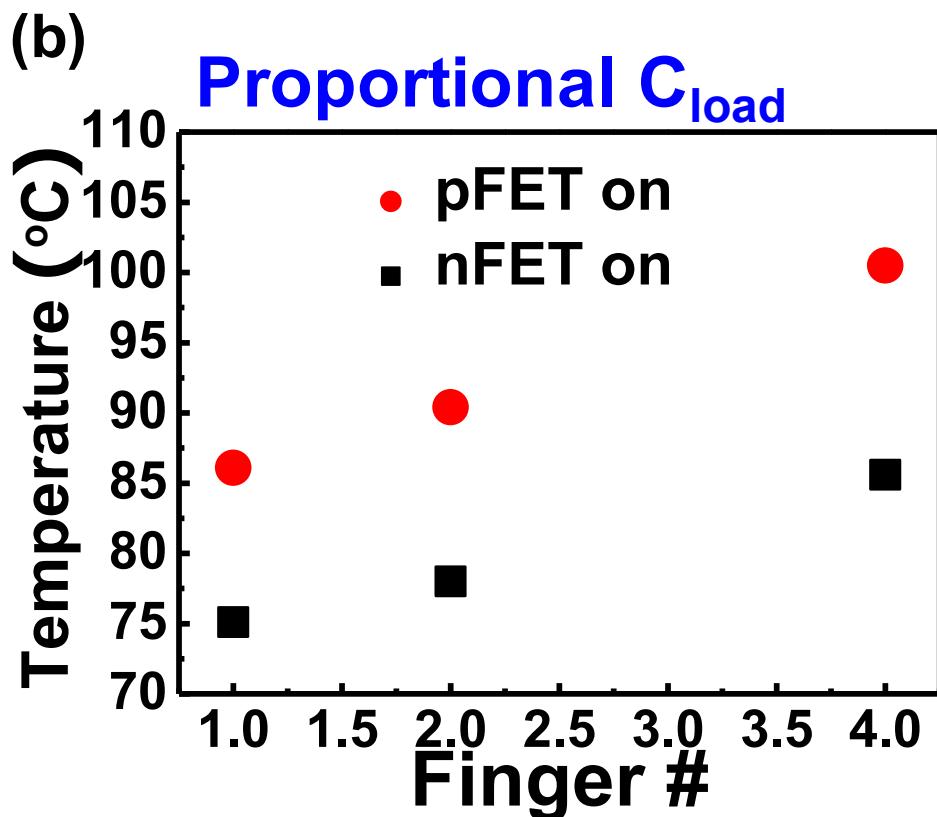

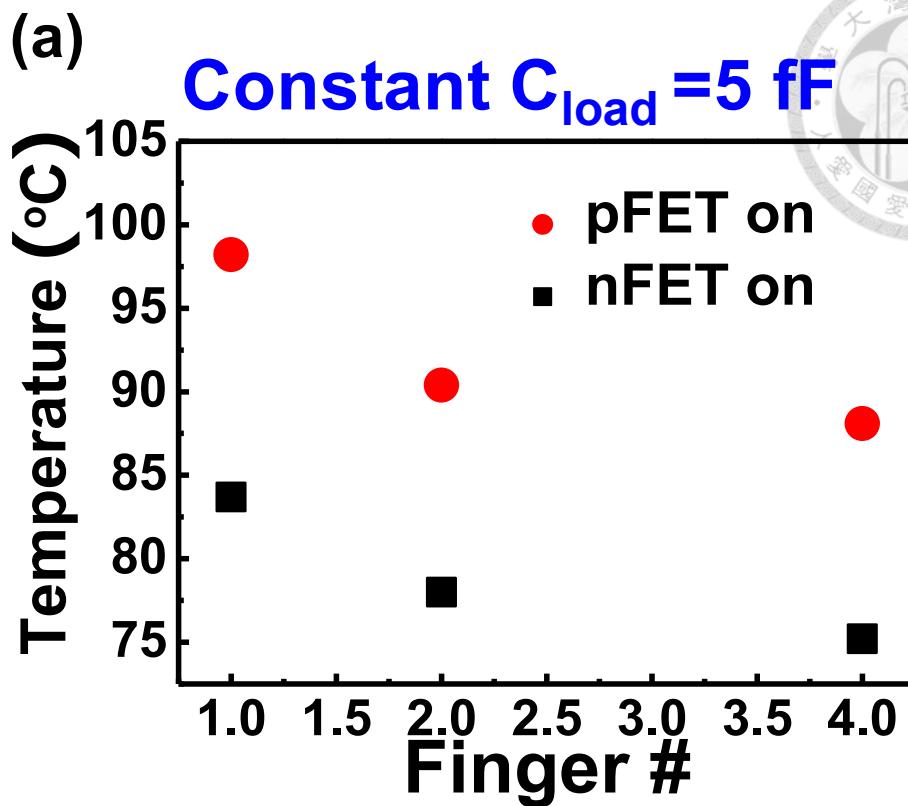

$T_{max}$  decreases with the increasing layout size when charging and discharging a 5fF output loading (Fig. 3. 8 (a).) The reduction of  $T_{max}$  is due to the reducing  $R_{th,BEOL}$  by increasing device area. However, in real circuit, the layout sizes of connected inverters are usually the same, i.e. the output capacitive load is proportional to the layout size, and the charge/ discharge time increases as the output load increases.

**Fig. 3.7**  $T_{\text{max}}$  of an inverter (2-fin-1-finger n/pFinFETs) with different  $I_{\text{on}}$ , and (b) the temperature evolution