國立臺灣大學電機資訊學院電機工程研究所

#### 博士論文

Graduate Institute of Electrical Engineering College of Electrical Engineering and Computer Science National Taiwan University Doctoral Dissertation

#### 具多字元狀態轉移之高效字串比對引擎

Efficient String Matching Engines with Multiple-Character State Transitions

## 陳建吉

Chien-Chi Chen

### 指導教授:王勝德教授

Advisor: Sheng-De Wang, Ph.D.

中華民國 103 年 6 月

June 2014

國立臺灣大學博士學位論文

## 口試委員會審定書

具多字元狀態轉移之高效字串比對引擎 Efficient String Matching Engines with Multiple-Character State Transitions

本論文係陳建吉君(學號 D93921012)在國立臺灣大學電機工程 學系完成之博士學位論文,於民國 103 年 7 月 22 日承下列考試委員 審查通過及口試及格,特此證明。

口試委員:

王际德

(指導教授)

(簽名)

Ø (簽名)

系主任

### 致謝

十年磨一劍,很高興能順利完成學位。首先,最感謝的當然是我的 指導教授,王勝德老師,感謝他的耐心與支持,我才得以完成學位。 另外,在這些年中,許多來來去去的學長與學弟妹們,互相的提攜與 打氣,也是我前行的力量之一。進入博士班的同時,也是我的生活變 化的開始。首先,身分變成已婚單身的狀態,然後陸續接觸一些成長 課程,包括兩次的單車環島,想法和生活慢慢地變得更爲自在和積 極。與我成長的同時,三個男孩也一起成長,真心感謝他們的獨立, 讓我能專注於自己的事。最常被問的是,爲何要花這麼多時間在這學 位上,其實在回到學生身分,專注於求學的過程當中,就是一種成就 吧。隨著學業的完成,我的十年大運將進入比較具有挑戰的階段,也 意味著,我的另一階段的生活體驗即將開始。

感謝老天,謝謝所有,出現在我生命中的貴人。

## 中文摘要

由 Aho 和 Corasick 所提出的演算法 (簡稱 AC 演算法) 可以很有 效率地在一段文字中搜尋多個關鍵字所在的位置,因而被廣泛地使用 於完全字串比對。然而,AC 演算法在運作時,只能一次處理一個字 元,因而其效能受限於運作時脈。本論文依據 AC 演算法,提出新穎 的具有多字元狀態轉移之字串比對架構,可以平行檢視多個字元,藉 以加倍提升字串比對的效能。首先, 說明實作 AC 演算法的三種有限 自動機 (finite automaton, 簡稱 FA) 的作法,包括確定性有限自動 機 (Deterministic Finite Automaton,簡稱 DFA)、非確定有限自動機 (Nondeterministic Finite Automaton, 簡稱 NFA)、以及複合有限自動 機 (Hybrid Finite Automaton,簡稱 hybrid FA) 的作法。接著,提出 一種推導演算法,藉以將前述 FA 推導為多字元的 FA,使其能夠平 行檢視多個字元。同時,因為平行檢視多個字元所引起的對齊問題 (alignment problem),也藉由輔助轉移函式 (assistant transition) 來解 決。所推導的多字元 FA 使用可程式元件來評估,所得到的評估結果 顯示其能有效地加倍提升字串比對的效能。其中所得到的最佳結果為 16字元 AC-NFA 的實作,其可運作於 167.36MHz 的時脈,換算得到的 字串比對效能為 21.4Gbps。

關鍵字:字串比對,確定性及非確定有限自動機,入侵偵測系統

# Abstract

The algorithm of Aho and Corasick (AC-algorithm) can locate multiple keywords in a text efficiently; and thus it is widely used in the exact string matching. However, the AC-algorithm processes the text character by character with a performance limited by the processing clock. This thesis proposes novel string-matching architectures with multiple-character state transitions based on the AC-algorithm, which can inspect multiple characters in parallel to multiply the throughput. At first, three finite automaton (FA) approaches including Deterministic Finite Automaton (DFA), Nondeterministic Finite Automaton (NFA), and hybrid FA approaches are presented to implement the AC-algorithm. Subsequently, a derivation algorithm is proposed to derive these FAs to multi-character FAs to allow for the inspection of multiple characters in parallel. Additionally, the alignment problem, which occurs while multiple characters are being inspected in parallel, is solved by using assistant transitions. The derived multi-character FAs are evaluated on programmable devices and the evaluation results indicate that the throughput can be multiplied effectively. The achievable throughput of the best result is 21.4Gbps obtained by a 16-character AC-NFA implementation operating at a 167.36MHz clock.

**Keywords:** String-matching, deterministic and nondeterministic finite automaton, intrusion detection system

# Contents

| 致        | 謝     |                                          | i            |

|----------|-------|------------------------------------------|--------------|

| 中        | 文摘    | 要                                        | iii          |

| Al       | ostra | let                                      | $\mathbf{v}$ |

| Co       | onter | nts                                      | vii          |

| Li       | st of | Figures                                  | xi           |

| Li       | st of | Tables                                   | ciii         |

| 1        | Intr  | oduction                                 | 1            |

|          | 1.1   | Exact String Matching and Motivations    | 1            |

|          | 1.2   | Approach Overview                        | 2            |

|          | 1.3   | Thesis Organization                      | 4            |

| <b>2</b> | Rela  | ated Work                                | <b>5</b>     |

|          | 2.1   | Optimization in Hardware                 | 5            |

|          | 2.2   | Multi-Character Hardware Approaches      | 6            |

|          | 2.3   | Software Approaches                      | 7            |

| 3        | Ahc   | o-Corasick Algorithm and Implementations | 9            |

|          | 3.1   | AC-trie                                  | 9            |

|          | 3.2   | AC-DFA                                   | 12           |

|          | 3.3   | AC-NFA                                   | 15           |

|          | 3.4   | Hybrid AC-FA                             | 18           |

|          | 3.5   | Priority Multiplexer                     | 21           |

| 4        | Mu    | lti-Character State Transitions          | <b>23</b>    |

|          | 4.1   | Alignment Problem and Previous Work      | 23           |

|          |     |         |                                      | ALG1     |    | the N | 臺    | OTOTOTO<br>NOTOTO |

|----------|-----|---------|--------------------------------------|----------|----|-------|------|-------------------|

|          | 4.2 | Deriva  | ation of Multi-Character Transitions |          | (  |       |      | 25                |

|          | 4.3 | Deriva  | ation Algorithm                      | 1        | 0  | LIN.  | 5    | 29                |

|          | 4.4 | Comp    | parison of Derivation Approaches     |          | 17 | 4     |      | 31                |

|          |     | 4.4.1   | The proposed approach                | <u>.</u> | 愛  |       | ・騨   | 31                |

|          |     | 4.4.2   | Yamagaki et al. approach             | •        |    | 976   | 1010 | 31                |

|          |     | 4.4.3   | Yang et al. approach                 |          |    |       |      | 33                |

|          |     | 4.4.4   | Summary of comparison                |          | •  | •     |      | 34                |

| <b>5</b> | Mu  | lti-Cha | aracter String-Matching Approaches   |          |    |       |      | 37                |

|          | 5.1 | Multi-  | -Character AC-DFA                    |          | •  |       |      | 38                |

|          |     | 5.1.1   | Implementation                       |          |    |       |      | 39                |

|          |     | 5.1.2   | Matching example                     |          |    |       |      | 44                |

|          |     | 5.1.3   | Experiment and evaluation            |          |    |       |      | 44                |

|          | 5.2 | Multi-  | -Character AC-NFA                    |          |    |       |      | 48                |

|          |     | 5.2.1   | Implementation                       |          |    |       |      | 49                |

|          |     | 5.2.2   | Matching example                     |          |    |       |      | 51                |

|          |     | 5.2.3   | Experiment and evaluation            |          |    |       |      | 52                |

|          | 5.3 | Multi-  | -Character Hybrid AC-FA              |          |    |       |      | 56                |

|          |     | 5.3.1   | Implementation                       |          |    |       |      | 56                |

|          |     | 5.3.2   | Matching example                     |          |    |       |      | 59                |

|          |     | 5.3.3   | Estimation of required stages        |          |    |       |      | 60                |

|          |     | 5.3.4   | Experiment and evaluation            | •        |    |       |      | 62                |

| 6        | Cor | nfigura | ble Architectures                    |          |    |       |      | 63                |

|          | 6.1 | Config  | gurable stage architecture           |          |    |       |      | 63                |

|          |     | 6.1.1   | Block diagram                        |          |    |       |      | 64                |

|          |     | 6.1.2   | Experiment and evaluation            |          |    |       |      | 65                |

|          | 6.2 | Config  | gurable data-width architecture      |          |    |       |      | 68                |

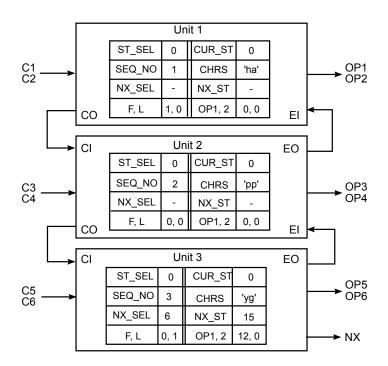

|          |     | 6.2.1   | Basic rule unit                      |          | •  |       |      | 68                |

|          |     | 6.2.2   | Example of three-unit group          |          |    |       |      | 71                |

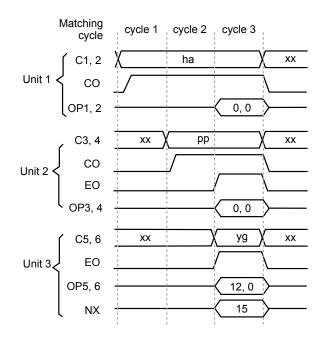

|          |     | 6.2.3   | Waveform of three-unit group         |          |    |       |      | 72                |

|          |     | 6.2.4   | Experiment and evaluation            |          | •  | •     |      | 73                |

| 7        | Cor | nparis  | on of Approaches                     |          |    |       |      | 75                |

|          | 7.1 | Comp    | paring Results                       |          |    |       |      | 75                |

|          | 7.2 | Discus  | ssions                               |          |    |       |      | 77                |

#### Contents

#### 8 Conclusions

Bibliography

# List of Figures

| 1.1  | Overview of the proposed work                              | 2  |

|------|------------------------------------------------------------|----|

| 3.1  | AC-trie                                                    | 9  |

| 3.2  | Examples of matching operations                            | 11 |

| 3.3  | AC-DFA                                                     | 12 |

| 3.4  | Basic AC-DFA implementation block diagram                  | 12 |

| 3.5  | Implementation of AC-DFA with TCAM and SRAM                | 13 |

| 3.6  | Implementation of AC-DFA with priority multiplexer         | 14 |

| 3.7  | AC-NFA                                                     | 15 |

| 3.8  | Implementation of AC-NFA                                   | 16 |

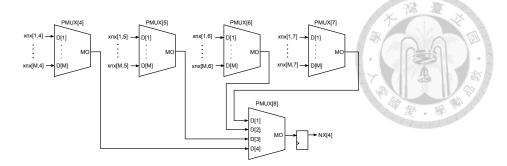

| 3.9  | Multi-stage architecture of AC-NFA                         | 17 |

| 3.10 | Block diagram of a stage unit                              | 18 |

| 3.11 | Hybrid AC-FA                                               | 19 |

| 3.12 | Implementation of hybrid AC-FA                             | 20 |

| 3.13 | Priority multiplexer implemented by chained multiplexers   | 20 |

| 3.14 | Priority multiplexer optimized for delay                   | 21 |

| 4.1  | Example of alignment problem                               | 23 |

| 4.2  | Example of 3-compressed FA                                 | 24 |

| 4.3  | Example of shallow states                                  | 24 |

| 4.4  | Architecture of three FSMs                                 | 25 |

| 4.5  | Concatenation operation                                    | 25 |

| 4.6  | Assistant transitions                                      | 26 |

| 4.7  | Derivation examples                                        | 27 |

| 4.8  | Regular-expression example                                 | 31 |

| 4.9  | Deriving 2-characters NFA by using the proposed approach   | 32 |

| 4.10 | Deriving 2-character NFA by using Yamagaki et al. approach | 33 |

| 4.11 | Deriving 2-character NFA by using Yang et al. approach     | 34 |

|      | 「 護 臺                                                                          | OTOTO . |

|------|--------------------------------------------------------------------------------|---------|

| 5.1  | Basic block diagram of a 3-character string matching engine                    | 37      |

| 5.2  | Waveform of matching operations                                                | 38      |

| 5.3  | Transitions of the 3-character AC-DFA                                          | 39      |

| 5.4  | Architecture for a 3-character AC-DFA                                          | 40      |

| 5.5  | Block diagram of a matching unit                                               | 41      |

| 5.6  | Matching example of the 3-character AC-DFA                                     | 43      |

| 5.7  | Growth of transitions of $k$ -character AC-DFAs $\ldots \ldots \ldots \ldots$  | 45      |

| 5.8  | Transitions and output multiplexers of the 3-character AC-NFA $\ . \ . \ .$    | 48      |

| 5.9  | Implementation of transitions of the 3-character AC-NFA                        | 50      |

| 5.10 | Matching example of the 3-character AC-NFA                                     | 51      |

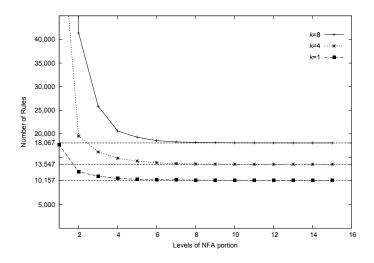

| 5.11 | Result curves for evaluation of $k$ -character AC-NFAs $\ldots \ldots \ldots$  | 52      |

| 5.12 | Transitions of multi-character hybrid AC-FA                                    | 57      |

| 5.13 | Implementation of 3-character Hybrid AC-FA                                     | 58      |

| 5.14 | Matching output circuit                                                        | 58      |

| 5.15 | Matching example of the 3-character hybrid AC-FA.                              | 59      |

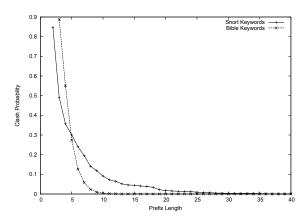

| 5.16 | The probability distribution of sharing common prefixes of various             |         |

|      | lengths                                                                        | 60      |

| 5.17 | Transitions versus NFA-levels for the $k\text{-character}$ Hybrid AC-FA $\ $ . | 61      |

| 6.1  | Main block diagram of the configurable architecture                            | 63      |

| 6.2  | Rule unit for the configurable stage architecture                              | 64      |

| 6.3  | State circuit of stages 1 through 3 for the configurable stage architec-       | -       |

|      | ture                                                                           | 64      |

| 6.4  | State circuit of the terminal stage for the configurable stage architec-       | -       |

|      | ture                                                                           | 65      |

| 6.5  | Rule unit for the configurable data-width architecture                         | 68      |

| 6.6  | Symbol descriptions of the configurable data-width rule-unit                   | 69      |

| 6.7  | Decisions of control signals for the configurable data-width rule-unit         | 70      |

| 6.8  | Example of three-unit group                                                    | 71      |

| 6.9  | Waveform of the three-unit group                                               | 72      |

| 0.9  | waveform of the three-unit group                                               | 72      |

# List of Tables

| 3.1 | States and transitions in an AC-DFA (Alicherry et al.)                                       | 13 |

|-----|----------------------------------------------------------------------------------------------|----|

| 5.1 | Transition rules of the 3-character AC-DFA                                                   | 42 |

| 5.2 | Rules for different $k$ -character AC-DFA $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 45 |

| 5.3 | Spaces for different k-character AC-DFA $\ldots$                                             | 47 |

| 5.4 | Implementation of 4-character AC-DFA in ASIC                                                 | 47 |

| 5.5 | Evaluation of multi-character AC-NFA with 1,000 Bible Keywords $~$ .                         | 53 |

| 5.6 | Evaluation of multi-character AC-NFA with 2,000 Bible Keywords $~$ .                         | 53 |

| 5.7 | Evaluation of multi-character AC-NFA with 1,000 Snort Keywords $~$ .                         | 54 |

| 5.8 | Evaluation with 1,000 Snort Keywords for Matching-Flag Output $~$ .                          | 55 |

| 5.9 | Implementing multi-character hybrid AC-FAs on FPGA                                           | 62 |

| 6.1 | Implementing the configurable architecture on FPGA                                           | 66 |

| 6.2 | Implementing the configurable architecture on ASIC                                           | 67 |

| 6.3 | Implementing the configurable architecture on FPGA $\ldots$                                  | 74 |

| 6.4 | Implementing the configurable architecture on ASIC                                           | 74 |

| 7.1 | Comparison of different approaches                                                           | 76 |

# Chapter 1 Introduction

String matching plays a major role in many applications, such as network intrusion detection systems (NIDS) and bioinformatics. String matching generally includes exact string matching and regular expression matching; exact string matching is more efficient yet less flexible for searching keywords in a text than regular expression matching. This thesis mainly focuses on developing efficient exact string matching engines.

#### 1.1 Exact String Matching and Motivations

Aho and Corasick have proposed an efficient algorithm (AC-algorithm) for exact string matching that can locate all occurrences of multiple keywords in a text in a one pass search [1]. Some applications like NIDS that need to inspect the data stream on line usually first use exact string matching to find suspected data quickly, then check the results further by other more complicated and slower approaches, such as regular expression matching.

The network bandwidth has ever been increasing as the advances of communication and integrated circuit technology. The throughput of packet inspection for NIDS must also be sped up to keep up with the network throughput otherwise the packet inspection will become the bottleneck of the network security check. A hardware string matching implementation can effectively accelerate the packet inspection process. In early work, most hardware implementations of the string matching inspect the packet data character by character, and the throughput of string matching is limited by the achievable clock rate of the hardware [2,3]. Recently, some hardware string matching approaches attempted to inspect multiple characters in a single cycle to further improve the throughput of packet inspection [4–7]. Although some researches attempted to develop a string matching engine capable of inspecting multiple characters in parallel, a systematic approach for developing such a string matching engine has yet to be developed. Furthermore, most of the researches developed the architecture according to the properties of keyword sets to optimize the performance, which lack flexibility that different keyword sets can be processed by simply updating the setting data. Therefore, this work intends to develop an intuitive and systematic derivation approach to derive multi-character transitions from an original finite state machine (FSM). Moreover, various architectures are proposed to implement the derived multi-character transitions. A generalized multi-character string matching architecture is also proposed, which can process different keyword sets by simply updating the configurations.

Figure 1.1: Overview of the proposed work

#### 1.2 Approach Overview

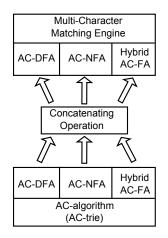

This thesis presents approaches based on the AC-algorithm to enhance the performance of exact string matching. The overview of this research can be illustrated as Fig. 1.1. A prefix-tree created according to the AC-algorithm is known as an AC-trie, which consists of goto functions and failure functions. All the occurrences of keywords can be located in a one pass search through the goto functions and the failure functions in the matching process. However, the failure functions in an AC-trie causing multiple state transitions in a matching cycle make it inconvenient to implement the AC-algorithm in a deterministic hardware circuit. A general approach is converting an AC-trie to a Deterministic Finite Automaton (DFA), called AC-DFA, or a Nondeterministic Finite Automaton (NFA), called AC-NFA, to eliminate the failure functions and then implementing the derived AC-DFA or AC-NFA in a hardware circuit. The advantage of the AC-DFA approach is that it can be implemented as a general architecture, while its disadvantage is space expensive. In contrast, the advantage of the AC-NFA approach is space efficient, while its disadvantage is that the hardware implementation is dependent on the keyword set. This thesis proposes a hybrid finite automaton, called hybrid AC-FA, that combine the AC-DFA and AC-NFA to combine both the advantages of DFA and NFA.

However, the string matching engine inspects a text character by character with a performance limited by the achievable maximum operating clock; therefore it needs to inspect multiple characters in parallel to further increase the performance. While multiple characters are being inspected in parallel, besides the complexity is increased, a common problem has to be considered is the alignment problem of starting and ending characters. The alignment problem includes two cases: a pattern does not begin at the first character of the inspecting characters, and a pattern does not end at the last character of the inspecting characters. Consider the inspecting characters 'they' as an example, in which the pattern 'he' begins at the second character and ends at the third character. In this scenario, neither the beginning of the pattern aligns with the first character of the inspecting characters nor the ending of the pattern aligns with the last character of the inspecting characters.

This thesis develops an intuitive algorithm to derive multi-character transitions from an AC-DFA, an AC-NFA, or a hybrid AC-FA, where each transition can match multiple characters at a time. This derivation algorithm also includes using assistant transitions and a pseudo state to resolve the alignment problem. This thesis also proposes architectures to implement the derived multi-character AC-DFA, AC-NFA, and hybrid FA. Moreover, a multi-stage architecture with configurable scheme is also proposed to provide flexibility in the number of characters inspected in parallel and in the changing of keyword sets. Evaluations are performed for the proposed architectures, respectively, to show their effectiveness. The main contributions of this work can be summarized as follows.

- A systematic approach that performs concatenation operations iteratively is devised to derive multi-character transitions from the transitions of the ACalgorithm, in which assistant transitions are introduced to solve the alignment problem.

- Several architectures are proposed to implement the derived multi-character

transitions. The features of the AC-algorithm that provide a matching output in every matching cycle are preserved by introducing priority multiplexers to determine the corresponding matching output for all inspected characters in every matching cycle in the proposed multi-character string matching engines.

- The space required for implementing a derived k-character AC-NFA is O(k). The proposed multi-character hybrid AC-FA approach has the feature that the number of transitions grow nearly linearly with respect to the number of characters under inspection in parallel.

- A configurable architecture is devised from the proposed multi-stage architecture that can process different keyword sets by simply updating the configuration data.

#### **1.3** Thesis Organization

The rest of this thesis is organized as follows: Chapter 2 introduces related stringmatching literature. Chapter 3 first describes the AC-algorithm briefly and then presents approaches for implementing the AC-algorithm. Next, Chapter 4 proposes the derivation algorithm for multi-character FA and Chapter 5 describes the implementations of the derived multi-character FAs. Chapter 6 proposes configurable architectures for multi-character string matching. Chapter 7 compares the proposed approaches with related works. Conclusions are finally drawn in Chapter 8.

# Chapter 2 Related Work

Among the string-matching algorithms, the algorithms of Aho-Corasick [1] and Bloom [8] are used in many applications for filtering out specific data efficiently. The Bloom algorithm accelerates the string matching by allowing for a small number of falsely matched patterns; however, a further exact verification is required for confirming whether the result is false positive. The Bloom algorithm can be implemented in hardware with high space efficiency [9]. In contrast, the AC-algorithm is an exact string-matching algorithm that can locate multiple patterns in a text with linear time complexity. Since the proposed approaches in this thesis are mainly based on the AC-algorithm, the following discussion of related work focuses on the AC-algorithm.

#### 2.1 Optimization in Hardware

Due to the progress and flexibility of the programmable devices such as FPGA, developers can design and evaluate variant architectures according to the features of the AC-algorithm. Nevertheless, the resources of programmable devices are limited, with some works attempting to increase the hardware efficiency. To improve the memory efficiency, Tuck et al. [2] developed a bitmap-compression and path-compression approach for the AC-algorithm, capable of reducing the required memory and improving the performance on hardware implementation. Zha and Sahni [3] improved the bitmap-compression and path-compression approach by requiring considerably less memory. Alternatively, Alicherry et al. [4] implemented the AC-algorithm by integrating a Ternary Content Addressable Memory (TCAM) and a Static Random-Access Memory (SRAM) that utilizes ternary matching of TCAM to achieve the matching of characters expressed in negation expressions,

subsequently reducing the space required for storing the state transitions. Lin and Liu [10] and Pao et al. [11] applied pipeline architectures to implement the character trie that only contains go of functions of the AC-trie to reduce the space introduced by the failure functions. Hua et al. [12] developed another approach based on a block-oriented scheme instead of the usual byte-oriented processing of patterns to minimize the memory usage. Dimopoulos et al. [13] developed a Split-AC algorithm that partitions a whole AC-trie into multiple smaller tries to increase memory efficiency.

Several researches developed hybrid string-matching approaches combining DFA and NFA to obtain both the advantages of DFA and NFA while avoid their disadvantages. The previous hybrid approaches include exact and regular-expression string matching approaches. For example, Yang et al. [14] proposed the head-body finite automaton (HBFA) that partitions an AC-trie to a head DFA (H-DFA) and a body NFA (B-NFA) to improve the performance of soft implementation of the ACalgorithm. Becchi et al. [15] proposed a hybrid-FA solution for regular-expression string matching to bring together the strengths of both DFA and NFA, i.e. space efficiency and a deterministic hardware-implementation. In the hybrid-FA of Becchi et al., the nodes causing state explosion retain an NFA encoding, while the rest are transformed into DFA nodes.

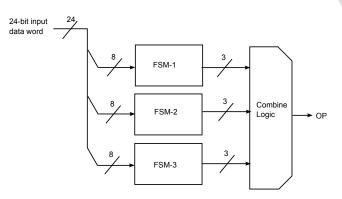

#### 2.2 Multi-Character Hardware Approaches

Because of the flexibility of programmable devices, some works have developed string-matching architectures that can inspect multiple characters in parallel to multiply the throughput of string matching. However, developing an approach capable of inspecting multiple characters in parallel must consider both the complexity and the alignment problem incurred in k-character matching processes. As an extension of the AC-algorithm, Sugawara et al. [16] proposed a string-matching method called Suffix-Based Traversing (SBT) to process multiple input characters in parallel and reduce the lookup table size. Alicherry et al. [4] proposed a k-compressed AC-DFA to achieve a parallel k-character matching engine. A k-compressed AC-DFA consists only of the states whose depth is a multiple of k in the original AC-trie and the leaf states of the original AC-trie, where the alignment problem is solved by using additional shallow states. Other works used multiple FSMs to achieve parallelism and solve the alignment problem, where each FSM is responsible for processing a pattern beginning at a different position, respectively [5–7]. However, those approaches require specific logics to combine thematching results from the FSMs. The approaches of Yamagaki et al. [17] and Katashita et al. [18] solve the alignment problem by using additional states and transitions.

#### 2.3 Software Approaches

Recently, many software implementations of the AC-algorithm utilize the power of the multicore in CPU or GPU to accelerate string matching. For example, Scarpazza et al. [19] proposed an optimized algorithm for the IBM Cell/B.E processor, which is a heterogeneous multicore processor comprised of a 64-bit processor core and eight synergistic processor cores, to achieve high-performance exact string matching. In that algorithm, keywords are split to fit in the local memories of the processing cores to reach extremely high throughput for each processor.

However, Salmela et al. [20] developed a software approach capable of processing multiple characters in parallel. That approach uses short substrings of length q, referred to as q-grams, which process q characters as a single character, and bit parallelism to increase filtering efficiency. Nevertheless, their approach is designed to match a set of keywords with the same length. Because of advanced semiconductor technologies, multiple processing cores can be packaged in a single CPU or GPU chip. Recently, many software implementations of the AC-algorithm use the power of the multicore in CPU or GPU to accelerate string matching. For example, Scarpazza et al. proposed an optimized algorithm for the IBM Cell/B.E processor, which is a heterogeneous multicore processor comprised of a 64-bit processor core and eight synergistic processor cores, to achieve high-performance exact string matching [19, 21]. In that algorithm, keywords are split to fit in the local memories of the processing cores to reach extremely high throughput for each processor. Yang et al. [14] and Yang and Prasanna [22] derived an approach using a headbody finite automaton (HBFA) to improve the match ratio on multicore processors and implements the HBFA in multiple threads on the multicore system to achieve high throughput. Villa et al. presented a software approach for the AC-algorithm on the Cray XMT multithreaded shared memory machine, capable of achieving a throughput of 28Gbps [23]. The approach of Tumeo et al. assigns different packets to different CUDA/GPU threads, as proposed by NVIDIA, to increase the efficiency of pattern matching [24]. Tumeo et al. later evaluated several software implementations of the AC-algorithm on shared and distributed memory architectures [25]. Herath et al. applied multicore CPUs to accelerate the string matching used in biology applications [26].

Software and hardware approaches significantly differ in achieving the parallelism. Software approaches achieve parallelism by splitting an input text into multiple chunks and then processing the chunks by multiple threads, respectively, where each thread still inspects the input text character by character. Conversely, hardware approaches achieve parallelism by inspecting multiple characters in parallel. Both approaches can multiply the throughput of string matching. However, software and hardware approaches also differ in that the former can have a larger dictionary size.

臺

# Chapter 3

# Aho-Corasick Algorithm and Implementations

The algorithm proposed by Aho and Corasick (AC-algorithm) is an exact stringmatching algorithm that can locate the occurances of multiple patterns in a text with a linear time complexity. Therefore, the AC-algorithm is used in many applications to fast filter out the specific data. This chapter first explains the AC-algorithm briefly and then presents various implementations of the AC-algorithm.

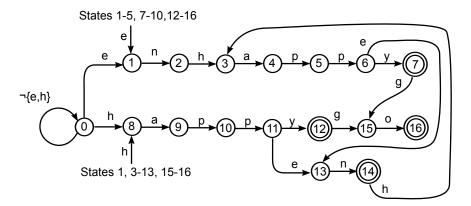

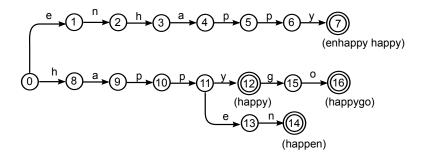

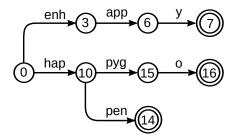

Figure 3.1: AC-trie

#### 3.1 AC-trie

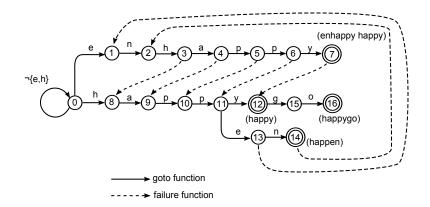

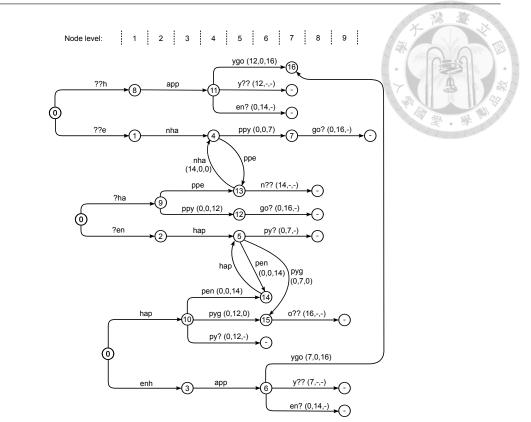

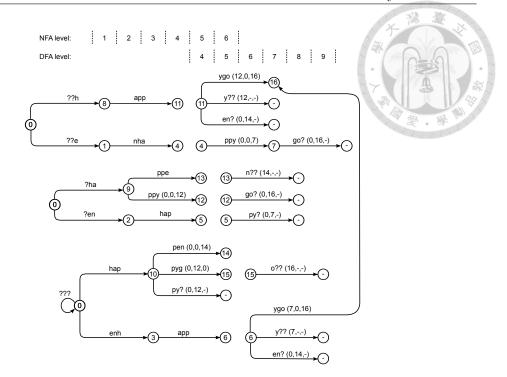

A prefix-tree built according to the AC-algorithm is known as an AC-trie that consists of goto and failure functions. Fig. 3.1 illustrates an AC-trie built on the keyword set {enhappy, happy, happen, happygo}. In this figure, the circled numbers denote states, which are called nodes alternatively. In addition, the double circled numbers denote output states, or output nodes, that have non-empty matching outputs. The physical and dashed lines denote goto and failure functions respectively. State 0 is also known as the initial state or the root node. Every non-initial state has a failure function, while the failure functions linked to the initial state are not shown for clarity. In an AC-trie, the depth of a node is also called the level of it. A property of the failure function is that a state only links to another state in the smaller level through the failure function. For example, the failure function of state 7 in level 7 links to state 12 in level 5.

A matching cycle in the AC-algorithm is defined as a period that begins with inputting a character and ends with outputting a matching output. There is only one active state in an AC-trie at any time. In a matching cycle, the goto functions of the active state are checked first. If none of the goto functions is matched, then the state transits to a new state through the failure function and the goto functions of the new activated state are checked continuously. Since all non-initial states are linked to the initial state eventually through the failure functions and the initial state has the goto functions for all characters, it ensures that a matched goto function can be found in every matching cycle. In the matching process, an input string is processed character by character and we call the character under processing as an inspecting character. A matching cycle leads to a matching output, which is represented by a state number. If a keyword is matched, the matching output is a non-zero state number; otherwise the matching output is state 0.

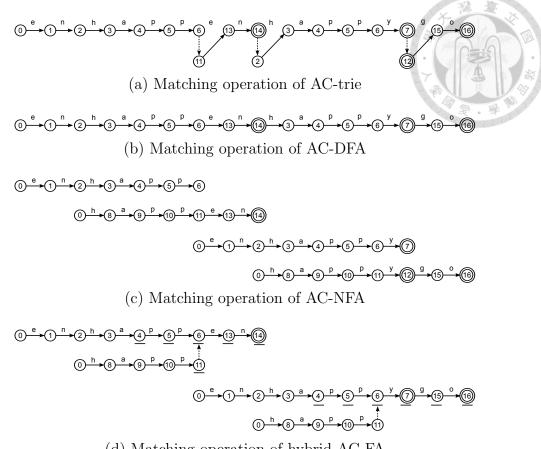

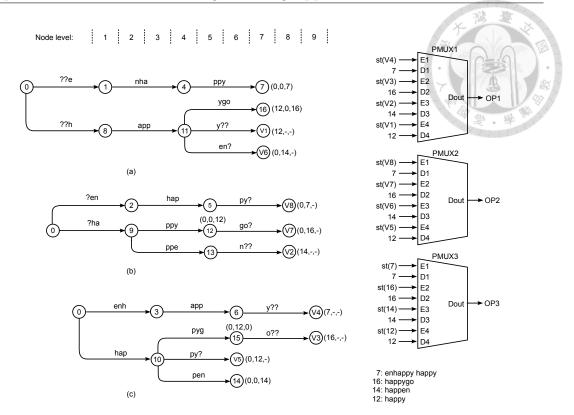

The AC-algorithm can be implemented in various approaches, which are described later, and the matching operations of these approaches are illustrated together in Fig. 3.2 for comparison. The inspecting texts of these matching examples are the same which is 'enhappenhappygo'. The matching operation of the AC-trie is illustrated in Fig. 3.2(a). In response to the characters 'enhapp', the transition traverses through the states 0, 1, 2, 3, 4, and 5 sequentially. In response to the next character 'e', none of the goto functions of state 5 matches with this character, so that the state transits to 11 following the failure function of state 5 and the operation continues to match the goto functions of state 11. In response to the following character 'n', the state transits to 14 which is a output state and we have a matching output 'happen'. State 14 is a terminal state, therefore according to its failure function, the state transits to 2 when the next character is input and then the matching process goes on from the state 2. Similarly, in response the remaining characters, the transition traverses through the states 3, 4, 5, 6, 7, 12, 15, and 16 sequentially;

(d) Matching operation of hybrid AC-FA

Figure 3.2: Examples of matching operations

where the transition from 7 to 12 is a transition according to the failure function of state 7. In the remaining matching operation, we have matching outputs on states 7 and 16 which are 'enhappy happy' and 'happygo' respectively.

With the failure functions, all matched keywords can be found in a one-pass search by using an AC-trie. Nevertheless, when an AC-trie is implemented in hardware the complexity will be increased due to the property that often more than one state transition are needed to find a matched goto function through the failure functions. An AC-trie can be implemented as a DFA (AC-DFA) or an NFA (AC-NFA). The DFA and NFA approaches have significant different features. This thesis proposes a hybrid finite automaton approach that combines the DFA and NFA approach to implement the AC-algorithm (hybrid AC-FA). The proposed hybrid AC-FA approach has both the advantages of DFA and NFA approaches. The AC-DFA, AC-NFA, and hybrid AC-FA approaches are described in the following sections.

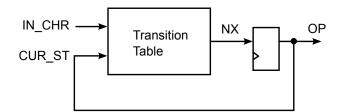

#### 3.2 AC-DFA

Fig. 3.3 illustrates the DFA converted from the original AC-trie. The transitions pointed to the states 1 and 8 that are derived from the failure functions are denoted together, respectively, for clarity in this figure. Fig. 3.2(b) illustrates the matching operations of the AC-DFA which is straightforward and the explanation of the matching operations is omitted. Fig. 3.4 illustrates the block diagram for implementing the AC-DFA. The transition table is implemented as a lookup table generally. The next state NX is determined by the input character IN\_CHAR, current state CUR\_ST, and the transition table. The next state NX is looped back as the current state CUR\_ST to be used in the next matching cycle. However, the transition table of AC-DFA typically is a sparse table, and thus it is inefficient in space utilization.

Figure 3.3: AC-DFA

Figure 3.4: Basic AC-DFA implementation block diagram

Alicherry et al. has analyzed the AC-DFA constructed for the signatures obtained from 100 viruses in the Internet [4]. Table 3.1 summarizes the number of states at a certain depth and the number of transitions to the states at that depth in the AC-DFA. The analysis result indicates that the number of transitions to the states at depth 1 is as high as 96.4% of the total transitions. Notably, most of the transitions to smaller depths are mainly the next transitions derived from failure functions.

| 1able 5.1.  | Diates al | iu transi | tions m | an AO- | DTA(A) | nenerry  | et al.) |  |

|-------------|-----------|-----------|---------|--------|--------|----------|---------|--|

| Depth (d)   | 1         | 2 3       |         | 4      | 5      | $\geq 6$ | Total   |  |

| States      | 56        | 89        | 100     | 102    | 102    | 7248     | 7698    |  |

| Transitions | 421,243   | 7,576     | 551     | 165    | 121    | 7382     | 437,038 |  |

Table 3.1: States and transitions in an AC-DFA (Alicherry et al.)

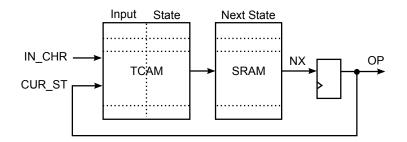

Accordingly, Alicherry et al. proposed an alternative AC-DFA implementation that uses a TCAM and a SRAM to implement the transition table, in which a wildcard character is used to resolve the problem of transition explosion. Each TCAM entry maps a transition in the AC-DFA to an index; and the TCAM index is used to compute the address of the corresponding memory block in the SRAM. In a matching cycle, the TCAM-based approach first obtains a matching index from the TCAM according to the inspecting character and current state, and then obtains a next state from the SRAM according to this matching index.

Figure 3.5: Implementation of AC-DFA with TCAM and SRAM

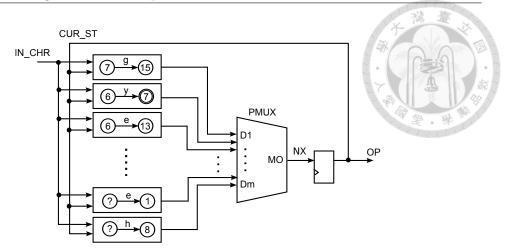

Since a TCAM only outputs indexes according to the matching results, an additional SRAM is required for obtaining next states from the resulting indexes in the TCAM-based approach. This thesis develops a hardware architecture, shown in Fig. 3.6, that can achieve the feature as integrating the TCAM and SRAM to implement the AC-DFA. This proposed architecture consists of multiple rule units and these rule units can be configured according to the keyword set to be processed, in which each rule unit processes a transition respectively.

Two transitions beginning from the initial state are  $\delta_1(0,e)=1$  and  $\delta_1(0,h)=8$ . In order to be distinguishable with a multi-character transition which will be described

Figure 3.6: Implementation of AC-DFA with priority multiplexer

later, the notation  $\delta_1$  with a subscript 1 means a 1-character transition. In this figure, the initial state is replaced by a wildcard character '?', and thus the two transitions of the initial state are replaced by  $\delta_1(?,e)=1$  and  $\delta_1(?,h)=8$ . In this way, the transitions linked to states 1 and 8 derived from the failure functions can be omitted, such as  $\delta_1(1,e)=1$ ,  $\delta_1(1,h)=8$ , and so on. Because of the wildcard character, multiple rules may be activated simultaneously. For example, when the current state is 6 and the input character is 'e', the transitions  $\delta_1(6,e)=13$  and  $\delta_1(?,e)=1$  are activated simultaneously.

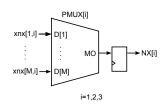

In a typical TCAM, the conflict situation caused by multiple potential results is resolved by using a priority encoder to determine a final matching index. In this work, the conflict situation arising from multiple activated rules is resolved by using a priority multiplexer to determine a final matching result. In Fig. 3.6, the priority multiplexer PMUX has m inputs D1 through Dm. If the inputs Di and Dj are both valid and i < j, then the priority of Di is higher than that of Dj; and thus, the priority multiplexer selects the input Di to be output through MO. For PMUX, input D1 has the highest priority, and input Dm has the lowest priority. When none of the inputs is valid, PMUX outputs a default value, such as 0; this ensures that the next state should return to the initial state when none of rules is matched. In Fig. 3.6, the upper rule unit has a higher priority. As a result, when the conflict situation that  $\delta_1(6,e)=13$  and  $\delta_1(?,e)=1$  are activated simultaneously is happen, the priority multiplexer PMUX determines the next state is 13.

#### 3.3 AC-NFA

If the failure links are removed and simultaneously activation of multiple states is allowed, an AC-trie becomes an NFA. Fig. 3.7 illustrates the AC-NFA obtained from the original AC-trie by removing the failure links. After converting an AC-trie to an AC-NFA, all matched transitions are done currently. The parallelism implicit in hardware makes it more feasible to keep track of concurrent state transitions. The transitions of an AC-NFA are only the goto functions of the original AC-trie. In the proposed approach, the complexity in terms of number of transitions remains the same, whereas the failure functions are transformed into the concurrent transitions that fit the hardware intrinsically.

Fig. 3.2(c) illustrates the matching example of the AC-NFA with the same input 'enhappenhappygo'. In response to the characters 'enhapp', a transition sequence begins from state 0 and ends at state 6, which does not match any keyword. In response the characters beginning from the third character, another transition sequence traverses states 0, 8, 9, 10, 11, 13, and 14, which matches the keyword 'happen'. The characters beginning from the seventh character initialize a transition sequence traverses states 0 to 7 and matches the keyword 'enhappy'. Similarly, the characters beginning from the ninth character initialize a transition sequence traverses states 0, 8, 9, 10, 11, 12, 15, and 16, which matches the keyword 'happygo'. As can be seen by comparing Fig. 3.2(a) and (c), in every matching cycle, when a state is activated in the AC-trie, all the states linked to through the failure functions from the active state are activated simultaneously in the AC-NFA. For example, when state 3 is activated, state 8, which is pointed by the failure function of state 3, is activated simultaneously. Therefore the failure functions are not necessary if multiple states are allowed to be activated simultaneously.

Figure 3.7: AC-NFA

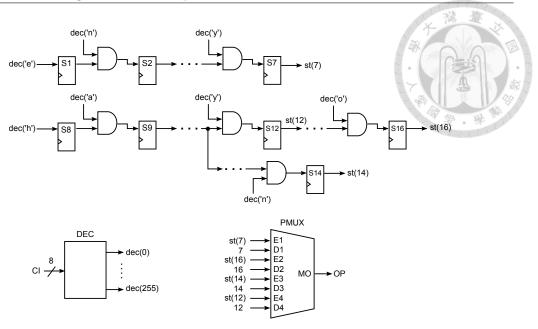

Fig. 3.8 illustrates the implementation of the AC-NFA, where some similar por-

Figure 3.8: Implementation of AC-NFA

tions are omitted in the circuit for clarity. The AC-algorithm provides only one matching output in every matching cycle, while multiple states may be activated simultaneously in an AC-NFA. Therefore, an output circuit is required to determine a matching output in the implementation of an AC-NFA. In this implementation, the final matching output OP is determined by using a priority multiplexer PMUX. Notation st(i) denotes the status of node i, where i represents the state number in the AC-NFA. For example, when the text under inspection is 'enhappy', states 7 and 12 are activated simultaneously. State 7 represents the string 'enhappy' and state 12 represents the string 'happy'; the former includes the later. Therefore, state 7 has a higher priority and is determined as the matching output.

In an AC-trie, each state represents a unique string. If a failure function links state  $S_1$  to state  $S_2$ , then the string represented by  $S_2$  is the postfix of the string represented by  $S_1$ . For example, state 12 represents the string 'happy', and state 7 represents the string 'enhappy'; in addition, the failure function of state 7 points to state 12, and the string 'happy' is the postfix of the string 'enhappy'. In an ACtrie, the matching output is simply the active state since only one state is activated at any time. Although activation of multiple states is allowed in an AC-NFA, the proper matching output from the multiple active states must be determined. For example, like the earlier case, states 7 and 12 are activated simultaneously. Since failure functions link higher states to lower-level states, the highest-level activated state in an AC-NFA should determine the final matching output. In the matching operation of the AC-algorithm, only a matching output is generated after every matching cycle. In the proposed NFA approach, the priority multiplexer PMUX shown in the lower right portion of Fig. 3.8 is used as an output selection circuit to determine the final matching outputs from multiple activated output nodes. Notably, the priority multiplexer PMUX in this figure differs from that in Fig. 3.6 in that each input group consists a control signal and a data signal; nevertheless, they are the same essentially and the difference in diagrams is convenient for explanation only.

This AC-NFA has four output nodes so that the priority multiplexer PMUX has four input groups (E1, D1) through (E4, D4), where inputs E1 through E4 are control signals and inputs D1 through D4 are data signals. The control signals E1 through E4 indicate whether the data inputs D1 through D4 are valid or not, respectively. If the inputs Ei and Ej are both true and i < j, then the priority of input Ei is higher than that of input Ej; in addition, the priority multiplexer selects the input Di to be output through MO. When none of the inputs is valid, the output MO is not valid either. However, the output MO of PMUX can output 0 if no matched output is available. Notation st(s) refers to the status of node s, which is true when node s is activated. Since higher-level nodes have a higher priority, signal st(9) has the highest priority and is connected to E1. The data sent to inputs D1 through D4 are the corresponding state numbers. Consider the previous example. Following acceptance of the text 'enhappy', both nodes 7 and 12 are activated and both st(7) and st(12) become true. Moreover, since the priority of st(7) is higher than that of st(12), PMUX selects the data 7 input from D1 as the matching output.

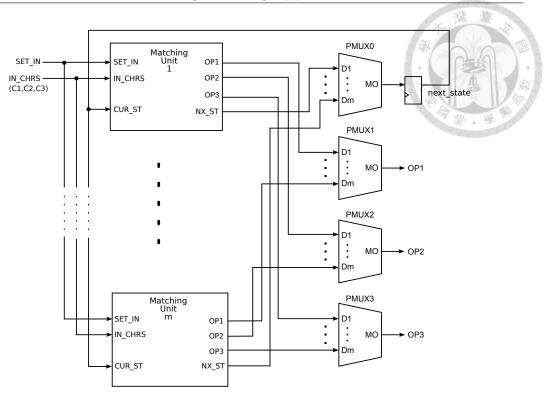

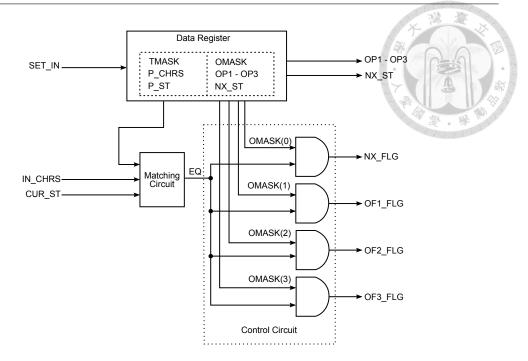

Figure 3.9: Multi-stage architecture of AC-NFA

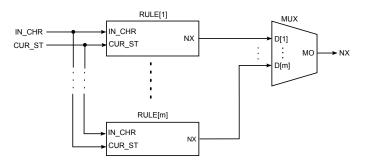

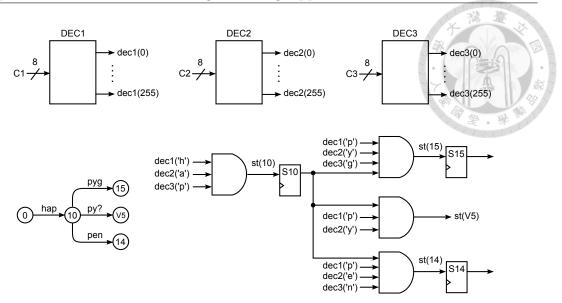

According to the observation, among the states with the same depth in an NFA derived from a given AC-trie, the number of active states  $n_a$  is no more than one, i.e.  $n_a \leq 1$ . Therefore, an AC-NFA can be implemented in a multi-stage architecture

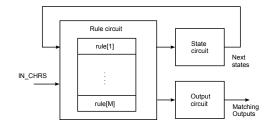

alternatively. In an AC-trie, the states with the same depth are known as in the same level. The states with the same depth represent different strings with the same length, and thus at most one state in a level can be activated in one time. Consequently, only one register is required to save the active state for each level in an AC-NFA. Fig. 3.9 illustrates a multi-stage architecture for implementing the AC-NFA. The multiple stages are arranged in a chain, in which each stage includes the transitions of the corresponding level. Fig. 3.10 illustrate the block diagram of a stage unit. A stage unit includes multiple rule units, in which each rule unit is responsible for matching one transition. Therefore, the number of rule units in a stage must be equal or greater than the number of transitions. A rule unit contains the information of its corresponding transition and matches the information with the input current state CUR\_ST and character IN\_CHAR in the matching operation. A rule unit is triggered when its pattern is matched with the inputs and then outputs the next state NX according to the transition.

Figure 3.10: Block diagram of a stage unit

#### 3.4 Hybrid AC-FA

The DFA approach has an attractive property that processing an input string involves one DFA state traversal per character, which implies a deterministic number of memory accesses. Namely, the memory bandwidth requirement for implementing a DFA is predictable and it is possible to implement a DFA in a lookup table approach. However, the number of transitions grows explosively when an AC-trie is converted to a DFA. In contrast, an NFA approach is efficient in the hardware size utilization. However, an NFA is difficult to be implemented in a pre-designed architecture, like a lookup table approach, since each input character can trigger multiple state transitions and multiple states can be active simultaneously. Generally, an NFA is suitable to be implemented in a programmable device.

Figure 3.11: Hybrid AC-FA

According to the analysis result in Table 3.1, the transitions increase dramatically in the lower levels due to the failure functions when an AC-trie is converted to a DFA. Accordingly, this work proposes a hybrid finite automaton to implement an AC-trie (Hybrid AC-FA), which has both the advantages of DFA and NFA. Fig. 3.11 shows a hybrid AC-FA that is obtained by dividing the AC-trie in Fig. 3.1 to NFA and DFA portions. In the NFA-portion, all failure functions are removed and only goto functions are remained; while in the DFA-portion, the failure functions are substituted by expanding goto functions. For the convenience of discussion, let the NFA levels are defined as the number of levels in NFA portion, in which level 0 is excluded. For example, there are three NFA levels in the hybrid AC-FA illustrated in Fig. 3.11. Notably, states 4 and 11 are in the DFA portion.

Comparing with the AC-DFA illustrated in Fig. 3.3, the transitions linked backwardly to states 1, 3, and 8 are eliminated in the hybrid AC-FA. In which, most of the removed transitions are linked backwardly to the states in levels 0 and 1, i.e. states 0, 1 and 8. Correspondingly, the hybrid AC-FA only has two more transitions, linked to states 13 and 15, respectively, than the AC-NFA illustrated in Fig. 3.7.

Like the multi-stage architecture for implementing the AC-NFA, only one register is required for saving the state for each level in the NFA portion. Furthermore, because at most one state is allowed to be activated in the DFA portion, only one register is required for keeping the state in the DFA portion. As a result, the stages and the registers required for keeping the states in the implementation of hybrid AC-FA can be predetermined, and this enables to design a general string-matching architecture based on the AC-algorithm. Because the transitions increase little as comparing with the AC-NFA approach, the hybrid AC-FA approach is efficient in space utilization.

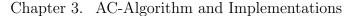

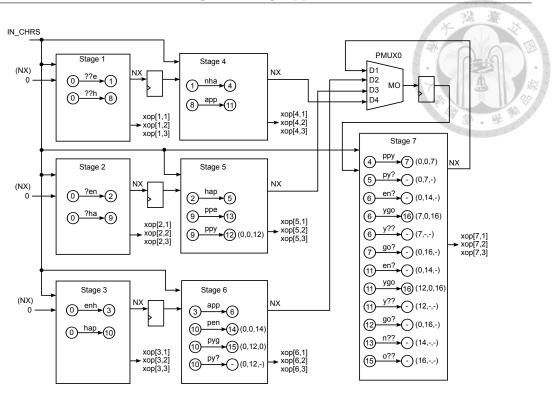

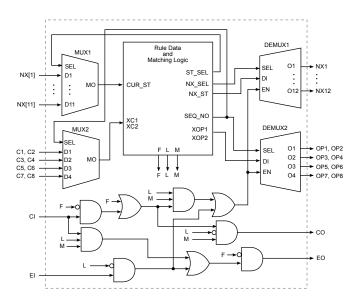

Fig. 3.12 shows the multi-stage architecture for implementing the hybrid AC-FA.

Figure 3.12: Implementation of hybrid AC-FA

Stages 1 to 4, which belong to the NFA portion, contain the transitions of levels 0 to 3 respectively. Stage 5, which is the terminal stage and belongs to the DFA portion, contains all of the transitions. Because only one state can be activated at most in each stage, priority multiplexer PMUX0 determines the next state for the terminal stage from the next states (NX) output from stage 4 and stage 5. The detail of each stage is same as the block diagram shown in Fig. 3.10. The next state (NX) generated by the *i*-th stage also represents the matching result xop*i* of that stage. PMUX1 determines the final matching output from the matching results xop1 to xop5.

Figure 3.13: Priority multiplexer implemented by chained multiplexers

# 3.5 Priority Multiplexer

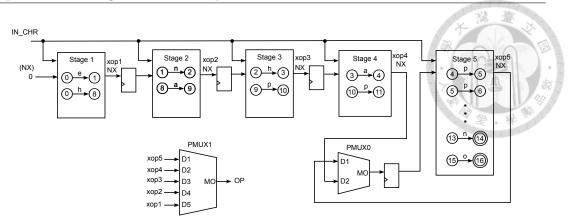

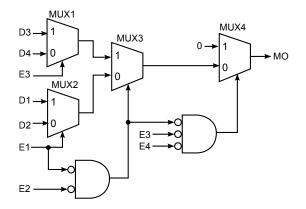

The priority multiplexer plays an important role in the proposed architectures and its implementation is described briefly here. The implementation of priority multiplexer mainly refers to the literature of Alera [27]. In a priority multiplexer, the select logic implies a priority, so the options to select the correct item must be checked in order. Fig. 3.13 illustrates a 4-to-1 priority multiplexer implemented by multiple chained multiplexers that evaluates each condition, or select bit, one at a time. However, this structure of chained multiplexers is generally bad for delay, since the critical path through the logic traverses through every multiplexer in the chain. As a result, the delay of the structure of chained multiplexers increases linearly respect with the number of data inputs.

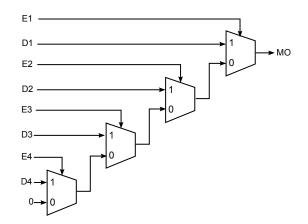

Figure 3.14: Priority multiplexer optimized for delay

Fig. 3.14 illustrates an alternate implementation of priority multiplexers to optimize the delay. This logic structure is just slightly more complicated than the standard priority multiplexer scheme, but significantly improves the delay through the logic. In this structure, if any of the two select lines E1 and E2 are high, then the 2-input AND gate chooses the upper half of the logic, otherwise it chooses the lower side. The enable signals E1 through E4 make the final choice of inputs, if all of the enable signals are low then the output MO is zero. The signal E1 has the highest priority in the figure. The levels of the chained multiplexers is  $log_2m$  for mdata inputs in the optimized structure. Therefore the delay of the optimized priority multiplexer reduces from O(m) to  $O(log_2m)$  for m data inputs.

# Chapter 4

# **Multi-Character State Transitions**

The throughput of a string-matching engine can be multiplied in the same operating speed when multiple characters can be processed in parallel in every matching cycle. Therefore, a 1-character finite automaton (FA), which processes only one character at a time, has to be derived to a multi-character FA for processing multiple characters in parallel. Furthermore, the alignment problem also has to be considered in the derivation of multi-character FA.

This chapter proposes an derivation algorithm to extend the AC-algorithm to be able to process multiple characters in parallel. This proposed algorithm can derive a 1-character FA, which could be an AC-DFA, an AC-NFA, or a hybrid AC-FA, to a multi-character FA by using iterative concatenation operations. In addition, assistant transitions and a virtual state are introduced to deal with the alignment problem in the derivation algorithm.

| Input:  | thishers |

|---------|----------|

| Match1: | -his     |

| Match2: | she      |

| Match3: | he       |

| Match4: | hers     |

Figure 4.1: Example of alignment problem

## 4.1 Alignment Problem and Previous Work

The alignment problem must be considered when multiple characters are inspected in parallel in every matching cycle. Fig. 4.1 uses an example to demonstrate the alignment problem. In which, the keyword set to be matched is {he, she, his, hers}. In this matching example, eight characters are inspected in parallel and the input text is 'thishers'. As can be seen, all the four keywords appear in the inspecting text; however, all the occurrences of keywords do not begin at the first character of the inspecting text.

Figure 4.2: Example of 3-compressed FA

An intuitive approach to convert a 1-character FA to a multi-character FA is merging multiple successive 1-character transitions to a multi-character transitions, like the k-compressed FA proposed by Alicherry et al. [4]. An example of 3-compressed FA is shown in Fig. 4.2. However, because some states are lost in a k-compressed FA as comparing with the original AC-trie, special process is required to deal with the alignment problem. In the Alicherry approach, shallow nodes are added to resolve the alignment problem as shown in Fig. 4.3. When a keyword does not appear in the first character of the inspecting character-chunk, an additional transition is needed to ensure the next state to fall into an existing state in the compressed FA. For example, when the input text is 'penhapp', the state first transits from the initial state to the the shallow state 2 according to 'pen' and then to state 3 according to the additional character 'h'. Consequently, two transitions are required when alignment problem occurs. Moreover, multiple transitions may be activated simultaneously because of the same prefix or suffix, such as the keywords 'hers' and 'she'; this further increases the complexity in hardware design.

Figure 4.3: Example of shallow states

Alternatively, Tripp proposed a architecture consisting of multiple identical FSMs, as shown in Fig.4.4, to solve the alignment problem [5]. In which, each FSM is

responsible to deal with a alignment case respectively. However, the multi-FSM architecture requires a combine logic circuit to determine the final matching results from the results of FSMs.

Figure 4.4: Architecture of three FSMs

### 4.2 Derivation of Multi-Character Transitions

This section proposes a derivation algorithm that derives 1-character transitions to multi-character transitions by using iterative concatenation operations. Before describing the concatenation operation, some related definitions are given as follows.

**Definition 1.** A k-character transition  $\delta_k(S_1, T) = S_2$  represents the state transit from the current state  $S_1$  to the next state  $S_2$  on a k-character string T.

For example, a 3-character transition  $\delta_3(10, \text{pyg})=15$  represents that the state transits from 10 to 15 on a 3-character string 'pyg'.

**Definition 2.** A transition  $\delta_k(S_2, T_2) = S_3$  is a successive transition of the transition  $\delta_l(S_1, T_1) = S_e$  if  $S_2 = S_e$ , implying that the starting state of  $\delta_k(S_2, T_2) = S_3$  is simply the end state of  $\delta_k(S_1, T_1) = S_e$ .

Figure 4.5: Concatenation operation

A new multi-character transition can be obtained by concatenating a transition with its successive transition. The concatenation operation is defined as follows and its diagram is shown in Fig.4.5:

**Definition 3.** (Concatenation of two transitions) Given a k-character transition  $\delta_k(S_1, T_1) = S_2$  and an *l*-character successive transition  $\delta_l(S_2, T_2) = S_3$ , where  $S_1$ ,  $S_2$ , and  $S_3$  denote states,  $T_1$  represents a k-character string, and  $T_2$  represents an *l*-character string. Then the concatenation of the two transitions is a (k+l)-character transition  $\delta_{k+l}(S_1, T_1T_2) = S_3$ .

| <u></u> ,, | (7)?-►(-)  | 12?-⊁(-)  |

|------------|------------|-----------|

| ()?-►(-)   | (14)?-►(-) | (16)?→(-) |

Figure 4.6: Assistant transitions

Besides the transitions of the 1-character FA, three types of assistant transitions are defined to facilitate the construction of multi-character transitions capable of solving the alignment problem.

**Definition 4.** (Assistant transitions) The first type of assistant transitions is defined as  $\delta_1(0, ?) = 0$  that denotes a transition from state 0 to state 0 on an arbitrary character. The second type of assistant transitions is defined as  $\delta_1(S_{op}, ?) = -$  that denotes a transition from an output state  $S_{op}$  to a pseudo state on an arbitrary character. The third type of assistants is defined as  $\delta_1(-, ?) = -$  that denotes a transition from a pseudo state to another pseudo state on an arbitrary character.

Fig. 4.6 shows examples of assistant transitions. Assistant transitions are denoted by dashed lines to distinguish them from the 1-character transitions of a original FA. The circled character '-' denotes a pseudo state that is a virtually defined state and nonexistent in an AC-trie. Furthermore, the symbol '?' denotes an arbitrary character. The first type assistant transition, i.e.  $\delta_1(0, ?) = 0$ , deals with the alignment problem in which the beginning of a pattern does not appear in the first character of the inspecting characters. The second type assistant transition, i.e.  $\delta_1(S_{op}, ?) = -$ , preserves the matching output for a situation in which the ending of a pattern does not appear in the final character of the inspecting characters. In Fig.4.6, the transitions beginning from states 7, 12, 14, and 16, respectively, and ending at pseudo states are examples of the second type assistant transitions. The

Figure 4.7: Derivation examples

third type assistant transition, i.e.  $\delta_1(-,?) = -$ , can follow a second type assistant transition to form a multi-character transition.

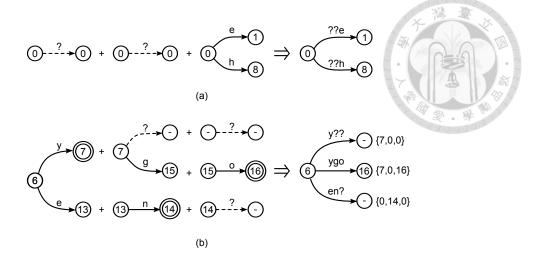

The examples shown in Fig. 4.7 explain how to derive 3-character transitions by repeating concatenation operations. These examples also explain the usages of the assistant transitions in the derivation. In this figure, '+' denotes the concatenation operation.

First, referring to Fig. 4.7(a), concatenating two assistant transitions  $\delta_1(0,?)=0$  obtains a 2-character transition  $\delta_2(0,??)=0$ ; and then concatenating the deriving transition with  $\delta_1(0,e)=1$  and  $\delta_1(0,h)=8$ , respectively, obtains two 3-character transitions  $\delta_3(0,??e)=1$  and  $\delta_3(0,??h)=8$ . Despite obtaining a 3-character transition  $\delta_3(0,??e)=0$ , concatenation of the transition  $\delta_2(0,??)=0$  with another  $\delta_1(0,?)=0$ , it is discarded owing to its uselessness. The transitions  $\delta_3(0,??e)=1$  and  $\delta_3(0,??h)=8$  imply that the state stays at state 0 for the first two any characters and then transits to state 1 or 8 on the third character 'e' or 'h', respectively. By using these derived transitions, the alignment problem arising from the situation that the first character of keywords appears at the third inspecting character is dealt with.

In the example of Fig. 4.7(b), state 6 has two goto functions,  $\delta_1(6,y)=7$  and  $\delta_1(6,e)=13$ . Concatenating  $\delta_1(6,y)=7$  with two assistant transitions  $\delta_1(-,?)=-$  obtains a 3-character transition  $\delta_3(6,y??)=-$ , and concatenating  $\delta_1(6,y)=7$  with other two transitions  $\delta_1(7,g)=15$  and  $\delta_1(15,o)=16$  obtains another 3-character transition  $\delta_3(6,ygo)=16$ . Concatenating  $\delta_1(6,e)=13$  with  $\delta_1(13,n)=14$  and  $\delta_1(-,?)=-$  obtains a 3-character transition  $\delta_3(6,en?)=-$ . States 7 and 14 are output states, particularly state 14 is a terminal state, each of which is concatenated with assistant transitions

to form a complete 3-character transition to preserve the matching output. Because the trailing two characters of the pattern in transition  $\delta_3(6,y??)=$ - are wildcard characters, the transition is always triggered along with the transition  $\delta_3(6,ygo)=16$ ; this conflict situation is resolved by introducing a priority multiplexer in the proposed hardware implementation. As a result, repeating the described concatenating operation iteratively can derive all k-character transitions from a given AC-trie for any required number k.

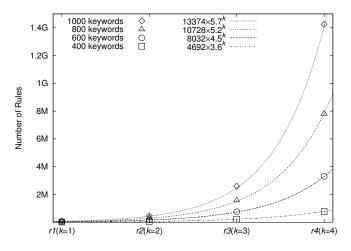

From an AC-NFA, we can infer that when the characters under simultaneous inspection are increased by one more, the number of transitions increased is equal to the number of output states. This observation is owing to that each output state is concatenated with an assistant transition to preserve the matching output for a situation that the following character is not matched. Next, consider the transition  $\delta_1(6,y)=7$  as an example, concatenating it with the successive transition  $\delta_1(7,g)=15$  can obtain  $\delta_2(6,yg)=15$  and concatenating it with the assistant transition  $\delta_1(7,?)=$ - can obtain  $\delta_2(6,y?)=$ -; the latter transition  $\delta_2(6,y?)=$ - is used to preserve the matching output for the situation that only the first character is matched with 'y'.

An NFA consisting of the k-character transitions derived from an AC-NFA is called as a k-character AC-NFA here. The proposed approach can be used to derive a k-character AC-NFA for any number k from an original AC-NFA, which is called 1-character AC-NFA alternatively. The growth of the derived k-character transitions is linear with respect to the number k. As a result, the number of the k-character transitions grows linearly with respect to k, the number of the characters to be inspected in parallel.

The result can be summarized as the following description. For a given AC-NFA with the number of 1-character transitions denoted as  $r_1$  and the number of output states denoted as  $n_{op}$ , then the number of the k-character transitions is obtained as follows:

$$r_k = r_1 + (k - 1) \times n_{op} \tag{4.1}$$

For instance, the AC-NFA example has 16 1-character transitions and four output states, and thus the number of 3-character transitions is  $16 + (3 - 1) \times 4 = 24$ .

```

Algorithm 1: Algorithm for deriving k-character transitions

Input : k: number of characters

NXSET: 1-character transition set

Output: TRSET: k-character transition set

1 begin

TRSET \leftarrow empty

\mathbf{2}

for each state Si do

3

begin

4

NSET \leftarrow all 1-character transitions of Si in NXSET

5

repeat k - 1 do

6

begin

7

TMPSET \leftarrow empty

8

for each transition NXi in NSET do

9

begin

10

NX\_ST \leftarrow \text{next state of } NXi

\mathbf{11}

for each transition NX_j of NX_ST do

\mathbf{12}

begin

13

NEW_TR \leftarrow \text{concatenate } NXi \text{ with } NXj

\mathbf{14}

TMPSET \leftarrow TMPSET \cup NEW\_TR

15

end

16

end

\mathbf{17}

NSET \leftarrow TMPSET

18

end

19

TRSET \leftarrow TRSET \cup NSET

\mathbf{20}

end

21

remove unused transitions from TRSET

22

return TRSET

\mathbf{23}

24 end

```

# 4.3 Derivation Algorithm

Algorithm 1 is a generalized algorithm for deriving multi-character transitions from an AC-trie. In this algorithm, the input parameter k is the number of characters to be inspected in parallel. The input parameter NXSET contains the original 1-character transitions that are derived according to the approach of AC-DFA, AC-NFA, or hybrid AC-FA. The output variable TRSET contains the resulting kcharacter transitions. By using multiple level iterations, this algorithm derives the k-character transitions for every state in the original AC-trie.

In line 2, TRSET is initialized. Statements in the loop between line 3 and line 21 derive all of the k-character transitions of every state Si. In line 5, the 1-character transitions of state Si are duplicated to variable NSET. The loop between line 7

and line 19 is repeated k - 1 times, in which the 1-character transitions of Si are concatenated with their successive 1-character transitions iteratively to derive the k-character transitions of Si. After executing the loop, NSET contains all of the kcharacter transitions of Si. In line 20, NSET is added to TRSET. The algorithm then returns to line 5 to process the next state continuously. The algorithm is terminated when all of the states are processed. Finally, TRSET contains the derived k-character transitions.

Now let's look into the loop between line 7 and line 19. In line 8, TMPSET is initialized. In the loop between line 10 and line 17, every transition NXi in NSET is expanded. In line 11, the next state of NXi is assigned to  $NX\_ST$ . In the loop between line 13 and line 16, NXi is concatenated with every transition NXj respectively beginning from  $NX\_ST$  to obtain new transitions. In line 14, NXi is concatenated with NXj to obtain a new transition  $NEW\_TR$ . In line 15,  $NEW\_TR$  is added to TMPSET. Here the number of the pattern characters of NXi.

Because the intermediate state is concealed after two transitions are concatenated, the matching outputs must be reserved in the concatenation operation in line 14. Moreover, some transitions consists of all assistant transitions that may be obtained in the concatenation process are not useful and are subsequently removed in line 22.

Now let's estimate the time complexity of the derivation algorithm by using k-character AC-NFA. According to equation (4.1), the number of transitions in a *i*-character AC-NFA is  $r_i = r_1 + (i - 1) \times n_{op}$ , implying that  $r_i$  concatenation operations are required to derive the *i*-character transitions from (*i*-1)-character transitions. Therefore, the total required concatenation operations  $T_c$  to derive the 1-character transitions to k-character transitions can be obtained as follows:

$$T_c = \sum_{i=2}^{k} (r_1 + (i-1) \times n_{op}) = (k-1) \times r_1 + \frac{2k}{k-1} \times n_{op}$$

Consequently, the time complexity of Algorithm 1 is  $O(k \times r_1 + n_{op})$ . Since a derived multi-character AC-DFA or hybrid AC-FA generally has more transitions than a multi-character AC-NFA for the same original AC-trie, the time complexity for deriving a multi-character AC-DFA or hybrid AC-FA should be greater than that for deriving a multi-character AC-NFA.

Figure 4.8: Regular-expression example

# 4.4 Comparison of Derivation Approaches

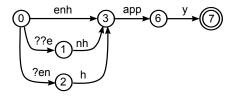

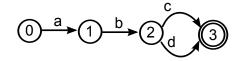

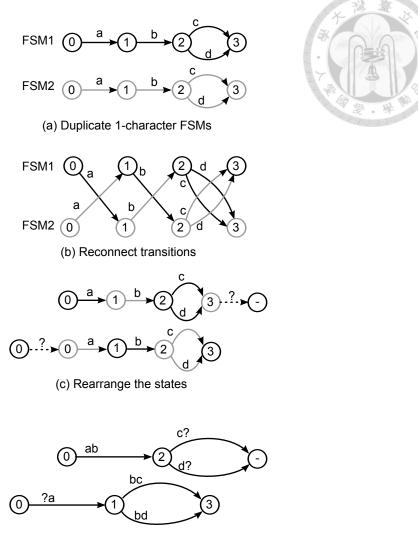

Some previous researches have proposed derivation approaches for deriving multicharacter transitions in different perspectives. This section discusses the approaches of Yamagaki et al. [17] and Yang et al. [28] for comparison. Since both their approaches derive the transitions of a regular expression to multi-character transitions, the regular expression "ab(c|d)" is used as an example for comparison; the FSM built on the regular expression example is shown in Fig. 4.8.

### 4.4.1 The proposed approach

First, the FSM example is derived to a 2-character FSM by using the proposed approach and the derivation process is briefly shown in Fig. 4.9. At the beginning, the 1-character transitions of the FSM are retrieved and the assistant transitions are prepared as shown in Fig. 4.9(a). In which, the transitions denoted as dashed lines are assistant transitions. Every transition is concatenated with its successive transitions to obtain 2-character transitions; the concatenation processes are shown Fig. 4.9(b). Finally, the resulting 2-character FSM is shown in Fig. 4.9(c).

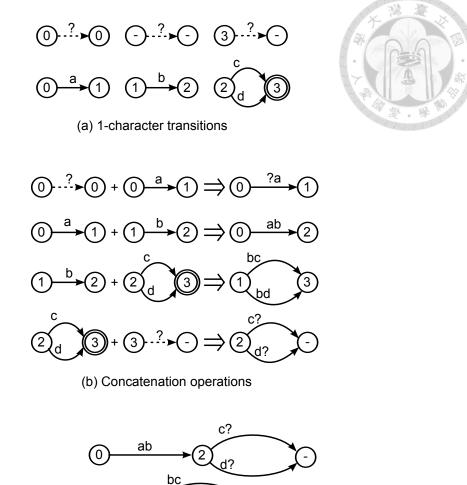

### 4.4.2 Yamagaki et al. approach

Yamagaki et al. derive multi-character transition by iteratively merging two successive transitions and solve the alignment problem by adding additional transitions for the initial state and all final states. Fig. 4.10 describes a derivation example of Yamagaki et al. [17]. In this example, the 1-character NFA of "ab(c|d)" is converted into a 2-character NFA. Fig. 4.10(a) shows the NFA graph obtained from the regularexpression example, where dashed edges show original edges. Before the derivation procedure, a self edge  $\delta_1(0,?)=0$  is added to the initial node and an additional transition  $\delta_1(S_f,?)=$ - is added for each final node  $S_f$ . The derivation procedure merges each of the transitions with its successive transition(s) respectively. These tasks are performed for all of the transitions, and then the 2-character NFA graph as shown in Fig. 4.10(b) is obtained. Fig. 4.10(c) shows the rearranged FSM to show how the

0 ?a 1 bd 3 (c) Resulting 2-character FSM

Figure 4.9: Deriving 2-characters NFA by using the proposed approach

alignment problem is resolved. Where the right final state, i.e. the added virtual node, becomes active when a match occurs at the first position of the two input character positions, and the left state, i.e. state 3, becomes active when a match occurs at the second character position. If matches occur at both positions, both states become active. Similarly, a 4-character NFA can be obtained from the new derived 2-character NFA by the merging operations. Consequently, a  $2^k$ -character NFA can be obtained by k iterations of the described derivation procedure.

(c) Rearrange the states

Figure 4.10: Deriving 2-character NFA by using Yamagaki et al. approach

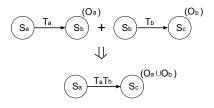

### 4.4.3 Yang et al. approach

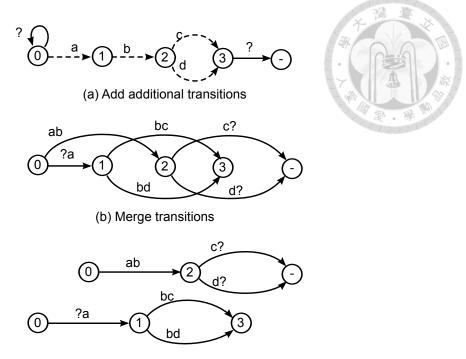

Yang et al. proposed a circuit-level spatial approach to construct a multi-character regular-expression matching engine [28]. Their approach accepts an *m*-character matching-engine circuit  $C_m$  and a *p*-character matching-engine circuit  $C_p$  for the same regular expression, and then merges the two input circuits by reconnecting the transitions to obtain an (m + p)-character matching-engine circuit  $C_{m+p}$  for the same regular expression. In the merging procedure, the states of one of the input circuits are converted to dummy nodes, and then the destination of each of the links is reconnected to the same destination node in the other circuit. Notably, the two input-circuits and the output circuit have the same states. As a result, merging two identical 1-character FSMs obtains a 2-character FSM; and merging the resulting 2character FSM and the original 1-character FSM further obtains a 3-character FSM. Repeating the procedures can obtain an FSM for processing a required number of characters in parallel.

An example of the merging procedure proposed by Yang et al. is shown in Fig. 4.11. In (a), FSM1 and FSM2 are two identical original FSMs. The nodes and transitions of FSM2 are denoted as grey color for clarity. In addition, the states in FSM2 are converted to dummy nodes. Fig. 4.11(b) illustrates the FSM after

(d) Resulting 2-character FSM

Figure 4.11: Deriving 2-character NFA by using Yang et al. approach

reconnecting the destination nodes. For example, the destination node of  $\delta(0, a) = 1$ in FSM1 is reconnected to state 1 in FSM2; and, on the other hand, the destination node of  $\delta(0, a) = 1$  in FSM2 is reconnected to state 1 in FSM1. The resulting FSMs after rearranged are shown in Fig. 4.11(c), where additional transitions are added for obtaining complete 2-character transitions. Finally, Fig. 4.11(d) shows the FSMs after removing the dummy nodes.

### 4.4.4 Summary of comparison

As can be seen in Fig. 4.10, 4.11, and 4.9, the resulting 2-character FSMs are all the same. While the derivation approach of Yamagaki et al. achieving by merging

operations does have the limitation that the number of characters to be inspected in parallel is restricted to  $2^k$ . In addition, the wildcard character is used to deal with the alignment problem in these approaches. Although the paper of Yang et al. does not mention how to resolve the alignment problem, the wildcard character is used implicitly in resolving the alignment problem in the circuit derived by using their approach.

Furthermore, the obtained 2-character FSM has the same states as the original FSM has, excepting the pseudo states added for dealing with the alignment problem. Moreover, the number of transitions increases linearly with respect to the number of transitions ended with final states, because of the assistant transitions added for preserving the matching information.

# Chapter 5

# Multi-Character String-Matching Approaches

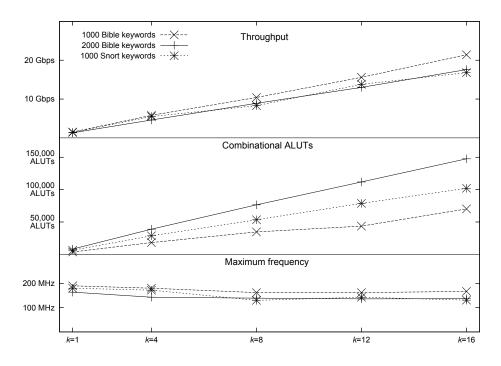

This chapter proposes various architectures for implementing the multi-character FAs, including AC-DFA, AC-NFA, and hybrid AC-FA, derived by the algorithm described in previous chapter. In addition, the proposed approaches are implemented in FPGA devices to evaluate the utilization of hardware resource and estimate achievable throughput.

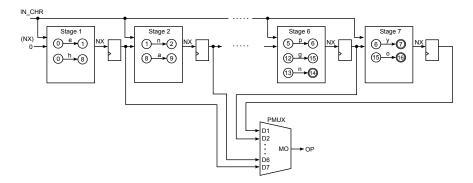

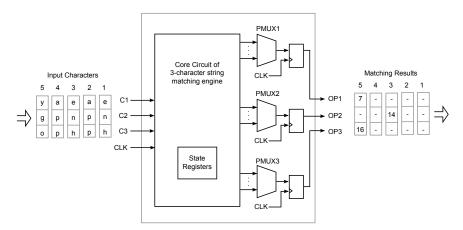

Figure 5.1: Basic block diagram of a 3-character string matching engine

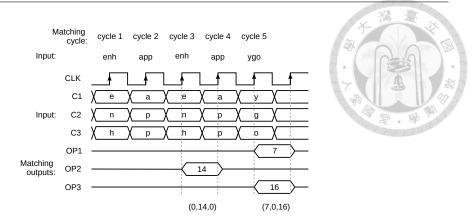

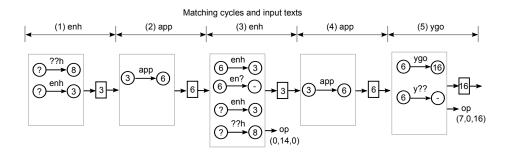

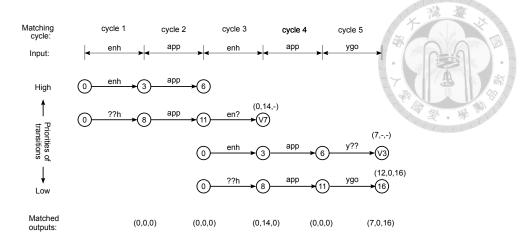

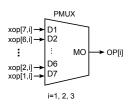

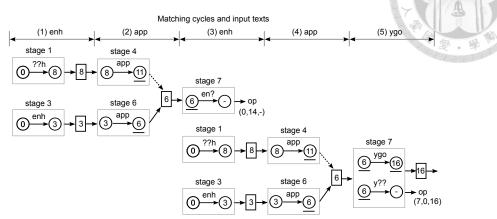

First, the generalized block diagram and matching operation of a multi-character string matching engine is described. This generalized block diagram and operation are applicable to the proposed architectures described in this thesis. Fig. 5.1 shows the complete bock diagram of a basic 3-character string matching engine, and Fig. 5.2 shows the waveform of the matching example with an input text 'enhappenhappygo'.

Figure 5.2: Waveform of matching operations

In every matching cycle, three characters are input via C1, C2, and C3 in parallel; and then, three corresponding matching outputs are generated from OP1, OP2, and OP3 after this matching cycle. In most of the implementations in this thesis, a matching cycle is equal to a clock cycle. Three registers are connected after PMUX1, PMUX2, and PMUX3 to save the matching outputs. A matching output can include a signal to indicate it is valid or not; the matching output is plotted as a zero line if it is invalid in the waveform.

The matching operations are synchronized with the clock signal CLK and data are latched in the rising edges of CLK. This input text is divided to five 3-character chunks 'enh', 'app', 'enh', 'app', and 'ygo' and then processed in five consecutive matching cycles, respectively. An inspecting 3-character chunk is input via IN\_CHRS, which includes C1 through C3, and three corresponding matching outputs are generated from OP1 through OP3 after one matching cycle. A valid matching output OP2, which is 14 or 'happen', after matching cycle 3; and two valid matching outputs OP1 and OP3, which are 7 and 16 or 'happy' and 'happygo' respectively, after matching cycle 5.

## 5.1 Multi-Character AC-DFA

This section proposes an efficient architecture for implementing the derived multicharacter AC-DFA. Fig. 5.3 illustrates the transitions of 3-character AC-DFA. In which, the growth of transitions is reduced by using a wildcard character to represent a unmatched character. Because the intermediate states are concealed when multiple characters are inspected simultaneously, the output set is denoted beside the pattern in a transition. For example, the output set denoted beside  $\delta_3(5,py?)=$ - is (0,17,-

Figure 5.3: Transitions of the 3-character AC-DFA