國立臺灣大學電機資訊學院資訊工程學系

## 博士論文

Department of Computer Science and Information Engineering College of Electrical Engineering and Computer Science National Taiwan University Doctoral Dissertation

## 可重定目標且高效能之動態二元碼轉譯器框架系統 Retargetable and Efficient Dynamic Binary Translation Framework

### 許俊琛 Chun-Chen Hsu

指導教授: 劉邦鋒博士

### 共同指導教授: 吴真貞博士

Advisor: Pangfeng Liu, Ph.D. Co-Advisor: Jan-Jan Wu, Ph.D.

中華民國 104 年 6 月

June, 2015

國立臺灣大學博士學位論文

## 口試委員會審定書

可重定目標且高效能之動態二元碼轉譯器框架系統 Retargetable and Efficient Dynamic Binary Translation Framework

本論文係<u>許俊琛</u>君(學號 D95922006)在國立臺灣大學資訊工程 學系完成之博士學位論文,於民國 104 年 7 月 17 日承下列考試委 員審查通過及口試及格,特此證明

口試委員:

(指導教授)

系主任

## Acknowledgements

Many people have contributed to this dissertation and I would like to acknowledge their contributions here. First of all, I thank my advisor, Prof. Pangfeng Liu, for providing me with the freedom and resources to do high-quality research, for being a caring teacher, and for teaching me all the fundamentals of being a good researcher. I want to thank my co-advisor, Dr. Jan-Jan Wu, for her high standards for research, endless patience and continuous encouragement. My life as a graduate student would have been very short and unproductive without her advices.

I'd like to give my very special thanks to Prof. Wei-Chung Hsu for always providing very useful technical insights and advices for my researches and for being a caring teacher. I thank Dr. Chien-Min Wang who always asks very sharp questions to polish my thoughts and ideas. I also thank Prof. Pen-Chung Yew for providing the research direction of this dissertation.

I want to thank members of the Computer System Group in Instituted of Information Science, Academia Sinica, and Parallel Distributed Lab in National Taiwan University. They all have contributed to this dissertation and my life in the past nine years. I am very appreicated those helpful discussions with Dr. Ding-Yong Hong in developing research ideas.

Finally, I cannot express with words my indebtedness to my parents and Celia for giving my their unconditional love and support at every step I have taken in

臺

iii

Hsu, Chun-Chen, Aug. 2015, Taipei

### 誌謝

許多人對這篇論文有著無比的貢獻, 我想在此致上我的感謝之意。 首先, 我要感謝的, 是我的博士論文指導教授劉邦鋒老師。我對電腦科學的研究興趣是由劉邦鋒老師所啓發 的, 沒有他我不會來唸博士班。在與他無數的討論過程中我學習到做學問的態度與方 法,他亦是我學術研究上的典範。 我再來要感謝我的共同指導老師, 吳眞貞老師。沒有 吳眞貞老師的督促與無比的耐心以鼓勵就不會有這篇論文的產生。 我要感謝徐慰中老 師, 他總是在技術問題上給我珍貴的回饋與建議。我感謝王建民老師, 他建立我對問題 的敏銳度。 我亦感謝游本中老師指導了這論文的研究方向。我很感激我在博士研究上有 以上老師的幫忙, 無比地感謝。 我也感謝中央研究院的系統實驗室的各個成員以及在臺 大資訊工程所 332 平行分散實驗室的各個成員。我特別感謝洪鼎詠博士, 我總是可以在 我們的討論中找到新的研究方向。

還有眞慧,感謝妳的陪伴,那總是可以安撫我燥鬱的心情,謝謝妳一起陪我走過博士最 後這幾年。 最後要感謝我的父母,許民先生以及余月玲女士。您們是我很大的精神支 柱,不只是我的博士在我一生的其他時刻也是。

> 許俊琛, 2015 年 8 月在臺北

## Abstract

Dynamic binary translation is one of the core technologies in virtualization to boost the performace of instruction set architecture (ISA) simulation. The key factors to the performace of dynamic binary translators are the quality of translated code and the ability to detect hot regions at runtime. This dissertation builds a retargetable dynamic binary translator framework and provides two hot region detection approaches to improve the performance of dynamic binary translators.

The quality of translated code is critical to the performance of a dynamic binary translator, which implements the semantics of the *guest ISA* instructions with the *host ISA* instructions, so the translated code is often carefully hand-optimized. However a hand-optimized translator is not retargetabile because it takes tremendous implementation efforts for software engineers to port it to a new host ISA.

This dissertation first proposes an LLVM+QEMU (LnQ) framework for building high performance and retargetable binary translators with existing compiler modules. The goal of LnQ framework is to enable the process of building high performance and retargetable dynamic binary translators with existing industrystrength compiler optimization passes and code generation backends. Compared to QEMU, the LnQ shows more than 2X speedup in CINT2006 for ARM-to-x86\_64 and x86-to-ARM dynamic binary translators compared to QEMU. Besides the quality of translated code, the ability to detect "hot regions" of guest applications also determines the performance of dynamic binary translators. Most dynamic binary translators target traces, i.e. frequently executed code paths, as code regions to be translated and optimized. The *Next-Executing-Tail (NET)* trace formation method is an important example of such techniques. Many existing trace formation schemes are variants of NET.

vi

This dissertation examines the inefficiency of NET-like trace formation algorithms. We found the formed traces may contain a large number of early exits that could be branched out during the execution. If this happens frequently, the program execution will spend more time in the slow binary interpreter or in the unoptimized code regions than in the optimized traces in code cache. The benefit of the trace optimization is thus lost. Traces with frequently taken early-exits are called *delinquent* traces.

This dissertation proposes a light-weight region formation technique called *Early-Exit Guided Region Formation (EEG)* to improve the efficiency of traces. It iteratively identifies and merges delinquent regions into larger code regions. It is shown the EEG achieves 1.23X and 1.11X speedup in CINT2006 for ARM-to-x86\_64 and x86-to-ARM DBTs compared to NET.

This dissertation also studies the procedure-based dynamic binary translator that detects hot procedures as its compilation (i.e. translation and optimization) unit. We compare the performance of our EEG region formation algorithm with procedure region.

### 摘要

動態二元碼翻譯是虛擬化技術的核心技術因為它可用來加速指令集模擬。 對於動態二元 碼翻譯器而言,其關鍵在於所翻譯的二元碼的質量,以及是否可以在程式執行過程找到 再優化增進效能的程式區段。 在這論文中,我們呈現一個可重置的二元碼翻譯系統,此 系統可產生高效能的動態二元碼翻譯器。 我們另提出二種執行熱區偵查方法來增加動態 二元碼翻譯器的效能。 對一動態二元碼翻譯器而言,其翻譯的二元碼對於效能的影響甚 為重要。故通常我們會對翻譯碼做手動優化。 然而這樣手動優化過的翻譯器是難以重置 到另一系統,因爲需要同樣的實作力氣來移植翻譯器到新的平台上。

此論文首先提出一容易重置的二元碼翻譯系統,稱為LLVM+QEMU (LnQ),利用現 有的編譯器技術來產生高效能的動態二元碼翻譯器。與 QEMU 相比, LnQ 在 ARM 到 x86\_64 及 x86 到 ARM 的動態二元碼翻譯器上於SPEC CINT2006中有高於2倍的 效能表現。此外,能否在程式執行過程中偵測出執行程式熱區也是影響效能的一關鍵因 素。在此論文中我們將指出現今熱區偵測方法不好的地方,亦即其所偵測的熱區會無法 完全執行,如果這樣的熱區很多的話將會導至效能不佳。我們首先提出測量此一弱點的 方法來證明此弱點眞的存在。進而我們再提出一改進此弱點的方法。我們在此論文中提 出一輕量級的熱區偵測技術稱為「Early-Exit Guided Region Formation (EEG)」。 EEG 能持續地尋找出無法完全執行的熱區並將它與其他熱區合併來改進效能。這方 法對於 ARM 到 x86\_64 的動態二元碼翻譯器能有效改進之前的方法約23%。對於 x86\_64 到 ARM的翻譯器約有11% 我們最後提出另一種以程序為單位的熱區偵測方 法。並比較EEG與此方法的優劣。

## Contents

| 0            | 試委員                                      | 自會審定書                                                                                                                                                                                                                                     | i                                                                      |

|--------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| A            | cknov                                    | wledgements                                                                                                                                                                                                                               | ii                                                                     |

| 誌            | 謝                                        |                                                                                                                                                                                                                                           | iv                                                                     |

| $\mathbf{A}$ | bstra                                    | $\mathbf{ct}$                                                                                                                                                                                                                             | v                                                                      |

| 摘            | 要                                        |                                                                                                                                                                                                                                           | vii                                                                    |

| Co           | onten                                    | nts v                                                                                                                                                                                                                                     | iii                                                                    |

| Li           | st of                                    | Figures                                                                                                                                                                                                                                   | xi                                                                     |

| Li           | st of                                    | Tables x                                                                                                                                                                                                                                  | iii                                                                    |

| 1            | <b>Intr</b><br>1.1<br>1.2                | oductionRetargetability of Dynamic Binary TranslatorsHigh Performance of Dynamic Binary Translators1.2.1Delinquent Trace1.2.2Solution 1: Early-Exit Guided Region Formation1.2.3Solution 2: Trace-Guided Procedure-Based Region Formation | <b>1</b><br>1<br>3<br>4<br>5<br>6                                      |

|              | $\begin{array}{c} 1.3\\ 1.4 \end{array}$ | Contributions                                                                                                                                                                                                                             | 7<br>9                                                                 |

| 2            | <b>Th</b><br>2.1                         | LnQ: Design and Implementation2.1.1LLVM Intermiediate Representation2.1.2IR Library and Instruction Description Table2.1.3LLVM IR Translator                                                                                              | <ol> <li>10</li> <li>11</li> <li>12</li> <li>13</li> <li>14</li> </ol> |

|              |                                          |                                                                                                                                                                                                                                           |                                                                        |

| $C \epsilon$ | onten | ts     | ix                                                           |

|--------------|-------|--------|--------------------------------------------------------------|

|              |       |        |                                                              |

|              |       | 2.1.4  | Emulation Module                                             |

|              | 2.2   |        | me Optimizations                                             |

|              |       | 2.2.1  | Block Linking                                                |

|              |       | 2.2.2  | Indirect Branch Target Caching                               |

|              |       | 2.2.3  | Shadow Stack                                                 |

|              | 2.3   | Perfor | mance Evaluation                                             |

|              |       | 2.3.1  | Experiment Settings                                          |

|              |       | 2.3.2  | Performance of $LnQ$                                         |

|              |       | 2.3.3  | Performance of LLVM Just-In-Time Compiler                    |

|              |       |        | 2.3.3.1 Execution Time Spent in Code Cache                   |

|              |       |        | 2.3.3.2 Translation Overhead                                 |

|              |       | 2.3.4  | Optimization Effects of Runtime Optimization                 |

|              |       | 2.3.5  | Slowdown of LnQ Compared to Native Run                       |

|              |       | 2.3.6  | Performance of ARM-to-IA32 LnQ                               |

|              |       | 2.3.7  | Performance of IA32-to-ARM LnQ                               |

|              | 2.4   | Concl  | uding Remarks                                                |

|              |       |        |                                                              |

| 3            |       | •      | r-Exit Guided Code Region Formation 35                       |

|              | 3.1   | 0      | n-Based Multi-threaded Dynamic Binary Translator 35          |

|              | 3.2   | °,     | Exit Index and Early-Exit Guided Region Formation 38         |

|              |       | 3.2.1  | Trace Formation Algorithm                                    |

|              |       | 3.2.2  | Early Exit Index                                             |

|              |       | 3.2.3  | Early-Exit Guided Region Formation                           |

|              |       | 3.2.4  | Spill Index of a Region                                      |

|              |       | 3.2.5  | Region Versus Trace                                          |

|              | 3.3   |        | mance Evaluation                                             |

|              |       | 3.3.1  | Performance Results of SPEC CPU2006                          |

|              |       |        | 3.3.1.1 Performance of NET* $\ldots \ldots \ldots \ldots 46$ |

|              |       |        | 3.3.1.2 Performance of EEG Region Formation 47               |

|              |       | 3.3.2  | Early Exit Index                                             |

|              |       | 3.3.3  | Performance Profiles of EEG                                  |

|              |       | 3.3.4  | Effect of The Threshold of Spill Index                       |

|              |       | 3.3.5  | Statistics of Selected Traces and Regions                    |

|              |       | 3.3.6  | Performance Comparison to Native Execution                   |

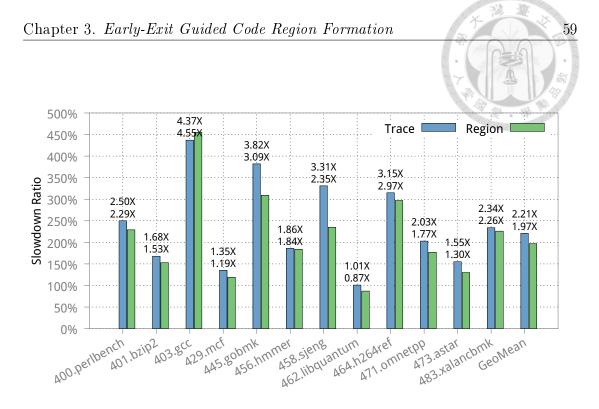

|              |       | 3.3.7  | Performance of EEG on IA32-to-ARM LnQ 58                     |

|              | 3.4   | Concl  | uding Remarks                                                |

| 4            | Tro   | ce-Gui | ded Procedure-Based Code Region Formation 61                 |

| -            | 4.1   |        | secture of Dynamic Binary Translator 61                      |

| Conten | 8                                                                                  |   |

|--------|------------------------------------------------------------------------------------|---|

| 4.2    | Procedure Compilation in Dynamic Binary Translation                                | 6 |

| 4.2    | 1 0 0                                                                              | 6 |

|        |                                                                                    | 6 |

|        | 10761019                                                                           | 6 |

| 4.3    | 0                                                                                  | 7 |

| 4.0    | 4.3.1 Experimental Environment and Settings                                        | - |

|        | r O                                                                                | - |

|        | -                                                                                  | - |

|        |                                                                                    | , |

| 4.4    |                                                                                    | , |

| 4.4    | Concluding Remarks                                                                 |   |

| 6 Rel  | ated Works                                                                         | 7 |

| 5.1    | Related Works of Dynamic Binary Translation (DBT)                                  | , |

|        | 5.1.1 QEMU                                                                         | 1 |

|        | 5.1.2 Retargetable Dynamic Binary Translators                                      | , |

|        | 5.1.3 Other Dynamic Binary Translators                                             | 1 |

| 5.2    | Related Works of Region Formation                                                  | 8 |

|        | 5.2.1 NET                                                                          | 8 |

|        | 5.2.2 Most Recently Executed Tail <sup>2</sup> $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 8 |

|        | 5.2.3 NETPlus                                                                      | 8 |

|        | 5.2.4 Last-Executed Iteration (LEI)                                                | 8 |

| 5.3    | Related Works of Language Virtual Machines                                         | 8 |

|        | 5.3.1 Method-Based Language Virtual Machines                                       | 8 |

|        | 5.3.2 Trace-Based Language Virtual Machines                                        | ą |

| 6 Cor  | clusion and Future Works                                                           | 8 |

|        |                                                                                    | 8 |

| 6.1    |                                                                                    |   |

## List of Figures

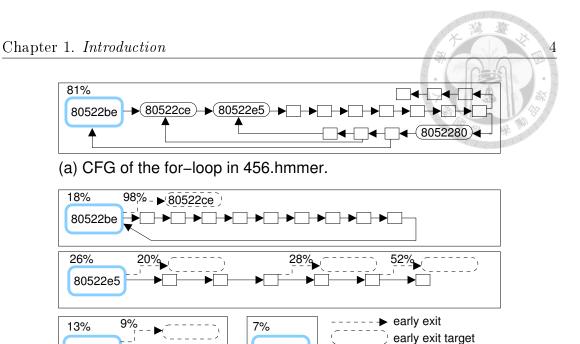

| 1.1          | An example of delinquent traces of NET in 456.hmmer                        | 4  |

|--------------|----------------------------------------------------------------------------|----|

| $2.1 \\ 2.2$ | The architecture of LnQ framework                                          | 11 |

|              | module.                                                                    | 11 |

| 2.3          | Illustration of the translation process.                                   | 13 |

| 2.4          | Illustration of the control flow in emulation module                       | 16 |

| 2.5          | Illustration of execution steps of block linking optimization.             | 19 |

| 2.6          | Illustration of execution steps of indirect branch target caching op-      |    |

|              | timization.                                                                | 20 |

| 2.7          | Illustration of execution steps of shadow stack optimization               | 22 |

| 2.8          | Speedup factors of LnQ in of SPEC CPU2006 compared with QEMU.              | 23 |

| 2.9          | Speedup factors of execution time spent in code cache of LnQ com-          |    |

|              | pared to QEMU. The numbers above bars are                                  | 26 |

| 2.10         | Performance of block linking, IBTC, and shaow stack                        | 29 |

| 2.11         | The reduction of percentage of dispatch time.                              | 30 |

| 2.12         | The slowdown of LnQ and QEMU compared with native run                      | 31 |

| 2.13         | Performance of ARM-to-I32 LnQ                                              | 32 |

| 2.14         | Performance of IA32-to-ARM LnQ                                             | 33 |

| 3.1          | Control flow of execution threads and optimization threads $\ldots$ .      | 36 |

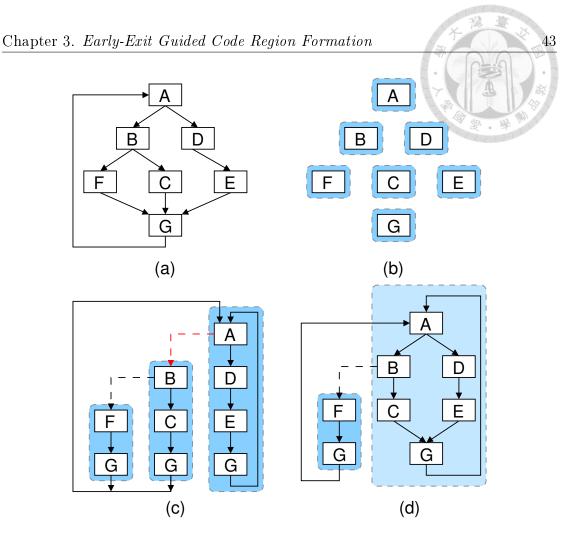

| 3.2          | Illustration of region formation.                                          | 43 |

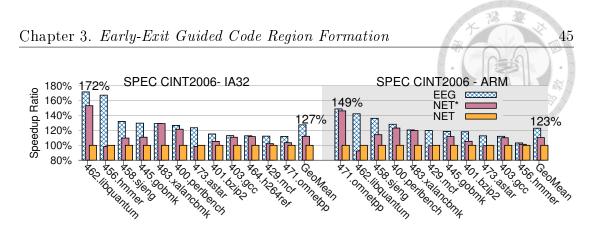

| 3.3          | Performance results of NET $^*$ and EEG compared to NET in IA32            |    |

|              | and ARM SPEC CINT2006                                                      | 45 |

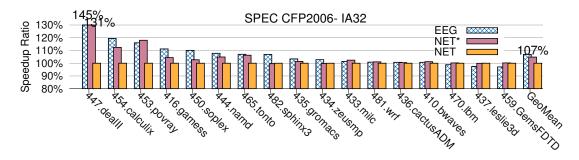

| 3.4          | Performance results of NET $^*$ and EEG compared to NET in SPEC            |    |

|              | CFP2006                                                                    | 45 |

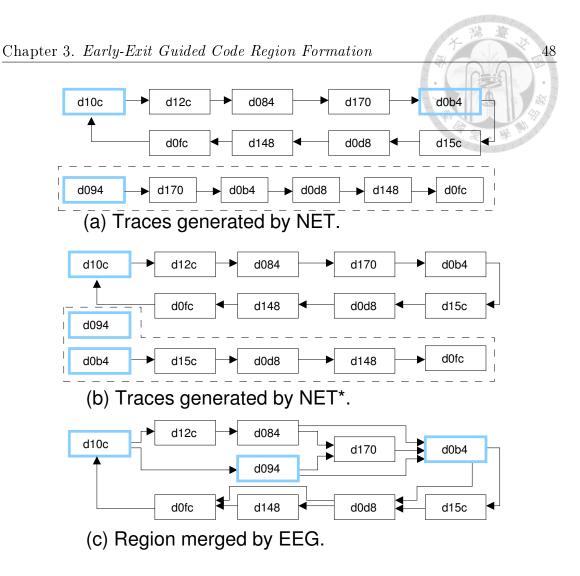

| 3.5          | Traces/regions generated by NET, NET* and EEG for a loop in                |    |

|              | function quantum_toffoli of ARM 462.libquantum                             | 48 |

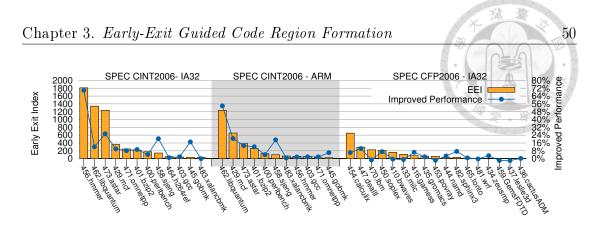

| 3.6          | Measured Early Exit Index in NET <sup>*</sup> and the performance improve- | _  |

|              | ment of EEG.                                                               | 50 |

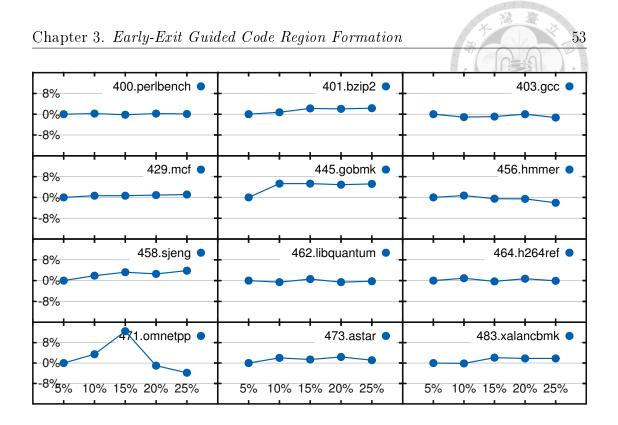

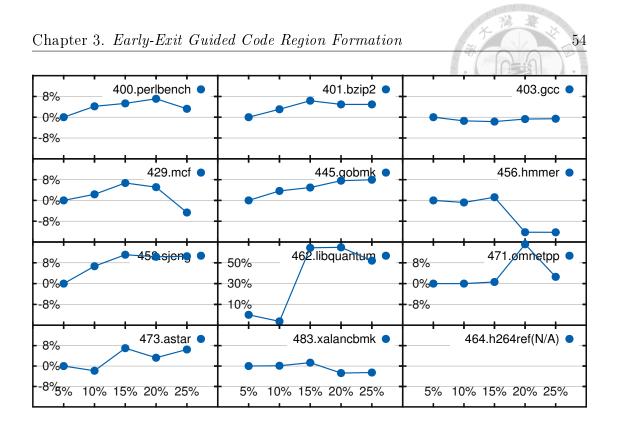

| 3.7          | Effect of spill index of IA32 CINT2006                                     | 53 |

| 4 - f | Rissure X 12 X                                                 |     |

|-------|----------------------------------------------------------------|-----|

| ιομ   | Figures                                                        | XII |

| 3.8   | Effect of spill index of ARM CINT2006                          | 54  |

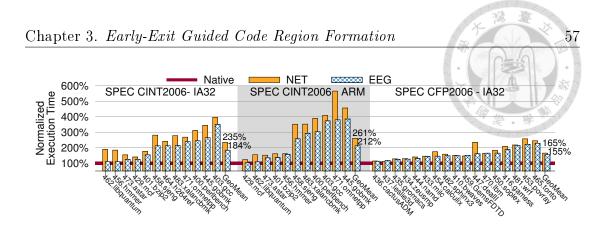

| 3.9   | Normalized execution time of EEG compared to native execution. | 57  |

| 3.10  | Normalized execution time of EEG compared to native execution  |     |

|       | on ARM host.                                                   | 59  |

| 4.1   | Control flow of main thread and optimization threads           | 63  |

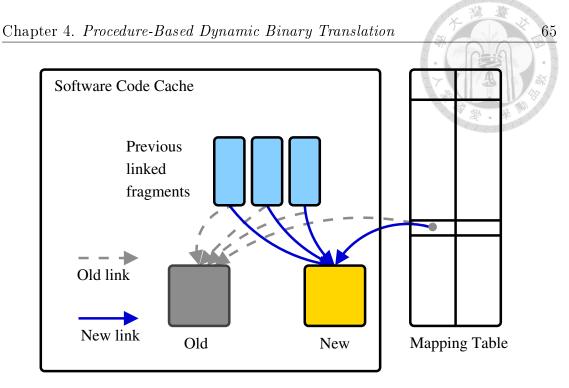

| 4.2   | When a new fragment is generated, we update the mapping table  |     |

|       | and the links between the new and old fragments                | 65  |

| 4.3   | Illustration of an example of Call-Return problem.             | 68  |

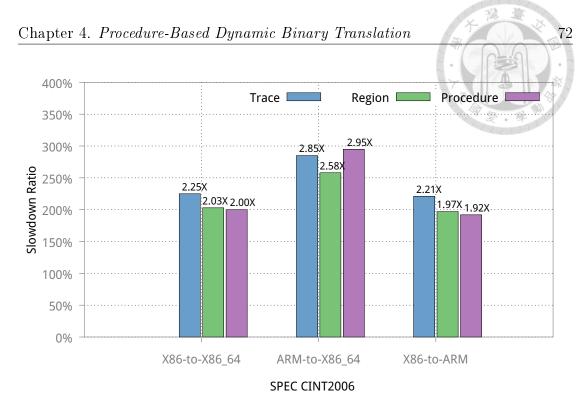

| 4.4   | Overview of performance of Procedure-Based LnQ.                | 72  |

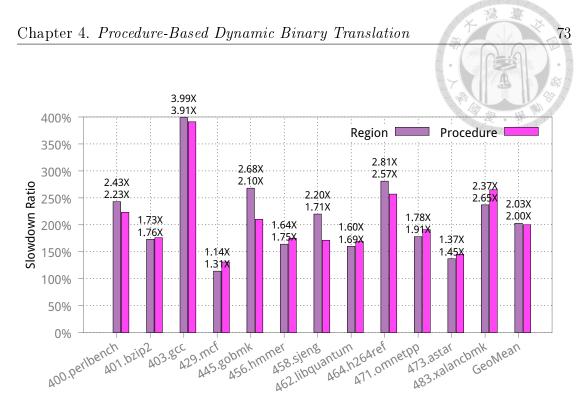

| 4.5   | Detailed Performance of Procedure-Based X86-to-X86_64 LnQ      | 73  |

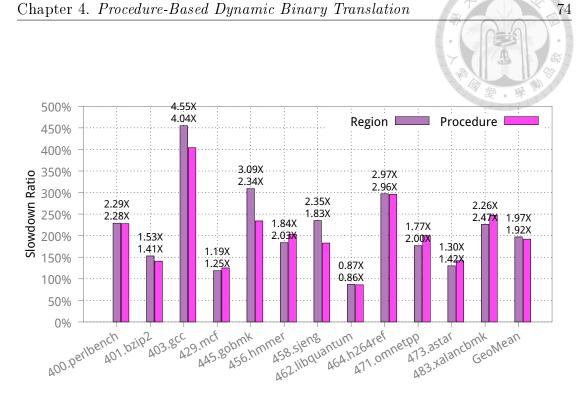

| 4.6   | Detailed Performance of Procedure-Based X86-to-ARM LnQ         | 74  |

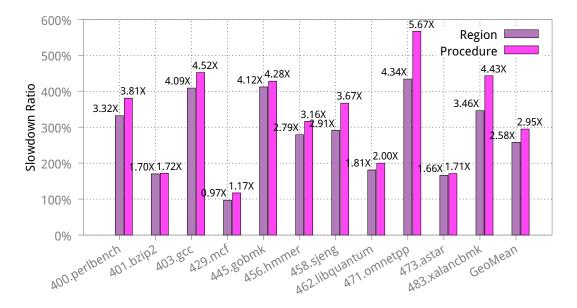

| 4.7   | Detailed Performance of Procedure-Based ARM-to-X86_64 LnQ.     | 74  |

## List of Tables

| 2.1 | Translation overheads of LnQ and QEMU. The number of guest<br>basic blocks, and total running time and translation time in seconds<br>are listed for each benchmarks. The numbers in parentheses are the<br>percentages of translation time versus total running time | 27      |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 3.1 | Reduced memory/branch instructions and cache misses of EEG for                                                                                                                                                                                                        | ۲1      |

|     | CINT2006 benchmarks                                                                                                                                                                                                                                                   | $^{91}$ |

| 3.2 | Number of traces/Regions and average blocks in NET $^*$ and EEG of                                                                                                                                                                                                    |         |

|     | IA32 CINT2006                                                                                                                                                                                                                                                         | 55      |

| 3.3 | Number of merges and percentage of execution time of regions in                                                                                                                                                                                                       |         |

|     | EEG of IA32 CINT2006                                                                                                                                                                                                                                                  | 55      |

| 3.4 | Number of traces/Regions and average blocks in NET* and EEG of ARM CINT2006                                                                                                                                                                                           | 56      |

| 0 5 |                                                                                                                                                                                                                                                                       | 00      |

| 3.5 | Number of merges and percentage of execution time of regions in                                                                                                                                                                                                       |         |

|     | EEG of ARM CINT2006                                                                                                                                                                                                                                                   | 56      |

|     |                                                                                                                                                                                                                                                                       |         |

## Chapter 1

## Introduction

### 1.1 Retargetability of Dynamic Binary Translators

Dynamic binary translation is a just-in-time (JIT) compilation from binary code of a guest ISA to a host ISA, which is widely used for transparent performance optimization [1-4], program instrumentation, security monitoring [5], supporting legacy applications, and system virtualization [6]. For example, Dynamo [7] uses dynamic binary translation techniques to improve execution performance. DynamoRIO [8] PIN [9], Valgrind [10], Strata [11, 12], and Umbra [13] uses dynamic binary translation techniques for program instrumentation.

If the guest ISA is different from the host ISA, we refer to it as a *cross-ISA* binary translator. Cross-ISA binary translators enable application to migrate from one hardware platform to another, or to provide a virtualized platform to run an application without the specific hardware. For example, FX!32 [14, 15] enables application to migrate from IA-32 to Alpha, and IA-32EL [16] enables application to migrate from IA-32 to Itanium. Other migration examples include [17– 22]. QEMU [23], VmWare [24], and other virtulization systems [25–28] use binary translation technique to provide server virtualization.

2

It takes tremendous efforts to build a cross-ISA translator because a cross-ISA translator must prepare a *carefully hand-optimized* translation template [14, 16] for *each* guest instruction. As a result it takes the same amount of effort to build a new cross-ISA translator because of the preparation of these carefully hand-optimized translation templates.

The difficulty in building cross-ISA translators motivates us to develop the LLVM [29] + QEMU (LnQ) framework. The goal of LnQ framework is to enable the process of building high performance and retargetable dynamic binary translators with *existing* optimizers and code generation backends. We address the retargetability issue by translating the guest instructions into a machine-independent intermediate representations (IR), which can be used by other compiler modules, e.g., a code optimizer.

With existing mature optimization techniques available from compiler backend, the quality of the translated code can be greatly improved. To further improve performance without sacrificing retargetability, we show that many binary translation optimizations can be implemented at the machine-independent IR level, so that they only need to be implemented once in LnQ and can be applied to every translator built within LnQ framework thereafter.

## 1.2 High Performance of Dynamic Binary Translators

Dynamic binary translators need to detect hot regions of guest applications at runtime in order to get high performance. The quality of the detected hot regions determines the extent and the types of optimization opportunities that can be exposed to dynamic binary translators, and thus, determines the ultimate quality of the final optimized code.

Nowadays, most dynamic binary translators target *traces*, i.e. frequently executed code paths, as code regions to be translated and optimized. Those dynamic binary translation systems [4, 8, 30] follow the well-known runtime trace formation algorithm, called Next-Executing-Tail (NET), developed in HP Dynamo [7]. The trace-based region formation approaches have also gained much attention in dynamic scripting languages [31, 32] and high-level language virtual machines [33–35] because they provide more optimization opportunities and generate higher quality codes.

Without expensive path profiling at runtime, NET forms a trace by selecting the basic blocks<sup>1</sup> that are most recently executed with minimal profiling overhead. The idea is that when a basic block becomes hot, it is likely that the following basic blocks are also hot.

$<sup>^{1}\</sup>mathrm{A}$  basic block is a sequence of instructions terminated by a control transfer instruction

(b) Traces generated by NET

FIGURE 1.1: An example of delinquent traces of NET in 456.hmmer.

80522ce

trace head

#### 1.2.1 Delinquent Trace

8052280

As a hot trace is formed by cascading a sequence of hot basic blocks, there will be a conditional branch at the end of each member basic block, referred to as the *early exit* of the trace. DBTs needs to generate *compensation code* at each of such early exits to handle the case when the conditional branch is taken [6]. If early exits are frequent, then not only will such extra compensation code need to be executed, but also program execution will spend more time in the slow binary interpreter or in unoptimized code regions. The benefit of trace optimization by the DBT is thus lost. Traces with frequently taken early-exits are called *delinquent* traces.

Since NET does not use edge profiling [7] information to select next basic blocks, early exits may occur when program behavior changes in different execution phases. For example, as shown in Figure 1.1(a), the function P7Viterbi in 456.hmmer (a SPEC CINT2006 CPU benchmark) contributes most of its execution time. **P7Viterbi** updates global variables according to different conditions in a performance critical for-loop.

5

NET splits the for-loop into four traces as shown in Figure 1.1(b). Each large rectangle represents a trace. The execution time of each trace, shown as the percentage of total execution time, is noted on the left top corner of the trace. The probability of an early exit being taken is also noted on each exit edge. Figure 1.1(b) shows a trace for a loop starting at 0x80522be. The probability of taking an early exit during the loop execution is  $98\%^2$ . Such a high probability for an early exit will certainly diminish the performance benefit expected from the loop trace.

#### **1.2.2** Solution 1: Early-Exit Guided Region Formation

To accomplish this, this dissertation proposes a light-weight technique called *Early-Exit Guided (EEG) region formation* to detect and merge delinquent regions. For example, The EEG region formation technique will merge those four traces into a large code region shown in Figure 1.1(a), which can improve its performance by 68%.

There are two key issues in EEG: (1) which regions should be merged, and (2) when to merge those regions. A simple approach for the first issue is to instrument counters into all traces. However, this approach is prohibitively expensive. Instead, we employ hardware-assisted dynamic profiling to select hot regions and to avoid monitoring and merging unimportant regions. To address the second issue, we

<sup>&</sup>lt;sup>2</sup>Section 3.3 describes the experiment environment and methodology

monitor regions by instrumenting counters to detect early exits. When the counter exceeds a threshold, we merge this region with the region that begins at the branch target of the early exit. We also employ a heuristic to decide whether it is beneficial to merge the selected regions or not. We will not merge regions if it will cause too much register pressure; i.e. too many store/load operations to spill and fill values between registers and the stack (see Section 3.2.4).

6

We also extent LnQ to a multi-threaded DBT system. In such a system, there is a pool of compilation threads. Each thread is capable of taking one trace as a compilation (i.e. translation and optimization) unit. Similar to the work of Bohm et al. [30], we separate compilation tasks from execution tasks to hide the compilation overhead. This is especially important because compiling procedures could induce large overhead if not off loaded from the execution.

## 1.2.3 Solution 2: Trace-Guided Procedure-Based Region Formation

By forming a larger code region beyond traces to an entire *procedure*, we can resolve the inefficiency issues of delinquent traces since the early exits of traces will be likely within the same procedure. Furthermore, as hot traces are usually identified more quickly than hot procedures, we could form and optimize traces to improve performance before hot procedures are identified. Identifying hot procedures basically uses the same profile information collected for trace formation. No additional profiling overhead is incurred. These advantages motivate us to integrate trace-guided optimizations into a procedure-based DBT.

#### Chapter 1. Introduction

Unlike traces, procedures often contain hundreds of blocks. Such large compilation scopes can better utilize the power of LLVM backend optimizations, e.g. loopbased optimizations, for higher quality code. We also identify and resolve issues that are specific to procedure-level compilation in DBT systems. For instance, information on target blocks of indirect branches are not readily available in binary, as opposed to high-level language virtual machines in which richer knowledge about procedures is available to their JIT compilers.

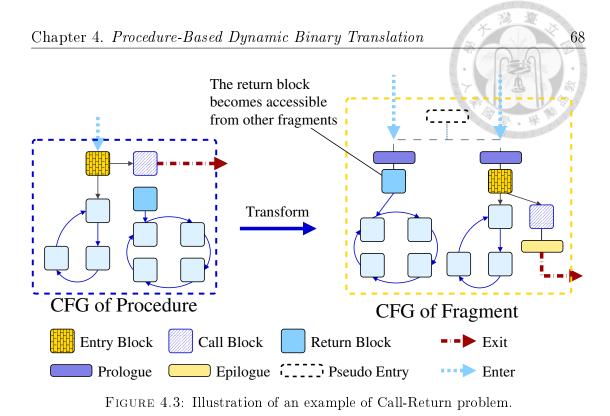

We also identify a *Call-Return problem* of procedure-based dynamic binary translation, in which a guest call instruction could make the block at its returned address unreachable. We solve this problem by making the unreachable block an entry block of the translated procedure and make it reachable (see Section 4.2.1).

We also propose two feedback-directed optimizations on procedures (see Section ??). The first optimization is Trace-Guided Block Reordering, in which it uses frequently-taken paths to order the basic blocks in translated procedures. The other optimization is Trace-Guided Partial Inlining, in which blocks of the taken paths in a called procedure are included using hot traces detected during hot trace-formation, as opposed to using meta-data annotated in byte code in Java [36].

### **1.3** Contributions

This dissertation makes the following major contributions:

- This dissertation presents the design and implementation of the LnQ framework, which can build high performance multi-threaded trace-based/procedurebased dynamic binary translators. We introduce several novel approaches to build high performance dynamic binary translators with existing compiler modules. LnQ dynamic binary translators can off-load compilation overhead to other cores and allow more aggressive and sophisticated optimizations to be done on the larger code regions during execution. We build x86-tox86\_64, ARM-to-x86\_64, x86-to-ARM, ARM-to-ARM binary translators to demonstrate the performance of LnQ.

- This dissertation identifies delinquent traces, and shows that many SPEC CINT2006 benchmarks suffers from the inefficiency of traces. Our experimental results show that there is a substantial amount of delinquent traces, and that more than 100 early exits are taken for every million executed instructions in 65% of SPEC CINT2006.

- This dissertation presents an *Early-Exit-Guided* region formation algorithm (EEG) that uses hardware-assisted dynamic profiling and instrumented software counters to detect and merge delinquent traces/regions into larger regions to resolve the efficiency problem of delinquent traces.

- This dissertation also presents thread-guided procedure-based region formation algorithms in dynamic binary translators. We identify a number of important issues in such a system and propose promising solutions to these issues. Two feedback-directed optimizations for procedures are proposed to leverage runtime profile information collected during trace formation and

optimization. The Trace-Guided Block Reordering approach guides the ordering of basic blocks in procedures according to frequently-taken paths detected during trace formation. And Trace-Guided Partial Inlining approach inlines hot code regions found during trace optimization.

9

### 1.4 Dissertation Organization

This dissertation has six chapters. Chapter 2 presents the design and implementation of LnQ framework including how we implement 3 retargetable runtime optimizations in LnQ. Chapter 3 shows techniques to detect delinquent traces and presents the EEG region formation algorithm for delinquent traces. Chapter 4 presents procedure-based region formation algorithms. Chapter 5 describes related works in dynamic binary translation and region formation. Chapter 6 provides concluding remarks to summarize our key results and insight presented in this dissertation, and suggestion for future researches in region formation.

## Chapter 2

# The LLVM+QEMU (LnQ) Framework

### 2.1 LnQ: Design and Implementation

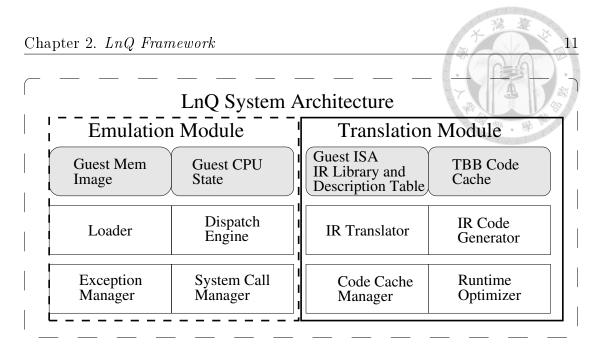

This section describes the design of LnQ – a framework that builds high performance dynamic binary translators. The LnQ framework consists of two modules - an *emulation module* and a *translation module*, as shown in Figure 2.1. We use QEMU [37] as our emulation module, and build the translation module with LLVM [38] compiler infrastructure.

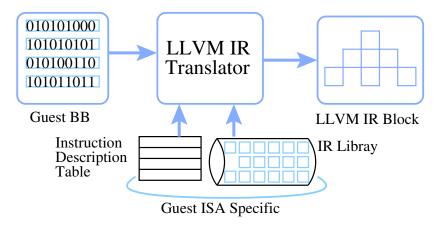

We first describe the design and execution flow of the translation module. Our translation module contains an *LLVM IR translator*, *IR libraries*, and an *instruction description table* of guest ISAs, as shown in Figure 2.2.

FIGURE 2.1: The architecture of LnQ framework

FIGURE 2.2: Illustration of the design and execution flow in LnQ translation module.

#### 2.1.1 LLVM Intermiediate Representation

We choose *LLVM virtual instruction set* as our intermediate representation (IR) of guest instructions for the following three reasons. First, the LLVM compiler infrastructure provides modular and reusable components for building an efficient just-in-time (JIT) runtime system. The LLVM infrastructure reduces the time

and cost to develop LnQ framework. Second, LLVM is an open source project and is well-documented. We believe that an open source project greatly improves component interoperability and enables future extension of our research work. Thirdly, LLVM IR is well-defined and can be easily manipulated by a rich set of API.

12

#### 2.1.2 IR Library and Instruction Description Table

To support a new guest ISA in LnQ framework, we need to provide LnQ the IR *library* and the *instruction description table* of the guest ISA. The IR library consists of pre-built LLVM IR templates for every guest instruction. These templates are referred to as *translation functions*. Each translation function implements the semantics of a guest instruction in C, and is compiled into LLVM IR with LLVM-enabled compliers, such as *clang, llvm - gcc*.

In addition to IR library we also need to provide an instruction description table that describes the *properties* of parameters related to the translation function of each guest instruction. A property of a parameter contains the type of the parameter (e.g. a constant or a register ID), and how to obtain the parameter (e.g. from the immediate operand of the decoded guest instruction).

This property approach improves guest ISA retargetability because guest ISA specific IR libraries and instruction description tables can be "plugged into" an LLVM IR translator. To support a new guest ISA, we only need to implement the semantics of all guest instructions with LLVM IR. Since the translation functions are written in C rather than in LLVM IR, it becomes much easier to support a new guest ISA in our LnQ framework.

13

#### 2.1.3 LLVM IR Translator

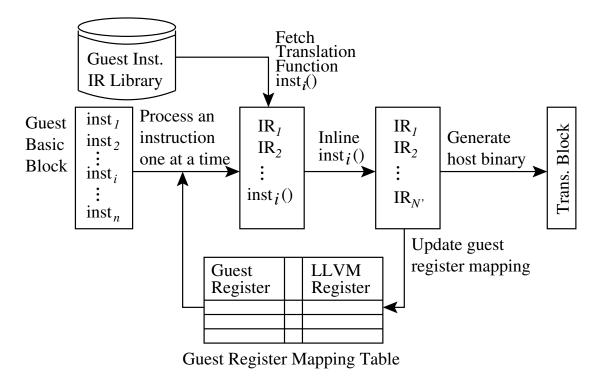

The LLVM IR translator translates guest instructions into LLVM IR one guest basic block at a time, and passes the LLVM IR to LLVM JIT to generate host instructions. Figure 2.3 Illustrates all steps of the translation flow.

FIGURE 2.3: Illustration of the translation process.

First the translator creates an empty LLVM function as the container of the generated IRs. Then the translator decodes a guest basic block from the starting address until it encounters a control transfer instruction, such as calls and branches. For each decoded instruction the translator fetches its translation function from IR library and supplies the needed arguments according to the instruction description table.

14

The translator creates a call instruction to the translation function after generating its arguments, inlines the translation function into the function body, then generate optimized code. After inlining all translation functions of guest instructions in current guest basic block, the generated LLVM function is sent to an optimization pass manager for optimization, and then sent to the code generator to generate host instructions. The LLVM inline API provides several optimizations to the inlined LLVM IRs, such as *Constant Propagation* and *Unreachable Basic Block Elimination*.

#### 2.1.3.1 Register Mapping

Register mapping maps guest registers to host registers in order to eliminate redundant loads and stores of guest registers. If we map guest registers to host registers, then we can retrieve guest register values from host registers, and only need to update guest registers values (kept in memory) when we leave a translated block.

We map guest registers to LLVM registers, and let LLVM register allocator to map LLVM registers to host registers. However, LLVM IR must follow Static Single Assignment (SSA) form in which each LLVM register can only be defined once. As a result we need a mapping table to map each guest register to its *current*  LLVM register, so that we can determine which LLVM register has a particular guest register from the mapping table.

15

The LLVM IR translator maintains the mapping table as follows. Initially the mapping table is empty. If we cannot find the corresponding LLVM register of a guest register in the mapping table, then the guest register was not loaded yet. The translator then creates a load instruction to load the guest register from memory to an LLVM register, and updates the mapping table so that future references to that guest register will be mapped to the LLVM register.

The translator looks up the mapping table mainly to determine which LLVM registers to use when constructing the arguments of a translation function. After constructing the arguments, the translator inlines the translation function.

If an inlined function, which is compiled by a LLVM-enabled complier, modifies guest registers, then according to SSA constraints on LLVM register, the LLVMenabled compiler places the new value of the guest register into another LLVM register. Therefore we need the following information to update the mapping table correctly – the modified guest registers and the new LLVM register this guest register should be mapped to.

Our solution is to associate the information of modified guest register and new LLVM register with every translation function. When the translator inlines the translation functions, it retrieves these information and will be able to update the mapping.

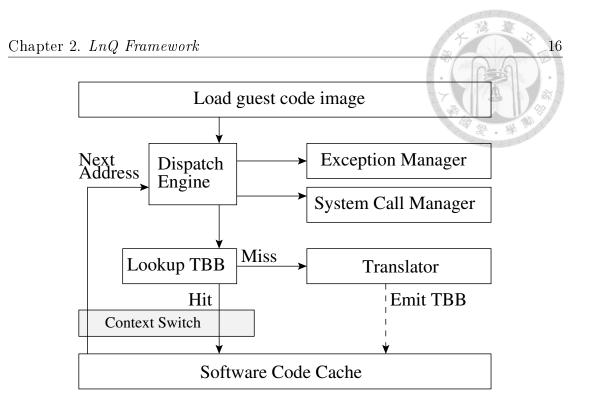

FIGURE 2.4: Illustration of the control flow in emulation module.

#### 2.1.4 Emulation Module

Figure 2.4 illustrates the execution flow of a dynamic binary translator. First the loader loads the guest application image into memory. The guest code image consists of basic blocks that end with a control transfer instruction, such as calls, branches, etc. Currently LnQ uses guest basic block as the unit for translation and execution. The emulation module then initializes the guest CPU state which represents the state of the guest machine processors. For example, an x86 guest CPU state contains program counter, general purpose registers, and the effags register, etc.

After initialization, the dispatch engine tries to locate the translated basic block of the current guest basic block, pointed by the guest program counter, with a directory to map the address of guest basic blocks to memory locations of their translated blocks in code cache. If the directory reports a hit for the current guest basic block, the control transfers to the memory location of its translated block in code cache. If we cannot find the translated block for the current guest basic block, the control transfers to the translation module, which will translate the current guest basic block and add an entry into the directory.

17

After the translated basic block is executed, the execution control transfers back to the emulation engine, which is referred to as *context switching*. The process is repeated until program terminates.

### 2.2 Runtime Optimizations

We can also integrate runtime optimizations that manipulate LLVM IRs to further improve the performance in LnQ framework. Those optimizations should be retargetable and not depend on either guest ISA or host ISA. Retargetability is an important goal of LnQ framework, and we expect those optimization techniques can be reused in all binary translators for all ISAs.

To demonstrate this ability, we implemented three classic optimizations that reduce the frequency of context switch between emulation engine and code cache. The three optimizations are *block linking*, *indirect branch target caching*, and *shadow stack*. We describe each of them in the following sections.

#### 2.2.1 Block Linking

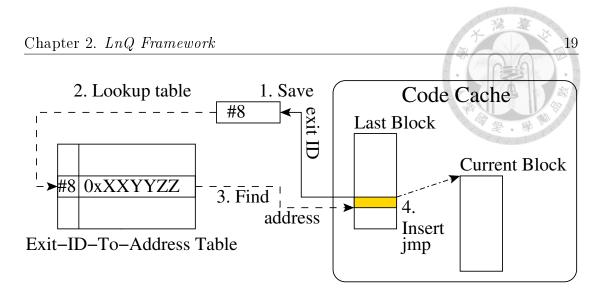

Block linking [7] links translated blocks in code cache so that program execution transfers directly from one code block to another so as to eliminate expensive context switching. Block linking targets at blocks that have a direct branch, a conditional direct branch, or a direct call instruction as the last instruction. We use "exit" to refer to these jump or call instruction that are at the end of a block, and each exit has an unique *exit ID*, and the destination of an exit is refer to as *branch target*.

Block linking can be either *proactive* or *lazy*. Proactive block linking links translated basic blocks whenever a new block is generated. A lazy block linking links translated basic blocks when a context switch occurs.

We choose lazy block linking for two reasons. First, lazy block linking links translated basic blocks only when the execution actually goes from one block to another. Second, when a new block is generated, proactive block linking must update the branch targets of all exits that go to the newly generated block, therefore we need a data structure that maps branch address of exits to the starting address of translated basic blocks. In contrast lazy block linking does not require this extra data structure, and will not incur extra maintenance overheads. Further comparisons between proactive and lazy block linkings can be found in [8, 39].

We implement block linking as follows. Before an execution thread leaves a block it stores the exit ID of the block in a specified thread-private memory location. Then the emulation engine locates the translated basic block pointed by the branch target, retrieves the exit ID that we just stored, then uses this exit ID to look into

FIGURE 2.5: Illustration of execution steps of block linking optimization.

an *exit-id-to-address* mapping table that maps exit id to the address of an exit in code cache.

The entries of exit-id-to-address table is added when LLVM JIT generates host instructions for exits. Then the emulation engine will be able to patch the branch target of the exit of the block the execution thread just left. Please refer to Figure 2.5 for an illustration of our implementation.

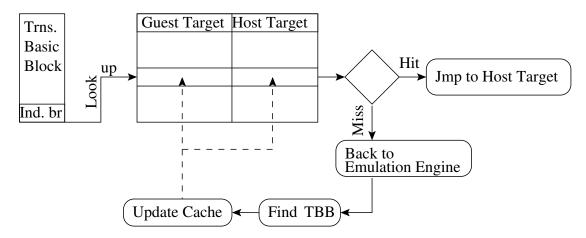

#### 2.2.2 Indirect Branch Target Caching

To further reduce the context switches, We use the indirect branch target caching (IBTC) to fast look up whether the target of the indirect branch has a translated basic block in code cache without returning to emulation engine. We add a IBTC lookup function calls at the ends of those blocks that end with indirect jumps and indirect calls instructions.

The IBTC contains a *shared cache* as shown in Figure 2.6. The shared cache is implemented as a direct-access hash table with 1K entry to cache all indirect

branches. The hash table is indexed by the last 10 bits of the guest target address. Given a guest target address, we use the last 10 bits as the key to index the shared cache. If the comparison successes, the control then transfers to the memory location of the translated basic block. Otherwise, the control transfers back to the emulation engine, and updates the shared cache after locating the TBB.

20

FIGURE 2.6: Illustration of execution steps of indirect branch target caching optimization.

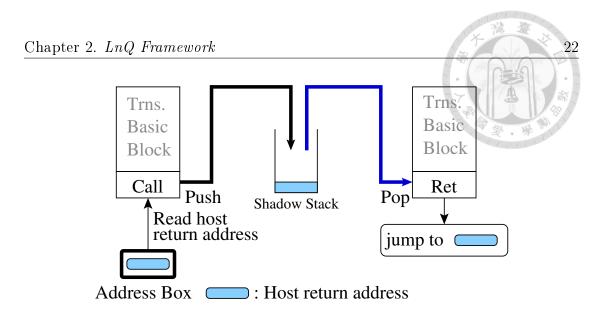

#### 2.2.3 Shadow Stack

Shadow stack (SS) optimizes function return mechanism in binary translation, and was first introduced in FX!32 [14]. Despite that a function return instruction can be viewed as an indirect branch, it can be optimized without indirect branch cache lookup. This is because the guest return address is known when the translator translates a guest call instruction since the call pushes the guest return address onto the stack.

If the translated basic block of the guest return address exists in code cache, the translator can push the memory location of the translated basic block onto a

ress when the funct

21

shadow stack, from which we can fetch the host return address when the function ends without looking up indirect branch cache or going back to emulation engine. However, if the block of the guest return address is not translated, we push the address that goes back to emulation engine.

The details of our implement of shadow stack are as follow. We assign a memory location, called *address box*, to each guest call instruction, which stores either the host return address or the return address back to emulation engine. If the guest return address does not yet have its translated basic block in code cache, we marks the address box as untranslated and stores the return address back to emulation engine in the address box. Then, when the translator generates a translated basic block, it checks whether there is a address box that should store the address of this translated block but is marked untranslated. If such address box is found, the translator marks the address box. For each guest call instruction, we insert instructions to push the content of its address box on top of the shadow stack. Please refer to Figure 2.7 as an illustration.

As for each guest return instruction, we insert pop shadow stack instructions in the end of the translated block. Note that we need to perform a check to see whether the guest return address is matched to the one stored on top of the shadow stack. If they are matched, the execution directly transfers to the address that is popped from the shadow stack. If the addresses are not matched, we flush the shadow stack since the shadow stack is no longer valid, and the execution transfers back to the emulation engine.

FIGURE 2.7: Illustration of execution steps of shadow stack optimization.

### 2.3 Performance Evaluation

We conduct experiments to evaluate LnQ by building an x86-to-x86\_64 dynamic binary translator with the LnQ framework. We use QEMU version 0.13.0 as the emulation engine module, and use LLVM version 2.8 to implement the translation module.

LnQ uses an LLVM class MCDisassembler to disassemble x86 machine instructions. We use X86GenDisassemblerTables.inc to generate the prototypes of translation functions and the instruction property table. We also use template functions to speedup the implementation of translation functions. For example, we use the add() template function to implement variations of add instructions for different types of parameters. We have implemented all instructions needed by SPEC CPU 2006.

We modified the LLVM library slightly to meet the needs of the emulation module. We instruct the register allocator not to use a specified host register which holds

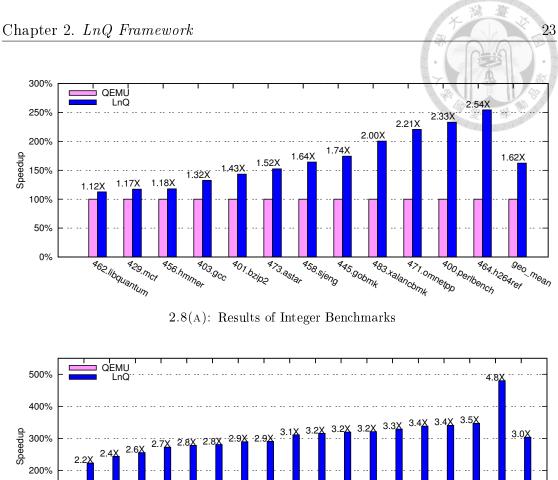

2.8(B): Results of Floating Point Benchmarks

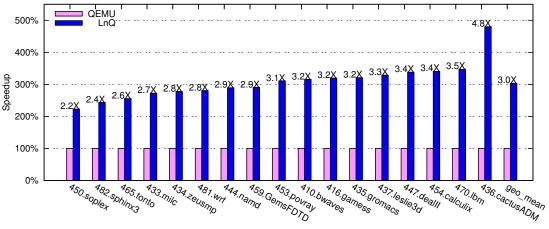

FIGURE 2.8: Speedup factors of LnQ in of SPEC CPU2006 compared with QEMU.

the base memory address of the guest CPU state. This is important because a dynamic binary translator needs one host register to hold the base address of the guest CPU state during the execution. For example, QEMU uses r14 as the CPU state register in x86\_64 host machine. If the register allocator allocates r14 register, the content of r14 will be overwritten and the application will crash.

101

24

We use the default optimization option provided by LLVM Just-In-Time compiler. The optimization level invoked by this default option is equivalent to GCC "-O2".

# 2.3.1 Experiment Settings

Our experiments were conducted on an Intel Core2 CPU 975 @ 3.33GH machine with 12GB of memory. The operating system is 64 bit Gentoo distribution Linux. We use SPEC CPU 2006 as our benchmarks. All benchmarks are compiled with GCC 4.3.4 with "-O2 -m32" flags.

We run all benchmarks via the standard SPEC *runspec* script with configuration files. We run each benchmark three times with reference inputs and take the average as the experiment result. We compare the performance of our LnQ with QEMU 0.13.0.

# 2.3.2 Performance of LnQ

We first compare the runtime performance of LnQ with QEMU. The results are shown in Figure 2.8 where Figure 2.8(a) shows results of integer benchmarks and Figure 2.8(b) shows results of floating point benchmarks. The Y-axis is speedup factor of running time of LnQ compared with QEMU.

As shown in Figure 2.8(a), the speedup factors range from 1.12X to 2.54X, and LnQ is 1.62 times faster than QEMU on average for integer benchmarks. The speedup factors improve significantly in floating benchmarks. For SPEC CFP 2006 benchmarks, the geometric mean of speedup factors is 3.02X compared to QEMU. The speedup factors range from 2.24X to 4.8X.

25

The main reason of this significant improvement is due to insufficient translation ability of QEMU. The QEMU translator, called Tiny Code Generator (TCG), does not support floating point operations yet [40]. As a result TCG translates all floating point instructions into helper function calls. On the other hand, the LLVM backend used in LnQ could generate host floating point instructions directly, and hence we gains much performance improvement than QEMU.

# 2.3.3 Performance of LLVM Just-In-Time Compiler

In this section, we evaluate the performance of LLVM Just-In-Time (JIT) compiler used in LnQ. As described in Section 2.1.4, the total running time of a dynamic binary translator can be divided into three portions: the dispatch time, the translation time and the execution time spent in code cache. Therefore, in the following two sections, we first evaluate the execution time spent in code cache, and then we evaluate the translation time of LLVM JIT.

Note that, for the sake of simplicity of presentation, we list only results of representative subset of SPEC 2006 as suggested in [41] in following experiments. We, however, still show the geometric means derived from all benchmarks of SPEC CINT 2006 and SPEC CFP 2006.

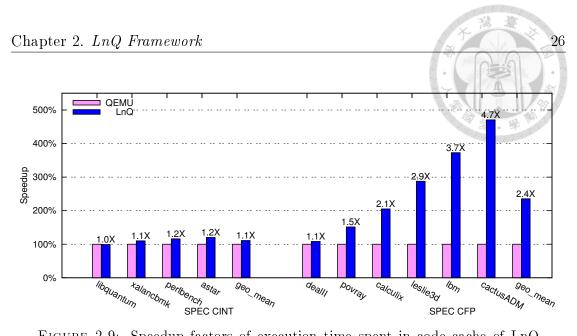

FIGURE 2.9: Speedup factors of execution time spent in code cache of LnQ compared to QEMU. The numbers above bars are

#### 2.3.3.1 Execution Time Spent in Code Cache

We begin by evaluating the execution time of LnQ and QEMU. To be a fair comparison, we turn off all the runtime optimizations used in LnQ and QEMU. We turn off Block Linking, IBTC, and Shadow Stack in LnQ, and Block Linking in QEMU, which is only runtime optimization in QEMU. We profile the execution time by insert timing function before entering code cache and after exiting code cache. The results are shown in Figure 2.9.

From Figure 2.9, we see the execution time spent in code cache of LnQ improves about 10% in integer benchmarks and about 135% in floating point benchmarks. The significant improvement of floating point benchmarks is again contributed by translation ability of LLVM JIT as explained in previous section. The improvement of translation quality in integer benchmarks is not as expected. Thus, the major improvement of integer benchmarks shown in Figure 2.8 can be contributed

|                        |                    |        |       |             |        | C     |

|------------------------|--------------------|--------|-------|-------------|--------|-------|

| Benchmarks             |                    | Blocks |       | LnQ         | QEMU 🔔 |       |

|                        |                    | DIOCKS | Total | Translation | Total  | Trns. |

|                        | perlbench          | 57592  | 1819  | 54.8 (3.0%) | 4240   | 0.22  |

| $\left  \right\rangle$ | libquantum         | 2801   | 1825  | 3.0 (0.2%)  | 2051   | 0.01  |

| CINT                   | astar              | 7970   | 1180  | 11.8 (0.7%) | 1798   | 0.04  |

| H                      | xalancbmk          | 29065  | 1208  | 27.6(2.3%)  | 2421   | 0.12  |

|                        | geo. mean of trns. |        |       | .16%        |        | 0%    |

| CFP                    | leslie3d           | 6074   | 3147  | 10.6 (0.2%) | 10344  | 0.03  |

|                        | calculix           | 14992  | 9871  | 18.6 (0.2%) | 33622  | 0.09  |

|                        | cuctusADM          | 9295   | 5650  | 10.6 (0.2%) | 27114  | 0.04  |

|                        | dealII             | 14976  | 2017  | 16.5 (0.8%) | 6814   | 0.07  |

|                        | lbm                | 2594   | 2834  | 2.9(0.1%)   | 9841   | 0.01  |

|                        | povray             | 12434  | 1644  | 14.9 (0.9%) | 5111   | 0.05  |

|                        | geo. mean of trns. |        |       | 0.35%       |        | 0%    |

TABLE 2.1: Translation overheads of LnQ and QEMU. The number of guest basic blocks, and total running time and translation time in seconds are listed for each benchmarks. The numbers in parentheses are the percentages of translation time versus total running time.

by runtime optimizations, which we further investigate the effects of runtime optimizations in Section 2.3.4.

### 2.3.3.2 Translation Overhead

We now evaluate the translation overhead of LnQ. Table 2.1 compares the numbers of blocks translated in all benchmarks, the translation time, and the translation time percentage (in parentheses) of LnQ and QEMU. First, the translation time of LnQ is approximate 1.16% and 0.35% for integer and floating point benchmarks, respectively. It is worth for long running guest applications although the translation time of LnQ is slower than QEMU. For example, it takes 54.8 seconds to translate **perlbench** but saves 1819 seconds in running time compared to QEMU. However, the translation overheads of LnQ may become intolerable for small jobs. For example, the translation overhead of 403.gcc benchmark is 28% of total running time in average. This is due to that there are large number of guest basic blocks, about 60,000, in 403.gcc benchmark, and the running time is not long enough to compensate the translation overhead. We have not addressed this problem in current LnQ framework. In future work, we may adopt two phase translation approach similar to IA-32 EL [16] into LnQ framework.

28

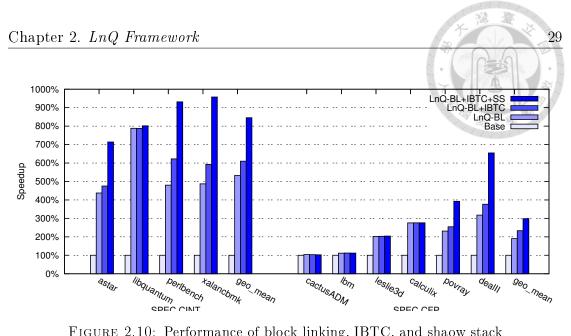

# 2.3.4 Optimization Effects of Runtime Optimization

We further investigate the effects of each runtime optimization techniques – Block Linking (BL), IBTC, and Shaow Stack (SS). We use LnQ without any runtime optimization as our baseline. We then evaluate the effect of each optimization by adding one optimization at a time in the order of Block Linking, IBTC, and Shadow Stack. Note that it is reasonable to present the optimization effects with BL, BL+IBTC, and BL+IBTC+SS combinations because these three optimizations aim at different cases as described in Section 2.2. The results are shown in Figure 2.10.

From Figure 2.10, the improvements of runtime optimizations are significant in integer benchmarks. We calculate the improvement by subtracting the speedup factor of each optimization combination with its previous one. The average improvements are 432%, 78%, and 236% for Block Linking, IBTC, and Shadow Stack, respectively. These significant improvements of integer benchmarks are because the integer benchmarks tend to have more complicated control flow than floating point benchmarks. The average improvements of runtime optimizations in floating

28

FIGURE 2.10: Performance of block linking, IBTC, and shaow stack

benchmarks are 90%, 43%, and 66% for Block Linking, IBTC, and Shadow Stack respectively.

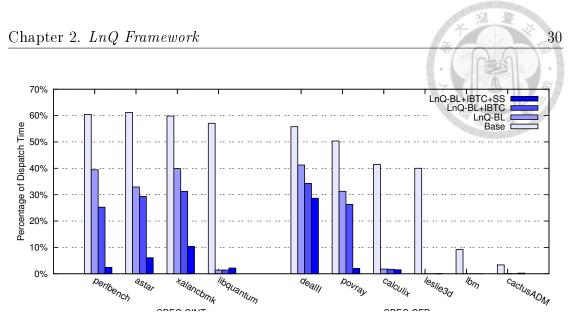

Because the purpose of these optimizations is to reduce the frequency of going back to emulation engine, we further investigate the effects of each optimizations by showing the reduction of percentages of dispatch time. The results are shown in Figure 2.11.

In Figure 2.11, we can see most benchmarks are benefit from Block Linking optimization, which explains the 432% improvement of Block Linking. As for IBTC optimization, only benchmarks using indirect branches have performance gain from IBTC optimization. For example, astar, libquantum, calculix, leslie3d, 1bm and cactusADM have less improvement from IBTC. Shadow Stack also improves most benchmarks.

Two additional notes, the first is although the dispatch time of some floating point

FIGURE 2.11: The reduction of percentage of dispatch time.

benchmarks are reduced dramatically, the improvements may not be that significant. This is because the dispatch time is not major part of total running time. For example, There are little dispatch time in cactusADM and lbm benchmarks. Section, the optimizations also improve the temporal locality of LnQ in that most program execution are in code cache.

# 2.3.5 Slowdown of LnQ Compared to Native Run

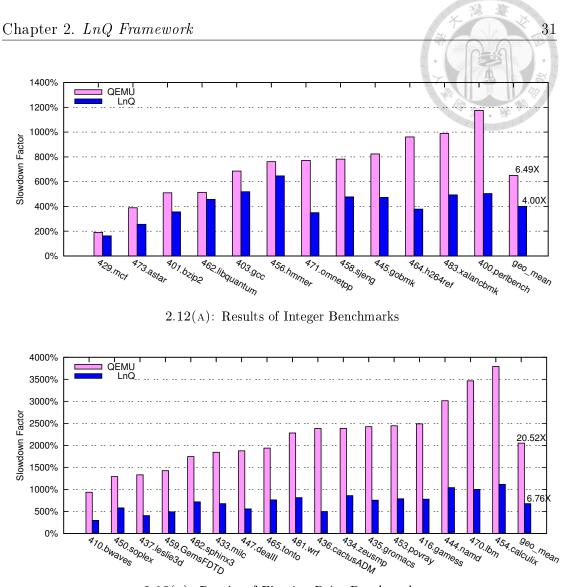

In the last experiment, we examine the slowdown factors of LnQ compared to the native runs. For native runs, we compile SPEC benchmarks only with the "-O2" option without the "-m32" option. The results are shown in Figure 2.12.

From Figure 2.12, the geometric means of slowdown factors in SPEC CINT2006 are 4.00X and 6.49X in LnQ and QEMU, respectively. The slowdown factors increase in SPEC CFP2006, which are 6.76X and 20.52X in LnQ and QEMU. The slowdown factors of floating point benchmarks are larger than those of integer

2.12(B): Results of Floating Point Benchmarks

FIGURE 2.12: The slowdown of LnQ and QEMU compared with native run.

benchmarks because the floating point operations in x86 architecture are stacklike operations, in which LnQ cannot perform register mapping for floating point registers. Results in Figure 2.12 shows that there is room for improvement fro dynamic binary translates.

FIGURE 2.13: Performance of ARM-to-I32 LnQ

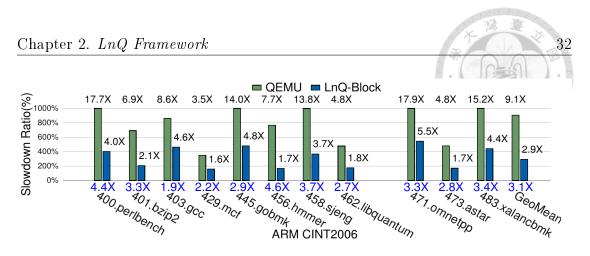

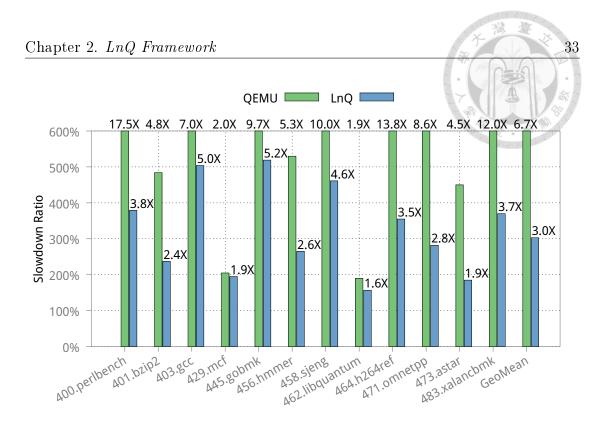

# 2.3.6 Performance of ARM-to-IA32 LnQ

In this section, we compare the performance of ARM-to-x86\_64 LnQ to QEMU.Results are shown in Figure 2.13. On average, LnQ has 2.9X slowdown compared to native run. Compared to QEMU's 8.1X slowdown, LnQ outperforms QEMU about 3.1X.

# 2.3.7 Performance of IA32-to-ARM LnQ

In this section, we compare the performance of IA32-to-ARM LnQ to QEMU. We conduct experiments on the Odroid-XU board with ARM Cortex-A15 1.7GHz dual core CPU and 2GB memory. Results are shown in Figure 2.14. On average, LnQ has 3X slowdown compared to native run. Compared to QEMU's 6.7X slowdown, LnQ outperforms QEMU about 2.23X. The results also show LnQ do keep its high performance in different host CPUs.

FIGURE 2.14: Performance of IA32-to-ARM LnQ

# 2.4 Concluding Remarks

This chapter introduces the LnQ (LLVM+QEMU) framework by which one can build high performance and retargetable dynamic binary translators with *existing* optimizers and code generation backends. In this chapter, we explain the design and implementation of LnQ framework. We use LLVM compiler infrastructure to design the IR library and the IR translator in the translation module. We also describe how to build IR library and the translation process of the IR translator. We also show how we perform register mapping and retargetable runtime optimizations in the IR translator.

We evaluate the performance of LnQ by building an x86-to-x86\_64 dynamic binary translator with LnQ framework. The experimental results show 1.62X speedup for

SPEC CINT2006 and 3.02X speedup for SPEC CFP2006 in average compared to QEMU. The translation overhead of LnQ is 1.16% of total running time. Also, the ARM-to-x86\_64 LnQ has 3.1X speedup compared to QEMU, and the IA32-to-ARM LnQ has 2.23X speedup compared to QEMU.

34

# Chapter 3

# The Early-Exit Guided Code Region Formation

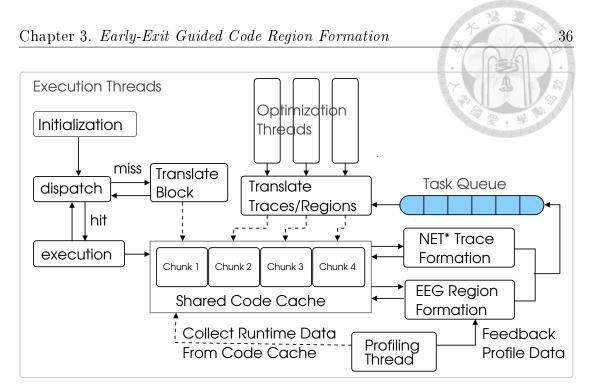

# 3.1 Region-Based Multi-threaded Dynamic Binary Translator

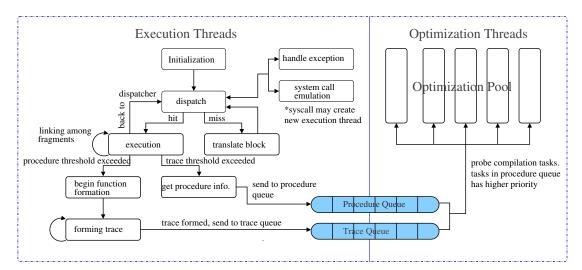

In this section, we describe the design of our region-based multi-threaded dynamic binary translator, called LnQ [42]. We have implemented the EEG scheme in LnQ. LnQ uses QEMU [37] as the front-end emulation engine, and uses LLVM [38] compilation infrastructure to handle its back-end code optimization and target code generation. We implement our EEG scheme using this framework. Figure 3.1 shows the major components and the control flow of our region-based multi-threaded dynamic binary translator.

FIGURE 3.1: Control flow of execution threads and optimization threads

We use *code segments* to refer *basic blocks* and *traces/regions*, and use *code fragment* to refer a *translated* code segment by DBT. Therefore, there are *basic block fragments* and *trace/region fragments*. Each code fragment has a *prologue* to load the guest architecture states, such as the content of the guest registers, from the memory to the host registers before execution. Also, each code fragment has an epilogue to store modified machine states back to memory before leaving the code fragment. Each code fragment has its own register mapping decided by the LLVM register allocator.

LnQ uses execution threads and optimization threads. Execution threads are responsible for translating basic blocks and executing translated code fragments. That is, if an execution thread reaches a new guest basic block during execution, the execution thread generates a basic block fragment using LLVM. Optimization threads generate optimized traces and regions fragments also using LLVM. Execution threads compile blocks with "O0" optimization level to minimize compilation overhead. On the other hand, optimization threads compile traces and regions with "O2" to generate optimized code. All execution threads share one software code cache. As shown in Figure 3.1, we partition the code cache into *sections*, and each thread has its own section to store the translated code fragments so that threads can generate code concurrently.

37

The DBT system separates trace compilation from program execution. By running optimization threads concurrently on other cores, the execution threads are not disrupted. Execution threads may create region compilation tasks and send them to a *Task Queue* (see Figure 3.1) when traces or regions are formed as described in Section 3.2. We use a lock-free concurrent FIFO queue [43] to implement the *task queue* so that execution threads can insert trace/region compilation tasks into the queue while the optimization threads take those tasks from the queue without locks.

When an optimization thread generates a new trace or region, it dispatch execution threads to the newly generated code fragment by *atomically* patching jump instructions in the code cache. To do this in IA32, we need to align the patched instructions to 4-byte alignment, and use the self-branch technique mentioned in [44] to patch jumps atomically.

# 3.2 Early Exit Index and Early-Exit Guided Region Formation

In this section, we first describe the NET algorithm used in our system. We then define an *early exit index* to quantify how often early exits are taken in a trace. Finally we describe our early exit guided region formation technique.

38

# 3.2.1 Trace Formation Algorithm

We adopt a modified NET algorithm called  $NET^*$ , which is similar to [30], to builds traces. The difference is that NET<sup>\*</sup> considers *all* basic blocks as *potential* trace head candidates, while NET only considers blocks which are targets of backward branches as *trace head* candidates in that they may form potential loops.

The NET<sup>\*</sup> algorithm has two advantages. First, the NET algorithm [7] was designed for DBT systems in which a *single* DBT thread is responsible for both execution and trace building. To reduce the overhead of building traces, NET needs to be very selective in potential traces. In contrast, NET<sup>\*</sup> can take advantage of modern multi-core platforms to offload the overhead of building traces. Hence, it can afford to try all basic blocks as potential trace heads.

Second, NET may not identify all loops by only considering targets of backward branches. By considering all basic blocks as possible trace heads, NET\* can discover more hot traces than NET can. As reported in Section 3.3.1.1, NET\* achieves 12% and 5% performance improvement on average over NET for SPEC CINT2006 and CFP2006 benchmarks, respectively.

Our NET<sup>\*</sup> algorithm works as follows. We instrument software counters to record the number of times each block is executed. A block becomes a *trace head* when the number of times the block has been executed exceeds a threshold value. NET<sup>\*</sup> forms a trace by appending blocks along the execution path until one of the following terminal conditions is met: (1) A branch to the trace head is taken, (2) The number of blocks exceeds a threshold, (3) The next block is the head of another trace, or (4) A guest system call instruction is encountered.

39

# 3.2.2 Early Exit Index

We first define an *early exit* of a trace. A trace can be a straight-line execution path or a cycle. If a trace is a straight-line path, then all exit edges along the path are early exits except the exit edge of the last basic block in the trace. If a trace is a cycle, all exit edges are early exit.

We define an *Early-Exit Index* (EEI) to measure the frequency of early exits taken in traces. More specifically, EEI is the number of early exits being taken for every million instructions executed in traces. It can be formally defined as in the following equation.

$$EEI = \frac{\sum_{i \in \Gamma} n_i \times \rho_i}{N}$$

where  $\Gamma$  is the set of traces,  $n_i$  is the number of times early exits being taken in trace i,  $\rho_i$  is the percentage of instructions executed in trace i, and N is the number of million instructions executed.

# 3.2.3 Early-Exit Guided Region Formation

In this section, we describe our proposed Early-Exit Guided (EEG) region formation scheme. It detects and merges regions that have frequently taken early exits. The key issues in EEG are (1) how to efficiently detect delinquent regions; and (2) when to merge them at runtime. We address them as follows.

40

The simplest approach to address the first issue is to instrument counters in all traces and regions. However, this approach is inefficient and may merge too many regions that are not frequently executed. Instead, we use a dynamic profiling approach with the help of on-chip hardware performance monitor (HPM) to select hot regions.

We create a profiling thread called *profiler* at the beginning of execution to perform dynamic profiling. The profiler collects program counters periodically for every million instructions retired. When a threshold number of samples are collected, the profiler accumulates the sample counts for each trace to determine the degree of *hotness* of each trace. The hotness of a trace is measured by the following equation.

$$H_T = \max\{\alpha, \beta\}$$

Here,  $\alpha$  is the percentage of instructions executed in the trace during the *last* sampling period, and  $\beta$  is the percentage of instructions executed in the trace during the *entire* execution. Intuitively,  $\alpha$  represents the hotness of the trace

during the last period, and  $\beta$  represents the accumulated *hotness* during the entire execution. We choose the maximum of  $\alpha$  and  $\beta$  as its hotness measure.

41

When the hotness of a trace exceeds a threshold, we start monitoring the trace by instrumenting counters to its early exits. Currently, we only monitor the early exits of conditional branches. If a counter exceeds a pre-defined threshold, it means the control leaves the region through the corresponding early exit very frequently. Then, we merge the monitored region with the target region of the early exit. We translate and optimize the merged region with our LLVM-based DBT, and replace the monitored region with the merged region.

We argue that the overhead of the instrumentation is negligible because early exits should be rarely taken. A frequently taken early exit would have triggered region formation when the counter exceeded the threshold.

# 3.2.4 Spill Index of a Region

The benefits of EEG region formation come from eliminating the overhead caused by frequently taken early exits, and potential optimization opportunities from a larger code region. Despite the fact that we can mostly eliminate the overhead of frequently taken early exits via region merging, we may not always have potential optimization opportunities from the merged region. In particular, if the quality of the translated code of a region is not good enough, it is not beneficial to merge such a region.

We define an index, called *Spill Index*, to assess the quality of the code generated by the LLVM compiler for a region formed by the EEG technique. A *spill instruction*

is an instruction for load/store operations between registers and stack. The *Spill Index* is the percentage of spill instructions in the translated code fragment. When the Spill Index of a code fragment exceeds a threshold, that region should not be further merged because a high percentage of spill instructions often forestalls good performance due to improper register allocation of the LLVM compiler.

42

# 3.2.5 Region Versus Trace

By creating larger regions, we reduce the amount of specialization that the compiler can do for traces. As we know, the benefit of traces comes from the instruction scheduling within traces [45].

However, we need to limit the instruction scheduling optimizations when we compile traces in dynamic binary translation, because we have to rematerialize full guest state in case a hardware exception or a signal was raised.

The main advantage of EEG region formation is that it can improve DBT performance by removing transition overhead among traces, such as removing redundant loads/stores of guest state among traces.

We use Figure 3.2 as an example to illustrate our region formation strategy. Figure 3.2(a) is the control flow graph (CFG) of a hot region in a guest application. During execution, each block is first translated as shown in Figure 3.2(b). Then NET\* forms three traces as in Figure 3.2(c). Trace A would be the first selected for early exit detection (see Figure 3.2(c)) since a loop is likely to become hot. Thus the early exit of A, marked by a dashed arrow from the trace started with

FIGURE 3.2: Illustration of region formation.

A (enclosed by the dotted rectangular) to the trace started with B, is monitored with an instrumented software counter.

We merge Trace A and Trace B to form a code region when the early exit is taken frequently. A code region, called Region A and is enclosed in the dotted rectangular in Figure 3.2(d), that consists of traces A and B is formed. After the code fragment of Region A is formed, we replace Trace A and Trace B with Region A so that Trace F now branches to Region A rather than to Trace A. Note that Region A will not be monitored because the spill index of Region A exceeds the threshold.

# 3.3 Performance Evaluation

In this section, we evaluate the performance of Early-Exit-Guided region formation algorithm in our LLVM-based parallel DBT systems. We start by describing our measurement methodology.