國立臺灣大學電機資訊學院電信工程學研究所

## 碩士論文

Graduate Institute of Communication Engineering College of Electrical Engineering and Computer Science National Taiwan University Master Thesis

毫米波頻段放大器及功率放大器之共模穩定性研究

Research of Amplifiers and Common-mode Stability of Power Amplifiers at Millimeter-wave Frequencies

莊博翔

## **Po-Hsiang Chuang**

指導教授: 王暉 博士

Advisor: Huei Wang, Ph.D.

中華民國107年12月

December 2018

#### 致謝

隨著論文的完成,我即將完成碩士學位,研究所生涯也將告一段落。首先,我要感謝我的指 導教授,王暉老師。一路以來對我無私的幫助,無論是在學術領域的研究上給予建議、方向,以 及寶貴的經驗,或是在問題解決上給予的指導與鼓勵,都使我有所成長。感謝林坤佑老師,在計 畫上的領導及幫助,以及給予我研究上的幫助,讓我解決許多問題。感謝蔡作敏老師、蔡政翰老 師,無論是在計畫上,以及研究上給予我無私的幫助及建議。同時,感謝天文所的章朝盛博士、 翁守賢博士及郭岳芳博士在研究上的幫助,以及提供天文所的量測環境,使研究能更加完整。感 謝口試委員們,黃天偉教授、林坤佑教授、蔡作敏教授、及蔡政翰教授所提供的建議,使得此碩 士論文能得以更加完整。

在研究所生涯中,學長姊、同學,以及學弟們的幫助,讓我有所成長也得以解決許多的問題。 博士班的學長姊中,感謝林毓軒學長、蕭元鴻學長、吳依靜學姊、陳俊年學長、王云杉學長、張 立奇學長、葉光聖學長、高堃堯學長、鄭人豪學長、吳茗航學長、林宜賢學長、林文傑學長,以 及鐘杰穎學長。碩士班的學長姊中,感謝周正峯學長、張育銓學長、陳柏羽學長、周昱廷學姊、 能繼康學長、林弘皓學長、吳振緯學長、王俊凱學長、區逸群學長、陳泓翰學長、許峰毓學長, 以及黃炫又學長。

碩士班同學中,感謝容麟、政宇、彥志、飛飛、碩軒、騰遠、宗瑾、俊名、紹庭,以及展鳴。 碩士班學弟中,感謝潁、洋、煒程、子兼、智尹、凱皇、柏澤、岱宥、彥廷、旻憲,以及武震。

最後,謝謝我摯愛的人們。謝謝家人的支持與鼓勵,謝謝夥伴及朋友們的陪伴,讓我得以順 利完成碩士學位。

博翔 2018.12.31

i

### 中文摘要

本論文介紹一個製作於砷化鎵假型高速電子場效電晶體製程之低雜訊放大器、一個製作 於互補式金屬氧化物半導體製程之開闢鍵控調變器,以及一個製作於互補式金屬氧化物半導 體製程之功率放大器。

首先為一個應用於第五代行動通訊之Q頻段低雜訊放大器以0.15 微米砷化鎵假型高速電 子場效電晶體製程設計與製作,此低雜訊放大器採用三級共源級的架構,第一共源級採用源 級衰退技術以達到均衡的雜訊及增益表現,而第二、三共源級則是採用 RC 回授技術以達到 寬頻表現,另外,放大器第三級前後之匹配網路採用 π型匹配網路以達到寬頻的阻抗匹配。 在第一次實驗結果後,電晶體模型不準確導致量測與模擬結果的不一致,在進一步討論與分 析後提出模擬上的修正方法,修改晶片設計後再藉由第二次晶片製作及實驗結果驗證所提修 正方法之正確性。此低雜訊放大器放大器達到優異的 3-dB 頻寬(24.7 至 40.0 GHz)以及平均增 益(22.2 dB)表現,雜訊指數則在寬頻(27.9 至 40.0 GHz)下皆低於 3 dB。

之後描述一個應用於短距無線通訊之 60-GHz 頻段開關鍵控調變器以 90 奈米互補式金屬 氧化物半導體製程設計與製作,此調變器結合了發射機中調變以及輸出放大之功能,進而達 到在未來的應用上低複雜度與高效率的發射機架構。此調變器基於共源共柵架構,並採用在 此提出的一基於變壓器之回授技術,此技術能提升調變器「開」狀態下的增益及輸出功率表 現,以及「關」狀態下的隔離度表現,另外,為了降低基頻調變訊號輸入路徑上的 RC 常數 以減輕高速率傳輸下基頻調變訊號的失真,該路徑透過一串接電感及到地電容的設計以達到 所要目的。藉由採用基於變壓器之回授技術,此開關鍵控調變器於 60-GHz 達到優異的輸出 1-dB 功率壓縮點(7.0 dBm)、小訊號增益(10.2 dB)、以及「開-關」隔離度(45.4 dB)表現,在開 關鍵控調變上,此調變器能達到 10 Gb/s 之傳輸速率,由於變壓器所需的低佈局空間優勢,加 上僅需單一調變訊號輸入路徑,此調變器達到相當小的晶片佈局。

ii

最後則討論一個應用於短距無線通訊之 W 頻段功率放大器以 65 奈米互補式金屬氧化物 半導體製程設計與製作,藉由於輸出端採用一基於變壓器之放射對稱功率結構,以達到低損 耗及阻抗匹配上的不平衡,此二項參數皆在極高頻的功率放大器設計上有相當大的重要性。 在第一次實驗後於毫米波頻段發現非預期的振盪現象,在討論以及多方面的穩定性分析後判 斷為共模訊號下位於輸出級的不穩定現象,並提出針對輸出級前後採用的變壓器設計的電路 修改方法,在不影響差動訊號下之阻抗匹配情況的前提下,消除共模訊號下之不穩定現象, 經過在第二次晶片製作,實驗顯示非預期振盪之問題已解決,並驗證所提出修改方法的正確 性。另外,亦討論了用於極高頻功率放大器電路設計時的變壓器模型問題。

關鍵字 - 砷化鎵假型高速電子場效電晶體、第五代行動通訊、低雜訊放大器、寬頻、Q 頻段、 互補式金屬氧化物半導體、開闢鍵控調變、調變器、功率放大器、發射機、共栅共源、變壓 器回授、隔離度、60 GHz、V 頻段、功率結合結構、毫米波振盪現象、共源訊號不穩定現象、 W 頻段。

## ABSTRACT

The thesis presents a GaAs pHEMT low noise amplifier, a CMOS on-off keying modulator, and a CMOS power amplifier.

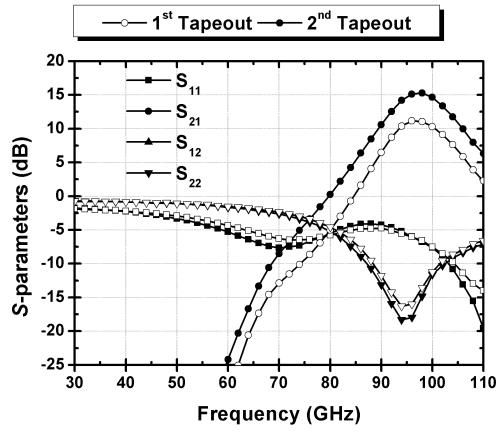

Firstly, a Q-band low noise amplifier for fifth-generation communication applications is designed and realized in 0.15- $\mu$ m GaAs pHEMT. The LNA consists of three common-source stages. Source degeneration is adopted at the first stage for a balanced noise and gain performance, and RC-feedback is adopted at the latter two stages for its wideband characteristics. In addition,  $\pi$ -type matching networks are used at the third stage for wideband impedance matching. Inaccurate device modeling caused disagreement between the measurement and simulation results of the original LNA. The modeling issues are discussed and analyzed, and corrections to the simulation setups are proposed and verified via the measurement results of a modified LNA in the second tape-out. The LNA exhibits wide 3-dB bandwidth from 24.7 to 40.0 GHz, with average gain of 22.2 dB. The noise figure is below 3 dB from 27.9 to 40.0 GHz, with average of 2.6 dB from 26 to 40 GHz.

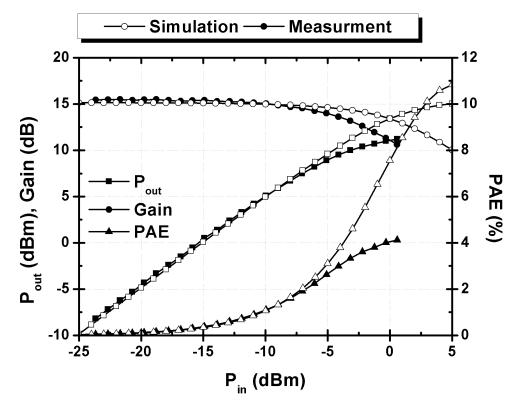

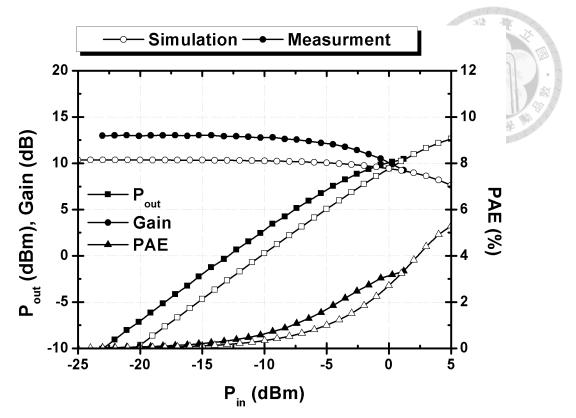

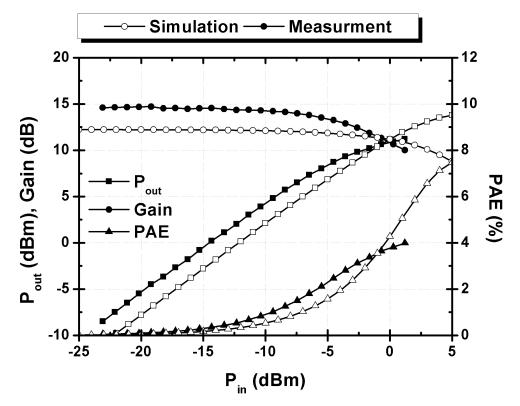

Secondly, a 60-GHz OOK modulator for short range wireless communications is designed and realized in 90-nm CMOS. By combining the functions of modulation and output amplification in a single circuit, a transmitter of lower complexity and higher efficiency can be achieved for future applications. A novel transformer-feedback technique is proposed for the cascode-based modulator for improvements in output power, gain performances at on-state, and isolation performance at off-state. A data input network is designed to achieve low RC time constant, and avoids distortion of the baseband data signal at high data rates. With the proposed transformer-feedback technique, the modulator achieves an  $OP_{1dB}$  of 7.0 dBm, gain of 10.2 dB, and on-off isolation of 45.4 dB at 60 GHz. For OOK modulation, data rates of up to 10 Gb/s have been measured. Due to the compact transformer and the single modulation path required, the modulator achieves a compact layout footprint of 471 x 519  $\mu$ m<sup>2</sup> with RF and DC pads included.

Finally, a W-band power amplifier is designed and realized in 65-nm CMOS. A transformer-based radial-symmetric power combining structure is adopted at the output for low insertion loss and matching imbalances, which are critical in PA designs at such high frequencies. Undesired oscillations at millimeter-wave frequency were observed during measurement of the original PA. Discussions and various stability analyses are performed to identify the issue as common-mode instabilities at the output stage. Modifications to the transformers at the output stage are proposed in order to eliminate the common-mode instabilities, without altering the impedance matching conditions in differential mode. The proposed modifications are verified through the absence of undesired oscillations during the measurement of a modified PA in the second tape-out. Modeling issues of high frequency transformer designs are also discussed.

Index Terms – GaAs pHEMT, fifth-generation (5G) communications, low noise amplifier, wideband, Q-band, CMOS, on-off keying (OOK), modulator, power amplifier, transmitter, cascode, transformer feedback, isolation, 60 GHz, V-band, power combining, millimeter-wave oscillation, common-mode instability, W-band.

| CONTENTS |

|----------|

|----------|

|           |         | CONTENTS                                                         |       |

|-----------|---------|------------------------------------------------------------------|-------|

| 口試委員審     | 寄定書     |                                                                  | #     |

| 致謝        |         |                                                                  | i     |

| 中文摘要      |         |                                                                  | ii    |

| ABSTRAC   | T       |                                                                  | iii   |

| CONTENT   | S       |                                                                  | vi    |

| LIST OF F | IGURE:  | S                                                                | ix    |

| LIST OF T | ABLES   |                                                                  | xxiii |

| Chapter 1 | Introd  | luction                                                          | 1     |

| 1.1       | Backg   | rounds and Motivations                                           | 1     |

| 1.2       | Literat | ture Surveys                                                     | 4     |

|           | 1.2.1   | Q-band LNA                                                       | 4     |

|           | 1.2.2   | 60-GHz OOK Modulator                                             | 6     |

|           | 1.2.3   | W-band PA                                                        | 7     |

| 1.3       | Contri  | butions                                                          | 9     |

|           | 1.3.1   | Q-band LNA in 0.15-µm GaAs pHEMT                                 | 9     |

|           | 1.3.2   | 60-GHz OOK Modulator in 90-nm CMOS                               | 10    |

|           | 1.3.3   | Common-mode stability of W-band PA in 65-nm CMOS                 | 11    |

| 1.4       | Thesis  | organization                                                     | 11    |

| Chapter 2 | A Q-l   | band Low Noise Amplifier for Fifth-Generation Wireless Communica | ation |

|           | Receiv  | ver Applications in 0.15-µm GaAs pHEMT                           | 13    |

| 2.1       | Introd  | uction                                                           | 13    |

| 2.2       | Circui  | t Design                                                         | 15    |

|           | 2.2.1   | Bias Condition and Device Selection                              | 15    |

|        | 2.2.2                                            | First Stage Design                                                                                                                                                                                                                                                                                                                                                                          | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 2.2.3                                            | Second and Third Stage Design with Wideband Performance                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.2.4                                            | 7 33 1014                                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.3    | Exper                                            | imental Results                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.4    | Discu                                            | ssion and Second Tape-out                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.4.1                                            | Modeling Issue of Device with Source Degeneration                                                                                                                                                                                                                                                                                                                                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.4.2                                            | Design Modification and Second Tape-out43                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.4.3                                            | Experimental Results                                                                                                                                                                                                                                                                                                                                                                        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.5    | Sumn                                             | nary47                                                                                                                                                                                                                                                                                                                                                                                      | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| pter 3 | 6 A 60                                           | -GHz On-Off Keying Modulator with Transformer Feedback for Shor                                                                                                                                                                                                                                                                                                                             | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | Rang                                             | e Wireless Communications in 90-nm CMOS51                                                                                                                                                                                                                                                                                                                                                   | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.1    | Introd                                           | uction                                                                                                                                                                                                                                                                                                                                                                                      | Ĺ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.2    | Trans                                            | former Feedback in Cascode-Based Circuits                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 3.2.1                                            | On-state                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 3.2.2                                            | Off-state                                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.3    | Circu                                            | it Design62                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 3.3.1                                            | Bias Condition and Device Selection                                                                                                                                                                                                                                                                                                                                                         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 3.3.2                                            | Transformer Design                                                                                                                                                                                                                                                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 3.3.3                                            | In/Output Matching and Baseband Data Input Network72                                                                                                                                                                                                                                                                                                                                        | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 3.3.4                                            | EM Simulation                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 3.3.5                                            | Simulation Results                                                                                                                                                                                                                                                                                                                                                                          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4    | Exper                                            | imental Results85                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 3.4.1                                            | On/Off-state Measurements                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 3.4.2                                            | Modulation Measurements                                                                                                                                                                                                                                                                                                                                                                     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.5    | Sumn                                             | nary                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.4<br>2.5<br><b>pter 3</b><br>3.1<br>3.2<br>3.3 | 2.2.3<br>2.2.4<br>2.3 Exper<br>2.4 Discu<br>2.4.1<br>2.4.2<br>2.4.3<br>2.5 Summ<br><b>pter 3 A 60</b><br><b>Rang</b><br>3.1 Introd<br>3.2 Trans<br>3.2.1<br>3.2.2<br>3.3 Circui<br>3.3.1<br>3.2.2<br>3.3 A 60<br><b>Rang</b><br>3.1<br>100<br>3.2<br>3.2<br>3.3<br>3.2.1<br>3.2.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.1<br>3.3.2<br>3.3.1<br>3.3.2<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5 | 2.2.3       Second and Third Stage Design with Wideband Performance       24         2.2.4       Simulation Results       28         2.3       Experimental Results       34         2.4       Discussion and Second Tape-out       38         2.4.1       Modeling Issue of Device with Source Degeneration       38         2.4.2       Design Modification and Second Tape-out       43         2.4.3       Experimental Results       45         2.5       Summary       47         pter 3       A 60-GHz On-Off Keying Modulator with Transformer Feedback for Short         Range Wireless Communications in 90-nm CMOS       51         3.1       Introduction       51         3.2       Transformer Feedback in Cascode-Based Circuits       58         3.2.1       On-state       58         3.3       Circuit Design       66         3.3.1       Bias Condition and Device Selection       62         3.3.4       EM Simulation       72         3.3.5       Simulation Results       73         3.4       EM Simulation       72         3.3.5       Simulation Results       73         3.4       EM Simulation       72         3.4.1       On/Off-state Measurements |

| Chapter 4 | A Stu  | dy on Common-mode stability of Millimeter-wave Power Am | olifiers using a |

|-----------|--------|---------------------------------------------------------|------------------|

|           | W-bai  | and Design in 65-nm CMOS Process                        |                  |

| 4.1       |        | luction                                                 |                  |

|           | 4.1.1  | Transformer-based Power Combining                       |                  |

| 4.2       | Circui | it Design                                               | 112              |

|           | 4.2.1  | Neutralization Technique                                | 112              |

|           | 4.2.2  | Device Selection and Output Stage Design                | 114              |

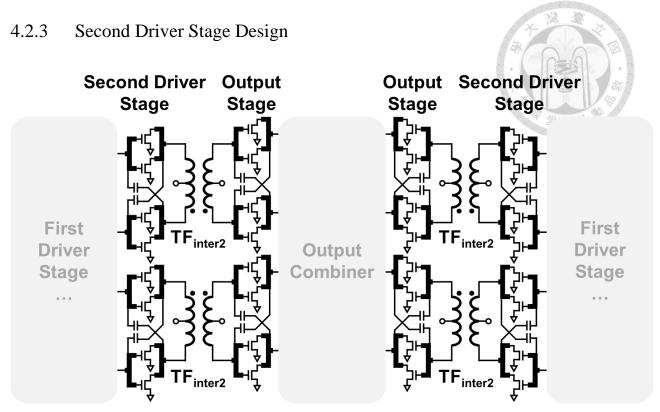

|           | 4.2.3  | Second Driver Stage Design                              | 123              |

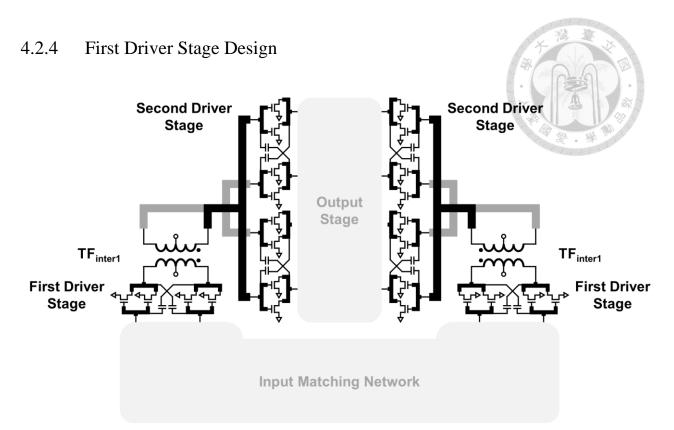

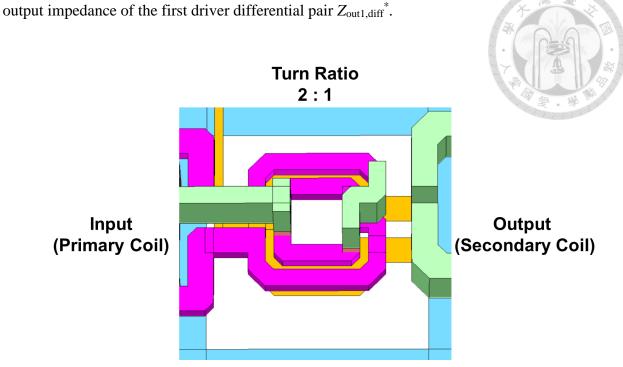

|           | 4.2.4  | First Driver Stage Design                               | 129              |

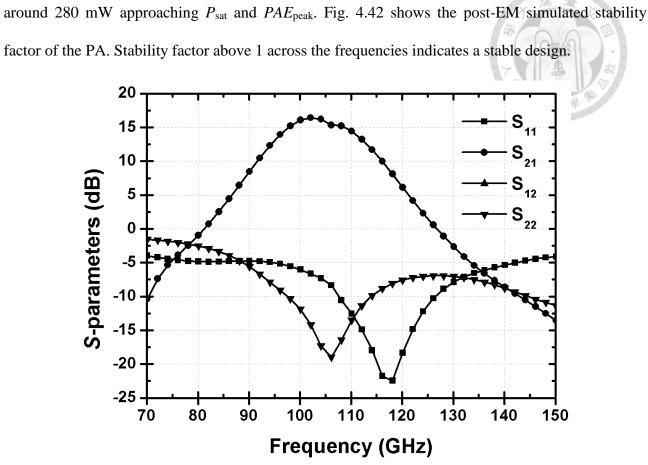

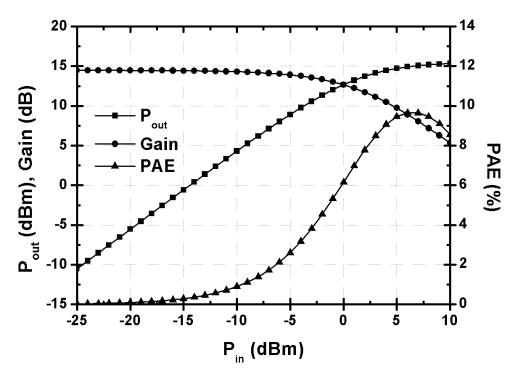

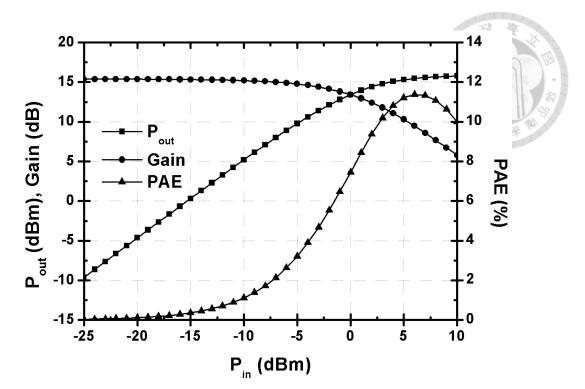

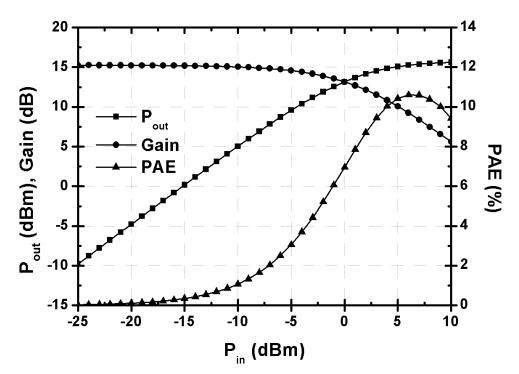

|           | 4.2.5  | Simulation Results                                      | 133              |

| 4.3       | Experi | rimental Results                                        |                  |

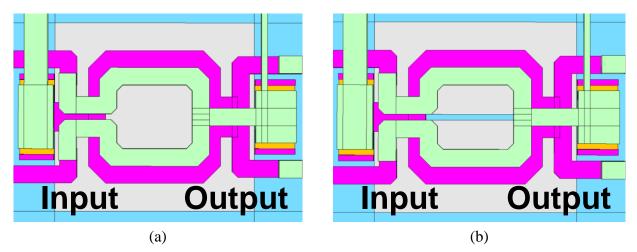

| 4.4       | Discus | ssion and Second Tape-out                               | 144              |

|           | 4.4.1  | Common-Mode Instability                                 | 144              |

|           | 4.4.2  | Design Modification                                     | 150              |

|           | 4.4.3  | Transformer Test Circuit                                | 163              |

|           | 4.4.4  | Experimental Results                                    | 164              |

| 4.5       | Summ   | nary                                                    | 174              |

| Chapter 5 | Concl  | lusions                                                 | 177              |

| REFEREN   | CES    |                                                         |                  |

## LIST OF FIGURES

<u>大</u> 湯

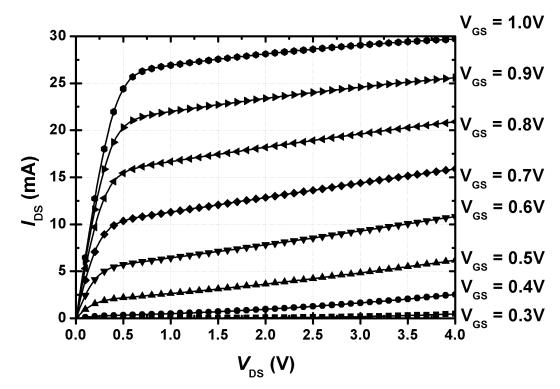

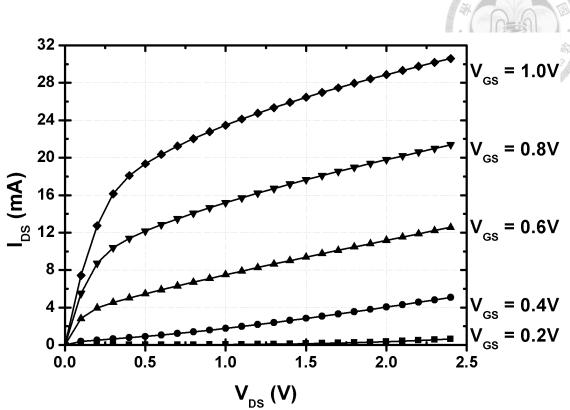

| Fig. 2.1.  | Simulated DC-IV curves of the device with gate periphery of 2f x 25 $\mu$ m                                     |

|------------|-----------------------------------------------------------------------------------------------------------------|

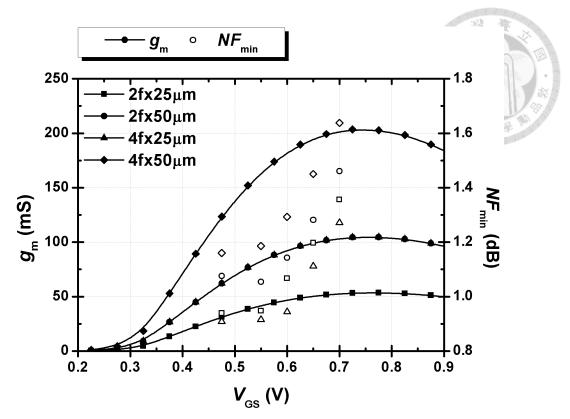

| Fig. 2.2.  | Simulated $g_m$ and $NF_{min}$ of the devices with different gate-periphery configurations                      |

|            | versus $V_{\rm GS}$ at $V_{\rm DS} = 2.0$ V                                                                     |

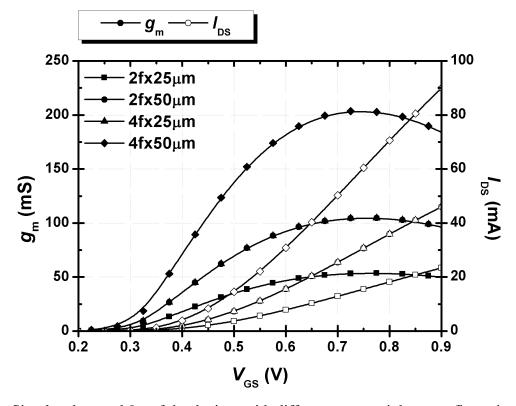

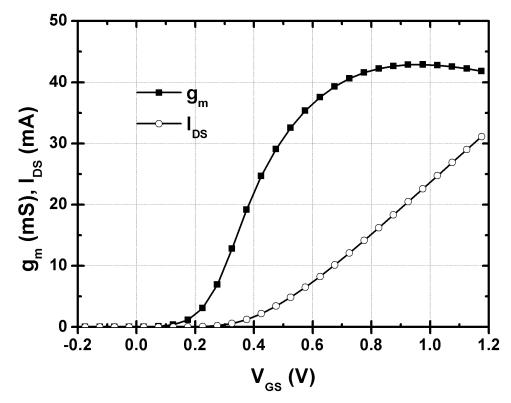

| Fig. 2.3.  | Simulated $g_{\rm m}$ and $I_{\rm DS}$ of the devices with different gate-periphery configurations versus       |

|            | $V_{\rm GS}$ at $V_{\rm DS} = 2.0$ V                                                                            |

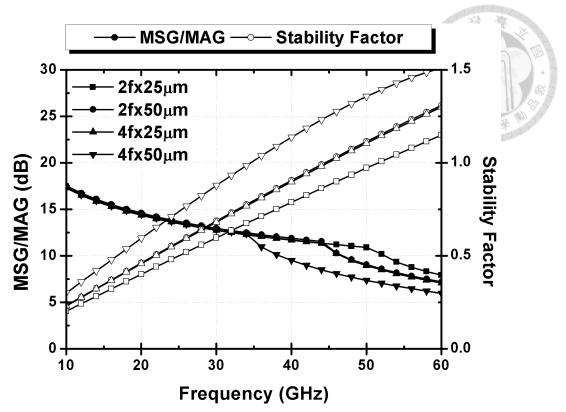

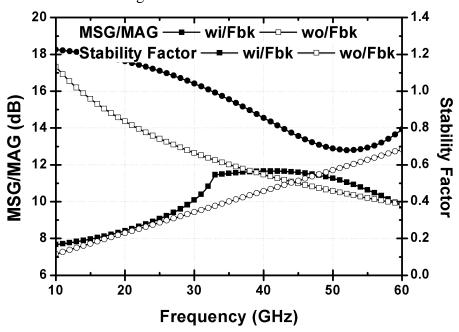

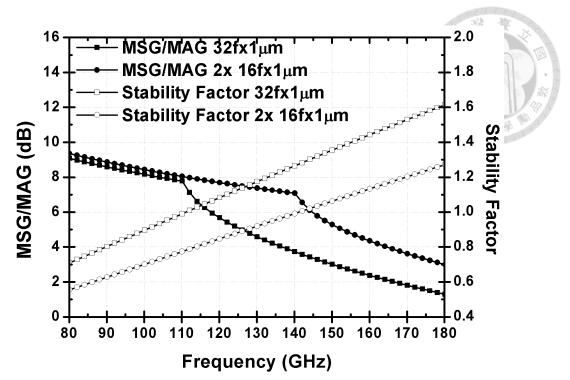

| Fig. 2.4.  | Simulated MSG/MAG and stability factor of the devices with different gate-periphery                             |

|            | configurations at $[V_{GS}, V_{DS}] = [0.6 \text{ V}, 2.0 \text{ V}].$                                          |

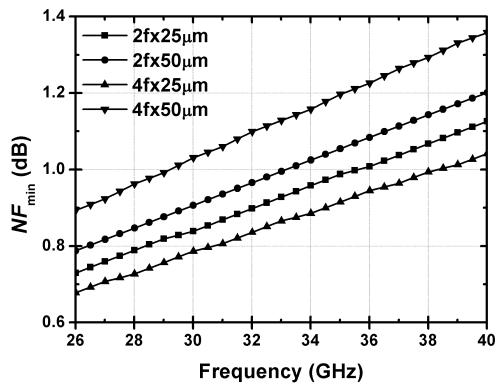

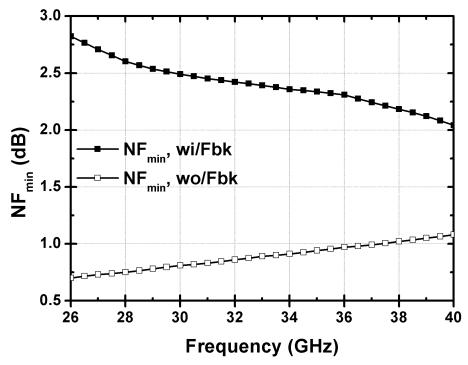

| Fig. 2.5.  | Simulated $NF_{min}$ of the devices with different gate-periphery configurations at [ $V_{GS}$ , $V_{DS}$ ]     |

|            | = [0.6 V, 2.0 V]                                                                                                |

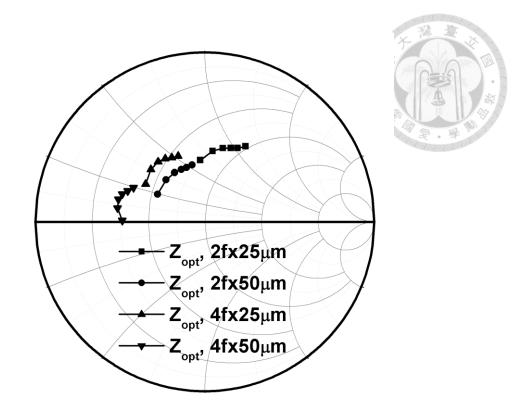

| Fig. 2.6.  | Simulated $Z_{opt}$ of the devices with different gate-periphery configurations at [ $V_{GS}$ , $V_{DS}$ ]      |

|            | = [0.6 V, 2.0 V]                                                                                                |

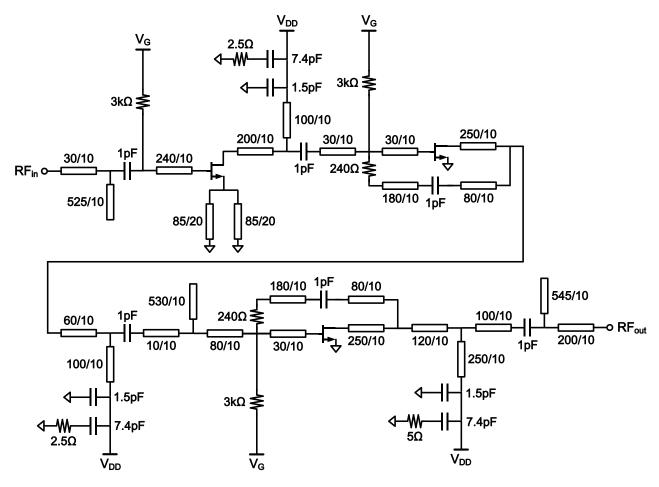

| Fig. 2.7.  | Schematic of the proposed Q-band LNA19                                                                          |

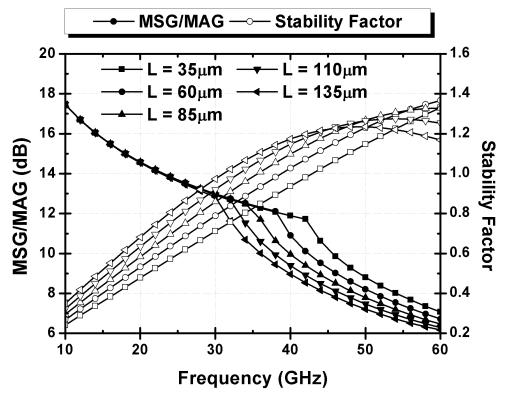

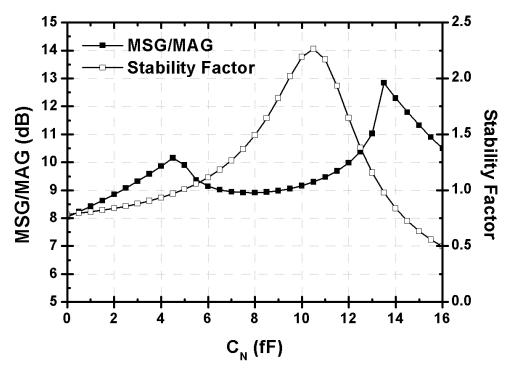

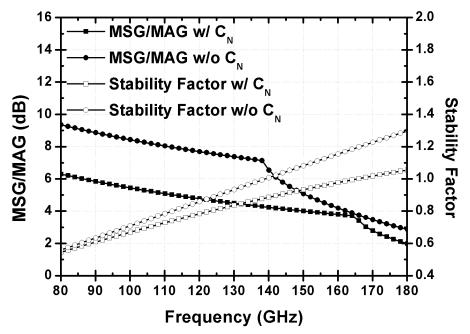

| Fig. 2.8.  | Simulated MSG/MAG and stability factor of the 2f x 25 $\mu m$ device with different                             |

|            | lengths of TL <sub>deg</sub> 's                                                                                 |

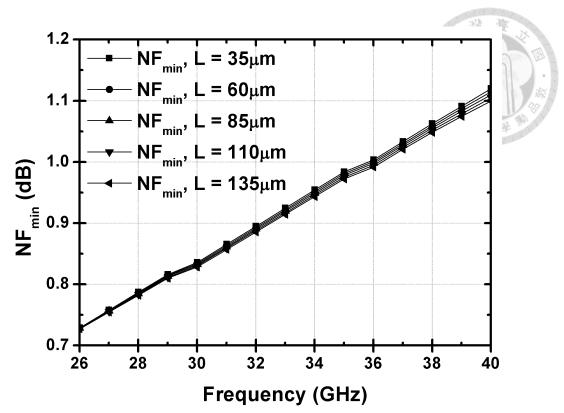

| Fig. 2.9.  | Simulated $NF_{min}$ of the 2f x 25 $\mu$ m device with different lengths of TL <sub>deg</sub> 's22             |

| Fig. 2.10. | Simulated $Z_{opt}$ and $Z_{in,conj}$ of the 2f x 25 µm device with different lengths of TL <sub>deg</sub> 's22 |

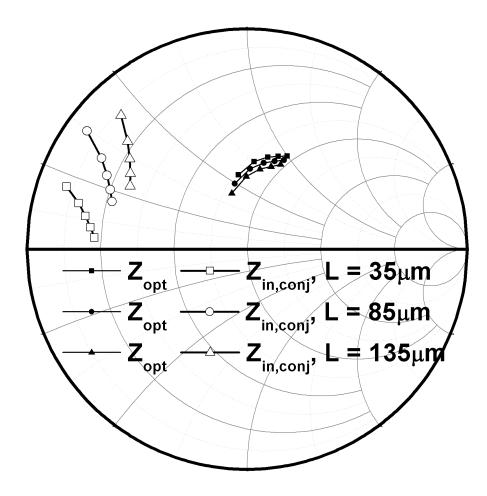

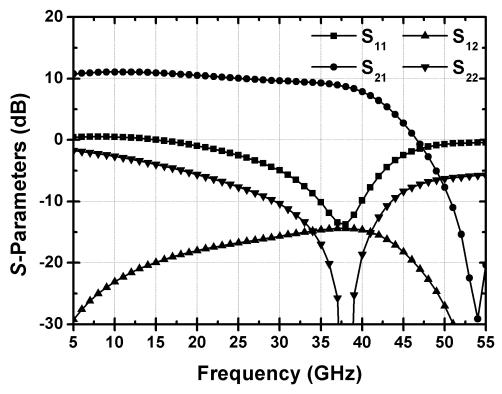

| Fig. 2.11. | Simulated S-parameters of the first stage complete with the input matching network23                            |

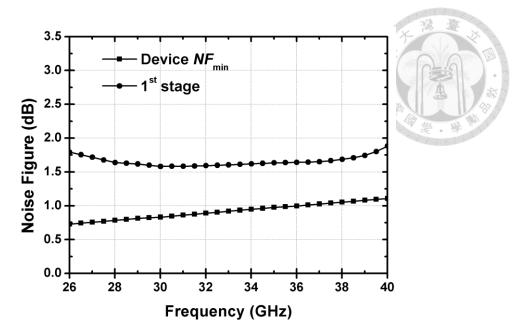

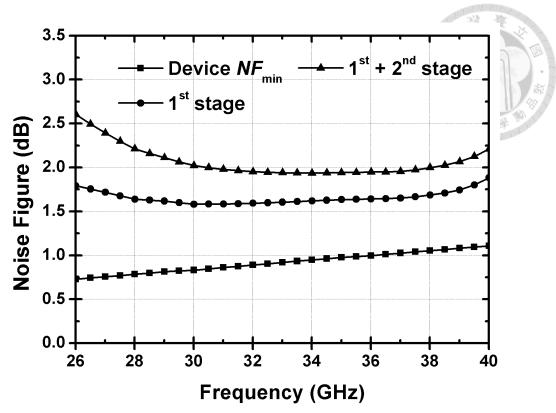

| Fig. 2.12. | Simulated noise figure of the first stage complete with the input matching network24                            |

| Fig. 2.13. | Simulated MSG/MAG and stability factor of the 2f x 25 $\mu m$ device with/without the                           |

|            | proposed RC-feedback25                                                                                          |

| Fig. 2.14. | Simulated $NF_{min}$ of the 2f x 25 µm device with/without the proposed RC-feedback25                           |

| Fig. 2.15. | Simulated S-parameters of the first and second stages complete with the input and                               |

|            | inter-stage matching networks                                                                                   |

| Fig. 2.16. | Simulated noise figure of the first and second stages complete with the input and             |

|------------|-----------------------------------------------------------------------------------------------|

|            | inter-stage matching networks                                                                 |

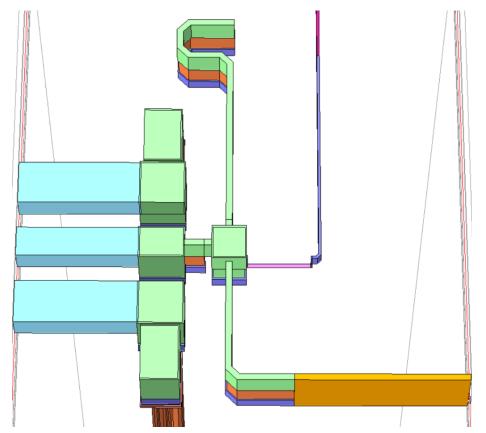

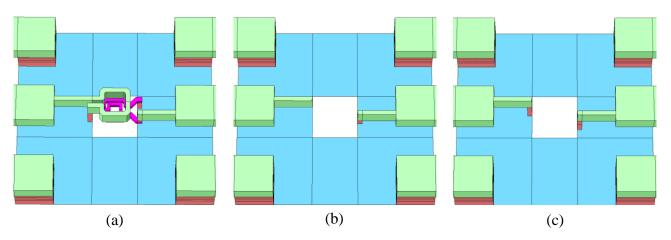

| Fig. 2.17. | 3-D rendering of the input matching network with the GSG RF pads used for EM                  |

|            | simulation                                                                                    |

| Fig. 2.19. | 3-D rendering of the inter-stage matching network between the second and third stages         |

|            | used for EM simulation                                                                        |

| Fig. 2.18. | 3-D rendering of the inter-stage matching network between the first and second stages         |

|            | used for EM simulation                                                                        |

| Fig. 2.20. | 3-D rendering of the output matching network with the GSG RF pads used for EM                 |

|            | simulation                                                                                    |

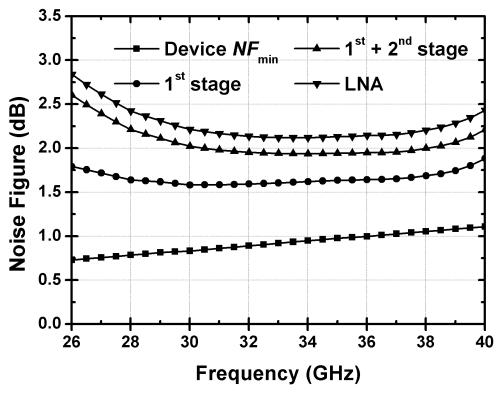

| Fig. 2.22. | Simulated noise figure of the proposed Q-band LNA                                             |

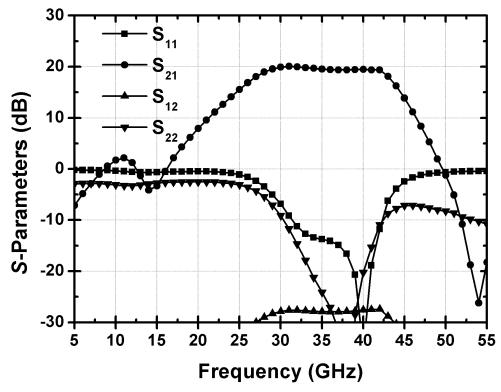

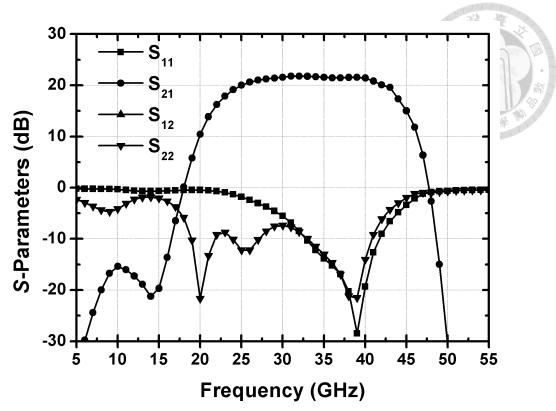

| Fig. 2.21. | Simulated S-parameters of the proposed Q-band LNA                                             |

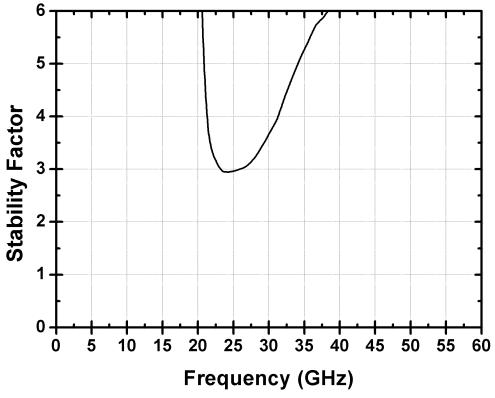

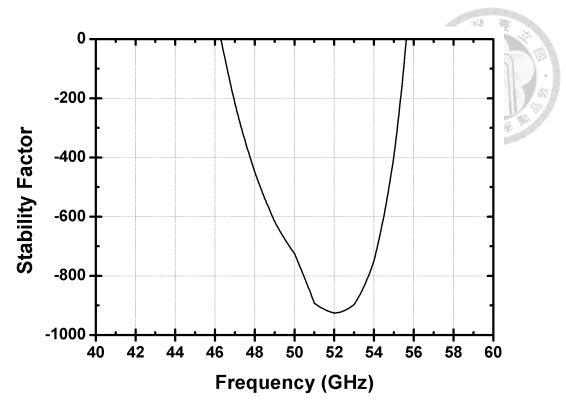

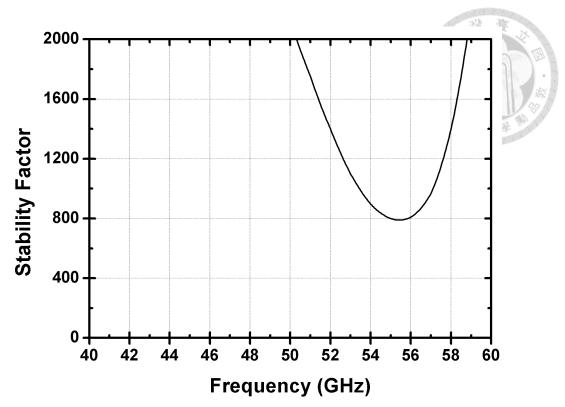

| Fig. 2.23. | Simulated stability factor of the proposed Q-band LNA                                         |

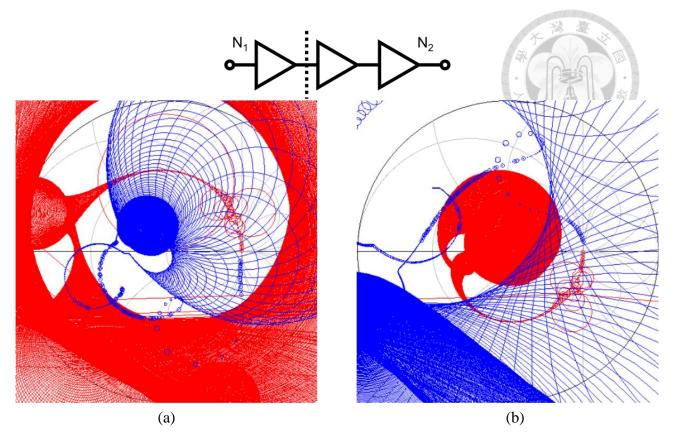

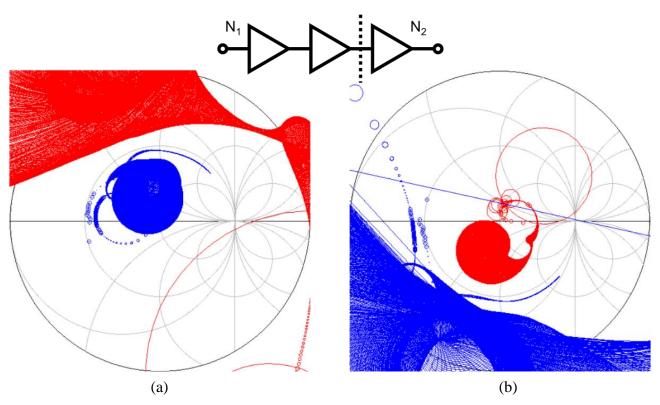

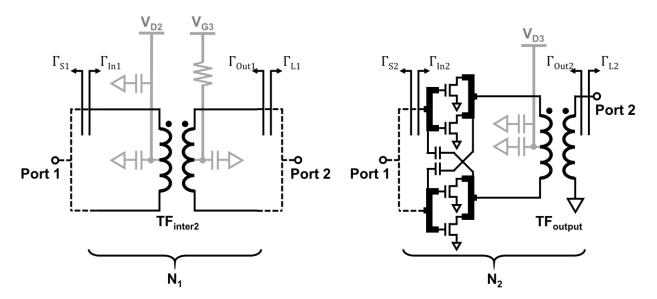

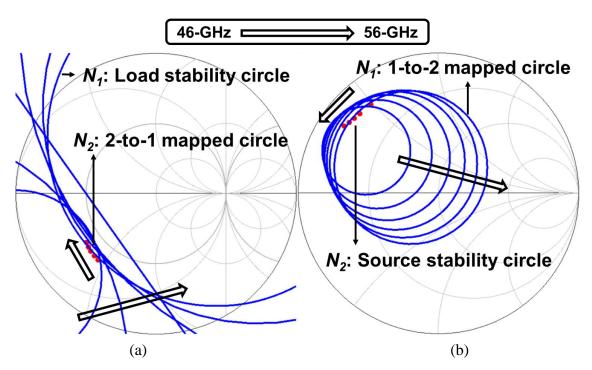

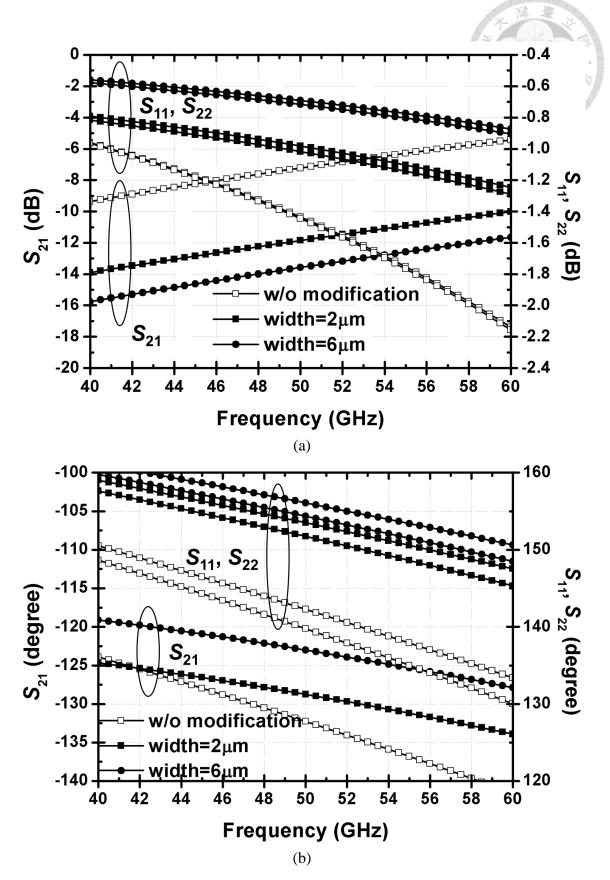

| Fig. 2.24. | Simulated inter-stage stability analyses between the first and second stages, with (a)        |

|            | load stability circles of $N_1$ compared with 2-to-1 mapped circles of $N_2$ , and (b) source |

|            | stability circles of $N_2$ compared with 1-to-2 mapped circles of $N_1$                       |

| Fig. 2.25. | Simulated inter-stage stability analyses between the second and third stages, with (a)        |

|            | load stability circles of $N_1$ compared with 2-to-1 mapped circles of $N_2$ , and (b) source |

|            | stability circles of $N_2$ compared with 1-to-2 mapped circles of $N_1$                       |

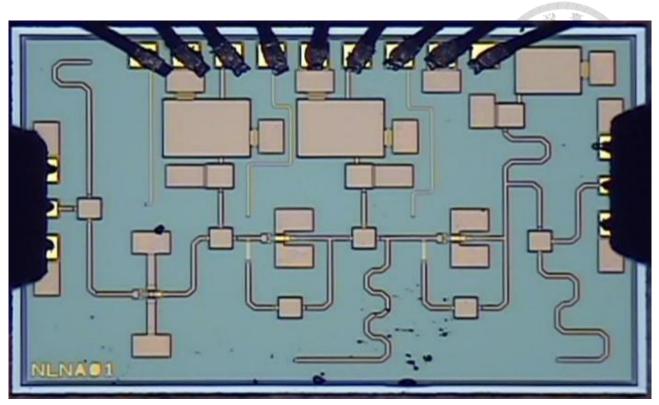

| Fig. 2.26. | Die photograph of the proposed Q-band LNA                                                     |

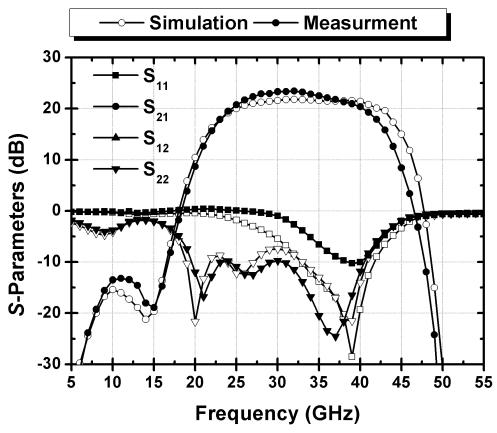

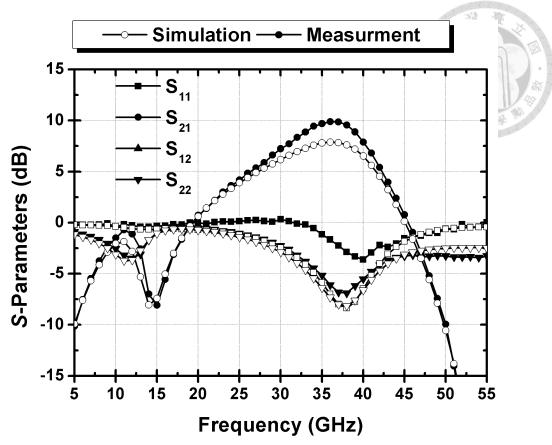

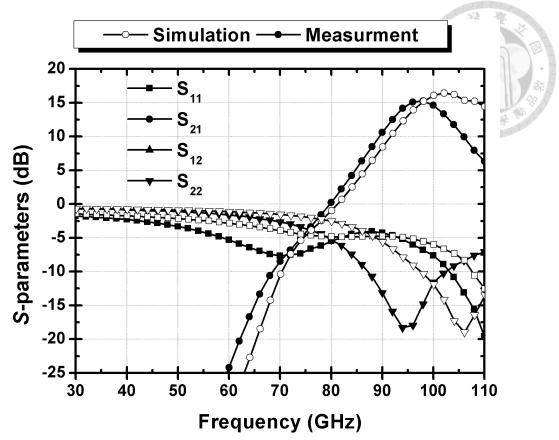

| Fig. 2.27. | Measured and simulated S-parameters of the proposed Q-band LNA35                              |

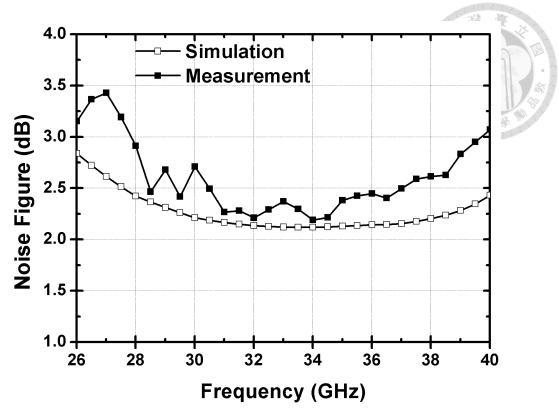

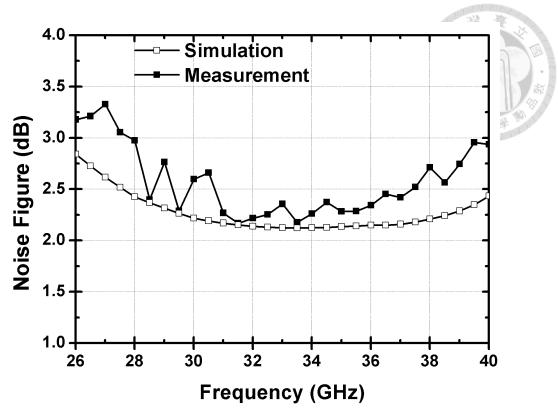

| Fig. 2.28. | Measured and simulated noise figure of the proposed Q-band LNA                                |

| Fig. 2.30. | Measured and simulated S-parameters of the third stage test circuit                           |

| Fig. 2.29. | Measured and simulated S-parameters of the first stage test circuit                           |

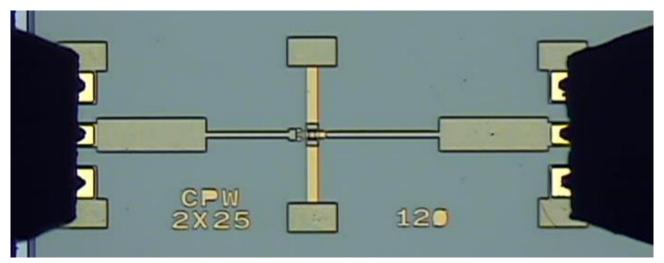

| Fig. 2.31. | Die photograph of the test-key for the 2f x 25 $\mu$ m CPW-configuration device with 85 x                            |

|------------|----------------------------------------------------------------------------------------------------------------------|

|            | 20 μm TL <sub>deg</sub> 's                                                                                           |

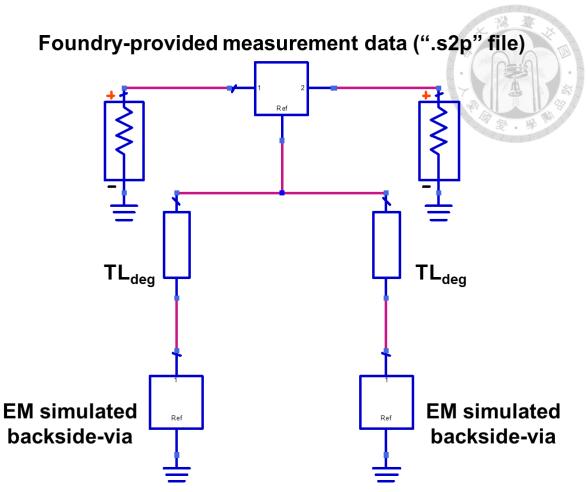

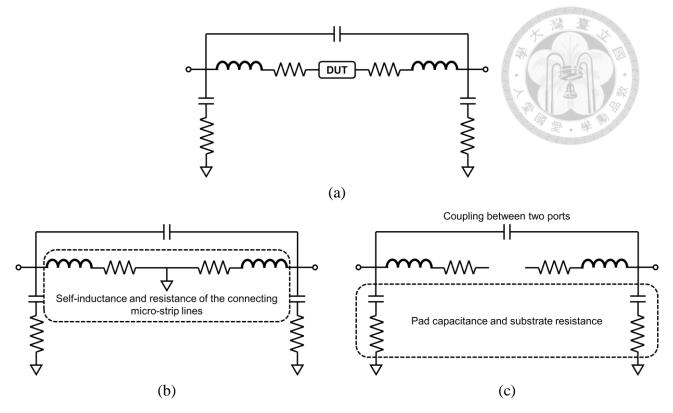

| Fig. 2.32. | Simulation setup for CPW-configuration devices with TL <sub>deg</sub> 's in Agilent ADS                              |

| Fig. 2.33. | Measured and simulated magnitudes (in dB) of the S-parameters of the 2f x 25 $\mu$ m                                 |

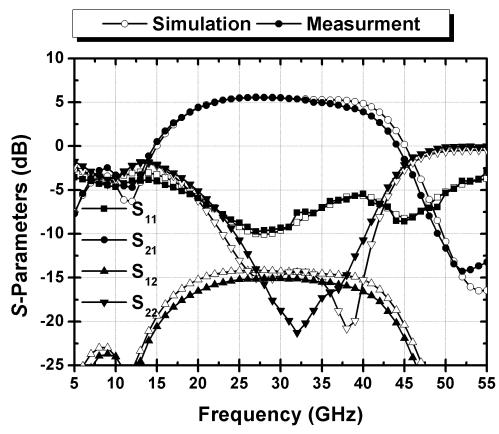

|            | CPW-configuration device with 85 x 20 $\mu$ m TL <sub>deg</sub> 's40                                                 |

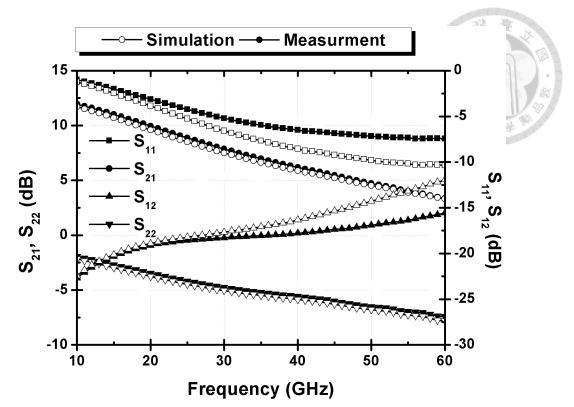

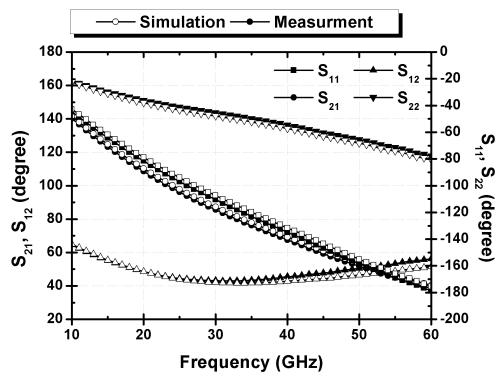

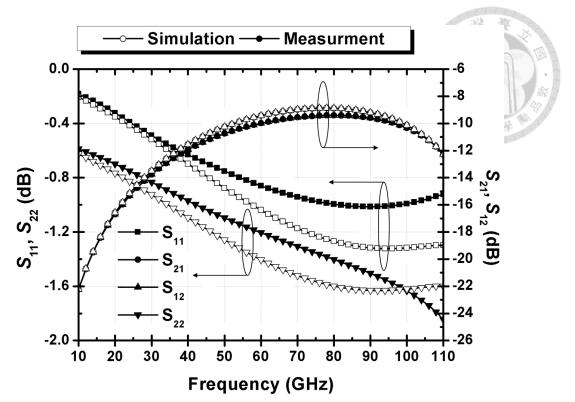

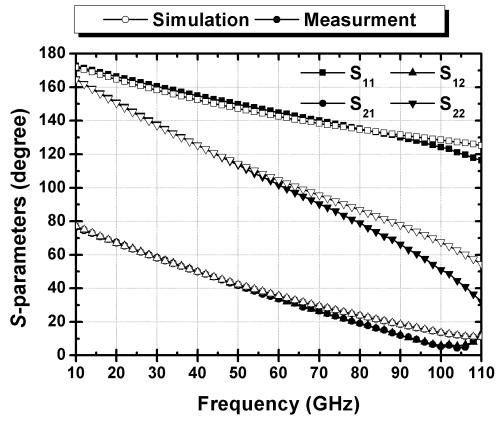

| Fig. 2.34. | Measured and simulated phases of the S-parameters of the 2f x 25 $\mu m$                                             |

|            | CPW-configuration device with 85 x 20 $\mu$ m TL <sub>deg</sub> 's40                                                 |

| Fig. 2.35. | Measured and simulated S-parameters of the proposed LNA. The measurement results                                     |

|            | of the test-key is used as the device at the first stage in the simulation, instead of the                           |

|            | foundry-provided measurement data41                                                                                  |

| Fig. 2.36. | Measured and simulated magnitudes (in dB) of the S-parameters of the 2f x 25 $\mu m$                                 |

|            | CPW-configuration device with 85 x 20 $\mu$ m TL <sub>deg</sub> 's. Length of the TL <sub>deg</sub> 's in simulation |

|            | is shortened by 60 μm to 25 μm42                                                                                     |

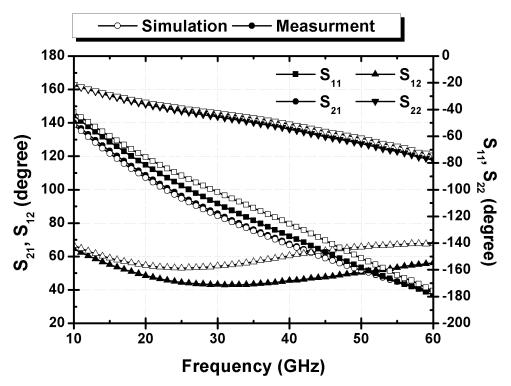

| Fig. 2.37. | Measured and simulated phases of the S-parameters of the 2f x 25 $\mu m$                                             |

|            | CPW-configuration device with 85 x 20 $\mu$ m TL <sub>deg</sub> 's. Length of the TL <sub>deg</sub> 's in simulation |

|            | is shortened by 60 μm to 25 μm42                                                                                     |

| Fig. 2.38. | Measured and simulated S-parameters of the proposed LNA, with the proposed                                           |

|            | correction applied in the simulation                                                                                 |

| Fig. 2.39. | Post-EM simulated S-parameters of the modified LNA with the proposed correction44                                    |

| Fig. 2.40. | Post-EM simulated noise figure of the modified LNA with the proposed correction44                                    |

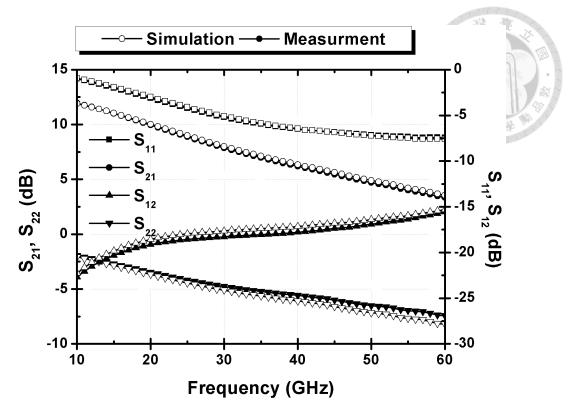

| Fig. 2.41. | Measured and simulated S-parameters of the modified LNA, with the proposed                                           |

|            | correction applied in the simulation                                                                                 |

| Fig. 2.42. | Measured and simulated noise figure of the modified LNA, with the proposed                                           |

|            | correction applied in the simulation47                                                                               |

xi

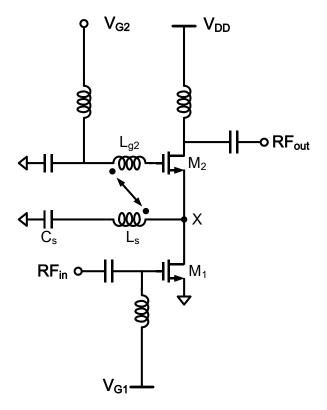

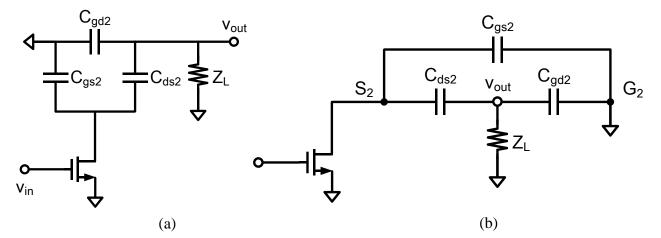

| Fig. 3.1.  | Schematic of the proposed cascode-based transformer feedback technique                             |

|------------|----------------------------------------------------------------------------------------------------|

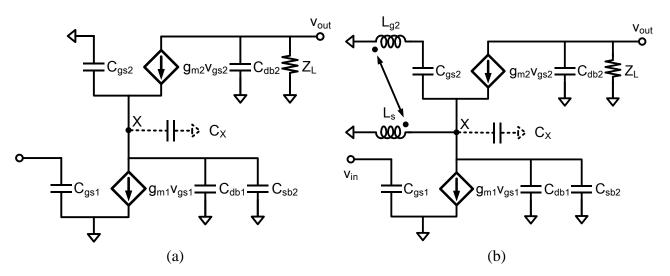

| Fig. 3.2.  | Small-signal equivalent circuit models of a cascode circuit at on-state (a) without and            |

|            | (b) with the proposed transformer feedback                                                         |

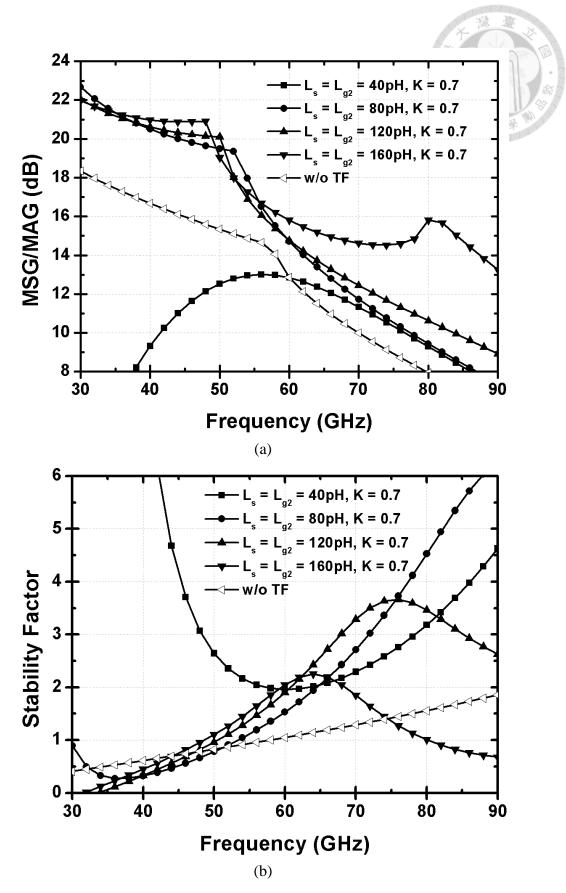

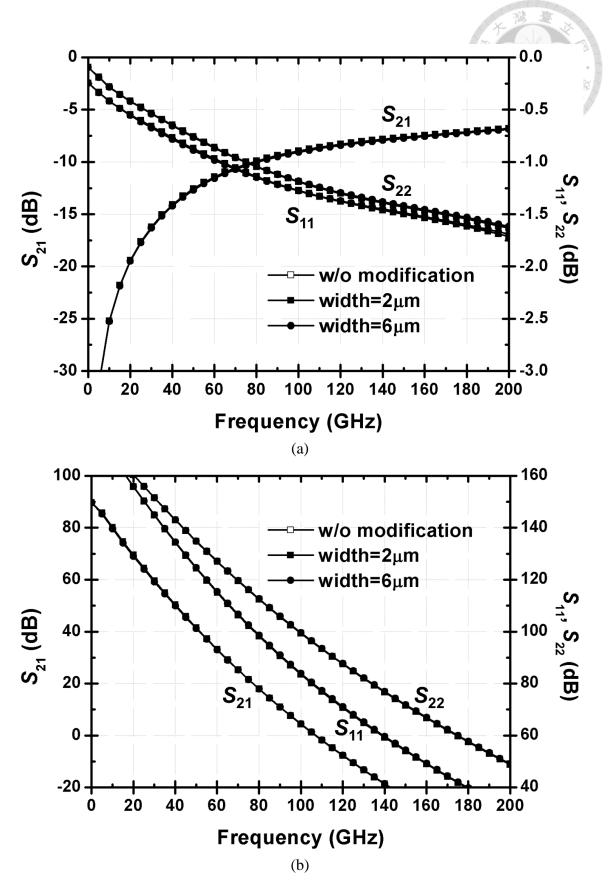

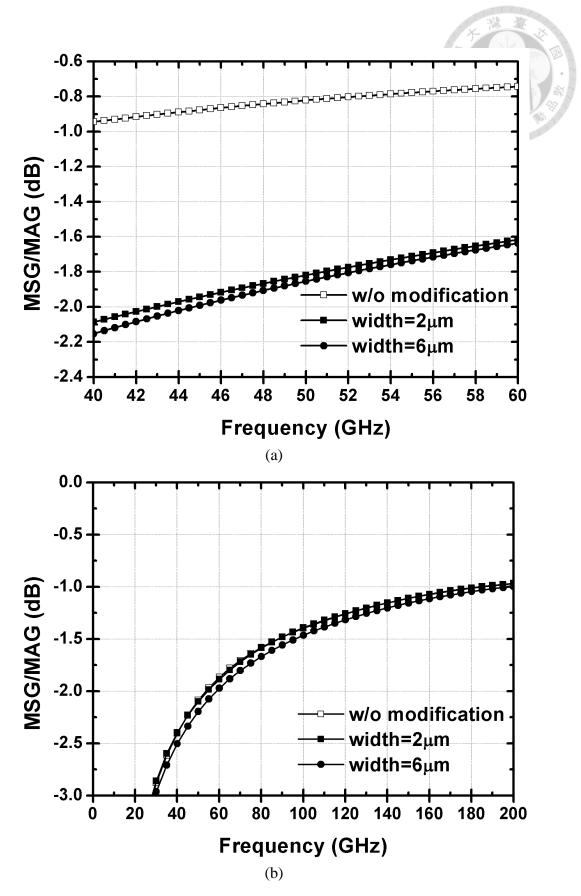

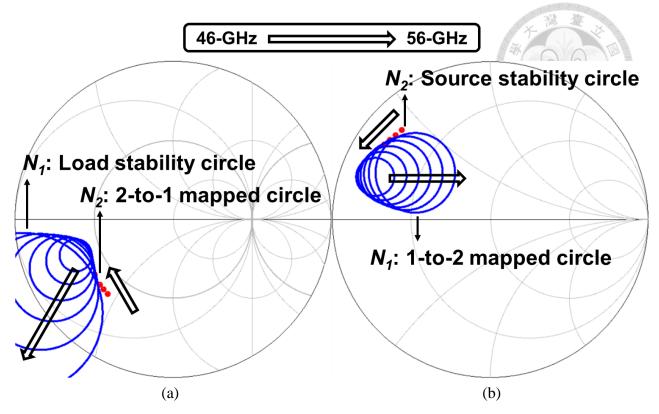

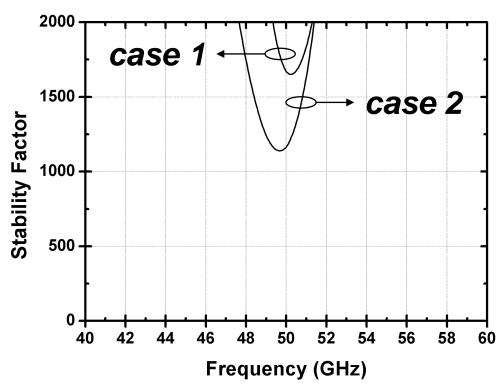

| Fig. 3.3.  | Simulated (a) MSG/MAG and (b) stability factor of the cascode circuit with different               |

|            | configurations of the transformer                                                                  |

| Fig. 3.4.  | Small-signal equivalent circuit models of a cascode structure at off-state                         |

| Fig. 3.5.  | Small-signal equivalent circuit model of a cascode structure at off-state with the                 |

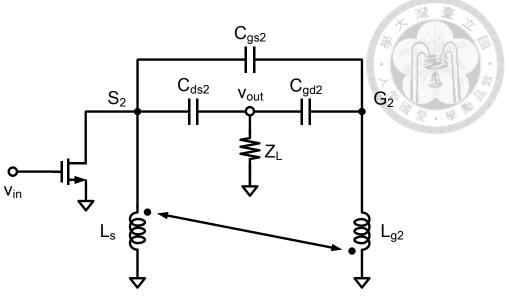

|            | proposed transformer feedback                                                                      |

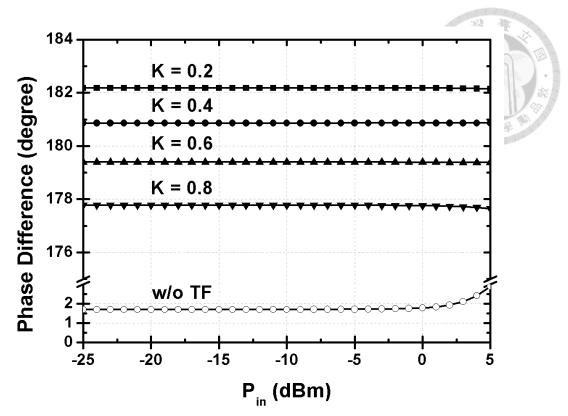

| Fig. 3.6.  | Simulated phase difference between node $S_2$ and $G_2$ versus different $P_{in}$ levels at        |

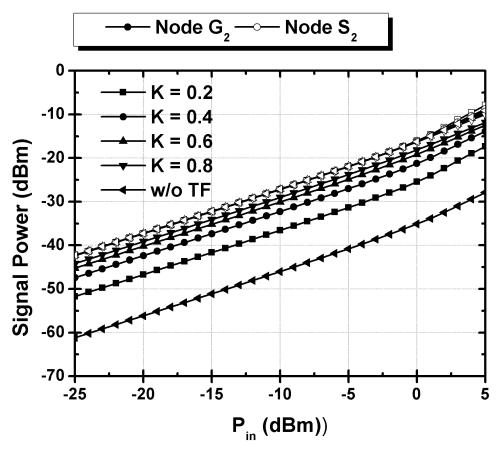

|            | 60-GHz60                                                                                           |

| Fig. 3.7.  | Simulated signal power at $S_2$ and $G_2$ (in dBm) versus different $P_{in}$ levels at 60-GHz60    |

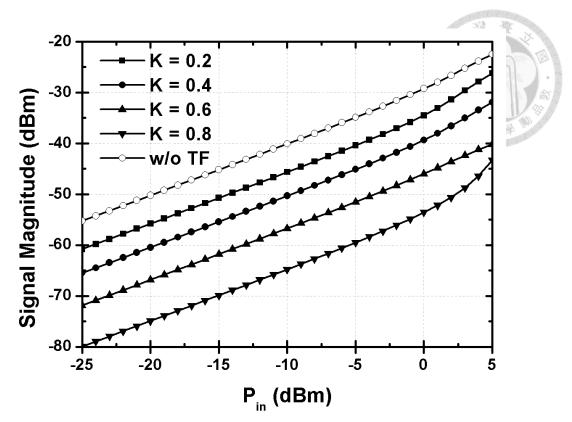

| Fig. 3.8.  | Simulated signal magnitude at the output node (in dBm) at 60-GHz61                                 |

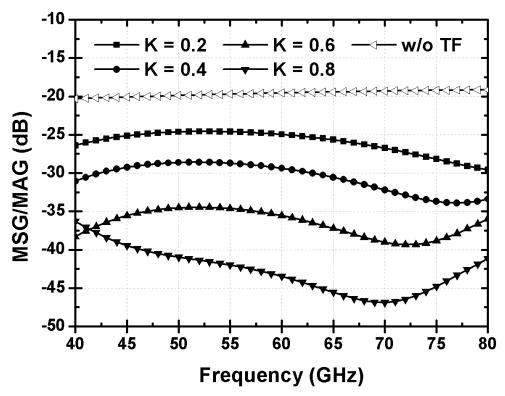

| Fig. 3.9.  | Simulated MSG/MAG of a cascode circuit at off-state with different transformer                     |

|            | coupling coefficients61                                                                            |

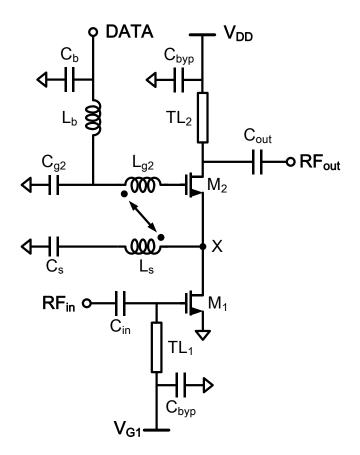

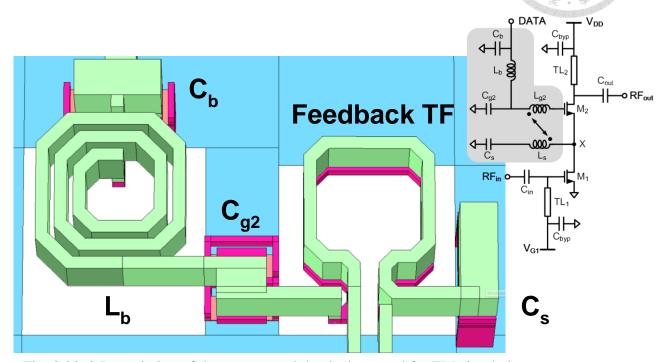

| Fig. 3.10. | Schematic of the proposed OOK modulator                                                            |

| Fig. 3.11. | Simulated DC-IV curves of the cascode circuit with two identical device gate                       |

|            | peripheries of 20f x 2 µm64                                                                        |

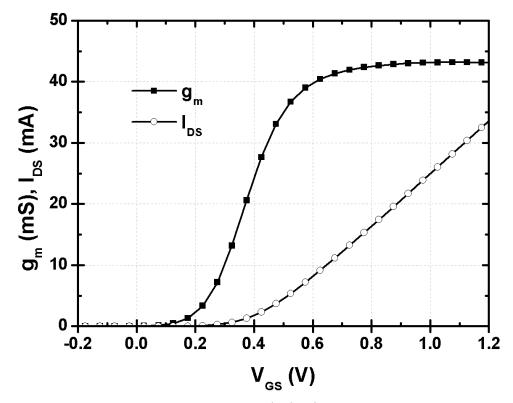

| Fig. 3.12. | Simulated $g_{\rm m}$ and $I_{\rm DS}$ of a 20f x 2µm device in common-source configuration versus |

|            | different $V_{\rm GS}$ at $V_{\rm DS} = 1.0$ V64                                                   |

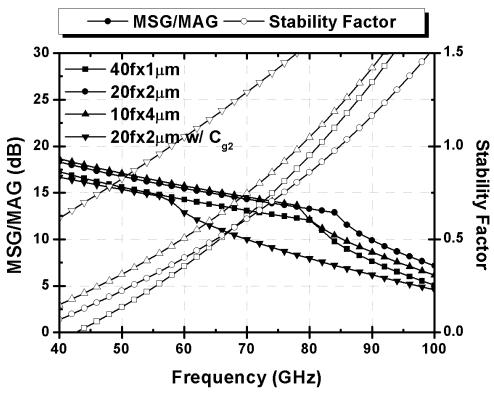

| Fig. 3.13. | Simulated MSG/MAG and stability factor of the cascode circuit with different                       |

|            | configurations of a total 40 µm gate-periphery65                                                   |

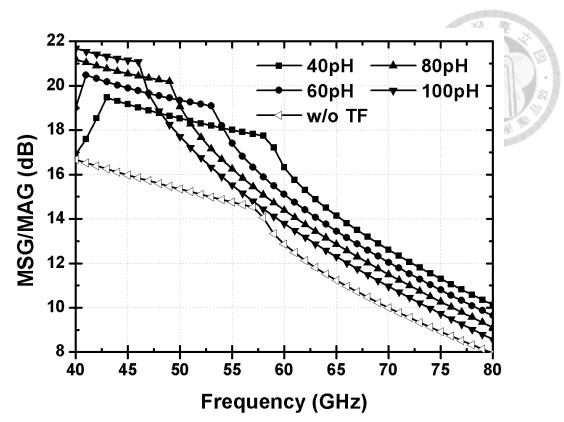

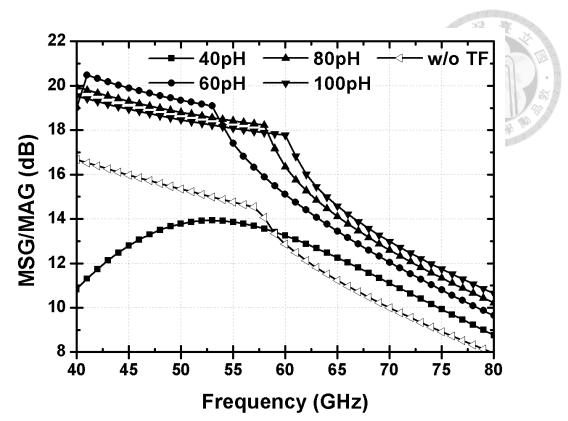

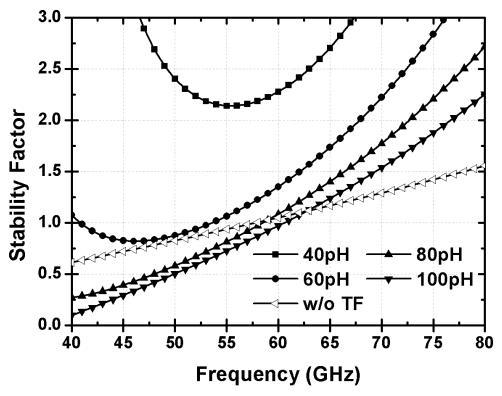

| Fig. 3.14. | Simulated MSG/MAG of the cascode circuit at on-state with fixed $L_s = 60$ pH and                  |

|            | varying <i>L</i> <sub>g2</sub> from 40 to 100 pH67                                                 |

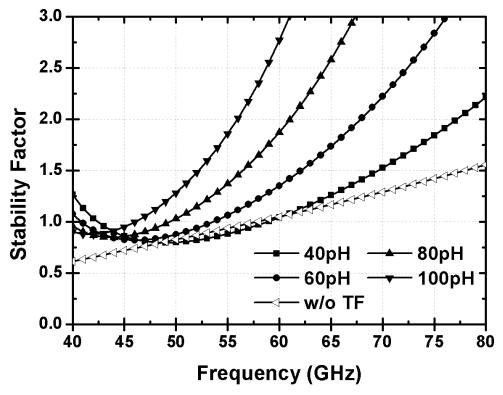

|            | -                                                                                                  |

| Fig. 3.15. | Simulated stability factor the cascode circuit at on-state with fixed $L_s = 60$ pH and       |

|------------|-----------------------------------------------------------------------------------------------|

|            | varying <i>L</i> <sub>g2</sub> from 40 to 100 pH67                                            |

| Fig. 3.16. | Simulated MSG/MAG of the cascode circuit at on-state with fixed $L_{g2} = 60$ pH and          |

|            | varying <i>L</i> <sub>s</sub> from 40 to 100 pH68                                             |

| Fig. 3.17. | Simulated stability factor of the cascode circuit at on-state with fixed $L_{g2} = 60$ pH and |

|            | varying <i>L</i> <sub>s</sub> from 40 to 100 pH68                                             |

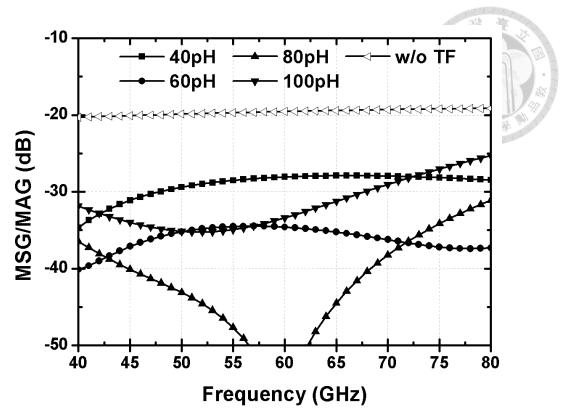

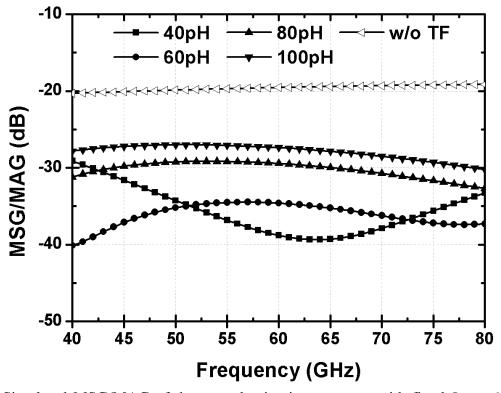

| Fig. 3.18. | Simulated MSG/MAG of the cascode circuit at off-state with fixed $L_s = 60$ pH and            |

|            | varying <i>L</i> <sub>g2</sub> from 40 to 100 pH69                                            |

| Fig. 3.19. | Simulated MSG/MAG of the cascode circuit at on-state with fixed $L_{g2} = 60$ pH and          |

|            | varying <i>L</i> <sub>s</sub> from 40 to 100 pH69                                             |

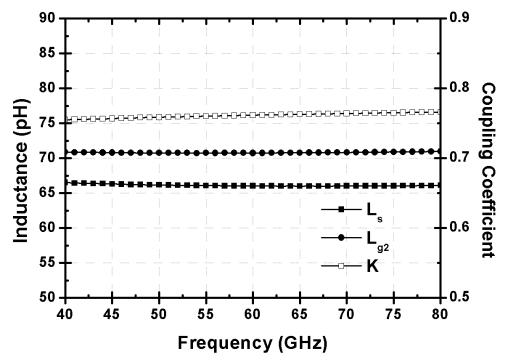

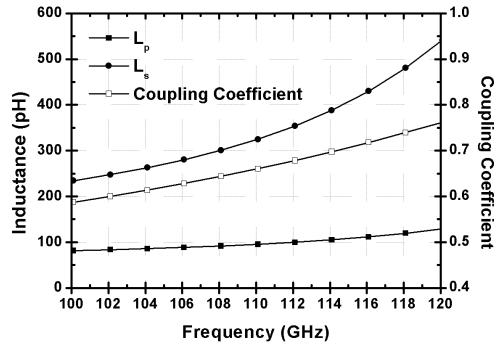

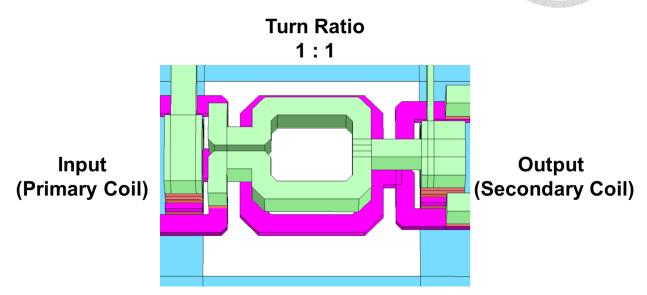

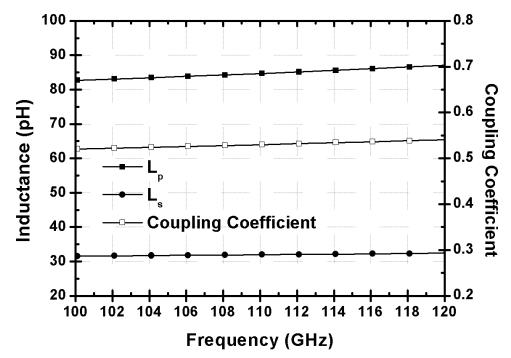

| Fig. 3.20. | Post-EM simulated parameters of the feedback transformer                                      |

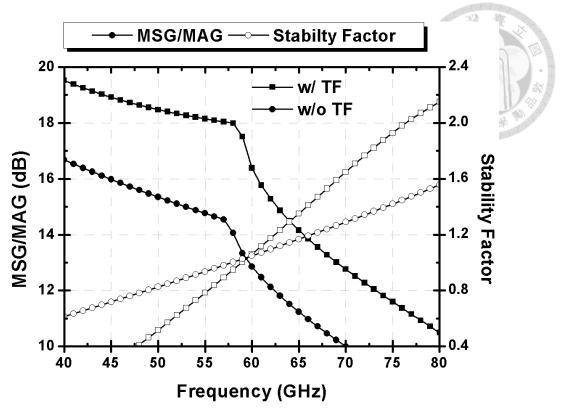

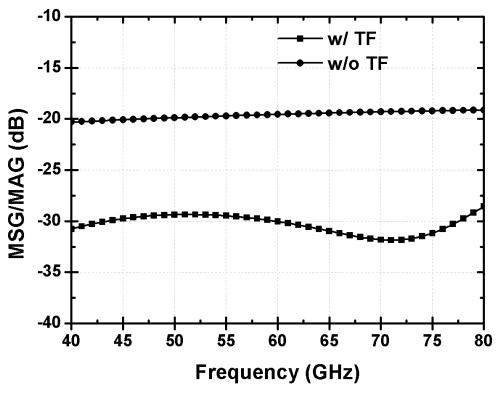

| Fig. 3.21. | Post-EM simulated MSG/MAG and stability factor of the cascode circuit with                    |

|            | transformer feedback at on-state71                                                            |

| Fig. 3.22. | Post-EM simulated MSG/MAG of the cascode circuit with transformer feedback at                 |

|            | off-state71                                                                                   |

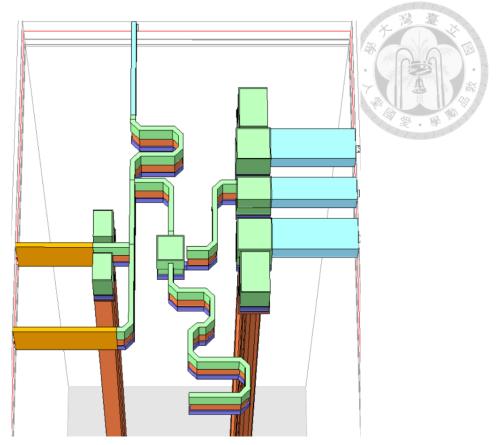

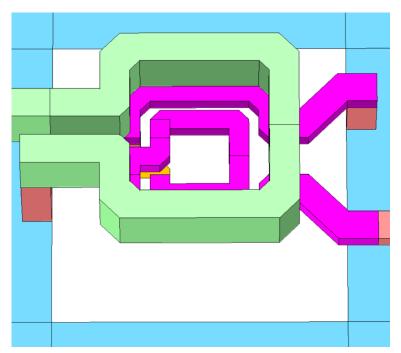

| Fig. 3.23. | 3-D rendering of the area around the devices used for EM simulation73                         |

| Fig. 3.24. | Simulated S-parameters of the proposed modulator at on-state74                                |

| Fig. 3.25. | Simulated S-parameters of the proposed modulator at off-state74                               |

| Fig. 3.26. | Simulated large-signal performances of the proposed modulator at 60 GHz at on-state           |

|            |                                                                                               |

| Fig. 3.27. | Simulated large-signal performances of the proposed modulator at on-state versus              |

|            | frequency77                                                                                   |

| Fig. 3.28. | Simulated large-signal performances of the proposed modulator at 60 GHz at off-state.         |

|            |                                                                                               |

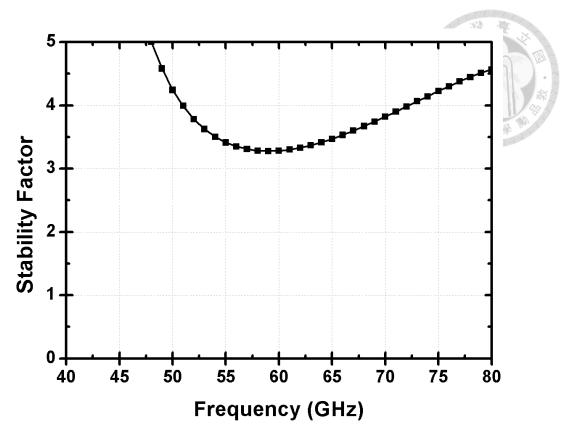

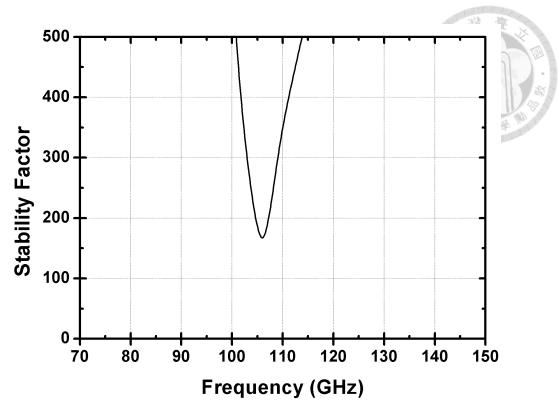

| Fig. 3.29. | Simulated stability factor of the proposed modulator at on-state                                       |

|------------|--------------------------------------------------------------------------------------------------------|

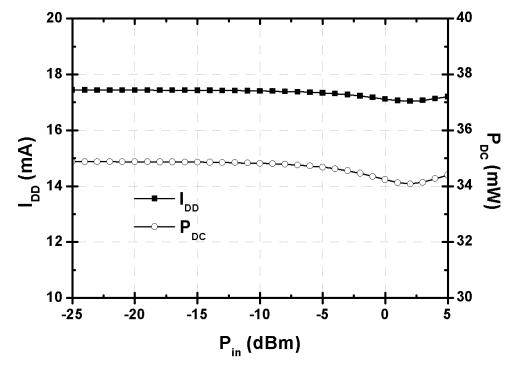

| Fig. 3.30. | Simulated drain current ( $I_{DD}$ ) and power consumption ( $P_{DC}$ ) at on-state versus $P_{in}$ 78 |

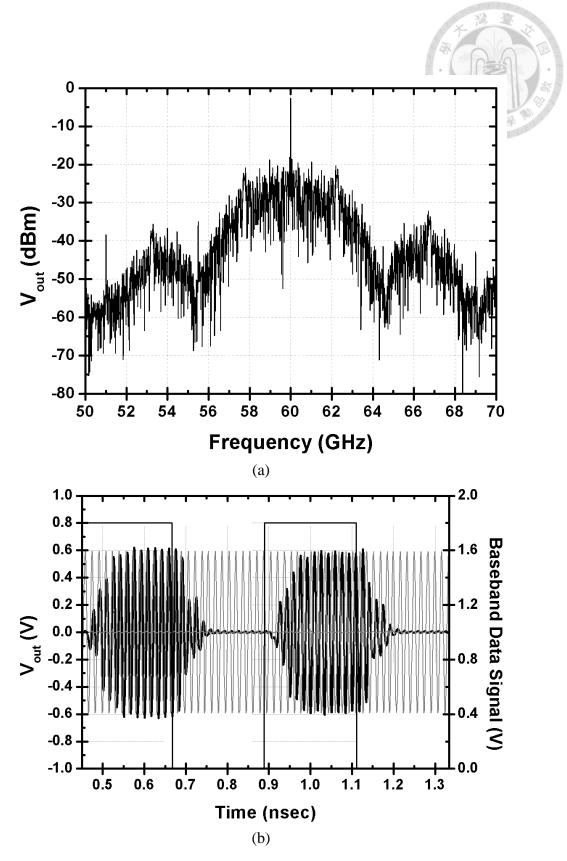

| Fig. 3.31. | Simulated output (a) spectrum and (b) waveform of the modulated signal at data rate of                 |

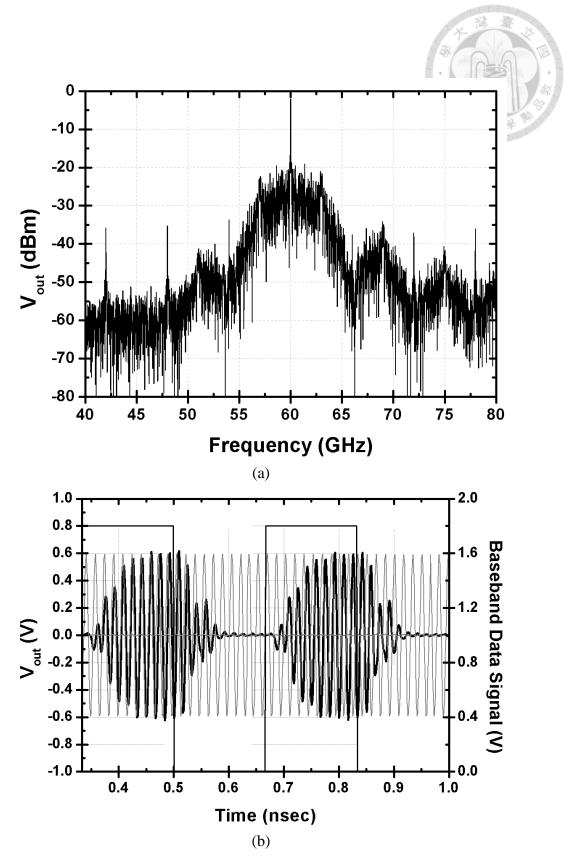

|            | 4.5 Gb/s                                                                                               |

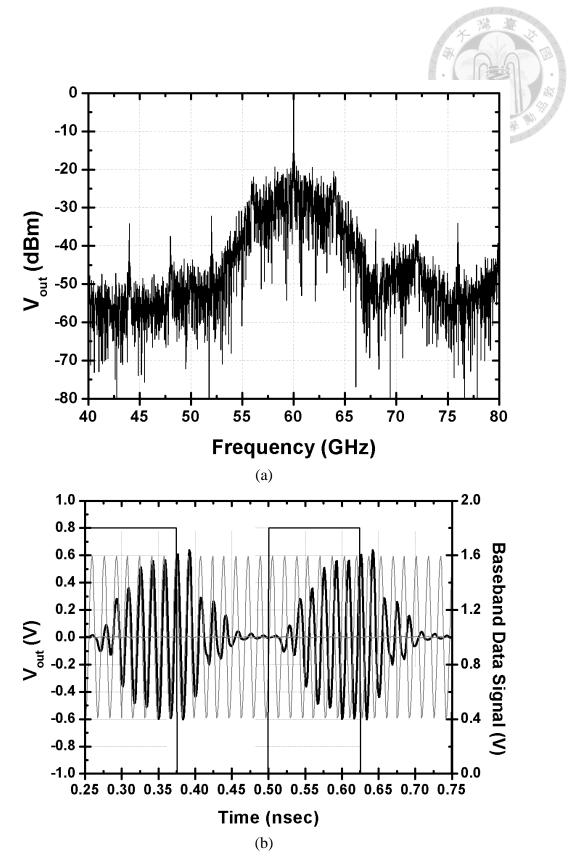

| Fig. 3.32. | Simulated output (a) spectrum and (b) waveform of the modulated signal at data rate of                 |

|            | 6 Gb/s                                                                                                 |

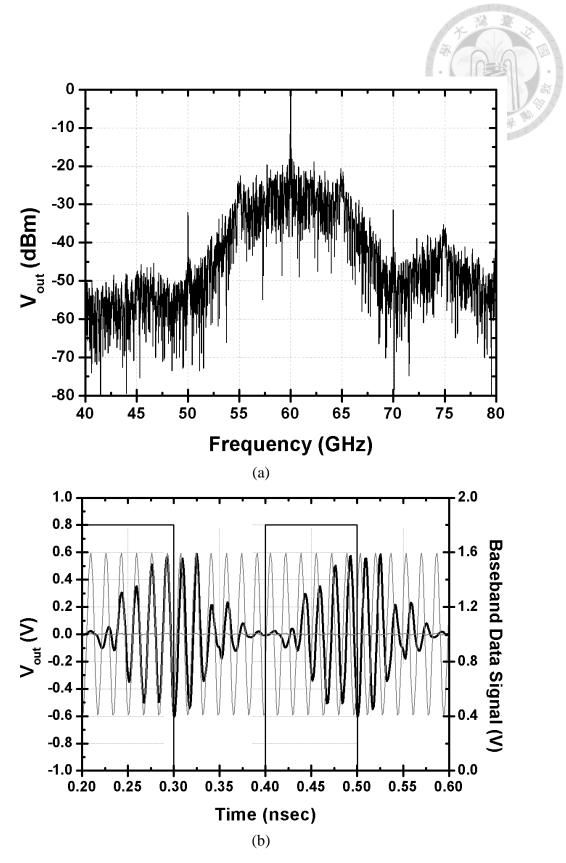

| Fig. 3.33. | Simulated output (a) spectrum and (b) waveform of the modulated signal at data rate of                 |

|            | 8 Gb/s                                                                                                 |

| Fig. 3.34. | Simulated output (a) spectrum and (b) waveform of the modulated signal at data rate of                 |

|            | 10 Gb/s                                                                                                |

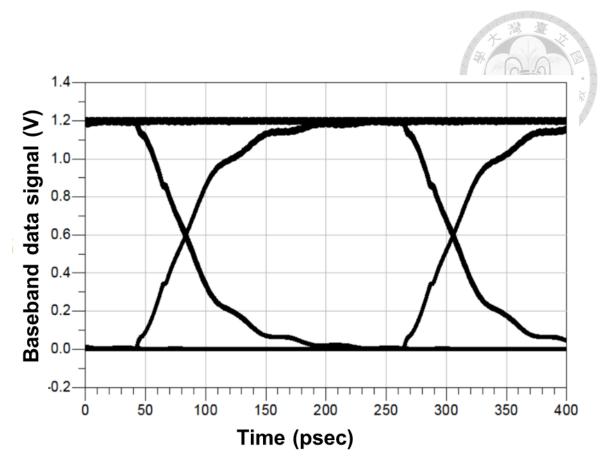

| Fig. 3.35. | Simulated eye pattern of the OOK modulation at data rate of 4.5 Gb/s                                   |

| Fig. 3.36. | Simulated eye pattern of the OOK modulation at data rate of 6 Gb/s                                     |

| Fig. 3.37. | Simulated eye pattern of the OOK modulation at data rate of 8 Gb/s                                     |

| Fig. 3.38. | Simulated eye pattern of the OOK modulation at data rate of 10 Gb/s                                    |

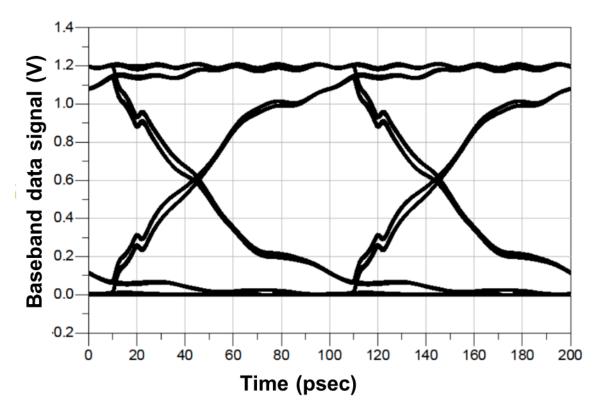

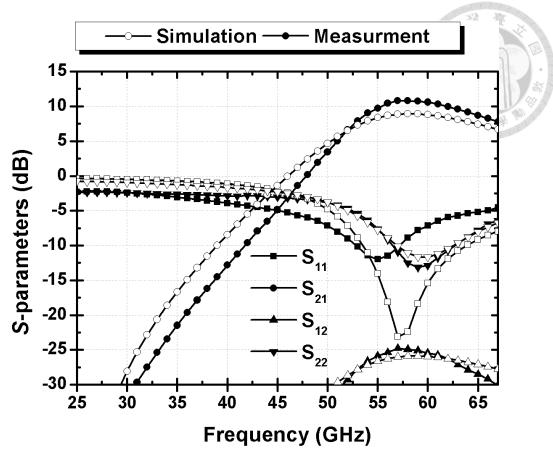

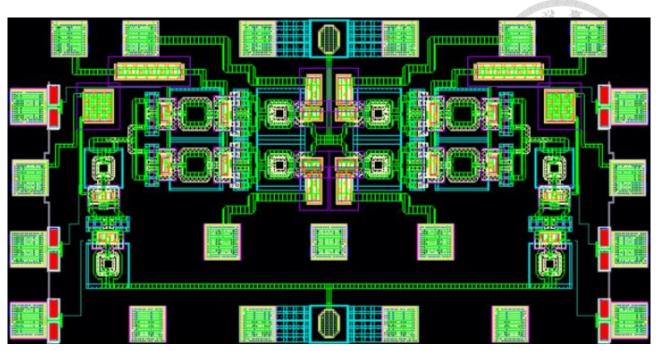

| Fig. 3.39. | Die photograph of the proposed OOK modulator                                                           |

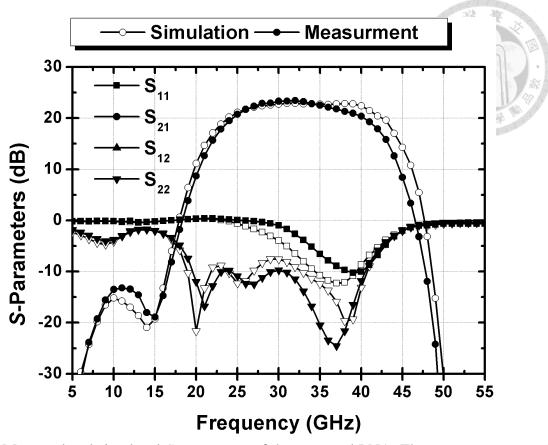

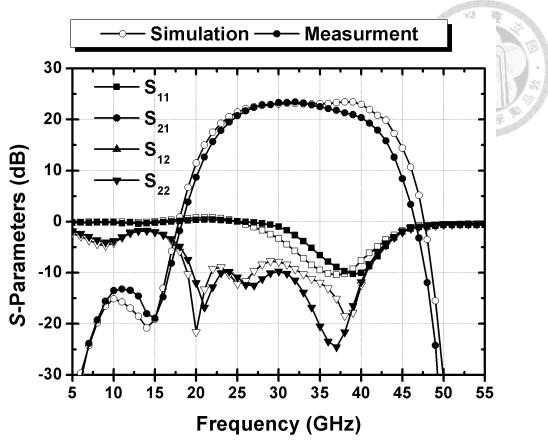

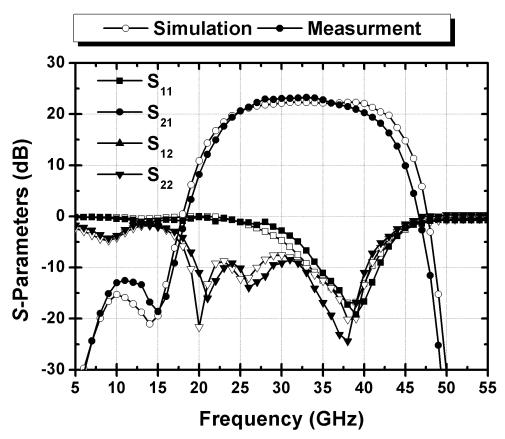

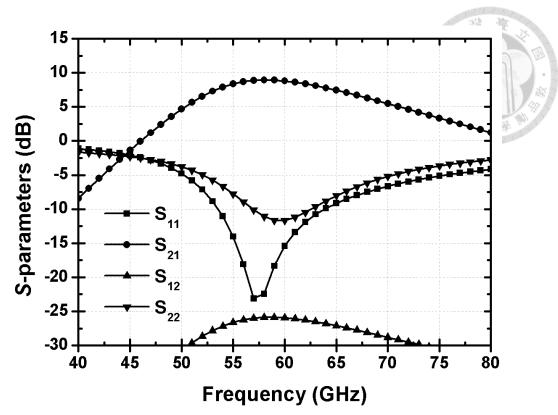

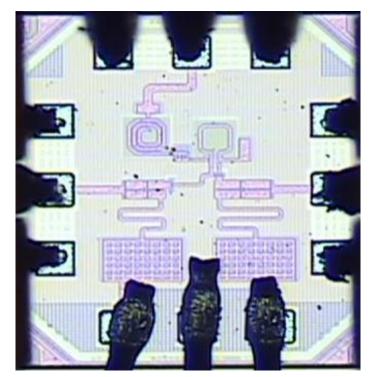

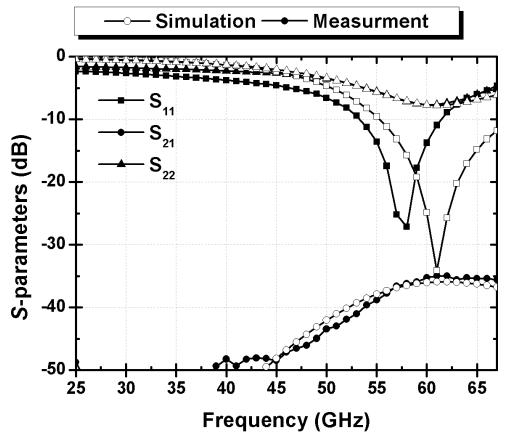

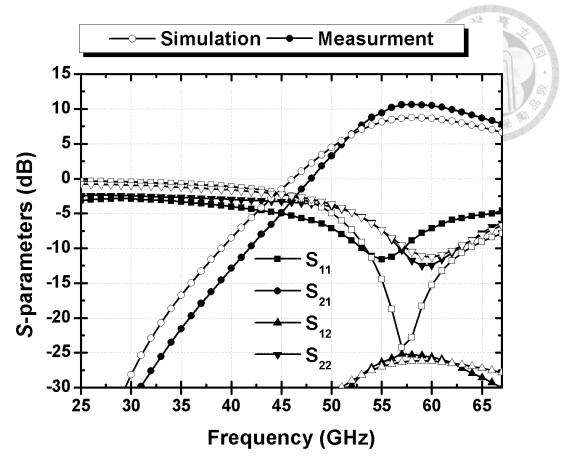

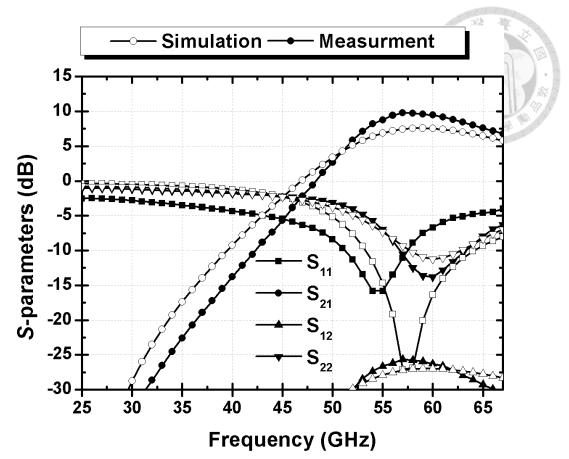

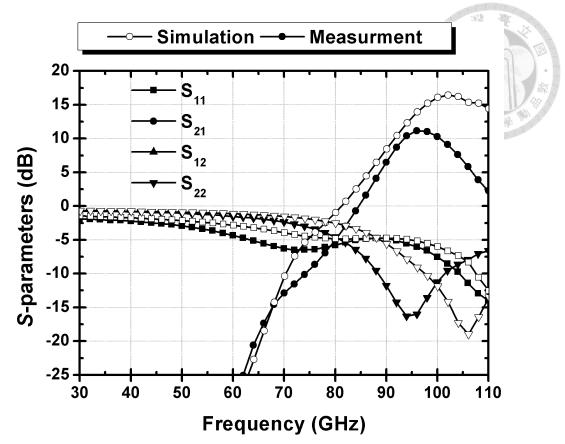

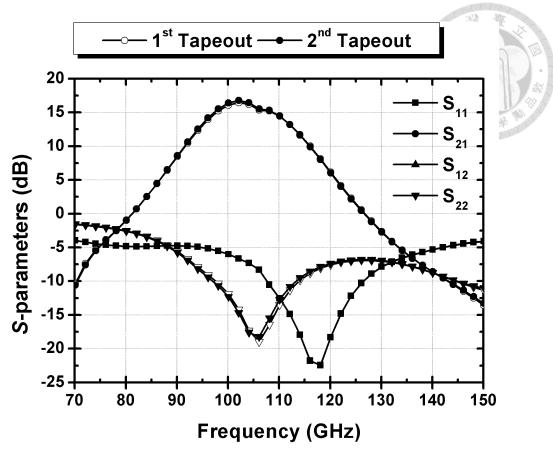

| Fig. 3.40. | Measured and simulated S-parameters of the proposed modulator at on-state                              |

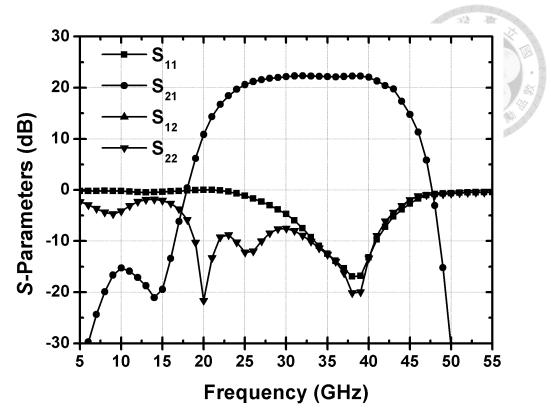

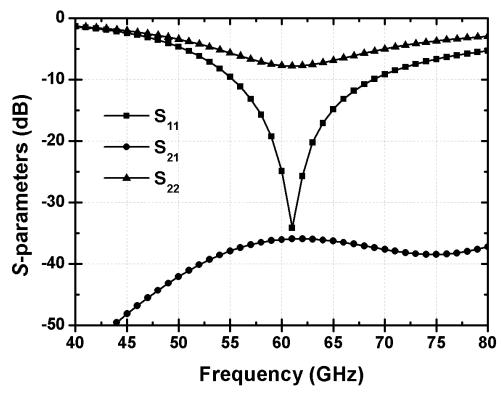

| Fig. 3.41. | Measured and simulated S-parameters of the proposed modulator at off-state                             |

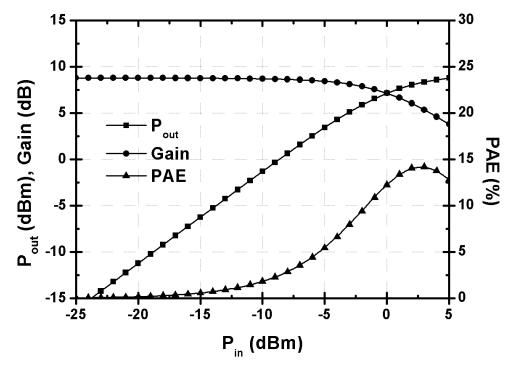

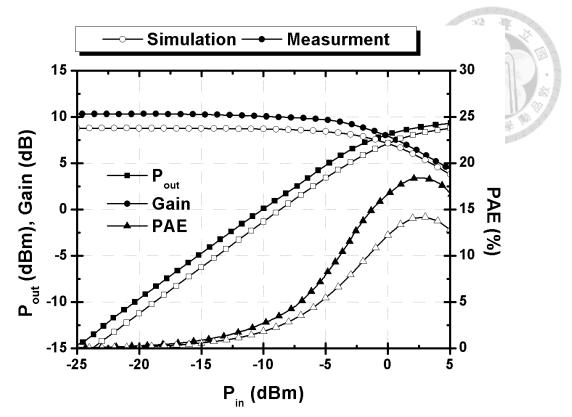

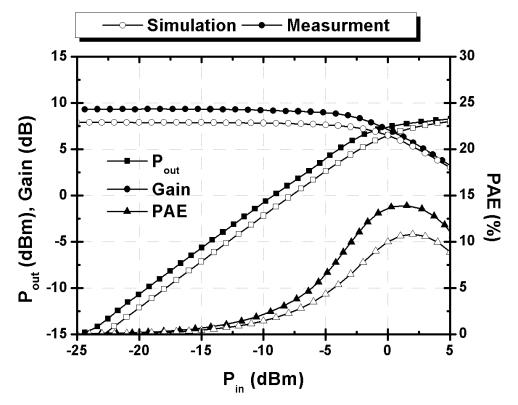

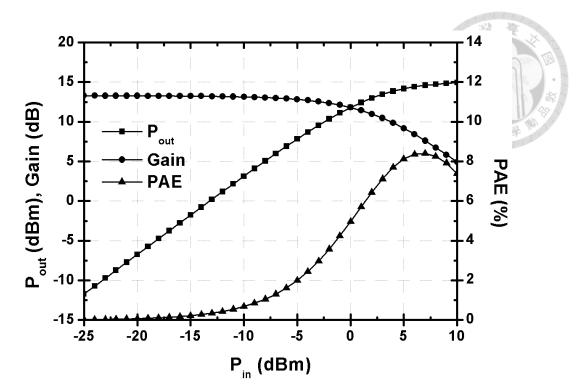

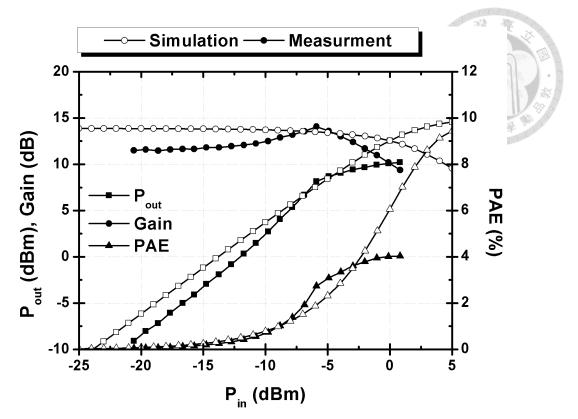

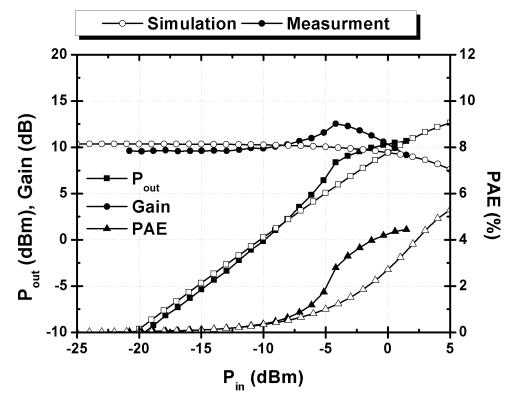

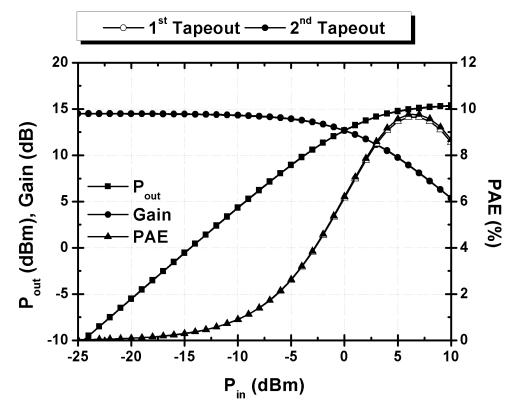

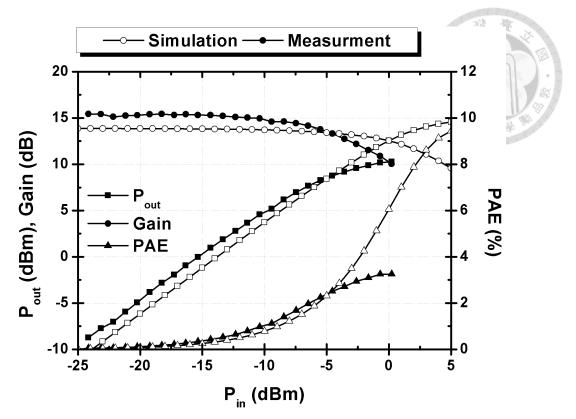

| Fig. 3.42. | Measured and simulated large-signal performances of the proposed modulator at                          |

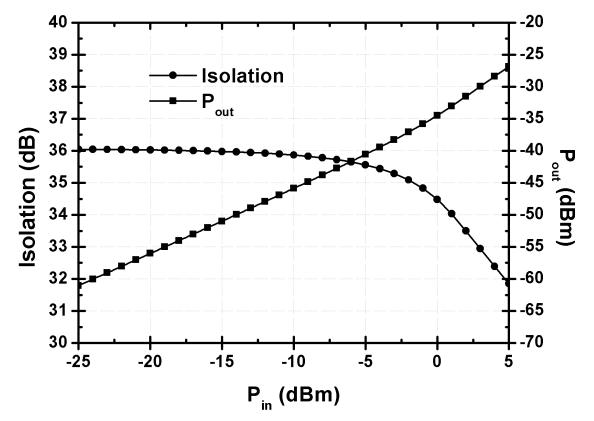

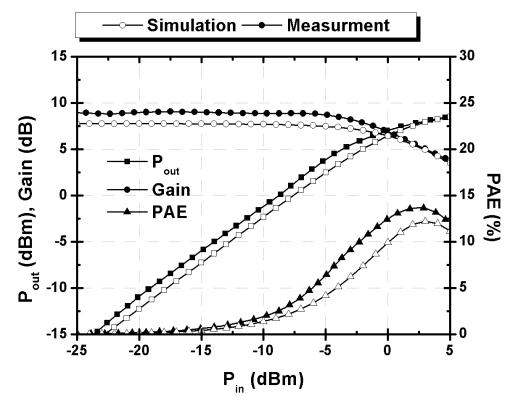

|            | on-state at 60 GHz                                                                                     |

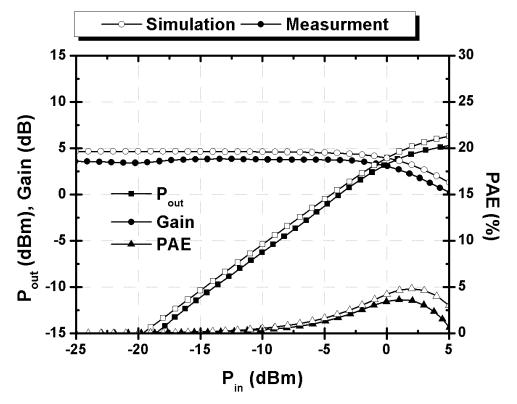

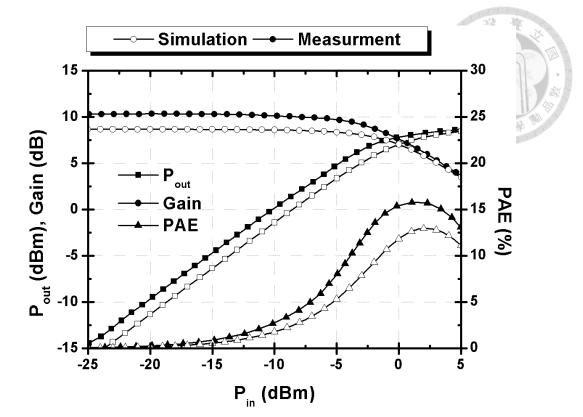

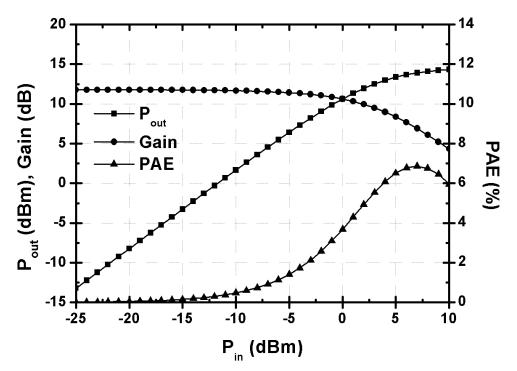

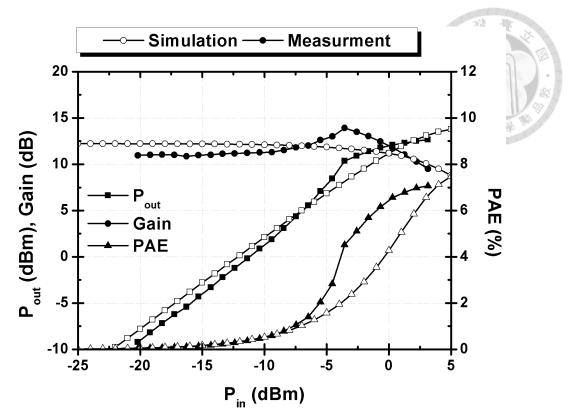

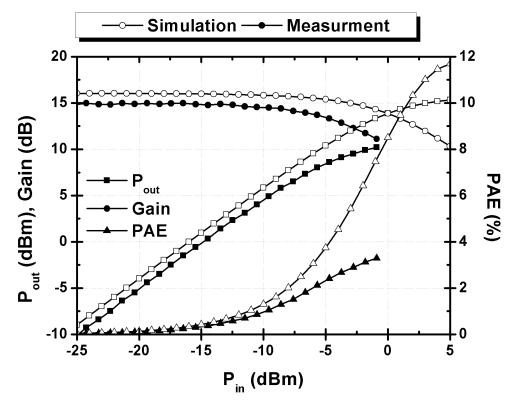

| Fig. 3.43. | Measured and simulated large-signal performances of the proposed modulator at                          |

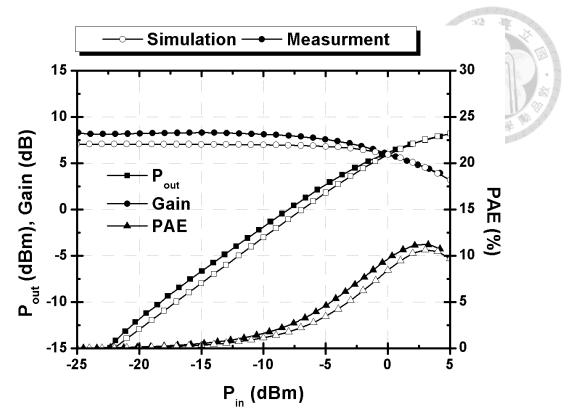

|            | on-state at 50 GHz                                                                                     |

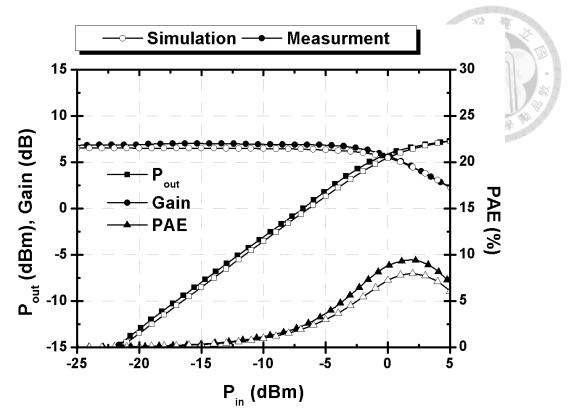

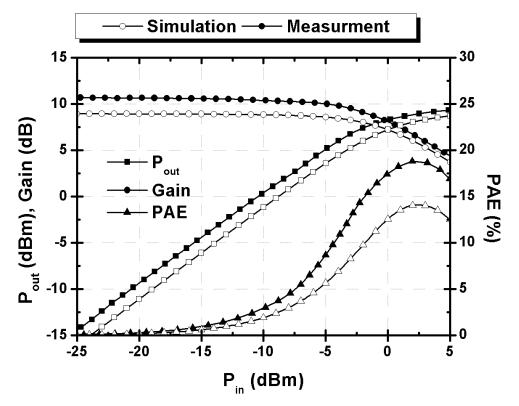

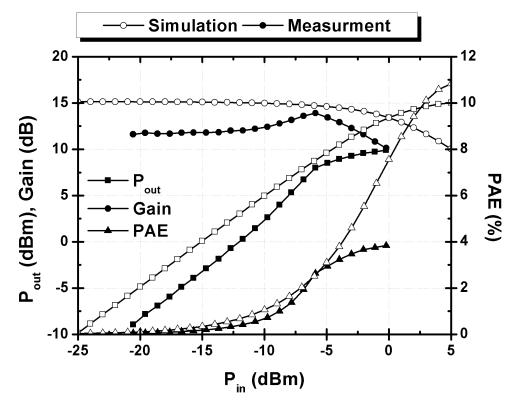

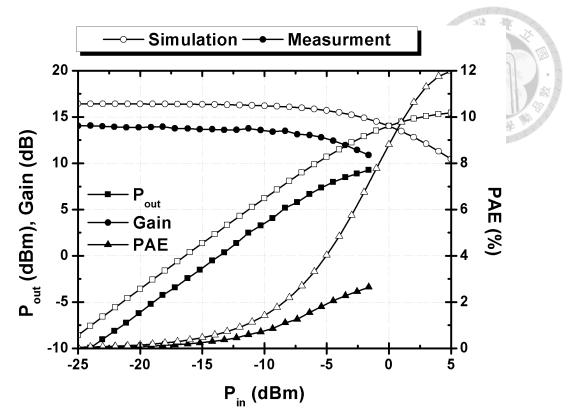

| Fig. 3.44. | Measured and simulated large-signal performances of the proposed modulator at                          |

|            | on-state at 52 GHz                                                                                     |

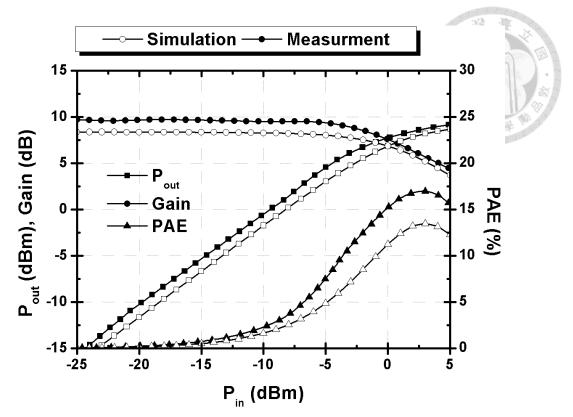

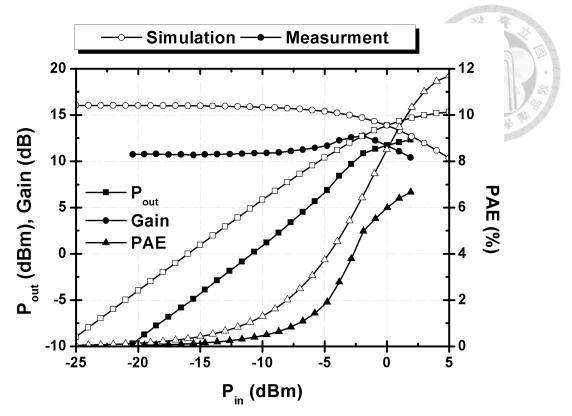

| Fig. 3.45. | Measured and simulated large-signal performances of the proposed modulator at                          |

|            | on-state at 54 GHz                                                                                     |

| Fig. 3.46. | Measured and simulated large-signal performances of the proposed modulator at                                                  |

|------------|--------------------------------------------------------------------------------------------------------------------------------|

| Fig. 3.47. | on-state at 56 GHz                                                                                                             |

| Fig. 3.48. | Measured and simulated large-signal performances of the proposed modulator at<br>on-state at 62 GHz                            |

| Fig. 3.49. | Measured and simulated large-signal performances of the proposed modulator at<br>on-state at 64 GHz                            |

| Fig. 3.50. | Measured and simulated large-signal performances of the proposed modulator at on-state at 66 GHz                               |

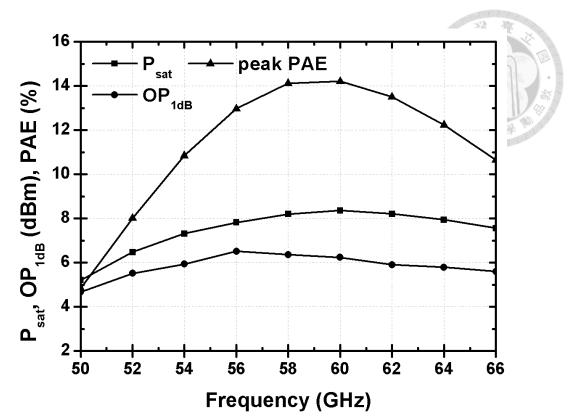

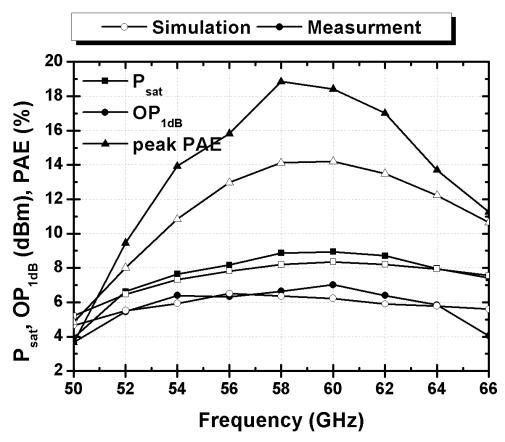

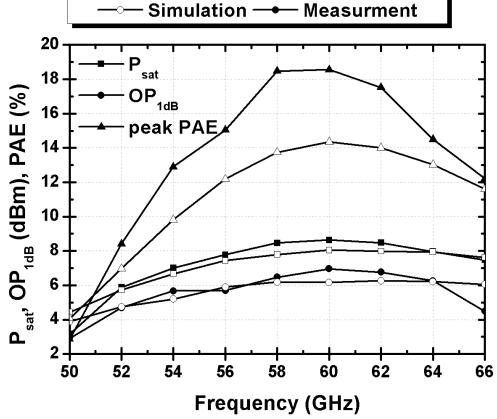

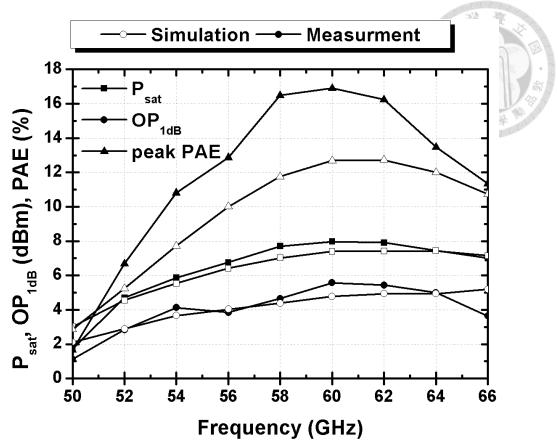

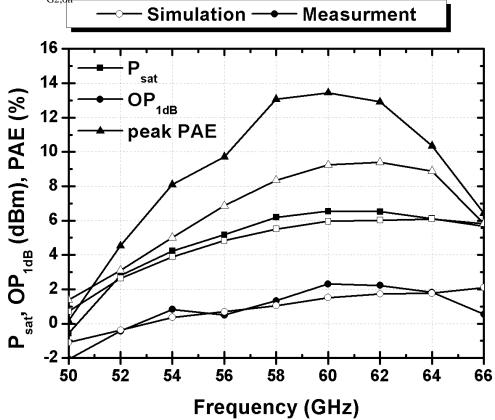

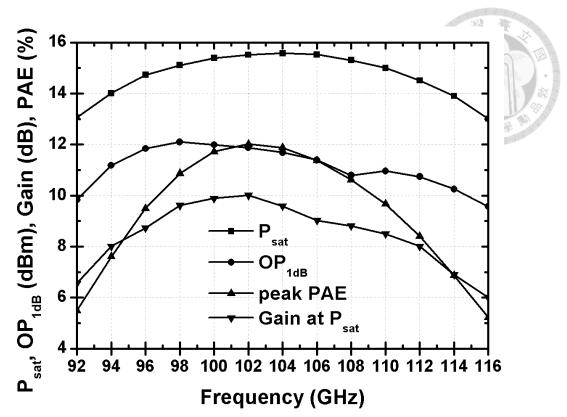

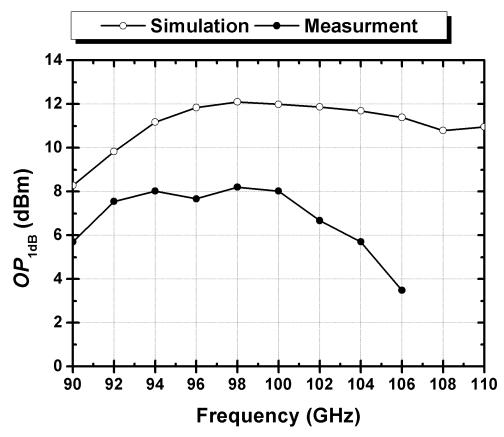

| Fig. 3.51. | Measured and simulated large-signal performances of the proposed modulator at<br>on-state versus frequency                     |

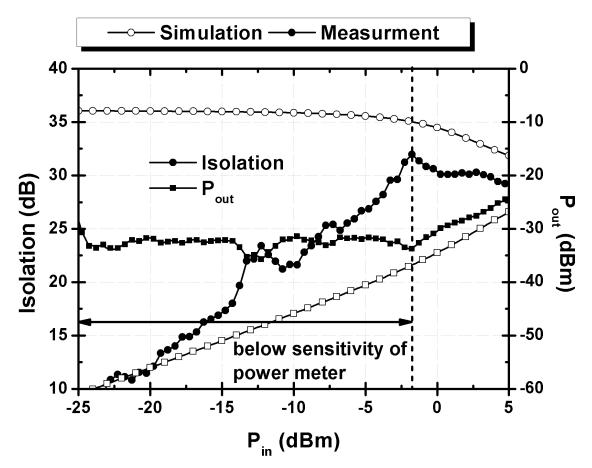

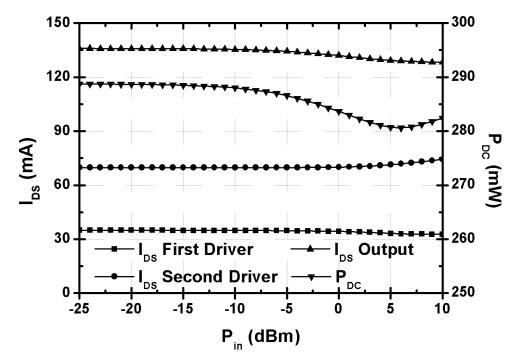

| Fig. 3.52. | Measured and simulated large-signal performances of the proposed modulator at off-state at 60 GHz                              |

| Fig. 3.53. | Measured and simulated S-parameters of the proposed modulator at on-state with $V_{G2,on}$<br>= 1.6 V                          |

| Fig. 3.54. | Measured and simulated S-parameters of the proposed modulator at on-state with $V_{G2,on}$<br>= 1.4 V                          |

| Fig. 3.55. | Measured and simulated S-parameters of the proposed modulator at on-state with $V_{G2,on}$<br>= 1.2 V                          |

| Fig. 3.56. | Measured and simulated large-signal performances of the proposed modulator versus frequency with $V_{\rm G2,on} = 1.6$ V       |

| Fig. 3.57. | Measured and simulated large-signal performances of the proposed modulator versus frequency with $V_{G2,on} = 1.4 \text{ V}97$ |

| Fig. 3.58. | Measured and simulated large-signal performances of the proposed modulator versus                          |

|------------|------------------------------------------------------------------------------------------------------------|

|            | frequency with $V_{G2,on} = 1.2$ V                                                                         |

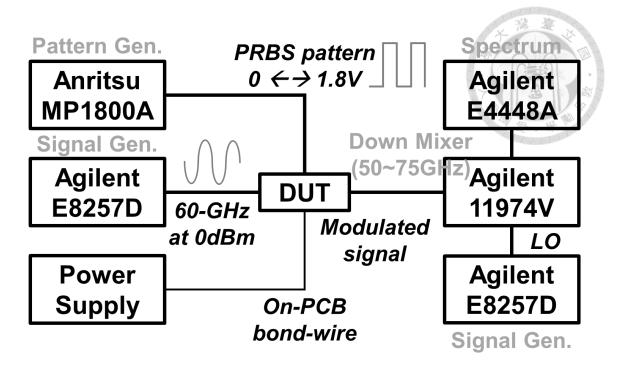

| Fig. 3.59. | Setup for modulation measurements in frequency-domain                                                      |

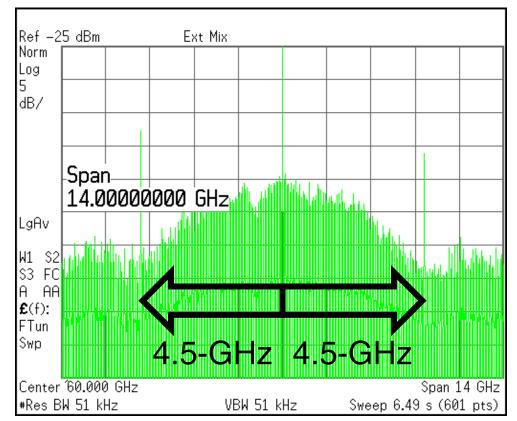

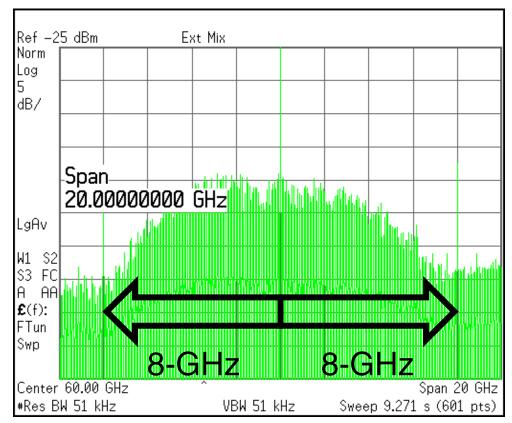

| Fig. 3.60. | Measured output spectrum of the modulated signal at data rate of 4.5 Gb/s99                                |

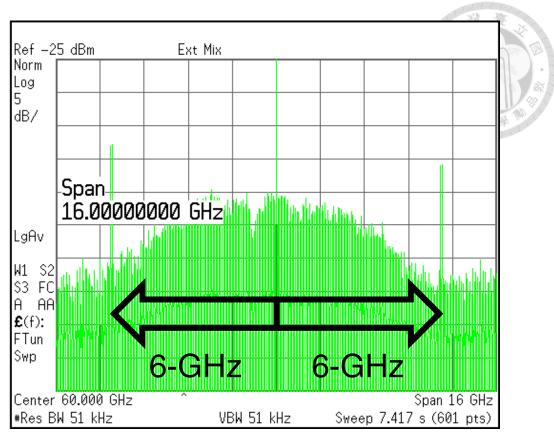

| Fig. 3.61. | Measured output spectrum of the modulated signal at data rate of 6 Gb/s100                                 |

| Fig. 3.62. | Measured output spectrum of the modulated signal at data rate of 8 Gb/s100                                 |

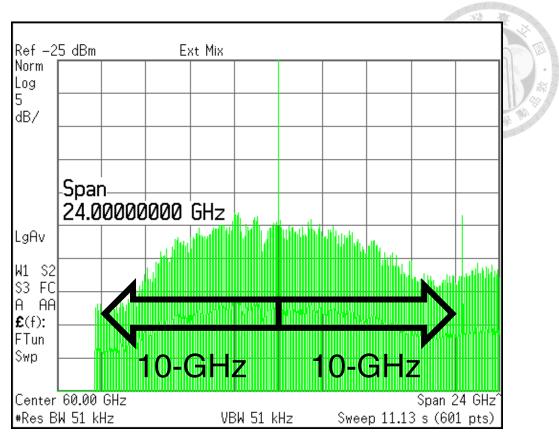

| Fig. 3.63. | Measured output spectrum of the modulated signal at data rate of 10 Gb/s101                                |

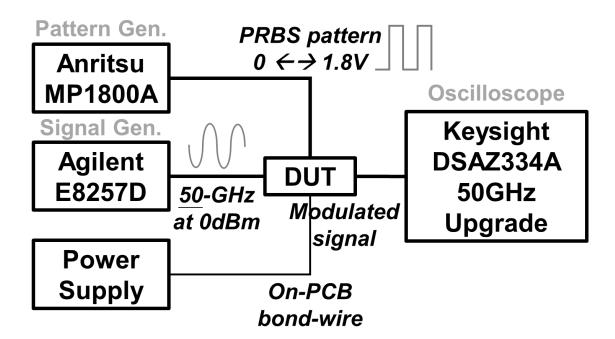

| Fig. 3.64. | Setup for modulation measurements in time-domain                                                           |

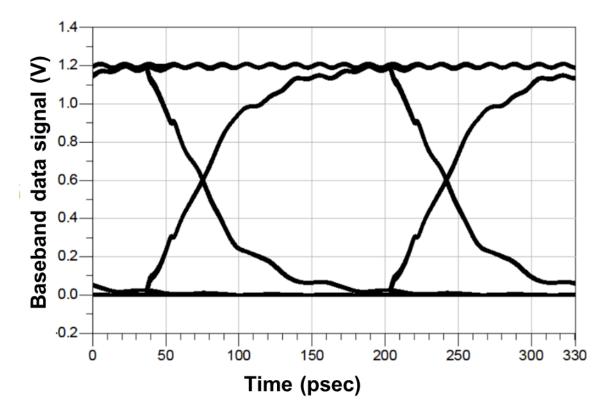

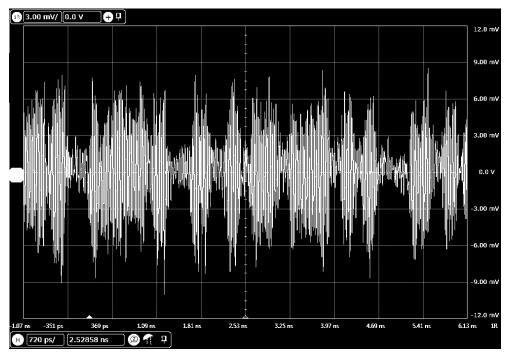

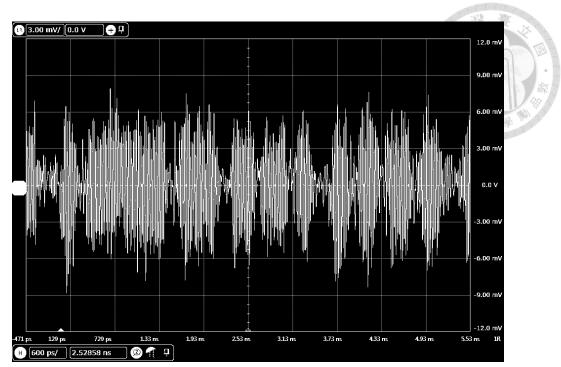

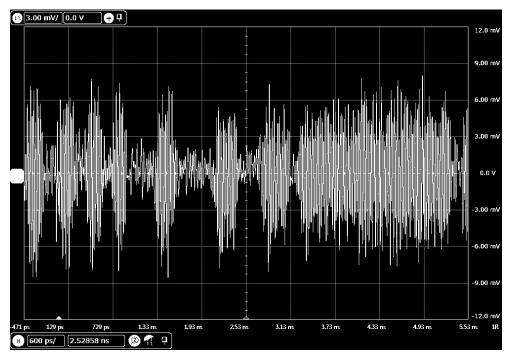

| Fig. 3.65. | Measured output waveform of the modulated signal at data rate of 4.5 Gb/s102                               |

| Fig. 3.66. | Measured output waveform of the modulated signal at data rate of 6 Gb/s102                                 |

| Fig. 3.67. | Measured output waveform of the modulated signal at data rate of 8 Gb/s103                                 |

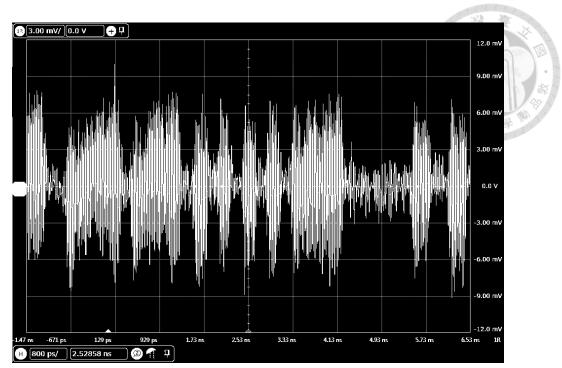

| Fig. 3.68. | Measured output waveform of the modulated signal at data rate of 10 Gb/s 103                               |

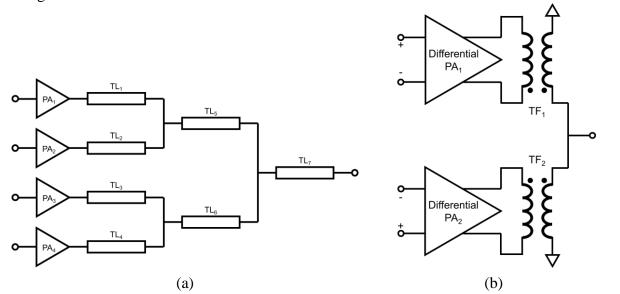

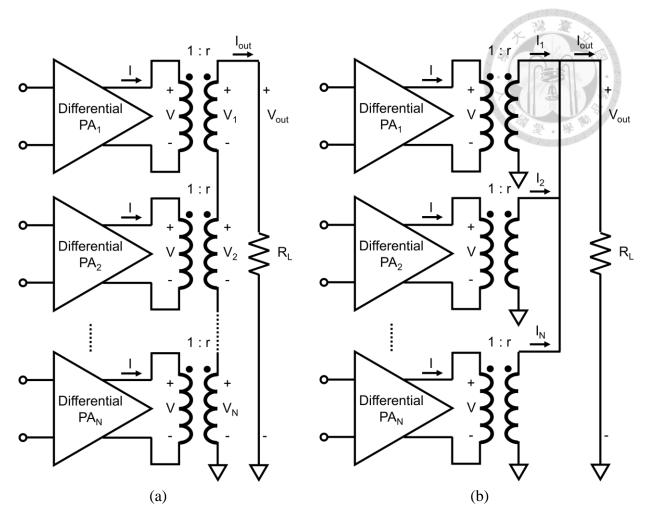

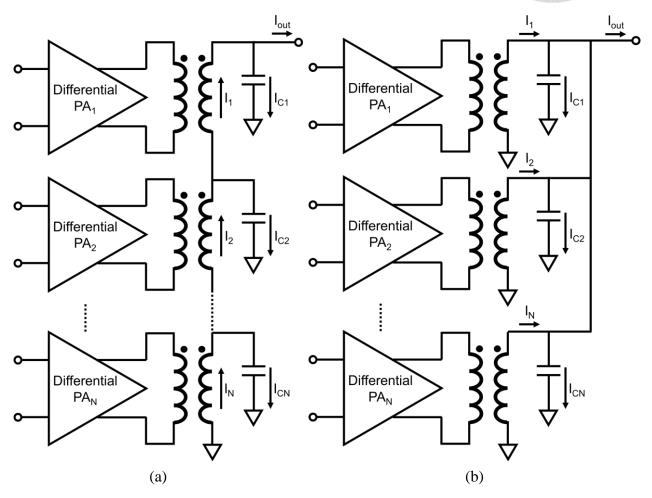

| Fig. 4.1.  | Commonly used power combining structures: (a) binary power combining (b)                                   |

|            | transformer-based power combining                                                                          |

| Fig. 4.2.  | Schematics of (a) voltage-combining configuration, and (b) current-combining                               |

|            | configuration of transformer-based power combining109                                                      |

| Fig. 4.3.  | Schematics of (a) voltage-combining configuration, and (b) current-combining                               |

|            | configuration of transformer-based power combining, with the parasitic capacitances                        |

|            | considered 111                                                                                             |

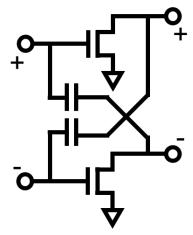

| Fig. 4.4.  | Schematic of neutralization technique implementation in differential mode with                             |

|            | cross-coupled capacitors between device gate and drain                                                     |

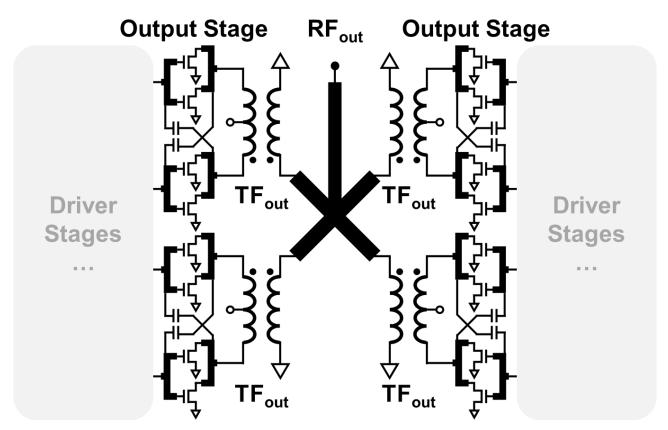

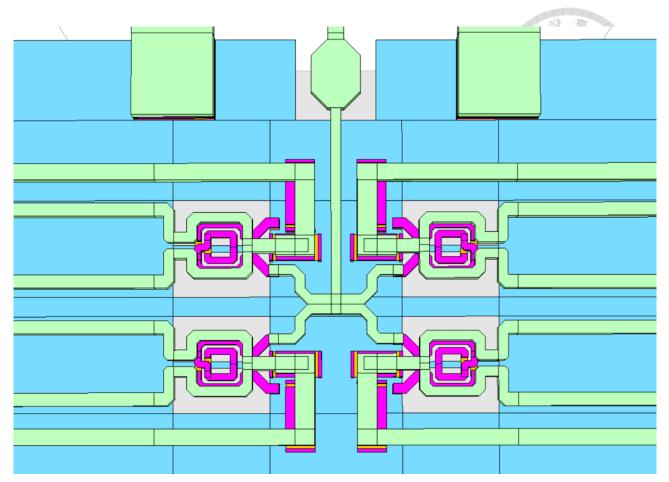

| Fig. 4.5.  | Schematic of the output stage complete with the four-way transformer-based power                           |

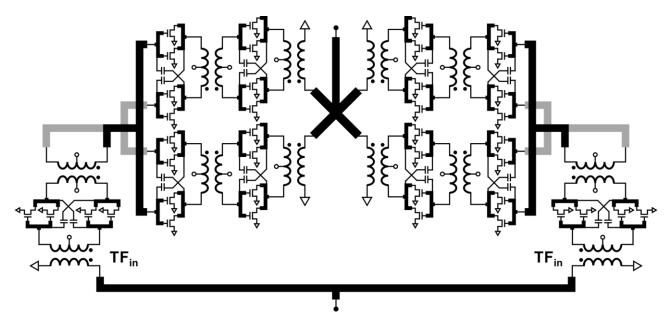

|            | combiner                                                                                                   |

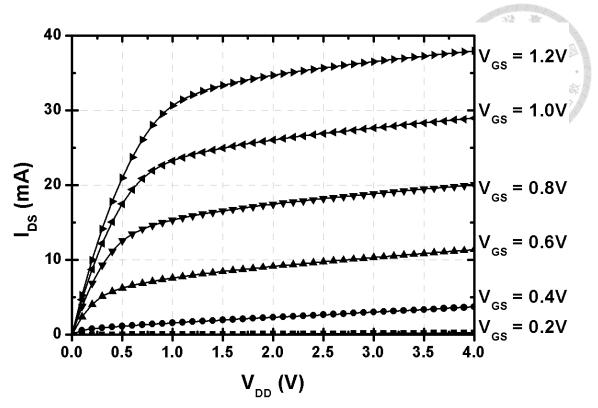

| Fig. 4.6.  | Simulated DC-IV curves of the device with gate-periphery of 32f x 1 $\mu$ m 115                            |

| Fig. 4.7.  | Simulated $g_{\rm m}$ and $I_{\rm DS}$ of the 32f x 1µm device versus $V_{\rm GS}$ at $V_{\rm DS} = 1.2$ V |

|            | #                                                                                                          |

|            | 010101010                                                                                   |

|------------|---------------------------------------------------------------------------------------------|

| Fig. 4.8.  | Simulated MSG/MAG and stability factor of a single 32f x 1 $\mu$ m device compared with     |

|            | two parallel-combined 16f x 1 µm devices116                                                 |

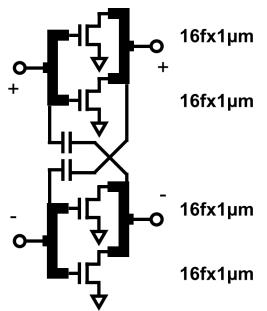

| Fig. 4.9.  | Schematic of the output stage differential pair with four 16f x 1 µm devices                |

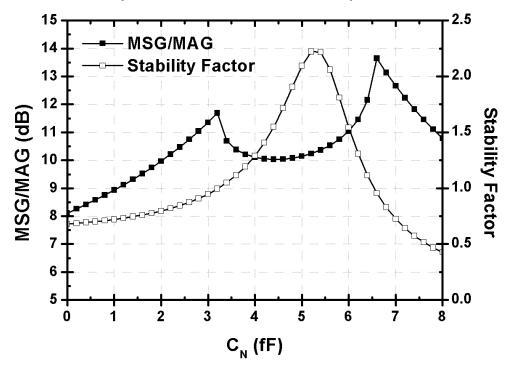

| Fig. 4.10. | Simulated MSG/MAG and stability factor of the output differential pair at 110 GHz           |

|            | versus different values of C <sub>N</sub> 117                                               |

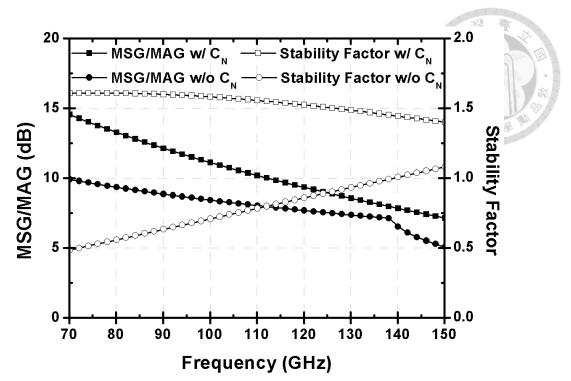

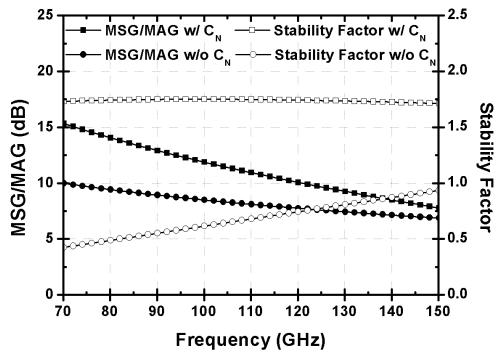

| Fig. 4.11. | Post-EM simulated MSG/MAG and stability factor of the output differential pair118           |

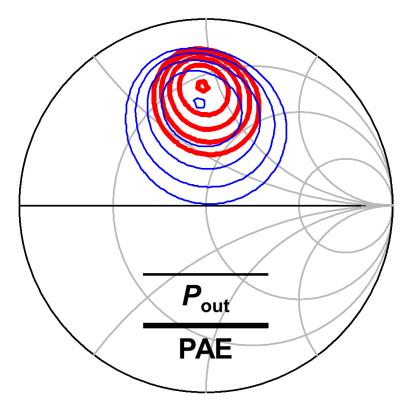

| Fig. 4.12. | Post-EM simulated power contours of the output differential pair                            |

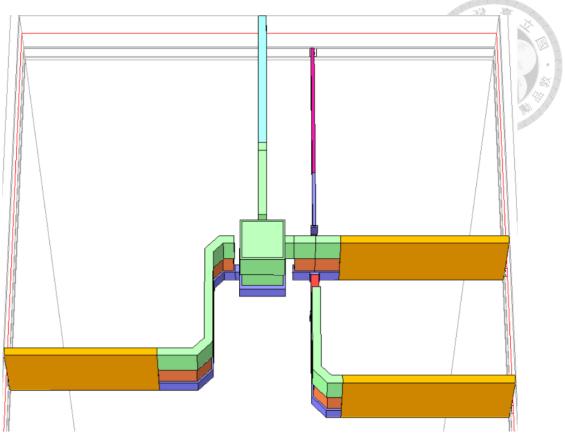

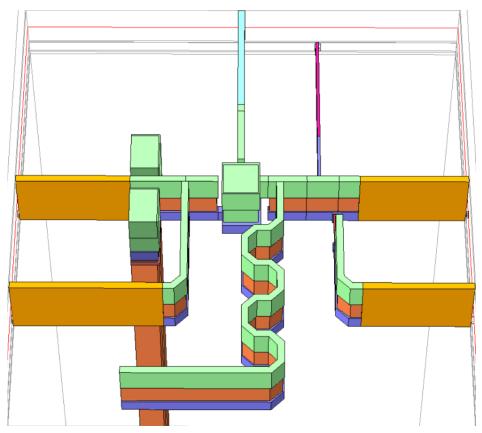

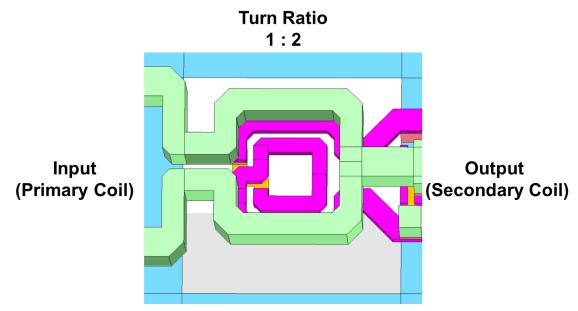

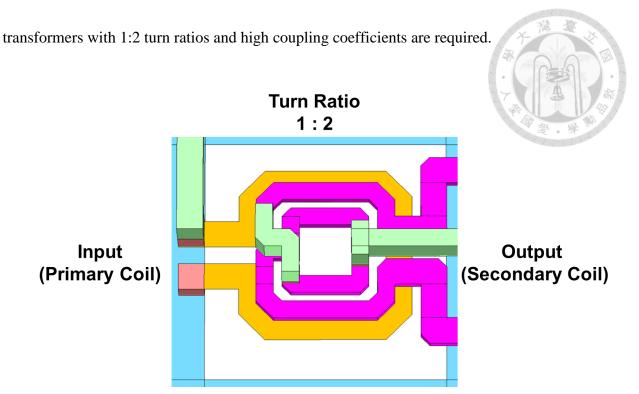

| Fig. 4.13. | 3-D rendering of the output transformer TF <sub>out</sub> used for EM simulation            |

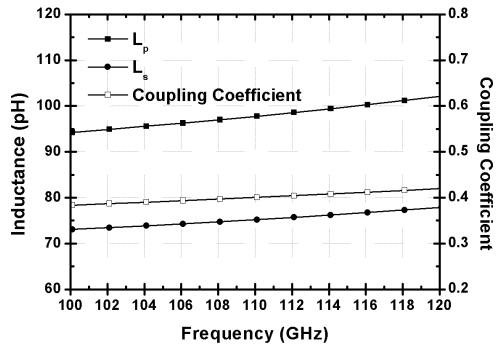

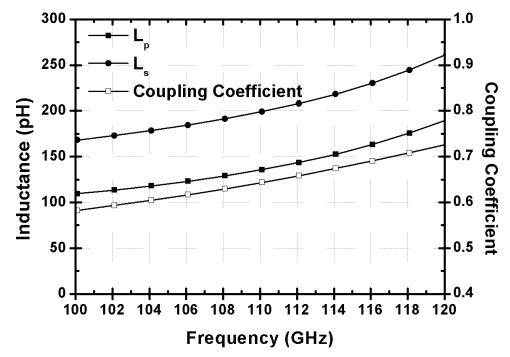

| Fig. 4.14. | Post-EM simulated parameters of the output transformer TF <sub>out</sub> 119                |

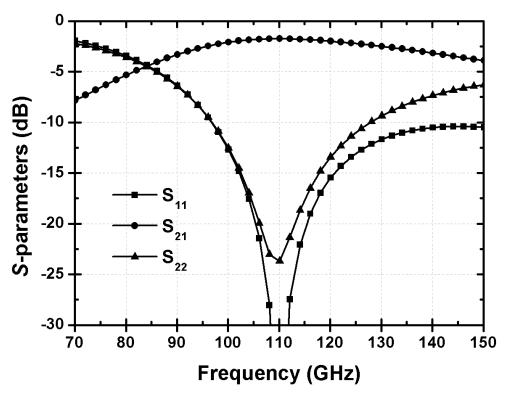

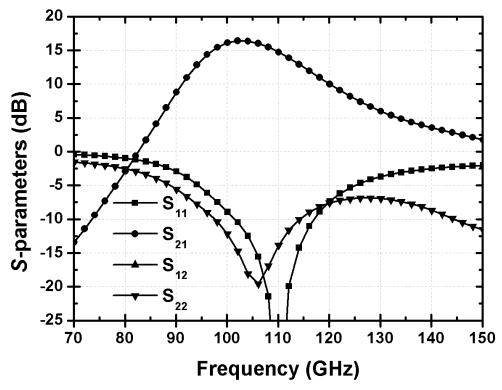

| Fig. 4.15. | Post-EM simulated S-parameters of the four-way transformer-based power combiner             |

|            |                                                                                             |

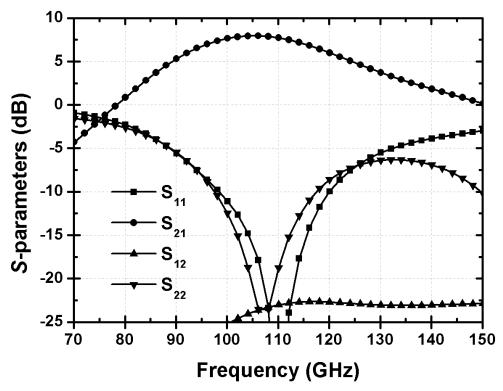

| Fig. 4.16. | Simulated S-parameters of the output stage complete with the four-way                       |

|            | transformer-based power combiner                                                            |

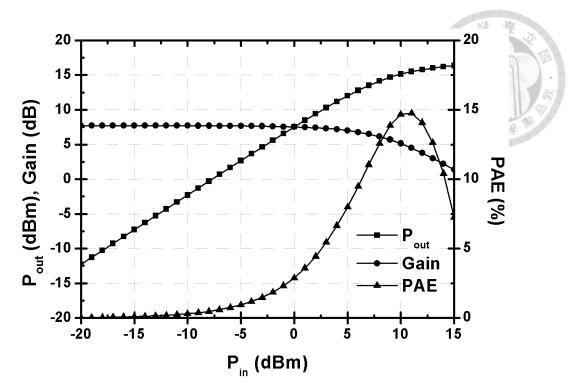

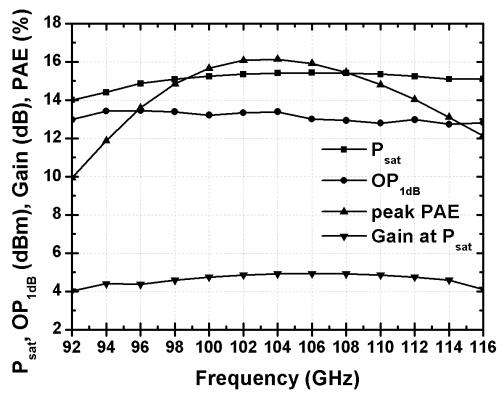

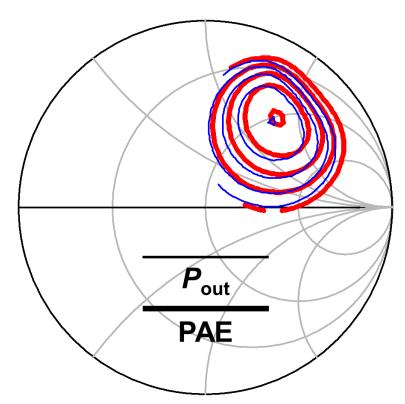

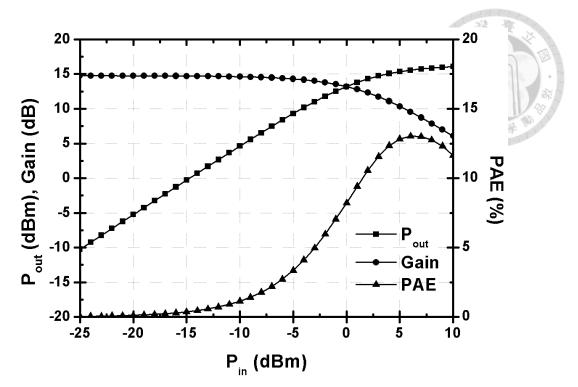

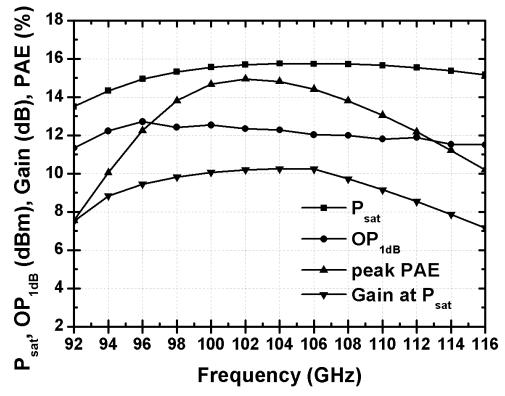

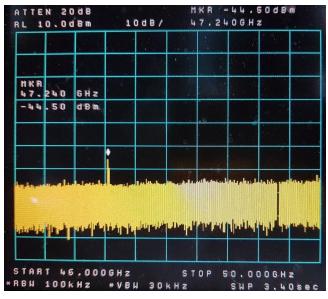

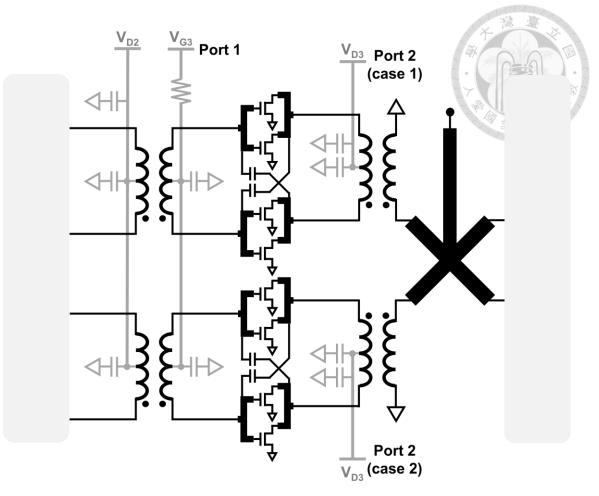

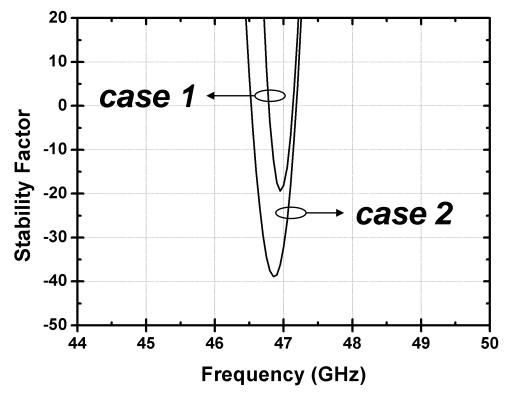

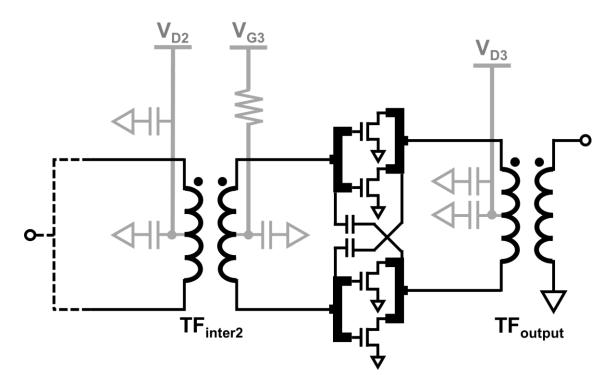

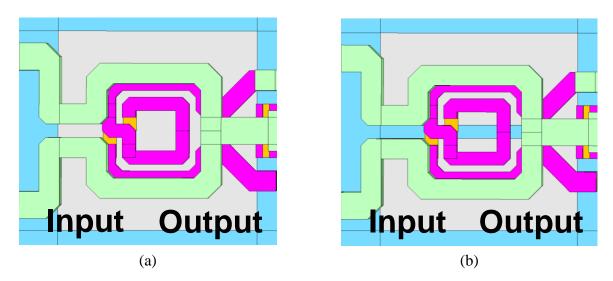

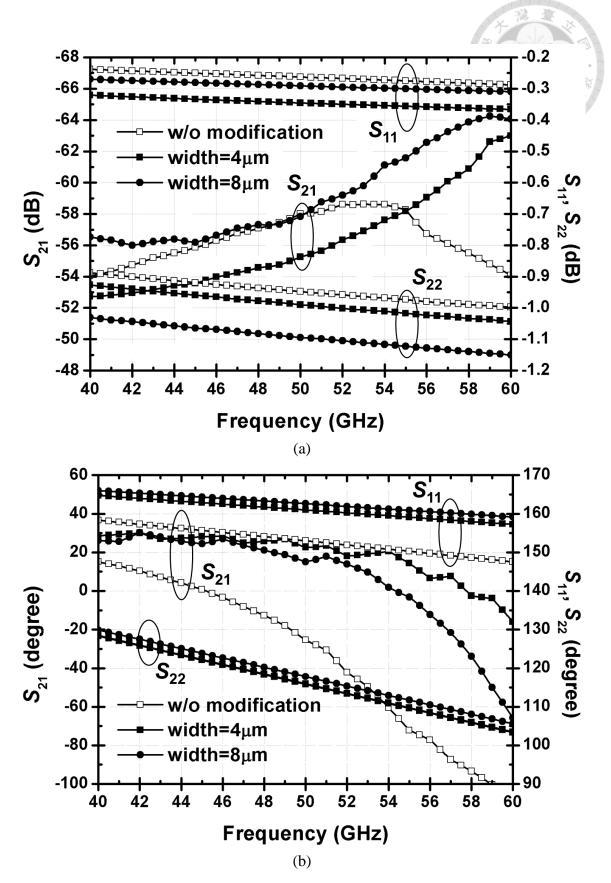

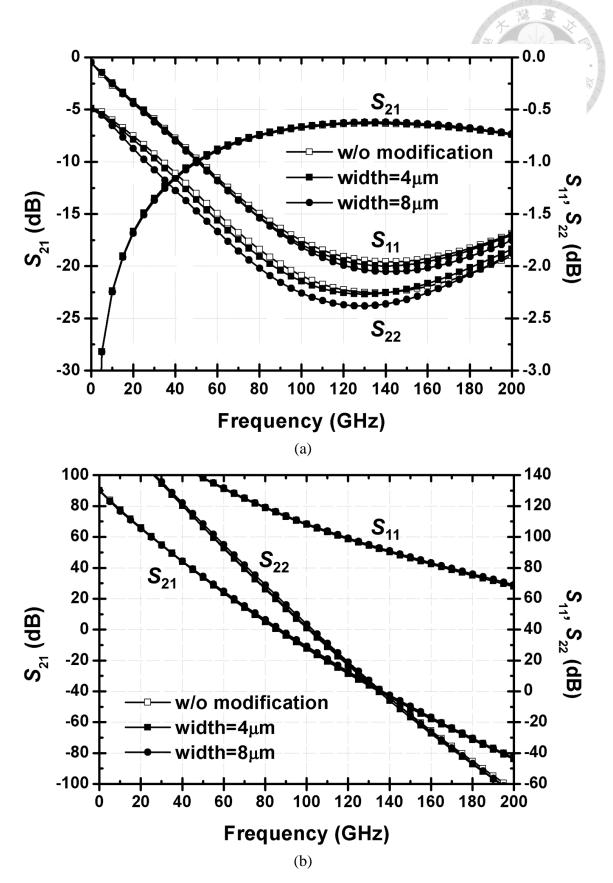

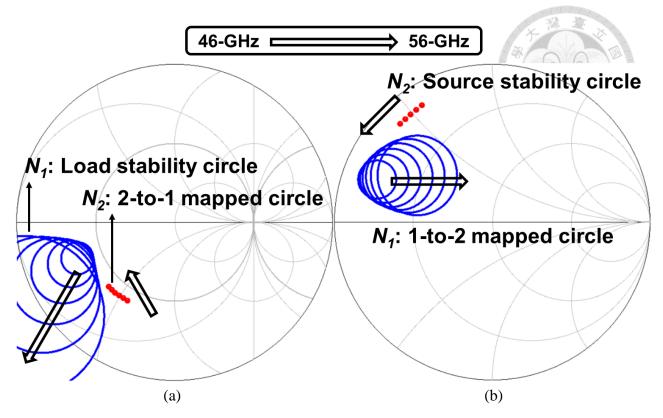

| Fig. 4.17. | Simulated large-signal performance at 110 GHz of the output stage complete with the         |