國立臺灣大學電機資訊學院電子工程學研究所

### 碩士論文

Graduate Institute of Electronics Engineering College of Electrical Engineering & Computer Science National Taiwan University Master Thesis

利用動態相位控制機制之快速鎖定

全數位鎖相迴路

An All-Digital Phase-Locked Loop with Dynamic Phase Control for Fast Locking

莊昀蓁

ぞ・学

Chuang, Yun-Chen

指導教授:林宗賢 博士

Advisor: Lin, Tsung-Hsien, Ph.D.

中華民國一百年五月

May, 2011

## 國立臺灣大學碩士學位論文 口試委員會審定書

利用動態相位控制機制之快速鎖定全數位鎖相迴路

## An All-Digital Phase-Locked Loop with Dynamic Phase Control for Fast Locking

本論文係 莊昀蓁君(R97943006)在國立臺灣大學電子工程研究 所 ICS 組完成之碩士學位論文,於民國 100 年 5 月 5 日承下列考試委 員審查通過及口試及格,特此證明

口試委員:

| ·武女貝· | 77732                                |  |

|-------|--------------------------------------|--|

|       | ···································· |  |

|       | 「「「「                                 |  |

| 主任、所長 | 張耀文                                  |  |

|       | 1                                    |  |

An All-Digital Phase-Locked Loop with Dynamic Phase Control for Fast Locking

By

Yun-Chen Chuang

### THESIS

Submitted in partial fulfillment of the requirement for the degree of Master of Science in Electronics Engineering at National Taiwan University Taipei, Taiwan, R.O.C.

May 2011

Approved by :

ale Jon-they Lee Sten-Tuan

Advised by: Approved by Director: <u>Maconen</u> Chang

### 致謝

三年充實的研究所生涯,隨著這本論文的完成即將畫下句點。一方面為自己 完成了碩士學位感到開心,另一方面卻對這段學校生活有著種種不捨的心情。

首先要特別感謝我的指導教授林宗賢博士。很感謝當初有機會能讓我在老師 的研究團隊中逐步學習、成長。研究上,在遭遇瓶頸時教授適時為我指引方向, 在與教授的討論中,我學習到做研究應有的態度和解決問題的方法。日常生活中, 教授也對我們賦予關愛,能讓我們有勇氣持續堅持、努力。

感謝口試委員劉深淵教授、李泰成教授與魏駿愷博士抽空前來給我們指導, 提供了許多論文、晶片實作與設計上的建議與經驗分享,讓我的論文能更臻於完 善。

感謝 BL430 晶片研發實驗室的大家,很幸運能認識這麼好的一群人。感謝博 士班學長,劉耀鴻(Mark)、黃柏勳(勳爺)、邱威豪(豪哥)、蔡宜霖(Jolin)、吴俊寬 (copa)學長,在研究方面提供許多寶貴經驗。尤其是勳爺與 Jolin 總是不吝嗇分享 很多電路與 Layout 的技巧,也時常關心我的研究進度,謝謝你們。感謝 95 級的 學長姐,廖冠超(超哥)、陳昱諭(yuyu 學姊)、楊承勳、周健榮、方語賢,感謝你 們提供許多寶貴的經驗,讓我們能依循學長姐的腳步前進。感謝 96 級的學長姐, 王麒雲(奶哥)、程健源(Mike)、劉慧賢(老外一學姊)、黃昱翔、何承諺,因為你們 的優秀表現,成為我心中不變的偶像,謝謝學長姐教導我們研究上的工作,也帶 我們出去玩,留下許多美好的回憶。最需要感謝的是同屆的同學,劉崴寧(A0)、 詹瑋珊(zion)、張育誠(小青蛙)、羅皓鴻(小羅),一起修課、一起熬夜下線,一起 經歷了最困難與最快樂的日子,未來也期待這份難得的友誼會永遠持續下去。尤 其是我的好鄰居 A0,從碩一就坐在你旁邊,雖然你位子有點亂,但是我很高興能 夠認識像你這麼特別的人,除了研究之外,也在人生的想法上提供我很多不同的 面向。98 級的學弟們,林振堅(阿堅)、許守鎮(D4)、蕭博允(小三)、陳立廣(阿廣)、

VII

我有任何困難時,你們總是很樂意傾聽、並伸出援手,跟你們的相處也讓我學習 到很多日常生活上的各種知識;99級的學弟們,涂智展(J大)、林君豫(kiwi)、劉 承恩(Jeff)、陳建祐(龍哥)、黃必青,謝謝能夠和這麼好相處的你們在同一個實驗 室,平常能夠自在地聊天、吃晚餐、聽你們打嘴砲。正各自在為研究努力的學弟 們,實驗室的未來就交給你們了。

另外也要感謝電子所的女孩們,黃婷筠(浪子)、吳璧儒(鴨子)、黃敬婷、范 姜敏容,太幸運能跟你們成為好朋友,因為有你們的陪伴就覺得所有的壓力都能 一掃而空。尤其感謝鴨子,你總是會讓我覺得非常溫暖。

最後,卻也是最重要的,要感謝家人無私的關愛與包容。感謝爸爸、媽媽讓 我在心情煩悶時總是能感受到家庭的溫暖,感謝哥哥時常關心我實驗室生活、在 研究上面也願意與我討論不同領域的知識。謝謝你們一路的支持與幫助,也不時 督促我要趕快畢業,今天我才能順利地完成碩士學位。在此,將此論文獻給最親 愛的家人。

# To My Dear Family

謹獻給我的家人

摘要

本篇論文實現了一個利用動態時間窗來控制相位資訊的全數位鎖相迴路,實 作上提出雙模式雙路徑的操作來達成快速鎖定與低時脈抖動的特性。補償相位的 路徑利用動態改變除數的方式,而頻率的修正則由前饋路徑直接調變數位振盪 器。除此之外,雙模式的設定使得迴路在鎖定後能切換至窄頻寬且妥善設計其阻 尼係數。由於在鎖定過程中,鎖相迴路維持在一個較小的相位誤差,因此鎖定時 間可有效地縮短;可程式化的數位濾波器設計也使得鎖定後的效能能夠獲得控 制。在電路層面上,使用不對稱延遲單元減少在時序數位轉換器的功耗與面積, 後端具有錯誤校正的編碼器可用來減輕時序放大電路的規格要求;數位振盪器的 部分,則是選擇具有較細解析度與較佳相位雜訊之電感電容架構。因此,提出之 系統架構可實現一低時脈抖動與快速鎖定的全數位鎖相迴路。

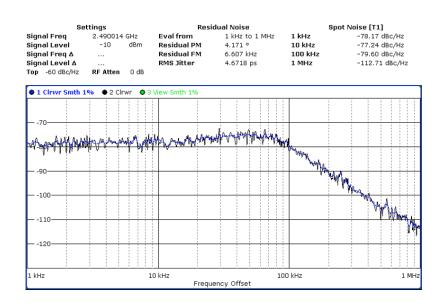

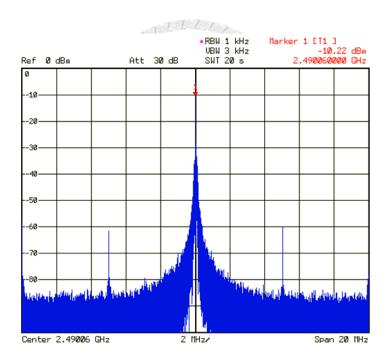

使用台積電 0.18 微米製程設計一應用於 2.4 GHz 頻帶之全數位頻率合成器。 在 5-25 MHz 的跳頻距離下,鎖定時間皆小於 5 µs;中心頻率為 2.49 GHz 時,量 測到的時脈抖動為 1.93 ps,相位雜訊於 100 kHz 與 1 MHz 頻率偏移下分別為-79.6 dBc/Hz 和-112.7 dBc/Hz,參考頻率突波於 5 MHz 頻率偏移下低於-50 dBc。整個 鎖相迴路操作在 1.8 V 共花費 10.35 mA 電流,晶片面積為 1.8 mm<sup>2</sup>。

IX

This thesis presents an all-digital phase-locked loop (ADPLL) featuring a dynamic phase compensation by a set of the auxiliary timing window. When frequency hopping occurs, the compensation scheme is implemented in both frequency and phase domain for fast settling. The detected phase error is continuously sent to the divider chain which changes the divider ratio, and directly modulates the frequency of the digital-controlled oscillator (DCO) through a digital feed-forward path at the same time. The proposed method allows the ADPLL maintaining a small phase error throughout the frequency acquisition process; thereby reducing setting time. Because of the switching mode operation, the mentioned techniques can solve the trade-off between low jitter and fast lock. An uneven-step time-to-digital converter (TDC) with an error correction encoder is implemented to relax circuit design and save power consumption. The DCO adopts the LC-based architecture because it has the finer tuning gain and better phase noise performance. The proposed ADPLL is implemented to optimize timing jitter and lock time.

The proposed technique is incorporated in the design of a 2.4 GHz ADPLL and fabricated in the TSMC 0.18  $\mu$ m CMOS technology. With less than 5  $\mu$ s lock time in hopping frequency from 5 MHz to 25 MHz, the measured rms jitter from a 2.49 GHz carrier is about 1.93 ps. The phase noise at 100 kHz and 1 MHz is -79.6 dBc/Hz and -112.7 dBc/Hz, respectively. The reference spur at 5 MHz offset is under -50 dBc. The whole circuit dissipates 10.35 mA from a 1.8 V supply and the chip area is 1.8 mm<sup>2</sup>.

## Table of Contents

| Chapter 1 Introduction                                                   | 1  |

|--------------------------------------------------------------------------|----|

| 1.1 Motivation                                                           | 1  |

| 1.2 Thesis Overview                                                      | 2  |

| Chapter 2 Introduction to All-Digital Phase-Locked Loops (ADPLLs)        | 3  |

| 2.1 The Basics of Analog Phase-Locked Loop (PLL)                         | 3  |

| 2.2 State of the Art ADPLLs                                              | 5  |

| 2.3 The Basics of ADPLL Building Blocks and Modeling                     | 7  |

| 2.3.1 Phase/Frequency Detector (PFD) and Time-to-Digital Converter (TDC) | 8  |

| 2.3.2 Digital Loop Filter (DLF) and Digital-Controlled Oscillator (DCO)  | 9  |

| 2.3.3 Divider                                                            | 11 |

| 2.4 Summary                                                              | 13 |

| Chapter 3 A Fast-Locking ADPLL using Dynamic Phase Control               |    |

| 3.1 Introduction                                                         |    |

| 3.2 Principle of the Proposed Method                                     | 16 |

| 3.2.1 Background                                                         | 17 |

| 3.2.2 Phase Error Compensation                                           | 18 |

| 3.2.3 Proposed ADPLL Architecture                                        | 20 |

| 3.2.4 Control Mechanism of DLF                                           | 23 |

| 3.3 Linear Model Analysis of Proposed ADPLL                              | 24 |

| 3.3.1 ADPLL in Frequency Acquisition Mode                                | 24 |

| 3.3.2 ADPLL in Phase Tracking Mode                                       | 26 |

| 3.3.3 Stability Analysis                                                 | 28 |

| 3.3.4 Transient Behavior                                                 | 30 |

| 3.3.5 Output Spur                                                        | 31 |

| 3.3.6 Phase Noise and Jitter                                             | 32 |

| 3.3.7 Design Example and Behavior System Simulation                      | 36 |

| Chapter 4 Design and Implementation of the ADPLL                         | 42 |

| 4.1 Circuit Implementations                                              |    |

| 4.1.1 PFD and TDC                                                        | 42 |

| 4.1.2 Divider                                                            | 47 |

| 4.1.3 DCO                                                                | 50 |

| 4.1.4 DLF and Delta-Sigma Modulator (DSM)                                | 57 |

| Chapter 5 Experimental Results                               | 59 |

|--------------------------------------------------------------|----|

| 5.1 Test Setup                                               | 59 |

| 5.2 Chip Pin Configurations and Printed Circuit Board Design | 60 |

| 5.2.1 Chip Pin Configurations                                | 60 |

| 5.2.2 Printed Circuit Board (PCB) Design                     | 61 |

| 5.3 The DC supply Regulator                                  | 62 |

| 5.4 Experimental Results                                     | 63 |

| 5.4.1 Lock Time Measurement Results                          | 63 |

| 5.4.2 Timing Jitter Measurement Results                      | 65 |

| 5.4.3 Phase Noise and Reference Spur Measurement Results     | 66 |

| 5.5 Summary of Measured Results                              | 67 |

| Chapter 6 Conclusions and Future Work                        | 70 |

| 6.1 Conclusions                                              | 70 |

| 6.2 Future work                                              | 70 |

| References                                                   |    |

## List of Figures

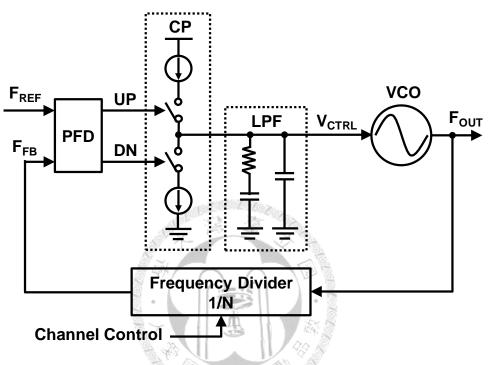

| Fig. 2-1 | The block diagram of a typical CP PLL                                            |

|----------|----------------------------------------------------------------------------------|

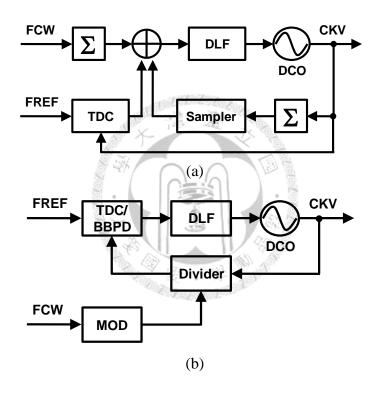

| Fig. 2-2 | Two alternatives of ADPLLs: (a) the ADPLL without divider, and (b) the           |

|          | ADPLL with divider                                                               |

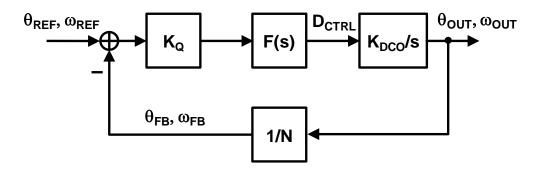

| Fig. 2-3 | The linear model of a typical ADPLL in phase domain7                             |

| Fig. 2-4 | The analysis of a classical delay-chain TDC in (a) the conceptual brief, and (b) |

|          | the linear model                                                                 |

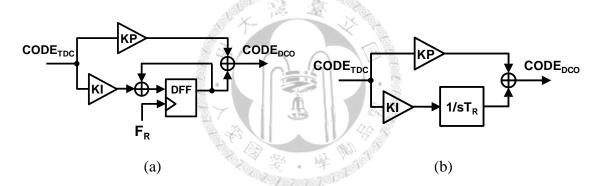

| Fig. 2-5 | DLF for a type-II second-order ADPLL: (a) block diagram, and (b) Linear          |

|          | model                                                                            |

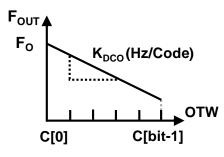

| Fig. 2-6 | Input-output characteristic of the DCO 10                                        |

|          | Linear model of the DCO                                                          |

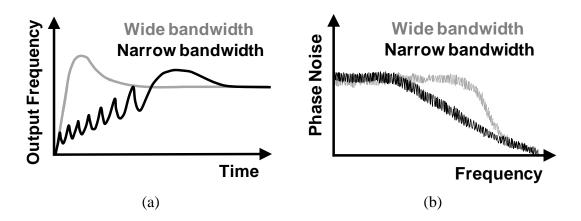

| Fig. 3-1 | The impacts of different loop bandwidths on (a) settling time, and (b) phase     |

|          | noise                                                                            |

| Fig. 3-2 | Block diagram of a PLL with bandwidth switching method                           |

| Fig. 3-3 | Block diagram of a PLL with frequency presetting                                 |

| Fig. 3-4 | Conceptual locking process in typical ADPLL and ADPLL with phase error           |

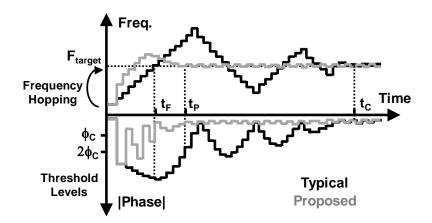

|          | compensation                                                                     |

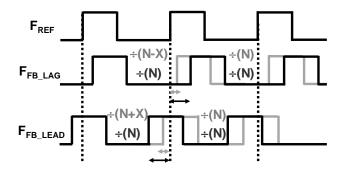

| Fig. 3-5 | The timing diagram of divider ratio modification for phase error compensation.   |

|          |                                                                                  |

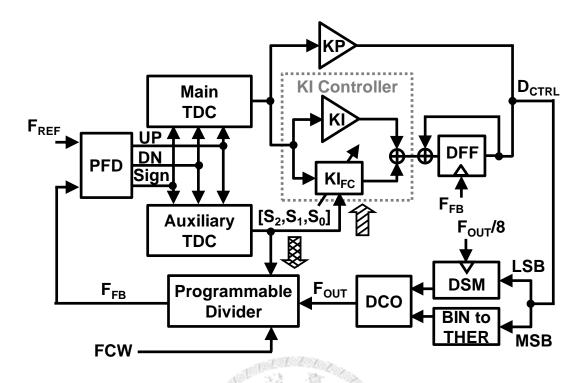

| Fig. 3-6 | The proposed dynamic phase control ADPLL                                         |

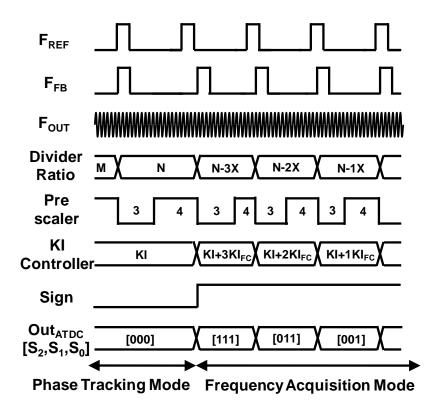

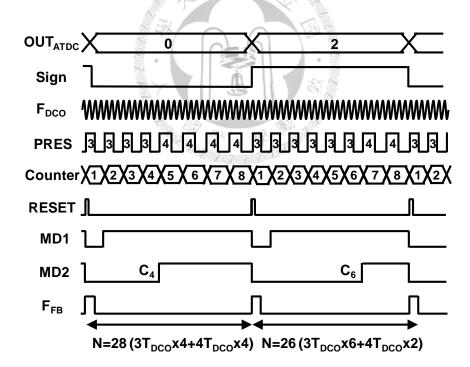

| Fig. 3-7 | Operation timing diagram of the proposed architecture                            |

| Fig. 3-8 | The linear model of the proposed ADPLL in frequency acquisition mode 24          |

| Fig. 3-9 | The linear model of the proposed ADPLL in phase tracking mode                    |

| Fig. 3-1 | 0 Bode plots in (a) frequency acquisition mode, and (b) phase tracking mode. 29  |

| Fig. 3-11 The timing waveform and spectrum in different case: (a) ideal, and (b) real. 33  |

|--------------------------------------------------------------------------------------------|

| Fig. 3-12 The linear model of a ADPLL with internal and external noise sources 33          |

| Fig. 3-13 Behavior model of the proposed ADPLL in Matlab Simulink                          |

| Fig. 3-14 Bode plot of the ADPLL in (a) open loop simulation, and (b) closed loop          |

| simulation                                                                                 |

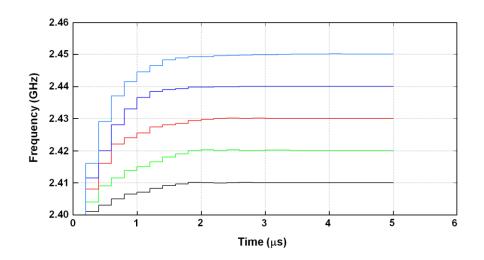

| Fig. 3-15 Simulated locking behaviors for various frequency hopping distances              |

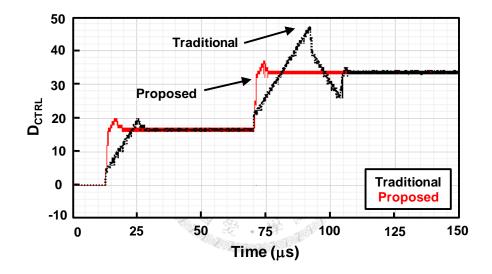

| Fig. 3-16 Comparison of locking behaviors between traditional ADPLL and the                |

| proposed ADPLL under the same loop bandwidth and damping factor                            |

| Fig. 4-1 DFF based PFD (a) the block diagram, and (b) the timing diagram                   |

| Fig. 4-2 The schematic of the current-controlled delay cell                                |

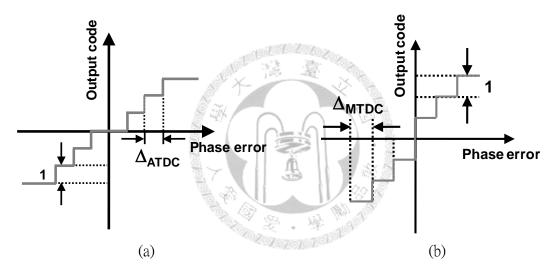

| Fig. 4-3 The characteristic curves of (a) auxiliary TDC, and (b) main TDC 44               |

| Fig. 4-4 An uneven-step Vernier TDC in (a) 5-bit architecture, and (b) a conceptual        |

| diagram for 3-bit TDC 45                                                                   |

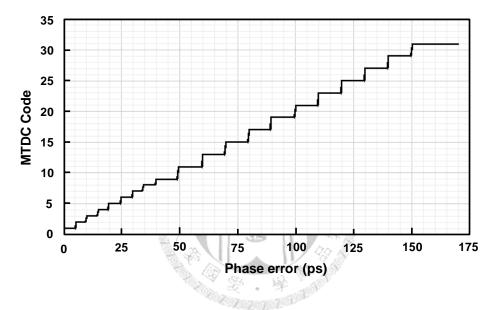

| Fig. 4-5 The simulation result of 5-bit uneven-step TDC                                    |

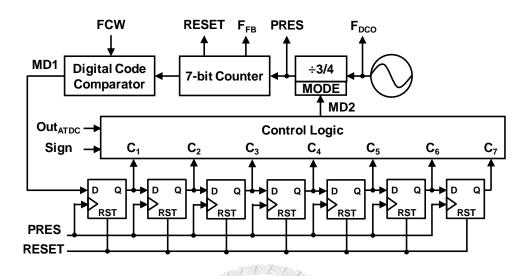

| Fig. 4-6 Modified programmable divider for phase compensation purpose                      |

| Fig. 4-7 The design of divider chain: an example illustrated by timing diagram with 3-bit  |

| counter                                                                                    |

| Fig. 4-8 The modified $\div 3/4$ dual-modulus divider: (a) the modified structure, (b) the |

| operated timing diagram under $\div 3$ mode, and (c) the operated timing diagram           |

| under ÷4 mode                                                                              |

| Fig. 4-9 Implemented block diagram of DCO system: (a) architecture, and (b) varactor       |

| array                                                                                      |

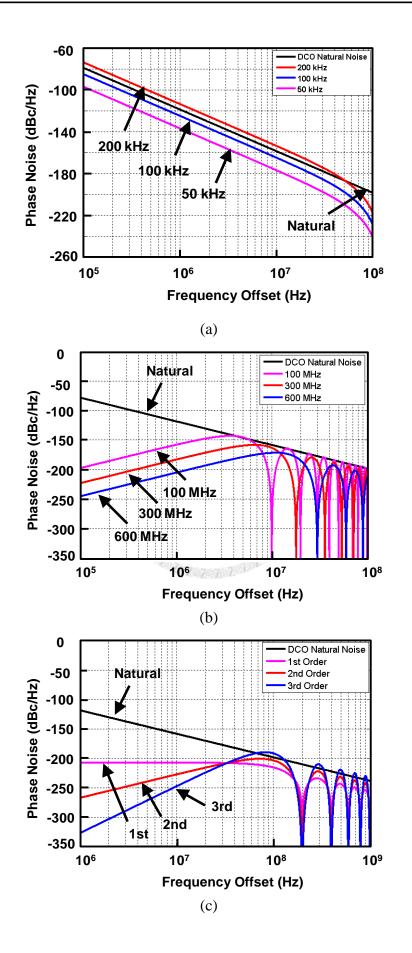

| Fig. 4-10 Phase noise due to frequency quantization with (a) different frequency           |

| resolution step, (b) different dithering frequency of $\Sigma\Delta$ modulator, and (c)    |

| different order of $\Sigma\Delta$ modulator                                                |

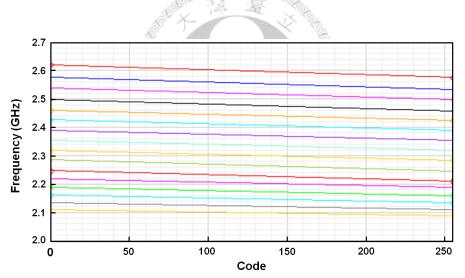

| Fig. 4-11 The DCO tuning curves simulation results                                         |

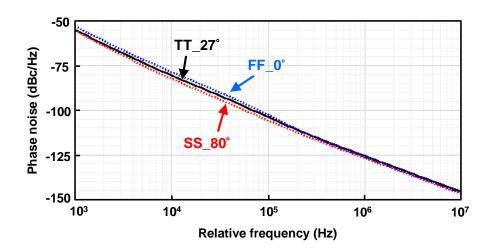

| Fig. 4-12 DCO phase noise simulation results                                           |

|----------------------------------------------------------------------------------------|

| Fig. 4-13 Block diagram of the DLF for a type-II second-order ADPLL 58                 |

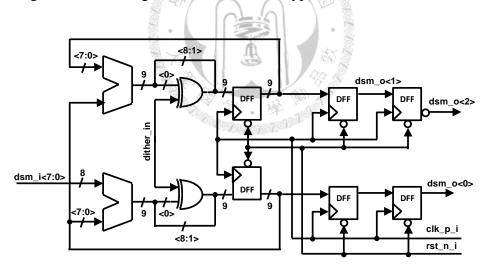

| Fig. 4-14 Block diagram of the second-order MASH-II $\Sigma\Delta$ modulator           |

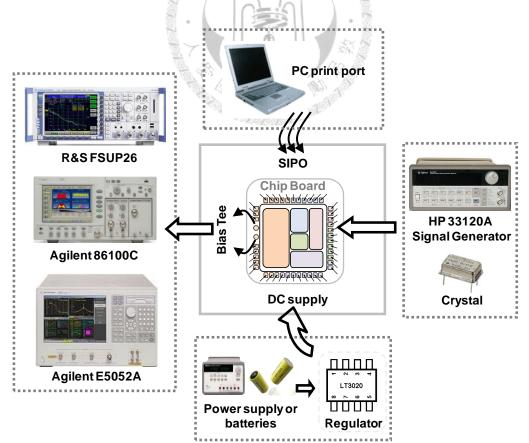

| Fig. 5-1 Measurement setup 59                                                          |

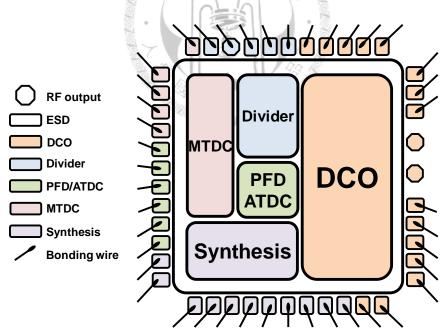

| Fig. 5-2 Pin configurations and power domain diagram                                   |

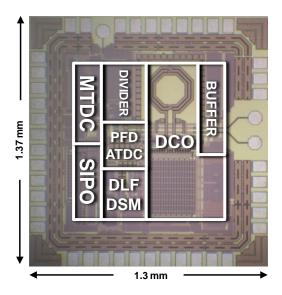

| Fig. 5-3 Die photo of this work 61                                                     |

| Fig. 5-4 Fabricated PCB for measurement: (a) top view, and (b) bottom view 61          |

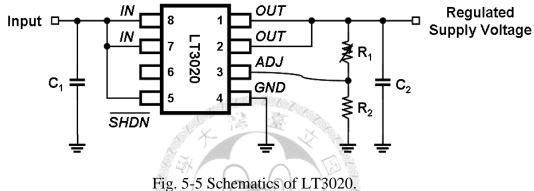

| Fig. 5-5 Schematics of LT3020                                                          |

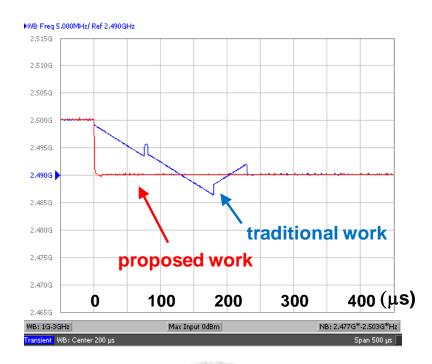

| Fig. 5-6 The comparison on settling behavior under different approaches by monitoring  |

| DCO output frequency to settle within $\pm 100$ ppm of desired frequency. (blue:       |

| traditional work, and red: proposed work) 64                                           |

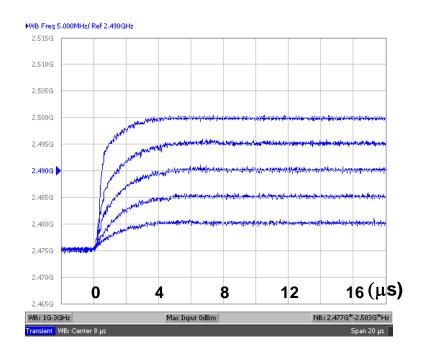

| Fig. 5-7 The settling behavior under different hopping frequency by using the proposed |

| dynamic phase control technique                                                        |

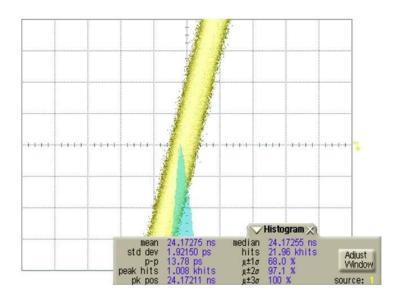

| Fig. 5-8 The measured jitter histogram                                                 |

| Fig. 5-9 The measured phase noise at 2.49 GHz output frequency                         |

| Fig. 5-10 The measured output spectrum at 2.49 GHz output frequency                    |

## List of Tables

| Table 5-1 Measured performance summary | 68 |

|----------------------------------------|----|

| Table 5-2 ADPLL performance comparison | 69 |

## Chapter 1 Introduction

### **1.1 Motivation**

Frequency synthesizers are the key building blocks for most of modern electronics and communication systems, including radio receivers, mobile telephones, and satellite receivers. A typical wireless communication system incorporates a RF transceiver to convert a RF signal down to a base-band signal, or convert a base-band signal up to a RF signal. Therefore, a local oscillator (LO) is required in most RF transceivers. For different communication channels, the frequency of LO signal is demanded to be programmable, which is usually generated by phase-locked loop (PLL) based frequency synthesizer.

With the explosive growth of the wireless communication, the need has arisen to reduce cost and power consumption of mobile devices. The demand for high-level integration and maximal flexibility can be best achieved using a digital or digital-intensive approach. Considering the circuit design of system-on-chip (SoC) in the future deep sub-micron CMOS technologies, the integration of high performance analog synthesizers on the same silicon together with massive and high speed digital cores will become more and more challenging. In this sense, the robustness of the synthesizers against noise from the supplies or from the substrate will be a major issue. Therefore, the emerging of all-digital phase-locked loop (ADPLL) architectures is an important example for wireless applications [1]-[3].

The settling time of the frequency synthesizer is an important performance. For most time-division multiple access (TDMA) communication systems, the synthesizers have to switch to another frequency in a restricted time slot, otherwise it may degrade the data rate. On the other hand, the quality of the wireless communication is greatly affected by the performance of the frequency synthesizer, such as phase noise, spur performance, power consumption, and fabricated cost. In general, a small loop bandwidth PLL is needed to suppress the timing jitter, but it leads to a slow settling speed at the same time. For a conventional structure, it may fail to satisfy stringent communication specifications even if ADPLLs are a new trend.

The 2.4 GHz industrial, scientific and medical (ISM) band is widely used by various wireless systems, such as wireless local area network (WLAN), Bluetooth and Zigbee. In this thesis, a digital LC-PLL using dynamic phase control for 2.4 GHz ISM band application is presented. The goal is to deal with the trade-offs between settling time and jitter performance.

### **1.2 Thesis Overview**

This thesis is composed of six chapters. In Chapter 2, the fundamental introduction in analog PLLs and ADPLLs will be shortly addressed. Furthermore, the building blocks and modeling of basic ADPLLs are illustrated. In Chapter 3, the proposed ADPLL is presented for fast locking without damaging its jitter performance. In this chapter, the proposed techniques are introduced and analyzed with the loop linear model and design considerations. Chapter 4 shows circuit implementations of the important building blocks. Chapter 5 shows measurement results of the proposed ADPLL as well as the comparison of conventional ADPLLs and this work. Finally, the conclusions and future work of this thesis are described in Chapter 6.

### Chapter 2

## Introduction to All-Digital Phase-Locked Loops (ADPLLs)

### 2.1 The Basics of Analog Phase-Locked Loop (PLL)

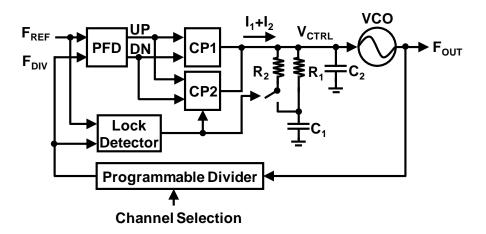

Based on the operation principle of a simple PLL [4], the charge pump PLL (CP PLL) is developed as shown in Fig. 2-1. It is the most popular way to synthesize the frequency in wireless communication.  $F_{REF}$  is input reference frequency and  $F_{FB}$  is the output frequency of voltage-controlled oscillator (VCO) divided by frequency divider, N. The phases of  $F_{REF}$  and  $F_{FB}$  are compared by phase/frequency detector (PFD) which estimates the time difference between their closest edges, and then the CP charge/discharge the low pass filter (LPF) according to the UP/DN pulse. The current pulse generated by CP is converted into the control voltage,  $V_{CTRL}$ , through the LPF. The main task of LPF is to suppress the glitches introduced by CP in every phase comparison. The loop automatically adjusts the VCO control voltage by the feedback mechanism. After the loop is locked, the output frequency is the multiple frequency of  $F_{REF}$ , which is

$$F_{OUT} = N \times F_{FB} = N \times F_{REF}. \tag{2-1}$$

As the nano-meter CMOS technology advances, a highly integrated system is required. However, the implementation of traditional RF and analog circuits is more complicated in the deep-submicron CMOS. Analog PLLs may encounter capacitor leakage, current mismatch, and limited dynamic range under low supply voltage, leading to higher noise floor and spurious tone. The design of a high performance analog synthesizer becomes a big challenge in the future. Consequently, the digital-intensive approach can relax this situation and allow more digital switching noise to be coupled into the high precision analog section through the power supply network and the low resistance substrate.

Fig. 2-1 The block diagram of a typical CP PLL.

There are many advantages in digital solution compared to analog one. The digital approach improves time-to-market due to reusable modules and portable process. The lack of on-chip passive components and analog functional blocks reduces sensitivity to process-voltage-temperature (PVT) variations. It brings major benefits of solving the design issues including current mismatch, capacitor leakage and shrunk dynamic range in analog implementation. Area occupation, possibly power consumption will be decreased. The production test of the synthesizer can be done using straightforward digital methods, like built-in self-test (BIST). The control signal in systematical calibration block can also be recorded and performed by an auxiliary memory since the digital nature of ADPLL. However, the digital approach of the frequency synthesizers

will face the problems about finite resolution and quantization error. In the next section, some of the state of the art ADPLLs will be illustrated.

### 2.2 State of the Art ADPLLs

In the 1970's, there are several papers about digital frequency synthesizers [5]-[7]. However, because of the lack of a practical low jitter digital-controlled oscillator (DCO), the achievable performance in digital PLLs were far away from those of the analog loops. In the 1980's, the development of the CP PLL with type-IV PFD, removed some limitations of prior analog PLLs based on the multiplier phase detector. This fact finally discarded the hopes of digital PLLs to catch up with the performances of analog ones. For all 80's and 90's high performance frequency synthesizers, they were almost implemented by the analog architecture. However, the attention of recent researches has moved into digital loops due to advanced processes. The current researches are studied on ADPLL which is a semi-analog system but all input/output control of building blocks defined as digital level. A digital loop has been proposed and implemented in [8]. The lack of a low jitter DCO has been overcome by connecting a digital-to-analog converter between the digital filter and a conventional analog VCO. The work [9] presents the architecture based on  $\Delta\Sigma$  noise shaping which could achieve better performances in a discrete-time operation.

There are two alternatives of ADPLLs according to the existence of the divider block. First, the phase domain ADPLL without divider was reported in [10], which allows its loop control circuit to be implemented in a fully digital manner. Its block diagram is shown in Fig. 2-2 (a). The phase error is resolved by subtracting the integral and fractional timing information from reference phase. Due to the edge counting nature, the quantization resolution is limited by the DCO clock period. For wireless applications, a finer resolution is required. Therefore, a time-to-digital converter (TDC) is achieved for the purpose of the fractional error correction. The reference phase is obtained by accumulating the frequency command word (FCW); the integral part is determined by counting the number of DCO rising edge while the fractional part measures the time difference between the reference clock and the next rising edge of the DCO clock. Then, the calculated amount is filtered by a digital loop filter (DLF). Finally, the output of DLF is fed to DCO to adjust the output frequency. Besides, it is important to deal with the accuracy of the DCO period normalization factor in TDC.

Fig. 2-2 Two alternatives of ADPLLs: (a) the ADPLL without divider, and (b) the ADPLL with divider.

Another ADPLL structure with divider is illustrated in Fig. 2-2 (b). According to the method of the phase sensing, the ADPLL with divider can be roughly classified into two categories. They are bang-bang based ADPLL for binary phase detection [11] and TDC based ADPLL for linear phase detection [12], respectively. These frames look understandable because the building blocks are converted from traditional analog PLLs. The phase error is digitized by the quantization circuit, such as bang-bang phase detector (BBPD) or TDC. This digital output code is proportional to the phase error between the reference clock and feedback clock. After processed by DLF, the filtered value is sent to DCO monitoring the output drift in a negative feedback manner. The bang-bang based ADPLL only provides tri-state output which cannot reflect the magnitude of phase error. For this reason, the bandwidth and ability of the frequency tracking in TDC based ADPLL are better than bang-bang based ADPLL, but the TDC design is more sensitive to environment variation.

### 2.3 The Basics of ADPLL Building Blocks and Modeling

The major difference between analog PLL and ADPLL is the controlled interconnection. All of the control signals in analog PLL are processed in analog voltage and current domains. In an ADPLL, the control signals are processed by digital code. Because of the discrete-time operations and quantization effect, some modification and approximation are required to model an ADPLL in order to make the linear analysis method available [13].

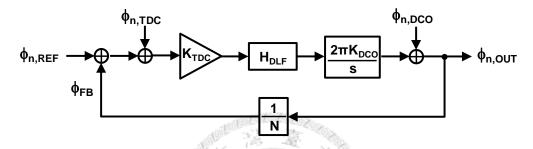

The essential components of a TDC based ADPLL includes PFD, TDC, DLF, DCO and divider. The phase-domain model of a typical ADPLL is shown in Fig. 2-3. In the next section, the models of the building blocks are introduced step by step. Once the linear model is built, the stability and dynamic of the loop can be analyzed.

Fig. 2-3 The linear model of a typical ADPLL in phase domain.

### 2.3.1 Phase/Frequency Detector (PFD) and Time-to-Digital Converter (TDC)

The main purpose of a PFD is to detect the phase error between  $\theta_{REF}$  and  $\theta_{FB}$ . The phase-domain model can be simply expressed by a subtractor in Fig. 2-3. The phase error is distinguished by the timing difference of UP/DN pulse and then sent to the quantizer. Followed by a PFD, the TDC based quantizer is utilized. The conceptual structure and waveform is shown in Fig. 2-4 (a). A TDC, comprised of a chain of delay elements and the sum operator, counts the cell numbers of inverter delays in logic "high". The output from each inverter is an input to a register, which is clocked with the rising edge of a stop signal, *NEXT*. A thermometer code is then generated at the register output corresponding to the measurement interval between *Start* and *NEXT*. Finally, the equivalent binary code sends into DLF. The resolution of TDC is derived from an inverter delay,  $\Delta_{TDC}$ . If the phase difference is much larger than the TDC resolution, the input-output characteristic of PFD/TDC is similar to the transfer curve in the analog-to-digital converter (ADC).

Fig. 2-4 The analysis of a classical delay-chain TDC in (a) the conceptual brief, and (b) the linear model.

The phase difference is converted to time domain by PFD and TDC. The linear model of a TDC has been shown in Fig. 2-4 (b), and the building block can be modeled as a gain plus quantization noise. Accordingly, the transfer function is

$$K_Q = \frac{T_{REF}}{2\pi\Delta_{TDC}} \,. \tag{2-2}$$

There are several sources which affect the performance of a TDC, including quantization error, linearity issue, and randomness due to thermal effect. In the closed-loop operation, the TDC quantization of timing estimation affects the phase noise at the ADPLL output. Similar to ADC quantization process calculations, the quantization noise of TDC can be derived from assuming the white noise with uniformly distributed as shown in [14]:

$$S_{Q,TDC}(s) = \frac{\Delta_{TDC}^2}{12}$$

(2-3)

It is a low-pass transfer function from TDC noise. Therefore, the output phase noise introduced by the TDC is

$$S_{\varphi,OUT}(s) = \frac{\left(2\pi\Delta_{TDC}\right)^2}{12T_{REF}} \left|\frac{NG(s)}{1+G(s)}\right|^2,$$

(2-4)

where  $T_{REF}$  is the reference period, *N* is divider ratio, and G(s) is the open loop gain of ADPLL. It reveals that the noise contribution from TDC could be minimized by improving the TDC resolution and increasing the sampling rate.

#### **2.3.2 Digital Loop Filter (DLF) and Digital-Controlled Oscillator (DCO)**

Choosing different DLF structures affect the type and order of ADPLL. The type-I PLL generally features faster dynamics, but the steady phase error does not go to zero in place of a constant amount which is proportional to the frequency offset. Compared with the type-I first-order ADPLL by only a proportional gain in DLF, a type-II second-order ADPLL has the advantages of good DCO noise attenuation, small static phase error as the loop locked, and better design flexibility between bandwidth and tracking ability. Fig. 2-5 shows the block diagram of proportional-integral (PI) controller and s-domain linear model of DLF for a type-II second-order ADPLL. The integral path is made by a digital accumulator. In mathematical analysis, the integrator is replaced by  $z^{-1}/1-z^{-1}$  in the z-domain model, and then converted into s-domain model using  $s=F_R(z-1)$  with a reasonable assumption of the frequency much smaller than  $F_R$  [15]. In order to achieve more noise attenuation, a higher order ADPLL which cascades with a single-pole IIR filter can be chosen [13].

Fig. 2-5 DLF for a type-II second-order ADPLL: (a) block diagram, and (b) Linear model.

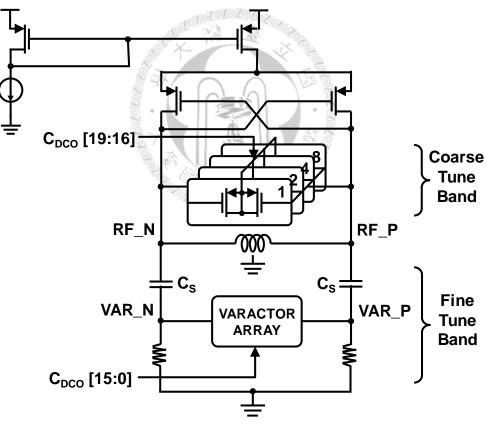

DCO is a crucial building block in an ADPLL system. It converts control code to modulate the output frequency according to the phase error in PFD. The input-output characteristic curve is shown in Fig. 2-6.

Fig. 2-6 Input-output characteristic of the DCO.

The relationship between the digital oscillator tuning word (OTW) and output frequency ( $F_{OUT}$ ) can be expressed by

$$F_{OUT} = F_O + K_{DCO}OTW , \qquad (2-5)$$

where  $F_O$  is the output free-running frequency of DCO when OTW is zero, and  $K_{DCO}$  is the gain of its transfer function.

In order to improve the frequency resolution in digital operation, a delta-sigma modulation (DSM) is implemented between a DLF and DCO. Finally, a DCO has two noise sources including nature noises (e.g., thermal noises and flicker noises of components ( $S_N$ ) and additional noises derived from DSM ( $S_Q$ )). The s-domain linear model is shown in Fig. 2-7. The mathematical analysis will be described in 4.1.3 in detail.

$$X[n] \xrightarrow{S_Q(f)} K_{DCO} \xrightarrow{Z_{\pi/S}} \Phi_{DCO}(t)$$

Fig. 2-7 Linear model of the DCO.

#### 2.3.3 Divider

In time-domain, the gain of the frequency divider is simply a scale factor, N. However, the effect of the frequency division in the phase-domain is phase modulation. The phase of the input signal is modulated by a sinusoidal signal with the modulation frequency,  $\omega_m$ , which is

$$\phi_{in}(t) = \omega_{in}t + \phi_d \sin(\omega_m t), \qquad (2-6)$$

where  $\phi_d$  is peak phase deviation magnitude of the input signal. According to the relationship between frequency and phase, the instantaneous frequency is the derivative of the input phase, and it can be expressed as

$$\omega_{inst}(t) = \frac{1}{2\pi} \frac{d\phi_{in}(t)}{dt} = \omega_{in} + \phi_d \omega_m \cos(\omega_m t).$$

(2-7)

After the divide ratio is specified by channel selection, the output frequency of the divider can be rewritten as

$$\omega_{div}(t) = \frac{\omega_{inst}}{N} = \frac{\omega_{in}}{N} + \frac{\phi_d \omega_m \cos(\omega_m t)}{N}.$$

(2-8)

Taking the integral value of  $\omega_{div}$ , and then the phase of the output signal can be derived as follows:

$$\phi_{div}(t) = \int \omega_{div}(t) dt = \frac{\omega_{in}t}{N} + \frac{\phi_d \sin(\omega_m t)}{N} = \frac{\phi_{in}(t)}{N}.$$

(2-9)

Eq. (2-9) shows the input phase deviation magnitude is inversely proportional to the divide ratio, *N*. Besides, the modulation frequency,  $\omega_m$ , is not influenced by the frequency divider. Eventually, the phase-domain transfer function of the frequency divider only behaves as a gain stage with value 1/N.

On the other hand, the choosing of a different divider ratio is related to output noise performance. Phase noise is a critical specification in the local oscillator of radio systems. It is a ratio of noise power to output carrier power in a 1 Hz bandwidth at a given offset from the carrier. This performance typically bears on the receiver sensitivity. The total phase noise in a PLL can be expressed as [4]

$$L_{total} = L_{in-band} - 10\log f_{REF} - 20\log N , \qquad (2-10)$$

where  $L_{in-band}$  is the phase noise due to the synthesizer itself and  $f_{REF}$  is the input reference frequency.

### 2.4 Summary

This chapter introduced an overview of the basic principle of analog PLLs. The previous works of ADPLLs and their categories were first developed. The phase-domain formation of each building block for linear model analysis was finally derived.

## Chapter 3 A Fast-Locking ADPLL using Dynamic Phase Control

### 3.1 Introduction

PLL based frequency synthesizer is an essential component in wireless communication system. Many communication standards have stringent requirement on the settling time of frequency synthesizer. A typical PLL can be approximated as an under-damped second-order system. The settling time of PLL is governed by loop bandwidth and damping factor. We can express the settling time as below [16]:

$$t_{s} = \frac{-1}{\zeta \omega_{n}} ln \left( \frac{f_{tol} \sqrt{1 - \zeta^{2}}}{N \Delta \omega} \right).$$

(3-1)

$\zeta$  is the damping factor,  $\omega_n$  is the nature frequency,  $f_{tol}$  is frequency tolerance range, and N is divider ratio. From the equation shown, PLL settling time is inversely proportional to loop bandwidth. A simple way to increase PLL settling speed is to enlarge the loop bandwidth. However, there are some constrains on the choice of the loop bandwidth, because it will directly affect the phase noise and spurs performance.

Fig. 3-1 illustrates the settling time and phase noise under different loop bandwidths [17]. In addition to the design consideration, the loop bandwidth is limited by the stability requirement [18][19]. There exists a well-known rule of thumb in PLL, which is the loop bandwidth should be less than 1/10 of reference frequency. If the loop bandwidth is too wide, the PLL becomes less stable or even fails to lock.

Fig. 3-1 The impacts of different loop bandwidths on (a) settling time, and (b) phase noise.

On the other hand, the multiplication of the DCO gain ( $K_{DCO}$ ) and the proportional gain in DLF (KP) should be minimized under a given integral gain in DLF (KI) to achieve the best performance of an output jitter [20]. In frequency response, the magnitude of the transfer function will have the widest pass-band without any peaking when  $\zeta = 0.707$ . If the transfer function is modeled as A(s) (=Vo(s)/Vin(s)), the normalized peak value,  $M_p$ , is obtained by calculating the slope of A(s),

$$M_{p} = \frac{A(j\omega_{p})}{A_{o}} = \frac{1}{2\zeta\sqrt{1-\zeta^{2}}}.$$

(3-2)

$A_o$  is the dc gain of the transfer function,  $\omega_p$  denotes the frequency as the peaking happened, and  $\zeta$  is the damping factor.

The variance of the long-term PLL absolute jitter is related to the phase noise as [21]

$$\sigma_{t,PLL}^{2} = \frac{1}{\left(2\pi f_{out}\right)^{2}} \int_{-f_{o}/2}^{f_{o}/2} S_{\phi,PLL}(f_{m}) df_{m}, \qquad (3-3)$$

where  $f_{out}$  is the output frequency and  $S_{\phi,PLL}$  is the total phase noise in the system. It is straightforward to calculate the total output phase noise by summing the contributions of the different noise sources. Assuming dominate noise from reference input, jitter performance will degrade with increasing loop bandwidth. More details about phase noise of an ADPLL will be described in Section 3.3.6.

With the increasing of the loop bandwidth for fast locking operation, the noises from PFD/TDC/Divider are much harder to be suppressed. It reveals that a wider loop bandwidth allows more noise and reference spurs to feed through to the output. But a scale-down loop bandwidth produces a phenomenon of cycle slipping because the loop excessively suppresses DCO modulation. For a smaller bandwidth design may make the system close to the instability limit, the jitter is also dramatically regenerated due to frequency peaking [20]. Thus, it is required to design a high-performance PLL based frequency synthesizer to make trade-offs between low jitter and fast lock.

To address those critical issues, an ADPLL with dynamic phase compensation is presented. The system is operated in dual switching manipulations which are frequency acquisition mode and phase tracking mode. Dual-path operations are implemented in feed-forward DCO modulating (frequency compensation path) and dynamic divider adjustment (phase compensation path). In order to verify the idea, the proposed ADPLL is realized at the 2.4 GHz band. Methods to relax design restrictions mentioned above will be described in this section.

### 3.2 Principle of the Proposed Method

In this section, we will introduce certain backgrounds, which are bandwidth switching and frequency presetting for reducing lock time. In addition, implemented topologies of feed-forward function and phase error compensation are introduced in the following. Both of them will be implemented in frequency acquisition mode.

## 3.2.1 Background

Bandwidth switching is the candidate architecture for improving settling time of PLL. Fig. 3-2 depicts a typical PLL which incorporates the bandwidth switching technique. The main idea is to widen loop bandwidth during the locking process and change the loop into a desired narrow bandwidth once the loop is approaching locked state. The architecture is implemented by increasing CP current into  $I_1+I_2$ . Meanwhile, for maintaining the loop stability, the resistance on LPF is reduced to  $R_1//R_2$ . Nevertheless, due to the loop stability effects, the improvement on locking speed will be restricted by the expanding ratio of loop bandwidth. The adjustable loop bandwidth can be done by dynamically adjusting the CP current, VCO gain, divide ratio, and filter parameters [16][22].

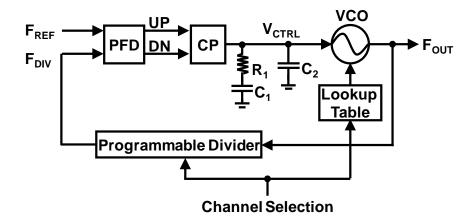

Another common design approach is frequency presetting by utilizing a lookup table [23][24]. Fig. 3-3 shows a sketch of this presetting frequency approach. The lookup table initially records all the proper configurations for each channel. When the frequency hopping occurs, this lookup table enables the PLL to preset the VCO into the desired output frequency according to the memorized configurations. A very fast settling time is then achieved since the output frequency is preset directly. However, it is difficult to generate an accurate lookup table, since the frequency setting configuration for each channel is sensitive to PVT variations. Consequently, this approach often requires complicated calibrations to realize such a lookup table.

Fig. 3-2 Block diagram of a PLL with bandwidth switching method.

Fig. 3-3 Block diagram of a PLL with frequency presetting.

## 3.2.2 Phase Error Compensation

In locking process, the phase error accumulates rapidly on each reference cycle, because the phase error is the integration of frequency error. The locking features are conceptually shown in Fig. 3-4. The conventional transient process leads to a large phase error, which prevents the loop from being locked even though the output frequency at  $t_F$  is correct. With the increasing of the distance of hopping frequency, this phase error grows greatly. Hence, if the phase error can be continuously monitored and well-controlled, the lock time in extra phase tracking can be significantly reduced

$(t_P \ll t_C)$  [16]. This thesis implemented a phase error compensation technique that dynamically cancels integrated phase error during locking process.

Fig. 3-4 Conceptual locking process in typical ADPLL and ADPLL with phase error compensation.

The phase error compensation is accomplished by altering the divider ratio of the programmable divider. The compensation principle is graphically illustrated in Fig. 3-5. For example, if the phase of  $F_{REF}$  leads  $F_{FB\_LAG}$  by a threshold level at a particular cycle, the phase error may grow to a larger value in the next cycle. Thus, the divider ratio is reduced to *N*-*X*, where *X* depends on the phase error magnitude. On the other hand, if  $F_{FB\_LEAD}$  leads  $F_{REF}$ , the divider ratio will be increased to *N*+*X*. According to the threshold levels, this procedure continues until the phase error at the PFD input is sufficiently small.

Fig. 3-5 The timing diagram of divider ratio modification for phase error compensation.

Because the operation of phase error compensation continuously reflects to PFD input, the shrunk phase information has a side effect on restricting DCO frequency update. Therefore, an auxiliary frequency modulation mechanism is required to extend loop bandwidth at the same time when phase error compensation technique is activated. When operating in frequency acquisition mode, both compensation of frequency calibration and phase error adjustment are automatically utilized according to the threshold level.

#### 3.2.3 Proposed ADPLL Architecture

Fig. 3-6 depicts the architecture of the proposed ADPLL. An auxiliary TDC (ATDC) are implemented the timing window to detect the coarse range and polarity of phase error. Based on the amount of phase error, the adjustable delay cell of an ATDC generates corresponding thermometer codes,  $[S_2, S_1, S_0]$ , which is sent into KI controller and programmable divider. The least significant bit (LSB) of ATDC,  $S_0$  is also an important mark to determine the loop operating in different modes. The system is operated in dual-mode which is frequency acquisition mode in binary detection and phase tracking mode in linear detection. We combine dual-path techniques of feed-forward frequency modulation and phase error compensation in frequency acquisition mode to achieve a fast-locking ADPLL. The system chose appropriate loop parameters to optimize damping factor for low-jitter performance. In the beginning of the locking process, the frequency acquisition mode is first activated and the main TDC (MTDC) circuit is modeled as a BBPD. A digital-controlled feed-forward function is used for modulating DCO frequency directly with the slash arrow and a dynamic divider adjustment in phase error compensation path is illustrated with the meshed arrow in Fig. 3-6.

Fig. 3-6 The proposed dynamic phase control ADPLL.

It is known that the principle of typical PLL is to adjust the output frequency by detecting the phase error. Small phase error results in slow frequency switching. When the phase error compensation path is enabled, if phase error is reduced during each reference cycle, it may cause the control code ( $D_{CTRL}$ ) changing slowly to correct the output frequency. To solve this problem, a feed-forward frequency compensation path is incorporated. The main signal path from MTDC to DLF becomes a binary detection without magnitude information of phase error, because the whole range of MTDC is designed smaller than the resolution of ATDC. Thus, it can inject extra gain to modulate DCO frequency by changing KI whenever the phase error compensation is applied, which effectively increases the speed of frequency acquisition. A flexible KI controller is implemented using shift registers and logic operators instead of multipliers. The compensated amount is based on ATDC output. More shift bits are applied if frequency error is large. Besides, the loop stability is not compromised in this structure because the compensation scheme effectively provides a zero in the loop

transfer function [16]. Finally, once this loop approaches locked state, the phase error is adequately small. The ATDC and the associated compensation paths are off. The loop returns to normal TDC based ADPLL operation.

Fig. 3-7 Operation timing diagram of the proposed architecture.

Fig. 3-7 illustrates the operation timing diagram of the proposed method. Once the synthesizer changes to another channel and divide ratio alters from M to N (N>M), an equivalent phase error is generated due to frequency error.  $S_0$  is a mode detection. The quantization feature of ATDC and *Sign* signal reflects phase error between  $F_{REF}$  and  $F_{FB}$ . According to the ATDC output, the divide ratio decreases and the next edge of  $F_{FB}$  arrives earlier to compensate the large phase error. At the same time, the frequency compensation gain,  $KI_{FC}$ , will be regulated by KI controller to speed up locking behavior. The two path compensations are terminated and system sets adapted KP and KI for a stable transfer function. Under this situation, the system maintains the phase

error small enough and the loop bandwidth is narrow without frequency peaking. Therefore, low-jitter characteristic can be realized in locked condition.

#### 3.2.4 Control Mechanism of DLF

We propose a novel method to modulate DCO for frequency compensation with taking advantage of the feed-forward architecture. If the phase subtraction circuit in ADPLL is modeled as a BBPD, it can directly control *KI* in DLF to achieve an inherent compensation function instead of using original analog manners [30][31]. The mechanism has advantages of the digital programmable feature and saves an additional path. The gain of feed-forward frequency compensation will be analyzed in Section 3.3.1.

It is important to design proper loop parameters in order to achieve a low-jitter performance in fast-locking topology. In addition to realizing a frequency modulation path in the locking process, the mechanism of damping factor correction is needed in phase tracking mode. This correction circuit can be employed in the DLF block because of their digital nature in selecting filter parameters. For an expected bandwidth  $(\omega_n)$ , which is determined by *KI*, *KP* can be derived from closed loop transfer function by assuming  $\zeta > 1$ .

$$KP > \frac{2N\Delta_{MTDC}}{T_{REF}K_{DCO}}\omega_n, \qquad (3-4)$$

where *N* is divider ratio;  $\Delta_{MTDC}$  is MTDC resolution;  $T_{REF}$  is reference frequency;  $K_{DCO}$  is DCO gain. From this point of view, we can observe that there are a set of optimum loop parameters to meet a narrow bandwidth without frequency peaking for a low-jitter ADPLL in the locked state.

## 3.3 Linear Model Analysis of Proposed ADPLL

In this section, the calculation steps for the proposed ADPLL parameters are illustrated. First, the linear model in different modes which are frequency acquisition mode and phase tracking mode will be introduced. Then we briefly present stability, locking transient, output spur, phase noise, and jitter. Finally, we have an example to design the proposed architecture by behavior simulation tool.

## 3.3.1 ADPLL in Frequency Acquisition Mode

In the traditional analog PLL, signals between circuit blocks are continuous and linear. The s-domain linear analysis method is appropriate for this kind of system. But in the ADPLL, because of the discrete time operations and the quantization effect, in order to make the linear analysis method available, some modification and approximation are needed to model an ADPLL. The conversion between the s-domain and z-domain is shown in [13].

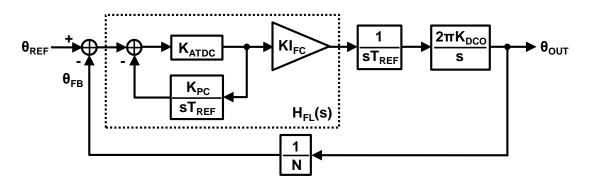

Fig. 3-8 The linear model of the proposed ADPLL in frequency acquisition mode.

As mentioned above, the frequency acquisition mode is first activated at the beginning of the locking process. In order to reduce the area and power of MTDC, the programmable ATDC is used to detect coarse phase error and compensate loop characteristic instantly. The overall equivalent model under the frequency acquisition mode is depicted in Fig. 3-8. The quantization noise of TDC and DCO are neglected in

this model. If the desired steady-state loop bandwidth is small, the *KP* and *KI* will be small. And we design the LSB of ATDC greater than the whole MTDC range. In a standard ADPLL architecture, the building blocks of phase quantizer and DLF can be ignored in the following analysis.  $H_{FL}(s)$  describes the transfer function of the fast-locking module, which is expressed in (3-5),

$$H_{FL}(s) = \frac{sT_{REF}K_{ATDC}KI_{FC}}{sT_{REF} + K_{ATDC}K_{PC}}.$$

(3-5)

The transfer function of the coarse timing window is represented by  $K_{ATDC}$ , it can be modeled as  $T_{REF}/2 \pi \Delta_{ATDC}$ ,  $\Delta_{ATDC}$  is the resolution of ATDC. The gain of phase error compensation is represented by  $K_{PC}=2\pi T_{UT}/T_{REF}$ ,  $T_{UT}$  is the equivalent time of unit code change,  $T_{UT}=N_{SH}T_{OUT}$  ( $N_{SH}$  represents the shift of divider ratio due to a unit code from ATDC). And the gain of KI controller is modeled as  $KI_{FC}$ . Hence, the open-loop transfer function can be derived as below:

$$H_{OPEN,FA}(s) = \frac{\theta_{REF}(s)}{\theta_{FB}(s)} = H_{FL}(s) \cdot \frac{1}{sT_{REF}} \cdot \frac{2\pi K_{DCO}}{s} \cdot \frac{1}{N}$$

$$= \frac{2\pi K_{ATDC} KI_{FC} K_{DCO}}{NT_{REF}} \frac{1}{s\left(s + \frac{K_{ATDC} K_{PC}}{T_{REF}}\right)} \cdot$$

(3-6)

Note that such compensation operation provides a zero at s=0 in the transfer function  $H_{FL}(s)$ , and it cancels out one pole at s=0. In addition, it is worth noting that the loop in frequency acquisition mode contains only a pole at the origin, which is unlike type-II PLL having two poles at s=0. The system is switched to type-I operation which features the fast lock characteristic.

The closed-loop transfer function can be derived as below:

$$H_{CLOSED,FA}(s) = \frac{\theta_{OUT}(s)}{\theta_{REF}(s)}$$

$$= \frac{2\pi K_{ATDC} KI_{FC} K_{DCO}}{T_{REF}} \frac{1}{s^2 + s \frac{K_{ATDC} K_{PC}}{T_{REF}} + \frac{K_{ATDC} KI_{FC} K_{DCO}}{NT_{REF}}}$$

(3-7)

By comparing with the 2<sup>nd</sup> order system closed-loop transfer function in control theory, both the damping factor ( $\zeta_{FA}$ ) and natural frequency ( $\omega_{n,FA}$ ) are calculated by:

$$\zeta_{FA} = \frac{K_{PC}}{2T_{REF}} \sqrt{\frac{K_{ATDC}NT_{REF}}{KI_{FC}K_{DCO}}},$$

(3-8)

and

$$\omega_{n,FA} = \sqrt{\frac{K_{ATDC}KI_{FC}K_{DCO}}{NT_{REF}}}$$

. (3-9)

Based on the above derived expressions, the behavior of the proposed ADPLL can be predicted and well-controlled by proper selections of loop parameters.

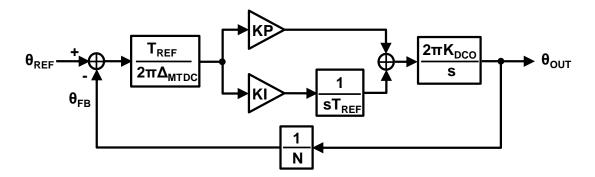

#### 3.3.2 ADPLL in Phase Tracking Mode

After the initial frequency is locked roughly using the frequency acquisition mode, the architecture can be further simplified as a type-II second-order TDC based ADPLL in phase tracking mode. The s-domain linear model is shown in Fig. 3-9. According to the models of building blocks in 2.3, the open loop transfer function of proposed ADPLL in locked state is given by

$$H_{OPEN,PT}(s) = \frac{\theta_{REF}(s)}{\theta_{FB}(s)} = \frac{T_{REF}}{2\pi\Delta_{MTDC}} \cdot \frac{sT_{REF}KP + KI}{sT_{REF}} \cdot \frac{2\pi K_{DCO}}{s} \cdot \frac{1}{N}.$$

(3-10)

Fig. 3-9 The linear model of the proposed ADPLL in phase tracking mode.

On the other hand, the close loop transfer function can be calculated as

$$H_{CLOSED,PT}(s) = \frac{\theta_{OUT}(s)}{\theta_{REF}(s)} = \frac{\frac{KP \cdot KI \cdot K_{DCO}T_{REF}}{\Delta_{MTDC}}s + \frac{KI \cdot K_{DCO}}{\Delta_{MTDC}}}{s^2 + \frac{KP \cdot KI \cdot K_{DCO}T_{REF}}{N\Delta_{MTDC}}s + \frac{KI \cdot K_{DCO}}{N\Delta_{MTDC}}}.$$

(3-11)

In this case, the damping factor  $(\zeta_{PT})$  and natural frequency  $(\omega_{n,PT})$  in phase tracking mode are also derived by comparing with a standard 2<sup>nd</sup> order system closed-loop transfer function:

$$\zeta_{PT} = \frac{T_{REF} KP}{2} \sqrt{\frac{K_{DCO}}{N \cdot KI \cdot \Delta_{MTDC}}}, \qquad (3-12)$$

and

$$\omega_{n,PT} = \sqrt{\frac{K_{DCO}KI}{\Delta_{MTDC}N}}$$

. (3-13)

Based on the numerical analysis and appropriate simplification between open loop and closed loop transfer function [32], we can derive unity gain bandwidth ( $\omega_T$ ) and phase margin (*PM*) from closed loop parameters:

$$\omega_{T,PT} = \omega_{n,PT} \sqrt{\left[\sqrt{4\zeta_{PT}^4 + 1} - 2\zeta_{PT}^2\right]}, \qquad (3-14)$$

and

$$PM_{PT} = \cos^{-1} \left[ \sqrt{4\zeta_{PT}^4 + 1} - 2\zeta_{PT}^2 \right].$$

(3-15)

Based on the definition of the closed loop -3dB bandwidth,  $|H(j\omega_{-3dB})| = |H(j0)|/2$ , we can realize the closed loop -3 dB bandwidth is

$$\omega_{-3dB,PT} = \omega_{n,PT} \sqrt{1 + 2\zeta_{PT}^2 + \sqrt{2 + 4\zeta_{PT}^2 + 4\zeta_{PT}^4}} .$$

(3-16)

From an observation of mathematical analysis, we can find out that there are several parameters can be designed in an ADPLL. *N* and  $T_{REF}$  are determined by reference frequency and target frequency and they are always defined by specifications.  $\Delta_{MTDC}$  and  $K_{DCO}$  are limited by the CMOS process without special techniques. Therefore, the *KI* and *KP* are the best candidates to characterize the system. It is easy to design different nature frequency and damping factor by selecting different combinations of *KP* and *KI*, because of the digital nature of DLF implementation. Not only the stability issue but also lock time and timing jitter will be affected due to a wrong parameter design. A damping factor around 0.707 is commonly used to get better performance. The larger *KP/KI* represents the better stability. The larger *KI* reveals the wider bandwidth under the same stability, but the larger *KP* induces larger steady state jitter.

## 3.3.3 Stability Analysis

For most fast-locking PLL, system stability should be carefully analyzed since the loop dynamic has been changed. To assure loop stability of the proposed approach, the analysis of the loop characteristic during frequency acquisition mode and locked state must be provided.

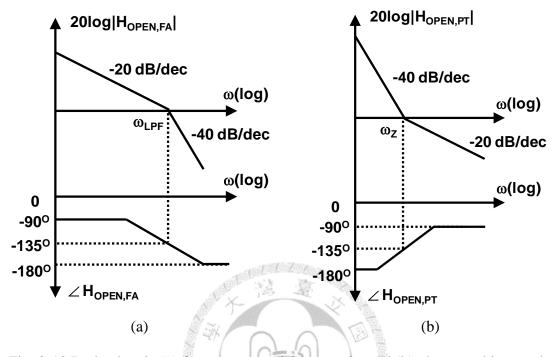

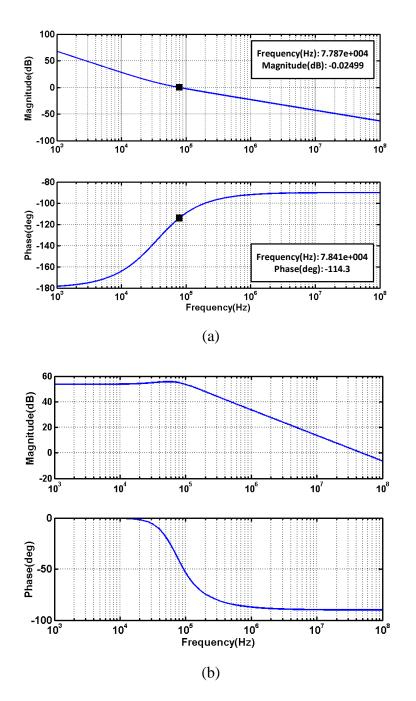

By utilizing the open loop transfer function (3-6), the bode plots of the magnitude and phase of the loop gain is obtained. As depicted in Fig. 3-10 (a), the loop gain begins from infinity at  $\omega$ =0 and falls at a rate of -20 dB/dec for  $\omega < \omega_{LPF}$  and at a rate of -40 dB/dec thereafter. By analyzing the bode diagram, the phase margin in frequency acquisition mode can be obtained.

Fig. 3-10 Bode plots in (a) frequency acquisition mode, and (b) phase tracking mode.

The stability behavior can also be analyzed by the root locus of their poles and zeros in the complex plane as the parameter  $K=K_{ATDC}KI_{FC}K_{DCO}/NT_{REF}$  varies. From Eq. (3-6), the two poles of the closed-loop system are given by

$$s_{1,2} = \frac{-2\zeta\omega_n \pm \sqrt{4\zeta^2 \omega_n^2 - 4\omega_n^2}}{2} = (-\zeta \pm \sqrt{\zeta^2 - 1})\omega_n.$$

(3-17)

When K=0, the two poles lie on  $s_1=-\omega_{LPF}=-K_{ATDC}K_{PC}/T_{REF}$  and  $s_2=0$ , and the damping factor ( $\zeta$ ) is infinity. As K increases,  $\zeta$  decreases and the two poles move toward each other on the real axis. For  $\zeta=1$ , the two poles are identical,  $s_1=s_2=-\omega_{LPF}/2$ . As K increases further, the two poles become complex and  $\zeta$  drops which causes the loop become less stable.

On the other hand, the bode plot is obtained in Fig. 3-10 (b) by open loop transfer function (3-10) under phase tracking mode. The loop gain begins from infinity at  $\omega$ =0

and changes a rate from -40 dB/dec to -20 dB/dec at  $\omega = \omega_Z$ . If the  $\omega_Z$  is designed equal to the gain-crossover (0-dB) frequency, the phase margin is 45°.From Eq. (3-10), the zero frequency is derived by

$$\omega_z = \frac{KI}{KP \cdot T_{REF}}.$$

(3-18)

Thus, the phase margin in a locked state can be redefined by  $\omega_Z$  and  $\omega_T$ .

$$PM = tan^{-1} \left(\frac{\omega_T}{\omega_Z}\right). \tag{3-19}$$

## **3.3.4 Transient Behavior**

Settling time is defined as the time at which the response settles to within some percentage of the final steady state value. Since the proposed ADPLL spends most time operating in frequency acquisition mode, it is reasonable to approximate the ADPLL settling time by analyzing the settling time of linear model in frequency acquisition mode described above. For  $0 < \zeta < 1$ , applying a  $\Delta \omega$  step input as a certain hopping frequency, the output frequency is described according to Eq. (3-6),

$$\omega_{OUT}(s) = N \cdot \omega_{FB}(s) = N \frac{\omega_n^2}{s^2 + 2\zeta \omega_n s + \omega_n^2} \frac{\Delta \omega}{s}.$$

(3-20)

By applying the *inverse Laplace transform*, the time-domain response can be obtained:

$$\omega_{OUT}(t) = L^{-1} \left\{ \omega_{OUT}(s) \right\}$$

$$= \left[ 1 - \frac{e^{-\zeta \omega_n t}}{\sqrt{1 - \zeta^2}} \sin(\omega_n \sqrt{1 - \zeta^2} t + \theta) \right] N \Delta \omega \cdot u(t), \qquad (3-21)$$

where  $\theta = tan^{-1} \left( \frac{\sqrt{1 - \zeta^2}}{\zeta} \right). \qquad (3-22)$

The frequency error can be expressed by

$$\Delta \omega_{OUT}(t) = \frac{e^{-\zeta \omega_n t}}{\sqrt{1 - \zeta^2}} \sin(\omega_n \sqrt{1 - \zeta^2} t + \theta) N \Delta \omega \cdot u(t).$$

(3-23)

The settling time can be approximated by finding the time when the value of  $\Delta \omega_{OUT}$ remains within some percentage of its final value. That is,

$$\left|\Delta\omega_{OUT}(t_s)\right| = \left|\frac{e^{-\zeta\omega_n t_s}}{\sqrt{1-\zeta^2}}\sin(\omega_n\sqrt{1-\zeta^2}t+\theta)N\Delta\omega\cdot u(t)\right|.$$

(3-24)

$$\frac{e^{-\zeta \omega_n t_s}}{\sqrt{1-\zeta^2}} N\Delta \omega \le f_{tol}, \qquad (3-25)$$

where  $f_{tol}$  (frequency tolerance range) is a given percentage of the locking frequency.

By calculating Eq. (3-25), the settling time can be derived by

STA /

$$t_{s} = \frac{-\ln(\frac{f_{tol}\sqrt{1-\zeta^{2}}}{N\cdot\Delta\omega})}{\zeta\omega_{n}} = \frac{\ln(\frac{\Delta\omega_{oUT}}{f_{tol}\sqrt{1-\zeta^{2}}})}{\zeta\omega_{n}},$$

(3-26)

101

where  $\Delta \omega_{OUT}$  is the frequency error that output frequency needs to change.

## 3.3.5 Output Spur

Under the assumption of narrow band frequency modulation, the power level of the spurious tones compared to the carrier can be approximated as [11]:

2010701010

$$P_{spur} = 20 \log\left(\frac{1}{2}\beta\right) (dBc), \qquad (3-27)$$

where  $\beta$  is the modulation index defined as the ratio of frequency deviation ( $\Delta \omega$ ) to the frequency of modulation wave  $(\omega_m)$  in a frequency modulation system when using a sinusoidal modulating wave. However, for a symmetric square wave with frequency of  $\omega_m$  as the modulating input, it can be expressed in the following Fourier series representation:

$$g_{square}(t) = \sum_{n=1.odd}^{\infty} \frac{2}{\pi} \frac{1}{n} sin(n\omega_m t).$$

(3-28)

The modulation index of the nth harmonic for *Fourier series* decomposition of a square modulating wave becomes:

$$\beta_n = \frac{2}{\pi n} \frac{\Delta \omega_{pp}}{n \omega_m}, \qquad (3-29)$$

where  $\Delta \omega_{pp}$  is the peak to peak frequency deviation. It should be noted that in most cases, only the fundamental component (*n*=1) would really matter. The output clock of an ADPLL system is frequency modulated by a periodic control signal in locked state, leading to spurious tone emission. An inspection reveals that larger  $\Delta \omega_{pp}$  and smaller  $\omega_m$  will increase the power level of the spurs. But the analysis is performed under the noise-free assumption. In fact, the noise will randomize the spurious energy.

#### 3.3.6 Phase Noise and Jitter

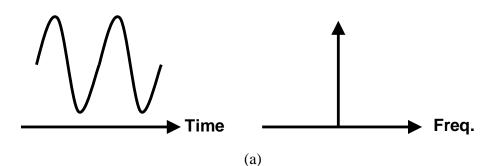

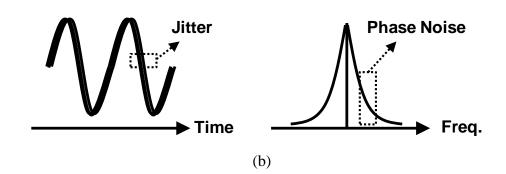

Phase noise and jitter performance are important indicators of the signal quality in a PLL system, which are determined by frequency domain and time domain, respectively. An ideal sinusoidal signal is shown in Fig. 3-11 (a). However, there are many issues in non-linearity and quantization error will cause non-ideal profile, which is illustrated in Fig. 3-11 (b). The real frequency spectrum resembles a skirt-like shape and the real DCO output waveform varying the zero-crossing points with time.

Fig. 3-11 The timing waveform and spectrum in different case: (a) ideal, and (b) real.

Fig. 3-12 The linear model of a ADPLL with internal and external noise sources.

In Fig. 3-12, the linear model of a tradition ADPLL is illustrated again including the internal and external noise sources.  $\phi_{n,REF}$  is the phase noise from input reference clock,  $\phi_{n,TDC}$  is the phase noise due to the quantization of TDC, and  $\phi_{n,DCO}$  is the phase noise on the DCO output produced by itself. To find out the total output noise of the ADPLL, the expression of the power spectral density (PSD) of each noise source is required.

In this paragraph, we will separately introduce each generated noise in different building blocks. First, the phase noise PSD of the reference clock can be estimated according to the signal generator specifications. Secondly, the TDC is modeled as a linear block with a gain  $K_{TDC}$  (= $T_{REF}/2\pi \Delta_{TDC}$ ) and a quantization noise ( $S_{Q,TDC} = \Delta^2_{TDC}/12$ ). Finally, the PSD of the noise from DCO will be derived. Consider the differential LC tank cross-coupled pair oscillator, the generated phase noise can be express as [33]

$$S_{\varphi,DCO}(\Delta f) = \frac{\bar{i}_n^2 / \Delta f}{q_{max}^2} \frac{\Gamma_{rms}^2}{8\pi^2 \Delta f^2}, \qquad (3-30)$$

where  $i_n^2/\Delta f$  is the PSD of the equivalent parallel current noise,  $\Gamma_{rms}$  is the rms value of the impulse sensitivity function (ISF) associated with that noise source ( $\Gamma_{rms}^2=0.5$ when the system output can be assumed to be a sinusoidal waveform),  $q_{max}$  is the maximum signal charge swing which is defined as the product of the tank capacitance and maximum signal swing  $C_{tank}V_{swing}$ , and  $\Delta f$  is the offset frequency from carrier. In a simplified stationary approach, the total noise power of the tank is mainly due to the cross-coupled transistor pair and the ohmic losses in the tank inductor:

$$\frac{i_n^2}{\Delta f} \approx 2kT\gamma\mu_n C_{ox} \frac{W}{L} V_{ov} + \frac{4kT}{R_p}, \qquad (3-31)$$

where  $R_p$  ( $\approx 2\pi f_{osc}L_{tank}Q$ ) is the equivalent parallel resistance at the frequency of oscillation  $f_{osc}$ , T is the temperature, k is Boltzmann constant,  $\mu_n$  is the mobility of the carriers in the channel,  $C_{ox}$  is the oxide capacitance per unit area, W and L are the width and length of the MOS transistor,  $V_{ov}$  is the gate drive of the MOS transistor, and  $\gamma$  is the channel length modulation coefficient.

From the model shown in Fig. 3-12, it is straightforward to calculate the total output phase noise by summing the contributions of the different noise sources:

$$S_{\phi,ALL}(\Delta f) = \left(S_{\phi,REF}(\Delta f) + S_{\phi,TDC}(\Delta f)\right) \left|\frac{NH(\Delta f)}{N+H(\Delta f)}\right|^{2} + S_{\phi,DCO}(\Delta f) \left|\frac{N}{N+H(\Delta f)}\right|^{2},$$

(3-32)

where

$$H(\Delta f) = \frac{K_{DCO}K_{TDC}}{j\Delta f}H_{DLF}(\Delta f)$$

. (3-33)

In a more precise model of DLF, the output sequence is reconstructed by the zero-order-hold operation which can be expressed as a sinc function in frequency domain. Consequently, the frequency response of DLF is shown in [20]

$$H_{DLF}(f) = \frac{\sin\left(\frac{\pi f}{f_{REF}}\right)}{\left(\frac{\pi f}{f_{REF}}\right)} \left(KP + \frac{KI}{1 - e^{-j2\frac{\pi f}{f_{REF}}}}\right) e^{-j\frac{\pi f}{f_{REF}}}.$$

(3-34)

On the other part of time domain measurement, jitter is defined as an important quality criterion. There are many previous works focus on finding a systematic relation between timing jitter and key design parameters like the reference frequency, output frequency, loop bandwidth, and power consumption [34]-[36]. The brief aims at defining a benchmark figure-of-merit (FoM) to evaluate the PLL jitter ( $\sigma_i$ ) in relation to the consumed power (*P*),

$$FoM = 10 \cdot log\left[\left(\frac{\sigma_t}{Is}\right)^2 \cdot \frac{P}{ImW}\right].$$

(3-35)

Jitter may result from phase noise or sidebands. Therefore, the supply/substrate noise, device noise, and periodic disturbance of control code will degrade jitter performance. However, the timing jitter can be broken down into two categories which are long-term jitter and short-term jitter. In the classification of short-term jitter, it has two types which are cycle-to-cycle jitter ( $\Delta T_{cc,rms}$ ) and period jitter ( $\Delta T_{rms}$ ). From Eq. (3-36) and (3-37), the different definitions can be noticed.

$$\Delta T_{cc,rms} = \lim_{N \to \infty} \sqrt{\frac{1}{N} \sum_{n=1}^{N} \left(T_{n+1}^2 - T_n^2\right)^2} , \qquad (3-36)$$

and

$$\Delta T_{rms} = \lim_{N \to \infty} \sqrt{\frac{1}{N} \sum_{n=1}^{N} \Delta T_n^2}$$

, (3-37)

where  $T_{n+1}$  and  $T_n$  represent the period and next period, respectively. In [37], it derives a relationship between phase noise and cycle-to-cycle jitter assuming the PLL has a loop bandwidth,  $2\pi f_u$ .

$$\Delta T_{cc,rms} = \frac{1}{\sqrt{2\pi f_u}} S_{\phi}(\Delta \omega) \frac{\Delta \omega}{\omega_o}, \qquad (3-38)$$

where  $\omega_o$  denotes the oscillation frequency,  $S_{\phi}(\Delta \omega)$  is the phase noise power at an offset frequency of  $\Delta \omega$ .

#### 3.3.7 Design Example and Behavior System Simulation

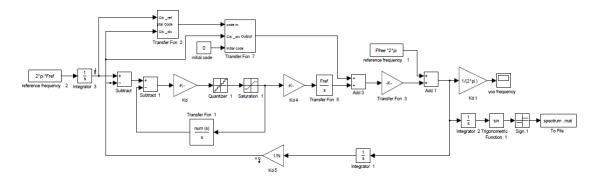

In this thesis, a 2.4 GHz integer-N frequency synthesizer with dynamic phase compensation is realized. Since the transistor simulation usually takes very long time, it is inefficient and a waste of time to try the system behavior by transistor simulation. Therefore, it is recommended to simulate the behavior model by mathematical tools before performing the transistor simulation. To verify the correctness of the loop characteristic and loop parameters described above, the linear phase-domain model simulation should be taken firstly. Fig. 3-13 shows behavior model of the proposed ADPLL constructed by Matlab Simulink.

In this section, a design example of the proposed ADPLL with following specification has been shown:

- Reference frequency  $F_{REF} = 5 \text{ MHz}$

- Phase margin  $PM = 60^{\circ}$

- Unity gain bandwidth in phase tracking mode  $F_{T,PT} = 80 \text{ kHz}$

- Unity gain bandwidth in frequency acquisition mode  $F_{T,FA} = 300 \text{ kHz}$

- Divider ratio N = 480

- DCO gain  $K_{DCO} = 200 \text{ kHz/Code}$

- MTDC resolution  $\Delta_{\text{MTDC}} = 5 \text{ ps}$

Fig. 3-13 Behavior model of the proposed ADPLL in Matlab Simulink.

To design the fast lock operation, the parameter analysis of the ADPLL in frequency acquisition mode must be applied. The open loop gain is given by Eq. (3-6), where the pole frequency  $(\omega_p)$  is

$$\omega_p = \frac{K_{ATDC} K_{PC}}{T_{REF}}.$$

(3-39)

The phase margin of the system is given by

$$PM = 180^{\circ} - 90^{\circ} - tan^{-1}(\frac{\omega_{T,FA}}{\omega_p}), \qquad (3-40)$$

where  $\omega_{T,FA}$  is the unit gain frequency in frequency acquisition mode, and the relationship between  $\omega_{T,FA}$  and  $\omega_P$  is obtained as

$$\omega_{T,FA} = \omega_p \tan(90^\circ - PM). \tag{3-41}$$

From the definition of unit gain frequency, a correlated formula can be defined as

$$\left|H_{OPEN,FA}(j\omega_{T,FA})\right| = 1.$$

(3-42)

$$\left|\frac{2\pi K_{ATDC}KI_{FC}K_{DCO}}{NT_{REF}} \times \frac{1}{\left(-\omega_{T,FA}^{2} + j\omega_{T,FA}\omega_{p}\right)}\right| = 1.$$

(3-43)

$$\omega_{T,FA} \sqrt{\omega_{T,FA}^2 + \omega_p^2} = \frac{2\pi K_{ATDC} K I_{FC} K_{DCO}}{N T_{REF}}.$$

(3-44)

Replacing  $\omega_p$  in Eq. (3-41) to (3-44), the parameter  $KI_{FC}$  and  $K_{ATDC}$  is obtained as

$$KI_{FC} = \frac{NK_{PC}\omega_{T,FA}\sqrt{1 + (tan(90^{\circ} - PM))^{2}}}{2\pi K_{DCO}},$$

(3-45)

and

$$K_{ATDC} = \frac{T_{REF}\omega_{T,FA}}{K_{PC}(tan(90^{\circ} - PM))}$$

. (3-46)

However, the limited number of ATDC bit leads to limited amount of compensation. Therefore, the larger frequency hopping distance, the more bits of ATDC output is needed [16]. In our application specification, it is reasonable to choose 3-stage ATDC. Thus,  $K_{PC}$  is limited by the circuit implementation and lacks of flexibility, so it is designed first and then calculate the other parameters,  $KI_{FC}$  and  $K_{ATDC}$ , according to loop specification,  $\omega_{T,FA}$  and phase margin.

In the phase tracking mode, the standard PLL analysis is applied to calculate the design parameters of the ADPLL. Since the definition of unity gain bandwidth  $(|H_{OPEN,PT}(j\omega_{T,PT})|=1)$ , the *KP* and *KI* can be found from Eq. (3-18) and (3-19):

$$KP = \frac{N\Delta_{MTDC}\omega_{T,PT}\sin(PM)}{T_{REF}K_{DCO}},$$

(3-47)

and

$$KI = \frac{\omega_{T,PT} T_{REF} KP}{tan(PM)}$$

. (3-48)

For the 0.18 µm CMOS process, the delay of an inverter is about 30 ps. If we implement Vernier delay-chain TDC, the resolution of the MTDC can be design about 5 ps. Because of the application range and the PVT variations, a 8-bit DCO structure is selected for a reasonable DCO gain ( $K_{DCO}$ =200 kHz/Code). The corresponding loop parameters calculated by (3-45) and (3-46) is given by  $KI_{FC}$ =10.39  $\cong$  2<sup>3.5</sup>,  $K_{ATDC}$ =51.96 ( $\Delta_{ATDC}$  =613 ps),  $K_{PC}$ =0.0125 ( $T_{UT}$ =400 ps). Considering a 8-bit DSM for DCO resolution enhancement, the value of the proportional gain *KP* and integral gain *KI* of DLF are found as KP=6.6864  $\cong$  2<sup>2.5</sup> and KI=0.388  $\cong$  2<sup>-1.5</sup> from Eq. (3-47) and Eq. (3.48), respectively. The Bode plot of the ADPLL is shown in Fig. 3-14. With the approximation of power of two, the gain of *KP* and *KI* is able to be implemented as a shifter instead of a multiplier.

In this work, the loop not only switches its bandwidth but also changes to type-I operation during the frequency acquisition mode. And it is known that type-I PLL achieves faster settling time than type-II [4]. Fig. 3-15 illustrates the transient simulation for various frequency hopping distances with Matlab Simulink. Fig. 3-16 illustrates the comparison of the locking behaviors between conventional ADPLL and fast-locking ADPLL with AHDL.

Fig. 3-14 Bode plot of the ADPLL in (a) open loop simulation, and (b) closed loop simulation.

Fig. 3-15 Simulated locking behaviors for various frequency hopping distances.

Fig. 3-16 Comparison of locking behaviors between traditional ADPLL and the proposed ADPLL under the same loop bandwidth and damping factor.

# Chapter 4 Design and Implementation of the ADPLL

## 4.1 Circuit Implementations

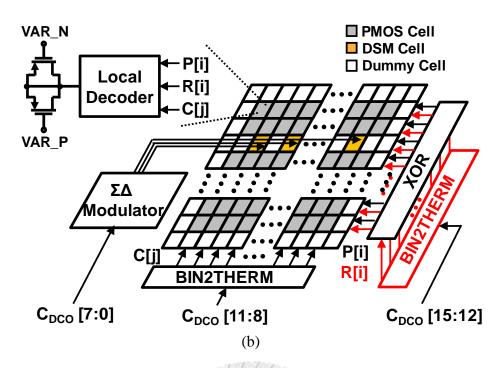

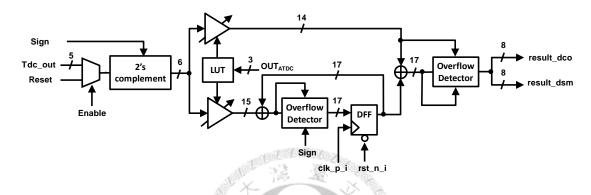

In order to verify the proposed compensation technique, this work realized a 2.4 GHz low-jitter, fast-locking ADPLL. Fig. 3-6 shows the overall architecture of the proposed ADPLL. Basically, the structure is based on a conventional type-II second-order TDC based digital frequency synthesizer. The traditional phase quantizer is composed of a PFD, phase selector, and a 5-bit TDC (Main TDC, MTDC). The additional timing window is realized by a 3-stage TDC (Auxiliary TDC, ATDC). A first-order PI structure is implemented as a 16-bit DLF and the KI controller determines the frequency capture range. The system calibrates proper loop parameters in order to achieve a low-jitter performance. The DCO core is controlled by 8-bit most significant bit (MSB) output of the DLF and DCO resolution is enhanced by an 8-bit DSM. This section describes the key building blocks design. All the PFD/TDC, divider, DCO, and synthesis circuits are described in detail.

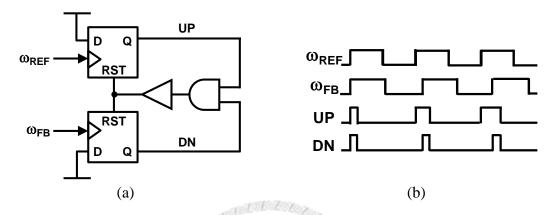

#### 4.1.1 PFD and TDC

The PFD is used to detect the phase and frequency differences between the input reference clock and the feedback output signal of the divider. The circuit of PFD can be realized by various ways. Fig. 4-1 (a) shows a simple implementation consisting of two edge-triggered, resettable D flip-flops (DFF) with their D inputs tied to a logical "high". The DFF is triggered by the rising edge of  $\omega_{REF}$  and  $\omega_{FB}$ . Once both UP and DN become logical "high", the two DFFs are reset simultaneously. The related timing

diagrams are shown in Fig. 4-1 (b). The pulse width difference between signal UP and DN reflects the phase error. This information delivers to both MTDC and ATDC. The pulse hold time, which UP and DN are simultaneously in logical "high", is designed long enough to cover the whole MTDC delay range.

Fig. 4-1 DFF based PFD (a) the block diagram, and (b) the timing diagram.

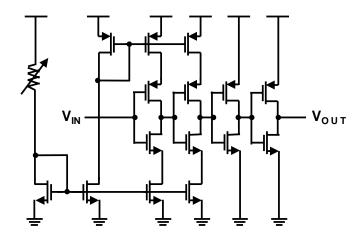

The 3-stage ATDC is implemented like to a coarse timing window. The main function of the 7-level quantizer is to sense the phase error and generate the proper control code to facilitate fast lock operation. Based on the concept of digital discriminator-aided phase detector (DAPD) described in [17], we design a programmable delay cell using current-controlled bias to cover a desired delay. Fig. 4-2 illustrates a simple current-controlled delay circuit chosen in this work. On the other hand, the proposed MTDC is based on a Vernier TDC with 5-bit uneven-step architecture. However, there are some considerations of the location of deadzone in the transfer curve between MTDC and ATDC. The characteristic curves are shown in Fig. 4-3. In a ATDC design, the deadzone locates on horizontal plane instead of the vertical plane in MTDC. The resolution in an ATDC must be greater than the whole cover range of MTDC for system stability,  $\Delta_{ATDC} > (2^5-1)\Delta_{MTDC}$ .

Fig. 4-2 The schematic of the current-controlled delay cell.

Fig. 4-3 The characteristic curves of (a) auxiliary TDC, and (b) main TDC.

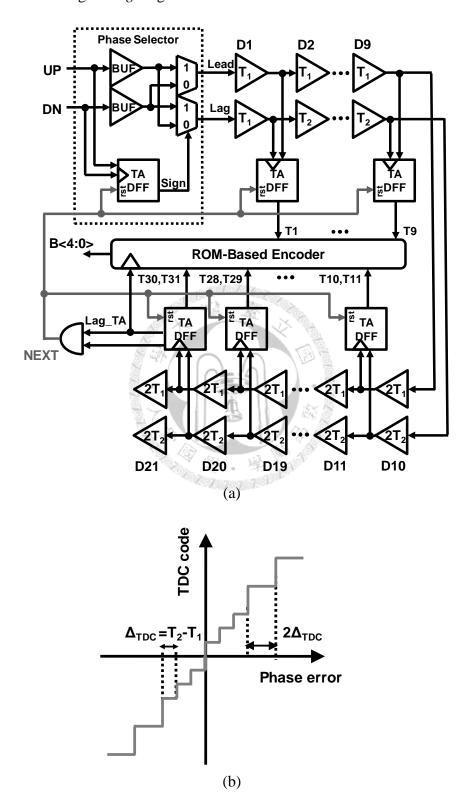

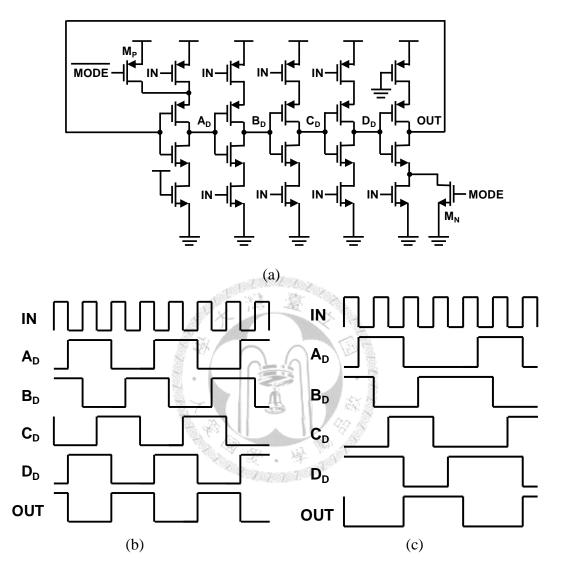

Fig. 4-4 (a) shows the proposed structure of the MTDC circuit including a phase selector. The 5-bit Vernier TDC can only convert the phase difference to digital codes but cannot judge which one is lead or lag. Therefore, a phase selector is implemented to determine the phase relation between *UP* and *DN* and outputs a *Sign* signal to the MTDC [31]. The structure of the phase selector is shown in Fig. 4-4 (a) within a dotted box. It is composed of two multiplexers (MUXs), two buffers (BUFs), a time amplifier (TA), and a DFF. Before each phase comparison, the signal *NEXT* from the MTDC will reset the *Sign* signal to logical "high". If the *UP* signal leads, the decision circuit

(TA+DFF) outputs a logical "low" signal and vice versa. The delay circuit, BUF, is important in ensuring the *Sign* signal arrives earlier than *UP* and *DN*.

Fig. 4-4 An uneven-step Vernier TDC in (a) 5-bit architecture, and (b) a conceptual diagram for 3-bit TDC.

A Vernier architecture defines the resolution not by the absolute delay time of a unit cell, but the relative timing difference, which improves the effective resolution. As a result, two-path structure are required doubles power and area of inverter cells. In this work, an uneven-step TDC is implemented to relax this constraint. The transfer curve with a 3-bit uneven-step TDC for conceptual illustration is shown in Fig. 4-4 (b). The complete delay chain has been divided into two segments. The first segment has the shortest delay time cells, which determines the TDC quantization noise in the lock state. The inverter numbers of first segment are designed to cover sufficient delay range due to circuit PVT variation in steady state. The other segment uses cells of double delay time by adding load MOS capacitors to inverter output nodes. The uneven-step architecture extends the detection range, but it will not affect the phase noise performance and result in overall power savings. The circuit operation principle is as follows. The Lead signal from the phase selector is sent to the path consisting of  $T_1$  delay cells and the Lag signal is sent to the path consisting of  $T_2$  delay cells. The decision circuit detects that the Lag signal leads the Lead signal and converts the phase error between Lead and Lag into a set of digital codes with a resolution of  $\Delta_{TDC}$  $(=T_2-T_1)$ . When the signals already cross the both delay lines, the NEXT signal will reset the phase selector.

Conventionally, a DFF is used as the phase decision circuit in a TDC to quantize the time difference of these two input pulses. To enhance the time resolution, the cascade inverter-based TA is adopted [31]. In our design, it can relax the design limited of TA with a modified ROM-based encoder which includes bubble error removal mechanism and avoiding metastability. The bubbles, or called sparkles, usually occur near the transition point of the thermometer code. In the conversion of thermometer to 1-of-N code, the bubble error can be removed by adding a three-input NAND. On the other hand, an efficient technique by employing Gray coding as an intermediate step between the thermometer and binary codes can avoid metastability occurrence.

The input/output characteristic simulation result is shown in Fig. 4-5. The resolution of this MTDC is around 5 ps. From Eq. (2.4), the phase noise introduced by the TDC is -100.23 dBc/Hz.

Fig. 4-5 The simulation result of 5-bit uneven-step TDC.

## 4.1.2 Divider