### 國立臺灣大學電機資訊學院光電工程學研究所

### 碩士論文

Graduate Institute of Photonics and Optoelectronics College of Electrical Engineering and Computer Science

> National Taiwan University Master Thesis

於玻璃基板與塑膠基板上製作

高效能氧化鋅薄膜電晶體

High Performance ZnO Thin Film Transistors

on Both Glass and Plastic Substrates

研究生: 劉建承

Liu, Chien Cheng

指導教授: 黃建璋 博士

中華民國 九十六 年 七 月

July 2007

國立臺灣大學碩士學位論文

# 口試委員會審定書

於玻璃基板與塑膠基板上製作

高效能氧化鋅薄膜電晶體 High Performance ZnO Thin Film Transistors on Both Glass and Plastic Substrates

本論文係 劉建承 君 (R94941024) 在國立臺灣大學光 電工程學研究所完成之碩士學位論文,於民國九十六年七月 十七日承下列考試委員審查通過及口試及格,特此證明

| 口試委員: | 黄建南      | (簽名) |

|-------|----------|------|

|       | (指導教授)   | 民般道  |

|       | 陳夏君      |      |

|       |          |      |

| 所長    | 高机步 (簽名) |      |

#### 謝 誌

今年早春特地赴會椰林大道上的杜鵑花季,她們仍然開得那麼理直氣壯,頗 有「乃校」之風;荏苒光陰,幾場梅子雨,幾件羽毛衣,回首兩年多在台大的研究 生涯,也曾經如此理直氣壯,漸漸,卻也學會真正用心傾聽。

由衷感謝指導老師黃建璋博士在學術研究上的悉心引導,不僅在研究主題上 給予精闢的指導及見解,也讓我有機會參與資策會無線網路感測的計畫,從中學 習到天線傳播的相關理論;另外,在協助帶領大學部光電實驗的電光調變器實驗 中,也學到不少有趣的應用,這趟碩士班的學涯,收穫良多。也感謝口試委員陳 奕君教授以及陳敏璋教授不吝指教,而讓這本論文更具完整性。

由衷感謝 402 實驗室的所有夥伴們。和育昇一起分享討論實驗、製程、原理 以及女人,挑燈夜戰馬力歐賽車為的是那些令人又愛又恨的 data;和下巴、子樸、 子揚、志豪共度豬羊變色的那些夜晚;和成熟穩重的旻諺哥以及倜儻瀟灑萬人迷 小銘討論深奧的物理;兩位博班學長正彬哥、柯董真是實驗室活力的泉源;還有 可愛的學弟們孟倫、振印、弘憲、兩儀、原禎,光中、世驊、小潘、宏禮,你們 讓 402 充滿了無盡的歡笑。

由衷感謝方瑜老師,弭平了我左腦和右腦的齟齬,讓我的生活不致分裂而得 以發展更完整的性靈。或快或慢,或理性或感性,或邏輯或用情...;學會用我的 兩種步伐,陪著我平穩前進。學會不偏廢任一種心智,隨心所欲,隨緣立善,「妻 子」和「情人」一樣,都得用力珍惜。

也感謝在台北求學階段一路相伴的所有好朋友:口條清晰報新聞的專家「查爾 頓」,適合當聊天系藝人的「大柔」學妹,走音救星吉他手「小綿羊」,十年深厚交情 小吃攤正妹「花枝」和「米粉」,遠在溫哥華的重量級笑話高手「鄧弼」,聊心事的話 匣子「痞堅」,未來的大作家「志摩」弟,大學麻吉「國勳」、「家豪」、「譽達」、「奕寰 」...,族繁不及備載;和你們一起朝馳江皐,夕濟西澨,上山下海,放任我們的 年少輕狂於歌聲笑語中,我們一起拼湊的燦爛時光,都將積澱在我的漫漫長夜裡。

最大的感謝要獻給老爸、老媽,你們無怨悔的支持以及全然的信任,使我可 以安心地去實踐我的志願及夢想;夜闌人靜時,憶起老爸的千萬交代「要活得快樂」,竊想有這麼開明的父母親,人生就足以快活了。小時候住在家裡面,長大了之 後,我的家,反而住進了我裡面,如影隨形。

漫步在曲徑通幽的舟山路上,兩岸景色依舊青山,依舊夕陽,許多的回憶在 這美麗的台大校園裡,終不散;許多的感恩在我的心中,雖不見。滿載而歸的六 年歲月,僅以數筆,略表心意,不盡之情,就拈花微笑吧。

i

2007年7月25日於台北長興街

### Abstract

This thesis focuses on two aspects of ZnO thin film transistors, the ZnO-TFTs fabricated on glass substrates and the flexible ZnO-TFTs fabricated on polymer substrates.

The first part demonstrates a high-performance enhancement-mode ZnO TFT on a glass substrate. Before realizing the TFT device, the characteristics of ZnO thin films are examined to find out the optimal deposition conditions. The ZnO thin film is deposited by RF magnetron sputtering with the presence of  $O_2$  at low deposition rate and low temperature. The  $I_{DS}$  of the ZnO-TFT on glass substrates is as high as 1 mA when biased at the saturation region  $V_{DS} = 10-20$  V and  $V_{GS} = 5$  V without any post thermal anneal. The  $I_{on}/I_{off}$  ratio is  $3 \times 10^6$ . We believe the results are among the best ZnO TFTs ever obtained.

The second part focuses on the flexible ZnO-TFT on PET (polyethylene terephthalate) substrates. All the patterns are defined by standard photolithography with only two steps in order to reduce the distortion of PET substrates. The ZnO thin film is deposited by RF magnetron sputtering at low temperature in presence of  $O_2$ . The gas flow ratio of Ar to  $O_2$  is based on the optimal conditions obtained in the case of the ZnO-TFTs on glass substrates. Titanium is also employed in substitution for ITO as the source and the drain layers to improve the electrical performance. The I<sub>DS</sub>–V<sub>DS</sub> curves along with optical transmission of the whole TFT are presented.

### 摘要

本論文研究製作於玻璃基板與塑膠基板上之氧化鋅薄膜電晶體的特性。

在實現薄膜電晶體元件之前,本文首先探討氧缺陷對氧化鋅薄膜 導電特性的影響,藉由濺鍍沉積氧化鋅薄膜時控制 Ar 和 O<sub>2</sub> 的比例, 以及利用氧電漿對氧化鋅薄膜表面進行處理,以獲得最佳製備氧化鋅 薄膜的成長環境。根據此最佳化條件,本研究在玻璃基板上製作出高 效能增強型氧化鋅薄膜電晶體,在 V<sub>DS</sub>=10-20, V<sub>CS</sub>=5V 的偏壓下,操 作電流可高達 1mA,開關電流比可達3×10<sup>6</sup>,是目前氧化鋅薄膜電晶體 的研究工作中,效能表現最好之一。

本文進一步探討製作於塑膠基板上之氧化鋅薄膜電晶體的特性。 採用兩步驟的黃光製程,以防止塑膠基板在化學溶劑中產生變形;而 受限於塑膠基板的玻璃轉換溫度,所有薄膜均在室溫下濺鍍成長,氧 化鋅的成長條件是利用玻璃基板上的最佳結果。另外,採用金屬鈦作 為汲極和源極,以改善接觸電阻。塑膠基板上之氧化鋅薄膜電晶體的 電特性曲線和可見光穿透率均本文中亦有論及。

iii

# **Table of Contents**

謝誌

### 摘要

### <u>page</u>

| Chapter 1 | Introduction   | 1 |

|-----------|----------------|---|

| Chapter   | 1 Bibliography | 5 |

| Chapter 2  | Literature Review and Theory                       |

|------------|----------------------------------------------------|

| 2.1 Transi | istors                                             |

| 2.1.1      | Working principle of field effect transistors 6    |

| 2.1.2      | Operation of thin film transistors                 |

| 2.1.3      | Si-based thin film transistors 17                  |

| 2.1.4      | Oxide-semiconductor-based thin film transistors 21 |

| 2.1.5      | Flexible thin film transistors                     |

| 2.2 Prope  | rty of Materials 26                                |

| 2.2.1      | Zinc oxide (ZnO) 26                                |

| 2.2.2      | Indium tin oxide (ITO) 33                          |

| 2.2.3      | Insulating materials                               |

| 2.3 Prope  | rty of Substrates                                  |

| 2.3.1      | Glass substrate                                    |

| 2.3.2      | Polymer substrates                                 |

| 2.4 Plasm  | a Reaction and Sputtering 44                       |

| Chapter 2  | Bibliography 47                                    |

### <u>page</u>

| Chapter 3 | Fabrication of ZnO TFTs on a Glass Substrate 52    |

|-----------|----------------------------------------------------|

| 3.1 Fabri | cation Process                                     |

| 3.2 Resu  | Its and Analysis 55                                |

| 3.2.1     | Quality of ZnO thin films 55                       |

| 3.2.2     | Performance of the ZnO-TFTs                        |

| 3.2.3     | Performance of the best ZnO-TFT 79                 |

|           |                                                    |

| Chapter 4 | Fabrication of ZnO TFTs on Plastic Substrates      |

| 4.1 Fabri | cation Process                                     |

| 4.2 Resu  | lts and Analysis                                   |

| 4.2.1     | Using ITO as the source and drain                  |

| 4.2.2     | Using Ti as the source and drain                   |

|           |                                                    |

| -         | Conclusions and Recommendations for Future Work 91 |

| 5.1 Cond  | clusions                                           |

| 5.2 Reco  | ommendations for Future Work                       |

# **List of Figures**

| Figu | <u>re</u>                                                                        | <u>page</u> |

|------|----------------------------------------------------------------------------------|-------------|

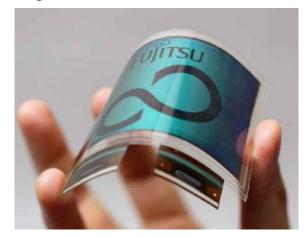

| 1.1  | The display application of flexible electronics. (a) Fujitsu                     |             |

|      | e-paper. (b) An e-paper newspaper. (c) E-papers look like real                   |             |

|      | sheets of paper. (d) A foldable display                                          | 4           |

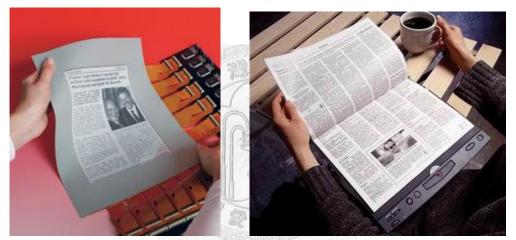

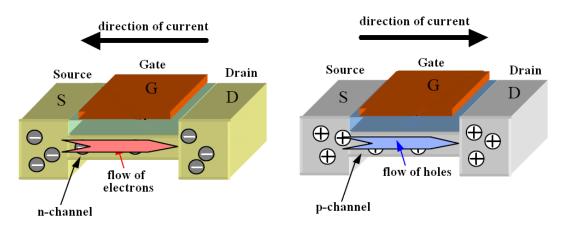

| 2.1  | FETs: (a) n-channel FET; (b) p-channel FET                                       | 7           |

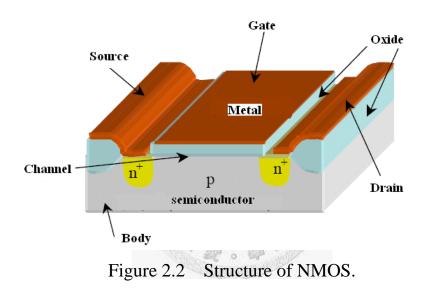

| 2.2  | Structure of NMOS                                                                | 7           |

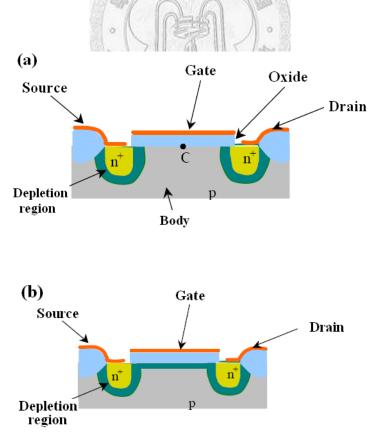

| 2.3  | The depletion region and the channel at different gate bias. (a)                 |             |

|      | $V_G=0$ , (b) $V_G < V_{th}$ , (c) $V_G = V_{th}$ , (d) $V_G > V_{th}$           | 8~9         |

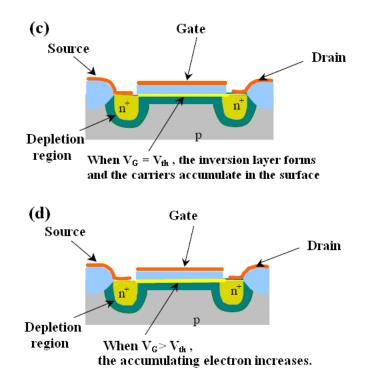

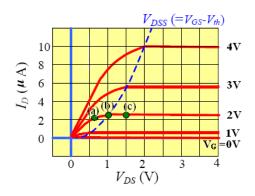

| 2.4  | Output characteristics when V <sub>DS</sub> is quite small                       | 9           |

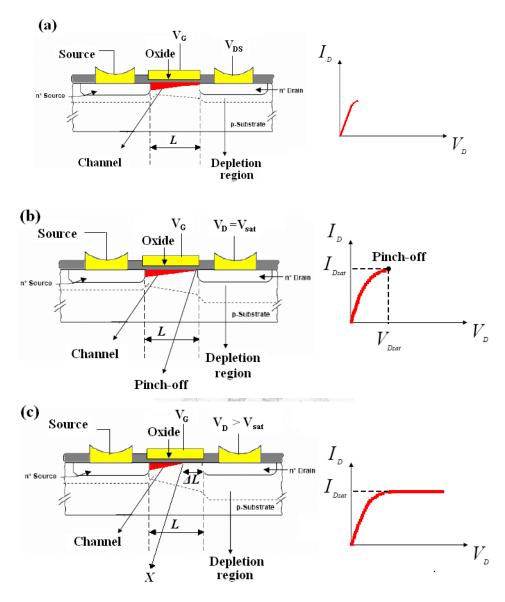

| 2.5  | Variation of channel and depletion region at a constant $V_G$                    |             |

|      | when (a) $V_{DS} < V_{Dsat}$ ; (b) $V_{DS} = V_{Dsat}$ ; (c) $V_{DS} > V_{Dsat}$ | 11          |

| 2.6  | Output characteristics                                                           | 11          |

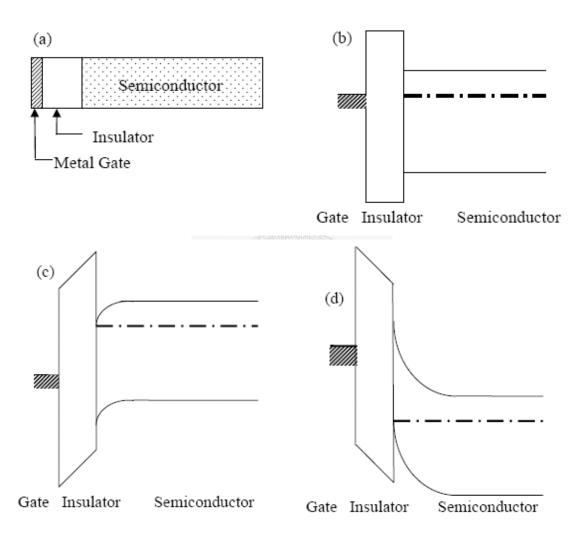

| 2.7  | (a) The cross-section of a MOS capacitor and corresponding                       |             |

|      | energy band diagrams for several biasing conditions: (b)                         |             |

|      | equilibrium, (c) accumulation ( $V_{GS} > 0$ V), and (d) inversion               |             |

|      | $(V_{GS} < 0 \ V)$                                                               | 14          |

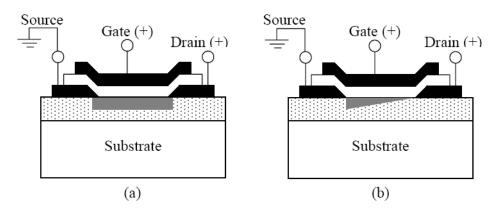

| 2.8  | An n-channel accumulation-mode TFT operating in (a)                              |             |

|      | pre-pinch-off and (b) post-pinch-off regime                                      | 15          |

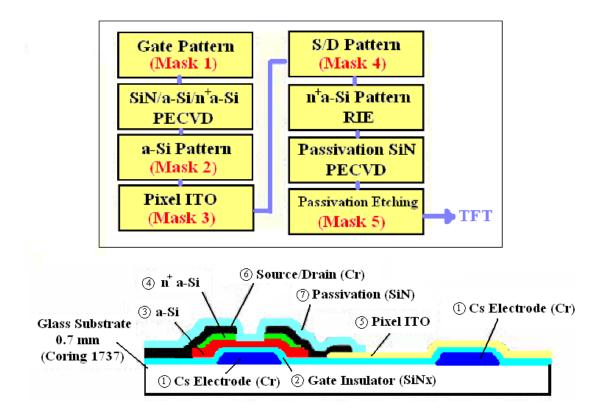

| 2.9  | Structure of an a-Si TFT and in the inset, the flowchart                         |             |

|      | outlines the processes for making an a-Si TFT array using a                      |             |

|      | bottom-gate TFT structure and an independent storage                             |             |

|      | capacitor                                                                        | 17          |

| 2.10 | Cross-sectional view of a (a) MOSFET and (b) TFT                                 | 18          |

| 2.11 | Four thin-film transistor configurations: (a) staggered                          |             |

|      | bottom-gate, (b) coplanar bottom-gate, (c) staggered                             |             |

|      | top-gate, and (d) coplanar top-gate                                              | . 20        |

| 2.12 | Material properties of IGZO system. Room temperature Hall                        |             |

|      | mobility and carrier concentration as functions of chemical                      |             |

|      | composition. Values outside and inside parentheses show                          |             |

|      | Hall mobility in $cm^2/Vs$ and carrier concentration in $10^{18} cm^{-3}$ ,      |             |

|      | respectively                                                                     | . 24        |

|      |                                                                                  |             |

| 2.13 | 5                                                                                                                                                | 28 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.14 | Energy levels of native defects in ZnO. The donor defects are                                                                                    |    |

|      | $Zn_i^{2\bullet}$ , $Zn_i^{\bullet}$ , $Zn_i^{\bullet}$ , $V_0^{2\bullet}$ , $V_0^{\bullet}$ , $V_0$ and the acceptor defects are $V_{Zn}^{"}$ , |    |

|      | V <sub>Zn</sub>                                                                                                                                  | 28 |

| 2.15 | A simplified section of the unit cell of $In_2O_3$ (ITO, as well).                                                                               |    |

|      | The distance between the oxygen atoms varies between 2.8                                                                                         |    |

|      | and 2.9 Å                                                                                                                                        | 34 |

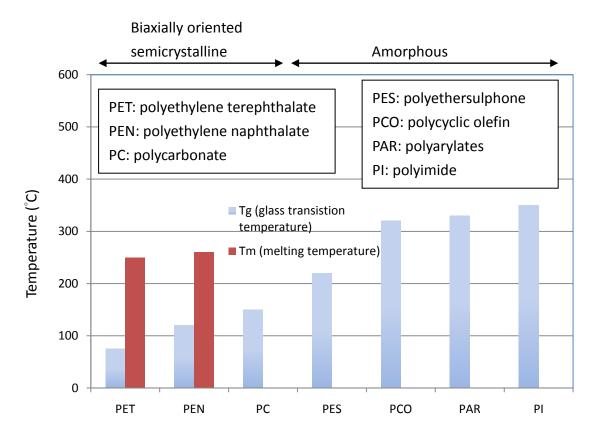

| 2.16 | Comparison of a range of plastics by glass transition                                                                                            | 39 |

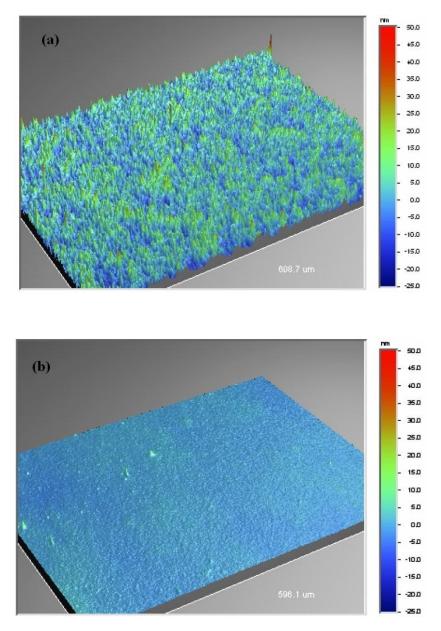

| 2.17 | Surface roughness of (a) Teonex Q83 and (b) Teonex Q65,                                                                                          |    |

|      | films produced by DuPont                                                                                                                         | 43 |

| 2.18 | The process of Ar plasma generation                                                                                                              | 45 |

| 2.19 | Magnetron sputtering                                                                                                                             | 46 |

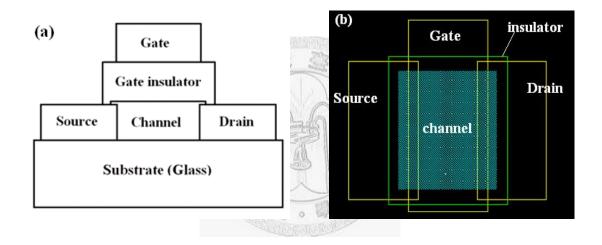

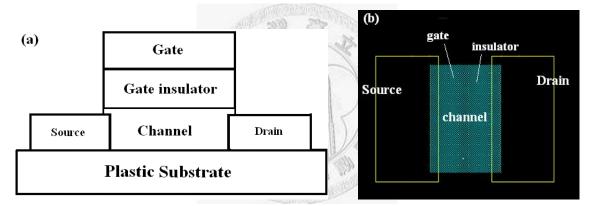

| 3.1  | The structure of the ZnO-TFT on a glass substrate. (a) A                                                                                         |    |

|      | schematic cross-sectional view of TFT structure. (b) A                                                                                           |    |

|      | perspective from top view                                                                                                                        | 52 |

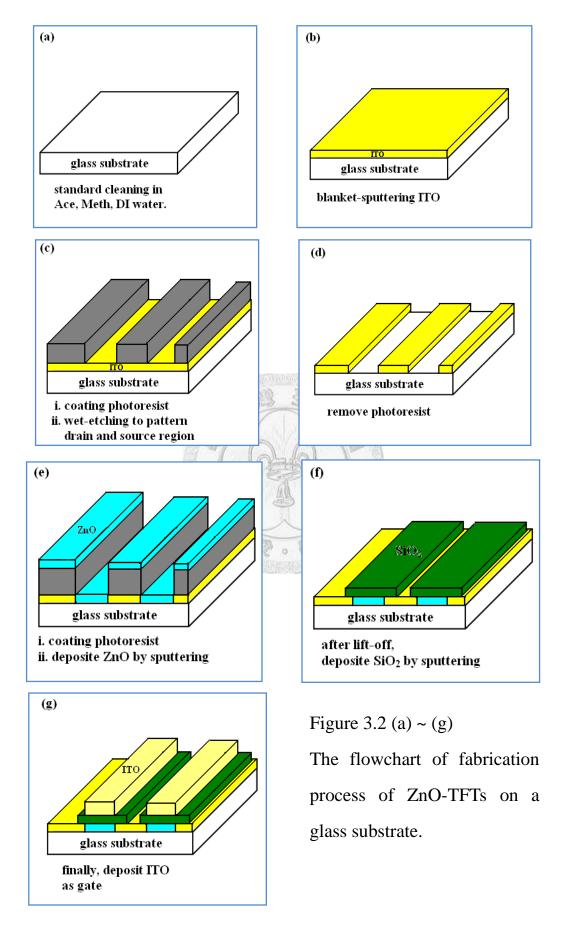

| 3.2  | (a) $\sim$ (g) The flowchart of fabrication process of ZnO-TFTs                                                                                  |    |

|      | on a glass substrate                                                                                                                             | 54 |

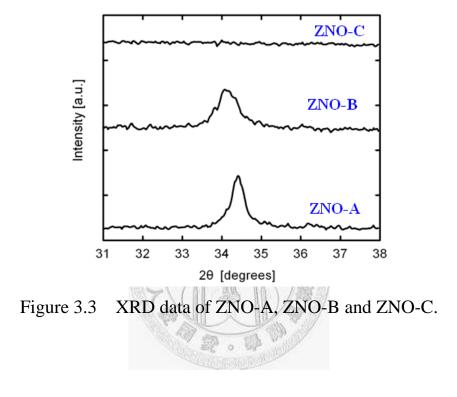

| 3.3  | XRD data of ZNO-A, ZNO-B and ZNO-C                                                                                                               | 56 |

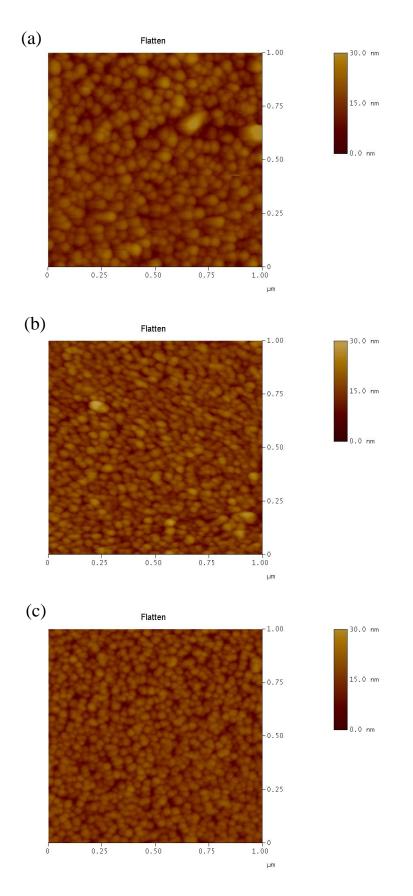

| 3.4  | AFM images of (a) ZNO-A, (b) ZNO-B and (c) ZNO-C                                                                                                 | 57 |

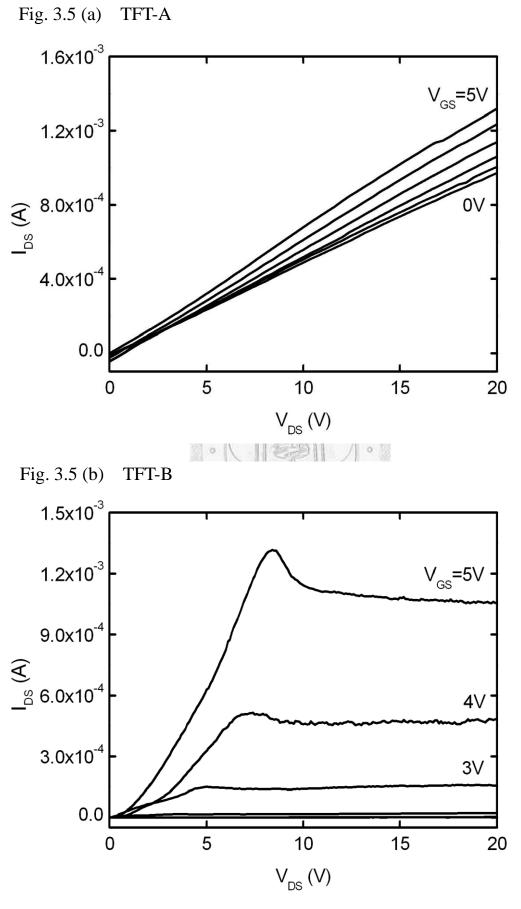

| 3.5  | I-V curves of the TFTs with (a) ZNO-A, (b) ZNO-B, and (c)                                                                                        |    |

|      | ZNO-C as channel layers, respectively 58~                                                                                                        | 59 |

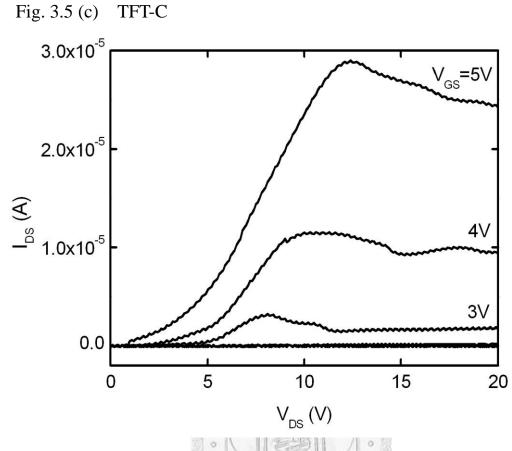

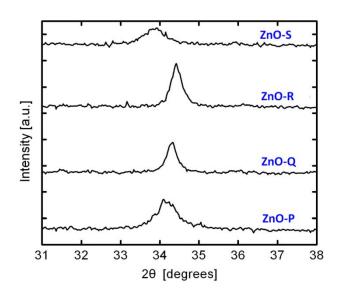

| 3.6  | XRD data of ZNO-P, ZNO-Q, ZNO-R, and ZNO-S                                                                                                       | 61 |

| 3.7  | Resistivity of ZNO-P, ZNO-Q, ZNO-R, and ZNO-S                                                                                                    | 62 |

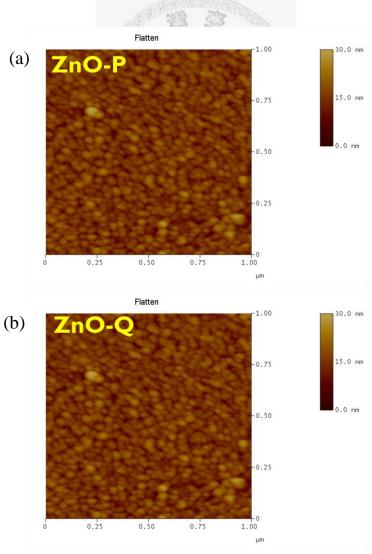

| 3.8  | AFM images of (a) ZNO-P, (b) ZNO-Q, (c) ZNO-R, and (d)                                                                                           |    |

|      | ZNO-S                                                                                                                                            | 63 |

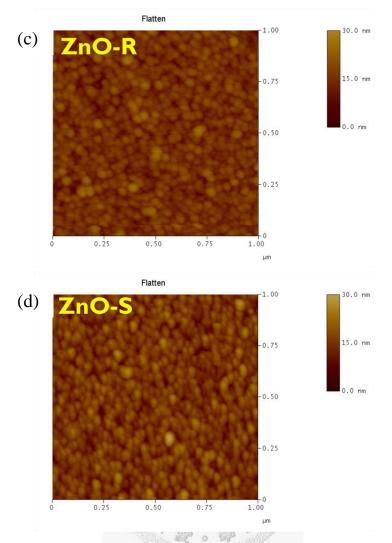

| 3.9  | I-V curves of the TFTs (a) TFT-P, (b) TFT-Q, (c) TFT-R, and                                                                                      |    |

|      | (d) TFT-S. For TFT-P and TFT-R, the transfer curves are                                                                                          |    |

|      | included                                                                                                                                         | 64 |

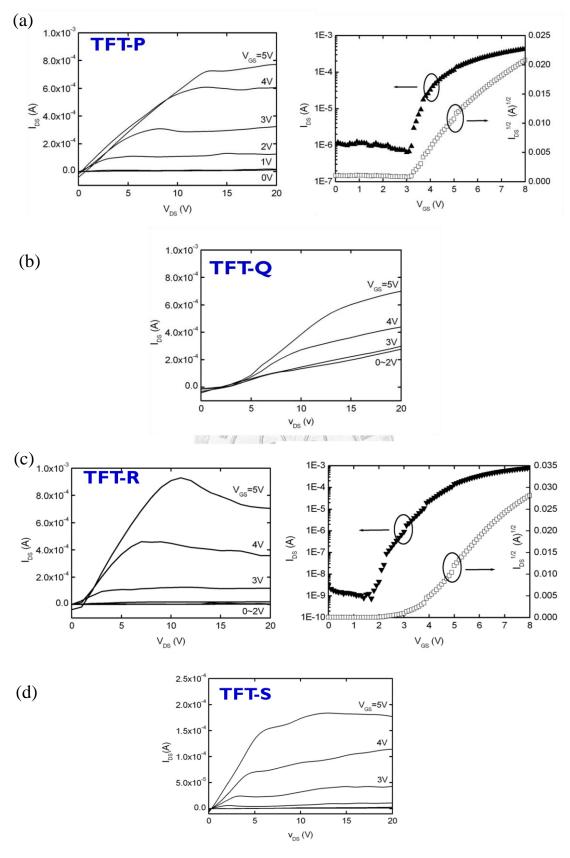

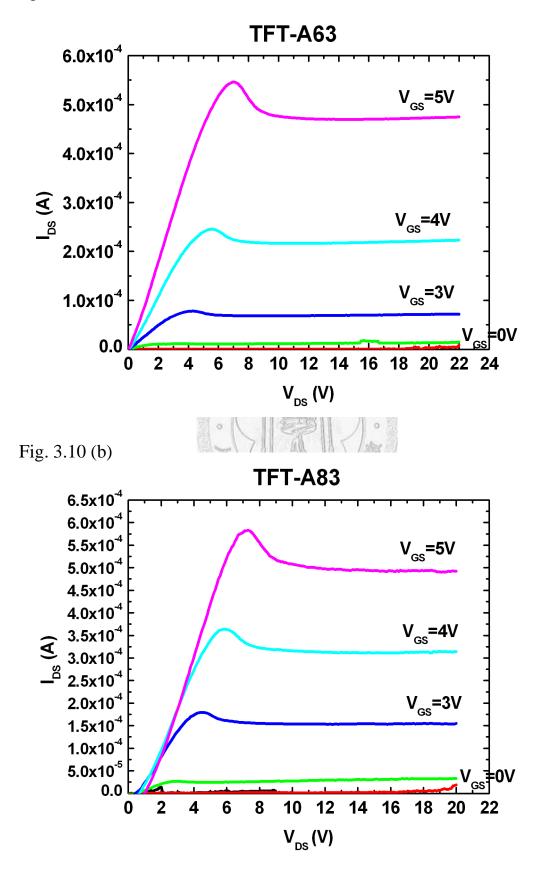

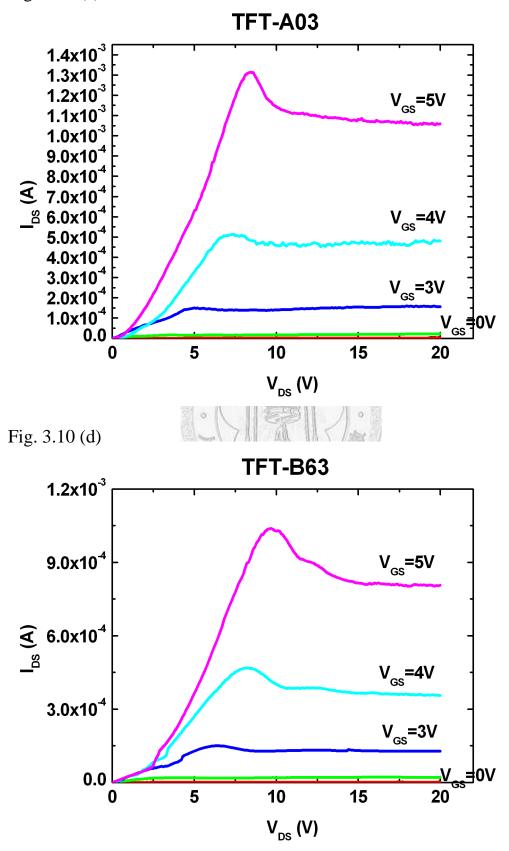

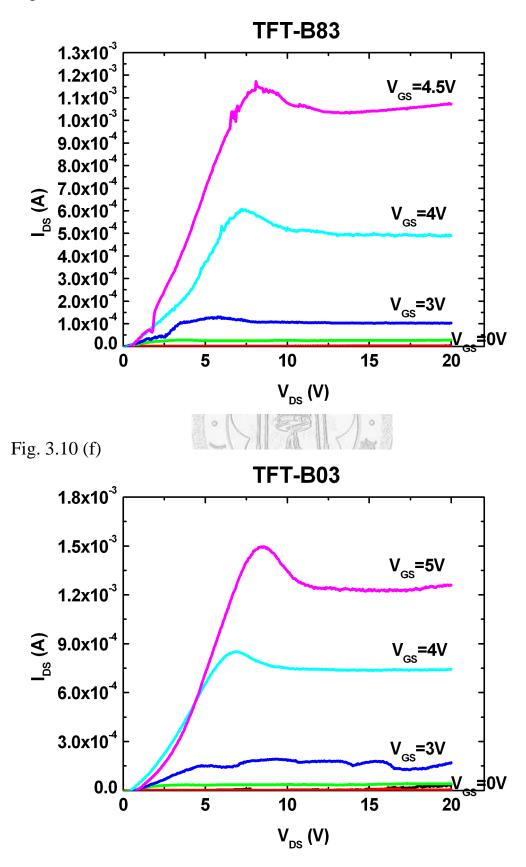

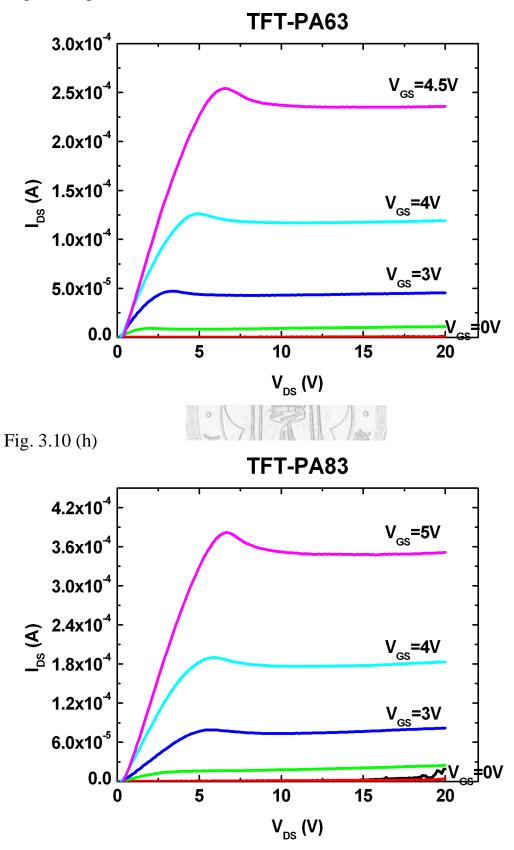

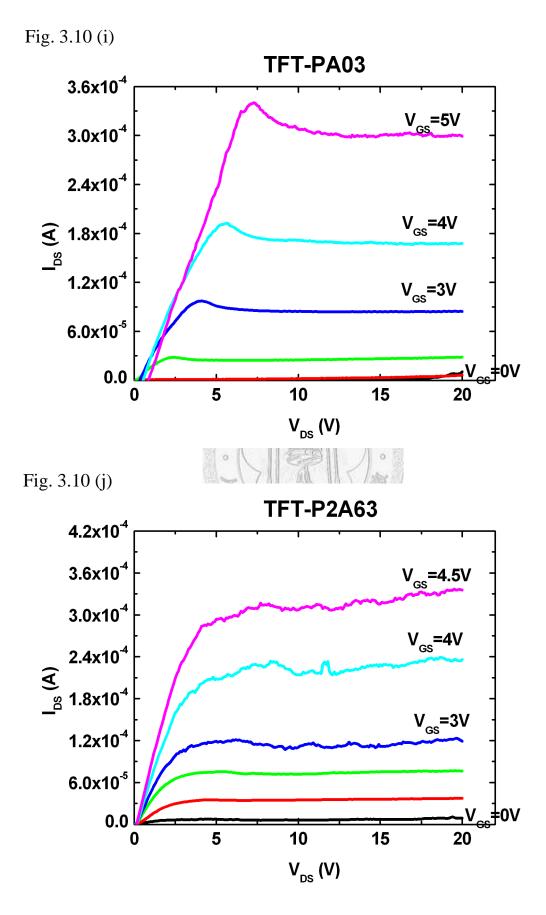

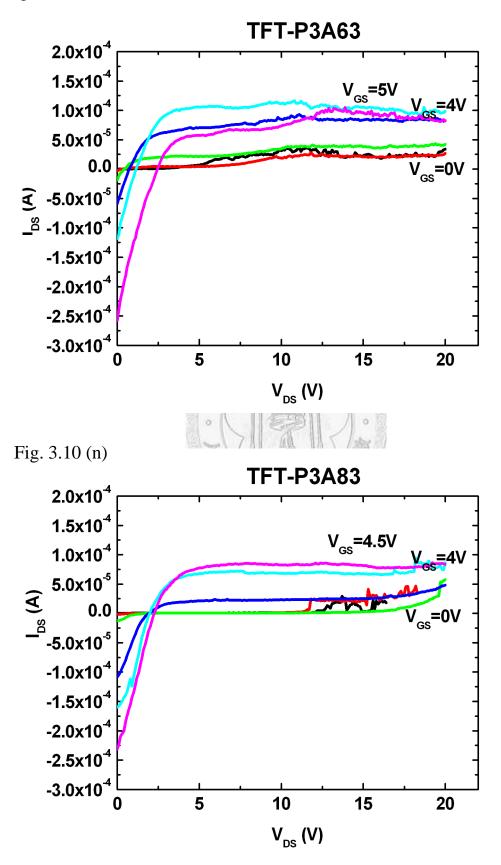

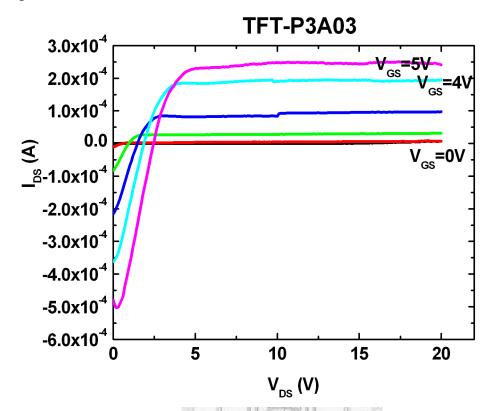

| 3.10 | (a) ~ (o) The I-V curves of the ZnO-TFTs fabricated in                                                                                           |    |

|      | various conditions as listed in Table 3.2                                                                                                        | 76 |

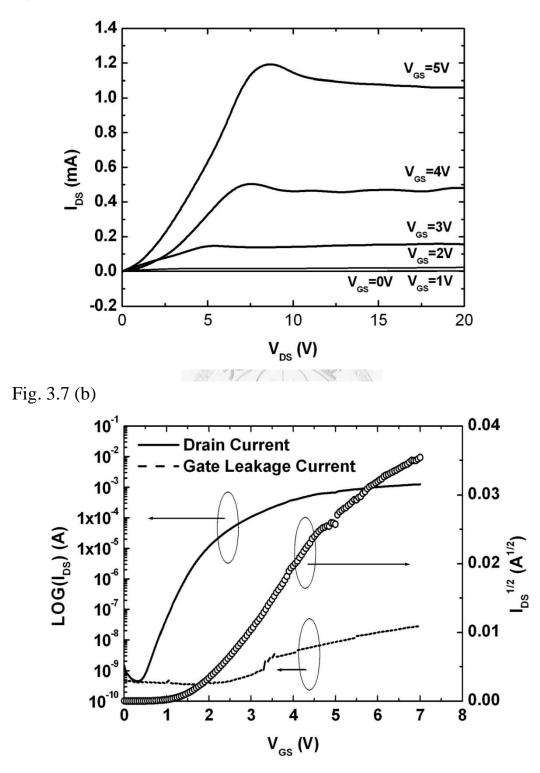

| 3.11 | Electrical characteristics of the best ZnO-TFT before alloy. (a)                                                                                 |    |

|      | $I_{DS}$ - $V_{DS}$ curves. (b) Log scale $I_{DS}$ and $I_{GS}$ as a function of $V_{GS}$ at $V_{DS}=20V$ , and the $(I_{DS})^{1/2}$ - $V_{GS}$ curve for determining the |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | threshold voltage                                                                                                                                                         | 81 |

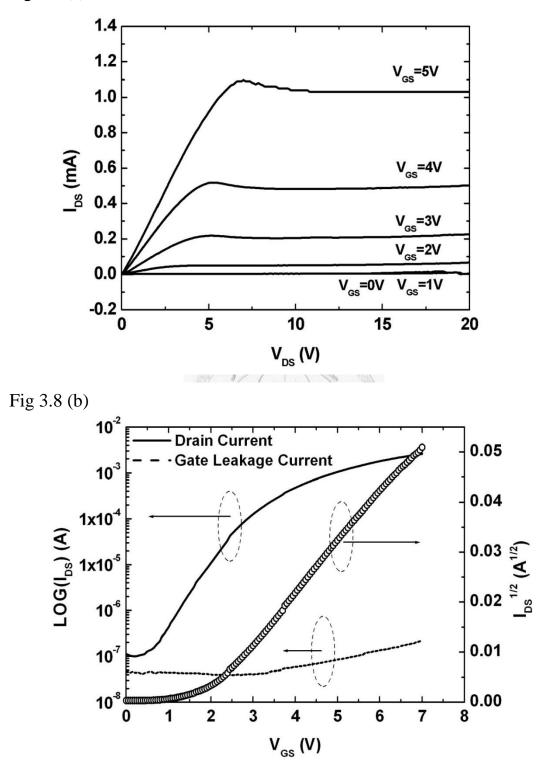

| 3.12 | Electrical characteristics of the best ZnO-TFT subject to rapid                                                                                                           |    |

|      | thermal process in $N_2.$ (a) $I_{DS}$ - $V_{DS}$ curves. (b) Log scale $I_{DS}$                                                                                          |    |

|      | and $I_{GS}$ as a function of $V_{GS}$ at $V_{DS}$ =20V, and the $(I_{DS})^{1/2}$ - $V_{GS}$                                                                              |    |

|      | curve                                                                                                                                                                     | 82 |

| 4.1  | The structure of the ZnO-TFT on a plastic substrate. (a) A                                                                                                                |    |

|      | schematic cross-sectional view of TFT structure. (b) A                                                                                                                    |    |

|      | perspective from top view                                                                                                                                                 | 83 |

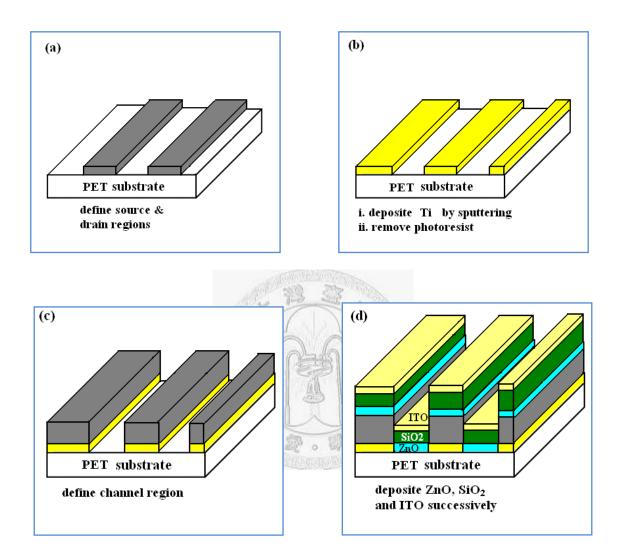

| 4.2  | (a) $\sim$ (e) The flowchart of fabrication process of the                                                                                                                |    |

|      | ZnO-TFT on PET substrate                                                                                                                                                  | 85 |

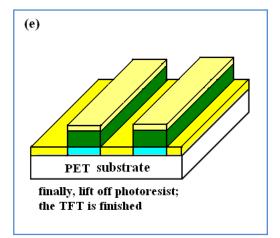

| 4.3  | The $I_{DS}$ - $V_{DS}$ curves of the ZnO-TFT on a PET substrate, using                                                                                                   |    |

|      | ITO as the source and drain. The $I_{DS}$ is 70µA when biased at                                                                                                          |    |

|      | $V_{DS}=20V$ and $V_{GS}=4V$                                                                                                                                              | 87 |

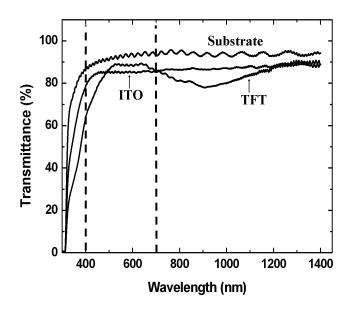

| 4.4  | Transmittance as a function of wavelength for the ZnO TFT on                                                                                                              |    |

|      | a PET substrate                                                                                                                                                           | 88 |

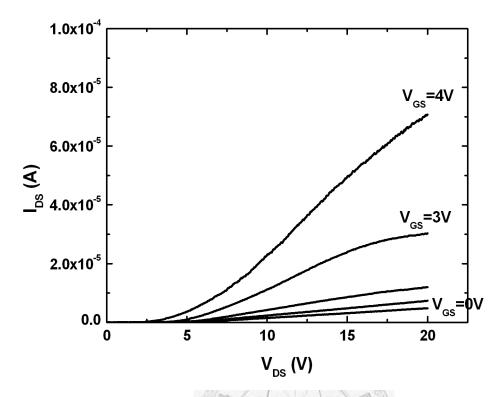

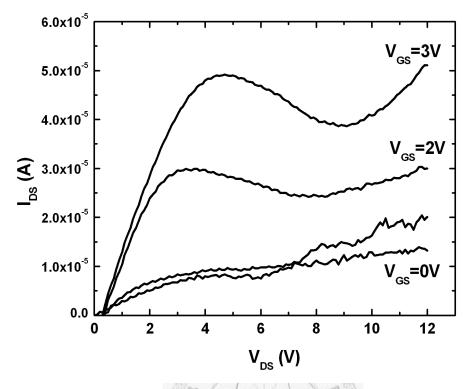

| 4.5  | The $I_{DS}$ - $V_{DS}$ curves of the ZnO-TFT on a PET substrate, using                                                                                                   |    |

|      | Ti as the source and drain. The $I_{DS}$ is 50µA when biased at                                                                                                           |    |

|      | $V_{DS}$ =12V and $V_{GS}$ =3V                                                                                                                                            | 90 |

|      |                                                                                                                                                                           |    |

# **List of Tables**

| <u>Table</u> | <u>e</u>                                                                                   | age |

|--------------|--------------------------------------------------------------------------------------------|-----|

| 2.1          | Wide band gap-based TFTs, processing methods employed,                                     |     |

|              | and electrical performance characteristics for several different                           |     |

|              | channel materials. The maximum processing temperature,                                     |     |

|              | deposition method, mobility, drain current on-to-off ratio, and                            |     |

|              | threshold voltage are included                                                             | 22  |

| 2.2          | Flexible TFTs on plastic, substrate, processing methods                                    |     |

|              | employed, and electrical performance characteristics for                                   |     |

|              | several different channel materials. The maximum processing                                |     |

|              | temperature, deposition method, mobility, drain current                                    |     |

|              | on-to-off ratio, and threshold voltage are included                                        | 25  |

| 2.3          | Properties of ZnO                                                                          | 27  |

| 2.4          | (a) For crystal MX, the symbols are defined. (b) Reactions of                              |     |

|              | defect ionization in ZnO 29-                                                               | ~30 |

| 2.5          | Dielectric constants of various insulating materials.                                      |     |

|              | Permittivity of free space $\varepsilon_0$ is 8.85419×10 <sup>-12</sup> C <sup>2</sup> /Jm | 35  |

| 2.6          | Property of glass substrates produced by famous producer in                                |     |

|              | the global world                                                                           | 37  |

| 2.7          | Property of Corning 1737                                                                   | 38  |

| 2.8          | Basic properties of plastic films used for base substrates. (Note:                         |     |

|              | The information in this table is taken from different datasheets                           |     |

|              | and should only be taken as illustrative.)                                                 | 40  |

| 2.9          | Solvent resistance of polymer substrates                                                   | 41  |

| 3.1          | ZnO thin films grown in three conditions                                                   | 56  |

| 3.2          | Summary of the results obtained in various ratios of Ar to O <sub>2</sub>                  | 60  |

| 3.3          | ZnO thin films post-passivated in four conditions                                          | 61  |

| 3.4          | Summary of the results obtained in various duration of O <sub>2</sub>                      |     |

|              | plasma treatment                                                                           | 66  |

| 3.5          | The ZnO-TFTs fabricated in various conditions and their                                    |     |

|              | related performance I <sub>DS</sub> and On-off ratio included                              | 68  |

| 3.6 | The comparison of the channel behaviors and corresponding |    |  |

|-----|-----------------------------------------------------------|----|--|

|     | I-V curves of an NMOS and a ZnO-TFT                       | 78 |  |

# High Performance ZnO Thin Film Transistors on Both Glass and Plastic Substrates

## Chapter 1

## Introduction

In 1962, P. K. Weimer presented the first thin-film transistor (TFT) with a micro-crystalline cadmium sulfide semiconducting channel layer, an evaporated gate dielectric, and gold source, drain, and gate contacts [1].

In 1988, when a 14-in active-matrix (AM) TFT display was demonstrated, the electronics industries then recognized that the dream of a wall-hanging television had become a reality, thus promoting liquid crystal display (LCD) manufacturers to the "major leagues" in the electronics industry [2]. The TFT technology figured as a brilliant technology for active-matrix liquid-crystal displays (AM-LCD) with the advent of amorphous or poly-crystalline silicon as the semiconducting channel material. Nevertheless, the opaque Si-based TFTs curtailed the aperture ratio of conventional TFT-LCDs. Transparent thin film transistors thus emerged as the new focus for TFT-LCDs.

The candidates in the transparent electronics field have been mainly with respect to oxide semiconductors such as zinc oxide, tin dioxide, indium zinc oxide, etc. This thesis in the first place is devoted to the discussion of the development of fabricating zinc oxide thin film

#### transistors on glass substrates.

The cathode ray tube (CRT) and AM-LCD recently celebrated their 100<sup>th</sup> and 25<sup>th</sup> anniversary, respectively [3]. The arrival of portable electronic devices has put a premium on durable, lightweight, and inexpensive display component, which triggers the research on flexible electronics. Moreover, flexible display technology enables flexible electronics devices such as electronic papers (e-paper) to be "green" products in substitution for paper. As we know it, "Greenhouse Effect" concerns all human beings in the global world in the 21<sup>th</sup> century. Fig. 1.1 shows some display application of flexible electronics [4].

The convergence of state-of-the-art technologies (substrates, conducting layers, barrier layers, electro-optic materials, thin film transistor technologies, and manufacturing process) is accelerating the flexible flat panel display concept closer to commercial reality. The thesis secondly investigates the characteristics of flexible zinc oxide thin film transistors on a polymer substrate.

This thesis is organized as follows.

Chapter 2 "*Literature Review and Theory*" provides background information including overviews of transistors, previous work both in the Si-based and transparent TFT fields for a comparison of the work presented in this thesis, material properties, substrate properties, and sputtering technology background.

Chapter 3 "Fabrication of ZnO TFTs on a Glass Substrate" consists of

device fabrication procedures for glass substrates and describes results obtained with regard to the ZnO TFTs developed in this work.

Chapter 4 "*Fabrication of ZnO TFTs on Plastic Substrates*" consists of device fabrication procedures for polymer substrates and presents the results obtained with regard to the ZnO TFTs developed in this work.

Chapter 5 "*Conclusions and Recommendations for Future Work*" consists of a summary of the conclusions drawn from the experiments performed in this thesis and recommendations for future work on ZnO-TFTs fabricated on both glass and plastic substrates.

Fig. 1.1 (a)

Fig. 1.1 (b)

Fig. 1.1 (c)

Figure 1.1 (a) ~ (d) The display application of flexible electronics. (a)Fujitsu e-paper. (b) An e-paper newspaper. (c) E-papers look like real sheets of paper. (d) A foldable display.

### **Chapter 1** Bibliography

[1] P. K. Weimer. "The TFT – A new thin film transistor", Proceeding of the IEEE, 1962.

[2] H. Kawamoto, "The history of liquid-crystal displays", Proceeding of the IEEE, 2002.

[3] Gregory P. Crawford, "Flexible Flat Panel Displays", John Wiley & Sons, Ltd.

[4] http://www.fujitsu.com/global/about/rd/200509epaper.html

# Chapter 2

## **Literature Review and Theory**

#### **2.1 Transistors**

#### 2.1.1 Working principles of field-effect transistors

The field-effect transistor (FET) is a type of transistors and depends on an electric field to control the shape and hence the conductivity of a channel in a semiconductor material. An FET with electrons flowing in the channel in semiconductor is so called an "n-channel" FET and likewise a 'p-channel' FET with holes flowing in the channel. Fig. 2.1(a) and (b) demonstrates the two kinds of FETs, i.e. n-channel FET and the p-channel FET respectively. The FET controls the flow of carriers by affecting the size and shape of a conductive channel created and influenced by voltage applied across the gate and source terminals.

FETs can also be categorized by the structure. Three mostly known may be "junction field-effect transistor" (JFET), "thin film transistor" (TFT) and "metal-oxide-semiconductor field-effect transistor" (MOSFET). MOSFET is theoretically stated as follows to form a basic concept of operation principles of FETs.

An n-channel MOSFET (NMOS) along with the device structure is shown in Fig. 2.2.

Figure 2.1 FETs: (a) n-channel FET; (b) p-channel FET.

In the first instance, consider the case the voltage between source and drain ( $V_{DS}$ ) is quite small compared to the voltage between source and gate ( $V_{GS}$ ). When gate is at zero bias (relative to source), the  $n^+$ -p- $n^+$  structure can be seen as a reverse cascade of two pn junction diodes and no current flows through the path; NMOS is cut-off, as illustrated in Fig. 2.3 (a). As applying a small positive voltage to gate, the majority carriers (holes) in p-type semiconductor will be repelled and then the depletion region forms in the surface of p-type semiconductor, as illustrated in Fig. 2.3(b). Once

gate voltage achieves the threshold voltage (V<sub>th</sub>), the inversion layer (channel) exactly appears in the surface of *p*-type semiconductor and the minority carriers (electrons) start to accumulate in the channel, as illustrated in Fig. 2.3(c). With increasing gate voltage, the number of accumulating electrons increases while the depletion region almost remains constant, as illustrated in Fig. 2.3(d). Fig. 2.4 shows the output characteristics (I<sub>D</sub>–V<sub>DS</sub> curves at different gate bias) mentioned above. The uniform distribution (since V<sub>GS</sub>  $\approx$  V<sub>DS</sub>) of electrons results in the same effective channel thickness (*t*) everywhere so the resistance described by  $R_{DS}=\rho L/Wt$  ( $\rho$  for resistivity of p-type semiconductor, *L* for channel length, *W* for channel width) is nearly constant and I–V curves looks almost linear or ohmic.

Figure 2.3 The depletion region and the channel at different gate bias. (a)

Figure 2.4 Output characteristics when V<sub>DS</sub> is quite small.

What if  $V_{DS}$  increases? If  $V_{DS}$  increases,  $V_{GD}$  becomes smaller than  $V_{GS}$  and thus the channel thickness begins to be asymmetric. From Fig. 2.5 (a), it is obviously seen that the channel thickness beside drain is

thinner than that beside source. Because of the reduction of the average channel length, the resistance rises and hence the I–V curve starts bending downwards. When  $V_{DS}$  achieves  $V_{Dsat}$  (onset of saturation), the inversion layer beside drain disappears and the channel beside drain is exactly pinched off, as illustrated in Fig. 2.5(b). Beyond  $V_{Dsat}$ , the pinched-off length of the channel slightly increases ( $\Delta L \ll L$ ) and depletion region between drain and channel comes into being, as illustrated in Fig. 2.5 (c).

To furthermore explain the saturated behavior beyond  $V_{Dsat}$ , point X is defined as the place where the inversion layer exactly disappears when  $V_{DS}$ >  $V_{Dsat}$ , as seen in Fig. 2.5 (c). By definition,  $V_{GX}$  is always equal to  $V_{th}$ and is independent of  $V_{DS}$ . Therefore,  $V_{XS}$  is also independent of  $V_{DS}$ . In addition, the effective channel length and the carrier (electrons) concentration both are less affected by  $V_{DS}$  since  $\Delta L \ll L$ . As a result,  $I_D$ remains constant when  $V_{DS} > V_{Dsat}$ .

The typical output characteristics of NMOS are shown in Fig. 2.6 with three marked points (a), (b), and (c) corresponding to Fig 2.5 (a), Fig 2.5 (b) and Fig 2.5 (c), respectively.

Since the channel of NMOS is enhanced to be active by applied gate voltage, such NMOS is an enhancement-mode FET. On the contrary, the channel of depletion-mode FETs is depleted to be inactive by applied gate voltage.

Figure 2.5 Variation of channel and depletion region at a constant  $V_G$  when (a)  $V_{DS} < V_{Dsat}$ ; (b)  $V_{DS} = V_{Dsat}$ ; (c)  $V_{DS} > V_{Dsat}$ .

Figure 2.6 Output characteristics.

The current-voltage relationship can be expressed as follows [1]. In the non-saturation region, we will obtain

$$I_{D} = \frac{1}{2} \mu_{n} C_{OX} \frac{W}{L} [2(V_{GS} - V_{th})V_{DS} - V_{DS}^{2}] \dots 2^{-1}$$

and, in the saturation region, we will have

$$I_{\rm D} = \frac{1}{2} \mu_{\rm n} C_{\rm OX} \frac{W}{L} (V_{\rm GS} - V_{\rm th})^2 \dots 2^{-2}$$

where  $\mu_n$  is the mobility of the electrons in the inversion layer and,

$$C_{OX} = \frac{\epsilon_{OX}}{t_{OX}}$$

.....2-3

where  $\epsilon_{0X}$  is the permittivity of the oxide and  $t_{0X}$  is the thickness of the oxide.

#### 2.1.2 Operation of thin film transistors

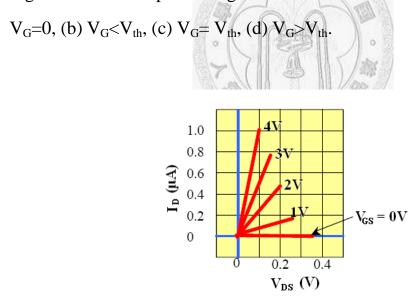

The operation of TFT and MOSFET is similar in that the current from the source to the drain is modulated by the applied gate electric field. Current modulation in a TFT or a MOSFET can be explained if the metal-oxide-semiconductor (MOS) part of the TFT is considered as a capacitor [2].

Fig. 2.7 shows the cross-section and energy band diagrams of a MOS capacitor with an n-type semiconductor. Fig. 2.7 (b) shows the equilibrium state, without gate bias applied, for an ideal case in which no charge is present in the insulator or at the insulator/semiconductor interface so that the energy bands are flat.

A positive voltage applied to the gate electrode, as shown in Fig. 2.7 (c), causes the energy bands to bend downwards, hence increasing the electron concentration at the insulator-semiconductor interface. The interface is therefore more conductive than the bulk of the semiconductor. This mode of operation in which majority carriers, electrons in this case, accumulate at the insulator-semiconductor interface and give rise to the channel current is denoted as the accumulation-mode operation. When a small to moderate negative voltage is applied to the gate electrode, majority carrier electrons are repelled from the insulator-semiconductor interface so that a depletion layer is formed. When a larger negative voltage is applied the gate, as shown in Fig. 2.7 (d), the depletion layer reaches a maximum thickness after which minority carriers, holes in this case, form a conductive channel at the insulator-semiconductor interface. This conductive channel gives rise to what is denoted inversion-mode operation,

since the conductivity type is inverted with respect to the semiconductor bulk. MOSFETs usually operate in inversion-mode whereas TFTs operate in accumulation-mode.

Figure 2.7 (a) The cross-section of a MOS capacitor and corresponding energy band diagrams for several biasing conditions: (b) equilibrium, (c) accumulation ( $V_{GS} > 0$  V), and (d) inversion ( $V_{GS} < 0$  V).

Figure 2.8 shows a three terminal n-channel TFT for accumulation-mode operation. A positive voltage is applied to the gate electrode to attract electrons to the insulator-semiconductor interface and

forms an accumulation layer. The drain electrode is biased positively with respect to the source to attract electrons from the accumulation channel. At zero or small positive voltages applied to the drain electrode, the accumulation layer formed, as shown in Fig. 2.8 (a), is uniform from the source end to the drain end of the channel. At a small drain voltage, the TFT operates as resistor where the drain current (I<sub>D</sub>) increases linearly with increase in the drain voltage (V<sub>DS</sub>). However, at slightly larger drain voltages, the linear dependence of I<sub>D</sub> on V<sub>DS</sub> changes to a quadratic dependence on  $V_{DS}$ . This entire regime of TFT operation, where  $I_D$ increases with increasing  $V_{DS}$ , is called triode or pre-pinch-off. As  $V_{DS}$  is further increased, the effective voltage between the gate and drain  $(V_{GD})$ decreases, which decreases the electron concentration at the drain end of the accumulation layer. The drain voltage, at which the accumulation channel is fully depleted of electrons, is called the pinch-off voltage and is denoted as  $V_{Dsat}$ . When  $V_{DS} \ge V_{Dsat}$ , drain voltage has no effect on  $I_D$  so that the drain current saturates. This is referred to as the post-pinch-off regime, and is shown in Fig. 2.8 (b).

Figure 2.8 An n-channel accumulation-mode TFT operating in (a) pre-pinch-off and (b) post-pinch-off regime.

Depending on the gate voltage required to form an accumulation layer, TFT can be classified as either an enhancement-mode or a a depletion-mode device. In enhancement-mode operation of an n-channel TFT, a positive voltage must be applied to the gate electrode to create an accumulation layer at the insulator-semiconductor interface. For depletion-mode operation, the accumulation layer is already present at zero gate voltage. Thus, for an n-channel TFT, a negative gate voltage has to be applied to deplete the accumulation channel and turn the device off. Therefore, an enhancement-mode device is a "normally-off" device, whereas a depletion-mode device is "normally on". In an ideal TFT model in which traps are neglected, the TFT would be a depletion-mode device because of the presence of zero-bias carriers (bulk carriers) available for current conduction. However, the presence of empty traps, which must be filled with carriers prior to the formation of the accumulation layer, gives rise to enhancement-mode operation of the TFT [3].

#### 2.1.3 Si-based thin film transistors

The structure of conventional a-Si TFTs for commercial TFT-LCDs is illustrated as Fig. 2.9. Typically, there are five to seven steps to make commercial a-Si TFTs and the flow of the fabrication process is also outlined in the inset of Fig. 2.9 [4].

Figure 2.9 Structure of an a-Si TFT and in the inset, the flowchart outlines the processes for making an a-Si TFT array using a bottom-gate TFT structure and an independent storage capacitor.

Obviously, there are significant differences between the structure of a MOSFET and a TFT. Fig. 2.10 shows typical cross-sectional views of a MOSFET and a TFT.

Figure 2.10 Cross-sectional view of a (a) MOSFET and (b) TFT.

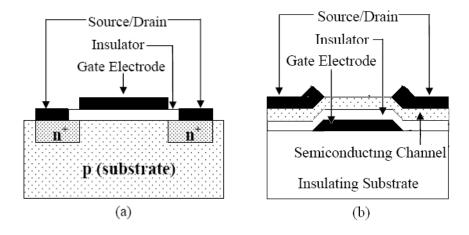

As evident from Fig. 2.10, the substrate of a TFT is an insulating material, while the substrate of a MOSFET is a semiconductor material (p-type) of opposite polarity as the source and drain diffusions (n-type). Source and drain contacts to the semiconducting channel material are injecting contacts to the channel in a TFT structure, instead of ohmic contacts to a pn junction as in a MOSFET.

Four TFT device structures are possible, as indicated in Fig. 2.11, and are categorized as staggered or coplanar. In a staggered configuration, as shown in Figs. 2.11 (a) and 2.11 (c), the source/drain contacts are on opposite sides of the channel from the insulator, whereas in a coplanar configuration, as shown in Figs. 2.11 (b) and 2.11 (d), the source/drain contacts and the insulator are on the same side of the channel. Both the staggered and the coplanar configurations can further be classified as bottom-gate and top-gate structures. A bottom-gate TFT, also referred to an inverted TFT, has the gate insulator and gate electrode located beneath the channel, as shown in Figs. 2.11 (a) and 2.11 (b). In a top-gate device,

as shown in Figs. 2.11 (c) and 2.11 (d), the channel is covered by a gate insulator and gate electrode.

The coplanar structure is popular in polycrystalline silicon TFTs, whereas staggered structures are commonly used in amorphous silicon TFTs. The inverted, staggered structure is the most popular amorphous silicon TFT structure, because it gives the best transistor characteristics and offers significant process latitude [5].

Top-gate TFTs are usually fabricated with an aluminum gate since gate deposition is one of the last deposition steps in the fabrication process of this type of TFT, after which no high temperature processing is required. Passivation of the channel material by the gate insulator is an added advantage of a top-gate structure.

Figure 2.11 Four thin-film transistor configurations: (a) staggered bottom-gate, (b) coplanar bottom-gate, (c) staggered top-gate, and (d) coplanar top-gate.

As for the performance of a-Si TFTs reported so far, the field-effect mobility reaches from 0.1 to 2 cm<sup>2</sup>/Vs and the threshold voltage ranges from 2 to 10 V [6-9]. For polysilicon TFTs, the reported mobility can achieve as high as 50 cm<sup>2</sup>V/s and its threshold voltage is about 1V [10]. However, the fabrication temperature and the opacity of Si-based TFTs limit the possibilities of applications for transparent and/or flexible electronics.

#### 2.1.4 Oxide-semiconductor-based thin film transistors

The development of transparent and/or flexible electronics motivates the studies on oxide semiconductor materials such as ZnO [11], SnO<sub>2</sub> [12], IGZO (indium gallium zinc oxide) [13], and IZO (indium zinc oxide) [14]. Despite the amorphous structure of these materials, they attract attention mainly due to high electron mobility. Some examples already produce devices with field-effect mobilities reaching above 50 cm<sup>2</sup>/Vs and on-off ratio of 10<sup>-6</sup> to10<sup>-7</sup> [11-14].

Table 2.1 summarizes the work regarding wideband gap semiconductors for use as TFTs [12], for this work is directly relevant to the research reported in this thesis.

The use of ZnO channel in the field effect transistor as one of the *majority* carrier devices has been demonstrated in 1968 with using a bulk single crystal [15]. Notably, it's the *majority* carrier that transports in the channel and no inversion layer is induced by applied gate voltage in the cases of ZnO-based TFTs.

Table 2.1 Wide band gap-based TFTs, processing methods employed, and electrical performance characteristics for several different channel materials. The maximum processing temperature, deposition method, mobility, drain current on-to-off ratio, and threshold voltage are included.

| Channel          | Max. Proc. | Dep.             | Mobility              | On-Off          | Threshold   | Ref. |

|------------------|------------|------------------|-----------------------|-----------------|-------------|------|

| Material         | Temp. (°C) | Method           | (cm <sup>2</sup> /Vs) | Ratio           | Voltage (V) |      |

| ZnO              | Room Temp  | RFS <sup>a</sup> | 2                     | 10 <sup>6</sup> | 0           | [16] |

| ZnO              | 300        | $PLD^b$          | 7                     | 10 <sup>7</sup> | 0           | [17] |

| ZnO              | 450        | PLD              | 0.97                  | 10 <sup>5</sup> | -1          | [18] |

| ZnO              | 700        | IBS <sup>c</sup> | 2.5                   | 10 <sup>7</sup> | 10-20       | [19] |

| ZnO              | 700        | $\mathbf{SC}^d$  | 0.2                   | 107             | 10-20       | [20] |

| (Zn,Mg)O         | 600        | PLD              | 5.32                  | 10 <sup>3</sup> | 3           | [21] |

| SnO <sub>2</sub> |            | PLD              | 5 5/4                 | 2               | -2          | [22] |

| IZO              | 600        | RFS              | 45-55                 | 10 <sup>6</sup> | -20 ~ -10   | [14] |

| ZTO              | 600        | RFS              | 20-50                 | 10 <sup>7</sup> | -5 ~ +5     | [23] |

| IGZO             | Room Temp  | PLD              | 5.6                   | 10 <sup>3</sup> | 1.6         | [13] |

<sup>*a*</sup> radio frequency sputtering

<sup>b</sup> pulsed layer deposition

<sup>c</sup> ion beam sputtering

<sup>*d*</sup> spin coating

#### 2.1.5 Flexible thin film transistors

There are three main choices for flexible substrates, which include polymeric, thin glass and steel foil. As far as roll-up, lightweight, impact resistance, and cost are concerned, polymeric substrates are the first choice. A number of issues are discussed for TFTs on polymeric substrates. Process temperature limitations as a function of polymer type is one of the biggest challenges since polymers undergoing deformation at high temperature conditions invalid the TFTs. The detailed properties of some polymeric substrates are expounded in section 2.3.2.

The popular materials nowadays for channel layer are *a*-Si, pentacene (organic), and oxide semiconductor such as ZnO. *a*-Si deposited at limited low temperature achieves poor crystallization and hence quite low mobility, usually less than 2 cm<sup>2</sup>/Vs. Post-approaches like thermal annealing are needed to improve the electrical performance of *a*-Si TFTs on plastic. As for organic materials, the low mobility and poor reliability restrain its development while organic TFTs (OTFTs) need lower process temperature.

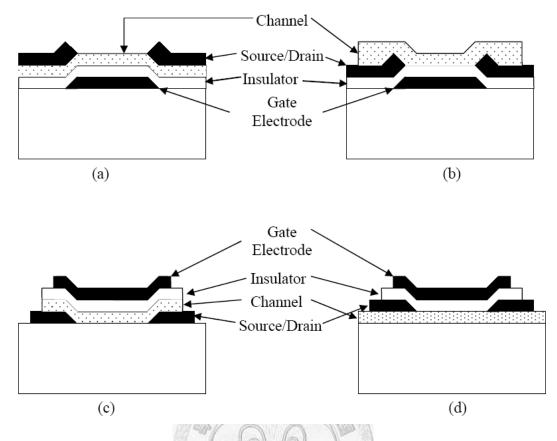

Amorphous and polycrystalline ZnO can be obtained by sputtering at room temperature with high mobility. In addition, the carrier concentration can be engineered by controlling the dopants or the  $O_2$ presence. Fig. 2.12 shows the material properties of indium-gallium-zinc oxide (IGZO) system [26].

Table 2.2 summarizes the representative work of flexible TFTs on plastic to date, kinds of popular materials and common substrates included.

Figure 2.12 Material properties of IGZO system. Room temperature Hall mobility and carrier concentration as functions of chemical composition. Values outside and inside parentheses show Hall mobility in  $cm^2/Vs$  and carrier concentration in  $10^{18}$  cm<sup>-3</sup>, respectively.

Table 2.2 Flexible TFTs on plastic, substrate, processing methods employed, and electrical performance characteristics for several different channel materials. The maximum processing temperature, deposition method, mobility, drain current on-to-off ratio, and threshold voltage are included.

| Channel          | Substrate <sup><i>i</i></sup> | Max. Proc. | Dep.               | Mobility    | On-Off            | Threshold | Ref. |

|------------------|-------------------------------|------------|--------------------|-------------|-------------------|-----------|------|

| Material         |                               | Temp. (°C) | Method             | $(cm^2/Vs)$ | Ratio             | Voltage   |      |

|                  |                               |            |                    |             |                   | (V)       |      |

| a-Si:H           | PEN                           | 120        | PECVD <sup>e</sup> | 0.8         | $10^{6} - 10^{7}$ | 4.5       | [24] |

| a-Si:H           |                               | 180        | PECVD              | 0.8~1       | $10^{6}$          | 3         | [25] |

| a-IGZO           | PET                           | Room Temp  | PLD                | 10          | $10^{6}$          | 1.3       | [26] |

| ZnO              | PI                            | Low Temp   | RFS                | 50          | $10^{5}$          | 3.2       | [27] |

| ZTO              | PI                            | 300        | RFS                | 14          | $10^{6}$          | -8.8      | [28] |

| Pentacene        | PEN                           |            | TE <sup>g</sup>    | 0.67        | $10^{4}$          | -0.88     | [29] |

| $\mathrm{CNT}^h$ |                               | Room Temp  | IP <sup>f</sup>    | 47,662      | 1.08              | -2.5      | [30] |

<sup>*e*</sup> plasma-enhanced chemical deposition

<sup>f</sup> inject printing

<sup>*g*</sup> thermal evaporation

<sup>*h*</sup> carbon nanotube

<sup>*i*</sup> also see section 2.3.2

#### **2.2 Property of Materials**

#### 2.2.1 Zinc Oxide (ZnO)

ZnO material has drawn much attention recently for its good optical and electrical properties. With such potential advantages as wide bandgap (3.4eV), large exciton binding energy (60meV), high Hall mobility and so on, ZnO is widely studied in various fields such as thin film transistors, transparent conducting electrodes, varistors, ultraviolet emitting diodes, etc. Besides, ZnO even becomes a popular material for commercial cosmetic products and sunglasses because of its capability of absorption of ultraviolet light.

The property of ZnO is listed in Table 2.3 [31]. Because the bandgap of ZnO is 3.4eV, ZnO is transparent in the visible light. Transparent oxide semiconductor materials make possible replacement of opaque Si as channel layer of TFTs and improvement of aperture ratio of TFT-LCD. ZnO is a promising candidate among these oxide semiconductors. Furthermore, polycrystalline ZnO thin film can be achieved at lower growth temperature by methods of sputtering, pulsed laser deposition, chemical vapor deposition, molecular beam epitaxy, and inkjet printing, etc. Better crystallization means higher mobility and hence higher operating current. In these respects, ZnO is more attractive and feasible than organic- or Si-based TFTs when cheap and/or transparent substrates made of glass or polymer are chosen.

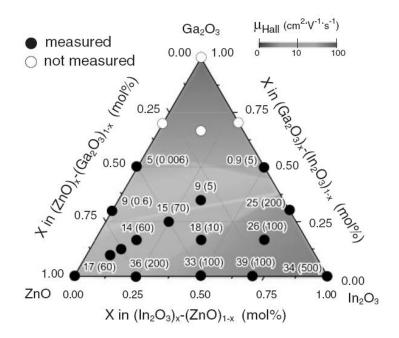

ZnO crystallizes with the wurtzite structure is shown in Fig. 2.13.

| Property                                               | Value                                              |  |  |  |  |

|--------------------------------------------------------|----------------------------------------------------|--|--|--|--|

| Crystalline                                            | Hexagonal                                          |  |  |  |  |

| Lattice parameter at 300K:                             |                                                    |  |  |  |  |

| a                                                      | 3.252 Å                                            |  |  |  |  |

| С                                                      | 5.313 Å                                            |  |  |  |  |

| c/a                                                    | 1.602 Å (1.633 for ideal hexagonal structure)      |  |  |  |  |

| Density                                                | $5.606 \text{ g/cm}^3$                             |  |  |  |  |

| Stable phase at 300K                                   | Wurtzite                                           |  |  |  |  |

| Melting point                                          | 1975°C                                             |  |  |  |  |

| Thermal conductivity                                   | 0.6, 1–1.2                                         |  |  |  |  |

| Linear expansion coefficient (/°C)                     | $a: 6.5 \times 10^{-6}$<br>$c: 3.0 \times 10^{-6}$ |  |  |  |  |

| Static dielectric constant                             | 8.656                                              |  |  |  |  |

| Refractive index                                       | 2.008, 2.029                                       |  |  |  |  |

| Energy gap                                             | 3.4eV, direct                                      |  |  |  |  |

| Intrinsic carrier concentration                        | $< 10^{6} \mathrm{cm}^{-3}$                        |  |  |  |  |

| Exciton binding energy                                 | 60 meV                                             |  |  |  |  |

| Electron effective mass                                | 0.24                                               |  |  |  |  |

| Electron Hall mobility at 300K for                     | $200 \text{ cm}^2/\text{Vs}$                       |  |  |  |  |

| low n-type conductivity                                | 200 CIII / V S                                     |  |  |  |  |

| Hole effective mass                                    | 0.59                                               |  |  |  |  |

| Hole Hall mobility at 300K for low p-type conductivity | $5-50 \text{ cm}^2/\text{Vs}$                      |  |  |  |  |

Table 2.3Properties of ZnO

Figure 2.13 Crystal structure of wurtzite ZnO.

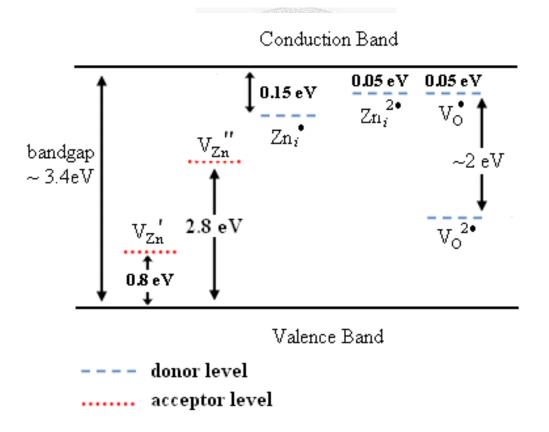

Figure 2.14 Energy levels of native defects in ZnO. The donor defects are  $Zn_i^{2\bullet}$ ,  $Zn_i^{\bullet}$ ,  $Zn_i^{\bullet}$ ,  $V_0^{2\bullet}$ ,  $V_0^{\bullet}$ ,  $V_0$  and the acceptor defects are  $V_{Zn}^{"}$ ,  $V_{Zn}^{"}$ .

For *n*-type ZnO, it's considered that zinc interstitials (Zn<sub>*i*</sub>) and oxygen vacancies (V<sub>0</sub>) act as donors and may account for the *n*-channel behavior [27]. The model that Zn<sub>*i*</sub> and V<sub>0</sub> are indentified as dominant donors in ZnO however is challenged by some novel theory and experiment [32], but others find the amount of  $O_2$  when depositing ZnO film does affect the conductivity and carrier concentration of ZnO. The reaction of defects in ZnO is listed in Table 2.4 and the related ionization energy is diagramed in Fig. 2.14 [33].

| $M_i$ M atom on interstitial site |

|-----------------------------------|

|                                   |

- $X_i$  X atom on interstitial site

- N<sub>M</sub> Impurity N on M site

- V<sub>M</sub> Vacancy on M site

Table 2.4

M<sub>M</sub>

X<sub>X</sub>

- V<sub>X</sub> Vacancy on X site

- V<sub>i</sub> Vacant interstitial site

- e' Electron in conducting band

- h<sup>·</sup> Hole in valence band

Table 2.4(b) Reactions of defect ionization in ZnO

$$Zn_{i} \Leftrightarrow Zn_{i}^{\bullet} + e'$$

$$Zn_{i}^{\bullet} \Leftrightarrow Zn_{i}^{2\bullet} + e'$$

$$V_{o} \Leftrightarrow V_{o}^{\bullet} + e'$$

$$V_{o}^{\bullet} \Leftrightarrow V_{o}^{2\bullet} + e'$$

$$V_{Zn} \Leftrightarrow V_{Zn}' + h^{\bullet}$$

$$V_{Zn}' \Leftrightarrow V_{Zn}'' + h^{\bullet}$$

The two mechanisms for explaining the behavior of *n*-type ZnO are also stated in detail by *Richard A. Swalin* [34]. The symbols of the following equations have been defined in Table 2.4.

(a) Formation of anion vacancies with complete ionization of anion vacancy donors according to the following reaction:

$$O_0 = \frac{1}{2}O_2(g) + V_0^{\bullet} + e' \dots 2.4$$

where  $V_0^{\bullet}$  is a singly ionized oxygen vacancy and *e'* is an electron in conducting band. (The symbol [•] indicates the "hole-character" of the defect). Oxygen vacancies form a shallow electron donor level close (~0.05 eV) to the conduction band and are readily ionized near room temperature, contributing free electrons. This reaction can undergo further ionization with liberation of another electron into the conduction band [27]; that is,

$$O_0 = \frac{1}{2}O_2(g) + V_0^{2\bullet} + 2e' \dots 2.5$$

(b) Formation of ionized cation interstitials according to the following reaction:

$$\operatorname{Zn}(g) = \operatorname{Zn}_{i}^{\bullet} + e' \dots 2.6$$

Physically, this corresponds to transferring a neutral zinc atom from the vapor phase to an interstitial position. Interstitial cations tend to act as donors and, in this case, since the donor level (~0.05 eV) lies so close to the conduction band, the interstitials would be completely ionized. There could be a second ionization step according to:

The equilibrium constants for the processes (a) and (b) are:

The quantities  $p_{O_2}$  and  $p_{Z_n}$  are not independent of each other, since for the reaction for the formation of ZnO,

$$Zn(s) + \frac{1}{2}O_2(g) = ZnO(s)....2.10$$

there is an equilibrium constant

yielding

$$KK_{b} = [Zn_{i}^{\bullet}][e']p_{O_{2}}^{\frac{1}{2}}....2.12$$

If  $p_{O_2}$  decreases, [e'] increases and thereby so is the conductivity  $\sigma$ .

Further evidence concerning the nature of the defect structure comes from self-diffusion studies of Zn in ZnO. From these studies it is found that the diffusion coefficient is very high. The activation energy for the diffusion of Zn in ZnO is 0.55 eV, or 53KJ/g-atom. This value is too low for diffusion by a vacancy mechanism. The only way to explain this fast diffusion is to postulate the existence of interstitial Zn, therefore giving support to alternative (b) above. Since interstitial Zn ions are produced in concentration equal to the electron concentration,

thus, the conductivity

## 2.3.2 Indium Tin Oxide (ITO)

So far, the most widely used materials for transparent conducting oxides (TCO) are zinc oxide(ZnO), tin oxide(SnO<sub>2</sub>), and indium oxide (INO). Compared to ZnO, SnO<sub>2</sub>, and INO, tin-doped indium oxide (ITO) has lower electrical resistivity (about  $10^{-4} \Omega$  cm) and higher optical transparency (above 85% at 550 nm). As a result, ITO is more and more significant in the field of display devices, photovoltaic cells, and opto-electronic devices.

As an *n*-type degenerate semiconductor with wide bandgap ( $3.5 \text{ eV} \sim 4.3 \text{ eV}$ ) and high work-function ( $4.5 \text{ eV} \sim 5.3 \text{ eV}$ ), the mechanisms of conductive ITO can be attributed to tin dopants and oxygen vacancies. The two reactions are described as follows [35]:

$O_0 = \frac{1}{2}O_2(g) + V_0^{2^{\bullet}} + 2e' \dots 2.15$

and

$$2SnO_{2}^{\text{In}_{2}O_{3}} = 2Sn_{\text{In}} + 3O_{2} + 2e' + \frac{1}{2}O_{2}$$

....2.16

where  $Sn_{In}^{\bullet}$  denotes the  $Sn^{+4}$  which replaces  $In^{+3}$  site in  $In_2O_3$  crystal. The rest symbols in these expressions are same as what have been defined in section 2.2.1.

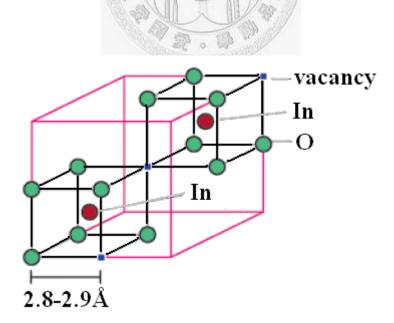

One oxygen vacancy donates two electrons as donors. In addition, since the atom size and mass of tin dopant close to what of indium, it's possible for  $\text{Sn}^{+4}$  to replace  $\text{In}^{+3}$  and then a free electron is formed as a donor. The cubic bixbyite structure of  $\text{In}_2\text{O}_3$  crystal (of ITO crystal as well) is illustrated in Fig. 2.15.

The need for ITO thin film had led to the development of various deposition techniques. Both vacuum techniques, e.g. evaporation and sputtering, and non-vacuum techniques, e.g. sol-gel and ink-jet printing. Among numerous methods, magnetron sputtering can deposit films over large areas at higher deposition rate than conventional evaporation and it needs lower fabrication temperature than evaporation. Magnetron sputtering is rationally considered to be one of the best methods for preparing ITO films. High quality ITO films grown by magnetron sputtering have already been reported since 1990's [36].

The properties of sputtered ITO are proven to be quite sensitive to sputtering environment, such as substrate temperature [37], target-to-substrate distance [38], pressure of oxygen and/or hydrogen [39], RF power [40], and post-deposition annealing treatment [41].

Figure 2.15 A simplified section of the unit cell of  $In_2O_3$  (ITO, as well). The distance between the oxygen atoms varies between 2.8 and 2.9 Å

## 2.2.3 Insulating materials

The performance of a TFT is also related with the insulating layer, which can be explained from equation 2-1, 2-2 and 2-3. From equation 2-3, higher dielectric constant leads to larger capacitance and hence the TFTs can operate in ON and OFF states distinguishably; that is, high current for ON state and low current for OFF state. The dielectric constants of the most commonly used insulating materials are listed in Table 2.5. Those materials with dielectric constants higher than that of SiO<sub>2</sub> are termed "high-*k*" materials.

Table 2.5 Dielectric constants of various insulating materials. Permittivity of free space  $\epsilon_0$  is 8.85419×10<sup>-12</sup> C<sup>2</sup>/Jm

| Material                       | Dielectric constant |

|--------------------------------|---------------------|

| SiO <sub>2</sub>               | 3.9                 |

| Si <sub>3</sub> N <sub>4</sub> | 7                   |

| $Al_2O_3$                      | 9                   |

| $Y_2O_3$                       | 15                  |

| $La_2O_3$                      | 30                  |

| $TiO_2$                        | 80                  |

| HfO <sub>2</sub>               | 25                  |

| ZrO <sub>2</sub>               | 25                  |

| Ta <sub>2</sub> O <sub>5</sub> | 26                  |

## **2.3 Property of Substrates**

#### 2.3.1 Glass substrate

The glass substrates for fabrication of TFTs have to satisfy the following demands.

- (1) To be alkali-free to prevent alkali ions from diffusing into TFT arrays.

- (2) High resistance to chemical solutions such as etchant, developer and cleanser.

- (3) Low coefficient of thermal expansion (CTE).

- (4) Good Flatness and Surface Quality

Table 2.6 [42] summarizes the characteristics of some glass substrates produced by the main producer in the global world.

Among these glass substrate, Corning 1737 and Corning 7359 are very popular for fabrication of TFTs in lab stage. Table 2.7 provides the property of Corning 1737 [43].

| Producer | Products   | Density<br>(g/cm <sup>3</sup> ) | Strain Point<br>(°C) | CTE<br>(Multiply by<br>10 <sup>-7</sup> cm/cm/°C) |

|----------|------------|---------------------------------|----------------------|---------------------------------------------------|

|          | Eagle 2000 | 2.370                           | 668                  | 32.5                                              |

| Corning  | 1737       | 2.545                           | 666                  | 37.8                                              |

|          | 7059       | 2.752                           | 593                  | 46.6                                              |

| Asahi    | AN-100     | 2.506                           | 670                  | 35.5                                              |

|          | AN-635     | 2.77                            | 635                  | 48                                                |

| NEC      | OA-2       |                                 |                      |                                                   |

| NEG      | NA-10      | 2.511                           | 651                  | 36.6                                              |

| NHT      | NA-45      |                                 |                      |                                                   |

|          | NA-35      | 2.500                           | 650                  | 36.7                                              |

| POI      | POI        | <2.500                          | 645                  | 32~37                                             |

Table 2.6Property of glass substrates produced by famous producer inthe global world.

| Glass Co                                                      | 1737                              |      |  |

|---------------------------------------------------------------|-----------------------------------|------|--|

| 1                                                             | Alkali Free Borosilicate          |      |  |

| C                                                             | Clear                             |      |  |

| Princ                                                         | Optics & electrical<br>substrates |      |  |

| Thermal Expansion<br>Multiply by<br>10 <sup>-7</sup> cm/cm/°C | 0 - 300°C.                        | 37.6 |  |

|                                                               | Strain point °C.                  | 666  |  |

| Viscosity Data                                                | Annealing point °C.               | 721  |  |

|                                                               | Softening point °C.               | 975  |  |

| Densi                                                         | Density g/cm <sup>3</sup>         |      |  |

| Log <sub>10</sub> of Volume<br>Resistivity ohm/cm.            | 250°C                             | 13.5 |  |

| Dielectric<br>Properties                                      | Dielectric constant               | 5.7  |  |

| (1 KHz 20°C)                                                  | Loss factor %                     | .10  |  |

| Refractive inc                                                | 1. 518                            |      |  |

| Transmittar                                                   | ~70% (320 nm)<br>~90% (360 nm)    |      |  |

|                                                               | >90% (380-2600 nm)                |      |  |

Table 2.7Property of Corning 1737.

## 2.3.2 Polymer substrates [44]

The plastic films that have been given serious consideration as flexible substrate for flexible electronics are show in Fig. 2.16, their abbreviations, glass transition temperature and crystallization included. The glass transition temperature limits the thermal budget of fabrication of electronic devices.

Figure 2.16 Comparison of a range of plastics by glass transition.

The clarity of the film is important for transparent electronics. A total light transmission (TLT) of >85% over 400–800 nm is typical of what is required for this application. All the base films described above meet this criterion, except for PI which is yellow; see table 2.8.

A wide range of solvents and chemicals can be used when fabricating

electronic devices on polymer substrates. Amorphous polymers in general have poor solvent resistance compared to semicrystalline polymers; see table 2.9. This deficiency is overcome by the application of a hardcoat layer (e.g.  $SiO_2$ ,  $SiN_x$  etc.) double-side coated to the polymer films, which significantly improves the solvent and chemical resistance.

Table 2.8Basic properties of plastic films used for base substrates. (Note:The information in this table is taken from different datasheets and shouldonly be taken as illustrative.)

|                                  | PET  | PEN  | PC      | PES | PAR | PCO  | PI     |

|----------------------------------|------|------|---------|-----|-----|------|--------|

| CTE<br>(-55 to 85 °C) ppm/°C     | 15   | 13   | 60-70   | 54  | 53  | 74   | 17     |

| Transmission<br>at 400–700nm (%) | >85  | >85  | >90     | 90  | 90  | 91.6 | yellow |

| Water absorption (%)             | 0.14 | 0.14 | 0.2-0.4 | 1.4 | 0.4 | 0.03 | 1.8    |

| Young's modulus<br>(GPa)         | 5.3  | 6.1  | 1.7     | 2.2 | 2.9 | 1.9  | 2.5    |

| Tensile strength<br>(MPa)        | 225  | 275  | NA      | 83  | 100 | 50   | 231    |

|             | Unit                               | PEN  | PET  | PC      | PES     |

|-------------|------------------------------------|------|------|---------|---------|

| Ketone      | Acetone                            | Good | Good | Fair    | No good |

|             | MEK                                | Good | Good | Fair    | -       |

| Alcohol     | Methanol                           | Good | Good | Good    | -       |

|             | Ethanol                            | Good | Good | Good    | Good    |

|             | Isopropanol                        | Good | Good | Good    | -       |

|             | Butanol                            | Good | Good | Good    | -       |

| Ester       | Ethyl acetate                      | Good | Good | Fair    | Good    |

| Hydrocarbon | Formalin                           | Good | Good | No good | -       |

|             | Tetrachroloethane                  | Good | Good | -       | Good    |

| Acid        | 10% HCl                            | Good | Good | -       | Good    |

|             | 10% HNO <sub>3</sub>               | Good | Good | -       | Good    |

|             | 10% H <sub>2</sub> SO <sub>4</sub> | Good | Good | -       | Good    |

|             | Acetic acid                        | Good | Good | -       | -       |

| Alkali      | 10% NaOH                           | Good | Fair | -       | Good    |

|             |                                    |      | 0    |         |         |

Table 2.9Solvent resistance of polymer substrates.

Polymers absorb water and oxygen and the amount of water and oxygen they absorb can have a very detrimental effect on both substrate and electronic devices. In principle, a perfect layer of silica only a few nanometers thick should reduce the diffusion of water and oxygen to acceptable levels (just as the 2–3 nm native oxide layer on silicon wafers protects the wafer surface from further oxidation) although in practice thin film coatings can have defects that provide easy paths for water and oxygen molecules to penetrate. This particularly retards the progress of organic electronic devices in that they require water vapor transmission rate of  $<10^{-6}$  g/m<sup>2</sup> per day and oxygen transmission rates of  $<10^{-5}$  mL/m<sup>2</sup> per day and no base polymer at present meets these extremely demanding

requirements.

The surface smoothness and cleanliness of the flexible substrates are essential to ensure the integrity of subsequent layers such as barrier and conductive coatings. With PET and PEN films, improvements in surface quality can be achieved through control of recipe and film process. This is demonstrated in Fig. 2.17 [45], which highlights the substantial reduction of surface defect peaks with two different grades of PEN film.

The surface defects which remain in the Teonex Q65, in Fig. 2.17 (b), however, are still detrimental to the performance of thin overlying layers. To remove them entirely requires the application of a coating layer, typically comprised of a scratch-resistant material. This acts to smooth over all the underlying surface defeats and additionally help to prevent surface scratches on handling.

Figure 2.17 Surface roughness of (a) Teonex Q83 and (b) Teonex Q65, films produced by DuPont.

## 2.4 Plasma reaction and sputtering [46]

Plasma is typically a partially ionized gas and is considered to be a distinct state of matter, in contrast to gases because of its unique properties. The reactions to form plasma in a vacuum system include dissociation, excitation, ionization and glow discharge. For gas  $X_2$ , the reactions can be expressed as follows:

$$e^- + X_2 \rightarrow 2X + e^-$$

(dissociation).....2.17

$$e^- + X \rightarrow X^* + e^-$$

(excitation) .....2.18.1

$$e^- + X_2 \rightarrow X_2^* + e^-$$

(excitation) .....2.18.2

$$e^- + X_2 \rightarrow X_2^+ + 2e^-$$

(ionization) .....2.19

$$e^- + X_2 \rightarrow X_2^+ + 2e^-$$

(glow discharge) .....2.20

in which electrons emitted by two parallel electrode plates under DC or AC bias collide with the gas  $X_2$  to form plasma.

Plasma generation requires electrons with high kinetic energy K:

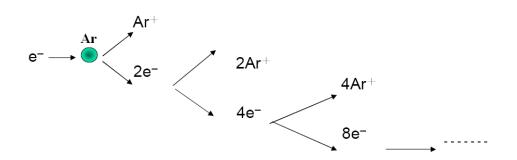

where E is electric field,  $\lambda$  is mean free path, V is electrode voltage and de is electrode distance. Thus, plasma is generated in high voltage bias to increase V and in low pressure to increase  $\lambda$ . Take argon (Ar) for example; the process of plasma generation can be conceptually diagramed as in Fig. 2.18.

Figure 2.18 The process of Ar plasma generation.

Bombarded by accelerating ions with high energy in the plasma, the surface particles of target are then sputtered and deposit on the substrate. (Reference [47] detailed the mechanism of nucleation and growth of thin film.)

The two electrode plates of DC sputter have to be conductors or the charges will accumulate on the non-conductive plates and then the plasma reaction will stop. AC sputter can prevent charges from accumulating on the electrode plates by changing the electrode polarity periodically. Therefore, DC sputter is suitable for sputtering conductive material such as metal while AC sputter is suitable for both conductive and insulating material such as SiO<sub>2</sub>. The lowest frequency for AC sputter must be higher than 100 Hz to maintain plasma reaction. The AC sputter system of which frequency is 13.56 MHz is called an RF (radio frequency) sputter. In RF case, the electrons obtain kinetic energy through oscillation in the field.

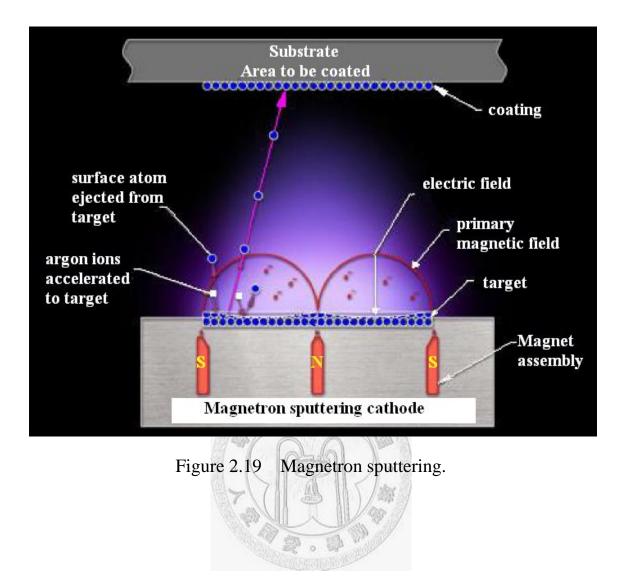

An RF magnetron sputter system applies a magnetic field so that electrons can accelerate electrons and increase collision of electrons with gases in a helix path between electrode plates, as illustrated in Fig. 2.19.

## Chapter 2 Bibliography

- Donald A. Neamen, "Semiconductor Physics and Devices 3<sup>rd</sup>", McGraw Hill, p.486–495.

- [2] A. C. Tickle, "Thin-Film Transistors". New York: John Wily and Sons, 1969.

- [3] C. R. Kagan and P. Andry, "Thin-Film Transistors". New York: Marcel Dekker, Inc., p. 6, 2003.

- [4] For detailed fabrication flow of a-Si TFTs, the following website provides animation and is strongly recommended. http://www.auo.com/auoDEV/content/technology/AUOprocessCT.swf

- [5] Mater thesis, Ganesh Chakravarthy Yerubandi, "Discrete Trap Modeling of Thin-film Transistors", Chapter 2, Oregon State University, 2005.

- [6] Jai Il Ryu, Young Jin Choi, In Keun Woo, Byeong Chun Lim, Jin Jang, "High performance a-Si TFT with ITO/n+ ohmic layer using a Ni-silicide", Journal of Non-Crystalline Solids, 2000.

- [7] Byung Chul Ahn, Jeong Hyun Kim, Dong Gil Kim, Byeong Yeon Moon, Kyung Ha Lee, Soon Sung Yoo, Min Koo Han and Jin Jang, "Fabrication of high performance APCVD a-Si TFT using ion doping", Journal of Non-Crystalline Solids, 1993.

- [8] A Comparison of the Performance and Reliability of Wet-Etched and Dry-Etched a-Si:H TFT's", IEEE transactions on electron devices, 1998.

- [9] Chi-Wen Chen, Ting-Chang Chang, Po-Tsun Liu, Hau-Yan Lu, Kao-Cheng Wang, Chen-Shuo Huang, Chia-Chun Ling, and Tesung-Yuen Tseng, "High-Performance Hydrogenated Amorphous-Si TFT for AMLCD and AMOLED Applications", IEEE electron device letters, 2005.

- [10] Chia-Pin Lin, Bing-Yue Tsui, Ming-Jui Yang, Ruei-Hao Huang, and Chao-Hsin Chien, "High-Performance Poly-Silicon TFTs Using HfO<sub>2</sub> Gate Dielectric", IEEE electron device letters, 2006.vv

- [11] C.C. Liu, Y.S. Chen and J.J. Huang, "High-performance ZnO

thin-film transistors fabricated at low temperature on glass substrates", Electronics letters, 2006.

- [12] Master thesis, Rick E. Presley, "Transparent electronics: thin-film transistors and integrated circuits", Chapter 4, Oregon State University, 2006.

- [13] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano and Hi. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors", Nature, 2004.

- [14] N. L. Dehuff, E. S. Kettenring, D. Hong, H. Q. Chiang, J. F. Wager, R. L. Hoffman, C.-H. Park, and D. A. Keszler, "Transparent thin-film transistors with zinc indium oxide channel layer," Journal of Applied Physics, 2005.

- [15] G. F. Boesen and J. E. Jacobs, "ZnO Field-Effect Transistor", Proceeding Letters, IEEE, 1968.

- [16] P. F. Carcia, R. S. McLean, M. H. Reily, and G. Nunes, "Transparent ZnO thin-film transistor fabricated by rf magnetron sputtering," Applied Physics Letters, 2003.

- [17] J. Nishii, F. M. Hossain, S. Takagi, T. Aita, K. Saikusa, Y. Ohmaki, I. Ohkubo, S. Kishimoto, A. ira Ohtomo, T. Fukumura, F. Matsukura, Y. Ohno, H. Koinuma, A. H. Ohno, and M. Kawasaki, "High mobility thin film transistors with transparent ZnO channels," Japanese Journal of Applied Physics, 2003.

- [18] S. Masuda, K. Kitamura, Y. Okumura, S. Miyatake, H. Tabata, and T. Kawai, "Transparent thin film transistors using ZnO as an active channel layer and their electrical properties," Japanese Journal of Applied Physics, 2003.

- [19] R. L. Hoffman, B. J. Norris, and J. F. Wager, "ZnO-based transparent thin-film transistors," Applied Physics Letters, 2003.

- [20] B. J. Norris, J. Anderson, J. F. Wager, and D. A. Keszler, "Spin-coated zinc oxide transparent transistors," Journal of Physics D: Applied Physics, 2003.

- [21] Y. Kwon, Y. Li, Y. W. Heo, M. Jones, P. H. Holloway, D. P. Norton, Z.

V. Park, and S. Li, "Enhancement-mode thin-film field-effect transistor using phosphorus-doped (Zn,Mg)O channel," Applied Physics Letters, 2004.

- [22] M. W. J. Prins, K.-O. Grosse-Holz, G. Muller, J. F. M. Cillessen, J. B. Giesbers, R. P. Weening, and R. M. Wolfd, "A ferroelectric transparent thin-film transistor," Applied Physics Letters, 1996.

- [23] H. Q. Chiang, J. F. Wager, R. L. Hoffman, J. Jeong, and D. A. Keszler, "High mobility transparent thin-film transistors with amorphous zinc tin oxide channel layer," Applied Physics Letters, 2005.

- [24] A. Sazonov, D. Striakhilev, C.-H. Lee, and A. Nathan, "Low-Temperature Materials and Thin Film Transistors for Flexible Electronics", Proceedings of the IEEE, 2005.

- [25] I-C. Cheng, A. Z. Kattamis, K. Long, J. C. Sturm, and S. Wagner, "Self-Aligned Amorphous-Silicon TFTs on Clear Plastic Substrates", IEEE, 2006.

- [26] K. NOMURA, A.TAKAGI, T. KAMIYA, H. OHTA, M. HIRANO and H. HOSONO, "Amorphous Oxide Semiconductors for High-Performance Flexible Thin-Film Transistors", Japanese Journal of Applied Physics, 2006.

- [27] P. F. Carcia, R. S. Mclean, and M. H. Reilly, "Oxide engineering of ZnO thin-film transistor for flexible electronics", Journal of SID, 2005.

- [28] W.B. Jackson, G.S. Herman, R.L. Hoffman, C. Taussig, S. Braymen, F. Jeffery, and J. Hauschildt, "Zinc tin oxide transistors on flexible substrates", Journal of Non-Crystalline Solids, 2006.

- [29] Jong H. Na,M. Kitamura, D. Lee, and Y. Arakawa, "High performance flexible pentacene thin-film transistors fabricated on titanium silicon oxide gate dielectrics", Applied Physics Letters, 2007.

- [30] J. Vaillancourt, X. Lu, X. Han and D.C. Janzen, "High-speed thin-film transistor on flexible substrate fabricated at room temperature", Electronics Letters, 2006.

- [31] S. J. Pearton, D. P. Norton, K. Ip, Y. W. Heo, and T. Steiner "Recent advances in processing of ZnO" Journal of Vacuum Science and Technology, May/June, 2004.

- [32] D. C. Look, G. C. Farlow, P. Reunchan, S. Limpijumnong, S. B. Zhang, and K. Nordlund, "Evidence for Native-Defect Donors in n-Type ZnO", Physical Review Letters, 2005.

- [33] Adapted from L. Schmidt-Mende, J. L. MacManus-Driscoll, "ZnO nanostructures, defects, and devices", Materials Today, 2007.

- [34] Richard A. Swalin, "Thermodynamics of Solids", 2<sup>nd</sup> edition, JOHN

WILEY & SONS, New York, U.S.A., 1972.