國立臺灣大學電機資訊學院電子工程學研究所

碩士論文

Graduate Institute of Electronics Engineering

College of Electrical Engineering & Computer Science

National Taiwan University

Master Thesis

使用 0.5V 級緣體上矽金氧半動態臨限電壓技術設計

低功率系統應用

0.5V SOI DTMOS Technique for Design

Optimization of Low-Power System Applications

林志祥

Chih-Hsiang Lin

指導教授：郭正邦 博士

Advisor: James B. Kuo, Ph.D.

中華民國 98 年 6 月

June 2009

碩士論文

使用 0.5V 絝緣體上矽金氧半動態臨限電壓技術設計低功率系統應用

林志祥 撰

國立臺灣大學碩士學位論文

口試委員會審定書

使用 0.5V 絝緣體上矽金氧半動態臨限電壓技術設

計低功率系統應用

0.5V SOI DTMOS Technique for Design

Optimization of Low-Power System Applications

本論文係林志祥君（R96943094）在國立臺灣大學電子工程研究所完成之碩士學位論文，於民國 98 年 06 月 20 日承下列考試委員審查通過及口試及格，特此證明

口試委員：

郭正卯

(指導教授)

賴予呈

林志強

蔡成宗

陳正雄

系主任、所長

WSJ

# **0.5V SOI DTMOS Technique for Design Optimization of Low-Power System Applications**

By

Chin-Hsiang Lin

## **THESIS**

Submitted in partial fulfillment of the requirement

for the degree of Master of Science in Electronics

Engineering

at National Taiwan University

Taipei, Taiwan, R.O.C.

June, 2009

Approved by :

Chen-Hsiang Lin Cheng-Tzung Tsai Jerry Lin

Lee J.R.

Advised by :

James R. Kind

Approved by Director :

Shyue-Shan Lin

# 致謝

首先，能夠完成這篇論文，要感謝我的指導教授郭正邦博士，不僅在學業研究上給予指導，更教導學生在做人處事的原則，感謝老師的叮嚀教誨，鼓勵學生要有信心，相信只要肯努力，就一定能成功。

再來，要感謝實驗室的其他同學和學長姐，互相的關心與幫助，使我能夠在碩士的生活更加充實。

最後，一定要特別感謝的就是一直以來支持我的父母、女友鍾嘉玲和家人，在這段時間對我的支持與照顧，讓我可以順利度過每一次的挑戰與難關，無後顧之憂，專心勇往直前，謝謝你們。

# 中文摘要

本篇論文研究主要是探討在奈米製程的 bulk 和 CMOS 技術下，使用動態臨限電壓矽金氧半（Dynamic Threshold MOS ; DTMOS）技術最佳化設計低功率系統的應用。第二章為應用 90 奈米多重臨界電壓互補式矽金氧半（MTCMOS）技術去實現 BP-DTMOS-DT (Bulk PMOS Dynamic Threshold MOS with Dual Threshold) 的技術設計最佳化低功率系統的應用。比較使用 BP-DTMOS-DT 類型的邏輯閘 cells 元件與 BP-DTMOS-DT 版本的 GDSPOM 最佳化一個 0.5V 16-bit 的乘法器電路，與經由正常 HVT/LVT 類型的邏輯閘 cells 元件與 GDSPOM 最佳化後的乘法器電路，在操作頻率為 250MHz 的條件下，前者可以減少 22% 的靜態功率消耗。第三章為使用 SOI 結構，去實現使用 DTMOS 的技術來設計最佳化低功率超大型積體電路系統的應用。使用 SOI DTMOS 類型的邏輯閘 cells 元件經由 SOI DTMOS 版本 GDSPOM 程序，最佳化設計一個 0.5V 16-bit 絝緣體上 (SOI) 乘法器電路，透過此技術最佳化後的乘法器電路，在滿足操作頻率的條件下，與由全部都使用 SOI DTMOS 邏輯閘 cells 元件組成的乘法器電路比較，可以減少 30% 的功率消耗，第四章為結論和未來研究方向。

# ABSTRACT

This thesis reports DTMOS technique for design optimization of low-power system applications using nanometer bulk and SOI CMOS technologies. In Chapter 2, a 0.5V bulk PMOS dynamic-threshold technique enhanced with dual threshold (MTCMOS): BP-DTMOS-DT for design optimization of low-power system application using 90nm multi-threshold CMOS technology is presented. Via the BP-DTMOS type logic cell technique generated by the gate-level dual-threshold static power optimization methodology(GDSPOM) procedure, a 0.5V 16-bit multiplier circuit has been designed and optimized, showing a reduction of in 22% static power at the operating frequency of 250MHz as compared to the conventional HVT/LVT type counterpart optimized by the GDSPOM reported before. In Chapter 3, a 0.5V SOI CMOS dual-threshold circuit technique via DTMOS is explained for design optimization of low-power VLSI system applications. Via the DTMOS technology for implementing the SOI version of the GDSPOM, a 16-bit SOI multiplier circuit has been designed, showing a performance with 30% less power consumption as compared to the one designed purely in DTMOS, at  $V_{DD} = 0.5V$ .

# 目錄

|                                                                                                                                                                                                                               |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 口試委員會審定書 .....                                                                                                                                                                                                                | i    |

| 致謝 .....                                                                                                                                                                                                                      | iii  |

| 中文摘要 .....                                                                                                                                                                                                                    | iv   |

| ABSTRACT .....                                                                                                                                                                                                                | v    |

| 目錄 .....                                                                                                                                                                                                                      | vi   |

| 圖表 .....                                                                                                                                                                                                                      | viii |

| Chapter 1 導論 (Introduction) .....                                                                                                                                                                                             | 1    |

| 1.1 互補式矽金氧半超大型積體電路發展的趨勢 (CMOS VLSI Trends) .....                                                                                                                                                                              | 1    |

| 1.2 絝緣體上矽金氧半 (SOI MOS) .....                                                                                                                                                                                                  | 5    |

| 1.3 功率消耗 (Power Consumption) .....                                                                                                                                                                                            | 7    |

| 1.4 論文架構 (Thesis Organization) .....                                                                                                                                                                                          | 9    |

| Chapter 2 0.5V Bulk PMOS 動態臨限電壓技術使用雙臨界電壓電路最佳化設計低功<br>率 90 奈米系統應用 (0.5V Bulk PMOS Dynamic-Threshold with Dual Threshold<br>(BP-DTMOS-DT) Technique for Design Optimization of Low Power 90nm CMOS<br>System Application) ..... | 10   |

|                                                                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 互補式矽金氧半和動態臨限電壓矽金氧半的源由（MTCMOS and DTMOS Trends） .....                                                                                      | 10 |

| 2.2 Bulk PMOS 動態臨限電壓金氧半元件技術（BP-DTMOS Technology） .                                                                                            | 12 |

| 2.3 Bulk PMOS 動態臨限矽金氧半元件邏輯閘電路（BP-DTMOS-DT Logic Cell） .....                                                                                   | 15 |

| 2.4 BP-DTMOS-DT GDSPOM .....                                                                                                                  | 18 |

| 2.5 效能（Performace） .....                                                                                                                      | 21 |

| 2.6 討論（Discussion） .....                                                                                                                      | 28 |

| <br>Chapter 3 使用 0.5V 絝緣體上矽金氧半元件動態臨限電壓技術最佳化設計低功率系統應用（0.5V SOI DTMOS Technique for Design Optimization of Low-Power System Applications） ..... | 31 |

| 3.1 絝緣體上動態臨限電壓矽金氧半元件技術（SOI DTMOS Technlogy） .                                                                                                 | 31 |

| 3.2 絝緣體上動態臨限電壓矽金氧半元件邏輯閘電路（SOI DTMOS Logic Cell） .....                                                                                         | 37 |

| 3.3 絝緣體上動態臨限電壓矽金氧半元件技術元件資料庫（SOI DTMOS Cell Library） .....                                                                                     | 42 |

| 3.4 絝緣體上動態臨限電壓矽金氧半元件 GDSPOM ( SOI DTMOS GDSPOM ) .....                                                                                        | 44 |

|                                                        |    |

|--------------------------------------------------------|----|

| 3.5 絝緣體上動態臨限電壓矽金氧半系統應用 (SOI DTMOS System) .....        | 46 |

| Chapter 4 結論和未來研究方向 (Conclusion and Future Work) ..... | 53 |

| 參考文獻 .....                                             | 55 |

# 圖表

|                                                                                                                                                       |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 圖 1.1 電晶體製程技術與尺寸縮小的發展趨勢.....                                                                                                                          | 1  |

| 圖 1.2 供應電壓和臨界電壓縮小的趨勢發展.....                                                                                                                           | 3  |

| 圖 1.3 動態功率與靜態功率在不同製程技術下的關係.....                                                                                                                       | 4  |

| 圖 1.4 SOI元件構造.....                                                                                                                                    | 5  |

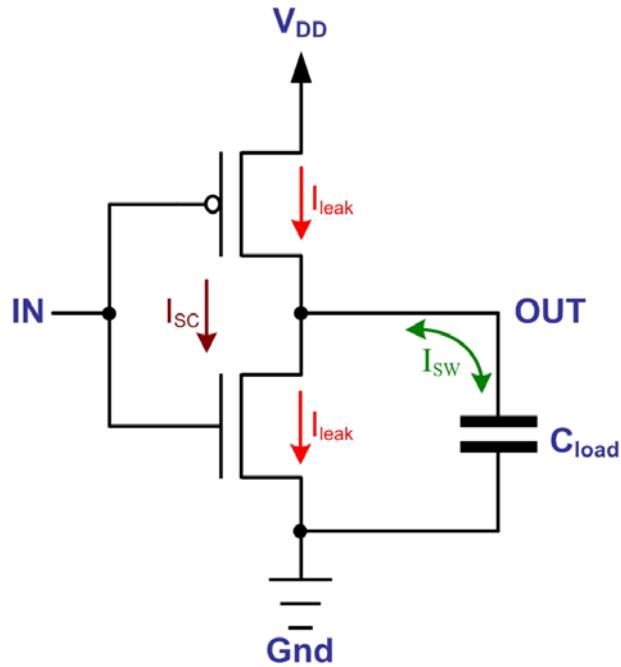

| 圖 1.5 CMOS反向器電路的基本電流流向.....                                                                                                                           | 7  |

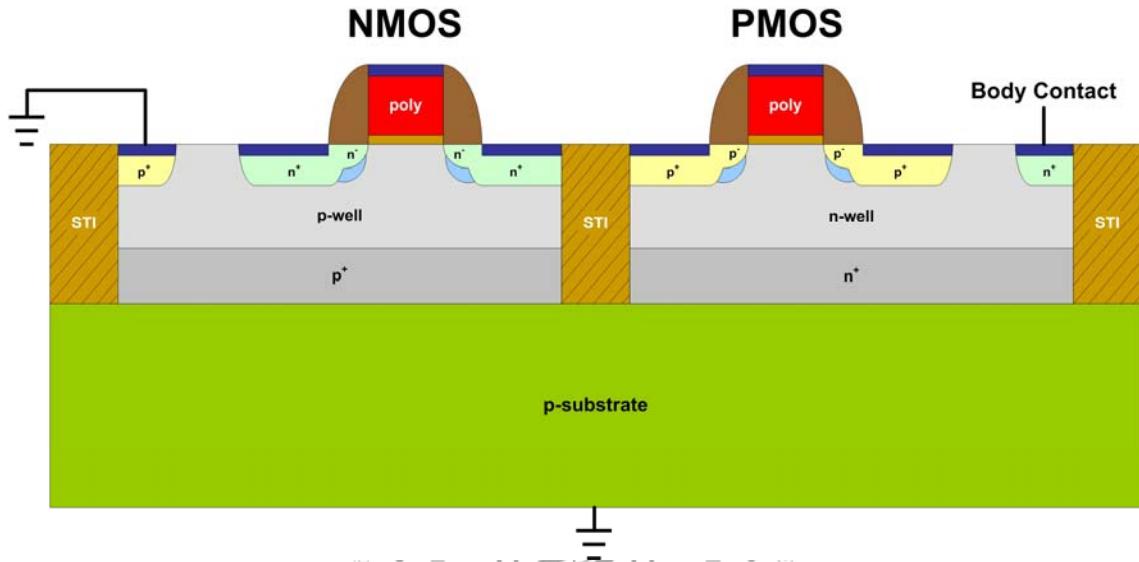

| 圖 2.1 當 $V_{DD}=0.5V$ 電路應用 90 奈米技術標準 bulk 互補型矽金氧半 (CMOS) 元件的橫截面.....                                                                                  | 12 |

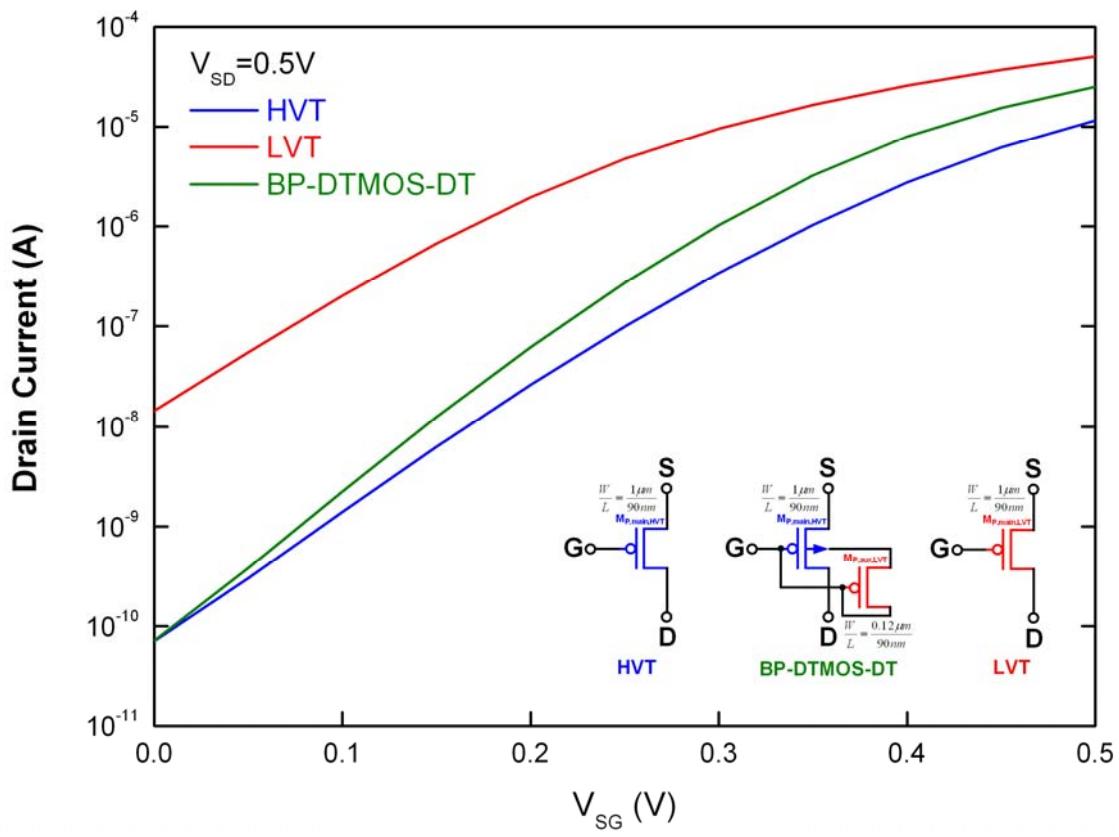

| 圖 2.2 高臨界電壓(HVT)、低臨界電壓(LVT)和Bulk P型矽金氧半元件動態臨限電壓(BP-DTMOS)的P型矽金氧半元件使用雙重臨限電壓(BP-DTMOS-DT)元件在90奈米互補型矽金氧半元件使用MTCMOS技術， $V_{SD}=0.5V$ ，汲極(Drain)電流的特性..... | 14 |

| 圖 2.3 使用BP-DTMOS-DT與90奈米互補型矽金氧半元件技術的0.5V NAND邏輯閘的電路與佈局圖。注意N型矽金氧半元件 (NMOS) 是使用低臨界電壓 (LVT) 電晶體元件.....                                                   | 15 |

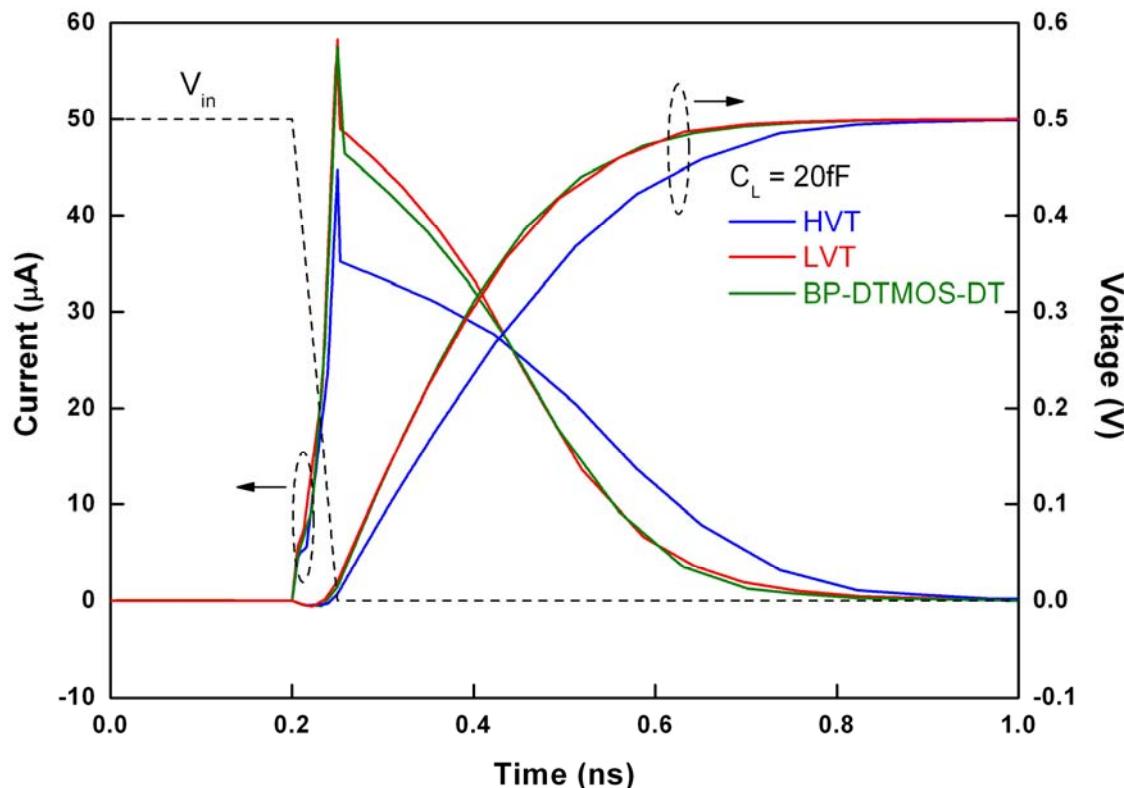

| 圖 2.4 顯示使用HVT、LVT與BP-DTMOS-DT元件技術的0.5V NAND邏輯閘電路的電壓與電流在上拉(pull-up)期間的暫態波形.....                                                                        | 16 |

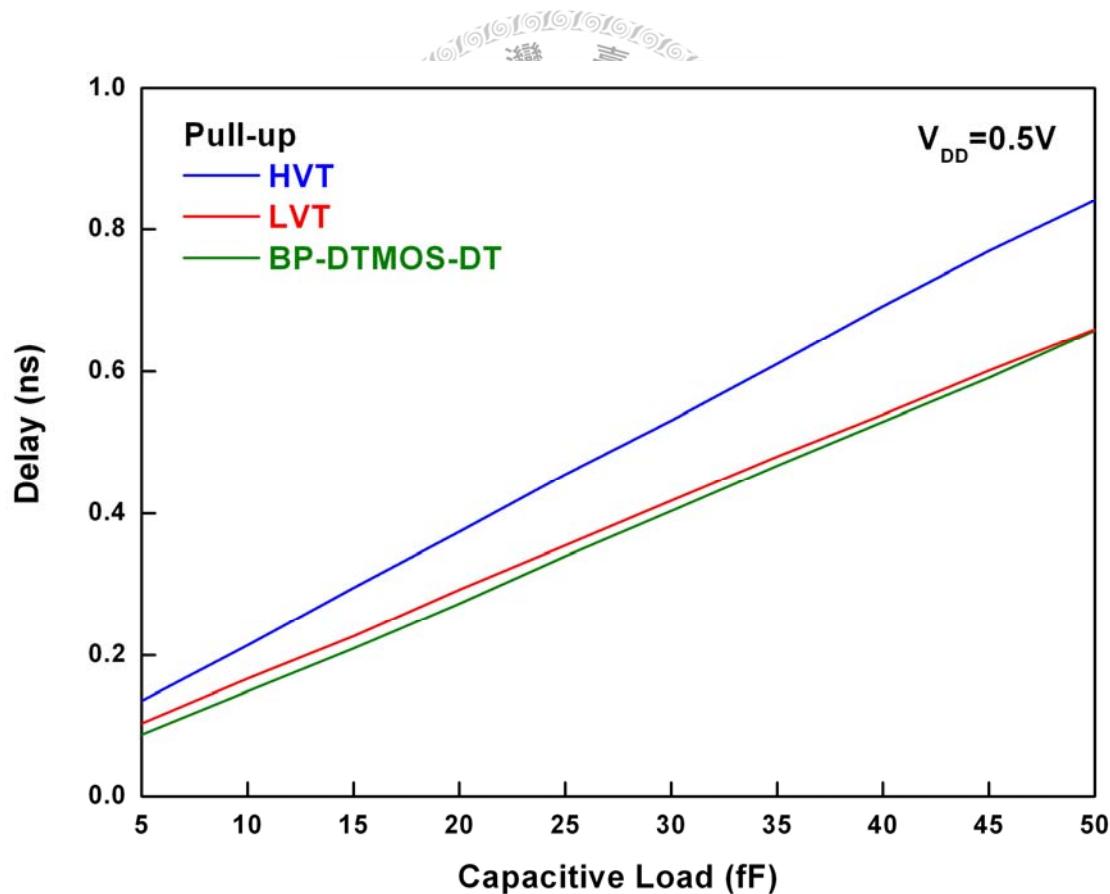

| 圖 2.5 0.5V NAND 邏輯閘電路在使用高臨界電壓 (HVT)、低臨界電壓(LVT) 和 BP-DTMOS-DT元件技術在上拉 (pull-up) 暫態時，傳遞延遲時間與電                                                            |    |

|                                                                                                                                                  |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 容負載的比較.....                                                                                                                                      | 17 |

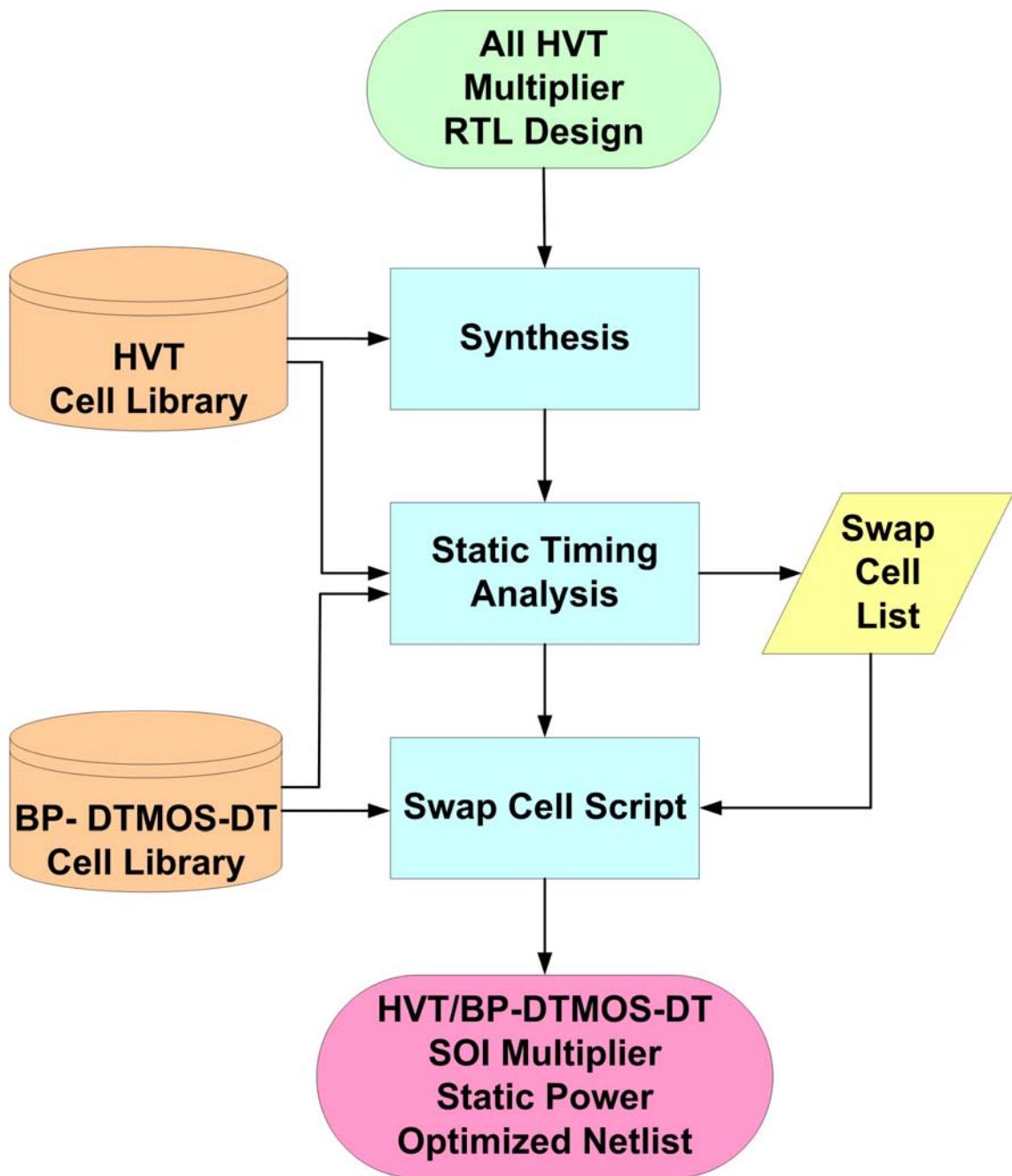

| <b>圖 2.6 用兩種邏輯層級的臨界電壓做總功率最佳化(gate-level dual-threshold static power optimization methodology ; GDSPOM) BP-DTMOS-DT版</b>                          |    |

| 本的程序，使用MTCMOS技術去設計高速度且低功率的系統應用之流程                                                                                                                |    |

| 圖 .....                                                                                                                                          | 20 |

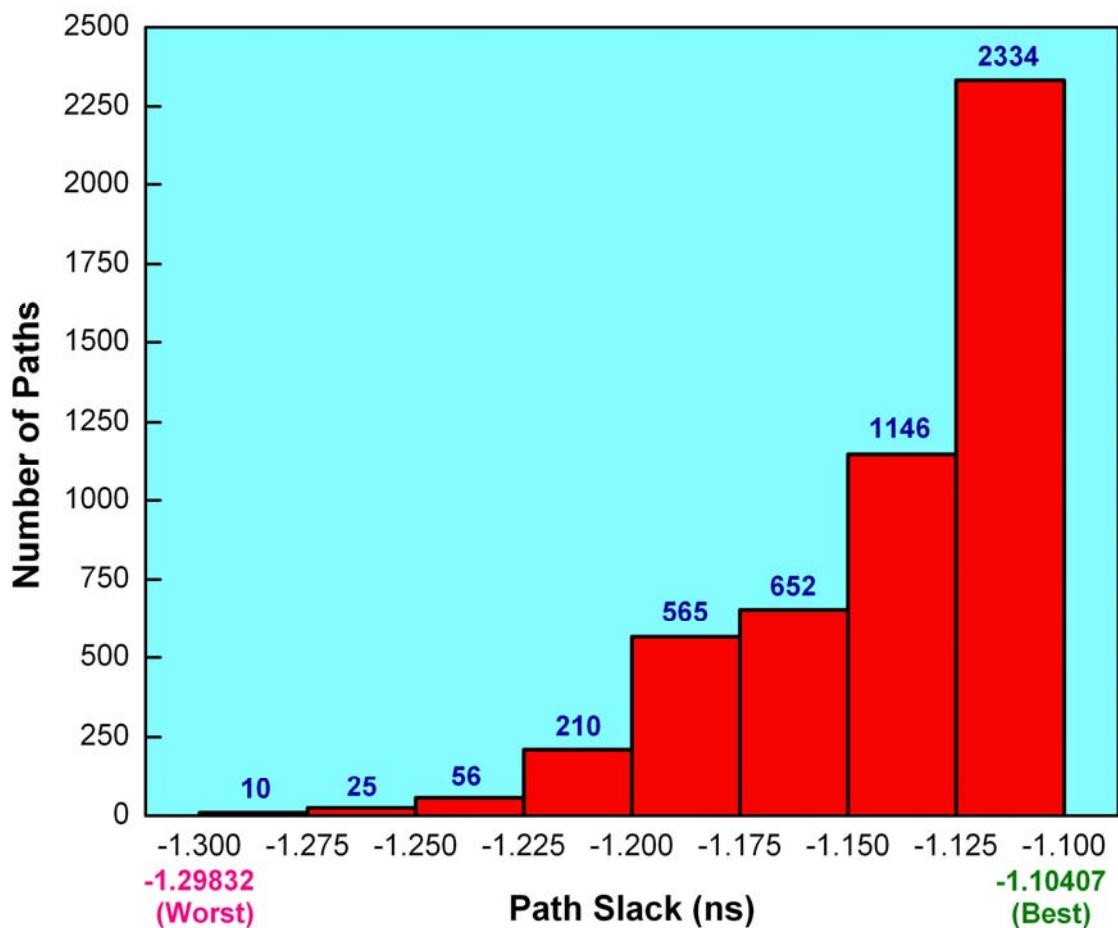

| <b>圖 2.7 在0.5V下全部使用高臨界電壓 (HVT) 邏輯閘cells的0.5V 16-bit乘法器電路中違反時間限制的路徑分布圖.....</b>                                                                   | 22 |

| 圖 2.8 BP-DTMOS-DT版本的GDSPOM程序使用HVT和BP-DTMOS-DT兩種邏輯閘cells去最佳化0.5V 16-bit乘法器的電路概要圖 .....                                                            | 23 |

| <b>圖 2.9 使用 BP-DTMOS-DT 版本的 GDSPOM 程序前，使用全部為高臨界電壓 (HVT) 邏輯閘 cells 組成的 0.5V 16-bit 乘法器電路，由輸入端 IN1<sub>4</sub> 到輸出端 P<sub>26</sub> 的時間路徑.....</b>  | 24 |

| 圖 2.10 使用BP-DTMOS-DT版本的GDSPOM程序後使用高臨界電壓 (HVT) 和 BP-DTMOS-DT兩種邏輯閘cells最佳化後組成的0.5V 16-bit乘法器電路，由輸入端IN1 <sub>4</sub> 到輸出端P <sub>26</sub> 的時間路徑..... | 25 |

| <b>圖 2.11 經由BP-DTMOS-DT版本的GDSPOM程序，使用高臨界電壓 (HVT) 和 BP-DTMOS-DT兩種邏輯閘cells最佳化0.5V 16-bit乘法器電路的靜態功率消耗和使用BP-DTMOS-DT邏輯閘cells的百分比例.....</b>           | 26 |

| 圖 2.12 經由之前論文所通過版本的GDSPOM程序，使用高臨界電壓 (HVT) 和                                                                                                      |    |

|                                                                                                                                                                                                                                   |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 低臨界電壓 (LVT) 兩種邏輯閘cells最佳化0.5V 16-bit乘法器電路的靜態<br>功率消耗和使用低臨界電壓 (LVT) 邏輯閘cells的百分比例.....                                                                                                                                             | 27 |

| 圖 2.13 0.5V 16-bit乘法器電路分別使用全部為高臨界電壓 (HVT) 類型、高臨界<br>電壓 (HVT) 和低臨界電壓 (LVT) 的類型與高臨界電壓 (HVT) 和<br>BP-DTMOS-DT類型的邏輯閘cells所組成，內部節點中主要路徑 (critical<br>path) 上從輸入端IN <sub>14</sub> (乘法器中被乘數的第4個bit) 到輸出端P <sub>26</sub> 的電壓<br>暫態波形..... | 29 |

| 圖 2.14 0.5V 16-bit乘法器電路分別使用全部為高臨界電壓類型、高臨界電壓和低<br>臨界電壓類型與高臨界電壓和BP-DTMOS-DT類型的邏輯cells所組成，內<br>部節點中主要路徑 (critical path) 上從輸入端IN <sub>14</sub> (乘法器中被乘數的第<br>4個bit) 到輸出端P <sub>26</sub> 的電流暫態波形.....                                  | 30 |

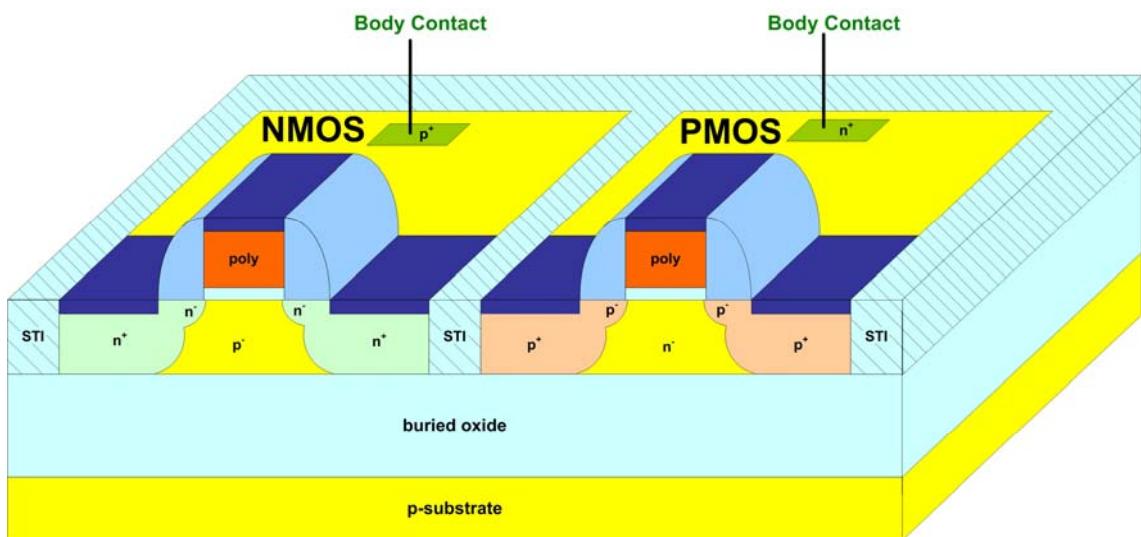

| 圖 3.1 90nm 級緣體上(SOI)CMOS 的橫截面圖.....                                                                                                                                                                                               | 32 |

| 圖 3.2 使用級緣體上(SOI)動態臨限電壓矽金氧半元件(DTMOS)技術的 NMOS<br>和 PMOS 元件.....                                                                                                                                                                    | 33 |

| 圖 3.3 動態臨限電壓矽金氧半元件 (DTMOS) 與非動態臨限電壓矽金氧半元件<br>(Non-DTMOS)的元件在 90 奈米互補型矽金氧半元件使用 MTCMOS 技<br>術, 當 $V_{DS} = 0.5V$ 時, 汲極( Drain )電流的特性.....                                                                                           | 34 |

| 圖 3.4 動態臨限電壓矽金氧半元件 (DTMOS) 與非動態臨限電壓矽金氧半元件<br>(Non-DTMOS)的元件在 90 奈米互補型矽金氧半元件使用 MTCMOS 技                                                                                                                                            |    |

|                                                                                                                                                                                               |           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 術, 當 $V_{GS} = 0.5V$ 時, 汲極(Drain)電流的特性.....                                                                                                                                                   | 35        |

| <b>圖 3.5 使用絕緣體上(SOI)動態臨限電壓矽金氧半元件(DTMOS) 0.5V NAND<br/>邏輯閘使用 90 奈米互補型矽金氧半元件技術的電路佈局.....</b>                                                                                                    | <b>37</b> |

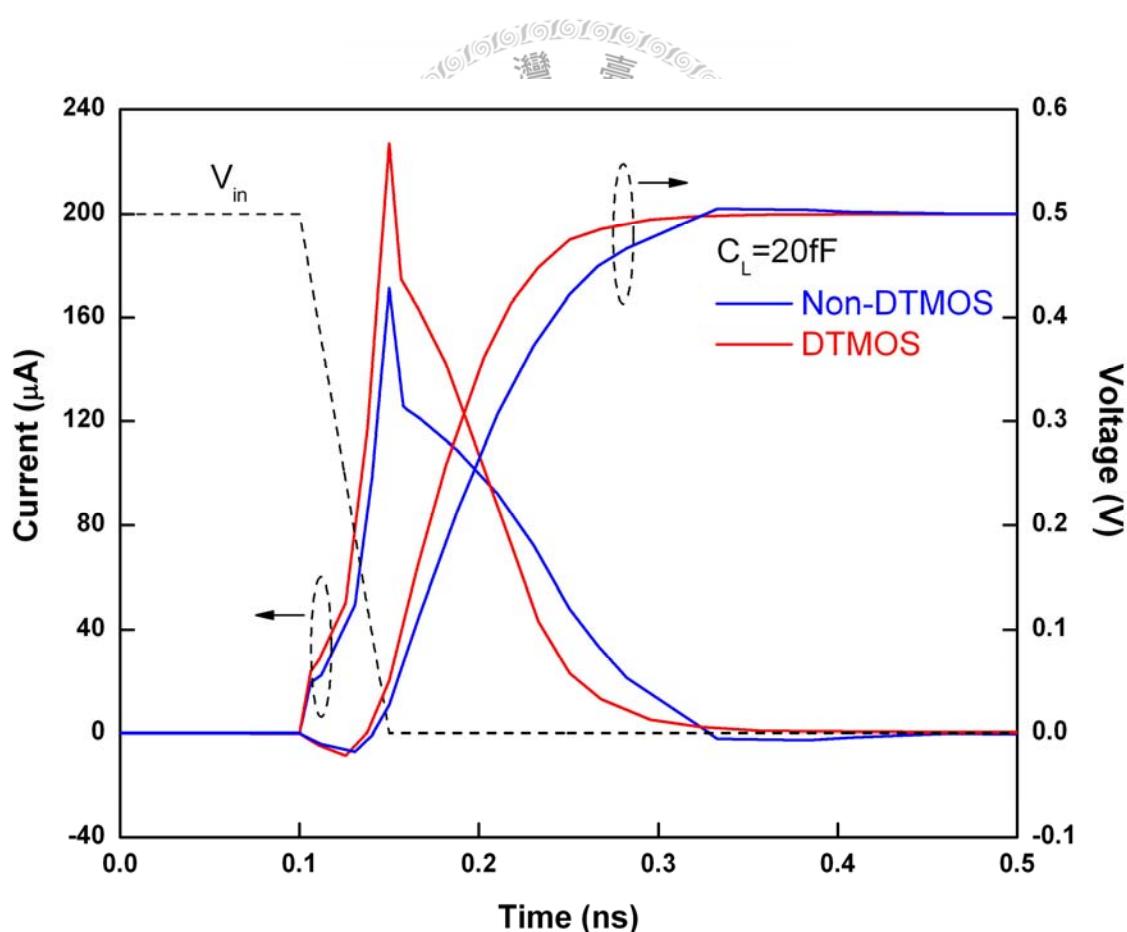

| <b>圖 3.6 顯示使用絕緣體上(SOI)動態臨限電壓矽金氧半元件(DTMOS) 0.5V<br/>NAND 邏輯閘電路電壓和電流, 在上拉(pull-up)的期間的暫態波形.....</b>                                                                                             | <b>38</b> |

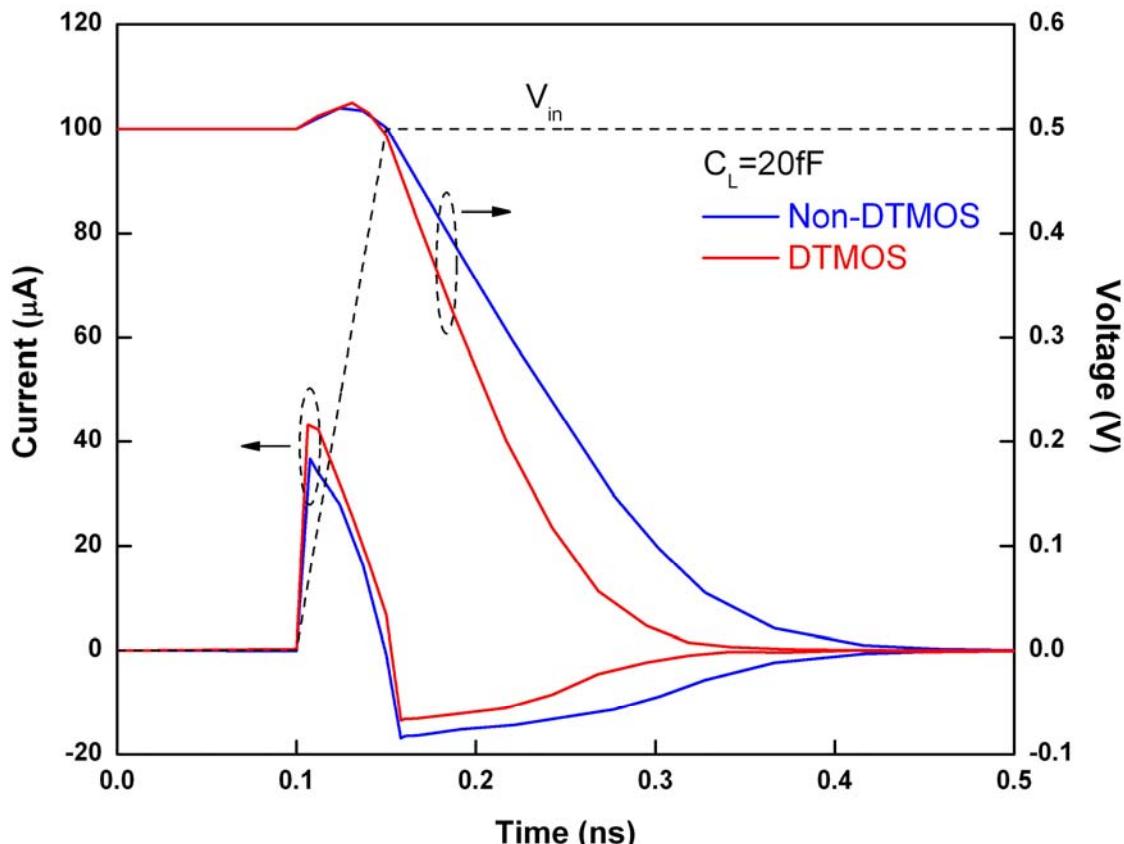

| <b>圖 3.7 顯示使用絕緣體上(SOI)動態臨限電壓矽金氧半元件(DTMOS) 0.5V<br/>NAND 邏輯閘電路電壓和電流, 在下拉(pull-down)的期間的暫態波<br/>形.....</b>                                                                                      | <b>39</b> |

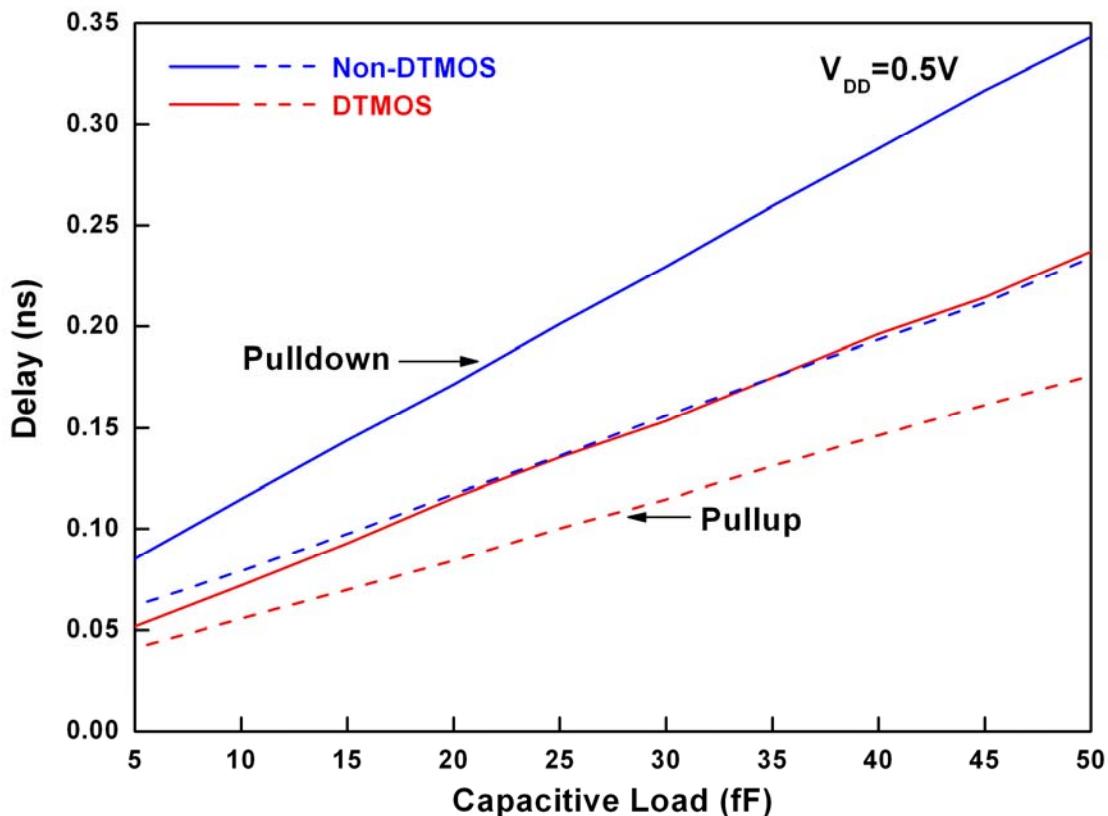

| <b>圖 3.8 0.5V NAND 邏輯閘電路在使用絕緣體上(SOI)動態臨限電壓矽金氧半<br/>元件(DTMOS)技術在上拉與下拉暫態時, 傳遞延遲時間與電容負載的<br/>比較.....</b>                                                                                         | <b>41</b> |

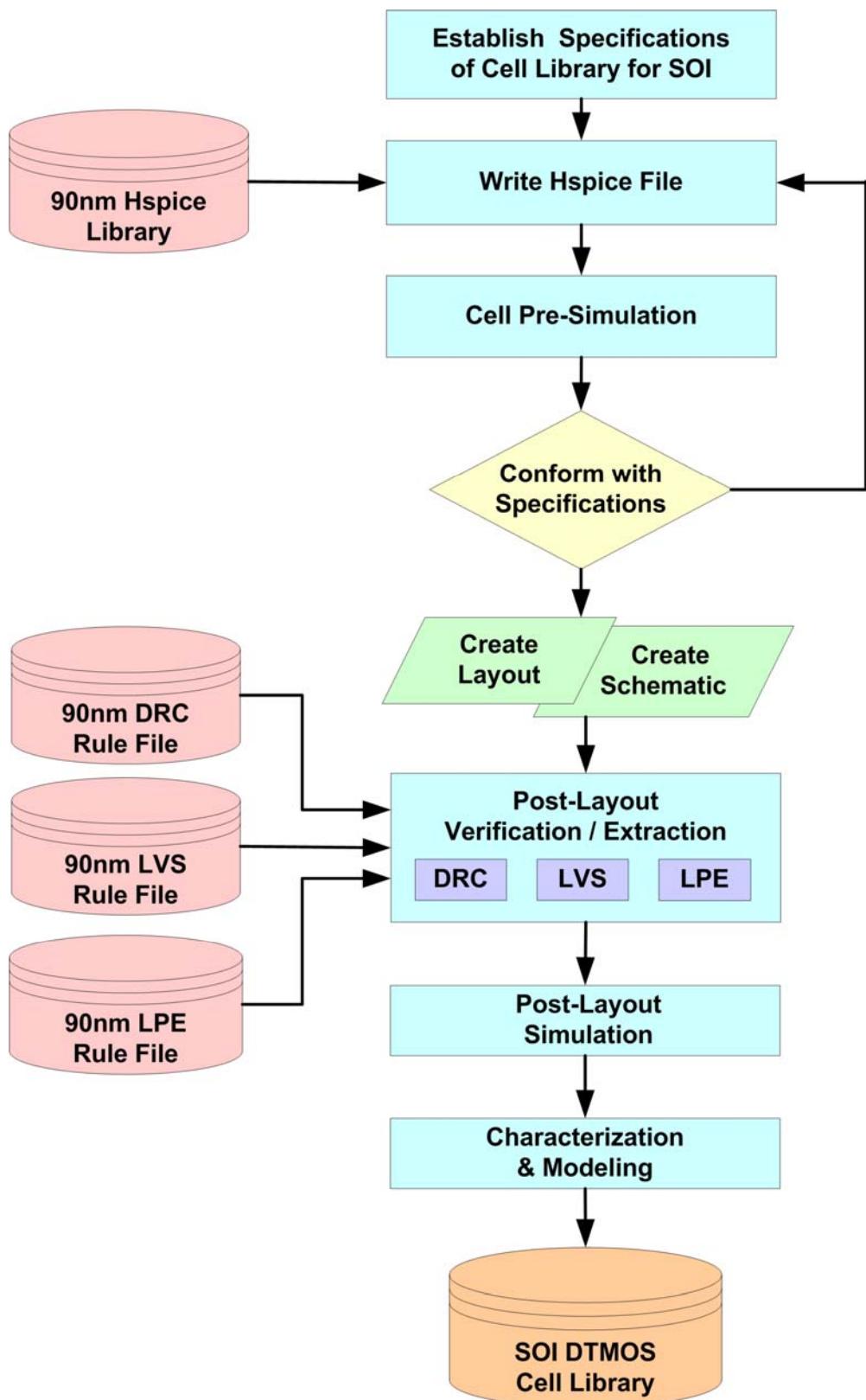

| <b>圖 3.9 絝緣體上(SOI)動態臨限電壓矽金氧半元件(DTMOS)標準元件資料庫建<br/>立流程圖.....</b>                                                                                                                               | <b>43</b> |

| <b>圖 3.10 用兩種邏輯層級的臨界電壓做總功率最佳化(gate-level dual-threshold<br/>static power optimization methodology ; GDSPOM)絝緣體上動態臨限電<br/>壓矽金氧半元件(SOI-DTMOS)版本的程序, 使用MTCMOS技術去設<br/>計高速度且低功率的系統應用之流程圖.....</b> | <b>45</b> |

| <b>圖 3.11 在未經過 SOI DTMOS 版本的 GDSPOM 程序前, 在 0.5V 下全部使用非<br/>動態臨限電壓矽金氧半元件(Non-DTMOS) 邏輯閘 cells 元件的 0.5V</b>                                                                                     |           |

|                                                                                                                                                      |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 16-bit SOI 乘法器電路中違反時間限制的路徑分布.....                                                                                                                    | 47 |

| 圖 3.12 經由 SOI DTMOS 版本的 GDSPOM 程序，使用 Non-DTMOS 和 SOI<br>DTMOS 兩種邏輯閘 cells 元件去最佳化 0.5V 16-bit SOI 乘法器電路的<br>電路概要圖.....                                | 48 |

| 圖 3.13 使用 SOI DTMOS 版本的 GDSPOM 程序前，使用全部為 Non-DTMOS<br>邏輯閘 cells 元件組成的 0.5V 16-bit SOI 乘法器電路，由輸入端 $IN1_{10}$ 到<br>輸出端 $P_{28}$ 的時間路徑.....             | 49 |

| 圖 3.14 使用 SOI DTMOS 版本的 GDSPOM 程序後，使用 Non-DTMOS 和 SOI<br>DTMOS 兩種邏輯閘 cells 最佳化組成的 0.5V 16-bit SOI 乘法器電路，<br>由輸入端 $IN1_{10}$ 到輸出端 $P_{28}$ 的時間路徑..... | 50 |

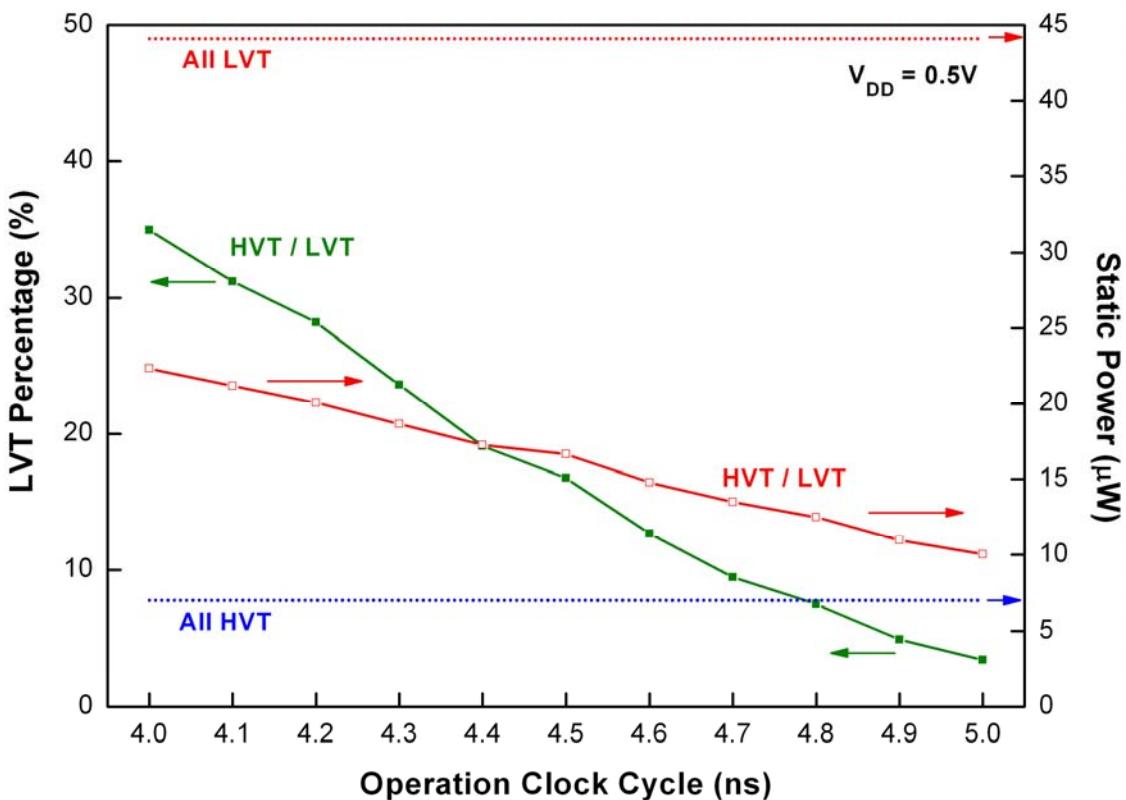

| 圖 3.15 經由 SOI DTMOS 版本的 GDSPOM 程序，使用 Non-DTMOS 和 SOI<br>DTMOS 兩種邏輯閘 cells 元件最佳化 0.5V 16-bit SOI 乘法器電路的靜態<br>功率消耗和使用 SOI DTMOS 邏輯閘 cells 元件的百分比例..... | 51 |

# Chapter 1

## 導論

### Introduction

#### 1.1 互補式矽金氧半超大型積體電路發展的趨勢 (CMOS

VLSI Trends)

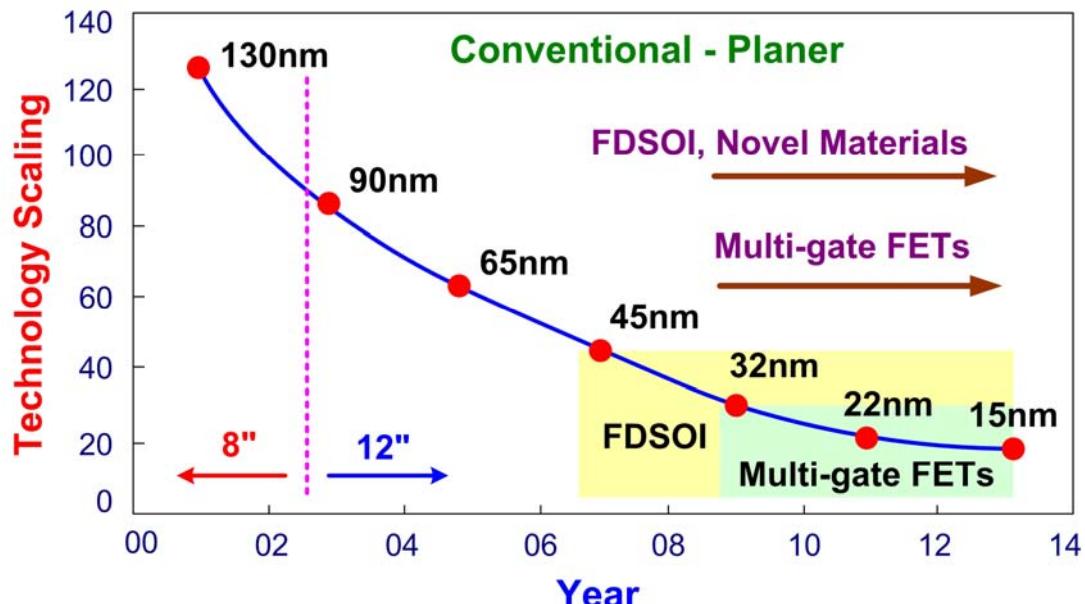

互補式矽金氧半 (CMOS) 的技術在過去數十年來以很平穩迅速的速度發展

[1]，現今已發展至奈米的時代，如圖 1.1 所示[2]。隨著晶片面積大小不斷的下降，

圖 1.1：電晶體製程技術與尺寸縮小的發展趨勢

| 生產年份                | 2001    | 2004    | 2007    | 2010    | 2013    | 2016    |

|---------------------|---------|---------|---------|---------|---------|---------|

| 技術 (nm)             | 130     | 90      | 65      | 45      | 32      | 22      |

| $V_{DD}$ (V)        | 1.1-1.2 | 0.9-1.2 | 0.8-1.1 | 0.7-1.0 | 0.6-0.9 | 0.5-0.8 |

| 晶片上區域時脈 (MHz)       | 1684    | 4171    | 9285    | 15079   | 22980   | 39683   |

| 單一晶片電晶體個數 (百萬顆電晶體)  | 276     | 533     | 1106    | 2212    | 4424    | 8848    |

| 每各晶片的DRAM電容 (Gbits) | 0.54    | 1.07    | 2.15    | 4.29    | 8.59    | 34.36   |

| 允許散熱片的最大功率(W)       | 130     | 158     | 189     | 198     | 198     | 198     |

表 1.1：半導體技術的藍圖

Gordon Moore 預測在未來的十年內，晶片中電晶體的數量每兩年會增加為原來的兩倍，這就是所謂的莫爾定律 (Moore's Law) [3]。當電晶體密度增加時，功率也會增加，設計者不只是要求達到一個單純的時間或功率的目標，而是要努力追求速度、功率消耗和面積的彼此平衡，讓速度盡量加快，功率盡量減少為目標。表 1.1 是超大型積體電路(VLSI)的發展趨勢以及晶片內容概述[4]。且由於可攜式電子消費型產品，如行動電話、PDA 與筆記型電腦等一類的快速的發展，使得資訊的傳遞變得更為迅速有效率，然而在產品上的要求更為輕薄及省電快速已是當前的趨勢[1]。隨著晶片的功能的也越來越多元，晶片內的電路隨著晶片功能的強大而變的設計上越來越複雜，電晶體數也越來越龐大，所以必須使用先進的製程技術來實現。製程技術不斷的進步，元件的尺寸越來越小，與單位面積所能容納的元件也日益增加，單位功能的電路製造成本亦隨而減少。隨著元件尺寸的縮小化，

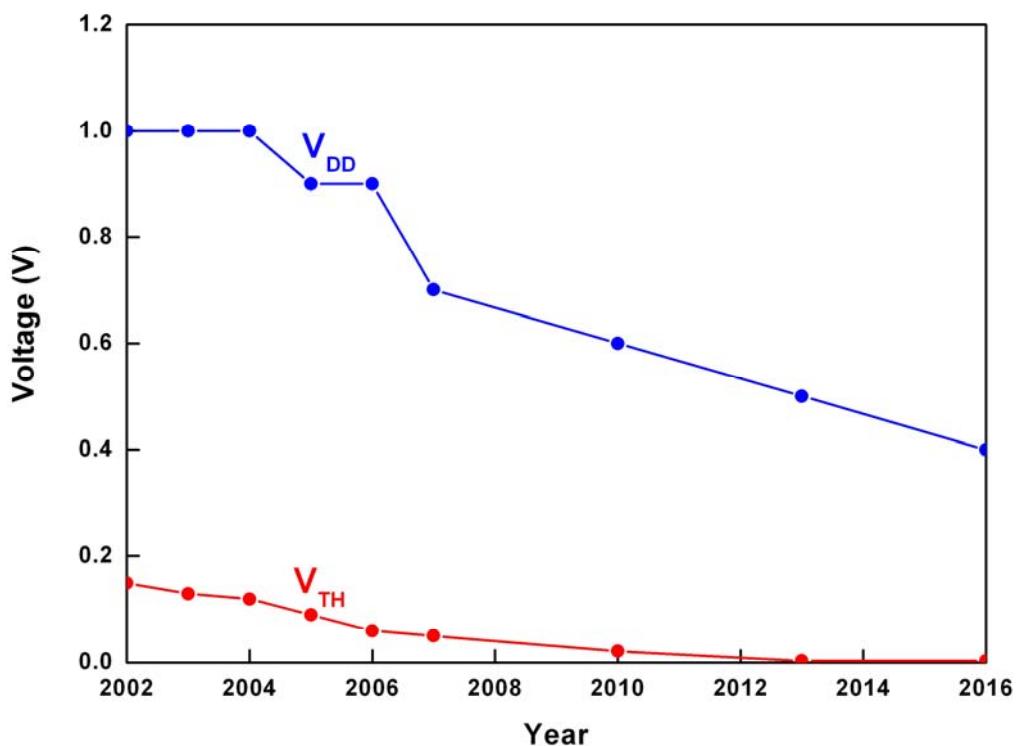

雖然使元件的雜散效應變小速度變快，但在不降低操作電壓之下，整體電路所消耗的功率將變的極為龐大，單位面積增加的功率消耗所產生的讓熱量，將導致電路的溫度上升，使得電路的速度效能下降及穩定性遭受影響。基於上述的原因，所以使得積體電路的設計趨向低電壓（Low Voltage）低功率（Low Power）[5]。在低功率（Low Power）CMOS 的時代，如圖 1.2 所示，供應電壓（supply voltage） $V_{DD}$  持續被縮小之中[6]， $V_{TH}$  也同步的縮小。 $V_{DD}$  的縮小主要是因為元件製程的縮小，但為了防止內部高電場效應所驅使，所以低電壓是必然的一個趨勢。要配合  $V_{DD}$  的話， $V_{TH}$  也必須要同步的縮小，但  $V_{TH}$  的縮小，必須要考慮元件內部現象的問題，包括次臨界（subthreshold）斜率等。 $V_{DD}$  縮小以後，我們通常稱為低電壓

圖 1.2：供應電壓和臨界電壓縮小的趨勢發展

電路，低電壓電路在事實上對於低功率是有幫助的，但是低電壓可能會造成驅動電流的縮小，這各對於高速（high speed）的性能是不利的。所以對我們未來的奈米時代的 SOC 電路系統而言，我們將使用  $V_{DD}$  很小，同時我們又希望速度要很快，這各就變成很大的挑戰。我們剛才提到  $V_{TH}$  的縮小，事實上  $V_{TH}$  不容易縮小，主要的原因，就是因為次臨界（subthreshold）斜率的關係對於漏電影響很大。但在降低操作電壓的同時，矽金氧半的驅動能力將也會隨之下降，雖然在製程上可以調動臨限電壓以加強電流驅動能力，但臨限電壓無法無限制的降低。過低的臨界電壓將引起次臨界區域（subthreshold region）的漏電現象會增加反而造成功率

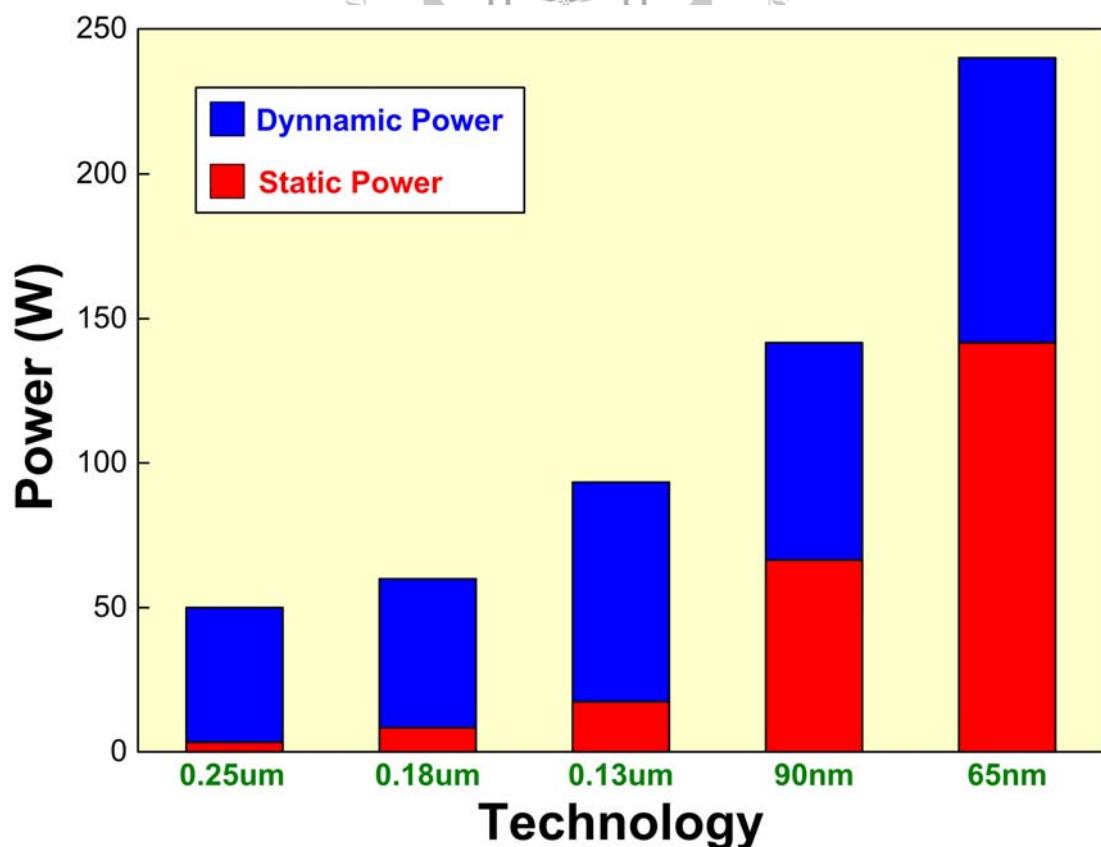

圖 1.3：動態功率與靜態功率在不同製程技術下的關係

消耗大幅上升，因此便有許多設計方法以電路的觀點來達到低功率低電壓得設計目標，因此在降低電壓的同時，元件的電流驅動能力能同時不會受到太大的影響。在奈米時代快速發展的趨勢下，靜態功率消耗會變成總功率消耗裡重要的因素，如圖 1.3[7] 得知，靜態功率確實遠大於動態功率的影響。因此在未來的研究中，靜態功率如何最佳化的降低，將顯得非常重要。目前許多電路設計的技巧適用於低電壓操作，包括多臨界電壓互補式矽金氧半元件技術（multi threshold CMOS technology；MTCMOS）[8][9]，或使用目前最受歡迎的方法之一是利用絕緣體上動態臨界電壓矽金氧半元件（SOI DTMOS）的技術[10][11]，絕緣體上（Silicon-on-Insulator；SOI）[12]矽金氧半製程被視為未來 VLSI 系統電路設計很好的選擇之一。

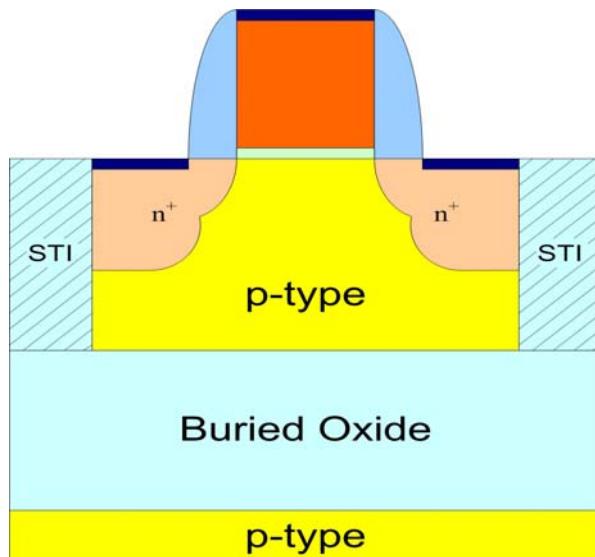

## 1.2 絝緣體上矽金氧半（SOI MOS）

圖 1.4： SOI 元件構造

隨著奈米的時代來臨，絕緣體上矽金氧半則具有許多優勢，如元件密度高、低消耗功率、二次效應較小、抗輻射能力強及可相容於現代的超大型積體電路的技術等。而且近年來其技術已相當成熟，並且有相當多產品已上市，所以使用此技術為下一代積體電路設計的趨勢。如圖 1.4 中為 SOI 元件圖，其中 SOI 元件結構在矽基底（silicon substrate）上有一層淺埋氧化層（buried oxide），而在潛埋氧化層（buried oxide）上的矽薄膜（thin film）上可用以建立元件及電路，SOI MOS 元件由於元件與元件之間是相互以氧化層隔離而非建立於同一基底（substrate）之上，所以 SOI MOS 元件具有下列優點：因為潛埋氧化層（buried oxide）的結構可提供良好的絕緣能力，因此在 SOI MOS 中不會有 latch-up 的問題，抗輻射能力強，寄生電容較為小，轉導（transconductance）優於 bulk 元件，次臨限斜率（subthreshold slope）較為陡，另外，由於矽薄膜（silicon thin-film）結構，使電場效應較 bulk MOS 元件為小也比較規則，二次效應小，短通道效應（short channel effect）較為小，元件密度高，可和現有的超大型積電技術相容等優點。在目前電路應用已有 SOI 元件所製成的微控制器中央處理單元（Microcontroller）[13]、動態及靜態隨機存取記憶體（DRAM、SRAM）[14]及各式電路[15]，這些電路在效能上均較 bulk 有較好的表現，使得 SOI CMOS 成為下一代技術很好的選擇。

## 1.3 功率消耗 (Power Consumption)

圖 1.5: CMOS 反向器電路的基本電流流向

分析一個積體電路的功率分為動態功率 (dynamic power) 與靜態功率 (static power) 兩種[16]。圖 1.5 是一個 CMOS 反向器電路的基本電流流向。動態功率是指改變一個標準元件 (cell) 電路的輸入值時，標準元件的功率消耗。動態功率主要是由標準元件內部功率 (internal power) 和淨交換功率 (net switching power) 這兩種功率組合而成。標準元件內部功率是指當電路轉換時， $V_{DD}$  與 GND 之間會在短暫的時間裡發生短路的功率消耗，就如同標準元件內部電容發生充放電的現象。如圖 1.5 所示，短路電流 (short-circuit current)  $I_{SC}$  是標準元件內部功率的一個因素，可以用下列式子表示之：

$$P_{internal} = I_{sc} \cdot V_{dd}$$

淨交換功率是描述，一個標準元件電路的輸出端負載電容，在充放電時的功

率消耗。這個功率計算是動態功率的主要部份，可由圖 1.5 所示，交換電流

(switching current)  $I_{sw}$  是產生淨交換功率的主要原因。淨交換功率的數值與邏

輯轉換速度是成正比比例關係，而在電路分析裡，時脈頻率 ( $f_{clk}$ ) 和輸出交換參

數 ( $\alpha$ ) 是用來定義邏輯轉換速度，於是淨交換功率可由下列式子來表示：

$$P_{switching} = C_{load} \cdot V_{dd} \cdot \alpha \cdot f_{clk}$$

靜態功率是指隨時都會出現的功率消耗，即使是電路於穩態 (steady state)

下的狀態[17]。如圖 1.5 所示，漏電流 (leakage current)  $I_{lk}$  的存在是因為現實中，

電路狀態並不會理想的轉換，漏電流可由下列式子表示：

$$P_{leakage} = I_{lk} \cdot V_{dd}$$

形成靜態功率最主要的原因是由於次臨界 (subthreshold) 的漏電流，而這個

電流是當電晶體停止運轉實時，電晶體中從源極往閘極的電流。次臨界的漏電流

大小是決定臨界電壓 (threshold voltage ;  $V_t$ ) 的因素，而高臨界電壓元件與低臨

界電壓元件比較，有較小次臨界漏電流的特性[18]。下列式子是表示估算電晶體的

次臨界電流的方程式[19]：

$$I_{subthreshold} \approx K e^{-\frac{V_{gs} - V_t}{nV_T}} \cdot \left( 1 - e^{\frac{-V_{ds}}{V_T}} \right)$$

其中：

|        |                                  |

|--------|----------------------------------|

| $g$    | = gate terminal                  |

| $s$    | = source terminal                |

| $d$    | = drain terminal                 |

| $V_t$  | = threshold voltage              |

| $V_T$  | = thermal voltage                |

| $K, n$ | = technology dependent constants |

總電流功率可由下個式子表示：

$$P_{total} = P_{internal} + P_{switching} + P_{leakage}$$

## 1. 4 論文架構 (Thesis Organization)

在本論文中，將利用 SOI DTMOS 的技術結合 MTCMOS 的技術設計應用在系統電路上，首先會先在第二章中，使用 BP-DTMOS-DT (Bulk PMOS DTMOS with Dual Threshold) 與高臨界電壓 (HVT) 的標準元件資料庫與 BP-DTMOS-DT 版本的 GDSPOM 演算法去最佳化 0.5V 16-bit 乘法器電路，使乘法器能達到低電壓低功率消耗符合操作頻率的高效能設計，並與使用低臨界電壓 (LVT) 與高臨界電壓 (HVT) 元件資料庫經 GDSPOM 最佳化設計乘法器電路的效能做比較。接著在第三章中，使用絕緣體上 (SOI) 的架構，建立 SOI DTMOS 標準元件資料庫，並結合 Non-DTMOS 標準元件資料庫，再經由 SOI DTMOS 版本的 GDSPOM 最佳化設計 0.5V 16-bit SOI 乘法器數位電路，使其電路系統達到高效能低電壓低功率消耗的電路系統設計。最後在第四章則是本篇論文最後的總結，它可以提供未來對此研究有興趣的人提供一些方向。

## Chapter 2

**0.5V Bulk PMOS 動態臨限電壓技術使

用雙臨界電壓電路最佳化設計低功率 90

奈米系統應用**

**0.5V Bulk PMOS Dynamic-Threshold

with Dual Threshold (BP-DTMOS-DT)

Technique for Design Optimization of

Low Power 90nm CMOS System

Application**

### 2.1 互補式矽金氧半和動態臨限電壓矽金氧半的源由 (MTCMOS and DTMOS Trends)

臨界電壓( $V_t$  ; threshold voltage)會影響到矽金氧半(MOS)元件的電流與訊號傳遞延遲時間，一般而言，具有較高臨界電壓(HVT)的電晶體會有較低漏電流特性與較長傳遞延遲時間的特性，反之，具有較低臨界電壓(LVT)的電晶體會

有較高漏電流與較短地延遲時間的特性。在低功率系統電路的應用中，多重臨界電壓互補型矽金氧半元件（multi-threshold CMOS；MTCMOS）電路技術，已經在低功率和高速度性能的最佳化電路設計中為它們的長處而被採用[20][21][22]。使用 90 奈米多重臨界電壓互補型矽金氧半元件（MTCMOS）技術，與先前已被建立的程序：閘級的雙重臨界電壓靜態功率最佳化的演算法（gate-level dual-threshold static power optimization methodology；GDSPOM）[23]。動態臨限電壓互補型矽金氧半元件（DTCMOS）電路技術已經被先前的研究報告得知，可提高使用低功率（Low Power）[10]供應電壓的絕緣體上（SOI）互補型矽金氧半元件（CMOS）數位電路速度的性能。事實上，動態臨界電壓互補型矽金氧半元件（CMOS）電路技術也可以作為標準的 bulk 互補型矽金氧半元件技術的 P 型矽金氧半（PMOS）元件達成低功率（Low Power）和高速度的性能[24][25]。在本實驗中，經由高臨界電壓（HVT）與 bulk P 型矽金氧半動態臨限電壓互補型矽金氧半元件使用雙臨界電壓技術（bulk PMOS DTMOS with dual threshold；BPDTMOS-DT）的標準元件與 BP-DTMOS-DT 版本的 GDSPOM 最佳化過程，產生達成 MTCMOS 技術應用的目標，去測試一個 0.5V 16-bit 乘法器數位電路。去比較操作頻率在 250MHz 時，與使用 HVT/LVT 標準元件的組合，將會減少 22% 的靜態漏電功率。在下列的章節中，BP-DTMOS-DT 的技術將首先描述，並根據 BP-DTMOS-DT 版本的 GDSPOM 最佳化程序去討論其系統電路的性能。

## 2.2 Bulk PMOS 動態臨限電壓矽金氧半元件技術 (BP-DTMOS Technology)

圖 2.1：當  $V_{DD}=0.5V$  電路應用 90nm 技術 bulk 互補型矽金氧半元件的橫截面

圖 2.1 為顯示出一個典型當  $V_{DD}=0.5V$  電路應用 90 奈米 bulk 互補型矽金氧半 (CMOS) 元件的橫截面圖，如圖所示，N 型矽金氧半 (NMOS) 是在 p-well 裡面，p-well 的 contact 為  $p^+$  通常是直接接地，p 型基體 (p-substrate) 也是接地，現在我們所使用的 DTMOS 技術，只能引用在 P 型矽金氧半 (PMOS) 裡面，因為 PMOS 的 well 是單獨的基極聯接 (Body Contact)，可以拿出來控制它的基極 (Body) 電壓。N-well 裡面的 Body Contact，它的電壓只會大於 0V 或小於  $V_{DD}=0.5V$ 。而現在 p 型基體 (p-substrate) 是接地，所以介於 n-well 的 Body Contact 與 p-substrate 之間永遠是 reverse biased，isolation 沒有問題。

現在利用 body contact 可使 n-well 中之 PMOS 元件導入如同 SOI 之 DTMOS 技術，稱之為 bulk PMOS DTMOS (BP-DTMOS) 技術。對於一個 90 奈米互補型矽金氧半元件 (CMOS) 技術以多重臨界電壓 (MTCMOS) 的技術，應用高臨界電壓 (HVT) 和低臨界電壓 (LVT) 標準元件混合組合應用，是可用來做 low-power 及 high speed 之最佳化。高臨界電壓 (HVT) 元件有較低的漏電流特性但打開 (turn on) 電流較小，低臨界電壓 (LVT) 元件則有較大的打開 (turn on) 電流但較高的漏電流特性。然而，當元件關閉的時候，它們的漏電流不能忽略，其中造成低功率的消耗是可被接受的。現基於 MTCMOS 技術可再加上 BP-DTMOS 的技術，如上節所述，以達成 low-power 高速性能的目標，如圖 2.2 所示，採取雙重臨界電壓互補型矽金氧半元件 (MTCMOS) 技術使用小比例尺寸 (W/L) 低臨界電壓 (LVT) 的為輔助電晶體和大比例尺寸 (W/L) 高臨界電壓 (HVT) 的為主要電晶體，這個 BP-DTMOS-DT 元件結合了高臨界電壓 (HVT) 和低臨界電壓 (LVT) 電晶體元件的優點，由於主要的 HVT 電晶體元件的支配，從輔助的 LVT 電晶體元件的漏電流以後，它在次臨界區域 (subthreshold region) 中的低漏電流，使用小比例尺寸的電晶體可以被疏忽。在強烈的反轉區間它的汲極 (Source) 電流被提高，是由於動態地降低輔助 LVT 電晶體元件的臨界電壓的大小。它是使用 MTCMOS 技術一起提高的一個新的 Bulk DTMOS 元件，再結合雙重臨界電壓技術 (MTCMOS) 為：BP-DTMOS-DT。

圖 2.2：高臨界電壓(HVT)、低臨界電壓(LVT)和Bulk P型矽金氧半元件動態臨限電壓(BP-DTMOS)的P型矽金氧半元件使用雙重臨限電壓(BP-DTMOS-DT)元件在90奈米互補型矽金氧半元件使用MTCMOS技術， $V_{SD}=0.5V$ ，汲極(Drain)電流的特性

## 2.3 Bulk PMOS 動態臨限矽金氧半元件邏輯閘電路

(BP-DTMOS-DT Logic Cell)

圖 2.3：使用 BP-DTMOS-DT 與 90奈米互補型矽金氧半元件技術的0.5V NAND 邏輯閘電路與佈局圖。注意N型矽金氧半元件是使用低臨界電壓（LVT）電晶體元件。

圖 2.3 是表示 0.5V NAND 邏輯閘電路使用 90 奈米互補型矽金氧半元件技術，以 MTCMOS 的應用使用 BP-DTMOS-DT 的技術。注意 N 型矽金氧半(NMOS)元件採用低臨界電壓(LVT)電晶體元件。如圖所示，以動態控制 BP-DTMOS-DT

元件的臨界電壓，以小比例尺寸輔助的 P 型金氧半（PMOS）元件來控制大比例尺寸主要的電晶體的基極（Body）電壓。圖 2.4 顯示使用 HVT、LVT 與 BP-DTMOS-DT 技術的 0.5V NAND 邏輯閘電路的電壓與電流在上拉期間（pull-up）的波形，輸出電容負載為  $20\text{fF}$  法拉。如圖所示，電路使用 BP-DTMOS-DT 技術的傳遞延遲時間接近使用 LVT，但它的暫態電流比較小。

圖 2.4：顯示使用 HVT、LVT 與 BP-DTMOS-DT 元件技術的 0.5V NAND 邏輯閘電路的電壓與電流在上拉（pull-up）期間的暫態波形

圖 2.5 顯示 0.5V NAND 邏輯閘電路在使用高臨界電壓 (HVT)、低臨界電壓 (LVT) 和 BP-DTMOS-DT 元件技術在上拉 (pull-up) 暫態時，傳遞延遲時間與電容負載的比較圖形。在此圖中，BP-DTMOS-DT 的傳遞延遲時間接近低臨界電壓 (LVT) 元件。當輸出電容負載為 20f 法拉時，BP-DTMOS-DT 的傳遞延遲時間將會比高臨界電壓 (HVT) 元件減少 27%。因此，使用 BP-DTMOS-DT 技術，可以使得邏輯閘元件電路在低功率低操作電壓下，獲得高速度與低功率消耗的性能。

圖 2.5：0.5V NAND 邏輯閘電路在使用高臨界電壓 (HVT)、低臨界電壓 (LVT) 和 BP-DTMOS-DT 元件技術在上拉 (pull-up) 暫態時，傳遞延遲時間與電容負載的比較

## 2.4 BP-DTMOS-DT GDSPOM

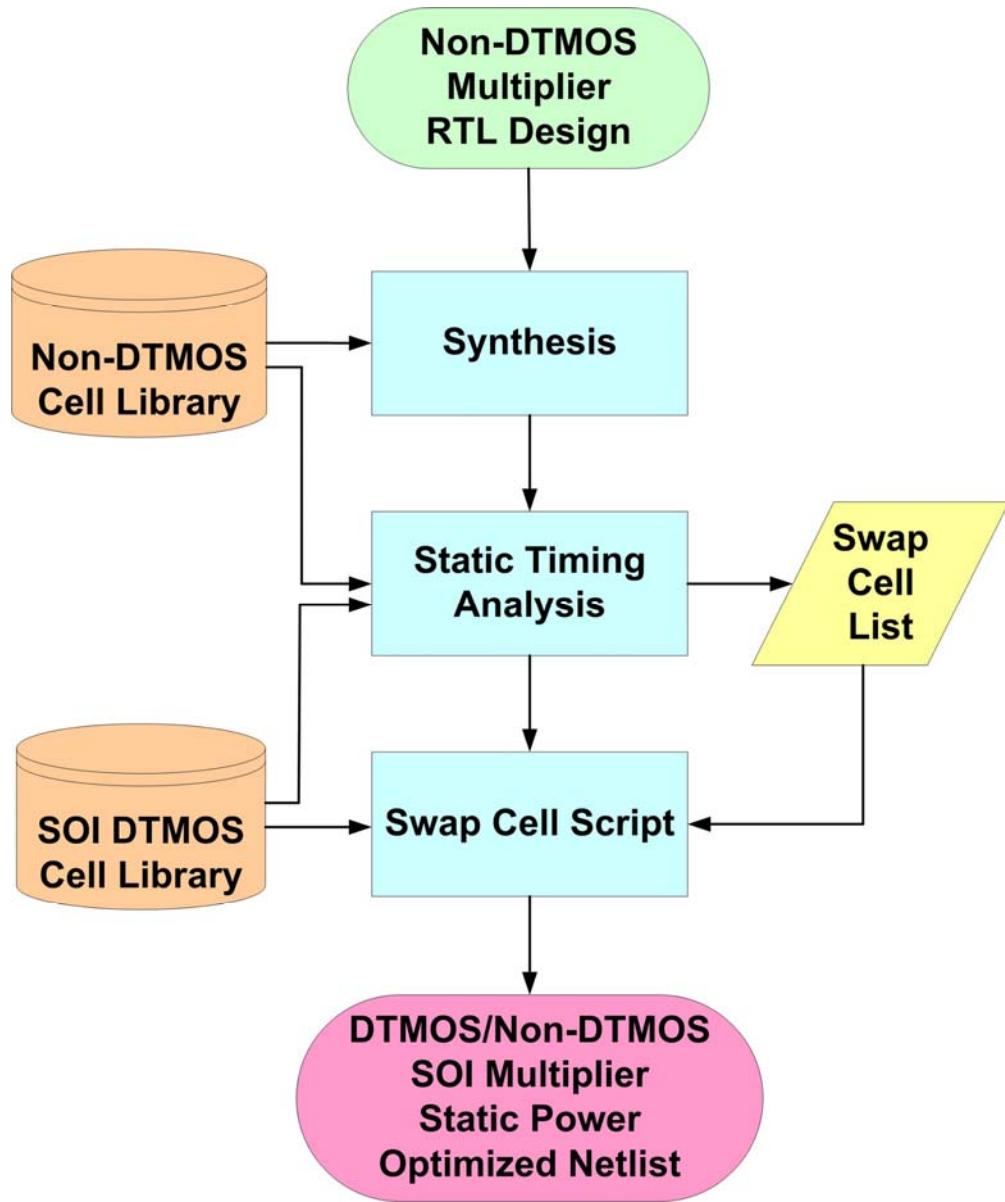

圖 2.6 顯示使用兩種邏輯層級的臨界電壓做總功率最佳化 (gate-level dual-threshold static power optimization methodology ; GDSPOM) BP-DTMOS-DT 版本的程序，使用 MTCMOS 技術去設計高速度且低功率的系統應用之流程圖。為了要用應用 BP-DTMOS-DT 的技術去實現 GDSPOM 的程序，首先使用兩種所建立好的標準元件資料庫。第一種標準元件資料庫的類型為 N 型矽金氧半 (NMOS) 與 P 型矽金氧半 (PMOS) 元件都使用高臨界電壓 (HVT) 電晶體元件，將它命名為高臨界電壓 (HVT) 標準元件資料庫。第二種標準元件資料庫的類型為 P 型矽金氧半 (PMOS) 元件使用 BP-DTMOS-DT 的技術，N 型矽金氧半 (NMOS) 元件使用低臨界電壓 (LVT) 電晶體元件，將它命名為 BP-DTMOS-DT 標準元件資料庫。為了要建立 BP-DTMOS-DT 版本的 GDSPOM 程序，時間模型與功率模型在標準元件資料庫中以已使用 BP-DTMOS-DT 邏輯閘 cells 電路建立。如圖 2.6 所示，BP-DTMOS-DT 版本的 GDSPOM 程序第一個步驟為暫存器轉移層次語言 (RTL) 的硬體描述設計，再使用高臨界電壓 (HVT) 標準元件資料庫的互補型矽金氧半元件經過設計編譯器 (Design Compiler) 去做合成 (synthesis)，得到一個邏輯層次電路檔 (gate level netlist)。之後用 PrimeTime 工具做靜態時序分析 (STA)，使電路必須在符合時間限制下，把不符合時間限制的路徑找出來，即  $slack < 0$  的所有路徑，將其路徑中重複性最高的前幾個邏輯閘 cell 取出其資訊，

預備替換為 BP-DTMOS-DT 標準元件資料庫，之後產生一個必須交換邏輯閘 cell 的資料檔（Swap cell list），再將此資料檔經由直譯程式（TCLSH）來執行交換邏輯閘程式（Swap Cell Script），最後這一個 0.5V 16-bit 乘法器數位電路的電路檔是包含高臨界電壓（HVT）標準元件資料庫的元件與 BP-DTMOS-DT 標準元件資料庫的元件，亦是電路速度最佳化後的結果。此即為 BP-DTMOS-DT 版本的 GDSPOM 程序流程說明，如圖 2.6 所示。

圖 2.6：用兩種邏輯層級的臨界電壓做總功率最佳化(gate-level dual-threshold

static power optimization methodology ; GDSPO) BP-DTMOS-DT版本的程

序，使用 MTCMOS 技術去設計高速度且低功率的系統應用之流程圖

## 2.5 效能 (Performance)

為了評估用於 BP-DTMOS-DT 版本的 GDSPOM 程序的 BP-DTMOS-DT 電路技術，是否可有效率的在低功率系統上應用，使用 BP-DTMOS-DT 技術去設計三個以華勒樹[26]架構所建立 0.5V 16-bit 乘法器數位電路。設計從同樣暫存器轉移層次語言 (RTL) 的來源，第一個乘法器電路使用由全部高臨界電壓(HVT)類型的邏輯閘 cells 組成，第二各乘法器電路使用全部 bulk P 型矽金氧半元件動態臨界電壓矽金氧半元件使用雙臨界電壓技術(BP-DTMOS-DT)類型的邏輯閘 cells 組成，最後一個乘法器電路為經由 BP-DTMOS-DT 版本的 GDSPOM 程序使用高臨界電壓 (HVT) 和 BP-DTMOS-DT 兩種類型的邏輯閘 cells 經最佳化後組合的乘法器電路。這個設計目標的操作頻率為 250MHz。相關所使用的標準元件資料庫被開發建立用於這項研究，下章節將會有相關發建立的流程說明。在這 0.5V 16-bit 乘法器電路中，它有 7000 個邏輯閘 cells，一共大約 30,000 個矽金氧半元件。圖 2.7 為表示在 0.5V 下全部使用高臨界電壓 (HVT) 邏輯閘 cells 的 0.5V 16-bit 乘法器電路中違反時間限制的路徑分布圖。如圖所示，在 250MHz 的操作頻率限制下，大約有五千條路經不符合速度測試的要求。由圖可知其中有 10 條路徑為最長的延遲時間，這些就是易堵塞的路徑在決定 16-bit 乘法器電路的操作速度的主要因素。

圖 2.7：在0.5V下全部使用高臨界電壓 (HVT) 邏輯閘cells的0.5V 16-bit乘法器電

路中違反時間限制的路徑分布圖

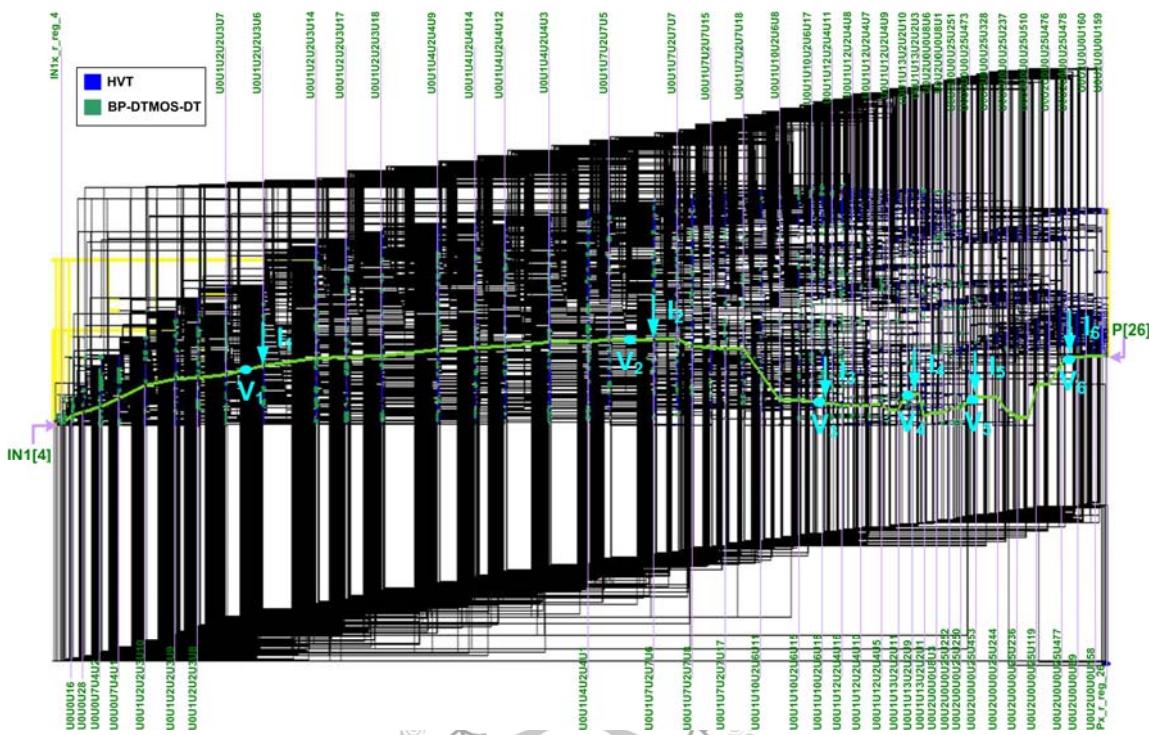

圖 2.8：BP-DTMOS-DT 版本的 GDSPOM 程序使用 HVT 和 BP-DTMOS-DT 兩種邏輯閘 cells 去最佳化 0.5V 16-bit 乘法器的電路概要圖

在這項研究中，BP-DTMOS-DT GDSPOM 程序替換了 38% cells，從高臨界

電壓（HVT）類型置換成 bulk P 型矽金氧半（PMOS）元件動態臨限電壓矽金氧

半元件使用雙臨界電壓技術(BP-DTMOS-DT)類型，以達到 250MHz 操作頻率速度

限制的要求。圖 2.8 為 BP-DTMOS-DT 版本的 GDSPOM 程序使用 HVT 和

BP-DTMOS-DT 兩種邏輯閘 cells 去最佳化後產生的 0.5V 16-bit 乘法器電路的概

要圖，其中高臨界電壓（HVT）類型的邏輯閘 cells 為藍色，BP-DTMOS-DT 類型

的邏輯閘 cells 為綠色，黃色的線為最初違反時間限制由輸入端 IN1<sub>4</sub> 到輸出端 P<sub>26</sub>

的主要路徑（critical path）。

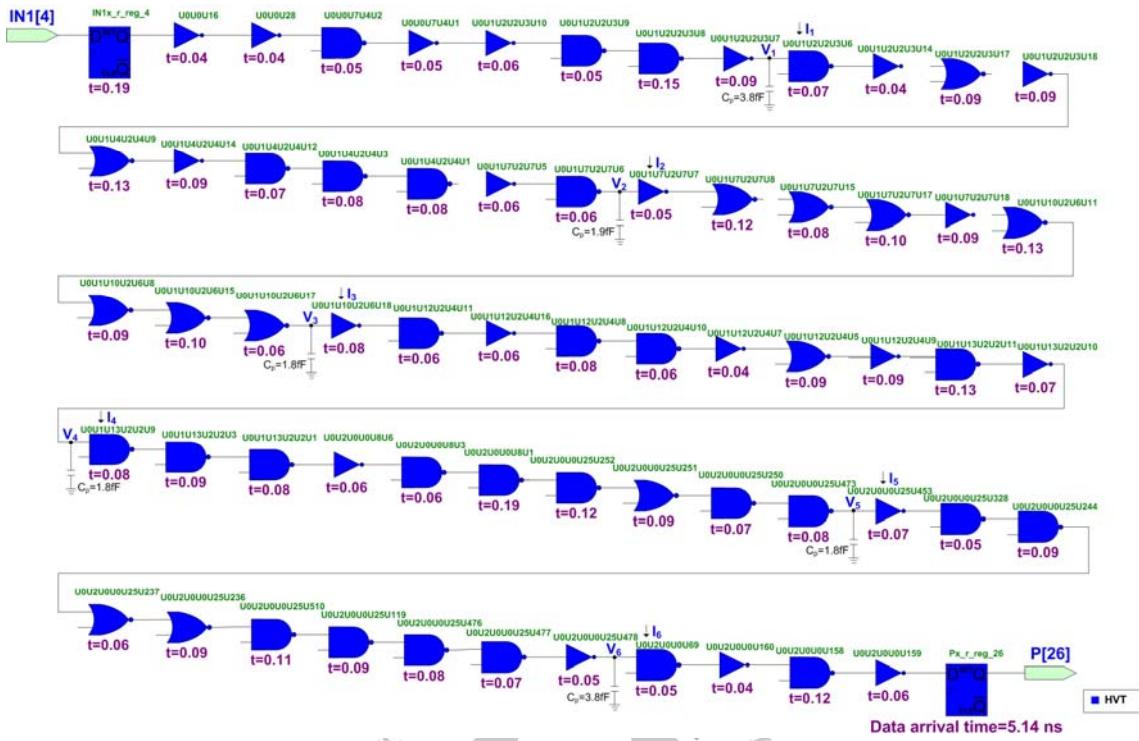

圖 2.9：使用 BP-DTMOS-DT 版本的 GDSPOM 程序前，使用全部為高臨界電壓 (HVT) 邏輯閘 cells 組成的 0.5V 16-bit 乘法器電路，由輸入端 IN1<sub>4</sub> 到輸出端 P<sub>26</sub> 的時間路徑

圖 2.9 使用 BP-DTMOS-DT 版本的 GDSPOM 程序前，使用全部為高臨界電壓 (HVT) 邏輯閘 cells 組成的 0.5V 16-bit 乘法器電路由輸入端 IN1<sub>4</sub> (乘法器中被乘數的第 4 個位元) 到輸出端 P<sub>26</sub> (乘法器中第 26 個位元的乘數) 的時間路徑。

圖 2.10 為使用 BP-DTMOS-DT 版本的 GDSPOM 程序後，使用高臨界電壓(HVT) 和 BP-DTMOS-DT 兩種邏輯閘 cells 最佳化後組成的 0.5V 16-bit 乘法器電路，由輸入端 IN1<sub>4</sub> 到輸出端 P<sub>26</sub> 的時間路徑。這個路徑是選擇由原本使用全部為高臨界電壓 (HVT) 邏輯閘 cells 組成的 0.5V 16-bit 乘法器電路的主要路徑，來顯示

圖 2.10：使用 BP-DTMOS-DT 版本的 GDSPOM 程序後使用高臨界電壓 (HVT) 和 BP-DTMOS-DT 兩種邏輯 cells 最佳化後組成的 0.5V 16-bit 乘法器電路，由輸入端 IN1<sub>4</sub> 到輸出端 P<sub>26</sub> 的時間路徑

怎麼交換不同類型邏輯閘 cells 去成功解決違反時間限制的路徑。如圖 2.9 所示，在使用 BP-DTMOS-DT 版本的 GDSPOM 程序前，在操作頻率為 250MHz 限制下，此路徑的到達時間 (arrival time) 為 5.74ns。如圖 2.10 在使用 BP-DTMOS-DT 版本的 GDSPOM 程序後，許多的 cells 置換為 bulk P 型矽金氧半元件動態臨限電壓矽金氧半元件使用雙臨界電壓技術 (BP-DTMOS-DT) 類型的 cells，使到達時間變為 3.74ns，使此路徑可以達到操作頻率為 250MHz 的限制條件。

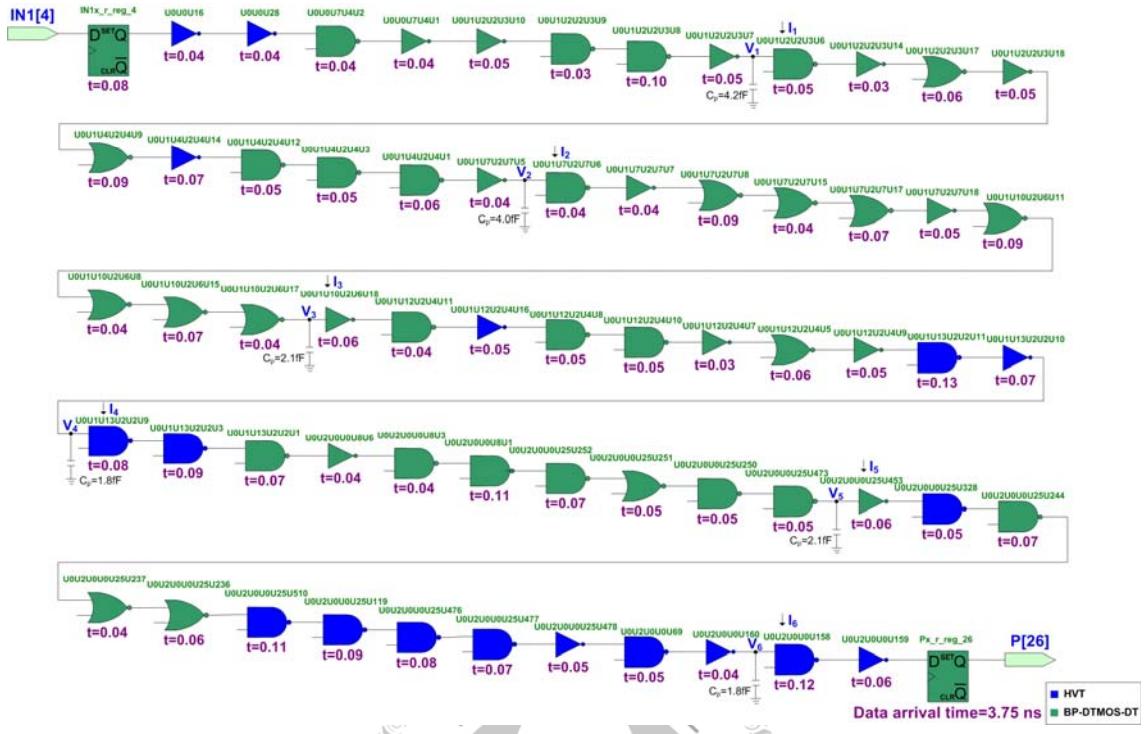

圖 2.11：經由 BP-DTMOS-DT 版本的 GDSPOM 程序，使用高臨界電壓（HVT）和 BP-DTMOS-DT 兩種邏輯閘 cells 最佳化 0.5V 16-bit 乘法器電路的靜態功率消耗和使用 BP-DTMOS-DT 邏輯閘 cells 的百分比例

圖 2.11 所示為經由 BP-DTMOS-DT 版本的 GDSPOM 程序，使用高臨界電壓（HVT）和 BP-DTMOS-DT 兩種邏輯閘 cells 最佳化 0.5V 16-bit 乘法器電路的靜態功率消耗和使用 BP-DTMOS-DT 邏輯閘 cells 的百分比例。圖 2.12 為經由之前論文所通過的 GDSPOM 程序，使用高臨界電壓（HVT）和低臨界電壓（LVT）兩種邏輯閘 cells 最佳化 0.5V 16-bit 乘法器電路的靜態功率消耗和使用低臨界電壓（LVT）邏輯閘 cells 的百分比例。BP-DTMOS-DT 版本的 GDSPOM 程序的優點

圖 2.12：經由之前論文所通過版本的GDSPOM 程序，使用高臨界電壓（HVT）和低臨界電壓（LVT）兩種邏輯閘cells 最佳化0.5V 16-bit乘法器電路的靜態功率消耗和使用低臨界電壓（LVT）邏輯閘cells 的百分比例

為，可以透過比較 0.5V 16-bit 乘法器電路經過最佳化後的設計，使用高臨界電壓（HVT）和 BP-DTMOS-DT 邏輯閘 cells 元件，與使用之前標準 GDSPOM 程序，使用高臨界電壓（HVT）和低臨界電壓（LVT）邏輯閘 cells 組合的實驗結果。如圖 2.11 所示，以 HVT 和 BP-DTMOS-DT 混合組合的方法，靜態洩漏功率消耗能大幅的減少，當操作頻率為 250MHz 的限制條件下，從  $22\mu$  瓦特減少到  $17\mu$  瓦特，當操作頻率為 200MHz 的限制條件下，從  $10\mu$  瓦特減少到  $7.5\mu$  瓦特。相反

的，使用全部都為低臨界電壓（LVT）類型的 cells 元件，靜態洩漏功率為消耗為  $44\mu$  瓦特。因此，透過 BP-DTMOS-DT 版本 GDSPOM 程序，使用 HVT 和 BP-DTMOS-DT 邏輯閘 cells，可以獲得操作頻率為 250MHz 的限制條件下減少 61% 的靜態洩漏功率的性能，在操作頻率為 200MHz 的限制條件下減少 81% 靜態洩漏功率的性能。

## 2.6 討論 (Discussion)

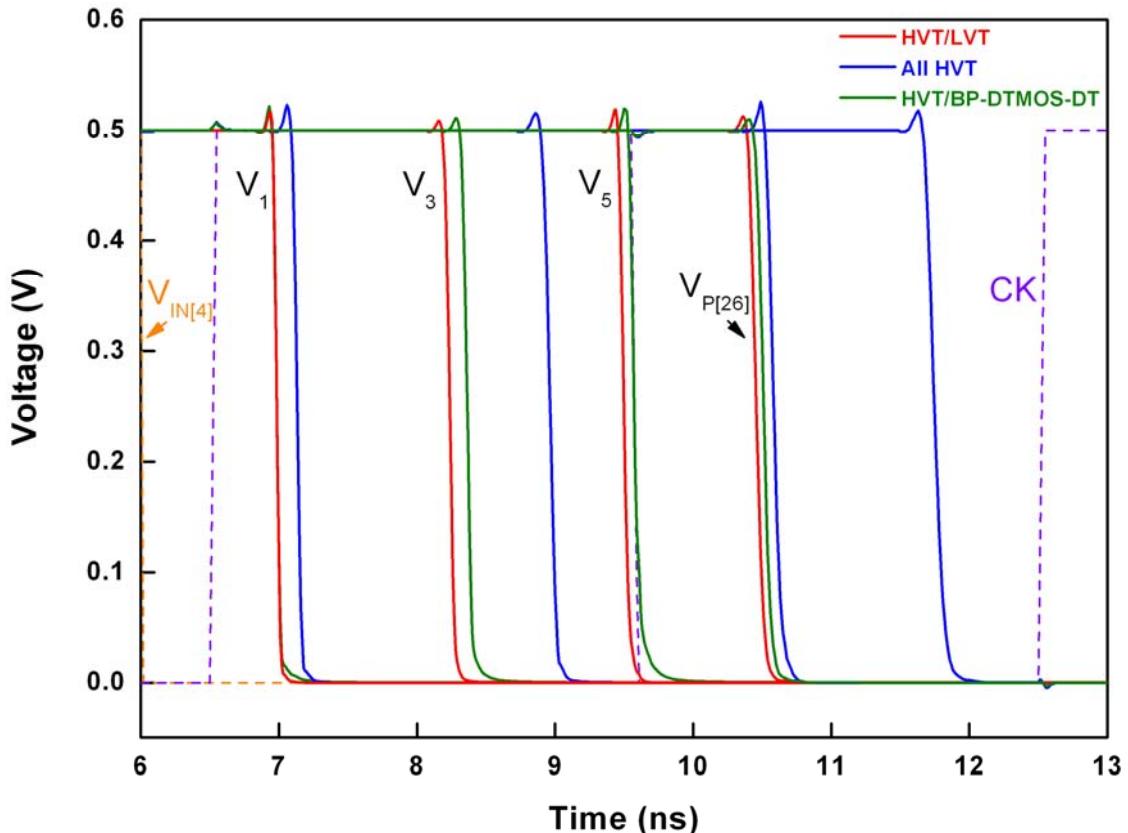

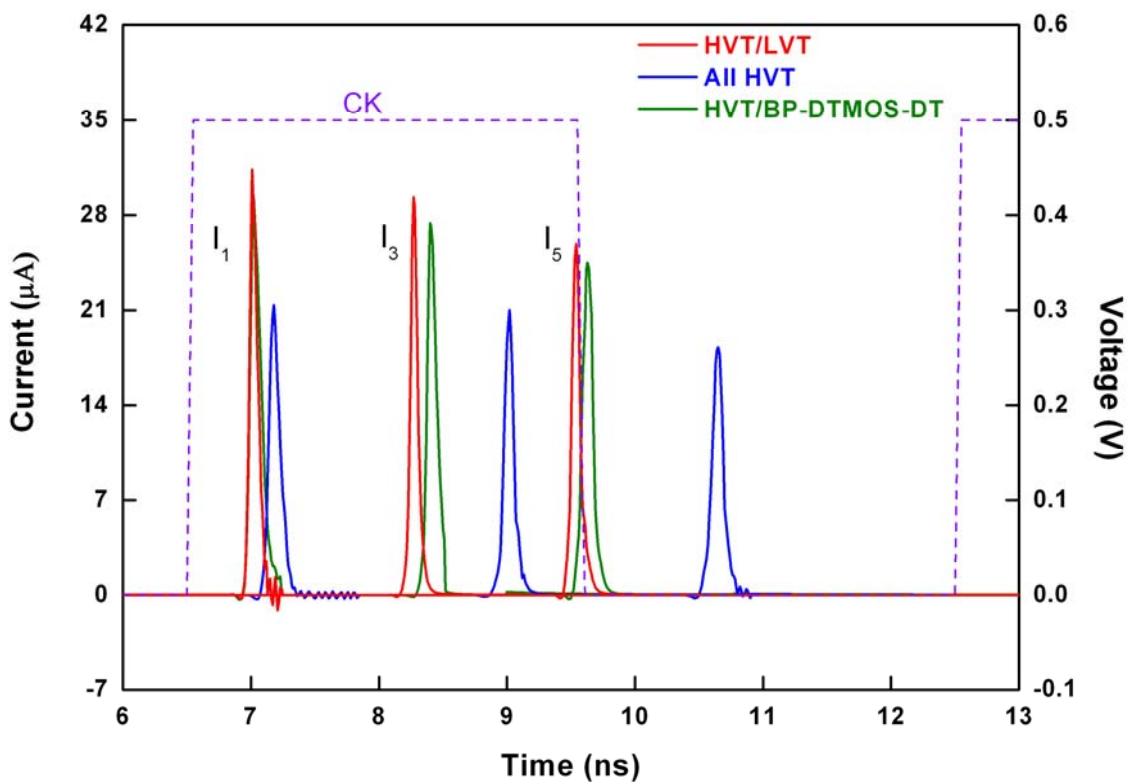

在本研究所提出的 BP-DTMOS-DT 技術的邏輯閘 cells 應用，去減少靜態洩漏功率的消耗不是系統電路設計僅有的方法，它也可能是有利於使用在削減動態功率消耗。圖 2.13、2.14 分別為 0.5V 16-bit 乘法器電路分別使用全部為高臨界電壓（HVT）類型、高臨界電壓（HVT）和低臨界電壓（LVT）類型的組合與高臨界電壓（HVT）和 BP-DTMOS-DT 類型的組合的邏輯閘 cells 所組成，為內部節點中主要路徑（critical path）上從輸入端 IN<sub>14</sub>（乘法器中被乘數的第 4 個 bit）到輸出端 P<sub>26</sub> 的電壓與電流暫態波形。如圖所示，電壓波形在暫態瞬間的期間與電流波形，都與動態消耗功率有關聯，也取決予被採取的邏輯閘 cell 電路的種類為何。0.5V 16-bits 乘法器電路使用全部為 HVT 類型的 cells 的時候，在內部節點的暫態電流顯示出來與其他兩者比較為最小的峰值（peak）。而使用 HVT 和 LVT 組合的類型的 peak 為最大，HVT/BP-DTMOS-DT 組合的類型的 peak 則在前述兩者之

間。所以使用 HVT/BP-DTMOS-DT 組合的類型方法不僅為提高交換速度有利的方法。它在減少靜態和動態功率消耗上也是有用的。

圖 2.13：0.5V 16-bits 乘法器電路分別使用全部為高臨界電壓 (HVT) 類型、高臨界電壓 (HVT) 和低臨界電壓 (LVT) 的類型與高臨界電壓 (HVT) 和 BP-DTMOS-DT 類型的邏輯閘 cells 所組成，內部節點中主要路徑 (critical path) 上從輸入端 IN14 (乘法器中被乘數的第4個bit) 到輸出端 P<sub>26</sub> 的電壓暫態波形

圖 2.14：0.5V 16-bits 乘法器電路分別使用全部為高臨界電壓（HVT）類型、高臨界電壓（HVT）和低臨界電壓（LVT）類型與高臨界（HVT）電壓和BP-DTMOS-DT類型的邏輯閘cells所組成，內部節點中主要路徑（critical path）上從輸入端IN1<sub>4</sub>（乘法器中被乘數的第4個bit）到輸出端P<sub>26</sub>的電流暫態波形

# Chapter 3

## 使用 0.5V 絝緣體上矽金氧半元件動態臨限電壓技術最佳化設計低功率系統應用

### 0.5V SOI DTMOS Technique for Design Optimization of Low-Power System Applications

#### 3.1 絝緣體上動態臨限電壓矽金氧半元件技術 (SOI DTMOS Technology)

絝緣體上 (SOI) 矽金氧半元件因為具有淺埋氧化層 (buried oxide) 的結構可提供良好的絕緣能力，因此不會有 latch-up 的問題，抗輻射能力強，寄生電容較小，轉導 (transconductance) 優於 bulk 元件，次臨界斜率 (subthreshold) 較為抖。由於矽薄膜 (silicon thin-film) 結構，使電場效應較 bulk CMOS 元件為小，也較規則，二次效應小，短通道效應 (short channel effect) 較為小，元件密度高，可和現有的超大型積體電路技術相容等優點。絝緣體上 (SOI) 製程技術為

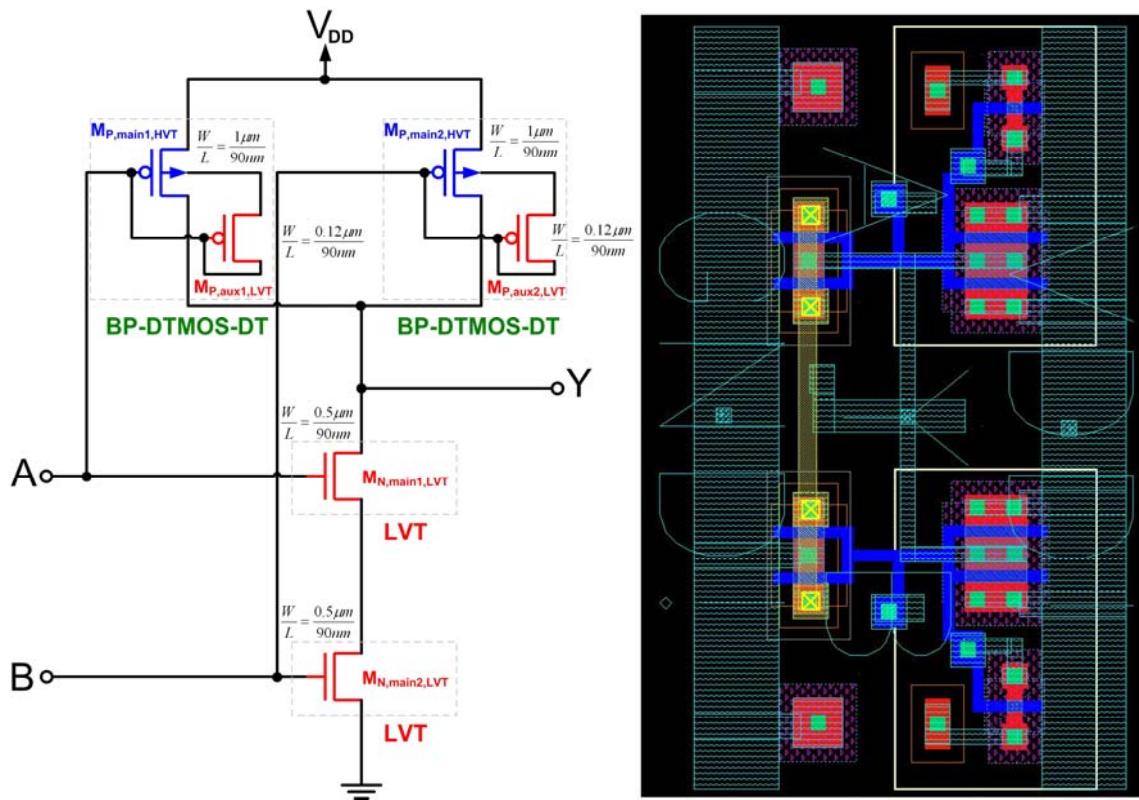

目前及未來積體電路設計的主流之一，此製程適於低電壓、低功率、高密度的電路設計，由於元件的結構及技術的成熟，使得 DTMOS 電路技術在此製程上得以實現。圖 3.1 為使用 90 奈米絕緣體上（SOI）的 CMOS 橫截面圖，如圖所示，主要是把 thin film 的 body contact 可以拉出來，body contact 可以跟閘極（Gate）連接在一起，或經由輔助（Auxiliary）電晶體去做連接控制，如圖 3.2 所示。

圖 3.1：90nm 絝緣體上（SOI）CMOS 的橫截面圖

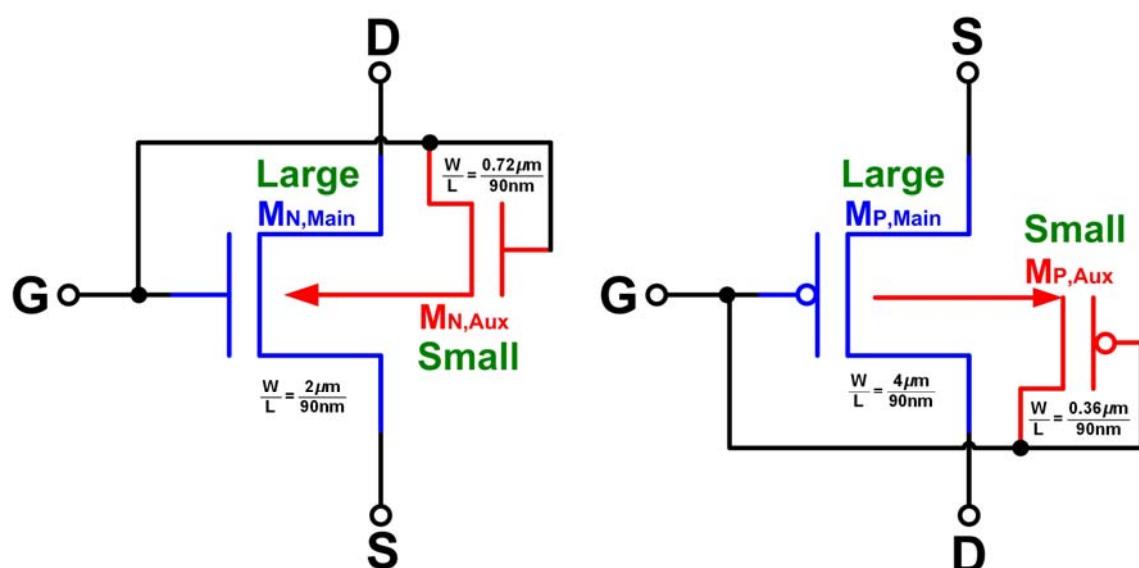

圖 3.2 使用絝緣體上（SOI）動態臨限電壓矽金氧半元件（DTMOS）技術的 NMOS 和 PMOS 元件。如圖所示，對一個 NMOS 元件來說，它的基極（Body）可經輔助電晶體接至閘極（Gate），即可完成基極（Body）控制。然而可以機動性動態運載（carry）控制臨界電壓，對這主要電晶體而言，為了防止輔助電晶體

連接帶來的副作用，因此把輔助電晶體 W/L 的尺寸縮小，降子所造成的漏電流很微小就可以不用列入計算。而 PMOS 元件具有 NMOS 元件對稱的效應。對圖中 NMOS 而言，值得注意的是輔助電晶體的汲極（Drain）和閘極（Gate）是接在一起的，但輔助電晶體的汲極（Drain）和閘極（Gate）跟主要電晶體的閘極（Gate）是分開的。事實上，這各小（Small）尺寸的輔助電晶體只是利用它來控制主要電晶體的基極（Body）的 back gate 偏壓，跟主要電晶體的汲極（Drain）跟源極（Source）是分開的。藉由輔助電晶體使用結果，特別適合低電壓，然而我們所有的研究探討都是在探討在 0.5V 供應電壓 ( $V_{DD}$ ) 的條件下。

圖 3.2: 使用絕緣體上(SOI)動態臨限電壓矽金氧半元件(DTMOS)技術的 NMOS 和 PMOS 元件

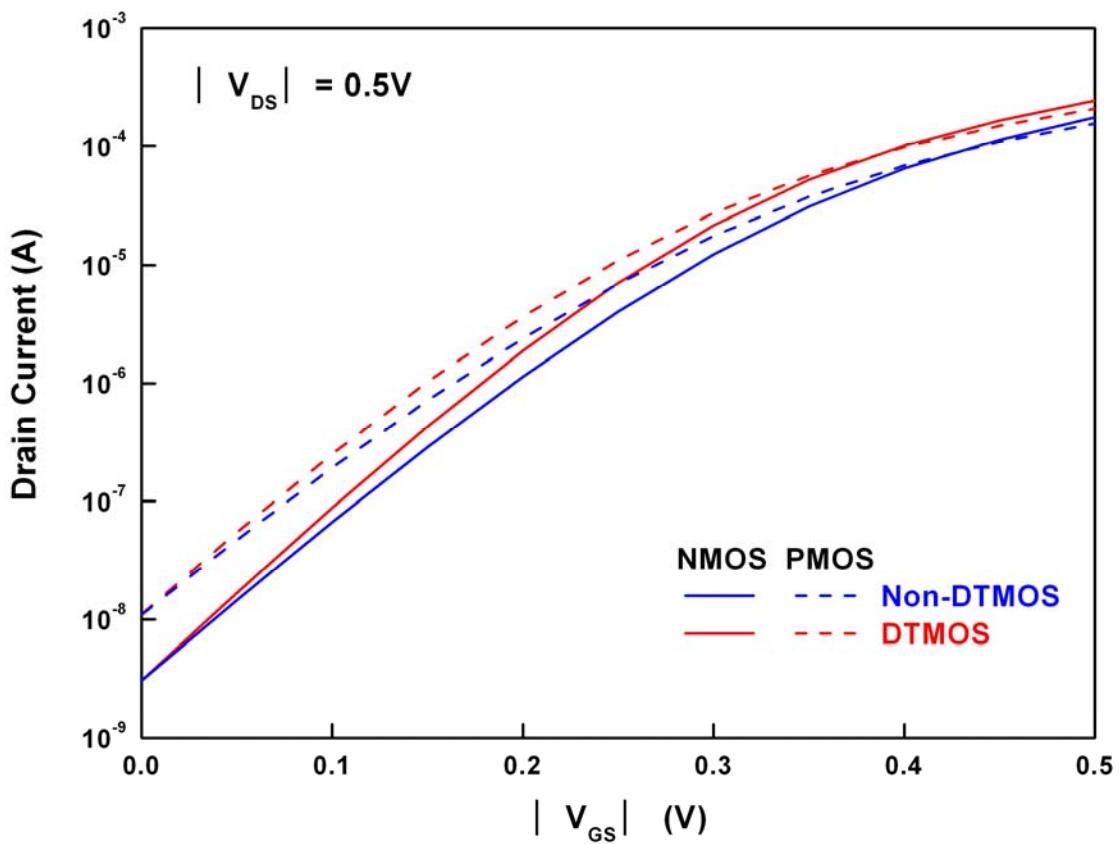

圖 3.3：動態臨限電壓矽金氧半元件 (DTMOS) 與非動態臨限電壓矽金氧半元件 (Non-DTMOS) 的元件在 90 奈米互補型矽金氧半元件使用 MTCMOS 技術，當  $|V_{DS}| = 0.5V$  時，汲極 (Drain) 電流的特性

圖 3.3 為動態臨限電壓矽金氧半元件 (DTMOS) 與非動態臨限電壓矽金氧半元件 (Non-DTMOS) 的元件在 90 奈米互補型矽金氧半元件使用 MTCMOS 技術，當  $|V_{DS}| = 0.5V$  時，汲極 (Drain) 電流的特性，其中 NMOS 元件是實線，PMOS 元件是虛線。由圖可知，DTMOS 的次臨界 (subthreshold) 斜率比較抖，但在強反轉區間 (strong inversion) 的時候，有高強電流，降子 DTMOS 的切換 (switching) 速度會較快，但靜態功率消耗會較小。以上的敘述特性都適用於 NMOS 與 PMOS

元件。事實上，最好的絕緣體上（SOI）就是因為都使用氧化物（oxide）來做隔離，所以 NMOS 元件所使用的動態臨限電壓矽金氧半元件（DTMOS）的技術，照樣適用於 PMOS 元件裡面。

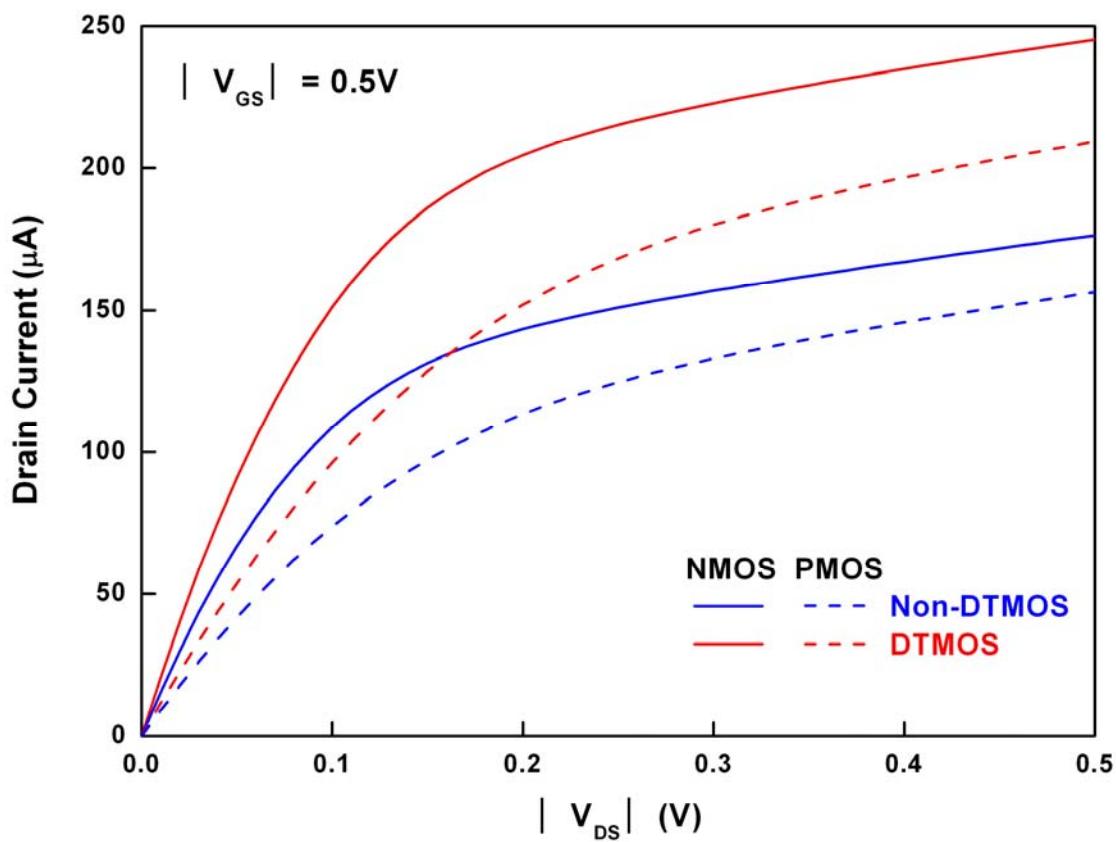

圖 3.4 為動態臨限電壓矽金氧半元件（DTMOS）與非動態臨限電壓矽金氧半元件（Non-DTMOS）的元件在 90 奈米互補型矽金氧半元件使用 MTCMOS 技術，當  $|V_{GS}| = 0.5V$  時，汲極（Drain）電流的特性。此圖我們是再次強調在強反轉區間（strong inversion）的時候，使用動態臨限電壓矽金氧半元件（DTMOS）的技術的 N 型矽金氧半元件（NMOS）和 P 型矽金氧半元件（PMOS）都會提供更強大的電流。我們了解絕緣體上動態臨限電壓矽金氧半元件（SOI DTMOS）的好處後，接下來在下一章節中，我們將利用此技術去做成一個 NAND 邏輯閘。

圖 3.4：動態臨限電壓矽金氧半元件（DTMOS）與非動態臨限電壓金氧半元件（Non-DTMOS）的元件在 90 奈米互補型矽金氧半元件使用 MTCMOS 技術，當  $|V_{GS}| = 0.5\text{V}$  時，汲極（Drain）電流的特性

## 3.2 絝緣體上動態臨限電壓矽金氧半元件邏輯閘電路 (SOI DTMOS Logic Cell)

圖 3.5：使用絝緣體上 (SOI) 動態臨限電壓矽金氧半元件 (DTMOS) 0.5V NAND 邏輯閘使用 90 奈米互補型矽金氧半元件技術的電路佈局

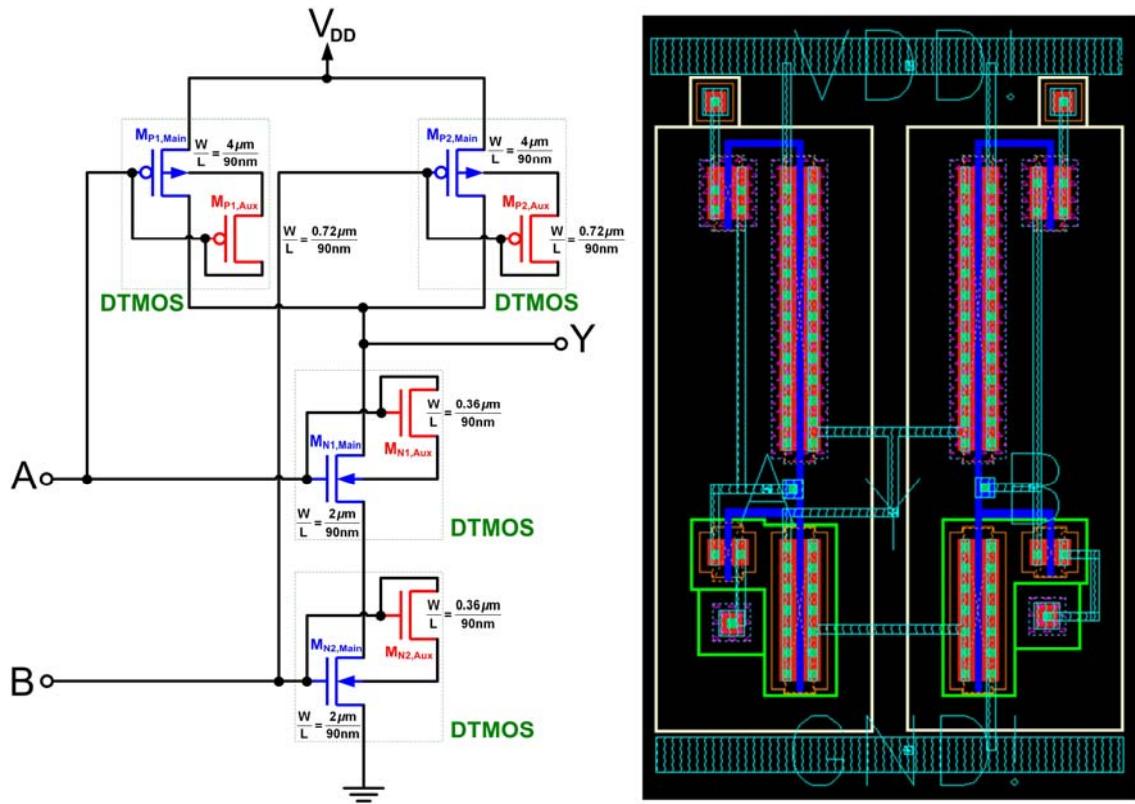

圖 3.5 為使用絝緣體上 (SOI) 動態臨限電壓矽金氧半元件 (DTMOS) 0.5V NAND 邏輯閘使用 90 奈米互補型矽金氧半元件技術的電路佈局，其中裡面的 NMOS 和 PMOS 都是使用動態臨限電壓矽金氧半元件 (DTMOS) 的技術所建立的，左邊為 NAND 邏輯閘的電路圖，右邊為 NAND 邏輯閘的佈局 (layout) 圖。

在此圖中，NAND 邏輯閘裡面所使用的輔助電晶體的 NMOS 和 PMOS 都是為小尺寸的電晶體，其相關尺寸為使用 90nm 的通道長度 (channel length)，而 NMOS 的寬度 (width) 為  $0.36\mu\text{m}$ ，PMOS 的寬度 (width) 為  $0.72\mu\text{m}$ 。主要電晶體的 NMOS 和 PMOS 都是使用大尺寸的電晶體，所謂的大尺寸電晶體，其相關尺寸為 NMOS 的寬度 (width) 為  $2\mu\text{m}$ ，PMOS 的寬度 (width) 為  $4\mu\text{m}$ ，也是使用 90nm 的通道長度 (channel length)，藉由此架構做接下 90nm SPICE 的相關模擬。

圖 3.6：顯示使用絕緣體上（SOI）動態臨限電壓矽金氧半元件（DTMOS）0.5V NAND 邏輯閘電路電壓和電流，在上拉（pull-up）的期間的暫態波形

圖 3.7：顯示使用絕緣體上 (SOI) 動態臨限電壓矽金氧半元件 (DTMOS) 0.5V NAND 邏輯閘電路電壓和電流，在下拉 (pull-down) 的期間的暫態波形

圖 3.6 為顯示使用絕緣體上 (SOI) 動態臨限電壓矽金氧半元件 (DTMOS) 0.5V NAND 邏輯閘電路電壓和電流，在上拉 (pull-up) 的期間的暫態波形。由圖可知，負載電容為 20f 法拉，輸入電壓從 0.5V 降至 0V，fall time 為 0.05ns，觀察圖形中 DTMOS 與 Non-DTMOS 在上拉 (pull-up) 時暫態的表現。從圖中可觀察暫態電流的趨勢，我們會發現 DTMOS 提供較大的切換 (switching) 電流，所以 DTMOS 的上拉 (pull-up) 電壓速度比較快。在上拉 (pull-up) 的時候，因為是以 PMOS 為主，所以我們可以觀察得知，使用 DTMOS 架構的 PMOS 在上拉 (pull-up)

暫態 (transient) 是比較重要的。

圖 3.7 為使用絕緣體上 (SOI) 動態臨限電壓矽金氧半元件 (DTMOS) 0.5V NAND 邏輯閘電路電壓和電流，在下拉 (pull-down) 的期間的暫態波形。在此圖中，下拉 (pull-down) 暫態的時候主要是以 NMOS 為主。同樣地，此張圖我們看到 DTMOS 的下拉 (pull-down) 的暫態速度比較快，同時在此圖中，我們把暫態電流也看出來。在下拉 (pull-down) 比較快的同時，事實上，暫態的電流對 DTMOS 也比較大，要再次強調一點，就是在下拉 (pull-down) 的時候，是以 NMOS 為主，PMOS 的影響較小。

圖 3.8：0.5V NAND 邏輯閘電路在使用絕緣體上（SOI）動態臨限電壓矽金半

元件（DTMOS）技術在上拉與下拉暫態時，傳遞延遲時間與電容負載的比較

圖 3.8 為 0.5V NAND 邏輯閘電路在使用絕緣體上（SOI）動態臨限電壓矽金

半元件（DTMOS）技術在上拉（pull-up）與下拉（pull-down）暫態時，傳遞延

遲時間與電容負載的比較，負載電容從 5f 法拉掃描到 50f 法拉， $V_{DD}$  為 0.5V。由

圖可知，使用了 DTMOS 類型的元件在上拉（pull-up）或下拉（pull-down）

特性都會比較快，較 Non-DTMOS 類型的元件改進許多。

### 3.3 絶緣體上動態臨限電壓矽金氧半元件技術元件資料庫 ( SOI DTMOS Cell Library )

以上兩節已經完成 SOI DTMOS 元件和 SOI DTMOS 邏輯閘電路的探討，此章節就是要將 DTMOS 的技術改進至 EDA 程式中使用，使得 SOI DTMOS 可以在後續的 high-level synthesis 中使用。為了 EDA tool 能應用起見，我們必須把原來 90nm bulk 的 cell library 相關 SOI 會使用到都標示出來，所以首先我們必須從 90nm HSPICE Library 出發。我們首先建立 SOI Cell Library 相關詳細規格，再把 SOI Library 相關的邏輯閘 cell 電路的 HSPICE 檔案建立起來，然後每個 cell 我們再做前置模擬 (pre-simulation)，模擬完後，在跟原來的檔案比較，確認沒問題。其次接下來去做基本邏輯閘 cell 的佈局 (layout)，需將佈局完成建立，由於 SOI 的規格跟 bulk 不一樣，所以我們必須一步一步將其建立出來。佈局完成後，接者建立 schematic，再來是佈局完的後置模擬 (post-simulation) [27][28]，分別使用 90nm DRC Design Rule 去驗證 DRC 佈局的正確性，再經由使用 90nm LVS Design Rule 去驗證 LVS 電路跟佈局的正確性，最後經過 90nm LPE Design Rule 去做 LPE 萃取出相關寄生參數，再將其相關寄生參數加入回原來 HSPICE 檔案中，去做後置佈局模擬 (post-layout simulation)，確認無誤，再將邏輯閘 cell 的特性相關數據模組化建立，再經由 Library Complier[29]後就可以完成 SOI DTMOS 標準元件資料庫。圖 3.9 即為 SOI DTMOS 元件資料庫建立的流程圖。

圖 3.9：絕緣體上矽(SOI)動態臨限電壓矽金氧半元件(DTMOS)標準元件資料庫

建立流程圖

### 3.4 絶緣體上動態臨限電壓矽金氧半元件 **GDSPOM ( SOI DTMOS GDSPOM )**

先前我們發展的閘級的雙重臨界電壓靜態功率最佳化的演算法 (gate-level dual-threshold static power optimization methodology ; GDSPOM)，我們之前已經在 bulk 中使用此技術於三年前。基本上就是想把一個系統的電路，能夠依據時間 (Timing) 的需求然後把它的靜態功率 (Static Power) 消耗做最佳化處理，達到低功率 (Low-Power) 的性能設計。原來的設計是在 bulk 的條件下，現在我們就要把此技術應用在到 90nm SOI 上，所以我們現在必須建立一套 SOI DTMOS GDSPOM 的流程。首先我們跟 bulk 的步驟相同，先建立從傳統 Non-DTMOS 的 16-bit 乘法器，從 RTL Design 出發，跟 bulk 的出發點是一樣的，然後我們根據 Non-DTMOS 標準元件資料庫去做合成 (Synthesis)，得到一個邏輯閘電路檔 (Gate Level Netlist)，這個電路檔裡的 cell 全部都是由 Non-DTMOS 邏輯閘 cells 所組成，之後做靜態時序分析 (Static Timing Analysis ; STA) [30]，使電路必須符合時間限制下，把不符合時間限制的路徑找出來，即  $slack < 0$  的所有路徑，將其路徑中重複性最高的前幾個 cell 取出其資訊預備替換為 SOI DTMOS 標準元件資料庫，之後產生一個必須交換邏輯閘 cell 的資料檔 (Swap cell list)，再將此資料檔經直譯程式 (TCLSH) 與先前所建立 SOI DTMOS 標準元件資料庫來執行交換邏輯閘程式 (Swap Cell Script)，最後就可以完成經由 SOI DTMOS 版本的 GDSPOM

程序所建立的 DTMOS/Non-DTMOS SOI 0.5V 16-bit SOI 乘法器電路。如圖 3.10。

圖 3.10：用兩種邏輯層級的臨界電壓做總功率最佳化(gate-level dual-threshold static power optimization methodology ; GDSPOM)絕緣體上矽動態臨限電壓金氧化半元件 (SOI-DTMOS) 版本的程序，使用 MTCMOS 技術去設計高速度且低功率的系統應用之流程圖

### 3.5 絝緣體上動態臨限電壓矽金氧半元件系統應用 ( SOI DTMOS System )

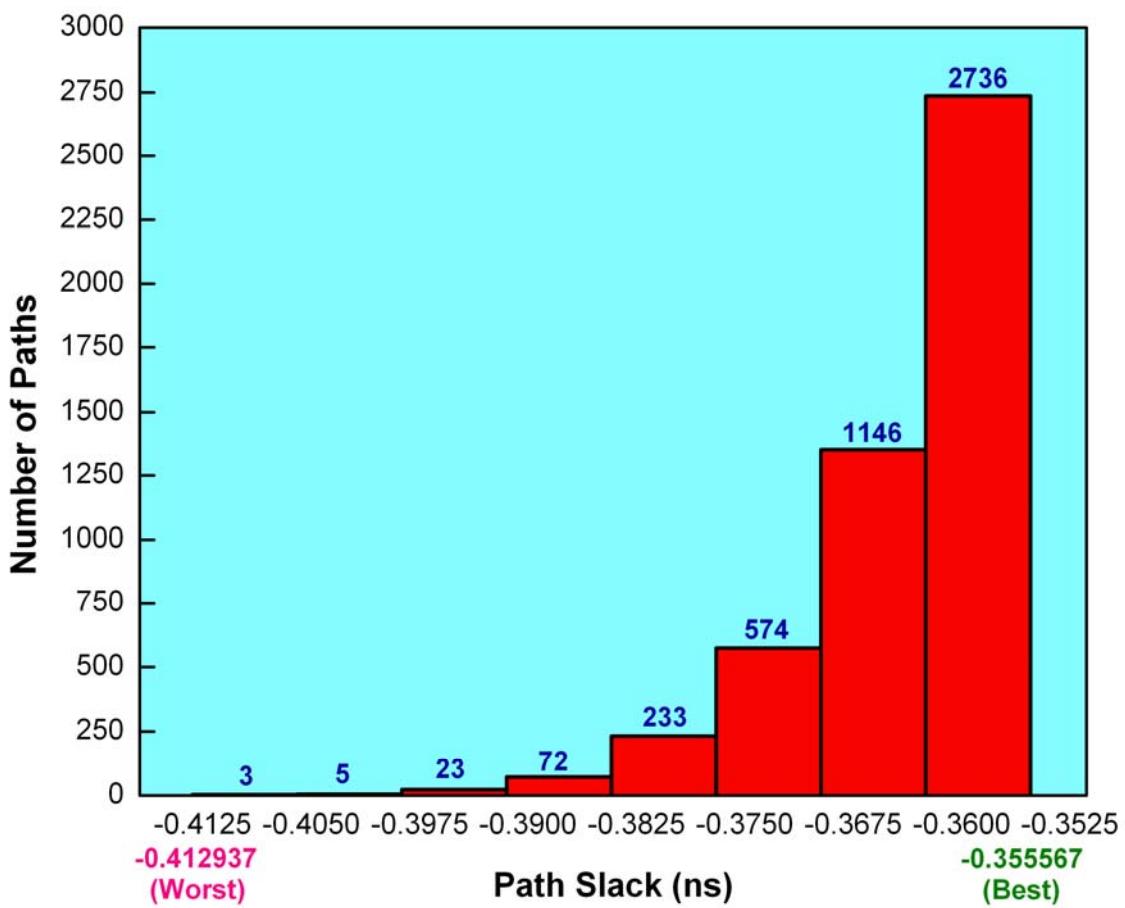

為了將 SOI DTMOS 的技術應用在系統上，分別經由設計兩個 16-bit 乘法器電路以華勒樹架構所建立。設計從同樣暫存器轉移層次語言 (RTL)來源，第一個乘法器電路使用全部 Non-DTMOS 邏輯閘 cells 組成，第二各乘法器電路使用 SOI DTMOD/Non-DTMOS SOI 邏輯閘 cells 元件所組成。這個設計目標的操作頻率為 400MHz 的限制條件。在這 16-bit 乘法器電路中，總共有 5371 邏輯閘。圖 3.11 在未經過 SOI DTMOS 版本的 GDSPOM 程序前，在 0.5V 下全部使用非動態臨界電壓矽金氧半元件 (Non-DTMOS) 邏輯閘 cells 的 16-bits 乘法器電路中違反時間限制的路徑分布圖。如圖所示，在操作頻率為 400MHz 限制下，分析 5000 條不符合時間限制的路徑，當不符合時間限制時就是有負的 slack 產生，表示訊號由輸入端到輸出端所需經過的時間大於所設定時間的值，例如，一條路徑的 slack 為 -0.25ns，就表示訊號經過這條路徑所需的時間比設定的時間慢 0.25ns，所以 slack 的值就是表示訊號經過這條路徑的時間與電路限定時間值的差。由圖可知，路徑 slack 介於 -0.4125 和 -0.4050 之間的路徑有 3 條，介於 -0.4050 和 -0.0.3975 之間的路徑有 6 條，以此類推。這些易造成時間延遲的路徑，是決定 0.5V 16-bit 乘法器電路的操作頻率的關鍵因素。

圖 3.11：在未經過 SOI DTMOS 版本的 GDSPOM 程序前，在 0.5V 下全部使用非動態臨限電壓矽金氧半元件(Non-DTMOS)邏輯閘 cells 元件的 0.5V 16-bit SOI 乘法器電路中違反時間限制的路徑分布

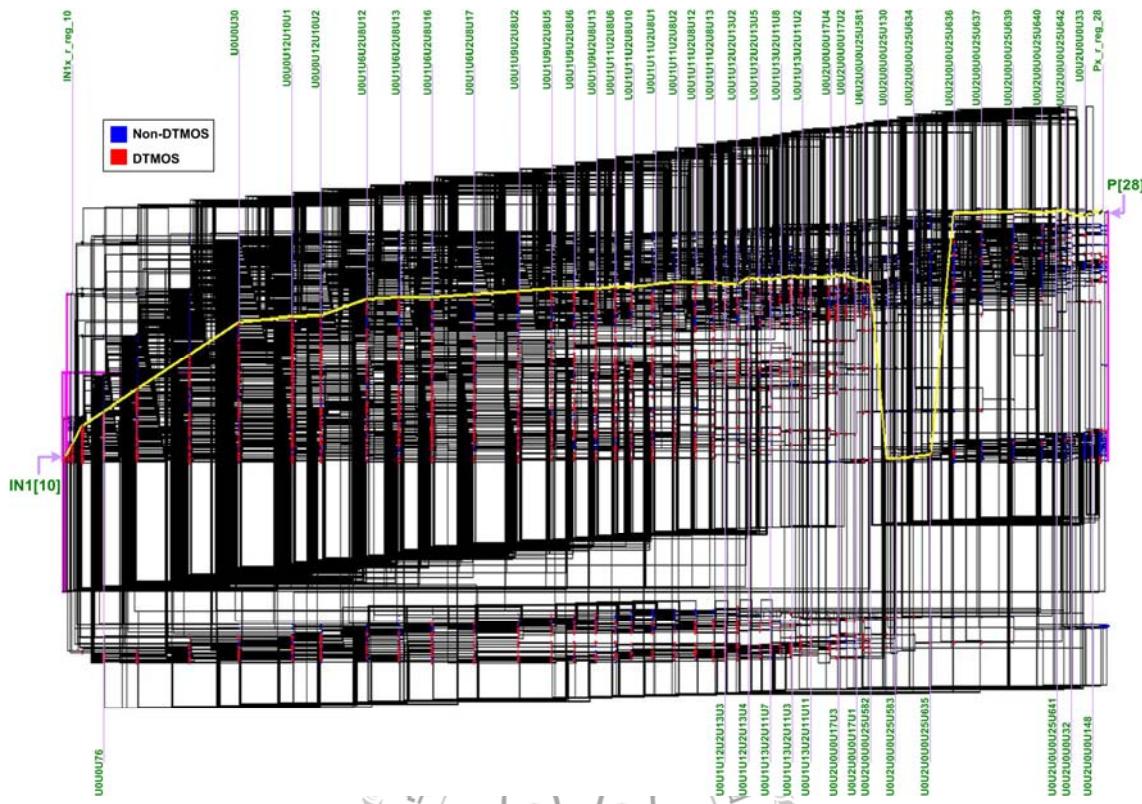

在這項研究中，透過 SOI DTMOS GDSPOM 程序替換了 2574 個邏輯閘 cells 約為總邏輯閘 cell 數量的 48%，從非動態臨限電壓矽金氧半元件 (Non-DTMOS) 的邏輯閘 cells 元件置換成絕緣體上動態臨限電壓矽金氧半元件 (SOI DTMOS) 的邏輯閘 cells 元件，就可以符合電路操作頻率 400MHz 的限制要求。

圖 3.12：經由 SOI DTMOS 版本的 GDSPOM 程序，使用 Non-DTMOS 和 SOI DTMOS 兩種邏輯閘 cells 元件去最佳化 0.5V 16-bit SOI 乘法器電路的電路概要圖

圖 3.12 為經由 SOI DTMOS 版本的 GDSPOM 程序，使用 Non-DTMOS 和 SOI DTMOS 兩種邏輯閘 cells 元件去最佳化 0.5V 16-bit SOI 乘法器電路的電路概要圖，其中藍色的部份為非動態臨限電壓矽金氧半元件（Non-DTMOS）的邏輯閘 cells 元件，紅色的部份為絕緣體上動態臨限電壓矽金氧半元件（SOI DTMOS）的邏輯閘 cells 元件，黃色的線為最初違反時間限制，由輸入端  $IN_{14}$  到輸出端  $P_{26}$  的主要路徑（critical path）。

圖 3.13：使用 SOI DTMOS 版本的 GDSPOM 程序前，使用全部為 Non-DTMOS

邏輯閘 cells 元件組成的 0.5V 16-bit SOI 乘法器電路，由輸入端  $\text{IN1}_{10}$  到輸出端  $P_{28}$  的時間路徑

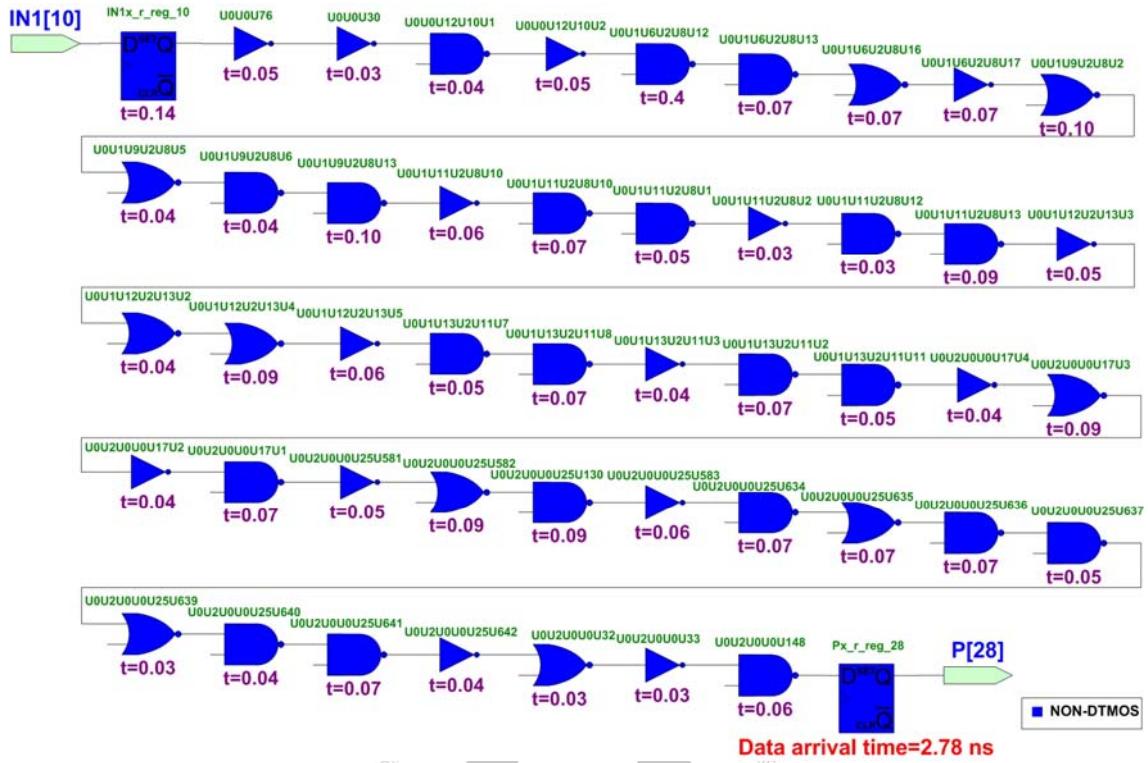

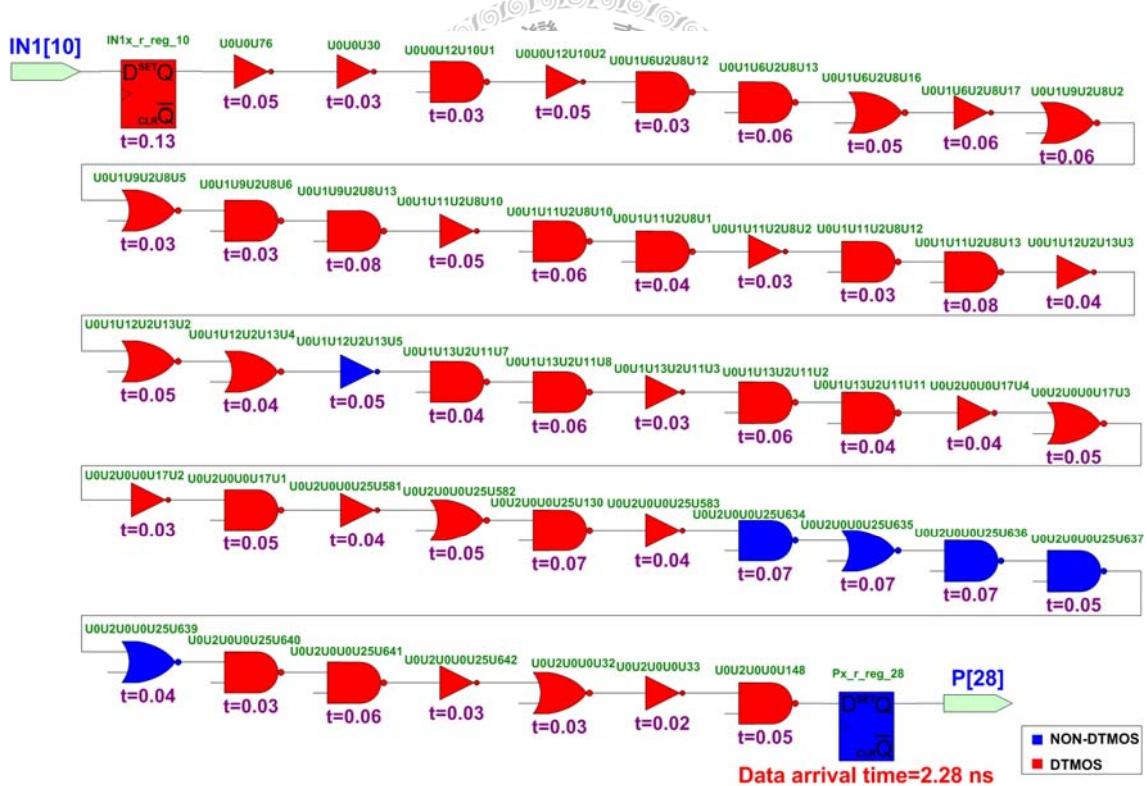

圖 3.13 為使 SOI DTMOS 版本的 GDSPOM 程序前使用全部為 Non-DTMOS

邏輯閘 cells 元件組成的 0.5V 16-bit 乘法器電路，由輸入端  $\text{IN1}_{10}$ （乘法器中被乘

數的第 10 個位元）到輸出端  $P_{28}$ （乘法器中第 26 個位元的乘數）的時間路徑。圖

3.14 為使用 SOI DTMOS 版本的 GDSPOM 程序後，使用 Non-DTMOS 和 DTMOS

兩種邏輯閘 cells 元件最佳化組成的 0.5V 16-bit 乘法器電路，由輸入端  $\text{IN1}_{10}$  到輸

出端  $P_{28}$  的時間路徑。這一個路徑是根據一個開經由全部由 Non-DTMOS 標準資

料元件庫去合成 0.5V 16-bit 乘法器電路中的主要路徑 (critical path)，用此路徑

來顯示如何交換邏輯閘 cell，去解決違反時間限制的路徑。如圖 3.13 所示，在尚未使用 SOI DTMOS 版本的 GDSPOM 程序前，在操作頻率為 400MHz 的限制條件下，此路徑的到達時間為 2.78ns。如圖 3.14 在使用 SOI DTMOS 版本的 GDSPOM 程序後，將原本主要路徑上許多 Non-DTMOS 邏輯閘 cells 元件置換 SOI DTMOS 邏輯閘 cells 元件，使到達時間變為 2.28ns，使此路徑可以達到操作頻率 400MHz 的限制條件。

圖 3.14：使用 SOI DTMOS 版本的 GDSPOM 程序後，使用 Non-DTMOS 和 SOI DTMOS 兩種邏輯閘 cells 最佳化組成的 0.5V 16-bit SOI 乘法器電路，由輸入端 **IN1<sub>10</sub>** 到輸出端 **P<sub>28</sub>** 的時間路徑

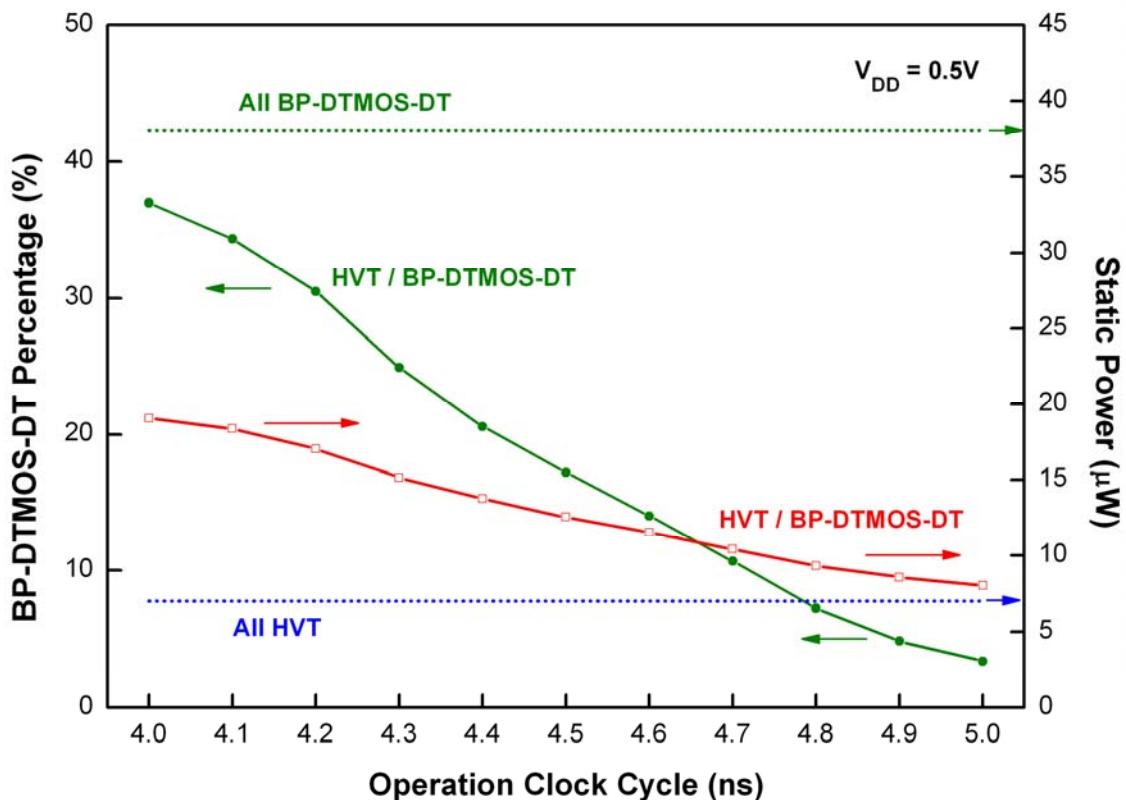

圖 3.15：經由 SOI DTMOS 版本的 GDSPOM 程序，使用 Non-DTMOS 和 SOI DTMOS 兩種邏輯閘 cells 元件最佳化 0.5V 16-bit SOI 乘法器電路的靜態功率消耗和使用 DTMOS 邏輯閘 cells 元件的百分比例

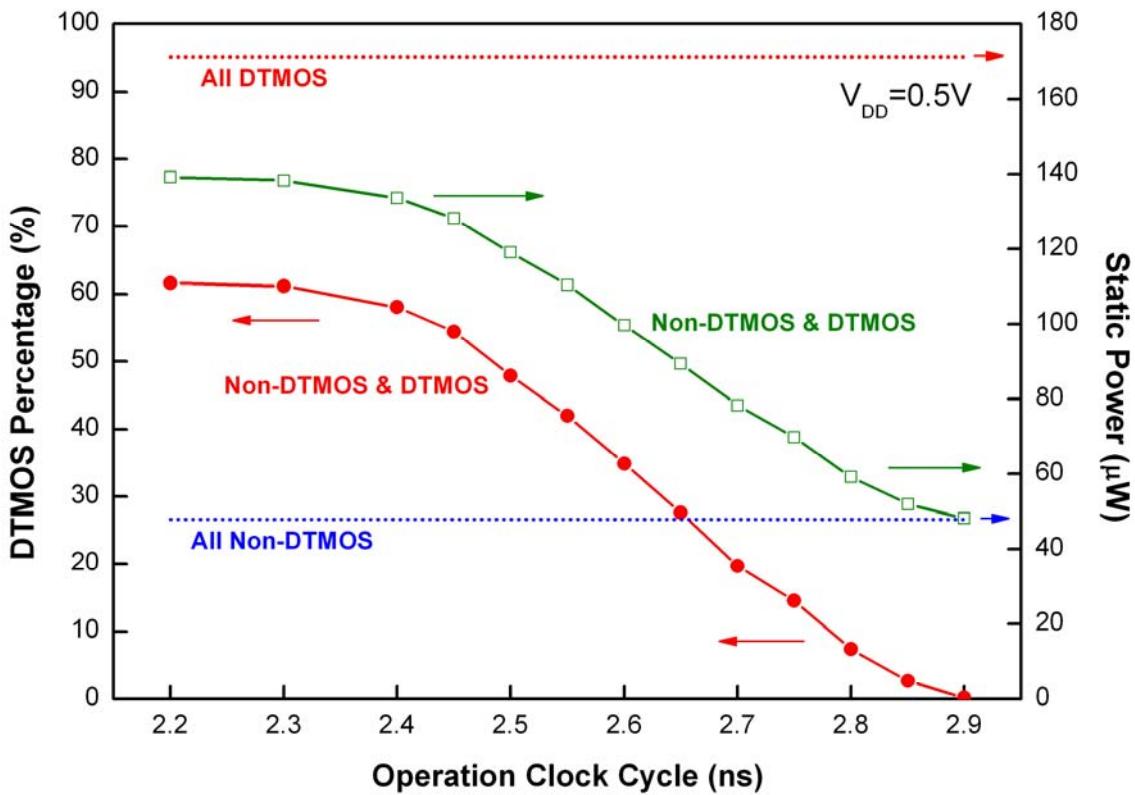

圖 3.15 為經由 SOI DTMOS 版本的 GDSPOM 程序，使用 Non-DTMOS 和 SOI DTMOS 兩種邏輯閘 cells 元件最佳化 0.5V 16-bits SOI 乘法器電路的靜態功率消耗和使用 DTMOS 邏輯閘 cells 元件的百分比例。由圖可知，在這三各 0.5V 16-bit 乘法器數位電路，分別為使用全部為 Non-DTMOS、全部為 SOI DTMOS 與 SOI DTMOS/Non-DTMOS 邏輯閘 cells 元件所組成，其中使用全部為 Non-DTMOS 邏輯閘 cells 元件組成的乘法器電路靜態功率消耗為  $48\mu\text{W}$  最小，但

無法到達操作頻率的限制要求。而使用全部為 SOI DTMOS 邏輯閘 cells 元件組成的 SOI 乘法器電路靜態功率消耗最大，為  $171\mu\text{W}$ 。採用 SOI DTMOS 版本的 GDSPOD 程序最佳化由 DTMOS/Non-DTMOS 邏輯閘 cells 元件組成的 SOI 乘法器電路，靜態功率消耗為  $171\mu\text{W}$ ，比使用全部為 SOI DTMOS 邏輯閘 cells 元件的減少了 30% 的靜態功率消耗。進一步評估這個 SOI DTMOS/non-DTMOS 設計性能的表現，使用不同操作頻率要求的乘法器電路，所造成乘法器電路的靜態功率消耗經由功率計算工具估算出。如圖 3.15 中，與使用全部為 SOI DTMOS 邏輯閘 cells 元件的相比，SOI DTMOS/non-DTMOS 邏輯閘 cells 元件組成的 SOI 乘法器電路有較少靜態功率消耗，更加緩慢的 SOI DTMOS/non-DTMOS 邏輯閘 cells 元件組成的 SOI 乘法器電路，只需要更少量 SOIDTMOS 邏輯閘 cells 元件，因此消耗更少的靜態功率。

# Chapter 4

## 結論和未來研究方向

### Conclusion and Future Work

在本篇論文中，第二章為了實現 SOI DTMOS 技術應用在 bulk 上，首先使用 90 奈米技術在 Bulk 的結構上應用 MTCMOS 的技術應用高臨界電壓（HVT）與低 臨界電壓（LVT）的矽金氧半元件結合動態臨限電壓矽金氧半（DTMOS）技術去 做動態臨界電壓控制，並利用此技術去建立 BP-DTMOS-DT 的標準元件資料庫， 再結合 BP-DTMOS-DT 版本的 GDSPOM 程序做功率最佳化的最佳化設計 0.5V 16-bit 乘法器數位電路。接著使用靜態時序分析方法，再加入 BP-DTMOS-DT 和 高臨界電壓（HVT）的標準元件資料庫分析，並與低臨界電壓（LVT）和高臨界電 壓（HVT）的標準元件資料庫使用 GDSPOM 最佳化後的 0.5V 16-bits 乘法器電路 比較。前者與後者比較，在達到電路速度限制的要求條件下，可以減低約 22.7% 的總功率消耗。

接著第三章使用絕緣體上（SOI）的技術去建立絕緣體上動態臨限電壓矽金氧 半元件（SOI DTMOS）電路架構的標準元件資料庫，在經由靜態時序分析，使用 SOI DTMOS 版本的 GDSPOM 功率最佳化的方法，去最佳化設計 0.5V 16-bit 乘

法器數位電路。使用 non-DTMOS 和 SOI DTMOS 的標準元件資料庫分析，在達到電路速度限制的要求下，使用 non-DTMOS 與 SOI DTMOS 標準元件經由 SOI DTMOS 版本的 GDSPOM 最佳化後，可比全部由絕緣體上動態臨限電壓矽金氧半（SOI DTMOS）元件標準元件資料庫所建立的 0.5V 16-bit 乘法器電路，可以減少約 30% 以上的總功率消耗。

使用動態臨限電壓矽金氧半(DTMOS)技術，不管是使用在已有的 bulk CMOS 結構的電路系統，或採取新穎的絕緣體上(SOI)結構設計的電路系統，都可以實現應用。並結合 BP-DTMOS 和 SOI DTMOS 兩個版本的 GDSPOM 最佳化功率的程序，可以快速的去最佳化一個擁有相同效能卻有較低的功率消耗的電路系統。

未來的研究方向可以將此改良方法應用在 Post-layout 設計層級，再去重新評估所有關於時間和功率消耗的數值。本篇論文目前是應用在 Pre-layout 設計層級，而接線延遲的值是由接線負載模型(wire load model)的數值評估而得到的。由於使用 Post-layout 有明確的實體電路佈局的值，於是將本篇論文的方法運用在 Post-layout 層級會得到更為精確的結果，並可以將系統電路擴大為 32-bit 乘法器電路上的應用。

總和以上結果，本篇論文所探討的方法是可以減少總功率消耗的方法，且它不只可用於傳統 Bulk 已存在的電路設計上，此方法還可以應用在絕緣體上(SOI)的電路設計上，使一種新穎且實用的方法。

## 參考文獻

- [1] J. B. Kuo, J. Lou, "Low-Voltage CMOS VLSI Circuits," Wiley, New York, 1999.

- [2] S. Chou, "Integration and innovation in the nanoelectronics era," IEEE International Solid-State Circuits Conference, vol. 1, pp. 36-41, Feb. 2005.

- [3] G .E. Moore, "Progress in Digital Integrated Electronics," International Electron Devices Meeting, Vol. 21, pp. 11-13, 1975.

- [4] ITRS, "ITRS 2004 Update Documents for Review,"

<http://www.itrs.net/Links/2004Update/2004Update.htm>.

- [5] A. Bellaouar, M. I. Elmasry, "Low-Power Digital VLSI Design : Circuits and System," Kluwer, 1996.

- [6] ITRS, "ITRS 2001 Documents for Review,"

<http://www.itrs.net/Links/2001UTRS/Home.htm>

- [7] Power Modelling and Leakage Reduction, "<http://eda.ee.ucla.edu/EE201A-04Spring/leakage~pres.ppt>"

- [8] T. Douseki, S. Shigematsu, J. Yamada, M. Harada, H. Inokawa, and T. Tsuchiya, "A 0.5V MTMOS/SIMOX Logic Gate," IEEE J. Solid-State Circuits, Vol. 32, No. 10, pp. 1604-1609, 1997.

- [9] S. Shigematsu, S. Muthoh, Y. Matsuya, Y. Tanabe, and J. Yamada, “A 1V High-Speed MTCMOS Circuit Scheme for Power-Down Application Circuits,” IEEE J. Solid-State Circuits, Vol. 32, No. 6, pp. 861–869, 1997.

- [10] F. Assaderaghi, D. Sinitsky, S. A. Parke, J. Bokor, P. K. Ko, and C. Hu, “Dynamic Threshold-Voltage MOSFET (DTMOS) for Ultra-Low Voltage VLSI,” IEEE Trans. Electron Devices, Vol. 44, No. 3, pp. 414–422, 1997.

- [11] C. Wann, F. Assaderaghi, R. Dennard, C. Hu, G. Shahidi, and Y. Taur, “Channel Profile Optimization and Device Design for Low-Power High-Performance Dynamic-Threshold MOSFET,” IEDM Digest, pp. 113–116, 1996.

- [12] J. B. Kuo and K. W. Su, “CMOS VLSI Engineering: Silicon-on-Insulator (SOI),” Kluwer: Dordrecht, 1998.

- [13] W. M. Huang, K. Papworth, M. Racanelli, J. P. John, J. Foerstner, H. C. Shin, H. Park, B. Y. Hwang, T. Wetteroth, S. Hong, H. Shin, S. Wilson and S. Cheng, “TFSOI CMOS Technology for Sub-1V Microcontroller Circuits,” IEDM Dig., pp. 148–151, 1986.

- [14] Y. Yamaguchi and Y. Inoue, “SOI DRAM: Its Features and Possibility,”

SOI Conf. Dig., pp. 122–124, 1995.

- [15] Y. Sato, Y. Kado, T. Tsuchiya, T. Kosugi, H. Ishii, and K. Nishimura, "300KG Gate-Array LSI using 0.25μm Ultra-Thin-Film Fully-Depleted CMOS/SIMOX with Tungsten-Deposited Source/Drain," SOI Conf. Dig., pp. 168–169, 1997.

- [16] "Power Compiler User Guide," 2007, 03.

- [17] S. Mukhopadhyay, K. Roy, "Leakage Estimation and Leakage Control for Nano-Scale CMOS Circuits," Design Automation Conference, 2004.

- [18] J. B. Kuo, "CMOS Digital IC," McGraw-Hill, Taiwan, 1996.

- [19] R. X. Gu, M. I. Elmasry, "Power dissipation analysis and optimization of deep submicron CMOS digital circuits," IEEE Journal of Solid-state Circuits, Vol. 31, Issue 5, pp. 707–713, May 1996.

- [20] J. B. Kuo, "Low-Voltage SOI CMOS Devices and Circuits," Wiley, New York, 2004.

- [21] Usami, K., Kawabe, N., Koizuki, M., Seta, K., Furusawa, T. "Automated Selective Multi-Threshold Design for Ultra-Low Standby Applications," Low Power Electronics and Design Conf Proc, pp. 202–206, 2002.

- [22] Kao, J., Narendra, S., Chandrakasan, A. "MTCNMOS Hierarchical Sizing

Based on Mutual Exclusive Discharge Pattern," Design Automation Conf. Proc, pp. 495–500, 1998.

[23] B. Chung and J. B. Kuo, "Gate-level dual-threshold static power optimization methodology (GDSPOM) using path-based static timing

analysis (STA) technique for SOC application"

[24] Shen, E, Kuo, J. B. "A Novel 0.8V BP-DTMOS Content Addressable Memory Cell Circuit Derived from SOI-DTMOS Techniques." IEEE Conf Elec Dev and Solid State Ckts, pp. 243–245, 2003.

[25] Shen, E, Kuo, J. B. "0.8V CMOS CAM Cell Circuit with a Fast Tag-Compare Capability Using Bulk PMOS Dynamic-Threshold (BP-DTMOS) Technique Based on Standard CMOS Technology for Low-Voltage VLSI Systems," IEEE International Symp. Circuits and Systems Proc, IV 583–586, 2002.

[26] Wallace, C. S. "A Suggestion for a Fast Multiplier. IEEE Trans Comput.", pp. 14–17, 1964.

[27] Synopsys, "Virtuoso Layout Editor User Guide," ~2005.12.

[28] Synopsys, "Virtuoso Layout XL Editor User Guide," ~2005.12.

[29] Synopsys, "Design Compiler User Guide," ~2007.03

[30] Synopsys, "PrimeTime User Guide," ~2007.06.