| 資 國                       | 國立臺灣大學電機資訊學院資訊工程學系<br>碩士論文                                                                                           |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|

| 訊工程學《                     | Department of Computer Science and Information Engineering<br>College of Electrical Engineering and Computer Science |

| 系 學                       | National Taiwan University                                                                                           |

|                           | Master Thesis                                                                                                        |

| 碩士論文                      |                                                                                                                      |

| 內局                        | 局部分群演算法用以合成低功率預先計算型                                                                                                  |

| 容可定                       | 內容可定址記憶體上的低成本參數擷取器                                                                                                   |

| 址<br>演<br>記<br>算          | Local Grouping Algorithm for Synthesizing Low-Cost                                                                   |

| 12<br>憶<br>開              | Parameter Extractor of Low-Power Pre-computation-Based                                                               |

| 可定址記憶體上的低成本參分群演算法用以合成低功率預 | Content Addressable Memory                                                                                           |

| 的成低                       |                                                                                                                      |

| 成本參預                      | 賴聰勝                                                                                                                  |

| <b>參</b> 數<br>類<br>先<br>計 | Tsung-Sheng Lai                                                                                                      |

| 取算器型                      | 指導教授: 賴飛照 博士                                                                                                         |

| 賴<br>聰<br>勝               | Advisor: Feipei Lai, Ph.D.                                                                                           |

| 撰                         | 中華民國 98 年 6 月                                                                                                        |

| 98                        | June, 2009                                                                                                           |

| 6                         |                                                                                                                      |

|                           |                                                                                                                      |

國立臺灣大學碩士學位論文

# 口試委員會審定書

局部分群演算法用以合成低功率預先計算型內容可定 址記憶體上的低成本參數擷取器

Local Grouping Algorithm for Synthesizing Low-Cost Parameter Extractor of Low-Power Pre-computation-Based Content Addressable Memory

本論文係<u>賴聰勝</u>君(學號 R96922071)在國立臺灣大學資訊工程 學系完成之碩士學位論文,於民國 98 年 6 月 14 日承下列考試委 員審查通過及口試及格,特此證明

口試委員:

颜中虚

(指導教授)

臣大峰 谢文姓.

te in the

呂育道

系主任

### 誌謝

經過了許多時間的努力,終於完成此篇論文,而最感謝的當然是我的指導教授賴飛羆老師,老師不僅教導我學術上的知識,並且也讓我學到生活上的許多道理,此外也提供了良好 的學習和實驗環境,使得我可以專心的將大部分時間放在研究上,努力完成了此篇論文,讓 我在台大的這幾年收穫許多。

也感謝口試委員汪大暉教授、莊仁輝教授、梁文耀教授以及蔡坤霖教授在口試時的指導 以及許多的建議,使我在口試的時候能夠更瞭解自己的論文以及報告還有哪些方面可以加強。

感謝我的家人,每次在我感到失望及沮喪時,陪我出外散心,紓解心中的不快,也讓我 被問題困惑時,可以轉換情緒,使得我能夠想到解決的方法,將困惑我的問題一一迎刃而解, 家人是我最大的精神支柱。

感謝李鴻璋教授對我的論文做建議以及指導和糾正,也感謝幫助我許多的彭治弘學長, 每次我有問題問時,都能以我較能理解的方式解釋給我聽,此外也常常和我討論,教我許多 的知識,讓我學到了許多的東西,而且此次論文題目的靈感也是來自於和學長的討論,此外 學長也在此篇論文幫了許多大忙,非常感謝學長大力相挺。

也感謝實驗室的同窗江忠桓、詹承浩還有李育安等和我一起修課及寫論文,大家一同克 服種種難關,以及 Low Power 組的學弟童顗叡、葉紘瑋、林志威、范聖欣、蕭錦濤、嚴天斈, 若不是有你們的幫忙以及大力的配合,計畫以及許多任務也無法順利的完成,且實驗室的歡 笑都是來自於大家,我會將這份美好的回憶珍藏在心底的。

也非常感謝親切的周憲政學長對我們這些學弟的照顧,常常關心我們這些學弟的學業狀況以及生活。

ii

### 摘要

因為內容可定址記憶體的高速特性,使得它在許多需要高速的設備中扮演著重要的角 色,但是它的耗電量也非常的高。在這篇論文中我們提出一個合成演算法用來合成低功率預 先計算型內容可定址記憶體上的參數擷取器,使得資料能夠被均勻的映射到每個參數,而且 硬體的成本也較少。此外我們也提出一個方法去減少當一些資料在區塊中大部分是相同時, 對參數擷取器所帶來的影響。實驗結果顯示,當和 Gate-Block Selection 演算法比較時,我 們的方法可以減少 58.88%的功率消耗,也可以省下 0.53%的 CMOS 電晶體數目。如果用我們提 出的捨去及交錯法去改善 Gate-Block Selection 演算法時,我們的方法仍然可以減少 13%的 功率消耗。

關鍵字:內容可定址記憶體、預先計算、低功率、低成本、合成演算法

### Abstract

Content addressable memory (CAM) plays an important role on the performance of some devices due to the high speed of CAM. But the power consumption of CAM is also high. In this work, we propose a synthesis algorithm to synthesize the parameter extractor for low-power pre-computation-base CAM (PB-CAM) such that the data can be mapped to parameters uniformly and the cost of the parameter extractor can also be lower. Moreover, we also propose a method to reduce the impact on mapping data to parameters when most data are identical in some data blocks. In the experimental results, the average reduction of the power consumption can achieve 58.88% and the number of CMOS transistors can save 0.53% when compared with Gate-Block Selection algorithm. If the Gate-Block Selection algorithm is also enhanced by our proposed discard and interlaced method (DAI method) then the power consumption can still be reduced by 13%.

Keywords: content addressable memory (CAM), pre-computation, low power, low cost, synthesis algorithm

### Contents

| 口試委員       | 會審定                             | こ書i                                         |

|------------|---------------------------------|---------------------------------------------|

| 誌謝         | •••••                           | ii                                          |

| 摘要         | • • • • • • • • • • • • • • • • | iii                                         |

| Abstract.  |                                 | iv                                          |

| Contents   | •••••                           | v                                           |

| List of Fi | gures                           | vii                                         |

| List of Ta | ables                           | ix                                          |

| Chapter 1  | Intro                           | oduction1                                   |

| 1.1        | Power                           | r Dissipation in CMOS VLSI Circuit1         |

|            | 1.1.1                           | Switching Power Dissipation                 |

|            | 1.1.2                           | Short-Circuit Power Dissipation             |

|            |                                 | Leakage Power Dissipation                   |

| 1.2        | Conce                           | ept of Content Addressable Memory4          |

|            | 1.2.1                           | Content Addressable Memory                  |

|            | 1.2.2                           | Applications of Content Addressable Memory5 |

|            | 1.2.3                           | CAM Cell                                    |

|            | 1.2.4                           | Write Operation of a CAM Cell7              |

|            | 1.2.5                           | Read Operation of a CAM Cell9               |

|            | 1.2.6                           | Search Operation of a CAM Cell 10           |

|            | 1.2.7                           | Match Line Structure                        |

| Chapter 2  | 2 Rela                          | ted Work 14                                 |

| 2.1        | Select                          | ive Pre-charge Scheme16                     |

| 2.2        | Pre-co                          | omputation Scheme17                         |

|            | 2.2.1                           | Ones Count Scheme                           |

|            | 2.2.2                           | Block-XOR Scheme                            |

|            | 2.2.3                           | Gate-Block Selection Algorithm              |

| 2.3 Motivation and Objective                       |  |

|----------------------------------------------------|--|

| Chapter 3 Proposed Approach                        |  |

| 3.1 The Benefit of Distributing the Data Uniformly |  |

| 3.2 Local Grouping Algorithm                       |  |

| 3.2.1 Definition of the Variables                  |  |

| 3.2.2 Top Level of Local Grouping Algorithm        |  |

| 3.2.3 Grouping Function                            |  |

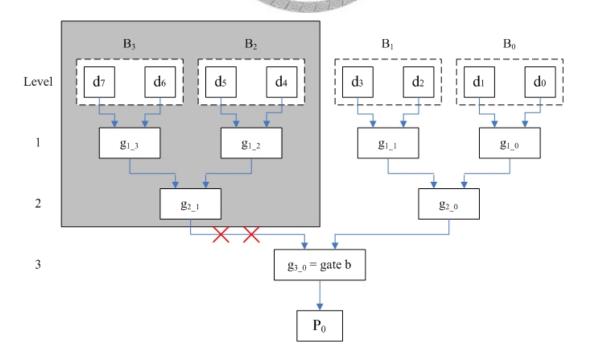

| 3.2.4 Find Gate Function                           |  |

| 3.2.5 Demonstration of Local Grouping Algorithm    |  |

| 3.2.6 Time Complexity of Local Grouping Algorithm  |  |

| 3.3 Discard and Interlaced Method                  |  |

| Chapter 4 Experimental Results                     |  |

| 4.1 Experimental Environment                       |  |

| 4.2 Results                                        |  |

| 4.2.1 Experimental Results of Random Data          |  |

| 4.2.2 Experimental Results of MiBench              |  |

| Chapter 5 Conclusion                               |  |

| References                                         |  |

## **List of Figures**

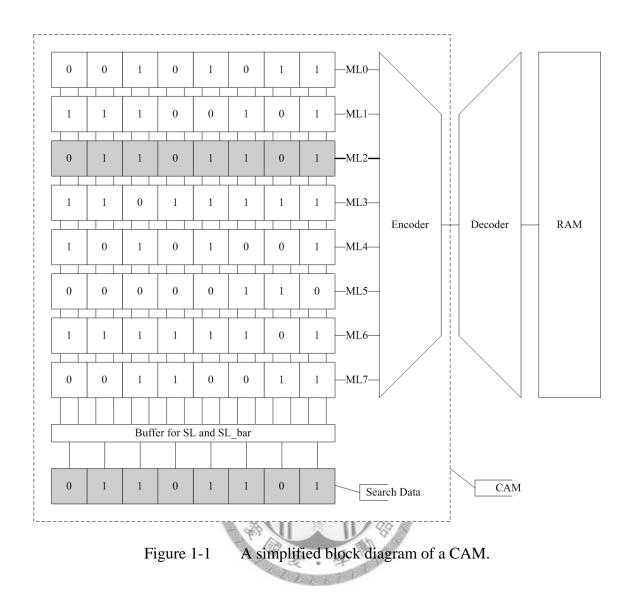

| Figure 1-1  | A simplified block diagram of a CAM5                                       |

|-------------|----------------------------------------------------------------------------|

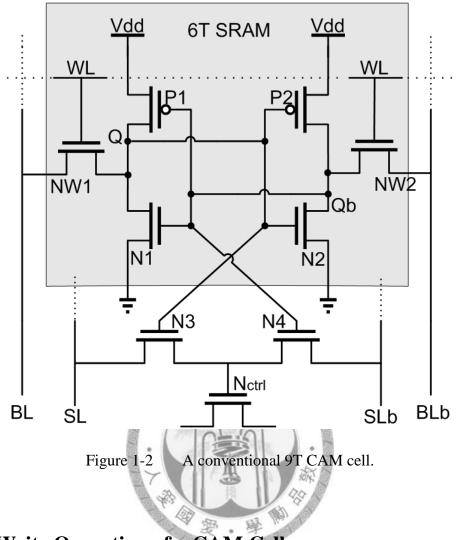

| Figure 1-2  | A conventional 9T CAM cell7                                                |

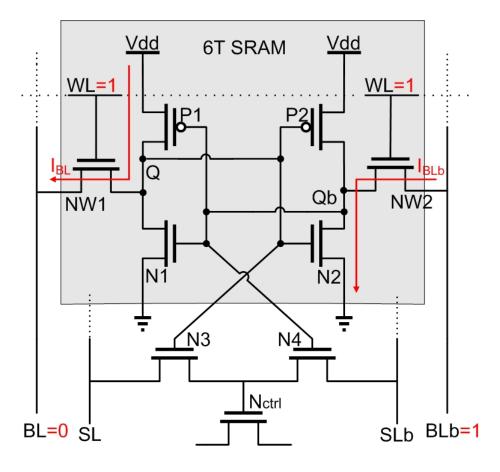

| Figure 1-3  | A 9T CAM cell performs a write operation                                   |

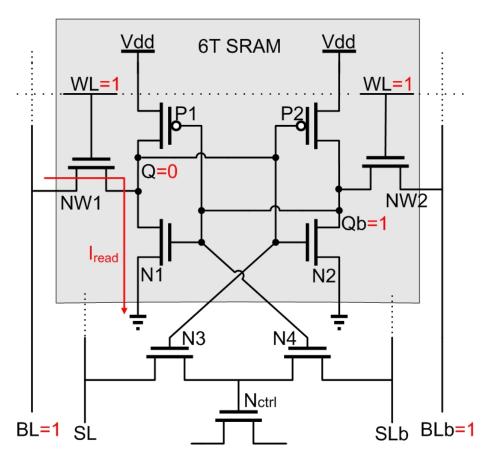

| Figure 1-4  | A 9T CAM cell performs a read operation9                                   |

| Figure 1-5  | (a) XOR type CAM cell. (b) XNOR type CAM cell10                            |

| Figure 1-6  | The schematic of CAM (four word CAM cells)11                               |

| Figure 1-7  | A NOR type match line                                                      |

| Figure 1-8  | A NAND type match line                                                     |

| Figure 2-1  | The simplified architecture of the selective pre-charge scheme16           |

| Figure 2-2  | The basic architecture of PB-CAM                                           |

| Figure 2-3  | 7T PB-CAM cell                                                             |

| Figure 2-4  | Static pseudo-NMOS CAM word circuit                                        |

| Figure 2-5  | Static parameter comparison circuit                                        |

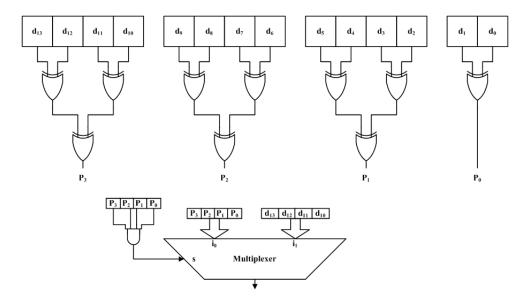

| Figure 2-6  | The 14 bits block-xor parameter extractor                                  |

| Figure 2-7  | The Gate-Block Selection Algorithm23                                       |

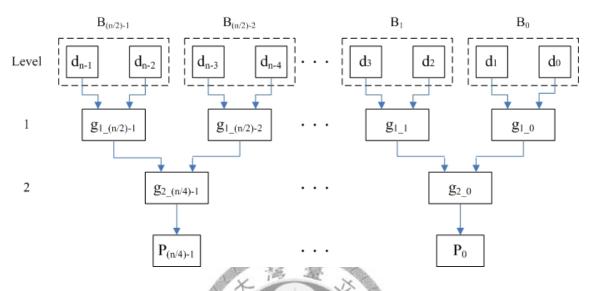

| Figure 3-1  | An example of the 2-level parameter extractor for the <i>n</i> bits data29 |

| Figure 3-2  | The top level of the local grouping algorithm                              |

| Figure 3-3  | The general grouping function                                              |

| Figure 3-4  | The simple grouping function for 2-bit block                               |

| Figure 3-5  | The function for distinguishing all gate types                             |

| Figure 3-6  | The status of reducing hardware cost of the parameter extractor            |

| Figure 3-7  | The find gate function                                                     |

| Figure 3-8  | The function of distinguishing gate types 5, 6 and 7                       |

| Figure 3-9  | The synthesized parameter extractor of the demonstrative example42         |

| Figure 3-10 | The discard and interlaced method                                          |

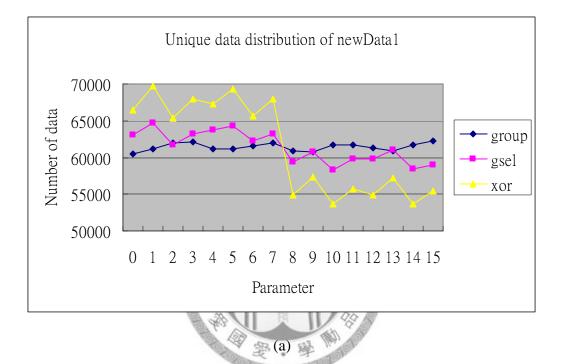

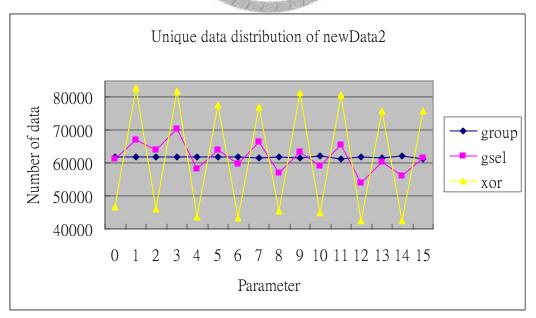

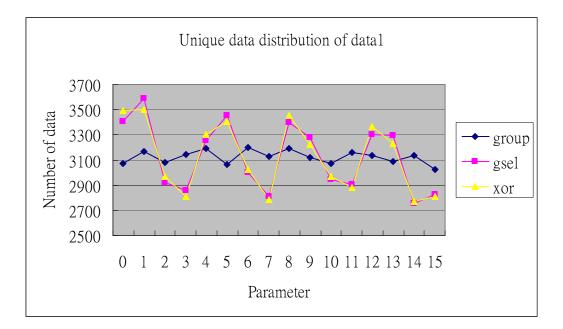

| Figure 4-1  | The unique data distribution of three random data sets                     |

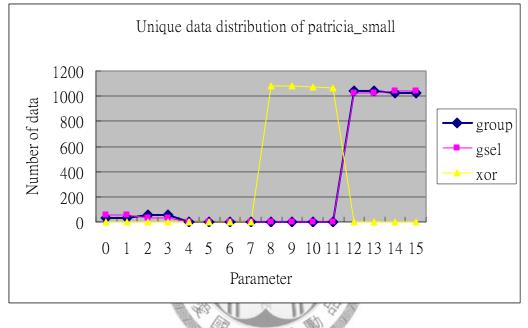

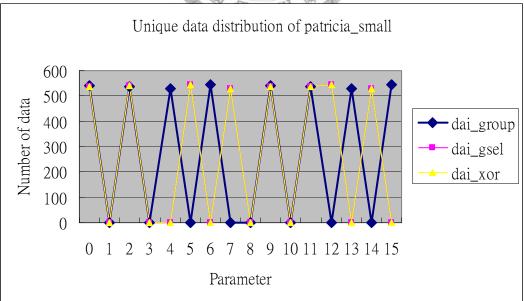

| Figure 4-2  | The data distribution of the patricia_small                                |

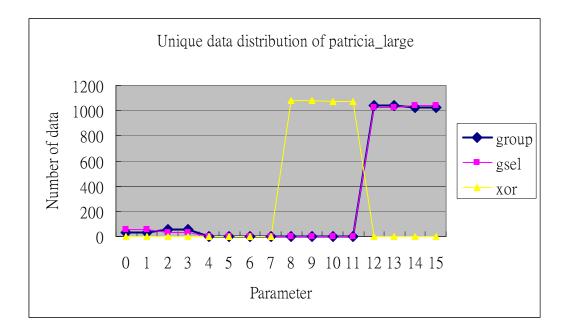

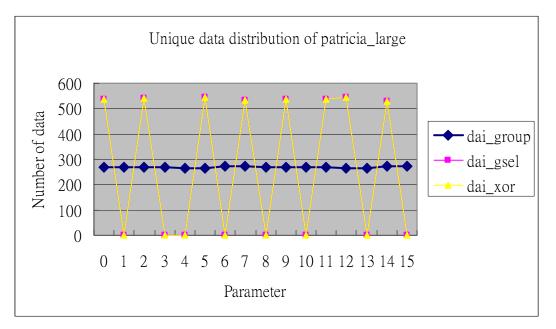

| Figure 4-3 | The data distribution of the patricia_ | _large60 |

|------------|----------------------------------------|----------|

|------------|----------------------------------------|----------|

## **List of Tables**

| Table 1-1  | The comparison of the number of rules between CAM and TCAM6                 |

|------------|-----------------------------------------------------------------------------|

| Table 1-2  | Search operations of XOR and XNOR type CAM cells 11                         |

| Table 1-3  | Comparison between NOR type and NAND type match lines                       |

| Table 2-1  | Number of data is related to the same parameter (ones count)                |

| Table 2-2  | Number of data is related to the same parameter (block-xor)                 |

| Table 2-3  | The time complexity of gate-block selection algorithm                       |

| Table 3-1  | The average number of matched rows for four 2-bit parameters                |

| Table 3-2  | The available synthesized gate types for 2-bit block. (a: msb, b: lsb) . 32 |

| Table 3-3  | An example of the benefit of using additional gate types                    |

| Table 3-4  | An example of the choice of the low-cost gate type                          |

| Table 3-5  | The method of finding the low-cost gate type                                |

| Table 3-6  | The relation of the logic gate type of the methods 2 and 4                  |

| Table 3-7  | An example to demonstrate local grouping algorithm. (First level) 40        |

| Table 3-8  | An example to demonstrate local grouping algorithm. (Second level) 41       |

| Table 3-9  | The time complexity of the local grouping algorithm                         |

| Table 3-10 | The comparison of the time complexity of the algorithms                     |

| Table 3-11 | An example of the problem of the identical data                             |

| Table 3-12 | An example to demonstrate the DAI method. (Steps 2 and 3)46                 |

| Table 3-13 | An example to demonstrate the DAI method. (Result)                          |

| Table 4-1  | The test data in the experiment                                             |

| Table 4-2  | The configurations for all schemes in the experiment                        |

| Table 4-3  | The configurations for each scheme in the experiment                        |

| Table 4-4  | The configuration for DAI method in the MiBench experiment                  |

| Table 4-5  | The standard deviation of each block in the MiBench experiment51            |

| Table 4-6  | The number of data in the random test data                                  |

| Table 4-7  | The standard deviation on the number of unique data that are mapped         |

|            | to each parameter in the random test data                                   |

| Table 4-8  | The high level simulation result.                                   | . 53 |

|------------|---------------------------------------------------------------------|------|

| Table 4-9  | The improvement rate of the high level simulation result            | . 53 |

| Table 4-10 | The number of data in the MiBench                                   | . 56 |

| Table 4-11 | The standard deviation on the number of unique data that are mappe  | d    |

|            | to each parameter in the MiBench                                    | . 57 |

| Table 4-12 | The high level simulation result in the MiBench.                    | . 58 |

| Table 4-13 | The average reduction rate of the high level simulation in MiBench. | . 58 |

| Table 4-14 | The average power consumption in MiBench                            | . 61 |

| Table 4-15 | The average reduction rate of the power consumption in MiBench      | . 61 |

| Table 4-16 | The average reduction rate of the power on the parameter extractor. | . 62 |

| Table 4-17 | The average reduction rate of the number of CMOS elements           | 62   |

### **Chapter 1** Introduction

The performance of modern devices becomes faster than before, however the power consumption and thermal of devices also increase. So the reduction of the power consumption of a device becomes an important issue for many researches especially for embedded systems and portable devices. Content addressable memory (CAM) is one hot topic in these researches. CAM can search for content in parallel within it; so many devices use it to increase performance such as the translation look-aside buffer (TLB) in microprocessors and the tag memory of caches. In the network, the ternary content addressable memory (TCAM) also plays an important role because it performs the routing lookup and packet classification in the network router. Although CAM can operate in high frequency, it also consumes much power. The high power consumption is not suitable for portable devices and embedded systems. Therefore, the reduction of the power consumption of CAM while maintaining its high speed searching performance is required. In this thesis, we proposed an algorithm to synthesize the parameter extractor of Pre-computation-based CAM and the parameter extractor can more uniformly map the data to each parameter. We also proposed a method to reduce the impact on mapping data to parameters when some blocks have a lot of identical data.

### **1.1 Power Dissipation in CMOS VLSI Circuit**

In the CMOS VLSI circuits, the power consumption can be separated into switching, short-circuit and leakage power consumption. So the average power consumption can be modeled by the following equation [1]:

$$P_{avg} = P_{switching} + P_{short-circuit} + P_{leakage}$$

(Equation 1-1)

#### **1.1.1 Switching Power Dissipation**

Switching power consumption is due to charging and discharging the parasitic capacitances when the transistors are switching. It is one of dominant sources of the power consumption in the CMOS circuits; the other is leakage power consumption. We can use the following equation to model the switching power consumption [2]:

$$P_{switching} = \alpha_{0 \to 1} \times C_L \times V_{dd}^2 \times f_{clk}$$

(Equation 1-2)

Where:

$\alpha_{0->1}$  = The 0 to 1 transition probability per clock cycle.

$C_L$  = The sum of all load capacitance.

$V_{dd}$  = The supply voltage of the circuit.

$$f_{clk}$$

= Clock frequency.

#### **1.1.2 Short-Circuit Power Dissipation**

When the NMOS and PMOS of a device are on simultaneously, there is a direct current path between power supply and ground that causes the short-circuit power consumption. If the supply voltage is lower than the sum of the threshold voltage of the NMOS and PMOS in the device  $(V_{dd} < V_m + |V_{tp}|)$  then the short-circuit current can be eliminated [1]. The short-circuit power consumption of a CMOS inverter can be estimated by the following equation [2]:

$$P_{short-circuit} = \frac{\beta}{12} \times (V_{dd} - 2V_t)^3 \times \frac{\tau}{T_{clk}}$$

(Equation 1-3)

Where:

$\beta$  = An effective transistor strength that is a constant which depends on the transistor sizes and the technology.

- = The threshold voltage of the NMOS and PMOS transistors.  $V_{t}$

- = Input rising/falling time. τ

$T_{clk}$  = Clock cycle time.

#### 1.1.3 Leakage Power Dissipation

Leakage power consumption can be separated into sub-threshold leakage and reverse-bias diode leakage as the following equation [2]:

$$P_{leakage} = (I_{sub-threshold} + I_{diode}) \times V_{dd}$$

(Equation 1-4)

$$I_{sub-threshold} = Ke^{(V_{gs} - V_t)/(nV_T)} (1 - e - \frac{V_{ds}}{V})$$

(Equation 1-5)

(Equation 1-5)

(Equation 1-6)

Where:

$$k, n = A$$

function of the technology

$$V_{gs}$$

= Gate-source voltage.

$I_{diode} = I_{S} \left( e^{\frac{V}{V_{T}}} - 1 \right)$

$$V_{ds}$$

= Drain-source voltage.

$V_t$ = Threshold voltage.

$V_T = KT / q$  = Thermal voltage.

$I_s$ = Reverse saturation current.

The sub-threshold current flows from source to drain when the transistors are off and the gate to source voltage is still below the threshold voltage. Therefore the transistors still conduct by weak current. The reverse-bias current flows through the reverse-biased diodes that are formed between the diffusion regions and the substrate. These currents

are small for former process technologies, but they are no longer neglected due to the popularity of deep-submicron technology [3].

#### **1.2 Concept of Content Addressable Memory**

In the following sections, we will introduce some concepts of CAM first. The topics include the architecture, operations and applications of CAM.

#### **1.2.1 Content Addressable Memory**

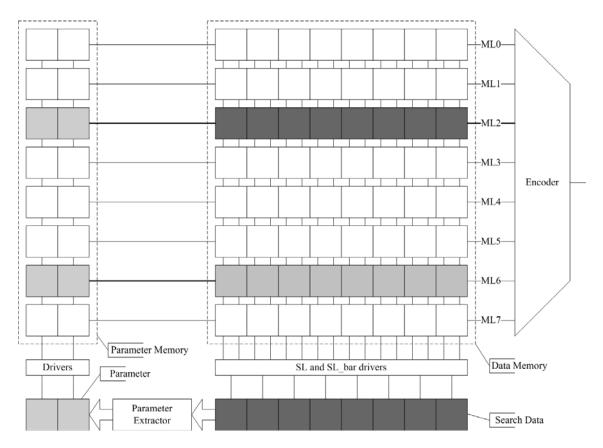

CAM is one kind of fully associative memory so it can search for the data that are stored in the memory in parallel. CAM is different from the random access memory (RAM). Because RAM uses the access address as input and decodes the address to find the data within it then output the data. But CAM uses the search data as input and compares the search data with the stored data within it in parallel. If the data is found then CAM will output some addresses to access a RAM and the RAM stores some data which are related to the data in CAM. For example, Figure 1-1 shows the simplified block diagram of CAM. The size of it is eight words and each word is stored in eight CAM cells. The data in the CAM compare with the search data from the search line (SL) buffers (or called drivers) and there is a match in this example. So the voltage of match line 2 (ML2) remains high and the others are discharged low when the NOR type match line is used. Then the encoder outputs an address and decoder decodes this address to load data from the RAM.

#### **1.2.2 Applications of Content Addressable Memory**

CAM is often used in many devices especially in computer networking devices. For example, the routing table of the network router and the policy table of the hardware firewall are implemented by CAM. It is used for packet forwarding and packet classification. CAM can be classified into two types. One is binary CAM as shown in Figure 1-1, the other is ternary CAM. Binary CAM is often used in computer devices but not network devices in recent years because it only can store two states "0" and "1" in a CAM cell. In this situation, it must contain many rules to gain high performance that causes the hardware cost become higher. So many network devices use ternary CAM to store the rules. Ternary CAM can store additional one state that is "don't care" state and therefore it can store more rules than binary CAM when the hardware cost is the same. For example, in Table 1-1 binary CAM needs four space to store the rules but the ternary CAM only needs one space.

| Table 1-1The comparison of the number of rules between CAM and TCAM. |  |  |

|----------------------------------------------------------------------|--|--|

| Rules                                                                |  |  |

| 0100                                                                 |  |  |

| 0101                                                                 |  |  |

| 0110                                                                 |  |  |

| 0111                                                                 |  |  |

| 01xx                                                                 |  |  |

|                                                                      |  |  |

Other applications of CAM include TLB [4], processor caches [5], database accelerators, artificial neural network and intrusion prevention system [6]. Thus we can see that CAM plays an important role in performance of devices in these applications. But it is only used in some devices that are related to the performance of systems due to the expensive cost of it.

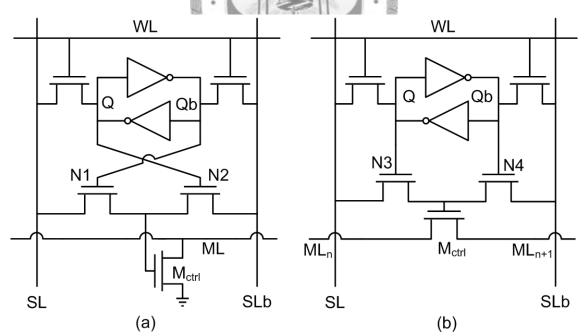

#### 1.2.3 CAM Cell

A CAM cell can search one bit data within it and the data can also be read from it or written into it through bit line by controlling the word line. A schematic of a conventional nine transistors CAM cell is shown in Figure 1-2. It uses six transistors static random access memory (SRAM) to store the data as shown in gray block of Figure 1-2. So the read and write operations of a CAM are the same as in a SRAM. The connection of the control transistor  $N_{ctrl}$  depends on which match line structure is used in the CAM. This transistor decides whether the match line of one word discharge or not. Detailed operations of a CAM cell will be introduced in next sections.

1.2.4 Write Operation of a CAM Cell

When CAM performs write operation of one word, the data are inputted to the bit line drivers. The bit line and bit line bar are driven with bit line drivers. Then word line of this word is charged to high. After these operations, the data will be written into each CAM cell of one word.

For example, Figure 1-3 shows write operation of a CAM cell. The data written into a CAM cell is zero so the bit line is logic 0 and bit line bar is logic 1. Furthermore, we want to write data into a CAM cell hence the word line is logic 1. Then the NMOS NW1 and NW2 are turned on. If the stored data Q is logic 0 then the voltage of this cell is almost stable. Otherwise the PMOS P1 is turned on and NMOS N1 is turned off. A current  $I_{BL}$  is generated from the V<sub>dd</sub> node to ground through P1 and NW1. At the same

time, the P2 is turned off and N2 is turned on. A current  $I_{BLb}$  is generated from the  $V_{dd}$  node to ground through NW2 and N2. For a while, the Q will become logic 0 and Qb become logic 1 due to the bit line drivers are designed mush stronger than the transistors in the CAM cell. Then P1 and N2 are turned off. N1 and P2 are turned on. The voltage of this CAM cell has become stable.

Figure 1-3 A 9T CAM cell performs a write operation.

In the explanation of the above example, we can know that the size of transistors and the drivers of CAM should be designed carefully to ensure that the write operations of a CAM are correct.

#### 1.2.5 Read Operation of a CAM Cell

When CAM performs read operation of one word, the bit line and bit line bar should be charged to logic 1 first. Then the word line of this word also is charged to high. After charging these lines, the data can be read from the bit line. An example is shown in Figure 1-4.

Figure 1-4 A 9T CAM cell performs a read operation.

In Figure 1-4, we assume that the stored data in this CAM cell is zero. The bit line and bit line bar is charged to high then so is the word line. After charging the word line, the NMOS NW1 and NW2 are turned on. A current  $I_{read}$  is generated from the  $V_{dd}$  node to ground through NW1 and N1. Note that when the read operation starts, the bit line drivers are turned off. Therefore the bit line will be discharged to logic zero when the size of N1 is larger than NW1. Because we need to ensure that the data will not flip when reading data from a CAM cell.

#### **1.2.6 Search Operation of a CAM Cell**

The 9T CAM cell [7] can be classified into two types according to its comparative method. One is XOR type CAM cell and the other is XNOR type CAM cell. The two CAM cells are shown in Figure 1-5 and the search line and the bit line are combined here. For instance, we assume that the stored data and the search data are logic 1 in these two CAM cells. Then N2 and N3 are turned on. N1 and N4 are turned off. Current flows through N2 and SLb to ground in Figure 1-5 (a) therefore  $M_{ctrl}$  is turned off. Moreover, the match line is pre-charged to high before searching data so the voltage of the match line will not be pulled down in this CAM cell. In Figure 1-5 (b), the  $M_{ctrl}$  is turned on because N3 is turned on and SL is logic 1. Therefore the CAM cell will pass the current to the next CAM cell that is connected with the same match line. If there is no next CAM cell then the match line will be connected to ground.

Figure 1-5 (a) XOR type CAM cell. (b) XNOR type CAM cell.

The search operation of these two CAM cells can be summarized in Table 1-2. If we replace the "on" state with logic 1 and the "off" state with logic 0 then the search operation is like the logic XOR and XNOR. This is why we name these two types as

XOR and XNOR types. Other structure of CAM cells can be found in [7, 8].

|   | Search operations of AOK and ANOK type CAW cens. |            |            |

|---|--------------------------------------------------|------------|------------|

|   |                                                  | XOR type   | XNOR type  |

| Q | SL                                               | $M_{ctrl}$ | $M_{ctrl}$ |

| 0 | 0                                                | Off        | On         |

| 0 | 1                                                | On         | Off        |

| 1 | 0                                                | On         | Off        |

| 1 | 1                                                | Off        | On         |

Table 1-2Search operations of XOR and XNOR type CAM cells.

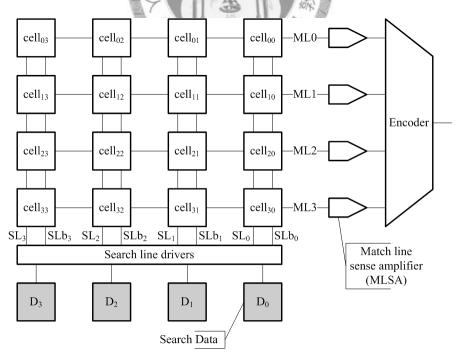

#### **1.2.7 Match Line Structure**

The match line connects several CAM cells to store one word data. It is used to determine which data match the search data. The simplified schematic is shown in Figure 1-6. The match lines are pre-charged to high first and then search data are inputted into search line drivers. After data are inputted to the search line drivers, they drive the search line and search line bar to perform search operation in each CAM cell.

Figure 1-6 The schematic of CAM (four word CAM cells).

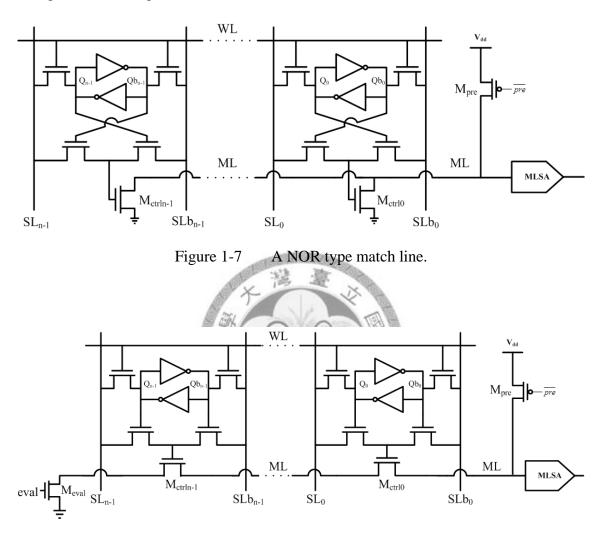

The match line structure [7] can also be classified into two types according to what kind of CAM cell we use in the CAM. If the XOR type CAM cells are used then the match line structure is NOR-type match line. Otherwise, it is NAND-type match line when the XNOR type CAM cells are used. These two match line structures are shown in Figure 1-7 and Figure 1-8.

Figure 1-8 A NAND type match line.

A typical search operation of a NOR type match line has three phases. These three phases include search line pre-charge, match line pre-charge and match line evaluation. Before searching data, the search line is pre-charged to low in order to prevent the match line connecting to ground. After disconnecting the match line from ground, the signal *pre* is asserted to turn on the PMOS  $M_{pre}$ . Then the match line is pre-charged to high. In this time, the search data are inputted into the match line drivers and evaluate the match line. If the search data word matches all the stored bits of the CAM cell on

the same match line then the voltage of the match line will remain high, otherwise it will be pulled down to low. The match line sense amplifier (MLSA) is responsible for sensing the voltage of a match line and outputting the strong voltage that are corresponded to the sensing voltage.

The search operation of a NAND type match line has two phases. These two phases include match line pre-charge and match line evaluation. Before searching data, the signal *pre* is asserted to turn on the PMOS  $M_{pre}$  and then the match line is pre-charged to high. After the match line is pre-charged, the search line can be driven by inputting the search data. Next, the signal *eval* is asserted to turn on the NMOS  $M_{eval}$  and the match line can be evaluated. If the search data matches the stored data then the voltage of the match line will be pulled down to low, otherwise it will remain high.

|                            |               | NOR type | NAND type |

|----------------------------|---------------|----------|-----------|

| Voltage of match           | When match    | High     | Low       |

| line                       | When mismatch | Low      | High      |

| Perfor                     | mance         | Fast     | Slow      |

| Power consumption High Low |               |          |           |

|                            |               |          |           |

Table 1-3Comparison between NOR type and NAND type match lines.

Table 1-3 shows the differences between NOR type and NAND type match lines. The performance of NOR type match line is faster than the NAND type due to the pull down path of the NAND type match line is too long when the stored data is matched. However, the power consumption of NOR type match line is higher than that of NAND type match line. Because in most applications, the search data matches only one data in CAM so the number of the discharged operations of the NOR type match line is more than that of NAND type.

### **Chapter 2** Related Work

In this chapter, we will introduce some designs on low power CAM briefly. Moreover, we will also introduce some designs that are related to our work in the following sections.

Most researches of the CAM are organized well and introduced in [7]. These researches of low power CAM focus on some topics. They include how to reduce the power consumption of the match line, search line and architecture. Some designs will be introduced in the followings.

In low-swing scheme [9], each match line is added an additional injection capacitance to share the charge with the match line. Therefore, the voltage of the match line is less than the supply voltage and the power consumption is less than the conventional design in the missing situation. Another scheme for reducing the power consumption of the match line is current-race scheme [10]. The match lines are pre-charged low and evaluated by charging the match lines with a current I<sub>ML</sub> from a current source. Furthermore, the search lines are also pre-charged to the search data during the match line is pre-charged. A sense amplifier with half-latch is used to fast sense the match result in each match line. In the missing state, the voltage of the match line is charged to  $I_{ML} \times R_{MI}/m$ , where *m* is the number of missing cells in one match line. Otherwise, the match line is charged to high voltage. Hence, this design can save the power consumption of the match line in the missing situation. Moreover, it can also save power on the search line because it eliminates the stage of the search line pre-charge low. The current-saving scheme [11, 12] is similar to the current-race scheme but a current control circuit is added on each match line to control the I<sub>ML</sub>. In missing state, the current is less than in the matching state.

Another power consumption of the CAM is search line driving scheme. In the conventional NOR type match line structure, the search line must be pre-charged to low first. If we eliminate the search line pre-charge phase then the dynamic power consumption of the search line in the pre-charge phase can be reduced [7]. Another scheme is hierarchical search line scheme [13]. It is based on pipeline scheme. In the first segment, the match line and search line always are active. But the match line is not pre-charged and the search line is inactive in the following segments when the match line is mismatched in the previous segment. Thus it can reduce the power consumption of the match line and search line. The bank-selection scheme [7, 14, 15] is another design to reduce power consumption, but it focuses on architecture level. The CAM is divided logically into several banks and each bank contains one continuous address space of the CAM. When the CAM performs the search operation, the search data word is divided logically into stored bits and bank-select bits. Then the bank-select bits are used to decide which bank will be active in this search operation. After the bank is active, the stored bits are compared with the search data in the bank. Therefore this scheme can reduce power consumption because only some banks are active in one search operation. But the drawback of the bank-selection scheme is bank overflow. This situation happens when the capacity of the bank is smaller than the number of the stored data.

In the researches of the routing table and TCAM, the topics include encoding the rules and reducing the power consumption of the priority encoder. Most researches focus on encoding the table in TCAM. However, the tables are encoded for binary CAM with a simple scheme in [16]. If the table is encoded then it can store the number of rules as the original design with less space. Therefore this method can reduce the hardware cost and power consumption. Furthermore, the priority encoder is one of the

dominant power consumption and delay of TCAM. A power-optimized 64-bit priority encoder is proposed in [17]. It improves the conventional priority encoder on delay and power consumption and it also can be pipelined.

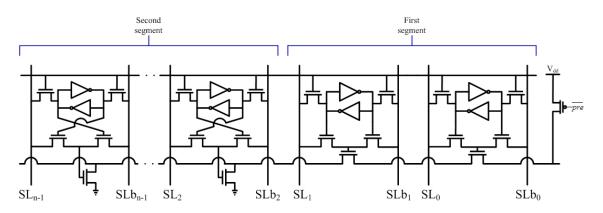

#### 2.1 Selective Pre-charge Scheme

The data words are divided into two segments in the selective pre-charge scheme [18]. Some bits of data are stored in the first segment and the others in the second segment. While the CAM performs search operation, the first segment is active and the relative bits of data are compared. If the relative bits of some data words are matched in the first segment then the associated match line in the second segment will be pre-charged to high. After that, the remaining bits of data are compared in the second segment. If the remaining bits of some data are matched then it means the search data is matched in the CAM. Otherwise, the searching data is mismatched. Therefore, this scheme reduces the power consumption of the match lines. However, if many stored data in the first segment are identical then the power consumption of the CAM is still high.

The simplified architecture of the selective pre-charge scheme is shown in Figure 2-1. The XNOR type CAM cells are used in the first segment and the XOR type CAM cell in the second segment.

Figure 2-1 The simplified architecture of the selective pre-charge scheme.

#### 2.2 Pre-computation Scheme

In this section, we will introduce the concept of pre-computation based CAM (PB-CAM). Then in the following sections, the three different designs of PB-CAM will be introduced.

Figure 2-2 The basic architecture of PB-CAM.

The PB-CAM is shown in Figure 2-2 which contains one parameter extractor, drivers, parameter memory, data memory and encoder. The parameters in the parameter memory are calculated from the data by the parameter extractor. When the search operation is performed, the data is inputted into the search line drivers and the parameter extractor. Then the parameter is outputted from the parameter extractor and inputted into drivers. Afterward, the parameter memory can perform the search operation. If the stored parameters are matched then the relative match line in the CAM is pre-charged. After that, the match line can be evaluated. If the stored data is also

matched then the match line remains high. Otherwise, it will be discharged low. This scheme is similar to selective pre-charge scheme but the efficiency of reducing the power consumption depends on the parameter extractor and search data.

#### 2.2.1 Ones Count Scheme

The PB-CAM is first proposed in [19]. The parameter extractor is implemented by the ones count function in [19]. The ones count parameter extractor counts the number of binary one which appears in one data word. However the hardware cost and delay of the ones count parameter extractor is expensive when the data word length grows. Furthermore, if we assume the data have a uniform distribution then the number of data that are mapped to parameters is not uniform. This situation is shown in Table 2-1 and the data word length is 14 bits. This distribution is not good for reducing the power consumption of the match line because many identical parameters may appear in the memory in one search operation.

| Ones count<br>parameter | Relative data    | Average probability |

|-------------------------|------------------|---------------------|

| 0                       | 1                | 0.0061035%          |

| 1                       | 14               | 0.0854492%          |

| 2                       | 91               | 0.5554199%          |

| 3                       | 364              | 2.2216797%          |

| 4                       | 1001             | 6.1096191%          |

| 5                       | 2002             | 12.2192383%         |

| 6                       | 3003             | 18.3288574%         |

| 7                       | 3432             | 20.9472656%         |

| 8                       | 3003             | 18.3288574%         |

| 9                       | 2002             | 12.2192383%         |

| 10                      | 1001             | 6.1096191%          |

| 11                      | 364              | 2.2216797%          |

| 12                      | 91               | 0.5554199%          |

| 13                      | 14               | 0.0854492%          |

| 14                      | 1                | 0.0061035%          |

| Total                   | $2^{14} = 16384$ | 100%                |

Table 2-1Number of data is related to the same parameter (ones count).

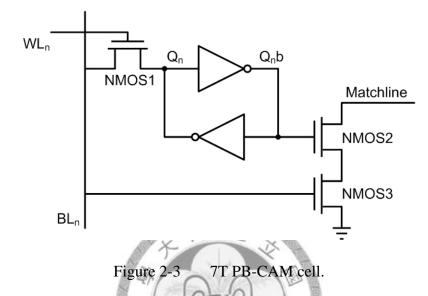

However the ones count parameter extractor is used to cooperate with 7T PB-CAM cell. This PB-CAM cell only uses seven transistors such that the hardware cost and power consumption of data memory are less than the conventional design. The circuitry of 7T PB-CAM cell is shown in Figure 2-3.

This 7T PB-CAM cell is not suitable for every parameter extractor because the match line remains high when  $Q_n = 1$  and  $BL_n = 0$ . However, the 7T PB-CAM cell cooperates with the ones count parameter extractor elegantly. We explain the operations in the following three conditions. First, if the parameter is matched and the data is also matched then the operation of the cell is correct. Second, if the parameter matches the incoming parameter but the data do not. It means the number of binary ones in the stored data and searching data are the same but they are different. Therefore there must be  $Q_i = 1$  and  $BL_i = 0$  in one cell and  $Q_j = 0$  and  $BL_j = 1$  in another cell of the same match line. So the match line is discharged by at least one cell. Third, if the parameter is mismatched and the data is also mismatched then the voltage of the match line is discharged by the static pseudo-NMOS CAM word circuit [19]. This circuit is shown in Figure 2-4. If the parameters are matched then the parameter comparison circuit outputs logic 0. Otherwise, it outputs logic 1. Therefore, the 7T PB-CAM cell can operate well

with the ones count parameter extractor.

Static pseudo-NMOS CAM word circuit.

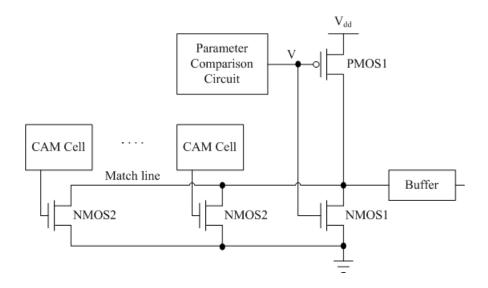

Figure 2-5 Static parameter comparison circuit.

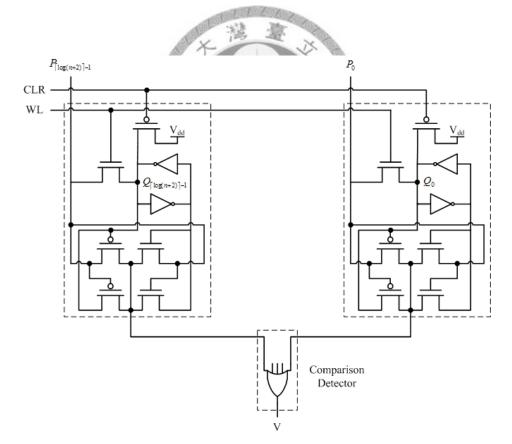

The parameter comparison circuit is shown in Figure 2-5. It performs three operations. First, in parameter setting operation, the CLR is set to logic 0. Then the stored parameter Q is charged to logic 1. The max parameter means invalid flag in this

circuit because the decimal representation of the max value of one parameter word is larger than the bit length of data. Second, in the parameter writing operation, the WL is asserted such that the parameter P can be written into the storage unit Q. Third, in the parameter comparing operation, if the input parameters P match the stored parameters Q then the comparison detector will output logic 0. Otherwise, it will output logic 1.

#### 2.2.2 Block-XOR Scheme

The block-xor scheme is proposed to improve the ones count parameter extractor in [20, 21] but it uses 9T CAM cell. The block-xor parameter extractor is composed of several two fan-in XOR gates. The block diagram of 14 bits block-xor parameter extractor is shown in Figure 2-6 and the design of the valid bit is in the below of Figure 2-6. If the parameters are all binary one then the 4 bits data in the *msb* are used as the parameter. Otherwise, the original parameters are used. So the data is invalid when the stored parameters are all binary one. Furthermore, when the 4 bits data in the *msb* are all binary one, the *msb* of the parameter will be 0. The multiplexer will select the parameter to output. In other words, this design does not have conflicting status.

Figure 2-6 The 14 bits block-xor parameter extractor.

If we assume that the distribution of the data is uniform then the block-xor parameter extractor can distribute the data to parameters more uniformly than the ones count parameter extractor. The distribution is shown in Table 2-2 and the data word length is 14 bits.

| 2 Nulliber             | of uata is related to the                                                                                                                                                                                                                                                     | same parameter (0100                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Block-xor<br>parameter | Relative data                                                                                                                                                                                                                                                                 | Average<br>probability                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0000                   | 1024                                                                                                                                                                                                                                                                          | 6.25%                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0001                   | 1024 + (1024/8)                                                                                                                                                                                                                                                               | 7.03125%                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0010                   | 1024 + (1024/8)                                                                                                                                                                                                                                                               | 7.03125%                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0011                   | 1024                                                                                                                                                                                                                                                                          | 6.25%                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0100                   | 1024 + (1024/8)                                                                                                                                                                                                                                                               | 7.03125%                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0101                   | 1024                                                                                                                                                                                                                                                                          | 6.25%                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0110                   | 1024                                                                                                                                                                                                                                                                          | 6.25%                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0111                   | 1024 + (1024/8)                                                                                                                                                                                                                                                               | 7.03125%                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1000                   | 1024 + (1024/8)                                                                                                                                                                                                                                                               | 7.03125%                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1001                   | 1024                                                                                                                                                                                                                                                                          | 6.25%                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1010                   | 1024                                                                                                                                                                                                                                                                          | 6.25%                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1011                   | 1024 + (1024/8)                                                                                                                                                                                                                                                               | 7.03125%                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1100                   | 1024                                                                                                                                                                                                                                                                          | 6.25%                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1101                   | 1024 + (1024/8)                                                                                                                                                                                                                                                               | 7.03125%                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1110                   | 1024 + (1024/8)                                                                                                                                                                                                                                                               | 7.03125%                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1111                   | Valid bit                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        | Block-xor           parameter           0000           0001           0010           0011           0100           0111           0100           0111           1000           1011           1001           1011           1010           1111           1100           1111 | Block-xor<br>parameterRelative data $0000$ $1024$ $0001$ $1024 + (1024/8)$ $0010$ $1024 + (1024/8)$ $0010$ $1024 + (1024/8)$ $0011$ $1024$ $0100$ $1024 + (1024/8)$ $0101$ $1024$ $0110$ $1024$ $0111$ $1024 + (1024/8)$ $1000$ $1024 + (1024/8)$ $1001$ $1024$ $1011$ $1024$ $1011$ $1024 + (1024/8)$ $1100$ $1024$ $1110$ $1024 + (1024/8)$ $1100$ $1024 + (1024/8)$ $1110$ $1024 + (1024/8)$ $1110$ $1024 + (1024/8)$ |

Table 2-2Number of data is related to the same parameter (block-xor).

#### 2.2.3 Gate-Block Selection Algorithm

The block-xor can distribute the data to parameters more uniformly when the data have a uniform distribution. However, if the data do not have a uniform distribution and most 4-bit *msb* data are identical then the power consumption is still high. In [22], a gate-block selection algorithm is proposed to synthesize the proper parameter extractor when the data do not have a uniform distribution. This scheme is suitable for the embedded systems because the algorithm must analyze the trace of the system first. Then it tries to find a proper parameter extractor for this system. Furthermore, one equation is used to formulate the average number of comparison operation in the

algorithm when one 2 fan-in gate is used to extract a parameter. This equation is shown in Equation 2-1.

$$C_{avg} = N_0 \times (1 - p) + N_1 \times p$$

=  $N_0 \times (\frac{N_0}{N_0 + N_1}) + N_1 \times (\frac{N_1}{N_0 + N_1})$  (Equation 2-1)

=  $\frac{N_0^2 + N_1^2}{N_0 + N_1}$

Where

P = For all data, the probability of a two fan-in gate outputting the logic 1 in one block.

$$N_0$$

= For all data, the number of zero entries in one parameter.

$N_1$  = For all data, the number of one entries in one parameter.

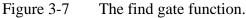

Gate-Block Selection AlgorithmInput Data = (D\_0, D\_1, ..., D\_{n-1})n: bit length of the input data,l: number of input bits for each partition block.Step 1: RecordNAND\_parameter (k) =

$$\overline{D_{2i} \bullet D_{2i+1}}$$

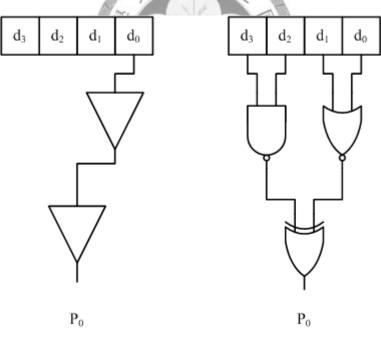

NOR\_parameter (k) =  $\overline{D_{2i} \bullet D_{2i+1}}$ XOR\_parameter (k) =  $\overline{D_{2i} \oplus D_{2i+1}}$ For i, k = 0, 1, ..., (n/2)-1,  $\forall$  input patternsStep 2: Compute NAND\_Cavg(k), NOR\_Cavg(k), XOR\_Cavg(k)Using Equation 2-1,  $\forall k$ Step 3: Select a logic gate with the minimal Cavg(k),  $\forall k$ Step 4: If generated parameter bits >  $\lceil n/l \rceil$ Repeat step 1 to step 3 and use previous generated parameter as input data.ElseFinishFigure 2-7The Gate-Block Selection Algorithm.

The gate-block selection algorithm is shown in Figure 2-7. In step 1, the output parameters of each gate are computed in each 2-bit block for all data. Then in step 2 and 3, the  $C_{avg}$  is computed for each gate. One logic gate which has minimal  $C_{avg}$  is selected for each 2-bit block. It means that the selected logic gate can make the average number of comparison operation lower than the others. In step 4, it determines whether the algorithm finishes or not.

| Level  | Time complexity of each level                  |

|--------|------------------------------------------------|

| 1      | Step 1: $m \times (n/2) \times g \times c_1$   |

|        | Step 2: $(n/2) \times g \times c_2$            |

|        | Step 3: $(n/2) \times c_3$                     |

|        | Step 4: $c_4$                                  |

|        | Step 1: $m \times (n/2^2) \times g \times c_1$ |

| 2      | Step 2: $(n/2^2) \times g \times c_2$          |

|        | Step 3: $(n/2^2) \times c_3$                   |

|        | Step 4: $c_4$                                  |

|        |                                                |

| Sec. 1 | Step 1: $m \times (n/2^k) \times g \times c_1$ |

| k k    | Step 2: $(n/2^k) \times g \times c_2$          |

|        | Step 3: $(n/2^k) \times c_3$                   |

|        | Step 4: $c_4$                                  |

Table 2-3The time complexity of gate-block selection algorithm.

We analyze the time complexity of gate-block selection algorithm in Table 2-3 when the size of each block is two bits. We also define some variables in the following.

Let

- *m*: The number of the unique data. The unique data means that only one data are chosen and the other duplicate data is discarded.

- *n*: The word length of data.

- k: The value of k is the level that we want to synthesize. The range of k is  $1 \le k \le \lceil \log_2 n \rceil$ .

- g: The number of different gate is used in the gate-block selection algorithm. They

are NAND, NOR, XOR in Figure 2-7. Therefore, the value of g is 3.

c: Constant value.

Therefore, the total time complexity is the sum of the time complexity of each level.

That is  $(c_1 \times m \times g \times n + c_2 \times g \times n + c_3 \times n) \times [1 - (\frac{1}{2})^k] + c_4 \times k$ . The time complexity is polynomial time O(mn).

#### porynomia time O(iiii).

### 2.3 Motivation and Objective

The block-xor scheme can not distribute data to different parameters uniformly when the data do not have a uniform distribution. Furthermore, the execution time of gate-block selection algorithm will grow when the number of different gates that are used to synthesize the parameter extractor is increasing in the algorithm. Therefore, we want to use more different gates to synthesize the parameter extractor for PB-CAM in order to distribute the data more uniformly than block-xor scheme and gate-block selection algorithm. We also want to decrease the execution time when more different gates are used. Moreover, we want to reduce the impact on mapping data to parameters when some blocks have a lot of identical data.

## **Chapter 3 Proposed Approach**

We will introduce the benefit of distributing the data uniformly and our synthesizing algorithm for the parameter extractor of PB-CAM in the following sections. We will also introduce the method to reduce the impact on mapping data to parameters when some blocks have a lot of identical data.

## 3.1 The Benefit of Distributing the Data Uniformly

| Ta       | Table 3-1The average number of matched rows for four 2-bit parameters. |          |          |       |                          |                             |                     |                                     |  |

|----------|------------------------------------------------------------------------|----------|----------|-------|--------------------------|-----------------------------|---------------------|-------------------------------------|--|

| msb<br>0 | msb<br>1                                                               | lsb<br>0 | lsb<br>1 | Case  | Paramet<br>er<br>example | Avg.<br>matc<br>h<br>(case) | Prob. of occurrence | Avg.<br>match<br>(distributi<br>on) |  |

| 2        | 2 2                                                                    |          | 2        | best  | 00, 01<br>10, 11         | 1                           | 2/3                 | 1.33                                |  |

|          |                                                                        | 2        | Els.     | worse | 00,00                    | 282                         | 1/3                 |                                     |  |

| 2        | 2                                                                      | 3        | 1        | best  | 00, 00<br>10, 11         | 1.5                         | 1                   | 15                                  |  |

| 2        | 2                                                                      | 3        | 1        | worse | 00, 00<br>10, 11         | 1.5                         | 1                   | 1.5                                 |  |

|          | 1                                                                      | 1 3      | 1        | best  | 00, 00<br>10, 01         | 1.5                         | 3/4                 | 1.75                                |  |

| 3        |                                                                        |          |          | worse | 00, 00 00, 11            | 2.5                         | 1/4                 | 1.75                                |  |

|          |                                                                        |          |          | best  | 00, 00<br>10, 10         | 2                           | 1                   |                                     |  |

| 2        | 2                                                                      | 4        | 0        | worse | 00,00                    | 2                           | 1                   | 2                                   |  |

|          | 1                                                                      | 4        | 0        | best  | 00, 00<br>00, 10         | 0 2.5                       |                     |                                     |  |

| 3        | 1                                                                      | 4        | 0        | worse | 00, 00<br>00, 10         | 2.5                         | 1                   | 2.5                                 |  |

| 4        | 0                                                                      | 4        | 0        | best  | 00,00                    | 4                           | 1                   |                                     |  |

| 4        | 0                                                                      | 4        | 4 0      | worse | 00, 00<br>00, 00         | 4                           | 1                   | 4                                   |  |

The average number of matched rows for four 2-bit parameters in the parameter memory is shown in Table 3-1 and each parameter bit is extracted from one data block. Although each parameter is related to one data, the data is not shown in Table 3-1. The first column to fourth column is the number of "zero" or "one" in the msb or lsb of the four 2-bit parameters. It means the distribution of each parameter bit. For example, in the second row, there are two binary ones and two binary zeros in the msb of these four 2 bits parameters as well as in the *lsb*. If we assume that these four parameters are all in the parameter memory and every parameter is searched one time. Then the average number of matched rows are (1 + 1 + 1 + 1) / 4 = 1 in the best case and (2 + 2 + 2 + 2) / 4 = 14 = 2 in the worse case. Moreover, the probability of the occurrence of the best case is  $4! / [4! / (2! \times 2!)]^2 = 2/3$  and  $2 \times [4! / (2! \times 2!)] / [4! / (2! \times 2!)]^2 = 1/3$ , the worse case. Therefore, the average number of matched rows under this distribution are  $1 \times (2/3) + 2 \times (1/3) = 4/3 \cong 1.33$ . We can see that the average matched rows are small when the data in the same block are mapped to parameters and the distribution of these parameters is uniform. Therefore, if we can map the data in the same block to parameters and the number of binary zeros in this parameter bit position is close to that of binary one. Then the average number of matched rows will decrease in the parameter memory. The power consumption will also be decreased in the PB-CAM because the number of the match lines being pre-charged in the data memory is decreasing. So our algorithm is based on this idea to distribute the data to the parameters such that the power consumption of PB-CAM is smaller than that of block-xor scheme and gate-block selection algorithm.

### **3.2 Local Grouping Algorithm**

In this section, we will introduce our algorithm. Before introducing the algorithm, we will define some variables and terminologies first. And then we also analyze the time complexity of our algorithm and compare it with that of gate-block selection algorithm.

#### **3.2.1 Definition of the Variables**

- $d_i$ : One bit of the data in the bit position *i*.

- $p_i$ : One bit of the parameter in the bit position *i*.

- *n*: The word length of the data. So the data is  $d_{n-1}d_{n-2}...d_1d_0$ .

- m: The number of unique data in the trace of the system. The unique data means that only one data are chosen from original data and the other duplicate data are discarded.

S: The set of unique data. So |S| = m.

- $B_i$ : Each data is divided into several blocks logically. The block  $B_i$  contains all data that are in the same position *i*.

- *bs*: The size of each block. The size of each block is two bits in this algorithm.

- *C<sub>i</sub>*: A set  $C_i = \{(0, c_0), (1, c_1), ..., (2^{bs} 1, c_{2^{bs}-1})\}$  contains several pairs for each *bs*-bit data block *B<sub>i</sub>*. The first element of the pair is the decimal representation of the *bs*-bit data in the block *B<sub>i</sub>*. The second element of the pair is the number of times the data appears in the data block *B<sub>i</sub>* of set *S*, which is relative to the first element of the pair.

- $g_{i_j}$ : A synthesized logic gate type of the parameter extractor in the *i*-th level and the position *j*.

An example of the synthesized parameter extractor is shown in Figure 3-1. This parameter extractor has two levels for n bits data. The level of the parameter extractor begins at one.

Figure 3-1 An example of the 2-level parameter extractor for the *n* bits data.

#### 3.2.2 Top Level of Local Grouping Algorithm

The top level of the local grouping algorithm is shown in Figure 3-2. In the lines 11 to 16, each 2-bit data block of all unique input data is analyzed and statistics gathered because we need the information to synthesize the proper parameter extractor. In the lines 18 to 21, the elements of the  $C_i$  of each block are sorted by the count of each decimal number in descending order. Then the sorted  $C_i$  is inputted into the *FindGate* function that will be introduced later. This function will output the proper type of the logic gate that can distribute the data block uniformly to one bit parameter. Then the output type is recorded. In the lines 23 to 29, if the level of the synthesized parameter extractor is that we want then the algorithm is finished. Otherwise, the new data are computed by the new generating gates and old data for next level. The other variables are also prepared for next level.

| 1  | Local Gr             | ouping Algorithm                                                                                |

|----|----------------------|-------------------------------------------------------------------------------------------------|

| 2  | Input:               |                                                                                                 |

| 3  | S:                   | The set of unique data.                                                                         |

| 4  | n:                   | The word length of data. So data is $d_{n-1}d_{n-2} \dots d_1d_0$ .                             |

| 5  | level:               | The number of levels of the parameter extractor that we want to                                 |

|    |                      | synthesize.                                                                                     |

| 6  | <b>Output</b> :      | The parameter extractor.                                                                        |

| 7  | Local va             | riable:                                                                                         |

| 8  | C <sub>i</sub> : Set | of counting pairs $\{(0, c_0), (1, c_1), (2, c_2), (3, c_3)\}$ for 2-bit block B <sub>i</sub> . |

|    | Initi                | al value of $c_0$ , $c_1$ , $c_2$ and $c_3$ is zero.                                            |

| 9  | li: The              | index of the level in the parameter extractor. Initial value is one.                            |

| 10 | {                    |                                                                                                 |

| 11 | for                  | all data $\in S$ {                                                                              |

| 12 |                      | <b>for</b> all 2-bit data block $d_{2i+1}d_{2i}$ , $i = 0$ to $\lfloor n/2 \rfloor - 1$ {       |

| 13 |                      | $j = decimal presentation of d_{2i+1}d_{2i};$                                                   |

| 14 |                      | $c_j = c_j + 1$ in the (j, $c_j$ ) of $C_i$ ;                                                   |

| 15 |                      | }                                                                                               |

| 16 | }                    |                                                                                                 |

| 17 |                      |                                                                                                 |

| 18 | for                  | $i = 0$ to $\lfloor n/2 \rfloor - 1 \{$                                                         |

| 19 |                      | Sort the elements $(0, c_0)$ , $(1, c_1)$ , $(2, c_2)$ and $(3, c_3)$ of $C_i$ in descending    |

|    |                      | order by $c_j$ , where $j \in \{0, 1, 2, 3\}$ ;                                                 |

| 20 |                      | $\textit{FindGate}$ (sorted $C_i$ ) and record the gate type in the li-th level and             |

|    |                      | i-th position of the parameter extractor;                                                       |

| 21 | }                    |                                                                                                 |

| 22 |                      |                                                                                                 |

| 23 | <b>if</b> ( ]        | li < level ) {                                                                                  |

| 24 |                      | Using the data set and the generating gates in the li-th level of the                           |

|    |                      | parameter extractor to compute the new data set and replace data set                            |

|    |                      | with the new data set;                                                                          |

| 25 |                      | n = word length of new data;                                                                    |

| 26 |                      | Initialize C <sub>i</sub> for new data; $//i = 0$ to $\lfloor n/2 \rfloor -1$                   |

| 27 |                      | li = li + 1;                                                                                    |

| 28 |                      | Goto line 11;                                                                                   |

| 29 | }                    |                                                                                                 |

| 30 | }                    | igure 3-2 The top level of the local grouping algorithm.                                        |

Figure 3-2 The top level of the local grouping algorithm.

### **3.2.3 Grouping Function**