Graduate Institute of Communication Engineering College of Electrical Engineering & Computer Science National Taiwan University Master Thesis

毫米波多埠切换器與功率放大器之研製

Design of Millimeter-Wave Multiple-Port Switches and

指導教授: 王暉 博士

Advisor: Huei Wang, Ph.D.

中華民國 98 年 6 月

June, 2009

電 國

信工 立

程研 灣

究 大

所 學

碩士論

文

毫米波多埠切換器與功率放大器之研製

賴 瑞

彬

撰

98 6

臺

# 國立臺灣大學碩士學位論文 口試委員會審定書

毫米波多埠切换器與功率放大器之研製

## Design of Millimeter-Wave Multiple-Port Switches and Power Amplifier

本論文係 賴瑞彬 君 (R96942008) 在國立臺灣大學電信工程學 研究所、所完成之碩士學位論文,於民國九十八年六月二十七日承下 列考試委員審查通過及口試及格,特此證明

口試委員:

EPE (簽名) (指導教授)

时客城 驾长表标

Fret 15

T\_ 10 \$

影你敬

(簽名)

系主任、所長

### 致謝

能夠完成這本論文,首先我要感謝我的指導教授,王暉老師。自大三下修了王老師的專題研究,至今共三年半的時間,我在王老師身上學到的不只是專業知識,更重要的是待人處 世以及解決問題該有的方法與態度。除了在王老師身上學到的東西,也很感謝王老師一直以 來給我機會參加研究、推薦我參加各種獎項,讓我在精神與生活上都能夠得到肯定與幫助。

同時要感謝的是,在我剛進入這個實驗室,給我指導良多的蔡作敏博士。蔡博士在學術上的熱忱、對實驗室的奉獻、個性上的耿直、對學問深入思索的態度,一直是我學習的榜樣。 無論如何,蔡學長等同是我在研究上的啟蒙導師,我對他有無限的感激。

接著感謝我的口試委員,林坤佑教授、蔡作敏博士、張志揚教授、陳咨吰博士,感謝你們在口試時提醒我的不足之處,以及讓我深入思考研究上沒注意到的問題,使本論文得以更加完善。

此外我要感謝這個實驗室的同仁,包含了許多學長、同學。感謝陳重均學長,背負著畢 業壓力,卻還是給我支援、協助我量測,在我不知所措時告訴我要把事情一件件完成。感謝 趙世峰學長,沒有學長的幫助以及校稿,我無法完成多埠切換器的論文。感謝小郭(哲嘉)學 長,學長總是很有條理的安排著和我量測的事情,讓我能夠如期的完成論文的進度。感謝紅 郭(京霖)學長,學長總是很熱忱的幫助別人,用心思考別人遇到的問題,在量測上也不遺餘 力的奉獻自己的時間給別人。感謝李杰穎學長,帶我進入這個實驗室,開始了我的研究生涯。 感謝野口(陳仲豪),和我一起進入這個實驗室,當初我們一起探索這個新世界。感謝我的實 驗室同學好夥伴,超哥(林介安)、SOSO(高堃堯)、鄭伊佐、鬆餅(紀秉松)、冠哥(林士凱)、蔡 宜倩、呂彥儒,我們一起經歷了這兩年研究與修課的歲月。也感謝其他電波組的好夥伴,我 們時常一起打球、一起分享電波組的八卦及生活點滴,白羊(莊皓翔)、星星憨(楊星瀚)、藍洵、 貓哥(謝易展)、豪哥(張家豪)、蕭偉成、香派(白英碩)、王澤宇、紀凱程。還要感謝辛苦的網 管,陳君朋學長,在我人生感到迷惑時給我提點。還有已經畢業的實驗室學長姐,小雷(雷明峰)、吳佩熹、老江(江昱嫺)。一起去亞特蘭大開會以及遊走東京的郭爸(哲均)、航航(翁榆航)、 爽年(任勇年)、黃智宇。感謝我的大學同學,無論在我傷心難過或是快樂時都給我支持,留 級(劉佶)、小黃(翊鑫)、江媽(怡萱)、老大(王尚平)、海參(陳凱昇)、中國風(鐘國峰)、阿冗(曾 鈺翔)、阿土(陳祥麟)。

還有我要感謝提供我在生活以及求學上補助的單位,陳安泰醫師在研究上給予我的肯 定,行天宮在我碩二以後提供我定期的補助,讓我減輕在外租屋生活的壓力。細數之下,我 要感謝的的人真的是太多了。

最後,我要感謝我的家人,感謝我的父母,在求學路上一直給予我支持,我常常因為壓 力而在家庭產生負面的情緒,想想我真不是一個好孩子,總讓您們包容我;也感謝我的兩位 兄長,有你們在,我才能安心的離開父母在外求學。

我還是得要感謝一個人,好燙(皓棠),從大學到研究所,一共陪我經歷了四年的歲月。 曾經,我們一起成長、一起歡笑、一起難過,我不是個成熟的人,總是讓妳受到委屈;感謝 妳這四年的包容,因為有妳在,讓我安心地朝自己的目標前進,因為有妳,讓我在人生感到 徬徨時而變得積極,也在我因為投入研究而與外界隔絕時還是陪在我身邊,雖然遺憾的是我 們沒能夠走完這段路。希望我們再見面時,我們都能更加懂得愛與珍惜。

ii

### 中文摘要

本論文包含毫米波單刀雙擲切換器、多埠切換器與中等功率放大器的研究。

本論文的第一部分說明射頻切換器的基本概念,進而展示兩個使用互補式金屬氧化半導 體(CMOS)製程的毫米波單刀雙擲切換器。這兩個毫米波單刀雙擲切換器是使用濾波器整合的 方式來設計。使用濾波器的方式來設計,不但可使切換器的濾波效果更顯著,也可以提升阻 抗匹配以及較好的隔離度。使用互補式金屬氧化半導體製程是現今整合系統於晶片上的趨 勢。本論文中的第一個單刀雙擲切換器使用65奈米CMOS製程,在40到80 GHz的頻率之間, 其置入損耗的量測值在3至5 dB之間,而隔離度則優於20 dB。另一個單刀雙擲切換器係使用 90奈米的CMOS製程製作,在60到110 GHz的頻率之間,其置入損耗的量測值在3至4 dB之間, 而隔離度則優於25 dB;就我們所知,後者是目前最高頻的CMOS切換器。

本論文的第二部份提出一個方法去分析毫米波多埠切換器的架構。這個分析方法是將多 埠切換器架構中的通道路徑做一個簡化模型來做數學分析,而此簡化模型也適用於分析任一 種多埠切換器架構。本論文實現了兩個使用砷化鎵高速場效電晶體(GaAs HEMT) 60 GHz的多 埠切換器來驗證此分析方法。實驗結果與分析相當吻合。

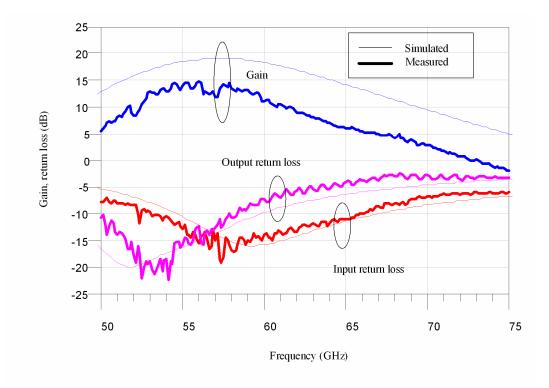

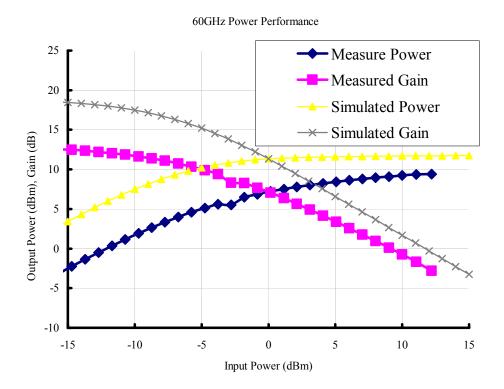

第三部份首先介紹微波功率放大器的基本設計步驟,然後研製了一個使用65奈米CMOS 的60 GHz 中等功率放大器。此60 GHz功率放大器的最高增益為14.5 dB而飽和功率則為9.5 dBm.

iii

### Abstract

This thesis includes the design of millimeter-wave SPDT switches, multiple-port switches, and a medium power amplifier.

The first part of the thesis focuses on the basics about how to design RF switches, and then demonstrates two MMW SPDT switches in CMOS process. These two MMW SPDT switches were designed by filter-integrated method. To integrate a switch with filter response can get sharper frequency response and enhance isolation. The CMOS process was adopted since the system on chip (SoC) is a trend in CMOS. One SPDT switch was designed in 65 nm CMOS, and it has an insertion loss about 3-4.5 dB and an isolation better than 20 dB in 40-80 GHz. The other SPDT switch was designed in 90 nm CMOS, and it has an insertion loss of 3-4 dB and isolation better than 25 dB in 60-110 GHz. To our knowledge, it is the highest frequency CMOS MMIC switch.

The second part presents a new method to analyze the topology of MMW multiple-port switches. The proposed method is suitable to analyze arbitrary multiple-port switch topology. This method is based on a simplified model of a through path of a multiple-port switch topology. Two 60 GHz multiple-port switches in GaAs HEMT process are demonstrated to verify this analysis. Good agreement with the analysis and the measured results are achieved.

The third part presents a 60-GHz medium power amplifier in 65 nm CMOS process. This PA demonstrates a peak gain of 14.5 dB and saturation power of 9.5 dBm.

### Contents

| Chapter 1 Introduction                                                      | 1   |

|-----------------------------------------------------------------------------|-----|

| 1.1 Motivation                                                              | 1   |

| 1.2 Literature Survey                                                       | 2   |

| 1.2.1 Radio Frequency Switches                                              | 2   |

| 1.2.2 Millimeter-Wave Power Amplifiers                                      | 4   |

| 1.3 Contributions                                                           | 4   |

| 1.4 Organization of the Thesis                                              | 6   |

| Chapter 2 Basics of Radio Frequency Switches                                | 8   |

| 2.1 Introduction                                                            | 8   |

| 2.2 Series-Shunt Switches                                                   | .10 |

| 2.3 Resonant-type Switches                                                  | 12  |

| 2.4 Distributed Switches                                                    | .14 |

| Chapter 3 Millimeter-Wave Filter-Integrated SPDT Switch                     | .16 |

| 3.1 Introduction                                                            | .16 |

| 3.2 Basic Concepts of Filter-Integrated Switches                            | 16  |

| 3.2.1 Synthesis of Microwave Filters                                        | .16 |

| 3.2.2 Transmission Line Integrated Filters                                  | 19  |

| 3.2.3 Filter-Integrated Switches                                            | 21  |

| 3.3 Circuit Implementation of V-band Filter-Integrated SPDT Switch in 65 nm |     |

| CMOS Process                                                                | 22  |

| 3.4 Experimental Results of V-Band SPDT Switch in 65 nm CMOS                | .30 |

| 3.5 Circuit Implementation of 60 to 110 GHz SPDT Switch in 90 nm CMOS       | .35 |

| 3.6 Experimental Results of 60 to 110 GHz SPDT Switch in 90 nm CMOS         | 38  |

| 3.7         | Summary                                                             |    |

|-------------|---------------------------------------------------------------------|----|

| Chapter 4   | Topology Analysis of Millimeter -Wave Multiple-Port Switches        | 44 |

| 4.1         | Introduction                                                        | 44 |

| 4.2         | Introduction to Different Type Multiple-Port Topologies             | 45 |

| 4.3         | Analytical Derivation of Insertion Loss of Multiple-Port Topologies | 46 |

| 4.4         | Analytical Derivation of Bandwidth of Multiple-Port Topologies      | 54 |

| 4.5         | Isolations of Multiple-Port Topologies                              | 57 |

| 4.6         | Summary of Topology Analysis                                        | 57 |

| Chapter 5   | Design of Millimeter-Wave Multiple-Port Switches                    | 59 |

| 5.1         | Introduction to MMIC Process                                        |    |

| 5.2         | Design of Unit Switch Cells                                         | 60 |

| 5.3         | Millimeter-Wave Multiple-Port Switches Design                       |    |

| 5.4         | Experimental Results                                                | 65 |

| 5.5         | Summary of Multiple-Port Switches                                   |    |

| Chapter 6   | V-band Medium Power Amplifier                                       | 76 |

| 6.1         | Introduction                                                        |    |

| 6.2         | Basic Concepts of Power Amplifiers                                  | 77 |

| 6.3         | Design of V-band Medium Power Amplifier                             | 79 |

| 6.4         | Experimental Results                                                | 84 |

| 6.5         | Summary                                                             | 88 |

| Chapter 7   | Conclusions                                                         | 90 |

| References  |                                                                     | 91 |

| Publication | ı List                                                              | 97 |

# **List of Figures**

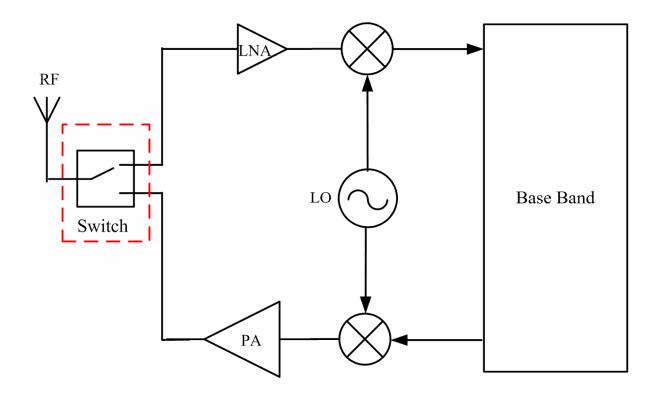

| Fig. 2.1. Typical BPSK RF transceiver.                           | 9  |

|------------------------------------------------------------------|----|

| Fig. 2.2. A SPDT switch terminated with $Z_0$                    | 9  |

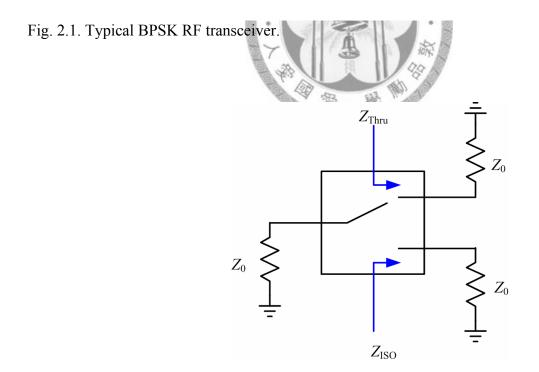

| Fig. 2.3. Series switch and its equivalent circuit               | 11 |

| Fig. 2.4. Shunt switch and its equivalent circuit.               | 11 |

| Fig. 2.5. A series-shunt switch, and its equivalent circuit.     | 12 |

| Fig. 2.6. Shunt type of a parallel resonator using a transistor. | 13 |

| Fig. 2.7. Series type of a parallel resonator using a transistor | 13 |

| Fig. 2.8. A distributed switch and its equivalent circuit.       | 15 |

|                                                                  |    |

| Fig. 3.1. Basic prototypes of low pass filters. (a) Prototype beginning with a shunt element. (b)      |

|--------------------------------------------------------------------------------------------------------|

| Prototype beginning with a series element                                                              |

| Fig. 3.2. A band pass filter composed of quarter-wavelength transmission lines                         |

| Fig. 3.3. Equivalent circuit of a shunt quarter-wavelength transmission line, it can be further        |

| synthesized with an off-state transistor                                                               |

| Fig. 3.4. Equivalent circuit of a series quarter-wavelength transmission line                          |

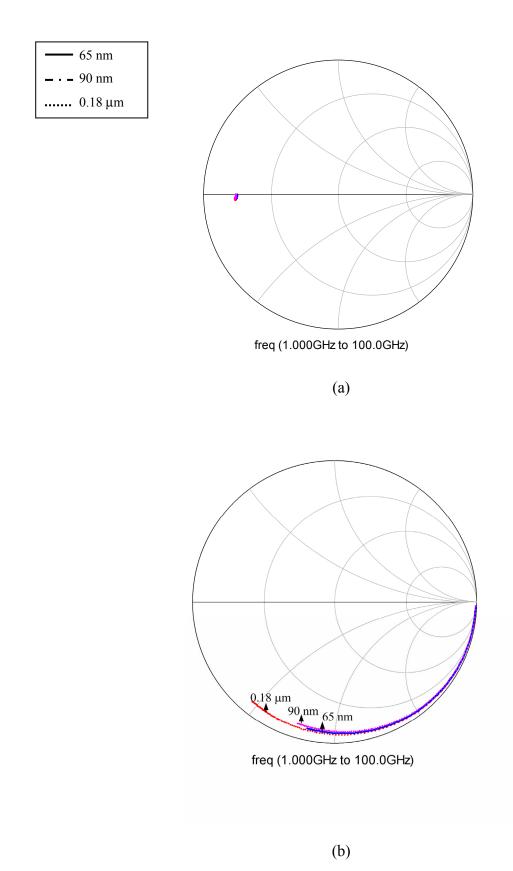

| Fig. 3.5. (a) The input impedance of on-state transistors for 0.18 $\mu$ m, 90 nm, and 65 nm CMOS. (b) |

| The input impedance of on-state transistors for 0.18 $\mu$ m, 90 nm, and 65 nm CMOS24                  |

| Fig. 3.6. Circuit schematic of a 60-GHz SPDT switch                                                    |

| Fig. 3.7. (a) The simplified model of a shunt off-state MOSFET. (b) The simplified model of a shunt    |

| off-state MOSFET without body-floating. (c) The simplified model of a shunt off-state MOSFET           |

| with body-floating                                                                                     |

| Fig. 3.8. The impedance of a passive NMOS in 65 nm CMOS. (a) On-state passive NMOS. (b)                |

| Off-state passive NMOS.                                                                |                   |

|----------------------------------------------------------------------------------------|-------------------|

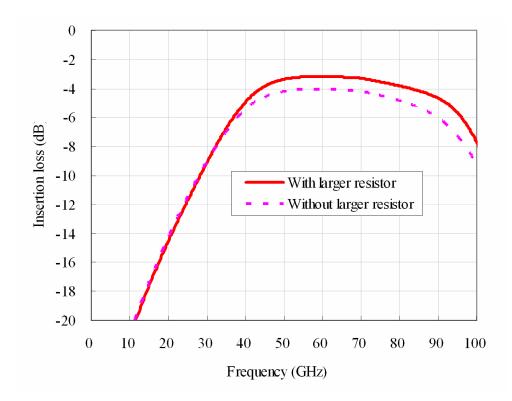

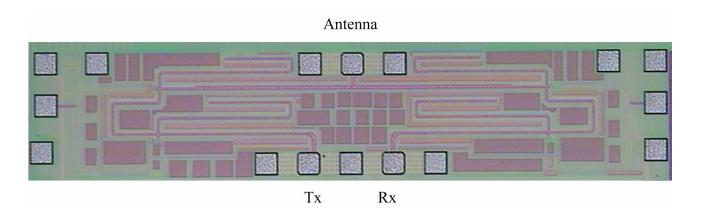

| Fig. 3.9. Simulated with and without large resistor between source and body. (a) In    | sertion loss, (b) |

| isolation                                                                              | 29                |

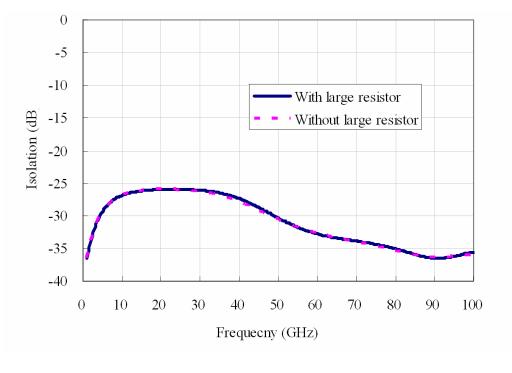

| Fig. 3.10. The chip photo of 60-GHz SPDT filter-integrated switch. The chip size is    | 1500 µm x 250     |

| μm.                                                                                    | 30                |

| Fig. 3.11. Simulated and measured insertion loss of 60-GHz SPDT switch                 | 32                |

| Fig. 3.12. Simulated and measured return loss of 60-GHz SPDT switch                    | 32                |

| Fig. 3.13. Simulated and measured isolation of SPDT switch                             |                   |

| Fig. 3.14. Measured insertion loss versus input power.                                 |                   |

| Fig. 3.15. Measured isolation versus input power                                       |                   |

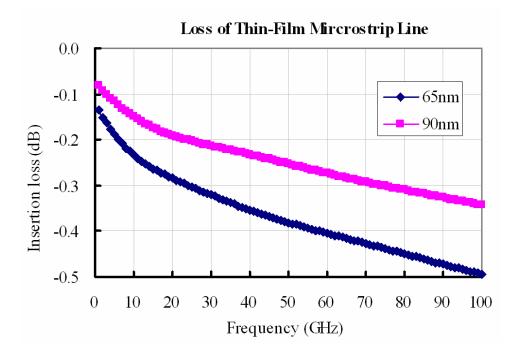

| Fig. 3.16. Comparison of the loss of thin-film microstrip lines in 65 nm CMOS and      | 90 nm CMOS.       |

| X X                                                                                    | 35                |

| Fig. 3.17. The impedance of a passive NMOS in 90 nm CMOS. (a) On-state pass            | ive NMOS. (b)     |

| Off-state passive NMOS.                                                                |                   |

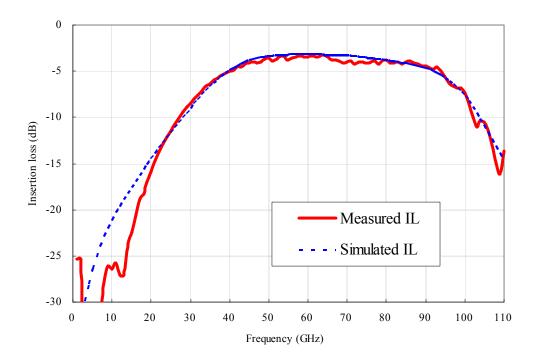

| Fig. 3.18. The chip photo of the 60-110 GHz SPDT switch with a size of 400 $\mu$ m x 7 | 50 µm38           |

| Fig. 3.19. Simulated and measured insertion loss of 60-110 GHz SPDT switch             | 40                |

| Fig. 3.20. Simulated and measured return loss of 60-110 GHz SPDT switch.               | 40                |

| Fig. 3.21. Simulated and measured isolation of 60-110 GHz SPDT switch.                 | 41                |

| Fig. 3.22. Measured power performance at 75 GHz of 60-110 GHz SPDT switch              | 41                |

|                                                                                        |                   |

| Fig. 4.1. Four types of multiple-port switch topology. (a) Binary-tree type. (b) Matt  | ix type. (c) Net  |

| e                |                 |                | 1           | 0, ()         | 2          |               | 21           |         |

|------------------|-----------------|----------------|-------------|---------------|------------|---------------|--------------|---------|

| type. (d) Rin    | g-binary type.  |                |             |               |            |               |              | 48      |

| Fig. 4.2. (a)    | Block diagran   | n for the on s | tate of the | e unit switc  | eh. (b) Ec | uivalent-ci   | rcuit model  | for the |

| off state of the | he unit switch. |                |             |               |            |               |              | 49      |

| Fig. 4.3 Equ     | ivalent circuit | models of a t  | hrough pa   | th for: (a) b | oinary-tre | e type, (b) i | matrix type, | (c) net |

| type, and (d) ring-binary type.                                               | 51 |

|-------------------------------------------------------------------------------|----|

| Fig. 4.4. Calculated frequency responses with respect to different topologies |    |

| rig. 4.4. Calculated nequency responses with respect to uniferent topologies  |    |

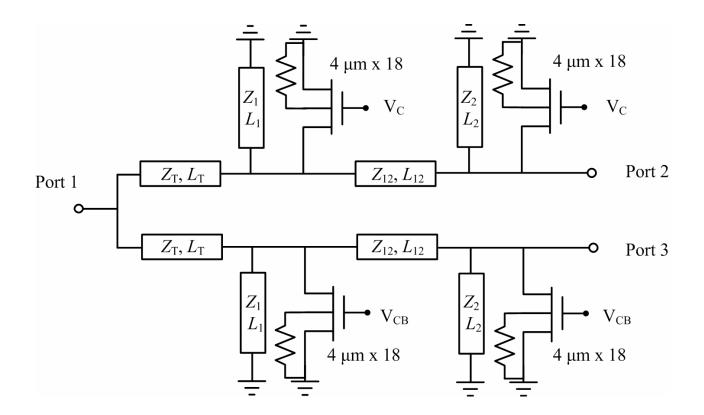

| Fig. 5.1. Circuit schematic of a distributed unit switch                                                  |

|-----------------------------------------------------------------------------------------------------------|

| Fig. 5.2. Circuit schematic of a filter-integrated unit switch                                            |

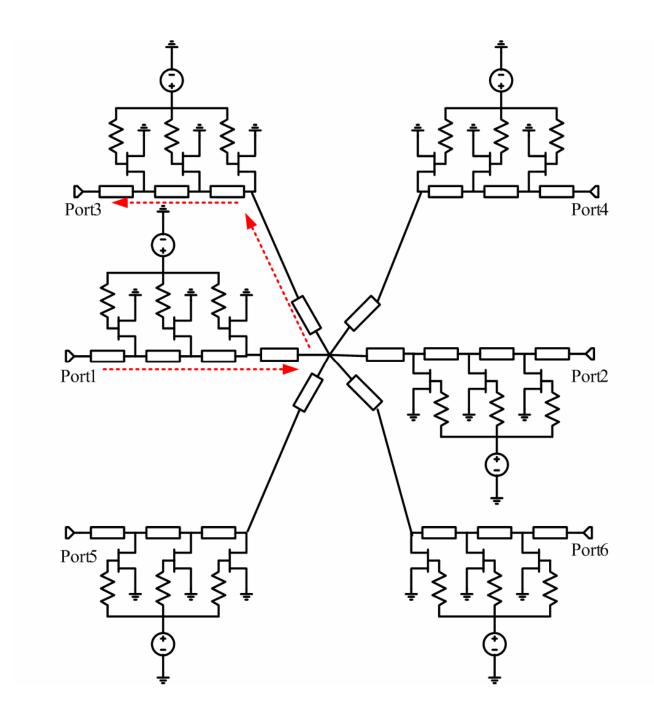

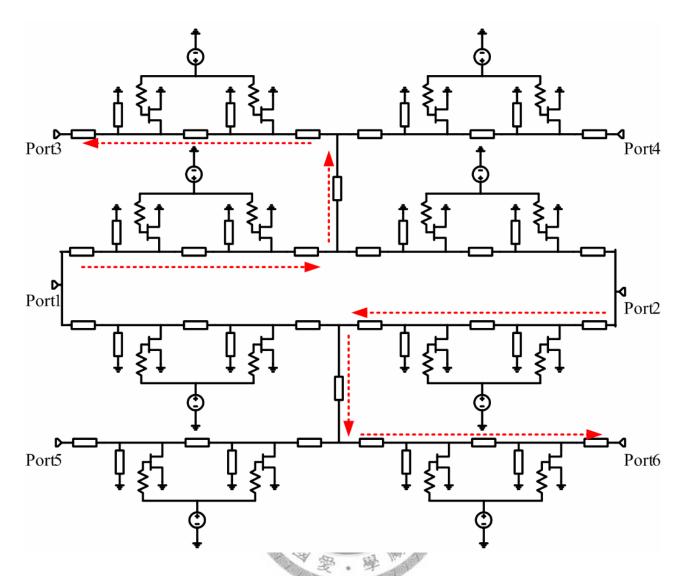

| Fig. 5.3. Schematic of MMW multiple-port switches: net-type topology based on distributed                 |

| switches                                                                                                  |

| Fig. 5.4. Schematic of MMW multiple-port switches: binary-ring topology based on filter-integrated        |

| switches                                                                                                  |

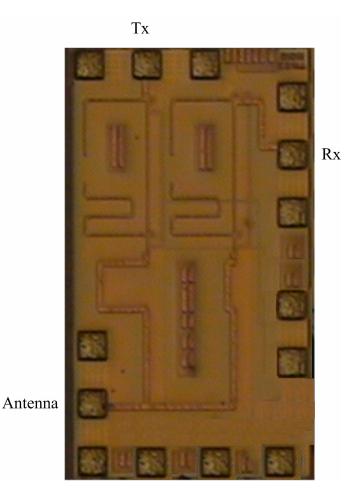

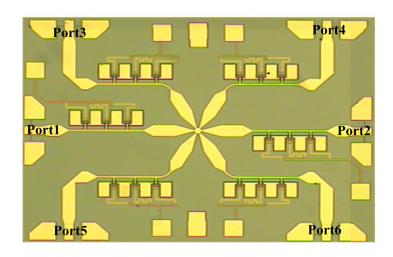

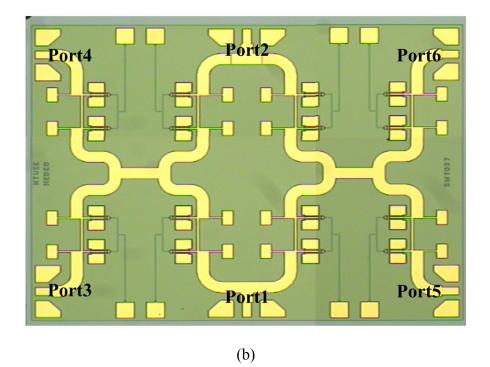

| Fig. 5.5. Chip photograph of the six-port switches. (a) Net-type topology with a size of $2.0 \times 1.5$ |

| mm <sup>2</sup> . (b) Ring-binary topology with a size of $2.5 \times 2.0 \text{ mm}^2$                   |

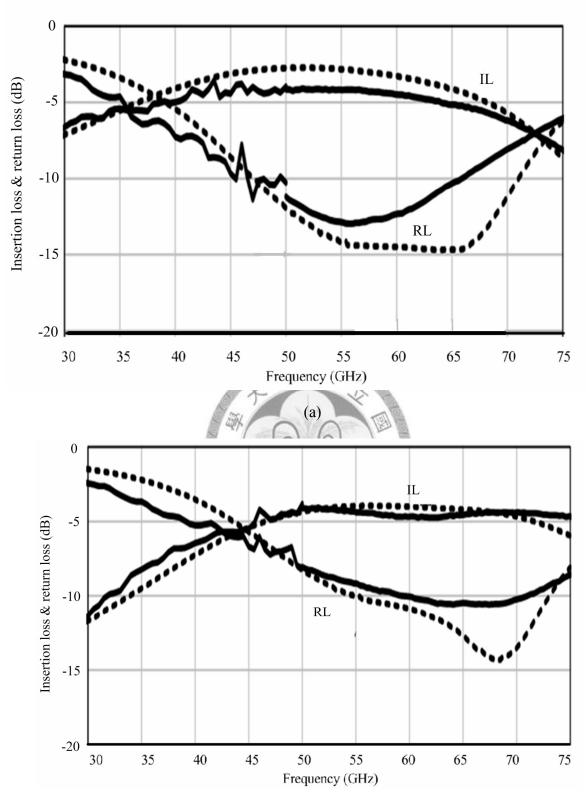

| Fig. 5.6. The net type multiple-port switch: (a) simulated and measured results of the insertion loss     |

| and return loss when port3 and port1 are on, (b) simulated and measured results of the insertion loss     |

| and return loss when port4 and port1 are on, and (c) measured results of port to port isolations70        |

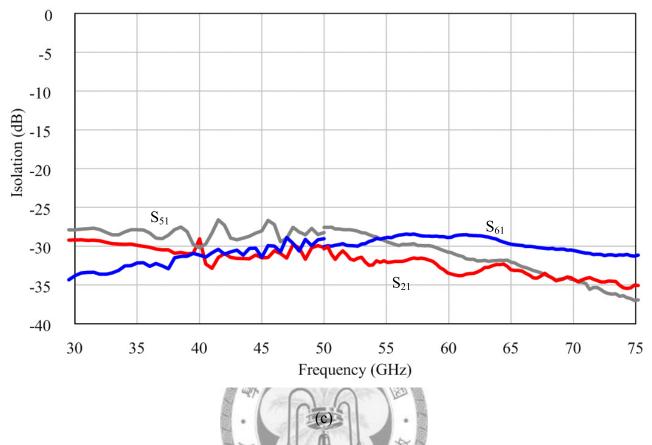

| Fig. 5.7 Simulated and measured of the ring-binary type multiple-port switch. (a) Insertion loss, (b)     |

| input /output return losses, and (c) port to port isolations                                              |

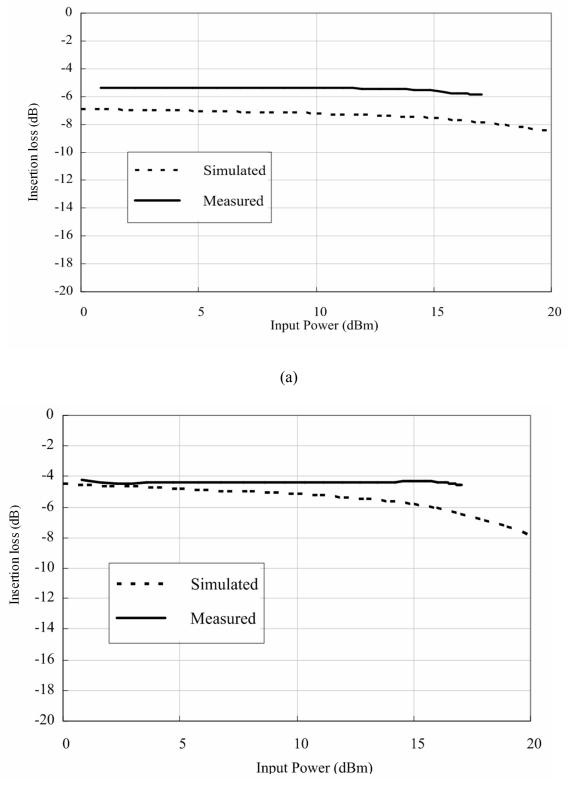

| Fig. 5.8. Simulated and measured insertion loss versus input power at 60 GHz of (a) net-type              |

| multiple-port switch, and (b) ring-binary multiple-port switch                                            |

| Fig. 6.1. Two-port microwave network                                                                    | 77     |

|---------------------------------------------------------------------------------------------------------|--------|

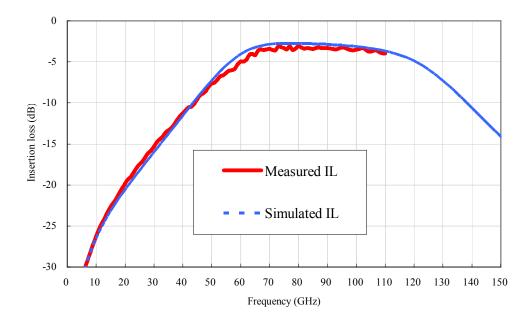

| Fig. 6.2. Simulated insertion loss of the thin-film microstrip line with length of 500 $\mu$ r          | n and  |

| characteristic impedance of 50 ohm                                                                      | 80     |

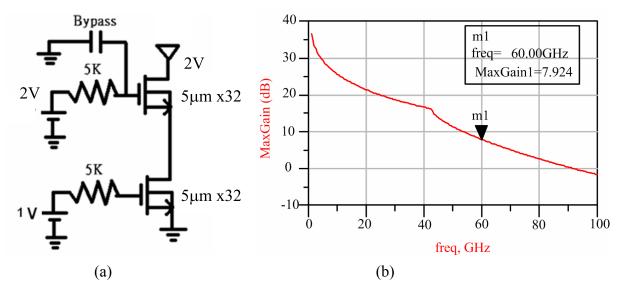

| Fig. 6.3. Circuit schematic of the 60-GHz PA.                                                           | 82     |

| Fig. 6.4. Device selection of output stage. (a) Output stage structure, and (b) $G_{\text{max}}$ of the | output |

| stage                                                                                                   | 83     |

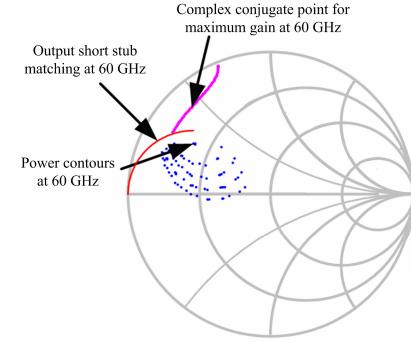

| Fig. | 6.5. Po | ower contours, complex conjugate point, and output short stub matching at 60 GHz83          |

|------|---------|---------------------------------------------------------------------------------------------|

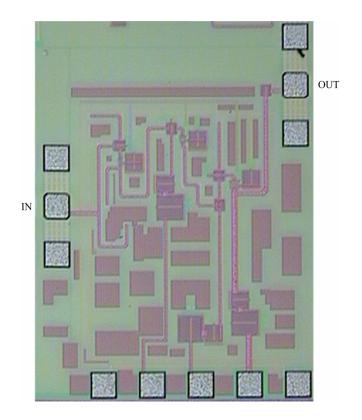

| Fig. | 6.6. C  | Thip photo of 60-GHz power amplifier. It is with a size of 550 $\mu$ m $\times$ 640 $\mu$ m |

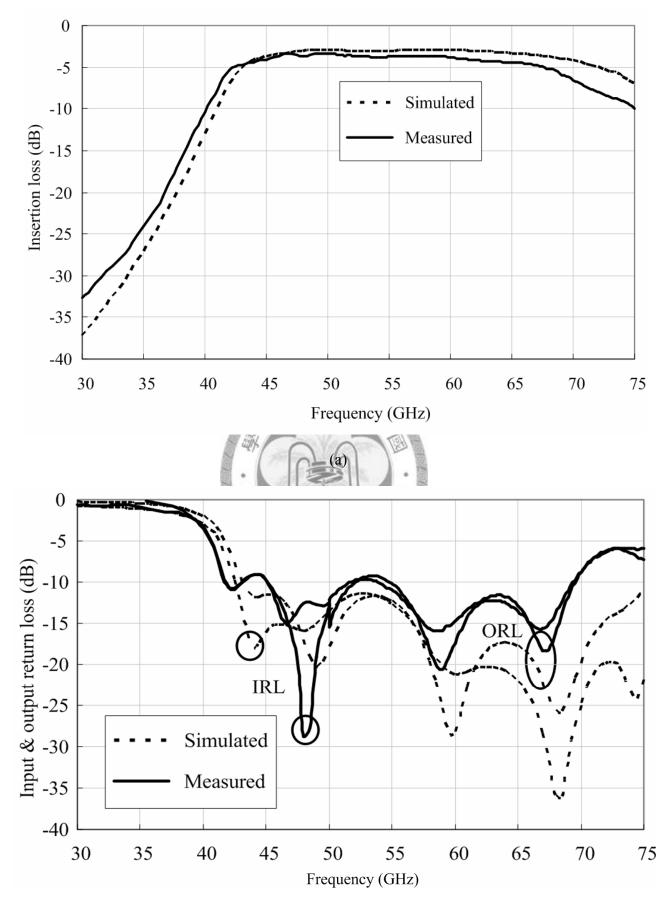

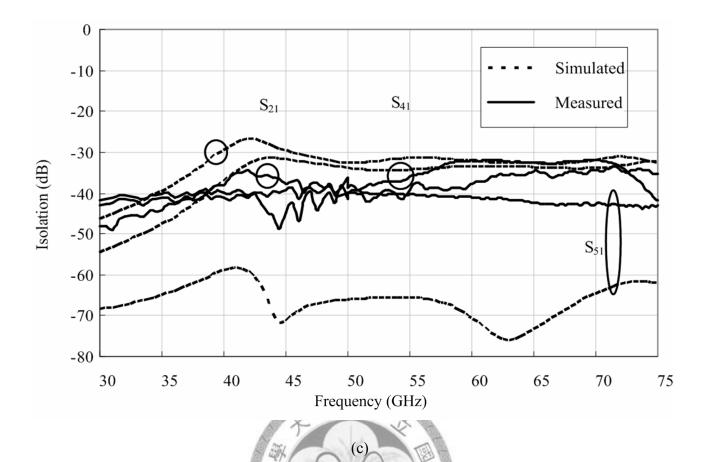

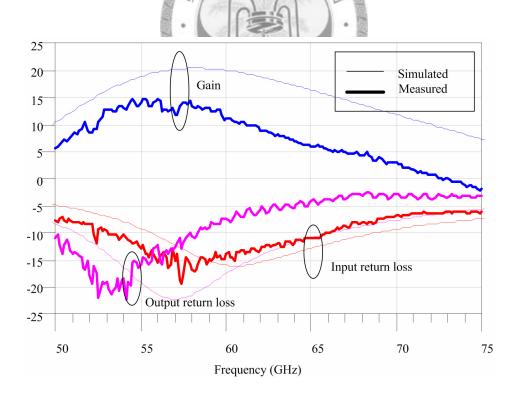

| Fig. | 6.7. Si | imulated and measured S-parameters of 60-GHz PA                                             |

| Fig. | 6.8. R  | e-simulated and measured S-parameters of the 60-GHz PA                                      |

| Fig. | 6.9. R  | e-simulated and measured power performance of 60-GHz power amplifier                        |

# **List of Tables**

| Table 1.1   | Summary of the performance and features for previously reported passive HEMT |

|-------------|------------------------------------------------------------------------------|

| MMIC switch | es                                                                           |

| Table 1.2   | Summary of the performance of reported 60-GHz power amplifier in CMOS        |

| process     |                                                                              |

| Table 3.1   | Summary of the performance of reported switches in CMOS process              |

| Table 4.1   | Summary of different multiple-port switch topology                           |

| Table 5.1   | Summary of the performace and features for previously reported passive HEMT  |

| MMIC switch | es and this work                                                             |

| Table 6.1   | Summary of the performance of reported 60-GHz power amplifier in CMOS        |

| process     |                                                                              |

## **Chapter 1 Introduction**

### **1.1 Motivation**

The developments of millimeter-wave communication systems have increased rapidly in recent years. To realize the wider bandwidth and higher data rate, performance of components of the RF front end should be enhanced as well. Switches control the signal path of wireless transceivers and should have enough power handling to transmit the output power from the power amplifier to transmission channel. Besides, to integrate a system on chip (SoC), the design using CMOS process is a trend. Therefore, the design of power amplifier in CMOS is also an important topic.

A beamformer system using multiple antennas both at the transmitter and receiver can improve the efficiency of the spectrum greatly by spatial multiplexing [17]–[20]. In a beamformer system, the design of the multiple-port switch is important.

Power amplifiers using GaAs HEMTs can achieve high performance, but it is difficult to integrate GaAs-based components with baseband circuits. Higher-level integration of wireless transceiver is a trend. CMOS process is suitable and high-level integration on chip. However, nanometer CMOS with lower breakdown voltage causes the poor power handling capability of the device.

Researches about multiple-port switches and CMOS power amplifiers are conducted in this thesis.

### **1.2 Literature Survey**

This literature surveys including radio frequency switches and MMW power amplifiers.

#### **1.2.1 Radio Frequency Switches**

RF switches are important components in the wireless communication systems. To design RF switches below 20 GHz, the series or series shunt switches [21] are suitable. Besides, power performance of RF switches are important, since the RF switches should have enough power handling capability to transmit the signal from power amplifiers. In higher frequency, the output power of power amplifiers is usually below 20 dBm, and hence, the power performance of MMW switches is not difficult to achieve.

To achieve the design around 20 GHz, one might use inductors to cancel the parasitic capacitance at desired frequency, but it also leads to a narrow band characteristics. Switches using traveling concept can achieve broadband characteristics [25]. Switches using impedance transformation technique [27] can achieve better isolations, but they cause more insertion loss, and the more insertion loss will make the noise figure of receivers increase and attenuate the output power of transmitters. Filter-integrated switches [31]-[32] can achieve better performances such as better return losses, isolations, and sideband rejection for the undesired bands.

#### Table 1.1

#### SUMMARY OF THE PERFORMANCE AND FEATURES FOR PREVIOUSLY REPORTED PASSIVE

| Technology | Design              | Frequency | Insertion  | Isolation | I/O           | Ref. |

|------------|---------------------|-----------|------------|-----------|---------------|------|

|            | Approach            | (GHz)     | Loss (dB)  | (dB)      |               |      |

| HEMT       | Resonant, series    | 94        | 1.6        | 22.5      | SPST          | [28] |

| HEMT       | Resonant, series    | 55~63     | < 3.2      | >23       | SPDT          | [29] |

| HJFET      | Series resonant,    | 57~61     | 3.9 ~ 5    | >30       | SPDT          | [30] |

|            | shunt               |           |            |           |               |      |

| HEMT       | $\lambda/4$ , shunt | 42~46     | < 1.6      | >30       | SPDT          | [33] |

| HEMT       | Impedance           | 53~61     | <4         | >30       | SPDT          | [27] |

|            | transformation      | A.        | A LE       |           |               |      |

|            | network, shunt      | ·         | SA         | 101010    |               |      |

| HEMT       | Traveling wave      | 70~102    | 3.9 ~ 5.5  | >30       | SPQT          | [34] |

|            | concept             | THE RE    | · # [11] & | Ser.      |               |      |

| HEMT       | Series              | 1~6       | 1.2 ~ 1.7  | >20       | Multiple-port | [39] |

| HEMT       | Filter-integrated   | 38 ~ 42   | < 4        | >25       | Multiple-port | [43] |

#### HEMT MMIC SWITCHES

Table 1.1 summarizes the previously reported performances and features of passive MMIC HEMT switches. There are few researches about multiple-port switches 10 GHz [39], because the simply shunt-series switch cell can still function well in this frequency range. To design MMW multiple-port switches, there are many constraints due to the high frequency characteristics. Resonant-type SPDT switch shows a narrow band in the *V*-band [29], and another SPDT switch shows an insertion loss of 4 dB [30].

#### **1.2.2 Millimeter-Wave Power Amplifiers**

CMOS power amplifier is a hot research topic in these years since it is still the bottleneck for the integration of a wireless transceiver. In past years, people use GaAs process to achieve high power performance in MMW frequency. Compared with GaAs process, the higher loss on silicon substrate, low supply voltage, and poor power handling capability make the design of power amplifier in CMOS a big challenge. Besides, the behavior of passive elements in CMOS process cannot be predicted precisely. The reported 60-GHz power amplifiers are summarized in table 1.2. Power amplifiers in [48] and [50] show poor gain and the poor gain will make the power amplifiers difficult be used in practical wireless transceivers. The power amplifier in [51] has a gain less than 10 dB regardless of an output power of 10 dBm. The power amplifier in [52] has a gain better than 10 dB but only has an output power of 6 dBm. Power amplifiers in [54] and [55] both shows a gain better than 20 dB and a saturation power better than 10 dBm, but theses two power amplifiers consume a great quantity of power.

### **1.3 Contributions**

In this thesis, the first filter-integrated SPDT switch using CMOS process is implemented. The high insertion loss due to silicon substrate is the challenge in the design of CMOS switches. A 60-GHz SPDT FIS in 65 nm CMOS process is implemented first and it has a size of 0.25 mm by 1.5 mm. This SPDT switch has an insertion loss of 3 dB at 60 GHz, and its isolation is about 23 dB. Furthermore, a 60 to 110 GHz SPDT FIS in 90 nm CMOS is also demonstrated. It has an insertion loss less than 4 dB and an isolation better than 25 dB in 60-110 GHz.

#### Table 1.2

PROCESS

| Process | Topology   | DC         | V <sub>ds</sub> | Frequency  | Power | Saturation | Ref. |

|---------|------------|------------|-----------------|------------|-------|------------|------|

|         |            | Biasing    |                 | (GHz)      | Gain  | Power(dBm) |      |

|         |            |            |                 |            | (dB)  |            |      |

| 65 nm   | 1-stage,   | 23mA,      | 1V              | 62         | 4.5   | 9          | [48] |

| CMOS    | CS         | 1.2V       |                 |            |       |            |      |

| 90 nm   | 3-stage,   | 26.5mA,    | 1.5V            | 60         | 4.7   | 9.3        | [50] |

| CMOS    | CS         | 1.5V       |                 | tim film a |       |            |      |

| 90 nm   | 2-stage,   | 23mA,      | 1V              | 57         | 9.8   | 10         | [51] |

| CMOS    | CS         | 1 <b>V</b> |                 |            |       |            |      |

| 90 nm   | 2-stage    | 30mA,      | 1.5V            | 60         | 14    | 6          | [52] |

| CMOS    | CC,        | 1.5V       | CIT'            | 8 I 7      | 款     |            |      |

|         | 1-stage CS |            | 國愛              | · # 10     |       |            |      |

| 90 nm   | 3-stage    | 100 mA,    | 0.9V            | 60         | 30    | 13.8       | [54] |

| CMOS    | cascode    | 1.8V       |                 |            |       |            |      |

| 90 nm   | DAT        | 153 mA,    | 0.9V            | 60         | 26    | 14.5       | [55] |

| CMOS    | combing +  | 1.8V       |                 |            |       |            |      |

|         | 3-stage,   |            |                 |            |       |            |      |

|         | cascode    |            |                 |            |       |            |      |

SUMMARY OF THE PERFORMANCE OF REPORTED 60-GHZ POWER AMPLIFIER IN CMOS

The second part of this thesis is the topic of topology analysis and design of multiple-port switches in GaAs PHEMTs. GaAs HEMTs have good power handling capability and the loss of GaAs substrate is relatively lower than CMOS process, and therefore, GaAs HEMTs are suitable to

be used for the multiple-port switch. An approach to analyze arbitrary topologies of multiple-port switch is proposed, and an analytic expression of the insertion loss, isolation, and bandwidth of each topology can be derived by this proposed approach. In this thesis, two multiple-port switches are demonstrated. The first one is composed of distributed switch cells, and the other is composed of filter-integrated switch cells. The cell based on the distributed type should have wider bandwidth than filter-integrated switch cells. However, from the experimental results, the multiple-port topology using filter-integrated switch cells has wider bandwidth than the multiple-port topology using distributed type. This can also validate the proposed analysis. The proposed analysis makes the conclusion that the limitation of multiple-port switches is determined by its topology, since the limitation of the topology of the multiple-port switch with distributed switch cells has narrower bandwidth. Two designs are presented in this thesis. The first multiple-port switch is formed by the net type topology and based on distributed switch cells. It has a size of 2.0 mm by 1.5 mm. The insertion loss is about 4-5 dB in 48-65 GHz, and its isolation is better than 25 dB. The other multiple-port switch is formed by the ring-binary topology and based on filter-integrated switch cells. It has a size of 2.5 mm by 2.0 mm. The insertion loss is about 3-4.5 dB in 43-66 GHz, and its isolation is better than 30 dB. Both multiple-port switches have input  $P_{1dB}$  better than 17 dBm due to the limitation of our power source under measurement.

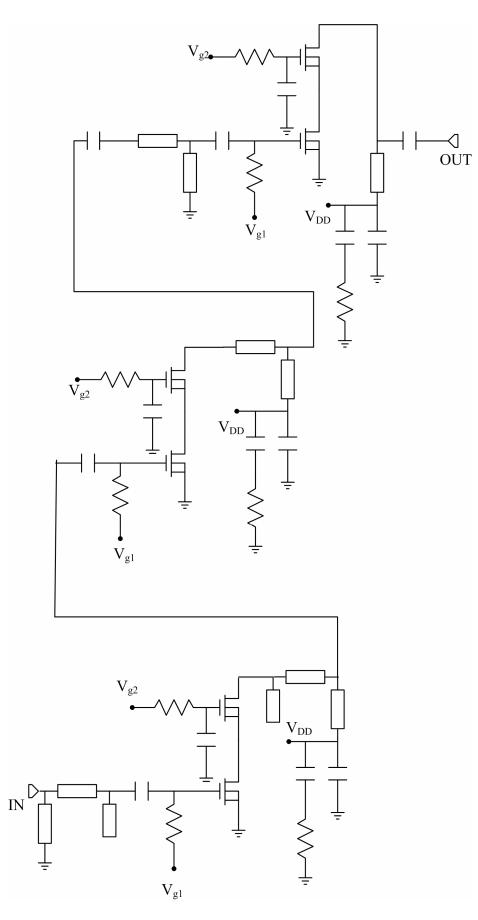

The third part is a 60 GHz power amplifier in 65 nm CMOS process. This power amplifier was designed based on cascading three stages of cascode amplifiers. This power amplifier has a size of 0.55 mm by 0.64 mm. It has a peak power gain of 14.5 dB at 57 GHz and a gain better than 10 dB in 51-61 GHz. The saturation output power is 9.5 dBm at 57 GHz.

### **1.4 Organization of the Thesis**

This thesis is organized as follows:

In chapter 2, some basic switch design approaches and the principles of switches from low frequency to MMW frequency are summarized.

In chapter 3, the basic theory about microwave filters are introduced. From the filter composed of basic lumped elements to transmission lines. After that, the concept of combination of transmission lines and switches is introduced. Finally, a SPDT switch in 65 nm CMOS and SPDT switch in 90 nm CMOS are demonstrated.

In chapter 4, the analysis of different multiple-port switch topologies is conducted.

In chapter 5, the experiment of two multiple-port switches is conducted to verify the analysis in chapter 4.

In chapter 6, a 60-GHz power amplifier in 65 nm CMOS process is demonstrated.

Finally, the conclusion of this thesis is drawn in chapter 7.

# Chapter 2 Basics of Radio Frequency Switches

### 2.1 Introduction [21]-[23]

Radio frequency (RF) switch plays a key role in wireless transceivers. As shown in Fig. 2.1, RF switches control the path that a transceiver transmits or receives RF signals. Switches have two mainly concerned specifications: insertion loss and isolation. A switch with good insertion loss would not attenuate signals too much. A switch with good isolations can block signal leakage from transmitter to receiver.

For single-pole-double-throw (SPDT) switches terminated with  $Z_0$  as in Fig. 2.2, the input impedance of the through-state path should be

$$Z_{Thru} = Z_0 \tag{2.1}$$

Besides, the input impedance of the isolated path should satisfy

$$Z_{ISO} \to \infty \tag{2.2}$$

Fig. 2.2. A SPDT switch terminated with  $Z_0$ .

Eq. (2.1) means that the through-state path transfers maximum power from the input port to through port, and Eq. (2.2) means that infinite impedance is required to block signal leakage to the isolated port. It should be noted that it is infinite impedance instead of low impedance. If the isolated path is composed of low impedance technique such as shunt transistors, there should be an impedance transformer to transform low impedance to high impedance, for example, quarter-wave length transmission lines. This concept is important and will be used in following sections.

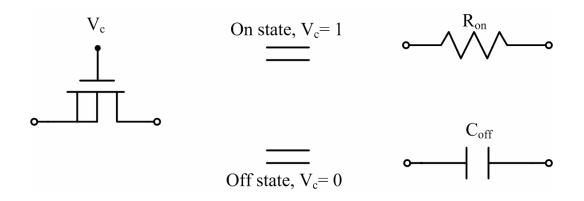

### 2.2 Series-Shunt Switches [21]-[23]

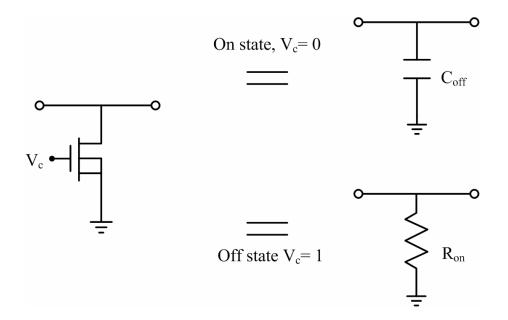

Series, shunt, or series-shunt is the most common approach to design RF switches. A common series switch is shown in Fig. 2.3. When the switch is on, its equivalent circuit is a series small resistor ( $R_{on}$ ), and this small resistor will not attenuate signals much. When the switch is off, its equivalent circuit is a capacitor ( $C_{off}$ ). A series capacitor has high pass characteristic, and thus it can block low frequency signal effectively. However, when the frequency goes higher, the isolation of the series switch degrades significantly.

A common shunt switch is shown in Fig. 2.4. When the switch is on, its equivalent circuit is a shunt capacitance ( $C_{off}$ ), and this shunt capacitance has a low pass characteristic. As the operating frequency goes higher, the shunt impedance goes lower, and this makes high frequency signals leaks to ground. When the shunt switch is off, its equivalent circuit is a shunt resistor ( $R_{on}$ ). This shunt resistor is of low impedance, and it drags signals to ground for isolation.

Fig. 2.3. Series switch and its equivalent circuit.

Fig. 2.4. Shunt switch and its equivalent circuit.

A series-shunt switch is shown in Fig. 2.5. It is a combination of series switch and shunt switch. When this series-shunt switch is off, both the series capacitor and shunt resistor enhance isolation much better. On the other hand, when the switch is on, the switch has more loss than the above mentioned switches. Regardless of this drawback, this kind of switch improves isolation greatly and thus it is much more useful in RF transceivers. Furthermore, the 3-dB bandwidth of this series-shunt switch locates at

Fig. 2.5. A series-shunt switch, and its equivalent circuit.

| $f_{3-dB} = \frac{1}{2\pi R_{on} C_{off}} $ (2.3) | 3) |

|---------------------------------------------------|----|

|---------------------------------------------------|----|

All the mentioned switches in this section are used for low frequency. The following sections introduce switched used in microwave or MMW frequency range.

## 2.3 Resonant-type Switches [28]-[30]

Fig. 2.7. Series type of a parallel resonator using a transistor.

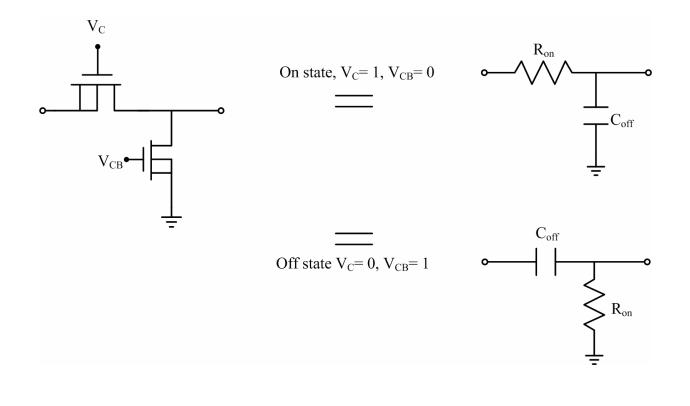

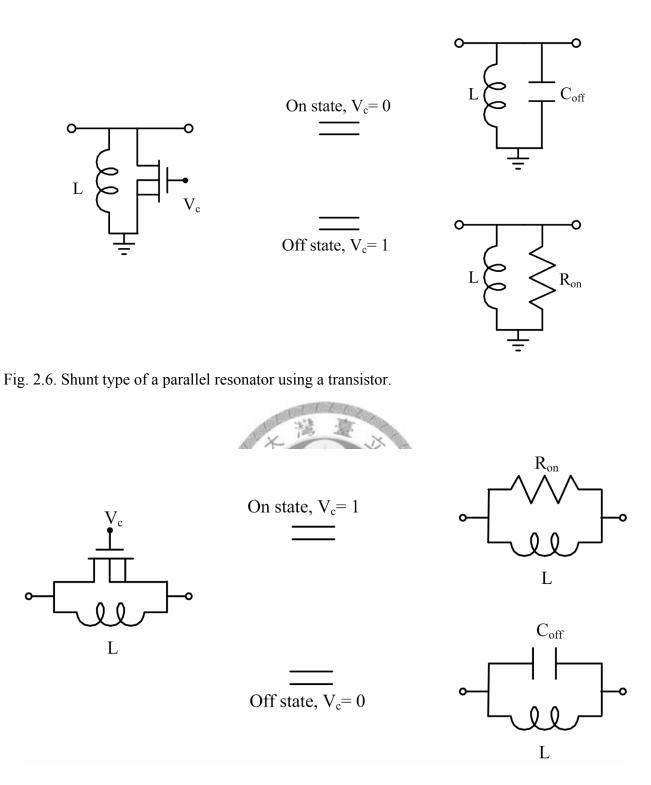

Resonant-type switches are one of the most popular switches in microwave or MMW frequency range. There are two commonly used resonant-type switches: one is to shunt a parallel resonator as in Fig. 2.6 and the other is to series a parallel resonator as in Fig. 2.7. A typical parallel

resonator is composed of one inductor parallel with one capacitor. When a transistor is off, it behaves like a capacitor, and we can use this capacitive characteristic to shunt an inductor to compose a parallel resonator as in Fig. 2.6 and Fig. 2.7.

These resonant-type switches can operate at any center frequency

$$f_0 = \frac{1}{2\pi L C_{off}} \tag{2.4}$$

However, there must be some constraints. First, the value of  $C_{\text{off}}$  has a certain range in each process. Besides, there is certain range of the value of inductors in practical design.

### 2.4 Distributed Switches [25]

Distributed switches are one of the most commonly used techniques because the characteristic of broad bandwidth. A distributed cell is shown in Fig. 2.8. When it is at on state, the transistor can be modeled as a capacitor. Therefore, the series L and the shunt  $C_{\text{off}}$  form an artificial transmission line. To make a through-state path, this artificial transmission line should be operated with characteristic impedance of  $Z_0$ .

$$Z_0 = \sqrt{\frac{L}{C_{off}}}$$

(2.5)

It can be noticed that if the value of inductors and the value of capacitors do not change with frequency, this through state can operate with infinite bandwidth. When the transistor is on, it

Fig. 2.8. A distributed switch and its equivalent circuit.

behaves like a small resistor. Therefore, the signal is pull to ground. To form a SPDT switch or a multiple-port switch, there must be one impedance transformer such as a quarter-wavelength transmission line before this isolated path, and the bandwidth of this impedance transformer is the limit of the bandwidth of a SPDT switch or a multiple-port switch.

Besides, there is a bandwidth limitation of a realized inductor because of self-resonant frequency. In MMW circuit design, a transmission line with high characteristic impedance  $Z_c$  and electrical length of  $\theta$  can behave like an inductor, and thus, inductors in Fig. 2.8 can be replaced by a transmission line which satisfies

$$\frac{L}{2} = Z_c \tan \theta \tag{2.6}$$

Although  $\theta$  changes with frequency to make the limitation of bandwidth, the bandwidth of switches composed of transmission lines is usually enough in realistic application.

# Chapter 3 Millimeter-Wave Filter-Integrated SPDT Switch

### 3.1 Introduction

MMW SPDT switches are one of the key components in RF front end. Low insertion loss, high isolation, and required power handling are important characteristics of a switch. Besides, in a communication system, a filter is often necessary to filter unwanted band. A switch and a filter can be merged into one single circuit [1]. This concept is used to design a 60-GHz SPDT switch in 65nm technology.

This chapter first introduces some kinds of microwave filters, and then the theory of filter-integrated switches is introduced. Finally, a *V*-band SPDT switch using 65nm CMOS technology and a 60-110GHz SPDY switch using 90 nm CMOS technology will be presented.

### **3.2 Basic Concepts of Filter-Integrated Switches [15]**

This section is composed of three subsections to let readers understand the principle of filter-integrated switches easier.

#### 3.2.1 Synthesis of Microwave Filters [2]-[3]

Microwave filters can be composed of T-sections of *L*-*C*, or  $\pi$ -sections of *L*-*C*. By cascading more T-sections or  $\pi$ -sections to synthesize a microwave filter, the sharper frequency response can be achieved to reject undesired band better. Some specific values of *L*-*C* can synthesize specific types of filters, such as Chebyshev filters or maximally flat filters. Chebyshev filters are also called equal ripple filters, because the transmission coefficient of them has equal ripple in desired band. The transmission coefficient of maximally flat filters is flat in its desired band. Besides, Chebyshev filters have sharper frequency response than maximally flat filters.

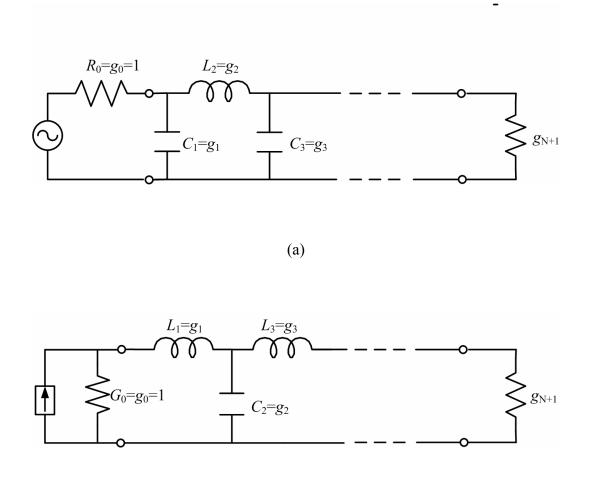

Low pass prototypes of microwave filters are shown in Fig. 3.1. Fig. 3.1(a) is a prototype of low pass filter, and it begins with a shunt capacitor. Fig. 3.1(b) is another prototype of low pass filter, and it begins with a series inductor. We denote the *L* and *C* in Fig. 3.1 as  $L_k$  and  $C_k$ , respectively. The values of  $L_k$  and  $C_k$  can be found by tables in microwave engineering books or microwave filter books such as [2],[3]. For a low pass filter, the design value of indeed inductor and capacitor can be found by

$$L_{k}' = \frac{R_{0}L_{k}}{\omega_{c}}$$

(3.1)

$$C_k' = \frac{C_k}{R_0 \omega_c} \tag{3.2}$$

$\omega_c$  is the cutoff frequency and  $R_0$  is the referenced impedance. Both  $\omega_c$  and  $R_0$  are given by the designer. Therefore, the designers only have to decide the order of the filter, cutoff frequency, and referenced impedance, and then the design of a low pass filter is finished.

(b)

Fig. 3.1. Basic prototypes of low pass filters. (a) Prototype beginning with a shunt element. (b) Prototype beginning with a series element.

The design procedure described above can be also used to high pass filters and low pass filters by some transformation. For high pass filter, frequency  $\omega$  should be substituted by  $-\omega_c/\omega$ . By doing so, the inductor in the prototype of a low pass filter will be replaced by a capacitor, and the capacitor will be replaced by an inductor.

For band pass filter, frequency  $\omega$  should be substituted by  $\frac{\omega_0}{\omega_2 - \omega_1} \left(\frac{\omega}{\omega_0} - \frac{\omega_0}{\omega}\right)$ , where  $\omega_0$

denotes the center frequency and  $\omega_0$  is the arithmetic mean of  $\omega_1$  and  $\omega_2$ . By using the above relationship, this will make the inductor in low pass prototype replaced by an inductor series with a

Fig. 3.2. A band pass filter composed of quarter-wavelength transmission lines.

capacitor, and the capacitor in low pass prototype replaced by a capacitor parallel with an inductor.

### 3.2.2 Transmission Line Integrated Filters [6]

In microwave frequency, the behavior of a transmission line can be viewed as an inductor or capacitor upon the length and termination. Therefore, there must be a transformation of transmission lines with inductors or capacitors. According to the previous subsection, the proper value of inductors and capacitors can form a microwave filter, and hence, proper transmission lines can similarly form a microwave filter. A transformation called Richard's transformation [3] can be used to prove the above described contents.

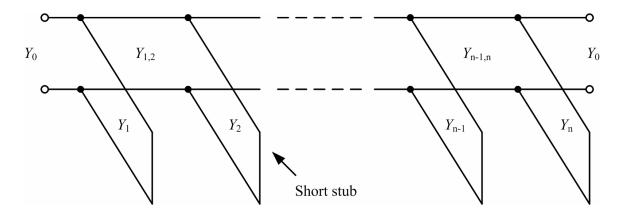

A microwave filter composed of shorted quarter-wavelength transmission lines will be introduced in this section. This kind of filter can be synthesized by short-circuited stubs of quarter-wavelength

Short-circuited stubs of quarter-wavelength replace the shunt element in Fig. 3.1(a), and series quarter-wavelength transmission lines replace the series elements in Fig. 3.1(a). Fig. 3.2 is the

transmission line integrated filter, and the lengths of all the transmission lines are quarter-wavelength.

$$\theta = \frac{\pi}{2} \left( 1 - \frac{FBW}{2} \right)$$

$$h = 2$$

$$\frac{J_{1,2}}{Y_0} = g_0 \sqrt{\frac{hg_1}{g_2}}$$

$$\frac{J_{n-1,n}}{Y_0} = g_0 \sqrt{\frac{hg_1g_{n+2}}{g_0g_{n-1}}}$$

$$\frac{J_{i,i+1}}{Y_0} = \frac{hg_0g_1}{\sqrt{g_ig_{i+1}}} \text{ for } i = 1 \text{ to } n - 1$$

$$Y_1 = g_0Y_0 \left( 1 - \frac{h}{2} \right) g_1 \tan \theta + Y_0 \left( N_{1,2} - \frac{J_{1,2}}{Y_0} \right)$$

$$Y_n = Y_0 \left( g_n g_{n+1} - g_0 g_1 \frac{h}{2} \right) \tan \theta + Y_0 \left( N_{n-1,n} - \frac{J_{n-1,n}}{Y_0} \right)$$

$$Y_i = Y_0 \left( N_{i-1,i} + N_{i,i+1} - \frac{J_{i-1,i}}{Y_0} - \frac{J_{i,i+1}}{Y_0} \right) \text{ for } i = 1 \text{ to } n - 1$$

$$Y_{i,i+1} = Y_0 \left( \frac{J_{i,i+1}}{Y_0} \right) \text{ for } i = 1 \text{ to } n - 1$$

$$(3.3)$$

, where *FBW* is the ratio of bandwidth to center frequency.

Eq. (3.3) is very useful to synthesize a filter of quarter-wavelength transmission lines. The designer only has to decide *FBW* and calculate the value of characteristic admittance of each stub, and then the design of a filter is finished.

Fig. 3.3. Equivalent circuit of a shunt quarter-wavelength transmission line, it can be further synthesized with an off-state transistor.

Fig. 3.4. Equivalent circuit of a series quarter-wavelength transmission line.

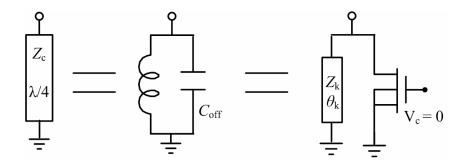

### 3.2.3 Filter-Integrated Switches [15]

The concept of filter-integrated switches was developed in [1]. Furthermore, the reduced-size version is further studied in [4]. The design principle of filter-integrated switches is based on the filter of quarter-wavelength short stubs. Since each quarter-wavelength short stub can be modeled as one inductor parallel with a capacitor near the center frequency of quarter-wavelength as in Fig. 3.3. Therefore, the shunt quarter-wavelength short stub can be replaced by an off-state transistor parallel with one high impedance ( $Z_k > Z_c$ ) short stub whose length is shorter than quarter-wavelength. Furthermore, since the equivalent circuit of one series quarter-wavelength transmission lines can be modeled as one two shunt capacitors with one series high impedance

transmission line less than quarter-wavelength as in Fig. 3.4 [5]. Therefore, the reduced-sized version of filter-integrated switches can be designed by combining the equivalent shunt  $C_k$  and  $C_{k+1}$  into the off-state transistors. Hence, the electrical length of series transmission lines can be reduced.

# 3.3 Circuit Implementation of V-band Filter-Integrated SPDT Switch in 65 nm CMOS Process

Before designing an RF switch, the choice of technology is considered first. The performance of the switch implemented in different processes is mainly dependent on the resistance of on-state transistor and the capacitance and resistance of off-state transistor. To compare the technologies fairly, the device size of each process is chosen to have the same resistance of the on-state transistor. Therefore, the process with smaller capacitance and larger resistance of off-state transistor is the one can operate higher frequency and can achieve better performance for the design of switches. The input impedance of on-state and off-state transistors for  $0.18 \mu$ m, 90 nm, and 65 nm CMOS are shown in Fig. 3.5. To achieve the on-state resistance the same for each process, the total gate width of the NMOS of  $0.18 \mu$ m CMOS is chosen as 96  $\mu$ m, the total gate width of the NMOS of 90 nm CMOS is chosen as 60  $\mu$ m, and the total gate width of the NMOS of 65 nm CMOS is chosen as 88  $\mu$ m. On this condition, the value of off-state capacitance at 60-GHz is 68.1 fF, 43.3 fF, and 39.5 fF for 0.18  $\mu$ m, 90 nm, and 65 nm CMOS, respectively. If the switch is designed to operate at the same center frequency with the same isolation, the process with longer gate length will provide the insertion loss with narrower bandwidth due to the larger off-state capacitance in longer gate length process. Besides, it can be seen from Fig. 3.5(b) that the resistance of the off-state NMOS for each process is very close to each other, and this means that the loss of switches in each process will be dominated by the loss of passive components such as inductors and thin-film microstrip lines. Furthermore, realized inductors and thin-film microstrip lines can only operate below their self-resonant frequency, and the self-resonant frequency is dependent on each process. For a switch operating at 100 GHz, the self-resonant frequency of passive components of the corresponding process should be higher than 100 GHz.

Fig. 3.6 shows the schematic of the designed 60-GHz SPDT switch. This switch is based on the filter-integrated type. All the transmission-lines in Fig. 3.6 are thin-film microstrip lines. The series-shunt approach only functions well in low frequency. The resonant approach can be used in MMW frequency, but it can only cover the band near the center frequency. Although distributed switches have the broadest bandwidth, it is necessary to shunt more transistors than the filter-integrated type, and hence it causes more insertion loss.

Fig. 3.5. (a) The input impedance of on-state transistors for 0.18  $\mu$ m, 90 nm, and 65 nm CMOS. (b) The input impedance of on-state transistors for 0.18  $\mu$ m, 90 nm, and 65 nm CMOS.

Fig. 3.6. Circuit schematic of a 60-GHz SPDT switch.

The choice of device size is important for switch design. The larger device has larger parasitic capacitors but smaller parasitic resistors. The smaller device has smaller parasitic capacitors but larger parasitic resistors. Since the through state of filter-integrated switches is composed of shunt off-state transistors, the higher parasitic capacitors reduce the bandwidth. Besides, the smaller shunt resistors can lead to better isolation since the function of isolation is by transforming low impedance to high impedance. The smaller the resistor locates at the right side of Smith chart, the higher impedance is achieved after quarter-wavelength transformation. Therefore, the larger device with smaller resistors can provide better isolation. There is trade off between larger devices and smaller devices.

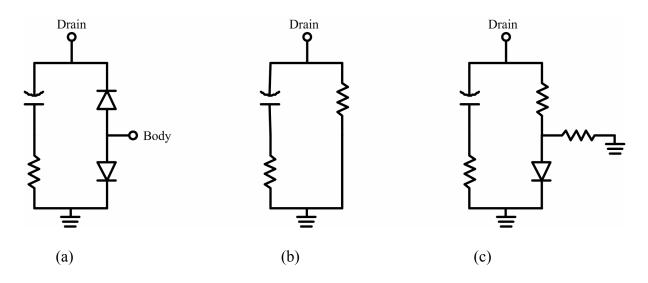

Fig. 3.7. (a) The simplified model of a shunt off-state MOSFET. (b) The simplified model of a shunt off-state MOSFET without body-floating. (c) The simplified model of a shunt off-state MOSFET with body-floating.

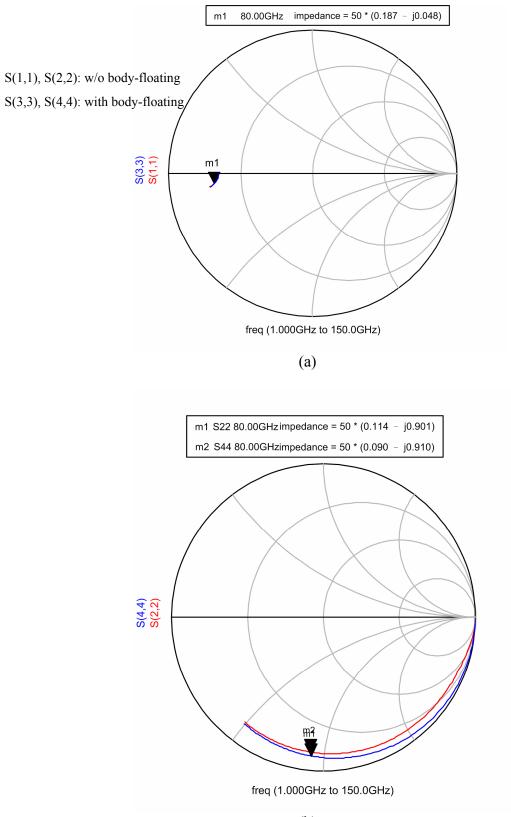

The large-signal simplified models for a shunt off-state MOSFET can be modeled as in Fig. 3.7 [7]. If the bulk of the shunt transistor is connected to ground, the simplified model is as shown in Fig. 3.7(b). If the bulk of the shunt transistor is connected to a large resistor, the simplified model is as shown in Fig. 3.7(c). Without body-floating, the diode between the body and the source is shorted, and hence, the current can flow from ground to drain through only one diode which is modeled as a resistor as in Fig. 3.7(b). With body-floating, the current from ground has to flow through the large resistor to drain as in Fig. 3.7(c). Therefore, under the same voltage swing at the drain, the current of the MOSFET with body-floating is less, and this leads to the equivalent impedance of a shunt MOSFET with body-floating higher. The results can be seen from Fig. 3.8(b). The power handling of a shunt MOSFET is mainly dependent on the pinch-on voltage  $V_{\rm B}$  of the parasitic diodes [7]. Besides, if the bulk is floating and connected to a negative voltage  $-V_{\rm bias}$ , the voltage swing at the drain of a shunt MOSFET can go from  $-V_{\rm B}$  to  $-(V_{\rm B}+ V_{\rm bias})$ . Therefore, the technique body-floating with negative bias at the bulk can improve the power handling and the insertion loss of a shunt-type switch.

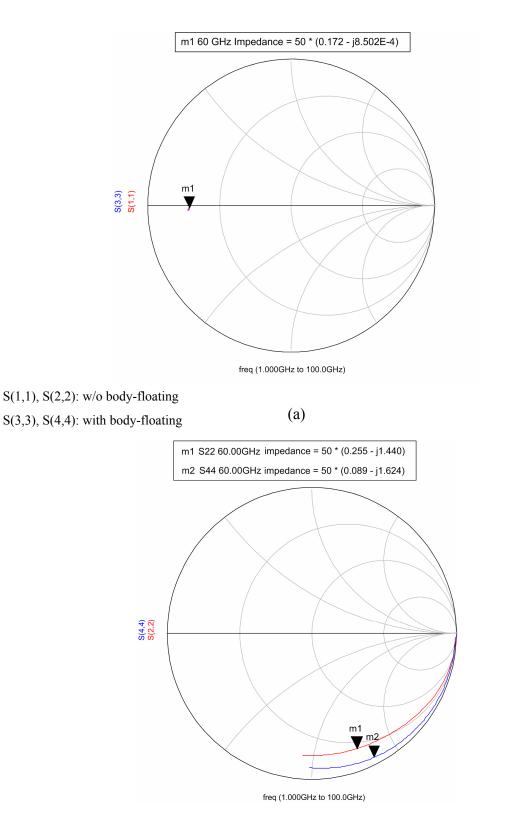

Fig. 3.8 shows the impedance of passive NMOS.  $S_{11}$  and  $S_{22}$  is the impedance of device with a

large resistor between source and body for on-state and off-state, respectively.  $S_{33}$  and  $S_{44}$  is the impedance of device *without* a large resistor between source and body for on-state and off-state, respectively. From this comparison in Fig. 3.8, we can know if there is a large resistor between source and body, the parasitic resistors of off-state transistors can be reduced. In our simulation based on the circuit in Fig. 3.6, the design with a large resistor between source and body can improve insertion loss better than 1 dB as shown in Fig. 3.9. Besides, due to adding a large resistor does not have much impact on on-state of transistors as in Fig. 3.8(b), the simulated isolation of the switch with large resistor is close to that without large resistor as shown in Fig. 3.9 (b).

In Fig. 3.6,  $Z_T$  is chosen for 50- $\Omega$ , and hence the width is about 7 µm for 65 nm CMOS technology.  $Z_1$ ,  $Z_2$ , and  $Z_{12}$  should be chosen for high impedance in CMOS, but the width of 4 µm can only achieve about 60- $\Omega$ ; therefore, the widths are all 4 µm. The width smaller than 4 µm causes very high loss, and that is why the narrower width of thin-film microstrip line is not used.  $L_T$  is about quarter-wavelength to achieve impedance transformation.  $L_1$ ,  $L_2$ , and  $L_{12}$  are chosen to meet the condition to design a 3<sup>rd</sup> filters as described in the previous sections. These lines behave like inductors because of high impedance. The 3<sup>rd</sup> filter-integrated switch has three shunt resonators. Two resonators are composed of the shunt off-state transistors with  $L_1$  and  $L_2$  at the through arm. The other is composed by the isolated arm which is formed by quarter-wavelength with on-state transistors.

Fig. 3.8. The impedance of a passive NMOS in 65 nm CMOS. (a) On-state passive NMOS. (b) Off-state passive NMOS.

(a)

(b)

Fig. 3.9. Simulated with and without large resistor between source and body. (a) Insertion loss, (b) isolation.

Fig. 3.10. The chip photo of 60-GHz SPDT filter-integrated switch. The chip size is 1500  $\mu$ m x 250  $\mu$ m.

# 3.4 Experimental Results of V-Band SPDT Switch in 65 nm CMOS

The chip photo of this V-band SPDT switch is shown in Fig. 3.10. The chip size is 1500  $\mu$ m x 250  $\mu$ m.

This SPDT switch is measured via on-wafer probing. Anritsu 37397D network analyzer is used to measure the S-parameters below 65 GHz. The simulated and measured insertion losses are shown in Fig. 3.11. The measured insertion loss quite agreed with simulated insertion loss. The insertion loss is about 3.2-4.5 dB in 40-80 GHz. The measured return loss is shown in Fig. 3.12. The measured return loss is better than 10 dB in 40-90 GHz. The measured isolation is about 20-27 dB in 40-80 GHz as shown in Fig. 3.13. There are some differences between the measured isolation and simulated isolation. If a small resistor about 5 ohm is added in the on-state of NMOS, the simulated isolation will become about 25 dB. The reason why the measured isolation cannot fit with simulated isolation might be the underestimate parasitic resistor of the NMOS in 65 nm CMOS.

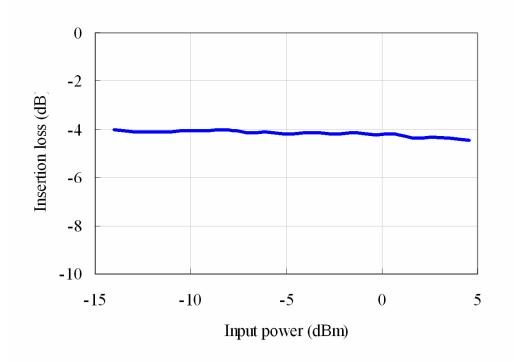

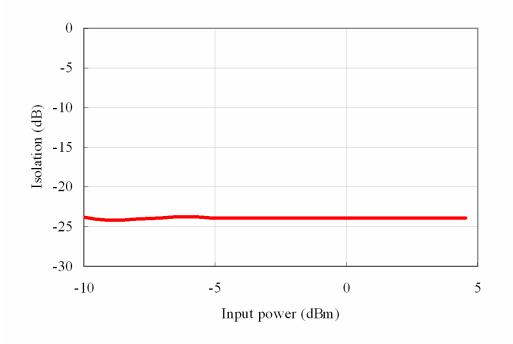

The measured insertion loss versus input power at 60 GHz is shown in Fig. 3.14. There is no obviously 1–dB insertion loss compression point. The measured isolation versus input power at 60 GHz is shown in Fig. 3.15. There is also no power compression point for isolation.

Fig. 3.11. Simulated and measured insertion loss of 60-GHz SPDT switch.

Fig. 3.12. Simulated and measured return loss of 60-GHz SPDT switch.

夓

Fig. 3.13. Simulated and measured isolation of SPDT switch.

Fig. 3.14. Measured insertion loss versus input power.

Fig. 3.15. Measured isolation versus input power.

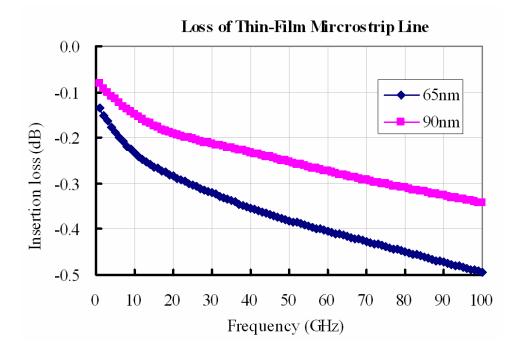

Fig. 3.16. Comparison of the loss of thin-film microstrip lines in 65 nm CMOS and 90 nm CMOS.

# 3.5 Circuit Implementation of 60 to 110 GHz SPDT Switch in 90 nm CMOS

In fact, the architecture of the 60 to 110 GHz SPDT switch using 90 nm CMOS is similar to Fig. 3.6 except that the device sizes are 4  $\mu$ m x 16 for 90 nm CMOS. The input impedance of the NMOS with and without body-floating is shown in Fig. 3.17.

The body-floating technique is also adopted to design this SPDT switch due to the benefits discussed in section 3.3. The resistance of on-state NMOS is chosen for 9 ohm to achieve an isolation of 30 dB in simulation. The capacitance of off-state NMOS is 0.435 pF. The lengths of thin-film microstrip lines in this switch are centered at 80 GHz. The width of 50-ohm thin-film microstrip lines in 90 nm CMOS is 10  $\mu$ m. The comparison between the loss of 50-ohm thin-film

microstrip lines in 65 nm CMOS and that of 90 nm CMOS is shown in Fig. 3.16. Since the lower loss in 90 nm CMOS, it is more suitable to use 90 nm CMOS to design passive RF elements including switches.

(b)

Fig. 3.17. The impedance of a passive NMOS in 90 nm CMOS. (a) On-state passive NMOS. (b) Off-state passive NMOS.

Fig. 3.18. The chip photo of the 60-110 GHz SPDT switch with a size of 400  $\mu$ m x 750  $\mu$ m.

## **3.6 Experimental Results of 60 to 110 GHz SPDT** Switch in 90 nm CMOS

The chip photo of this 60-110 GHz SPDT switch in 90 nm CMOS is shown in Fig. 3.18. The chip size is  $400 \ \mu m \ x \ 750 \ \mu m$ .

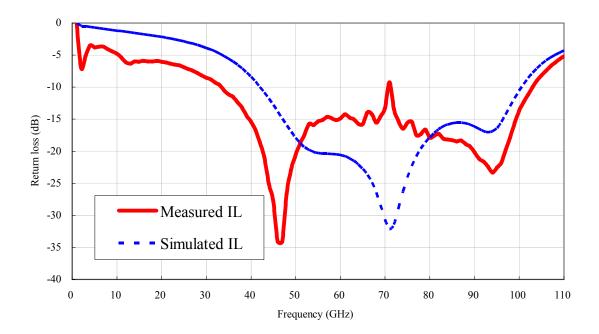

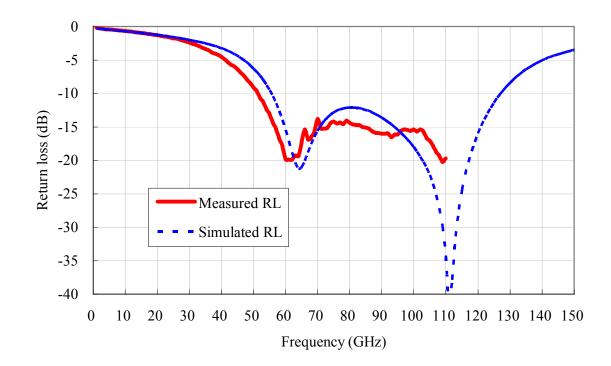

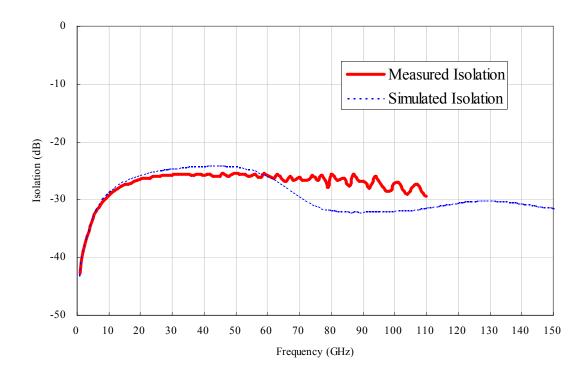

This SPDT switch is measured via on-wafer probing. Anritsu 37397D network analyzer is used to measure the S-parameters below 65 GHz. The simulated and measured insertion losses are

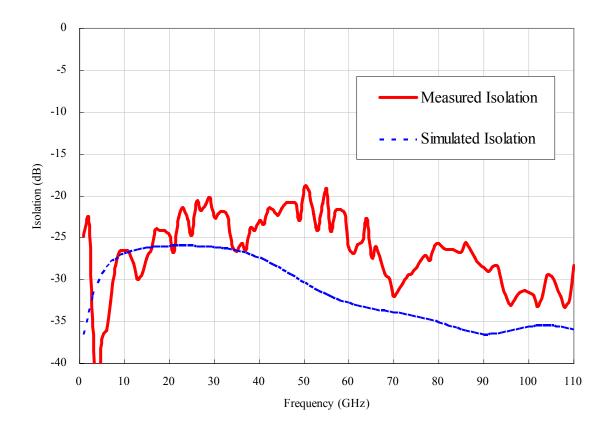

shown in Fig. 3.19. The measured insertion loss quite agreed with simulated insertion loss. The insertion loss is about 3-4 dB in 60-110 GHz. The measured return loss is shown in Fig. 3.20. The measured return loss is better than 10 dB in 50-110 GHz. The measured isolation is better than 25 dB in DC-110 GHz as shown in

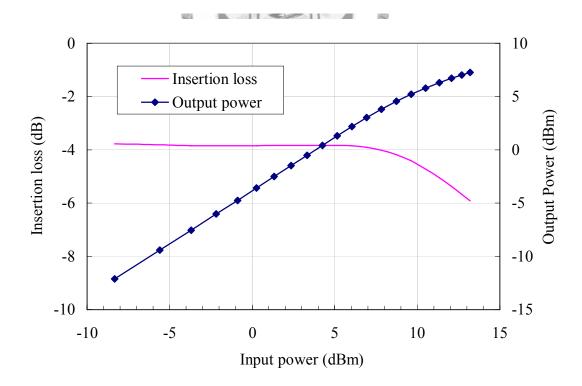

Fig. 3.21. The measured isolation also quite agreed with simulated isolation. The reason of the difference between the measured isolation and simulated isolation above 65 GHz is due to the precision of calibration for the band of 65-110 GHz. The measured power performance at 75 GHz of this 60-110-GHz SPDT switch is shown in Fig. 3.22, and the power performance of 1-dB compression point appears about  $P_{\rm in} = 10.5$  dBm.

The data above 110 GHz cannot be measured due to the limitation of the instruments. However, the 110-150-GHz frequency response can be predicted by simulation, and the simulated insertion loss goes more than 4 dB at 115 GHz.

Fig. 3.19. Simulated and measured insertion loss of 60-110 GHz SPDT switch.

Fig. 3.20. Simulated and measured return loss of 60-110 GHz SPDT switch.

Fig. 3.21. Simulated and measured isolation of 60-110 GHz SPDT switch.

Fig. 3.22. Measured power performance at 75 GHz of 60-110 GHz SPDT switch.

#### 3.7 Summary

The MMW SPDT switch using 65 nm CMOS process is demonstrated in this chapter. There is quite agreement between the measured results and simulated results. The insertion loss is about 3.2-4.5 dB in 40-80 GHz. The return loss is quite good and it is better than 10 dB in 40-80 GHz, since the filter-integrated switch topology can provide good matching. The isolation is about 20-27 dB in 40-80 GHz. There is no power compression point for insertion loss and isolation even the input power is 5 dBm.

Besides, the 60-110 GHz SPDT using 90 nm CMOS process is also demonstrated in this chapter. There is also a quite agreement between the measured results and simulated results. The insertion loss is about 3.0-4.0 dB in 60-110 GHz. The return loss is quite good and it is better than 10 dB in 50-110 GHz, since the filter-integrated switch topology can provide good matching. The isolation is better than 25 dB in DC-110 GHz. This switch is the highest frequency CMOS SPDT switch reported to date.

The comparison of CMOS switches is shown in Table 3.1. The SPST switch in 65 nm CMOS [8] shows good performance, but the design approach of simply shun transistors can only be used in SPST switch design. It can be observed that the 90 nm filter-integrated SPDT switch in this thesis has the highest operating frequency and has very good performance. Besides, since the passive components (thin-film microstrip lines) have higher loss in 65 nm CMOS than 90 nm CMOS in our simulation, it might be better to design passive RF components in 90 nm CMOS.

#### Table 3.1

#### SUMMARY OF THE PERFORMANCE OF REPORTED SWITCHES IN CMOS PROCESS

| 55 mm C14105  | i nei integi ateu   | עט <sup>-י</sup> טד | 5.277.3   | - 20      | 51 0 1 | work         |

|---------------|---------------------|---------------------|-----------|-----------|--------|--------------|

| 65 nm CMOS    | Filter-integrated   | 40~80               | 3.2~4.5   | >20       | SPDT   | work<br>This |

| 90nm CMOS     | Filter-integrated   | 65~110              | 3-4       | >25       | SPDT   | This         |

| HEMT          |                     |                     |           |           |        |              |

| 0.15 um GaAs  | Filter-integrated   | 40~60               | <1.5      | >22       | SPDT   | [16]         |

| HEMT          |                     |                     |           |           |        |              |

| 0.15 um GaAs  | Filter-integrated   | 42~67               | <2.5      | >27       | SPDT   | [15]         |

| CMOS          |                     |                     |           |           |        |              |

| 130 nm        | Series-shunt        | 33~43               | <3        | >25       | SPDT   | [14]         |

| 150 IIII 5100 | integrated          | 151478<br>141 2     |           | 20        | 51 0 1 | [13]         |

| 130 nm SiGe   | Transmission-line   |                     | 2~2.7     | >25       | SPDT   | [12]         |

| 90nm CMOS     | concept<br>LC-tuned | 24                  | 3.5       | 22        | SPDT   | [12]         |

| CMOS          |                     | X-                  | A A       | - 50      | 51 D 1 |              |

| 180 nm        | Traveling wave      | DC~50               | <6        | >38       | SPDT   | [11]         |

| CMOS          | integrated          |                     |           |           |        |              |

| 130 nm        | Transmission-line   | 57~66               | 4.5~5.8   | 24~26     | SPDT   | [10]         |

| CMOS          | concept             |                     |           |           |        |              |

| 90 nm         | Traveling wave      | 50~94               | <3.3      | >27       | SPDT   | [9]          |

| CMOS          |                     |                     |           |           |        |              |

| 65 nm         | Shunt               | DC-94               | 1.6       | 19-30     | SPST   | [8]          |

|               | Approach            | (GHz)               | Loss (dB) | (dB)      |        |              |

| Technology    | Design              | Frequency           | Insertion | Isolation | I/O    | Ref.         |

# Chapter 4 Topology Analysis of Millimeter -Wave Multiple-Port Switches

#### 4.1 Introduction

RF switches are important components in the front end of the RF transmit/receive (T/R) communication systems to control microwave signals. Recently, the importance of wireless service has increased rapidly, and higher network capacity with better performance is required. A beamformer system using multiple antennas both at the transmitter and receiver can improve the efficiency of the spectrum greatly by spatial multiplexing [17]–[20]. In a beamformer system, it is important to have a good multiple-port switch.

There are many approaches to design a passive field-effect transistor (FET) switch. For the frequency below 20 GHz, switches using series or shunt HEMTs (or FETs) in [21]-[23], and traveling-wave concepts in [24] are reported with good performances. In the millimeter-wave (MMW) frequency range, the traveling-wave concept is usually used to realize wideband switches [25], [26]. Switches using the impedance transformation technique are reported with good isolation [27], but they show narrowband performances and occupy a large chip area. MMW switches based on resonant-type structures or filter-integrated switches are reported with good performances in [28]–[32]; however, they are still narrowband designs. Nevertheless, most of the above-mentioned switches [21], [22], [25]-[30], [33]–[36] and switch products [37], [38] are single-pole-multiple-throw (SPMT) designs, and there are only a few studies that discuss multiple-port switches [39]–[43].

Multiple-port switches in series-shunt topology were reported with good performances below 10 GHz [39]–[41]. Multiple-port switches using microelectromechanical system (MEMS) technology presented good performances to around 20 GHz [42], but the MEMS process is not compatible to most monolithic microwave integrated circuit (MMIC) processes and the high voltage of the MEMS switch makes it not easy to use in real applications. A multiple-port bandpass filter-integrated switch is reported in [43], but it is designed for narrow bandwidth.

In this chapter, we have categorized MMW multiple-port switch topologies. The formulations of the bandwidth, insertion loss, and isolation with respect to different topologies are also derived. Based on the analysis, the limitations of RF performances of multiple-port switches are mostly dominated by their topologies instead of the unit switch cell. It means that once the topology is selected, the performances can be predicted according to the derived equations.

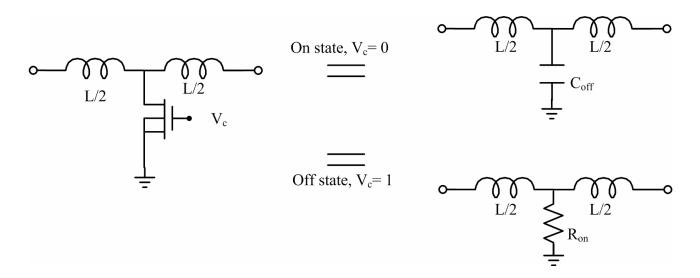

## 4.2 Introduction Topologies

**Type Multiple-Port**

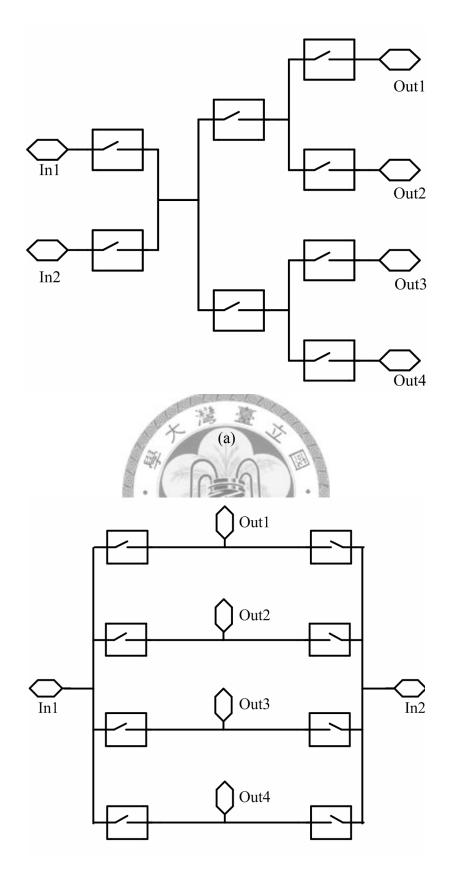

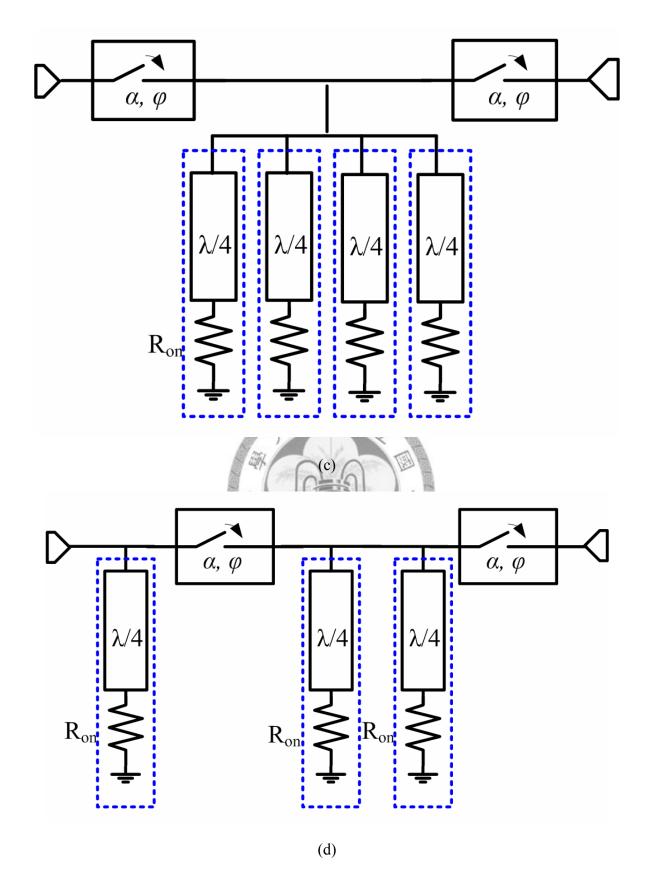

Fig. 4.1 shows four types of topologies of MMW multiple-port switches with two inputs and four outputs. For a signal flow from multi-input to multi-output, binary-tree logic is intuitively considered, and the topology is shown in Fig. 4.1(a). In [41], a matrix type structure was used to realize an  $n \times m$  switch. Similarly, a matrix topology can be used to form a multiple-port switch, as shown in Fig. 4.1(b). A net-type multiple-port topology is proposed in Fig. 4.1(c). Another topology to implement a multiple-port switch is a ring-binary type, which is shown in Fig. 4.1(d). Compared with the binary-tree topology in Fig. 4.1(a), the ring-binary type has the advantage of its simple control logic to control the signal flow [39].

## 4.3 Analytical Derivation of Insertion Loss of Multiple-Port Topologies

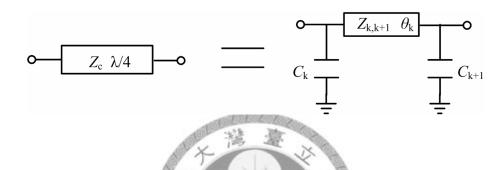

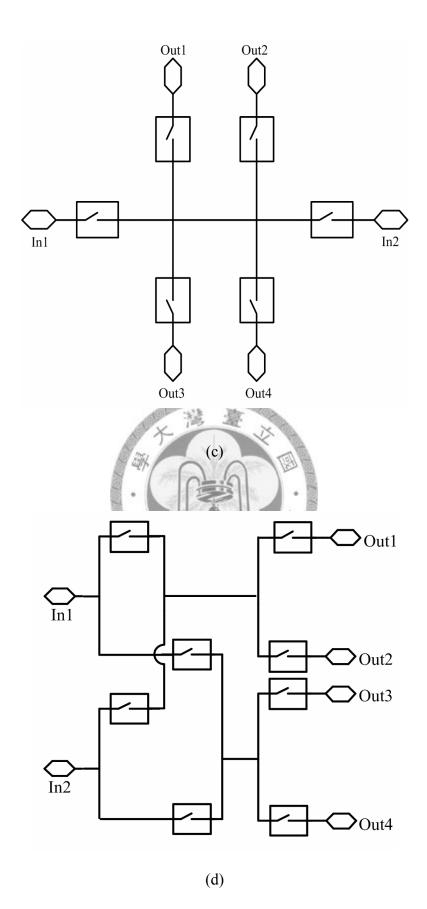

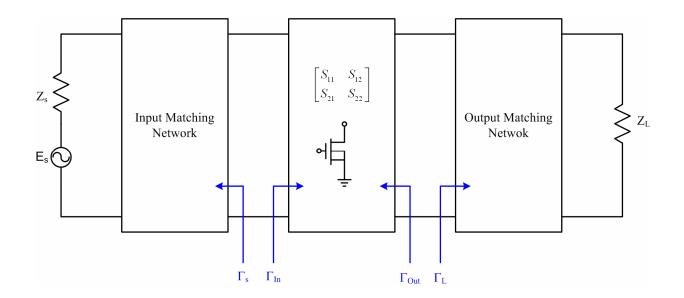

In order to analyze these four types of topologies in Fig. 4.1, we construct equivalent-circuit models to investigate the insertion loss and bandwidth performances in the thru-state. Simply a series, shunt, or series/shunt HEMT design approach is not suitable for a high-frequency switch. Fig. 4.2 shows a block diagram for the on state of the unit switch, and the equivalent-circuit model for the off state of the unit switch. For MMW passive HEMT switch design, a quarter-wavelength transmission line is needed to transform an off-state single-pole–single-throw (SPST) switch from low impedance into high impedance for blocking the RF signal [25]–[27], [29], [30], [33], [34]. Therefore, the quarter-wavelength transmission lines are included in the unit switches, as shown in the equivalent-circuit model of Fig. 4.2(b).

(b)

Fig. 4.1. Four types of multiple-port switch topology. (a) Binary-tree type. (b) Matrix type. (c) Net type. (d) Ring-binary type.

(a)

Fig. 4.2. (a) Block diagram for the on state of the unit switch. (b) Equivalent-circuit model for the off state of the unit switch.

Based on the unit switch defined above, the off-state unit switch is modeled as a quarter-wavelength transmission line connected by a small resistor with a parasitic inductor so we model a though path between the input port and output port of these four types of topologies, as shown in Fig. 4.3. In order to simplify the analysis, we ignore the parasitic inductor of on-state HEMTs. Since the unit switch is designed with the same characteristics, the behavior of each on-state unit switch is modeled as the loss of  $\alpha(f, C_{off})$  caused by the SPST switch and electrical delay of  $\phi$ , where *f* denotes frequency; furthermore, the input and output match of a unit switch is assumed perfect for simplicity.

The binary-tree type is analyzed first. The transmission coefficient, denoted as  $S_{21,a}$  of that, can be derived as

(b)

Fig. 4.3 Equivalent circuit models of a through path for: (a) binary-tree type, (b) matrix type, (c) net type, and (d) ring-binary type.

$$S_{21,a} = \mathcal{O}(f, C_{off}) e^{-j\phi} \times \frac{2(r_{on} + j\tan\theta)}{2r_{on} + 2 + j(2 + 2r_{on})\tan\theta} \times \mathcal{O}(f, C_{off}) e^{-j\phi} \times \frac{2(r_{on} + j\tan\theta)}{2r_{on} + 1 + j(1 + r_{on})\tan\theta} \times \mathcal{O}(f, C_{off}) e^{-j\phi}$$

(4.1)

where  $r_{\rm on}$  denotes the  $R_{\rm on}$  normalized by the referenced impedance of  $Z_0 = 50\Omega$ .

The electrical length of the quarter-wavelength transmission line for center frequency  $f_0$  can be represented by

$$\theta = \frac{\pi}{2} \times \frac{f}{f_0} \tag{4.2}$$

The magnitude of the transmission coefficient of the binary-tree-type topology can be derived

as

$$|S_{21,a}| = |\alpha(f, C_{off})|^{3} \frac{\sqrt{r_{on}^{2} + \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}}{\sqrt{(r_{on} + 1)^{2} + (1 + r_{on})^{2} \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}} \times \frac{2\sqrt{r_{on}^{2} + \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}}{\sqrt{(2r_{on} + 1)^{2} + (2 + r_{on})^{2} \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}}$$

(4.3)

· · · · ·

Similarly, the magnitude of the transmission coefficient of matrix type  $(S_{21,b})$  is obtained as

$$|S_{21,b}| = |\alpha(f, C_{off})| \frac{2\sqrt{r_{on}^{2} + \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}}{\sqrt{(2r_{on} + 3)^{2} + (2 + 3r_{on})^{2} \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}} \times \frac{2\sqrt{r_{on}^{2} + \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}}{\sqrt{(2r_{on} + 1)^{2} + (2 + r_{on})^{2} \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}}$$

(4.4)

and the magnitude of the transmission coefficient of net type  $(S_{21,c})$  is

$$\left|S_{21,c}\right| = \left|\alpha(f, C_{off})\right|^{2} \frac{\sqrt{r_{on}^{2} + \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}}{\sqrt{(r_{on} + 2)^{2} + (1 + 2r_{on})^{2} \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}}$$

(4.5)

The magnitude of the transmission coefficient of ring-binary type  $(S_{21,d})$  is

$$\left|S_{21,d}\right| = \left|\alpha(f, C_{off})\right|^{2} \frac{2\sqrt{r_{on}^{2} + \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}}{\sqrt{(2r_{on} + 1)^{2} + (2 + r_{on})^{2} \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}} \times \frac{\sqrt{r_{on}^{2} + \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}}{\sqrt{(r_{on} + 1)^{2} + (1 + r_{on})^{2} \tan^{2}(\frac{\pi}{2} \times \frac{f}{f_{0}})}}$$

(4.6)

From (4.3)–(4.6), we can find that the insertion loss can be represented as a general form

$$|S_{21}| = |S_{21,SPST}(f, C_{off})| \times |S_{21,topology}(R_{on}, \theta)|$$

$$(4.7)$$

where  $|S_{21, SPST}(f, C_{off})|$  represents the insertion loss of the unit switch, and the second term  $|S_{21, topology}(R_{on}, \theta)|$  stands for the loss caused by the loading effect according to different topologies described in Fig. 4.1(a)–(d), respectively.

The insertion loss  $|S_{21, SPST}$  (*f*,  $C_{off}$ )| in each topology from SPST switches is directly proportional to the number of unit switches along a through path from input port to output port. There are three unit switches along a through path for the binary- tree type; the matrix type has one, the net type has two, and the ring-binary type has two unit switches along a through path, respectively. It is observed that the matrix type has the lowest loss from unit switches and the binary-tree type suffers the most. However, the insertion loss resulted from the loading effect  $|S_{21}$ , topology ( $R_{on}$ ,  $\theta$ )| cannot be ignored. The switch with larger transistors can suppress the loading effect better because of the smaller parasitic resistor, but the performance of a unit switch would degrade due to the larger parasitic capacitor. To suppress insertion loss for each topology, we can choose the proper device size to compensate the loss caused by the unit switches and loading effect.

To summarize insertion losses for the four types of multipleport switches, the loss of a unit switch  $|S_{21, \text{SPST}}(f, C_{\text{off}})|$  is denoted by  $\alpha$  (dB), and we denote  $\beta_n$  as the loading effect  $|S_{21, \text{topology}}(R_{\text{on}}, \theta)|$  of shunt n (n = 1,2,3,4) quarter-wavelength transmission lines in decibels, respectively.  $\beta_2$  is approximately  $2\beta_1$ ,  $\beta_3$  is approximately  $3\beta_1$ , and  $\beta_4$  is approximately  $4\beta_1$ .

### 4.4 Analytical Derivation of Bandwidth of Multiple-Port Topologies

The frequency response of an SPST switch can usually cover many octave bandwidths [25], and the restriction of the bandwidth of a multiple-port switch is mainly dominated by its topology. Therefore, in the derivation, it is assumed that the loss of a SPST switch is constant over the band. Hence, the 1-dB bandwidth can be determined by solving

$$\left|S_{21,topology}\left(R_{on},\theta\right)\right|^{2} = 0.8\tag{4.8}$$

The 1-dB bandwidth of each topology is defined as

$$BW = f_2 - f_1 \tag{4.9}$$

where  $f_2$  denotes the upper 1-dB frequency and  $f_1$  denotes the lower 1-dB frequency.

Since the imperfect normalized resistor  $r_{on}$  is much less than 1, to simplify the analysis, we

ignore the high-order terms of  $r_{on}$ . By substituting (4.3) into (4.8), the 1-dB bandwidth of the binary-tree type is obtained as follows:

$$BW_{a} = 2f_{0} \left( 1 - \frac{2}{\pi} \tan^{-1} \left[ \frac{5 + 18r_{on} + \sqrt{25 + 188r_{on}}}{2(1 - 12r_{on})} \right]^{1/2} \right)$$

(4.10)

Similarly, the 1-dB bandwidths of other topologies are

$$BW_{b} = 2f_{0} \left( 1 - \frac{2}{\pi} \tan^{-1} \left[ \frac{10 + 28r_{on} + \sqrt{110 + 448r_{on}}}{2(1 - 16r_{on})} \right]^{1/2} \right)$$

$$BW_{c} = 2f_{0} \left( 1 - \frac{2}{\pi} \tan^{-1} 4 \sqrt{\frac{1 + r_{on}}{1 - 16r_{on}}} \right)$$

$$BW_{d} = 2f_{0} \left( 1 - \frac{2}{\pi} \tan^{-1} \left[ \frac{5 + 18r_{on} + \sqrt{25 + 188r_{on}}}{2(1 - 12r_{on})} \right]^{1/2} \right)$$

$$(4.11)$$

$$(4.12)$$

From (4.10)–(4.13), the 1-dB bandwidths of binary-tree type ( $BW_a$ ) and ring-binary type ( $BW_d$ ) are the same.

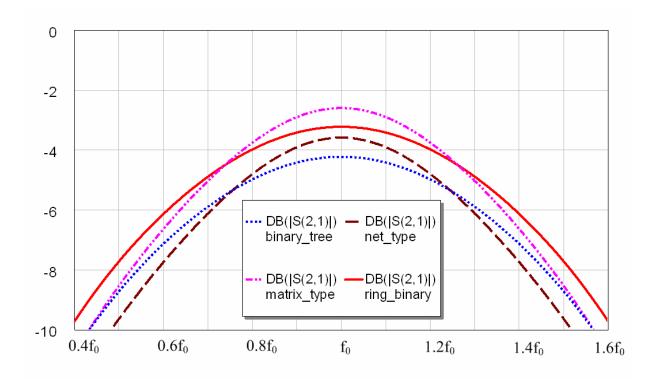

Fig. 4.4. Calculated frequency responses with respect to different topologies

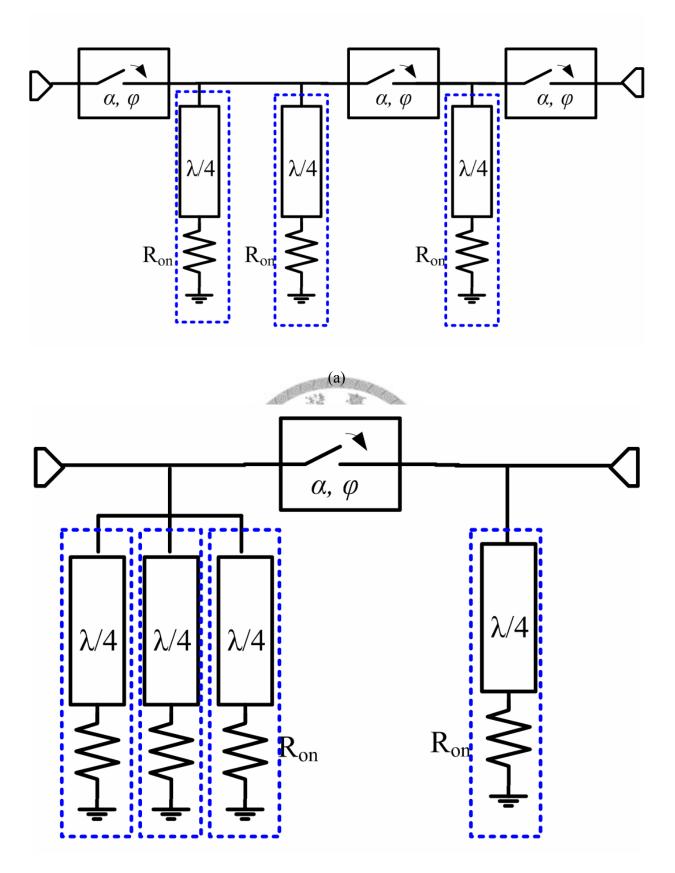

Frequency responses of different topologies for insertion loss and bandwidth according to (4.3)–(4.6) are plotted in Fig. 4.4. It is noted that, in Fig. 4.4,  $R_{on}$  is set to be 5 $\Omega$  in solving these equations, which is reasonable for an MMW switch in the GaAs HEMT process [25]. The loss  $\alpha$  of each unit switch is mainly affected by off-state capacitances of HEMTs. In solving these equations,  $\alpha$  is assumed to be 1 dB by considering that the reasonable  $C_{off}$  in the GaAs HEMT process [25] would lead to such an amount loss. From Fig. 4.4, we observe that the matrix type has the lowest insertion loss, and the binary-tree type has the highest insertion loss. The bandwidth of the binary-tree type and ring-binary type are better than the other two topologies. Owing to the severe loading effects, the bandwidths of the net type and matrix type are narrower than those of the other two types.

### 4.5 Isolations of Multiple-Port Topologies

Isolations can be approximately decided by the number of off-state unit switches that a signal undergoes from input port to output port, and this approximate evaluation would help a lot when we design switches. For the binary-tree type, the number of off-state unit switches between each port is one, two, or three. We denote the isolation that an off-state unit switch can provide as *ISO* (dB).

### 4.6 Summary of Topology Analysis

To implement a realistic multiple-port switch, the feasibility of layout should also be taken into consideration. There are more junctions and interconnect lines for binary-tree type, matrix type, and ring-binary type, and a larger chip area is required. The net type would be more compact since there is only a junction. It is observed that the net-type topology needs the least number of unit switches, only six, and the other topology requires eight unit switches.

Table 4.1 shows the comparison between different multiple-port switch topologies. Insertion loss, isolation, bandwidth, and the required number of unit switches are summarized. Each topology has its own merits. Since good isolation is much easier to achieve than low insertion loss, regardless of the greatest isolation of binary-tree type, we can find that the ring-binary-type topology is optimal for a broadband and low-loss multiple-port switch design. For narrowband multiple-port switch design, the net-type topology is adopted since the reduced number of composed unit switches would make this multiple-port switch much more compact than others.

#### Table 4.1

| Topology                | Binary-tree                               | Matrix type         | Net type             | Ring-binary          |

|-------------------------|-------------------------------------------|---------------------|----------------------|----------------------|

| Insertion loss          | $3\alpha + 3\beta_1$                      | $\alpha + 4\beta_1$ | $2\alpha + 4\beta_1$ | $2\alpha + 3\beta_1$ |

| Isolation               | $ISO, 2 \times ISO,$<br>or $3 \times ISO$ | ISO                 | ISO                  | ISO, or 2×ISO        |

| 1-dB bandwidth          | Broad (50%)                               | Narrow (30%)        | Narrow (30%)         | Broad (50%)          |

| Number of unit switches | 8                                         | 8                   | 6                    | 8                    |

#### SUMMARY OF DIFFERENT MULTIPLE-PORT SWITCH TOPOLOGY

# Chapter 5 Design of Millimeter-Wave Multiple-Port Switches

In this chapter, two MMW multiple-port switches using net-type topology and ring-binary-type topology, respectively, are realized to verify the analysis in chapter 4. The net-type multiple-port switch is designed by Dr. Shih-Fong Chao and the ring-binary-type multiple-port switch is designed by the author of this thesis.

### 5.1 MMIC Process

The process used in this design is WIN Semiconductors' 0.15-  $\mu$ m GaAs pHEMT. The HEMT device has a typical unit current gain cutoff frequency ( $f_T$ ) of higher than 85 GHz and maximum oscillation frequency ( $f_{max}$ ) of higher than 120 GHz at 1.5-V drain bias with peak dc transconductance ( $G_m$ ) of 495 mS/mm [44]. The gate–drain breakdown voltage is approximately 10 V, and the gate-to-source voltage at peak transconductance at 1.5-V drain–source voltage is 0.45 V.

These HEMTs are biased in the passive mode, and we model their passive small-signal equivalent circuit as on state and off state. The on-state model is represented as an inductor series with a resistor, and the off-state model is represented as an inductor series with a resistor and capacitor [27]. The gate of the on-state HEMT is biased at 0 V, and the gate of the off-state HEMT is biased at 3 V.

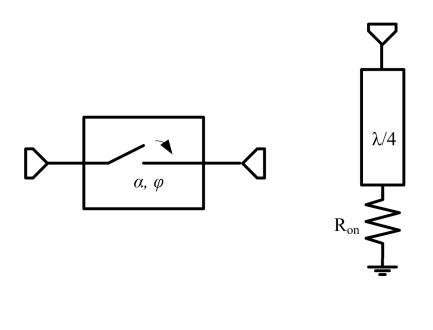

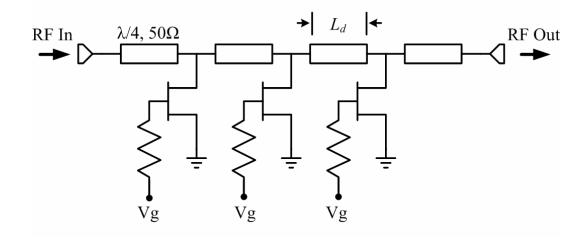

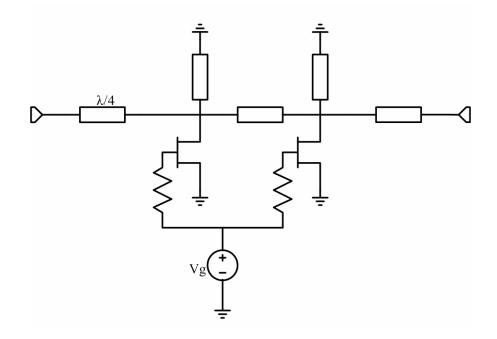

### 5.2 Design of Unit Switch Cells

The distributed unit switch with wideband characteristics [25] and a filter-integrated unit switch [32] are used for discussion in this section. A circuit schematic of the distributed unit switch is shown in Fig. 5.1. When the HEMTs are turned off, the periodically loaded off-state capacitor along with the inductive transmission line form an artificial transmission line of 50 $\Omega$  to pass the RF signal. When the HEMTs are turned on, the input node presents a low impedance. To form a multiple-port switch, a 50- $\Omega$  quarter-wavelength transmission line is needed to connect at the front of each SPST cell to transform from low impedance to high impedance at the isolated arm.