# 國立臺灣大學電機資訊學院電機工程學系

# 碩士論文

Department of Electrical Engineering

College of Electrical Engineering and Computer Science

National Taiwan University

Master Thesis

主動箝位電流饋入型雙主動橋式轉換器 之雙向控制策略

Bidirectional Control Strategy for Active-clamp Current-fed Dual Active Bridge Converters

> 葉昶均 Chang-Chun Yeh

指導教授: 陳耀銘 博士

Advisor: Yaow-Ming Chen, Ph.D.

中華民國 111 年 6 月

June, 2022

# 國立臺灣大學碩士學位論文口試委員會審定書

主動箝位電流饋入型雙主動橋式轉換器之雙向控制策略

Bidirectional Control Strategy for Active-clamp Current-fed Dual Active Bridge Converters

本論文係 葉昶均 君(學號 R09921034)在國立臺灣大學電機工程學 系完成之碩士學位論文,於民國 111 年 6 月 29 日承下列考試委員審查通 過及口試及格,特此證明。

口試委員:

持行者

系主任

文· 大·

# 致謝

首先,我要感謝我的指導教授 <u>陳耀銘</u> 教授,自我大三進入 EERPO 做專題開始,老師便提供我很多方面的協助,不論是學術方面的建議,專業課目修課的建議,或是獎助學金的申請,都受到老師很多的幫忙。也感謝口試委員 <u>陳偉倫</u> 教授、<u>陳</u>景然 教授、<u>楊士進</u> 教授、<u>唐丞譽</u> 教授及 <u>黃仁宏</u> 教授在口試時提供的寶貴意見,讓這篇論文的內容與質量更加完美。

接著,我要感謝 EERPO 實驗室的各位。感謝同屆同學 <u>承翰、哲彥、佳宜、念</u> 廷和<u>新甯</u>,在這兩年的時間裡,一起修課,一起討論,一起完成很多事情。感謝博 班學長 <u>元昭、文田、俊宏、騰緯、景傑、嘉洲、承戰</u>與 <u>Irham Fadlika</u>,在這兩年 的研究生生涯中,提供很多專業的資訊。感謝學長姐 <u>皓鈞、亦涵、蕙瀅、孟鈞、</u> 振嘉及博望,帶我更快熟悉研究事務。感謝學弟妹 <u>佳銘、文彥、學儒、志誠與家</u> 盈,負責實驗室許多事務。在此之中,我要特別感謝 DAB 組的成員 <u>承戰、蕙瀅、</u> 念廷,感謝承戰跟<u>蔥營</u>在這兩年來帶我們做實驗與分析數據,也藉由不斷的討論發 想出主題,感謝<u>念廷</u>跟我一起嘗試很多實驗,讓我更加精進實驗的能力。

最後,我想感謝這兩年來在身邊支持我的人,感謝我的家人繼續支持我讀研究所,在我遇到困難或煩惱時,只要一通電話或是一張車票,就能讓我再度充電再戰。感謝我的女友<u>芷薇</u>的陪伴,為這兩年的碩士生活留下許多特別的回憶。感謝我國高中與大學的朋友,認識這麼多年了,偶爾的吃飯或是出門走走,讓這兩年的研究生活增添不少樂趣。感謝台大鄉村服務社的朋友,儘管大家多已經畢業或不再參加社團活動,也會藉由半年一次的探營互相聚聚,一起見證社團新一代的轉變。

這兩年來受到許多人的幫忙,在此再次向各位說聲謝謝。之後大家也都開始進入不同的階段,我也要開始從學生轉變成上班族。在此先預祝大家之後身體健康,萬事如意,之後能再一起聚聚,謝謝各位。

# 摘要

本論文提出一個適用於主動箝位電流饋入型雙主動橋式轉換器(Active-clamped current-fed dual active bridge, AC-CFDAB)的雙向控制策略,透過雙重相位移的控制實現雙向能量傳輸,並擁有比現行調變方式更好的換向暫態,同時也可以讓電路操作在當前輸出功率下的最大效率點。

AC-CFDAB 的低壓側連波小且可以達到雙向能量傳輸,非常適合用於電池儲 能應用於低壓側電源的場合。然而,現階段對於實現軟切換的開關調變方法研究多 只適用於單向的能量傳輸,雙向操作需要涉及兩個不同控制方法的轉換,若是兩個 控制方式差異過大,換向瞬間的暫態突波會十分明顯,嚴重時會損壞整體電路。

本文首先提出一個可以實現雙向能量傳輸的修改型雙重相位移的開關調變方式,由於在雙向操作時並不需要變換調變方式,可以大幅降低改變功率流向操作時的暫態突波。同時只要設定足夠的停滯時間,全部的開關都可以實現零電壓切換。此外,雙重相位移也提供更高的控制自由度,除了傳輸能量之外,轉換效率也有機會被提升。本論文透過對雙重相位移的解耦合與相關分析,提出可以達到最大效率操作點的雙向控制策略。

為了驗證所提控制策略的正確性,本論文實作一組 48V/400V,720W 的原型電路。電腦模擬與實驗結果皆符合驗證所提控制策略的正確性。

關鍵字: 主動箝位電流饋入型雙主動橋式轉換器, 雙重相位移控制, 零電壓切換, 最大效率追蹤

## **ABSTRACT**

This thesis proposes a bidirectional control strategy for the active-clamped current-fed dual active bridge(AC-CFDAB) converter. By controlling the dual phase-shifts, the bidirectional power transmission can be achieved, the bidirectional transient is better than conventional modulation methods, and the maximum efficiency point can be tracked.

The AC-CFDAB converter has the small low-voltage-side current ripple and the ability of bidirectional power transmission, which is very suitable for energy storage applications. However, research of soft switching modulation method listed in literature only focus on the unidirectional power transmission. Two different modulation methods are required to achieve the bidirectional power transmission. Usually, an obvious current spike will be generated during the transition of the two modulation mothods. In the worst case, the converter may be damaged.

This thesis first proposes a modified dual-phase-shift modulation(MDPSM) method for the bidirectional operation of the AC-CFDAB. Since there is no change of the modulation method for MDPSM, the current spike of the bidirectional operation transient can be mitigated dramatically. Also, the zero-voltage-switching feature for all the switches can be achieved by adding the proper deadtime. Additionally, the control of dual-phase-shift provides an additional degree of freedom to control, so that improve the efficiency of the converter. In this thesis, the proposed MDPSM is used to realize the maximum efficiency tracking of the converter.

To validated the performance of the proposed MSPSM modhod, a 48V/400V, 720W AC-CFDAB prototype is built and tested. Computer simulations and experiment results are provided to the performance of the AC-CFDAB with the proposed MDPSM method.

Keywords: dual active bridge converter, daul-phase-shift control, zero voltage switching, maximum efficiency point tracking

v

# 目錄

| 口試委員審定書                                  |     |

|------------------------------------------|-----|

| 致謝                                       | ii  |

| 摘要                                       | iii |

| ABSTRACT                                 | iv  |

| 目錄                                       | V   |

| 圖目錄                                      | vii |

| 表目錄                                      | xi  |

| Chapter 1 Introduction                   | 1   |

| 1.1 Background                           | 1   |

| 1.2 Paper Review and Motive              | 2   |

| 1.3 Outline                              | 3   |

| Chapter 2 MDPSM for AC-CFDAB             | 5   |

| 2.1 Introduction to AC-CFDAB             | 5   |

| 2.1.1 AC-CFDAB Topology                  | 5   |

| 2.1.2 Existing Modulation Methods        | 7   |

| 2.2 Modified Dual Phase Shift Modulation | 9   |

| 2.2.1 Modulation Method                  | 10  |

| 2.2.2-Circuit Operation                  | 13  |

| 2.2.3 ZVS Condition                      | 20  |

| 2.3 Power Transmission Control           | 27  |

| 2.4 Bidirectional Transient Response     | 31  |

| Chapter 3 Power Efficiency Improvement   | 34  |

| 3.1 Efficiency Equation                  | 34  |

| 3.2 Maximum Efficiency Point Tracking Strategy     |     |

|----------------------------------------------------|-----|

| 3.2.1 Operation region                             | 41  |

| 3.2.2 Efficiency Analysis                          | 43  |

| 3.2.3 Strategy Scheme                              |     |

| 3.3 Parameter Design                               | 48  |

| Chapter 4 Hardware Implement                       | 49  |

| 4.1 Hardware Design                                | 49  |

| 4.1.1 Power Stage Circuits                         | 50  |

| 4.1.2 Control Stage Circuits                       | 56  |

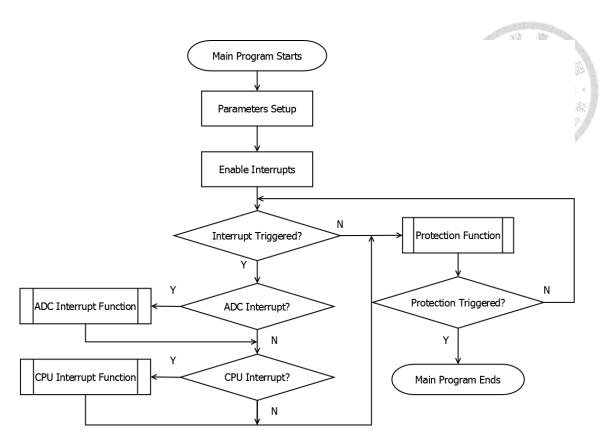

| 4.2 DSP Program                                    | 61  |

| 4.2.1 Main Program                                 | 61  |

| 4.2.2 Interrupt Functions                          | 64  |

| Chapter 5 Simulation and Experimental Verification | 67  |

| 5.1 Test Environment                               | 67  |

| 5.2 Steady-state Waveforms                         | 69  |

| 5.3 Bidirectional Transient                        | 88  |

| 5.4 Maximum Efficiency Point Tracking Strategy     | 92  |

| Chapter 6 Conclusion and Future Work               | 99  |

| 6.1 Summary                                        | 99  |

| 6.2 Future Works                                   | 100 |

| REFERENCES                                         | 101 |

# 圖目錄

| Fig. 1.1 DC microgrid system.                                      |       |

|--------------------------------------------------------------------|-------|

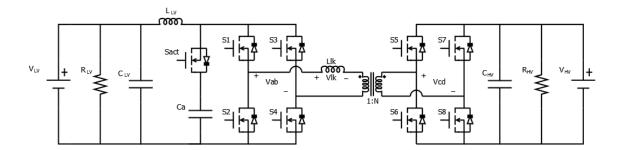

| Fig. 2.1 Topology of a AC-CFDAB converter                          | 要。學學5 |

| Fig. 2.2 Key waveform in ZVZCS modulation.                         | 8     |

| Fig. 2.3 Key waveform in SSM.                                      | 9     |

| Fig. 2.4 Key LVS waveform in MDPSM.                                | 11    |

| Fig. 2.5 Key HVS waveform in MDPSM.                                | 12    |

| Fig. 2.6 Key waveform in MDPSM.                                    | 13    |

| Fig. 2.7 Mode I in buck operation.                                 | 14    |

| Fig. 2.8 Mode II in buck operation.                                | 15    |

| Fig. 2.9 Mode III in buck operation.                               | 17    |

| Fig. 2.10 Mode IV in buck operation.                               | 18    |

| Fig. 2.11 Mode I in boost operation.                               | 19    |

| Fig. 2.12 Mode II in boost operation.                              | 19    |

| Fig. 2.13 Mode III in boost operation.                             | 20    |

| Fig. 2.14 Mode IV in boost operation.                              | 20    |

| Fig. 2.15 Deadtime setting in MDPSM.                               | 21    |

| Fig. 2.16 Equivalent resonant model.                               | 22    |

| Fig. 2.17 Nonideal transformer circuit.                            | 25    |

| Fig. 2.18 Modified nonideal transformer circuit.                   | 26    |

| Fig. 2.19 Power transmission in MDPSM.                             | 30    |

| Fig. 2.20 Bidirectional transient response of boost-buck operation | 31    |

| Fig. 2.21 Bidirectional transient response of buck-boost operation | 32    |

| Fig. 2.22 Leakage current waveform between SSM and MDPSM           | 33    |

|                                                                | 161616161616162 |

|----------------------------------------------------------------|-----------------|

| Fig. 3.1 Related waveform in efficiency equation               | 35              |

| Fig. 3.2 Switching transient behavior in [35].                 | 37              |

| Fig. 3.2 Operation region of D2.                               | 43              |

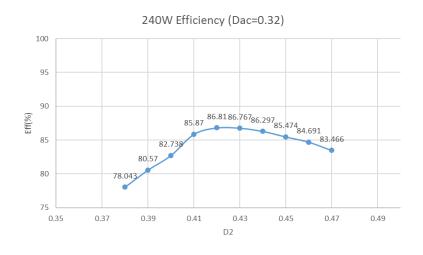

| Fig. 3.3 Relationship between D2 and efficiency with 240W case |                 |

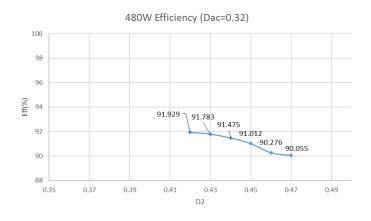

| Fig. 3.4 Relationship between D2 and efficiency with 480W case | 45              |

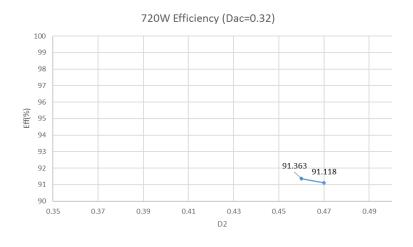

| Fig. 3.5 Relationship between D2 and efficiency with 720W case | 45              |

| Fig. 3.6 Control scheme for MEPT                               | 46              |

| Fig. 3.7 Control scheme for IL control loop.                   | 46              |

| Fig. 3.8 Control flowchart for efficiency control loop.        | 47              |

| Fig. 4.1 LVS power board                                       | 50              |

| Fig. 4.2 HVS power board                                       | 51              |

| Fig. 4.3 LVS driver board                                      | 52              |

| Fig. 4.4 HVS driver board                                      | 53              |

| Fig. 4.5 Driver circuit model in [39].                         | 54              |

| Fig. 4.6 Voltage sensing circuit                               | 56              |

| Fig. 4.7 Current sensing circuit.                              | 59              |

| Fig. 4.8 Control flowchart for main program.                   | 62              |

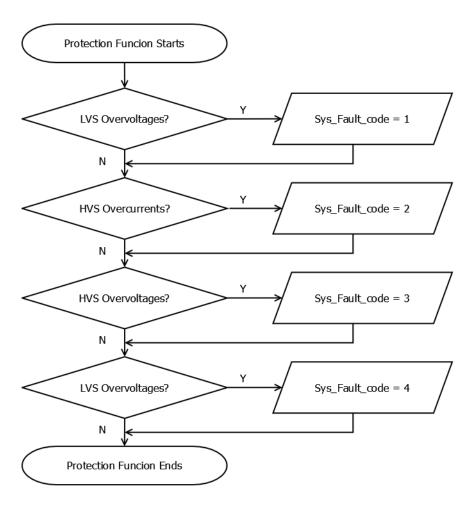

| Fig. 4.9 Control flowchart for protection function.            | 63              |

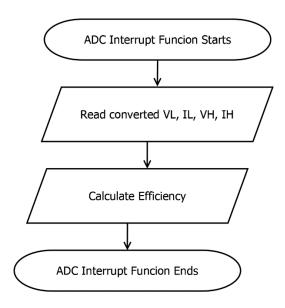

| Fig. 4.10 Control flowchart for ADC interrupt function         | 64              |

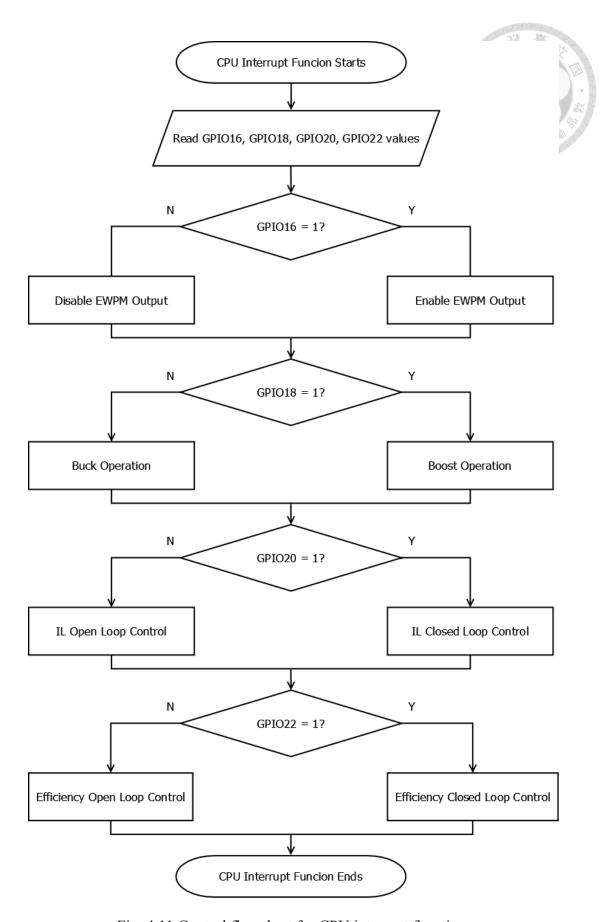

| Fig. 4.11 Control flowchart for CPU interrupt function         | 66              |

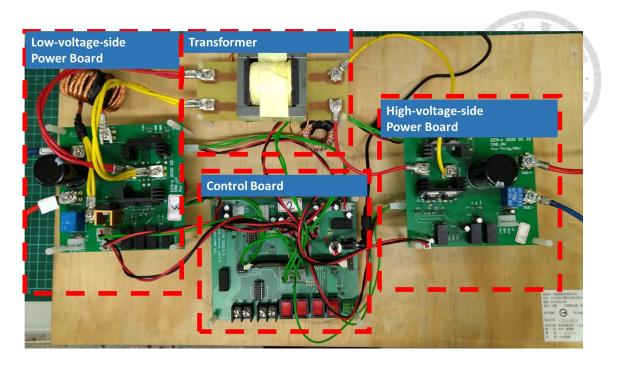

| Fig. 5.1 Test environment of the experiment.                   | 67              |

| Fig. 5.2 Photo of the hardware circuit.                        | 68              |

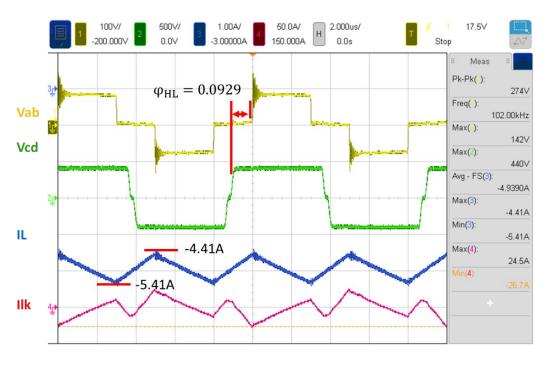

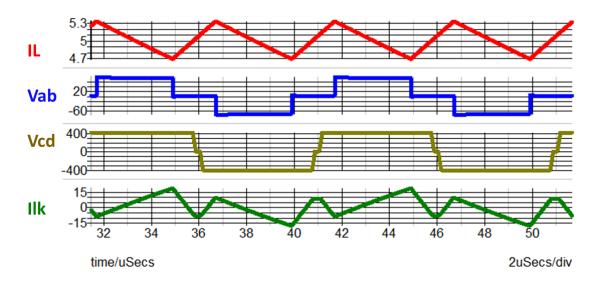

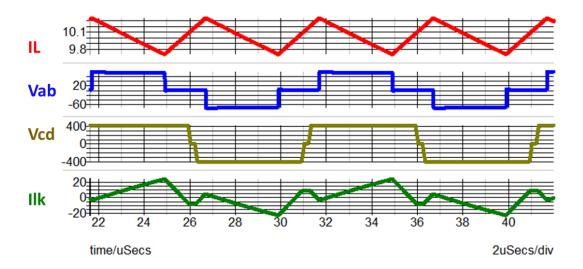

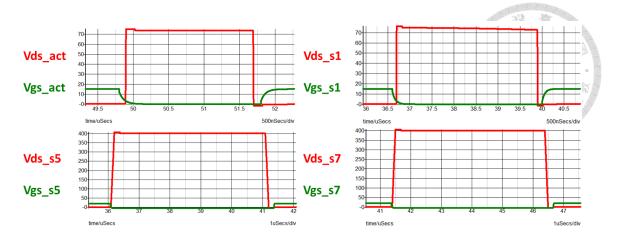

| Fig. 5.3 Simulation result of -240W steady-state waveform      | 70              |

| Fig. 5.4 Experiment result of -240W steady-state waveform      | 70              |

| Fig. 5.5 Simulation result of -240W ZVS waveform.              | 72              |

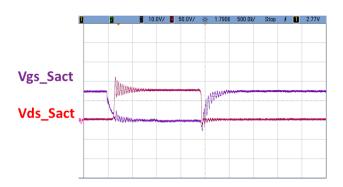

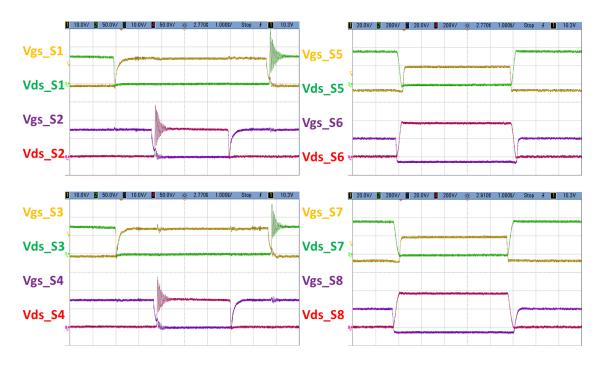

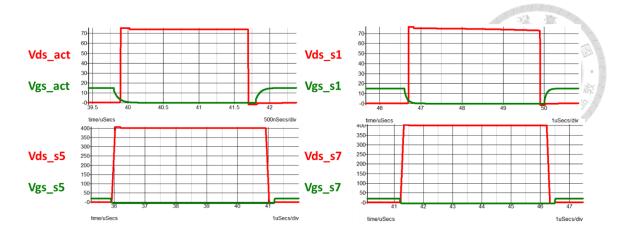

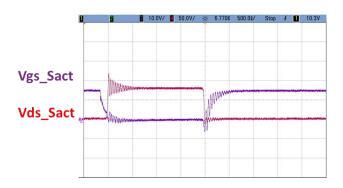

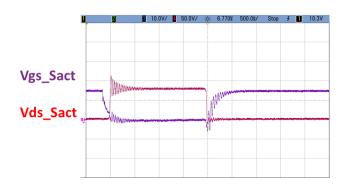

| Fig. 5.6 Experiment result of -240W Sact ZVS waveform.         | 111 |

|----------------------------------------------------------------|-----|

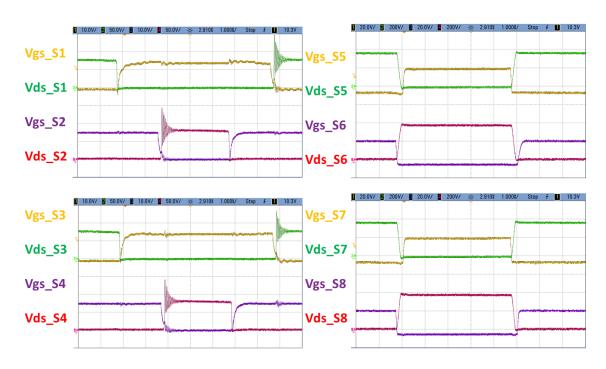

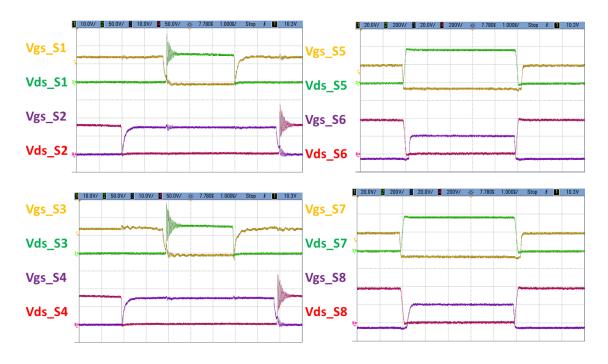

| Fig. 5.7 Experiment result of -240W SLV and SHV ZVS waveform.  | 72  |

| Fig. 5.8 Simulation result of -480W steady-state waveform.     | 73  |

| Fig. 5.9 Experiment result of -480W steady-state waveform.     | 73  |

| Fig. 5.10 Simulation result of -480W ZVS waveform.             | 75  |

| Fig. 5.11 Experiment result of -480W Sact ZVS waveform.        | 75  |

| Fig. 5.12 Experiment result of -480W SLV and SHV ZVS waveform. | 75  |

| Fig. 5.13 Simulation result of -720W steady-state waveform     | 76  |

| Fig. 5.14 Experiment result of -720W steady-state waveform.    | 76  |

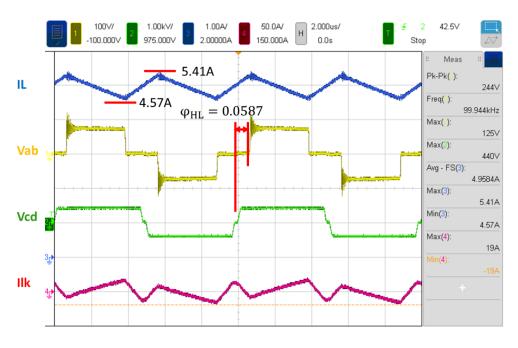

| Fig. 5.15 Simulation result of -720W ZVS waveform.             | 78  |

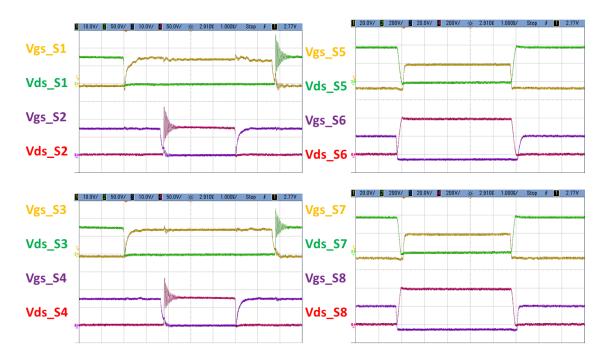

| Fig. 5.16 Experiment result of -720W Sact ZVS waveform.        | 78  |

| Fig. 5.17 Experiment result of -720W SLV and SHV ZVS waveform. | 78  |

| Fig. 5.18 Simulation result of 240W steady-state waveform.     | 79  |

| Fig. 5.19 Experiment result of 240W steady-state waveform.     | 79  |

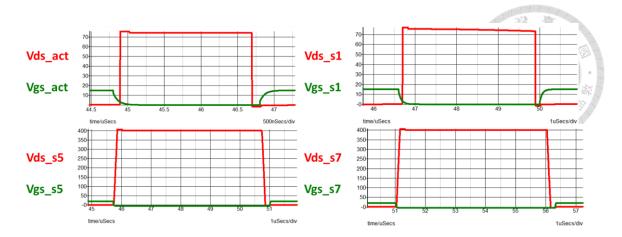

| Fig. 5.20 Simulation result of 240W ZVS waveform.              | 81  |

| Fig. 5.21 Experiment result of 240W Sact ZVS waveform          | 81  |

| Fig. 5.22 Experiment result of 240W SLV and SHV ZVS waveform   | 81  |

| Fig. 5.23 Simulation result of 480W steady-state waveform.     | 82  |

| Fig. 5.24 Experiment result of 480W steady-state waveform.     | 82  |

| Fig. 5.25 Simulation result of 480W ZVS waveform.              | 84  |

| Fig. 5.26 Experiment result of 480W Sact ZVS waveform          | 84  |

| Fig. 5.27 Experiment result of 480W SLV and SHV ZVS waveform   | 84  |

| Fig. 5.28 Simulation result of 720W steady-state waveform.     | 85  |

| Fig. 5.29 Experiment result of 720W steady-state waveform.     | 85  |

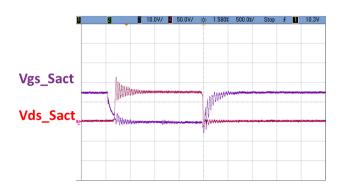

| Fig. 5.30 Simulation result of 720W ZVS waveform.              | 87  |

| Fig. 5.31 Experiment result of 720W Sact ZVS waveform          |    |

|----------------------------------------------------------------|----|

| Fig. 5.32 Experiment result of 720W SLV and SHV ZVS waveform   | 87 |

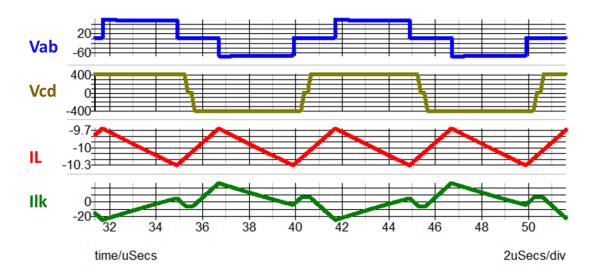

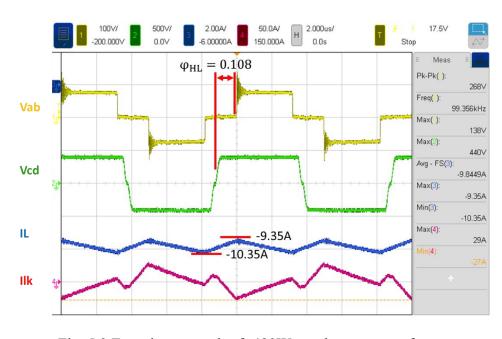

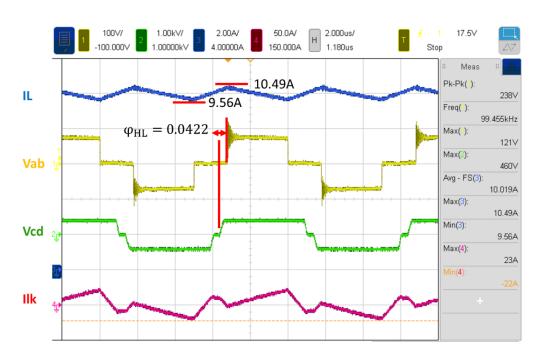

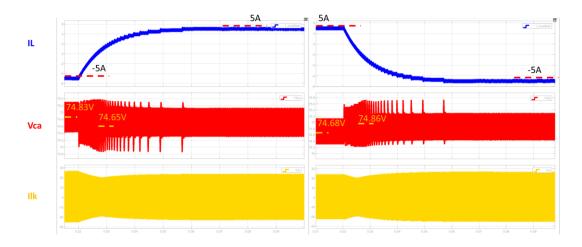

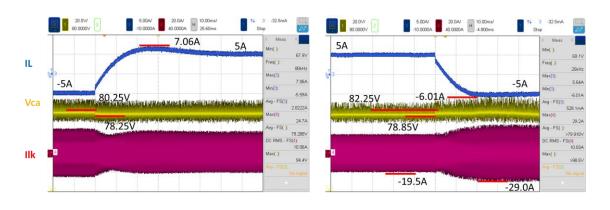

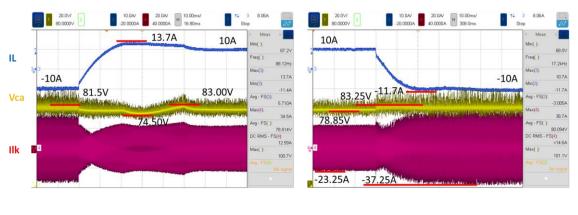

| Fig. 5.33 Simulation result of 240W bidirectional transient.   | 89 |

| Fig. 5.34 Experiment result of 240W bidirectional transient.   | 89 |

| Fig. 5.35 Simulation result of 480W bidirectional transient.   | 90 |

| Fig. 5.36 Experiment result of 480W bidirectional transient.   | 90 |

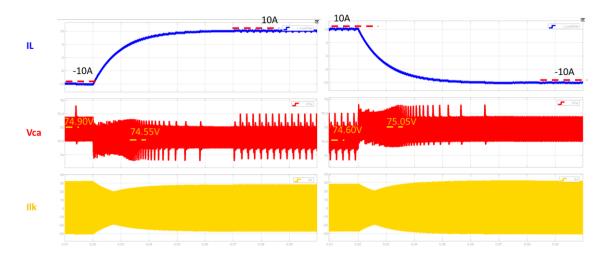

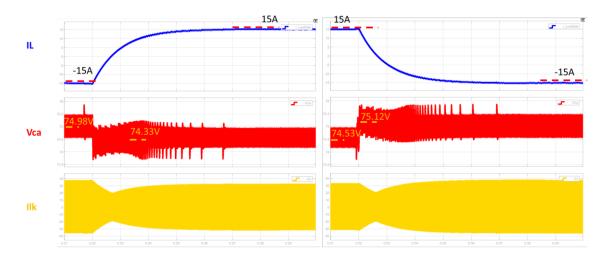

| Fig. 5.37 Simulation result of 720W bidirectional transient.   | 91 |

| Fig. 5.38 Experiment result of 720W bidirectional transient.   | 91 |

| Fig. 5.36 Experiment results of -240W efficiency control loop  | 93 |

| Fig. 5.37 Efficiency versus D2 chart in -240W case.            | 93 |

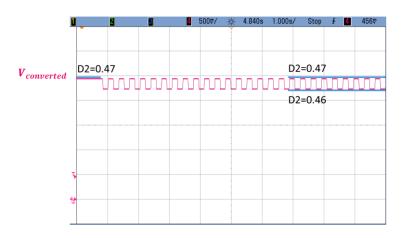

| Fig. 5.38 Experiment results of -480W efficiency control loop. | 94 |

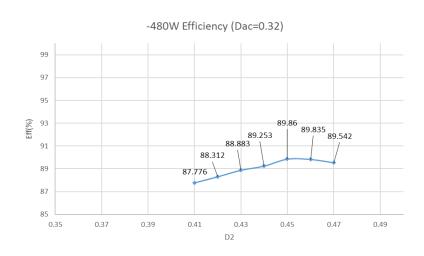

| Fig. 5.39 Efficiency versus D2 chart in -480W case.            | 94 |

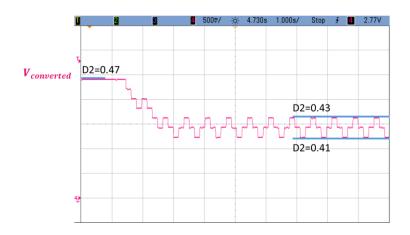

| Fig. 5.40 Experiment results of -720W efficiency control loop. | 95 |

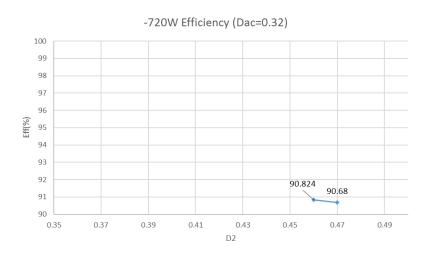

| Fig. 5.41 Efficiency versus D2 chart in -720W case.            | 95 |

| Fig. 5.42 Experiment results of 240W efficiency control loop.  | 96 |

| Fig. 5.43 Efficiency versus D2 chart in 240W case.             | 96 |

| Fig. 5.44 Experiment results of 480W efficiency control loop.  | 97 |

| Fig. 5.45 Efficiency versus D2 chart in 480W case.             | 97 |

| Fig. 5.46 Experiment results of 720W efficiency control loop.  | 98 |

| Fig. 5.47 Efficiency versus D2 chart in 720W case.             | 98 |

# 表目錄

| Table 2.1 Variables of ZVS condition for each switch.    |    |

|----------------------------------------------------------|----|

| Table 4.1 System specification.                          | 49 |

| Table 4.2 Transformer parameter.                         |    |

| Table 4.3 Design parameters of Sallen-Key filter         | 58 |

| Table 5.1 Comparing steady-state results in -240W case.  | 71 |

| Table 5.2 Comparing steady-state results in -480W case.  | 74 |

| Table 5.3 Comparing steady-state results in -720W case.  | 77 |

| Table 5.4 Comparing steady-state results in 240W case.   | 80 |

| Table 5.5 Comparing steady-state results in 480W case.   | 83 |

| Table 5.6 Comparing steady-state results in 720W case.   | 86 |

| Table 5.7 Contol parameters of the PI controller.        | 88 |

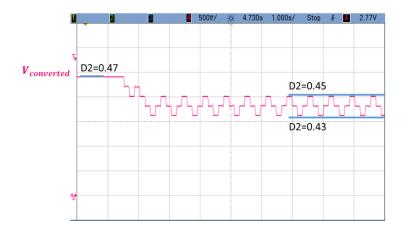

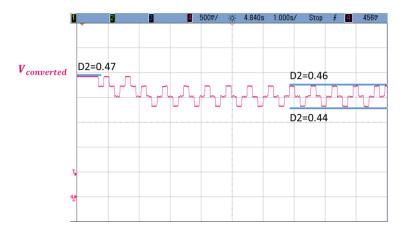

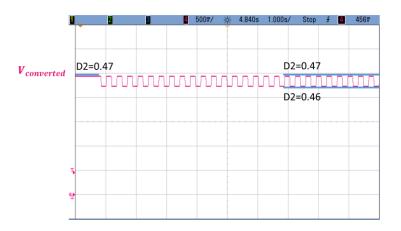

| Table 5.8 Relationshiop between D2 and converted voltage | 92 |

# **Chapter 1 Introduction**

# 1.1 Background

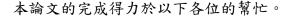

Nowadays, the necessity for renewable energy is gradually increasing. Due to the instability of renewable energy, battery energy storage systems(BESSs) are developed to increase the stability of the systems [1] - [5]. To transfer the energy between BESS and the DC bus, bidirectional dc-dc converters(BDCs) are brought into focus in recent years [6] - [10].

Fig. 1.1 DC microgrid system.

There are many topologies of BDCs, such as bidirectional buck converter [11], bidirectional buck-boost converter [12], bidirectional Ćuk converter [13], and so on. To assure more safety and the higher voltage gain ratio, isolated bidirectional dc-dc converters(IBDCs) are also considered. The conventional topologies of IBDCs include bidirectional push-pull converter [14], bidirectional flyback converter [15], dual half bridge converter [16], and dual active bridge(DAB) converter [17]. Among all topologies above, DAB converter is a popular choice with many advantages. For instance, the isolated topology of DAB provides higher safety than non-isolated BDCs, and DAB has

the wider voltage gain ratio compared to the dual half bridge converter. The transformer in DAB can be regarded as a resonant tank, which can achieve soft switching in some cases and increase efficiency [18]. With these features above, DAB converters have attracted a lot of attention in BESS [19].

DAB has two types by its sources. One is the voltage-fed (VF) DAB with two voltage sources. There is a lot of research about VFDAB. In [20] – [23] propose several modulation methods, namely single–phase-shift(SPS) control, extended-phase-shift(EPS) control, dual-phase-shift(DPS) control, and triple-phase-shift(TPS) control. To enhance the ability of soft switching, modified topologies are considered in [24] – [26]. However, VFDAB generates the huge input current ripple, which is harmful to batteries. In BESS, another type of DAB, named current-fed (CF) DAB, is always applied [27].

The topology of CFDAB includes one current source and one voltage source. With this topology, the current ripple can be smaller than VFDAB, which is more suitable in BESS. However, a new challenge caused by the imbalance current is a crucial issue for CFDAB. In [28], several modified topologies, such as L-L type CFDAB and active-clamped(AC) CFDAB, are studied. Also, a naturally-clamped method is introduced in [29]. Compare to all the solutions above, AC-CFDAB is a popular choice with the benefit of the simple and easy-controlled topology.

# 1.2 Paper Review and Motive

Most of the research about AC-CFDAB focuses on the soft switching modulation method. In [30], a primary-side modulation method is provided to achieve zero-voltage switching(ZVS) for all primary-side switches in buck operation. Regarding the use of IGBTs, a ZVZCS primary-side modulation method for buck operation is given in [31]. And [32] and [33] propose a synchronous rectified ZVZCS modulation method for buck

operation and a ZVS modulation method for boost operation. New ZVS modulation methods for buck and boost operation respectively are proposed in [34].

However, soft switching modulation methods proposed in [30] – [34] are just suitable for only buck or boost mode. For the bidirectional operation which involving in switching between buck and boost modes, two different modulation modes should be used. Bad switching transient, named the bidirectional transient, would be generated if the difference between buck and boost modulation methods is huge, which would be harmful to the circuit [34].

In this thesis, the bidirectional transient is improved by proposing a new bidirectional modulation method, named modified dual-phase-shift modulation(MDPSM). ZVS for all switches can also be achieved with proper setting. To regard more the efficiency, a maximum efficiency point tracking strategy(MEPT) is proposed based on MDPSM. With this strategy, a high-efficiency bidirectional power flow can be realized.

## 1.3 Outline

This thesis is organized into six chapters. Each chapter is introduced in the following.

In Chapter 2, AC-CFDAB is first introduced, including its topology and conventional modulation methods. Then, MDPSM, which can improve the bidirectional transient, is proposed. In addition, steady-state analysis and bidirectional transient are analyzed in the following sections.

In Chapter 3, the power efficiency is taken into account. MEPT based on MDPSM is proposed. The equations of efficiency are first introduced, followed by the introduction of MEPT. The design process is shown in the last section.

In Chapter 4, the hardware implement of rated 720W AC-CFDAB is introduced.

Details of the hardware circuit and the DSP program are shown in this chapter.

In Chapter 5, simulation and experiment results are shown. Steady-state waveform of MDPSM, bidirectional transient of MDPSM, and MEPT are verified and discussed in this chapter.

In Chapter 6, the conclusion and the major contribution are summarized. The future works are also listed in this chapter.

# **Chapter 2 MDPSM for AC-CFDAB**

In this chapter, details of the AC-CFDAB are introduced. In section 2.1, some basic information about AC-CFDAB is reviewed. Section 2.2 introduces the new proposed modified dual-phase-shift modulation(MDPSM) for AC-CFDAB, followed by the power transmission analysis in section 2.3. In section 2.4, the analysis of the bidirectional operation transient is in the end.

## 2.1 Introduction to AC-CFDAB

In this section, some crucial information including the topology and conventional modulation methods of AC-CFDAB is introduced. In subsection 2.1.1, the topology for AC-CFDAB is introduced. And the existing modulation methods are mentioned in subsection 2.1.2.

# 2.1.1 AC-CFDAB Topology

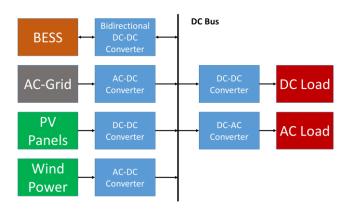

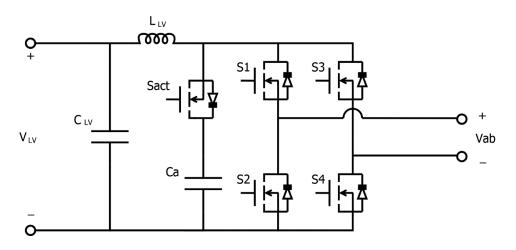

AC-CFDAB is composed of two active bridges, a large low-voltage-side inductor,  $L_{\rm LV}$ , an active clamp circuit, and a transformer. The detailed topology for AC-CFDAB is shown in Fig. 2.1.

Fig. 2.1 Topology of a AC-CFDAB converter.

The two voltage sides can be classified into "low-voltage-side(LVS)" and "high-voltage-side(HVS)" by the voltage. In general, LVS is always the current-fed side with a LVS inductor,  $L_{LV}$ , and the active clamp circuit. The main reason is that batteries prefer to lower voltage and lower current ripple side. In addition, the voltage-side is always in HVS.

After defining the voltage sides, operation modes are defined by the power flow. "Buck operation" means that the power flow is from HVS to LVS, while "boost operation" means that the power is transferred from LVS to HVS. Bidirectional operation means that the operation is changing from buck operation to boost operation or boost operation to buck operation.

$S_1 \sim S_4$  are named LVS switches( $S_{LV}$ ), while  $S_5 \sim S_8$  are called HVS switches( $S_{HV}$ ). In  $S_{LV}$ , upper and lower arm switches can turn on simultaneously to provide a current path for  $L_{LV}$ . However,  $S_{HV}$  should prevent that from shoot-through. Also, some key waveforms of  $S_{LV}$  and  $S_{HV}$  are different, so they are discussed separately in this thesis.

In  $S_{HV}$ , "leading-leg" and "lagging-leg" can be defined by the sequence of the turnon time. For instance, in the positive half cycle,  $S_5$  turns on earlier than  $S_8$ , so  $S_5$  is the leading-leg switch,  $S_{HV,lead}$ , and  $S_8$  is the lagging-leg switch,  $S_{HV,lag}$ . In this thesis,  $S_5$ and  $S_6$  are defined to the leading-leg switches, whereas  $S_7$  and  $S_8$  are the lagging-leg switches.

An active clamp circuit is composed of a switch,  $S_{\rm act}$ , and a capacitor,  $C_{\rm a}$ . The main purpose of active clamp circuit is to absorb the imbalance current between  $L_{\rm LV}$  and  $L_{lk}$ . It can be found that when  $S_{LVs}$  turn on,  $L_{\rm LV}$  and  $L_{lk}$  are connected together. To prevent from the huge voltage spike by the imbalance current, the active clamp circuit should be

placed.

An AC-CFDAB also contains a transformer. The main purpose of the transformer is to isolate the two voltage sides and enhance the voltage gain. In the following analysis, the leakage inductor,  $L_{lk}$ , and magnetic inductor,  $L_m$ , are taken into consideration. And the voltages of each side,  $V_{ab}$  and  $V_{cd}$ , play important roles in MDPSM.

## 2.1.2 Existing Modulation Methods

With the previous introduction of AC-CFDAB, it can be found that control methods for  $S_{LVs}$  and  $S_{HVs}$  are different. Upper and lower arms of  $S_{LVs}$  are able to turn on together due to the current-fed topology in LVS, so the common control method for  $S_{LVs}$  is the duty cycle control. However, since HVS is voltage-fed, upper and lower arms of  $S_{HVs}$  should prevent from shoot-through. The common control method for  $S_{HVs}$  is the phase shift control. With duty cycle control for LVS and phase shift control for HVS, there are some modulation methods for the two voltage sides to control the power flow of AC-CFDAB.

The modulation method, named ZVZCS modulation, is early proposed in [30] – [33]. In ZVZCS modulation, only one-voltage-side switches are controlled, while the other voltage side switches just provide the current path through their body diodes. For example, only  $S_{LVS}$  are controlled in boost mode, while  $S_{LVS}$  are the only control parameters in buck mode. The features of ZVZCS modulation are that soft-switching can be achieved in all controlled switches. In buck mode, ZCS can be achieved in  $S_{HV,lag}$ , and ZVS can be achieved in  $S_{HV,lead}$  and  $S_{act}$ . In boost mode, ZVS can be achieved in all  $S_{LVS}$  and  $S_{act}$ . The key waveform of the ZVZCS modulation is shown in Fig. 2.2.

Fig. 2.2 Key waveform in ZVZCS modulation.

In order to pursue higher efficiency, synchronous rectified(SR) technology is applied. However, to prevent from shoot-through with  $S_{act}$ , ZVZCS modulation has some limits in realizing SR. Some switches should turn on and turn off twice in a period, which is complex to generate switching signals. In [34], a secondary-side modulation(SSM) is proposed to solve this problem. In SSM, all of the switches, including  $S_{LV}$  and  $S_{HV}$ , are controlled, and the power flow is controlled by the HVS phase shift. Also, all switches can achieve ZVS with proper deadtime. The key waveform of SSM is shown in Fig. 2.3. However, the challenge in commuting operation is discussed in [34]. The main reason is that the control methods for switches are a little different between buck and boost modes, which causes poor transient when changing two different operation modes. To solve this problem, MDPSM is proposed in the next section.

Fig. 2.3 Key waveform in SSM.

## 2.2 Modified Dual Phase Shift Modulation

Dual Phase Shift Modulation (DPSM) is a very popular modulation method for VFDAB. The earliest concept of DPSM is first proposed in [35], and is used in VFDAB in [36]. The main concept of DSPM is that the total circuit is controlled by two phase shift, phase shift of  $S_{HV}$  and phase shift between  $S_{LV}$  and  $S_{HV}$ . This concept is also used to CFDAB in [37], but hasn't been used to AC-CFDAB at present.

In this section, Modified Dual Phase Shift Modulation (MDPSM), based on conventional DPSM, for AC-CFDAB is proposed. The feature of MDPSM is that it can achieve bidirectional operation without setting buck and boost modes dividedly, so bidirectional transient can be obviously improved. In subsection 2.2.1, the details of the modulation are introduced. Circuit operation is illustrated in subsection 2.2.2, power transmission is analyzed in subsection 2.2.3, and the ZVS condition is discussed in

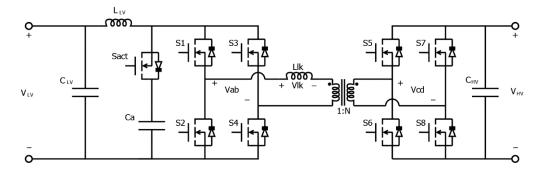

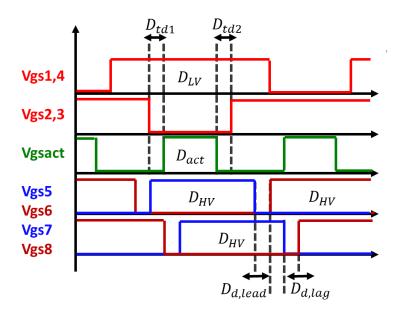

#### 2.2.1 Modulation Method

In this subsection, the switch modulation of MDPSM is proposed. The modulation of each part is introduced in the following.

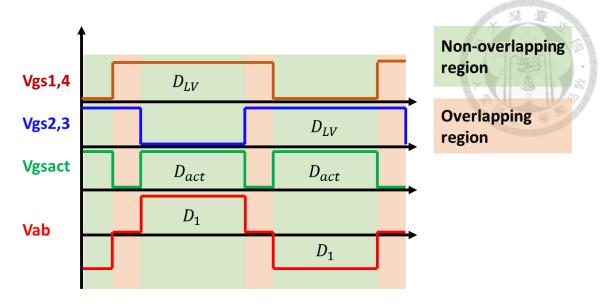

## (a) LVS modulation

In  $S_{LVs}$ , the duty cycles of  $S_{LVs}$ ,  $D_{LV}$ , are all the same and fixed.  $S_{LVs}$  have the same switching status with the diagonal switches and 180° phase difference between the adjacent switches. That is,  $S_1$  turns on and off together with  $S_4$ , and has 180° phase difference with  $S_2$  and  $S_3$ . Also, in order to provide a continuous current path in LVS,  $D_{LV}$  should be larger than 0.5, which generates a period named "overlapping region" that all  $S_{LVs}$  turn on. Besides, the "non-overlapping region" is the period that just two  $S_{LVs}$  turn on.

$S_{\rm act}$  should turn on to absorb imbalance current in the non-overlapping region because  $L_{\rm LV}$  and  $L_{lk}$  are connected together in that region. And  $S_{\rm act}$  must turn off in the overlapping region to prevent the active clamp capacitor, Ca, from shoot-through.

$V_{ab}$  is generated by LVS modulation. Fig. 2.4 shows the key LVS waveform of MDPSM. The duty cycle of  $V_{ab}$ ,  $D_1$ , is the period of the non-overlapping region, where LVS is connected with the active clamp circuit. Also,  $V_{ab}$  can be expressed as (2.1).

Fig. 2.4 Key LVS waveform in MDPSM.

$$V_{ab} = \begin{cases} V_{ca}, & non-overlapping\ region \\ & (positive-half-cycle) \\ 0, & overlapping\ region \\ -V_{ca}, & non-overlapping\ region \\ & (negative-half-cycle) \end{cases}$$

(2.1)

#### (b) HVS modulation

$S_{HVs}$  have the same and fixed duty cycle as 0.5 ideally, but HVS deadtime( $D_{ds}$ ) are always set to achieve ZVS in MDPSM. The upper arm switches should have 180° phase difference with the lower arm switches to prevent from shoot-through. The phase between leading-leg switch  $S_5$  and lagging-leg switch  $S_8$  is named as "HVS phase shift". The region between the turn-on time of  $S_5$  and  $S_8$  is called the "phase-shift region", while the other period is named the "non-phase-shift region".

$V_{cd}$  is generated by HVS modulation. Fig. 2.5 shows the key HVS waveform of MDPSM. The duty cycle of  $V_{cd}$ ,  $D_2$ , is the period of the non-phase-shift region, where HVS is connected with the HVS source. In addition,  $V_{cd}$  can be expressed as (2.2).

Fig. 2.5 Key HVS waveform in MDPSM.

$$V_{cd} = \begin{cases} V_{HV}, & non-phase-shift\ region \\ (positive-half-cycle) \\ 0, & phase-shifted\ region \\ -V_{HV}, & non-phase-shift\ region \\ (negative-half-cycle) \end{cases} \tag{2.2}$$

## (c) LVS-HVS Modulation

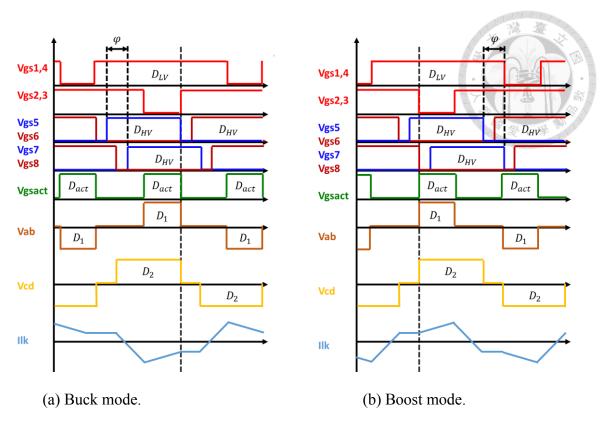

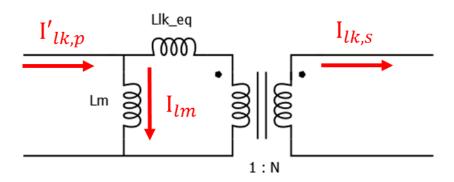

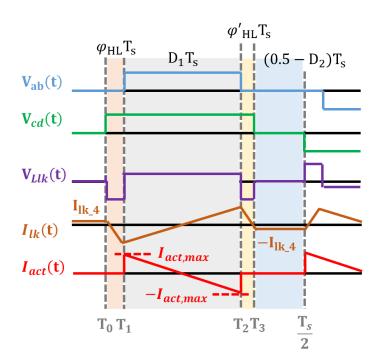

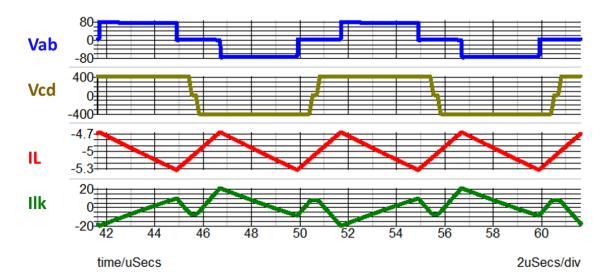

Fig. 2.6 shows the modulation of two voltage-side. The phase-shift between the rising edge of  $V_{\rm cd}$  and  $V_{\rm ab}$  is defined as  $\varphi_{\rm HL}$ , which is a control parameter in MDPSM. In addition,  $D_2$ , the duty cycle of  $V_{\rm cd}$  is also a control parameter. From the perspective of the controlled switches,  $\varphi_{\rm HL}$  is the phase-shift between the falling edge of  $S_1$  and  $S_8$ , and  $D_2$  is 0.5 minus HVS phase-shift. That is, two phase-shifts are controlled in MDPSM. In order to simplify the control, the two phase-shifts are decoupled. In MDPSM,  $\varphi_{\rm HL}$  is used to control the transfer power, and  $D_2$  is used to control the efficiency.

In MDPSM, some limits are set to realize some features. First,  $\, \varphi_{\rm HL} \,$  must be larger

than 0 and  $V_{\rm ca}$  must larger than  $\frac{V_{\rm H}}{N}$  to ensure ZVS for  $S_{act}$ . Also,  $\varphi_{\rm HL}$  must be smaller than  $D_2-D_1$  to ensure ZVS for  $S_{LVs}$ . That is, it can be derived that  $D_1 < D_2$  by the limit of  $\varphi_{\rm HL}$ . With this setting, the transmission power is negative correlated to  $\varphi_{\rm HL}$  and the bidirectional power transmission can be realized.

Fig. 2.6 Key waveform in MDPSM.

## 2.2.2 Circuit Operation

In this subsection, the circuit operation of MDPSM method is illustrated. There are four modes in a half cycle. The current paths of buck operation are shown in Fig. 2.7 - Fig. 2.10, and Fig. 2.11 – Fig. 2.14 show the current paths of boost operation. The detail analyses of the positive-half-cycle buck operation are shown first.

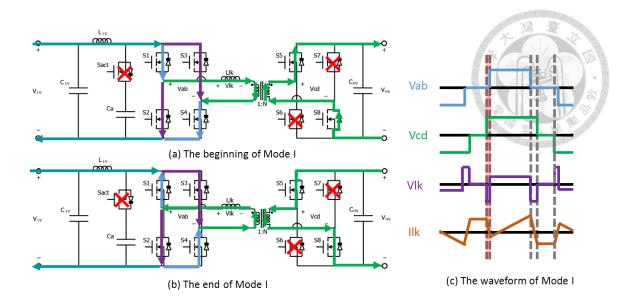

#### (a) Mode I.

Mode I begins as one  $S_{\rm HV,lead}$  ( $S_6$  in this case) turns off and ends when one  $S_{\rm LV}$  group ( $S_2$  and  $S_3$  in this case) turns off. The total period of this mode is  $\varphi_{\rm HL}T_{\rm S}$ . All  $S_{\rm LVs}$  and the other  $S_{\rm HV,lead}$  ( $S_5$  in this case) all turn on in this mode. One  $S_{\rm HV,lag}$  ( $S_8$  in this case) can achieve ZVS turn-on with the proper setting of the deadtime. The detailed

current paths are illustrated in Fig. 2.7.

Fig. 2.7 Mode I in buck operation.

After  $S_6$  turns off, the HVS current is forced to discharge the parasitic capacitor,  $C_{\rm ds8}$ . If  $S_8$  turn on after having already been discharged, that is, the proper deadtime of  $S_8$  is set,  $S_8$  can achieve ZVS turn-on.

To obey the Kirchhoff's Current Law(KCL), (2.3) and (2.4) can be written. It can be found in (2.4) that the imbalance current of  $I_L$  and  $I_{Lk}$  freewheels in  $S_{LVs}$ . Because this imbalance current is not involved in the power transmission, it can also be named "circulating current". In the light load case, circulating current plays an important role in the total power loss.

$$\begin{cases}

I_L = I_{S1} + I_{S2} \\

I_{Lk} = I_{S1} - I_{S2}

\end{cases}$$

(2.3)

$$\begin{cases} I_{S1} = \frac{I_L + I_{Lk}}{2} = I_L - \frac{I_L - I_{Lk}}{2} \\ I_{S2} = \frac{I_L - I_{Lk}}{2} \end{cases}$$

Also, in this mode, the voltage of  $L_{LV}$  is equal to  $V_{LV}$ , and  $V_{lk}$  is equal to  $-\frac{V_H}{N}$ .  $I_{lk}$  decreases gradually and finally commute, which is related to the ZVS for  $S_{act}$  in the next mode.

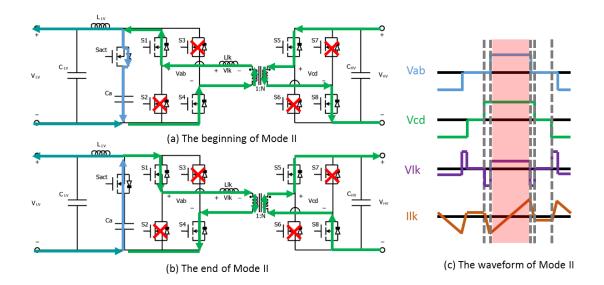

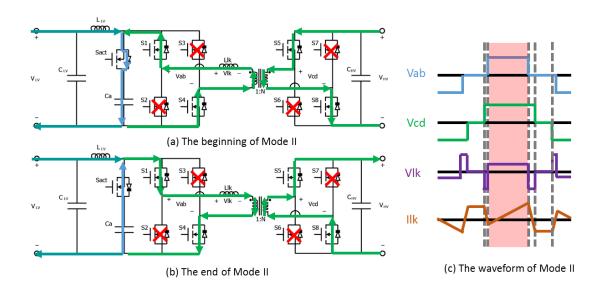

#### (b) Mode II.

Mode II begins as  $S_{LV}$  group ( $S_2$  and  $S_3$  in this case) turns off and ends when  $S_{act}$  turns off. The total period of this mode is  $D_{act}T_s$  (also  $D_1T_s$ ). It is the non-overlapping region defined in the last section.  $S_1$ ,  $S_4$ ,  $S_5$  and  $S_8$  all turn on in this mode, while  $S_2$ ,  $S_3$ ,  $S_6$  and  $S_7$  all turn off.  $S_{act}$  can achieve ZVS turn-on with proper setting of the deadtime. The detail current paths are in Fig. 2.8.

Fig. 2.8 Mode II in buck operation.

After  $(S_2, S_3)$  turn off, the circulating current in  $S_{LVs}$  is eliminated. The imbalance current of  $L_{LV}$  and  $L_{Lk}$  flows into the active clamp circuit. At the same time, the charge in  $C_{ds,act}$  is discharged. If the proper deadtime of  $S_{act}$  is set, ZVS of  $S_{act}$  can be achieved.

In this mode, the voltage of  $L_{\rm LV}$  is equal to  $V_{\rm Ca}$ , and  $V_{\rm lk}$  is equal to  $V_{\rm ca} - \frac{V_{\rm H}}{N}$ . Because  $V_{\rm ca}$  is larger than  $\frac{V_{\rm H}}{N}$  in MDPSM,  $I_{\rm lk}$  keeps increasing and finally changes its direction in this mode, which is related to the ZVS of some LVS switches in Mode III.

This mode is the only mode that the power is transferred to the load. In steady-state, the average of active clamp current,  $I_{\rm act}$ , is equal to zero, so the average of  $I_{\rm lk}$  is the average value of  $I_{\rm L}$  in this mode.

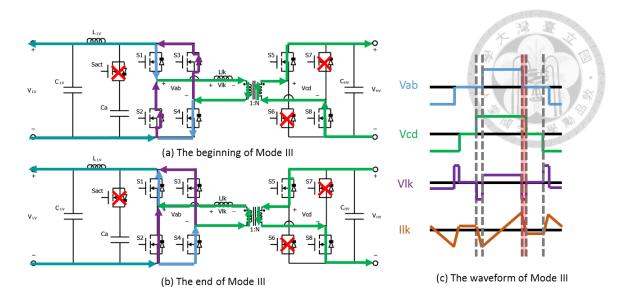

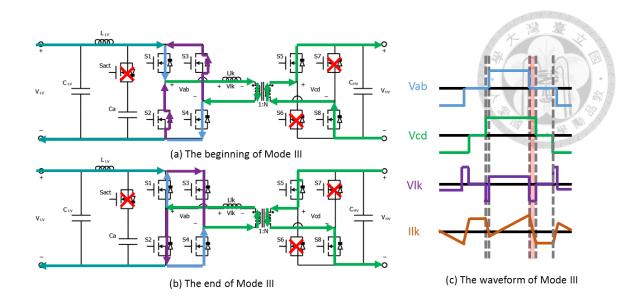

#### (c) Mode III.

Mode III begins as  $S_{\rm act}$  turns off and ends when one  $S_{\rm HV,lead}$  ( $S_5$  in this case) turns off. The total period of this mode is  $\varphi_{\rm HL}{}'T_{\rm S}$ . Switches  $S_1$ ,  $S_4$ ,  $S_5$  and  $S_8$  all turn on in this mode, while  $S_{\rm act}$ ,  $S_6$ , and  $S_7$  all turn off. One  $S_{\rm Lv}$  group ( $S_2$  and  $S_3$  in this case) can achieve ZVS turn on in this mode with proper deadtime. The detailed current paths are in Fig. 2.9.

Fig. 2.9 Mode III in buck operation.

After  $S_{\rm act}$  turns off, the imbalance current of  $I_{\rm L}$  and  $I_{\rm Lk}$  becomes the circulating current in  $S_{\rm LVs}$  and flows into  $S_2$  and  $S_3$ . The charges of  $C_{\rm ds2}$  and  $C_{\rm ds3}$  are discharged in this mode. If the property deadtime of  $S_2$  and  $S_3$  are set, both switches can achieve ZVS.

In this mode, the voltage of  $L_{LV}$  is equal to  $V_{LV}$ , and  $V_{lk}$  is equal to  $-\frac{V_H}{N}$ .  $I_{lk}$  keeps decreasing and finally change its direction in this mode, which is related to the ZVS of the  $S_6$  in Mode IV.

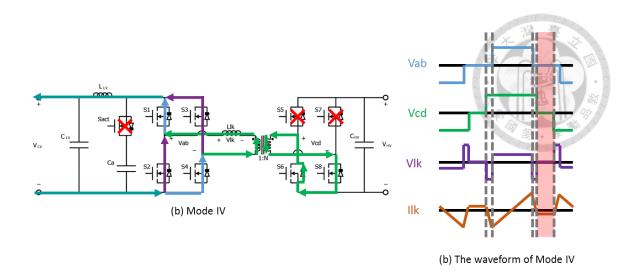

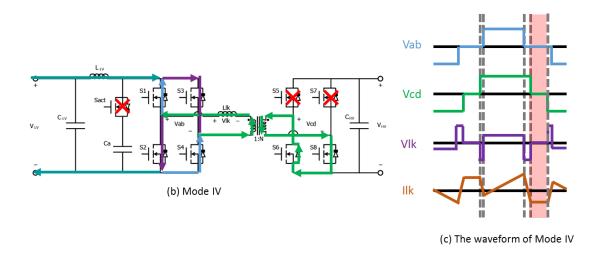

## (d) Mode IV.

Mode IV begins as one  $S_{\rm HV,lead}$  ( $S_5$  in this case) turns off and ends when one  $S_{\rm HV,lag}$  ( $S_8$  in this case) turns off. The total period of this mode is  $(0.5 - D_2)T_{\rm s}$ .  $S_1 \sim S_4$  and  $S_8$  all turn on in this mode, and the other  $S_{\rm HV,lead}$  ( $S_6$  in this case) can achieve ZVS turn on with the proper deadtime. The detailed current paths are in Fig. 2.10.

Fig. 2.10 Mode IV in buck operation.

After  $S_5$  turns off, the HVS leakage current flows into  $S_6$ . Also, the charge of  $C_{\rm ds6}$  is discharged in this mode. If the property deadtime of  $S_6$  is set, ZVS can be achieved.

In this mode, the voltage of  $L_{LV}$  is equal to  $V_{LV}$ , and  $V_{lk}$  is equal to 0, so  $I_{lk}$  doesn't change. And the direction of the leakage current plays a role in the ZVS for  $S_7$  in the other half cycle.

## (e) Boost operation case.

The previous analysis is all for buck operation. Because the concept of boost operation is similar to buck operation, the directions of current flows in boost operation are almost the same as the buck operation. Fig. 2.11 ~ Fig. 2.14 show the detailed waveforms in boost operation. Note that some periods of the mode are different with buck operation.

Fig. 2.11 Mode I in boost operation.

Fig. 2.12 Mode II in boost operation.

Fig. 2.13 Mode III in boost operation.

Fig. 2.14 Mode IV in boost operation.

## 2.2.3 ZVS Condition

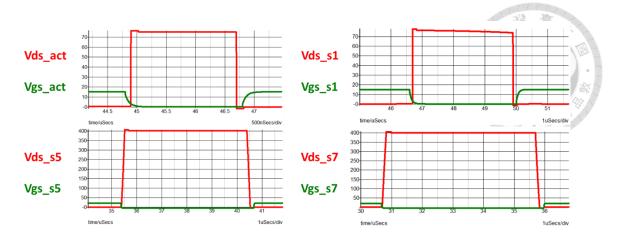

In section 2.2.2, it is proved that ZVS can be achieved by setting the proper deadtime of switches. In this subsection, details about the deadtime setting are introduced.

(a) Definition of variables.

$D_{td1}$  and  $D_{td2}$  are the time delays set in the non-overlapping region.  $D_{td1}$  means

the time delay between the beginning of the non-overlapping region and the rising edge of  $D_{act}$ , while  $D_{td2}$  means the time delay between the falling edge of  $D_{act}$  and the end of the on-overlapping region.  $D_{td1}$  can be regard as the deadtime of  $S_{act}$ , and  $D_{td2}$  can be seen as the deadtime of  $S_{LVs}$  In addition,  $D_{d,lead}$  is the deadtime of  $S_{HV,lead}$ , while  $D_{d,lag}$  is the deadtime of  $S_{HV,lag}$ . Fig. 2.15 illustrates the deadtime setting of each switch.

Fig. 2.15 Deadtime setting in MDPSM.

$I_{act,max}$  is the maximum current from the active clamp capacitor. It is related to the ZVS condition of  $S_{act}$  and can be derived by (2.5).

$$I_{act,max} = \frac{V_{ca} - \frac{V_H}{N}}{L_{lk}} \frac{D_{act} T_s}{2} = \frac{D_{act} T_s (V_{ca} - \frac{V_H}{N})}{2L_{lk}}$$

(2.5)

$I_{lk\_4}$  is the leakage current in Mode IV. Because  $V_{lk}$  is equal to 0 in Mode IV, the

leakage current doesn't change in the ideal case. It is related to the ZVS condition of the HVS switches. By (2.28) and (2.31), (2.6) can be derived.

$$I_{lk_{-4}} = \frac{T_s}{2L_{lk}} \left( D_2 \frac{V_H}{N} - D_{act} V_{ca} \right) \tag{2.6}$$

$I_{lm,max}$  is the maximum magnetic current of the transformer. If the magnetic inductor of the transformer is considered,  $I_{lm,max}$  is applied to modify some equations. The value of  $I_{lm,max}$  is shown in (2.7).

$$I_{lm,max} = \frac{V_H D_{act} T_s}{2NL_k} \tag{2.7}$$

#### (b) Equation for minimum deadtime.

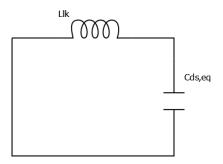

Fig. 2.16 is the equivalent circuit of the resonant discharging model. The differential equation can be written as (2.8) and the general solution is (2.9). With the initial condition of  $V_{ds0}$  and  $I_{ds0}$ , the particular solution can be shown in (2.10).

Fig. 2.16 Equivalent resonant model.

$$\begin{cases} V_{\rm ds}(t) = L_{\rm lk} \frac{dI_{\rm ds}(t)}{dt} \\ I_{\rm ds}(t) = -C_{\rm ds,eq} \frac{dV_{\rm ds}(t)}{dt} \end{cases}$$

$$V_{ds}(t) = C_1 \sin\left(\frac{t}{\sqrt{L_{lk}C_{ds,eq}}}\right) + C_2 \cos\left(\frac{t}{\sqrt{L_{lk}C_{ds,eq}}}\right)$$

(2.9)

$$V_{ds}(t) = -I_{ds0} \sqrt{\frac{L_{lk}}{C_{ds,eq}}} sin\left(\frac{t}{\sqrt{L_{lk}C_{ds,eq}}}\right) + V_{ds0} cos\left(\frac{t}{\sqrt{L_{lk}C_{ds,eq}}}\right)$$

(2.10)

To simplify the calculation, small-angle approximations (2.11) can be applied because the period of resonant is larger than the deadtime. And the simplified equation is (2.12), the minimum duty of deadtime,  $D_{deadtime,min}$ , can be calculated by (2.13).

$$\begin{cases} \sin(\theta) \approx \theta & \text{, when } \theta \text{ small} \\ \cos(\theta) \approx 1 - \frac{\theta^2}{2} \approx 1 & \text{, when } \theta \text{ small} \end{cases}$$

(2.11)

$$V_{\rm ds}(t) \approx V_{ds0} - \frac{I_{ds0}}{C_{\rm ds,eq}}t \tag{2.12}$$

$$D_{deadtime,min} \approx \frac{C_{ds,eq} * V_{ds0}}{I_{ds0} * T_s}$$

(2.13)

#### (c) ZVS condition of each switch.

In the previous part, the equation of  $D_{deadtime,min}$  is derived. To calculate the ZVS condition, that is,  $D_{deadtime,min}$ , some crucial variables need to be found.

In  $S_{act}$ , the ZVS turn-on timing is in Mode II, where the imbalance current between

$I_L$  and  $I_{lk}$  charges two  $S_{LVs}$  and discharges  $S_{act}$  simultaneously in the beginning. So the  $C_{\rm ds,eq}$  must be the sum of the three parasitic capacitors,  $V_{ds0}$  is the voltage of active clamp capacitor, and  $I_{ds0}$  is the imbalance current between  $I_L$  and  $I_{lk}$ , that is,  $I_{act,max}$ .

In  $S_{LV}$ , the ZVS turn-on timing is in Mode III, where the imbalance current between  $I_L$  and  $I_{lk}$  discharges two  $S_{LVs}$  and charges  $S_{act}$  simultaneously in the beginning. So the  $C_{ds,eq}$  must also be the sum of the three parasitic capacitors,  $V_{ds0}$  is the voltage of the active clamp capacitor, and  $I_{ds0}$  is  $I_{act,max}$ , too.

In  $S_{HV,lead}$ , the ZVS turn-on timing is in Mode IV, where the HVS leakage current discharges one  $S_{HV,lead}$  and charges one  $S_{HV,lag}$  simultaneously in the beginning. So the  $C_{ds,eq}$  must also be the sum of the two parasitic capacitors,  $V_{ds0}$  is the voltage of HVS source, and  $I_{ds0}$  is  $I_{lk,4}$  in the previous analysis.

In  $S_{HV,lag}$ , the ZVS turn-on timing is in Mode I, where the HVS leakage current charges one  $S_{HV,lead}$  and discharges one  $S_{HV,lag}$  simultaneously in the beginning. So  $C_{ds,eq}$ ,  $V_{ds0}$ , and  $I_{ds0}$  of  $S_{HV,lag}$  are same as  $S_{HV,lead}$ .

Table 2.1 organizes all variables of ZVS condition for each switch.  $D_{deadtime,min}$  can be calculated by (2.13), and is listed in (2.14) ~ (2.17).

Table 2.1 Variables of ZVS condition for each switch.

|                      | Turn-on timing | $C_{ m ds,eq}$            | $V_{ds0}$ | $I_{ds0}$     |

|----------------------|----------------|---------------------------|-----------|---------------|

| $S_{act}$            | Mode II        | $C_{ds,act} + 2C_{ds,LV}$ | $V_{ca}$  | $I_{act,max}$ |

| $S_{LV}$             | Mode III       | $C_{ds,act} + 2C_{ds,LV}$ | $V_{ca}$  | $I_{act,max}$ |

| S <sub>HV,lead</sub> | Mode IV        | $2C_{ds,HV}$              | $V_H$     | $I_{lk\_4}$   |

| $S_{HV,lag}$         | Mode I         | $2C_{ds,HV}$              | $V_H$     | $I_{lk\_4}$   |

$$D_{td1,min} = \frac{3C_{ds,act}V_{ca}}{I_{act,max}T_s}$$

$$D_{td2,min} = \frac{3C_{ds,act}V_{ca}}{I_{act,max}T_s}$$

(2.15)

$$D_{d,lead,min} = \frac{C_{ds,equ}V_{ds0}}{I_{lk_4}} = \frac{2C_{ds,HV}V_H}{I_{lk_4}}$$

(2.16)

$$D_{d,lag,min} = \frac{C_{ds,equ}V_{ds0}}{I_{lk_4}} = \frac{2C_{ds,HV}V_H}{I_{lk_4}}$$

(2.17)

## (d) ZVS condition for nonideal transformer

In the previous analysis, the transformer is supposed to be ideal with infinity  $L_m$ . However, due to the limit of the material,  $L_m$  could not be regarded as infinity in some design cases. The effect of  $L_m$  is discussed in this part.

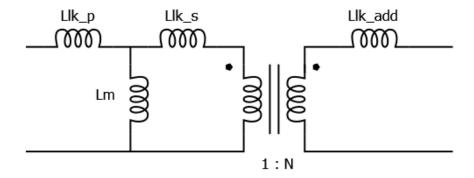

Fig. 2.17 Nonideal transformer circuit.

Fig. 2.17 shows the nonideal model of the transformer circuit.  $L_{lk,p}$  and  $L_{lk,s}$  are

the leakage inductors of primary and secondary sides,  $L_m$  is the magnetic inductor of the transformer, and  $L_{lk,add}$  is the additional inductor to increase the equivalent leakage inductor. Because the analysis of this nonideal model is too complex to analyze, the model should be modified by ignoring some effects. Fig. 2.18 shows the modified nonlinear model. In this model, it is supposed that  $\frac{L_{lk,add}}{N^2} \gg L_{lk,p}$  and  $L_{lk,eq}$  can be calculated by (2.18). With the modified model, the following analysis can be much easier.

$$L_{lk,eq} = L_{lk,p} + L_{lk,s} + \frac{L_{lk,add}}{N^2}$$

(2.18)

Fig. 2.18 Modified nonideal transformer circuit.

If the  $L_m$  is considered, (2.19) can be written by KCL. It can be found that the value of the primary-side leakage current is enhanced. The LVS ZVS condition considered this effect is rewritten as (2.20) ~ (2.22).

$$I'_{lk,p} = I_{lm} + I_{lk,s} * N$$

(2.19)

$$I'_{ac,max} = I_{ac,max} + I_{lm,max} (2.20)$$

$${D'}_{td1,min} = \frac{3C_{ds,act}V_{ca}}{I'_{act,max}T_s}$$

$$D'_{td2,min} = \frac{3C_{ds,act}V_{ca}}{I'_{act,max}T_s}$$

(2.22)

(2.21)

# 2.3 Power Transmission Control

In this section, the power transmission of MDPSM is analyzed.

The transmission power,  $P_{\rm T}$ , can be expressed as (2.23).

$$P_{\rm T} = \int_0^{T_s} V_{ab}(t) I_{lk}(t) dt = 2V_{ca} \int_0^{D_1 T_s} I_{lk}(t) dt$$

(2.23)

Assume  $L_{LV}$  is large enough to ignore the current ripple, (2.23) can be written as (2.24) because the average leakage current is equal to  $I_L$  in Mode II.

$$P_{\rm T} = 2D_1 V_{ca} I_L \tag{2.24}$$

(a) Calculation for  $V_{ca}$ .

$V_{ca}$  can be derived by the voltage-second balance of  $L_{LV}$ . The voltage-second balance of  $L_{LV}$  can be listed as (2.25), and  $V_{ca}$  in (2.26) can be solved by (2.25).

$$\int_{0}^{T_{S}} V_{L_{LV}}(t)dt = V_{ca} * (2D_{1}T_{S}) - V_{LV}T_{S} = 0$$

(2.25)

$$V_{ca} = \frac{V_{LV}}{2D_1}$$

## (b) Calculation for $I_L$ .

In the previous analysis, it can be found that  $I_L$  is the average leakage current in Mode II. To express the time equation of  $I_{lk}$ , the slope of  $I_{lk}$  is first calculated by (2.27).

$$V_{Llk} = L_{lk} \frac{dI_{lk}}{dt} \tag{2.27}$$

Because  $V_{Llk}$  and  $L_{lk}$  are known in each mode, the slope can be expressed as (2.28). Also the equation of  $I_{lk}(t)$  can be derived as (2.29). Also,  $\varphi'_{HL}$  can be calculated as (2.30) by other time constants.

$$\frac{dI_{lk}(t)}{dt} = \begin{cases} -\frac{V_{H}}{NL_{lk}} & , T_{0} \leq t < T_{1}(\text{Mode I}) \\ \frac{V_{ca} - \frac{V_{H}}{N}}{L_{lk}} & , T_{1} \leq t < T_{2}(\text{Mode II}) \\ -\frac{V_{H}}{NL_{lk}} & , T_{2} \leq t < T_{3}(\text{Mode III}) \\ 0 & , T_{3} \leq t < \frac{T_{s}}{2}(\text{Mode IV}) \end{cases}$$

(2.28)

$$I_{lk}(t) = \begin{cases} I_{lk}(T_0) - \frac{V_H}{NL_{lk}}t, & T_0 \le t < T_1 \\ I_{lk}(T_1) + \frac{V_{ca} - \frac{V_H}{N}}{L_{lk}}(t - T_1), & T_1 \le t < T_2 \\ I_{lk}(T_2) - \frac{V_H}{NL_{lk}}(t - T_2), & T_2 \le t < T_3 \\ I_{lk}(T_3), & T_3 \le t < \frac{T_s}{2} \end{cases}$$

(2.29)

$$\varphi'_{HL} = 0.5 - \varphi_{HL} - D_1 - (0.5 - D_2) = D_2 - D_1 - \varphi_{HL}$$

(2.30)

Considering the symmetry of the positive and negative half-cycle (2.31),  $I_{lk}(t)$  in Mode II can be expressed by (2.32). And  $I_L$  can be calculated by averaging the leakage current in Mode II (2.33).

$$I_{lk}(T_0) = -I_{lk}(T_3) (2.31)$$

$$I_{lk_{Modell}}(t) = \frac{T_s}{2L_{lk}N} \left[ (D_2 - 2\varphi_{HL})V_H - ND_1V_{ca} \right] + \frac{NV_{ca} - V_H}{L_{lk}N} (t - T_1)$$

(2.32)

$$I_{L} = \int_{T_{1}}^{T_{2}} I_{lk_{Modell}}(t) dt = \frac{T_{s} V_{H}}{2L_{lk} N} (D_{2} - 2\varphi_{HL} - D_{1})$$

(2.33)

(c) Power transmission and voltage gain.

Combine (2.24), (2.26), and (2.32), the power transmission can be expressed as (2.34):

$$P_{\rm T} = P_{\rm L} = V_L I_L = \frac{T_s V_L V_H}{2L_{lk} N} (D_2 - 2\varphi_{HL} - D_1)$$

(2.34)

Because  $V_L$  is fixed by the voltage source,  $I_L$  is also regard as the control target of the transfer power. Also, it can be found in (2.34) that the output power range is wider in controlling  $\varphi_{HL}$  than controlling  $D_2$ , so  $\varphi_{HL}$  is suitable for controlling transfer power by (2.35), and  $D_2$  is suitable to control other target, namely efficiency, in MDPSM.

$$\varphi_{HL} = \frac{D_2 - D_1}{2} - \frac{L_{lk} N I_L}{T_s V_H}$$

(2.35)

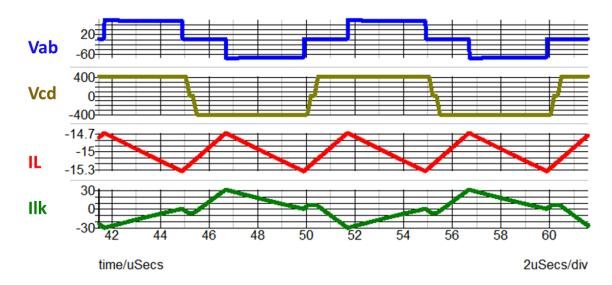

Fig. 2.19 shows the transfer power in MDPSM. Because the transfer power is proportional to  $I_L$  and  $I_L$  is related to  $\varphi_{HL}$ , the bidirectional operation can be achieved by changing the value of  $\varphi_{HL}$ , which leads to the better transient than applying two different modulation methods.

Fig. 2.19 Power transmission in MDPSM.

By (2.34), the voltage gain in buck mode,  $M_{buck}$ , can be derived as (2.36) by considering LVS load,  $R_{buck}$ , and the voltage gain in boost mode,  $M_{boost}$ , can be derived as (2.37) by considering HVS load,  $R_{boost}$ .

$$M_{buck} = \frac{V_L}{V_H} = \frac{2L_{lk}N}{T_s R_{buck} (D_2 - 2\varphi_{HL} - D_1)}$$

(2.36)

$$M_{boost} = \frac{V_H}{V_L} = \frac{T_s R_{boost} (D_2 - 2\varphi_{HL} - D_1)}{2L_{lk}N}$$

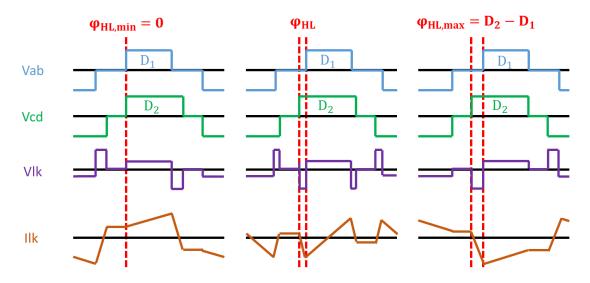

# 2.4 Bidirectional Transient Response

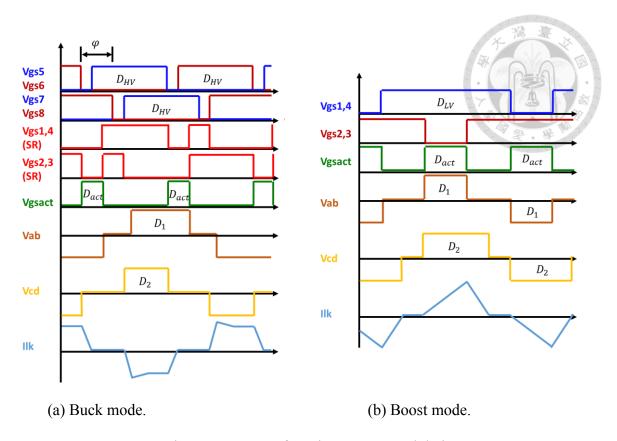

In section 2.2, MDPSM is proposed to improve the bidirectional transient compared to SSM. In this section, the waveforms of bidirectional transient responses are shown.

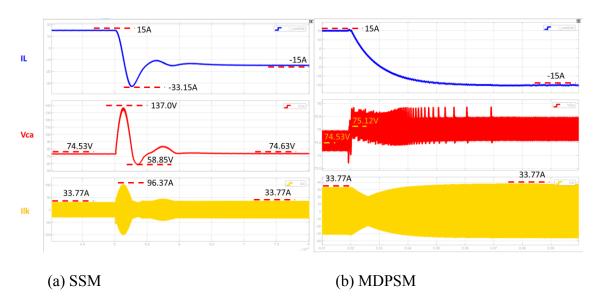

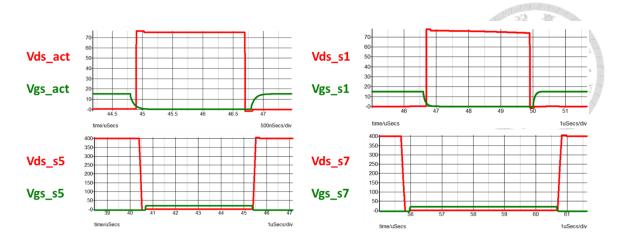

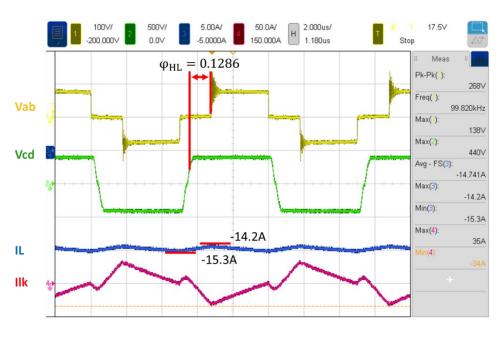

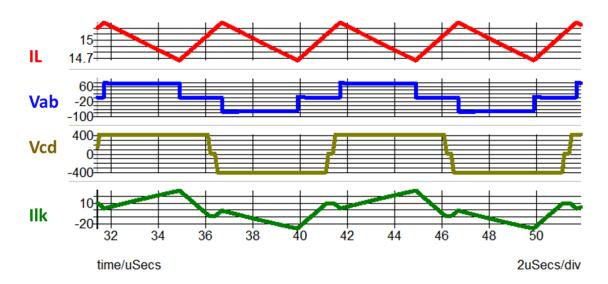

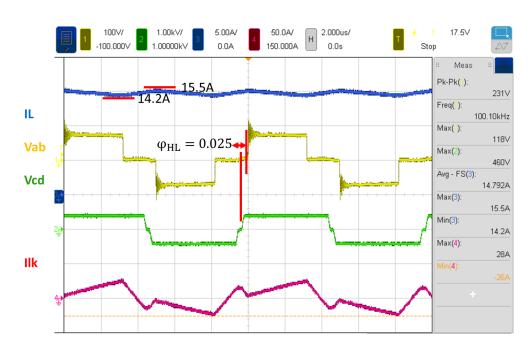

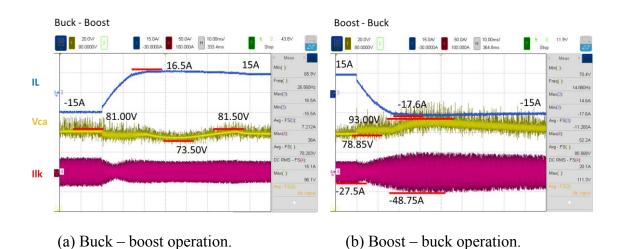

Fig. 2.20 shows the bidirectional transient response of 720W boost-buck operation. It can be found that in SSM, the overshoot of  $I_L$  is about 60.5%, while in MDPSM, the overshoot can be eliminated with proper control of  $\varphi_{HL}$ . Also, the spike of  $V_{ca}$  and  $I_{lk}$  decline obviously in MDPSM. The result shows that the Bidirectional transient response of MDPSM is improved in boost-buck operation.

Fig. 2.20 Bidirectional transient response of boost-buck operation.

Fig. 2.21 shows the bidirectional transient response in 720W buck-boost operation. Same as boost-buck operation, it can be found that the overshoot in  $I_L$  decreases in MDPSM. In addition, the spike in  $V_{ca}$  and  $I_{lk}$  can be improved in MDPSM. With the

cost of higher setting time, MDPSM has lower spike and higher security than SSM in buck-boost operation.

Fig. 2.21 Bidirectional transient response of buck-boost operation.

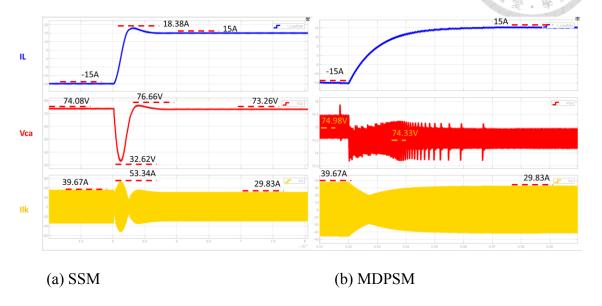

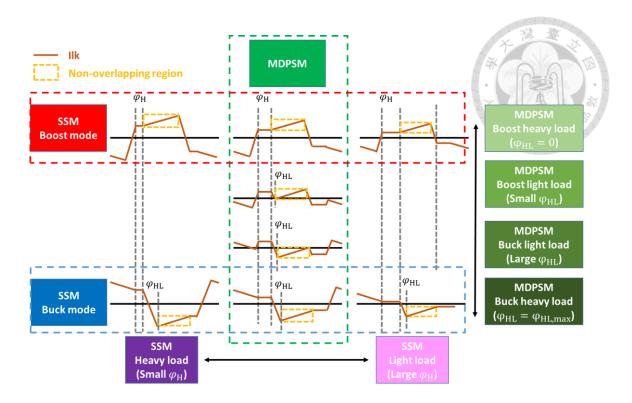

The concept of the bidirectional transient improvement can be shown in Fig. 2.22. Fig. 2.22 shows the difference of  $I_{lk}$  between SSM and MDPSM. The horizontal red frame shows the boost mode in SSM, while the horizontal blue frame is the buck mode in SSM. In addition, the vertical green frame illustrates the waveform in MDPSM.

Fig. 2.22 Leakage current waveform between SSM and MDPSM.

In Fig. 2.22, it can be found that the waveform of SSM is the full-load case in MDPSM. The difference between SSM and MDPSM is that SSM is controlled by HVS phase shift,  $\varphi_H$  with fixed  $\varphi_{HL}$ , while MDPSM is controlled by  $\varphi_{HL}$  with fixed  $\varphi_H$ . Though the control parameters of SSM and MDPSM are different, the analysis of SSM can be regard as the full-load case in MDPSM.

Then, the buck-boost operation in SSM can be seen as suddenly change the value of  $\varphi_{HL}$  from minimum to maximum, while maximum to minimum in boost-buck operation. That is, the huge bidirectional transient is generated by heavily changing  $\varphi_{HL}$ . However, in MDPSM, smooth change of  $\varphi_{HL}$  can be achieved with proper control, which leads to better bidirectional transient.

# **Chapter 3 Power Efficiency Improvement**

In Chapter 2, MDPSM that can improve the bidirectional operation transient is proposed. MDPSM uses two phase-shifts, namely  $\varphi_{HL}$  and  $D_2$ , to control the switches.  $\varphi_{HL}$  is used to control the transfer power and the detailed analysis is introduced in section 2.3. In this chapter, the other phase shift,  $D_2$ , is taken into account to improve the total power efficiency, and a control strategy for  $D_2$ , MEPT, is proposed.

Efficiency equations are provided in section 3.1. A maximum efficiency point tracking strategy(MEPT) for  $D_2$  is proposed in section 3.2 to improve the power efficiency. Details of designing the system parameter are finally introduced in section 3.3.

# 3.1 Efficiency Equation

Equations of efficiency are shown in this section. The transfer power of AC-CFDAB can be calculated by (2.34). If the power loss,  $P_{loss}$ , in (3.1) is considered, the equation becomes (3.2), where  $P_{sw}$  means the total switching loss,  $P_{con}$  means the total conduction loss,  $P_{core}$  means the total core loss,  $P_{copper}$  means the total copper loss of the magnetic components,  $P_{ESR}$  means loss caused by the ESR. The detailed equations of each power loss term are provided in the following.

$$P_{loss} = P_{sw} + P_{con} + P_{core} + P_{copper} + P_{ESR}$$

(3.1)

$$\eta = \begin{cases} \frac{P_L - P_{loss}}{P_L}, & P_L \ge 0\\ \frac{|P_L|}{|P_L| + P_{loss}}, & P_L < 0 \end{cases}$$

(3.2)

#### (a) RMS current equations.

The root-mean-square(RMS) values of current play important roles in  $P_{con}$ ,  $P_{copper}$ , and  $P_{ESR}$ . In this part, some key RMS current values in Fig. 3.1 are calculated.

Fig. 3.1 Related waveform in efficiency equation.

The RMS value of the leakage current,  $I_{lk,rms}$ , is calculated first. The leakage current value of each timing,  $I_{lk}(t)$ , is shown in (2.29). The leakage current values at the beginning of every mode are listed in (3.3) ~ (3.6).

$$I_{lk}(T_0) = I_{lk_4} = \frac{T_s}{2L_{lk}} \left( D_2 \frac{V_H}{N} - D_1 V_{ca} \right)$$

(3.3)

$$I_{lk}(T_1) = \frac{T_s}{2L_{lk}} [(D_2 - 2\varphi_{HL}) \frac{V_H}{N} - D_1 V_{ca}]$$

(3.4)

$$I_{lk}(T_2) = \frac{T_s}{2L_{lk}} \left[ (D_2 - 2\varphi_{HL} - 2D_1) \frac{V_H}{N} + D_1 V_{ca} \right]$$

$$I_{lk}(T_3) = -I_{lk_4} = -\frac{T_s}{2L_{lk}}(D_2\frac{V_H}{N} - D_1V_{ca})$$

Suppose  $I_L$  is well controlled,  $\varphi_{HL}$  can be written as (2.35), then the RMS value can be calculated by (3.7).

$$I_{lk,rms} = \sqrt{-\left(\frac{T_s^2 V_H}{3N L_{lk}^2}\right) D_2^3 + \left(\frac{T_s^2 V_H}{4N^2 L_{lk}^2}\right) (V_H + 2D_1 N V_{ca}) D_2^2}$$

$$-\left(\frac{D_1 T_s^2 V_H V_{ca}}{2N L_{lk}^2}\right) D_2 + \frac{D_1 V_{ca}}{6V_H L_{lk}^2} \left[ (1 - 2D_1) D_1 T_s^2 V_H V_{ca} + 12I_L^2 L_{lk}^2 N \right]$$

(3.7)

The RMS value of active clamp current,  $I_{act,rms}$ , is related to the loss of the active clamp circuit. The time equation of  $I_{act}$  can be expressed in (3.8) and its RMS value can be calculated by (3.9).

$$I_{act_{Mode\ II}}(t) = I_{act,max} - 2I_{act,max} \frac{t}{D_1 T_s}$$

(3.8)

$$I_{act,rms} = \sqrt{\frac{1}{\frac{T_s}{2}}} \int_0^{D_1 T_s} I_{act_{Mode\ II}}^2(t) dt = \left(V_{ca} - \frac{V_H}{N}\right) \frac{D_1 T_s}{2L_{lk}} \sqrt{\frac{2D_1}{3}}$$

(3.9)

#### (b) Switching loss term.

The total switching loss includes turn-on loss,  $P_{sw,r}$ , and turn-off loss,  $P_{sw,f}$  with

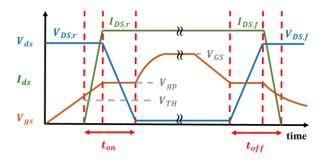

every switch (expressed as  $P_{sw,x}$  for switch x). The switching transient behavior refers to [38] and shows in Fig. 3.2, where  $t_{on}$  and  $t_{off}$  can be calculated by (3.10) and (3.11) from [38],  $V_{TH}$  is the threshold voltage, and  $V_{gp}$  is the voltage of Millar Plateau.

Fig. 3.2 Switching transient behavior in [38].

$$t_{on} = R_G C_{iss} \ln \left( \frac{V_{GS} - V_{TH}}{V_{GS} - V_{gp}} \right) + R_G C_{gd} \frac{V_{DS,r}}{V_{GS} - V_{gp}}$$

(3.10)

$$t_{off} = R_G C_{iss} \ln \left( \frac{V_{gp}}{V_{TH}} \right) + R_G C_{gd} \frac{V_{DS,f}}{V_{gp}}$$

(3.11)

The total switching loss term can be expressed by (3.12), where  $V_{DS,x}$  and  $I_{DS,x}$  can be found in Table 3.1.

$$P_{sw} = \sum_{x} \frac{1}{2} \left( V_{DS,r,x} I_{DS,r,x} t_{on,x} f_{sw} + V_{DS,f,x} I_{DS,f,x} t_{off,x} f_{sw} \right)$$

(3.12)

Table 3.1 Details of switching loss term variables.

| Switch               | $V_{DS,r,h}$ | $I_{DS,r}$                                                | $V_{DS,f}$ | $I_{DS,f}$             |

|----------------------|--------------|-----------------------------------------------------------|------------|------------------------|

| $S_{act}$            | $V_{ca}$     | $-I_{ac,max}$                                             | $V_{ca}$   | I <sub>ac,max</sub>    |

| $S_{LV}$             | $V_{ca}$     | $-\frac{I_{ac,max}}{2}$                                   | $V_{ca}$   | $\frac{I_{ac,max}}{2}$ |

| S <sub>HV,lead</sub> | $V_H$        | $-\frac{I_{lk\_4}}{N}$                                    | $V_H$      | $\frac{I_{lk\_4}}{N}$  |

| $S_{HV,lag}$         | $V_H$        | $-(\frac{I_{lk\_4}}{N} - \frac{V_H D_d T_s}{N^2 L_{lk}})$ | $V_H$      | $\frac{I_{lk\_4}}{N}$  |

$V_{DS,r,h}$  means  $V_{DS,r}$  in the hard-switching case. To consider the ZVS condition,  $V_{DS,r}$  value can be calculated by (3.13).

$$V_{DS,r,x} = \begin{cases} V_{DS,r,h,x}, & \text{if } I_{DS,r,x} \ge 0 \\ V_{DS,r,h,x}, * (1 - \frac{D_{d,x}}{D_{d,min,x}}), & \text{if } I_{DS,r,x} < 0, D_{d,x} < D_{d,min,x} \\ 0, & \text{if } I_{DS,r,x} < 0, D_{d,x} \ge D_{d,min,x} \end{cases}$$

(3.13)

#### (c) Conduction loss term.

The conduction loss term can be divided into three groups ( $S_{act}$ ,  $S_{LV}$  and  $S_{HV}$ ) and shown by (3.14), where  $R_{on,x}$  means the on-resistance of each switch and can be found in the datasheet.

$$P_{con} = \sum_{x} I_{rms,x}^{2} R_{on,x} = P_{con,act} + P_{con,LV} + P_{con,HV}$$

(3.14)

$P_{con,act}$  can be easily calculated by (3.9) and is equal to (3.15).

$$P_{con,act} = I_{rms,act}^{2} R_{on,act}$$

(3.15)

$P_{con,LV}$  can be calculated by equivalencing LVS turn-on resistances. In subsection 2.2.2, it can be found that  $I_L$  flows into four  $S_{LVs}$  in Mode II, while flows into two  $S_{LVs}$  in other modes. The equivalent resistance of  $S_{LVs}$  can be expressed as (3.14) and the conduction loss in  $S_{LVs}$  is shown in (3.17).

$$R_{on,LV,eq} = \frac{R_{on,LV} * (0.5 - D_1) + 2R_{on,LV} * D_1}{0.5} = (1 + 2D_1)R_{on,LV}$$

(3.16)

$$P_{con,LV} = I_L^2 R_{on,LV,eq} = (1 - 2D_1) I_L^2 R_{on,LV}$$

(3.17)

$P_{con,HV}$  can also be calculated by equivalencing HVS turn-on resistances. In subsection 2.2.2, it can be observed that HVS current,  $\frac{I_{lk}}{N}$ , flows into two  $S_{HVs}$  all the time. The total conduction loss of HVS switches can be written as (3.18).

$$P_{con,HV} = \left(\frac{I_{lk,rms}}{N}\right)^2 2R_{on,HV} \tag{3.18}$$

#### (d) Core loss term.

The core loss term is generated by the magnetic components. The conventional calculation process includes three steps. The first step is to calculate the maximum flux density,  $B_{max}$ , by Faraday's Law (3.19), where  $A_e$  means the effective core cross-section area. The second step is to calculate core loss per volume,  $P_v$ , by Steinmetz's equation (3.20), where k, a, and b are called the "Steinmetz's coefficients". In the end,

the core loss can be calculated by (3.21), where  $l_e$  means the magnetic path length

$$V = N * A_e \left| \frac{dB}{dt} \right| \tag{3.19}$$

$$P_V = k f^a B_{max}{}^b (3.20)$$

$$P_{core} = \sum_{x} P_{V,x} A_{e,x} l_{e,x}$$

(3.21)

#### (e) Copper loss term.

The copper loss term is generated by the magnetic components, too. The general form of the copper loss is (3.22), where the RMS current value of  $L_{LV}$  is  $I_L$ . The RMS current value of the transformer is equal to  $I_{lk,rms}$  or  $\frac{I_{lk,rms}}{N}$ , depending on the direction of the resistance. The resistance of a wire can be calculated by the resistance equation (3.23), where  $\rho$  means the resistivity of the wire, l means the length of the wire, and A means the cross-section area of the wire.

$$P_{copper} = \sum_{x} I_{rms,x}^{2} R_{wire,x}$$

(3.22)

$$R_{wire} = \rho \frac{l}{A} \tag{3.23}$$

#### (f) ESR loss term.

The ESR loss term is generated by the ESR of the active clamp capacitor,  $C_a$ , and

can be calculated by (3.24).

$$P_{ESR} = I_{act,rms}^{2} ESR_{act}$$

# 3.2 Maximum Efficiency Point Tracking Strategy

In this section, the analysis between the efficiency and  $D_2$  is introduced and maximum efficiency point tracking strategy(MEPT) is proposed. In subsection 3.3.1, operation region of  $D_2$  is analyzed, and the efficiency analysis with all operation region is shown in subsection 3.3.2. Finally, the strategy scheme is shown in subsection 3.3.3.

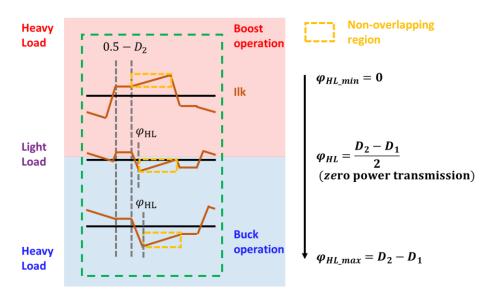

## 3.2.1 Operation region

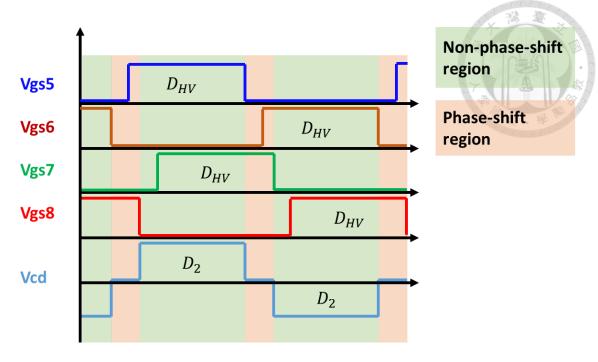

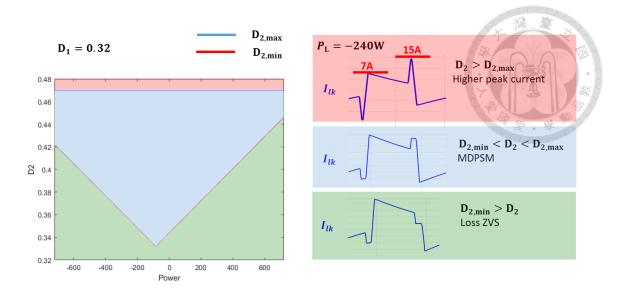

In the beginning, the operation region of  $D_2$  is analyzed. The maximum and minimum values of  $D_2$ ,  $D_{2,max}$  and  $D_{2,min}$ , are estimated in this subsection.

$D_{2,max}$  is analyzed first. To achieve ZVS for  $S_{HV,lead}$  in Mode IV, the period of Mode IV,  $0.5 - D_2$ , must be larger than  $D_d$ . That is,  $D_{2,max}$  can be expressed as (3.25).

$$D_{2,max} = 0.5 - D_d (3.25)$$

$D_{2,min}$  can be calculated in the following rules. There are two limits for  $D_{2,min}$ . The final value of  $D_{2,min}$  must consider the both two limits.

The first limit of  $D_{2,min}$  is from the minimum value of  $\varphi_{HL}'$ . The minimum value of  $D_2$  in this case can be expressed as  $D_{2,min1}$ .  $\varphi_{HL}'$  can be derived by (2.30), and  $\varphi_{HL}$  in (2.12) can be substituted by (2.35) if the output power is well controlled. The substituted equation is (3.26). Because  $\varphi_{HL}'$  is the period of Mode III, the time must be

longer than  $D_{td2}$  to assure the ZVS for the  $S_{LVs}$ . So  $\varphi_{HL}' = D_{td2}$ , and  $D_{2,min,1}$  is shown in (3.27).

$$\varphi'_{HL} = \frac{D_2 - D_1}{2} + \frac{L_{lk} N I_L}{T_S V_H}$$

(3.26)

$$D_{2,min1} = D_1 + 2D_{td2} - \frac{2L_{lk}NI_L}{T_sV_H}$$

(3.27)

The other limit of  $D_{2,min}$  is from the minimum value of  $\varphi_{HL}$ . The minimum value of  $D_2$  in this case can be expressed as  $D_{2,min2}$ . Because  $\varphi_{HL}$  should be larger than 0 in MDPSM, (3.28) can be derived by (2.35).

$$D_{2,min2} = D_1 + \frac{2L_{lk}NI_L}{T_SV_H} \tag{3.28}$$

The minimum value of  $D_2$  is limited by the above two equations, the final value of  $D_{2,min}$  is in (3.29).

$$D_{2,min} = \max(D_{2,min1}, D_{2,min2}) \tag{3.29}$$

Fig. 3.3 shows the operation region of  $D_2$ . MDPSM operates in the blue area. It can be found that the wider operation region is in the lighter load case. Also, If the setting of  $D_2$  is out of the analytical region, the circuit would loss ZVS and the operation is not included in MDPSM.

Fig. 3.3 Operation region of  $D_2$ .

## 3.2.2 Efficiency Analysis

In section 3.1, it can be found in (3.1) that the power efficiency is composed of five power loss terms. The relationship between  $D_2$  and each power loss is introduced in the following.

$P_{sw}$  term can be calculated by (3.12). It can be found that the turn-off switching loss is positively correlated to  $I_{lk\_4}$ , while the turn-on switching loss is negative correlated to  $P_{sw,f}$ . Because  $I_{lk\_4}$  is also positively correlated to  $D_2$  and ZVS can be achieved when  $D_2$  is large,  $P_{sw}$  term is positively correlated to  $D_2$  when operating in ZVS, while the relationship between  $D_2$  and  $P_{sw}$  term depends on cases.

$P_{con}$  term can be calculated by (3.14). The equation of  $I_{lk,rms}$  is shown in (3.7) and is negatively correlated to  $D_2$  with the system parameters in this thesis.

$P_{core}$  term is calculated by (3.21). The flux density of the transformer is negatively correlated to D<sub>2</sub>. By (3.20), it can be found that  $P_{core}$  is negatively correlated to D<sub>2</sub>.

$P_{copper}$  term is also related to  $I_{lk,rms}$ , which is positively correlated to  $D_2$ . So  $P_{copper}$  is positively correlated to  $D_2$ .

$P_{ESR}$  term is only related to  $I_{act,rms}$ , which is not related to  $D_2$ . So the change of  $D_2$  doesn't influence the value of  $P_{ESR}$ .

With the analyses above, it can be concluded that  $D_2$  is related to efficiency. Because  $P_{sw}$  and  $P_{con}$  play dominant parts in the total power loss, the effect of  $P_{core}$  can be neglected in the analysis. It can be found that the power efficiency is negatively correlated to  $D_2$  when operating in ZVS. When losing ZVS, the relation between  $D_2$  and the efficiency depends by the case.

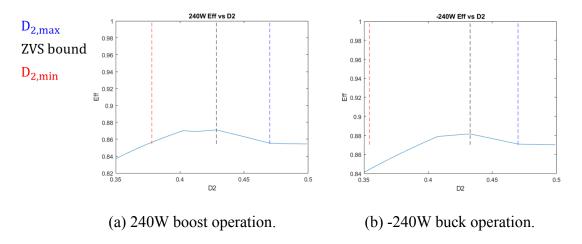

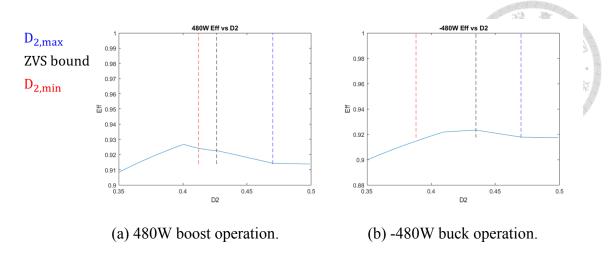

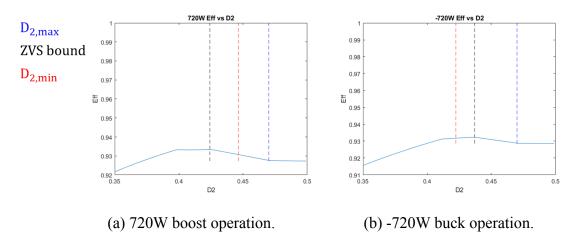

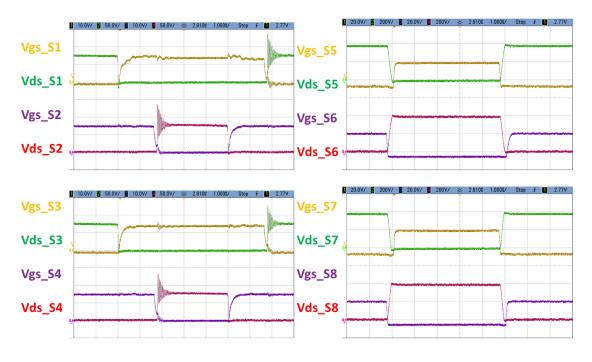

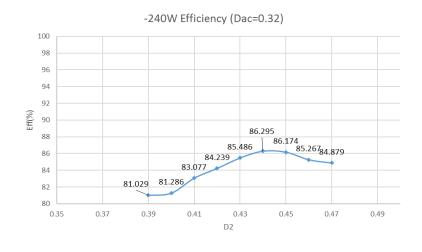

Fig. 3.4 - Fig. 3.6 show the relationship between  $D_2$  and total efficiency. It can be found that power efficiency is indeed negatively correlated to  $D_2$  when operating in ZVS. While losing ZVS, the relationship is not positively or negative correlated to  $D_2$  for sure. For instance, in 480W boost case, the efficiency is negatively correlated to  $D_2$ , while the efficiency is positively correlated to  $D_2$  in Fig. 3.5.

Fig. 3.4 Relationship between D<sub>2</sub> and efficiency with 240W case.

Fig. 3.5 Relationship between D<sub>2</sub> and efficiency with 480W case.

Fig. 3.6 Relationship between  $\ D_2$  and efficiency with 720W case.

## 3.2.3 Strategy Scheme

In subsection 3.2.2, a crucial conclusion that the total power efficiency is related to  $D_2$  can be made. To track the maximum efficiency point of  $D_2$ , MEPT based on MDPSM is proposed. The detail of MEPT shows in the following.

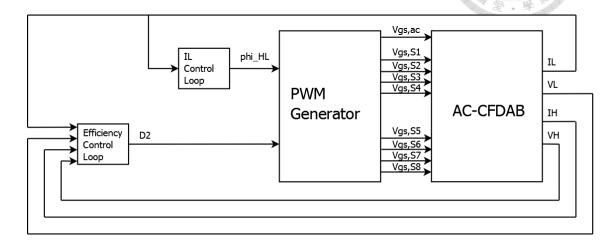

Fig. 3.7 shows the control scheme for MEPT. In MDPSM, the transfer power is controlled by  $\phi_{HL}$ , named " $I_L$  control loop". The maximum efficiency point can be tracked by  $D_2$ , that is, controlled by "efficiency control loop". Because the calculation of the maximum efficiency point is too complex to finish in the microcontroller, the

maximum efficiency point can be traced by some control methods, such as "perturb and observe method". The details of each control loop are shown in the following.

Fig. 3.7 Control scheme for MEPT.

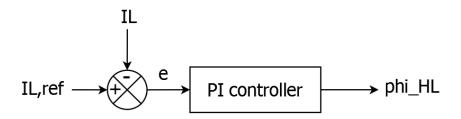

## (a) I<sub>L</sub> control loop

In  $I_L$  control loop, the transfer power can be controlled by  $\varphi_{HL}$ , so  $I_L$  is sensed in this control loop and a PI controller is set to control  $\varphi_{HL}$ . The detail control scheme is shown in Fig. 3.8.

Fig. 3.8 Control scheme for IL control loop.

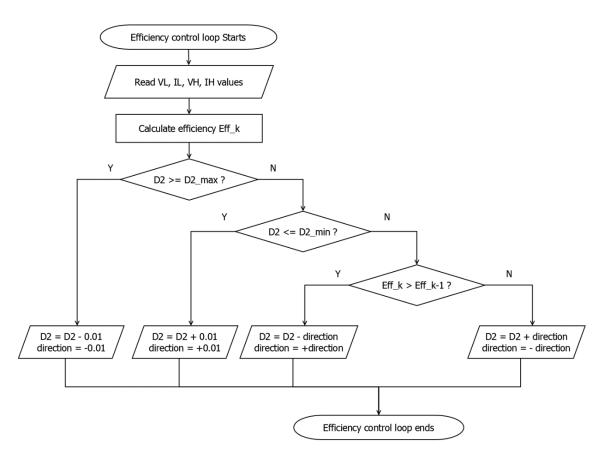

#### (b) Efficiency control loop

In efficiency control loop, the relationship between  $D_2$  and the efficiency is used. The control parameter of this control loop is  $D_2$ . To track the maximum efficiency point, the "perturb and observe method" is applied to find the maximum efficiency point. Also, in order to ensure the power transmission is correct before perturbing, this control loop should start perturb only when the steady-state of the  $I_L$  control loop is achieve. That is, the speed of this control loop should be slower than the  $I_L$  control loop.

Fig. 3.9 Control flowchart for efficiency control loop.

# 3.3 Parameter Design

In this section, the design process of some system parameters is provided as follows.

## (a) Design of $D_1$

$D_1$ , namely  $D_{act}$  in the active clamp circuit, is a parameter related to the range of  $\varphi_{HL}$  and  $P_f$ . The design process of  $D_1$  refers to [34]. In [34],  $D_1$  is set to be 0.4 in SSM. However, in MDPSM, the output power range is twice wider than SSM, which means that  $D_1$  should be smaller than 0.4 to realize the wider power range. So  $D_1$  is set to be 0.32.

#### (b) Design of $D_{2,open}$

$D_{2,open}$  is also a parameter related to the transfer power. By (2.31), it can be found that the larger  $D_2$  can generate wider output power range. To realize the maximum transfer with fixed  $D_1$ ,  $D_{2,open}$  should be set to 0.5- $D_d$ . In this case,  $D_{2,open}$  is set to 0.47.

#### (c) Design of the transformer

The system parameters in the transformer, namely N and  $L_{lk}$ , play important roles in the value of  $I_{lk}$  and  $I_L$ . In MDPSM,  $N_{min}$ , the minimum value of N, can be designed first due to the setting of  $V_{ca} \geq \frac{V_H}{N}$ , where  $V_{ca}$  can be calculated in (2.26). However, it can be found in (2.14) that the value of  $V_{ca} - \frac{V_H}{N}$  is related to the ZVS condition of  $S_{act}$ . To ensure the ZVS operation of  $S_{act}$ , the exact value of N is set to be 1.25\* $N_{min}$ . Then,  $L_{lk}$  can be designed by (2.31). In this case, N is set to be 6.75 and  $L_{lk}$  is set to be 2.02 $\mu$ H.

# **Chapter 4 Hardware Implementation**

In this chapter, a rated 720W AC-CFDAB converter is designed to verify MDPSM and MEPT. The hardware circuit is introduced first in section 4.1, followed by details of DSP program in section 4.2.

# 4.1 Hardware Design

In this section, the hardware design of an AC-CFDAB is introduced. The power stage circuit includes the power board and the driver board circuit. The control stage circuit contains sensor circuits and a microcontroller. The specification is in Table 4.1. The detail of designing the hardware circuit is introduced in this section.

Table 4.1 System specification.

| Rated Power                                               | 720W   |  |  |

|-----------------------------------------------------------|--------|--|--|

| LVS Voltage                                               | 48V    |  |  |

| HVS Voltage                                               | 400V   |  |  |

| Switching Frequency                                       | 100kHz |  |  |

| LVS Switching Node Duty (D <sub>1</sub> )                 | 0.32   |  |  |

| LVS Inductor (L <sub>LV</sub> )                           | 135μΗ  |  |  |

| Transformer Turning Ratio (N)                             | 6.75   |  |  |

| Transformer Leakage Inductor $(L_{lk})$                   | 2.02μΗ |  |  |

| Active Clamp Capacitor (Ca)                               | 20μF   |  |  |

| LVS Deadtime Ratio (D <sub>td1</sub> , D <sub>td2</sub> ) | 0.02   |  |  |

| HVS Deadtime Ratio $(D_{d,lead}, D_{d,lag})$              | 0.03   |  |  |

## 4.1.1 Power Stage Circuits

The power stage contains a LVS power board, a HVS power board, driver boards, and a transformer. Each of them is introduced in the following.

#### (a) Power boards.

In the LVS power board, there are a LVS capacitor, a LVS inductor, an active clamp circuit, and a full-bridge circuit. Fig. 4.1 shows the detail of the LVS power board.

Fig. 4.1 LVS power board.

The main purpose of the LVS capacitor,  $C_{LV}$ , is to stabilize the LVS voltage,  $V_{LV}$ , so a 470uF/450V electrolytic condenser, whose capacitance is higher than other type of capacitors, is chosen.

The LVS inductor,  $L_{LV}$ , plays an important role in decreasing the LVS current ripple. In this circuit, a 135uH inductor is chosen. Consider the core saturation and winding turns, two high flux core CH572060 are applied to realize  $L_{LV}$ .

The active clamp capacitor,  $C_a$ , is a key component in the active clamp circuit. The capacitance of  $C_a$  is related to the voltage ripple of  $V_{ca}$ , which is supposed to be a constant in the previous analysis and the transient time in load change. Take both the

factors into consideration, a 20uF capacitor is chosen. In addition, because active clamp is a crucial part in this circuit, a film capacitor is applied to ensure the stability in the experiment.

Cool MOSFETs are chosen in the active clamp switch,  $S_{act}$ , and full-bridge switches,  $S_1 \sim S_4$ . Cool MOSFET has lower on-resistance than convention MOSFET and is also cheaper than the wide-band-gap(WBG) MOSFET. It is a popular choice in the low voltage case. Due to the same maximum voltage and compatibility of the driver circuit, the Cool MOSFET IRFP4868PBF is chosen in all switches in the LVS power board.

Fig. 4.2 HVS power board.

Fig. 4.2 shows the detail of the HVS power board. There are a full-bridge circuit and a HVS capacitor,  $C_{HV}$ , in the HVS power board.

Same as  $C_{LV}$ ,  $C_{HV}$  is applied to stabilize the HVS voltage,  $V_{HV}$ , so a 470uF/450V electrolytic condenser is also chosen.

The power loss of HVS switches plays a crucial role in the total power loss. Because of the high maximum voltage, the withstand voltage of HVS switches must be higher than

LVS switches. However, it is a tradeoff between the withstand voltage and the turn-on resistance. Higher withstand voltage leads to higher turn-on resistance, which causes higher power loss. To decrease the power loss, WBG switches are chosen in this case. WBG MOSFETs have the higher bandgap and higher withstand voltage than conventional MOSFETs, which is popular in high voltage cases. In HVS power board, SiC MOSFETs, which are suitable for the high power case, H1M065F050 are chosen.

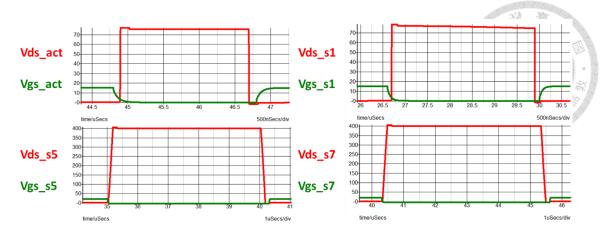

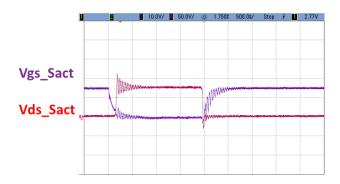

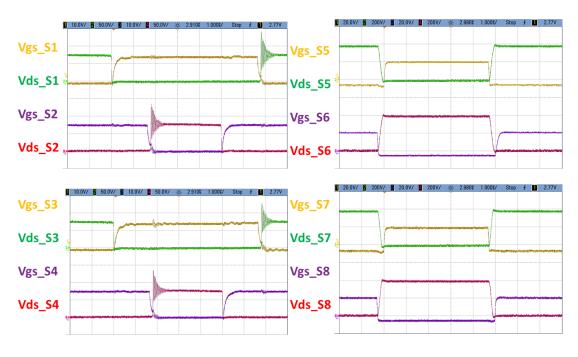

#### (b) Driver boards.

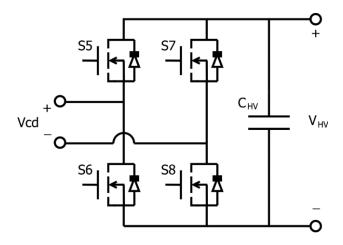

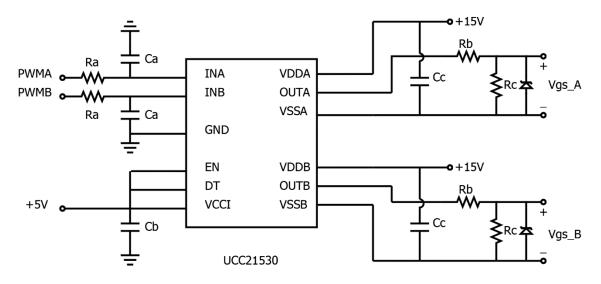

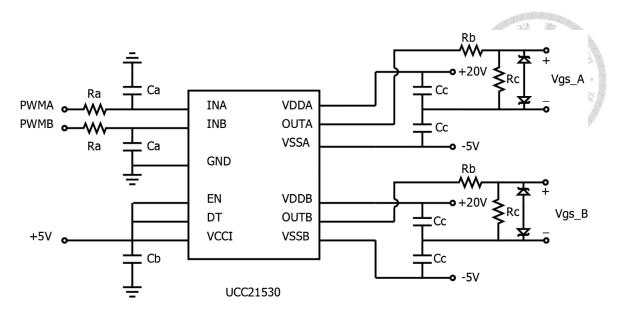

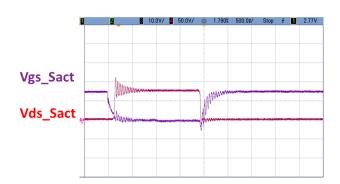

Fig. 4.3 and Fig. 4.4 are the circuit of LVS and HVS driver boards. Driver IC UCC21530 is chosen to drive both Cool MOSFETs and SiC MOSFETs. UCC21530 is an isolated dual-channel gate driver from TEXAS INSTRUMENTS. It has the proper output range (25V to -5V) and enough driver current (source current 4A/ sink current 6A) that is very suitable for both Cool MOSFETs and SiC MOSFETs. The details of the driver board designs are in the following.

Fig. 4.3 LVS driver board.

Fig. 4.4 HVS driver board.

$R_a$  and  $C_a$  form a RC low-pass filter to decrease the influence of the input noise. The cutoff frequency of the filter is in (4.1). In this case, the cutoff frequency is set to be 100MHz.

$$f_{cutoff} = \frac{1}{2\pi RC} \tag{4.1}$$

EN and DT pins are two functions of this driver IC. EN pin is related to the output channel. If EN is high, both output channel A and B are enable. While both output channel are disable as EN pulling low. DT pin is the dead time function pin. If deadtime resistor,  $R_{DT}$ , is placed between DT pin and GND pin, the output signal deadtime(ODT) is set by (4.2). If two output signal is overlapped, the DT function needs to be disable with DT pin connecting with VCCI pin. In this case, EN function must be enable and DT function must be enable, so both pins are connecting with VCCI pin.

$$ODT(in \ ns) = 10 * R_{DT}(in \ k\Omega)$$

(4.2)

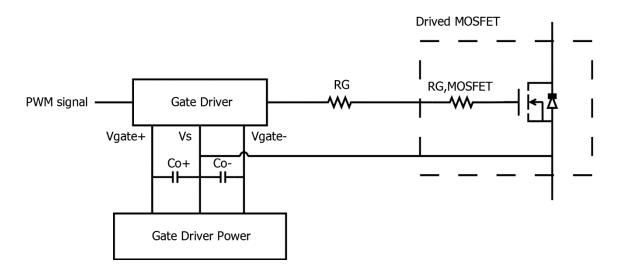

$R_b$  and  $C_c$  play an important role in the process of driving MOSFETs. The design process refers to [39] and the related model is in Fig. 4.5. The resistors and capacitors can be designed by  $(4.3) \sim (4.5)$ , where  $R_{G,min}$  is the additional gate resistor,  $C_{o+,min}$  is the minimum output capacitor for positive driver source,  $C_{o-,min}$  is the minimum output capacitor for negative driver source,  $V_{gate+}$  is the output positive gate voltage,  $V_{gate-}$  is the output negative gate voltage,  $I_{source}$  is the peak source current of the driver,  $R_{G,MOSFET}$  is the gate resistor of the MOSFET,  $Q_{gate}$  is the total driving power of the MOSFET,  $V_{drop}$  is the output voltage drop.

In this case,  $R_G$ , which is  $R_b$  in Fig. 4.3 and Fig. 4.4, is selected to be 5.1 $\Omega$ ,  $C_{o+}$  and  $C_{o-}$ , which are  $C_c$  in Fig. 4.3 and Fig. 4.4, are selected to be 10.22 $\mu$ F.

Fig. 4.5 Driver circuit model in [39].

$$R_{G,min} = \frac{V_{gate+}}{I_{source}} - R_{G,MOSFET}$$

(4.3)

$$C_{o+,min} = \frac{2 * Q_{gate} * V_{gate+}}{{V_{gate+}}^2 - (V_{gate+} - V_{drop})^2}$$

$$C_{o-,min} = \frac{2 * Q_{gate} * V_{gate-}}{{V_{gate-}}^2 - (V_{gate-} - V_{drop})^2}$$

The main purpose of  $R_c$  is to ensure the low voltage level when open loop. Its resistance should not be too small to influence the driving ability, so in this case  $R_c$  is chosen to be  $10k\Omega$ .

#### (c) Transformer design

The transformer isolates the switching node voltage,  $V_{ab}$  and  $V_{cd}$ . Its leakage inductor,  $L_{lk}$ , and magnetic inductor,  $L_m$ , play crucial roles in power transmission and ZVS condition. Also, in MDPSM,  $V_{ca}$  must be larger than  $\frac{V_H}{N}$ . With the limit above, the detailed parameter is set in Table 4.2. To consider the core saturation, EE65 material is chosen in this circuit.

Table 4.2 Transformer parameter.

| $L_{lk,LV}$      | 2.02 μΗ |  |  |

|------------------|---------|--|--|

| $L_{m,LV}$       | 66 μΗ   |  |  |

| N                | 6.75    |  |  |

| $R_{copper,LVS}$ | 0.006Ω  |  |  |

| $R_{copper,HVS}$ | 0.018Ω  |  |  |

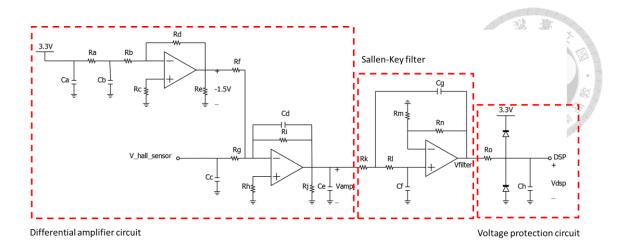

# 4.1.2 Control Stage Circuits

The control stage circuits contain a microcontroller and sensing circuits. In order to calculate the total efficiency, voltages and currents from LVS and HVS should be sensed. However, some output voltages of sensing components are too high for the microcontroller, so some additional circuits are applied to transfer the sensing signal. In this section, the detailed design of the control stage circuit is shown.

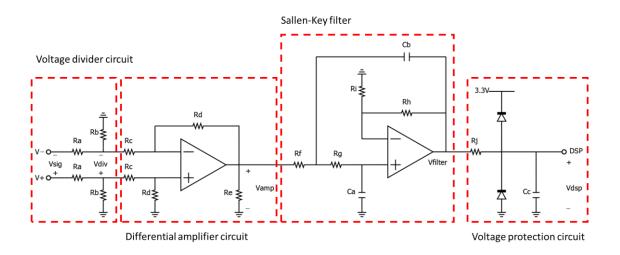

#### (a) Voltage sensing circuits

Voltage sensing circuits consist of two operational amplifiers, TL084, some voltagedivided resistors and some filter resistors and capacitors. These sensor circuits measure LVS and HVS voltage respectively. The topologies of LVS and HVS voltage sensing circuits are both the same and are shown in Fig. 4.6. A total voltage sensing circuit can be divided into a voltage divider circuit, a differential amplifier circuit, a Sallen-Key filter and a voltage protection circuit, all of which are introduced in the following.

Fig. 4.6 Voltage sensing circuit.

The voltage divider circuit transfers the input sensor signal,  $V_{sig}$ , into  $V_{div}$  by a simple resistor divider. To take the next stage resistor,  $R_c$ , into consideration, the overall transfer function is (4.6).

$$\frac{V_{div}}{V_{sig}} = \frac{R_b / / R_c}{R_a + R_b / / R_c} = \frac{R_b R_c}{R_a R_b + R_b R_c + R_a R_c}$$

(4.6)