## 國立臺灣大學電機資訊學院光電工程學研究所

#### 碩士論文

Graduate Institute of Photonics and Optoelectronics

College of Electrical Engineering and Computer Science

National Taiwan University

Master Thesis

以粒子群最佳化演算法設計適用於雙極化的高效率光柵 耦合器

Two-dimensional Grating Coupler Compatible with Dual Polarization Based on Particle Swarm Optimization

戴胤

Yin Dai

指導教授: 黃定洧博士 Advisor: Ding-Wei Huang, Ph.D.

> 中華民國 111 年 8 月 August 2022

#### 摘要

在科技迅速變化的現代,元件自動化設計可以大幅縮短元件開發時程,再搭配最佳化演算法設定合理的效能指數,便可快速產出符合各式需求的元件。

本篇論文將以 python 實作包含演算法在內的完整自動化設計流程,搭配製程簡單且最小線寬為 150 nm 的二維光柵耦合器,利用最佳化演算法來調整元件參數,過程會以 Ansys 公司的商用軟體 Lumerical-FDTD 來模擬元件效能。如此一來便可同時滿足:元件自動化設計、快速設計、高效元件設計的需求,提供一種設計模式給科技迅速變化的現代做為參考。

為了提高二維光柵耦合器的耦合效率,本篇論文使用了三種設計方法,分別為 繞射強度漸變型 (Apodized) 光柵、兩階段式蝕刻、傾斜的光柵排列。除此之外,為 了降低最佳化過程的 3D FDTD 模擬次數,採用了兩階段式的最佳化流程來縮小最佳 化演算法的搜索範圍。並且利用三次方樣條內插法來內插出光柵的各個週期中的漸 變參數,此種作法可減少元件的參數數量,藉此維持最佳化演算法的求解能力。

最後會與其他文獻設計出的二維光柵耦合器做比較,-3.2 dB 的元件耦合效率已足以證明此篇自動化、最佳化、快速設計流程的有效性。且鑒於本篇光柵耦合器並無使用金屬反射層等複雜結構,並最小蝕刻線寬 (Minimum Feature Size) 為 150 nm 的全蝕刻,單純的結構亦有利於製造量產。若未來需要考量其他項元件效能,做多目標式的元件設計,我們也只需將效能指數設為多目標函數,並沿用此種設計流程,便可快速設計出各式需求的元件。

關鍵字:二維光柵耦合器、矽光子學、積體光學、粒子群最佳化演算法、兩階段蝕刻、繞射強度漸變型光柵耦合器、自動化設計

#### **ABSTRACT**

As the technology changes rapidly nowadays, design automation can shorten the development time of device significantly. With the optimization algorithm by setting a proper figure of merit, we can develop various devices to meet different needs.

In this thesis, the design automation and optimization algorithm were implemented in Python. A design pattern of 2-D grating coupler which was easy to be fabricated, under the limitation of 150 nm minimum feature size, was applied with the commercial CAD software, Lumerical FDTD Solution from Ansys. Based on the design pattern, we can achieve automated design, fast development, device with high performance, to meet the technical needs today.

The 2-D grating coupler combined three design ideas: diffracting apodization, two step etching, and tilt grating lattice. In addition, the design flow was split into two steps so as to narrow the searching space of optimization algorithm and reduce the times of 3-D FDTD simulation. Furthermore, the number of parameters can be reduced and the searching ability of optimization algorithm can be sustained by applying the cubic spline interpolation to the parameters of apodized 2-D grating coupler.

The 2-D grating coupler is designed for C-band, and the performances of the optimized designed are: the incident light which electric field polarized parallel to its incident plane has peak of theoretical coupling efficiency is 48% (–3.2 dB) at wavelength equals to 1550 nm; polarization dependent loss is 0.17 dB; the –3 dB bandwidth is 40 nm; and the crosstalk between two waveguides is smaller than –15 dB between 100 nm bandwidth.

At the end of this thesis, the 2-D grating coupler was compared to the others, and the theoretical coupling efficiency is as high as -3.2 dB could validate the performance of the two steps design flow and the design automation in this thesis. Since the grating coupler is designed without complex structures like metal mirror, and the minimum feature size is 150 nm, it could meet the requirement for mass production. Also, it's possible to develop various devices for more complex needs by the multiple-objective optimization and the design flow in this thesis. We just need to make figure of merit as a function of the multiple objects.

Keywords: 2-D grating coupler, silicon photonics, integrated photonics, particle swarm optimization, two-step etching, apodized grating coupler, design automation

#### 致謝

首先我想感謝我的父母,只有他們可以包容我崎嶇又任性的求學歷程,並且無 怨無悔的支持我做出的各種決定。今天我能順利自大學及研究所畢業,不單只是興 趣驅使,也有一部分是我想成為足以令他們自豪的兒子。

接下來想感謝的是我的指導教授,黃定洧老師。老師的指導風格給了我非常大的自由研究空間。也正是老師放任我自由研究,盡情使用實驗室的各式資源,才能有我這篇論文的誕生。實驗室成員每週報告的文獻種類相當多元,黃定洧老師仍能根據他廣泛且淵博的知識提供各種見解給大家,也常常提示同學們可能的研究方向。雖然老師平常話不多酷酷的,但兩年的時間相處下來,可以感受到老師其實很熱衷教學與經驗知識的傳承,只要同學主動找老師請教。

接下來我想感謝鐘國芳學長,他在我操作光學模擬軟體、產出並分析元件數據時給了我很多建議,讓我少走了很多冤枉路,加快我的研究進度。學長經手過的元件也非常多元,每次跟學長的閒聊都讓我收穫不少。

最後我想感謝實驗室全員,老師給了學生們很大的自由做自主研究,但我大概 是最任性的那一位學生,實驗室庶務的部分幾乎沒有幫上忙,非常感謝實驗室同學 們接納我的任性。碩二時期更是與大家聊了許多產業與生涯選擇的話題,這讓我的 視野更加寬闊,也更能做出符合自己風格的選擇。

感謝一路走來所有與我有交流的人,我的每一個朋友,你們滿足了我喜歡跟人 交換意見的慾望,也促使我成長成現在的樣子,謝謝。

## 目錄

| 摘要                                          | A ji |

|---------------------------------------------|------|

| ABSTRACT                                    | ii   |

| 致謝                                          | iv   |

| 目錄                                          | v    |

| 圖目錄                                         | vii  |

| 表目錄                                         | ix   |

| 第一章 序論                                      | 1    |

| 1.1 元件背景介紹                                  | 1    |

| 第二章 研究方法與動機                                 | 4    |

| 2.1 時域有限差分法 (Finite Difference Time Domain) | 4    |

| 2.2 粒子群最佳化演算法 (Particle Swarm Optimization) | 7    |

| 2.3 光栅設計原理                                  | 9    |

| 2.4 實作最佳化演算法的平台與程式碼                         | 10   |

| 2.5 研究動機                                    | 11   |

| 第三章 文獻探討                                    | 13   |

| 3.1 兩階段蝕刻一維光柵設計                             | 13   |

| 3.2 雙橢圓二維光柵設計                               | 15   |

| 3.3 漸變型二維垂直光柵設計                             | 18   |

| 第四章 元件設計流程                                  | 22   |

| 4.1 設計流程簡介                | 22 |

|---------------------------|----|

| 4.2 第一階段 傾斜結構之均勻型光柵設計     | 25 |

| 4.3 第二階段 以均勻型光柵參數來設計漸變型光柵 | 27 |

| 第五章 數據分析與探討               |    |

| 5.1 耦合效率與串擾               | 31 |

| 5.2 極化相依損耗                | 33 |

| 5.3 光纖傾角容忍度分析             | 36 |

| 5.4 淺蝕刻位置偏移容忍度分析          | 38 |

| 第六章 結論與展望                 | 41 |

| 6.1 結論                    | 41 |

| 6.2 展望                    | 42 |

| 參考文獻                      | 43 |

## 圖目錄

| 昌 | 1.1 於 1990 年代所提出,電光整合晶片的構想1                                                        |

|---|------------------------------------------------------------------------------------|

|   | 1.2 1550nm 的光在 220nm 高的矽基通道波導中傳播時,模態等效折射率隨波導寬<br>  變化                              |

|   | 2.1 Yee Cell5                                                                      |

| 區 | 2.2 Yee Cell 中彼此錯開半步長的電場與磁場推移順序示意圖6                                                |

| 邑 | 2.3 入射光栅後依據布拉格條件畫出的繞射波向量圖9                                                         |

| 置 | 2.4 自動化設計下兩台電腦的工作流程圖10                                                             |

| 置 | 3.1 (a)兩階段蝕刻設計樣式(b)有無次波長光柵之耦合效率比較14                                                |

| 昌 | 3.2 雙橢圓二維光柵設計15                                                                    |

| 昌 | 3.3 橢圓短軸對應雙極化耦合頻譜變化16                                                              |

| 昌 | 3.4 光纖入射方向導致繞射波向量傾角示意圖16                                                           |

| 昌 | 3.5 垂直入射光栅後布拉格條件下的繞射波向量圖18                                                         |

| 昌 | 3.6 常見的垂直光柵設計模式(a)十字型(b)反射型19                                                      |

| 置 | 3.7 Watanabe 的二維光柵(a)二維光柵的俯視圖(b)光柵結構的截面圖20                                         |

| 邑 | 4.1 兩階段的設計流程示意圖                                                                    |

|   | 4.2 (a)元件模擬平台所使用的 SOI 晶圓示意圖(b)光源沿對稱軸入射示意圖(c)垂直<br>-射光源之電場極化角度示意圖,實際入射光會與法線夾 10°角24 |

|   | 4.3元件結構與參數示意圖,以5個參數設計均勻型的二維光栅25                                                    |

|   | ig  4.4 元件結構與參數示意圖,漸變型二維光柵單一週期中的參數,標示成橘色的 $ig  eta$ 固定設為第一階段的參數結果27                |

| 圖 4.5 依據表 4.2 的節點內插出漸變光柵各個週期內的參數變化   | 29                           |

|--------------------------------------|------------------------------|

| 圖 4.6 漸變型二維光柵耦光俯視圖,四張圖入射光之極化角度分別為    | $(a)0^{\circ} (b)45^{\circ}$ |

| (c)90° (d)135°                       | 30                           |

| 圖 5.1 漸變型二維光柵之耦合效率頻譜                 |                              |

| 圖 5.2 串擾隨波長之變化                       | 32                           |

| 圖 5.3 1550 nm 的入射光,耦合效率之於極化角度的變化     | 33                           |

| 圖 5.4 極化相依損耗頻譜(a)產生最大極化相依損耗的兩種極化之耦合光 | ć譜(b)由兩種                     |

| 極化之耦合效率差異取絕對值所算出的最大極化相依損耗光譜          | 34                           |

| 圖 5.5 光纖傾角誤差的設定方式                    | 36                           |

| 圖 5.6 不同光纖傾角下耦合效率的變化                 | 37                           |

| 圖 5.7 淺蝕刻位置偏移示意圖                     | 38                           |

| 圖 5.8 耦合效率隨淺蝕刻偏移之變化                  | 39                           |

# 表目錄

| 表 4.1 | 均勻二維光柵的參數      | 26 |

|-------|----------------|----|

| + 10  | 漸變型光柵各參數節點的值   |    |

| 表 4.2 | , 漸變型光柵各麥數即點的值 | 28 |

| 表 6.1 | 本論文與其他文獻的比較    | 41 |

### 第一章 序論

#### 1.1 元件背景介紹

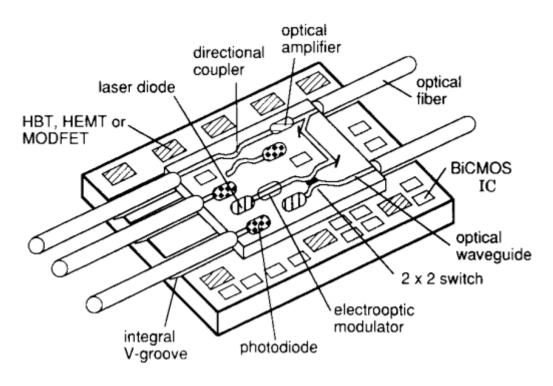

早在 1990 年代就有了積體光學的概念,當時科學家與工程師們想將光與電整合於單一晶片上,稱其為超晶片[1]如圖 1.1 所示。由於矽在波長大於 1.2 μm 的電磁波段為透明<sup>[2]</sup>,恰好可以適用於波長為 1.3 μm 與 1.55 μm 的常見光纖通訊波段。若以矽作為導光層 (Core)、二氧化矽作為包覆層 (Cladding),基於矽與二氧化矽的高折射率差使得光在矽基波導中的侷限性非常好,有利於做出面積更小、元件密度更高的矽光子晶片。再受益於發展成熟的 CMOS 製程,半導體產業中的 SOI (Silicon-on-Insulator) 晶圓,恰好可用於製造前述的矽基波導,上述種種原因使得積體光學相關研究中,又以矽光子積體迴路占了最大宗。

圖 1.1 於 1990 年代所提出,電光整合晶片的構想[1]

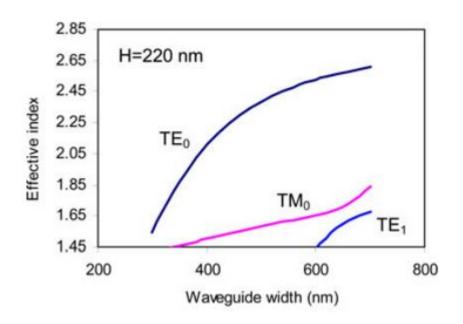

鑒於矽光子的先天優勢,許多文獻將各式元件整合到 SOI 的平台上,舉凡光調制器<sup>[3][4][5]</sup>、極化分離器<sup>[6][7]</sup>、多模干涉分光器<sup>[8][9]</sup>、耦合器<sup>[10][11]</sup>、用於分波長的陣列波導光柵<sup>[12][13]</sup>、結合表面電漿模態的模態轉換器等<sup>[14]</sup>。然而矽光元件在受惠於矽與二氧化矽帶來的高光場侷限性的同時,矽光元件的光源一直是個問題,舉例來說,波長為 1550 nm 的光在 220 nm 高的矽基通道波導中傳播時,模態等效折射率隨波導寬度變化如圖 1.2 所示。

圖 1.2 1550nm 的光在 220nm 高的矽基通道波導中傳播時,模態等效折射率隨波導寬 度變化<sup>[15]</sup>

由圖 1.2 可看出,若我們要將通道波導設計成僅 TEo 可以傳播的單模態形式,則波導的寬度必須小於 600 nm,相較之下,常見的 SMF-28 光纖中 1550 nm 的光模態場直徑為 10.4 µm<sup>[16]</sup>,且矽基波導的導光層是矽,SMF-28 的導光層是二氧化矽。光纖與矽基波導之間,無論是模態場大小還是模態等效折射率都差異甚大,因此耦合器做為晶片與外界的接口,更顯得重要,如何改善其耦合效率一直是熱門研究目標,常見的耦合器有兩種:端面耦合器 (Edge Coupler) 與光柵耦合器 (Grating Coupler)。端面耦合器有高耦合效率 (92%,-0.36 dB)<sup>[17]</sup>與寬頻 (耦合效率 > -2 dB,頻寬為 114

nm)<sup>[18]</sup>的優點。然而端面耦合器只能放在晶片的邊緣,光纖對準容忍度低,並需要對晶片的側面做拋光才能順利在晶片與光纖間耦光<sup>[19]</sup>。相對的,一維光柵耦合器的耦合效率較低 (71%,—1.5 dB),頻寬也較窄 (3 dB 頻寬為 66 nm)<sup>[20]</sup>。無論是頻寬或耦合效率,光柵耦合器皆不及端面耦合器,但光柵耦合器具有光纖對準容忍度高<sup>[10]</sup>、可以放在晶片的任何位置、免去晶片側面拋光製程等優點,使得光柵耦合器整合在晶片上的自由度較端面耦合器高。

為了改善光柵耦合器的耦合效率,各研究團隊提出了一些方法如:兩階段蝕刻的設計提高光柵的方向性 (Directionality)<sup>[21]</sup>,光柵頂端覆蓋多晶矽減少光柵與波導間的模態不匹配 (Mode Mismatch)<sup>[22]</sup>,繞射強度漸變型 (Apodized) 光柵設計<sup>[23]</sup>可減少光柵與光纖間的模態不匹配。

隨著耦合效率的改善,近年來相關研究開始轉向替光柵耦合器附加更多功能,例如:垂直型光柵耦合器用於多核光纖時可以減少封裝難度<sup>[20]</sup>,具有分極化功能的二維光柵耦合器<sup>[24]</sup>等。相較於發展成熟的一維光柵耦合器,二維光柵耦合器相關文獻的實驗量測耦合效率僅 55% (-2.6dB)<sup>[25]</sup>,且其最小線寬約為 40 nm,在耦合效率與如何適用於便宜的製程上,二維光柵耦合器的設計方式尚有很大的改進空間。

#### 第二章 研究方法與動機

此章節將介紹本篇研究中所使用到的模擬方法、最佳化方法、光栅設計原理以及設計流程使用到的工具,並於最後介紹本篇論文的研究動機。

#### 2.1 時域有限差分法 (Finite Difference Time Domain)

時域有限差分法是 1966 年由 Kane Yee 提出<sup>[26]</sup>,一種基於馬克斯威爾方程式的偏微分方程式所建構的差分求解模型,用於計算電磁波在經過均向性 (Isotropic) 材料後的行為。Yee 利用了,馬克斯威爾—法拉第方程式 (Maxwell-Faraday Equation) (2.1 式) 與安培—馬克斯威爾方程式 (Ampère-Maxwell Equation) (2.2 式):

$$\frac{\partial}{\partial t}\vec{H} = -\frac{1}{\mu}\nabla \times \vec{E} \tag{2.1}$$

$$\frac{\partial}{\partial t}\vec{E} = \frac{1}{\varepsilon}\nabla \times \vec{H} - \vec{J} \tag{2.2}$$

當傳播材料為均向性 (Isotropic) 並且傳播介質無電流時,2.1 式與 2.2 式中的介電係數  $\varepsilon$  (Permittivity)與磁導率  $\mu$  (Permeability) 皆為純量,且 $\vec{J}$  可省略。我們便可將 2.1 式與 2.2 式各分為三個方向的偏微分方程式,以下僅列出 x 方向的兩個偏微分方程式,2.3 式與 2.4 式。

$$\frac{\partial}{\partial t}H_{\chi} = -\frac{1}{\mu} \left( \frac{\partial}{\partial y} E_z - \frac{\partial}{\partial z} E_y \right) \tag{2.3}$$

$$\frac{\partial}{\partial t}E_{x} = \frac{1}{\varepsilon} \left( \frac{\partial}{\partial y} H_{z} - \frac{\partial}{\partial z} H_{y} \right) \tag{2.4}$$

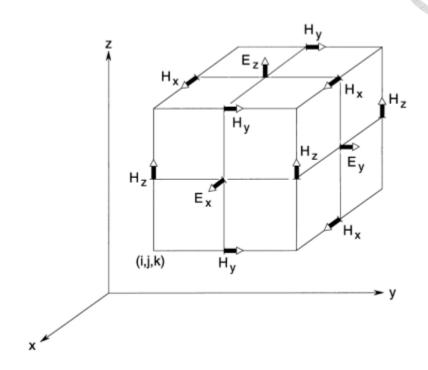

針對 x 方向的 2.3 式與 2.4 式加上未列出的 y, z 方向各兩式, 共六條偏微分方程, Yee 提出了一種非常巧妙的網格切割模型, 被稱為 Yee Cell, 如圖 2.1 所示。

相較於將所有電磁場向量擺放在同一個點上的作法,Yee Cell 將電場與磁場向量錯開半個空間步長 (Space Step),由於電場與磁場在空間上差了半個步長,所以時間上電場與磁場也錯開了半個時間步長 (Time Step)。所有電場向量間距與磁場向量間

距皆為一個空間步長, Yee Cell 這種網格排列方法可以將 2.3 式與 2.4 式兩偏微分方程式, 改成中央差分的方程式, 如 2.5 式與 2.6 式。

圖 2.1 Yee Cell

$$\frac{H_{x} \begin{vmatrix} t + \frac{1}{2} \\ i + \frac{1}{2} j, k \end{vmatrix} - H_{x} \begin{vmatrix} t - \frac{1}{2} \\ i + \frac{1}{2} j, k \end{vmatrix}}{\Delta t} =$$

$$- \frac{1}{\mu_{i+\frac{1}{2}j,k}} \left( \frac{E_{z} \begin{vmatrix} t \\ i + \frac{1}{2} j + \frac{1}{2} k \end{vmatrix}^{-E_{z}} \begin{vmatrix} t \\ i + \frac{1}{2} j - \frac{1}{2} k \end{vmatrix}}{\Delta y} - \frac{E_{y} \begin{vmatrix} t \\ i + \frac{1}{2} j, k + \frac{1}{2} \end{vmatrix}^{-E_{y}} \begin{vmatrix} t \\ i + \frac{1}{2} j, k - \frac{1}{2} \end{pmatrix}}{\Delta z} \right)$$

$$\frac{E_{x} \begin{vmatrix} t + 1 \\ i, j + \frac{1}{2} k + \frac{1}{2} \end{vmatrix} - E_{x} \begin{vmatrix} t \\ i, j + \frac{1}{2} k + \frac{1}{2} \end{vmatrix}}{\Delta t} =$$

(2.5)

$$-\frac{1}{\varepsilon_{i,j+\frac{1}{2},k+\frac{1}{2}}} \left( \frac{H_z|_{i,j+1,k+\frac{1}{2}}^{t+\frac{1}{2}} - H_z|_{i,j,k+\frac{1}{2}}^{t+\frac{1}{2}}}{\Delta y} - \frac{H_y|_{i,j+\frac{1}{2},k+1}^{t+\frac{1}{2}} - H_y|_{i,j+\frac{1}{2},k}^{t-\frac{1}{2}}}{\Delta z} \right)$$

(2.6)

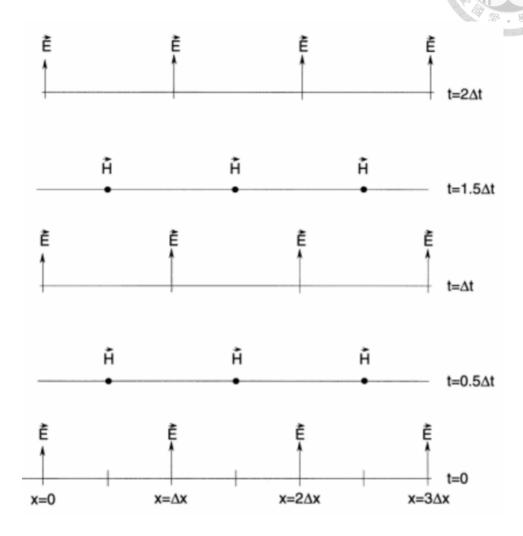

以 2.5 式與 2.6 式做為磁場與電場的推移方程式 (Evolution Equation),只要每次推進半個時間步長,交替做磁場與電場向量的時間推移 (Time Evolution),便可模擬電磁波於物質內的行為,此即為著名的時域有限差分法,其推移順序如圖 2.2 所示。

圖 2.2 Yee Cell 中彼此錯開半步長的電場與磁場推移順序示意圖[27]

## 2.2 粒子群最佳化演算法 (Particle Swarm Optimization)

粒子群最佳化演算法<sup>[28]</sup>是由社會科學家 James Kennedy 與電機工程學家 Russell Eberhart 於 1995 年提出的迭代模型,在問題空間中設置了複數的粒子 (Particle),計算各粒子於問題空間中的效能指數 (Figure of Merit, FOM) 後,所有的粒子會朝向已知效能指數最大的位置 (群體最佳解) 移動,同時粒子也會朝自己歷史位置中效能指數最大的位置 (個體最佳解) 移動,因此粒子群會以繞圈的方式聚集逼近群體最佳解。這種繞圈的收斂路徑使得粒子群最佳化演算法有良好的全域最佳解搜索能力,其迭代式為 2.7 式與 2.8 式:

$$x_i^{t+1} = x_i^t + v_i^{t+1} (2.7)$$

$$v_i^{t+1} = v_i^t + 2r_1(P_g^t - x_i^t) + 2r_2(P_i^t - x_i^t)$$

(2.8)

2.7式與 2.8式中,x 為粒子所在位置,v 為步長,i 為粒子的編號,t 為世代數, $r_1$  與  $r_2$  為由  $0 \sim 1$  之間的隨機數組成的向量,P 為粒子的個體最佳解位置,g 為具有群體最佳解的粒子之編號,最佳化過程便是利用 2.8 式決定所有粒子的步長,再利用 2.7式做為時間推移方程式,令所有粒子朝向群體最佳解位置靠近並搜索。

與經典的牛頓法最佳化相似,粒子群最佳化演算法的目標也是找到問題空間的極值(最大效能指數),然而牛頓法這類依靠梯度來找極值的演算法往往會受限於初始值的選擇,初始值會決定牛頓法找極值的範圍。且因為牛頓法是從單一方向去逼近極值,在面對非線性問題時,牛頓法有可能會收斂於反曲點 (Inflection Point) 而非極值。相較之下,粒子群最佳化演算法迭代的步長會乘上一個隨機數,並且同時受群體最佳解與個體最佳解所吸引,粒子會從各個方向逼近群體最佳解,這使得粒子群最佳化演算法即使在面對高階非線性問題時,也不會收斂在一個非極值的點上。

然而 James Kennedy 的粒子群最佳化演算法中,未提及問題空間的邊界設定與處理方式。為了適用於有最小線寬限制的製程,本論文會採用另一種名為速度調整—吸收型的變種粒子群最佳化演算法[29]。

速度調整代表調整了原始迭代模型決定步長的常數以確保模型收斂,將原始的步長方程式 2.8 式改寫成 2.9 式:

$$v_i^{t+1} = 0.72984v_i^t + 1.496172r_1(P_g^t - x_i^t) + 1.496172r_2(P_i^t - x_i^t)$$

(2.9)

吸收型代表,定義了粒子在試圖移動到任一維度所設定邊界之外時,會將粒子的該維度位置設定於邊界條件上,這種邊界處理方式恰好適用於有最小線寬限制的元件設計。根據該篇文獻提供的基準 (Benchmark) 測試結果,亦證明相較於原始的粒子群最佳化演算法,速度調整—吸收型粒子群最佳化演算法的求解能力較好<sup>[29]</sup>。

## 2.3 光栅設計原理

光柵耦合器的設計原理是利用製程做出週期性的結構,藉由調整光柵條紋與光柵週期的長度,基於 2.10 式的布拉格條件 (Bragg Condition) 算出適合的光纖傾角與光柵週期來讓光透過光柵繞射至我們想要的方向,即:耦合進波導的方向[30]。

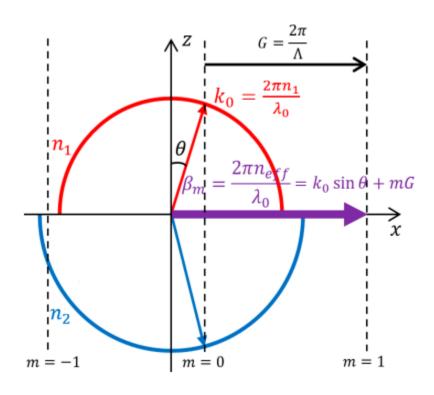

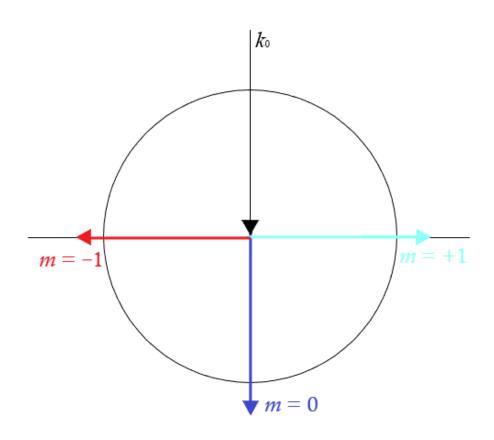

$$k_0 \sin \theta + mG = \beta_m \tag{2.10}$$

2.10 式中, $\theta$  為入射光方向與光栅法向量之夾角, $\beta_m$  為入射光栅後第 m 階繞射光之波向量(單位:公尺 $^{-1}$ ),G 為週期性光栅提供的倒置晶格向量(單位:公尺 $^{-1}$ ), $k_0$  為入射光於真空中的波向量(單位:公尺 $^{-1}$ )。由於高階繞射的光強度通常隨繞射階數的增加而減少,因此光栅耦合器的目標為產生平行於晶片表面的第 1 階繞射,並將其耦入波導中,示意如圖 2.3 紫色箭頭之繞射。

圖 2.3 入射光栅後依據布拉格條件畫出的繞射波向量圖[30]

## 2.4 實作最佳化演算法的平台與程式碼

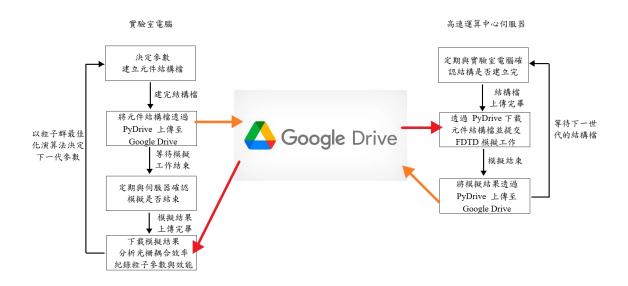

本篇論文同時使用了實驗室與高速運算中心的電腦,兩者負責工作如下

• 實驗室電腦:建立元件結構、分析模擬結果、實行最佳化演算法的迭代

高速運算中心:FDTD 運算

實作設計流程所使用資源如下

• PyDrive:控制電腦與雲端間資料的交換

• PyCharm:控制程式碼環境與版本

• Python 3.9:控制整個設計流程、實現自動化設計

程式碼位置-https://github.com/giginepuran/degree\_thesis

自動化設計的流程如圖 2.4 所示

圖 2.4 自動化設計下兩台電腦的工作流程圖

#### 2.5 研究動機

以往光學元件的設計總是需要經過各種複雜的光學模型,精準的預測電磁波經過元件後的各種行為。因此光學元件的設計者往往需要豐富的設計經驗,才能設計出足以滿足不同需求的光學元件。

1966 年 Kane Yee 就提出了時域有限差分法<sup>[26]</sup> (Finite-Difference Time-Domain,FDTD),利用馬克斯威爾方程式求解偏微分方程,只要根據光源的波長設定合理的時間與空間步長 (Step),切割出夠小的網格 (Mesh),確保時域有限差分模型收斂,便可利用此模型應對任何由均向性 (Isotropic)物質構成的光學元件結構,計算出電磁波經過元件後的行為。

雖時域有限差分法看似光學元件設計的萬能模型,但當時電腦計算能力完全無法滿足其計算需求。舉例來說,電腦中單精度浮點數 (Float) 的大小為 4 Bytes,而三維時域有限差分模型中的一個網格 (Mesh) 至少包含了電場與磁場各三個方向的向量其強度與相位資訊,再加上該網格位置所用物質的介電係數 (Permittivity) 與磁導率 (Permeability) 兩個複數,意即一個網格至少需要保存 6×2+2×2=16 個浮點數的值用於解偏微分方程,運算過程每有一個網格便需要使用 64 Bytes 的空間來儲存資料。

相較於時域有限差分運算過程的空間需求,當時的硬體規格可說是絕望性的不足。舉例來說,Intel 於 1970 年釋出了首個動態隨機存取記憶體 (Dynamic Random Access Memory, DRAM) 商品 Intel 1103<sup>[31]</sup>,該記憶體容量為 1 kbits 約等於 125 Bytes,僅能儲存2個三維時域有限差分的網格,就算利用讀寫網格資料的方式來節省記憶體需求,也會受限於當時儲存空間大小與讀寫速度的限制,嚴重降低運算速度。

時至今日,硬體規格以指數趨勢逐年成長,當年的時域有限差分也被用於快速 驗證各種複雜的光學元件設計。如今的光學元件設計者們可以根據已知的元件理論 模型,在知道元件大致輪廓的前提下搭配各種數值運算來找到最佳元件設計的收斂 解。雖然以往透過複雜的理論計算得出元件設計的全域最佳解非常浪漫,但在科技快速變化的現代,我們需要在開發耗時與元件性能間做出取捨。

如何快速、有效率的設計與驗證元件性能,早以是現今科技產業一大重點。恰好實驗室申請了國網中心的高速運算服務,滿足了最佳化演算法應用於元件設計時的大量時域有限差分計算需求,我們只需設定好最佳化流程中參數變動的上下限,便可找出符合我們現有下線服務之最小線寬限制下的最佳元件設計解,利用這類設計方法便可滿足設計快速、可製造且高效率元件的需求。

### 第三章 文獻探討

為了改善光柵耦合器的耦合效率,相關文獻的作法有:利用兩層式的交錯光柵來提高光柵繞射的方向性<sup>[32]</sup>、於光柵 0 階繞射側加入分散式布拉格反射器<sup>[33]</sup> (Distributed Bragg Reflector, DBR) 或金屬反射層<sup>[34]</sup>來減少 0 階穿透損耗。

綜觀以上兩種設計模式皆無法以標準的 CMOS 製程製作,不僅提高製造成本,若需要特規的製程步驟,也會限制光柵耦合器與其他光電元件的相容性,反而違背了積體光學元件的整合光電晶片初衷。考量到製程可行性,我認為改善光柵耦合器最好的方法為兩階段蝕刻的光柵設計與漸變型光柵設計,以下將就使用了這兩種設計方法與傾斜光柵排列的文獻,針對設計模式與參數設定方式作探討。

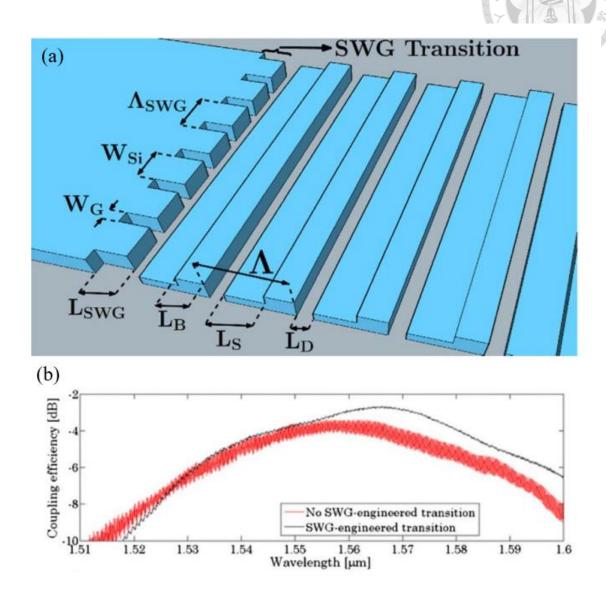

#### 3.1 兩階段蝕刻一維光柵設計

標題為「L-shaped fiber-chip grating couplers with high directionality and low reflectivity fabricated with deep-UV lithography」 [21]的文獻中,作者們利用了兩階段蝕刻出的 L-Shaped 光栅如圖 3.1(a),在一個周期的光柵中同時存在兩種蝕刻深度不同的條紋。這種作法可以想像成,此光柵是兩種週期相同的光柵的疊加,藉由調整兩種蝕刻深度的條紋寬度,使兩者的第 0 階穿透行破壞性干涉,來降低第 0 階穿透損耗,提高光柵的方向性 (Directionality),進一步提高耦合效率。

而兩階段蝕刻的設計,為了達成向下破壞性干涉,會需要兩種深度的蝕刻面積要夠大,單一週期中矽的占比會降低許多,導致了光柵區域的模態場型與等效折射率都會和波導的模態有所差異,進而在光柵進波導區間產生較強的背向反射,通常將此反射稱為模態不匹配損耗 (Mode Mismatch Loss)。

對此,此篇作者們於光柵與波導間區域設計了一段次波長光柵區域,調整次波長光柵的填空比 (Duty Cycle),將次波長光柵做為光柵與波導間的折射率匹配層,來

降低入波導的模態不匹配損耗。比對有無抗反射次波長光柵的結果如圖 3.1(b),最高耦合效率可自-3.4 dB 改善至-2.7 dB。

圖 3.1 (a)兩階段蝕刻設計樣式(b)有無次波長光柵之耦合效率比較[21]

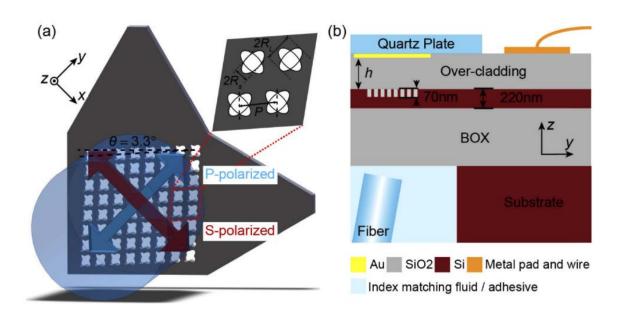

## 3.2 雙橢圓二維光柵設計

為了降低入射光經光柵反射回光纖的能量,一般光纖入射方向會與晶片表面之法向量夾一角度,這也直接導致了電場極化平行於入射面的P極化,與電場極化垂直於入射面的 S 極化之間,兩者會有相異的耦合頻譜<sup>[35]</sup>,便產生了極化相依損耗 (Polarization Dependent Loss,PDL) 用於描述因極化改變導致的耦合效率下降。

圖 3.2 雙橢圓二維光柵設計

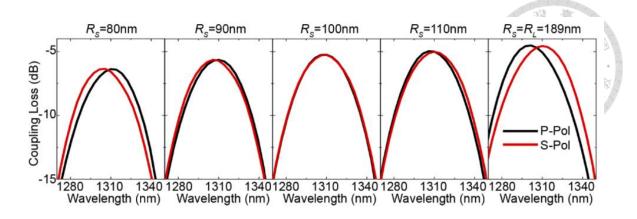

圖 3.2 是取自標題為「Two-dimensional grating coupler on silicon with a high coupling efficiency and a low polarization-dependent loss」的文獻  $^{[35]}$ 中二維光柵耦合器的設計圖。作者們利用兩個重疊的橢圓作為光柵的蝕刻形狀,如圖 3.2(a)右上角所示。之所以選擇雙橢圓的蝕刻形狀,是因為他們發現若維持橢圓蝕刻面積的同時去增加橢圓的長軸 $R_L$ 、減少橢圓的短軸 $R_S$ ,P極化的耦光頻譜會紅移,S 極化的耦光頻譜則是藍移,如圖 3.3。

圖 3.3 橢圓短軸對應雙極化耦合頻譜變化

圖 3.3 中最右邊為圓形蝕刻下的光柵耦合頻譜,可看到隨著短軸  $R_s$ 的漸縮,P極化與 S 極化的耦合頻譜會朝反方向位移,在將短軸調整成 100 nm 後,雖然耦合效率略為下降且頻寬變窄,取而代之的是可以換到近乎重合的雙極化耦合頻譜,如圖 3.3 中間  $R_s$ 為 100 nm 之頻譜圖,最大限度的降低極化相依損耗 (Polarization Dependent Loss,PDL)。他們設計出的二維光柵耦合器,在 78 nm 的波長區間,極化相依損耗可以維持在 0.2 dB 以下,已經優於眾多端面耦合器之極化相依損耗 [19]。也是目前二維光柵耦合器相關文獻中,極化相依損耗最低,適用頻寬最寬的一篇。

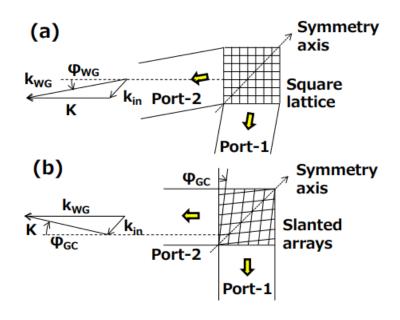

圖 3.4 光纖入射方向導致繞射波向量傾角示意圖[34]

然而此篇的光纖對準方向與光柵對稱軸平行,所以布拉格條件 2.10 式中的  $k_0$  (相當於圖 3.4 中的  $k_{\rm in}$ ) 不再平行於波導傳遞方向 (圖 3.4 中的  $k_{\rm wg}$ ),導致繞射波向量  $\beta_m$  也不平行於波導傳遞方向。若要配合斜向繞射,可以將波導也設計成斜的來對齊光柵出光傾角,示意如圖 3.4(a)。也可以像此篇作者,替光柵排列設計一個傾角,便可在維持兩個波導彼此垂直的情況下修正繞射出光的角度 $^{[36]}$ ,示意如圖 3.4(b)。

雖然此篇作者為了提升耦合效率,使用了金屬反射鏡與光纖從矽基板側耦光這類與積體光學晶片整合元件相左的設計。但其他細節的設計方式都很巧妙,特別是在調整橢圓長短軸的前提為固定蝕刻面積這項條件,維持了調整過程中光柵大略的等效折射率,相當於維持了整個布拉格條件 2.10 式,控制等效折射率這一變因,專注於調整長短軸造成的極化相依損耗,非常聰明的做法。

參考此篇光柵週期排列有一個傾角的設計,本次設計流程將會在取得均勻型二維光柵耦合器的元件參數後,沿用均勻型光柵的傾角參數與光柵週期,來加速接下來的漸變型二維光柵耦合器的設計流程。

## 3.3 漸變型二維垂直光柵設計

垂直型光栅最大的好處在於減少元件封裝時的難度<sup>[25]</sup>,封裝容易的優點更是體現在多核光纖 (Multi Core Fiber) 的使用上,不必針對光纖傾角額外調整光柵耦合器陣列的排列方式<sup>[20]</sup>。

相對的因為垂直入射光柵,布拉格條件 2.10 式中的  $\theta=0^{\circ}$ ,繞射的波向量全由 光柵結構決定,因此當入射光為垂直入射晶片表—面時,若目標是將 +1 階的繞射耦 入波導,那在晶片水平面上也必定會有與 +1 階繞射反向的 -1 階繞射產生。提高 +1 階強度的同時,-1 階的強度也會提高,繞射示意如圖 3.5 所示,這使得耦合效率 的提升有限。

圖 3.5 垂直入射光栅後布拉格條件下的繞射波向量圖

為了解決 -1 階繞射降低耦合效率的問題,部分文獻的垂直光柵作法是在 -1 階的尾端也做一個波導,形成十字型的光柵耦合器 $^{[37]}$ ,如圖 3.6(a)。或在 -1 階繞射方向的尾端,設計分散式布拉格反射器 (Distributed Bragg Reflector, DBR) 的結構來反射 -1 階繞射 $^{[38]}$ ,如圖 3.6(b)。

圖 3.6 常見的垂直光柵設計模式(a)十字型<sup>[35]</sup>(b)反射型<sup>[36]</sup>

然而圖 3.6(a)的設計需要多兩個漸縮模態轉換器 (Taper),後續若要合併 -1 階與 +1 階繞射,還需要額外加入耦合元件,大幅提升了元件占用面積。至於圖 3.6(b)的 設計則較難使用最佳化演算法做繞射強度漸變型 (Apodized)的光栅設計。

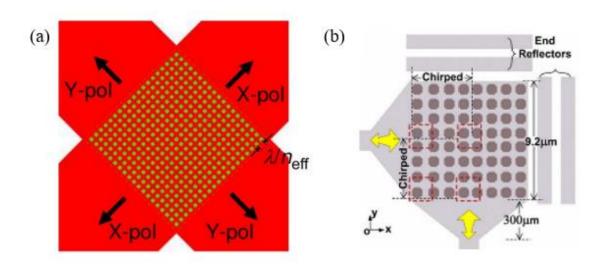

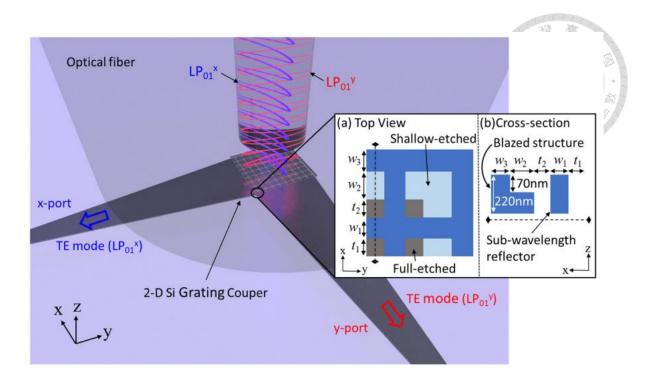

對此,「2-D Grating Couplers For Vertical Fiber-coupling In Two Polarizations」<sup>[25]</sup>,此篇文獻的作者 Watanabe 除了利用兩階段蝕刻的結構來設計光柵,還在每一個光柵週期中加入了用來反射—1 階繞射的次波長反射器 (Sub-Wavelength Reflector) 結構,如圖 3.7(b) 所示。這麼一來就可避免最佳化演算法將與波導反向的光柵結構設計成反射器,只為了稍微提升耦合效率,長遠來看這麼做只會被困在局部最佳解。

圖 3.7 Watanabe 的二維光柵(a)二維光柵的俯視圖(b)光柵結構的截面圖<sup>[25]</sup>

由於 Watanabe 的光栅設計為一個週期中有 5 個參數,整個光栅耦合器中有 20 個週期,若漸變型光柵耦合器的所有參數都做為一個維度,則他的最佳化演算法會需要面對一個 5 × 20 = 100 維度的問題,根據不同粒子群演算法模型相關文獻所提供的基準 (Benchmark) 測試結果[29][39][40],我們可看出高維度的問題會降低最佳化演算法尋找全域最佳解的能力。若一昧的提高演算法一世代中的粒子數量,雖然可以加強演算法的搜索能力,但元件模擬耗時會與粒子數量成正比,因此對於 FDTD 這種龐大網格的模擬運算而言,增加粒子數並非好方法。

為此,Watanabe 選定了 5 個光柵週期作為節點,利用 3 次方的樣條內插法 (Cubic Spline Interpolation) 來內插出 20 個光柵週期,內插法不只可以做出參數漸變來類比繞射強度漸變 (Apodized) 的設計,還可以有效降低元件的參數數量,整個元件的參數從 100 個被減少至 25 個,提供了最佳化演算法較好的全域最佳解搜索能力<sup>[20]</sup>,而此篇的理論耦合效率可達 -2.4 dB (58%),足以證明利用內差法設計出的繞射強度漸變型二維光柵,確實可以減少元件參數又維持演算法的搜索能力。

不過這篇垂直二維光柵的蝕刻最小線寬約為 40 nm,並無法用我們現有的下線服務做出來。並且垂直型光柵耦合器還需考慮由光柵反射的光打入光纖內,可能會造成量測元件時光源設備損壞的問題,Watanabe 在此篇論文中並沒有提到他的元件的反射損耗大小為何,是否會造成系統的損害。

製程的線寬限制使得我們無法像 Watanabe 在各個週期中同時設計兩階段蝕刻的 光栅結構與次波長反射器 (Sub-Wavelength Reflector),因此我們模擬過程所設定光源 入射方向仍是常見的 10°傾角,也不需擔心自光柵反射的光再次打入光纖。而本篇論 文的設計流程會效法 Watanabe 的三次樣條差值法,來減少繞射強度漸變型二維光柵 的參數數量。

### 第四章 元件設計流程

雖然粒子群演算法不像基因演算法般需要大量的個體數目來做隨機搜索,但 3D FDTD 的元件模擬耗時仍然相當龐大。舉例來說,跑一個模擬範圍約為  $15~\mu m \times 15$   $\mu m \times 5~\mu m$  的二維光柵設計,以 45~nm 細的網格模擬,實驗室個人電腦約需耗時 45~分鐘,即便是國家高速運算中心的超級電腦也需耗時 1~分鐘。

若我們粒子群演算法需要做 30 代的迭代,每一代需要分別對 80 個粒子做 3-D FDTD 運算,則個人電腦會需要花約 75 天的時間,超級電腦亦需要花 45 小時,才能 跑完此命題。如此龐大的模擬耗時,我們可以想像一下,設計一個元件時會提出複數的結構排列與參數範圍,若我們要在十種設計模式中選擇一中最好的,需要分別 對各設計模式進行驗證,使用超級電腦的驗證耗時便為 45×10 = 450 小時。因此,即便是擁有高速運算的資源與強大的最佳化演算法,在處理光學元件模擬時,如何 盡量用最少的粒子數與世代數快速驗證元件設計與搭配最佳化演算法的有效性仍然非常重要。

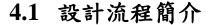

圖 4.1 兩階段的設計流程示意圖

本篇論文將設計流程拆成兩個階段,如圖 4.1 所示,第一階段會先用較少的世代數找出符合布拉格條件的均勻二維光柵之參數。第二階段會取用均勻型光柵的部分參數做為漸變型光柵的固定參數,再利用另一種參數組合來設計漸變型的光柵耦合器。這麼一來,我們便可利用較少的粒子數處理高維度的問題(漸變型光柵設計),也因為第二階段繼承了均勻光柵的部分參數,保障了當前設計模式具有一定程度的有效性,最佳化演算法一開始便可專注於漸變型的參數設計,也降低了最佳化所需的世代數。

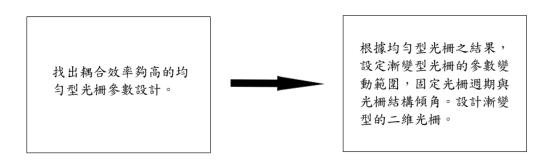

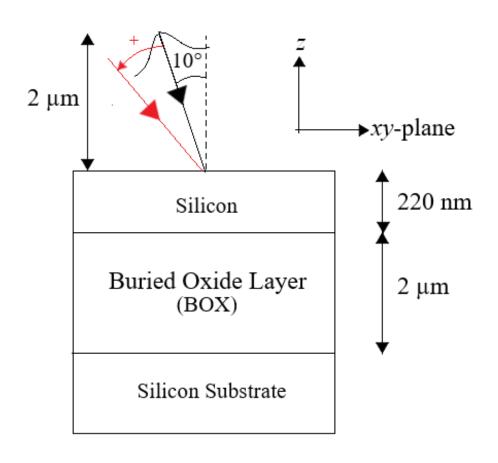

本論文設計過程僅使用商用軟體—Lumerical FDTD Solution 作為模擬元件性能的工具,並全程搭配 2.2 節提到的,速度改編—吸收型粒子群最佳化演算法,當作元件參數的決定依據。模擬平台設定為表面矽厚度為 220 nm 與埋入式氧化層(Buried Oxide Layer,BOX)厚度為 2  $\mu$ m 的 SOI 晶圓,如圖 4.2(a)所示。光源為模態場直徑(Mode Field Diameter,MFD)為 9.2  $\mu$ m 的高斯光場,並且擺放於 220 nm 厚的矽上方 2  $\mu$ m 的位置,如圖 4.2(a) 所示,並以  $10^\circ$  傾角入射平行於二維光柵的對稱軸,如圖 4.2(b) 所示。

最佳化過程中的入射光極化角度皆固定為  $45^\circ$ ,並以光柵耦入 +x 方向波導之 TE 基模 (Fundamental TE Mode) 的能量比例做為效能指數 (Figure of Merit,FOM)。 $45^\circ$  極化的入射光可以參考圖 4.2(c) 的圖例,雖然圖 4.2(c) 的  $45^\circ$  極化看似平行於 y 軸,但因為光源入射方向與法線有  $10^\circ$  的夾角,圖 4.2(c) 只是垂直入射下的極化角度示意圖,所以實際入射光的  $45^\circ$  極化方向不會平行於 y 軸。

圖 4.2 (a)元件模擬平台所使用的 SOI 晶圓示意圖(b)光源沿對稱軸入射示意圖(c)垂直 入射光源之電場極化角度示意圖,實際入射光會與法線夾 10°角

## 4.2 第一階段 傾斜結構之均勻型光柵設計

此階段中,粒子群演算法設定為:粒子數為10,元件參數數量為5

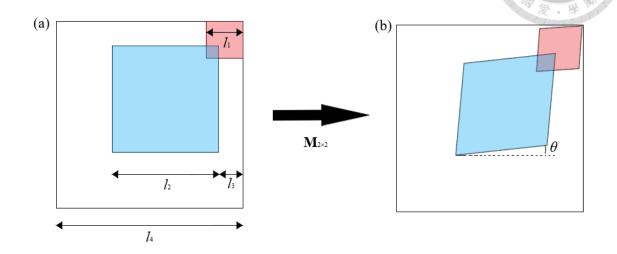

圖 4.3 元件結構與參數示意圖,以5個參數設計均勻型的二維光柵

$$\mathbf{M}_{2\times2} = \begin{bmatrix} \tan^2\theta + 1 & \tan\theta \\ \tan\theta & \tan^2\theta + 1 \end{bmatrix} \tag{4.1}$$

元件設計結構如圖 4.3 所示,圖 4.2(a)、4.2(b)為光柵單一週期中的結構,兩種顏色的四邊形分別代表了兩種不同的蝕刻深度,紅色為全蝕刻,藍色為 70 nm 淺蝕刻,兩蝕刻重疊部分則以全蝕刻為主,並且光柵週期個數固定設為 20 個。

其中, $l_1$ 為深蝕刻的長度, $l_2$ 為淺蝕刻的長度, $l_3$ 為淺蝕刻由該週期的邊緣內縮的距離, $l_4$ 為單一週期的長度, $\theta$  為光柵排列的傾角,利用  $d_1$  式的轉換矩陣  $\mathbf{M}_{2\times 2}$  便可做出傾斜排列的二維光柵。

第一階段的均勻型二維光柵耦合效率為 34.6% (-4.6 dB), 元件參數如表 4.1 所示。

表 4.1 均匀二維光栅的參數

| Parameter | Value  |

|-----------|--------|

| $l_1$     | 203 nm |

| $l_2$     | 388 nm |

| $l_3$     | 165 nm |

| $l_4$     | 658 nm |

| θ         | 3.1°   |

## 4.3 第二階段 以均匀型光栅参數來設計漸變型光柵

第二階段將會延用第一階段均勻型光柵的結果,此階段中,粒子群演算法設定為:個體數為10,參數數量為20。

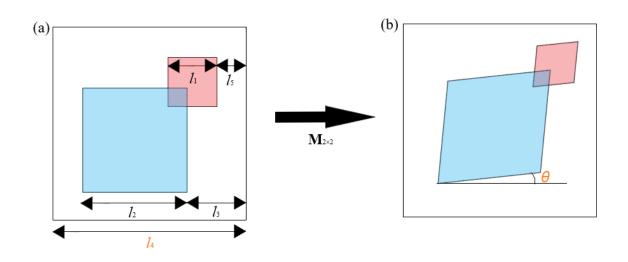

圖 4.4 元件結構與參數示意圖,漸變型二維光柵單一週期中的參數,標示成橘色的 14 與 θ 固定設為第一階段的參數結果

根據第一階段均勻型二維光柵的設計結果,第二階段固定了光柵週期  $l_4$  與光柵排列的傾角  $\theta$ 。原有參數的全、淺蝕刻大小  $l_1$  與  $l_2$  以及淺蝕刻內縮長度  $l_3$ ,會再加上全蝕刻內縮長度的參數  $l_5$ 。與第一階段相同,光柵週期數量維持 20 個,會利用 4.1 式的轉換矩陣  $\mathbf{M}_{2\times 2}$  做出傾斜排列的二維光柵。相較於第一階段的均勻型光柵耦合器,第二階段的光柵耦合器中每個週期內的  $l_1$ 、 $l_2$ 、 $l_3$ 、 $l_5$  四個參數都是不同的,本篇論文將利用這些參數的變化,做出漸變型光柵耦合器。

為了設計漸變型二維光柵,列出光柵中各參數隨週期的變化如 4.2 式。

$$l_i(n), i \in \{1, 2, 3, 5\}, 1 \le n \le 20 \tag{4.2}$$

類似於 3.3 節 Watanabe 的作法,本篇論文取了五個節點,分別為 n=1,5.75,10.5,15.25,20,利用三次樣條內插法去擬合  $l_1 \cdot l_2 \cdot l_3 \cdot l_5$ 的漸變函數 4.2 式,最後利用四個擬合函式決定第 1 到 20 的各週期中  $l_1 \cdot l_2 \cdot l_3 \cdot l_5$  四個參數的值。因此漸變型二維光柵的參數數量為 4 (週期內結構參數)乘上 5 (節點數),共 20 個參數。

利用此一方法將原本參數數量為 80 個的問題降至 20 個,來提高粒子群演算法的效能、有效率的節省計算資源並減少元件模擬費時。

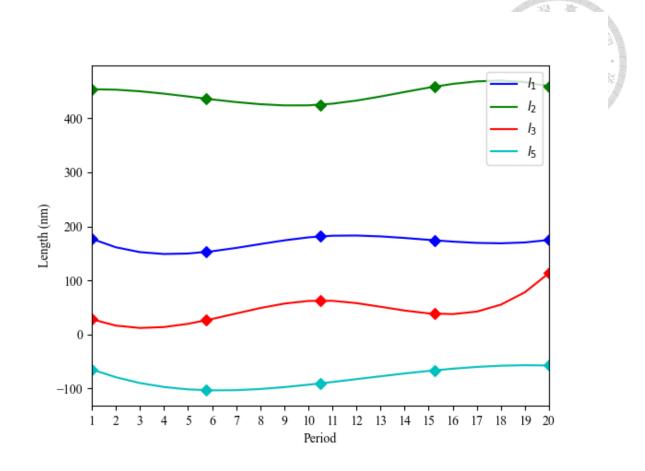

此階段完成的漸變型二維光柵耦合效率峰值為 48% (-3.19 dB),所有參數其節點的值如表 4.2 所示,依據節點做三次樣條內插後各個參數隨週期變化則如圖 4.5 所示。

表 4.2 漸變型光柵各參數節點的值

| Value of Nodes (nm) |        |         |        |        |        |  |  |  |  |  |  |

|---------------------|--------|---------|--------|--------|--------|--|--|--|--|--|--|

| n                   | 1      | 5.75    | 10.5   | 15.25  | 20     |  |  |  |  |  |  |

| $l_1$               | 177.01 | 152.68  | 181.58 | 174.26 | 175.00 |  |  |  |  |  |  |

| $l_2$               | 453.79 | 436.30  | 425.12 | 458.63 | 459.06 |  |  |  |  |  |  |

| $l_3$               | 28.31  | 26.24   | 62.88  | 38.27  | 113.60 |  |  |  |  |  |  |

| $l_5$               | -64.54 | -103.08 | -90.43 | -66.28 | -57.31 |  |  |  |  |  |  |

圖 4.5 依據表 4.2 的節點內插出漸變光柵各個週期內的參數變化

雖然表 4.2 提供節點值的大小列到小數點後 2 位,但在建構結構檔供 FDTD 模擬計算光柵的耦合效率時,會再將內插出來的所有參數四捨五入至整數,才作為漸變光柵各週期中的參數。

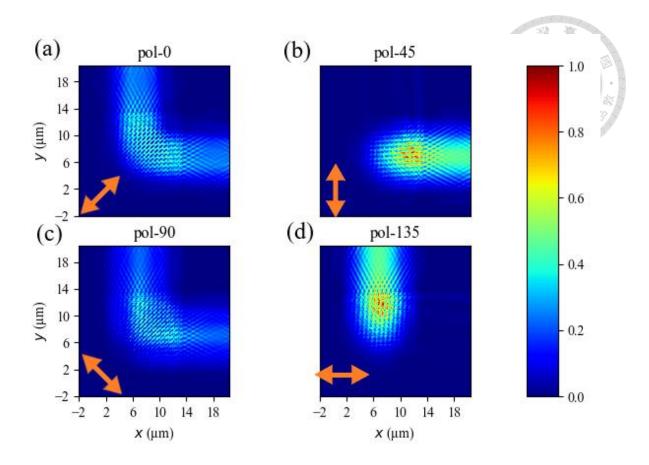

圖 4.6 為此小節完成之漸變型二維光柵,在維持 1550 nm 的入射光波長下,對於不同極化角度入射光之能量耦合方向的俯視圖。我們可以看到它除了可同時適用於不同極化的光源外,還具有分極化的功能,依據入射極化將光耦入特定方向的波導。

圖 4.6 漸變型二維光柵耦光俯視圖,四張圖入射光之極化角度分別為 (a)0°(b)45°(c)90°(d)135°

## 第五章 數據分析與探討

本章節將針對 4.3 節做出的漸變型二維光柵的耦合效率、頻寬、極化相依損耗做 元件效能的探討,再藉由模擬分析製程誤差對耦合效率造成的影響。

## 5.1 耦合效率與串擾

此小節之模擬設定皆為光源極化角度為 45°,並以耦入 x 方向波導基模之比例作 為耦合效率,極化角度與波導方向之示意圖可參考圖 4.2(c)。

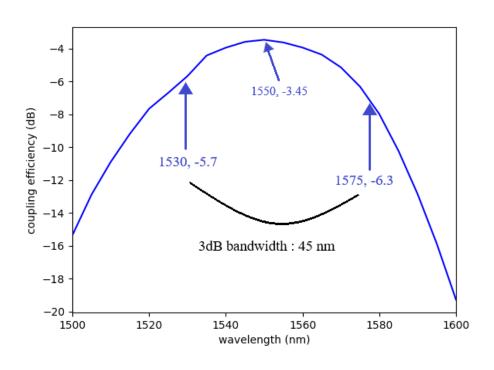

以本論文方法設計出的漸變型光栅,於 1550~nm 有最高耦合效率為 44.6% (-3.5~dB)。其 -3~dB 波段邊界約位於,1530~nm 處的耦合效率為 27.1% (-5.7~dB),1575~nm 處的耦合效率為 23.4% (-6.3~dB),故-3~dB 頻寬約為 45~nm,耦合效率對波長的變化則如圖 5.1~所示。

圖 5.1 漸變型二維光柵之耦合效率頻譜

接著考量此二維光柵的分光效果,若極化角度為 135°的入射光有少部分的訊號會耦入 x 方向的波導,該訊號對極化角度為 45°的入射光而言反而是雜訊,故定義串擾 CT (Crosstalk) 如 5.1 式。

$$CT^{x} = 10 \log_{10} \left( \frac{CE_{135^{\circ}}^{x}}{CE_{45^{\circ}}^{x}} \right)$$

(5.1)

5.1 式中, $CE_{45}^x$ 。為極化角度為  $45^\circ$  的入射光耦入 x 方向波導基模的耦合效率, $CE_{135}^x$ 。意義同前述,但極化角度為  $135^\circ$ 。分析串擾時,僅需以  $45^\circ$  的極化光入射,耦入 x 方向作為耦合效率  $CE_{45}^x$ 。,由於此二維光柵是斜對角對稱,其同時耦入 y 方向的耦合效率  $CE_{45}^y$ 。會等於  $135^\circ$  的極化光入射並耦入 x 方向波導的耦合效率  $CE_{135}^x$ 。,如此一來我們便可以單一極化光源分析該元件在特定波長下會產生的串擾。

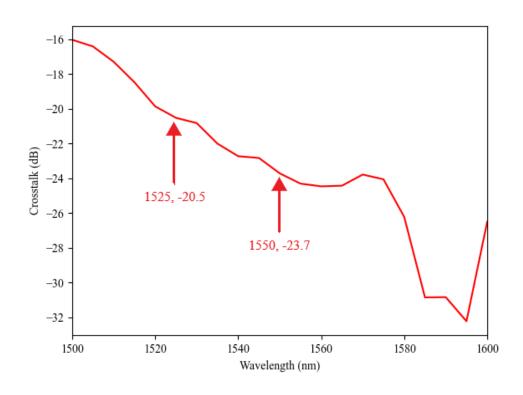

在  $1500 \text{ nm} \sim 1600 \text{ nm}$  的波段下,本元件的串擾皆低於 -16 dB。而在波長大於 1525 nm 的波段,串擾則皆低於 -20 dB,如圖 5.2 所示。

圖 5.2 串擾隨波長之變化

### 5.2 極化相依損耗

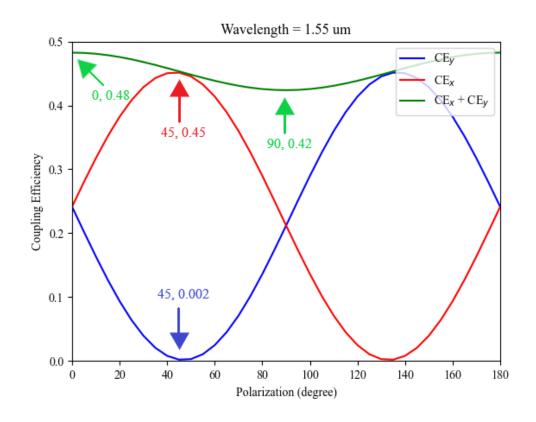

由於本二維漸變型光柵是斜對角對稱,極化角度為 45°與 135°的入射光源之間,理論上不會有極化相依損耗。固定以 1550 nm 作為入射光源,僅調整入射光極化角度 旋轉下,耦合效率的變化如圖 5.3 所示,可以看到圖形成左右對稱,因此極化角度為 45°與 135°的入射光之極化相依損耗確實為零,並且最大極化相依損耗應會發生於 極化角度為 0°與 90°的入射光源間。

圖 5.3 1550 nm 的入射光,耦合效率之於極化角度的變化

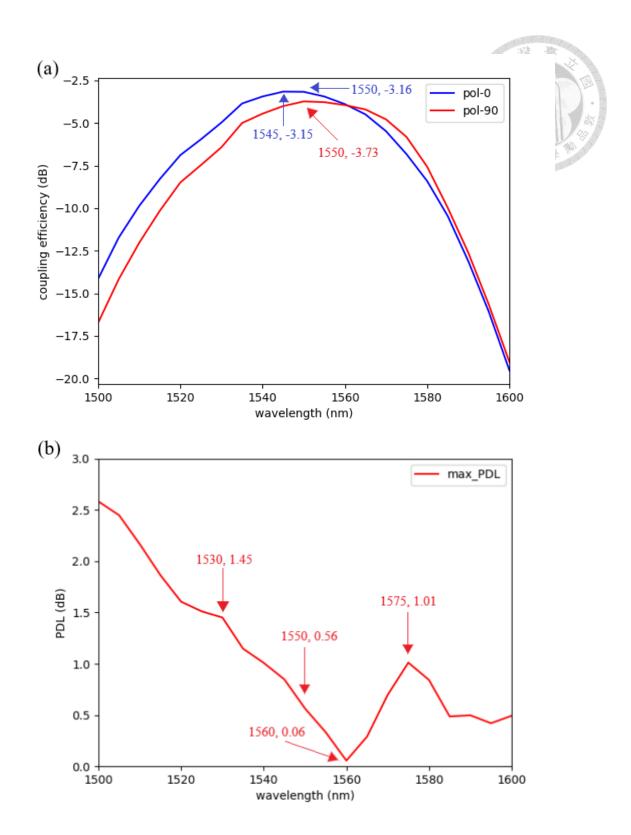

故此小節將針對極化角度為 0° (pol-0) 與 90° (pol-90) 兩種入射光分析本二維漸變型光柵耦合器的最大極化相依損耗頻譜,如圖 5.4。

圖 5.4 極化相依損耗頻譜(a)產生最大極化相依損耗的兩種極化之耦合光譜(b)由兩種極化之耦合效率差異取絕對值所算出的最大極化相依損耗光譜

圖 5.4(a)的數據顯示,pol-0 的耦合效率的峰值為 -3.15 dB 位於 1545 nm 處, 1550 nm 處的耦合效率則是 -3.16dB,pol-90 的峰值為 -3.85 dB,位於 1550 nm 處。 由於光譜數據是以 5 nm 當成波長的間隔,圖 5.4(a) 的零相依損耗之兩線交點無法於圖 5.4(b) 畫出來,根據 5.4(a) 曲線趨勢的判斷,零相依損耗應位於波長 1565 nm 至 1570 nm 之間。而 1530 nm 至 1575 nm 的 -3 dB 波段,最大極化相依損耗 (PDL) 均小於等於 1.45 dB。

綜觀非垂直入射型光柵耦合器的極化相依損耗問題,主流的作法還是類似 3.2 節的文獻,利用非對稱性的光柵圖形來微調兩種極化的耦合頻譜。然而這種作法與漸變型光柵耦合器難以相容。依我現有的最佳化演算法與流程,很難在調整漸變型光柵的參數變化來提高耦合效率的同時,又顧及不同極化耦合光譜的一致性。我目前也沒有看過可以同時做到低極化相依又利用漸變型光柵提高耦合效率的文獻。

3.2 節提到的文獻作者們,把光柵圖樣的微調自由度用於降低極化相依損耗,這使得他們只能使用金屬反射鏡式的設計進一步改善耦合效率。圖 3.3 為該團隊未替光柵加上金屬反射鏡時的耦合光譜,可以看到其耦合效率皆低於 31.6% (-5 dB)。相較之下,本篇論文所設計的二維漸變型光柵耦合器,未添加金屬反射鏡時 pol-0 的耦合效率峰值為 48% (-3.16 dB)。

### 5.3 光纖傾角容忍度分析

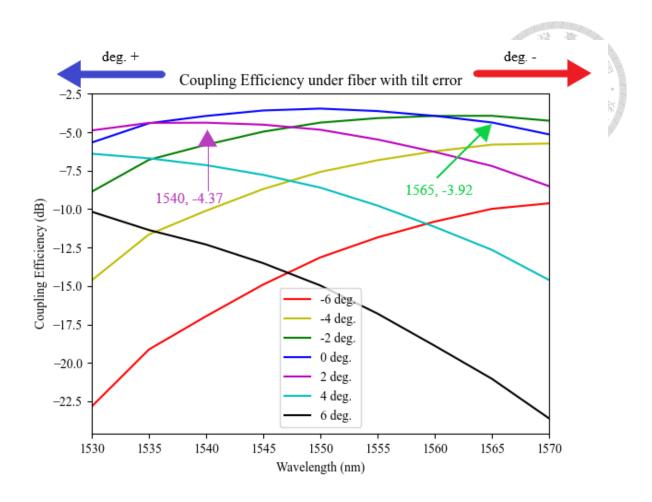

本論文設計流程中入射光源傾角皆是固定與晶片表面法線夾 10° 角,並將入射光源中心,與二維光柵的中心對齊。此小節將在維持光場中心對準晶片中心的前提下,分析入射角度變化在 1530 nm 至 1570 nm 波段,對其耦合效率的影響。光纖傾角誤差的設定如圖 5.5 所示,入射光極化角度固定為 45°,光纖傾角改變對耦合頻譜的影響如圖 5.6 所示。

圖 5.5 光纖傾角誤差的設定方式

圖 5.6 不同光纖傾角下耦合效率的變化

圖 5.6 中標示的兩色箭頭為,不同入射角下耦合效率頻譜之峰值位置。我們可發現若光纖入射方向與晶片表面法線的夾角變小,頻譜會紅移,反之則是藍移。根據 2.3 節也有提過的布拉格條件 5.1 式。若在其他條件皆不變的情況下,僅光纖入射角度  $\theta$  變小,導致 5.1 式左邊變小,由於  $\beta_m = \frac{2\pi n_{\rm eff}}{\lambda_0}$ ,為了維持布拉格條件的等式,需要  $n_{\rm eff}$  變小及  $\lambda_0$  變大,因此造成了頻譜的紅移,因而圖 5.6 的頻譜隨入射角度產生紅/藍移的現象是可預期的。

$$k_0 \sin \theta + mG = \beta_m \tag{5.1}$$

#### 5.4 淺蝕刻位置偏移容忍度分析

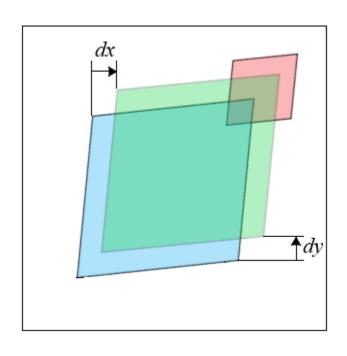

此次元件設計利用到兩階段蝕刻來提升光柵的耦合效率,鑒於兩種深度的蝕刻在製程上需使用不同的光罩,容易在曝光及蝕刻的位置上產生偏移。而全蝕刻的圖樣與光柵邊緣以及波導的製程可以使用同一道光柵,故不分析全蝕刻偏移誤差之影響。本小節僅分析,對 1550 nm 之入射光,淺蝕刻位置在 xy 水平面上偏移的製程誤差,對耦合效率之影響。圖 5.7 描繪的是二維漸變型光柵的單一個週期結構,紅色為全蝕刻,藍色為淺蝕刻,綠色為製程誤差導致的淺蝕刻偏移,將以紅色與綠色的結構作為含誤差的光柵設計來分析本元件的製程容忍度。分析時的光源設定如下:極化角度固定為 45°, 波長為 1550 nm, 耦合效率隨淺蝕刻製程誤差的變化如圖 5.8 所示。

圖 5.7 淺蝕刻位置偏移示意圖

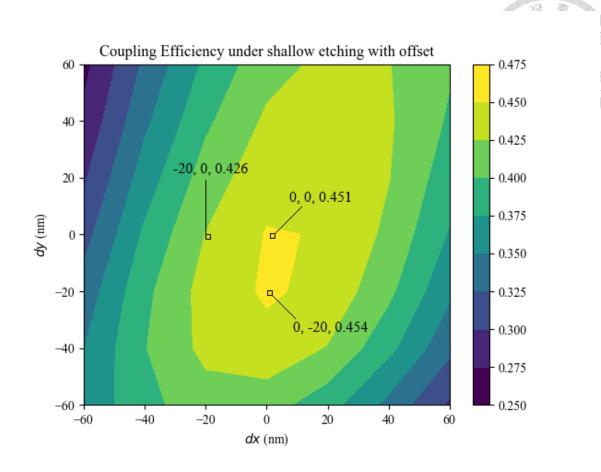

圖 5.8 耦合效率隨淺蝕刻偏移之變化

由圖 5.8 可發現,原始設計無製程誤差的淺蝕刻位置,對於  $45^\circ$  極化的入射光而言其耦合效率反而較淺蝕刻位置誤差  $dy=-20\,\mathrm{nm}$  還來的低。然而因為本二維光栅結構為斜對角對稱, $45^\circ$  極化最佳耦合效率的淺蝕刻偏移位置  $(0\,\mathrm{nm},-20\,\mathrm{nm})$ ,對於  $135^\circ$  極化而言其偏移位置會等效於圖 5.8 中  $(-20\,\mathrm{nm},0\,\mathrm{nm})$  的點。若為了提高  $45^\circ$  極化僅 0.3% 的耦合效率而將淺蝕刻向 y 方向偏移了  $-20\,\mathrm{nm}$ ,這反而會使得  $135^\circ$  極化的耦合效率下降約 2.5%。由圖 5.8 足以證明,當前設計已達到元件效能的區域最 佳解。

同樣根據圖 5.8,若 dx 維持在  $\pm 20$  nm 之間、dy 維持在 -20 nm  $\sim +60$  nm 之間,則對  $45^{\circ}$  極化的入射光而言,其耦合效率均可維持在 42.5% (-3.72 dB) 以上。但

考量到與之對稱的  $135^\circ$  極化入射光,本二維光柵耦合器對於淺蝕刻位置偏移的容忍 度 dx 與 dy 應皆須介於  $\pm 20$  nm 之間,才能較好的維持任一極化之耦合效率。

## 第六章 結論與展望

本論文融合了兩階段蝕刻與漸變形光柵,兩種較常見且製程較容易的光柵耦合器的設計模式。再套用設定了邊界條件處理方式與調整迭代式常數的速度調整吸收型—粒子群最佳化演算法,先用於設計均勻型的光柵耦合器,再沿用部分參數來設計漸變型光柵耦合器,此種設計方法可以節省漸變型光柵設計過程的運算耗時。與其他二維光柵設計相關文獻的比較如表 6.1 所示。

| Ref.      | Year | Wavelength | Fiber angle | CE          | Metal Mirror or | Platform        | Note     |

|-----------|------|------------|-------------|-------------|-----------------|-----------------|----------|

|           |      |            |             | (Sim/Exp)   | Vertical DBR    |                 |          |

|           |      |            |             | (dB)        |                 |                 |          |

| 41        | 2009 | 1550       | 10°         | NA / -5.6   | w/o             | SOI             | Focusing |

| 42        | 2014 | 1480       | 10°         | NA / -2.0   | w/o             | Double SOI      | Focusing |

| 43        | 2016 | 1550       | 15°         | -3.2 / -3.7 | w/o             | SOI             | Uniform  |

| 44        | 2016 | 1310       | 6°          | -3.2 / -3.3 | w/o             | SOI             | Uniform  |

| 45        | 2017 | 1550       | 10°         | -1.7 / NA   | w/              | SOI             | Apodized |

| 46        | 2017 | 1550       | 12°         | -1.4 / -1.8 | w/              | SOI +           | Uniform  |

|           |      |            |             |             |                 | BCB +           |          |

|           |      |            |             |             |                 | Glass Substrate |          |

| 25        | 2019 | 1550       | 0°          | -2.4 /-2.6  | w/o             | SOI             | Apodized |

| 47        | 2019 | 1550       | 12°         | -3.4 / -4.3 | w/o             | SOI             | Uniform  |

| 35        | 2020 | 1550       | 10°         | -1.7 / -2.3 | w/              | SOI             | Uniform  |

| This work | 2022 | 1550       | 10°         | -3.2 / NA   | w/o             | SOI             | Apodized |

表 6.1 本論文與其他文獻的比較

根據表 6.1 之比較,可發現若替二維光柵耦合器加入金屬反射鏡,其耦合效率均優於無金屬反射鏡的二維光柵耦合器。與其他無使用金屬反射鏡的二維光柵耦合器文獻做比較,雖然本篇的元件耦合效率不及 Watanabe 的元件設計<sup>[25]</sup>,但該篇製程最小線寬僅 40 nm,本篇則為 150 nm。

再比較於適用波段及耦合效率都與本篇相同,但製程相對簡單的文獻 43,該篇 設計模式使用了蝕刻深度作為元件設計參數,本篇論文則是固定蝕刻深度。且本篇 論文將光柵耦合器設計成繞射強度漸變型,使得本光柵耦合器具有較好的互益性 (Reciprocity),在固定光纖擺放位置的條件下,將光柵耦合器同時應用於光纖對晶片 與晶片對光纖之耦光,繞射強度漸變型的光柵耦合器相較於均勻型的光柵耦合器, 能更好的維持耦合效率[48]。

#### 6.2 展望

隨著量子科技的興起,極化態做為光子最容易調變及量測的量子態,恰好二維 光柵耦合器同時具有耦光與分極化功能,相信未來會有更多人研究如何進一步提高 其耦合效率。本篇論文提出一種有效的設計模式,可以在已知製程限制下快速的設 計出高耦合效率的二維光柵耦合器。

然而本篇所設計的二維光柵耦合器並沒有為了降低極化相依損耗做任何設計,結果使得極化相依損耗在 1550 nm 處為 0.56 dB,仍無法完美的適用於任何極化入射的光源。降低極化相依損耗的普遍做法是微調非對稱的蝕刻圖樣,藉由犧牲些許的耦合效率換取不同極化頻譜的重合,如同 3.2 節提及的雙橢圓型光柵設計,然而這種作法與漸變形光柵的設計方法可說是完全互斥的。

若要再結合不同的設計模式來做更複雜的設計,微調非對稱蝕刻圖樣同時利用 兩階段蝕刻提高光柵繞射方向性的文獻還沒有出現,利用這兩者的結合或許便能做 出兼顧極化相依損耗與耦合效率的二維光柵耦合器,然而非對稱圖形的選擇仍可能 會受限於製程最小線寬,因此我目前所見藉由非對稱圖樣降低極化相依損耗的文獻, 全部都是以圓形蝕刻作為基礎,頂多像 3.2 節般設計成雙橢圓的形式。

未來小線寬製程的普及與價格下降,也會讓二維光柵耦合器的結構設計有更多發揮的空間,鑒於本篇的最小線寬為 150 nm、光柵週期為 658 nm,個人認為改善光柵耦合器耦合效率的根本方法還是縮小全蝕刻的製程線寬,並且利用全蝕刻吃出不同填空比的次波長光柵來類比兩階段蝕刻式光柵的效果,除了可以像 Watanabe 在單一週期中做出不同功能的結構外,我們也不必擔憂不同道光柵間偏移造成的耦合效率下降。

# 参考文獻

- [1] Richard Soref, "Silicon-Based Optoelectronics," *Proceedings of the IEEE* vol. 81, pp. 1687–1706, 1993.

- [2] Richard Soref, "The Past, Present, and Future of Silicon Photonics," *IEEE Journal of Selected Topics in Quantum Electronics* vol. 12, pp. 1678–1687, 2006.

- [3] Michal Lipson, "Guiding, Modulating, and Emitting Light on Silicon—Challenges and Opportunities," *Journal of Lightwave Technology* vol. 23, pp.4222–4238, 2005.

- [4] David J. Thomson, Frederic Y. Gardes, Jean-Marc Fedeli, Sanja Zlatanovic, Youfang Hu, Bill Ping Piu Kuo, Evgeny Myslivets, Nikola Alic, Stojan Radic, Goran Z. Mashanovich, and Graham T. Reed, "50-Gb/s Silicon Optical Modulator," *IEEE Photonics Technology Letters* vol. 24, pp. 234–236, 2011.

- [5] G. T. Reed, G. Mashanovich, F. Y. Gardes, and D. J. Thomson, "Silicon optical modulators," *Nature Photon* vol. 4, pp. 518–526, 2010.

- [6] I. Kiyat, A. Aydinli, and N. Dagli, "A compact silicon-on-insulator polarization splitter," *IEEE Photonics Technology Letters* vol. 17, pp. 100–102, 2004.

- [7] T. K. Liang and H. K. Tsang, "Integrated polarization beam splitter in high index contrast silicon-on-insulator waveguides," *IEEE Photonics Technology Letters* vol. 17, pp. 393–395, 2005.

- [8] Zhen Sheng, Zhiqi Wang, Chao Qiu, Le Li, Albert Pang, Aimin Wu, Xi Wang, Shichang Zou, and Fuwan Gan, "A Compact and Low-Loss MMI Coupler Fabricated With CMOS Technology," *IEEE Photonics Journal* vol. 4, pp. 2272–2277, 2012.

- [9] Takui Uematsu, Yuhei Ishizaka, Yuki Kawaguchi, Kunimasa Saitoh, and Masanori Koshiba, "Design of a Compact Two-Mode Multi/Demultiplexer Consisting of Multimode Interference Waveguides and a Wavelength-Insensitive Phase Shifter for Mode-Division Multiplexing Transmission," *Journal of Lightwave Technology* vol. 30, pp. 2421–2426, 2012.

- [10] Dirk Taillaert, Wim Bogaerts, Peter Bienstman, Thomas F. Krauss, Peter Van Daele, Ingrid Moerman, Steven Verstuyft, Kurt De Mesel, and Roel Baets, "An out-of-plane grating coupler for efficient butt-coupling between compact planar waveguides and

- single-mode fibers," *IEEE Journal of Quantum Electronics* vol. 38, pp. 949–955, 2002.

- [11] Martin Papes, Pavel Cheben, Daniel Benedikovic, Jens H. Schmid, James Pond, Robert Halir, Alejandro Ortega-Moñux, Gonzalo Wangüemert-Pérez, Winnie N. Ye, Dan-Xia Xu, Siegfried Janz, Milan Dado, and Vladimír Vašinek, "Fiber-chip edge coupler with large mode size for silicon photonic wire waveguides," *Optics Express* vol. 24, pp. 5026–5038, 2016.

- [12] Wim Bogaerts, Pieter Dumon, Dries Van Thourhout, Dirk Taillaert, Patrick Jaenen, Johan Wouters, Stephan Beckx, Vincent Wiaux, and Roel G. Baets, "Compact Wavelength-Selective Functions in Silicon-on-Insulator Photonic Wires," *IEEE Journal of Selected Topics in Quantum Electronics* vol. 12, pp. 1384–1401, 2006.

- [13] Wim Bogaerts, Shankar Kumar Selvaraja, Pieter Dumon, Joost Brouckaert, Katrien De Vos, Dries Van Thourhout, and Roel Baets, "Silicon-on-Insulator Spectral Filters Fabricated With CMOS Technology," *IEEE Journal of Selected Topics in Quantum Electronics* vol. 16, pp. 33–44, 2010.

- [14] Zhuo Cheng, Jun Wang, Zeyuan Yang, Haiying Yin, Wei Wang, Yongqing Huang, and Xiaomin Ren, "Broadband and High Extinction Ratio Mode Converter Using the Tapered Hybrid Plasmonic Waveguide," *IEEE Photonics Journal* vol. 11 no. 3, 2019.

- [15] D. -X. Xu et al., "Silicon Photonic Integration Platform—Have We Found the Sweet Spot?," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 20, pp. 189–205, 2014.

- [16] Corning SMF-28 official information sheet

- [17] Minhao Pu, Liu Liu, Haiyan Ou, Kresten Yvind, and Jørn M. Hvam, "Ultra-low-loss inverted taper coupler for silicon-on-insulator ridge waveguide," *Optics Communications* vol. 283, pp. 3678–3682, 2010.

- [18] An He, Xuhan Guo, Kangnian Wang, Yong Zhang, and Yikai Su, "Low Loss, Large Bandwidth Fiber-Chip Edge Couplers Based on Silicon-on-Insulator Platform", *Journal of Lightwave Technology* vol. 38, pp. 4780–4786, 2020.

- [19] Xin Mu, Sailong Wu, Lirong Cheng, and H.Y. Fu, "Edge Couplers in Silicon Photonic Integrated Circuits: A Review," Applied Sciences vol. 10 no.4, 2020.

- [20] Tatsuhiko Watanabe, Masafumi Ayata, Ueli Koch, Yuriy Fedoryshyn, and Juerg Leuthold, "Perpendicular Grating Coupler Based on a Blazed Antiback-Reflection Structure," Journal of Lightwave Technology vol. 35, pp. 4663–4669, 2017.

- [21] Daniel Benedikovic, Carlos Alonso-Ramos, Diego Pérez-Galacho, Sylvain Guerber, Vladyslav Vakarin, Guillaume Marcaud, Xavier Le Roux, Eric Cassan, Delphine Marris-Morini, Pavel Cheben, Frédéric Boeuf, Charles Baudot, and Laurent Vivien, "L-shaped fiber-chip grating couplers with high directionality and low reflectivity fabricated with deep-UV lithography," *Optics Letters* vol. 42, pp. 3439–3442, 2017.

- [22] Günther Roelkens, Dries Van Thourhout, and Roel Baets, "High efficiency Silicon-on-Insulator grating coupler based on a poly-Silicon overlay," *Optics Express* vol. 14, pp. 11622–11630, 2006.

- [23] Xia Chen, Chao Li, Christy K. Y. Fung, Stanley M. G. Lo, and Hon K. Tsang, "Apodized Waveguide Grating Couplers for Efficient Coupling to Optical Fibers," IEEE *Photonics Technology Letters* vol. 22, pp. 1156–1158, 2010.

- [24] Dirk Taillaert, Harold Chong, Peter I. Borel, Lars H. Frandsen, Richard M. De La Rue, and Roel Baets, "A Compact Two-Dimensional Grating Coupler Used as a Polarization Splitter," *IEEE Photonics Technology Letters* vol. 15, pp.1249–1251, 2003.

- [25] T. Watanabe, Y. Fedoryshyn, and J. Leuthold, "2-D Grating Couplers for Vertical Fiber Coupling in Two Polarizations," *IEEE Photonics Journal* vol. 11, 2019.

- [26] Kane S. Yee, "Numerical Solution of Initial Boundary Value Problems Involving Maxwell's Equations in Isotropic Media," *IEEE Transactions on Antennas and Propagation* vol. **14**, pp. 302–307, 1966.

- [27] Shih-hui Chang, "Lecture 1. FDTD Finite Difference method and Yee Grid", National Cheng Kung University 108-1 Class: Solving Maxwell's Equations by Finite-Difference Time-Domain Method, 2019.

- [28] James Kennedy and Russell C. Eberhart. "Particle Swarm Optimization," *Proceedings of the IEEE International Conference on Neural Networks* vol. 4, pp. 1942–1948, 1995.

- [29] Sabine Helwig, Frank Neumann, and Rolf Wanka, "Particle Swarm Optimization with Velocity Adaptation," *IEEE Swarm Intelligence Symposium*, 2008.

- [30] Cheng, Lirong, Simei Mao, Zhi Li, Yaqi Han, and H. Y. Fu., "Grating Couplers on Silicon Photonics: Design Principles, Emerging Trends and Practical Issues," *Micromachines* vol. 11, no. 7, 2020.

- [31] Intel Corporation, "THE INTEL MEMORY DESIGN HANDBOOK," p.6-57, 1973.

- [32] Andrew Michaels and Eli Yablonovitch, "Inverse design of near unity efficiency perfectly vertical grating couplers," *Optics Express* vol. 26, pp. 4766–4779, 2018.

- [33] Huijuan Zhang, Chao Li, Xiaoguang Tu, Haifeng Zhou, Xianshu Luo, Mingbin Yu, and G. Q. Lo, "High efficiency silicon nitride grating coupler with DBR", *Optical Fiber Communication (OFC) Conference*, 2014.

- [34] Wissem Sfar Zaoui, Andreas Kunze, Wolfgang Vogel, and Manfred Berroth, "CMOS-Compatible Polarization Splitting Grating Couplers With a Backside Metal Mirror," *IEEE Photonics Technology Letters* vol. 25, pp. 1395–1397, 2013.

- [35] B. Chen, X. Zhang, J. Hu, Y. Zhu, X. Cai, P. Chen, and L. Liu, "Two-dimensional grating coupler on silicon with a high coupling efficiency and a low polarization-dependent loss," *Optics Express* vol. 28, pp. 4001–4009, 2020.

- [36] Yohei Sobu, Seok-Hwan Jeong, and Yu Tanaka, "Si-wire two-dimensional grating coupler with polarization-dependent loss of lower than 0.3 dB over a 60-nm-wide spectral range," *The Japan Society of Applied Physics* vol. 57, 2018.

- [37] Christopher R. Doerr, Peter J. Winzer, Young-Kai Chen, S. Chandrasekhar, Mahmoud S. Rasras, Long Chen, Tsung-Yang Liow, Kah-Wee Ang, and Guo-Qiang Lo, "Monolithic Polarization and Phase Diversity Coherent Receiver in Silicon," *Journal of Lightwave Technology* vol. 28, pp. 520–525, 2010.

- [38] Xia Chen, Chao Li, and Hon Ki Tsang, "Two dimensional silicon waveguide chirped grating couplers for vertical optical fibers," *Optics Communications* vol. 283, pp. 2146–2149, 2010.

- [39] Mauricio Zambrano-Bigiarini, Maurice Clerc, and Rodrigo Rojas, "Standard Particle Swarm Optimisation 2011 at CEC-2013: A baseline for future PSO improvements," *IEEE Congress on Evolutionary Computation*, 2013.

- [40] Sabine Helwig and Rolf Wanka, "Particle Swarm Optimization in High-Dimensional Bounded Search Spaces," *IEEE Swarm Intelligence Symposium*, 2007.

- [41] Frederik Van Laere, Wim Bogaerts, Pieter Dumon, Günther Roelkens, Dries Van Thourhout, and Roel Baets, "Focusing Polarization Diversity Grating Couplers in Silicon-on-Insulator," *Journal of Lightwave Technology* vol. 27, pp. 612–618, 2009.

- [42] L. Verslegers, A. Mekis, T. Pinguet, Y. Chi, G. Masini, P. Sun, A. Ayazi, K. Y. Hon, S. Sahni, S. Gloeckner, C. Baudot, F. Boeuf, and P. De Dobbelaere, "Design of Low-Loss Polarization Splitting Grating Couplers," *Advanced Photonics for Communications*, Advanced Photonics for Communications, 2014.

- [43] C. Lacava, L. Carrol, A. Bozzola, R. Marchetti, P. Minzioni, I. Cristiani, M. Fournier, S. Bernabe, D. Gerace, and L. C. Andreani "Design and characterization of low-loss 2D grating couplers for silicon photonics integrated circuits," *Silicon Photonics XI* vol. 9752, 2016.

- [44] Weike Wu, Tianhua Lin, Tao Chu, and Hua Zhang, "CMOS-Compatible High Efficiency Polarization Splitting Grating Coupler near 1310nm", *Asia Communications and Photonics Conference*, 2016.

- [45] María Félix Rosa, Pablo de la Torre Castro, Niklas Hoppe, Lotte Rathgeber, Wolfgang Vogel, and Manfred Berroth, "Novel design of two-dimensional grating couplers with backside metal mirror in 250 nm silicon-on-insulator," *International Conference on Numerical Simulation of Optoelectronic Devices*, 2017.

- [46] Yannong Luo, Zhichao Nong, Shengqian Gao, Huamao Huang, Yuntao Zhu, Liu Liu, Lidan Zhou, Jian Xu, Lin Liu, Siyuan Yu, and Xinlun Cai, "Low-loss two-dimensional silicon photonic grating coupler with a backside metal mirror," *Optics Letter* vol. 43, pp. 474–477, 2018.

- [47] Yanyun Xue, Hao Chen, Yujin Bao, Jianji Dong, and Xinliang Zhang, "Two-dimensional silicon photonic grating coupler with low polarization-dependent loss and high tolerance," *Optics Express* vol. 27, 22268–22274, 2019.

- [48] V. Kivijärvi, M. Erdmanis, and I. Tittonen, "Simulation of Light Coupling Reciprocity for a Photonic Grating," COMSOL, 2013.