# 國立臺灣大學工學院應用力學研究所

## 博士論文

Institute of Applied Mechanics

College of Engineering

National Taiwan University

Doctoral Dissertation

微波選擇性摻雜劑激活機制的發現及其在實現重 n 型摻雜 矽接面穩定性的作用

Discovery of a novel microwave-selective dopant activation mechanism and its role in junction stability for highly n-doped silicon

### 蔡俊雄

Chun-Hsiung Tsai

指導教授:李世光 博士, 許聿翔 博士

Advisor: Chih-Kung Lee, Ph.D., Yu-Hsiang Hsu, Ph.D.

中華民國 111 年9月

September, 2022

### 誌謝

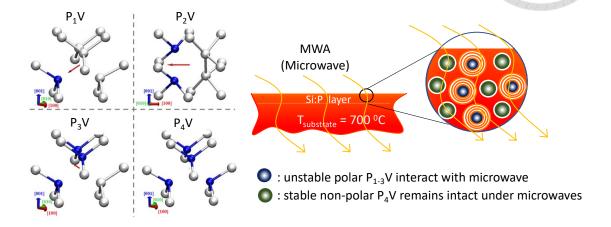

首先感謝李世光教授和許聿翔教授,他們給予我自由和寬廣的博士研究工作 空間,並即時審閱研究進度並提出建議,確保了研究成果的質量。特別是,他們對 提交給期刊的手稿進行非常詳細和嚴格的審查。另外我也特別感謝李教授太太 Julie Lee 神速又詳細到每一細節的論文審閱功力令人配服, 如果沒有老師們設定 的高標準,就不可能完成具體且嚴謹的研究工作。老師們親切博學嚴謹的治學態度 著實令我打從內心尊敬, 很慶幸自己能有這樣的際遇跟隨一流的學者耳濡目染。儘 管矽半導體產業已經是一項成熟的技術,但關於選擇性摻雜劑激活機制的發現和 它解決長久以來重 n 型摻雜矽接面熱穩定性問題所展現的潛能仍是令人鼓舞的劃 時代發現。它為退火技術開闢了新思路,並激勵未來的研究人員思考如何有效地應 用熱處理和非熱的能量耦合方式來克服材料退火面臨的熱預算相容性問題。這漫 長的六年的研究生過程可以說是轟轟烈烈,期間還歷經不可思義的跨國公司與學 校合作。我與台積電林佑明博士四年多的一百多次白板討論,我從完全無法解釋到 逐漸勾勒出實現低溫回火實驗結果背後的涵義。我通過與應用材料公司科學家 Hans-Joachim Ludwig Gossmann 的討論,他建議我聯繫在西班牙專門研究密度泛 函理論 (DFT) 計算的 Lourdes Pelaz 教授。 Lodures 教授的"DFT" 計算證實了 不穩定的低階磷空位簇 P<sub>n</sub>V(n=1-3) 恰巧都具非消失偶極矩,而穩定的 P<sub>4</sub>V 是非 極性的且沒有偶極子。該計算結果強化了我提出的選擇性摻雜劑退火模型,另外通 過與中央大學溫偉源教授使用 XRD 和正電子湮沒技術,本研究能夠表徵退火前後 Si:P應變遷移並驗證空位分佈變化以支持我提出的選擇性摻雜激活模型的合理性 也是跨校合作的團隊精神的表現.康奈爾大學教授 James C Hwang 根據微波腔中感 受器裝置的位置及其相對於諧振腔的臨界尺寸對微波場的分佈進行了建模得出在 三重平行基座之間建立駐波的能力是將微波能量有效地耦合到矽晶格中的非活性 摻雜劑結構的關鍵。 我對這些西方學者深厚學問與合作時展現開闊的心胸充滿配 服與感激、沒有他們在理論計算上的支援這牽連龐大的複雜工作不可能完成。最後 謝謝家人特別是養育我的父母親以及太太其禛在背後的體諒與包容讓我毫無懸念 得以完成具體且重要的半導體研究成果。

### 中文摘要

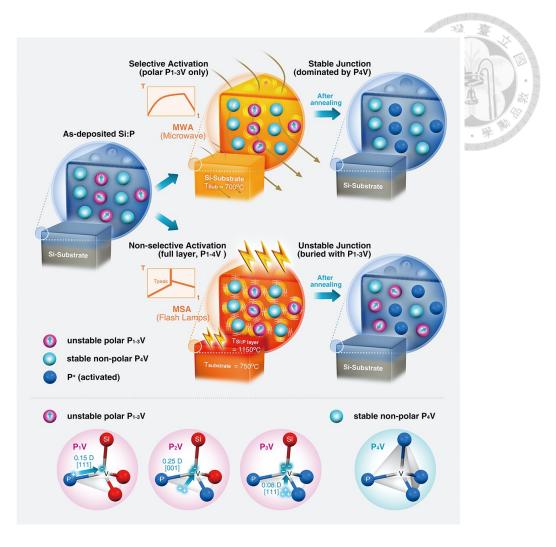

在現代 CMOS 3D 晶體管架構、FinFET 和環柵 (GAA) 納米片晶體管中,源 漏形成需要原位重摻雜外延矽層來滿足器件性能要求。然而,在過去 30 年中,眾 所周知,施者(donor)在高摻雜半導體中往往會失活。當矽中的施者濃度高於 2 x 10<sup>20</sup> at/cm<sup>3</sup> 時,將漸漸開始觀察到施者的失活並導致電導率下降。相關研究工作表 明施者喜好以圍繞空缺(Vacancy)組態出現, 而根據摻雜濃度的高低施者失活機制 是由於低階 PV 通過遷移和動態聚集 (DnV,n=1-4) 轉變為更高階 P2V、P3V. 甚至 在濃度高到 1 x 10<sup>21</sup> at/cm³ 可進一步轉化為 P<sub>4</sub>V 等施者空位簇 (donor-vacancy cluster)。這是由於其負形成能 P<sub>3</sub>V 和 P<sub>4</sub>V 在熱力學上是較有利的配置。因此,Si 中的施者濃度越高,其表現出的熱穩定性越低,這造成可用的自由載流子濃度因此 受到限制並且不能隨著供體化學濃度的增加而增加。現代 FinFET 和環柵(GAA)納 米片晶體管結構的源漏極中使用的典型磷濃度通常高於 2 x 10<sup>21</sup> at/cm3,因此源漏 結存在嚴重的熱穩定性問題。然而,據目前所知,儘管施者失活的機制透過過去四 十年各方研究已得到完整的理解, 但到目前為止, 施者失活仍被視為熱回火的本徵 問題因此還沒有關於這種現像是否可以得到緩解和解決的討論。雖然通過最先進 的閃光或激光退火進行額外的外延後摻雜劑活化是目前增加活化摻雜劑的唯一方 法,但其回火後活化摻雜劑的熱穩定性問題仍然存在。本研究的目的是進一步揭示 供體失活的機制並提供有關施者空位簇 (D<sub>n</sub>V) 的更有用的電子特性,以便能鑒往 知來可以開發一種替代退火解決方案,該解決方案不僅可以激活摻雜劑,還可以解 決熱穩定性問題。通過從頭計算(ab initio calculation),我發現了施者空位簇更多有 用的電子特性,如偶極矩、晶格振動頻率和形成能。本研究逐步應用這些特性之間 的關係來開發實用的退火解決方案,以克服長期存在的供體失活問題並將早期關 於供體失活機制的研究,即磷空位簇(P<sub>n</sub>V,n=1-4)動態聚集形成模型擴展到 P<sub>n</sub>V 偶極矩的從頭計算。結合已知的 PnV 形成能,理論計算證明熱不穩定的低階 PnV (n=1-3)總具有非零偶極矩而熱穩定的高階 P<sub>n</sub>V 則不具有淨偶極矩. 這個特別偶 極矩分佈可被用於透過與震盪電場選擇性的交互作用實現選擇性摻雜劑激活。通 過穩定和不穩定摻雜劑-空位簇之間的偶極矩區別,本研究嘗試開發一種能量選擇

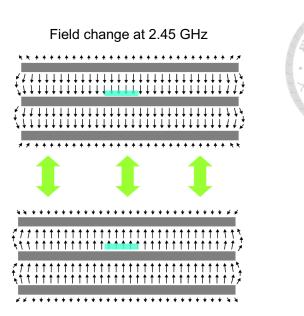

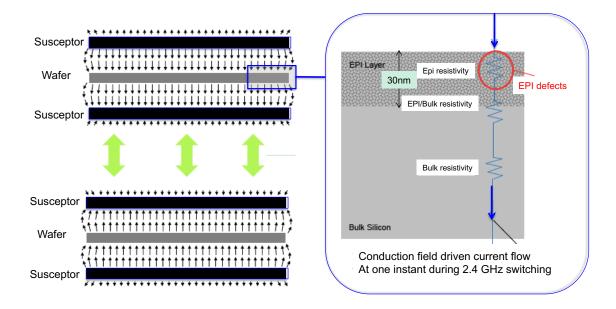

性相互作用退火方法來實現高 n 掺雜 Si 的熱穩定結(Junction)。選擇性摻雜劑激活工藝方案的實施有望通過消除不穩定的 P<sub>n</sub>V 來實現回火後只存在熱穩定的 P<sub>4</sub>V 從而實現穩定結。但對於擇性摻雜劑激活所需震盪電場邊界條件並非簡單可得,本研究將通過引入各種感受器(susceptor)配置來探索各種微波腔設置,以探索在低於700 攝氏度的最佳感受器配置下選擇性摻雜劑激活是否可被實現,在最佳感受器配置找到之後再根據微波腔中感受器設置的位置及其相對於諧振腔的臨界尺寸對微波場的分佈進行了建模。 得出的結論是,在三重平行感受器基座之間建立駐波的能力是將微波能量有效耦合到矽晶格中的非活性摻雜劑結構的關鍵。最後,通過涉及霍爾測量、二次離子質譜 (SIMS) 和 XRD 以及正電子湮沒技術的薄膜表徵技術,以實驗與分析方法驗證選擇性摻雜激活的機制。

關鍵字:施者失活、掺雜劑空位簇、微波回火、熱穩定結、掺雜劑激活、施者、磷空位簇、外延矽、退火

### **ABSTRACT**

In modern CMOS 3D transistor architectures, FinFETs, and gate-all-around (GAA) nanosheet transistors, source-drain formation requires in-situ heavily doped epitaxial silicon layers to meet device performance requirements. However, it has been known for the past 40 years that donors tend to be deactivated in highly doped Si. When the donor concentration of phosphorus in silicon is higher than 2 x 10<sup>20</sup> at/cm<sup>3</sup>, deactivation of the donors will start to be observed and lead to a decrease in conductivity. Relevant research has shown that donors prefer to move toward and form a structure around vacancies. At the doping concentration of 2 x 10<sup>20</sup> at/cm<sup>3</sup>, through the migration and dynamic aggregation of donors and vacancies, the deactivation mechanism can asymptotically transform donors into PV pairs, P2V, and higher-order P3V, etc. P3V can be further converted into donor vacancy clusters such as P<sub>4</sub>V at concentrations up to 1 x 10<sup>21</sup> at/cm<sup>3</sup>. This effect is due to the negative formation energy, which leads to the thermodynamically favorable configuration of P<sub>3</sub>V and P<sub>4</sub>V. Therefore, the higher the donor concentration in Si, the lower its thermal stability. This results in the available free carrier concentration being thus limited and challenging to increase with increasing donor chemical concentration. Typical phosphorous concentrations used in the source-drain of modern FinFET and gate-all-around (GAA) nanosheet transistor structures are typically higher than 2 x 10<sup>21</sup> at/cm<sup>3</sup>, so the source-drain junction has serious thermal stability issues. To the best of our knowledge, although the mechanism of donor inactivation has been well understood through tremendous studies over the past four decades, donor deactivation has so far been regarded as an inherent problem of thermal annealing. Thus, no discussion existed on whether this phenomenon can be alleviated and resolved. Although additional post-epitaxial dopant activation by state-of-the-art flash or laser annealing is currently the only way to increase activated dopants, the problem of thermal stability of their postannealing activated dopants persists. This study aims to reveal the mechanism of donor deactivation further and to investigate more useful electronic properties of donor vacancy clusters (D<sub>n</sub>V<sub>s</sub>) so that an alternative annealing solution beyond existing ones based purely on thermal effects can be developed. It not only activates dopants but also addresses long-term thermal stability issues associated with thermal-based annealing. Through ab initio calculations, several important electronic properties of donor-vacancy clusters, such as dipole moment, lattice vibrational frequency, and formation energy, are revealed in this work. The relationship between these properties will be used to develop practical annealing solutions to overcome the long-standing problem of donor deactivation. This work extended an earlier study on the mechanism of donor inactivation, namely the dynamic aggregation formation model of phosphorus-vacancy ( $P_nV$ , n = 1-4) clusters, to calculate P<sub>n</sub>V dipole moments. Combining with the known P<sub>n</sub>V formation energies, theoretical calculations have demonstrated that thermally unstable lower-order  $P_nV_s$  (n = 1-3) always have a non-zero dipole moment while thermally stable higher-order P<sub>n</sub>V s do not have a net dipole moment. Particularly, the distribution of this dipole moment can be used to achieve selective dopant activation through selective interaction with Microwave oscillating electric fields. Due to the clear difference between stable and unstable dopant-vacancy clusters, I am trying to develop an energy-selective interaction annealing method to achieve thermally stable junctions of highly n-doped Si. Interaction of microwave electric fields with polar phosphorus vacancy clusters (P<sub>n</sub>V) is expected to eliminate unstable low-order P<sub>n</sub>V (n=1-3) structures, which are the major contribution to the de-activation process. As a result, the typical donor deactivation phenomenon can be effectively suppressed. However, the oscillating electric field boundary conditions required for selective dopant activation are not readily available. Various microwave

cavity setups are explored by introducing various susceptor configurations to choose the optimal susceptor configuration. After finding the optimal susceptor configuration, selective dopant activation is successfully achieved. A model is also built for the microwave field distribution according to the location and dimension of the susceptor set in the microwave cavity. It is concluded that the ability to establish standing waves between triple-parallel pedestals is the key to the efficient coupling of microwave energy into inactive dopant structures in the silicon lattice. Finally, Hall measurements, secondary ion mass spectrometry (SIMS) and XRD, and positron annihilation techniques are applied for characterizations. It is experimentally and analytically verified to support the mechanism of selective doping activation.

Keywords: donor deactivation, dopant vacancy clusters, microwave annealing, thermally stable junctions, dopant activation, donors, phosphorus vacancy clusters, epitaxial Si:P, annealing

## **CONTENTS**

| 口試委    | .員~   | 會審定   | 書         |                  |          | •••••                                   |          |          | - Ass   | 要要        | #    |

|--------|-------|-------|-----------|------------------|----------|-----------------------------------------|----------|----------|---------|-----------|------|

| 誌謝     | ••••• | ••••• |           |                  |          |                                         |          |          |         |           | i    |

| 中文摘    | 要.    |       | •••••     |                  | •••••    | •••••                                   |          | •••••    |         |           | ii   |

| ABSTI  | RAC   | CT    |           |                  |          | •••••                                   |          |          |         |           | iv   |

| CONT   | EN'   | ΓS    |           |                  |          |                                         |          |          |         |           | vii  |

| LIST C | F F   | IGUR  | ES        | •••••            | •••••    |                                         |          | •••••    | •••••   |           | x    |

| LIST C | F T   | ABLE  | ES        |                  |          |                                         |          |          |         | •••••     | xvii |

| Chapte | er 1  | In    | troduct   | ion              | •••••    | •••••                                   | ••••••   | •••••    | ••••••  | ••••••    | 1    |

| Chapte | er 2  | C     | MOS Sc    | aling            | •••••    | •••••                                   | ••••••   | •••••    | •••••   | ••••••    | 12   |

| 2.1    |       | Tech  | nology s  | caling and       | its limi | its                                     |          | •••••    |         |           | 12   |

|        | 2     | .1.1  | CMOS      | scaling the      | ory      | •••••                                   |          | •••••    | •••••   |           | 13   |

|        | 2     | .1.2  | Moore'    | s Law            |          | • • • • • • • • • • • • • • • • • • • • |          |          | •••••   |           | 15   |

|        | 2     | .1.3  | Scaling   | to the limi      | ts       | •••••                                   |          |          | •••••   |           | 16   |

|        | 2     | .1.4  | The eff   | ect of scalin    | ng on tl | he circuit                              | perfor   | mance    | •••••   |           | 18   |

| 2.2    | 2     | Shor  | channe    | l effects        |          | •••••                                   |          |          |         |           | 19   |

|        | 2     | .2.1  | The "sh   | ort channe       | l" defir | nition                                  |          |          | •••••   |           | 19   |

|        | 2     | .2.2  | Drain-i   | nduced-bar       | rier-lov | wering (I                               | OIBL)    |          |         |           | 20   |

| 2.3    | 3     | 3D F  | inFET a   | nd Nano-Sl       | neet-Tr  | ansistor                                | structur | es       | •••••   |           | 22   |

| 2.4    | 1     | Chal  | lenge of  | junction fo      | rmatio   | n in 3D s                               | tructur  | e device | S       |           | 26   |

| Chapte | er 3  | Se    | elective  | <b>Epitaxial</b> | Si:P     | Source-                                 | Drain    | Forma    | tion in | <b>3D</b> | CMOS |

|        |       | Ti    | ansisto   | r Structure      | es       | ••••••                                  | ••••••   | •••••    | ••••••  | ••••••    | 29   |

| 3.1    | l     | The   | design co | onsideration     | n of epi | itaxial S/                              | D for N  | MOS      |         |           | 29   |

| 3.2       | Recessed source-drain                                                     |              | 755        |

|-----------|---------------------------------------------------------------------------|--------------|------------|

| 3.3       | Selective epitaxial Si:P growth                                           |              | 35         |

| 3.4       | Epitaxial Si:P sample preparation                                         |              | 37         |

| 3.5       | Dopant activation annealing                                               | 3            | 37         |

| Chapter 4 | Electronic properties of inactive dopant structures                       | 4            | 15         |

| 4.1       | Ab Initio Calculations                                                    | 4            | 15         |

| 4.2       | Energetic characterization                                                | 4            | 16         |

| 4.3       | Electronic density distribution of P <sub>n</sub> V clusters              | 4            | 18         |

| 4.4       | Dipole moment calculations                                                | 5            | 52         |

| 4.5       | Lattice vibrational mode calculations                                     | 5            | 54         |

| 4.6       | Dynamical donor-vacancy clustering phenomena in highly n-                 | doped silico | n          |

|           | 58                                                                        |              |            |

| 4.7       | Selective dopant activation through polar- D <sub>n</sub> V structures by | y Microway   | ve         |

|           | annealing                                                                 | 6            | 50         |

| Chapter 5 | Susceptor-assisted Microwave Selective Dopant Activation                  | on Annealin  | ıg         |

|           |                                                                           | 6            | 53         |

| 5.1       | Motivation of dopant activation by microwave annealing                    | 6            | 54         |

| 5.2       | The interaction of microwave with Si                                      | 6            | 56         |

| 5.3       | Dielectric heating                                                        |              | 71         |

| 5.4       | Suscetpor-assisted microwave annealing                                    | 8            | 30         |

| 5.5       | Simulation of the electric field distribution in the cavity               | 9            | <b>)</b> 1 |

| 5.6       | Selective dopant activation phenomena                                     | 9            | )3         |

| Chapter 6 | Conclusion                                                                | 9            | )9         |

| 6.1       | Summary of research work                                                  | 9            | )9         |

| 6.2       | Future work                                                               | 10           | )1         |

| Reference  | 103   |

|------------|-------|

|            |       |

| Appendix 1 | 116   |

|            | 3 X 游 |

| Appendix 2 | 117   |

## LIST OF FIGURES

| Figure 1.1 | Transistor evolution from Intel's past 90nm technology node to the future                |

|------------|------------------------------------------------------------------------------------------|

|            | evolution of the Angstrom era. This is mainly due to technological                       |

|            | innovations such as high-k dielectric and metal gate technology, FinFET 3D               |

|            | transistors, GAA nanosheet transistors, and strained silicon, through which              |

|            | Intel can keep up with the rhythm predicted by Moore's Law. [1]2                         |

| Figure 1.2 | Moore's Law Transistor Count 1970-2020. As shown, the transisror count is                |

|            | double for every two years [2]                                                           |

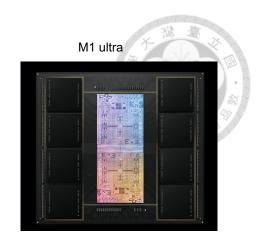

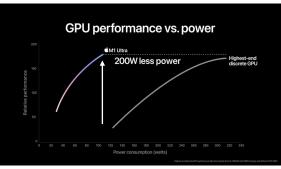

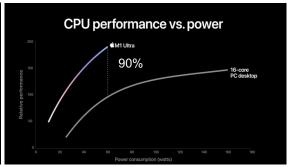

| Figure 1.3 | Released in 2022, the M1 Ultra combines two M1 Max chips in the same                     |

|            | package to drive the MAC studio. M1 Ultra, M1 Max, and M1 vary widely                    |

|            | in size and transistor cell count. For example, the original M1 chip used only           |

|            | about 16 billion transistors, while the single chip with dual dies design gives          |

|            | the M1 Ultra 114 billion transistors. It was 10 times more energy efficient              |

|            | than the best chips at the time [4, 5]4                                                  |

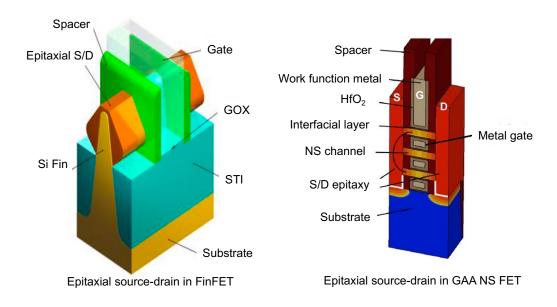

| Figure 1.4 | The epitaxial source-drain structure in FinFET and gate-all-around (GAA)                 |

|            | nano-sheet transistor structures [13, 14]5                                               |

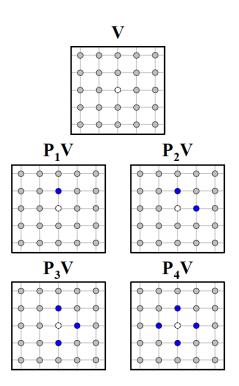

| Figure 1.5 | The net atomic dipole moment orientation of the P <sub>n</sub> V complex is indicated by |

|            | the red arrow in the center of the atomic structure. The white spheres are Si            |

|            | atoms, and the dark (blue) spheres are P atoms. Only atoms up to the second              |

|            | vacancy neighbor are shown for better visibility, and the net dipole is centered         |

|            | on the vacancy. The bonding of dangling bonds around vacancies in P <sub>2</sub> V can   |

|            | be clearly seen in this representation. The right inset depicts microwaves               |

|            | achieving selective dopant activation through energy coupling directly to                |

|            | non-vanishing dipole moments in $P_nV$ (n = 1-3). This contrasts with non-               |

| selective dielectric heating that supports the bulk temperature of the sample.          |

|-----------------------------------------------------------------------------------------|

| 7                                                                                       |

| Figure 2.1 Classical MOSFET scaling as described by Robert Dennard [33, 34]14           |

| Figure 2.2 "Moore's Law" was a far-reaching and dynamic observation made by Intel co-   |

| founder Gordon Moore in 1965, and the law was slightly revised in 1975. The             |

| graph shows that it is still accurate until 2020 [34]15                                 |

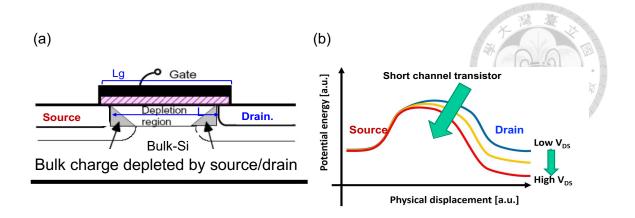

| Figure 2.3 Illustration of drain-induced-barrier-lowering (DIBL) [55]21                 |

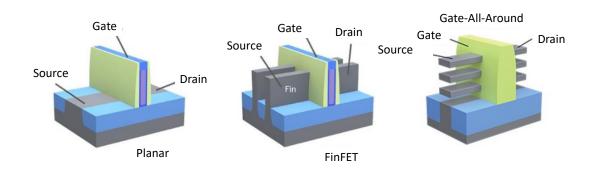

| Figure 2.4 FinFET vs gate-all-around (GAA) nano-sheet transistor [53, 54]21             |

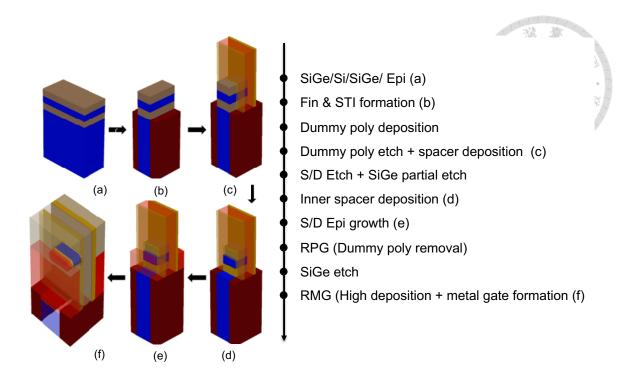

| Figure 2.5 NSFET process flow. (a) to (b) periodic Si/SiGe superlattice deposition and  |

| fin patterning, (c) to (e) polysilicon deposition and patterning followed by            |

| internal spacer etch and formation, (e) source-drain epitaxy formation, (f)             |

| Deposition of high-k dielectric and metal gate after etch process to remove             |

| polysilicon dummy gate. [75, 78]25                                                      |

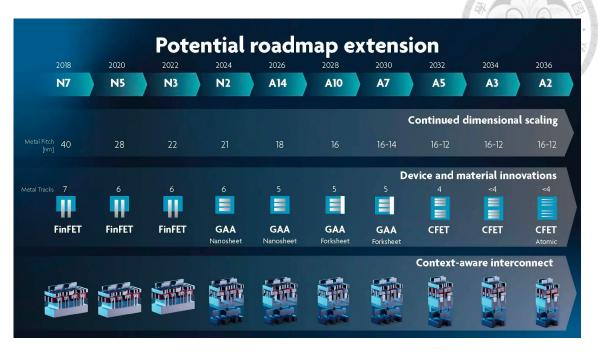

| Figure 2.6 IMEC CMOS scaling technology roadmap presented by IMEC CEO Luc Van           |

| den hove at Marriott Marquee's technology forum (2022)                                  |

| Figure 2.7 Ion implant shadowing effect (a) conventional extended ion implantation in   |

| planar transistor structure, (b) angled ion implantation in FinFET structure            |

| due to shadowing effect of 3D fin structure and additional photoresist height,          |

| (c) the shadowing effect on the shape of the fin and the aspect ratio of the            |

| trench, (d) The effect of implantation angle on fin dopant retention [81, 82].          |

| 27                                                                                      |

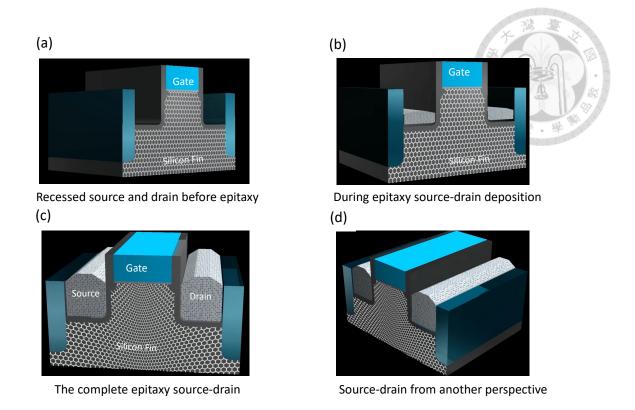

| Figure 3.1 Recess and epitaxial source-drain process sequence in a cross-sectional view |

| along the channel. (a) Recessed fin in the source-drain region, (b) Epitaxial           |

| source-drain during growth, (c) and (d) Full epitaxial source-drain after               |

| process operation in different views [112]                                              |

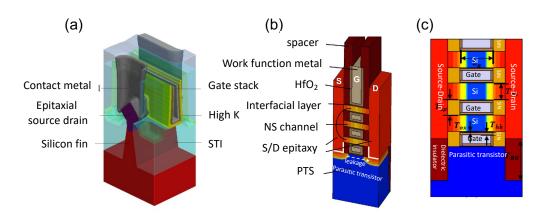

| Figure 3.2 (a) source-drain epitaxy formed by recessed fins in a FinFET structure, (b             |

|---------------------------------------------------------------------------------------------------|

| source-drain epitaxy shared by three nanosheet channels in a nanoshee                             |

| transistor structure, (c) NSFET source-drain with dielectric insulator at the                     |

| bottom to prevent leakage of parasitic transistors [113]                                          |

| Figure 3.3 AMAT Epi xP Centura epitaxy (a) system and (b) process chambers [117].30               |

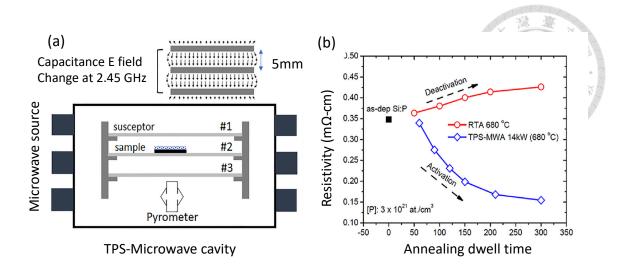

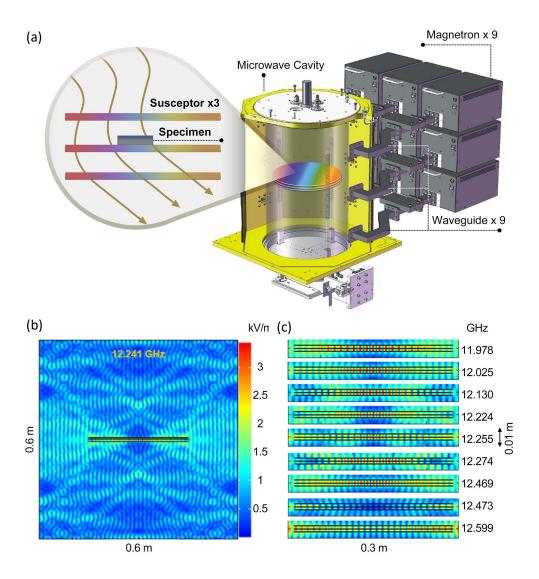

| Figure 3.4 (a) Susceptor setup in a microwave cavity using a triple-susceptor (TPS                |

| configuration where the sample is placed on the middle susceptor with                             |

| controlled spacing 5 mm. The inset depicted the E-field distribution between                      |

| susceptor plates. (b) The resistivity of Si:P was measured as a function of the                   |

| annealing time at 680 °C at RTA and MWA at 14 kW [120]                                            |

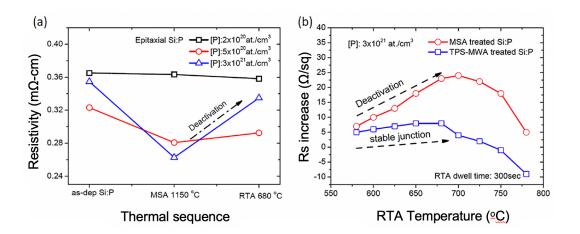

| Figure 3.5 (a) Variation of resistivity of Si:P substrates with thermal annealing sequence        |

| at different phosphorus concentrations. (b) Sheet resistance (R <sub>sh</sub> ) increase o        |

| Si:P samples correlates with RTA annealing temperature for two different                          |

| activation processes: TPS-MWA and MSA [120]4                                                      |

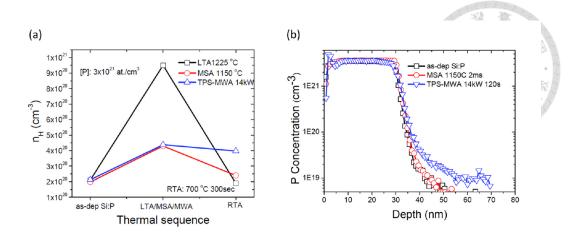

| Figure 3.6 (a) Changes of free carrier concentration before and after heat treatment of           |

| heavily doped Si:P layer with P concentration of 3 x 10 <sup>21</sup> at./cm <sup>3</sup> . (b    |

| Phosphorus SIMS profiles in the epitaxial Si:P film after various annealing                       |

| conditions [120]4                                                                                 |

| Figure 4.1 Schematic representation of the structures considered in <i>ab initio</i> calculations |

| Si atoms are represented with light grey circles, P atoms with dark gray (blue                    |

| circles, and vacancies with white circles [120]                                                   |

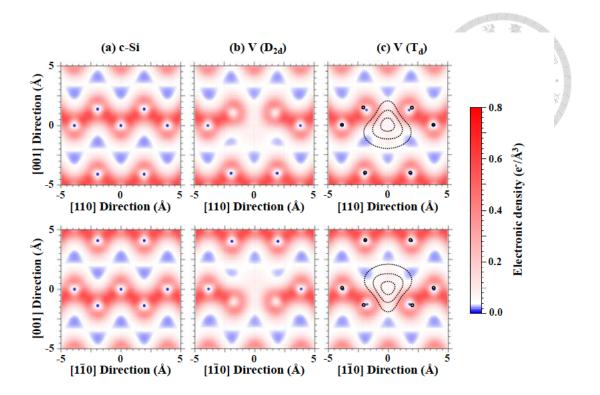

| Figure 4.2 Electronic density plots of valence electrons for c-Si and the Si vacancy in D2        |

| and Td symmetry. The origin of the graph is at the very center of the graph                       |

| corresponding to the position of the vacancy before the atomic configuration                      |

| is relaxed. The dark blue dots correspond to the core regions of the atoms, the                   |

|            | light blue regions represent the interstitial spaces of the structure, and the dark                    |

|------------|--------------------------------------------------------------------------------------------------------|

|            | red regions are the atomic bonds. The black circles and dashed outlines in (c)                         |

|            | represent atomic positions and positron density, respectively, taken from Ref.                         |

|            | [120, 135]                                                                                             |

| Figure 4.3 | Electronic density plots of valence electrons for P <sub>n</sub> V complexes. As in Fig. 1,            |

|            | the origin of plots is located at the center of the plot and corresponds to the                        |

|            | position of the vacancy before relaxing the atomic configuration. The same                             |

|            | color scale as in Fig. 1 is used. Black dashed circles indicate the location of P                      |

|            | atoms [120]                                                                                            |

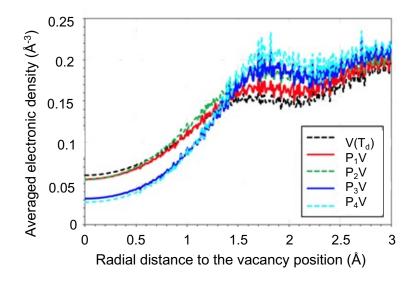

| Figure 4.4 | Averaged electronic density as a function of the vacancy position for $T_{\text{\scriptsize d}}$       |

|            | vacancy configuration and P <sub>n</sub> V complexes [120]                                             |

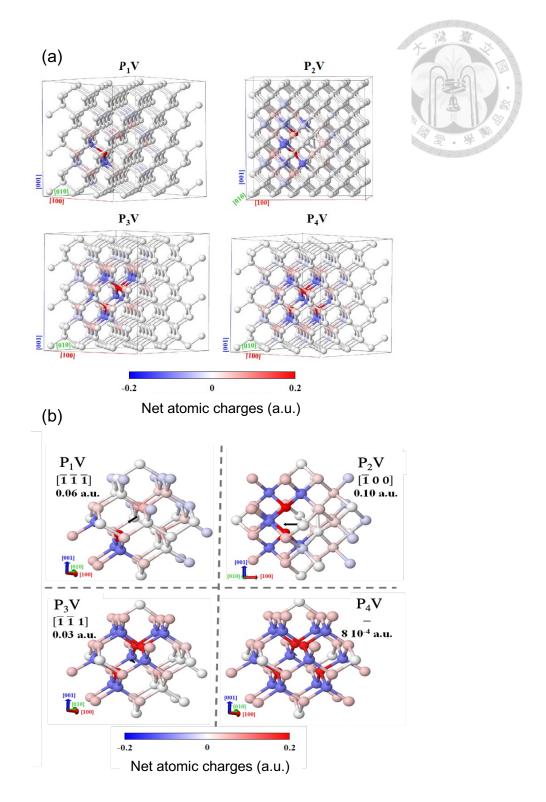

| Figure 4.5 | Net atomic charges in simulation cells containing the P <sub>n</sub> V complexes obtained              |

|            | from the electronic density distribution using CHARGEMOL program [120].                                |

|            | 53                                                                                                     |

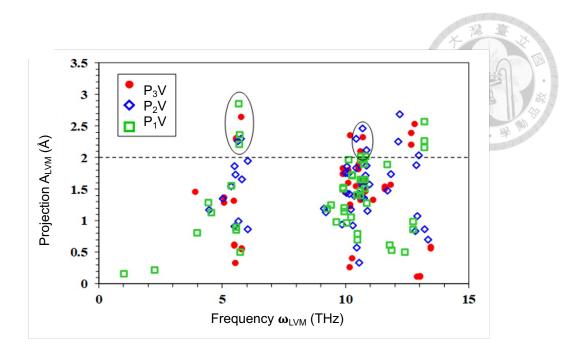

| Figure 4.6 | Mechanism of direct energy coupling and selective dopant activation.                                   |

|            | Projection of atomic displacements of LVMs calculated from Eq. (1) as a                                |

|            | function of their frequency for P <sub>1</sub> V-P <sub>3</sub> V clusters. The horizontal dashed line |

|            | indicates the threshold used to select highly aligned LMVs with the                                    |

|            | corresponding net dipole moment direction. Circles show those highly                                   |

|            | aligned LVMs with similar frequencies                                                                  |

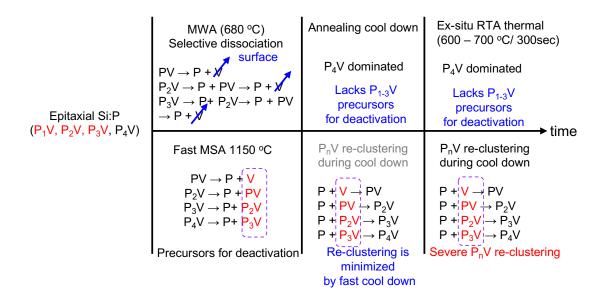

| Figure 4.7 | Comparison of reaction mechanisms during MWA annealing and MSA                                         |

|            | annealing in highly doped Si. MWA enables the selective dissociation of                                |

|            | lower order and unstable $P_nV$ (n=1-3), leaving behind an electrically activated                      |

|            | isolated P and P <sub>4</sub> V vacancy complex that leads a stable junction. Fast MSA                 |

|            | generates lower order P <sub>n</sub> V during the annealing process at leak temperature,               |

| the available low order $P_nV$ in doped Si serves as the precursor for continuous          |

|--------------------------------------------------------------------------------------------|

| P deactivation during cooling down process or upon a moderate RTA therma                   |

| budget62                                                                                   |

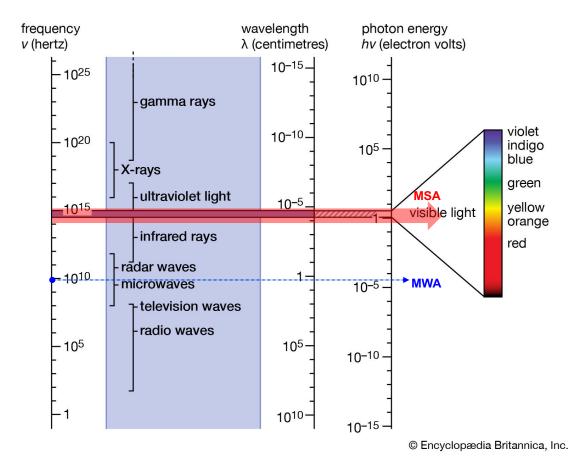

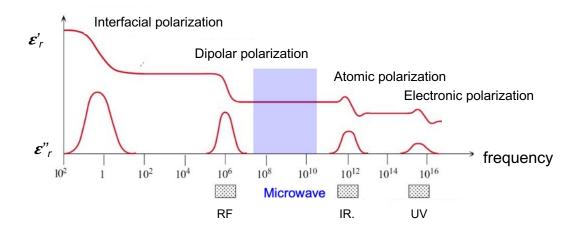

| Figure 5.1 The electromagnetic spectrum covers radio waves, microwaves, infrared           |

| ultraviolet, X-rays, and gamma rays. The narrow range of visible light is                  |

| between IR and UV and is shown enlarged on the right [150]65                               |

| Figure 5.2 Temperature and thermal budget comparisons for various annealing                |

| techniques, including MWA, RTA, selective-MWA, MSA (LSA)66                                 |

| Figure 5.3 The electromagnetic field is represented by the electric field E vector and the |

| magnetic field B vector are perpendicular to each other and perpendicular to               |

| the direction of propagation [150]67                                                       |

| Figure 5.4 "Electromagnetic wave frequency" dependent dielectric polarization              |

| mechanism. In the presence of interfacial, orientational dipolar, ionic, and               |

| electronic polarization mechanisms, the frequencies of the real and imaginary              |

| parts of the permittivity. [171]70                                                         |

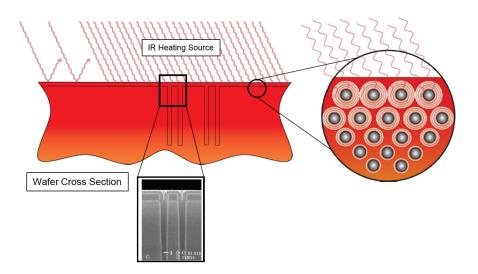

| Figure 5.5 RTA heating, heating is limited by thermal diffusivity and surface              |

| temperature73                                                                              |

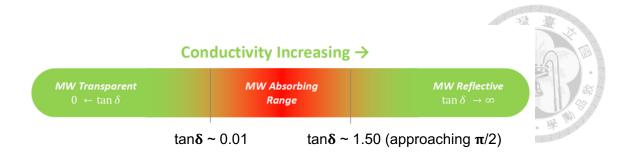

| Figure 5.6 Loss factor-dependent microwave absorption, microwaves are highly absorbed      |

| in materials with loss factors between 0.01 and 1.5, below 0.01 microwaves                 |

| penetrate the material, above 1.5, microwaves are reflected from the materia               |

|                                                                                            |

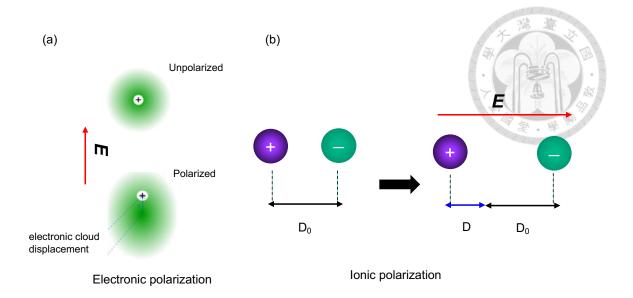

| Figure 5.7 Different polarization mechanisms; (a)Electronic polarization and (b) ionic     |

| polarization under external electric field                                                 |

| Figure 5.8 Dielectric heating polarization mechanisms in dielectric solid                  |

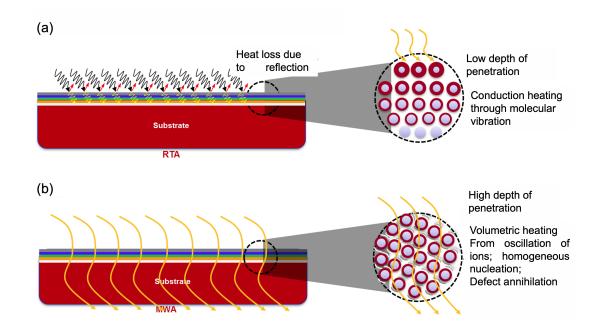

| Figure 5.9 (a) Conventional rapid thermal annealing (RTA) heating feature, heating is      |

|             | limited by thermal diffusivity and surface temperature, (b) Microwave          |

|-------------|--------------------------------------------------------------------------------|

|             | volume heating, heat is generated from inside the object                       |

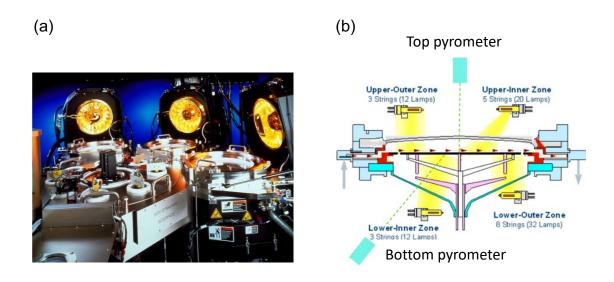

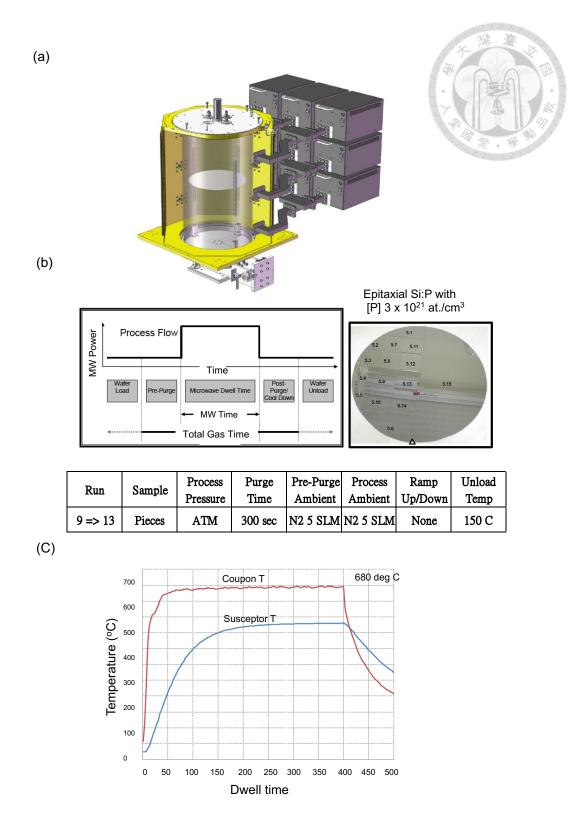

| Figure 5.1  | 0 Microwave annealing process, (a) Microwave annealing modules, nice           |

|             | magnetron, and the corresponding wave guide are shown, (b) The N2 ambient      |

|             | gas used in the annealing process, (c) The typical temperature vs. dwell time  |

|             | of microwave annealing process                                                 |

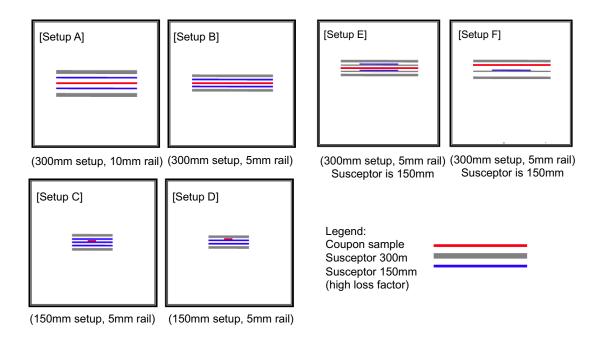

| Figure 5.11 | First trial run of the MWA cavity setup. A, B, and C-type susceptors have      |

|             | different area sizes and impurity doping degrees. Susceptors and samples of    |

|             | various sizes have undergone trial runs                                        |

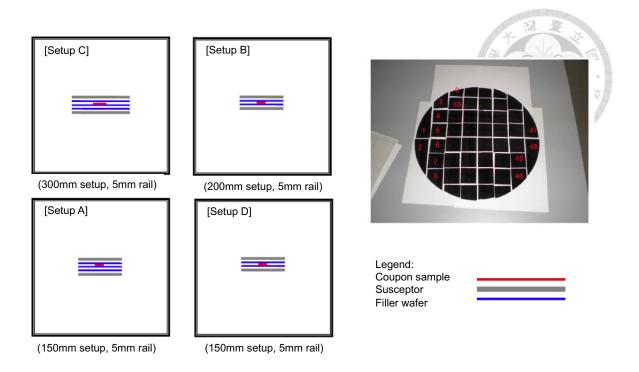

| Figure 5.12 | 2 Second trial run MWA cavity setup. Use only C-bases of different area sizes. |

|             | Samples are placed on pedestals of different area sizes. Also shows the area   |

|             | size of the test sample86                                                      |

| Figure 5.1. | 3 Optimized microwave cavity setup for activation of heavily doped Si:P        |

|             | dopants. The sample sits in a triple-parallel-susceptor is shown               |

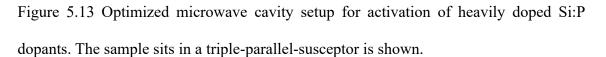

| Figure 5.1  | 4 Single susceptor configuration, Surface eddy currents are generated by       |

|             | conductive Si:P layers placed on a single susceptor configuration. When Si:P   |

|             | becomes more conductive by indirect or direct heating, it will reach a         |

|             | conductive heating regime and induce surface eddy currents90                   |

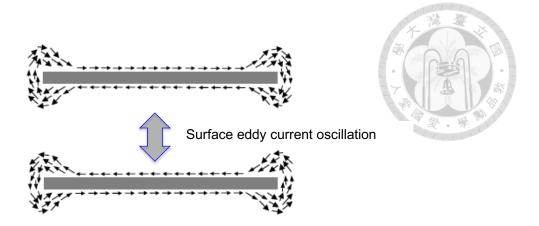

| Figure 5.15 | 5 Capacitive oscillatory fields established between triple parallel susceptor  |

|             | configurations. During switching at 2.45 GHz, the conducted field drives the   |

|             | current to flow for an instant                                                 |

| Figure 5.16 | Optimization of susceptor setup in microwave cavity, (a). Optimized triple     |

|             | parallel base setup with 5mm spacing between them, (b). E-field distribution   |

|             | for resonance at 12.241 GHz (5th harmonic of 2.45 GHz), (c). E-field           |

|             | distribution for eigenmodes around 12 241 GHz [188]                            |

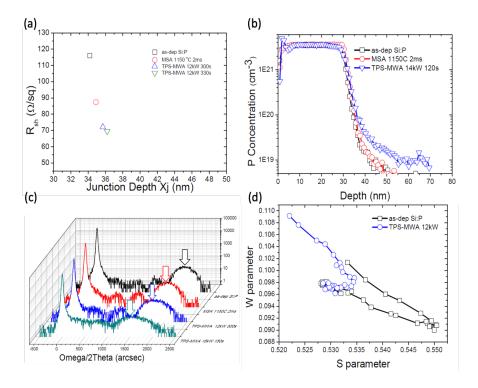

| Figure 5.17 Dopant activation characterization. (a) Rsh-Xj plot of epitaxial Si:P film                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| under various annealing conditions and (b) The corresponding Phosphorus                                                                                                                                                                             |

| SIMS profile in the epitaxial Si:P film. (c) HRXRD curves of epitaxial Si:P                                                                                                                                                                         |

| film annealed under various annealing conditions. (d) Vacancy defect state of                                                                                                                                                                       |

| S-W plot with positron energy as a running parameter for as-deposited Si:P                                                                                                                                                                          |

| and MWA annealed samples. The sharp turning point shifts to a smaller S-                                                                                                                                                                            |

| parameter value indicating a decrease in dopant vacancy clusters (P <sub>n</sub> V) [188].                                                                                                                                                          |

|                                                                                                                                                                                                                                                     |

| 97                                                                                                                                                                                                                                                  |

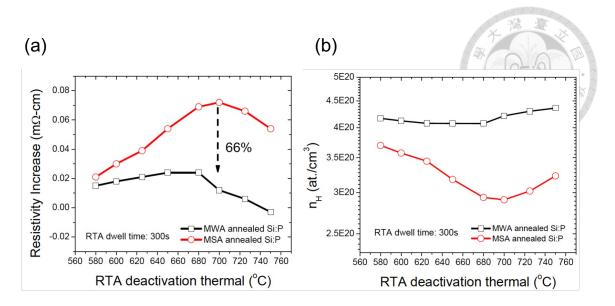

| Figure 5.18 Characterization of dopant deactivation by (a) resistivity change and (b)                                                                                                                                                               |

|                                                                                                                                                                                                                                                     |

| Figure 5.18 Characterization of dopant deactivation by (a) resistivity change and (b)                                                                                                                                                               |

| Figure 5.18 Characterization of dopant deactivation by (a) resistivity change and (b) free carrier concentration as a function of RTA temperature [188]98                                                                                           |

| Figure 5.18 Characterization of dopant deactivation by (a) resistivity change and (b) free carrier concentration as a function of RTA temperature [188]98  Figure 6.1 Kinetic differences in dopant activation during and after selective microwave |

## LIST OF TABLES

| Table 1.1 As of 2022, the transistor count in commercially available chips including           |

|------------------------------------------------------------------------------------------------|

| microprocessor, GPU, deep learning processor (DLP) and memory [4]-[10]                         |

| 3                                                                                              |

| Table 4.1 D <sub>n</sub> V Formation energy of studied complexes from Eq. [2]48                |

| Table 4.2 Net atomic dipole moment of P <sub>n</sub> V complexes evaluated from the electronic |

| density distribution. Dipole moments are in atomic units (a.u.)54                              |

| Table 4.3 Local vibration modes for $P_1V$ and $P_2V$ . Only atoms up to 2nd neighbors of the  |

| vacancy were moved to evaluate the Hessian matrix (16 atoms in total, which                    |

| are represented in the dipole analysis plots). This table shows the obtained                   |

| frequencies                                                                                    |

| Table 5.1 First microwave annealing (MWA) trial run results. A, B, C type susceptor are        |

| different in area size and impurity doping level. C-type susceptor of 150 mm                   |

| and a sample-to-susceptor distance of 5 mm provided the best interaction with                  |

| microwaves, as Rs before and after MWA showed the most significant                             |

| changes85                                                                                      |

| Table 5.2 Second trial run MWA results. The results confirmed that a C-type susceptor of       |

| 150 mm and a sample-to-susceptor distance of 5 mm were revalidated to                          |

| provide the best interaction with microwaves, as Rs before and after MWA                       |

| showed the most significant changes87                                                          |

### **Chapter 1** Introduction

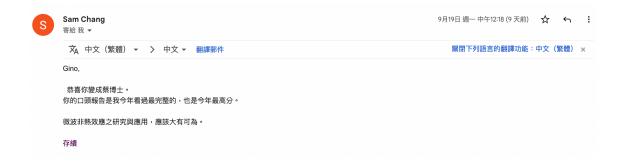

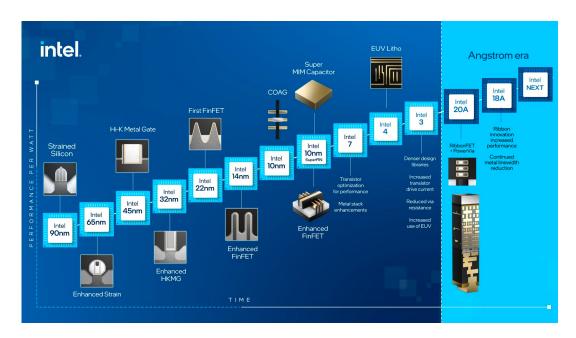

In recent decades, the semiconductor industry has developed a new generation of CMOS scaling processes every two years, with each generation reducing the minimum structure size by a factor of about 0.7 to achieve an improvement in area size of about 0.5. The innovation of squeezing more and more transistors onto a chip has resulted in doubling the number of transistors every two years (see Figure 1.1 and Figure 1.2)[1, 2] and maintaining the pace of Moore's Law [3]. However, due to the higher process complexity and the larger number of photomask steps, the development time for the latest technology generations, e.g., 5 nm and beyond, has taken longer than the normal two-year pace. Nevertheless, the 5-nm and 4-nm technologies used in iPhones offer above-average transistor density improvement, allowing us to increase transistor density at a rate that doubles approximately every two years.

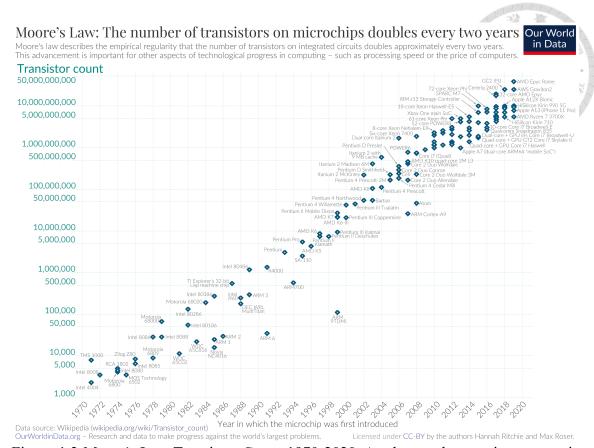

The impact of these remarkable scaling technologies of CMOS on human civilization can be seen from the most advanced electronic products in the market. For example, the Apple's M1 Ultra (two dies in one chip) commercial dual-chip microprocessor based on ARM has reached 114 billion, as shown in Table 1. The system was manufactured using TSMC's 5nm semiconductor manufacturing process [4, 5]. As shown in Figure 1.3, the power efficiency of the CPU and GPU of the M1 Ultra used in Studio 2022 MAC can be improved by a factor of 10 compared to the best products at that time. The largest number of transistors on an IC chip so far in 2020 is a deep learning engine, Cerebras' Wafer Scale Engine 2. It uses design strategies to bypass any non-running cores on the device, enabling up to 2.6 trillion MOSFET chips. This unique chip is manufactured by TSMC using a 7nm FinFET process [6]-[10]. These amazing achievements illustrate how innovation in manufacturing processes for further CMOS scaling is impacting modern

microelectronics and changing the real world. This dissertation, "Discovery of a novel microwave-selective dopant activation mechanism and its role in junction stability of highly n-doped silicon," is part of the effort to further scaling CMOS technology. This dissertation presents the problems of the dopant activation mechanism in CMOS scaling technology, explains how to obtain useful step-by-step hints from a long-standing problem, and uses the experience accumulated by the predecessors to discover the microwave-selective dopant activation mechanism to solve the problem.

Figure 1.1 Transistor evolution from Intel's past 90nm technology node to the future evolution of the Angstrom era. This is mainly due to technological innovations such as high-k dielectric and metal gate technology, FinFET 3D transistors, GAA nanosheet transistors, and strained silicon, through which Intel can keep up with the rhythm predicted by Moore's Law. [1]

Figure 1.2 Moore's Law Transistor Count 1970-2020. As shown, the transisror count is double for every two years [2].

| Year | Component                      | Name                  | Number of MOSFETs<br>(in billions)    |

|------|--------------------------------|-----------------------|---------------------------------------|

| 2022 | microprocessor<br>(commercial) | Apple M1 Ultra        | 114 (dual die in same chip)<br>1140 億 |

| 2022 | GPU                            | Nvidia H100           | 80                                    |

| 2020 | DLP                            | Colossus Mk2 GC200    | 59.4                                  |

| 2020 | any IC chip                    | Wafer Scale Engine 2  | 2600 (one wafer one die)<br>26000 億   |

| 2019 | any IC chip                    | Samsung's V-NAND chip | 2000 (stack)                          |

Table 1.1 As of 2022, the transistor count in commercially available chips including microprocessor, GPU, deep learning processor (DLP) and memory [4]–[10]

Figure 1.3 Released in 2022, the M1 Ultra combines two M1 Max chips in the same package to drive the MAC studio. M1 Ultra, M1 Max, and M1 vary widely in size and transistor cell count. For example, the original M1 chip used only about 16 billion transistors, while the single chip with dual dies design gives the M1 Ultra 114 billion transistors. It was 10 times more energy efficient than the best chips at the time [4, 5].

The silicon-based semiconductor manufacturing technology on which CMSO scaling relies is the origin of today's digital economy. Advanced chips have been the foundation for technological innovations such as artificial intelligence (AI) and next-generation wireless communication technologies through continuous development over the past few decades. High-speed electronic circuits on a chip wafer depend on the concentration of free charge carriers in CMOS transistors. Increasing free carrier concentration at Si junctions requires high concentrations of electroactive dopants,

usually determined by doping and annealing techniques. However, the introduction of transistors with three-dimensional (3D) nanostructures such as nanowires and nanosheets [13, 14] creates new challenges in forming impurity-doped regions. With the downsizing of CMOS to the 16-nm technology node, transistor structures have evolved from planar transistor structures to 3D FinFET transistor structures to meet performance requirements. Since the 2-nm technology node, 3D transistor structures have evolved to nano-sheet transistor structures that enable further scaling of CMOS. These 3D transistor structures require new source-drain formation techniques (Figure 1.4) to achieve abrupt control of the doping profile to meet short channel requirements while maintaining low series resistance, including source-drain (Rsd) and contact resistance (Rcsd).

Figure 1.4 The epitaxial source-drain structure in FinFET and gate-all-around (GAA) nano-sheet transistor structures [13, 14].

Recessed source-drain and heavily doped epitaxial SiP techniques were introduced [15]- [18]. However, heavily doped epitaxial Si:P with phosphorus concentrations higher than  $1 \times 10^{21}$  at./cm<sup>3</sup> exhibits severe donor stability problems, requiring post-annealing to

activate the doping. Post-epitaxial Si:P annealing techniques with millisecond annealing, such as flash annealing or laser annealing techniques with a time scale of micro- or nanoseconds, can promote dopant activation. However, these activated dopants are usually thermally unstable. This problem of inherent donor stability is a long-standing issue in semiconductor applications and leads to temperature limitations in subsequent CMOS fabrication processes after the S/D dopant activation annealing process.

Therefore, in this dissertation, an alternative annealing technique will be developed to solve the abovementioned high-temperature annealing problems. I started with an overview of low-temperature microwave annealing to improve the compatibility of the annealing technique with the materials used in modern CMOS fabrication. From today's scientific perspective, low-temperature targets for dopant activation are largely unphysical and unrealistic. This is because dopant activation is thermally based. Regardless of how heat is generated, they end up the same way in the physical world. The new low-temperature dopant activation method will run into the typical problems of inadequate dopant activation and damage repair, which are still essentially the same as with conventional rapid thermal annealing. However, relying on intuition alone, without a deep understanding of physics, one is sometimes free from the constraints of one's mind, which knows no barriers. This effect sometimes offers a new way to get in touch with a new physical world. This study aimed to achieve an R<sub>s</sub>-X<sub>i</sub> value comparable to conventional millisecond annealing at temperatures below 700 °C to avoid diffusion of dopants. This was finally completed after a lengthy study of overseas annealing devices and numerous experiments with various microwave cavity setups. This work has shown that microwaves can effectively activate doping of highly doped Si:P at temperatures below 700 °C when an optimal tri-parallel susceptor setup and sample configuration are used. Compared to the prior art, the obtained flat junctions were shown for the first time

to provide the high carrier concentration that MSA processes can typically achieve at temperatures above 1100 °C. In addition, microwave annealed junctions show excellent thermal stability at a moderate heat budget of 700 °C.

Figure 1.5 The net atomic dipole moment orientation of the  $P_nV$  complex is indicated by the red arrow in the center of the atomic structure. The white spheres are Si atoms, and the dark (blue) spheres are P atoms. Only atoms up to the second vacancy neighbor are shown for better visibility, and the net dipole is centered on the vacancy. The bonding of dangling bonds around vacancies in  $P_2V$  can be clearly seen in this representation. The right inset depicts microwaves achieving selective dopant activation through energy coupling directly to non-vanishing dipole moments in  $P_nV$  (n=1-3). This contrasts with non-selective dielectric heating that supports the bulk temperature of the sample.

However, this result has long puzzled us since conventional RTA annealing at or near 700 °C is unlikely to activate the heavily doped epitaxial Si:P, but rather deactivate the phosphorus (the donor). This implies that dopant activation must occur by mechanisms other than thermal effects. Through further investigation of the donor deactivation mechanism and additional ab initio calculations, it's found that the known dopant-vacancy clusters ( $P_nV$ , n=1-4) that dominate the donor deactivation mechanism have

individually different thermal stabilities and dipole moments. The thermally unstable  $P_nV$  (n=1-3) show a nonzero dipole moment dependence, while the thermally stable  $P_4V$  shows no dipole moment. Taking advantage of the different electronic properties of stable  $P_4V$  and unstable  $P_{1-3}V$ , this study aims to explain the annealing mechanism as a possible selective annealing scheme that can selectively activate thermally unstable  $P_nV$  structures (n = 1 -3) (Figure 1.5). Thus, the obtained annealed junction is thermally stable, and the heavily doped junctions can withstand the thermal budget ( $\sim 600$  - 700 degrees C) of other processes after the subsequent source-drain annealing process. In short, by discovering a novel phenomenon of selective dopant activation, efficient activation of dopants in highly n-doped silicon can be achieved at lower temperatures below  $700\,^{\circ}C$  with stable junctions.

Chapter 1 overviews how CMOS scaling has enabled transistor density and count over the past few decades and the practical implications. This chapter presents the motivation for this study and the explanation of how to address the typical problem of donor deactivation and how to achieve thermal stability in highly n-doped silicon. Donor deactivation is a long-standing problem in the semiconductor industry.

Chapter 2 discusses Moore's Law and its lofty insights into doubling the number of transistors on a chip every two years. Direct CMOS scaling is an important approach to implementing Moore's Law, and it continues to this day. CMOS scaling gradually leads to short-channel effects due to shortened gate length, or drain-induced barrier low (DIBL) effects. Short-channel effects are a fundamental problem that must be overcome by introducing 3D transistor structures such as FinFETs and gate-all-around (GAA) nanosheet transistors. The 3D transistor architecture revolutionizes the formation of source-drain junctions. In the past, the ion implantation technology used in planar transistor structure for a long time can no longer effectively distribute the dopant in the source-drain of the Fin structure due to the shadowing effect. The shadow effect is created

by the polysilicon gate of the 3D CMOS structure and the photoresist thickness required for the implanted photo process. The S/D of 3D transistor structures is formed by twostage steps of S/D groove process and CVD in-situ doped Si epitaxy process. Chapter 3 begins with an introduction to design considerations for source-drain epitaxy, including electrical conductivity, abrupt dopant distribution, and strain-engineered material properties that induce channel strain and enhance carrier mobility. Doped Si:P formation processes, such as those produced by chemical vapor deposition, are introduced. It then describes the donor deactivation issues associated with highly doped epitaxial Si:P and the requirements for post-epitaxial Si:P annealing processes. It is concluded that while millisecond annealing can satisfy the requirements for dopant activation and abrupt transition, the obtained junction is thermally unstable. This background motivated this work to investigate a new dopant activation technique that targets additional thermal stability requirements in addition to the basic dopant activation and abrupt junction requirements. At the end of this chapter, preliminary results of microwave annealing are briefly presented, which not only show that excellent dopant activation and abrupt junctions can be achieved at 680 °C are only possible with millisecond annealing at 1150 °C, but also show additional unique advantages in stabilizing junctions. Based on the collected data, it is suspected that the thermal stability advantage may be due to the nonvanishing dipole moment associated with the unstable donor vacancy clusters and their selective interaction with microwaves. This motivated us to perform ab initio calculations to reveal more useful electronic properties such as formation energies, electron density plots, and dipole moments of donor vacancy clusters. Chapter 4 provides an initial overview of previous research efforts to understand the mechanisms of donor deactivation. This work extends from the ab initio work of our earlier predecessors to our calculations of lattice vibrational modes and dipole moments of P<sub>n</sub>V to exploit their properties for

selective dopant activation, to be mentioned later. Chapter 5 gives a comprehensive insight into the interaction of microwaves with matter and silicon. This involves thermal and non-thermal effects. In terms of thermal effect, it is divided into conduction heating and dielectric heating. Dielectric heating involves dielectric losses due to all the different charge polarization phenomena. This knowledge helps us explain how microwaves couple energy with epitaxial Si:P layers and bulk silicon substrates. Next, this paper shows how microwave annealing systems can be explored and optimized to achieve the desired selective doping activation. By distinguishing between polar and non-polar P<sub>n</sub>Vs, this study experimented with microwave cavity setups, including various parallel pedestal setups, and ultimately found that dopants can be activated at temperatures below 700 °C. After the breakthrough of low temperature doping activation technology, it was verified that the junction realized by low temperature microwave doping activation technology showed unexpected thermal stability advantages, which is also a breakthrough in this research era. Finally, this work is devoted to understanding the origin of low-temperature microwave tempering and thermal stability. It first introduces the formation energies and dipole moments of vacancy dopant clusters and their junctions to build a model of selective dopant activation, including how microwaves select coupling energies to nonpolar P<sub>n</sub>V for low-temperature annealing and thermal stability. Chapter 6 summarizes the observations and points out that some mysteries remain in explaining how energy couples to P<sub>n</sub>V. Suggested research priorities for future interested researchers are also presented...

The related research results of this dissertation work have been previously published in two journals: "Tsai, *et al.* (2021). Achieving junction stability in heavily doped epitaxial Si: P. Materials Science in Semiconductor Processing, 127, 105672." and "Tsai, C. H., et al. (2022). Efficient and stable activation by microwave annealing of nanosheet

silicon doped with phosphorus above its solubility limit. Applied Physics Letters, 121(5), 052103." This diserttation has cited both papers and obtained permission to reuse content. Reuse permissions have been placed in the appendix.

.

### **Chapter 2 CMOS Scaling**

T The history of lithography has been related to shortening the wavelength of the light source, starting with the earliest lasers, through ArF and KrF, excimer lasers, and, more recently, extreme ultraviolet (EUV) lasers. This has played an important role in promoting the continuous development of CMOS scaling. However, lithography is generally expected to encounter obstacles to spatial resolutions beyond the sub-five nanometers. Although this application is still far away, the industry will consider other alternative light/energy sources of shorter wavelengths, such as electron beams or X-rays to achieve spatial resolution requirements.

CMOS scaling limitations in the nanometer range may come from the laws of physics. An example is when the source-drain ratio is very close (currently estimated to be 7nm), the carriers in the channel reach the ballistic limit; in this case, due to the short stroke. The carrier velocity reaches saturation velocity, causing the channel to drive current to advance, reach the limit and cannot ascend. The problem is that CMOS scaling will likely last at least 20 years before encountering a similarly more drastic revolutionary change. While the physical limit is often discussed, it is far from it. The evolution of transistor structure innovations from planar structures to 3D gate-all-around (GAA) transistor structures shows that the semiconductor industry is still very effectively following Moore's Law, overcoming various engineering bottlenecks, driving CMOS miniaturization, and deepening human civilization. In this chapter, the theory of CMOS scaling and the relationship between short-channel effects and innovations in 3D transistor structures that require new source-drain formation techniques in high-n-doped

silicon technology are described in detail. Dopant activation issues related to high n-doped silicon are the focus of the remainder of this article.

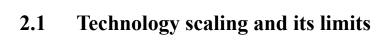

#### 2.1.1 CMOS scaling theory

In general, insights from "Moore's Law" [19-30] refer to the periodic and continuous scaling of the three-dimensional physical feature size of silicon-based complementary metal-oxide-semiconductor (CMOS) transistors through semiconductor design and fabrication. This theory of deep insight and huge vision has been the main driving force behind the production of today's complex electronic device technology. The scaling theory proposed by Dennard et al. in 1972 started this success story [31]. Although ten years later, the semiconductor industry began to practice this theory in CMOS transistors. From then to today, the semiconductor industry has integrated more and more transistors into a single integrated circuit (IC) chip. Even more surprising, the actual evolution of CMOS scaling is consistent with Gordon E. Moore's 1965 predictions. That is, the total number of transistors that can be integrated into a chip, or so-called chip transistor density, doubles approximately every two years [32] without a corresponding significant increase in chip cost.

Mead [33] and Dennard [23] had the foresight in the early 1970s that MOS transistor structures could be scaled to smaller physical sizes. Their proposed scaling theory describes explicitly strategies and methods for scaling metal-oxide-semiconductor field-effect transistors (MOSFETs) to continue the goals of increasing transistor area density, transistor performance, and reducing chip power consumption. The central idea calls for scaling the transistor's gate length, gate width, gate oxide thickness, and supply voltage by the same ratio and increasing the channel doping by the inverse of the same ratio (see Figure 2.1). The overall expected equivalent result would be a chip with a smaller area,

higher drive current transistors, and lower parasitic capacitance for lower power consumption. Despite the shrinking size, the theoretical design of scaling keeps the field strength in the MOS transistor constant across technology nodes. So the original design of scaling theory is constant field scaling. Therefore, constant field scaling requires lowering the supply voltage at each technology node. When transistor fabrication technology arrived in the 1980s, the constant-field scaling strategy was replaced by the new constant-voltage scaling thinking. In constant voltage scaling, only all dimensions of the MOSFET are scaled "s" times, but the supply voltage and terminal voltage are controlled unchanged during transistor scaling. Therefore, the electric field inside the device does not remain constant but increases from generation to generation. Until the early 1990s, gate dielectric TDDB and increased channel hot-carrying currents caused excessive power dissipation and heating when the electric field was increased. In severe cases, field-induced aging inside the device could cause serious product safety problems. Therefore, in the 1990s, constant field scaling was applied to technical scaling. This classic scaling theory was used successfully by the industry before the 130nm generation in the early 2000s.

Figure 2.1 Classical MOSFET scaling as described by Robert Dennard [33, 34]

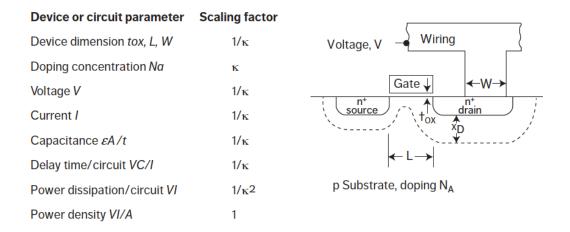

#### 2.1.2 Moore's Law

"Moore's Law" is famous because its scale scaling theory accurately predicts the practice and application of CMOS fabrication in transistor scaling. Intel co-founder Gordon Moore predicted in 1965 that chip improvements would allow processor speed and overall processing performance to double every two years. Unlike general physics, Moore's Law is purely a phenomenological observation until 2022. It has been accurate for 57 years. Moore's Law has become an evolutionary guide for computer processor manufacturing. Figure 2.2 shows its validity until today [34]. Thanks to Moore's Law, iPhones, iMAC, and various other devices are steadily improving. While it's intuitive that Moore's Law can't go on forever, predictions of the limits of size reduction have proven to be the most insightful horizons.

Figure 2.2 "Moore's Law" was a far-reaching and dynamic observation made by Intel cofounder Gordon Moore in 1965, and the law was slightly revised in 1975. The graph shows that it is still accurate until 2020 [34]

### 2.1.3 Scaling to the limits

Although the practice of scaling CMOS transistors has repeatedly surpassed some of the "wall barrier" predictions reported in [35], persistent pessimists still believe that it will fail in the nanoscale world. They often cite that CMOS transistors are approaching the physical boundaries of atomic and quantum mechanics [36]. Furthermore, it is worrying that the device itself cannot continue to operate stably and explore its limitations from an economic and technical point of view. The important challenges that may be the main obstacles to further scaling of CMOS are divided into five main parts, which are summarized as follows [37]:

**Physical size scaling brings challenges:** As devices shrink, tunneling and short-channel leakage currents will become more and more serious, which will affect and limit the performance of CMOS devices, especially the power consumption part.

Materials Science Challenge: The first is that dielectric materials, such as high-k materials for gate stack applications and very low-k materials for back-end (BEOL), cannot provide the required insulation while maintaining electrical properties. The second is that wiring materials such as copper, cobalt, and tungsten cannot provide reliable conduction for continuous scaling. These all rely on materials science innovations to overcome the above challenges.

**Power Consumption and Heat Disspitation Challenges:** This is because transistor scaling drives the rapid increase in the number of transistors per unit area integrated with technology, resulting in greater power consumption and higher heat dissipation. Inherent transistor leakage and advanced packaging play a key role in dealing with power and dissipation issues.

**Lithography Technical Challenges:** The bottleneck in lithography is related to the ability to provide sub-optical wavelength (e.g. sub-10 nm) resolution for fabricating CMOS devices. This relies on the development of light sources such as EUV and X-rays.

**Cost and Economic Challenges:** This is mainly due to rising production, manufacturing, and testing costs, which can become unaffordable from an economic point of view. As CMOS shrinks to the 2nm node, few players can afford the investment cost and risk..

However, apparently from the past to 2022, and 15 years from 2022, the above challenges do not appear to be any fundamental constraints preventing Moore's Law from characterizing integrated circuits. With endless device scaling, the complexity of semiconductor process technology continues to increase. This phenomenon acts as the "innovation engine" that drives Moore's Law [38]. For the past 20 years, the semiconductor industry has been developing next-generation process technologies. Each generation shrinks minimum feature sizes (such as Polygate-to-Polygate pitch and Finto-Fin pitch) by about 0.7, achieving an area scaling improvement of approximately 0.5x (see Figure 2). Recently, the increase in the complexity of scaling transistors has been accelerating. Advanced process technologies have extremely small feature sizes that require multiple exposures (multiple patterns) or EUV to reproduce these features on silicon accurately. With the advancement of technology nodes, the application of EUV [39]-[42] has gradually expanded from Back-End-of-Line (BEOL) to Middle-End-of-Line (MEOL) and is also widely used in Front-End-of-Line at 3nm and 2nm nodes. Line (FEOL). In addition, the evolution of transistors from planar transistor structures to 3D FinFET and nanosheet transistor structures [42]-[44] has further enhanced gate-tochannel control, and these technologies play a key role in enabling smaller size and higher

performance devices. Recent generations of technology, such as the sub-5nm node, took slightly longer than the normal two-year cadence. Nonetheless, semiconductor fabrication techniques have provided rapid, periodic improvements in transistor density, allowing us to increase transistor density.

Even if Moore's Law does not end in the next 15 years, the scientific community has long proposed several alternative material solutions in addition to Si materials to extend the life of CMOS scaling once Si reaches its performance limit. For example, two-dimensional materials (2DM) that are atomically monolayer thick have caused a great research boom in the past two decades to overcome the degradation of carrier mobility when the thickness of Si is reduced below 5 nm. Its unique electronic, thermal, and mechanical properties make 2DM an alternative possible approach to fabricate new complementary metal oxide semiconductor (CMOS) and CMOS devices [45]–[47].

### 2.1.4 The effect of scaling on the circuit performance

Transistor scaling is the primary method for implementing high-performance logic and memory devices. A 30% shrink per technology node for CMOS shrink will ultimately result in a 30% reduction in parasitic capacitance and doubling the device density before the gate length reaches its limit. This ultimately results in a 40% increase in clock frequency while significantly reducing power consumption and active power per conversion by roughly 60% and 50%, respectively.

With the industry's aggressive scaling of CMOS technology to improve performance, overcoming the detrimental short-channel effect (SCE) derived from shrinking channel lengths to reduce device leakage has been the focus of MOSFET scaling [48, 49]. As the channel length shrinks, this indirectly decreases gate-to-channel controllability due to increased charge sharing from source/drain, the so-called drain-induce-barrier-lowing (DIBL) effect. The progress of the introduction of new materials, the innovation of

transistor structures and related processes such as lithography, etching, and thin film deposition process continue to achieve this goal [48,49].

#### 2.2 Short channel effects

In CMOS transistors, the short-channel effect is evident when the channel length in the MOSFET is scaled down close to the depletion width of the source and drain junctions [50-52]. With aggressive technology scaling to improve performance, addressing the detrimental short-channel effects (SCE) caused by shrinking channel lengths has been a focus of MOSFET scaling. The introduction of the 3D FinFET transistor structure at the 16nm technology node is mainly to overcome this short-channel effect caused by CMOS scaling. These effects include drain-induced barrier reduction, velocity saturation, quantum confinement, and hot carrier degradation. Since their introduction in 1959, field-effect transistors (FETs) have been built primarily in the silicon plane. In 2012, at the 20nm node, to maintain the scaling path of Moore's Law, especially in suppressing the short channel problem, the industry made the first transition from "planar" MOSFET to Fin Field Effect Transistor (FinFET) architecture. Additionally, in 2020, to continue enabling CMOS scaling and overcoming the SCE, the semiconductor industry has migrated from FinFET to gate-all-around(GAA) nanosheet transistor structures [53, 54] at the 2nm technology node.

#### 2.2.1 The "short channel" definition

Lg is often used to denote the physical length of a CMOS transistor. The actual length of channel L is not equal to Lg, but Lg minus the gate and S/D overlap width. The overlap width of gate and S/D is derived from dopant diffusion and thus its control is related to the epitaxial S/D and annealing process. The gate lengths Lg > L and L always track Lg

(Figure 2.3(a)). Still, the difference (Lg - L) cannot be precisely quantified because the asymptotic profile of the lateral doping profile has no well-defined interface. The term short channel effect originates because CMOS scaling all involves more or less channel length scaling. And every channel length reduction always brings unwanted effects such as DIBL.

#### 2.2.2 Drain-induced-barrier-lowering (DIBL)

Drain-Induced Barrier Lowering (DIBL) is a special effect that occurs only in short channels with high drain voltages. Simply put, short channel lengths lead to crosstalk between source and drain. This can be explained by the fact that when a high positive voltage is applied to the drain, the depletion region formed around the drain and its thickness extends into the channel region, resulting in less charge near the gate requiring a smaller inversion voltage. The whole effect can also be explained by shortening the equivalent channel length and thus lowering the threshold voltage (Vt). The decrease in Vt is due to the penetration of the channel by the high drain electric field at high drain voltages, thus reducing the barrier height of the channel carriers (Figure 2.3) [55]. As a result, the injected carriers from the source to the channel increase significantly and lead to undesirable off-leakage currents. This threshold voltage effect is negligible for long-channel devices. To improve gate control of an increasingly shorter channels, the semiconductor industry has migrated from single-gate planar transistor structures to 3D transistor structures with multiple gates to enhance short-channel control.

Figure 2.3 Illustration of drain-induced-barrier-lowering (DIBL) [55]

Innovations in transistor architectures, such as FinFETs and gate-all-around (GAA) nanosheet FETs, can reduce the DIBL effect due to a higher level of gate control over the channel. This control comes from the fact that the potentially depleted region is bounded by the fin itself and does not extend into the body. FinFETs or GAA FETs are based on gates surrounding the transistors' source/drain and body regions (diffusions). Instead of just penetrating from the top like a planar gate, the channel can fully be depleted because the electric field is in all directions, including the top and sides of a FinFET or all around the GAA. This allows for better current control and maximizes channel controllability. The result is high power efficiency. The difference between FinFETs and GAA FETS transistor structures is shown in Figure 2.4 [53, 54].

Figure 2.4 FinFET vs gate-all-around (GAA) nano-sheet transistor [53, 54].

#### 2.3 3D FinFET and Nano-Sheet-Transistor structures

In a FinFET structure, the channel between the source and drain is fin-shaped. Compared to planar transistors, the gates are in contact with the fins on both sides and on the upper side, respectively, thus providing better control over the channel formed within the fins, so **FinFETs** greatly help with current leakage [56]-[58]. Since then, FinFET fin heights have increased to achieve higher device drive currents in the same footprint. This is significantly different from today's designs, where the gate stack is placed directly over the channel region. A larger area must be occupied in the planar structure to amplify the drive current through the gate width.

However, the increase in the height of the fin makes the formation of the source-drain junction impossible [59]-[61]. Due to the shadowing effect caused by the narrow Gate-to-Gate and Fin-to-Fin spacing, the directly radiated ions can only radiate orthogonally from a zero-degree angle. However, a fin height of about 50 nm cannot be achieved by ion implantation alone because the lateral ion distribution will be too large, and the ratio of the vertical to the lateral depth of ions is about two to one, resulting in a short channel problem [59], [62]- [64]. Section 2.4 will review and discuss the shadowing effect [59]-[61] of oblique ion implantation in 3D transistor structures.

The FinFET roadmap appears to be running out of steam as scaling technology is pushed beyond 3nm [66]-[68]. The widely adopted technology beyond FinFETs will be stacked nanosheet gates all around transistors. The gate all around or GAA transistor is an improved transistor structure where the gate contacts the channel from top & bottom, left, and right in four directions for a more aggressive transistor scaling application [69]-[73]. Such transistors are called gate-all-around nano-sheet-transistor field-effect

transistors (GAA NS FETS), and different variants of structures have been proposed [74, 75].

Early developments in GAA devices employed vertically stacked nanosheets. The number of nanosheets depends on the transistor application. Power-saving applications typically require only two sheets, while high-speed applications require three to four sheets. They consist of individual horizontal sheets surrounded by gate material on all sides. It achieves better-improved channel control than the tri-gate control of FinFETs. While FinFETs require multiple fins side-by-side to achieve net higher currents, the current-carrying capacity of GAA transistors is increased by stacking multiple nanosheets vertically, with the gate material wrapped around the channel. The CD width and thickness of the nanosheets can be flexibly adjusted and scaled according to the desired electrical properties of the selected components [76, 77]. However, as with fins, sheet widths and pitches will continue to shrink as technology evolves and our ability to print finer feature sizes continues to improve. At extreme scale conditions, the sheets may be about the same width as they are thick, in which case their structures would resemble nanowires.

It is worth noting that nanosheets may be conceptually simple in structure, but they pose great challenges to conventional CMOS fabrication processes [75, 78]. GAA nano sheet fabrication begins with the deposition of periodic superlattice SiGe/Si layers. Depending on the number of silicon sheets required, for example, three sheets require three periodically stacked SiGe/Si to be patterned (Figure 2.5). Due to etch-induced patterning effects, different sheet CD thicknesses are often observed at the top and bottom and cause severe device variation problems. Nano sheets FET fin patterning techniques are very similar to FinFETs, except that the inner spacers must be recessed in the SiGe

section before forming. The inner spacer CD is used to isolate the source-drain (S/D) from the gate, and it determines the overlap length between the gate and the S/D. Physically, it controls the source-drain extension dopant profile as well as the metal gate CD width. Electrically, it affects the series resistance and short-channel control performance because CD couples to the metal gate CD. That is, internal spacers play a very central role in nanosheet fabrication. Other processes, such as S/D epitaxy, also face challenges of the ground area is getting smaller, which the epitaxy often is smaller and affects the S/D conductivity.

After FinFET, GAA transistors possibly evolve into nanowires [79,80]. According to the currently available roadmap, these GAA-like structures will continue to be used in entire 3D transistor technology nodes. Transistor structures have undergone a long evolution from early planar structures to FinFET, GAA nanosheets. Those researchers who pioneered transistor innovations in the early days will be thrilled and honored with the impact they brought to the evolution of semiconductor manufacturing and deepening human civilization. People look forward to seeing what new end applications and capabilities will come with gate-all-around transistors.

Figure 2.5 NSFET process flow. (a) to (b) periodic Si/SiGe superlattice deposition and fin patterning, (c) to (e) polysilicon deposition and patterning followed by internal spacer etch and formation, (e) source-drain epitaxy formation, (f) Deposition of high-k dielectric and metal gate after etch process to remove polysilicon dummy gate. [75, 78].

In addition to GAA nanosheets, transistor structures such as GAA forksheet and more advanced complementary field effect transistor (CFET) architectures have been developed in recent years. As shown in Figure 2.6, the Imec roadmap showcases more than a decade of continuous logic expansion based on innovations in new transistor structures. At the N2 technology node, Imec demonstrated the transition to Gate-All-Around (GAA) nanosheets. Samsung is introducing GAA nanosheets for its 3nm node, and Intel and TSMC announced GAA nanosheets for 2nm (Intel 20A). After two generations of nanosheets, Imec transitioned to Forksheet. Fork sheets are a variant of nanosheets that reduce the orbital height of the battery. Two generations after Forksheet, Imec introduced CFETs. Intel and TSMC also have a lot of forward-looking evaluation

work going on with CFETs.

Figure 2.6 IMEC CMOS scaling technology roadmap presented by IMEC CEO Luc Van den hove at Marriott Marquee's technology forum (2022)

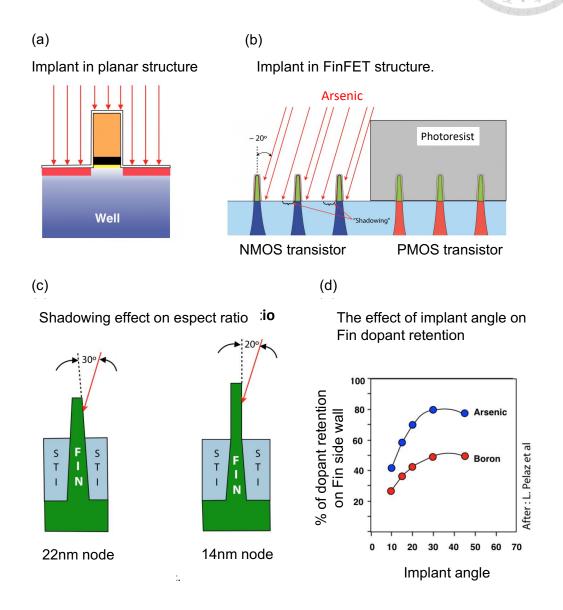

# 2.4 Challenge of junction formation in 3D structure devices

The 3D nature of FinFET and GAA transistor structures all present a unique set of manufacturing issues that can make yielding these devices challenging. This is especially true for extension implants that are in place before the formation of the nitride spacer, as shown in Figure 2.7(a), (b) [81,82]. In planar devices, extension implants are achieved by implanting dopants on both sides of the gate electrode at a 90-degree angle to the silicon surface (see Figure 2.7(a)). However, since the Fin channel in a FinFET device is perpendicular to the silicon surface, this methodology is not an option to avoid lateral over-diffusion. Instead, an angled implant is used, usually at a steep angle to the top and sides of the fin, as shown in Figure 2.5(b), 2.5(c). The problem with extension at such a steep angle is that a large percentage of the dopant is not retained on the fin but bounces

off. The relationship between the extended implant angle and the dopant remaining on the sidewalls is shown in Figure 2.5(d). As shown in this figure, the steeper the implant angle, the less dopant remains on the sidewalls of the fin.

Figure 2.7 Ion implant shadowing effect (a) conventional extended ion implantation in planar transistor structure, (b) angled ion implantation in FinFET structure due to shadowing effect of 3D fin structure and additional photoresist height, (c) the shadowing effect on the shape of the fin and the aspect ratio of the trench, (d) The effect of implantation angle on fin dopant retention [81, 82].