# 國立臺灣大學理學院物理學研究所

# 碩士論文

Department of Physics

College of Science

National Taiwan University

Master Thesis

以電漿輔助化學氣相沉積外延高品質鍺薄膜 High Quality Germanium Thin Film by PECVD

# 賴俊佑 Jyun-You Lai

指導教授:陳永芳 博士

Advisor: Yang-Fang Chen, Ph.D.

共同指導教授:陳賜原 博士

Co-Advisor: Szu-Yuan Chen, Ph.D.

中華民國 111 年 3 月 March, 2022

# 國立臺灣大學碩士學位論文口試委員會審定書

以電漿輔助化學氣相沉積外延高品質鍺薄膜 High Quality Germanium Thin Film by PECVD

本論文係賴俊佑君 (r08222063) 在國立臺灣大學物理學所完成之碩士學位論文,於民國 111 年 1 月 25 日承下列考試委員審查通過及口試及格,特此證明

| 口試委員: | 陳賜原 约30 考 | (簽名) |

|-------|-----------|------|

|       | (指導教授)    |      |

|       | 林丽结       |      |

|       | }         |      |

|       |           |      |

|       |           |      |

|       |           |      |

# 中文摘要

這項實驗中使用自製的電漿輔助化學氣相沉積系統,透過四氯化鍺蒸氣與氫原子之間的反應,讓單晶鍺薄膜生長在矽基板表面;為了達到高結晶品質、低雜質含量、高薄膜鍍率以及低表面粗糙度等目標,我們對生長溫度、氣體流量、射頻功率和處理步驟進行了優化。

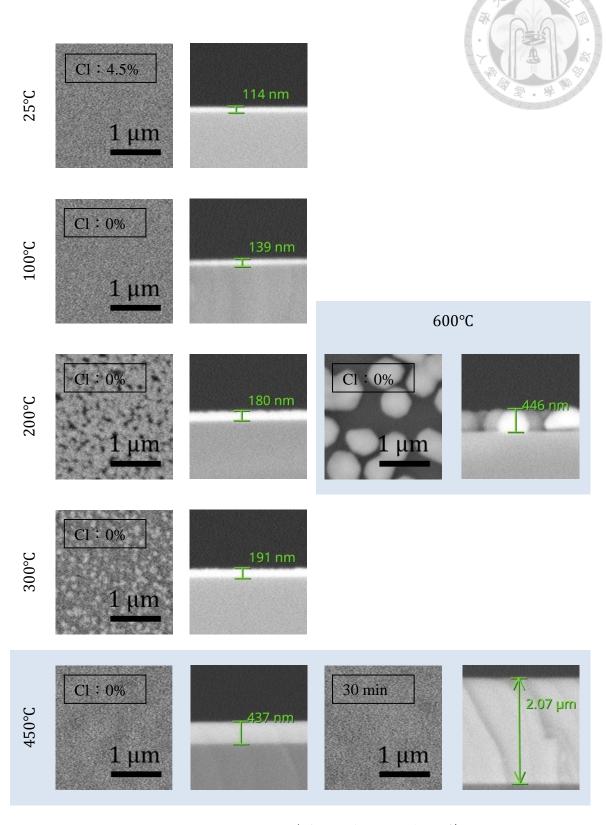

對結晶品質而言,生長溫度是非常重要的因素,室溫生長的鍺薄膜呈現非晶態,而生長溫度在100~600℃之間呈現單晶態;450℃時結晶品質顯著提升,600℃時結晶品質顯著降低,這種結晶行為推測受到四氯化鍺蒸氣與氫原子之間的反應機制所影響,和氫的脫附現象也有關聯。

而生長溫度也會影響雜質脫附,室溫生長的鍺薄膜有氣殘留,但生長溫度高於 100°C 的情況下幾乎完全脫附,其含量低於 EDX 的檢測極限;而生長溫度低於 300°C 的鍺薄膜有氫殘留,並在薄膜生長後或是後續退火中造成薄膜剝落,但生長溫度高於 450°C 的情況下幾乎完全脫附,在薄膜生長後或是後續退火中皆不會發生剝落。

氣體流量、射頻功率和處理步驟皆會改變四氯化鍺蒸氣和氫原子在反應腔體中的濃度,對薄膜鍍率和表面粗糙度而言是非常重要的因素;低氣體流量或低射頻功率的情況下,鍺薄膜容易受到來自起泡器和氣體管線中水氣或氧氣的影響,導致鍺薄膜被蝕刻並造成表面粗糙化;適當生長參數下可以降低其影響,並有效降低表面粗糙度。

電漿輔助化學氣相沉積所生長的單晶鍺薄膜在維持低雜質含量(低於 EDX 的檢測極限)、高薄膜鍍率(78 nm/min)和低均方根粗糙度(0.786 nm)的情況下,線性缺陷密度約為  $10^4 \text{ cm}^{-2}$ ;所製造的 700 nm 鍺薄膜光偵測器之暗電流密度以及響應率為  $4.2 \cdot 10^{-4} \text{ A/cm}^2$  和 0.08 A/W (@ 1550 nm)。

關鍵字:單晶鍺薄膜、電漿輔助化學氣相沉積、四氯化鍺、低線性缺陷密度

## **ABSTRACT**

In this study, germanium thin films epitaxially deposited on silicon substrates by using a home-made plasma-enhanced chemical vapor deposition system (PECVD) with GeCl<sub>4</sub>/H<sub>2</sub> as precursors. We optimized the growth temperature, gas flow rate, RF power, and operating procedures to achieve a impurity-free and high-quality monocrystalline germanium thin film with a low surface roughness and high deposition rate.

The growth temperature is important for the crystalline quality. For the growth temperature in range of 100~600 °C, the germanium thin film was monocrystalline. The crystalline quality significantly improved at 450 °C, but was reduced at 600 °C. This behavior may be attributable to the desorption of hydrogen and the reaction mechanism between germanium tetrachloride and hydrogen atoms.

The growth temperature is also important for the the desorption of impurity. Under a growth temperature of approximately 25 °C, chlorine was present in the germanium thin film, but no chlorine was detected for a growth temperature above 100 °C. With a growth temperature below 300 °C, a high hydrogen content remained in the germanium thin film, which can lead to blistering, but no blistering was detected after growth or during post growth annealing for a growth temperature above 450 °C.

The Gas flow rate, RF power, and operating procedures can change the concentration of germanium tetrachloride vapor and hydrogen atoms in the reaction chamber, which are important for the deposition rate and surface roughness. For a low gas flow rate or low RF power, the germanium thin film can be easily etched by oxygen and water vapor which come from the bubbler and gas pipelines. This etching can cause

a rough surface, but for appropriate growth parameters, a low root mean square (RMS) of surface roughness can be achieved.

For the monocrystalline germanium thin film grown by PECVD with a low impurity content (below the detection limit of energy-dispersive X-ray spectroscopy), low RMS surface roughness (0.786 nm) and high deposition rate (78 nm/min), the threading dislocation density (TDD) was approximately  $10^4$  cm<sup>-2</sup>. The Dark current density and responsivity of a 700 nm germanium thin film PIN photodetector were  $4.2 \cdot 10^{-4}$  A/cm<sup>2</sup> and 0.08 A/W (@ 1550 nm).

**Keywords:** monocrystalline germanium thin film, plasma-enhanced chemical vapor deposition, germanium tetrachloride, low threading dislocation density

# **CONTENTS**

| 口試委員會審定       | 書        |      |

|---------------|----------|------|

|               |          | 0.00 |

| ABSTRACT      |          | iii  |

| CONTENTS      |          | v    |

| LIST OF FIGUR | ES       | vii  |

| LIST OF TABLE | ES       | x    |

| Chapter 1 緒   | 論        | 1    |

| 1.1 研究        | 動機       | 1    |

| 1.2 绪薄        | 膜進展      | 2    |

| 1.3 鍺薄        | 膜光偵測器進展  | 4    |

| 1.4 四氯        | 化鍺進展     | 5    |

| 1.5 研究        | 目標       | 5    |

| Chapter 2 實   | 驗細節      | 6    |

| 2.1 元件        | 設計       | 6    |

| 2.1.1         | 光偵測器結構   | 6    |

| 2.1.2         | 光電二極體結構  | 7    |

| 2.1.3         | 歐姆接觸     | 8    |

| 2.1.4         | 表面鈍化     | 9    |

| 2.1.5         | 元件結構     | 9    |

| 2.1.6         | 響應率      | 10   |

| 2.1.7         | 暗電流密度    | 11   |

| 2.2 元件        | 製造       | 12   |

| 2.2.1         | 矽基板清洗    | 12   |

| 2.2.2         | 離子佈植     | 13   |

| 2.2.3         | 绪薄膜蝕刻    | 14   |

| 2.2.4         | 二氧化矽薄膜塗佈 |      |

| 2.2.5         | 二氧化矽薄膜蝕刻 |      |

| 2.2.6         | 蒸鍍電極     |      |

|         | 2.2.7 | 表面圖案化              |    |

|---------|-------|--------------------|----|

|         | 2.2.8 | 溶液與儀器              |    |

| 2.3     | 主要    | 實驗儀器               | 23 |

|         | 2.3.1 | 電漿輔助化學氣相沉積 (PECVD) | 23 |

|         | 2.3.2 | 掃描式電子顯微鏡 (SEM)     | 26 |

|         | 2.3.3 | X 光繞射儀 (XRD)       | 28 |

|         | 2.3.4 | 元件測量平台             | 30 |

| Chapter | 3 結   | ·果與討論              | 34 |

| 3.1     | 雜質    | 含量                 | 34 |

| 3.2     | 結晶    | 品質                 | 37 |

| 3.3     | 反應    | 機制                 | 39 |

| 3.4     | 薄膜    | 鍍率                 | 41 |

|         | 3.4.1 | 氣體流量               | 42 |

|         | 3.4.2 | 射頻功率               | 45 |

|         | 3.4.3 | 時間演化               | 48 |

|         | 3.4.4 | 穩態處理               | 51 |

|         | 3.4.5 | 簡化模型               | 55 |

| 3.5     | 表面    | 形貌                 | 57 |

| 3.6     | 線性    | 缺陷密度               | 61 |

| 3.7     | 光偵    | 測器                 | 63 |

| Chapter | 4 結   | - 論                | 65 |

| REFERE  | NCF   |                    | 66 |

# LIST OF FIGURES

| Figure 1.1  | (a)吸收係數對入射光波長關係圖[8],(b)暗電流密度對線性缺陷密度       |

|-------------|-------------------------------------------|

|             | 關係圖[8]。1                                  |

| Figure 1.2  | TEM 影像圖,(1)矽鍺緩衝層[14],(2)直接生長和兩步驟生長[10]。2  |

| Figure 1.3  | TEM 影像圖,1循環熱退火[18],(2)連續光雷射退火[21],(3)縱深比  |

|             | 捕獲[22]。3                                  |

| Figure 2.1  | 光伏效應和光偵測器結構之示意圖[38]。6                     |

| Figure 2.2  | 鍺薄膜光電二極體結構和能帶結構之示意圖[29]。7                 |

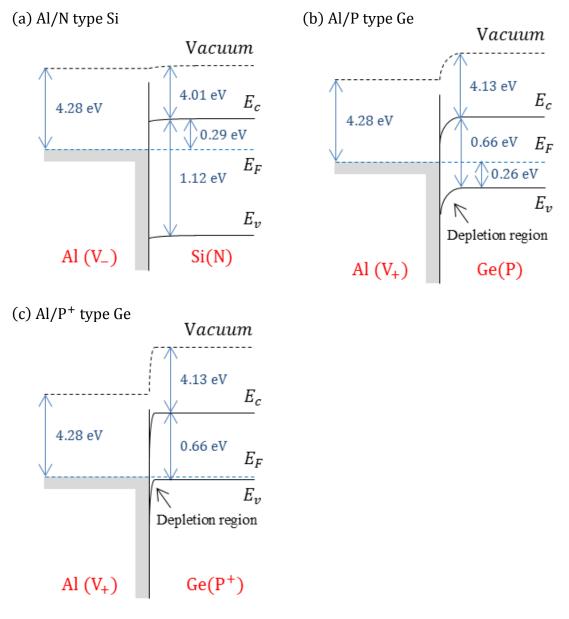

| Figure 2.3  | 鋁/矽介面和鋁/鍺介面的能帶結構示意圖[38]。8                 |

| Figure 2.4  | 元件結構和能帶結構之示意圖。9                           |

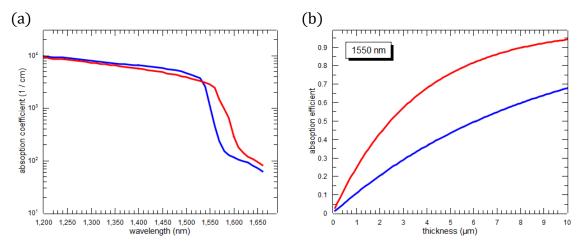

| Figure 2.5  | (a)吸收係數對入射光波長關係圖[42],(b)吸收效率對薄膜厚度關係       |

|             | 圖[42]。10                                  |

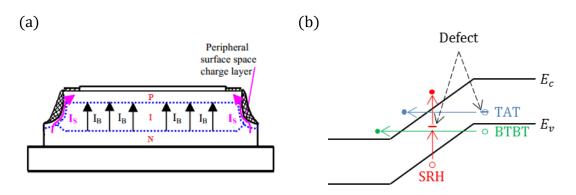

| Figure 2.6  | (a)體洩漏電流和表面洩漏電流之示意圖[44],(b) SRH、TAT和 BTBT |

|             | 洩漏電流之示意圖[45]。11                           |

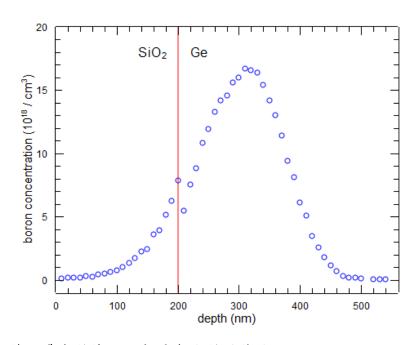

| Figure 2.7  | 掺雜濃度對摻雜深度關係圖(離子佈植)。13                     |

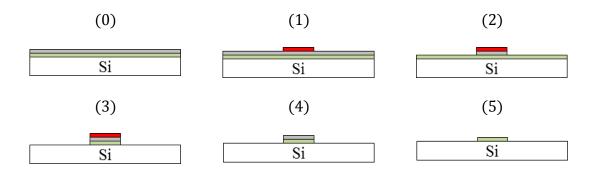

| Figure 2.8  | 各流程示意圖(鍺薄膜蝕刻)。14                          |

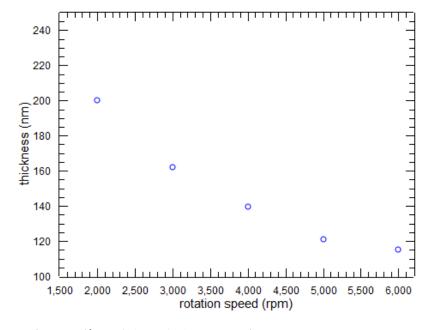

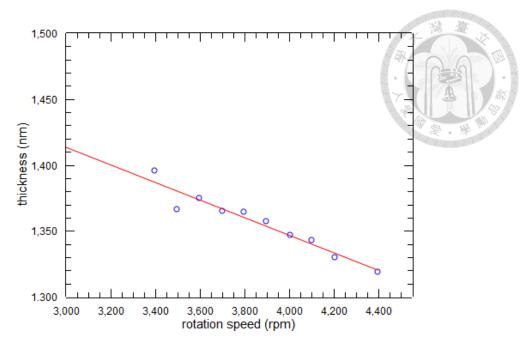

| Figure 2.9  | 二氧化矽薄膜厚度對塗佈轉速關係圖。15                       |

| Figure 2.10 | 各流程示意圖(二氧化矽薄膜蝕刻)。16                       |

| Figure 2.11 | 各流程示意圖(蒸鍍電極)。17                           |

| Figure 2.12 | 各流程示意圖(表面圖案化)。18                          |

| Figure 2.13 | 光阻薄膜厚度對塗佈轉速關係圖。19                         |

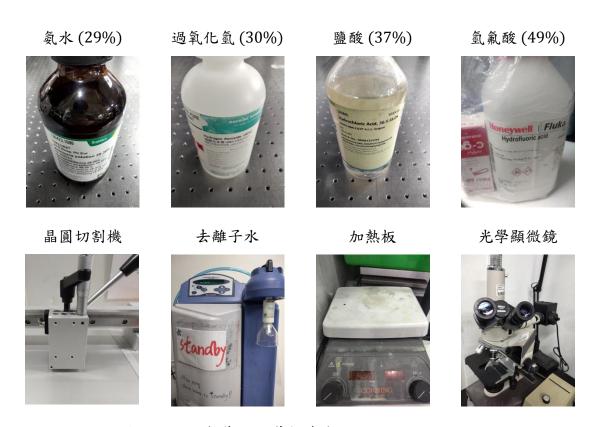

| Figure 2.14 | 所使用的溶液與儀器(矽基板清洗)。19                       |

| Figure 2.15 | 所使用的溶液與儀器(鍺薄膜蝕刻)。20                       |

| Figure 2.16 | 所使用的溶液與儀器(二氧化矽薄膜塗佈)。20                    |

| Figure 2.17 | 所使用的溶液與儀器(二氧化矽薄膜蝕刻)。21                    |

| Figure 2.18 | 所使用的溶液與儀器(蒸鍍電極)。21                        |

| Figure 2.19 | 所使用的溶液與儀器(表面圖案化)。22                       |

| Figure 2.20 | 電漿輔助化學氣相沉積系統的架設示意圖。23                     |

| Figure 2.21 | 反應腔體的架設示意圖。24                             |

| Figure 2.22 | (a)腔體氣壓對氣體流量關係圖,(b)矽基板溫度對供應電壓關係圖    | · 2  |

|-------------|-------------------------------------|------|

| Figure 2.23 | 所使用的溶液與儀器(電漿輔助化學氣相沉積)。              | 25   |

| Figure 2.24 |                                     | 26   |

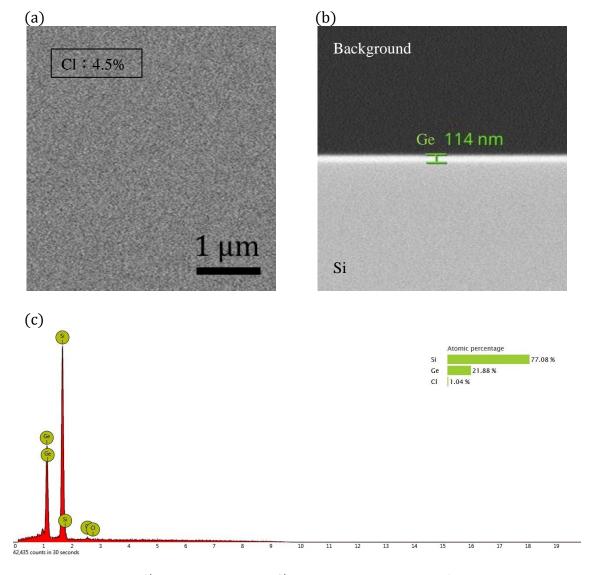

| Figure 2.25 | (a)鍺薄膜頂視圖,(b)鍺薄膜剖視圖,(c)EDX 測量結果。    | 27   |

| Figure 2.26 | X 光繞射儀。                             | 28   |

| Figure 2.27 | XRD 測量結果。                           | 29   |

| Figure 2.28 | 元件測量平台的校正結果(電阻測量)。                  | 30   |

| Figure 2.29 | 元件測量平台的校正結果(響應率測量)。                 | .31  |

| Figure 2.30 | 入射光強度對入射光波長關係圖(元件測量平台)。             | 32   |

| Figure 2.31 | 元件測量平台的架設示意圖。                       | 32   |

| Figure 2.32 | 所使用的各項儀器(元件測量平台)。                   | 33   |

| Figure 3.1  | SEM & EDX 影像圖,各鍍膜參數(改變生長溫度)的薄膜頂視圖和部 | 引視   |

|             | 圖以及 EDX 測量結果。                       | 35   |

| Figure 3.2  | OM 影像圖, 鍺薄膜退火前後的表面形貌。               | 36   |

| Figure 3.3  | 結晶態對生長溫度和薄膜鍍率的關係示意圖[68]。            | 37   |

| Figure 3.4  | 各鍍膜參數(改變生長溫度)的 XRD 測量結果。            | 38   |

| Figure 3.5  | 氫終止的矽基板表面之脫附溫度[71]。                 | 39   |

| Figure 3.6  | 四氯化鍺氫還原的反應機制示意圖。                    | .40  |

| Figure 3.7  | 薄膜鍍率對生長溫度關係圖。                       | .41  |

| Figure 3.8  | SEM 影像圖,各鍍膜參數(改變氣體流量)的薄膜頂視圖和剖視圖。    | 43   |

| Figure 3.9  | 薄膜鍍率對氣體流量關係圖。                       | .44  |

| Figure 3.10 | SEM 影像圖,各鍍膜參數(改變射頻功率)的薄膜頂視圖和剖視圖     | • 46 |

| Figure 3.11 | 薄膜鍍率對射頻功率關係圖。                       | .47  |

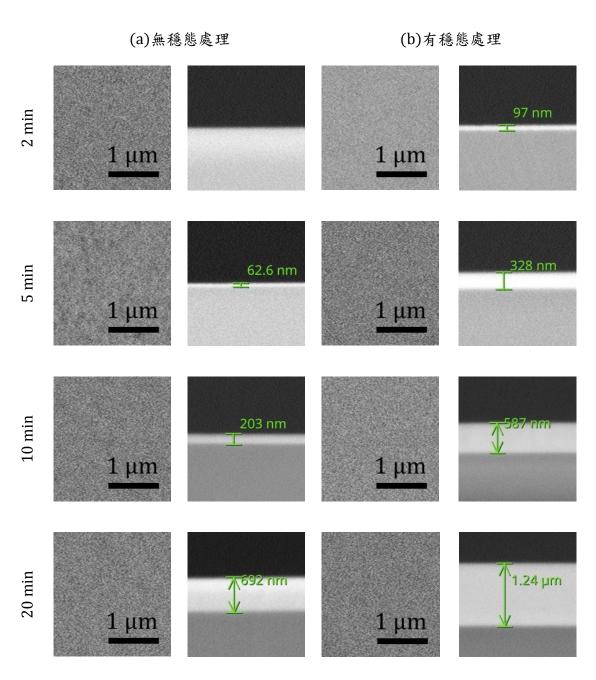

| Figure 3.12 | SEM 影像圖,各鍍膜參數(改變鍍膜時間)的薄膜頂視圖和剖視圖     | • 49 |

| Figure 3.13 | 薄膜鍍率對鍍膜時間關係圖。                       | 50   |

| Figure 3.14 | 4 SEM 影像圖,各鍍膜參數(改變穩態處理步驟)的薄膜頂視圖和音   | 引視   |

|             | 圖。                                  | 52   |

| Figure 3 15 | 蒲 <b>随 箍 恋 對 穩 能 處 理 時 的  </b>      | 53   |

| Figure 3.16 | SEM 影像圖,各鍍膜參數(改變穩態處理時的氣體流量)的薄膜頂  | 視    |

|-------------|----------------------------------|------|

| 国           | ]和剖視圖。                           | 54   |

| Figure 3.17 | 簡化模型所模擬的曲線。                      | 56   |

| Figure 3.18 | SEM 影像圖,各鍍膜參數(改變管線沖洗)的薄膜頂視圖和剖視圖。 | 59   |

| Figure 3.19 | SEM & AFM 影像圖, 鍺薄膜的頂視圖和剖視圖。      | 60   |

| Figure 3.20 | SEM 影像圖,各鍍膜參數使用溶液蝕刻後的表面形貌。       | 62   |

| Figure 3.21 | 所使用的溶液與藥品(線性缺陷密度測量)。             | 62   |

| Figure 3.22 | 元件的能帶結構示意圖。                      | 63   |

| Figure 3.23 | (a)暗電流密度對供應電壓關係圖,(b)響應率對入射光波長關係圖 | 。 64 |

# LIST OF TABLES

| Table 1.1  | 垂直入射的鍺薄膜光偵測器之性能以及所使用的技術。 | .4 |

|------------|--------------------------|----|

| Table 2.1  | 詳細流程以及各參數設定(矽基板清洗)。      | 12 |

| Table 2.2  | 各參數設定(離子佈植)。             | 13 |

| Table 2.3  | 詳細流程以及各參數設定(鍺薄膜蝕刻)。      | 14 |

| Table 2.4  | 詳細流程以及各參數設定(二氧化矽薄膜塗佈)。   | 15 |

| Table 2.5  | 詳細流程以及各參數設定(二氧化矽薄膜蝕刻)。   | 16 |

| Table 2.6  | 詳細流程以及各參數設定(蒸鍍電極)。       | 17 |

| Table 2.7  | 詳細流程以及各參數設定(表面圖案化)。      | 18 |

| Table 2.8  | 各參數設定(XRD 測量)。           | 29 |

| Table 2.9  | 各參數設定(暗電流密度測量)。          | 30 |

| Table 2.10 | 各參數設定(響應率測量)。            | 31 |

| Table 3.1  | 各鍍膜參數設定(改變生長溫度)。         | 34 |

| Table 3.2  | 各鍍膜參數設定(改變生長溫度)。         | 37 |

| Table 3.3  | 各鍍膜參數設定(改變氣體流量)。         | 12 |

| Table 3.4  | 各鍍膜參數設定(改變射頻功率)。         | 15 |

| Table 3.5  | 各鍍膜參數設定(改變鍍膜時間)。         | 18 |

| Table 3.6  | 各鍍膜參數設定(改變穩態處理步驟)。       | 52 |

| Table 3.7  | 各鍍膜參數設定(改變穩態處理時的氣體流量)。   | 53 |

| Table 3.8  | 各鍍膜參數設定(改變管線沖洗)。         | 58 |

| Table 3.9  | 鍍膜參數設定(均方根粗糙度測量)。        | 50 |

| Table 3.10 | 各鍍膜參數設定(線性缺陷密度測量)。       | 51 |

| Table 3.11 | 鍍膜參數設定(光偵測器)。            | 53 |

# Chapter 1 緒論

# 1.1 研究動機

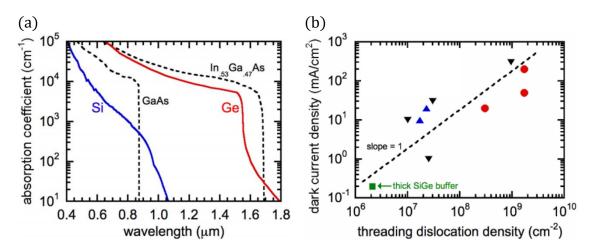

光纖通訊中的近紅外雷射和光偵測器,常使用生長在磷化銦基板上的 III-V 族材料製造而成[1],由於這些材料不僅成本昂貴且具有毒性,尋找新材料來解決這些問題成為了熱門領域;而鍺薄膜在近紅外波段中尚可接受的吸收係數以及與矽製程兼容的優勢[2],使其成為替代 III-V 族材料的候選之一;未來還可以應用在積體光路[2][3],或是作為其他材料在矽基板上生長所需的襯底,例如: GaAs、GeSn 等[4][5][6][7]; Figure 1.1(a)是吸收係數對入射光波長關係圖[8],其中鍺的截止波長約在 1.550 μm,能應用在近紅外波段的光纖通訊(1.3~1.6 μm)。

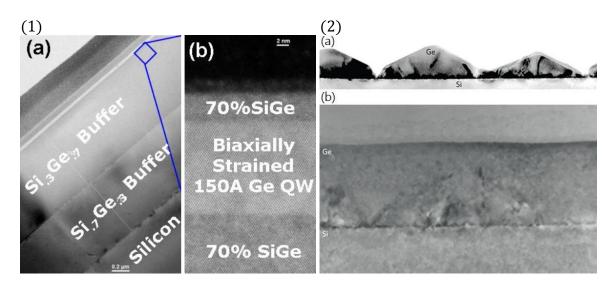

然而鍺的晶格常數比矽大了 4.2%,因此在矽基板表面直接生長的鍺薄膜會累積壓縮應力,並藉由形成晶格錯位或是以島狀/層狀生長模式來釋放壓縮應力 [9][10][11][12];前者會形成線性缺陷導致響應率降低或暗電流密度增加,後者會形成粗糙的表面對後續製程造成影響[8][10][11][12],近年來提出了許多生長或退火方法改善這些問題;Figure 1.2(2)(a)是直接生長下鍺薄膜的 TEM 影像圖[10],所造成的島狀/層狀生長模式會形成粗糙的表面,並有許多線性缺陷貫穿鍺薄膜,Figure 1.1(b)是暗電流密度對線性缺陷密度關係圖[8],其中暗電流密度和線性缺陷密度呈現正相關。

Figure 1.1 (a)吸收係數對入射光波長關係圖[8],(b)暗電流密度對線性缺陷密度關係圖[8]。

## 1.2 鍺薄膜進展

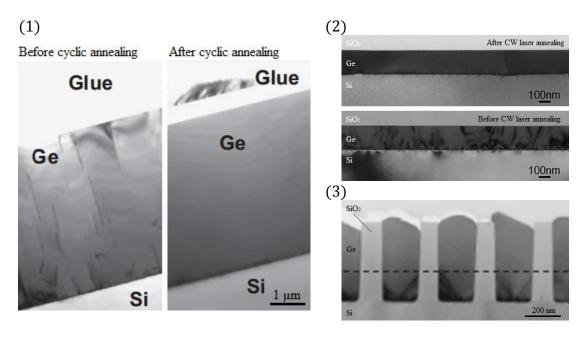

目前化學氣相沉積常使用四氫化鍺氣體作為前驅物,藉由熱解反應在矽基板表面生長鍺薄膜,透過矽鍺緩衝層[13][14]、兩步驟生長[15][16][17][18]、循環熱退火[15][16][18]、連續光雷射退火[19][20][21]或縱深比捕獲[22][23][24]等技術避免島狀/層狀生長模式並降低線性缺陷密度;Figure 1.2 以及Figure 1.3 是各種生長或退火技術下鍺薄膜的TEM影像圖,貫穿鍺薄膜的黑色線條為線性缺陷。

矽鍺緩衝層能避免島狀/層狀生長模式發生並降低線性缺陷密度;在鍺薄膜生長前預先引入矽鍺緩衝層,藉由緩慢增加矽鍺緩衝層中鍺的含量,緩解晶格常數差異所導致的壓縮應力[11][12];透過這種方式能將線性缺陷密度降至 2.1·10<sup>6</sup> cm<sup>-2</sup> [13],Figure 1.2(1)是使用矽鍺緩衝層技術下鍺薄膜的 TEM 影像圖[14],通常需要厚度達數微米的矽鍺緩衝層,並配合化學機械研磨降低表面粗糙度,因此在應用上受到限制。

兩步驟生長也能避免島狀/層狀生長模式發生並降低線性缺陷密度;在鍺薄膜生長時分為低溫生長(300~400°C)和高溫生長(600~700°C),先低溫生長約30~60 nm 的種子層用來限制島狀生長發生(由於低溫下表面遷移率較低),再用高溫生長以提升薄膜鍍率和結晶品質[10][11][12][15];透過這種方式能將線性缺陷密度降至 $10^8\sim10^9$  cm $^{-2}$  [10],Figure 1.2(2)(b)是使用兩步驟生長技術下鍺薄膜的TEM 影像圖[10],許多線性缺陷侷限在種子層中。

Figure 1.2 TEM 影像圖, (1)矽鍺緩衝層[14], (2)直接生長和兩步驟生長[10]。

循環熱退火能進一步降低線性缺陷密度;在鍺薄膜生長後重複數次的低溫退火(700~800°C)和高溫退火(900~1000°C),由於矽基板和鍺薄膜之間熱膨脹係數的差異,退火過程中會產生熱應力並驅使線性缺陷位移並湮滅(位移至邊界而湮滅或是向量相反的線性缺陷互相湮滅)[15][19];透過這種方式能將線性缺陷密度降至  $10^7 \sim 10^8$  cm<sup>-2</sup> [15], Figure 1.3(1)是使用循環熱退火技術下鍺薄膜的 TEM 影像圖[18],退火後線性缺陷密度明顯降低。

連續光雷射退火也能進一步降低線性缺陷密度;在鍺薄膜生長後使用數次的雷射退火,退火過程中會產生熱應力並驅使線性缺陷位移並湮滅[15][19];雷射峰值溫度略高於鍺薄膜熔點時,側向再結晶能進一步降低線性缺陷密度[21];透過這種方式能將線性缺陷密度降至  $10^6 \sim 10^7$  cm<sup>-2</sup> [21], Figure 1.3(2)是使用連續光雷射退火技術下鍺薄膜的 TEM 影像圖[21],退火後線性缺陷密度明顯降低。

循環熱退火和連續光雷射退火需要較高的處理溫度,降低了矽製程兼容的可行性,而縱深比捕獲使用另一種方式讓線性缺陷湮滅;在鍺薄膜生長前預先引入圖案化的二氧化矽,讓線性缺陷能夠位移至邊界而湮滅[10][11][12][22];透過這種方式能將線性缺陷密度降至 1.6·10<sup>6</sup> cm<sup>-2</sup> [23], Figure 1.3(3)是使用縱深比捕獲技術下鍺薄膜的 TEM 影像圖[22],能完全湮滅斜向貫穿的線性缺陷。

Figure 1.3 TEM 影像圖,(1)循環熱退火[18],(2)連續光雷射退火[21],(3)縱深 比捕獲[22]。

# 1.3 绪薄膜光偵測器進展

由於尚未有研究將連續光雷射退火和縱深比捕獲等技術應用在鍺薄膜光偵測器的製造上,所以這裡總結了使用化學氣相沉積(CVD)、電漿輔助化學氣相沉積(PECVD)以及分子束磊晶(MBE)等系統,配合矽鍺緩衝層、兩步驟生長以及循環熱退火等技術所製造的鍺薄膜光偵測器。

Table 1.1 是垂直入射的鍺薄膜光偵測器之性能以及所使用的技術,近 10 年主要研究集中在鍺薄膜光偵測器的波導集成[3][25];其中處理溫度較低的鍺薄膜光偵測器與矽製程兼容的可行性較高,在低溫生長且不需要後續退火的情況下,我們所製造的鍺薄膜光偵測器之暗電流密度和響應率的表現優異。

| 發表年份      | 薄膜厚度 | 響應率         | 暗電流密度               | 使用技術                     |

|-----------|------|-------------|---------------------|--------------------------|

| 1998 [13] | 1500 | 0.13 @ 1300 | $1.5 \cdot 10^{-4}$ | CVD<br>矽鍺緩衝層             |

| 2001 [26] | 1000 | 0.55 @ 1300 | $3 \cdot 10^{-2}$   | CVD<br>兩步驟生長<br>循環熱退火    |

| 2004 [27] | 200  | 0.02 @ 1300 | $2 \cdot 10^{-4}$   | MBE<br>(低溫生長)            |

| 2007 [28] | 1000 | 0.2 @ 1550  | $1\cdot 10^{-3}$    | PECVD<br>兩步驟生長<br>循環熱退火  |

| 2009 [29] | 1000 | 0.04 @ 1550 | $4.6 \cdot 10^{-3}$ | PECVD<br>(低溫生長)          |

| 2009 [29] | 1000 | 0.4 @ 1550  | $4.1 \cdot 10^{-5}$ | PECVD<br>(低溫生長)<br>循環熱退火 |

| This work | 700  | 0.08 @ 1550 | $4.2 \cdot 10^{-4}$ | PECVD<br>(低溫生長)          |

| (單位)      | nm   | A/W @ nm    | cm <sup>-2</sup>    | -                        |

Table 1.1 垂直入射的鍺薄膜光偵測器之性能以及所使用的技術。

## 1.4 四氯化鍺進展

目前化學氣相沉積常使用四氫化鍺氣體作為前驅物,藉由熱解反應在矽基板表面生長鍺薄膜;但由於四氫化鍺氣體的高危險性,我們使用較安全的四氯化鍺液體取代,藉由氫還原反應在矽基板表面生長鍺薄膜;許多研究也使用四氯化鍺液體作為前驅物,例如:透過化學氣相沉積在具有鍺種子層的矽基板上生長鍺薄膜[30][31],透過化學氣相沉積在矽鍺基板表面生長鍺薄膜[32],透過電漿輔助化學氣相沉積在鎢電極上生長鍺晶體[33],透過電漿輔助化學氣相沉積合成鍺奈米晶體,並在矽基板表面旋轉塗佈奈米晶體鍺薄膜[34][35][36] [37]。

由於受到四氯化鍺蒸氣進行氫還原反應的成長機制所限制[30],尚未有研究 能直接在矽基板表面生長鍺薄膜;而這項實驗中透過自製的電漿輔助化學氣相沉 積系統,成功實現在矽基板表面直接生長單晶鍺薄膜,並首次將這種方法應用在 鍺薄膜光偵測器的製造。

## 1.5 研究目標

為了提高鍍膜系統的安全性,我們使用四氯化鍺液體作為前驅物;為了降低 製程複雜度,這項實驗使用自製的電漿輔助化學氣相沉積系統生長鍺薄膜,以解 決四氯化鍺蒸氣無法直接在矽基板表面生長鍺薄膜的問題;並對生長溫度、氣體 流量、射頻功率和處理步驟等各項鍍膜參數進行了優化。

為了提升鍺薄膜光偵測器的性能,必須提高結晶品質並降低雜質含量,以避免線性缺陷或是薄膜雜質造成響應率降低或是暗電流密度增加;而表面粗糙度和薄膜鍍率也需要維持在適當水平,以避免對後續製程造成影響,並減少鍍膜所需的時間。

綜合以上所述,我們希望在矽基板表面直接生長高品質單晶鍺薄膜,並達到線性缺陷密度低於 10<sup>6</sup> cm<sup>-2</sup>、雜質含量低於 EDX 的檢測極限、均方根粗糙度低於 1 nm 以及薄膜鍍率高於 40 nm/min 等目標;並將所生長的單晶鍺薄膜製作成鍺薄膜光偵測器,而鍺薄膜光偵測器能夠達到暗電流密度低於 10<sup>-5</sup> A/cm<sup>2</sup> 以及響應率高於 0.8 A/W (@ 1550 nm) 等目標。

# Chapter 2 實驗細節

## 2.1 元件設計

#### 2.1.1 光偵測器結構

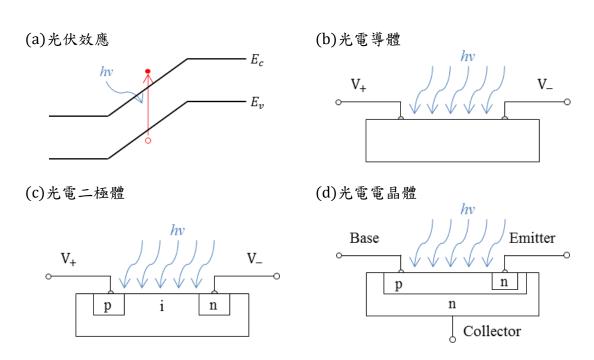

Figure 2.1(a)是光伏效應示意圖,位於價帶的電子在吸收入射光能量後躍遷至 導帶並形成電子電洞對,這些電子電洞對在電場的作用下所形成的電流被稱為光 電流。

Figure 2.1(b)(c)(d)是光電導體、光電二極體和光電電晶體結構示意圖[38]; 光電導體利用正負電極施加電場收集光伏效應所產生的光電流,但缺點是暗電流 較高;光電二極體利用內電場收集光電流,反向偏壓降低暗電流,特殊設計下能 透過雪崩效應讓光電流產生增益並提高響應率;光電電晶體利用內電場收集光電 流,透過電晶體的功能讓光電流產生增益並提高響應率。

在斟酌元件性能和製程複雜度後,我們選擇光電二極體結構製造鍺薄膜光偵 測器。

Figure 2.1 光伏效應和光偵測器結構之示意圖[38]。

#### 2.1.2 光電二極體結構

Figure 2.2 是鍺薄膜光電二極體結構和能帶結構之示意圖[29], (a)水平鍺PIN 結構, (b)垂直鍺PIN結構, (c)垂直鍺PI矽N結構, (d)垂直鍺NI矽P結構;由於 (a)(b)結構需要進行兩次離子佈植或兩次薄膜生長,為了降低製程複雜度,我們 選擇(c)(d)結構;由於兩者在矽/鍺介面間電洞能障的差異,前者光電流收集效率較高,後者暗電流密度較低[29]。

在斟酌元件性能和製程複雜度後,我們選擇垂直鍺(PI)矽(N)結構製造鍺薄膜 光偵測器。

#### (a)水平鍺PIN結構 (b)垂直绪PIN結構 hv hv $V_{-}$ $V_{-}$ $V_{+}$ $V_{+}$ Ge(P) Ge(I) Ge(N)Ge(P) Ge(I) Ge(N) (c)垂直鍺PI矽N結構 (d)垂直绪NI矽P結構 $V_{-}$ $V_{-}$ $V_{+}$ Ge(P) Ge(I) Si(N) Ge(N) Ge(I) Si(P) Vacuum Vacuum 4.13 eV 4.01 eV $E_c$ 4.01 eV 0.66 eV 0.29 eV 4.13 eV 0.26 eV 1.12 eV $E_F$ 1.12 eV $E_{F}$ () 0.26 eV 0.29 eV 0.66 eV $E_v$ Ge(P) Ge(I) Si(P) Ge(I) Si(N) Ge(N)

Figure 2.2 鍺薄膜光電二極體結構和能帶結構之示意圖[29]。

#### 2.1.3 歐姆接觸

為了降低製程複雜度,我們統一使用鋁電極接觸 N type Si 和 P type Ge ,前者功函數正好匹配能形成歐姆接觸,但後者功函數不匹配無法形成歐姆接觸;因此我們對 P type Ge 進行重摻雜,重摻雜後空乏區寬度縮小,電流能透過穿隧效應導通並形成歐姆接觸[38];Figure 2.3 是鋁/矽介面和鋁/鍺介面的能帶結構示意圖[38],(a) Al/N type Si,(b) Al/P type Ge,(c) Al/P+ type Ge ,其中(a)(c)介面能夠形成歐姆接觸。

Figure 2.3 鋁/矽介面和鋁/鍺介面的能帶結構示意圖[38]。

#### 2.1.4 表面鈍化

由於表面懸空鍵可能會形成複合中心,捕獲電子或電洞導致響應率降低 [39],或是形成表面洩漏電流的通道導致暗電流密度增加[40];因此我們在鍺薄膜 和矽基板表面塗佈二氧化矽薄膜用來鈍化表面[41],而鍺薄膜和矽基板與鋁電極接觸的區域,使用原生氧化層鈍化表面。

#### 2.1.5 元件結構

Figure 2.4(a)(b)是元件頂視圖和剖視圖之示意圖,其中有鍺薄膜(綠色)、二氧化矽薄膜(灰色)和鋁電極(金色);鍺薄膜生長後經過離子佈植、鍺薄膜蝕刻、二氧化矽薄膜塗佈、二氧化矽薄膜蝕刻和蒸鍍電極等製程,詳細參數請見 2.2 元件製造;Figure 2.4(c)是能帶結構示意圖,使用 N type 矽基板生長鍺薄膜,離子佈植對鍺薄膜進行 P type 重摻雜,蒸鍍鋁作為金屬電極。

## (a)元件表面

#### (b)元件截面

#### (c)能帶結構

Figure 2.4 元件結構和能帶結構之示意圖。

#### 2.1.6 響應率

公式(1)是光電二極體的響應率 R (A/W) 和入射光波長 $\lambda$  (nm)、收集效率 $\eta_c$  (0~100%)、表面反射率 r (0~100%)、吸收係數  $\alpha$  (cm<sup>-1</sup>) 以及薄膜厚度W (cm) 之間的關係[42],其中普朗克常數  $h=6.626\cdot 10^{-34}$  m<sup>2</sup>·kg/s、真空光速 $c=3\cdot 10^8$  m/s、基本電荷  $e=1.6\cdot 10^{-19}$  C。

$$R = \frac{e\lambda}{hc} \cdot \eta_c \cdot (1 - r) \cdot (1 - e^{-\alpha W}) \tag{1}$$

公式(1)中許多因素影響元件的響應率;線性缺陷或是懸空鍵會捕獲電子或電洞導致收集效率降低[42],可以調整生長或退火方法減少線性缺陷和懸空鍵,以提升元件的響應率;表面反射會降低入射光強度,可以利用抗反射膜減少反射光,以提升元件的響應率;吸收係數和薄膜厚度會影響吸收效率 (1-e-aw),可以增加薄膜厚度或是利用張應力提高吸收係數[43](張應力來自矽基板和鍺薄膜之間熱膨脹係數的差異),以提升元件的響應率。

Figure 2.5(a)是吸收係數對入射光波長關係圖[42],其中藍色曲線來自沒有應力的鍺,紅色曲線來自 0.2% 張應力的鍺薄膜;張應力會導致鍺薄膜的能隙變小,截止波長變大,並提高 1550 nm 的吸收係數[43]; Figure 2.5(b)是吸收效率對薄膜厚度關係圖[42],其中藍色曲線來自沒有應力的鍺,紅色曲線來自 0.2% 張應力的鍺薄膜;相同厚度下具有張應力的鍺薄膜在 1550 nm 的吸收效率較高。

Figure 2.5 (a)吸收係數對入射光波長關係圖[42], (b)吸收效率對薄膜厚度關係圖[42]。

#### 2.1.7 暗電流密度

公式(2)是光電二極體的暗電流密度 $J(A/cm^2)$ 和元件半徑D(cm)、表面洩漏電流密度 $J_S(A/cm)$ 以及體洩漏電流密度 $J_B(A/cm^2)$ 之間的關係[40],其中係數4為無量網常數。

$$J = J_{\rm B} + \frac{4}{D} \cdot J_{\rm S} \tag{2}$$

公式(2)中許多因素影響元件的暗電流密度;其中表面洩漏電流是表面懸空鍵所引發的電流洩漏[40],可以透過表面鈍化減少表面懸空鍵或是增加元件半徑,以降低元件的暗電流密度;而體洩漏電流來自反向飽和電流、Shockley-Read-Hall (SRH)洩漏電流、Trap assisted tunneling (TAT) 洩漏電流和 Band-to-band tunneling (BTBT)洩漏電流[40];線性缺陷和懸空鍵可能以 SRH 洩漏或 TAT 洩漏的方式導致暗電流密度增加,可以調整生長或退火方法減少線性缺陷和懸空鍵,以降低元件的暗電流密度;BTBT 洩漏在電場大於  $5\cdot10^8$  V/m 時開始佔主導地位 [40],而這項實驗中鍺薄膜內的電場約為  $5\cdot10^6$  V/m,因此可以忽略不計 BTBT 洩漏所造成的暗電流。

Figure 2.6(a)是體洩漏電流和表面洩漏電流之示意圖[44],前者來自光電二極體內部的空乏區,後者來自光電二極體表面的懸空鍵;Figure 2.6(b)是SRH、TAT和 BTBT洩漏電流之示意圖[45],前兩者是由缺陷所引發的電流洩漏,缺陷會降低電子躍遷至導帶的能障,並導致暗電流密度增加,後者是在高電場下所發生的穿隧效應。

Figure 2.6 (a) 體洩漏電流和表面洩漏電流之示意圖[44], (b) SRH、TAT 和 BTBT 洩漏電流之示意圖[45]。

# 2.2 元件製造

#### 2.2.1 矽基板清洗

我們使用市售的 N type (100) 矽晶圓,雙面拋光且厚度約  $525 \, \mu m$ ,使用磷進行 N type 摻雜,電阻率約  $8\sim15\,\Omega\cdot cm$ ,摻雜濃度約  $5\cdot10^{14}\, cm^{-3}$ ;使用晶圓切割機切成  $1\times1$  公分的矽基板後,浸入 SC-1、SC-2 和稀釋氫氟酸等溶液中清洗,以去除微粒、有機汙染物和表面氧化層。

SC-1 溶液中含有過氧化氫、氫氧化銨和去離子水,能夠分解或溶解有機汙染物,並利用鹼性溶液中矽基板和微粒皆帶負電的特性分離靜電吸附的微粒[46]; SC-2 溶液中含有過氧化氫、鹽酸和去離子水,能夠和痕量金屬發生反應並溶解金屬汙染物[47];稀釋氫氟酸中含有氫氟酸和去離子水,能夠蝕刻矽基板表面的二氧化矽,並形成二氫化物鈍化表面[48]。

Table 2.1 是詳細流程以及各參數設定,步驟(1)(2)(3)之間浸入去離子水中洗 去溶液以避免互相汙染,步驟(3)之後浸入去離子水中洗去溶液,氮氣吹乾表面後 使用光學顯微鏡檢測;矽基板清洗後存放在氮氣箱中,以避免再次汙染和氧化 [49][50], Figure 2.14 是所使用的溶液和儀器。

矽基板清洗的同時啟動電漿輔助化學氣相沉積系統,將氣體管線和反應腔體抽至真空後(~0.01 Torr),使用氫氣沖洗氣體管線和起泡器;先以 400 sccm 的流量沖洗氣體管線 10 分鐘,以去除氣體管線中的水氣和氧氣,再以 400 sccm 的流量沖洗氣體管線和起泡器 10 分鐘,以去除起泡器中的水氣和氧氣;系統準備就緒後將矽基板置入反應腔體中生長鍺薄膜,詳細架設請見 2.3.1 電漿輔助化學氣相沉積 (PECVD),詳細鍍膜參數請見 3.7 光偵測器。

| 步驟  | 溶液或儀器                | 參數   | 時間     |

|-----|----------------------|------|--------|

| (1) | 氨水:過氧化氫:去離子水=1:1:5   | 75°C | 20 min |

| (2) | 鹽酸:過氧化氫:去離子水 = 1:1:6 | 75°C | 20 min |

| (3) | 氫氟酸:去離子水 = 1:50      | 室溫   | 3 min  |

Table 2.1 詳細流程以及各參數設定(矽基板清洗)。

#### 2.2.2 離子佈植

為了製造光電二極體的能帶結構, 豬薄膜生長後進行離子佈植; 表面塗佈二氧化矽薄膜(詳細參數請見 2.2.4 二氧化矽薄膜塗佈)以避免豬薄膜濺射汙染離子佈植的腔體, 黏在六吋晶圓上並裝入晶圓盒後以保鮮膜包覆, 送至國研院進行離子佈植,使用硼對豬薄膜進行 P type 重摻雜,無需進行退火即有電活性[51];透過調整離子佈植的加速電壓控制摻雜深度,摻雜劑量控制摻雜濃度,偏轉角度避免通道效應,旋轉角度避免陰影效應。

Table 2.2 是各參數設定,使用硼對鍺薄膜進行 P type 重摻雜,加速電壓為 110 keV,摻雜劑量為  $3\cdot 10^{14} \text{ cm}^{-2}$ ,Figure 2.7 是摻雜濃度對摻雜深度關係圖,使用 SRIM 軟體對離子佈植的結果進行模擬,其中摻雜濃度約  $5\cdot 10^{18} \text{ cm}^{-3}$ ,摻雜深度約 400 nm,鍺薄膜的摻雜深度約 200 nm。

|      | 掺雜元素 | 加速電壓    | 掺雜劑量                              | 偏轉角度 | 旋轉角度 |

|------|------|---------|-----------------------------------|------|------|

| 各項參數 | 硼    | 110 keV | $3 \cdot 10^{14} \text{ cm}^{-2}$ | 7°   | 359° |

Table 2.2 各參數設定(離子佈植)。

Figure 2.7 掺雜濃度對摻雜深度關係圖(離子佈植)。

####

為了製造光電二極體的元件結構,離子佈植後進行鍺薄膜蝕刻;表面圖案化後(詳細參數請見 2.2.7 表面圖案化),先使用緩衝氧化物蝕刻液蝕刻二氧化矽薄膜,再使用過氧化氫蝕刻鍺薄膜(超聲波輔助)[52];過氧化氫會與矽或鍺反應生成二氧化矽或二氧化鍺,前者不溶於水而後者會溶解在水中,且二氧化矽不會再與過氧化氫反應從而終止蝕刻,因此能夠明確判斷蝕刻終點;蝕刻完成後先使用丙酮去除光阻薄膜,再使用緩衝氧化物蝕刻液去除二氧化矽薄膜。

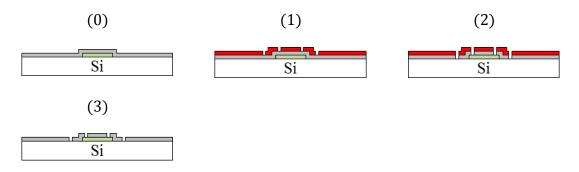

Table 2.3 是詳細流程以及各參數設定,步驟(2)(3)(4)(5)之間浸入去離子水中洗去溶液以避免互相汙染,步驟(5)之後浸入去離子水中洗去溶液,氮氣吹乾表面後使用光學顯微鏡檢測,Figure 2.8 是各流程示意圖,其中有鍺薄膜(綠色)、二氧化矽薄膜(灰色)、光阻薄膜(紅色),Figure 2.15 是所使用的溶液和儀器。

| 步驟  | 溶液或儀器              | 參數 | 時間            |

|-----|--------------------|----|---------------|

| (1) | (表面圖案化)            | -  | -             |

| (2) | 蝕刻二氧化矽薄膜:緩衝氧化物蝕刻液  | 室溫 | 3 min         |

| (3) | 蝕刻鍺薄膜:過氧化氫 (超聲波清洗) | 室溫 | 100<br>nm/min |

| (4) | 去除光阻薄膜:丙酮          | 室溫 | 1 min         |

| (5) | 去除二氧化矽薄膜:緩衝氧化物蝕刻液  | 室溫 | 3 min         |

Table 2.3 詳細流程以及各參數設定(鍺薄膜蝕刻)。

Figure 2.8 各流程示意圖(鍺薄膜蝕刻)。

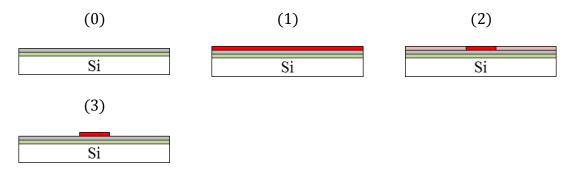

### 2.2.4 二氧化矽薄膜塗佈

為了降低表面懸空鍵對響應率和暗電流密度的影響,錯薄膜蝕刻後進行二氧化矽薄膜塗佈;使用市售溶液(700A)塗佈二氧化矽薄膜,由於此溶液在大氣中進行旋轉塗佈時,二氧化矽薄膜容易產生氣泡和裂痕,因此我們在手套箱中塗佈二氧化矽薄膜;先使用加熱板進行低溫短暫烘烤,讓溶劑揮發以避免汙染物吸附,再使用加熱板進行高溫長時間烘烤,以提升二氧化矽薄膜的品質。

Table 2.4 是詳細流程以及各參數設定,步驟(1)之前將矽基板和700A 溶液移入手套箱,步驟(2)之後移出手套箱,步驟(3)之後靜置冷卻並使用光學顯微鏡檢測,Figure 2.9 是二氧化矽薄膜厚度對塗佈轉速關係圖,數據取自溶液使用手冊,Figure 2.16 是所使用的溶液和儀器。

| 步驟  | 溶液或儀器         | 參數       | 時間     |

|-----|---------------|----------|--------|

| (1) | 塗佈二氧化矽薄膜:700A | 2000 rpm | 20 s   |

| (2) | 加熱板烘烤         | 100°C    | 10 min |

| (3) | 加熱板烘烤         | 400°C    | 60 min |

Table 2.4 詳細流程以及各參數設定(二氧化矽薄膜塗佈)。

Figure 2.9 二氧化矽薄膜厚度對塗佈轉速關係圖。

#### 2.2.5 二氧化矽薄膜蝕刻

為了讓金屬電極能夠接觸鍺薄膜與矽基板,二氧化矽薄膜塗佈後進行二氧化矽薄膜蝕刻,以打開金屬電極的接觸窗口;表面圖案化後(詳細參數請見 2.2.7 表面圖案化),使用緩衝氧化物蝕刻液蝕刻二氧化矽薄膜,由於此溶液不會蝕刻鍺薄膜或矽基板,因此能夠明確判斷蝕刻終點,蝕刻完成後使用丙酮去除光阻薄膜。

Table 2.5 是詳細流程以及各參數設定,步驟(2)(3)之間浸入去離子水中洗去溶液以避免互相汙染,步驟(3)之後浸入去離子水中洗去溶液,氮氣吹乾表面後使用光學顯微鏡檢測。

Figure 2.10 是各流程示意圖,其中有鍺薄膜(綠色)、二氧化矽薄膜(灰色)、 光阻薄膜(紅色), Figure 2.17 是所使用的溶液和儀器。

| 步驟  | 溶液或儀器             | 溫度 | 時間    |

|-----|-------------------|----|-------|

| (1) | (表面圖案化)           | 1  | -     |

| (2) | 蝕刻二氧化矽薄膜:緩衝氧化物蝕刻液 | 室溫 | 3 min |

| -   | 去離子水              | 室溫 | 1 min |

| (3) | 去除光阻薄膜:丙酮         | 室溫 | 1 min |

| -   | 去離子水→氮氣吹乾→光學顯微鏡檢測 | -  | -     |

Table 2.5 詳細流程以及各參數設定(二氧化矽薄膜蝕刻)。

Figure 2.10 各流程示意圖(二氧化矽薄膜蝕刻)。

#### 2.2.6 蒸鍍電極

為了製造光電二極體的元件結構,二氧化矽薄膜蝕刻後進行蒸鍍電極;表面圖案化後(詳細參數請見 2.2.7 表面圖案化),使用去離子水清洗表面(超聲波輔助),以去除表面汙染物並讓天然氧化層重新生長,天然氧化層能夠鈍化表面並提升鈦黏著層的效果;氮氣吹乾表面後使用加熱板烘烤,以去除表面吸附的水氣;在真空中蒸鍍5nm的鈦作為黏著層,195nm的鋁作為金屬電極,蒸鍍完成後使用丙酮去除光阻薄膜(超聲波輔助)。

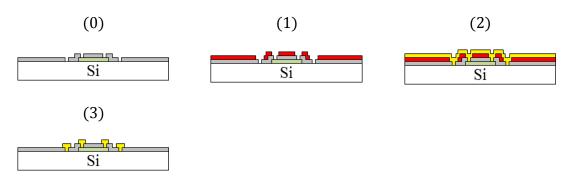

Table 2.6 是詳細流程以及各參數設定,步驟(2)之前將矽基板、鎢舟、鈦金屬和鉛金屬移入蒸鍍機,步驟(2)之後移出蒸鍍機,步驟(3)之後浸入去離子水中洗去溶液,氮氣吹乾表面後使用光學顯微鏡檢測,Figure 2.11 是各流程示意圖,其中有鍺薄膜(綠色)、二氧化矽薄膜(灰色)、光阻薄膜(紅色)、鉛電極(金色),Figure 2.18 是所使用的溶液和儀器。

| 步驟  | 溶液或儀器             | 參數     | 時間     |

|-----|-------------------|--------|--------|

| (1) | (表面圖案化)           | -      | -      |

|     | 去離子水(超聲波輔助)       | 室溫     | 10 min |

| _   | 氮氣吹乾→加熱板烘烤        | 120°C  | 1 min  |

| (2) | 蒸鍍黏著層:鈦           | 5 nm   | -      |

|     | 蒸鍍金屬電極:鋁          | 195 nm | -      |

| (3) | 去除光阻薄膜:丙酮 (超聲波輔助) | 室溫     | 10 min |

Table 2.6 詳細流程以及各參數設定(蒸鍍電極)。

Figure 2.11 各流程示意圖(蒸鍍電極)。

#### 2.2.7 表面圖案化

為了製造光電二極體的元件結構, 豬薄膜蝕刻、二氧化矽薄膜蝕刻和蒸鍍電極等製程需要進行表面圖案化;以市售光阻劑(DSAM-3020)塗佈光阻薄膜後,先使用加熱板進行短暫烘烤,讓溶劑揮發避免汙染物吸附,再使用紫外線曝光,改變光阻薄膜的分子結構,然後使用加熱板再次短暫烘烤,以消除駐波效應;以市售顯影液(DPD-200)顯影後,先浸入去離子水中洗去溶液並使用氮氣吹乾表面,再使用加熱板進行烘烤,以提升光阻薄膜的品質。

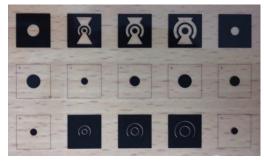

Table 2.7 是詳細流程以及各參數設定,硬烤結束之後使用光學顯微鏡檢測, Figure 2.12 是各流程示意圖,其中有鍺薄膜(綠色)、二氧化矽薄膜(灰色)、光阻 薄膜(紅色),Figure 2.13 是光阻薄膜厚度對塗佈轉速關係圖,數據取自溶液使用 手冊,Figure 2.19 是所使用的溶液和儀器。

| 步驟  | 溶液或儀器            | 參數       | 時間    |

|-----|------------------|----------|-------|

| (1) | 光阻薄膜塗佈:DSAM-3020 | 1000 rpm | 10 s  |

|     |                  | 3000 rpm | 30 s  |

| -   | 加熱板烘烤(軟烤)        | 120°C    | 60 s  |

| (2) | 光阻薄膜曝光:曝光機       | 405 nm   | 40 s  |

| -   | 加熱板烘烤(曝後烤)       | 120°C    | 60 s  |

| (3) | 光阻薄膜顯影:DPD-200   | 室溫       | ~60 s |

| -   | 加熱板烘烤(硬烤)        | 120°C    | 120 s |

Table 2.7 詳細流程以及各參數設定(表面圖案化)。

Figure 2.12 各流程示意圖(表面圖案化)。

Figure 2.13 光阻薄膜厚度對塗佈轉速關係圖。

# 2.2.8 溶液與儀器

Figure 2.14 所使用的溶液與儀器(矽基板清洗)。

過氧化氫 (30%)

Figure 2.15 所使用的溶液與儀器(鍺薄膜蝕刻)。

旋轉塗佈機

加熱板

光學顯微鏡

Figure 2.16 所使用的溶液與儀器(二氧化矽薄膜塗佈)。

#### 緩衝氧化物蝕刻液

去離子水

光學顯微鏡

Figure 2.17 所使用的溶液與儀器(二氧化矽薄膜蝕刻)。

超聲波震洗機

丙酮

去離子水

光學顯微鏡

蒸鍍機

Figure 2.18 所使用的溶液與儀器(蒸鍍電極)。

DPD-200

去離子水

加熱板

旋轉塗佈機

光學顯微鏡

光罩

Figure 2.19 所使用的溶液與儀器(表面圖案化)。

# 2.3 主要實驗儀器

## 2.3.1 電漿輔助化學氣相沉積 (PECVD)

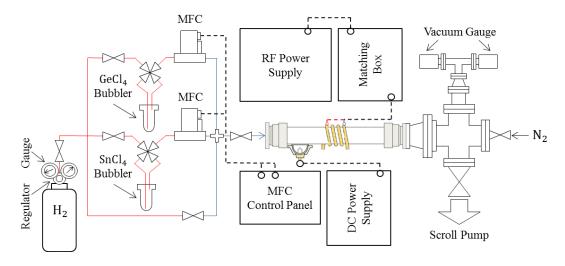

這項實驗中我們使用自製的電漿輔助化學氣相沉積系統生長鍺薄膜,實驗架設上參考了許多論文[34][53][54][55][56];Figure 2.20 是電漿輔助化學氣相沉積系統的架設示意圖,使用 1000 W、13.56 MHz 的射頻電源供應器和自動阻抗匹配器提供電漿能量,自動阻抗匹配器內部有兩個電控可變電容調整阻抗匹配,能避免輸出功率反射而損壞儀器;直徑 2 inch、長度 40 cm 的石英玻璃管作為反應腔體,內部填裝數個直徑 1.8 inch、長度 6~12 cm 的石英玻璃內管,鍍膜結束使用砂纸清潔內管表面以再次使用。

反應腔體前端連接質量流量控制器(MFC)、起泡器和氫氣鋼瓶;四氯化鍺液體存放在起泡器中,內部氣壓固定為24.7 psi,四氯化鍺蒸氣的分壓為1.47 psi;起泡器氣壓由氫氣鋼瓶的調壓閥和氣壓計控制並讀取,而MFC負責控制氣體流量,並藉由氫氣將四氯化鍺蒸氣引入反應腔體;起泡器氣壓和氣體流量皆影響四氯化鍺蒸氣在反應腔體的濃度分布,前者影響氣體比例,後者影響補充速率。

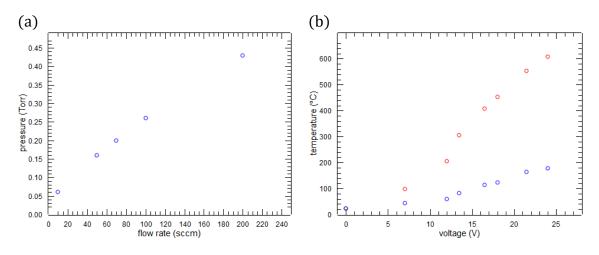

反應腔體後端連接渦卷幫浦、氮氣管線和電容式真空計;前兩者負責抽真空和破真空,後者負責讀取氣壓,真空度可達 0.01 Torr; Figure 2.22(a)是腔體氣壓對氣體流量關係圖,正常情況下連接渦卷幫浦的閥門固定全開,腔體氣壓隨著氣體流量增加而提升,必要時可以微調閥門改變腔體氣壓。

Figure 2.20 電漿輔助化學氣相沉積系統的架設示意圖。

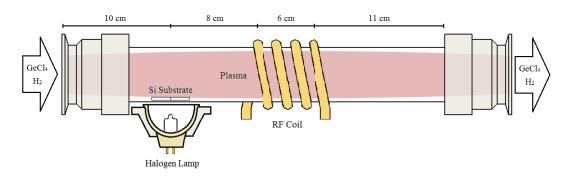

Figure 2.21 是反應腔體的架設示意圖,使用 4 匝、直徑 2.2 inch、長度 6 cm 的電感線圈產生感應耦合電漿;電感線圈套在石英玻璃管外側,放置於反應腔體中央,由 1/4 inch 的銅管製成,必要時可以使用冷卻水進行冷卻。

矽基板放置於反應腔體內 10 cm 的位置,使用 24 V、250 W 的石英鹵素燈加熱矽基板,並透過直流電源供應器控制石英鹵素燈,調整供應電壓能夠改變矽基板溫度並使用 K type 熱電偶測量;Figure 2.22(b)是矽基板溫度對供應電壓關係圖,紅色圓圈是使用石英鹵素燈加熱 3 分鐘後的矽基板溫度,藍色圓圈是停止加熱 1 分鐘後的矽基板溫度;使用石英鹵素燈進行加熱能夠迅速達到平衡溫度,對 450 ℃ 而言加熱約 3 分鐘就能達到平衡。

這項實驗中透過石英鹵素燈的供應電壓控制基板溫度(25~600°C),使用質量流量控制器控制氣體流量(10~50 sccm),使用射頻電源供應器控制射頻功率(10~50 W);並對生長溫度、氣體流量、射頻功率和處理步驟等各項鍍膜參數進行了優化以達到研究目標;Figure 2.23 是所使用的溶液與儀器。

Figure 2.21 反應腔體的架設示意圖。

Figure 2.22 (a)腔體氣壓對氣體流量關係圖,(b)矽基板溫度對供應電壓關係圖。

#### 射頻電源供應器

阻抗匹配器

直流電源供應器

電感和鹵素燈

氫氣鋼瓶(99.99%)

質量流量控制器

渦卷幫浦

質量流量控制器操控面板

砂紙(P4000)

起泡器

四氯化鍺(99.99%)

Figure 2.23 所使用的溶液與儀器(電漿輔助化學氣相沉積)。

## 2.3.2 掃描式電子顯微鏡 (SEM)

掃描式電子顯微鏡利用電子槍產生電子束,並使用電磁透鏡聚焦後對樣品表面進行掃描;電子束會和樣品表面進行交互作用,產生二次電子和特徵 X 射線;前者主要來自樣品表面,因此能對表面形貌進行分析,後者主要來自能階躍遷,因此能對元素成分進行分析;透過二次電子探測器以及能量色散 X 射線光譜儀(EDX)接收訊號後,能夠檢測樣品的表面形貌和元素成分[57]。

Figure 2.24 是我們使用的掃描式電子顯微鏡,用來對表面形貌、薄膜厚度、線性缺陷密度和元素成分進行分析;可以從薄膜頂視圖和剖視圖分析表面形貌和薄膜厚度;在蝕刻溶液的輔助下,線性缺陷密度也可以從薄膜頂視圖分析,並使用公式(3)計算鍺薄膜的線性缺陷密度;元素成分可以從 EDX 所測量的原子百分比分析,並使用公式(4)計算鍺薄膜的氣含量。

$$TDD = \frac{N}{A} \tag{3}$$

公式(3)是線性缺陷密度 TDD ( $1/\text{cm}^2$ ) 的計算方式,其中  $A(\text{cm}^2)$  是頂視圖的測量面積, N 是測量面積內蝕刻坑的數量;使用溶液蝕刻後,線性缺陷會形成蝕刻坑,而薄膜頂視圖能夠分析蝕刻坑的數量,並透過蝕刻坑數量和測量面積計算線性缺陷密度[58][59]。

Figure 2.24 掃描式電子顯微鏡。

公式(4)是鍺薄膜的氣含量之計算方式,其中Clat%是氯的原子百分比 Ge at%是鍺的原子百分比。

$$Cl content = \frac{Cl at\%}{Ge at\% + Cl at\%} \cdot 100\%$$

(4)

Figure 2.25(a)是鍺薄膜的頂視圖,並在左上角標記鍺薄膜內的氣含量;(b)是 鍺薄膜的剖視圖,其中黑色區域是影像背景,中間白色區域是鍺薄膜,白色區域 下方是矽基板;(c)是 EDX 測量結果,可以看到來自矽、鍺和氯的特徵 X 射線, 右上角是矽、鍺和氯的原子百分比,EDX 的測量軟體會自動分析訊號強度並換算 出原子百分比,以上數據取自 3.1 雜質含量。

Figure 2.25 (a) 緒薄膜頂視圖, (b) 緒薄膜剖視圖, (c) EDX 測量結果。

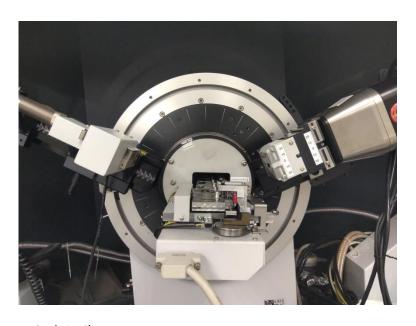

## 2.3.3 X 光繞射儀 (XRD)

X 光繞射儀利用高能電子轟擊銅靶作為 X 射線源,並使用測角儀對樣品進行掃描; X 射線入射樣品時會被原子內的電子散射,排列有序的原子在特定入射角散射的 X 射線會形成建設性干涉;而排列方式不同的原子會在不同角度形成建設性干涉,因此能對晶格結構進行分析;透過 X 射線探測器接收訊號後,能夠檢測樣品的晶格結構[60]。

公式(5)是建設性干涉時晶面間距 d (Å) 和入射角度  $\theta$  之間的關係,以及晶面間距 d (Å) 和晶格常數 a (Å) 之間的關係;其中係數 2 為無量綱常數, n 是繞射階數, (h,k,l) 是晶面指數,而 X 射線波長  $\lambda=1.54056$  Å、矽的晶格常數  $a_{Si}=5.431$  Å、鍺的晶格常數  $a_{Ge}=5.658$  Å;透過公式(5)可以計算理論峰值位置, Si(400) 以及 Ge(400) 分別位於 69.127° 和 65.989° (2 $\theta$ )。

$$2d \cdot \sin \theta = n \cdot \lambda \qquad d = a/\sqrt{h^2 + k^2 + l^2} \tag{5}$$

Figure 2.26 是我們使用的 X 光繞射儀,用來對元素成份、晶格指向、薄膜應力和結晶品質進行分析;由於元素成份、晶格指向和薄膜應力會造成晶面間距改變,前兩者會造成大幅改變而後者只會稍微改變;因此元素成份和晶格指向從峰值位置分析,而薄膜應力從峰值位置的偏移計算[61];由於晶界、缺陷和應變會造成半高全寬的加寬,因此結晶品質可以從峰值的半高全寬判斷[62][63]。

Figure 2.26 X 光繞射儀。

公式(6)是薄膜應力  $\varepsilon$  和晶面間距 d (Å) 之間的關係,其中  $d_{\text{film}}$  (Å) 是薄膜的晶面間距, $d_{\text{bulk}}$  (Å) 是塊材的晶面間距,  $\varepsilon_{\perp}$  是垂直方向的薄膜應力、 $\varepsilon_{\parallel}$  是水平方向的薄膜應力[61],係數 1.33 為無量綱常數;透過公式(5)可以計算鍺塊材 Ge(400) 的晶面間距  $d_{\text{bulk}}=1.4145$  Å。

$$\varepsilon_{\perp} = \frac{d_{\text{film}} - d_{\text{bulk}}}{d_{\text{bulk}}} \cdot 100\% \qquad \varepsilon_{\parallel} = -1.33 \cdot \varepsilon_{\perp} \tag{6}$$

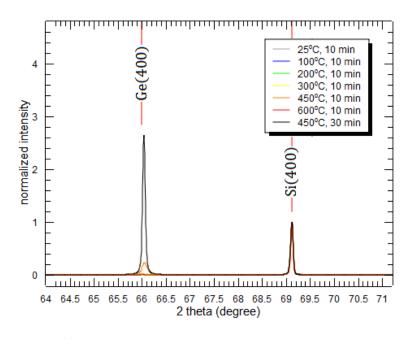

Table 2.8 是各參數設定,測量範圍為 10~80°,角度間隔為 0.008°,X 光繞射儀對半高全寬所造成的儀器加寬約為 0.057°,取自 Si(400) 的半高全寬;Figure 2.27 是 XRD 測量結果,可以看到來自矽基板和鍺薄膜的訊號;黑色曲線中 Si(400) 的繞射峰位於 69.127°,半高全寬為 0.057°,而 Ge(400) 的繞射峰位於 66.044°,半高全寬為 0.064°;為了計算鍺薄膜的水平應力,我們使用公式(5)將黑色曲線中 Ge(400) 的峰值位置換算成鍺薄膜的晶面間距,再透過公式(6)計算出 鍺薄膜的水平應力為 0.097%,以上數據取自 3.2 結晶品質。

|      | 起始角度 | 最終角度 | 角度間隔   | 時間間隔   | 儀器加寬   |

|------|------|------|--------|--------|--------|

| 各項參數 | 10°  | 80°  | 0.008° | 0.05 s | 0.057° |

Table 2.8 各參數設定(XRD 測量)。

Figure 2.27 XRD 測量結果。

## 2.3.4 元件測量平台

我們架設自製的元件測量平台測量暗電流密度,使用 keithley-2400 對元件輸出電壓並測量電流,透過 labview 程式自動化測量;先對市售的電阻進行測量,確認測量誤差是否合理,再測量鍺薄膜光偵測器的暗電流密度。

Table 2.9 是各參數設定,測量範圍為-2~2 V,電壓間隔為 0.1 V,薄膜面積為 0.0314 cm²,吸收面積為 0.00785 cm²; Figure 1.1(b)是暗電流密度對線性缺陷密度關係圖[8],薄膜面積計算出來的暗電流密度可以大致判斷線性缺陷密度的數量級,吸收面積計算出來的暗電流密度和前者對比可以判斷元件設計的好壞。

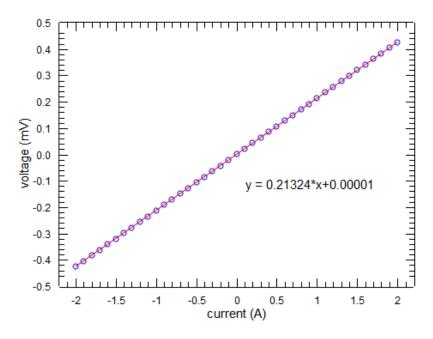

Figure 2.28 是元件測量平台的校正結果,藍色圓圈是電阻測量結果(使用元件測量平台對 $4700\pm5\%\Omega$ 的電阻進行測量),紅色曲線是測量結果的回歸曲線,曲線斜率所計算的電阻值為 $4689.5\Omega$ ,測量誤差在容許範圍內(約為0.22%)。

|      | 供應電壓 | 電壓間隔 | 測量時間 | 薄膜面積            | 吸收面積            |

|------|------|------|------|-----------------|-----------------|

| 各項參數 | -2~2 | 0.1  | ~2   | 0.0314          | 0.00785         |

| (單位) | V    | V    | S    | cm <sup>2</sup> | cm <sup>2</sup> |

Table 2.9 各參數設定(暗電流密度測量)。

Figure 2.28 元件測量平台的校正結果(電阻測量)。

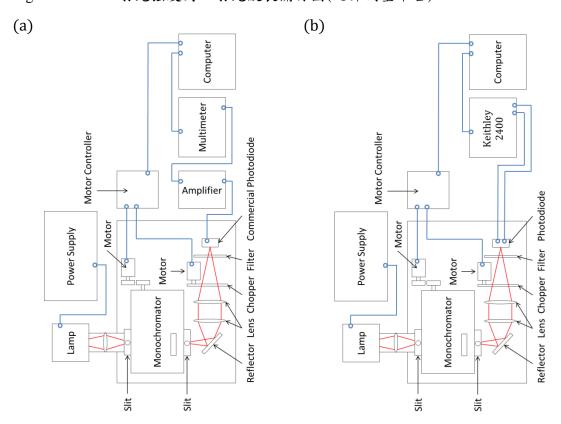

我們架設自製的元件測量平台測量響應率,使用石英鹵素燈作為光源,斬波器控制光源開關,單光儀控制入射光波長;透過高通濾光片 (850 nm) 消除光栅所產生的二階繞射,反射鏡和凸透鏡將光束聚焦在光偵測器上;使用電控馬達控制單光儀和斬波器, keithley-2400 對元件輸出電壓並測量電流,透過 labview 程式自動化測量;先對市售的鍺光偵測器進行測量,確認測量誤差是否合理,再測量鍺薄膜光偵測器的響應率。

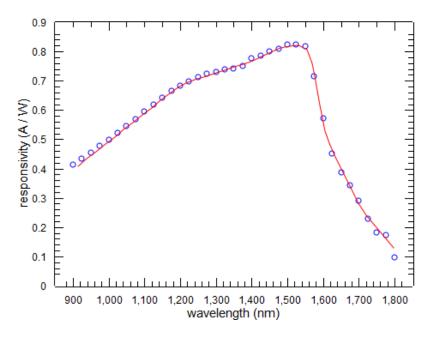

Table 2.10 是各參數設定,供應電壓為-2V,測量範圍為900~1800 nm,波長間隔為25 nm,單光儀解析度約為26.5 nm; Figure 2.29 是元件測量平台的校正結果,藍色圓圈是響應率測量結果(使用元件測量平台對市售的鍺光偵測器進行測量),紅色曲線是理論響應率(數據取自市售的鍺光偵測器之儀器使用手冊),測量誤差在容許範圍內(約為0.42%@1300 nm)。

|      | 供應電壓 | 入射光波長    | 波長間隔 | 狹縫寬度 | 儀器色散  |

|------|------|----------|------|------|-------|

| 各項參數 | -2   | 900~1800 | 25   | 0.5  | 53    |

| (單位) | V    | nm       | nm   | mm   | nm/mm |

Table 2.10 各參數設定(響應率測量)。

Figure 2.29 元件測量平台的校正結果(響應率測量)。

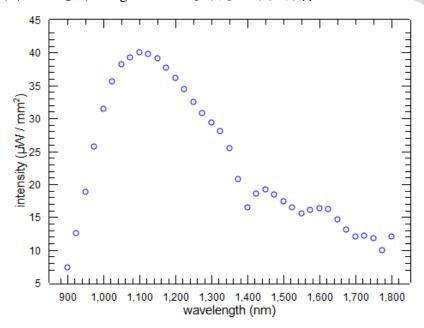

Figure 2.30 是入射光強度對入射光波長關係圖,使用市售的鍺光偵測器對入射光強度進行測量,光強度約只有 15.6 μW/mm² @ 1550 nm, Figure 2.31 是元件測量平台的架設示意圖,(a)測量入射光強度的架設示意圖,(b)測量暗電流密度和響應率的架設示意圖,Figure 2.32 是所使用的各項儀器。

Figure 2.30 入射光強度對入射光波長關係圖(元件測量平台)。

Figure 2.31 元件測量平台的架設示意圖。

### 市售的鍺光偵測器

直流電源供應器

石英鹵素燈

單光儀

透鏡、斬波器和濾光片

鍺光偵測器放大器

數位電表

keithley-2400

Figure 2.32 所使用的各項儀器(元件測量平台)。

# Chapter 3 結果與討論

# 3.1 雜質含量

電漿輔助化學氣相沉積中,高能量的電子和前驅物相互碰撞,並引發前驅物的電離或解離;這些高能量的前驅物讓薄膜可以在低溫下生長,但也會讓非預期的反應同時發生,所以經常有反應副產物帶來的雜質汙染;這項實驗中需要面對氫和氯的殘留,兩者皆以化學吸附的方式殘留在鍺薄膜內部;許多論文研究不同生長或退火溫度下,鍺薄膜內部氫和氯的脫附現象[36][64][65][66];在適當的生長或退火溫度下,能有效降低氫和氫的殘留。

其中氫的殘留會導致薄膜剝落,當後續製程的處理溫度大於脫附溫度時,氫 氣會從鍺薄膜內部釋放出來,並向薄膜表面或是矽/鍺介面擴散;由於氫氣擴散速 率的差異(在鍺薄膜內大於矽基板內),矽/鍺介面會累積氫氣而形成氣泡並導致鍺 薄膜剝落[66];為了避免雜質殘留以及薄膜剝落對元件性能和後續製程造成不良 影響,我們對生長溫度進行了優化。

這項實驗中固定薄膜生長時的腔體氣壓(0.14 Torr)、射頻功率(50 W)、氣體流量(40 sccm)和處理時間(10 min),透過石英鹵素燈的供應電壓改變基板溫度(25~600°C),藉此研究生長溫度對薄膜雜質的影響,並使用 EDX 對薄膜雜質進行分析,由於 EDX 無法直接測量氫含量,因此我們透過薄膜剝落的現象大致判斷氫含量;Table 3.1 是各鍰膜參數設定,鍰膜流程分為基板預熱和薄膜生長,前者讓基板溫度達到穩定,後者讓電漿產生促使薄膜生長。

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度   | 處理時間  |  |

|------|--------|------|--------|--------|--------|-------|--|

| 穩態處理 |        | None |        |        |        |       |  |

| 基板預熱 | 0.14   | 0    | 40     | Close  | 25~600 | 3     |  |

| 薄膜生長 | 0.14   | 50   | 40     | Open   | 25~600 | 10    |  |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C)   | (min) |  |

Table 3.1 各鍍膜參數設定(改變生長溫度)。

Figure 3.1 SEM & EDX 影像圖,各鍍膜參數(改變生長溫度)的薄膜頂視圖和剖視圖以及 EDX 測量結果。

Figure 3.1 是各鍍膜參數的 EDX 測量結果,其中室溫生長的鍺薄膜有氣殘留,但生長溫度在 100℃以上幾乎完全脫附,其含量低於 EDX 的檢測極限,推測脫附溫度約在 100℃,和參考論文的研究結果一致[36]。

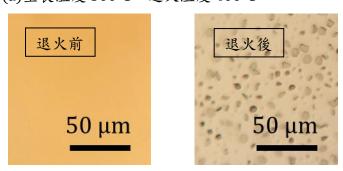

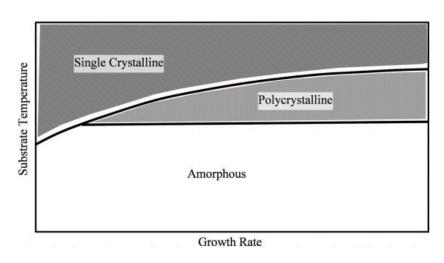

Figure 3.2 是鍺薄膜退火前後的表面形貌,(a)生長溫度 300℃,在大氣中退火 30 分鐘後薄膜出現剝落,(b)生長溫度 450℃,在大氣中退火 30 分鐘後薄膜沒有剝落;氫的脫附溫度約在 200~300℃之間,當溫度達到 450℃以上幾乎只殘留在薄膜表面[36][64][65][66];因此生長溫度在 25~200℃之間,薄膜生長後不會剝落,但會在後續退火中剝落;生長溫度在 200~300℃之間,低鍍率下在薄膜生長後或是後續退火中皆不會剝落,但高鍍率下可能在薄膜生長後或是後續退火中剝落;而生長溫度在 450℃以上,薄膜生長後或是後續退火中皆不會剝落。

根據這項實驗結果,生長溫度設為 450°C 能有效避免氫和氯的殘留以及鍺薄膜剝落;而生長溫度在 200°C 以上開始出現表面粗糙化的跡象,推測是汙染物(水氣和氧氣)所造成的蝕刻現象,生長溫度約 600°C 時出現局部生長的現象,推測是四氯化鍺氫還原的反應機制所造成,這些結果我們在 3.3 反應機制 和 3.5 表面形貌中進行詳細分析。

#### (a)生長溫度 300°C、退火溫度 400°C

### (b)生長溫度 450°C、退火溫度 540°C

Figure 3.2 OM 影像圖, 鍺薄膜退火前後的表面形貌。

# 3.2 結晶品質

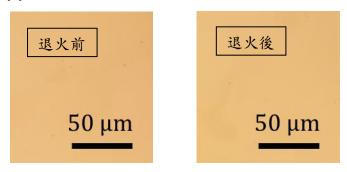

許多論文對鍺薄膜的生長溫度和退火溫度或結晶溫度進行了研究[67][68],對結晶品質而言生長溫度相當重要,為了提升結晶品質我們對生長溫度進行了優化; Figure 3.3 是結晶態對生長溫度和薄膜鍍率的關係示意圖[68],其中生長溫度對結晶態影響較大,高溫環境下原子較容易克服結晶活化能而形成單晶或多晶,低溫環境下原子較難克服結晶活化能而形成非晶。

Figure 3.3 結晶態對生長溫度和薄膜鍍率的關係示意圖[68]。

這項實驗中固定薄膜生長時的腔體氣壓(0.14 Torr)、射頻功率(50 W)、氣體流量(40 sccm)和處理時間(10 min),透過石英鹵素燈的供應電壓改變基板溫度(25~600℃),藉此研究生長溫度對結晶品質的影響,並使用 XRD 對結晶品質進行分析; Table 3.2 是各鍍膜參數設定,鍍膜流程分為基板預熱和薄膜生長,前者讓基板溫度達到穩定,後者讓電漿產生促使薄膜生長。

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度   | 時間    |  |

|------|--------|------|--------|--------|--------|-------|--|

| 穩態處理 |        | None |        |        |        |       |  |

| 基板預熱 | 0.14   | 0    | 40     | Close  | 25~600 | 3     |  |

| 薄膜生長 | 0.14   | 50   | 40     | Open   | 25~600 | 10    |  |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C)   | (min) |  |

Table 3.2 各鍍膜參數設定(改變生長溫度)。

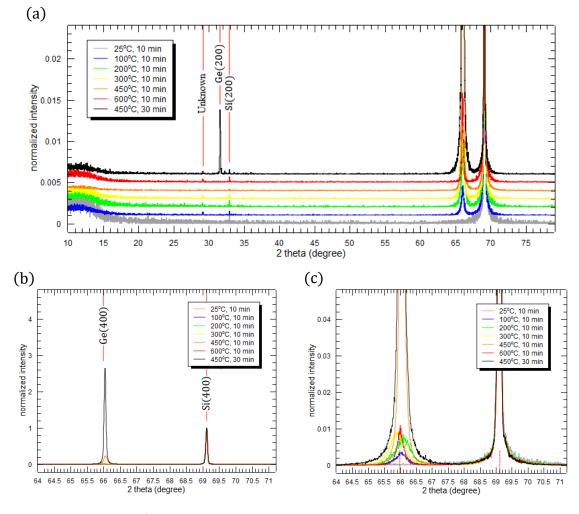

Figure 3.4 是各鍍膜參數所測量出的 Theta - 2Theta 曲線,並使用 Si(400)的峰值強度進行歸一化;(a)曲線中出現 Si(400)、Ge(400)、Si(200)、Ge(200)的繞射峰和未知峰值(峰值強度低,推測來自鍺薄膜的表面氧化層);(b)(c)室溫生長的鍺薄膜呈現非晶態,生長溫度在  $100\sim600^{\circ}$ C 之間呈現單晶態, $100\sim300^{\circ}$ C 之間結晶品質較差, $450^{\circ}$ C 時結晶品質顯著提升(峰值強度最高且半高全寬最窄), $600^{\circ}$ C 時結晶品質顯著降低。

根據這項實驗結果,生長溫度設為 450°C 時結晶品質最好,且結晶品質隨著薄膜厚度增加而提升;薄膜厚度約 400 nm 時,薄膜應力為 0.126% 而半高全寬為 0.123°,薄膜厚度約 2000 nm 時,薄膜應力為 0.097% 而半高全寬為 0.064°,非常接近 Si(400) 的半高全寬(0.057°);將 XRD 的測量結果和 3.1 雜質含量的實驗結果對照,推測 100~300°C 氫的殘留會降低結晶品質[69];而 600°C 結晶品質嚴重降低是因為局部生長造成表面覆蓋率降低所導致。

Figure 3.4 各鍍膜參數(改變生長溫度)的 XRD 測量結果。

# 3.3 反應機制

3.1 雜質含量的實驗結果中,生長溫度約 600°C 時出現局部生長的現象,我們認為這是四氯化鍺氫還原的反應機制所導致;並參考使用四氯化鍺進行原子層沉積的論文[70],我們認為氫終止的矽基板表面才會與四氯化鍺蒸氣發生反應。

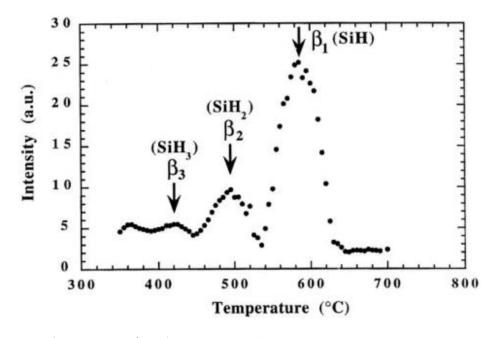

Figure 3.5 是氫終止的矽基板表面之脫附溫度[71],其中三氫化物約 420 °C 開始脫附,二氫化物約 500 °C 開始脫附,一氫化物約 580 °C 開始脫附;將脫附溫度和 3.1 雜質含量的實驗結果對照,生長溫度約 600°C 時出現局部生長的現象,推測是因為表面氫化物的脫附所造成;而以下是我們所提出的四氯化鍺氫還原之反應機制:

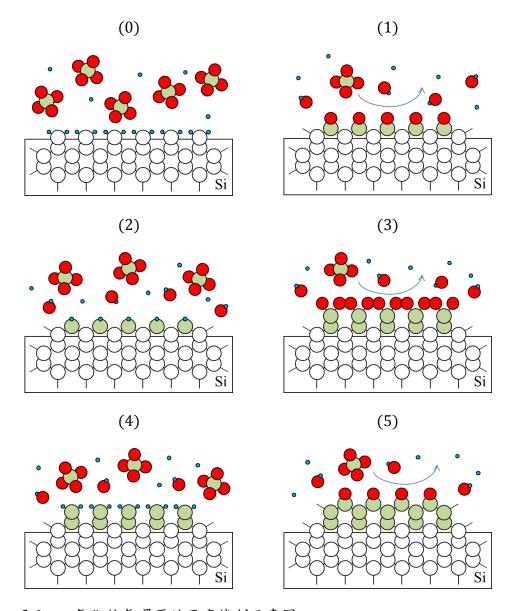

- (1)四氯化鍺蒸氣和氫終止的表面反應,生成氯終止的表面

- (2)在氫原子的作用下,重新生成氫終止的表面

薄膜隨著這些步驟的循環而增長,反應機制與原子層沉積類似,差別只在不需等待氫或氯完全終止表面;這個反應機制可以解釋局部生長的現象,由於生長溫度約600℃時,矽基板溫度足夠使表面氫化物完全脫附,雖然在氫原子的作用下可以再次生成氫終止的表面,但仍會有局部表面沒有被氫終止,所以反應機制的第一步驟不會發生,導致局部生長的現象。

Figure 3.5 氫終止的矽基板表面之脫附溫度[71]。

Figure 3.6 是四氯化鍺氫還原的反應機制示意圖,其中有氫原子(藍色)、鍺原子(綠色)和氣原子(紅色);步驟(0)是氫氟酸清洗後的矽基板表面,並會形成二氫化物鈍化表面[48],步驟(1)(3)(5)會形成氣終止的表面並限制四氯化鍺蒸氣進一步反應,步驟(0)(2)(4)重新形成氫終止的表面。

在我們所提出的反應機制中,反應速率正比於四氯化鍺蒸氣和氫原子的碰撞機率,而碰撞機率正比於四氯化鍺蒸氣和氫原子的濃度,因此我們推測這是二級反應;公式(7)是反應速率方程式,參考這個反應機制後,假設四氯化鍺蒸氣和氫原子皆為一級反應,公式(7)的各項參數說明請見 3.4 薄膜鍍率。

Figure 3.6 四氯化鍺氫還原的反應機制示意圖。

# 3.4 薄膜鍍率

公式(7)是反應速率 r (cm<sup>-3</sup>·s<sup>-1</sup>)和反應速率常數 k (cm<sup>3</sup>·s<sup>-1</sup>)、四氯化鍺蒸氣濃度 [GeCl<sub>4</sub>] (cm<sup>-3</sup>) 以及氫原子濃度 [H] (cm<sup>-3</sup>) 之間的關係;而反應速率常數是活化能  $E_a$  (J·mol<sup>-1</sup>) 和環境溫度 T (K)的函數,其中 A (cm<sup>3</sup>·s<sup>-1</sup>) 是阿瑞尼斯常數,理想氣體常數 R=8.31 J·K<sup>-1</sup>·mol<sup>-1</sup>。

$$r = k \cdot [GeCl_4] \cdot [H] = A \cdot e^{-E_a/RT} \cdot [GeCl_4] \cdot [H]$$

(7)

公式(7)中許多因素影響薄膜鍍率,其中生長溫度、四氯化鍺蒸氣濃度和氫原子濃度是相當重要的因素;為了維持低雜質含量和高結晶品質等目標,我們將生長溫度設為450°C,並透過調整氣體流量、射頻功率、鍍膜時間和處理步驟來改變四氯化鍺蒸氣和氫原子的濃度以提升薄膜鍍率。

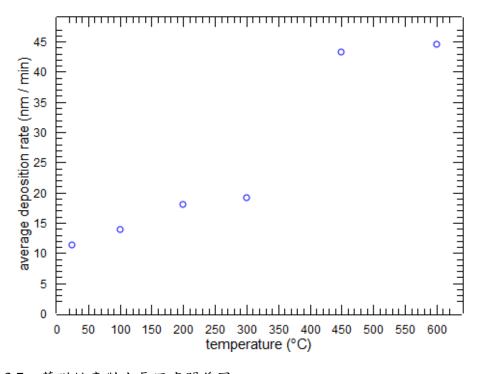

Figure 3.7 是薄膜鍍率對生長溫度關係圖,數據取自 3.1 雜質含量和 3.2 結晶品質,薄膜鍍率隨著生長溫度增加而提升,但也受到反應機制和汙染物蝕刻的影響,請見 3.3 反應機制和 3.5 表面形貌。

Figure 3.7 薄膜鍍率對生長溫度關係圖。

## 3.4.1 氣體流量

為了提升薄膜鍍率我們對氣體流量進行了優化;由於四氯化鍺蒸氣會與氫原子發生反應,因此反應腔體中四氯化鍺蒸氣濃度會隨著位置變化,越接近進氣口濃度越高;而氣體流量能夠改變四氯化鍺蒸氣的補充速率,並影響四氯化鍺蒸氣濃度以及薄膜鍍率。

這項實驗中固定薄膜生長時的腔體氣壓(0.16 Torr)、射頻功率(40 W)、基板溫度(450°C)和處理時間(10 min),透過質量流量控制器改變氣體流量(10~50 sccm),藉此研究氣體流量對薄膜成長的影響,並使用 SEM 對表面形貌和薄膜鍍率進行分析;Table 3.3 是各鍍膜參數設定,鍍膜流程分為穩態處理、基板預熱和薄膜生長,前兩者讓四氯化鍺蒸氣濃度和基板溫度達到穩定,後者讓電漿產生促使薄膜生長;此外我們在基板預熱前增加穩態處理步驟,並比較有無穩態處理的差異。

### (a)無穩態處理

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |  |

|------|--------|------|--------|--------|------|-------|--|

| 穩態處理 |        | None |        |        |      |       |  |

| 基板預熱 | 0.16   | 0    | 10~50  | Close  | 450  | 3     |  |

| 薄膜生長 | 0.16   | 40   | 10~50  | Open   | 450  | 10    |  |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C) | (min) |  |

#### (b)有穩態處理

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |

|------|--------|------|--------|--------|------|-------|

| 穩態處理 | 0.43   | 0    | 200    | Open   | 300  | 3     |

| 基板預熱 | 0.16   | 0    | 10~50  | Open   | 450  | 3     |

| 薄膜生長 | 0.16   | 40   | 10~50  | Open   | 450  | 10    |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C) | (min) |

Table 3.3 各鍍膜參數設定(改變氣體流量)。

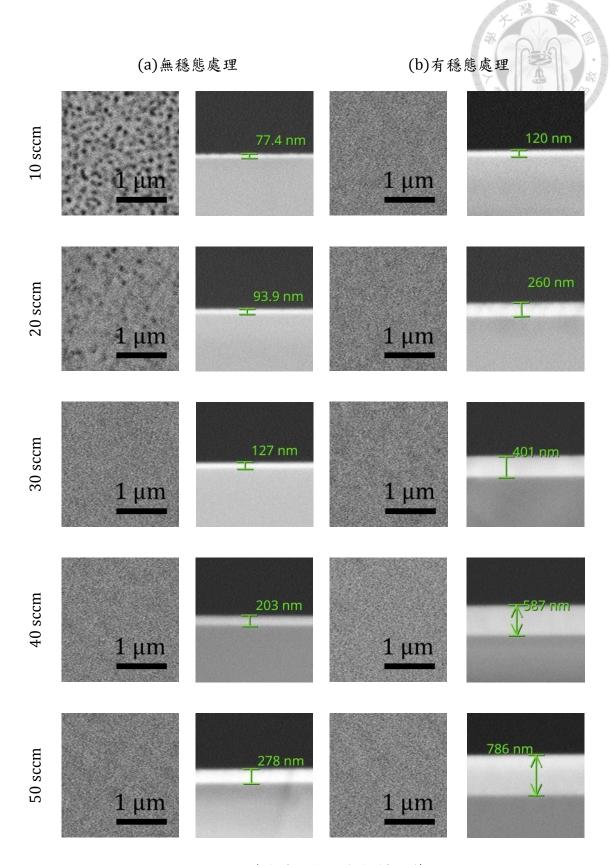

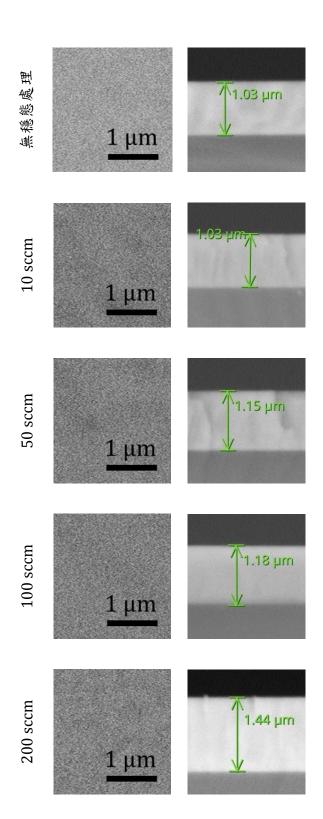

Figure 3.8 SEM 影像圖,各鍍膜參數(改變氣體流量)的薄膜頂視圖和剖視圖。

Figure 3.8 是各鍍膜參數的薄膜頂視圖和剖視圖;沒有進行穩態處理的情況下,低氣體流量時表面形貌較粗糙;有進行穩態處理的情況下,氣體流量對表面形貌的影響不大;推測這是汙染物(水氣和氧氣)所造成的蝕刻現象,這項結果我們在3.5 表面形貌中進行詳細分析。

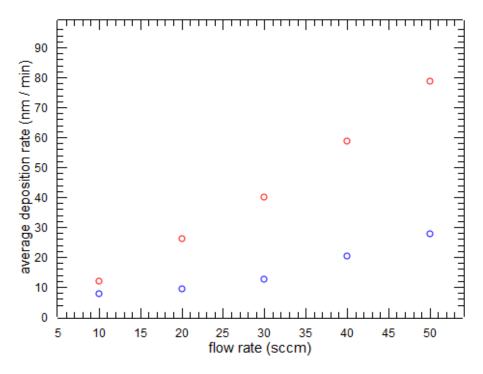

Figure 3.9 是薄膜鍍率對氣體流量關係圖,其中紅色圓圈有進行穩態處理,藍色圓圈沒有進行穩態處理;進行穩態處理的情況下,薄膜鍍率顯著提升,推測是四氯化鍺蒸氣的初始濃度不同所導致,這項結果我們在 3.4.4 穩態處理中進行詳細分析。

Figure 3.9 中薄膜鍍率隨著氣體流量增加而提升,這可以藉由反應速率方程式解釋;氫原子濃度維持不變的情況下(固定射頻功率),四氯化鍺蒸氣的補充速率隨著氣體流量增加而提升,因此抵達矽基板位置的四氯化鍺蒸氣濃度增加;而反應速率正比於四氯化鍺蒸氣濃度和氫原子濃度的乘積,因此薄膜鍍率隨著氣體流量增加而提升,這項結果我們在 3.4.5 簡化模型中進行詳細分析。

根據這項實驗結果,在進行穩態處理的情況下,氣體流量設為 40~50 sccm 能滿足我們對薄膜鍍率的要求,同時表面形貌尚可接受。

Figure 3.9 薄膜鍍率對氣體流量關係圖。

## 3.4.2 射頻功率

為了提升薄膜鍍率我們對射頻功率進行了優化;由於四氯化鍺蒸氣會與氫原子發生反應,因此反應腔體中四氯化鍺蒸氣濃度會隨著位置變化,越接近進氣口濃度越高;而射頻功率能夠改變氫原子的濃度和四氯化鍺蒸氣的消耗速率,同時影響氫原子和四氯化鍺蒸氣的濃度以及薄膜鍍率。

這項實驗中固定薄膜生長時的腔體氣壓(0.16 Torr)、氣體流量(50 sccm)、基板溫度(450°C)和處理時間(10 min),透過射頻電源供應器改變射頻功率(10~50 W),藉此研究射頻功率對薄膜成長的影響,並使用 SEM 對表面形貌和薄膜鍍率進行分析;Table 3.4 是各鍍膜參數設定,鍍膜流程分為穩態處理、基板預熱和薄膜生長,前兩者讓四氣化鍺蒸氣濃度和基板溫度達到穩定,後者讓電漿產生促使薄膜生長;此外我們在基板預熱前增加穩態處理步驟,並比較有無穩態處理的差異。

### (a)無穩態處理

|      | 腔體氣壓   | 射頻功率  | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |  |

|------|--------|-------|--------|--------|------|-------|--|

| 穩態處理 |        | None  |        |        |      |       |  |

| 基板預熱 | 0.16   | 0     | 50     | Close  | 450  | 3     |  |

| 薄膜生長 | 0.16   | 10~50 | 50     | Open   | 450  | 10    |  |

| (單位) | (Torr) | (W)   | (sccm) | (None) | (°C) | (min) |  |

#### (b)有穩態處理

|      | 腔體氣壓   | 射頻功率  | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |

|------|--------|-------|--------|--------|------|-------|

| 穩態處理 | 0.43   | 0     | 200    | Open   | 300  | 3     |

| 基板預熱 | 0.16   | 0     | 50     | Open   | 450  | 3     |

| 薄膜生長 | 0.16   | 10~50 | 50     | Open   | 450  | 10    |

| (單位) | (Torr) | (W)   | (sccm) | (None) | (°C) | (min) |

Table 3.4 各鍍膜參數設定(改變射頻功率)。

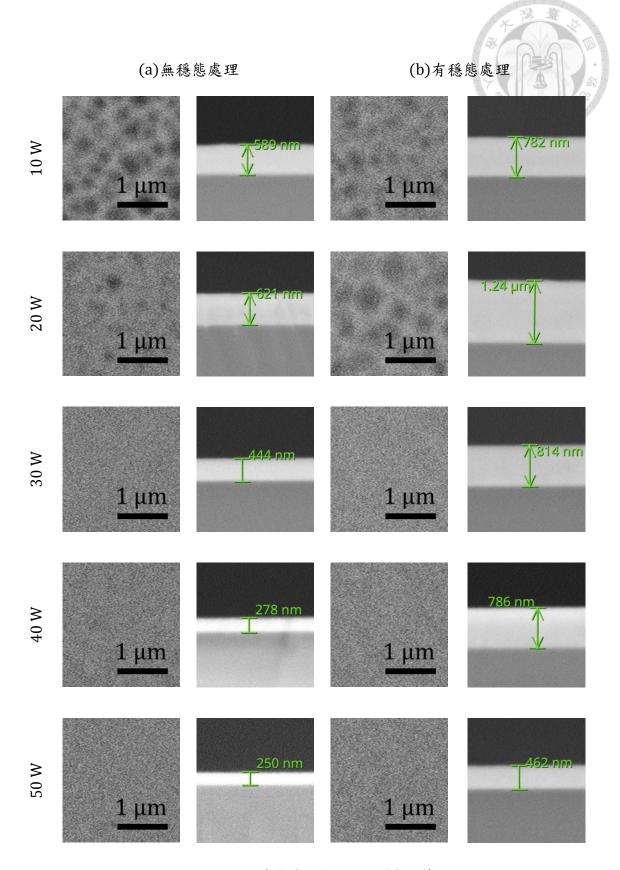

Figure 3.10 SEM 影像圖,各鍍膜參數(改變射頻功率)的薄膜頂視圖和剖視圖。

Figure 3.10 是各鍍膜參數的薄膜頂視圖和剖視圖;不論是否有進行穩態處理,低射頻功率時表面形貌皆較粗糙;推測是汙染物(水氣和氧氣)所造成的蝕刻現象,這項結果我們在 3.5 表面形貌中進行詳細分析。

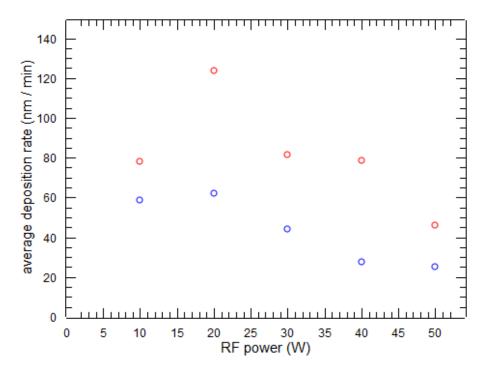

Figure 3.11 是薄膜鍍率對射頻功率關係圖,其中紅色圓圈有進行穩態處理,藍色圓圈沒有進行穩態處理;進行穩態處理的情況下,薄膜鍍率顯著提升,推測是四氯化鍺蒸氣的初始濃度不同所導致,這項結果我們在 3.4.4 穩態處理中進行詳細分析。

Figure 3.11 中薄膜鍍率在特定射頻功率最高,這可以藉由反應速率方程式解釋;四氯化鍺蒸氣的補充速率維持不變的情況下(固定氣體流量),四氯化鍺蒸氣的消耗速率隨著射頻功率增加而提升,因此抵達矽基板位置的四氯化鍺蒸氣濃度減少,但氫原子濃度隨著射頻功率增加而提升;而反應速率正比於四氯化鍺蒸氣濃度和氫原子濃度的乘積,因此薄膜鍍率在特定射頻功率最高,這項結果我們在3.4.5 簡化模型中進行詳細分析。

根據這項實驗結果,在進行穩態處理的情況下,射頻功率設為 40~50 W 能滿足我們對薄膜鍍率的要求,同時表面形貌尚可接受。

Figure 3.11 薄膜鍍率對射頻功率關係圖。

## 3.4.3 時間演化

為了增加薄膜厚度我們可以調整鍍膜時間;但隨著時間演化和薄膜厚度增長,薄膜應力可能有所不同並造成表面形貌的改變,常見應力來源有下列兩種: (1)矽基板和鍺薄膜之間晶格常數差異所造成的應力,(2)矽基板和鍺薄膜之間熱膨脹係數差異所造成的應力;前者可能導致島狀/層狀生長模式[9],後者可能造成薄膜裂痕的產生[72][73]。

這項實驗中固定薄膜生長時的腔體氣壓(0.16 Torr)、射頻功率(40 W)、氣體流量(40 sccm)和基板溫度(450°C),透過處理時間(2~20 min)改變薄膜厚度,藉此研究薄膜成長隨時間的變化,並使用 SEM 對表面形貌和薄膜鍍率進行分析; Table 3.5 是各鍍膜參數設定,鍍膜流程分為穩態處理、基板預熱和薄膜生長,前 兩者讓四氯化鍺蒸氣濃度和基板溫度達到穩定,後者讓電漿產生促使薄膜生長;此外我們在基板預熱前增加穩態處理步驟,並比較有無穩態處理的差異。

### (a)無穩態處理

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |  |

|------|--------|------|--------|--------|------|-------|--|

| 穩態處理 |        | None |        |        |      |       |  |

| 基板預熱 | 0.16   | 0    | 40     | Close  | 450  | 3     |  |

| 薄膜生長 | 0.16   | 40   | 40     | Open   | 450  | 2~20  |  |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C) | (min) |  |

#### (b)有穩態處理

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |

|------|--------|------|--------|--------|------|-------|

| 穩態處理 | 0.43   | 0    | 200    | Open   | 300  | 3     |

| 基板預熱 | 0.16   | 0    | 40     | Open   | 450  | 3     |

| 薄膜生長 | 0.16   | 40   | 40     | Open   | 450  | 2~20  |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C) | (min) |

Table 3.5 各鍍膜參數設定(改變鍍膜時間)。

Figure 3.12 是各鍍膜參數的薄膜頂視圖和剖視圖;各鍍膜時間 (2~20 min)和薄膜厚度 (0~1.24 μm) 的表面形貌差異不大,沒有發現島狀/層狀生長模式或熱應力所造成的裂痕;前者可能是因為反應機制所造成,氯終止的表面限制四氯化鍺蒸氣進一步反應,並抑制了島狀成長的發生;後者則是因為尚未達到裂痕產生的臨界厚度,生長溫度 450 ℃ 時臨界厚度約為 4 μm [73]。

Figure 3.12 SEM 影像圖,各鍍膜參數(改變鍍膜時間)的薄膜頂視圖和剖視圖。

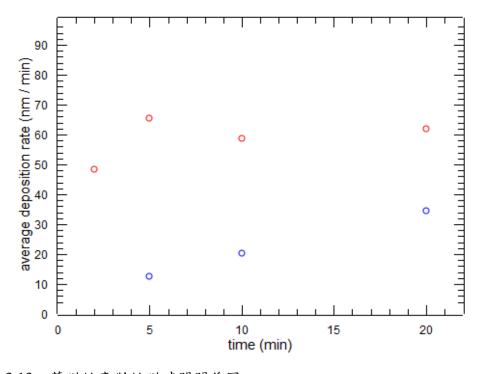

Figure 3.13 是薄膜鍍率對鍍膜時間關係圖,其中紅色圓圈有進行穩態處理,藍色圓圈沒有進行穩態處理;進行穩態處理的情況下,薄膜鍍率顯著提升,推測是四氯化鍺蒸氣的初始濃度不同所導致,這項結果我們在 3.4.4 穩態處理中進行詳細分析。

Figure 3.13 中沒有進行穩態處理的情況下,薄膜鍍率隨著鍍膜時間增加而逐漸提升,這可以藉由反應速率方程式解釋;四氯化鍺蒸氣的補充速率和氫原子濃度維持不變的情況下(固定氣體流量和射頻功率),隨著時間演化四氯化鍺蒸氣濃度逐漸達到穩態,因此抵達矽基板位置的四氯化鍺蒸氣濃度增加;而反應速率正比於四氯化鍺蒸氣濃度和氫原子濃度的乘積,因此薄膜鍍率隨著鍍膜時間增加而逐漸提升,這項結果我們在 3.4.5 簡化模型中進行詳細分析。

Figure 3.13 中進行穩態處理的情況下,鍍膜時間對薄膜鍍率的影響不大,這可以藉由反應速率方程式解釋;由於經過穩態處理後四氯化鍺蒸氣濃度已經達到穩態,因此抵達矽基板位置的四氯化鍺蒸氣濃度不隨時間改變;所以鍍膜時間對薄膜鍍率的影響不大,這項結果我們在 3.4.5 簡化模型中進行詳細分析。

根據這項實驗結果,在進行穩態處理的情況下,鍍膜時間設為 5~20 min 對薄膜鍍率的影響不大,同時表面形貌尚可接受。

Figure 3.13 薄膜鍍率對鍍膜時間關係圖。

# 3.4.4 穩態處理

3.4.1 氣體流量、3.4.2 射頻功率和 3.4.3 時間演化的實驗結果中,穩態處理能顯著提升薄膜鍍率;這個步驟中四氯化鍺蒸氣提早進入反應腔體,我們推測薄膜鍍率提升的可能原因是,反應腔體中四氯化鍺蒸氣濃度提早達到穩態,因為四氯化鍺蒸氣的初始濃度較高而提升薄膜鍍率。

這項實驗中固定薄膜生長時的腔體氣壓(0.14 Torr)、射頻功率(50 W)、氣體流量(40 sccm)和基板溫度(450°C)以及處理時間(10 min),透過穩態處理和腔體沖洗改變四氯化鍺蒸氣的初始濃度,藉此研究初始濃度對薄膜成長的影響,並使用 SEM 對表面形貌和薄膜鍍率進行分析;Table 3.6 是各鍍膜參數設定,鍍膜流程分為穩態處理、腔體沖洗、基板預熱和薄膜生長,前兩者會改變四氯化鍺蒸氣的初始濃度,後兩者讓基板溫度達到穩定並產生電漿促使薄膜生長。

#### (a)無穩態處理

|      | 腔體氣壓                   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |  |  |  |

|------|------------------------|------|--------|--------|------|-------|--|--|--|

| 穩態處理 |                        | None |        |        |      |       |  |  |  |

| 腔體沖洗 |                        |      | No     | one    |      |       |  |  |  |

| 基板預熱 | 0.14                   | 0    | 40     | Close  | 450  | 3     |  |  |  |

| 薄膜生長 | 0.14 50 40 Open 450 10 |      |        |        |      |       |  |  |  |

| (單位) | (Torr)                 | (W)  | (sccm) | (None) | (°C) | (min) |  |  |  |

#### (b)有穩態處理

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |  |

|------|--------|------|--------|--------|------|-------|--|

| 穩態處理 | 0.43   | 0    | 200    | Open   | 300  | 3     |  |

| 腔體沖洗 | None   |      |        |        |      |       |  |

| 基板預熱 | 0.14   | 0    | 40     | Open   | 450  | 3     |  |

| 薄膜生長 | 0.14   | 50   | 40     | Open   | 450  | 10    |  |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C) | (min) |  |

### (c)有穩態處理+腔體沖洗

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |

|------|--------|------|--------|--------|------|-------|

| 穩態處理 | 0.43   | 0    | 200    | Open   | 300  | 3     |

| 腔體沖洗 | 0.43   | 0    | 200    | Close  | 300  | 3     |

| 基板預熱 | 0.14   | 0    | 40     | Close  | 450  | 3     |

| 薄膜生長 | 0.14   | 50   | 40     | Open   | 450  | 10    |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C) | (min) |

Table 3.6 各鍍膜參數設定(改變穩態處理步驟)。

Figure 3.14 是各鍍膜參數的薄膜頂視圖和剖視圖,(a)四氯化鍺蒸氣沒有提早進入反應腔體,(b)四氯化鍺蒸氣提早進入反應腔體,(c)四氯化鍺蒸氣提早進入反應腔體並沖洗腔體將其移除;其中薄膜厚度(b)>(a)≅(c),因此可以確定是反應腔體中四氯化鍺蒸氣濃度提早達到穩態,因為四氯化鍺蒸氣的初始濃度較高而提升薄膜鍍率。

Figure 3.14 SEM 影像圖,各鍍膜參數(改變穩態處理步驟)的薄膜頂視圖和剖視圖。

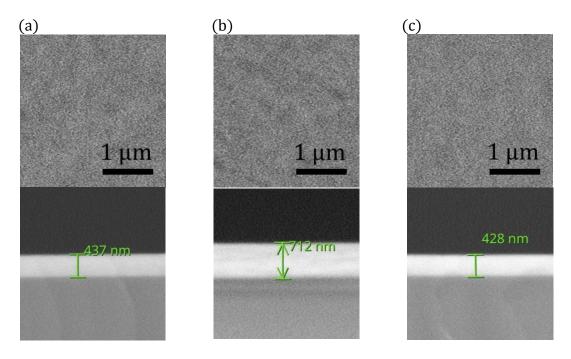

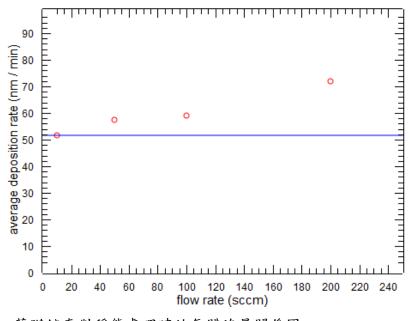

下列實驗中固定薄膜生長時的腔體氣壓(0.16 Torr)、射頻功率(40 W)、氣體流量(50 sccm)和基板溫度(450°C)以及處理時間(10 min),透過穩態處理時的氣體流量(10~200 sccm)改變四氯化鍺蒸氣的初始濃度,藉此研究初始濃度對薄膜成長的影響,並使用 SEM 對表面形貌和薄膜鍍率進行分析;Table 3.7 是各鍍膜參數設定,鍍膜流程分為穩態處理、基板預熱和薄膜生長,前兩者讓四氯化鍺蒸氣濃度和基板溫度達到穩定,後者讓電漿產生促使薄膜生長。

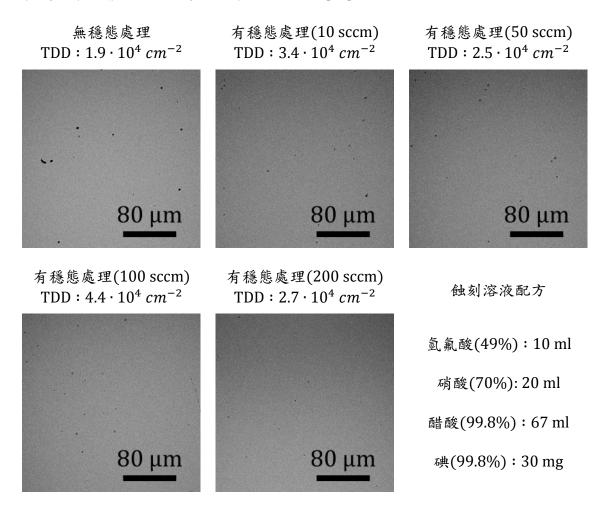

Figure 3.16 是各鍍膜參數的薄膜頂視圖和剖視圖,各氣體流量下表面形貌差異不大; Figure 3.15 是薄膜鍍率對穩態處理時的氣體流量關係圖,其中紅色圓圈有進行穩態處理,藍色直線沒有進行穩態處理;薄膜鍍率隨著氣體流量增加而提升,穩態處理時的氣體流量設為 200 sccm 能顯著提升薄膜鍍率。

|      | 腔體氣壓      | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |

|------|-----------|------|--------|--------|------|-------|

| 穩態處理 | 0.06~0.43 | 0    | 10~200 | Open   | 300  | 3     |

| 基板預熱 | 0.16      | 0    | 50     | Open   | 450  | 3     |

| 薄膜生長 | 0.16      | 40   | 50     | Open   | 450  | 10    |

| (單位) | (Torr)    | (W)  | (sccm) | (None) | (°C) | (min) |

Table 3.7 各鍍膜參數設定(改變穩態處理時的氣體流量)。

Figure 3.15 薄膜鍍率對穩態處理時的氣體流量關係圖。

Figure 3.16 SEM 影像圖,各鍍膜參數(改變穩態處理時的氣體流量)的薄膜頂視圖和剖視圖。

## 3.4.5 簡化模型

為了解釋 3.4.1 氣體流量、3.4.2 射頻功率和 3.4.3 時間演化中的實驗結果,我們對這個系統進行下列簡化,並對四氯化鍺蒸氣濃度和平均鍍率進行模擬:

- (1) 氫原子濃度和射頻功率成正比,但氫原子濃度不隨位置改變。

- (2)四氯化鍺蒸氣濃度和氣體流量 F 成正比,隨著位置遠離進氣口而指數衰退,隨著射頻功率 P 增加而指數衰退,隨著時間增加而逐漸達到穩態。

總結上述簡化我們將氫原子濃度[H]、四氯化鍺蒸氣濃度[GeCl4] 近似成:

$$[H] \approx A \cdot P \tag{8}$$

$$[GeCl_4] \approx B \cdot F \cdot e^{-aPx} \cdot (1 - e^{-bt})$$

(9)

公式(8)是氫原子濃度 [H] (cm<sup>-3</sup>) 和射頻功率 P(W) 之間的關係,其中  $A(W^{-1}\cdot cm^{-3})$  為常數;公式(9)是四氯化鍺蒸氣濃度 [GeCl<sub>4</sub>] (cm<sup>-3</sup>) 和氣體流量 F(sccm)、射頻功率 P(W)、位置 x(cm) 以及時間 t(min) 之間的關係;其中  $B(sccm^{-1}\cdot cm^{-3})$ 、 $a(W\cdot cm)^{-1}$  以及  $b(min)^{-1}$  皆為常數;反應腔體進氣端位置 為 x=0,反應腔體末端位置為 x=40 cm。

$$R \approx C \cdot P \cdot F \cdot e^{-aPx} \cdot \left(T + \frac{1}{b}e^{-bT} - \frac{1}{b}\right) / T$$

(10)

由於平均鍍率乘以鍍膜時間正比於反應速率對時間的積分,因此將公式 (8)(9)代入公式(7)後對時間積分並除以鍍膜時間可以得到公式(10);公式(10)是平均鍍率 R (nm/min) 和射頻功率 P(W)、氣體流量 F (sccm) 以及鍍膜時間 T (min) 之間的關係,其中 C  $(W\cdot min\cdot sccm/nm)^{-1}$  為常數。

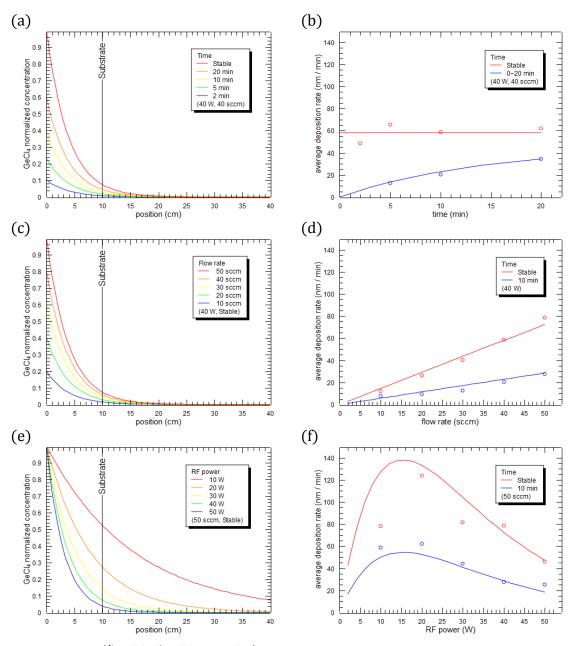

我們使用公式(9)模擬四氯化鍺蒸氣濃度在反應腔體中的分布狀態,公式(10)模擬平均鍍率,並調整  $a \cdot b$  和 C = 項 數讓模擬曲線符合實驗結果,其中  $a = 0.0065 \cdot b = 0.11 \cdot C = 0.488$ ; Figure 3.17 是簡化模型所模擬的曲線,其中(a)(c)(e)是歸一化的四氯化鍺蒸氣濃度在反應腔體中的分布狀態,四氯化鍺蒸氣濃度隨著鍍膜時間、氣體流量和射頻功率而改變;而(b)(d)(f)是薄膜鍍率對各鍍膜參數的關係圖,其中紅色曲線鍍膜時間設為趨近無限大,代表四氯化鍺蒸氣濃度已達到穩態。

Figure 3.17(a)(b)四氯化鍺蒸氣濃度隨著鍍膜時間增加而逐漸達到穩態,所以沒有進行穩態處理的情況下,薄膜鍍率隨著鍍膜時間增加而逐漸提升,進行穩態處理的情況下,薄膜鍍率顯著提升且不隨鍍膜時間改變; Figure 3.17(c)(d)四氯化鍺蒸氣濃度隨著氣體流量增加而提升,所以薄膜鍍率隨著氣體流量增加而提升;Figure 3.17(e)(f)四氯化鍺蒸氣濃度隨著射頻功率增加而降低,但氫原子濃度隨著射頻功率增加而提升,所以薄膜鍍率在特定射頻功率最高。

模擬結果尚能符合實驗數據的趨勢,能夠提供定性上的解釋,定量上則需要更深入的研究才能完善這個模型。

Figure 3.17 簡化模型所模擬的曲線。

# 3.5 表面形貌

3.1 雜質含量、3.2 結晶品質、3.4.1 氣體流量 和 3.4.2 射頻功率的實驗結果中,生長溫度在 200℃ 以上開始出現表面粗糙化的跡象,低氣體流量和低射頻功率的情況下,表面形貌更加糟糕;3.4.3 時間演化的實驗結果中,可以排除鍍膜時間、薄膜鍍率和薄膜厚度等可能因素,所以我們推測這是起泡器和氣體管線中汙染物(水氣和氧氣)所造成的蝕刻現象。

許多論文研究在水氣或氧氣環境下氧化鍺的生長,兩者皆會和鍺薄膜反應生成一氧化鍺或二氧化鍺,其中一氧化鍺會在 400 ℃ 開始脫附,並造成鍺薄膜的蝕刻 [74][75][76][77];由於我們的系統中有電漿存在,可能會降低一氧化鍺生成或脫附所需的溫度,而這種蝕刻現象將會導致表面粗糙化。

$$2Ge(s) + O_2(g) \rightarrow 2GeO(g) \tag{11}$$

$$Ge(s) + H_2O(g) \to GeO(g) + H_2(g)$$

(12)

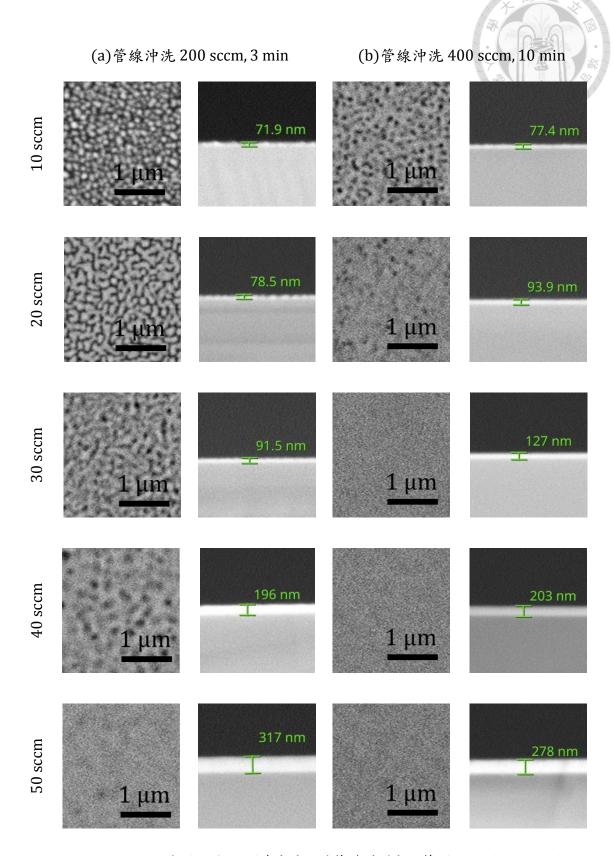

這項實驗中固定薄膜生長時的腔體氣壓(0.16 Torr)、射頻功率(40 W)、氣體流量(10~50 sccm)和基板溫度(450°C)以及處理時間(10 min),透過管線沖洗時的氣體流量和沖洗時間改變汙染物的初始濃度,藉此研究汙染物對薄膜成長的影響,並使用 SEM 對表面形貌進行分析;Table 3.8 是各鍍膜參數設定,鍍膜流程分為管線沖洗、穩態處理、基板預熱和薄膜生長,前者讓汙染物的初始濃度降低,後三者讓四氯化鍺蒸氣濃度和基板溫度達到穩定並產生電漿促使薄膜生長。

### (a)管線沖洗 200 sccm, 3 min

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |  |  |

|------|--------|------|--------|--------|------|-------|--|--|

| 管線沖洗 | 0.43   | 0    | 200    | Open   | 25   | 3     |  |  |

| 穩態處理 |        | None |        |        |      |       |  |  |

| 基板預熱 | 0.16   | 0    | 10~50  | Close  | 450  | 3     |  |  |

| 薄膜生長 | 0.16   | 40   | 10~50  | Open   | 450  | 10    |  |  |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C) | (min) |  |  |

#### (b)管線沖洗 400 sccm, 10 min

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |  |  |

|------|--------|------|--------|--------|------|-------|--|--|

| 管線沖洗 | 0.74   | 0    | 400    | Open   | 25   | 10    |  |  |

| 穩態處理 |        | None |        |        |      |       |  |  |

| 基板預熱 | 0.16   | 0    | 10~50  | Close  | 450  | 3     |  |  |

| 薄膜生長 | 0.16   | 40   | 10~50  | Open   | 450  | 10    |  |  |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C) | (min) |  |  |

Table 3.8 各鍍膜參數設定(改變管線沖洗)。

Figure 3.18 是各鍍膜參數的薄膜頂視圖和剖視圖;以 200 sccm 沖洗三分鐘的情況下,各氣體流量的薄膜表面皆較粗糙;以 400 sccm 沖洗十分鐘的情況下,只有氣體流量 10~20 sccm 的薄膜表面較粗糙。

結合 3.1 雜質含量、3.2 結晶品質、3.4.1 氣體流量、3.4.2 射頻功率和這項實驗結果,我們認為這是起泡器和氣體管線中汙染物(水氣和氧氣)所造成的蝕刻現象;且生長溫度、薄膜鍍率和汙染物濃度會決定這個蝕刻現象的嚴重與否,而固定生長溫度下,薄膜鍍率和汙染物濃度會受到氣體流量和射頻功率所影響。

Figure 3.1 中生長溫度在 200℃ 以上開始出現表面粗糙化的跡象;推測是 25~100℃ 時蝕刻速率較低,所以蝕刻現象較不明顯;200~300℃ 時蝕刻速率開始提高,所以蝕刻現象較為明顯;450℃ 時薄膜鍍率開始提高,所以蝕刻現象較不明顯。

Figure 3.8 中低氣體流量時出現表面粗糙化的現象,推測是氣體流量較低時薄膜鍍率較低,所以蝕刻現象較為明顯; Figure 3.10 中低射頻功率時出現表面粗糙化的現象,推測是射頻功率較低時汙染物濃度較高(在電漿中衰減較少),所以蝕刻現象較為明顯。

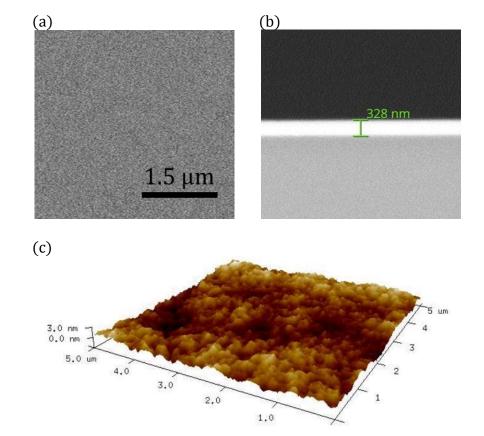

雖然表面形貌會受到汙染物(水氣和氧氣)的影響,但適當的生長參數下(高氣體流量和高射頻功率),能降低其影響且均方根粗糙度可達 0.786 nm,表面形貌和詳細參數請見 Figure 3.19 和 Table 3.9。

Figure 3.18 SEM 影像圖,各鍍膜參數(改變管線沖洗)的薄膜頂視圖和剖視圖。

下列實驗中薄膜生長時的使用高氣體流量(40 sccm)和高射頻功率(40 W),以降低汙染物(水氣和氧氣)對表面形貌的影響,並透過穩態處理步驟進一步提升薄膜鍍率;Table 3.9 是鍍膜參數設定,鍍膜流程分為穩態處理、基板預熱和薄膜生長,前兩者讓四氯化鍺蒸氣濃度和基板溫度達到穩定,後者讓電漿產生促使薄膜生長;Figure 3.19(a)(b)是薄膜頂視圖和剖視圖,(c)是 AFM 影像圖,均方根粗糙度可達 0.786 nm。

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |

|------|--------|------|--------|--------|------|-------|

| 穩態處理 | 0.43   | 0    | 200    | Open   | 300  | 3     |

| 基板預熱 | 0.16   | 0    | 40     | Open   | 450  | 3     |

| 薄膜生長 | 0.16   | 40   | 40     | Open   | 450  | 5     |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C) | (min) |

Table 3.9 鍍膜參數設定(均方根粗糙度測量)。

Figure 3.19 SEM & AFM 影像圖, 鍺薄膜的頂視圖和剖視圖。

# 3.6 線性缺陷密度

許多論文使用蝕刻溶液對鍺薄膜的線性缺陷密度 (TDD) 進行研究[58][59], 這項實驗中我們使用蝕刻溶液對鍺薄膜蝕刻 10 秒,並使用 SEM 對線性缺陷密度 進行分析。

為了維持高結晶品質、低雜質含量、高薄膜鍍率和低表面粗糙度等目標,這項實驗中固定薄膜生長時的腔體氣壓(0.16 Torr)、射頻功率(40 W)、氣體流量(50 sccm)和基板溫度(450°C),並改變穩態處理時的氫氣流量(10~200 sccm),藉此研究穩態處理對線性缺陷密度的影響,並使用 SEM 對線性缺陷密度進行分析; Table 3.10 是各鍍膜參數設定,鍍膜流程分為穩態處理、基板預熱和薄膜生長,前兩者讓四氯化鍺蒸氣濃度和基板溫度達到穩定,後者讓電漿產生促使薄膜生長,並在薄膜生長後直接對線性缺陷密度進行測量,Figure 3.21 是所使用的溶液與藥品。

### (a)無穩態處理

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |  |

|------|--------|------|--------|--------|------|-------|--|

| 穩態處理 |        | None |        |        |      |       |  |

| 基板預熱 | 0.16   | 0    | 50     | Close  | 450  | 3     |  |

| 薄膜生長 | 0.16   | 40   | 50     | Open   | 450  | 20    |  |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C) | (min) |  |

#### (b)有穩態處理

|      | 腔體氣壓      | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |

|------|-----------|------|--------|--------|------|-------|

| 穩態處理 | 0.06~0.43 | 0    | 10~200 | Open   | 300  | 3     |

| 基板預熱 | 0.16      | 0    | 50     | Open   | 450  | 3     |

| 薄膜生長 | 0.16      | 40   | 50     | Open   | 450  | 20    |

| (單位) | (Torr)    | (W)  | (sccm) | (None) | (°C) | (min) |

Table 3.10 各鍍膜參數設定(線性缺陷密度測量)。

Figure 3.20 是各鍍膜參數使用溶液蝕刻後的表面形貌,其中黑色區域為蝕刻坑;穩態處理時的氫氣流量(10~200 sccm)對線性缺陷密度的影響不大,線性缺陷密度皆為~10<sup>4</sup> cm<sup>-2</sup>;而使用循環熱退火或是縱深比捕獲等技術下,線性缺陷密度約為~10<sup>6</sup> cm<sup>-2</sup>,推測是這種類似原子層沉積的反應機制,將晶格錯位侷限在幾個原子層內,因此降低了線性缺陷密度[78]。

Figure 3.20 SEM 影像圖,各鍍膜參數使用溶液蝕刻後的表面形貌。

Figure 3.21 所使用的溶液與藥品(線性缺陷密度測量)。

## 3.7 光偵測器

為了製造鍺薄膜光偵測器的元件結構和能帶結構,在矽基板表面生長單晶鍺薄膜後,經過離子佈植、鍺薄膜蝕刻、二氧化矽薄膜塗佈、二氧化矽薄膜蝕刻和蒸鍍電極等一系列製程,並使用自製的元件測量平台分析鍺薄膜光偵測器的暗電流密度和響應率。

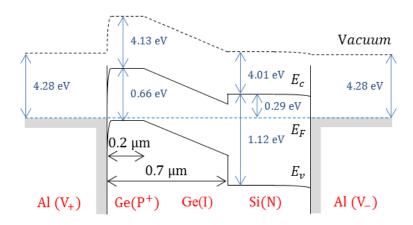

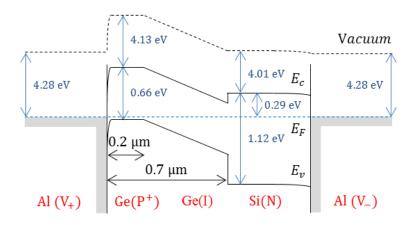

為了維持高結晶品質、低雜質含量、高薄膜鍍率和低表面粗糙度等目標,這項實驗中薄膜生長時的腔體氣壓設為 0.16 Torr、射頻功率設為 40 W、氣體流量設為 50 sccm、基板溫度設為 450°C; Table 3.11 是鍍膜參數設定,鍍膜流程分為穩態處理、基板預熱和薄膜生長,前兩者讓四氯化鍺蒸氣濃度和基板溫度達到穩定,後者讓電漿產生促使薄膜生長; Figure 3.22 是元件的能帶結構示意圖,使用N type 矽基板生長鍺薄膜,離子佈植對鍺薄膜進行 P type 重掺雜,蒸鍍鋁作為金屬電極,其中鍺薄膜厚度約 700 nm。

|      | 腔體氣壓   | 射頻功率 | 氣體流量   | 前驅物    | 基板溫度 | 處理時間  |

|------|--------|------|--------|--------|------|-------|

| 穩態處理 | 0.43   | 0    | 200    | Open   | 300  | 3     |

| 基板預熱 | 0.16   | 0    | 50     | Open   | 450  | 3     |

| 薄膜生長 | 0.16   | 40   | 50     | Open   | 450  | 10    |

| (單位) | (Torr) | (W)  | (sccm) | (None) | (°C) | (min) |

Table 3.11 鍍膜參數設定(光偵測器)。

Figure 3.22 元件的能帶結構示意圖。

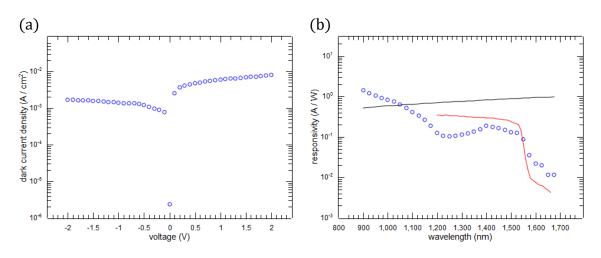

Figure 3.23(a)是暗電流密度對供應電壓關係圖,使用吸收面積計算的暗電流密度為 1.7·10<sup>-3</sup> A/cm<sup>2</sup>,使用薄膜面積計算的暗電流密度為 4.2·10<sup>-4</sup> A/cm<sup>2</sup>;由於薄膜面積是吸收面積的四倍,所以吸收面積計算出來的暗電流密度是薄膜面積計算出來的暗電流密度的四倍,為了進一步降低暗電流密度,元件設計上還有能夠改進的空間;當線性缺陷密度低於 10<sup>6</sup> cm<sup>-2</sup> 時,表面洩漏電流的影響開始逐漸提升[40],而我們的線性缺陷密度約 10<sup>4</sup> cm<sup>-2</sup>,所以表面洩漏電流可能不容忽視;為了達到我們所設定的研究目標,可能需要對表面鈍化或是後續退火進行詳細研究,以降低元件的暗電流密度。

Figure 3.23(b)是響應率對入射光波長關係圖,藍色圓圈是響應率測量結果, 鍺薄膜光偵測器的響應率為 0.11 A/W (@ 1350 nm) 和 0.08 A/W (@ 1550 nm); 紅色曲線是使用公式(1)所計算的鍺薄膜光偵測器之理論響應率(鍺薄膜厚度 700 nm 且不具張應力的情況下),黑色曲線是使用公式(1)所計算的理論響應率 (入射光完全被吸收的情況下),兩者皆不考慮光電流的湮滅或增益,其中元件表 面的二氧化矽薄膜能夠將表面反射率(@ 1550 nm)降低至 28%。

Figure 3.23(b)中入射光波長在 900~1050 nm 之間,鍺薄膜光偵測器的響應率大於入射光完全被吸收時的理論響應率,推測光電流受到某種機制所增益,而且這個波段有來自矽基板的貢獻;而入射光波長在 1200~1600 nm 之間,鍺薄膜光偵測器的響應率小於理論響應率(鍺薄膜厚度 700 nm 且不具張應力的情况下),推測受到鍺薄膜內部懸空鍵的影響導致光電流湮滅;為了達到我們所設定的研究目標,可能需要對後續退火進行詳細研究,以提升元件的響應率。

Figure 3.23 (a)暗電流密度對供應電壓關係圖,(b)響應率對入射光波長關係圖。

## Chapter 4 結論

這項實驗中使用自製的鍍膜系統在矽基板表面生長單晶鍺薄膜,以四氯化鍺液體作為前驅物取代高危險性的四氫化鍺氣體,電漿輔助化學氣相沉積用來解決四氯化鍺蒸氣無法直接在矽基板表面生長鍺薄膜的問題;為了達到高結晶品質、低雜質含量、高薄膜鍍率以及低表面粗糙度等目標,我們對生長溫度、氣體流量、射頻功率和處理步驟進行了優化;藉由調整生長溫度提高結晶品質並降低雜質含量,調整氣體流量、射頻功率和處理步驟提高薄膜鍍率並降低表面粗糙度。

對結晶品質和雜質脫附而言,生長溫度是非常重要的因素,室溫生長的鍺薄膜呈現非晶態,而生長溫度在 100~600°C 之間呈現單晶態;100~300°C 之間結晶品質較差,450°C 時結晶品質顯著提升,600°C 時結晶品質顯著降低,這種結晶行為推測受到四氯化鍺蒸氣與氫原子之間的反應機制所影響,和氫的脫附現象也有關聯;室溫生長的鍺薄膜有氣殘留,但生長溫度高於 100°C 的情況下幾乎完全脫附,其含量低於 EDX 的檢測極限;而生長溫度低於 300°C 的鍺薄膜有氫殘留,並在薄膜生長後或是後續退火中造成薄膜剝落,但生長溫度高於 450°C 的情況下幾乎完全脫附,在薄膜生長後或是後續退火中皆不會發生剝落;因此將生長溫度設為 450°C,能有效避免氫和氯的殘留以及鍺薄膜剝落,同時結晶品質也得到顯著提升。

對薄膜鍍率和表面粗糙度而言,氣體流量、射頻功率和處理步驟是非常重要的因素,皆會改變反應腔體中四氯化鍺蒸氣和氫原子的濃度;低氣體流量或低射頻功率的情況下,鍺薄膜容易受到來自起泡器和氣體管線中水氣或氧氣的影響,導致鍺薄膜被蝕刻並造成表面粗糙化,但適當生長參數下可以降低其影響;因此我們將氣體流量設為 40~50 sccm,射頻功率設為 40~50 W,並透過穩態處理提升薄膜鍍率,能有效降低表面粗糙度,同時滿足高薄膜鍍率的目標。

電漿輔助化學氣相沉積所生長的單晶鍺薄膜在維持低雜質含量(低於 EDX 的檢測極限)、高薄膜鍍率(78 nm/min)和低均方根粗糙度(0.786 nm)的情況下,線性缺陷密度約為  $10^4$  cm<sup>-2</sup>;所製造的 700 nm 鍺薄膜光偵測器之暗電流密度以及響應率為  $4.2 \cdot 10^{-4}$  A/cm<sup>2</sup> 和 0.08 A/W (@ 1550 nm),可能需要對表面鈍化以及後續退火進行研究,以降低元件的暗電流密度並提升響應率。

## REFERENCE

- [1] S. Mokkapati and C. Jagadish, "III-V compound SC for optoelectronic devices", *Materials Today*, vol. 12, no. 4, pp. 22-32, 2009.

- [2] V. Reboud et al., "Germanium based photonic components toward a full silicon/germanium photonic platform", *Progress in Crystal Growth and Characterization of Materials*, vol. 63, no. 2, pp. 1-24, 2017.

- [3] D. Benedikovic et al., "Silicon-germanium receivers for short-wave-infrared optoelectronics and communications", *Nanophotonics*, vol. 10, no. 3, pp. 1059-1079, 2020.

- [4] S. Zaima et al., "Growth and applications of GeSn-related group-IV semiconductor materials", *Science and Technology of Advanced Materials*, vol. 16, no. 4, p. 043502, 2015.

- [5] Y. Buzynin et al., "GaAs/Ge/Si epitaxial substrates: Development and characteristics", *AIP Advances*, vol. 7, no. 1, p. 015304, 2017.

- [6] J. Zheng et al., "Recent progress in GeSn growth and GeSn-based photonic devices", *Journal of Semiconductors*, vol. 39, no. 6, p. 061006, 2018.

- [7] Y. Du et al., "Growth of high-quality epitaxy of GaAs on Si with engineered Ge buffer using MOCVD", *Journal of Materials Science: Materials in Electronics*, vol. 32, no. 5, pp. 6425-6437, 2021.

- [8] Y. Ishikawa and S. Saito, "Ge-on-Si photonic devices for photonic-electronic integration on a Si platform", *IEICE Electronics Express*, vol. 11, no. 24, p. 20142008, 2014.

- [9] D. Eaglesham and M. Cerullo, "Dislocation-free Stranski-Krastanow growth of Ge on Si(100)", *Physical Review Letters*, vol. 64, no. 16, pp. 1943-1946, 1990.

- [10] J. Michel et al., "High-performance Ge-on-Si photodetectors", *Nature Photonics*, vol. 4, no. 8, pp. 527-534, 2010.

- [11] P. Goley and M. Hudait, "Germanium based field-effect transistors: Challenges and opportunities", *Materials*, vol. 7, no. 3, pp. 2301-2339, 2014.

- [12] H. Ye and J. Yu, "Germanium epitaxy on silicon", *Science and Technology of Advanced Materials*, vol. 15, no. 2, p. 024601, 2014.

- [13] S. Samavedam et al., "High-quality germanium photodiodes integrated on silicon substrates using optimized relaxed graded buffers", *Applied Physics Letters*, vol. 73, no. 15, pp. 2125-2127, 1998.

- [14] R. Pillarisetty et al., "High mobility strained germanium quantum well field effect transistor as the p-channel device option for low power (Vcc = 0.5 V) III-V CMOS architecture", 2010 International Electron Devices Meeting, pp. 6.7.1-6.7.4, 2010.

- [15] H. Luan et al., "High-quality Ge epilayers on Si with low threading-dislocation densities", *Applied Physics Letters*, vol. 75, no. 19, pp. 2909-2911, 1999.

- [16] J. Hartmann et al., "Reduced pressure-chemical vapor deposition of intrinsic and doped Ge layers on Si(001) for microelectronics and optoelectronics purposes", *Journal of Crystal Growth*, vol. 274, no. 1-2, pp. 90-99, 2005.

- [17] V. Shah et al., "Effect of layer thickness on structural quality of Ge epilayers grown directly on Si(001)", *Thin Solid Films*, vol. 519, no. 22, pp. 7911-7917, 2011.

- [18] Y. Yamamoto et al, "Low threading dislocation density Ge deposited on Si (100) using RPCVD", *Solid-State Electronics*, vol. 60, no. 1, pp. 2-6, 2011.

- [19] Z. Liu et al., "Diode laser annealing on Ge/Si (100) epitaxial films grown by magnetron sputtering", *Thin Solid Films*, vol. 609, pp. 49-52, 2016.

- [20] J. Zhang et al., "Modeling of continuous wave laser melting of germanium epitaxial films on silicon substrates", *Materials Express*, vol. 7, no. 5, pp. 341-350, 2017.

- [21] Z. Liu et al., "Reduction of threading dislocation density in sputtered Ge/Si(100) epitaxial films by continuous-wave diode laser-induced recrystallization", *ACS Applied Energy Materials*, vol. 1, no. 5, pp. 1893-1897, 2018.

- [22] J. Park et al., "Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping", *Applied Physics Letters*, vol. 90, no. 5, p. 052113, 2007.

- [23] J. Park et al., "Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth", *Electrochemical and Solid-State Letters*, vol. 12, no. 4, pp. 142-144, 2009.

- [24] Y. Huangfu et al., "Heteroepitaxy of Ge on Si(001) with pits and windows transferred from free-standing porous alumina mask", *Nanotechnology*, vol. 24, no. 18, p. 185302, 2013.

- [25] J. Cui et al., "High-performance microring resonator Ge-on-Si photodetectors by optimizing absorption layer length", *IEEE Photonics Journal*, vol. 12, no. 4, pp. 1-8, 2020.

- [26] H. Luan et al., "High efficiency photodetectors based on high quality epitaxial germanium grown on silicon substrates", *Optical Materials*, vol. 17, no. 1-2, pp. 71-73, 2001.

- [27] P. Bandaru et al., "Fabrication and characterization of low temperature (<450°C) grown p-Ge/n-Si photodetectors for silicon based photonics", *Materials Science* and Engineering: B, vol. 113, no. 1, pp. 79-84, 2004.

- [28] L. Colace et al., "Low dark-current germanium-on-silicon near-infrared detectors", *IEEE Photonics Technology Letters*, vol. 19, no. 22, pp. 1813-1815, 2007.

- [29] J. Osmond et al., "Ultralow dark current Ge/Si(100) photodiodes with low thermal budget", *Applied Physics Letters*, vol. 94, no. 20, p. 201106, 2009.

- [30] H. Ishii and Y. Takahashi, "Growth and etching of germanium films by chemical vapor deposition in a GeCl<sub>4</sub> H<sub>2</sub> gas system", *Journal of The Electrochemical Society*, vol. 135, no. 6, pp. 1539-1543, 1988.

- [31] J. Park et al, "Reduced-pressure chemical vapor deposition of epitaxial Ge films on Si(001) substrates using GeCl<sub>4</sub>", *Electrochemical and Solid-State Letters*, vol. 10, no. 11, pp. H313-H316, 2007.

- [32] J. Park et al., "Mechanism investigation of temperature dependent growth and etching process of GeCl<sub>4</sub> on SiGe surface: ab-initio study", 2021 International Conference on Simulation of Semiconductor Processes and Devices, pp. 233-237, 2021.

- [33] R. Kornev et al, "Application of RF (13.56 MHz) arc discharge for plasma chemical conversion of volatile chlorides of silicon and germanium.", *Plasma Physics and Technology*, vol. 6, no. 2, pp. 127-130, 2019.

- [34] R. Gresback et al, "Nonthermal plasma synthesis of size-controlled, monodisperse, freestanding germanium nanocrystals", *Applied Physics Letters*, vol. 91, no. 9, p. 093119, 2007.

- [35] Z. Holman and U. Kortshagen, "Solution-processed germanium nanocrystal thin films as materials for low-cost optical and electronic devices", *Langmuir*, vol. 25, no. 19, pp. 11883-11889, 2009.

- [36] Z. Holman et al, "Germanium and silicon nanocrystal thin-film field-effect transistors from solution", *Nano Letters*, vol. 10, no. 7, pp. 2661-2666, 2010.

- [37] A. Ahadi et al., "Controlled synthesis of germanium nanoparticles by nonthermal plasmas", *Applied Physics Letters*, vol. 108, no. 9, p. 093105, 2016.

- [38] D. A. Neamen, "Semiconductor Physics and Devices: Basic Principles (4th ed)" McGraw-Hill, 2012.

- [39] R. S. Bonilla et al, "Dielectric surface passivation for silicon solar cells: A review", Physica Status Solidi, vol. 214, no. 7, p. 1700293, 2017.

- [40] B. Son et al, "Dark current analysis of germanium-on-insulator vertical p-i-n photodetectors with varying threading dislocation density", *Journal of Applied Physics*, vol. 127, no. 20, p. 203105, 2020.

- [41] T. Chang et al, "Application of the low dielectric methyl-silsesquiazane (MSZ) as a passivation layer on TFT-LCD", *Thin Solid Films*, vol. 515, no. 3, pp. 1117-1120, 2006.

- [42] L. Colace and G. Assanto, "Germanium on silicon for near-infrared light sensing", *IEEE Photonics Journal*, vol. 1, no. 2, pp. 69-79, 2009.

- [43] Y. Ishikawa et al, "Strain-induced band gap shrinkage in Ge grown on Si substrate", *Applied Physics Letters*, vol. 82, no. 13, pp. 2044-2046, 2003.

- [44] V. Obreja et al, "Reverse leakage current instability of power fast switching diodes operating at high junction temperature", 2005 IEEE 36th Power Electronics Specialists Conference, pp. 537-540, 2005.

- [45] G. R. Savich, "Analysis and suppression of dark currents in mid-wave infrared photodetectors", *Unpublished doctoral dissertation*, University of Rochester, 2015.

- [46] M. Itano et al, "Particle removal from silicon wafer surface in wet cleaning process", *IEEE Transactions on Semiconductor Manufacturing*, vol. 6, no. 3, pp. 258-267, 1993.

- [47] W. Kern, "The evolution of silicon wafer cleaning technology", *Journal of The Electrochemical Society*, vol. 137, no. 6, pp. 1887-1892, 1990.

- [48] S. Ciampi et al, "Wet chemical routes to the assembly of organic monolayers on silicon surfaces via the formation of Si-C bonds: Surface preparation, passivation and functionalization", *Chemical Society Reviews*, vol. 39, no. 6, p. 2158, 2010.

- [49] M. Morita et al, "Growth of native oxide on a silicon surface", *Journal of Applied Physics*, vol. 68, no. 3, pp. 1272-1281, 1990.

- [50] T. Hattori, "Ultraclean Surface Processing of Silicon Wafers", Springer, 1998.

- [51] K. Jones and E. Haller, "Ion implantation of boron in germanium", *Journal of Applied Physics*, vol. 61, no. 7, pp. 2469-2477, 1987.

- [52] I. Huygens et al., "Etching of germanium in hydrogenperoxide solutions", *ECS Transactions*, vol. 6, no. 2, pp. 375-386, 2007.

- [53] L. St-Onge and M. Moisan, "Hydrogen atom yield in RF and microwave hydrogen discharges", *Plasma Chemistry and Plasma Processing*, vol. 14, no. 2, pp. 87-116, 1994.

- [54] H. Yoshiki, "Equivalent circuit model of an inductive RF discharge with a helical external coil", *Japanese Journal of Applied Physics*, vol. 39, pp. 598-601, 2000.

- [55] C. Samuell and C. Corr, "Low-pressure hydrogen plasmas explored using a global model", *Plasma Sources Science and Technology*, vol. 25, no. 1, p. 015014, 2015.

- [56] D. Rauner et al., "Investigation of the RF efficiency of inductively coupled hydrogen plasmas at 1 MHz", *AIP Conference Proceedings*, vol. 1869, no. 1, p. 030035, 2017.

- [57] A. Mohammed, and A. Abdullah, "Scanning electron microscopy (SEM): A review", *Proceedings of the 2018 International Conference on Hydraulics and Pneumatics, Baile Govora, Romania*, pp. 77–85, (2018).

- [58] H. Luan et al., "High-quality Ge epilayers on Si with low threading-dislocation densities", *Applied Physics Letters*, vol. 75, no. 19, pp. 2909-2911, 1999.

- [59] B. Alharthi et al., "Low temperature epitaxy of high-quality Ge buffer using plasma enhancement via UHV-CVD system for photonic device applications", *Applied Surface Science*, vol. 481, pp. 246-254, 2019.

- [60] E. Ameh, "A review of basic crystallography and x-ray diffraction applications", The International Journal of Advanced Manufacturing Technology, vol. 105, no. 7-8, pp. 3289-3302, 2019.

- [61] D. Cannon et al., "Tensile strained epitaxial Ge films on Si(100) substrates with potential application in L-band telecommunications", *Applied Physics Letters*, vol. 84, no. 6, pp. 906-908, 2004.

- [62] J. Ayers, "The measurement of threading dislocation densities in semiconductor crystals by X-ray diffraction", *Journal of Crystal Growth*, vol. 135, no. 1-2, pp. 71-77, 1994.

- [63] Y. Miao et al, "Evaluation of threading dislocation density of strained Ge epitaxial layer by high resolution x-ray diffraction", *Chinese Physics B*, vol. 26, no. 12, p. 127309, 2017.

- [64] M. Hiller et al, "Hydrogen-induced platelets in Ge determined by Raman scattering", *Physical Review B*, vol. 71, no. 4, p. 045208, 2005.

- [65] J. Weber et al, "Hydrogen in germanium", *Materials Science in Semiconductor Processing*, vol. 9, no. 4-5, pp. 564-570, 2006.

- [66] S. Choi et al., "Formation and suppression of hydrogen blisters in tunnelling oxide passivating contact for crystalline silicon solar cells", *Scientific Reports*, vol. 10, no. 1, p. 6972, 2020.

- [67] J. Greene, "Epitaxial crystal growth by sputter deposition: Applications to semiconductors. Part 2", *Critical Reviews in Solid State and Materials Sciences*, vol. 11, no. 3, pp. 189-227, 1983.

- [68] Z. Liu et al, "Epitaxial growth of Ge on Si by magnetron sputtering", *in Epitaxy*, Intech, 2018.

- [69] A. Keita et al, "Highly retarded crystallization in hydrogenated amorphous germanium; emergence of a porous nanocrystalline structure", *Thin Solid Films*, vol. 615, pp. 145-151, 2016.

- [70] S. Sugahara et al., "A proposed atomic-layer-deposition of germanium on Si surface", *Japanese Journal of Applied Physics*, vol. 36, pp. 1609-1613, 1997.

- [71] V. Le Thanh, "Fabrication of SiGe quantum dots: a new approach based on selective growth on chemically prepared H-passivated Si(100) surfaces", *Thin Solid Films*, vol. 321, no. 1-2, pp. 98-105, 1998.

- [72] V. Yang et al, "Crack formation in GaAs heteroepitaxial films on Si and SiGe virtual substrates", *Journal of Applied Physics*, vol. 93, no. 7, pp. 3859-3865, 2003.

- [73] Z. Liu, "Virtual Ge substrates for high efficiency III-V solar cells", *Unpublished doctoral dissertation*, The University of New South Wales, 2014.

- [74] X. Zhang et al., "Thermal desorption of ultraviolet-ozone oxidized Ge(001) for substrate cleaning", *Journal of Vacuum Science & Technology A: Vacuum Surfaces and Films*, vol. 11, no. 5, pp. 2553-2561, 1993.

- [75] K. Prabhakaran and T. Ogino, "Oxidation of Ge(100) and Ge(111) surfaces: an UPS and XPS study", *Surface Science*, vol. 325, no. 3, pp. 263-271, 1995.

- [76] R. Kaiser et al., "Germanium substrate loss during thermal processing", *Microelectronic Engineering*, vol. 88, no. 4, pp. 499-502, 2011.

- [77] L. de los Santos Valladares et al., "Thermal oxidation of amorphous germanium thin films on SiO<sub>2</sub> substrates", *Semiconductor Science and Technology*, vol. 31, no. 12, p. 125017, 2016.

- [78] H. Shih et al., "Ultralow threading dislocation density in GaN epilayer on near-strain-free GaN compliant buffer layer and its applications in hetero-epitaxial LEDs", *Scientific Reports*, vol. 5, no. 1, p. 13671, 2015.