國立臺灣大學理學院應用物理學研究所

# 碩士論文

Graduate Insititute of Applied Physics College of Science National Taiwan University Master Thesis

原子層成長氧化層/砷化鎵之介面特性研究 Interfacial Electrical Properties of Y<sub>2</sub>O<sub>3</sub>/GaAs and Al<sub>2</sub>O<sub>3</sub>/GaAs MOS capacitors

張從文

Tsung-Wen Chang

指導教授: 洪銘輝 博士

郭瑞年 博士

Advisor : Minghwei Hong, Ph.D.

Raynien Kwo, Ph.D.

中華民國 106 年7月

July 2017

# Acknowledgement

首先要非常感謝我的指導教授—洪銘輝老師與郭瑞年老師還有國家奈米研究 實驗室的陳博士的幫助,在這三年的期間,老師以開放的方式讓我們發揮所長,以 嚴謹的方式指導我們完成碩士論文;也謝謝郭瑞年老師、陳仕鴻老師老師抽空幫我 口試,並給我許多寶貴的意見,在口試期間聽到不少實用的建議及可以改進的方向。

謝謝研究室的大家,包括已經畢業的大雄、小傅,還有博宇、延勳、獻文、承 曄、毓傑,研究室裡大大小小的事情,都能有效率的一起解決,這段期間是非常難 得的合作經驗。在研究的方向還有進度上也感謝你們督促我給我建議。也感謝常常 陪伴給予打氣的朋友,在這段期間的鼓勵及各式各樣的聊天紓壓。

最後要謝謝家人,在接近口試的期間,常常的那段日子,感謝家人一直注意我 的身體健康,給予各種關心,是最強的後盾!

張從文 謹致

于國立台灣大學應用物理學研究所

中華民國一零六年八月二十一日

# 摘要

因為相對高的電子遷移率,砷化鎵被視為取代矽基材的重要材料,因為其和矽 相對小的晶格差,而被廣泛的研究。同時,原子層沉積由於其相當好的覆蓋性以及 成長速度控制,也已經被產業廣泛的使用。

和產業上使用矽和二氧化矽之介面不同,砷化鎵和高介電係數氧化層很難維 持良好的介面特性,因此電容電壓量測下,頻率分散是很常見的現象,此篇論文致 力於研究邊界缺陷和介面缺陷在不同氧化層在砷化鎵上的行為。頻率分散主要由 於穿隧效應去和半導體載子進行交換,因次對溫度不應該有響應。然而在多數報導 中,頻率分散對溫度的響應均被觀測到。

本實驗使用原子層沉積氧化鋁和氧化釔成長在砷化鎵上,量測電容電壓、電容 頻率、電導電壓、電流電壓及准靜態電容電壓等方式分析介面缺陷和邊界缺陷在電 性上的表現。從中的分析可以得知,氧化釔以及砷化鎵顯示相當良好的介面特性, 相反的氧化鋁以及砷化鎵的介面態位密度則相當高。同時在變溫量測時,頻率分散 在氧化釔以及砷化鎵的電壓電容特性隨著溫度改變,經過模擬和實驗的比較可以 得知,此現象無法以已經被發表之隨溫度變化的缺陷截面積解釋。本論文提出嚴謹 的計算及模擬顯示出此現象應歸因於隨溫度變化的氧化釔砷化鎵能量差,成功的 解釋了隨溫度變化的頻率分散。

關鍵字:頻率分散、砷化鎵、氧化釔、邊界缺陷、氧化鋁。

II

# Abstract

Due to the relatively high electron mobility, GaAs and InGaAs are the leading candidates as n-channel materials in post-Si generation. In<sub>0.53</sub>Ga<sub>0.47</sub>As inversion channel n-MOSFETs have been demonstrated promising device performance using atomic-layer-deposited (ALD) high-k dielectrics. [1] However, a lattice constant of 5.87Å of In<sub>0.53</sub>Ga<sub>0.47</sub>As is difficult to be integrated onto the platform a Si(001) wafer. Instead, GaAs, with a lattice constant of 5.65Å, is about half of the lattice mismatch between In<sub>0.53</sub>Ga<sub>0.47</sub>As and Si. Owing to the advantages mentioned above, GaAs and low-In content InGaAs metal-oxide- semiconductor (MOS) capacitors have been intensively studied, aiming for developing high speed and low power devices. Besides, with excellent uniformity and conformal coverage in nanometer thick film growth, atomic layer deposition (ALD) has been widely employed in depositing high-k dielectrics for MOSFETs since the 45 nm node. Therefore, as an urgent issue, intensive efforts in ALD high-k dielectrics on GaAs(001) have been carried out to characterize and perfect these interfaces.

Frequency dispersion (FD) is an important index for characterizing oxidesemiconductor interfaces. ALD-oxides on GaAs usually give a large FD in capacitancevoltage (CV) curves of the MOS capacitors (MOSCAPs), particularly on n-GaAs. [2,3] Research efforts have been carried out to explain the origin of the large FD in oxides/(In)GaAs interfaces. A model assuming an exponentially decaying spatial distribution of traps from the oxide/semiconductor interface into the bulk oxide layer explained the large FD of CVs at accumulation by the interfacial traps. [4] However, this model failed to explain the dispersion in the low frequency range and the temperaturedependent dispersion. Later, a distributed border trap model based on tunneling mechanism between the oxide/semiconductor interface and the trap states in gate dielectric accounted for the large FD of CVs and conductance (GV) at accumulation. [5] Also, Chen et al combined these two models to fit the CV and GV characteristics in depletion region to inversion region. [6] However, most reported high-k/III-V systems yielded high trap densities up to  $10^{13} \text{ eV}^{-1}\text{cm}^{-2}$  as well as undesired interfacial native oxides, such that the corresponding analyses on capacitance-frequency (CF) characteristics lead to unconvincing results. [7,8] The very few high-k/GaAs(001) heterostructures reported with low interfacial trap densities (*D<sub>it</sub>*'s) are ultra-high vacuum (UHV) e-beam evaporated Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) and ALD-Y<sub>2</sub>O<sub>3</sub> on GaAs(001). [9]

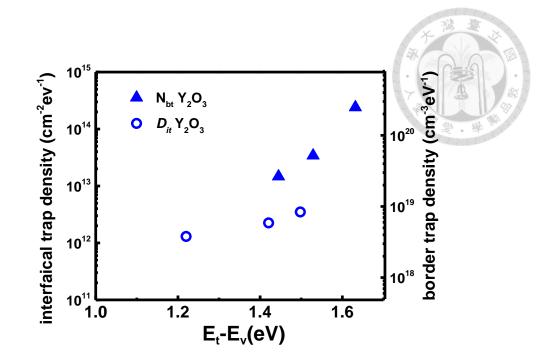

In the thesis, Al<sub>2</sub>O<sub>3</sub> and Y<sub>2</sub>O<sub>3</sub> were atomic-layer-deposited (ALD) on molecular beam epitaxy grown GaAs-(4×6). Oxide capacitance was carefully extracted by consider the accumulation layer thickness in GaAs. The oxide/semiconductor interface were characterized using CV characteristic, CF characteristic, QSCV measurement and conductance method. The CF analyses are in agreement with the conclusions given by QSCV and GV measurements for both hetero-structures. Both systems exhibit similar border trap densities, but greatly different  $D_{it}$ 's. Moreover, the  $D_{it}$  spectrum without mid gap peak is observed in Y<sub>2</sub>O<sub>3</sub>/GaAs samples. Showing low density of states below  $10^{12}$ cm<sup>-2</sup>eV<sup>-1</sup>, Y<sub>2</sub>O<sub>3</sub>/GaAs hetero-structure is promising for achieving inversion channel MOSFET with subthreshold swing under 75mV/dec. Another important issue discussed in the thesis is the temperature dependence frequency dispersion. After the simulation, the observed temperature dependence of frequency dispersion pointed out a temperature dependent barrier height, which is further confirmed by J-E characteristic. We concluded that the barrier height is temperature dependent, and should be extracted by electrical measurement. Moreover, the commonly observed temperature dependent frequency dispersion result from the temperature dependent barrier height (tunneling attenuation coefficient). Thus, the border trap density should be plotted with the right barrier height. Keyword: GaAs, Y<sub>2</sub>O<sub>3</sub>, Al<sub>2</sub>O<sub>3</sub>, border traps, frequency dispersion

| Contents                                              | · · · |

|-------------------------------------------------------|-------|

| AcknowledgementI                                      | X.    |

| 摘要                                                    | ÿ     |

| Abstract III                                          |       |

| ContentsVI                                            |       |

| List of Figures                                       |       |

| List of TablesXI                                      |       |

| 1. Introduction                                       |       |

| 1.1 Background1                                       |       |

| 1.2 Ultimate CMOS III-V compounds                     |       |

| 1.3 High-к dielectric on GaAs 4                       |       |

| 1.4 Frequency dispersion and border trap analysis     |       |

| 2. Theory and Instruments                             |       |

| 2.1 Film deposition methods                           |       |

| 2.1.1 Molecular Beam Epitaxy (MBE)                    |       |

| 2.1.2 Atomic layer deposition (ALD) 10                |       |

| 2.2 Metal-oxide-semiconductors Capacitors (MOSCAPs)11 |       |

| 2.2.1 Measurement equipment 12                        |       |

| 2.2.2 Conduction mechanisms in dielectric films       |       |

| 2.2.3 Ideal CV characteristics                        |       |

| 2.2.4 $D_{it}$ extraction methods                     |       |

| 2.3 Interfacial trap model and border trap model      |       |

| 3. Experiments Procedures                             |       |

| 3.1 Sample Preparation                                |       |

| 3.2 Preparation of GaAs (001)-4×6 surface                                                                |

|----------------------------------------------------------------------------------------------------------|

| 3.3 Atomic-layer-deposited high-к 29                                                                     |

| 3.4 Post deposition annealing condition                                                                  |

| 3.5 Metal electrode deposition                                                                           |

| 3.6 Electrical measurement                                                                               |

| 4. Results and Discussion                                                                                |

| 4.1 Comparison of CV characteristics of $Y_2O_3$ and $Al_2O_3$ passivated GaAs                           |

| surface                                                                                                  |

| 4.1.1 CV characteristics                                                                                 |

| 4.1.2 Oxide capacitance and electrical parameters                                                        |

| 4.2 CF charcteristics and Simulations 44                                                                 |

| 4.3 QSCV and conductance measurement                                                                     |

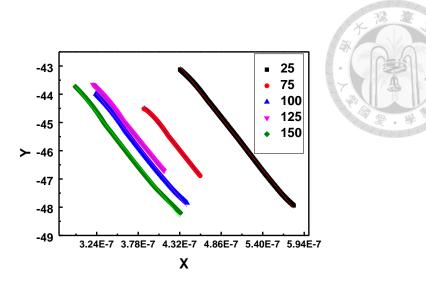

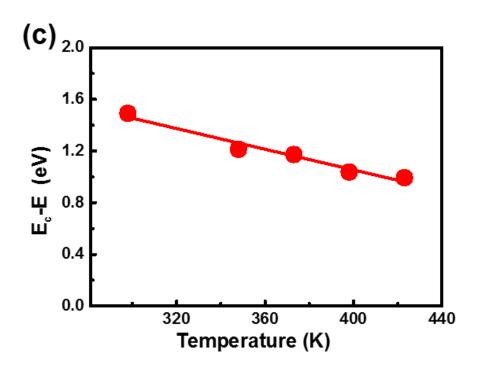

| 4.4 Multiple temperature measurement of Y <sub>2</sub> O <sub>3</sub> /n-GaAs                            |

| 4.4.1 Temperature dependentce of CV and CF characteristics and barrier                                   |

| lowering                                                                                                 |

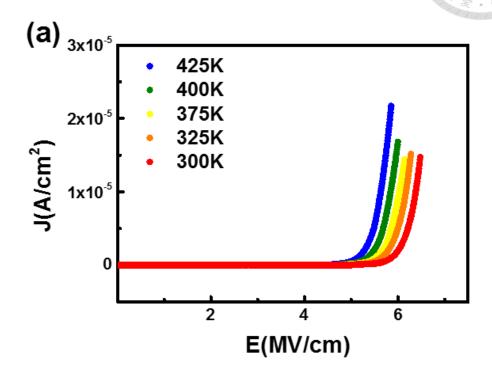

| 4.4.2 JE characteristics and barrier height lowering                                                     |

| 5. Conclusion                                                                                            |

| Reference                                                                                                |

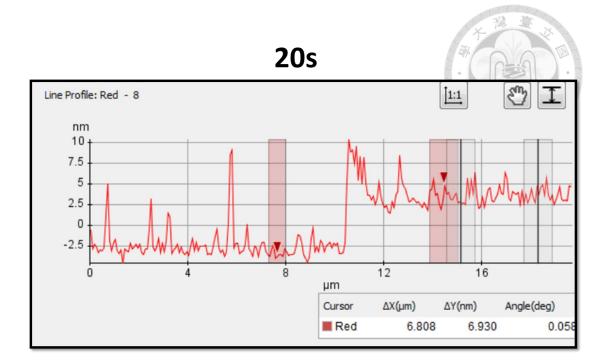

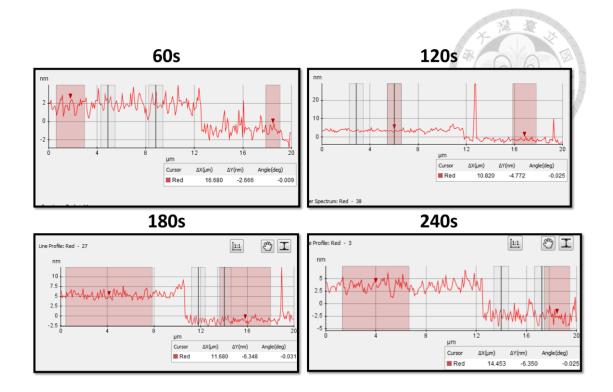

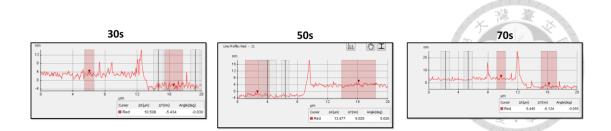

| Appendix- Dry etch of Al <sub>2</sub> O <sub>3</sub> /Y <sub>2</sub> O <sub>3</sub> bi-layer oxide stack |

# List of Figures

| List of Figures                                                                   |

|-----------------------------------------------------------------------------------|

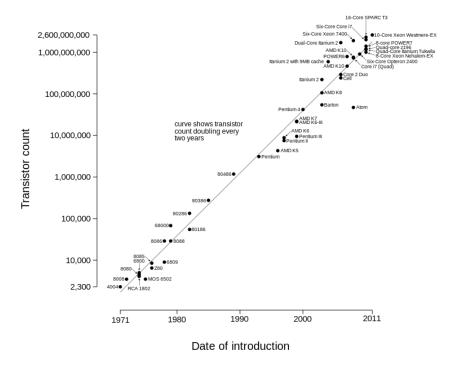

| Figure 1-1 The Moore's Law and CPU transistors counts from 1971 to 2011 2         |

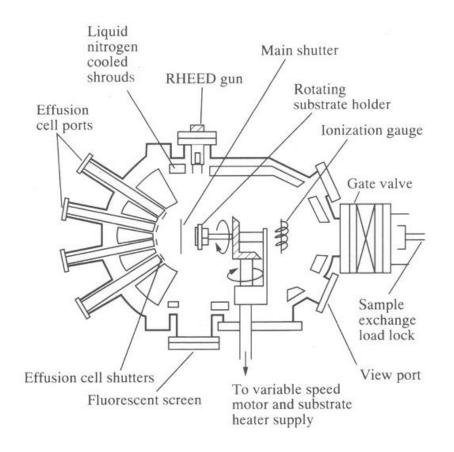

| Figure 2-1 The typical construction of a MBE system                               |

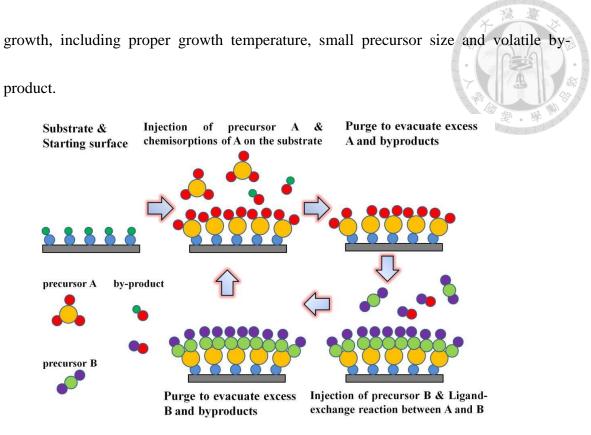

| Figure 2-2 Illustration of ALD reaction cycle11                                   |

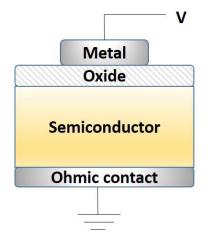

| Figure 2-3 Typical MOSCAP 12                                                      |

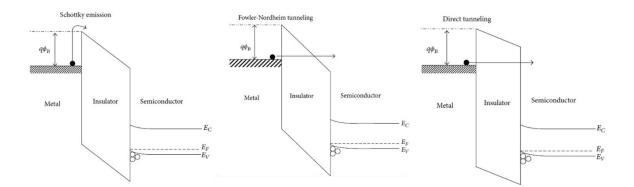

| Figure 2-4 Band diagram of Shottky emission, FN tunneling and direct tunneling.   |

|                                                                                   |

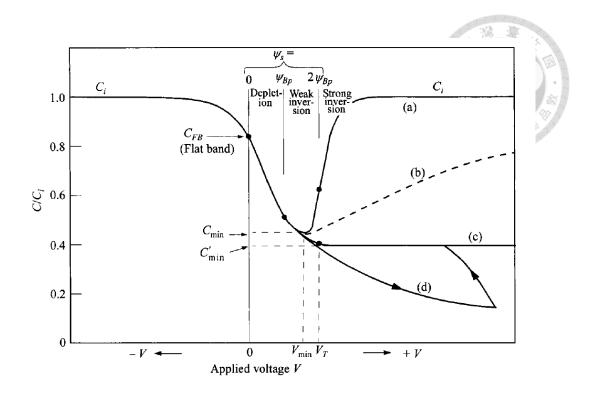

| Figure 2-5 MOS CV curves at (a) low frequency (b) intermediate frequency (c) high |

| frequency (d) deep depletion 19                                                   |

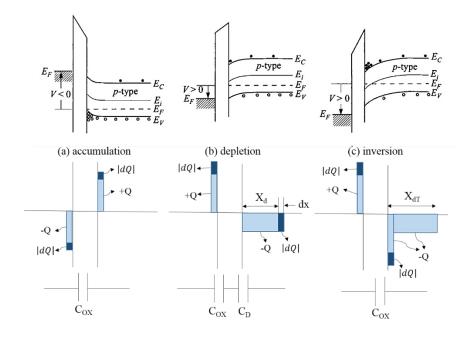

| Figure 2-6 Band diagram of ideal MOSCAP at (a) accumulation region (b) depletion  |

| region (c) inversion region 19                                                    |

| Figure 2-7 Equivalent circuits including interface trap effect                    |

| Figure 2-8 Equivalent circuits at high frequency 21                               |

| Figure 2-9 Equivalent circuits at low frequency                                   |

| Figure 2-10 Illustration of Gray-Brown method                                     |

| Figure 2-11 Schematic diagram of tunneling between border traps in dielectric and |

| the conduction band of semiconductor                                              |

| Figure 2-12 RC equivalent circuit for border trap model                           |

| Figure 3-1 Schematic diagram of multi-chamber MBE/ALD/analyses UHV system         |

|                                                                                   |

| Figure 3-2 Schematic cross-sectioin of GaAs MOSCAP with Ni metal gate and         |

| Ti/Au back electrode                                                              |

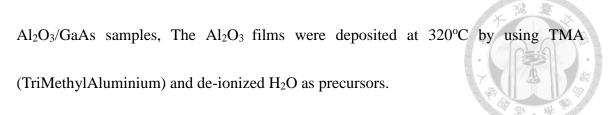

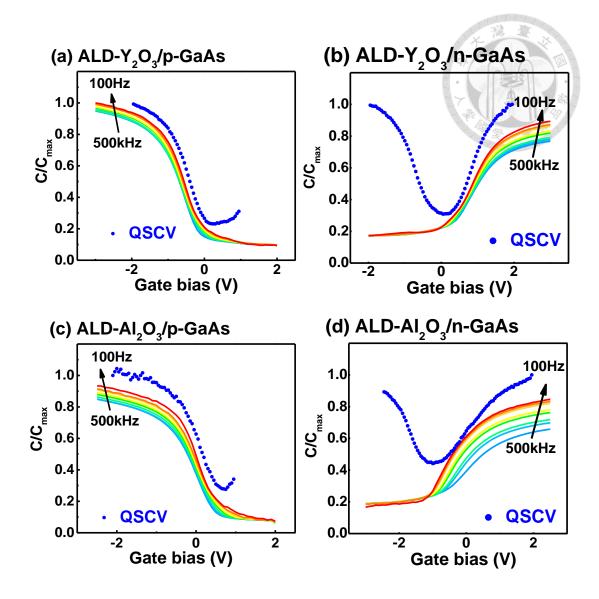

| Figure 4-1 CVs of MOSCAPs of ALD- $Y_2O_3$ on (a) p-type and (b) n-type GaAs, and |

| ALD-Al <sub>2</sub> O <sub>3</sub> on (c) p-type and (d) n-type GaAs              |

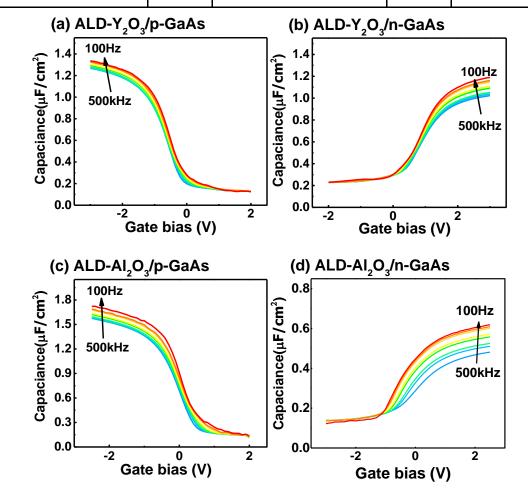

| Figure 4-2 CVs of ALD (a) $-Y_2O_3$ and (b) $-Al_2O_3$ on n-GaAs measured at 150°C                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                               |

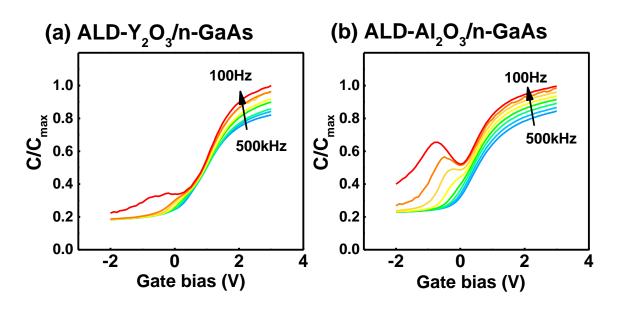

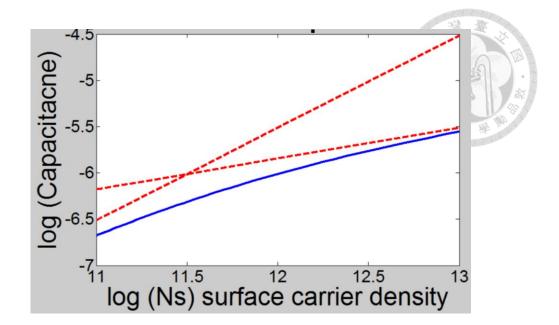

| Figure 4-3 (a) p-type (b) n-type accumulation capacitance versus surface carrier                                                              |

| density. Blue line is the $C_{total}$ versus carrier density. While the red lines are the                                                     |

| $C_{acc}^{DOS}$ and $C_{acc}^{thickness}$ versus carrier density, respectively                                                                |

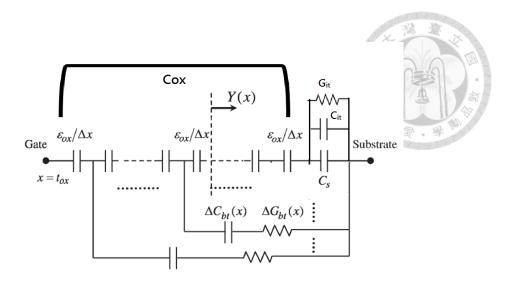

| Figure 4-4 Equivalent circuit combined border traps and interfacial traps 45                                                                  |

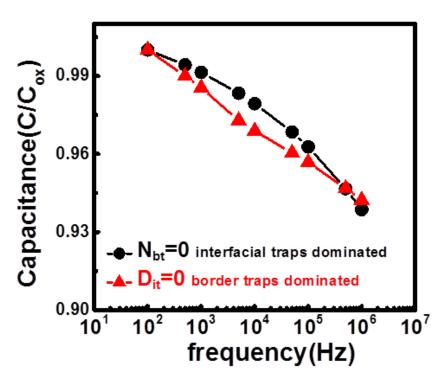

| Figure 4-5 The simulation of C-log(F) characteristics. The black line corresponds to                                                          |

| a interfacial-trap dominated C-log(F) curve with a simulation parameter Nbt (border trap                                                      |

| density) set to be zero, whereas the red line corresponds to a border-traps dominated C-                                                      |

| log(F) curve with a simulation parameter $D_{it}$ (interfacial trap density) set to be zero 46                                                |

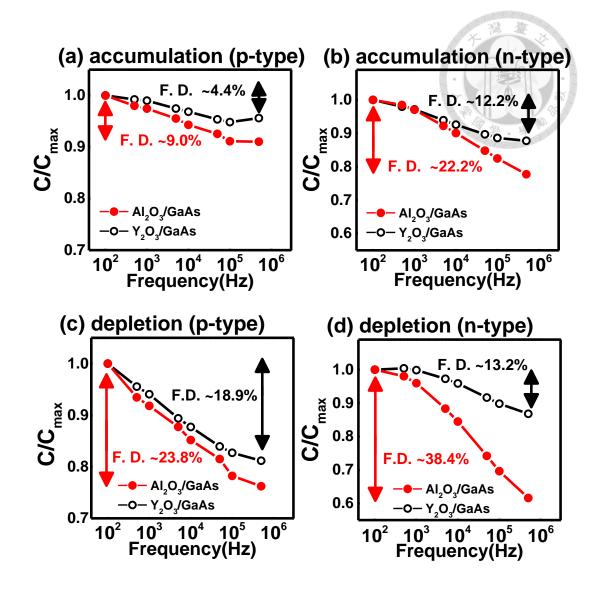

| Figure 4-6 CFs of ALD-Y <sub>2</sub> O <sub>3</sub> and -Al <sub>2</sub> O <sub>3</sub> on (a) p-type and (b) n-type GaAs in                  |

| accumulation region, and (c) p-type and (d) n-type GaAs in depletion region                                                                   |

| Figure 4-7 CVs and QSCVs of MOSCAPs of ALD- $Y_2O_3$ on (a) p-type and (b) n-                                                                 |

| type GaAs, and ALD-Al <sub>2</sub> O <sub>3</sub> on (c) p-type and (d) n-type GaAs                                                           |

| Figure 4-8 <i>D<sub>it</sub></i> spectra of ALD-Y <sub>2</sub> O <sub>3</sub> and -Al <sub>2</sub> O <sub>3</sub> on GaAs by QSCVs and GVs 53 |

| Figure 4-9 CVs of Y <sub>2</sub> O <sub>3</sub> /n-GaAs at different temperature 55                                                           |

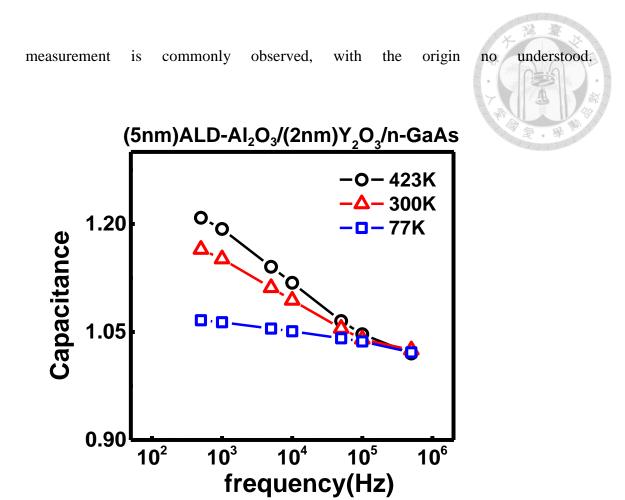

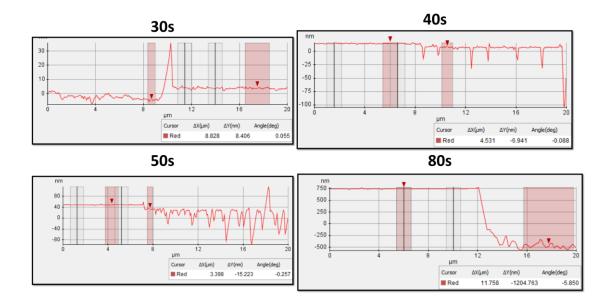

| Figure 4-10 CF characteristic of Y <sub>2</sub> O <sub>3</sub> /n-GaAs at different temperature                                               |

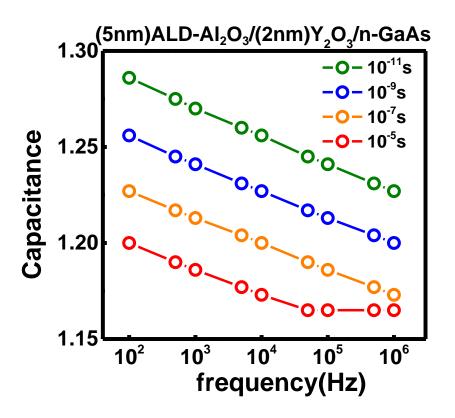

| Figure 4-11 CF simulation with fixed parameter of dielectric constant $\kappa$ =20, $\kappa$ =                                                |

| $7nm^{-1}$ , $C_s = 3 \times 10^{-6}F$ , $N_{bt} = 1 \times 10^{20}cm^{-3}$ , $C_{ox} = 1.41 \times 10^{-6}F$ and traps                       |

| time constant of $1 \times 10^{-11}s$ , $1 \times 10^{-9}s$ , $1 \times 10^{-7}s$ and $1 \times 10^{-5}s$ are plotted in                      |

| red, orange, blue and olive, respectively                                                                                                     |

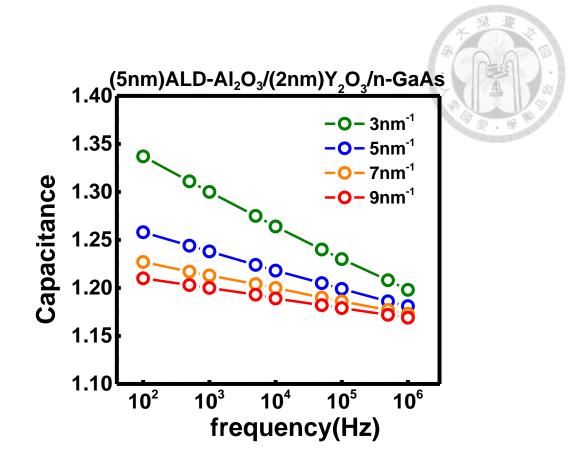

| Figure 4-12 CF simulation with fixed parameter of dielectric constant $\kappa$ =20, traps                                                     |

log scale, on the left and right axis, respectively. The blue triangles show the border traps density, while the blue hollow circles show the interfacial trap density, respectively.... 66

# List of Tables

| List of Tables                                                                                          |

|---------------------------------------------------------------------------------------------------------|

| Table 1-1 List of electrical and basic parameter of semiconductors       4                              |

| Table 1-2 List of common used dielectric properties    5                                                |

| Table 1-3 Frequency dispersion in C-V measurement of different works7                                   |

| Table 4-1 Frequency dispersion in C-V measurement of different works                                    |

| Table 4-2 Electrical parameter calculated by using estimation of Cox=Cmax                               |

| Table 4-3 Electrical parameter calculated by using estimation of $C_{ox}$ with the first                |

| calculation                                                                                             |

| Table 4-4 List of barrier height versus temperature between Y <sub>2</sub> O <sub>3</sub> and n-GaAs 65 |

#### 1. Introduction

#### **1.1 Background**

In the past 40 years, SiO<sub>2</sub>/Si has served as the transistor gate dielectric and channel materials in Si CMOS technology. Aiming for higher speed, lower power consumption and higher transistor density, the Si CMOS technology is kept scaling down. The so called "Moore's Law" was observed and described the in by Gordon E. Moore in 1965 as shown in **Fig 1-1**. SiO<sub>2</sub> thickness has been scaling down at 0.7 per generation until 130nm nodes, as at 90nm and 65nm nodes the SiO<sub>2</sub> ran out of atoms. The scaling of SiO<sub>2</sub> gate dielectric thickness suffers from large gate leakage. To keep Moore's Law, the semiconductors industry face unavoidable challenge to find an alternative dielectric to replace SiO<sub>2</sub>. The gate leakage current is related to the physical thickness of gate oxide, while the capacitance is proportional to dielectric constant divided by gate oxide thickness. Therefore, the semiconductor industry search for an alternative insulting material with a higher relative dielectric constant to replace SiO<sub>2</sub>. Note that the material have to be compatible with CMOS technology and high thermal stability and low density of states in contact with channel material Silicon.

Owing to the high dielectric constant, the HfO<sub>x</sub> based high- $\kappa$  became the leading candidates for replacing the long-standing SiO<sub>2</sub>. HfO<sub>2</sub> benefit from forming stable

interfacial layer of SiO<sub>x</sub> and HfSiO<sub>x</sub> with Si, and exhibit good interface with Si. However, Fermi-level pinning occurs at HfO<sub>x</sub>-poly-Si gate. To avoid the Hf-Si bonds, The doped poly-Si gate is replaced by metal gate to prevent poly-Si gate depletion. [10] In 2007, Hfbased oxide as gate dielectric and metal gate has been employed in Intel's 45nm node, which is the demonstration of working 45nm processor integrating high-k with metal gate. The breakthrough of HKMG technology has helped to continue the scaling down of semiconductor industry.

Microprocessor Transistor Counts 1971-2011 & Moore's Law

**Fig 1-1** The Moore's Law of CPU transistor counts against dates of introduction; note the logarithmic vertical scale; the line corresponds to exponential growthwith transistor count doubling every two years.

#### 1.2 Ultimate CMOS: III-V compounds

For ultimate CMOS, the performance cannot be simply fulfilled by using Si as channel material even with HKMG technology. The drive current in saturation region of MOSFET can be simply expressed by  $I_{Dsat}=W_gQ\mu E$ , where  $W_g$  is the gate width, Q is the surface charge,  $\mu$  is the carrier mobility. Compared to Si channel, III-V compounds possess high electron or hole mobility for future MOS transistor application as shown in **Table 1-2**. In<sub>0.53</sub>Ga<sub>0.47</sub>As and GaAs with more than five times larger electron mobility than Si, is promising for high speed and high performance MOS device. Owing to high electron mobility and direct band gap, GaAs and InGaAs has been leading candidates to replace long-standing Si channel.

To replace the Si channel in Si CMOS technology, there are serval challenges must be overcome as follows. (1) Small lattice mismatch with Si for integration with mature Si CMOS technology. (2) Thermal stability interface with high dielectric constant oxides compatible with CMOS process. (3) Low interfacial density of states with high dielectric constant gate dielectric. (4) Suitable band gap to avoid short channel effect such as bandto-band tunneling. Therefore, GaAs is outstanding in III-V compounds with only 4% lattice mismatch with Si, 8500cm<sup>2</sup>/V-s electron mobility and 1.424eV band gap energy. Although In<sub>0.53</sub>Ga<sub>0.47</sub>As has extremely high electron mobility of 12000 cm<sup>2</sup>/V-s, but large lattice mismatch with Si and small band gap energy is not suitable for future CMOS technology.

Over 40 years, the excellent Si/SiO<sub>2</sub> interface is the backbone of semiconductor industry. The ability to continuous downscaling of the dimension of Si-based MOSFET is attributed to SiO<sub>2</sub>'s superior electrical and material properties. Which are low leakage current, ultra high thermal stability and low interfacial traps with Si. To replace the Si channel with III-V compounds, the excellent interfacial properties is required.

|                     | symbo            | Si                 | Ge                 | GaAs                | InAs               | In <sub>0.53</sub> G | unit                 |

|---------------------|------------------|--------------------|--------------------|---------------------|--------------------|----------------------|----------------------|

|                     | 1                |                    |                    |                     |                    | ao.47As              |                      |

| Dielectric constant | κ                | 11.7               | 16.2               | 12.9                | 15.15              | 13.9                 | -                    |

| Band gap energy     | Eg               | 1.12               | 0.661              | 1.424               | 0.354              | 0.74                 | eV                   |

| Intrinsic           | ni               | $1 \times 10^{10}$ | 2×10 <sup>13</sup> | $2.1 \times 10^{6}$ | 1×10 <sup>15</sup> | 6.3×10 <sup>11</sup> | cm <sup>-3</sup>     |

| carrier             |                  |                    |                    |                     |                    |                      |                      |

| concentration       |                  |                    |                    |                     |                    |                      |                      |

| Electron mobility   | $\mu_{e}$        | 1400               | 3900               | 8500                | 40000              | 12000                | cm <sup>2</sup> /V-s |

| Hole mobility       | $\mu_{\rm h}$    | 450                | 1900               | 400                 | 500                | 300                  | cm <sup>2</sup> /V-s |

| Electron effective  | m <sup>*</sup> e | 0.98m*             | 1.6 m*             | 0.063 m*            | 0.023 m*           | 0.041m*              | -                    |

| mass                |                  |                    |                    |                     |                    |                      |                      |

| Hole effective      | $m_{h}^{*}$      | 0.49               | 0.33               | 0.51 m*             | 0.41 m*            | 0.45 m*              | -                    |

| mass                |                  | m*                 | m*                 |                     |                    |                      |                      |

| Lattice mismatch    |                  | 0%                 | 4.17%              | 4.08%               | 11.55%             | 8.06%                |                      |

| with Si             |                  |                    |                    |                     |                    |                      |                      |

**Table 1-1**. List of electrical and basic parameter of semiconductors.

## 1.3 High-k dielectric on GaAs

Unlike the case of SiO<sub>2</sub> on Si, the native oxide of GaAs are not stable and leaky.

Different methods and treatments have been adopted to oxidize GaAs surface, including

thermal, anodic, and plasma oxidation of GaAs. [11] But, the As<sub>2</sub>O<sub>3</sub> and As<sub>2</sub>O<sub>5</sub> on GaAs surface cause the Fermi-level pinning at the interface. The first encouraging result to unpin GaAs Fermi-level is Gadolinium Oxide on GaAs. Lateral, different kinds of high- $\kappa$  dielectric on GaAs had been reported, including La<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> on GaAs. Among all the reported works, large mid-gap Dit(E) peak > 10<sup>13</sup>cm<sup>-2</sup>eV<sup>-1</sup> and large frequency dispersion in capacitance-voltage measurement is still observed.

To find a suitable gate dielectric on GaAs, serval different high-k material are listed as **Table 1-2**. Aiming for high performance MOS device, the high- $\kappa$ /GaAs heterostructure should have some critical properties. Sufficient valance band offset and conduction band offset between high- $\kappa$  material and GaAs is necessary to prevent gate leakage under large bias. In **Table 1-3**, great potential of rare-earth oxide is presented with high dielectric constant and enough band offset.

| Dielectric                               | SiO <sub>2</sub> | Al <sub>2</sub> O <sub>3</sub> | HfO <sub>2</sub> | Gd <sub>2</sub> O <sub>3</sub> | Y <sub>2</sub> O <sub>3</sub> | La <sub>2</sub> O <sub>3</sub> |

|------------------------------------------|------------------|--------------------------------|------------------|--------------------------------|-------------------------------|--------------------------------|

| Dielectric constant κ                    | 3.9              | 9                              | 20               | 14                             | 20                            | 30                             |

| Band gap (Eg)                            | 8.9              | 8.7                            | 5.7              | 5.8                            | 5.8                           | 4.3                            |

| Conduction band offset<br>with GaAs (eV) | 3.3              | 3.2                            | 1.5              | 1.55                           | 2.2                           | 2.4                            |

| Valance band offset with<br>GaAs (eV)    | 4.2              | 4.1                            |                  | 2.85                           | 2.1                           | 0.5                            |

Table 1-2. List of common used dielectric properties

### 1.4 Frequency dispersion and border traps analysis

It is well-known that the traps level inside semiconductor bandgap can reduce the device performance and cause Fermi-level pinning. The subthreshold swing will reflect the density of states inside GaAs bandgap. Therefore, lots of characterization methods have been developed in order to probe the trap density inside GaAs bandgap. But, with low conduction band density of states, the traps inside conduction band could drastically reduce GaAs based n-MOSFET performance. The traps inside conduction band could result in insufficient mobility far from theory prediction and low inversion channel concentration. So, we are looking forward to characterize the traps inside the conduction band. Some reliable results have been carried out to probe the traps inside conduction band. For example, split C-V and Hall measurement have been measured, and the difference between two measurements is attributed to traps response. [12] The distribution of *Dit* inside the conduction band was then evaluated by combining the split C-V method and Hall measurement. However, the fast traps and slow traps cannot be distinguished using the above method. Fortunately, the frequency dispersion at accumulation in C-V measurement can provide us some useful information.

Frequency dispersion (F. D.) in C-V measurement arise when trap states can communicate with semiconductors energy band. Therefore, F. D. is used for oxide/semiconductor interfacial properties characterization. Unlike the ideal C-V characteristic of SiO<sub>2</sub>/Si case free from frequency dispersion, large frequency dispersion is usually observed in C-V characteristic of high-k oxide/GaAs MOS devices as listed in

Table 1-3. To understand the physical origin of frequency dispersion, different model has

been carried out to explain the observed phenomenon. It was not until Hasegawa proposed the high density of interfacial states for anodic oxides on GaAs surface that workers generally ascribe the anomaly to a high density of interfacial states. [4] However, at accumulation region, the time constant of interfacial traps is far too short for the range of frequencies below 1kHz. On the other hands, traps inside the gate insulator close to interface can communicate with conduction or valance band through tunneling, and do have longer time constant consistent with experimental data. Yu Yuan has proposed a distributed model based on tunneling mechanism for border traps to explain the observed frequency dispersion. [5]

| Structure                                                             | <b>F. D.</b> | Structure                                                             | <b>F. D.</b> | reference |

|-----------------------------------------------------------------------|--------------|-----------------------------------------------------------------------|--------------|-----------|

| Al <sub>2</sub> O <sub>3</sub> /p-GaAs                                | 11.1%        | Al <sub>2</sub> O <sub>3</sub> /n-GaAs                                | 52.8%        | [13]      |

| Al <sub>2</sub> O <sub>3</sub> /AlN/p-GaAs                            | 13.4%        | Al <sub>2</sub> O <sub>3</sub> /AlN/n-GaAs                            | 26.5%        | [14]      |

| Al <sub>2</sub> O <sub>3</sub> /p-GaAs                                | 9.0%         | Al <sub>2</sub> O <sub>3</sub> /n-GaAs                                | 22.2%        | This work |

| Al <sub>2</sub> O <sub>3</sub> /Y <sub>2</sub> O <sub>3</sub> /p-GaAs | 4.4%         | Al <sub>2</sub> O <sub>3</sub> /Y <sub>2</sub> O <sub>3</sub> /n-GaAs | 12.2%        | This work |

Table 1-3. Frequency dispersion in C-V measurement of different works

#### 2. Theory and Instruments

#### 2.1 Film deposition methods

#### 2.1.1 Molecular Beam Epitaxy (MBE)

Molecular beam epitaxy (MBE) was first developed by A. Y. Cho and J. R. Arthur in early 1970s. MBE is a process for growing thin, epitaxy films of a wide variety of materials, including semiconductors, oxides and toplogical insulators. In the MBE process, the beam of atoms or molecules in an ultra-high-vacuum ( $\sim 10^{-10}$ torr) are incident upon a heated crystal to form a crystalline layer. Note that the composition of the films can be changed rapidly, and produce almost atomically abrupt interface. The ability of producing a large range of unique structure such as supper-lattice and quantum-well device is benefit from the cleanliness of the growth environment, precise control of composition and excellent thickness control.

The growth rate for MBE is determined by the source flux, so the composition of the grown epi-layer and doping concentration can be estimated by the source evaporation rate. To grow a high quality thin film, the time for deposition of a monolayer should be longer than the surface-diffusion-incorporation time to avoid the incorporated atoms from being buried by the incoming monolayer. Moreover, the substrate temperature is an important parameter during MBE process. Growth under low substrate temperature, the

rearrangement is not sufficient and lead to poor crystal quality. If the substrate temperature is too high, atoms may desorb from surface. Growth at an adequate growth temperature, atoms have enough energy to move to the proper position and not desorb from the surface.

In Fig 2-1, a typical MBE system is shown. During the growth, effusion cells are heated by a foil heater. Reflective high energy electron diffraction (RHEED) is used for define the crystal quality and the surface structure of a growing film. And liquid nitrogen cooled shrouds and cooling equiment with fluid water are the coolant.

Fig. 2-1 The typical construction of a MBE system.

#### 2.1.2 Atomic layer deposition (ALD)

Atomic-layer-deposition (ALD) is a thin film technology based on surface controlled thin film deposition. The technique was first developed for nanolaminate insulators and zinc sulfide phosphor films for thin film electroluminescent displays. And now become a powerful resource for highly competitive products and advance nanotechnology research. ALD is well-known for its precise thickness control, pin hole free and excellent conformal thin films for 3-D structure device. [15]

Unlike the conventional chemical vapor deposition (CVD), ALD is a self-limiting growth mechanism. Based on the self-limiting reactions, ALD have superior conformity on high aspect ratio structure. A general ALD process consists of four steps as shown in Fig. 2-2, including (1) pulse of the precursor A into the chamber and react with the substrate through a self-limiting process that only one monolayer is formed at the surface, (2) purge of inert gas such as nitrogen to carry out the unreacted precursors and by-products, (3) pulse of counter reactant precursor B into the chamber and Ligant-exchange between A and B, (4) purge of inert gas such as nitrogen to carry out the unreacted precursors is then cycled until the thickness is achieved. Moreover, serval condition is crucial for ALD

Fig. 2-2 illustration of ALD reaction cycle

#### 2.2 Metal-Oxide-Semiconductor Capacitors (MOSCAPs)

Excellent oxide/semiconductor interface is the backbone of the CMOS technology. So, characterization of metal-oxide-semiconductor hetero-structure become an urgent issue and widely studied. The MOS structure was first proposed by Moll and Pfannand Garrett in 1959. The first successful MIS structure was soon carried out in 1960 by Ligenza and Spitzer using thermal grown SiO<sub>2</sub> on Si. [16] Lateral, Nicollian and Brews have developed a comprehensive and in-depth treatment of MOSCAPsa. [17] Since the system is directly related to most devices and integrated circuits. Metal-oxidesemiconductor capacitors (MOSCAPS) is widely applied for oxide/semiconductor interface.

Fig. 2-3 Typical MOSCAP.

### 2.2.1 Measurement equipment

To characterize the MOSCAPs, capacitance-voltage (C-V) characteristic, currentvoltage (I-V) characteristic, conductance method (G-V) and quasi-static CV (QSCV) measurement are the common use measurements. C-V curves of MOSCAPs were measured with a DC voltage and a small AC current (25mV~30mV) from 100Hz to 1MHz using Agilent 4284A LCR Meter. J-E characteristic were measured using Agilent 4156C Precision Semiconductor Parameter Analyzer and HP 8510C network analyzer. Note that all the measurement were measured in the dark to prevent extra generation of carriers.

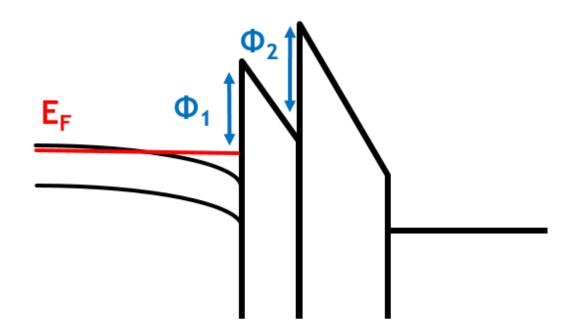

#### 2.2.2 Conduction mechanisms in dieletric films

The conduction mechanism in high  $\kappa$  dieletric thin films plays an important role in application of high  $\kappa$  material. Since the application of dielectric films is a major subject for the semiconductors industry especially for CMOS technique. Diligent studies have been carried out to examine the conduction mechanism in dielectric films. The conduction in thin dielectric films can be classified into electrode-limited conduction mechanism and bulk-limited conduction mechanism. The electrode-limited conduction mechanism depends on the physical properties between the electrode dielectric interface such as barrier height and effective mass difference. While the bulk-limited conduction mechanism depends on the electrical properties of dielectric itself, such as trap level and trap density. [18]

The Shottky emission, Fowler-Nordhiem tunneling and direct tunneling are the main electrode-limited conduction mechanisms. Shottky emission occurs if the electrons can obtain enough thermal energy to overcome the energy barrier between electrode (semiconductor) and dielectric. The so called thermionic emission is one of the most commonly observed conduction mechanism. The expression of Shottky emission is as followed.

$$J = AT^{2} \exp\left(\frac{-q(\phi_{B} - \sqrt{qE/(4\pi\varepsilon_{r}\varepsilon_{o})})}{kT}\right)$$

(1)

Where A is the Richardson constant, T is the absolute temperature,  $q\phi_B$  is the conduction band offset, E is the electrical field across the insulator, k is the Boltzman's constant,  $\varepsilon_o$  is the permittivity in vacuum and  $\varepsilon_r$  is the optical dielectric constant. Note that Shottky emission is not strongly dependent of gate voltage. To verify a Shottky emission, the plot of log(J/T<sup>2</sup>) versus E<sup>1/2</sup> should be linear.

When the energy of the incident is less than the potential barrier, quantum theory predicted that the electron wave function can penetrate through the barrier. Fowler-Nordhiem tunneling (F-N) occurs when large electrical field is applied, so that the electron can tunnel through the triangular potential barrier. Using the well-known WENTZEL-KRAMERS-BRILLOUIN (WKB) approximation and Taylor expansion near Fermi-level, the expression of F-N tunneling can be expressed by

$$J = \frac{q^3 E^2}{8\pi h q \phi_B} \exp\left(\frac{-8\pi (2qm_T)^{1/2}}{3hE} \phi_B^{3/2}\right)$$

(2)

Where  $m_T$  is the effective tunneling mass in the dielectric. The FN tunneling occurs at high electrical field. To verify the FN tunneling, the plot of  $\ln(J/E^2)$  versus 1/E must be linear, with the slope related to the barrier height as follow.

$$S = -6.83 \times 10^7 \sqrt{\frac{m_T}{m_0} \phi_B{}^3}$$

(3)

If the bias across the dielectric is not large enough, the electron have to tunnel through the whole dielectric thickness. In general, when the oxide thickness less than 3.5nm, direct tunneling dominates. While oxide layer thicker than 5nm, FN tunneling dominates. The illustration of the three different electrode-limited conduction mechanism are shown in Fig. 2-4.

Fig. 2-4 Band diagram of Shottky emission, FN tunneling and direct tunneling

Unlike electrode-limited conduction, bulk-limited conduction depend on the electrical properties of the dielectric. Poole-Frenkel Emission, Ohmic conduction, Hopping conduction and Grain-boundary-limited conduction are the commonly observed bulk-limited conduction mechanism. Poole-Frenkel Emission is so called internal Shottky emission. The electrons in the trapping center with enough thermal energy can excited to dielectric conduction band. Hopping conduction happens when trapped electrons tunnel from one trap site to another in the dielectric films. While Grain-boundary-limited conduction is observed in a polycrystalline dielectric material. The grain boundary would build a grain boundary potential energy related to the grain boundary trap density.

#### 2.2.3 Ideal CV characteristics

To characterize the MOS structure, C-V characteristic is powerful and provide some important parameters. The MOS capacitance is extracted from the admittance measurement by the LCR meter.

$$Y = i\omega C + G \tag{3}$$

Where Y is the measured admittance, G is conductance and C is the capacitance. And the MOS capacitance is defined as the differential of charge change by gate bias.

$$C = \frac{dQ}{dV_g}$$

(4)

For an ideal MOSCAP, the measured capacitance equals to oxide capacitance in series with semiconductor capacitance. For simplicity, we assumed the flat band voltage equals to zero. We now consider an ideal metal/oxide/p-semiconductor system under different bias. The C-V curves and band diagram are shown in Fig. 2-5 and Fig. 2-6.

(1) Gate bias V = 0 V (flat band)

This is so called the flat band condition, which occurs when the Fermi-level of semiconductor is aligned with metal Fermi-level. Therefore, no extra charge and field exist in the system. And now, the semiconductor capacitance is given by

$$C_{FB} = \frac{\varepsilon_s}{L_D} \quad L_D = \sqrt{\frac{kT\varepsilon_s}{N_A q^2}} \tag{5}$$

$\varepsilon_s$  is the permittivity of semiconductor, N<sub>A</sub> is the doping concentration and L<sub>D</sub> is the Debye length in the semiconductor. The Debye length is defined by the distance in semiconductor which local electrical field can affect the distribution of free charge carriers.

#### (2) Gate bias V <0 (accumulation region)

Under negative bias, holes accumulate at p-semiconductor surface and an accumulation layer of holes is induced. When a small AC signal is applied, the hole would immediately response to the voltage change as illustrate in Fig 2.6 (a). When the semiconductor capacitance is much larger than oxide capacitance, the measured capacitance is just-like a parallel-plate capacitor equals to oxide capacitance. But, the keep scaling down of CET make oxide capacitance close to semiconductor capacitance, which will be detail discussed in Chapter 4.

$$C_{(acc)} = \frac{1}{\frac{1}{C_s} + \frac{1}{C_{ox}}} \approx C_{ox}$$

(6)

(3) Gate bias V <0  $\psi_B > \psi_s > 0$  (depletion region)

In this region, space charge region is formed.  $\psi_B$  is the Fermi-level potential with respect to midgap, while  $\psi_s$  is surface Fermi-level.

$$\psi_{Bp} \approx \frac{2kT}{q} \ln\left(\frac{N_A}{n_i}\right) \tag{7}$$

And no accumulation of charge near the surface. A small AC voltage signal would cause a change in the space charge width. Thus the measure capacitance is

$$C_{(del)} \approx rac{1}{rac{arepsilon_s}{W_D} + rac{1}{C_{ox}}}$$

(4) Gate bias V < 0,  $2\psi_B > \psi_S > \psi_B$  (weak inversion region)

In weak inversion region, the maximum depletion width is not reached. But the very small inversion carrier is accumulated at the surface. Therefore, the capacitance is just like the case in depletion region. The maximum depletion width is given by

$$W_D = \sqrt{\frac{4\varepsilon_s kT ln(N_A/n_i)}{q^2 N_A}} \tag{9}$$

(5) Gate bias V < 0,  $\psi_s > 2\psi_B$  (strong inversion region)

In strong inversion region, the electron accumulate at the semiconductor surface if the minority response time can respond to the measure frequency. Thus the capacitance equals to the oxide capacitance. But if the measure frequency is too high that the minority carrier response cannot follow, the measured capacitance equals to  $C_{min}$  as shown in Fig. 2-6 (c). Moreover, if the DC sweep is too fast for minority carrier to response, deep depletion would be observed as in Fig. 2-5 (d).

(8)

Fig. 2-5 MOS C-V curves. (a) low frequency (b) intermediate frequency (c) high

frequency (d) deep depletion.

Fig. 2-6 Band diagram of ideal MOSCAP at (a) accumulation region (b) depletion

region (c) inversion region.

#### 2.2.4 *D<sub>it</sub>* extraction methods

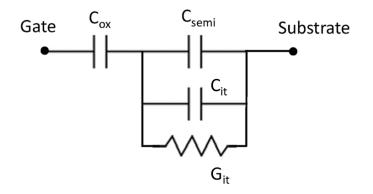

In non-ideal case, charge would be trapped in the oxide or at the oxide/semiconductor interface. The trap would exchange charge with semiconductor bands and result in nonideal C-V characteristic, such as "stretch-out" effect, frequency dispersion, trap-induced inversion humps, Fermi-level pining and so on. Moreover, the traps affect charge transport in the channel in MOSFET application. In the past years, diligent efforts and characterization were carried out to probe the so called interfacial traps at oxide/semiconductor interface. Fig. 2-7 shows the equivalent circuits incorporating  $C_{it}$  (interfacial traps capacitance).

Fig. 2-7 Equivalent circuits including interface-trap effect

#### **Terman method**

Terman method is a method which can extract  $D_{it}$  from high frequency measured C-

V characteristics. It was first proposed by Terman in 1965, which was one of the first

methods for extracting interfacial traps density. Terman method assumed that the interfacial traps cannot response to high-frequency AC signals but can response to the DC signals, leading to C-V curves stretch-out. With the measured high-frequency capacitance, we can deduce the depletion capacitance and the corresponding surface potential as in Fig 2.8. Differentiate the difference between the ideal  $V_g - \psi_s$  calculated from theory and the one obtained from measurement. We can extract the  $D_{it}$  value using the relation.

$$D_{it} = \frac{C_{ox}}{q^2} \frac{d\Delta V_G}{d\psi_s}$$

(10)

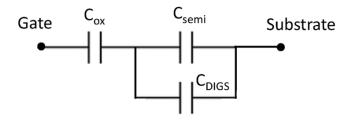

Gate  $C_{ox}$   $C_{semi}$  Substrate

$\bullet$   $\bullet$   $\bullet$

Fig. 2-8 Equivalent circuits at high frequency

## **QSCV** measurement

It was so called low frequency method and was first developed by Berglund. [19] Unlike Terman method, QSCV measurement use DC current sweep at very low rate to ensure every trap response to applied voltage. The measure capacitance is obtained integration of total current divided by change of gate bias.

$$C = \frac{\Delta Q}{\Delta V_g} \quad \Delta Q = \int I dt \tag{11}$$

At low measurement frequency, the  $G_{it}$  (conductance) can be neglected. The corresponding equivalent circuit is shown in Fig 2.9. With Berglund integral, one con derive the  $\psi_s$ - $V_G$  relationship.

$$\frac{d\psi_s}{dV_G} = \frac{C_{ox}}{C_{ox} + C_D + C_{it}} = 1 - \frac{(C_D + C_{it})}{C_{ox} + C_D + C_{it}} = 1 - \frac{C_{LF}}{C_{ox}}$$

(12)

$$\psi_s(V_2) - \psi_s(V_1) = \int_{V_1}^{V_2} 1 - \frac{C_{LF}}{C_{ox}} \, \mathrm{dV} + \mathrm{constant}$$

(13)

Again, we can use the ideal  $V_g - \psi_s$  calculated from theory and the one obtained from measurement. We can extract the  $D_{it}$  value using the above equation.

Fig. 2-9 Equivalent circuits at low frequency

#### **Conductance method**

The conductance method is first proposed by Nicollian and Goetzberger in 1967. [17] Conductance method is well-known for its ability of measuring interface trap of densities lower than  $10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup>. The conductance method extract the  $D_{it}$  value from the equivalent parallel conductance ( $G_p$ ) of an MOSCAP. By dividing the parallel conductance by the measured frequency, one can derive the  $D_{it}$  value.

$$\frac{G_P}{\omega} = \frac{C_{it}\omega\tau_{it}}{1+(\omega\tau_{it})^2} \tag{14}$$

Where  $\tau_{it} = \frac{\exp(\Delta E/k_B T)}{\sigma v_t N}$ ,  $\Delta E$  is the trap level from band edge,  $\sigma$  is the capture-

cross-section,  $v_t$  is the thermal velocity and N is the conduction band/valance band density of states. However, the above equation is valid for single level trap. In real case we have to consider a continuous distributed trap energy in the band gap. Leads to

$$\frac{G_P}{\omega} = \frac{qD_{it}}{2\omega\tau_{it}}\ln[1 + (\omega\tau_{it})^2]$$

(15)

At  $\omega = 1/\tau_{it}$ ,  $\frac{G_P}{\omega}$  reach its maximum value, and the interfacial trap density is

$$D_{it} \approx \frac{2.5}{q} \left(\frac{G_P}{\omega}\right)_{max} \tag{16}$$

Note that the conductance method is only valid in depletion region, while the equivalent circuit cannot be applied in inversion and accumulation region. Since the interfacial trap time constant is related to the temperature and trap energy level, the various temperatures of measurement is needed to obtain completed  $D_{it}$  spectrum in semiconductor.

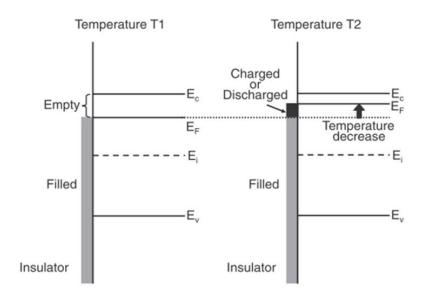

#### **Gray-Brown method**

Gray-Brown method move the semiconductor Fermi-level by changing the measure temperature as shown in Fig. 2-10. As we know, the Fermi-level in bulk GaAs move toward the band edge as temperature decrease. This Fermi-level movement would not affected by interfacial traps since it is the bulk property. However, the interfacial trap is charged or discharged when the Fermi-level moves, and the surface potential is changed. Therefore, the flat band voltage changes to compensate the interfacial trap effect. The interfacial trap density can be extracted from the following relation.

$$D_{it} = \frac{C_{ox}[\left(V_{fb}^{T_{i+1}} - V_{fb}^{T_i}\right) - (E_f^{T_{i+1}} - E_f^{T_i})/q]}{q(E_f^{T_{i+1}} - E_f^{T_i})}$$

(17)

Fig. 2-10 Illustration of Gray-Brown method

#### 2.3 Interfacial trap and border traps model

Unlike the ideal SiO<sub>2</sub>/Si interface with extremely low trap density, it is hard to achieve low  $D_{it}$  in high- $\kappa$ /(In)GaAs, resulting in large frequency dispersion in CV curves. Research efforts have been carried out to explain the origin of the large FD in oxides/(In)GaAs interfaces. In 1980, Hasegawa has proposed a model assuming an exponentially decaying spatial distribution of traps from the oxide/semiconductor interface into the bulk oxide layer to explain the large FD of CVs at accumulation by the interfacial traps. [4] The equivalent circuit is shown in Fig. 2-8. The parallel capacitance, conductance and assumed traps distribution are as follows.

$$N_T(x) = N_{T0} \exp(-\alpha x) \tag{18}$$

$$C_{it} = \frac{q^2 N_{T0}}{2\kappa} (\omega \tau_0)^{(\alpha/2\kappa)} \int_0^{1/\omega \tau_0} z^{(\alpha/2\kappa)} \tan^{-1}(z) dz$$

(19)

$$G_{it} = \frac{q^2 N_{T0}}{4\kappa} (\omega \tau_0)^{(\alpha/2\kappa)} \int_0^{1/\omega \tau_0} z^{(\alpha/2\kappa)} \ln(1+z^{-2}) dz$$

(20)

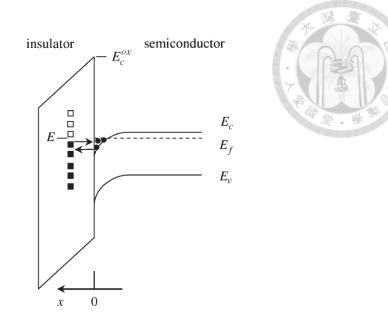

$\alpha$  is the decay constant for interfacial traps distribution, which is about 1 nm<sup>-1</sup>,  $\kappa$

is the tunneling attenuation constant and  $N_T$  is the trap density at the interface. However, the time constant of interfacial traps is far too short for the range of measure frequencies below 1kHz. The interfacial traps model cannot fully explain the measured C-V characteristic. Thus, Yu Yuan has proposed a distributed model for border traps in 2011 based on tunneling mechanism. [5] Unlike previous publication, which the border traps are modeled by a lump RC circuit. The proposed model reflect the distributed nature of traps over the depth in gate oxide. In the model, the traps inside gate dielectric close to interface can exchange with semiconductor conduction/valance band through tunneling as shown in Fig. 2-11.

Fig. 2-11 Schematic diagram of tunneling between border traps in dielectric and the conduction band of semiconductor

The border traps within depth  $\Delta x$  at x is represented by  $\Delta C_{bt}$  and connected with  $\Delta G_{bt}$ . The traps that reside inside the dielectric possess a longer time constant than that of the interfacial traps. One can use the Wentzel-Kramers-Brillouin (WKB) approximation to derive the time constant  $\tau(x)$  of border traps at depth x into the dielectric.  $\Delta C_{bt}$  and  $\Delta G_{bt}$  are related by the time constant  $\tau(x)$ .

$$\Delta C_{bt} = q^2 N_{bt} \Delta x \quad \frac{\Delta C_{bt}}{\Delta G_{bt}} = \tau(x) = \tau_0 \exp(2\kappa x) \tag{21}$$

Where  $\tau_0$  is the time constant of the interfacial traps;  $\kappa$  is the attenuation coefficient for the electron wave decay under the band offset barrier;  $N_{bt}$  is the border trap density in units of  $cm^{-3}$ . For Y<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> on n-GaAs, the attenuation coefficient  $\kappa$  is given by

$$\kappa = \sqrt{2m(E_{offset})}/\hbar$$

Moreover, the time constant of interfacial traps  $\tau_0$  can be determined by the following relationship

$$\tau_0 = \left(\sigma v_{th} N_{eff}\right)^{-1} \exp(|E_M - E_{Fs}|/kT)$$

(23)

Where  $\sigma$  is the capture cross section (10<sup>-15</sup> cm<sup>2</sup>), v<sub>th</sub> the electron thermal velocity,

$E_M$  the edge of majority carrier band,  $E_{Fs}$  the surface Fermi level and  $N_{eff}$  the effective conduction band density of states. The corresponding RC equivalent circuits for border traps model is shown in Fig. 2-12, and the recursive nature of the border traps gives the differential equation for the admittance as follow.

Fig. 2-12 RC equivalent circuit for border trap model

With the combination of the interfacial model and border trap model, we can better understand the frequency dispersion in C-V measurement. We can also extract the trap properties with the two models.

(22)

# **3. Experimental Procedures**

# **3.1 Sample Preparation**

The growth of ALD-Al<sub>2</sub>O<sub>3</sub>(5nm)/ALD-Y<sub>2</sub>O<sub>3</sub>(2nm) and ALD-Al<sub>2</sub>O<sub>3</sub> on freshly MBE grown p- and n-GaAs(001)-4×6 were carried out in a multi-chamber MBE/ALD/analyses UHV system as shown in Fig. 3-1. The system consist of one solid source GaAs-based III-V MBE chamber, one Ge-based MBE chamber, two arsenic-free oxide deposition chambers, in-situ XPS analytical systems, in-situ SPM systems and in-situ ALD chamber. All the systems are linked together under ultra-high vacuum.

in-situ in-situ Under 10<sup>-10</sup> torr **XPS SPM** Wafer in  $\rightarrow$ transfer modules oxide and oxide and oxide III-VSi-Ge metal metal ALD MBE **MB**E MBE **MBE** metal

Fig. 3-1 Schematic diagram of multi-chamber MBE/ALD/analyses UHV system

# 3.2 Preparation of GaAs (001)-4×6 surface

In this work, the 2-inch n<sup>+</sup>-GaAs (001) and p<sup>+</sup>-GaAs (001) wafers were used as the substrate. Before the growth, the wafers was heated to about  $600^{\circ}$ C to desorb the

ALD

native oxide. To avoid trap diffusion from GaAs wafers, supper-lattice of GaAs(10 Å)/AlGaAs(10Å) was first deposited on GaAs wafer before GaAs buffer layer deposition. After supper-lattice deposition, a 100nm thick n-/p- GaAs buffer layer with  $1 - 5 \times 10^{17} \ cm^{-3}$  Si/Be doped were epitaxial deposited. We then transfer the wafers to an Asfree chamber for surface reconstruction. The reflection High-energy Electron Diffraction (RHEED) was used for monitoring the GaAs surface reconstructions. After serval minutes annealing at 550°C, GaAs surface reconstructed from  $2 \times 4$  to  $4 \times 6$  surface reconstruction.

#### 3.3 Atomic-layer-deposited high ĸ

Lateral, the samples were subsequently transferred into the ALD chamber for oxide deposition. In deposition of Al<sub>2</sub>O<sub>3</sub>(5nm)/Y<sub>2</sub>O<sub>3</sub>(2nm)/GaAs samples, the films were deposited at 270°C with Y(ETCP)<sub>3</sub> and H<sub>2</sub>O as precursors. [20] The growth rate is about ~0.15nm/cycle. After 1nm Y<sub>2</sub>O<sub>3</sub> deposition, the samples were transfer into an ultra-high vacuum chamber for UHV annealing. The UHV annealing remedy the interface and get rid of unreacted precursors as well as ligands. We then transfer the wafer back to ALD chamber to finish the growth. An ALD-Al<sub>2</sub>O<sub>3</sub> capping layer of 5nm-thick on top of the Y<sub>2</sub>O<sub>3</sub>/GaAs has prevented Y<sub>2</sub>O<sub>3</sub> from moisture absorption in air. In deposition of

# **3.4** Post deposition annealing condition

Optimized post deposition annealing (PDA) was conducted at 900°C for 60s in  $N_2$  for  $Y_2O_3$ /GaAs samples, and 550°C 30s in  $N_2$  followed by 850°C 10s in He for  $Al_2O_3$ /GaAs samples, prior to the gate metal deposition.

# 3.5 Metal electrode deposition

The gate metal of the MOSCAPs was deposited by e-beam evaporation of nickel (Ni) 100nm through a shadow mask with  $7.85 \times 10^{-5} cm^2$  in area, the back contact was deposited by thermal evaporation of gold (Au) 100nm/ titanium (Ti) 30nm. The Schematics of MOSCAPs structure are shown in Fig. 3-2.

| Y₂O₃/p-GaAs                                                                                                       | Y₂O₃/n-GaAs                                                                                                       | X N N                                    |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Ni                                                                                                                | Ni                                                                                                                |                                          |

| ALD-Al <sub>2</sub> O <sub>3</sub> (5nm)                                                                          | $ALD-Al_2O_3$ (5nm)                                                                                               |                                          |

| $ALD-Y_2O_3$ (2nm)                                                                                                | $ALD-Y_2O_3 (2nm)$                                                                                                |                                          |

| GaAs-Be-doped                                                                                                     | GaAs-Si-doped                                                                                                     | 2000 10101010101010101010101010101010101 |

| Super Lattice                                                                                                     | Super Lattice                                                                                                     |                                          |

|                                                                                                                   |                                                                                                                   |                                          |

| GaAs-P <sup>+</sup>                                                                                               | GaAs-N <sup>+</sup>                                                                                               |                                          |

| GaAs-P <sup>+</sup><br>TiAu                                                                                       | GaAs-N⁺<br>TiAu                                                                                                   |                                          |

| TiAu                                                                                                              |                                                                                                                   | 5                                        |

| TiAu                                                                                                              | TiAu                                                                                                              | 5                                        |

| TiAu<br>Al₂O₃/p-GaAs                                                                                              | TiAu<br>Al <sub>2</sub> O <sub>3</sub> /n-GaAs                                                                    | 5                                        |

| TiAu<br>Al <sub>2</sub> O <sub>3</sub> /p-GaAs<br>Ni<br>ALD-Al <sub>2</sub> O <sub>3</sub> (5nm)<br>GaAs-Be-doped | TiAu<br>Al <sub>2</sub> O <sub>3</sub> /n-GaAs<br>Ni<br>ALD-Al <sub>2</sub> O <sub>3</sub> (8nm)<br>GaAs-Si-doped | 5                                        |

| TiAu<br>Al <sub>2</sub> O <sub>3</sub> /p-GaAs<br>Ni<br>ALD-Al <sub>2</sub> O <sub>3</sub> (5nm)                  | TiAu<br>Al <sub>2</sub> O <sub>3</sub> /n-GaAs<br>Ni<br>ALD-Al <sub>2</sub> O <sub>3</sub> (8nm)                  | 5                                        |

| TiAu<br>Al <sub>2</sub> O <sub>3</sub> /p-GaAs<br>Ni<br>ALD-Al <sub>2</sub> O <sub>3</sub> (5nm)<br>GaAs-Be-doped | TiAu<br>Al <sub>2</sub> O <sub>3</sub> /n-GaAs<br>Ni<br>ALD-Al <sub>2</sub> O <sub>3</sub> (8nm)<br>GaAs-Si-doped | 5                                        |

Fig. 3-2 Schematic cross-section of GaAs MOSCAP

with Ni metal gate and Ti/Au back electrode.

# **3.6 Electrical measurement**

The CV characteristic and conductance characteristics were measured at room temperature with frequency from 100Hz to 1MHz using Agilent 4284 LCR meter. The current versus voltage (I-V) characteristics and QSCV were measured in dark at room temperature by Precision Semiconductor Parameter Analyzer Agilent 4156C.

#### 4. Results and Discussion

# 4.1 Comparison of C-V characteristic between Al<sub>2</sub>O<sub>3</sub> and Y<sub>2</sub>O<sub>3</sub> passivated GaAs surface

GaAs and InGaAs are the leading candidates to replace Si as the n-channel material for future complementary MOSFETs because of their relatively high electron mobilities. With a lattice mismatch of 8% with Si(001), In<sub>0.53</sub>Ga<sub>0.47</sub>As is difficult to be integrated onto the Si(001) platform. In comparison, GaAs with a smaller lattice mismatch of 4% with Si is much easier to be grown on Si(001). Besides, with excellent uniformity and conformal coverage in nanometer thick film growth, atomic layer deposition (ALD) has been widely employed in depositing high-k dielectrics for MOSFETs since the 45 nm node. Therefore, as an urgent issue, intensive efforts in ALD high-k dielectrics on GaAs(001) have been carried out to characterize and perfect these interfaces. C-V characteristic is one of the most useful measurement to characterize the oxide/semiconductor interface through MOSCAPs device. And most of the fundamental problem in the device performance, reliability and stability are related to the oxide/semiconductor interface quality. In this part, comparison of C-V curves between Al<sub>2</sub>O<sub>3</sub>/GaAs and Y<sub>2</sub>O<sub>3</sub>/GaAs is demonstrated. Moreover, some carefully extraction of oxide capacitance is calculated.

#### **4.1.1 CV characteristics**

Figure 4.1 (a) and 1(b) show the CVs of  $Y_2O_3$  on p- and n-GaAs, while 4.1(c) and 4.1 (d) show those of Al<sub>2</sub>O<sub>3</sub> on p- and n-GaAs. FDs of 4% (12%) in accumulation were measured for  $Y_2O_3/p(n)$ -GaAs, smaller than those of 9% (22.2%) for Al<sub>2</sub>O<sub>3</sub>/p(n)-GaAs. Unlike other work using ex-situ ALD approach usually give a large FD as in Table. 4-1. Ex-situ AlN passivation layer and sulfur-passivation GaAs surface still result in large frequency dispersion. [13,14] Our in-situ ALD approach without passivation layer and surface treatment result in reasonable frequency dispersion. Both Al<sub>2</sub>O<sub>3</sub>/GaAs and Y2O3/GaAs samples show typical C-V characteristics for p-type samples and small frequency dispersion from inversion to accumulation. However, large difference in n-type counterparts is observed. The much smaller frequency dispersion at depletion region is observed in Y<sub>2</sub>O<sub>3</sub>/GaAs sample than Al<sub>2</sub>O<sub>3</sub>/GaAs sample, indicating lower interfacial trap density. Note that no inversion behavior is observed, which is attributed to the long minority carrier response time.

|                                                                       |              |                                                                       |       | A             |

|-----------------------------------------------------------------------|--------------|-----------------------------------------------------------------------|-------|---------------|

| Structure                                                             | <b>F. D.</b> | Structure                                                             | F. D. | reference     |

| Al <sub>2</sub> O <sub>3</sub> /p-GaAs                                | 11.1%        | Al <sub>2</sub> O <sub>3</sub> /n-GaAs                                | 52.8% | G. B et, al   |

| Al <sub>2</sub> O <sub>3</sub> /AlN/p-GaAs                            | 13.4%        | Al <sub>2</sub> O <sub>3</sub> /AlN/n-GaAs                            | 26.5% | T. Aoki et,al |

| Al <sub>2</sub> O <sub>3</sub> /p-GaAs                                | 9.0%         | Al <sub>2</sub> O <sub>3</sub> /n-GaAs                                | 22.2% | This work     |

| Al <sub>2</sub> O <sub>3</sub> /Y <sub>2</sub> O <sub>3</sub> /p-GaAs | 4.4%         | Al <sub>2</sub> O <sub>3</sub> /Y <sub>2</sub> O <sub>3</sub> /n-GaAs | 12.2% | This work     |

Table. 4-1 frequency dispersion in C-V measurement of different works

Fig. 4-1 CVs of MOSCAPs of ALD-Y<sub>2</sub>O<sub>3</sub> on (a) p-type and (b) n-type GaAs, and ALD-

Al<sub>2</sub>O<sub>3</sub> on (c) p-type and (d) n-type GaAs.

Furthermore, we have measured CVs at 150°C at different frequency to investigate the interfacial and border trap responses in depletion and weak inversion regions. Figure 4-2 shows the CVs of Y<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> on n-GaAs measured at 150°C in dark. With a band gap of 1.42 eV and a low conduction band density of states, GaAs possesses a relatively longer minority-carrier response time than Si, such that minority carriers should not respond to common measured frequencies in inversion region even at 150°C. As GaAs possess a very long minority carrier generation time, and therefore, cannot follow the measurement frequency even at high temperatures. The humps in depletion and weak inversion regions of Al<sub>2</sub>O<sub>3</sub>/n-GaAs are therefore attributed to the trap-induced capacitance responses rather than a true inversion behavior as shown in Fig. 4-2.

Fig. 4-2. CVs of ALD (a)  $-Y_2O_3$  and (b)  $-Al_2O_3$  on n-GaAs measured at 150°C.

#### 4.1.2 Oxide capacitance and electrical parameters

Effective oxide thickness is an important index for characterization MOS structure. In the past, we simply use the maximum capacitance in CV to determine the oxide capacitance. Here, the maximum capacitance of  $Y_2O_3/n$ -GaAs and  $Y_2O_3/n$ -GaAs are 1.336 µF/cm<sup>2</sup> and 1.189µF/cm<sup>2</sup>, respectively. If we determine the oxide capacitance through maximum capacitance, the  $Y_2O_3/n$ -GaAs and  $Y_2O_3/p$ -GaAs would give different results. But,  $Y_2O_3/n$ -GaAs and  $Y_2O_3/p$ -GaAs with the same oxide stacks should give the same oxide capacitance. Therefore, we cannot simply determine the oxide capacitance by the maximum capacitance at accumulation. The measured capacitance at accumulation equals to oxide capacitance in series with semiconductor capacitance. When the oxide capacitance is relative small, we can ignore the contribution of semiconductor capacitance. However, as the oxide thickness is thin enough, the semiconductor capacitance have to be considered.

To derive semiconductor capacitance, two condition are considered. [21] At low electrical field region, the capacitance of semiconductor is dominated by finite density of states. Under the approximation of 3-D electron gas, Boltzman distribution and Possion equation, the surface carrier concentration is given by

$$N_s \approx \left(2n_{p0}p_{p0}\right)^{\frac{1}{2}} L_D \exp(\beta \varphi_s/2)$$

<sup>(25)</sup>

Here,  $\beta = \frac{q}{k_B T}$ ,  $n_{p0}$  and  $p_{p0}$  are electron concentration and hole concentration

in the bulk,  $L_D$  is Debye length mention above and  $\varphi_s$  is the surface potential. Now the semiconductor capacitance at accumulation dominated by finite density of states is

$$C_{acc}^{DOS} = \frac{q\partial N_s}{\partial \varphi_s} = \frac{q^2}{2k_B} \times \frac{N_s}{T}$$

(26)

At high electrical field region, the accumulation layer is affected by the 2-D quantization of carriers. The accumulation thickness can be expressed by

$$C_{acc}^{thickness} = \frac{\varepsilon_{GaAs}}{Z_{acc}} \approx \left(\frac{11\varepsilon_{GaAs}^2 q^2}{72\hbar^2}\right) \times m_{GaAs}^{1/3} \times N_s^{1/3}$$

(27)

Where  $\varepsilon_{GaAs}$  is the permittivity of GaAs,  $Z_{acc}$  is the average thickness of 2D electron gas and  $m_{GaAs}$  is the perpendicular effective mass of GaAs. To obtain the total accumulation capacitance

$$(C_{total})^{-1} = (C_{acc}^{DOS})^{-1} + (C_{acc}^{thickness})^{-1}$$

(28)

To further understand the behavior of capacitance versus surface carrier density. We plotted the capacitance versus surface carrier density diagram for p-GaAs and n-GaAs substrate at Fig. 4-3 (a) and (b). At low electrical field, the p-GaAs and n-GaAs capacitance-carrier density curve are identical. But at large electrical field, the capacitance are dominated by the thickness of 2-D electron gas layer, which is related to the effective mass of the carrier. The electron effective mass of GaAs is 0.063m<sub>0</sub>, which is about an order smaller than the hole effective mass of GaAs 0.51m<sub>0</sub>. The much smaller

effective mass result in much smaller semiconductor capacitance, which explains the observed lower  $C_{max}$  at GaAs n-type samples than p-type counterparts. From Fig. 4-3, at surface carrier density of  $10^{13}$  cm<sup>-2</sup>, the capacitance of semiconductor is  $3.36 \,\mu$ F/cm<sup>2</sup> and  $6.31 \,\mu$ F/cm<sup>2</sup>, respectively. The semiconductor capacitance of  $3.36 \,\mu$ F/cm<sup>2</sup> and  $6.31 \,\mu$ F/cm<sup>2</sup> correspond to accumulation thickness of 3.40nm and 1.81nm. Comparing the capacitance of semiconductor to the oxide capacitance, which is about 1-2  $\mu$ F/cm<sup>2</sup>, the semiconductor capacitance cannot be neglected.

Fig. 4-3 (a) p-type accumulation capacitance versus surface carrier density. Blue

line is the  $C_{total}$  versus carrier density. While the red lines are the  $C_{acc}^{DOS}$  and  $C_{acc}^{thickness}$  versus carrier density, respectively.

Fig. 4-3 (b) n-type accumulation capacitance versus surface carrier density. Blue line is the  $C_{total}$  versus carrier density. While the red lines are the  $C_{acc}^{DOS}$  and  $C_{acc}^{thickness}$  versus carrier density, respectively.

Before we start to calculate the oxide capacitance of the  $Y_2O_3/Al_2O_3$  and  $Al_2O_3$ stacks, we first have to know the Debye length of GaAs, which can be extracted from the doping concentration of GaAs substrate. Fortunately, we can extract the doping concentration by the measured  $C_{min}$ .

$$C_{min} = \frac{\varepsilon_s}{W_D}, W_D = \sqrt{\frac{4\varepsilon_s kT ln(N_A/n_i)}{q^2 N_A}}$$

(29)

The Debye length and flat band capacitance are as follows

$$L_D = \sqrt{\frac{kT\varepsilon_s}{N_A q^2}} \quad C_{FB} = \frac{\varepsilon_s}{L_D} \tag{30}$$

The flat band voltage is the corresponding gate voltage when measured capacitance equals to flat band capacitance. Note that high frequency measured C-V is used to ensure no traps response.

Next, we have to know the surface carrier density at accumulation region. We assumed that there is no trap response at high frequency, and the surface carrier density at accumulation region is estimated by

$$N_s \approx \int_{V_{FB}}^{V_{acc}} C_m dV \tag{31}$$

Where  $V_{FB}$  is the flat-band voltage  $V_{acc}$  is the gate bias at  $C_{max}$ , and  $C_m$  is the measured capacitance at high frequency (500kHz). For convenience, I summarize the parameters of all samples in Table. 4-2. In order to get the accurate  $C_{ox}$ ,  $C_{ox}$  was first estimated by the  $C_{max}$  at p-type samples accumulation. Then we do the calculation above to extract the oxide capacitance. Note that the Al<sub>2</sub>O<sub>3</sub>/n-GaAs gives large frequency dispersion such that the calculation is meaningless.

| structure                                                     | Y <sub>2</sub> O <sub>3</sub> /n-GaAs | Y <sub>2</sub> O <sub>3</sub> /p-GaAs |  |

|---------------------------------------------------------------|---------------------------------------|---------------------------------------|--|

| Al <sub>2</sub> O <sub>3</sub> /Y <sub>2</sub> O <sub>3</sub> | 5nm/2nm                               | 5nm/2nm                               |  |

| $C_{max}(\mu F/cm^2)$                                         | 1.189                                 | 1.336                                 |  |

| $C_{min}(\mu F/cm^2)$                                         | 0.230                                 | 0.127                                 |  |

| $N_A(/cm^3)$                                                  | 1.19 × 10 <sup>18</sup>               | $2.90 \times 10^{17}$                 |  |

| $L_D(nm)$                                                     | 5.00                                  | 10.11                                 |  |

| $C_{FB}(\mu F/cm^2)$                                          | 0.843                                 | 0.690                                 |  |

| $V_{FB}(V)$                                                   | 1.5                                   | -0.6                                  |  |

| $N_s(/cm^2)$                                                  | 1.30 × 10 <sup>13</sup>               | 1.95 × 10 <sup>13</sup>               |  |

| $C_{acc}^{GaAs}(\mu F/cm^2)$                                  | 3.103                                 | 6.86                                  |  |

| $m_{GaAs}(m_0)$                                               | 0.063                                 | 0.51                                  |  |

| $C_{ox}(\mu F/cm^2)$                                          | 1.53                                  | 1.55                                  |  |

| EOT(nm)                                                       | 2.25                                  | 2.23                                  |  |

Table. 4-2 electrical parameter calculated by using estimation of Cox=Cmax

After the carefully extraction of all the critical parameter, Cox now can be calculated

by using

$$\frac{1}{C_{acc}^{1MHz}} = \frac{1}{C_{ox}} + \frac{1}{C_{acc}^{GaAs}}$$

(32)

Here we use  $C_{acc}^{1MHz}$ , the high frequency measured capacitance at accumulation to make

sure no trap response at this frequency, and we get the whole capacitance from semiconductor carrier response. Now the Y<sub>2</sub>O<sub>3</sub>/p-GaAs and Y<sub>2</sub>O<sub>3</sub>/n-GaAs give the same oxide capacitance. Note that the recalculated C<sub>ox</sub> is about  $1.55\mu$ F/cm<sup>2</sup>, which is larger than the first estimation of  $1.336\mu$ F/cm<sup>2</sup>. This indicates that the first estimation might cause some error. Therefore, we further recalculate the parameter follow the same procedure as above, but change the C<sub>ox</sub> as the one we obtained. The recalculated parameters are listed at Table. 4-3.

Table. 4-3 electrical parameter calculated by using estimation of  $C_{ox}$  with the first

calculation.

| structure                                                     | Y <sub>2</sub> O <sub>3</sub> /n-GaAs | Y <sub>2</sub> O <sub>3</sub> /p-GaAs |  |

|---------------------------------------------------------------|---------------------------------------|---------------------------------------|--|

| Al <sub>2</sub> O <sub>3</sub> /Y <sub>2</sub> O <sub>3</sub> | 5nm/2nm                               | 5nm/2nm                               |  |

| $C_{max}(\mu F/cm^2)$                                         | 1.189                                 | 1.336                                 |  |

| $C_{min}(\mu F/cm^2)$                                         | 0.230                                 | 0.127                                 |  |

| $N_A(/cm^3)$                                                  | 1.12 × 10 <sup>18</sup>               | $2.79 \times 10^{17}$                 |  |

| $L_D(nm)$                                                     | 5.14                                  | 10.3                                  |  |

| $C_{FB}(\mu F/cm^2)$                                          | 0.913                                 | 0.653                                 |  |

| $V_{FB}(V)$                                                   | 1.6                                   | -0.7                                  |  |

| $N_s(/cm^2)$                                                  | 0.9 × 10 <sup>13</sup>                | $1.60 \times 10^{13}$                 |  |

| $C_{acc}^{GaAs}(\mu F/cm^2)$                                  | 2.8                                   | 6.3                                   |  |

| $m_{GaAs}(m_0)$                                               | 0.063                                 | 0.51                                  |  |

| $C_{ox}(\mu F/cm^2)$                                          | 1.60                                  | 1.60                                  |  |

| EOT(nm)                                                       | 2.15                                  | 2.15                                  |  |

In Table. 4-3, the same oxide capacitance for p-GaAs and n-GaAs are presented, which is close to the one we obtained at the first calculation. In this section, we concluded that the extraction of oxide capacitance should consider the semiconductor capacitance at accumulation. With right characterization, Al<sub>2</sub>O<sub>3</sub>/Y<sub>2</sub>O<sub>3</sub>/p-GaAs and Al<sub>2</sub>O<sub>3</sub>/Y<sub>2</sub>O<sub>3</sub>/n-GaAs with the same oxide stacks gave the same oxide capacitance. Moreover, Y<sub>2</sub>O<sub>3</sub> passivated GaAs surface demonstated excellent C-V characteristic with extremely small frequency dispersion.

# 4.2 CF characteristics and Simulations

As we commonly use frequency dispersion as an important index for characterizing oxide-semiconductors interface. Researchers are eager to know the physical origin of frequency dispersion. As mention in Chapter 2, two important models were proposed and explain the physical origin of frequency dispersion. The most reasonable explanation of frequency dispersion at accumulation is the exchange of charge between the border trap inside the oxides and the semiconductors. To analyze the interfacial traps and border traps response, capacitance-log(frequency) (CF) characteristics were employed.

With the models mentioned above, we can combine the two models together as shown in Fig. 4-4.

Fig. 4-4 Equivalent circuit combined border traps and interfacial traps

Here, initial admittance is given by  $Y(0) = j\omega(C_{it} + C_s) + G_{it}$  as follows.