國立臺灣大學電機資訊學院電子工程學研究所

碩士論文

Graduate Institute of Electronics Engineering

College of Electrical Engineering & Computer Science

National Taiwan University

Master Thesis

一個操作在 0.9 伏特電壓的高速雙通道時間交錯連續

漸進式類比至數位轉換器

A 0.9V High-Speed Two-Channel Time-Interleaved SAR

ADC

黃柏超

Po-Chao Huang

指導教授：陳信樹博士

Advisor: Hsin-Shu Chen, Ph.D.

中華民國 105 年 7 月

July, 2016

國立臺灣大學碩士學位論文

口試委員會審定書

一個操作在 0.9 伏特電壓的高速雙通道時間交錯連續漸

進式類比至數位轉換器

A 0.9V High-Speed Two-Channel Time-Interleaved SAR

ADC

本論文係黃柏超君 (R03943045) 在國立臺灣大學電子工程學研究所完成之碩士學位論文，於民國 105 年 7 月 28 日承下列考試委員審查通過及口試及格，特此證明

口試委員：

陳信樹

陳信樹 (指導教授)

許雲翔

劉純成

系主任、所長

劉淳成

# A 0.9V High-Speed Two-Channel Time-Interleaved SAR ADC

By

Po-Chao Huang

## THESIS

Submitted in partial fulfillment of the requirement

for the degree of Master of Science in Electronics Engineering

at National Taiwan University

Taipei, Taiwan, R.O.C.

July. 2016

Approved by :

Ju-Shy Chen Chun-Cheng Liu Hsin-Shu Chen

Advised by :

Hsin-Shu Chen

Approved by Director :

Shen-Juan Lin

## 致謝

感謝家人與朋友對我的支持，感謝陳信樹教授的指導，感謝學長耀升、宏彥、宗翰、成銘、郁暉、紀懷、柏詩學姊、藝薰、文杰、維家、世偉、楷越、瑞民、蜜迪以及學弟昭輝、鼎國、韋安、懷正、立宇、均哲、豐任、維駿、相文在研究上的幫助與支持，有各位的幫助，在台大電子所研究的這兩年才能順利圓滿。

## 摘要

近年來，每秒幾億次至十幾億次的中解析度類比至數位轉換器的應用越來越廣泛。本論文提出了一個操作在 0.9 伏特電壓每秒十五億次取樣的八位元兩通道時間交錯式連續漸進式類比至數位轉換器，是以 40 奈米 CMOS 設計。

本論文為了解決時間交錯式連續漸進式類比至數位轉換器的子通道間時脈偏移不匹配問題，提出了一個不需要時脈偏移校正的低時脈偏移的解多工器。為了提高子通道的取樣速度與電能效益，提出了一個使用電荷分配的兩階段連續漸進式類比至數位轉換器與自我觸發閘的技巧。

本時間交錯式連續漸進式類比至數位轉換器在每秒十五億次的取樣速度與奈奎斯特的輸入頻率之下有七點一位元的有效位元，其主動面積只有  $0.014\text{mm}^2$ 。功率消耗為  $3.1\text{mW}$ ，達到一個優異的品質因數為  $15\text{ fJ/conversion-step}$ ，其適合用在高電能效益的無線通訊與乙太網路應用中。

**關鍵詞：**類比至數位轉換器、時間交錯式、連續漸進式、高速、高電能效益、低時脈偏移解多工器、兩階段

# Abstract

Recently, hundreds MS/s to 1GS/s medium resolution Analog-to-Digital Convertors (ADCs) are used extensively in applications. This thesis proposes a 0.9V 8-bit 1.5GS/s two-channel time-interleaved SAR ADC in 40nm CMOS.

This thesis proposes a low-skew demultiplexer to solve the timing skew problem between the sub-channels without timing skew calibration. In order to improve the sampling frequency and the energy-efficiency of the sub-channel, the two-step SAR ADC with charge sharing technique and the self-triggered latch technique are proposed.

This time-interleaved SAR ADC achieves an ENOB of 7.1 at the conversion rate of 1.5GS/s with Nyquist rate input. The active area is only 0.014 mm<sup>2</sup>. It consumes 3.1mW and gets the good FoM of 15fJ/conversion-step. It is suitable for the energy-efficient wireless communication and Ethernet network application.

**Keyword:** analog-to-digital converter (ADC), time-interleaved, successive-approximation register (SAR), high speed, energy-efficient, low-skew demultiplexer, two-step

# Contents

|                                                                  |     |

|------------------------------------------------------------------|-----|

| 摘要.....                                                          | I   |

| Abstract.....                                                    | II  |

| Contents.....                                                    | III |

| List of Figures.....                                             | V   |

| List of Tables.....                                              | VII |

| Chapter 1 Introduction.....                                      | 1   |

| 1.1 Motivation.....                                              | 1   |

| 1.2 Thesis Organization .....                                    | 2   |

| Chapter 2 Fundamentals of Analog-to-Digital Converter.....       | 4   |

| 2.1 Introduction.....                                            | 4   |

| 2.2 Performance Metrics .....                                    | 4   |

| 2.2.1 Offset and Gain Error.....                                 | 4   |

| 2.2.2 Differential and Integral Nonlinearity (DNL and INL) ..... | 5   |

| 2.2.3 Signal-to-Noise Ratio (SNR) .....                          | 6   |

| 2.2.4 Total Harmonic Distortion (THD) .....                      | 7   |

| 2.2.5 Spurious Free Dynamic Range (SFDR).....                    | 7   |

| 2.2.6 Signal to Noise and Distortion Ratio (SNDR).....           | 8   |

| 2.2.7 Effective Number of Bits (ENOB).....                       | 8   |

| 2.2.8 Figure of Merit (FoM) .....                                | 9   |

| 2.3 ADC Architectures .....                                      | 9   |

| 2.3.1 Flash Architecture .....                                   | 10  |

| 2.3.2 Pipelined Architecture.....                                | 11  |

| 2.3.3 Successive-Approximation-Register (SAR) Architecture ..... | 12  |

| 2.3.4 Pipelined-SAR Architecture.....                            | 13  |

| 2.3.5 Time-Interleaved Architecture .....                        | 14  |

| Chapter 3 Time-Interleaved SAR ADC.....                          | 17  |

| 3.1 Introduction.....                                            | 17  |

| 3.2 Error Sources in Time-Interleaved ADC Architecture.....      | 17  |

| 3.2.1 Offset Mismatch.....                                       | 17  |

| 3.2.2 Gain Mismatch.....                                         | 19  |

| 3.2.3 Timing Skew Mismatch .....                                 | 21  |

| 3.3 Proposed Low-Skew Demultiplexer Architecture .....           | 25  |

| 3.3.1 Principle .....                                            | 25  |

| 3.3.2 Low-Skew Demultiplexer.....                                | 26  |

| 3.4 Proposed Two-Step SAR Sub-ADC Architecture.....              | 31  |

|                                                 |    |

|-------------------------------------------------|----|

| 3.4.1 Charge sharing technique.....             | 31 |

| 3.4.2 Self-Triggered Latch technique .....      | 37 |

| 3.5 Design Consideration.....                   | 40 |

| 3.5.1 Offset Mismatch Error .....               | 40 |

| 3.5.2 Gain Mismatch Error .....                 | 41 |

| 3.5.3 Switching Method.....                     | 42 |

| 3.5.4 Accuracy Consideration .....              | 44 |

| 3.5.5 Speed Consideration .....                 | 63 |

| 3.6 Summary .....                               | 65 |

| Chapter 4 Circuit Implementation.....           | 66 |

| 4.1 Introduction.....                           | 66 |

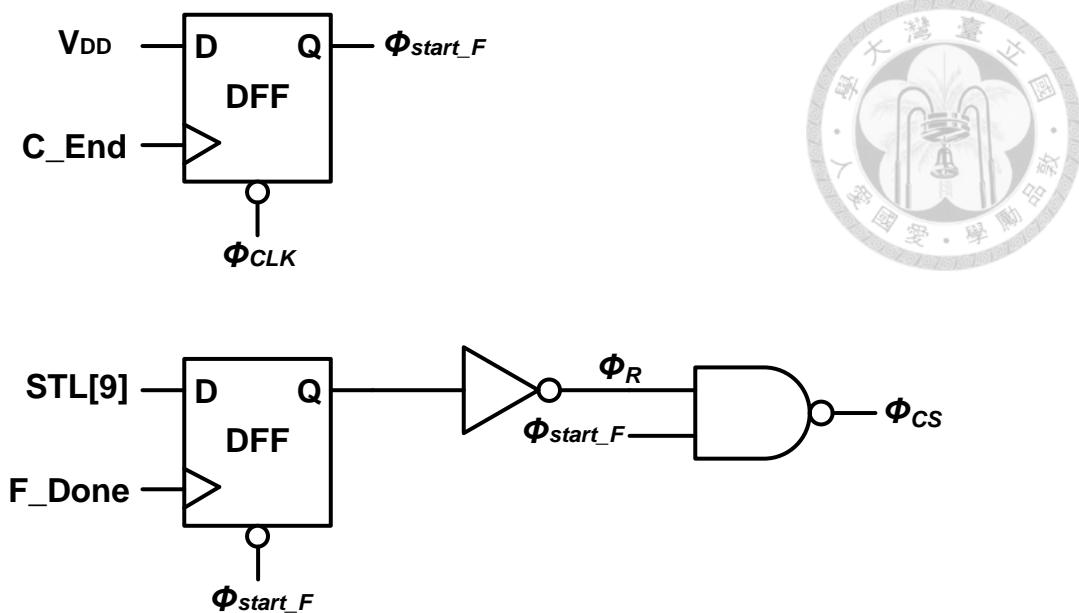

| 4.2 Clock Phase Generator.....                  | 66 |

| 4.3 Two-Step SAR Sub-ADC .....                  | 68 |

| 4.3.1 Comparator .....                          | 68 |

| 4.3.2 SAR Logic .....                           | 70 |

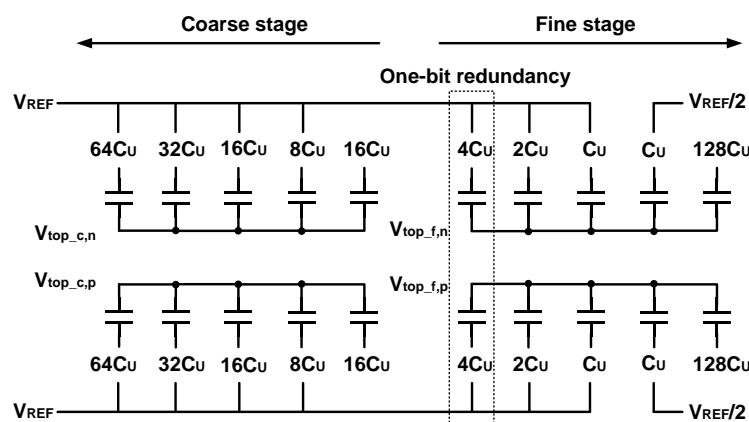

| 4.3.4 Capacitive DAC .....                      | 71 |

| 4.3.5 Charge Sharing Timing Control Logic ..... | 72 |

| 4.4 Summary .....                               | 74 |

| Chapter 5 Measurement Results.....              | 75 |

| 5.1 Introduction.....                           | 75 |

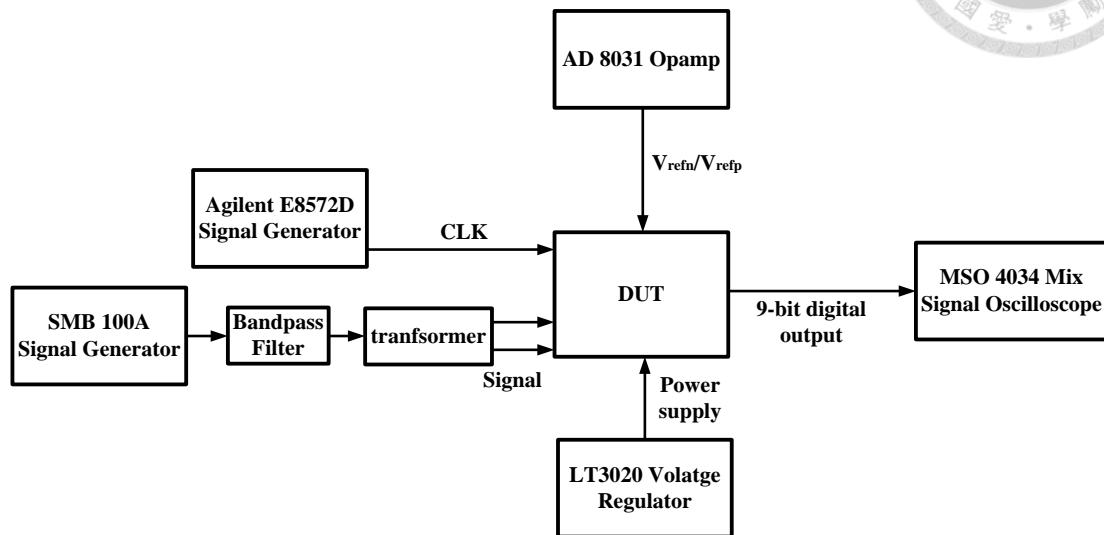

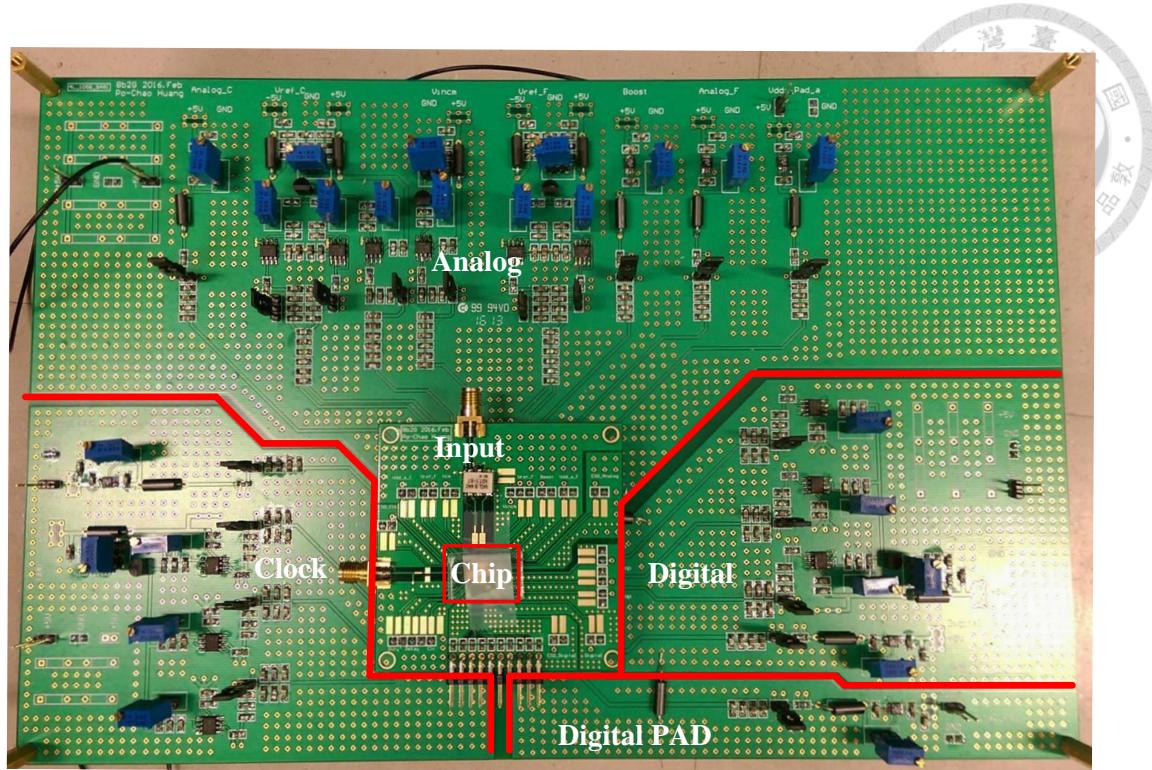

| 5.3 Test Setup.....                             | 75 |

| 5.4 PCB Design.....                             | 76 |

| 5.5 Measurement Results .....                   | 78 |

| 5.5.1 Static Performance .....                  | 80 |

| 5.5.2 Dynamic Performance .....                 | 80 |

| 5.6 Summary .....                               | 83 |

| Chapter 6 Conclusions and Future Work.....      | 84 |

| Bibliography.....                               | 86 |

## List of Figures

|                                                                                                                                                                              |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

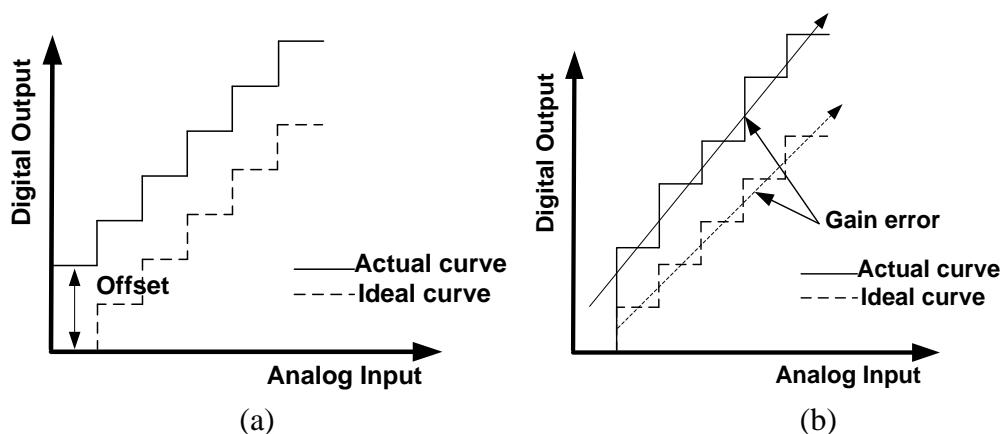

| Fig. 2.1 ADC transfer characteristic with (a) offset and (b) gain error .....                                                                                                | 4  |

| Fig. 2.2 DNL and INL in the ADC transfer characteristic .....                                                                                                                | 5  |

| Fig. 2.3 Total harmonic distortion in FFT spectrum .....                                                                                                                     | 7  |

| Fig. 2.4 Spurious free dynamic range in FFT spectrum.....                                                                                                                    | 8  |

| Fig. 2.5 Flash architecture.....                                                                                                                                             | 11 |

| Fig. 2.6 Pipelined ADC architecture .....                                                                                                                                    | 12 |

| Fig. 2.7 SAR ADC architecture .....                                                                                                                                          | 13 |

| Fig. 2.8 Pipelined-SAR ADC architecture .....                                                                                                                                | 14 |

| Fig. 2.9 Time-interleaved ADC architecture.....                                                                                                                              | 15 |

| Fig. 2.10 Timing diagram of time-interleaved ADC.....                                                                                                                        | 15 |

| Fig. 3.1 Time-interleaved architecture with offset mismatch .....                                                                                                            | 18 |

| Fig. 3.2 Transfer characteristic of time-interleaved architecture with offset mismatch .....                                                                                 | 18 |

| Fig. 3.3 Time-interleaved architecture with gain mismatch .....                                                                                                              | 20 |

| Fig. 3.4 Transfer characteristic of time-interleaved architecture with gain mismatch.                                                                                        | 20 |

| Fig. 3.5 Time-interleaved architecture with timing skew mismatch.....                                                                                                        | 22 |

| Fig. 3.6 Time-interleaved architecture with timing skew mismatch.....                                                                                                        | 22 |

| Fig. 3.7 Architecture of the proposed ADC with low-skew De-MUX .....                                                                                                         | 26 |

| Fig. 3.8 Timing diagram of the proposed ADC .....                                                                                                                            | 27 |

| Fig. 3.9 Single-ended schematic of the proposed low-skew demultiplexer .....                                                                                                 | 28 |

| Fig. 3.10 Waveform of $G_1$ , $G_2$ , and $V_{in}$ of low-skew De-MUX .....                                                                                                  | 29 |

| Fig. 3.11 Block diagram of sub-ADC with STL technique .....                                                                                                                  | 32 |

| Fig. 3.12 Timing diagram of sub-ADC .....                                                                                                                                    | 34 |

| Fig. 3.13 (a) The conventional method (b) the proposed STL technique .....                                                                                                   | 40 |

| Fig. 3.14 Timing diagram fo STL technique.....                                                                                                                               | 40 |

| Fig. 3.15 Equivalent model of the proposed charge sharing technique .....                                                                                                    | 44 |

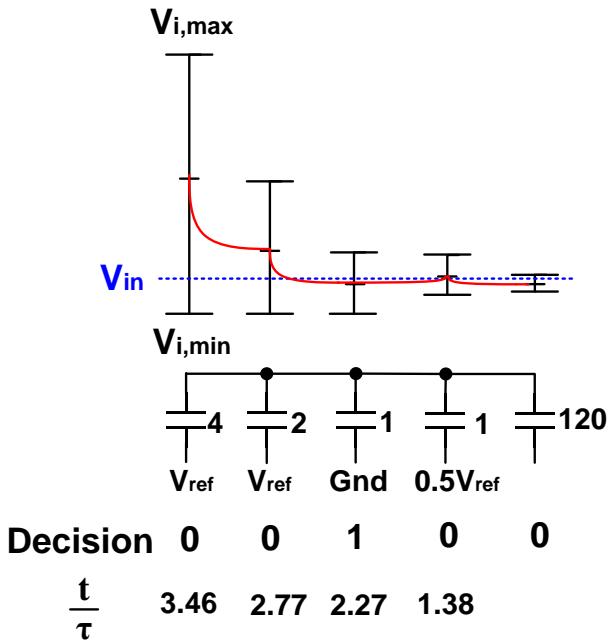

| Fig. 3.16 Detail of the switching scheme and the time needed for settling is given in multiples of time constant for a settling error $< 0.5 V_{LSB}$ in the fine stage..... | 51 |

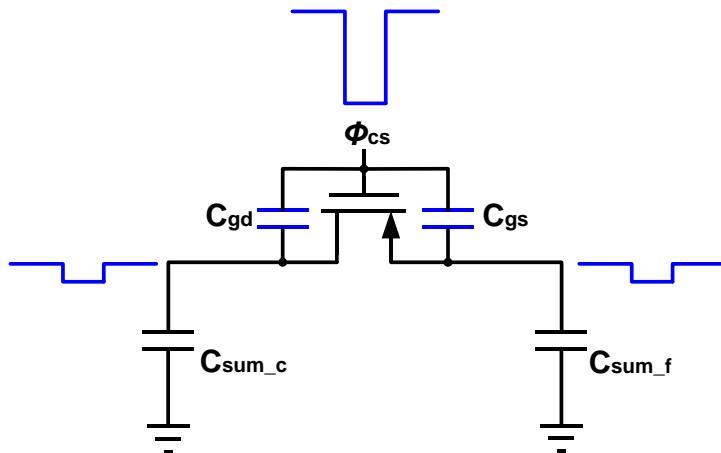

| Fig. 3.17 Clock feedthrough model of the charge sharing switch .....                                                                                                         | 52 |

| Fig. 3.18 Charge injection model of the charge sharing switch.....                                                                                                           | 54 |

| Fig. 3.19 Signal feedthrough model of the charge sharing switch.....                                                                                                         | 57 |

| Fig. 3.20 Timing diagram of the signal feedthrough .....                                                                                                                     | 58 |

| Fig. 3.21 Switching voltage feedthrough model of the charge sharing switch.....                                                                                              | 61 |

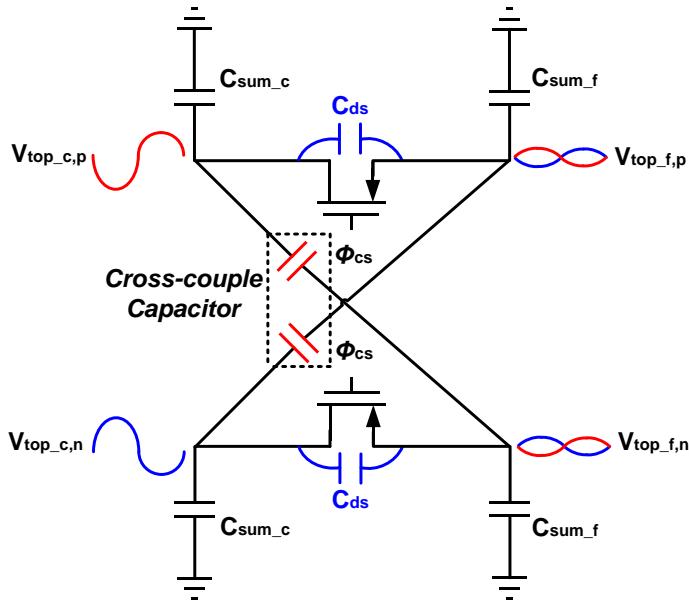

| Fig. 3.22 Cross-coupled capacitors with charge sharing switches.....                                                                                                         | 63 |

---

|                                                                                                                                                         |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

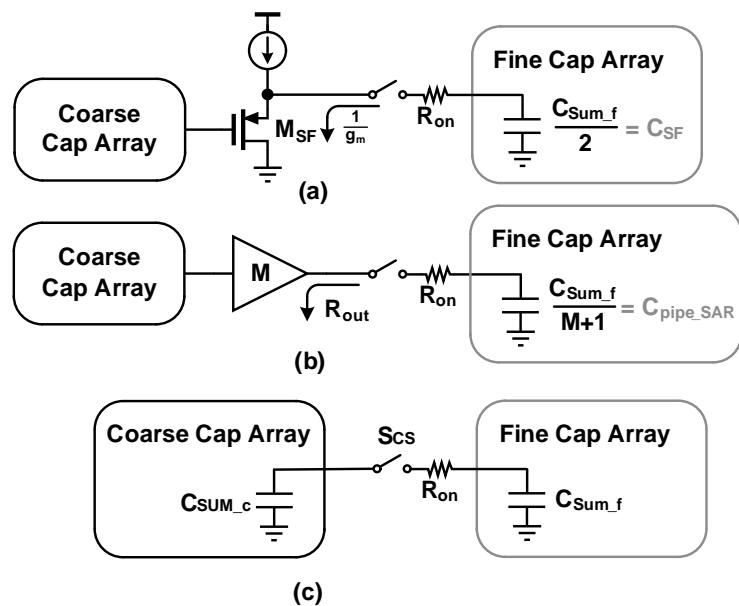

| Fig. 3.23 Block diagram of (a) the source follower topology (b) the traditional pipelined-SAR with opamp (c) the proposed charge sharing technique..... | 65 |

| Fig. 4.1 Clock phase generator .....                                                                                                                    | 67 |

| Fig. 4.2 Timing diagram of clock phase generator .....                                                                                                  | 67 |

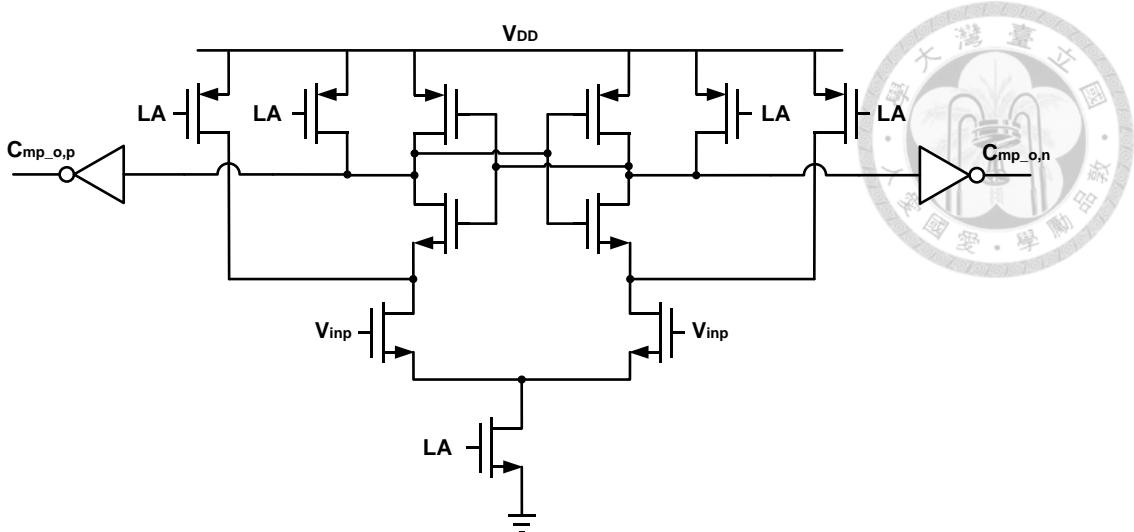

| Fig. 4.3 Strong-arm latch dynamic comparator .....                                                                                                      | 70 |

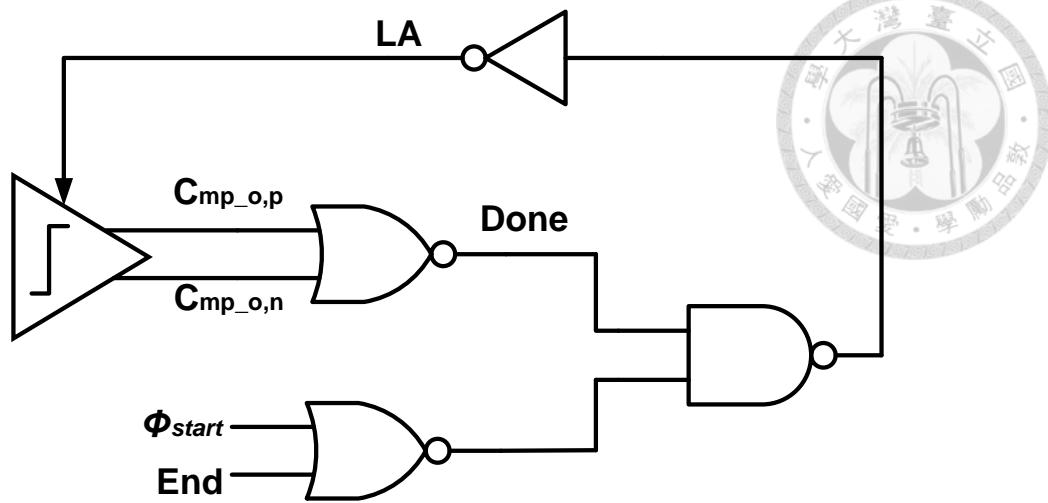

| Fig. 4.4 SAR control logic .....                                                                                                                        | 71 |

| Fig. 4.5 Capacitor array of the coarse and fine stage .....                                                                                             | 71 |

| Fig. 4.6 Charge sharing timing control logic .....                                                                                                      | 73 |

| Fig. 4.7 Timing diagram of charge sharing timing control logic .....                                                                                    | 73 |

| Fig. 5.1 Test setup .....                                                                                                                               | 76 |

| Fig. 5.2 PCB Photo .....                                                                                                                                | 77 |

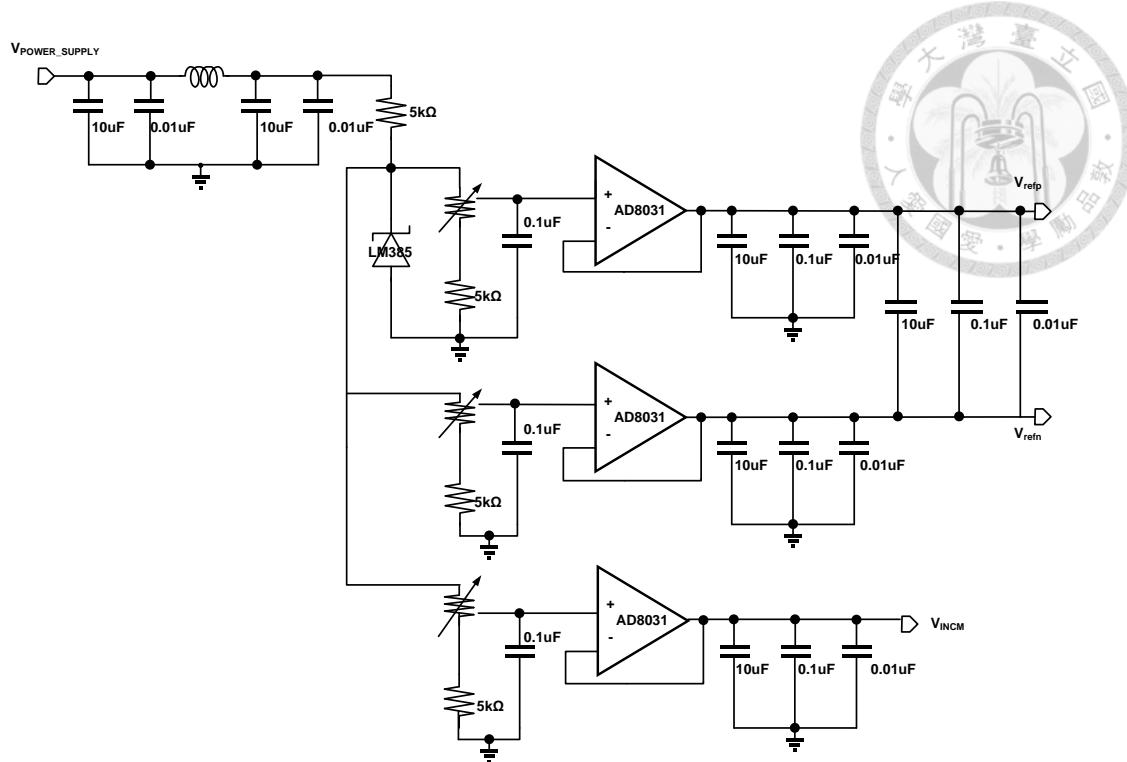

| Fig. 5.3 Schemtaic of reference voltage generation.....                                                                                                 | 78 |

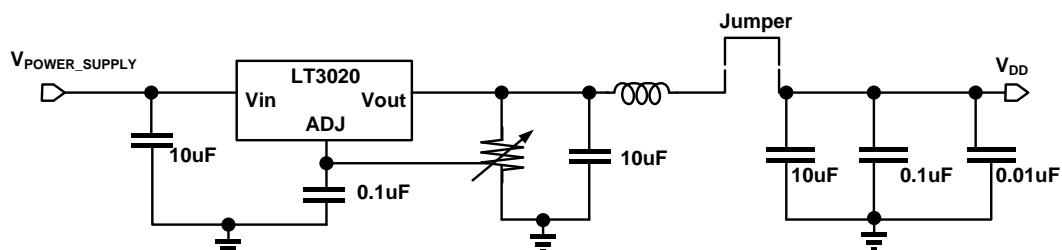

| Fig. 5.4 Schematic of power supply generation.....                                                                                                      | 78 |

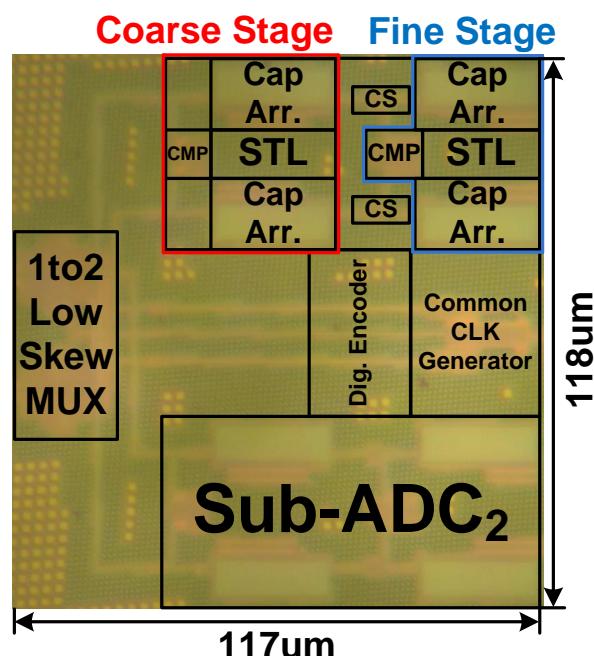

| Fig. 5.5 Die photo .....                                                                                                                                | 79 |

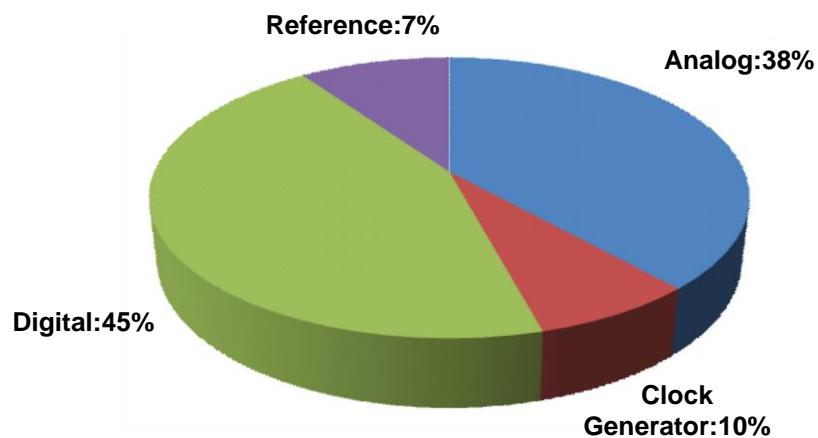

| Fig. 5.6 Power dissipation.....                                                                                                                         | 79 |

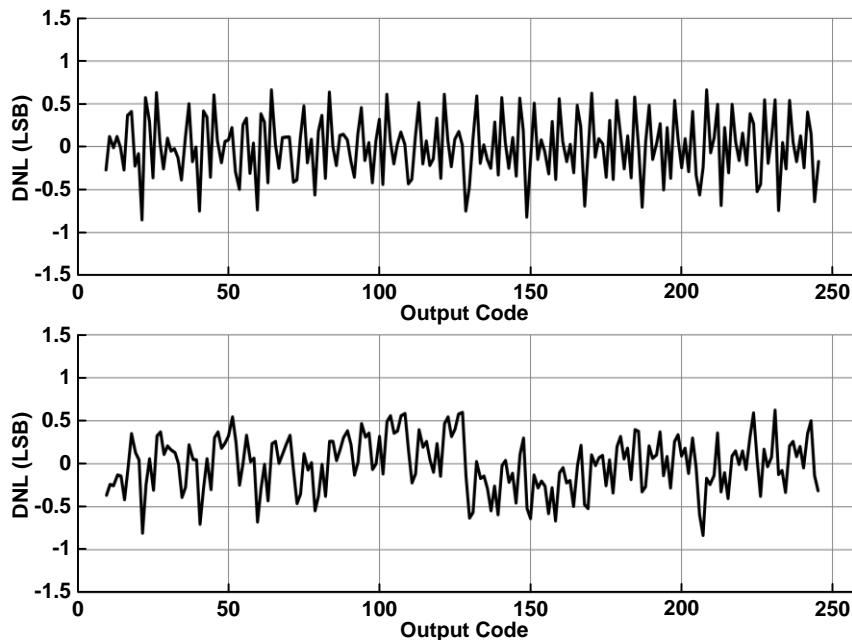

| Fig. 5.8 Measured DNL/INL plot .....                                                                                                                    | 80 |

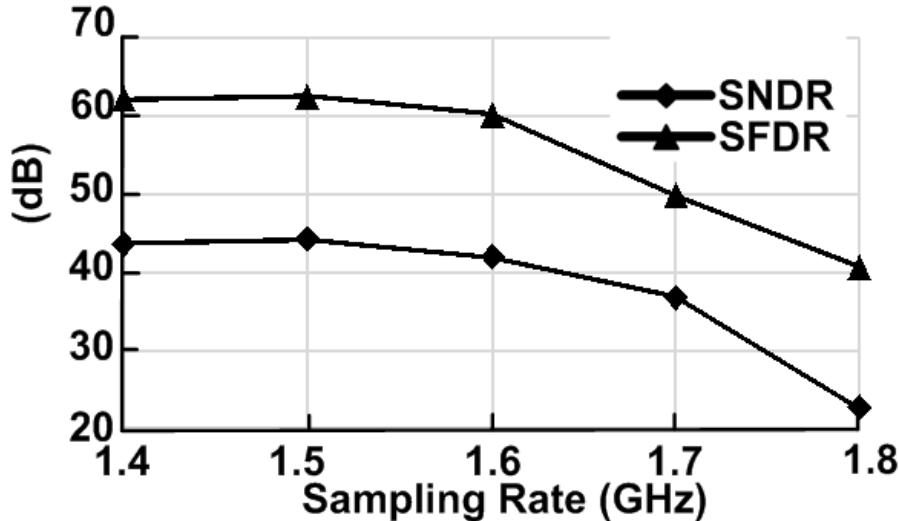

| Fig. 5.9 Measured SNDR/SFDR versus sampling rate with 1MHz input .....                                                                                  | 81 |

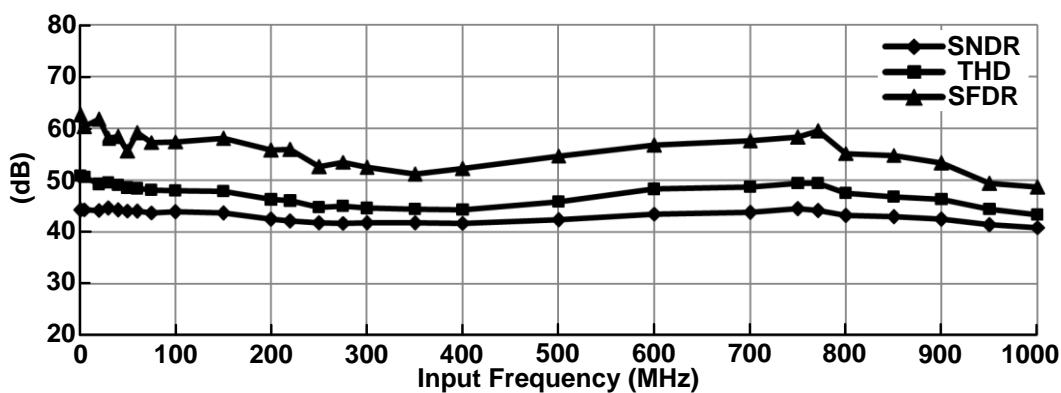

| Fig. 5.10 Measured SNDR/SFDR/THD versus input frequency at 1.5GS/s .....                                                                                | 81 |

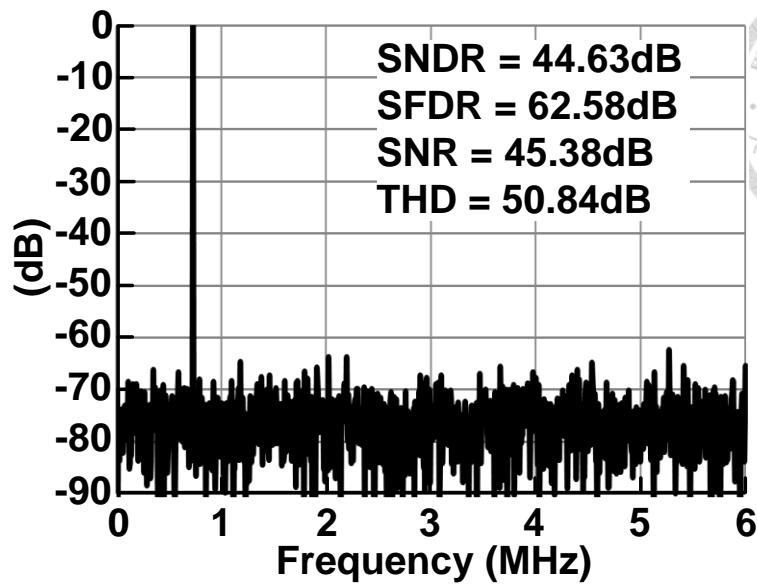

| Fig. 5.11 Measured FFT spectrum at 1.5GS/s with 0.73MHz input.....                                                                                      | 82 |

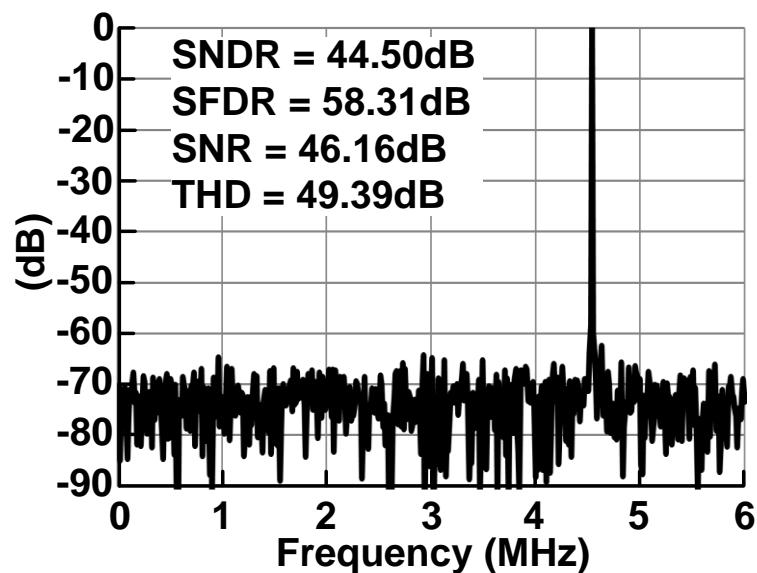

| Fig. 5.12 Measured FFT spectrum at 1.5GS/s with 748.5MHz input.....                                                                                     | 82 |

## List of Tables

Table. 5.1 Performance summary performance summary and comparison ..... 83

# Chapter 1 Introduction

## 1.1 Motivation

Hundreds MS/s to 1GS/s medium resolution Analog-to-Digital Convertors (ADCs) are used in applications such as Ethernet networks, wireless communication systems and hard disk read channels.

Flash ADC is the fastest architecture to achieve GS/s sampling rate ( $F_S$ ), but its power consumption and area turns up exponential when its resolution rises. Pipelined ADC is also a high-speed architecture and its cost increases linearly as its resolution grows. However, it needs lots of high-bandwidth but power-hungry residue amplifiers.

Successive-approximation register (SAR) ADC is a popular architecture due to its simple, energy-efficient architecture. But, the speed of SAR ADC is limited by the regeneration time of the comparator and the digital loop delay time. Several methods are reported to speed up  $F_S$  of the SAR ADCs such as [1][2]. However, it degrades the charming FoM performance when single-channel 8-bit ADCs work at their speed limitations of around 0.9-1.3GS/s [1]-[3].

Time-interleaved (TI) ADC [12]-[15] is the most intuitive method to increase  $F_S$  by paralleling many slow but energy-efficient sub-ADC channels. Besides,

time-interleaved architecture can relax the tradeoff between the speed and power. The small area and energy-efficient SAR ADC is one of the best choice used for interleaved sub-ADCs. Nevertheless, the high-speed multi-phase clock generator and the complex timing skew calibration circuit consume large power dissipation [36]-[38] calibration. The high-speed and energy-efficient two-step SAR ADCs are selected for sub-ADCs. The sub-ADC utilizes the charge-sharing (CS) technique and self-triggered latch (STL) technique to achieve high-speed and low-power dissipation.

## 1.2 Thesis Organization

There are 6 chapters in this thesis. In chapter 1, the motivation and thesis organization are introduced briefly. In chapter 2, the fundamentals of Analog-to-Digital Converter are discussed. Besides, the commonly used high speed ADC architectures are described. In chapter 3, the error source of the time-interleaved ADC is reviewed. Then the proposed two-channel time-interleaved SAR ADC is presented to solve the timing skew problem of the time-interleaved ADC. Besides, the design consideration of the proposed high-speed and energy-efficient two-step SAR sub-ADC is present. In chapter 4, the circuit implementation of the proposed two-channel time-interleaved SAR ADC is present in detail. In chapter 5, the

measurement results and measurement methods are presented. Finally, the conclusion and future work are discussed in chapter 6.

# Chapter 2 Fundamentals of Analog-to-Digital Converter

## 2.1 Introduction

ADC is used extensively in many applications such as portable devices and sensors. The different applications pay attention on different characteristics of ADC. In order to judge the performance of ADC, the performance metrics are defined in Section 2.2. Besides, the various architectures of ADC are introduced in Section 2.3.

## 2.2 Performance Metrics

### 2.2.1 Offset and Gain Error

Fig. 2.1 (a) shows the offset error in the transfer curve of ADC. The offset error is defined as the shift of the actual curve from the ideal curve. Fig. 2.1 (b) depicts the gain error in the transfer curve of ADC. The gain error is defined as the difference of the slope of the ideal curve and actual curve, where the offset error is removed.

Fig. 2.1 ADC transfer characteristic with (a) offset and (b) gain error

### 2.2.2 Differential and Integral Nonlinearity (DNL and INL)

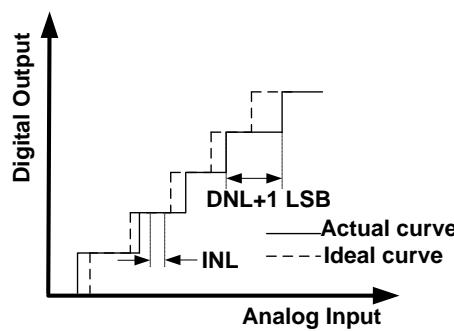

Differential nonlinearity (DNL) is given as the difference between each step size of the actual ADC from the ideal width of 1 LSB, where the offset and gain error are removed. Therefore, DNL can be written as:

$$DNL = \frac{V_{n+1} - V_n}{V_{LSB}} - 1, \quad 0 \leq n \leq (2^N - 1) \quad (2.1)$$

where  $V_n$  is the transition point of digital output code  $n$ ,  $N$  is number bit resolution of ADC and  $V_{LSB}$  is the voltage level of 1LSB which equals to the ADC full scale amplitude divided by  $2^N$ . Therefore, DNL is expressed in LSB. If each step size of the actual ADC is equal to 1 LSB, DNL is equal to zero. And, if digital output code  $n$  is never appeared, the corresponding DNL is equal to -1.

Integral nonlinearity (INL) is defined as the maximum deviation of the actual curve from the ideal curve and its unit is also expressed in LSB. The INL can be derived by integrating DNL from code 0 to code  $n$ . The plot describes DNL and INL is shown in Fig. 2.2.

$$INL(n) = \sum_{i=1}^n DNL(i) \quad (2.2)$$

Fig. 2.2 DNL and INL in the ADC transfer characteristic

### 2.2.3 Signal-to-Noise Ratio (SNR)

Signal-to-noise ratio (SNR) is the ratio of the signal power (usually measured for a sine input) to the total noise power produced by quantization in the output code domain and the ADC circuitry in the band of interest. Quantization noise  $\varepsilon_q$  is a major noise source of ADC caused by the limited quantization levels. It means the difference of the analog input and the digital output. The waveform after the A/D conversion experiences both positive and negative quantization error. It can be assumed that the quantization noise  $\varepsilon_q$  is a random variable uniformly distributed between  $[-\Delta/2, +\Delta/2]$ , where  $\Delta$  is equal to 1 LSB. Thus, the noise power can be used to express the influence by quantization noise. The power of quantization noise can be expressed as

$$P_{eq} = \frac{1}{\Delta} \int_{-\Delta/2}^{+\Delta/2} \varepsilon_q^2 \times d\varepsilon_q = \frac{\Delta^2}{12} \quad (2.3)$$

If input signal is a sinusoid wave with amplitude  $\frac{V_{ref}}{2}$ , the power of input signal is equal to

$$P_{in} = \frac{1}{T} \int_0^T \left( \frac{V_{ref}}{2} \sin(2\pi ft) \right)^2 \cdot dt = \frac{(2^N \cdot \Delta)^2}{8} \quad (2.4)$$

where  $f$  is the input frequency, N is the resolution of the ADC.

According to (2-3) and (2-4), SNR is generally expressed in dB as follows:

$$SNR|_{dB} = 10 \log \left( \frac{P_{in}}{P_{eq}} \right) = 10 \log \left( \frac{3 \cdot 2^{2N}}{2} \right) = 6.02N + 1.76 \quad (2.5)$$

### 2.2.4 Total Harmonic Distortion (THD)

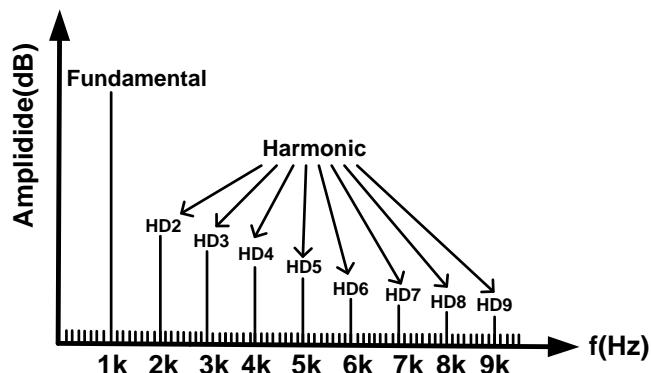

Total harmonic distortion (THD) is the ratio of the power of all the harmonics to the power of signal. The result is generally expressed in dB and it is usually a positive number. THD is an indication of nonlinearity while harmonics are dominated by the repetitive error sources in the convertor. The plot presents THD is shown in Fig. 2.3 and THD is expressed as follows:

$$THD|_{dB} = 10 \log \left( \frac{P_{hd}}{P_{in}} \right) \quad (2.6)$$

Fig. 2.3 Total harmonic distortion in FFT spectrum

### 2.2.5 Spurious Free Dynamic Range (SFDR)

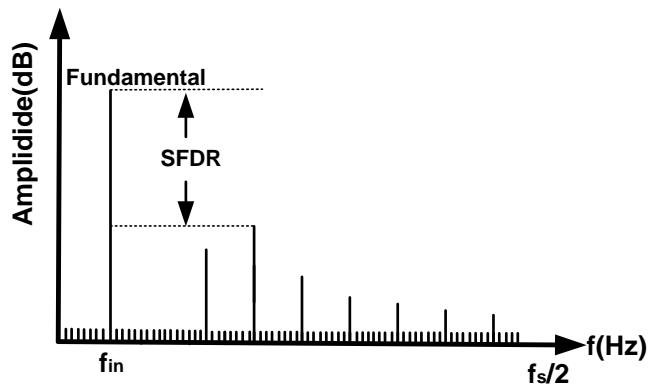

The spurious-free dynamic range (SFDR) is the ratio of the signal power to the largest spurious in the frequency domain. SFDR means how well an ADC can detect a very small signal simultaneously in the presence of a very large signal. It is one of the crucial requirements in the wireless communication application. The plot presents SFDR is shown in Fig. 2.4 and SFDR can be defined as:

$$SFDR|_{dB} = 10 \log \left( \frac{P_{in}}{\text{The largest spurious power}} \right) \quad (2.7)$$

Fig. 2.4 Spurious free dynamic range in FFT spectrum

### 2.2.6 Signal to Noise and Distortion Ratio (SNDR)

Signal to noise and distortion ratio (SNDR) is the ratio of the signal power to the sum of total noise power and total harmonic distortion power. SNDR is written as:

$$SNDR|_{dB} = 10 \log \left( \frac{P_{in}}{P_n + P_{hd}} \right) \quad (2.8)$$

### 2.2.7 Effective Number of Bits (ENOB)

The effective number of bits (ENOB) is a measure based on the SNDR of an ADC converter. It describes the achieved resolution of ADC including noise and harmonic distortion. In equation (2-5), SNDR is replaced by SNR to calculate ENOB:

$$ENOB|_{bit} = \frac{SNDR|_{dB} - 1.76}{6.02} \quad (2.9)$$

### 2.2.8 Figure of Merit (FoM)

Figure of Merit (FoM) is a mixed performance metric for ADC based on the total power dissipation, sampling frequency and accuracy. It is used to judge the performance of ADC. There are two commonly used *FoM* definitions: Walden *FoM* and Schreier *FoM*.

$$\text{Walden FoM} = \frac{\text{Total Power Dissipation}}{F_s \times 2^{\text{ENOB}}} \quad (2.10)$$

$$\text{Schreier FoM} = \text{SNDR}_{\text{dB}} + 10 \log\left(\frac{F_s / 2}{\text{Total Power Dissipation}}\right) \quad (2.11)$$

Walden *FoM* is suitable for low-resolution designs. Schreier *FoM* is suitable for high-resolution designs that also push bandwidth. In this thesis, Walden *FoM* is used to compare this work with previous works and state-of-the-art.

## 2.3 ADC Architectures

ADC can be classified into two types, Nyquist rate ADC and oversampling ADC. The sampling rate of Nyquist rate ADC is slightly larger than twice the input bandwidth, which allows the accuracy reproduction the original waveform.

For an oversampling ADC, the signal is sampled many times with a sampling frequency such higher than Nyquist rate to remove the noise outside the band of interest to improve the accuracy. In the following section, several Nyquist rate ADC architectures are discussed for high-speed application.

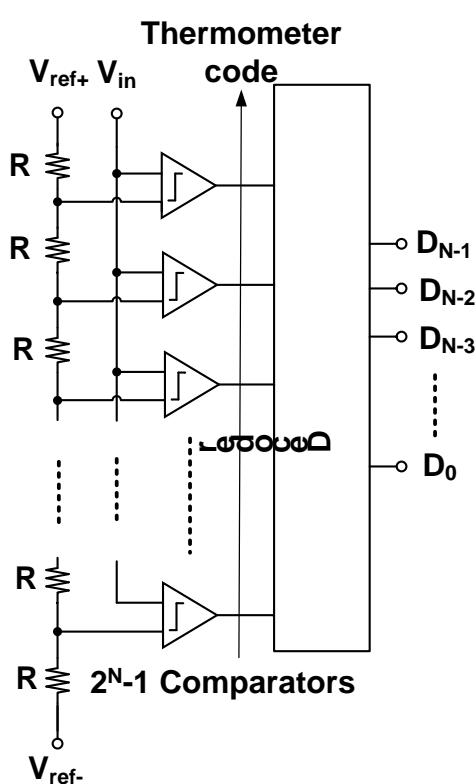

### 2.3.1 Flash Architecture

Fig. 2.5 shows the normal architecture of flash ADC. It is composed of  $2^N - 1$  comparators, a resistor ladder and a decoder, where N represents the resolution of ADC. The resistor ladder consists of  $2^N$  equal segments and provides  $2^N$  voltage level for comparison. The operation process is that the comparators compare the input signal with these voltage levels simultaneously and generate the comparator outputs. The comparator outputs are in the form of the thermometer code and converted to binary code by the decoder. Consequently, the flash ADC has the smallest latency time than other architectures for the single-channel ADC.

However, flash ADC suffers from the input-referred offset of comparators and the exponential growing area when its resolution rises up. Pre-amplifier and average network are commonly used to solve the problem of the input-referred offset. Besides, interpolation technique is proposed to reduce the hardware area caused by numerous comparators [16]. Nevertheless, the flash ADC still consumes large power dissipation.

Fig. 2.5 Flash architecture

### 2.3.2 Pipelined Architecture

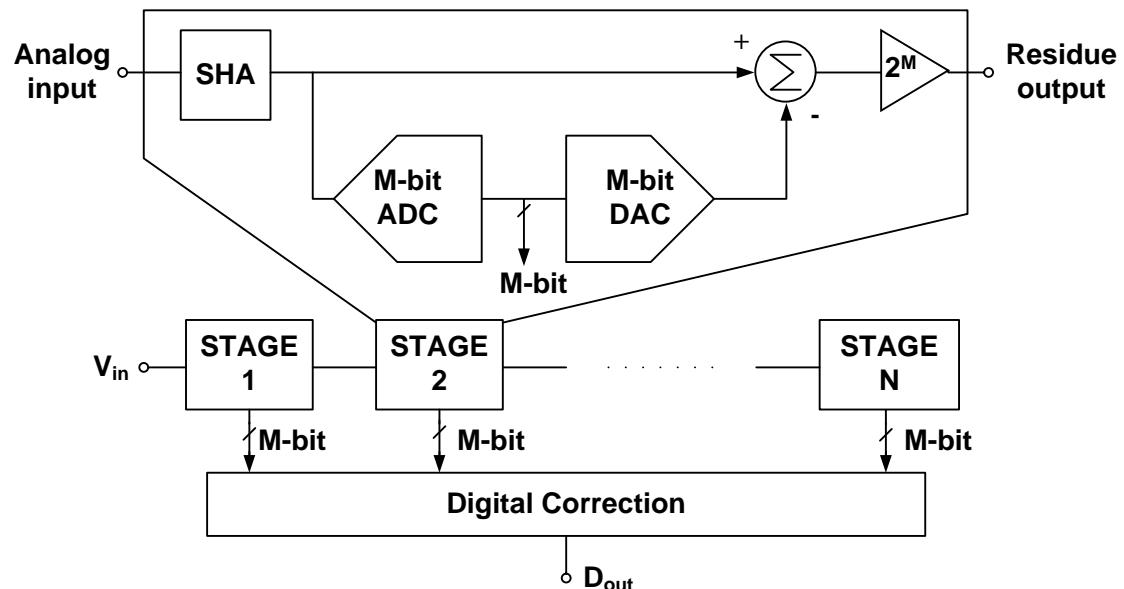

Fig. 2.6 depicts the block diagram of pipelined ADC. It consists of a series of identical stages separated by a sample-and-hold amplifier (SHA) where SHA is the part of sub-stage. If the resolution of the sub-stage is M-bit, it generates the M-bit digital output and a residue voltage for the next stage. The residue voltage will be amplified for the next stage by the residue amplifier. Compared with flash architecture, the number of the comparators can be reduced because the residue is amplified to full-scale. By utilizing the pipelined architecture, the latency can be greatly reduced and it can achieve the high conversion rate.

However, the bottleneck of the pipelined ADC is the high-bandwidth but power-hungry residue amplifiers in the sub-stages. The residue amplifiers consume large power dissipation to achieve the speed and accuracy requirements.

Fig. 2.6 Pipelined ADC architecture

### 2.3.3 Successive-Approximation-Register (SAR) Architecture

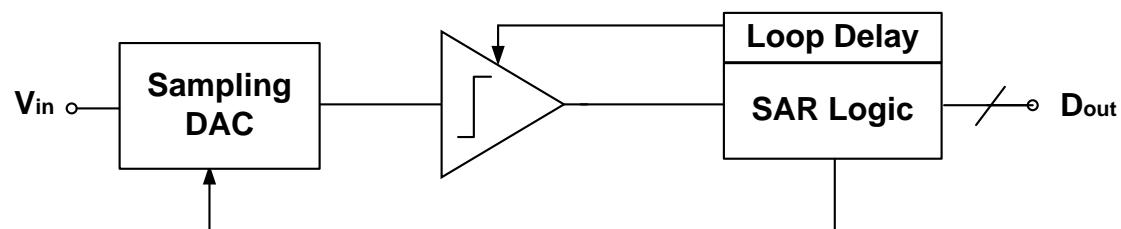

Recently, successive-approximation-register (SAR) ADC becomes popular with the advanced CMOS process because most parts of SAR ADC are digital circuits. Fig. 2.7 shows the block diagram of the successive-approximation-register (SAR) ADC. SAR ADC consists of a sampling DAC, a comparator, loop delay cells and the SAR logic.

The operation process is that input signal is sampled on the sampling DAC, and then the comparator regenerates input signal and generates the comparator results.

The comparator results are delivered to the SAR logic and the DAC. The SAR logic stores the comparator results and the DAC sets the corresponding switching for the following SAR conversion. Thanks to the SAR algorithm and the simple architecture without residue amplifier, it results in the good power-efficiency and small area.

Furthermore, the offset issue caused by the comparator doesn't degrade the linearity of the SAR ADC. The offset can be removed in the digital domain.

However, in the N-bit conventional SAR ADC, the latency is very long because it needs to regenerative input signal for N times in one data conversion. The speed of SAR ADC is limited by the regeneration time of the comparator and the digital loop delay time. It results in the long latency which is N times larger than the flash architecture.

Fig. 2.7 SAR ADC architecture

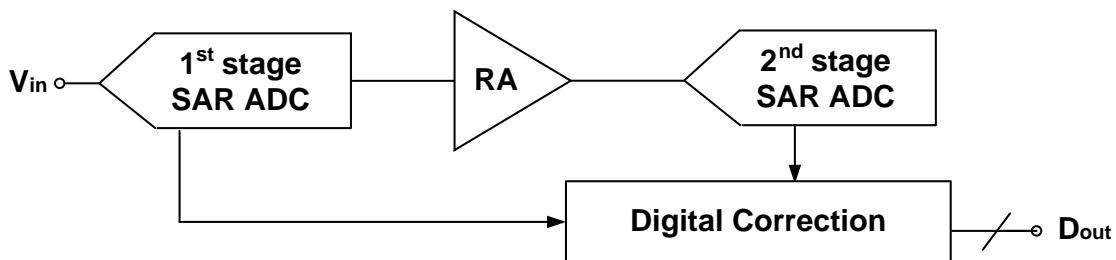

#### 2.3.4 Pipelined-SAR Architecture

Fig. 2.8 shows the block diagram of a Pipelined-SAR ADC[11]. The block diagram of the pipelined-SAR ADC consists of two stages of SAR ADCs and an inter-stage residue amplifier. Combining the high conversion rate of pipelined ADC

and the energy efficiency of SAR ADC, the pipelined-SAR ADC gets the advantages from these two architectures.

The operation process is that the 1<sup>st</sup> stage SAR ADC samples input signal and then resolves the MSB decision. After the MSB decision, the residue is stored on the 1<sup>st</sup> stage SAR ADC and be delivered to the 2<sup>nd</sup> stage SAR ADC by the residue amplifier. Thus, the 2<sup>nd</sup> stage SAR ADC resolves the LSB decision of the previous input signal and the 1<sup>st</sup> stage SAR ADC samples the next input signal.

But, a low-noise high-bandwidth residue amplifier is not only power-hungry, but also hard to design in advanced CMOS process.

Fig. 2.8 Pipelined-SAR ADC architecture

### 2.3.5 Time-Interleaved Architecture

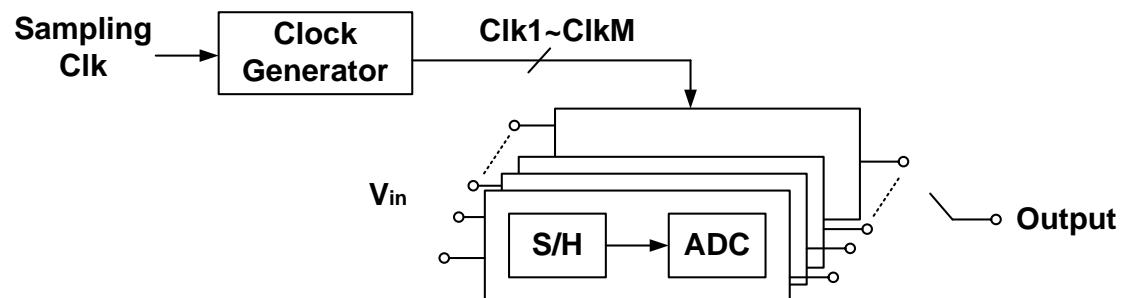

Time-interleaved (TI) ADC is the most intuitive method to increase FS by paralleling many sub-ADC channels. Fig. 2.9 shows the block diagram of time-interleaved ADC. Time-interleaved ADC consists of the clock generator and M channels sub-ADCs, which perform as the single channel ADC and can be implemented by any ADC architecture such as flash, pipelined or SAR.

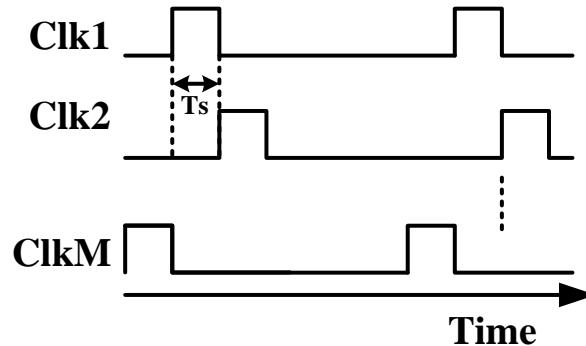

The operation process is that the clock generator generates  $\text{Clk1}$  to  $\text{ClkM}$ , which trigger  $M$  channels sub-ADCS to sample input signal and perform the conversion. When the conversion of the sub-ADCs is finished, the conversion results are realigned and delivered to the output. Fig. 2.10 shows the timing diagram of time-interleaved ADC.

Fig. 2.9 Time-interleaved ADC architecture

Fig. 2.10 Timing diagram of time-interleaved ADC

The small area and energy-efficient SAR ADC is one of the best choice used for interleaved sub-ADCs. Accordingly, by paralleling many sub-ADC channels, time-interleaved ADC can relax the tradeoff between the speed and power. Nevertheless, the high-speed multi-phase clock generator consumes large power dissipation when the number of sub-ADC channels grows.

Besides, the channel mismatches between the M channel sub-ADCs including the offset mismatch, gain mismatch and skew mismatch deteriorate the performance of time-interleaved ADC. Although the offset mismatch and the gain mismatch can be calibrated without complex calibration [8], the timing skew mismatch degrades of time-interleaved ADC and needs complicated calibration circuit to eliminate the timing skew mismatch.

## Chapter 3 Time-Interleaved SAR ADC

### 3.1 Introduction

This chapter will describe the proposed time-interleaved SAR ADC. First, the error sources in time-interleaved ADC will be discussed in Section 3.2. After understanding the error sources in time-interleaved ADC, the proposed low-skew demultiplexer will be described in Section 3.3. In Section 3.4, the two-step SAR sub-ADC architecture is elaborated. The design consideration of the time-interleaved SAR ADC will be discussed and analyzed. Finally, the summary will be discussed in Section 3.6.

### 3.2 Error Sources in Time-Interleaved ADC Architecture

#### 3.2.1 Offset Mismatch

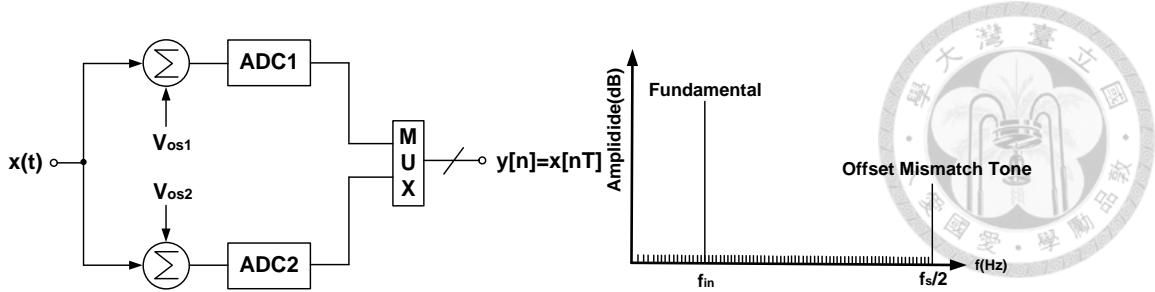

Fig. 3.1 shows a two-channel ADC with offset mismatch. The two sub-ADCs are identical except for the offset voltages  $V_{osi}$ , where  $i$  represents 1 or 2. The different offset voltages  $V_{osi}$  cause the offset of the transfer characteristic of time-interleaved architecture, as shown in Fig. 3.2.

Fig. 3.1 Time-interleaved architecture with offset mismatch

Fig. 3.2 Transfer characteristic of time-interleaved architecture with offset mismatch

mismatch

A mathematical analysis of the output of the time-interleaved ADC with only offset mismatch is derived in the following equation. A two-channel time-interleaved ADC is taken for the example. The output of the time-interleaved ADC [9] in Fig. 3.1 with a sinusoidal input  $x(t) = \cos(2\pi f_{in} n T_s)$  is

$$y[n] = \cos(2\pi f_{in} n T_s) + V_{os1}, n = \text{even} \quad (3.1)$$

$$y[n] = \cos(2\pi f_{in} n T_s) + V_{os2}, n = \text{odd} \quad (3.2)$$

Let  $V_{os} = \frac{(V_{os1} + V_{os2})}{2}$  and  $\Delta V_{os} = V_{os1} - V_{os2}$ . Then the output of the time-interleaved ADC can be given as

$$y[n] = \cos(2\pi f_{in} n T_s) + V_{os} + (-1)^n \frac{\Delta V_{os}}{2} \quad (3.3)$$

Using  $(-1)^n = \cos(\frac{2\pi f_s n T_s}{2})$ , (3.3) can be written as

$$y[n] = \cos(2\pi f_{in} n T_s) + V_{os} + \frac{\Delta V_{os}}{2} \cos\left[2\pi\left(\frac{f_s}{2}\right)n T_s\right] \quad (3.4)$$

The second and third terms in (3.4) validate that the different offset voltage of the time-interleaved ADC give a dc value and a periodic additive pattern in the output of the time-interleaved ADC. In frequency domain, the different offset voltages  $V_{osi}$  cause a distortion tone at  $f_s / 2$ .

Generally, for an M-channel time-interleaved ADC, the distortion caused by offset mismatch is signal independent and appears at

$$f_{noise} = k \cdot f_s / M, k = 0, 1, \dots, M-1 \quad (3.5)$$

The noise power caused by offset mismatch can be expressed as

$$P_{noise} = \sigma_{offset}^2 \quad (3.6)$$

where the channel offset mismatches are Gaussian random variables with zero mean, and  $\sigma_{offset}$  is the standard deviation of offset mismatch.

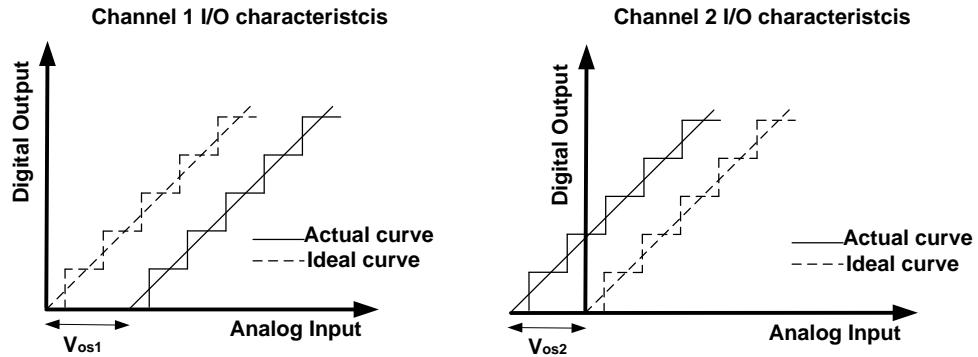

### 3.2.2 Gain Mismatch

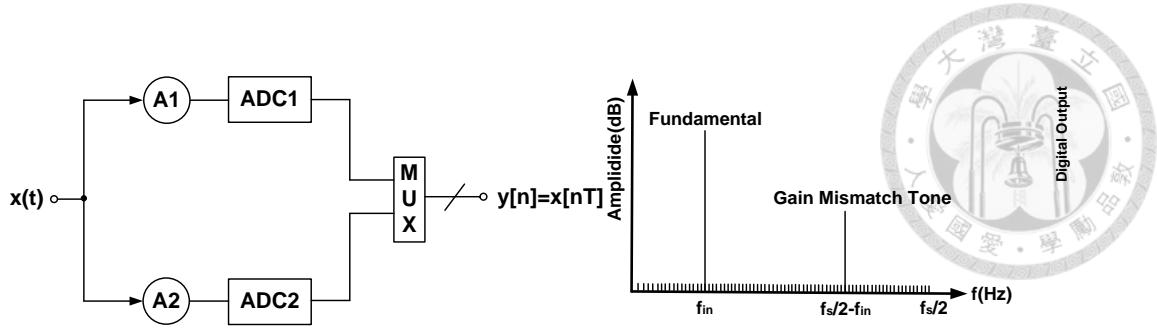

Fig. 3.3 shows a two-channel ADC with gain mismatch. The two sub-ADCs are identical except for the gain of each channel  $A_i$ , where  $i$  represents 1 or 2. The different gains of each channel  $A_i$  cause the difference of the slope of the transfer characteristic of time-interleaved architecture, as shown in Fig. 3.4.

Fig. 3.3 Time-interleaved architecture with gain mismatch

Fig. 3.4 Transfer characteristic of time-interleaved architecture with gain

mismatch

A mathematical analysis of the output of the time-interleaved ADC with only gain mismatch is derived in the following equation. A two-channel time-interleaved ADC is taken for the example. The output of the time-interleaved ADC [9] in Fig. 3.3 with a sinusoidal input  $x(t) = \cos(2\pi f_{in} n T_s)$  is

$$y[n] = A_1 \cos(2\pi f_{in} n T_s), n = \text{even} \quad (3.7)$$

$$y[n] = A_2 \cos(2\pi f_{in} n T_s), n = \text{odd} \quad (3.8)$$

Let  $A = \frac{(A_1 + A_2)}{2}$  and  $\Delta A = A_1 - A_2$ . Then the output of the time-interleaved ADC can

be given as

$$y[n] = \left[ A + (-1)^n \frac{\Delta A}{2} \right] \cos(2\pi f_{in} n T_s) \quad (3.9)$$

Using  $(-1)^n = \cos(\frac{2\pi f_s n T_s}{2})$ , the (3.9) can be written as

$$y[n] = A \cos(2\pi f_{in} n T_s) + \frac{\Delta A}{2} \cos\left[2\pi(f_{in} - \frac{f_s}{2})n T_s\right] \quad (3.10)$$

In (3.10), the first term is the scaled input and the second term is the image due to channel gain mismatch. The second term in (3.10) shows that the image amplitude is proportional to the gain error  $\Delta A$ . In frequency domain, the different gain of each channel  $A_i$  cause a distortion tone at  $f_s / 2 - f_{in}$ .

In general, M-channel time-interleaved ADC, the distortion caused by gain mismatch occurs at

$$f_{noise} = \pm f_{in} + k \cdot f_s / M, k = 0, 1, \dots, M-1 \quad (3.11)$$

The noise power caused by gain mismatch can be expressed as

$$P_{noise} = (A \cdot \sigma_{gain})^2 \quad (3.12)$$

where  $A$  is the amplitude of a sine input and the channel gain mismatches are Gaussian random variables, and  $\sigma_{gain}$  is the standard deviation of gain mismatch.

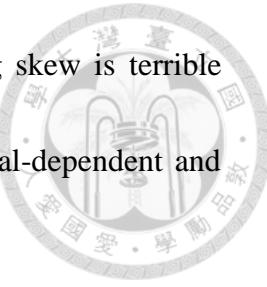

### 3.2.3 Timing Skew Mismatch

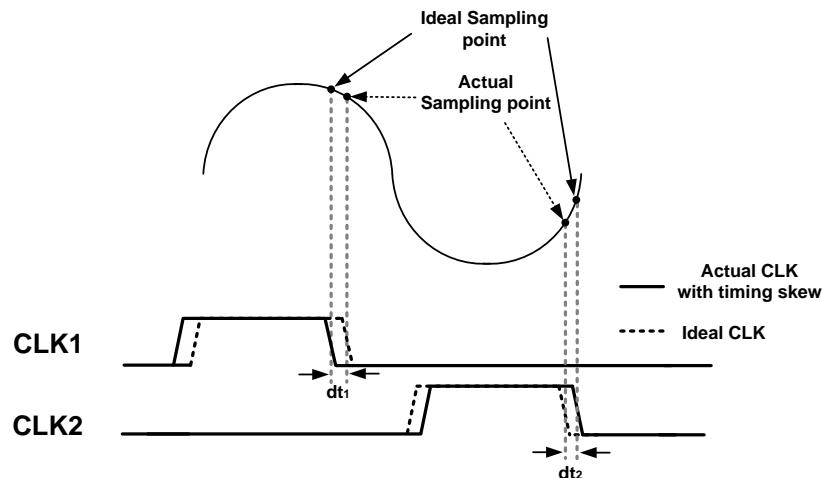

Fig. 3.5 shows a two-channel ADC with timing skew mismatch. The two sub-ADCs are identical except for the skewed  $CLK_i$ , where  $i$  represents 1 or 2. The skewed  $CLK_i$  causes the different sampling time shift of the time-interleaved

architecture, as shown in Fig. 3.6. The error caused by the timing skew is terrible when the input signal has large slew rate. That is, the error is signal-dependent and serious with high frequency input signal.

Fig. 3.5 Time-interleaved architecture with timing skew mismatch

Fig. 3.6 Time-interleaved architecture with timing skew mismatch

A mathematical analysis of the output of the time-interleaved ADC with only timing skew mismatch is derived in the following equation. A two-channel time-interleaved ADC is taken for the example. Assuming that ADC1 samples input signal at a time  $T_s + \Delta t$  after ADC2, where  $\Delta t$  is the timing skew deviated from ideal timing, so the combination of the two channels samples the input signal at times

$nT_s + \frac{\Delta t}{2} - (-1)^n \frac{\Delta t}{2}$ . The output of the time-interleaved ADC [9] in Fig. 3.5 with a sinusoidal input  $x(t) = \cos(2\pi f_{in} nT_s)$  is

$$y[n] = \cos \left\{ 2\pi f_{in} \left[ nT_s + \frac{\Delta t}{2} - (-1)^n \frac{\Delta t}{2} \right] \right\} \quad (3.13)$$

$$\begin{aligned} &= \cos \left[ 2\pi f_{in} (nT_s + \frac{\Delta t}{2}) \right] \cos \left[ (-1)^n 2\pi f_{in} \frac{\Delta t}{2} \right] \\ &+ \sin \left[ 2\pi f_{in} (nT_s + \frac{\Delta t}{2}) \right] \sin \left[ (-1)^n 2\pi f_{in} \frac{\Delta t}{2} \right] \end{aligned} \quad (3.14)$$

Using the facts that  $\cos(x)$  is an even function and  $\sin(x)$  is an odd function, and

$(-1)^n = \cos(n\pi)$ , (3.14) can be given as

$$\begin{aligned} y[n] &= \cos \left[ 2\pi f_{in} (nT_s + \frac{\Delta t}{2}) \right] \cos \left( 2\pi f_{in} \frac{\Delta t}{2} \right) \\ &+ \sin \left[ 2\pi f_{in} (nT_s + \frac{\Delta t}{2}) \right] \cos(n\pi) \sin \left( 2\pi f_{in} \frac{\Delta t}{2} \right) \end{aligned} \quad (3.15)$$

Using the facts that  $\sin(a)\cos(n\pi) = \sin(a - n\pi)$ , and  $n\pi = \frac{2\pi f_s n T_s}{2}$ , the output of

the time-interleaved ADC can be given as

$$\begin{aligned} y[n] &= \cos \left[ 2\pi f_{in} (nT_s + \frac{\Delta t}{2}) \right] \cos \left( 2\pi f_{in} \frac{\Delta t}{2} \right) \\ &+ \sin \left[ 2\pi f_{in} (nT_s + \frac{\Delta t}{2}) + \frac{2\pi f_s n T_s}{2} \right] \sin \left( 2\pi f_{in} \frac{\Delta t}{2} \right) \\ &= \cos \left( 2\pi f_{in} \frac{\Delta t}{2} \right) \cos \left[ 2\pi f_{in} n T_s + 2\pi f_{in} \frac{\Delta t}{2} \right] \end{aligned} \quad (3.16)$$

$$+ \sin \left( 2\pi f_{in} \frac{\Delta t}{2} \right) \sin \left[ 2\pi \left( f_{in} - \frac{f_s}{2} \right) n T_s + 2\pi f_{in} \frac{\Delta t}{2} \right] \quad (3.17)$$

In (3.17), the first term is input signal which phase shift is  $2\pi f_{in} \frac{\Delta t}{2}$ , and the

second term shows that the image is  $90^\circ$  out of phase with the image due to gain

mismatch in (3.10). The added phase shift  $2\pi f_{in} \frac{\Delta t}{2}$  results from the average delay of

$\frac{\Delta t}{2}$  caused by the timing skew mismatch of  $\Delta t$ . In frequency domain, the distortion

which is caused by the skewed  $CLK_i$  results in a distortion tone at  $f_s/2 - f_{in}$ . It represents that the error signal with a period of  $M/f_s$  is modulated by input frequency  $f_{in}$ .

For an M-channel time-interleaved ADC, the distortion caused by timing skew mismatch occurs at

$$f_{noise} = \pm f_{in} + k \cdot f_s / M, k = 0, 1, \dots, M-1 \quad (3.18)$$

The noise power caused by timing skew mismatch can be expressed as

$$P_{noise} = (A \cdot 2\pi f_{in} \cdot \sigma_{skew})^2 \quad (3.19)$$

where  $A$  is the amplitude of a sine input and the channel timing skew mismatches are Gaussian random variables with zero mean, and  $\sigma_{skew}$  is the standard deviation of timing skew. As a result, SNDR can be approximated as [35],

$$SNDR \cong 20 \cdot \log \left( \frac{1}{\sigma_{skew} 2\pi f_{in}} \right) - 10 \log \left( 1 - \frac{1}{M} \right) \quad (3.20)$$

For an 8 bit 1.5GS/s time-interleaved ADC with the Nyquist rate input frequency,  $\sigma_{skew}$  should be less than 1ps to fit in with the 8-bits requirement. Such a good timing matching is difficult to realize in modern CMOS process.

### 3.3 Proposed Low-Skew Demultiplexer Architecture

#### 3.3.1 Principle

There are some methods to solve the problem of timing skew mismatch without complicated timing skew calibration.

A global S/H and a source follower are used in [4] to solve the skew issue. The static power consumption of the source follower cannot be overlooked with its heavy-loading and high-linearity characteristics. Besides, in order to provide full-swing inputs for the sub-ADCs, it also needs another higher-than-nominal supply voltage, which worsens the FoM performance.

The channel-selection-embedded bootstrap circuit [5] is reported to replace the power-hungry source follower [4]. However, it takes different discharging paths for two bootstrap channels, which suppresses its low-skew feature. The stored sampled signal is also hard to pass another set of bootstrap switch without re-buffering.

The low-skew demultiplexer (De-MUX) is proposed to suppress the skew issue without the complicated timing skew calibration or the power-hungry source follower. The proposed low-skew De-MUX combines the global clock signal with the bootstrap circuit. Even though the clock signal of each channel is skewed, the actual sampling timing of each channel is aligned with global clock signal. Besides, the proposed low-skew De-MUX takes the common discharge path of each channel. It results in the

low-skew characteristic because the sampling timing is dependent on global clock signal. Besides, the common discharge path of each channel ensures the skew issue can be suppressed furthermore. Therefore, the timing skew of each channel will not cause the different sampling time shift of time-interleaved architecture.

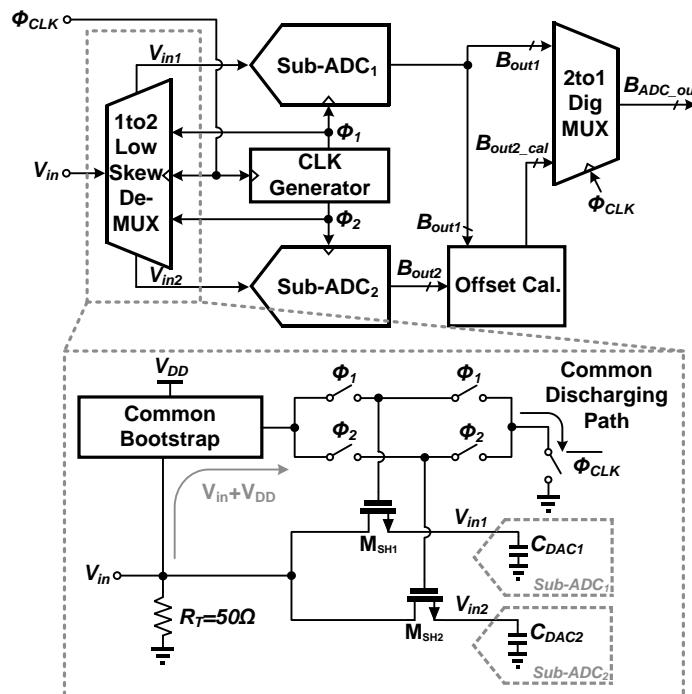

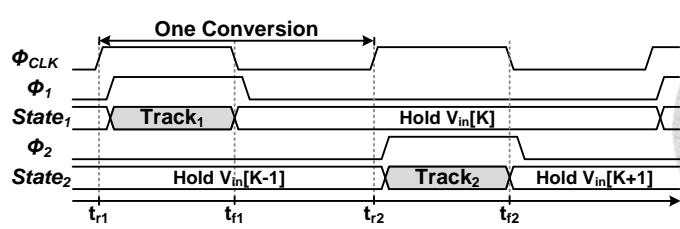

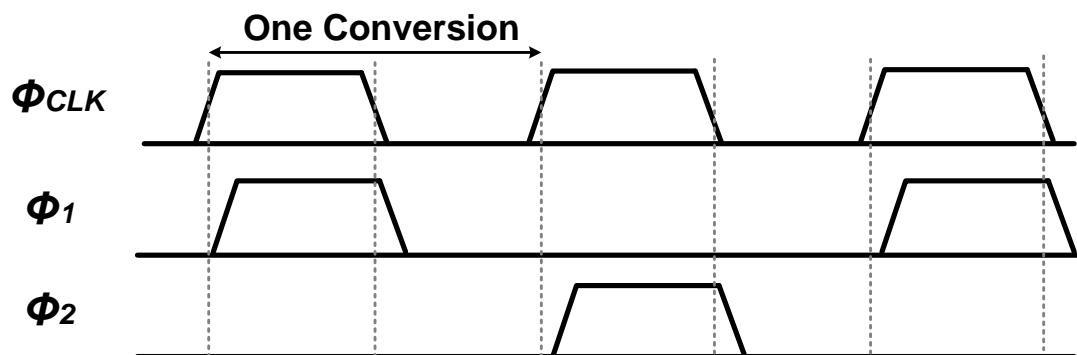

### 3.3.2 Low-Skew Demultiplexer

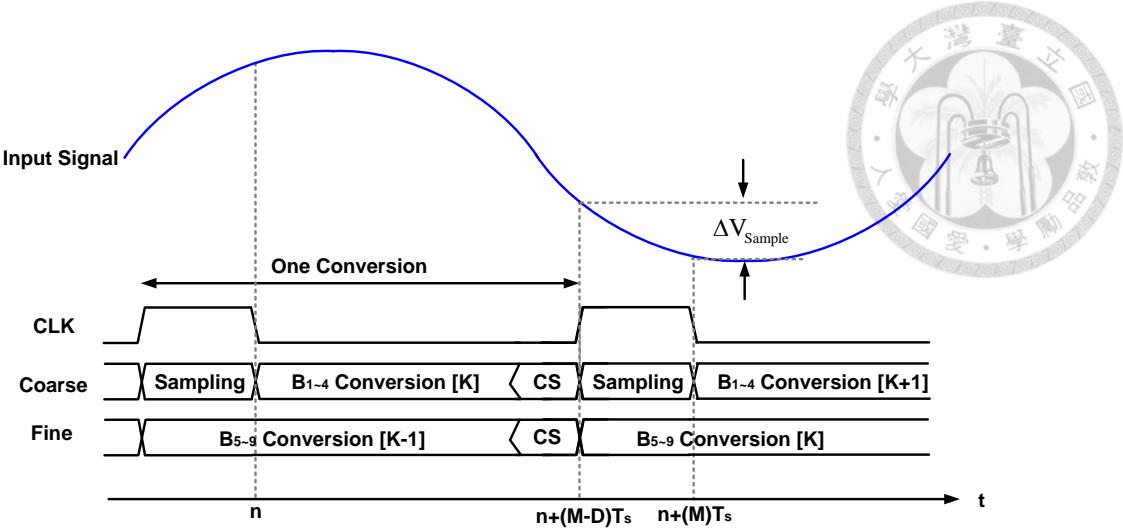

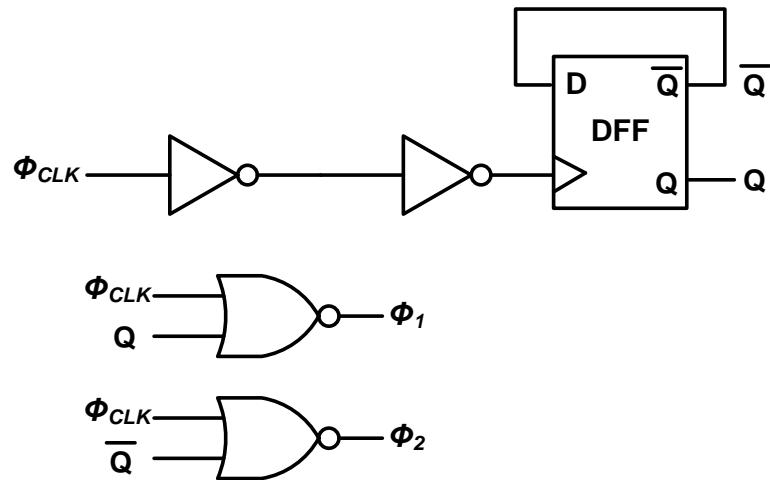

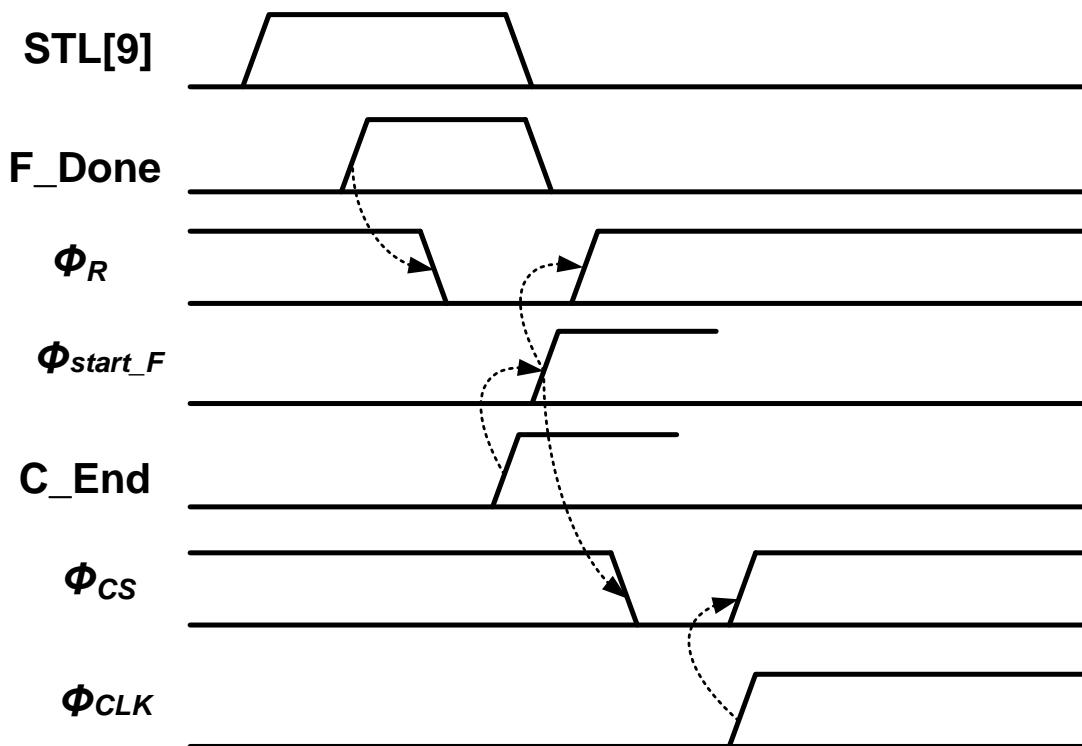

Fig. 3.7 illustrates the block diagram of the overall ADC. It consists of two sub-ADCs, a 1-to-2 low-skew De-MUX, a shared clock generator, an offset calibration circuit and a 2-to-1 digital output multiplexer. Fig. 3.8 illustrates its timing diagram and the states of the sub-ADCs. The global clock,  $\Phi_{CLK}$ , is divided by 2 to generate the control signals of sub-ADCs,  $\Phi_1$  and  $\Phi_2$ .

Fig. 3.7 Architecture of the proposed ADC with low-skew De-MUX

Fig. 3.8 Timing diagram of the proposed ADC

At the Track<sub>1</sub> phase, the gate of  $M_{SH1}$  is bootstrapped to  $V_{in} + V_{DD}$  to make the turn-on resistance of  $M_{SH1}$  a small constant value. It increases tracking linearity of the low-skew De-MUX. On the other hand, the sub-ADC<sub>2</sub> is resolving the previous sampled signal,  $V_{in}[K-1]$ , at the Hold<sub>2</sub> phase. By using the common discharging path, the low-skew De-MUX suppresses the skew mismatch between the two sub-ADCs. It ensures that  $C_{DAC1}$  of the sub-ADC<sub>1</sub> holds  $V_{in}[K]$ , which is aligned with the falling edge of the global clock,  $\Phi_{CLK}$ , at  $t_{f1}$ . Subsequently, the sub-ADC<sub>2</sub> tracks and holds the next input signal,  $V_{in}[K+1]$ , and so on. In contrast to  $\Phi_1$  and  $\Phi_2$ ,  $\Phi_{CLK}$  is directly from the clock buffers, so it also has low-noise characteristic. It improves the accuracy of low-skew De-MUX.

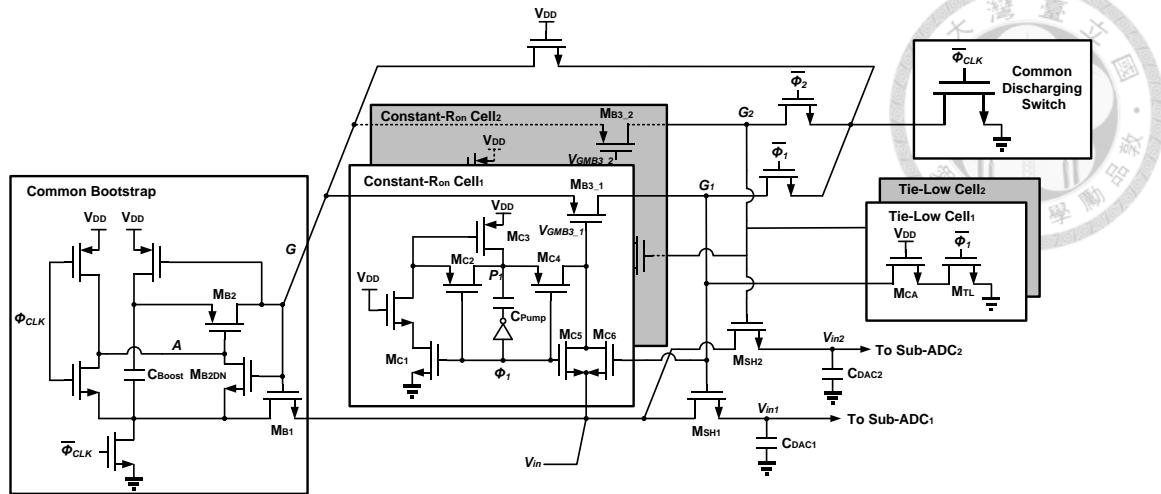

A single-end schematic of the proposed low-skew De-MUX is shown in Fig. 3.9. Four major parts with sub-ADC sampling switches,  $M_{SH1}$  and  $M_{SH2}$ , in this De-MUX includes a common bootstrap circuit, a common discharging switch, constant- $R_{on}$  cells and tie-low cells.

Fig. 3.9 Single-ended schematic of the proposed low-skew demultiplexer

The common bootstrap circuit uses  $C_{\text{Boost}}$  to boost node  $G$  to  $V_{in} + V_{DD}$  at the  $\text{Track}_i$  phases, which are depicted as the gray intervals in Fig. 3.8, where  $i$  either 1 or 2 for the  $i$ th channel.  $C_{\text{Boost}}$  resets its stored charge when  $\Phi_{\text{CLK}}$  is low. The bootstrapped voltage on the node  $G$  is transferred to nodes  $G_i$  and it keeps the turn-on resistance ( $R_{\text{on}}$ ) of  $M_{\text{SHi}}$  constant and independent of  $V_{in}$ . Since the two  $\text{Track}_i$  phases between the two sub-ADCs are not overlapped, the bootstrap circuit can be shared by both channels. Thus, it reduces the number of  $C_{\text{Boost}}$  by half. In this work, the capacitance value of  $C_{\text{Boost}}$  is about 500fF and it dominates the area of the bootstrap circuit.

$\Phi_1$  and  $\Phi_2$  are generated by a clock phase generator. It has large skew mismatch and bad noise performance. To suppress the skew sensitivity of  $\Phi_1$  and  $\Phi_2$ , the low-skew De-MUX lets the nodes  $G_1$  and  $G_2$  use the same discharging path at the falling edge of  $\Phi_{\text{CLK}}$ , which is  $t_{f1}$  and  $t_{f2}$  in Fig. 3.8, respectively. The sampled

instance of  $M_{SHi}$  is synchronized by the falling edge of  $\Phi_{CLK}$  at  $t_{f1}$  and  $t_{f2}$ . Thus, the sensitivity of skew mismatch between  $\Phi_1$  and  $\Phi_2$  can be reduced as long as the falling edge of  $\Phi_{CLK}$  is precise.

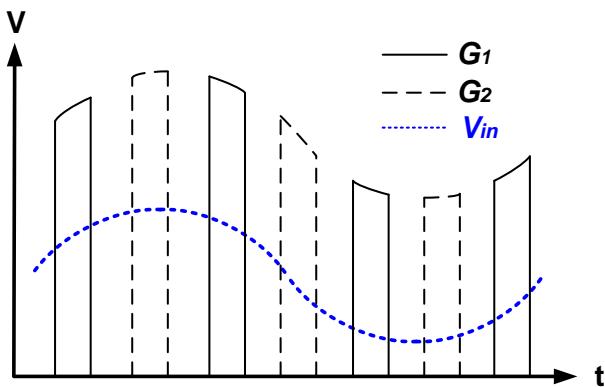

To enhance the linearity of  $M_{SHi}$ , it is necessary to sustain the nodes  $G$  and  $G_i$  higher than  $V_{in}$  by  $V_{DD}$  at the Track $i$  phase, as shown in Fig. 3.10.

The turn-on resistance of  $M_{SHi}$  can be derived as [24]

$$R_{on} = \frac{1}{\mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})} \quad (3.21)$$

Due to the common bootstrap and constant- $R_{on}$  cell,  $V_{GS}$  of  $M_{SHi}$  is constant and it results in the turn-on resistance of  $M_{SHi}$  is signal-independent. Besides,  $R_{on}$  of the path from  $V_{in}$  to nodes  $G$  and  $G_i$  also requires to be signal-independent. The common bootstrap uses  $M_{B2DN}$  to let nodes  $A$  and  $G$  equal to  $V_{in}$  and  $V_{in} + V_{DD}$ , respectively, so that  $R_{on}$  of  $M_{B2}/M_{B1}$  is kept constant.

Fig. 3.10 Waveform of  $G_1$ ,  $G_2$ , and  $V_{in}$  of low-skew De-MUX

The gate of  $M_{B3_i}$  cannot be connected to ground at the  $Track_i$  phase, because the  $V_{GS}$  of  $M_{B3_i}$  would become  $-(V_{in} + V_{DD})$ , which causes signal-dependent  $R_{on}$  of  $M_{B3_i}$ . The linearity of  $G_i$  is affected. Hence, the constant- $R_{on}$  cell<sub>i</sub> is used to keep  $R_{on}$  of  $M_{B3_i}$  constant. It uses  $M_{C5-6}$  to tie  $V_{GMB3_i}$  to  $V_{in}$  at the  $Track_i$  phase and keeps  $V_{GS}$  of  $M_{B3_i}$  at  $-V_{DD}$ . To avoid corrupting the sampled signal on  $C_{DACi}$ ,  $M_{B3_i}$  should block the bootstrapped voltage,  $V_{in} + V_{DD}$ , of the node  $G$  at the  $Hold_i$  phase, so the constant- $R_{on}$  cell<sub>i</sub> pumps  $V_{GSB3_i}$  to  $2V_{DD}$ , by using the  $M_{C1-4}$  and  $C_{Pump}$ . All devices in the constant- $R_{on}$  cells are allowed to use small sizes to save area and power, because it only needs to drive the parasitic capacitance of  $V_{GSB3_i}$ . In this work,  $C_{Pump}$  is designed to be 100fF. However, the  $V_{GS}$  or  $V_{DS}$  of  $M_{C2-6}$  and  $M_{B3_i}$  in the constant- $R_{on}$  cell are near  $2V_{DD}$  during the hold phase. If the proposed ADC is used in product, there is a reliability issue in the low-skew De-MUX.

The common discharging switch requires a set of small-sized switches, tie-low cell, which is used to avoid a floating node at the  $Hold_i$  phase. It would tie the node  $G_i$  to ground when common discharging switch is open. Because the tie-low cells are only used to define the floating nodes, the smallest channel width and length of  $M_{CA}$  and  $M_{TL}$  are selected in this work.

Two channels of sub-ADCs share the same clock phase generator [3] without any waste of power and area. It is well-known to accelerate the conversion rate in

high-speed single-channel SAR ADCs by prolonging the conversion phase up to 75% of the clock period. However, it requires twice the clock frequency to generate the quarter phase. It doubles the power consumption of the clock phase generator for only single-channel usage. Fortunately, it is advantageous to utilize this quarter clock generator, which can be shared to generate  $\Phi_1$  and  $\Phi_2$ , for the two-channel SAR ADC.

### **3.4 Proposed Two-Step SAR Sub-ADC Architecture**

#### **3.4.1 Charge sharing technique**

The choice of the sub-ADC is important for time-interleaved ADC. The small area and energy-efficient SAR ADC is one of the best choice used for interleaved sub-ADCs. There are various methods to expedite SAR ADCs, such as Multi-bit per cycle [5], [8] or multi-comparator [2], [10] technique which reduces digital loop time to enhance the speed of SAR ADCs. However, the offset mismatch of comparators needs foreground calibration and the kickback noise among comparators deteriorates its accuracy. The opamp-based Pipelined-SAR ADC [18]-[20] or pseudo differential source follower [21] was proposed to enhance the conversion rate of SAR ADC. But, the static current consumption degrades the FoM performance.

One of the two-step SAR architecture [1] was proposed to enhance the conversion rate of SAR ADC. It consists of a coarse stage and two fine stages. During

the sampling phase and the MSB conversion phase, the coarse stage and one of the fine stages are connected by the switches. After finishing the MSB conversion, the coarse stage and one of the fine stages are isolated by the switches between the coarse and fine stages. Then one of the fine stages starts to resolve the residue. Simultaneously, the coarse stage connected to the other fine stage for sampling next input signal. By utilizing this two-step architecture [1], it can enhance the conversion rate. But, the switch mismatch between the coarse stage and the two fine stages results in the serious bandwidth mismatch. During the sampling phase, the coarse and fine stages sample different input signal due to the different input bandwidth of sampling network, which also causes the terrible bandwidth mismatch.

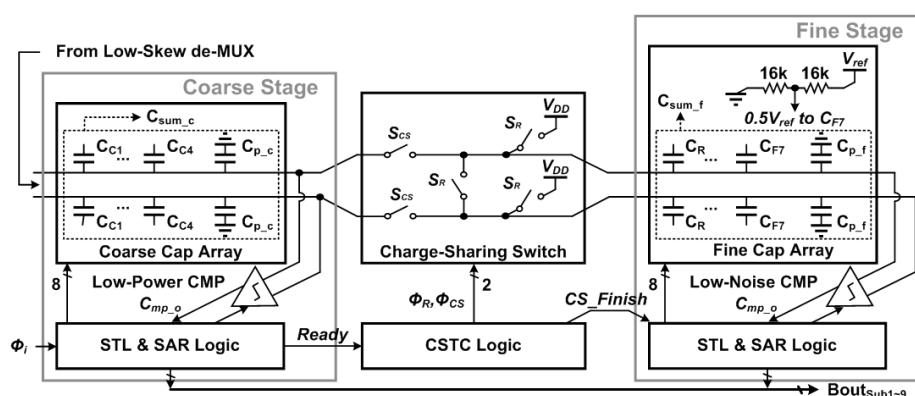

The proposed energy-efficient two-step SAR sub-ADC is shown in Fig. 3.11. Since its timing arrangement is similar to that of pipelined-SAR ADCs, it can achieve high conversion rate. Rather than using a power-hungry residue amplifier, the charge sharing technique is used to reduce the power consumption of analog-part circuitry.

Fig. 3.11 Block diagram of sub-ADC with STL technique

In order to transfer the residue from the coarse stage to the fine stage, the proposed charge sharing technique is used to transfer the residue passively. Besides, it is also immune from the output voltage headroom and linearity issues.

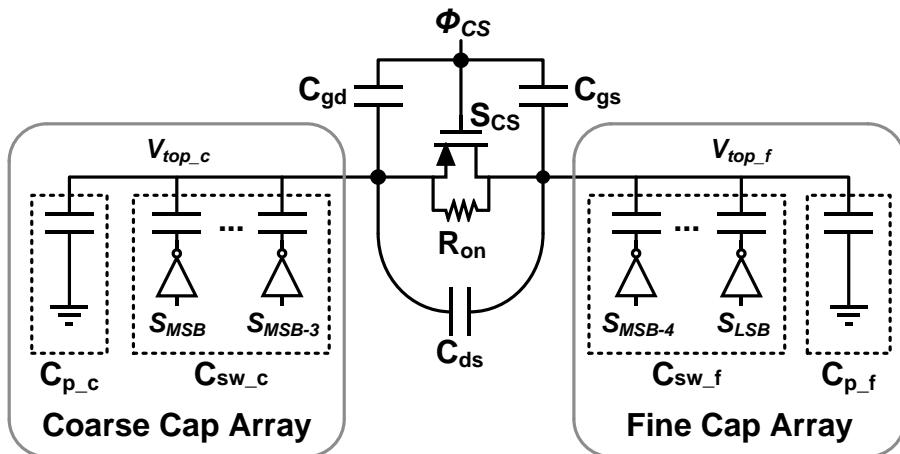

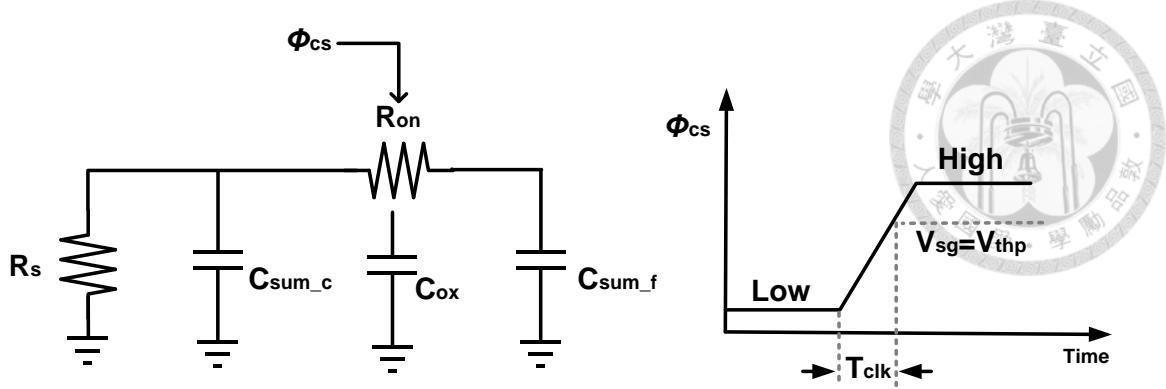

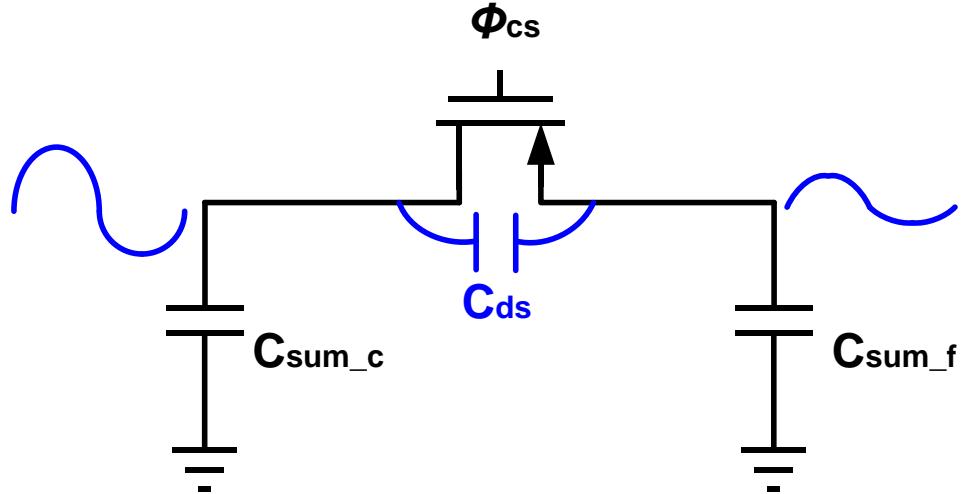

The proposed SAR sub-ADC comprises a coarse stage, a fine stage, a set of charge sharing switches and charge sharing timing control (CSTC) logic. The coarse and fine stages are connected by the charging sharing switches which include PMOS sharing switches  $S_{CS}$  and reset switches  $S_R$ . The set of charge sharing switches are controlled by the charge sharing timing control signals  $\Phi_{CS}$  and  $\Phi_R$  which are generated by the CSTC logic. Both the coarse and fine stages consist of the proposed STL SAR logic, a capacitor array, a dynamic comparator and loop delay logic.  $C_{p\_c}$  and  $C_{p\_f}$  are the whole parasitic capacitance at the top plates of coarse and fine capacitor arrays, respectively. The coarse capacitor array with capacitors  $[C_{C1} \ C_{C2} \ C_{C3} \ C_{C4}]$ , which equal to  $[64C \ 32C \ 16C \ 8C]$ , resolves the MSBs, where  $C$  is the unit capacitance. The fine capacitor array with capacitors  $[C_R \ C_{F5} \ C_{F6} \ C_{F7}]$ , which equal to  $[4C \ 2C \ C \ C]$ , provides the small voltage swing for the residue voltage to resolve the LSBs. The  $C_R$  in the fine capacitor array is used for one-bit redundancy [22].

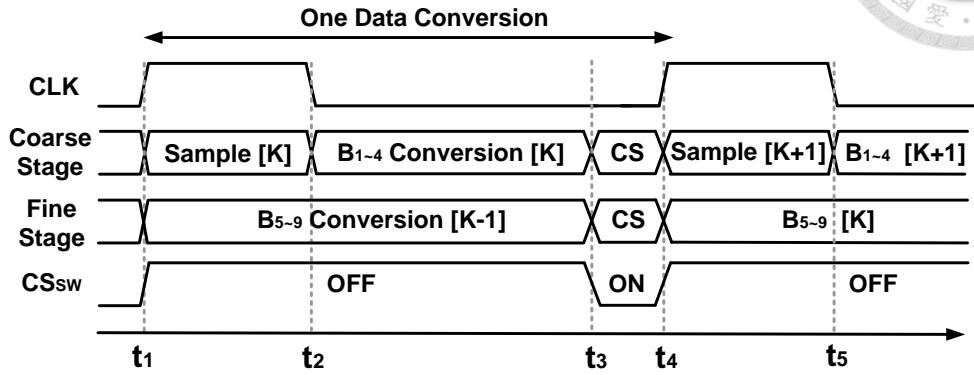

The timing diagram of the proposed sub-ADC is illustrated in Fig. 3.12. During the sampling phase from  $t_1$  to  $t_2$ , input signal  $V_{in}[K]$  is sampled on the coarse stage by the low-skew De-MUX, where the  $K$  represents the  $K$ th sampling. After

sampling the input signal, the low-skew De-MUX is turned off and the coarse stage starts to resolve first 4 MSB of  $V_{in}[K]$ .

Fig. 3.12 Timing diagram of sub-ADC

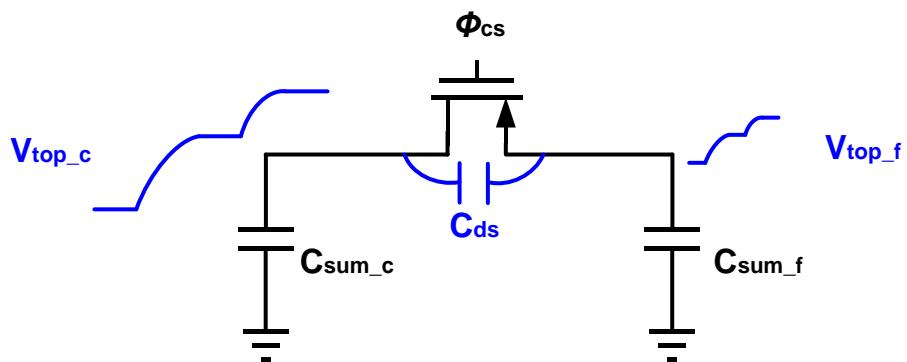

During the conversion phase from  $t_2$  to  $t_3$ , the coarse and fine stages utilize set-and-up switching method [23] to enhance the conversion rate. When both the coarse and fine stages finish their successive bit conversions, the residue is stored on the top plate of the two capacitor array. In order to prepare for the next charge sharing, the top plate of the fine stage capacitor array is reset to the power supply  $V_{DD}$  by  $S_R$ . Simultaneously, the bottom plate of the fine stage capacitor array is reset to the ground.

At  $t_3$ , the charge sharing timing control signals turn off the  $S_R$  and then turn on the  $S_{CS}$  to transfer the residue. As mentioned before, by utilizing the set-and-up switching method to a high level, the residue voltage on the coarse cap array is near to

$V_{DD}$ . Consequently, the charge sharing switches  $S_{CS}$  can be only PMOS instead of a transmission gate switch. It not only simplifies the switch design but also increases the conversion rate of the coarse and fine stages. Besides, the charge sharing technique can transfer the residue fast and be low power.

Next, when the CLK is high, charge sharing switches are turned off and the coarse stage starts to sample the next input signal  $V_{in}[K+1]$ . At the same time, the fine stage starts to resolve the rest of LSB of  $V_{in}[K]$ . Therefore, the two-step SAR ADC with charge sharing technique can achieve high conversion rate and low power dissipation. Unlike [1], the fine stage only samples the DC residue voltage from the coarse stage, the bandwidth mismatch of the  $S_{CS}$  will not cause the bandwidth mismatch tone.

The one-bit redundancy provides  $\pm 16$ LSB tolerance, which corrects errors including the offset mismatch between the coarse and fine stages, the large noise of the coarse comparator, the settling error of the coarse capacitor array. Therefore, this redundancy range makes the coarse stage faster and more energy-efficient. The coarse and fine stage could have different design for the speed and power optimization. The coarse stage uses a low-power comparator to resolve the first four MSBs. The one-bit redundancy relieves DAC settling requirement, so the loop delay time of the coarse stage is shorter than that of the conventional architecture. By utilizing the two-step

architecture, the fine stage has sufficient time to resolve the rest of LSBs with a low-noise comparator. As a result of small voltage swing of the rest of conversion, the loop delay time of the fine stage can much shorter than that of the conventional architecture. It not only saves the power consumption but also increases the conversion rate of the ADC.

Based on the simulation results, the power of the coarse low-power comparator is more energy-efficient than that of the fine low-noise comparator by around 2.7 times in this work. The fine comparator only needs to resolves the rest of 5 comparisons, instead of the conventional 8 comparisons in a complete conversion. The analog power of ADC is saved by about 15% comparing with that of the conventional architecture [23].

Although the multiple reference architecture [1] could reduce the total size of the capacitor arrays and tune the switched voltage headroom of the fine stage, it requires multiple reference voltage generators (RVGs). The reference voltage is one of the most sensitive voltages in the ADC because any noise on the reference voltage would affect its resolution directly. The multiple reference architecture needs an extra strong but power-hungry RVG to suppress the noise on the reference voltage.

The resistor ladder technique [2] can use only one reference voltage to generate another reference voltage. A  $32k\Omega$  resistor ladder is used to generate  $0.5V_{ref}$  for  $C_{F7}$

---

so that  $C_{sum\_c}$  and  $C_{sum\_f}$  are smaller than those of [3] by 2 times. Despite the fact that the  $0.5V_{ref}$  increases the turn-on resistance of the bottom-plate switches, the  $0.5V_{ref}$  generated by the resistor ladder is used for LSB in the fine stage.

Thanks to the resistor ladder, the ADC can use only one reference voltage. It can not only reduce the total capacitance of the coarse and fine stage, but also make the charge sharing technique faster. The speed consideration will be discussed in Sec. 3.5.5.

It is a remarkable fact that the total capacitance size of the coarse stage is designed to be equal to that of the fine stage to use only one reference voltage and to ensure proper switched voltage headroom of the fine capacitor array. The details will be explained in Sec. 3.5.4.1.

### 3.4.2 Self-Triggered Latch technique

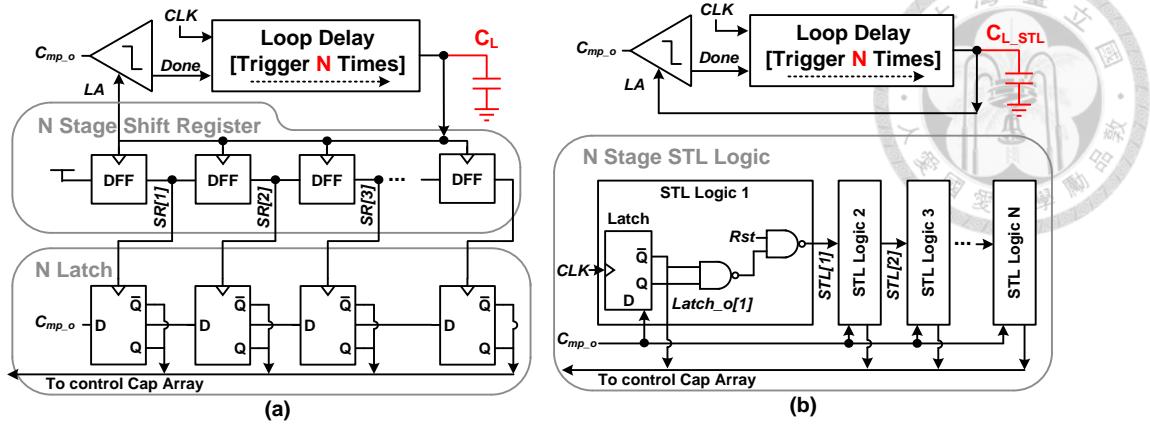

Fig. 3.13(a) shows the loop control block diagram of the conventional asynchronous SAR ADC. It consists of loop delay cells, shift registers and latches [17]. The operation process is that the loop delay cells trigger the shift register to generate latch control signals, SRs. Then, SRs set the latches to store all the results of the comparator output  $C_{mp\_o}$  [23]. N-bit asynchronous SAR ADC needs N stage shift

registers and  $N$  latches. As a result, the capacitor loading of the comparator control signal LA is derived as

$$C_L = C_{p\_loop} + N \times C_{DFF} \quad (3.22)$$

where  $C_{p\_loop}$  is the parasitic capacitance on LA and  $C_{DFF}$  is the input capacitance of the shift register clock port. To regenerate  $N$  times, the loop would trigger the comparator  $N$  times. The dynamic power consumption of the loop delay cells is calculated as

$$PD_{CONV} = N \times C_L \times V_{DD}^2 \times f \quad (3.23)$$

where  $V_{DD}$  is the digital power supply voltage and  $f$  is the conversion frequency of the ADC.  $C_L$  is usually large. It increases the dynamic power dissipation and slows down the speed of the loop. The self-triggered latch (STL) technique is proposed as shown in Fig. 3.13(b). By removing the conventional shift-registers, this technique let the latch stage be self-triggered by the previous stage. The CLK signal triggers the loop delay cells and the first stage of STL. The first stage of STL starts to latch the comparator results  $C_{mp\_o}$ . When the first latch stage is regenerative, it would trigger the next latch stage and so on. The loading capacitor  $C_{L\_STL}$  on LA in the proposed technique is equal to  $C_{p\_loop}$ , which is smaller than that of the conventional method. Although this technique adds two NAND gates per stage, their power dissipation is

still smaller than one D-flip-flop. The dynamic power dissipation of the STL technique is calculated as

$$PD_{STL} = N \times C_{p\_Loop} \times V_{DD}^2 \times f \quad (3.24)$$

Based on the post-layout simulation results, the STL technique saves 20% digital power and 50% digital area. It makes the ADC faster and more energy-efficient. Fig. 3.14 shows the timing diagram of the STL technique.

When LA rises at  $t_A$ , the comparator starts to regenerate the input signal. The comparison is finished and Done rises at  $t_B$ . The time from  $t_A$  to  $t_B$  is defined to be  $T_{CMP}$ . Done takes the duration of  $T_{Loop}$  to go through the loop delay cells and then pulls LA to a low level from  $t_B$  to  $t_C$ . At the same time, the latch starts to latch the comparator results  $C_{mp\_o}$  and uses  $T_{Latch}$  from  $t_B$  to  $t_D$ . When the latch is finished at  $t_D$ , it uses  $T_{STL}$  which is two NAND gate delay to pull up STL and opens the next latch. The comparator reset time takes the duration of  $T_{Rst}$  from  $t_C$  to  $t_E$ . To make the STL technique operate normally, the following criterion should be held.

$$T_{Loop} + T_{Rst} < T_{Latch} + T_{STL} \quad (3.25)$$

where  $T_{Loop}$  is the delay of one high-speed NAND gate and one inverter.  $T_{STL}$  is the delay of two small-sized NAND gates.  $T_{Rst}$  is also shorter than  $T_{Latch}$ , because  $T_{Rst}$  does not require regenerative operation. Accordingly, they can be designed to guarantee no timing issue in the STL technique.

Fig. 3.13 (a) The conventional method (b) the proposed STL technique

Fig. 3.14 Timing diagram for STL technique

## 3.5 Design Consideration

### 3.5.1 Offset Mismatch Error

The offset mismatch error of the proposed time-interleaved two-step SAR ADC includes the offset mismatch between the sub-ADCs and the offset mismatch error between the coarse and fine stages. The offset mismatch between the sub-ADCs can be calibrated in digital domain. Assuming that the offset voltage of the sub-ADC is

zero and the input signal is periodical, the averaged digital output is equal to its mid value. The same rule applies to other sub-ADCs suffered from the offset mismatch, and the corresponding averaged digital output is not equal to its mid value. The offset voltage of each channel can be derived by collecting the averaged digital output of each channel and subtracting the mid value. Then the residues can be compensated to the digital output of the corresponding channels.

However, the offset mismatch between the coarse and fine stages cannot be calibrated in digital domain, which results in the serious distortion. The comparator offset between the coarse and fine stages is the main factor. As mentioned in Section 3.4, the one-bit redundancy provides +/- 16LSB tolerance. It provides the code overlapping between the coarse and fine stages, which correct the offset mismatch between the coarse and fine stages. As long as the offset mismatch between the coarse and fine stages is smaller than the redundancy cover range, it will not degrade the linearity of sub-ADCs.

### 3.5.2 Gain Mismatch Error

The gain mismatch error of the proposed time-interleaved two-step SAR ADC includes the gain mismatch error between the sub-ADCs and the gain mismatch error between the coarse and fine stages. The gain mismatch error between the sub-ADCs

---

can be calibrated background in digital domain [8][11]. However, the gain mismatch error between the coarse and fine stages cannot be calibrated in the digital domain, which will cause the serious distortion.

The capacitor mismatch between  $C_{sum\_c}$  and  $C_{sum\_f}$  is the main factor. In this work, the mismatch sigma  $\sigma$  of unit switched capacitor is around 1% with a unit capacitance of 1fF. It is an extrapolated result of the fabrication process datasheet. To equalize the gain of the coarse and fine stages, most of  $C_{p\_c}$  and  $C_{p\_f}$  are made up of the same architecture with unit capacitance. The other parasitic capacitance of routing metal is relatively smaller so that it can be neglected in this work. Thus, the unit capacitor mismatch of  $C_{p\_c}$  and  $C_{p\_f}$  is also assumed to be 1%. Based on the result of 10,000 Monte Carlo simulations, ENOB can reach around 7.9 bits for  $3\sigma$  variation in this time-interleaved ADC. It indicates that the gain mismatch error caused by the parasitic capacitance mismatch is negligible in this work. Similar to [27]-[29], it also claims that the gain mismatch error can be neglected for medium resolution ADC.

### 3.5.3 Switching Method

The switching method of ADC is related to the conversion speed, comparator noise, and the switch type of the charge sharing technique. The variation of input common-mode voltage during the conversion is related to the switching method. The  $V_{CM}$ -based switching method [30] or the split-and-monotonic switching method [22]

can keep the input common-mode voltage constant. However, the conversion speed during the LSB conversion becomes slower because the difference of input signal is shrunk gradually by SAR algorithm.

The monotonic switching method [23] is used to enhance the conversion speed. Based on [31], assuming that the comparator with N-type input pair is select, the higher input common-mode voltage makes the comparator delay time shorter. It is useful for high-speed application because the longest delay time of the comparator occurs during the LSB conversion.

Although the delay time of the comparator can be improved by the monotonic switching method, the higher comparator noise and the dynamic offset caused by the variation of input common-mode voltage degrade the performance of ADC. Fortunately, the comparator noise is relatively small in this work, and the dynamic offset can be tolerated by the one-bit redundancy.

Consequently, the N-type comparator and set-and-up switching method are selected for coarse and fine stages in this work. By utilizing the set-and-up switching method to a high level, the residue voltage stored on the top plate of the coarse capacitor array is near to  $V_{DD}$ . The charge sharing switch  $S_{CS}$  can be implemented with only a PMOS switch instead of a transmission-gate switch. It not only simplifies the switch design but also increases the speed of the coarse and fine stages.

### 3.5.4 Accuracy Consideration

#### 3.5.4.1 Proper Switching Voltage

Fig. 3.15 illustrates the single-ended equivalent models of the charge sharing switch  $S_{CS}$ , and the coarse and fine capacitor arrays to implement the proposed charge sharing technique.  $C_{sw\_c}$  and  $C_{sw\_f}$  are the total switched capacitors of the coarse and fine capacitor arrays, respectively.  $C_{p\_c}$  and  $C_{p\_f}$  are the sums of dummy capacitors, and all parasitic capacitance at the top plates of the coarse and fine capacitor arrays, respectively.  $C_{gs}$ ,  $C_{gd}$  and  $C_{ds}$  are the parasitic capacitance of the charge sharing switch, and  $R_{on}$  is the turn-on resistance of the charge sharing switch.

Fig. 3.15 Equivalent model of the proposed charge sharing technique

At the beginning of the CS phase,  $S_{CS}$  is turned off. Since the coarse stage has already resolved the first 4 bits, the residue voltage of the input signal  $V_{Res}[K]$  is remained on the top plate voltage of the coarse capacitor array, where  $K$  denotes the  $K$ th sampling. The top plate of the fine capacitor array is reset to  $v_{dd}$  in the

meanwhile. When  $S_{CS}$  is turned on during the CS phase, the top plate voltage of the fine stage  $V_{top\_f}[K]$  can be calculated as

$$V_{top\_f}[K] = \alpha \times V_{Res}[K] + \beta \times V_{DD} \quad (3.26)$$

where  $\alpha$  and  $\beta$  are the charge sharing coefficients of the residue voltage and the reference voltage, respectively. In this work,  $V_{DD}$  is used as the reference voltage.

$$\alpha = \frac{C_{Sum\_c}}{C_{Sum\_f} + C_{Sum\_c}} \quad (3.27)$$

$$\beta = \frac{C_{Sum\_f}}{C_{Sum\_f} + C_{Sum\_c}} \quad (3.28)$$

where  $C_{Sum\_c}$  and  $C_{Sum\_f}$  are equal to  $C_{p\_c} + C_{tot\_c}$ , and  $C_{p\_f} + C_{tot\_f}$ , respectively.

Because the second term of (3.26) is independent of  $K$ , i.e., signal-independent, it can be canceled in a differential configuration. The value of  $\alpha$  is critical to the gain mismatch between the coarse and fine stages, which affects the resolution considerably.

In order to prove that the multiple reference voltage is necessary without the additional dummy capacitor or different size of unit capacitance, we take an  $N$ -bit conventional two-step SAR ADC for example: the coarse stage resolves the first  $M$ -bit of input signal, and the residue is transferred to the fine stage for the  $(N-M)$ -bit conversion. Assuming that

$$C_{Sum\_c} = k \times C_{Sum\_f} \quad (3.29)$$

where  $k$  is the capacitor coefficient ratio of the coarse and fine stages and there is no extra parasitic capacitance in the  $C_{\text{Sum\_c}}$  and  $C_{\text{Sum\_f}}$ . That is, the charge sharing coefficient  $\alpha$  is equal to  $\frac{k}{k+1}$ , and

$$C_{\text{Sum\_c}} = k \cdot 2^{N-2M-1} \cdot [2^{M-1}, 2^{M-2}, \dots, 2^1, 2^0, 2^0] \quad (3.30)$$

$$C_{\text{Sum\_f}} = [2^{N-M-2}, 2^{N-M-3}, \dots, 2^1, 2^0, 2^0] \quad (3.31)$$

In order to performing the binary search of the SAR algorithm, the switching voltage of the first  $M$ -bit is equal to

$$\left[ \frac{1}{2^1}, \frac{1}{2^2}, \dots, \frac{1}{2^M} \right] \times V_{\text{ref\_c}} \quad (3.32)$$

where  $V_{\text{ref\_c}}$  is the reference voltage of the coarse stage.

Besides, the switching voltage of the rest of  $(N-M)$ -bit is equal to

$$\left[ \frac{1}{2^1}, \frac{1}{2^2}, \dots, \frac{1}{2^{N-M+1}} \right] \times V_{\text{ref\_f}} \quad (3.33)$$

where  $V_{\text{ref\_f}}$  is the reference voltage of the fine stage. According to the binary search and the charge sharing technique, the first term of switching voltage of the fine stage

$\frac{1}{2^1} V_{\text{ref\_f}}$  is equal to the last term of switching voltage of the coarse stage  $\frac{1}{2^M} V_{\text{ref\_c}}$  multiply by  $\frac{\alpha}{2}$ .

Thus,

$$\frac{1}{2} \times V_{\text{ref\_f}} = \frac{1}{2^M} \times \frac{\alpha}{2} \times V_{\text{ref\_c}} \quad (3.34)$$

$$V_{\text{ref\_f}} = \frac{1}{2^M} \times \frac{k}{k+1} \times V_{\text{ref\_c}} \quad (3.35)$$

(3.35) proves that it is impossible to use only one reference without adding the additional dummy capacitor or selecting the different size unit capacitance in the coarse and fine stages.

Because the different size unit capacitance suffers from the serious capacitor mismatch issue, it is an unavailable method in this work. Accordingly, adding the additional dummy capacitor is the only one solution for only one reference voltage. The following equation shows that by adding the additional dummy capacitor is valid for only one reference voltage.

If the dummy capacitor  $C_{p\_f}$  is added to the fine capacitor array, the corresponding switching voltage of the rest of (N-M)-bit is equal to

$$\left[ \frac{2^{N-M-2}}{2^{N-M-1} + C_{p\_f}}, \frac{2^{N-M-3}}{2^{N-M-1} + C_{p\_f}}, \dots, \frac{1}{2^{N-M-1} + C_{p\_f}} \right] \times V_{ref\_f} \quad (3.36)$$

Similarly, based on the binary search and the charge sharing technique, the first term of switching voltage of the fine stage  $\frac{2^{N-M}}{2^{N-M+1} + C_{p\_f}} V_{ref\_f}$  is equal to the last term of switching voltage of the coarse stage  $\frac{1}{2^M} V_{ref\_c}$  multiply by  $\frac{\alpha}{2}$ .

That is,

$$\frac{2^{N-M-2}}{2^{N-M-1} + C_{p\_f}} V_{ref\_f} = \frac{1}{2^M} \times \frac{\alpha}{2} \times V_{ref\_c} \quad (3.37)$$

$$\frac{2^{N-1}}{\alpha} \times \frac{V_{ref\_f}}{V_{ref\_c}} = 2^{N-M-1} + C_{p\_f} \quad (3.38)$$

$$C_{p\_f} = 2^{N-1} \times \frac{k+1}{k} \times \frac{V_{ref\_f}}{V_{ref\_c}} - 2^{N-M-1}$$

If we make  $V_{ref\_c}$  equals to  $V_{ref\_f}$ , then

$$C_{p\_f} = 2^{N-1} \times \frac{k+1}{k} - 2^{N-M-1} \quad (3.40)$$

In terms of the consideration of SNR, the capacitor coefficient ratio of the coarse and fine stages  $k$  should greater or equal to one to make the fine stage get more residues from the coarse stage.

Thus,  $k$  is selected for one to compensate the least comparator in the fine stage and  $C_{p\_f}$  is added to the fine capacitor array which equals to

$$C_{p\_f} = 2^N - 2^{N-M-1} \quad (3.41)$$

Consequently, by adding some capacitor in the fine capacitor array can maintain proper switching for the SAR algorithm and, as mentioned in Sec. 3.4, only one reference voltage is utilized in this work.

Although by selecting the different size unit capacitance in the coarse and fine stages may reduce the total capacitance of the two stages, the different size unit capacitance suffers from the serious capacitance mismatch. It will cause the serious gain mismatch error between the coarse and fine stages which degrade the linearity of ADC.

Based on the aforementioned reason,  $k$  is designed to be 1 and  $\alpha$  is equal to be 0.5. That is,  $C_{\text{Sum\_c}}$  equals to  $C_{\text{Sum\_f}}$ , and the gain of the coarse stage is the same as that of the fine stage. The switched voltage headroom of the fine capacitor array is 0.5 time of that of the coarse capacitor array. As mentioned before, to avoid using another reference voltage, the equivalent reference voltage,  $0.5V_{\text{DD}}$ , is designed by accurately controlling the ratio between  $C_{p\_f}$  and  $C_{\text{tot\_f}}$ . Thus, the fine stage can resolve the shared signal,  $0.5V_{\text{res}}[K]$ , subsequently.

Besides, as mentioned in Sec. 3.4, a  $32k\Omega$  resistor ladder is used for the LSB switching in the fine state, which can not only reduce the total capacitance of the coarse and fine stages, but also expedite the speed of the charge sharing.

Because there is no extra redundancy for the LSB decisions in the fine stage, the settling error of the fine stage should be smaller than 0.5 LSB. Although the proposed charge sharing technique results in  $\alpha$  times reduction of the residue voltage, which indicates that the  $V_{\text{LSB}}$  is attenuated by  $\alpha$ , the switching voltage for the fine stage is reduced by the same factor. The time  $t$  needed for the switching follows [2]

$$\Delta V \cdot e^{\frac{-t}{\tau}} < 0.5 \cdot V_{\text{LSB}} \quad (3.42)$$

where  $\Delta V$  represents the switching voltage,  $\tau$  represent the RC time constant and  $t$  represents the settling time.

Based on (3.42), despite the attenuation of  $V_{LSB}$ , the time needed for settling in the fine stage is the same as the conventional architecture. However, thanks to the two-step architecture and the small voltage swing in the fine stage, the loop delay time of the fine stage can be much shorter than that of the conventional architecture. Values are given in multiples of time constants  $\tau$  for a settling error 0.5 LSB in the fine stage, as shown in Fig. 3.16. It also indicates that the time needed for LSB switching is relaxed, and the least time for settling within 0.5  $V_{LSB}$  is the LSB switching of the fine stage. The increment of the turn-on resistance caused by the 0.5  $V_{ref}$  from the resistor ladder can be tolerated. Thus, the 0.5Vref from the resistor ladder is used only for LSB in the fine stage.

Besides, the gain mismatch error between the coarse and fine stages can be tolerated in this work, as mentioned in Sec. 3.5.2.

Fig. 3.16 Detail of the switching scheme and the time needed for settling is given in multiples of time constant for a settling error  $< 0.5 V_{LSB}$  in the fine stage

### 3.5.4.2 Nonlinearity of Charge Sharing Switch

Although the proposed charge sharing technique has a lot of advantages, there are some nonlinearity in the charge sharing switches  $S_{CS}$ , which includes clock feedthrough, charge injection, signal feedthrough and switching voltage feedthrough. By utilizing the proposed charge sharing technique, the residue transferred to the fine stage is used for the LSB conversion and its accuracy is important. Besides, after finishing the charge sharing, the coarse stage is used to sample next input signal. The

nonlinearity of the coarse stage which results from charge sharing switch can be ignored. Consequently, the nonlinearity analysis is only for the fine stage.

The first nonlinearity is clock feedthrough, which can be modelled as shown in Fig. 3.17. In the beginning of the charge sharing,  $\Phi_{CS}$  is from  $V_{DD}$  to ground to turn on the charge sharing switch, and the voltage variation of  $\Phi_{CS}$  results in the voltage variation by  $C_{gs}$  and  $C_{gd}$ .

Fig. 3.17 Clock feedthrough model of the charge sharing switch

When  $\Phi_{CS}$  is from  $V_{DD}$  to ground, the voltage variation of the clock feedthrough is equal to [24]

$$\frac{C_{gs,1}}{C_{gs,1} + C_{sum\_f}} V_{DD} \quad (3.43)$$

where  $C_{gs,1}$  is the parasitic capacitance between gate and source at the beginning of the charge sharing. At the end of the charge sharing,  $\Phi_{CS}$  is from ground to  $V_{DD}$  to

turn off the charge sharing switch, and the voltage variation of  $\Phi_{CS}$  results in the voltage variation by  $C_{gs}$  and  $C_{gd}$ .