國立臺灣大學電機資訊學院電信工程學研究所

# 碩士論文

Graduate Institute of Communication Engineering College of Electrical Engineering & Computer Science National Taiwan University Master Thesis

互補式金氧半導體功率放大器之線性化技術研究

Research on Linearization Technique for CMOS Power Amplifier

Yu-Chung Hsu

指導教授:林坤佑 博士

Advisor: Kun-You Lin, Ph.D.

中華民國 99 年 7 月

July, 2010

### 誌謝

能完成這篇論文,要先感謝所有的口試委員,你們寶貴的意見讓論文更加的 完整。我要特別感謝我的指導教授林坤佑老師,在當初沒有找教授的情況下,老 師收留了我,並且在我研究的路上,變成了亦師亦友的人。跟老師的討論往往十 分愉快。而且,要是沒有老師協助修改論文,那這一篇論文應該會一直處於一種 混沌的狀態,也是因為老師對於論文品質的要求,我才會盡全力構思論文,進而 真的想出了一點東西。最重要的是,老師嚴謹的風範和開明的個性,讓我學會腳 踏實地的做研究,接下來的日子裡繼續一起早起打羽球吧。

另外,我要感謝實驗室的每一位成員。無論是在我要爆炸的時候的緊急援助, 還是我後來沒有參加 meeting 的事情上,對我給予最大的支持與鼓勵。真的十分謝 謝大家!印象最深刻的是我後來都很機車的在要交什麼文件之前,直接殺去實驗 室找例如謝家瑜說:「乀,測試報告寄一份給我」或者「乀,論文初稿寄一份給我」 之類的,雖然她後來去發哥工作了還不肯請客,而且還害我請乾杯這麼大一攤, 而且平常吃飯還很不合群(狂婊XD),我還是很感謝他;或者還會找張益誌要bypass 的 gds 和 EM 檔,順便連 RF-pad 的也來一下,然後順便玩一下他的肚子(?)之 類的;亦或是占用吳仁鉅空曠的位置,他要用的時候還硬是不離開,然後手機裡 明明記的是彭朋瑞的電話,結果名字一直是吳仁鉅之類的;或者黃冠傑明明就幫 我認養了一隻貓,結果他要回高雄的時候寄養我還擺臭臉,而且還有一件給他的 貓的 NIKE 外套還放在我這邊,後來他都只能托他的學姐幫忙養之類的。

SOSO 學長在量測上面幫了我很大的忙,無論是怎樣不合理的量測時間,SOSO 總是會非常有義氣的配合我。在無塵室的量測過程中,也是很細心的指導我各種 需要注意的事項還有要量測的參數。然後因為我一時興起答應他要寫個十行,搞 得我現在想不到要怎麼寫下去。如果寫說他會幫我下完針以後他就會說阿我上去 抽個煙等一下再回來,或者會說我去旁邊上個逼你把一些數據抄一抄......的子虛 烏有的罪名似乎也是很不夠意思吧......的話是也還好啦。其實真的很感謝他很用 心的幫我,比如說量 power 的時候,我們居然發瘋的連 cable 什麼的都一個一個 Pin 給他打上去,最後連轉接頭都量了,我絕對不會承認後來我其實有點懶得把這些 因素都考慮進去,不過 SOSO 這麼用心,而且還跟我一個人念數據一個人打數據, 真是超感人的都受不了了。最重要的是,可以在無塵室亂唱一堆老歌很有趣。

我還要感謝敏哥,剛進實驗室的時候他細心的教導和系統性的設計方法,讓 我在之後的晶片設計上能夠以有效率的方式完成。敏哥熱愛研究的心,一直是我 的榜樣,是我的目標。最對不起的人是郭京霖學長,在 MTK 計劃的進行中我造成 了他很多的麻煩,很多對於 PA 的基礎知識也是跟學長學的。師叔高瑞智在我需要 幫助的時候總是會挺身而出,無論是工作站或者照晶片或者量測等千奇百怪的問 題總是有求必應,向你尋求幫助的時候總是很安心,連在打羽球的時候和吃21 世 紀的時候和喝啤酒的時候,都是最重要的班底。我很感謝宗錞,雖然你是我的學 弟,但是你鍥而不捨的研究精神是我作不到的,我也很享受跟你討論的時刻。後 來因為私人因素很多東西都要你罩我,真的是十分的對不起也十分的感激。我很 高興也很慚愧可以當你的學長。蔡兆璿也在 0.18 μm 要下線時幫了我很多忙,因為 有你的幫忙,我才能在最後一刻把東西生出來,希望你能在研究上能夠有所突破, 更加細心,風光的順利畢業。

另外我想感謝我家的三隻貓,雖然都很笨而且有時候很麻煩,但是在照顧你 們的過程中,我開始學會更有耐心,生活中也比較不無聊。還要感謝我親愛的女 朋友,常常要從新竹來台北真的是辛苦你了,沒有你的陪伴我人生中會少了許多 色彩。每一次跟你相處的過程都是我最珍惜的回憶。

最後,我要感謝我的家人,雖然我很少回高雄又喜歡把自己弄得很忙沒有時間,但是我真的很愛你們,你們是我最後的支柱。僅把這篇獻給我父親,因為有 你打下的基礎,我才有機會寫出這篇誌謝文。我很希望可以以現在的年紀和體會 跟你聊天,跟你談論事情。

ii

## 中文摘要

這篇論文將提出一個可以使用在毫米波頻段的改良式線性器,具有改善互補 式金氧半導體功率放大器的功能。在此之前所提出的線性器是使用在 40 GHz,並 使用了砷化鎵高電子移動率電晶體製程,展現了良好的特性。然而,同樣的架構 卻難以在 60 GHz 頻段有效的移植到互補式金氧半導體製程。因此,我們探討了現 性器的詳細運作情形,並提出以相位延遲線來改善普通線性器的改進。另外,我 們提出了一個偏壓優化的方法,可以保證針對特定功率放大器可以找到最適合的 線性器大小及其控制偏壓。

我們使用 90 奈米 LP 互補式金氧半導體來製作一個在 60 GHz 的功率放大器, 並且完全的以提升 1 dB 衰減點為目標,來做出優化。量測的結果,功率放大器在 增益 1 dB 衰減點呈現了高達 14%的功率附加效率。並且,其還具有 15 dB 的小訊 號增益、13.7 dBm 的增益 1 dB 衰減輸出功率以及 15.4 dBm 的飽和輸出功率。這 是我們所知,在所有發表過的電路中,使用互補式金氧半導體製程在增益 1 dB 衰 減點有最高功率附加效率的 60 GHz 功率放大器。

關鍵字:功率放大器、60 GHz、高功率附加效率、線性器、V 頻段、前置性衰減、 線性化技術

TON

# ABSTRACT

In this dissertation, a modified cold-FET pre-distortion linearizer is proposed to improve the linearity of the millimeter-wave CMOS power amplifiers. The previous reported cold-FET linearizer as applied to a 40 GHz power amplifier with a low-loss built-in linearizer in GaAs HEMT technology [6]. However, the effect of the linearizer is not good enough when we try to transplant the technique to 60 GHz using CMOS technology. Therefore, we investigate the operation detail of the linearizer and propose a modified linearizer by adding a delay line. Besides, a bias optimization method that can effectively guarantee the linearity of specific cascode device for power amplifier application is also presented.

A 60GHz cascode power amplifier with modified linearizer is then fabricated under 90-nm LP CMOS technology and fully characterized to enhance its linearity which demonstrated by its extremely well  $OP_{1dB}$ . The measurement results of the power amplifier show a power-added-efficiency at  $OP_{1dB}$  up to 14% while maintaining 15 dB small signal gain, 13.7 dBm  $OP_{1dB}$  and 15.4 dBm  $P_{sat}$ . It is the highest power-added-efficiency at  $OP_{1dB}$  for millimeter-wave CMOS power amplifiers which ever been published.

Index Terms — Power Amplifier, PA, High PAE, Linearizer, 60 GHz, V-band, Pre-distortion, Linearization Technique

# CONTENTS

| 口試委員會      | 下審定書                                         | #  |

|------------|----------------------------------------------|----|

| 誌謝         |                                              | .i |

| 中文摘要       | i                                            | ii |

| ABSTRAC    | тi                                           | v  |

| CONTENT    | S                                            | v  |

| LIST OF FI | IGURES vi                                    | ii |

| LIST OF TA | ABLES                                        | ii |

| Chapter 1  | Introduction                                 | 1  |

|            | Background and Motivation                    | 1  |

|            | Literature Survey                            | 2  |

| 1.3        | Contributions                                |    |

| 1.4        | Dissertation Organization                    | 8  |

| Chapter 2  | Linearity of MMW Power Amplifier             | 9  |

| 2.1        | Introduction of Power Amplifier              | 9  |

| 2.         | 1.1 Introduction                             | 9  |

| 2.         | 1.2 Important Parameters1                    | 0  |

| 2.2        | Linearity Consideration of Power Amplifier1  | 2  |

| 2.2        | 2.1 Nonlinear Distortion Characterization1   | 2  |

| 2.2        | 2.2 AM-AM Characteristic1                    | 3  |

| 2.2        | 2.3 Nonlinearity from two-tone input signal1 | 4  |

| Chapter 3  | Cold-FET Linearizer with Delay Line1         | 7  |

| 3.1        | Pre-distortion Linearizer                    | 8  |

|        | 3.1.1 | Pre-distortion Technique                               | 19 |

|--------|-------|--------------------------------------------------------|----|

|        | 3.1.2 | Loss Characteristic of Pre-Distortion Linearizer       | 20 |

|        | 3.1.3 | Cascading with Power Amplifier                         | 22 |

| 3.2    | Cold  | I FET Linearizer                                       | 25 |

|        | 3.2.1 | Introduction                                           | 25 |

|        | 3.2.2 | Operation Principle                                    | 25 |

|        | 3.2.3 | Challenge of CMOS Process in V-band                    | 27 |

| 3.3    | Mod   | lified Cold-Mode Linearizer Using Delay Line           | 29 |

|        | 3.3.1 | Guideline to Develop a Modified Linearizer             | 30 |

|        | 3.3.2 | Modified Cold-Mode Linearizer                          | 30 |

|        | 3.3.3 | Intuitive Interpretation of the Modification           | 32 |

| 3.4    | Ope   | ration Detail of Modified Linearizer                   | 33 |

|        | 3.4.1 | Analysis of Possible Effects during Operation          | 33 |

|        | 3.4.2 | Earlier Saturation Region                              | 36 |

|        | 3.4.3 | Lower Current Loss at Saturation Region                | 41 |

|        | 3.4.4 | Varying Resistor Effect                                | 43 |

|        | 3.4.5 | Verification of the modified linearizer                | 49 |

| 3.5    | Con   | clusion                                                | 52 |

| Chapte | r4 A  | 60GHz Cascode Power Amplifier with Modified Linearizer | 53 |

| 4.1    | Intro | oduction                                               | 53 |

|        | 4.1.1 | Motivation                                             | 53 |

|        | 4.1.2 | Objective                                              | 54 |

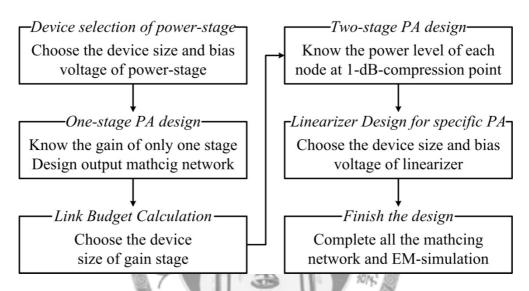

|        | 4.1.3 | Design Flow                                            | 55 |

| 4.2    | Prev  | ious Published Literatures                             | 57 |

|        | 4.2.1 | Cascode Device and the Proposed Power Amplifier        | 57 |

|         | 4.2.2 | Amplifier with Linearizer                              | 58  |

|---------|-------|--------------------------------------------------------|-----|

|         | 4.2.3 | High PAE Power Amplifier                               | 59  |

| 4.3     | Pre-l | Design a Two-Stage Power Amplifier                     | 59  |

|         | 4.3.1 | Device Selection                                       | 61  |

|         | 4.3.2 | One -Stage Power Amplifier                             | 68  |

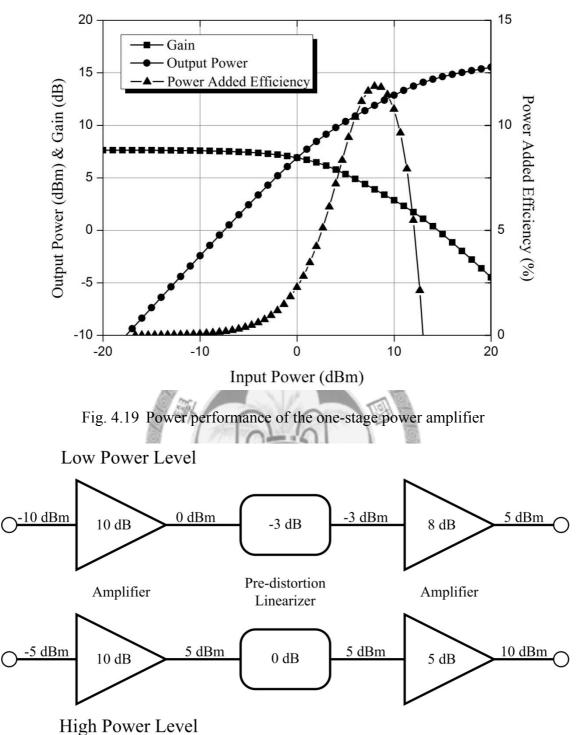

|         | 4.3.3 | Link Budget                                            | 71  |

|         | 4.3.4 | Conventional Two-Stage Power Amplifier                 | 73  |

|         | 4.3.5 | Power Performance at Different Node of Power Amplifier | 76  |

| 4.4     | Integ | gration of Linearizer to Power Amplifier               | 76  |

|         | 4.4.1 | Power Division and Gain compensation                   | 77  |

|         | 4.4.2 | Linearizer Size and Control Voltage Selection          | 82  |

|         | 4.4.3 | Two-stage Power Amplifier with Modified Linearizer     | 90  |

| 4.5     | Mea   | surement Results                                       | 97  |

|         | 4.5.1 | S-parameter                                            | 98  |

|         | 4.5.2 | Power Performance                                      | 100 |

|         | 4.5.3 | IMD3                                                   | 101 |

|         | 4.5.4 | Debug and Discussion                                   | 103 |

| 4.6     | Cone  | clusion                                                | 107 |

| Chapter | 5 C   | onclusions                                             | 109 |

| REFERI  | ENCE  |                                                        | 110 |

# **LIST OF FIGURES**

| Fig. 1.1  | Frequency allocation of different country in V-band [1]2                     |

|-----------|------------------------------------------------------------------------------|

| Fig. 2.1  | Simplified building blocks of conventional communication system9             |

| Fig. 2.2  | Definition of input and output 1-dB compression point14                      |

| Fig. 2.3  | Spectrum around fundamental tone after intermodulation14                     |

| Fig. 2.4  | Definition of third-order interception point16                               |

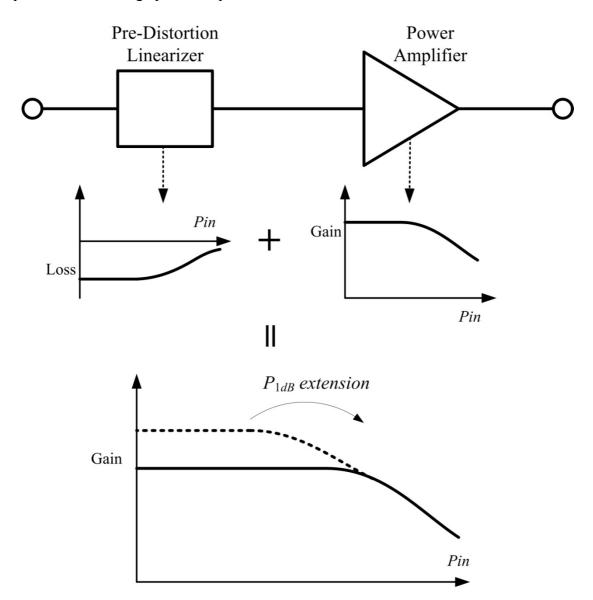

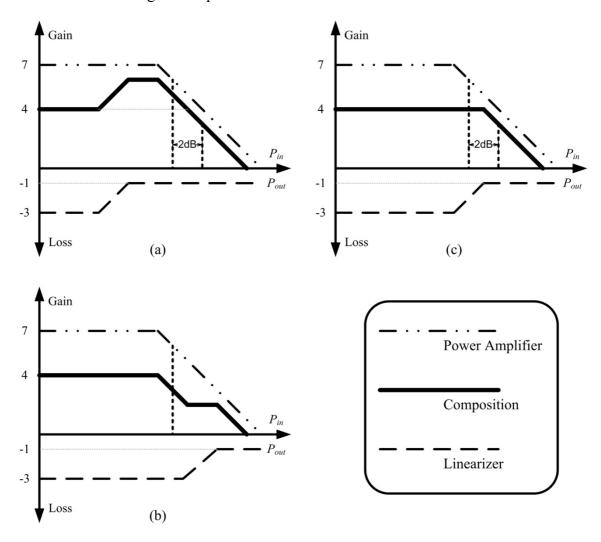

| Fig. 3.1  | Pre-distortion effect by cascading power amplifier with a linearizer         |

| Fig. 3.2  | Gain characteristics of power amplifier with and without pre-distortion      |

|           | technique                                                                    |

| Fig. 3.3  | Loss characteristic of a linearizer                                          |

| Fig. 3.4  | Consideration of cascading a linearizer with a power amplifier22             |

| Fig. 3.5  | Composite power performance for that the output power level of linearizer    |

|           | is (a) lower than (b) higher than, and (c) equal to the input power of power |

|           | amplifier at 1-dB compression point23                                        |

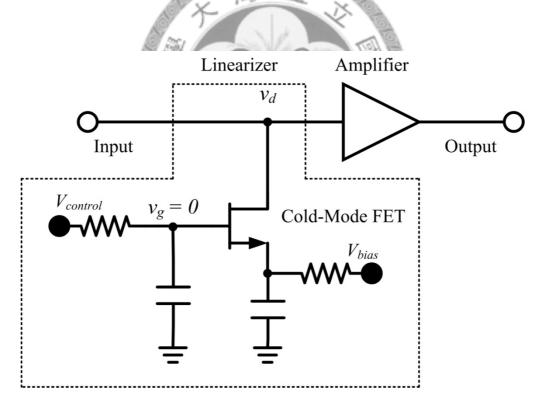

| Fig. 3.6  | Former proposed cold-FET linearizer [6]24                                    |

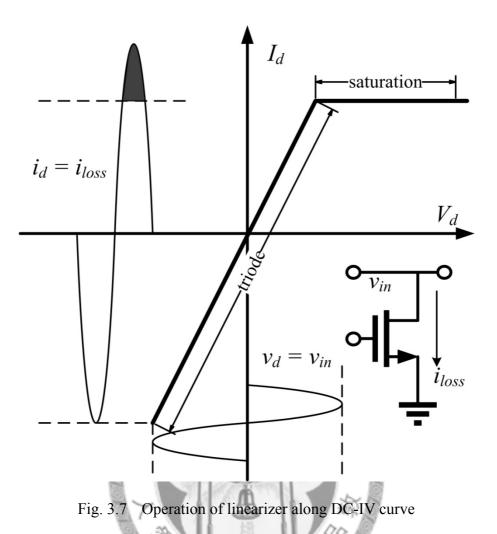

| Fig. 3.7  | Operation of linearizer along DC-IV curve                                    |

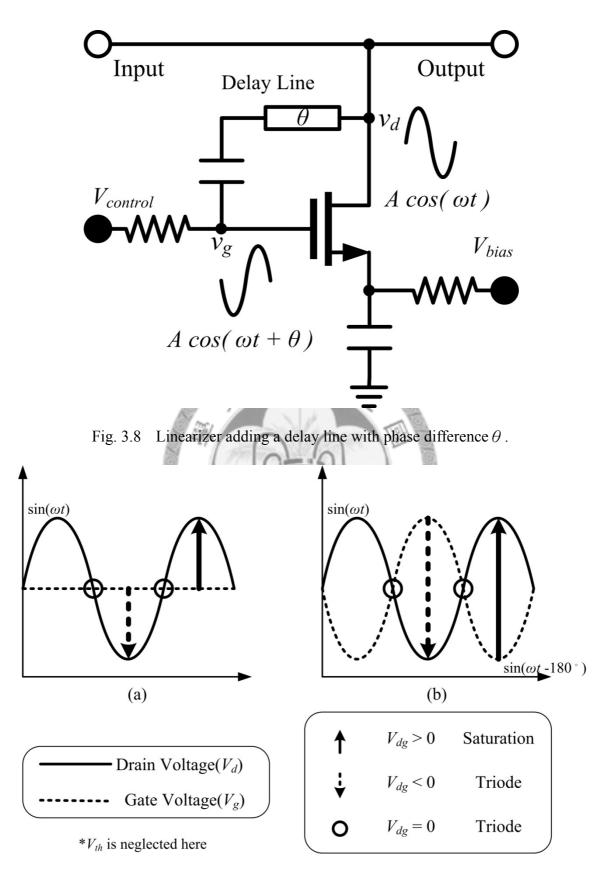

| Fig. 3.8  | Linearizer adding a delay line with phase difference0                        |

| Fig. 3.9  | The saturation condition of transistor of linearizer when the gate an drain  |

|           | are connected by (a) no delay line, and (b) a 180 degree delay line31        |

| Fig. 3.10 | Large signal operation of cold-FET linearizer with delay line                |

| Fig. 3.11 | Negative voltage swing at gate makes linearizer to enter saturation region   |

|           | easier                                                                       |

|           |                                                                              |

Fig. 3.12 The value of (a) gate voltage and drain voltage, (b) left-hand-side of

|           | equation (3.7), and (c) current in saturation region of linearizer with and  |

|-----------|------------------------------------------------------------------------------|

|           | without delay line                                                           |

| Fig. 3.13 | Constant up-swinging current after entering saturation region40              |

| Fig. 3.14 | Current reduction after entering saturation region41                         |

| Fig. 3.15 | Effect of varying admittance. Multiply (a) voltage at drain with constant    |

|           | admittance or (b) varying admittance to form current of linearizer under (c) |

|           | constant admittance or (d) varying admittance46                              |

| Fig. 3.16 | Self-compensation under 90° admittance variation                             |

| Fig. 3.17 | Simulate the loss characteristic of pre-distortion linearizer                |

| Fig. 3.18 | Loss curves of conventional linearizer and modified linearizer50             |

| Fig. 3.19 | Loss curves of linearizer with 90 and 180 degree delay line                  |

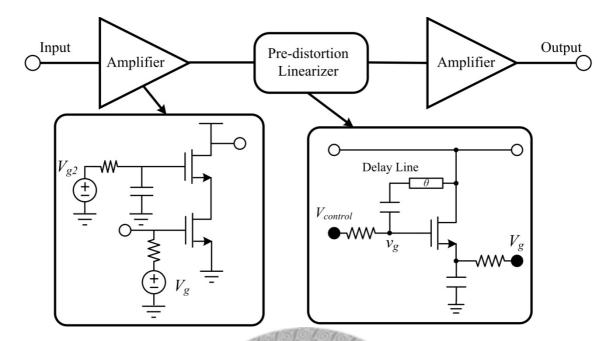

| Fig. 4.1  | Block diagram of the two-stage power amplifier with linearizer inserted in   |

|           | front of the power stage                                                     |

| Fig. 4.2  | Design flow of a two-stage power amplifier with linearizer                   |

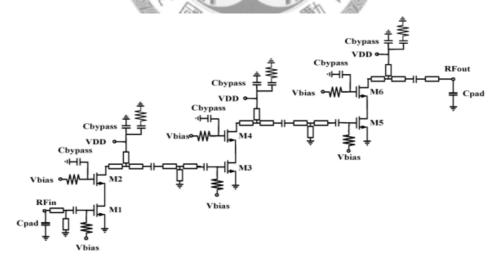

| Fig. 4.3  | Schematic of a three-stage cascode power amplifier [7]56                     |

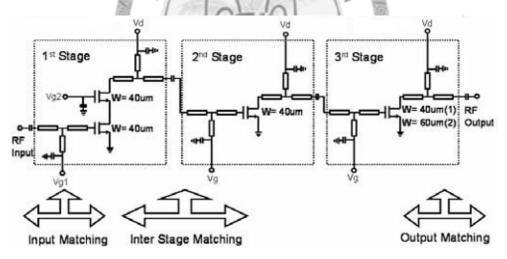

| Fig. 4.4  | Circuit schematic of three-stage 60GHz CMOS power amplifiers with the        |

|           | cascode device in first stage [14]57                                         |

| Fig. 4.5  | Circuit schematic of a 24GHz CMOS power amplifiers with a built-in           |

|           | linearizer in 0.18 µm CMOS process [15]58                                    |

| Fig. 4.6  | Circuit schematic of differential, transformer coupled CMOS PA [9]59         |

| Fig. 4.7  | Circuit schematic of cascode device60                                        |

| Fig. 4.8  | Comparison of maximum gain between common-source and cascode device.         |

|           |                                                                              |

| Fig. 4.9  | Maximum gain at 60 GHz and drain current versus gate bias voltage62          |

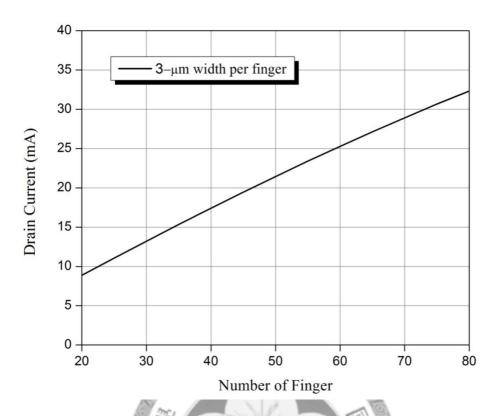

| Fig. 4.10 | Drain current of device with different total gate width and 0.7-V $V_{g}$ 64 |

| Fig. 4.11 | Maximum available gain of device with different total gate width64            |

|-----------|-------------------------------------------------------------------------------|

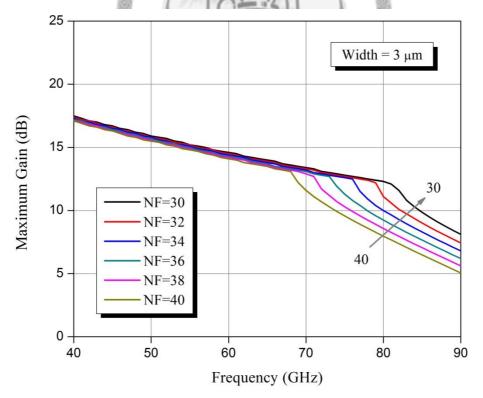

| Fig. 4.12 | Maximum gain of 90 µm device with different number of finger65                |

| Fig. 4.13 | Comparison of power performance of same total gate width power stage          |

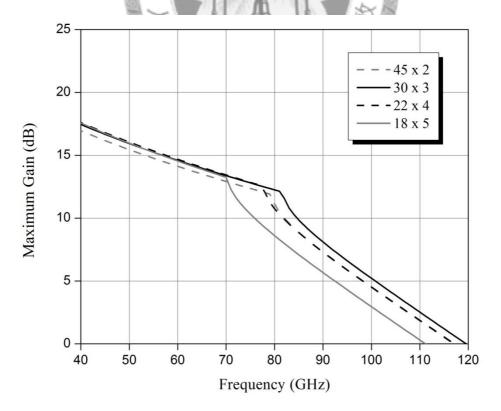

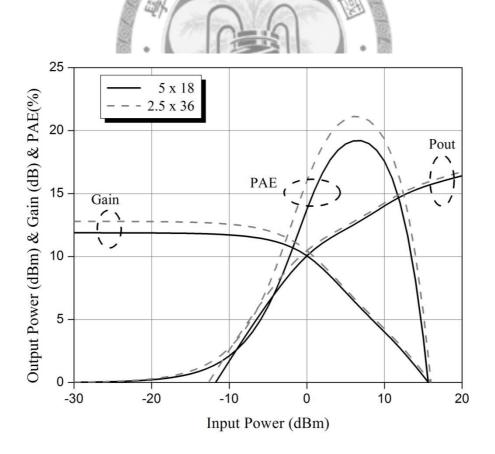

|           | with different finger                                                         |

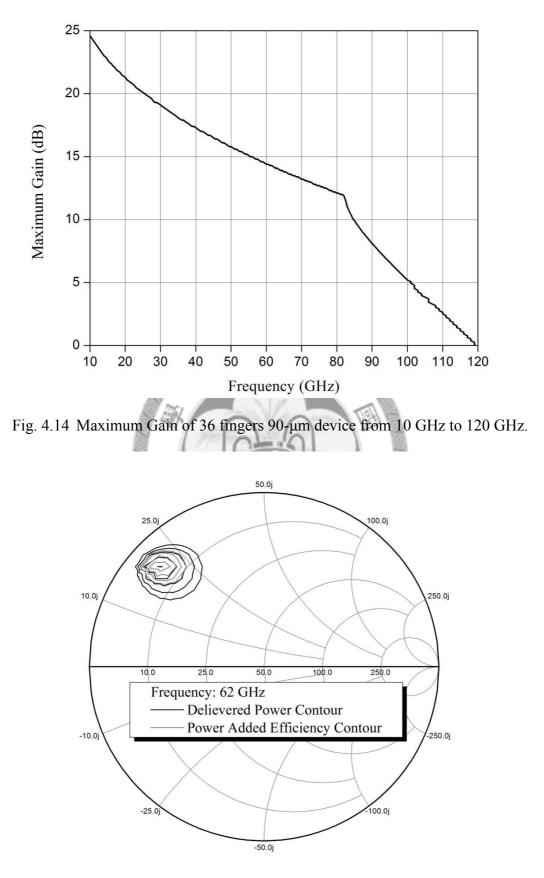

| Fig. 4.14 | Maximum Gain of 36 fingers 90-µm device from 10 GHz to 120 GHz67              |

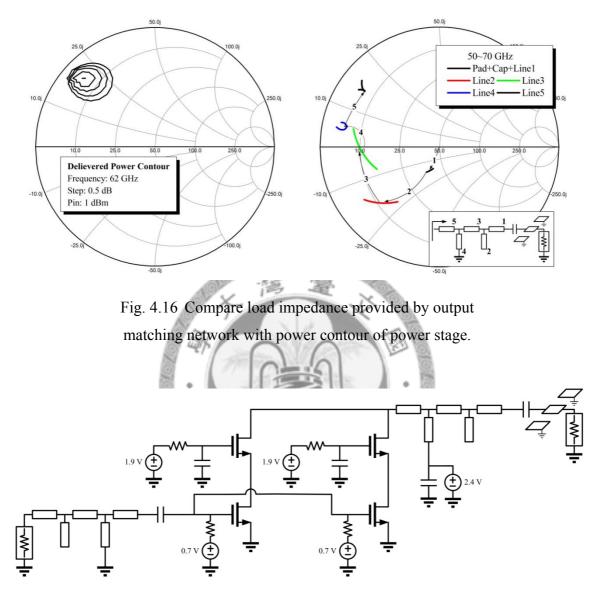

| Fig. 4.15 | Load-pull simulation of 36 fingers 90-µm device at 62 GHz67                   |

| Fig. 4.16 | Compare load impedance provided by output matching network with power         |

|           | contour of power stage                                                        |

| Fig. 4.17 | Circuit schematic of one-stage power amplifier                                |

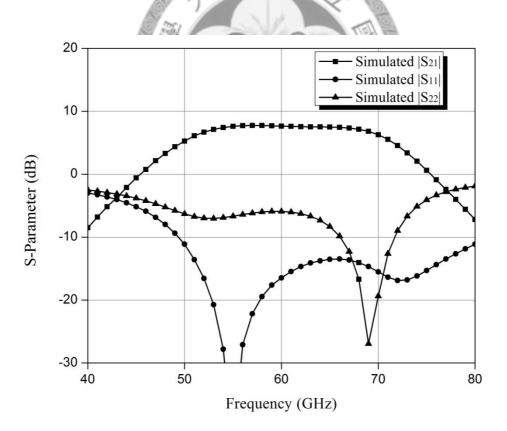

| Fig. 4.18 | S-parameter of the one-stage power amplifier70                                |

| Fig. 4.19 | Power performance of the one-stage power amplifier71                          |

| Fig. 4.20 | Link budget of two-stage power amplifier with linearizer71                    |

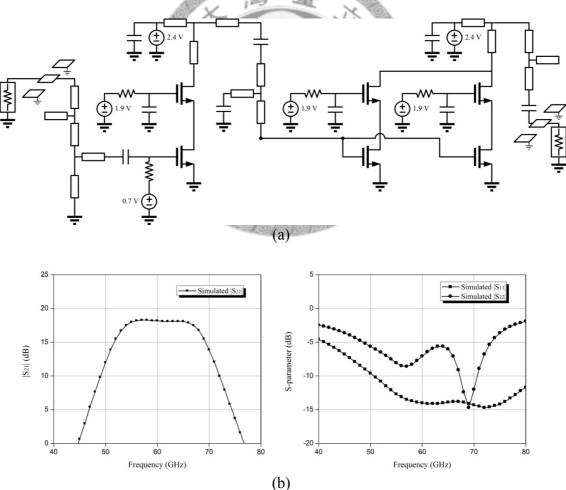

| Fig. 4.21 | (a) Circuit schematic and (b) S-parameter simulation result, of conventional  |

|           | two-stage power amplifier74                                                   |

| Fig. 4.22 | Power performance of conventional two-stage power amplifier75                 |

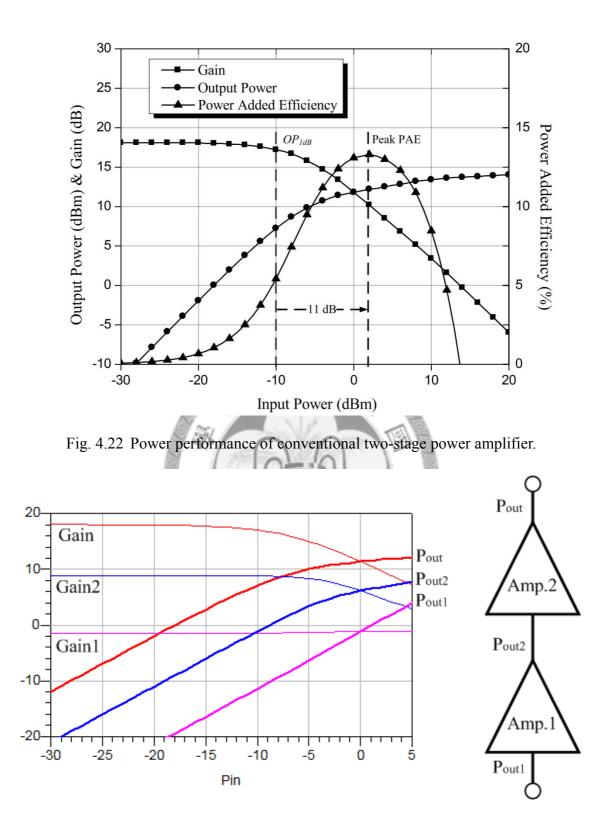

| Fig. 4.23 | Gain curve and output power of conventional two-stage power amplifier at      |

|           | different node of the circuit75                                               |

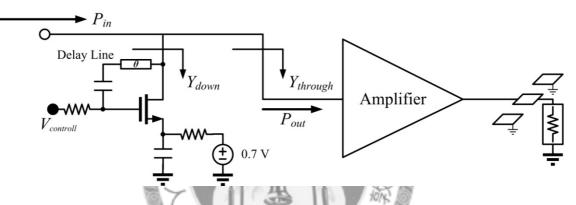

| Fig. 4.24 | Input power is divided by the admittance of amplifier and linearizer77        |

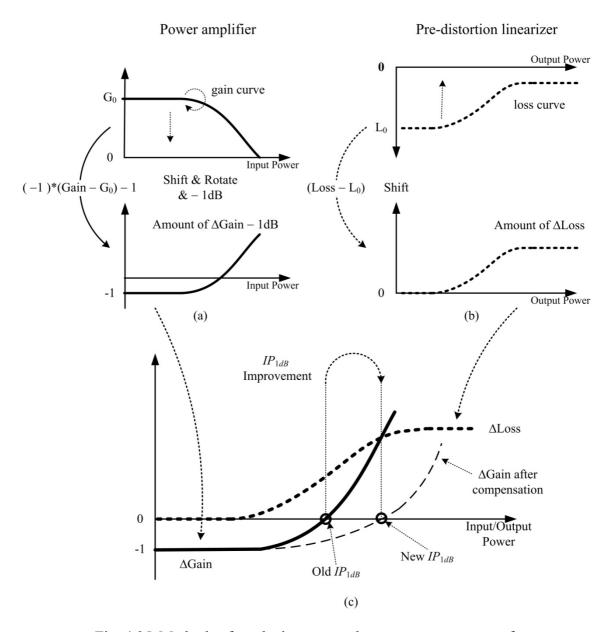

| Fig. 4.25 | Methods of producing curves that represents amount of (a) gain                |

|           | compression, and (b) loss deviation. Place the two curves together to form    |

|           | the (c) compensation curve79                                                  |

| Fig. 4.26 | (a) Loss curve of linearizer under different control voltage. (b) Envelope of |

|           | loss deviation curve for specific total gate width. (c) Interception of loss  |

|           | deviation curves and gain compression curves. (d) Choose adequate total       |

|           | gate width by using envelopes of loss deviation curves with different total   |

|           | Х                                                                             |

|           | gate width                                                                               |

|-----------|------------------------------------------------------------------------------------------|

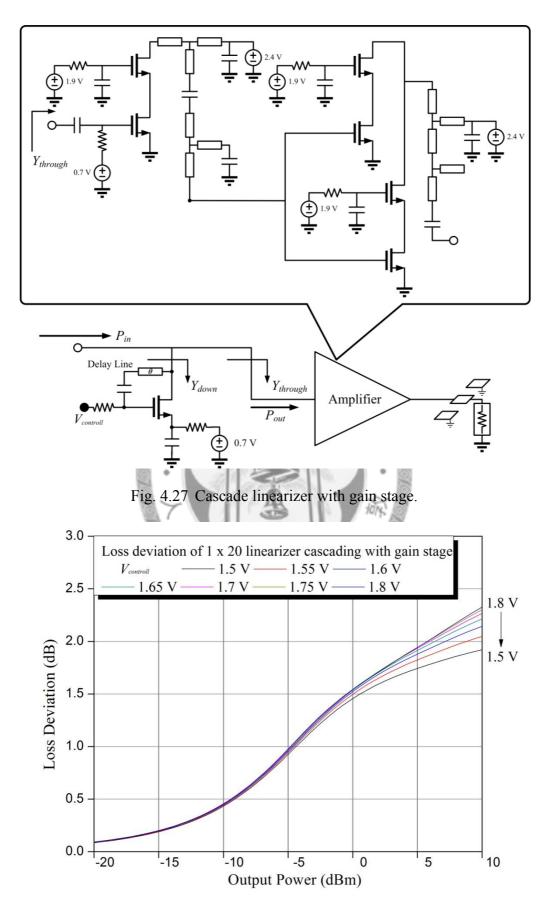

| Fig. 4.27 | Cascade linearizer with gain stage                                                       |

| Fig. 4.28 | Loss deviation curve of 20-µm-gate-width linearizer cascading gain stage.83              |

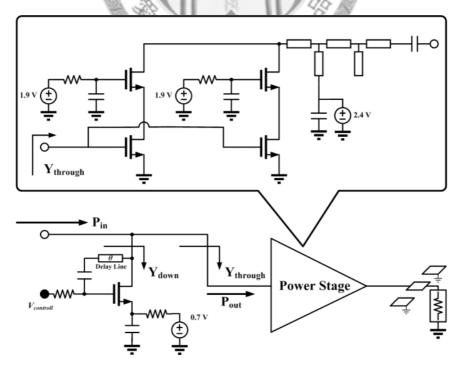

| Fig. 4.29 | Cascade linearizer with power stage                                                      |

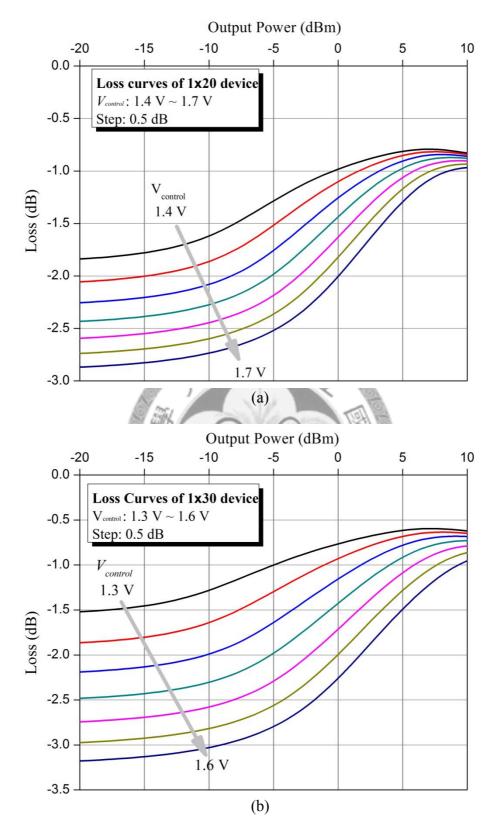

| Fig. 4.30 | Loss curves of linearizer with (a) 20-µm (b) 30-µm total gate width under                |

|           | different control voltage                                                                |

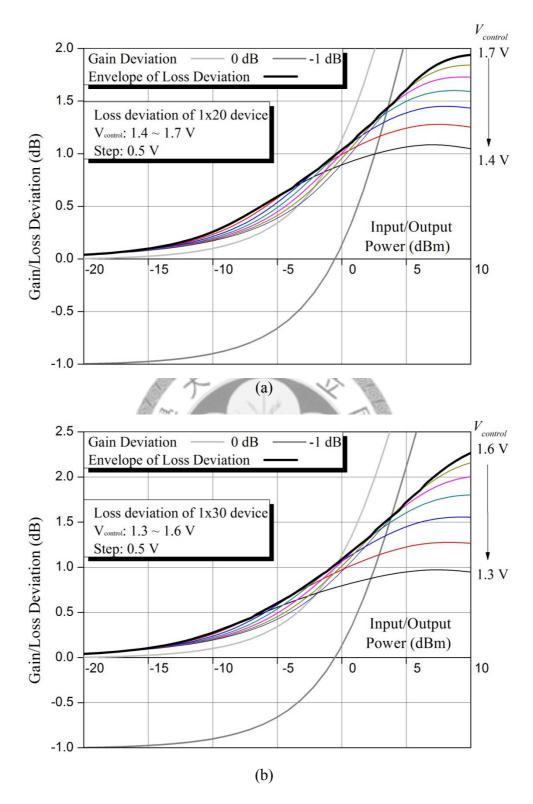

| Fig. 4.31 | Loss deviation curve of linearizer with (a) 20- $\mu$ m (b) 30- $\mu$ m total gate width |

|           | under different control voltage and the envelope of them                                 |

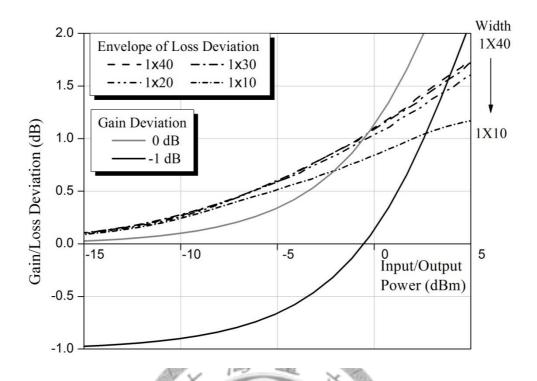

| Fig. 4.32 | Envelopes of loss deviation curves with different total gate width                       |

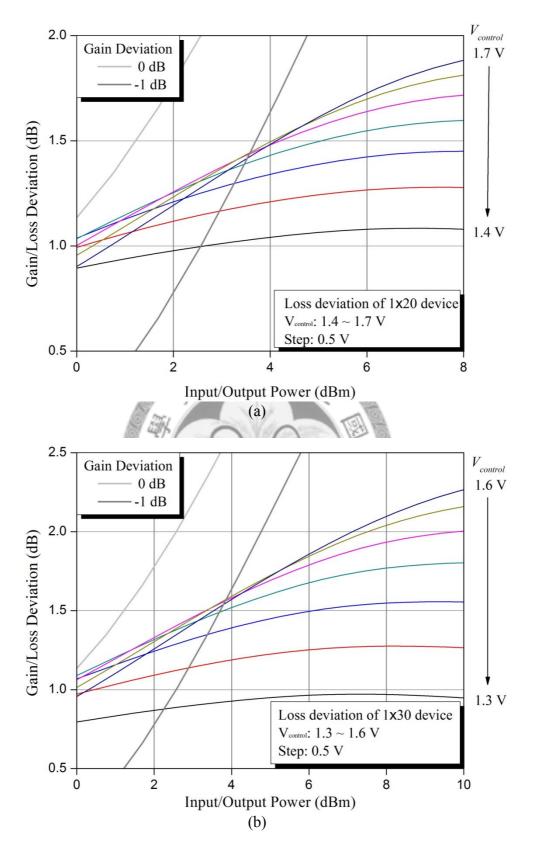

| Fig. 4.33 | The detail figure of loss deviation curve of linearizer with (a) 20- $\mu$ m (b)         |

|           | 30-µm total gate width under different control voltage                                   |

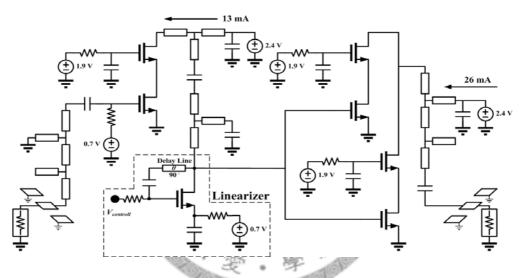

| Fig. 4.34 | Circuit Schematic of two-stage power amplifier with modified linearizer90                |

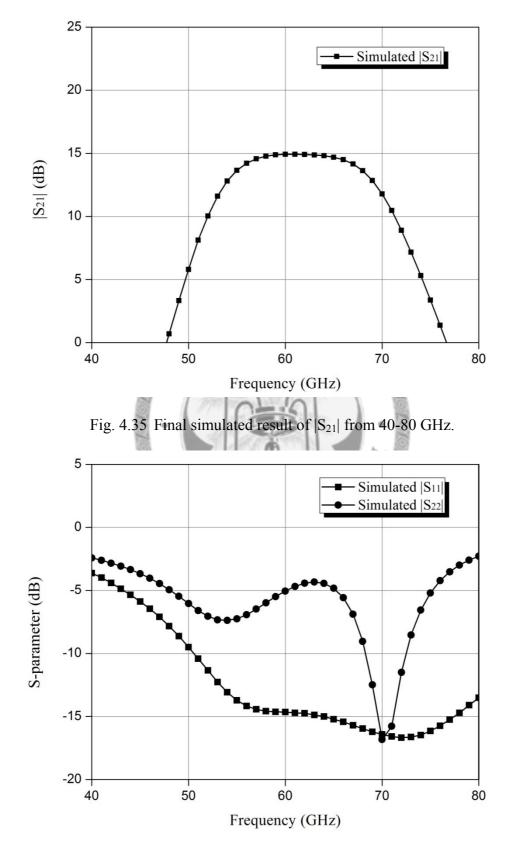

| Fig. 4.35 | Final simulated result of  S <sub>21</sub>   from 40-80 GHz91                            |

| Fig. 4.36 | Final simulated result of $ S_{11} $ and $ S_{22} $ from 40-80 GHz91                     |

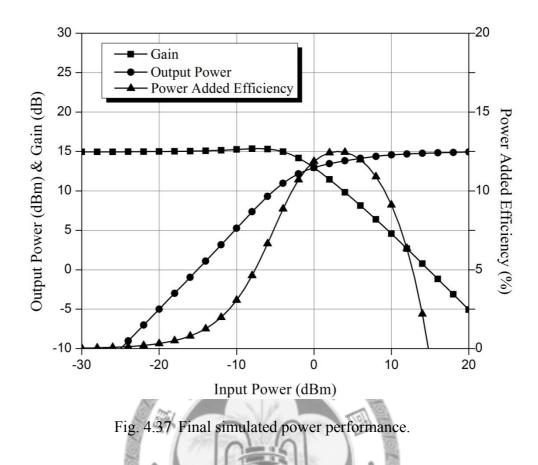

| Fig. 4.37 | Final simulated power performance                                                        |

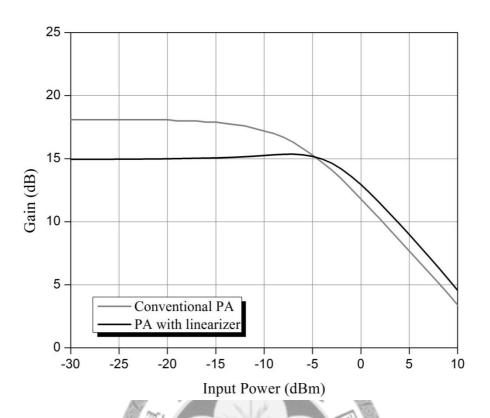

| Fig. 4.38 | Comparison of AM-AM characteristics of power amplifier with modified                     |

|           | linearizer and conventional power amplifier without linearizer                           |

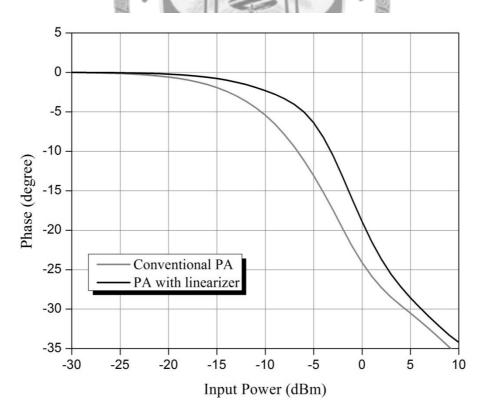

| Fig. 4.39 | Comparison of AM-PM characteristics of power amplifier with modified                     |

|           | linearizer and conventional power amplifier without linearizer                           |

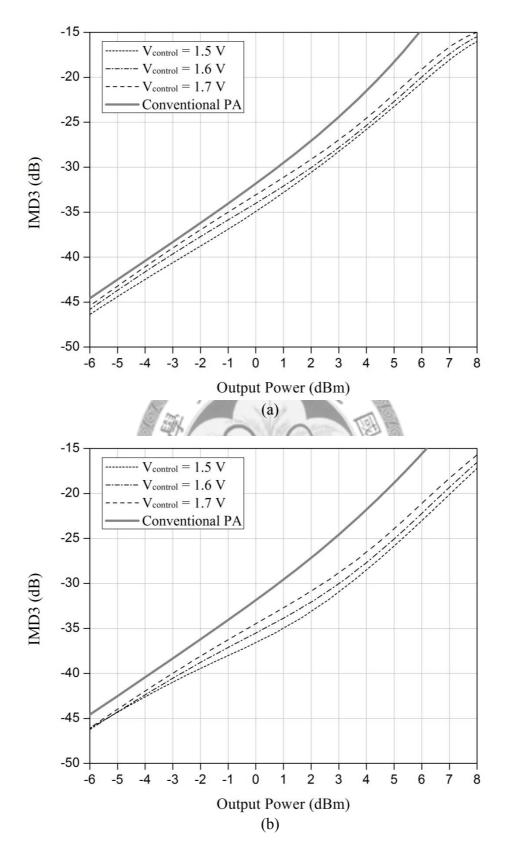

| Fig. 4.40 | (a) Upper-side-band and (b) lower-side-band IMD3 of conventional power                   |

|           | amplifier and power amplifier with modified linearizer under different                   |

|           | control voltage94                                                                        |

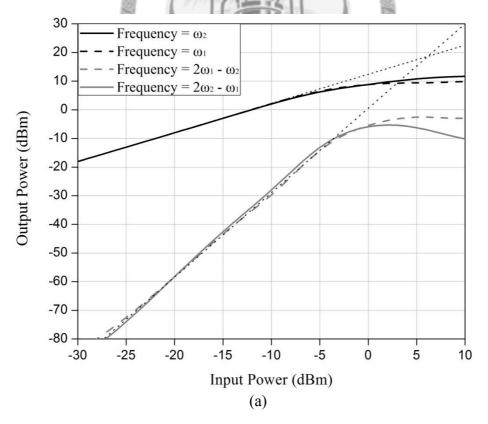

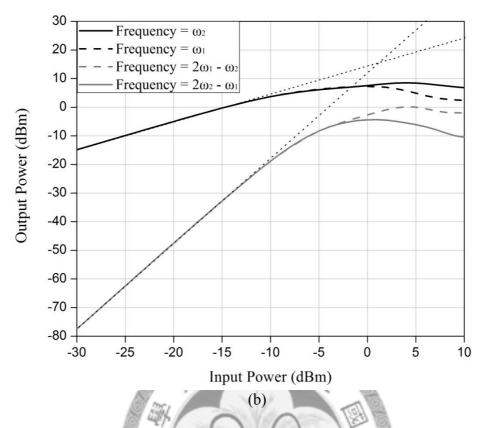

| Fig. 4.41 | IIP3 of (a) power amplifier with modified linearizer under 1.6-V control                 |

|           | voltage and (b) conventional power amplifier without linearizer96                        |

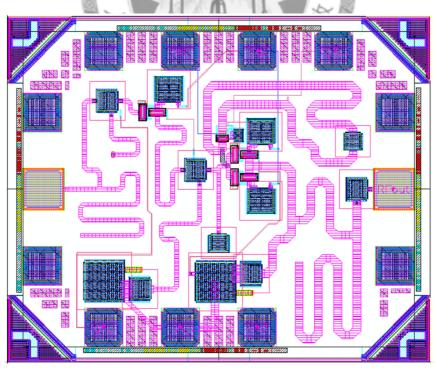

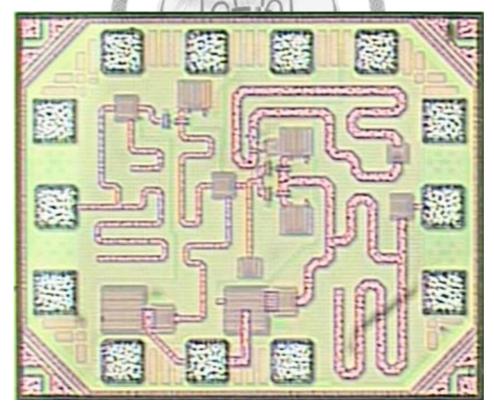

| Fig. 4.42 | Layout of the 57-66 GHz power amplifier with size of 0.45 x $0.55 \text{ mm}^2$ 96       |

| Fig. 4.43 | Chip photo of the 57-66 GHz power amplifier chip with size of 0.45 x 0.55           |

|-----------|-------------------------------------------------------------------------------------|

|           | mm <sup>2</sup> including all the testing pads97                                    |

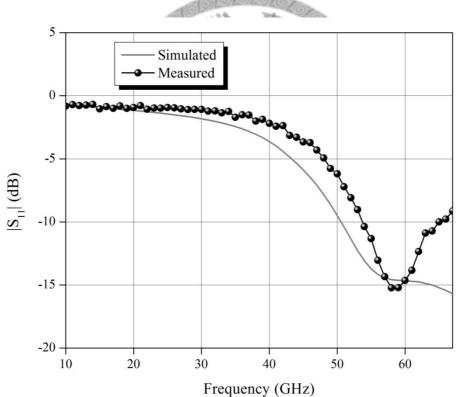

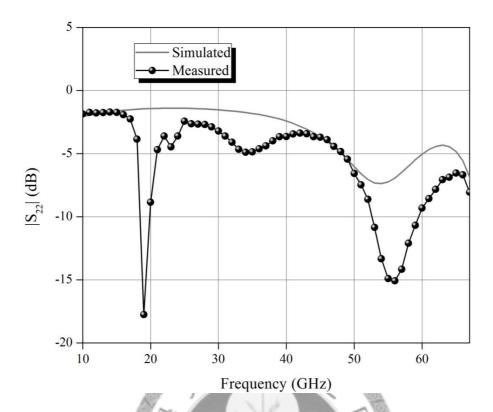

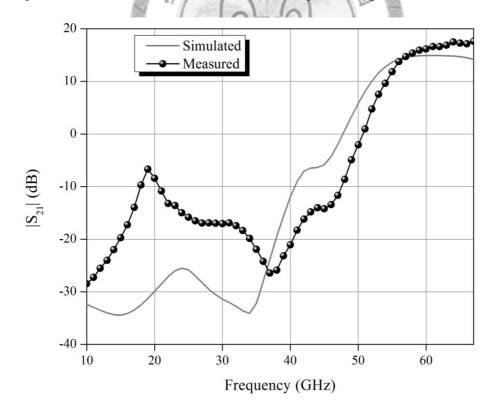

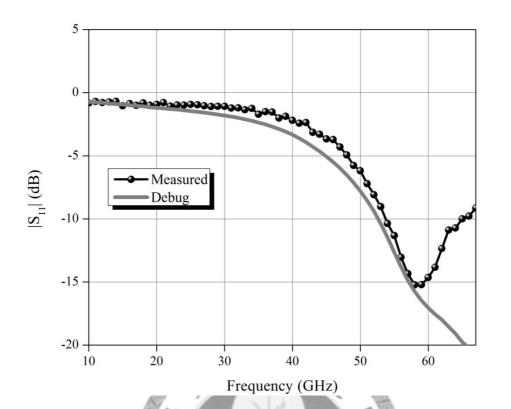

| Fig. 4.44 | Simulated and measured $ S_{21} $ of the power amplifier from 30-67 GHz98           |

| Fig. 4.45 | Simulated and measured $ S_{22} $ of the power amplifier from 30-67 GHz99           |

| Fig. 4.46 | Simulated and measured $ S_{21} $ of the power amplifier from 30-67 GHz99           |

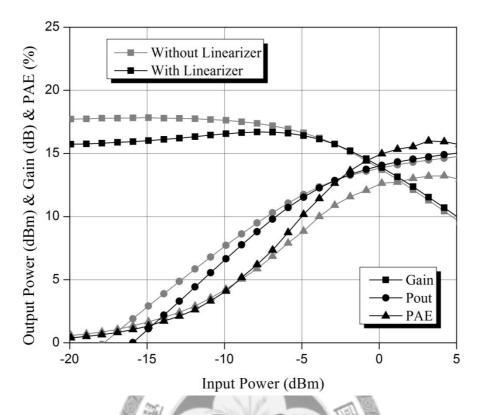

| Fig. 4.47 | The measured $P_{out}$ , Gain, and PAE versus $P_{in}$ when the linearizer of power |

|           | amplifier is turn-on and turn-off at 60 GHz100                                      |

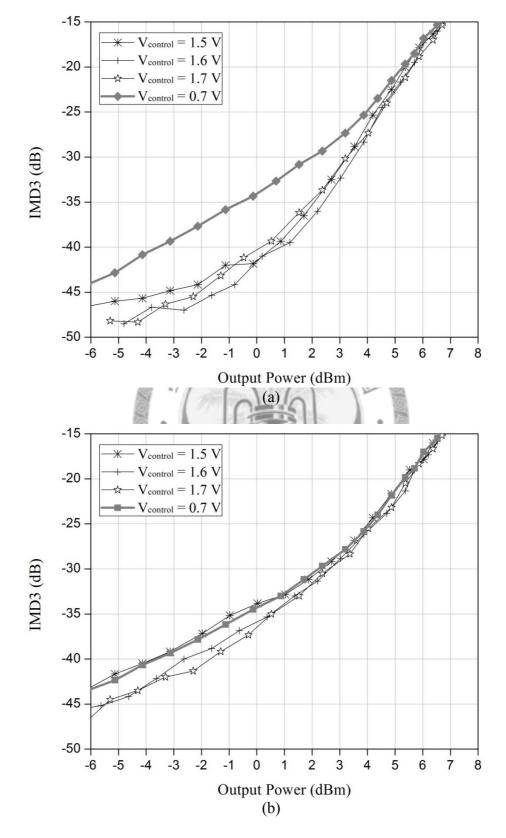

| Fig. 4.48 | Measured (a) upper-side-band and (b) lower-side-band IMD3 of power                  |

|           | amplifier with modified linearizer biased by different control voltage102           |

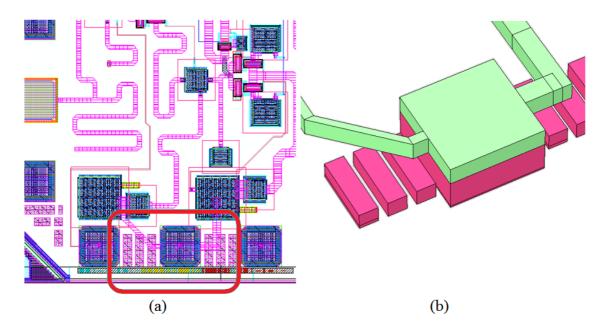

| Fig. 4.49 | (a) Layout and (b) EM-simulation of DC-pad for $V_{dd}$ 103                         |

| Fig. 4.50 | Debug and measured $ S_{11} $ of the power amplifier from 10-67 GHz104              |

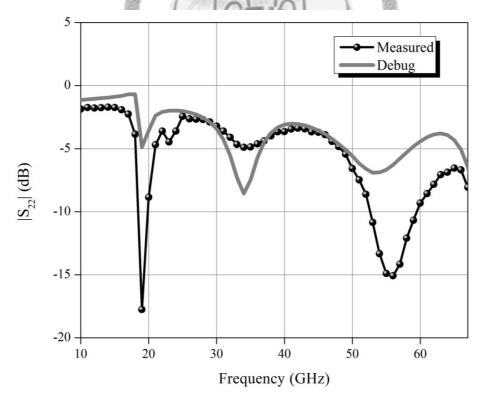

| Fig. 4.51 | Debug and measured $ S_{22} $ of the power amplifier from 10-67 GHz104              |

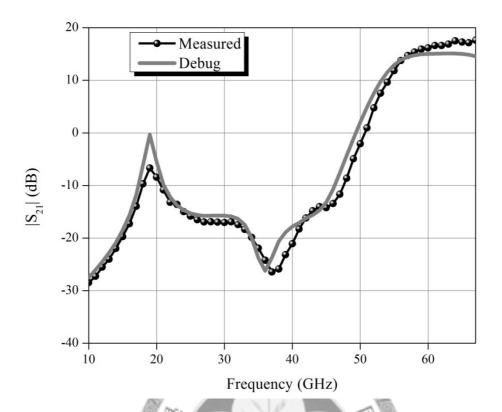

| Fig. 4.52 | Debug and measured $ S_{21} $ of the power amplifier from 10-67 GHz105              |

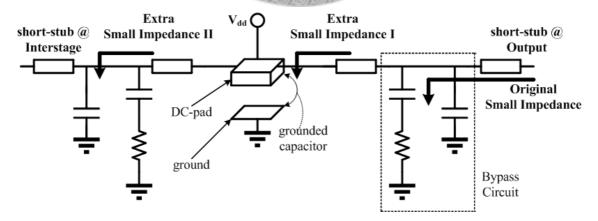

| Fig. 4.53 | Connecting bypass circuits of inter-stage and output matching networks              |

|           | back-to-back through DC-pad of V <sub>dd</sub> 106                                  |

|           |                                                                                     |

# LIST OF TABLES

| Table 1.1 | V-band power amplifiers on GaAS pHEMT and SiGe BiCMOS process3      |

|-----------|---------------------------------------------------------------------|

| Table 1.2 | V-band power amplifiers on 90-nm CMOS process4                      |

| Table 1.3 | V-band power amplifiers on 65-nm and 45-nm CMOS process             |

| Table 3.1 | Definitions of variables regarding DC bias and signal voltage35     |

| Table 4.1 | Power performance of different chips for different frequencies101   |

| Table 4.2 | Comparison of this work with excellent power amplifier in V-band on |

|           | CMOS process107                                                     |

| Table 4.3 | Performance of this work                                            |

|           |                                                                     |

# Chapter 1 Introduction

### **1.1 Background and Motivation**

As the demands for wireless communication technology are growing rapidly recently, higher and higher data rate is required for high speed transmission. Although high frequency and complex digital modulation schemes are solutions for higher data rate communication system, the bottleneck is the linearity of a communication system. Power amplifier, which consumes the most power in a communication system and is the most likely to saturate is the key component that manages the power efficiency and linearity of a communication system. However, traditional linearization techniques are not suitable for high-frequency application and are always complicated. Moreover, the purpose is even more challenged while using CMOS technology because of its higher substrate loss and severe parasitic effect in high frequency band. Our goal is to research possible solution of linearization technique for millimeter-wave frequencies using CMOS technology and design a power amplifier that can achieve excellent performance by the aid of linearization technique.

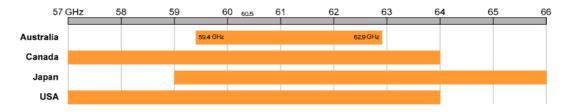

In the past few years, 7 GHz of contiguous bandwidth have been assigned for unlicensed use at millimeter-wave (MMW) frequencies around 60 GHz in different country, for example U.S. (57–64 GHz) and Japan (59–66 GHz), as shown in Fig. 1.1 [1]. The frequency band planed to be used is called V-band, which is an area that many techniques are still under research. The linearization technique that can help to enhance the precious power performance of power amplifier in the V-band is one of them. Therefore, we would like to develop a linearization technique that can be used in V-band.

#### Frequency Allocation

Shown below are the frequency allocations in the regions specified in the earlier paragraph.

Fig. 1.1 Frequency allocation of different country in V-band [1].

### **1.2 Literature Survey**

As V-band has become a more and more popular frequency band, a lot of power amplifiers for application in V-band are proposed. The power amplifiers have been demonstrated with various monolithic microwave integrated circuit (MMIC) technologies. List of proposed power amplifier on different technologies are shown from Table 1.1 to Table 1.3.

Since HEMT technology has advantages of high electron mobility, power amplifier with more than 27 dBm output power was proposed in 1997 with a 21 % peak power-added-efficiency (PAE) [16] using 0.1 µm pHEMT process. Another circuit demonstrates a even higher peak PAE of 26 % using process 0.15 µm pHEMT process [33]. Since 0.1 µm pHEMT process is a better process than 0.15 µm pHEMT process, the latter PA demonstrate a better design skill and is also practical for commercial use.

SiGe BiCMOS is another technology that provides possible solution for a highly integrated power amplifier in V-band. Some SiGe power amplifier has high peak PAE of 20.9 % with an acceptable output power [35], while some provides higher output power 20 dBm but lower peak PAE [34]. Unfortunately, the latter one has a poor 1-dB-compression output power ( $OP_{1dB}$ ) of only 13.1 dBm. The largest output power is demonstrated in 2007 with 23.1-dBm saturation power ( $P_{sat}$ ) [10]. It also demonstrates

good linearity with a 20-dBm  $OP_{1dB}$ . However, the PAE only has a value of 6.4% that would consume more DC power.

| Ref.                         | Topology           | Process | Freq. | Gain  | $OP_{1dB}$ | $P_{sat}$ | Peak    | Vdd | Area     |

|------------------------------|--------------------|---------|-------|-------|------------|-----------|---------|-----|----------|

| Kel.                         | ropology           | 1100035 | (GHz) | Ualli |            | (dBm)     | PAE (%) | (V) | $(mm^2)$ |

| [16] 1997                    | 2-stage            | 0.1 µm  | 62.5  | 13    | N/A        | 27.5      | 21      | 5   | 10.35    |

| JSSCC                        | CS                 | pHEMT   | 02.5  | 13    | IN/A       | 27.5      | 21      | 5   | 10.55    |

| [33] 2009                    | 3-stage            | 0.15 µm | 60    | 17    | N/A        | 27.5      | 26      | 6   | 10.62    |

| IMS                          | Cascode            | pHEMT   | 00    | 17    | 1,111      | 27.0      | 20      | U   | 10.02    |

| [34] 2006                    | 2-stage<br>(diff.) | 0.13 µm | 60    | 18    | 13.1       | 20        | 12.7    | 4   | 0.975    |

| ESSCIRC                      | Cascode            | SiGe    | 500   |       | OLOTON:    |           |         |     |          |

| [35] 2006                    | 1-stage            | 0.13 µm | 58    | 4.2   | N/A        | 11.5      | 20.9    | 1.2 | 0.98     |

| ASSCC                        | CS                 | SiGe    | 130   | 4.2   | N/A        | 11.5      | 20.9    | 1.2 | 0.98     |

| [10] 2007                    | 2-stage<br>DAT     | 0.13 µm | 60    | 13    | 20         | 23.1      | 6.4     | 4   | 3.42     |

| TMTT                         | Cascode            | SiGe    |       |       | 100        | 1.1       |         |     |          |

| ✤DC/RF pads are not included |                    |         |       |       |            |           |         |     |          |

Table 1.1 V-band power amplifiers on GaAS pHEMT and SiGe BiCMOS process.

Another most well known Si-based technology is the CMOS technology. The limitation of conductive substrate has been overcome by the smaller gate length which results in higher  $f_{max}/f_T$ . The first class of CMOS technology that can be used for designing V-band power amplifier is the 90-nm CMOS technology. A lot of V-band power amplifiers using 90-nm CMOS technology have been proposed from 2007, as listed in Table 1.2. Some have small gain, which is difficult for practical use [17],[19],[21],[24]. Power amplifier constructed with cascode device can provide higher gain and high output power [18], [7], [8]. The milestone is a three stage power cascode power amplifier which can provide gain of 31.3 dB,  $P_{sat}$  of 16.2 dBm and peak PAE of 14% [7]. But the power amplifier has poor  $OP_{1dB}$  resulted from poor linearity of cascode device. Therefore, some amplifier would use the cascode device for gain stage to

provide higher gain and use common source device for power stage to provide acceptable linearity [14], [28].

| D-f       | Tancles     | Duo      | Freq.  | Cain   |            | P <sub>sat</sub> | Peak                               | Vdd     | Area                    |     |        |

|-----------|-------------|----------|--------|--------|------------|------------------|------------------------------------|---------|-------------------------|-----|--------|

| Ref.      | Topology    | Process  | (GHz)  | Gain   | $OP_{1dB}$ | (dBm)            | PAE (%)                            | (V)     | $(mm^2)$                |     |        |

| [17] 2007 | 3-stage     | 90 nm    | 60     | 5.0    | 6.4        | 0.2              | 74                                 | 15      | 0.15                    |     |        |

| JSSCC     | CS          | CMOS     | 60     | 5.2    | 6.4        | 9.3              | 7.4                                | 1.5     | 0.15                    |     |        |

| [14] 2008 | 1-stage ca. | 90 nm    |        |        |            |                  |                                    |         |                         |     |        |

| ISSCC     | 2-stage CS  | CMOS     | 60     | 17     | 5.1        | 8.4              | 5.8                                | 1.5     | 0.99                    |     |        |

| [19] 2008 | 4-stage     | 90 nm    | 60     | 8.3    | 8.2        | 10.6             | N/A                                | 1.2     | N/A                     |     |        |

| ISSCC     | CS          | CMOS     | 00     | 8.5    | 0167       | 10.0             | 1N/A                               | 1.2     | $\mathbf{N}/\mathbf{A}$ |     |        |

| [20] 2008 | 3-stage     | 90 nm    | 62     | 1/1 3  | 10.5       | 11.5             | 8.2                                | 1       | 0.18 🔆                  |     |        |

| ISSCC     | CS          | CMOS     | X-02 P | 14.5   | 10.5       | 11.5             | 0.2                                | 1       | 0.10                    |     |        |

| [21] 2008 | 2-stage     | 90 nm    | 60     | 5.6    | 9          | -12.3            | 8.8                                | 1       | 0.25                    |     |        |

| ISSCC     | CS (diff.)  | CMOS     | 00     | 5.0    | 0          | 12.5             | 0.0                                | 1       | 0.23                    |     |        |

| [28] 2009 | 1-stage ca. | 90nm     | 6      | 1      | 2          |                  |                                    |         |                         |     |        |

| IMS       | 3-stage CS  | CMOS     | 60     | 20     | 8.2        | 12               | 9                                  | 1       | 0.65                    |     |        |

| [23] 2009 | 3-stage     | 90 nm    | 60     | 10     | 00         | . "" B           | 6.9                                | 1       | 0.64                    |     |        |

| RFIC      | CS          | CMOS     | 60     | 10     | 8.8        | 12.6             | 0.9                                | 1       | 0.64                    |     |        |

| [24] 2009 | 3-stage     | 90 nm    | 60 3   | 4.4    | 12.1       | 14.2             | 5.8                                | 1       | 1.2                     |     |        |

| RFIC      | CS          | CMOS     | 00 =   | 2 4.4  | -12.1      | 14.2             | 3.8                                | 1       | 1.2                     |     |        |

| [22] 2010 | 4-stage     | 90 nm GP | 60     | 20.6   | 18.2       | 19.9             | 14.2                               | 1       | 2 25                    |     |        |

| ISSCC     | CS          | CMOS     | 00     | 20.0   | 18.2       | 19.9             | 14.2                               | 1       | 3.25                    |     |        |

| [18] 2008 | 3-stage     | 90 nm    | 51.2   | 19.5   | 3.1        | 8.2              | 4.2                                | 2       | 1.13                    |     |        |

| JSSCC     | Cascode     | CMOS     | 31.2   | 19.5   | 5.1        | 0.2              | 4.2                                | 2       | 1.15                    |     |        |

| [7] 2009  | 3-stage     | 90nm GP  | 50.70  | 21.2   | 11.7       | 16.2             | 14                                 | 2.4     | 0.22                    |     |        |

| MWCL      | Cascode     | CMOS     | 50-70  | 31.3   | (60G)      | 16.2             | 14                                 | 2.4     | 0.33                    |     |        |

|           | 3-stage     |          | 57-69  | 26.1   | 10.5       | 14.5             | 10.5                               | 1 0     |                         |     |        |

| [8] 2008  | DAT         | 90nm GP  | (Gain) | 26.1   | 10.5       |                  | (60 G)                             | 1.8     | 0.64                    |     |        |

| CSICS     | Cascode     | CMOS     | 57-69  | 200    | 145        | 10               | 12.2                               | 7**     | 0.64                    |     |        |

|           |             |          | (Gain) | 26.6   | 14.5       | 18               | (60 G)                             | 3**     |                         |     |        |

| [9] 2008  | 3-stage     | 90nm LP  |        |        |            |                  | 19.3*                              |         |                         |     |        |

| RFIC      | CS (diff.)  | CMOS     | 58-63  | 15     | 15         | 15               | 10.2                               | 12.5    |                         | 1.2 | 0.15 🔆 |

|           | DC/RF pads  |          | ad *fc | r only | one chin   | **7 /            | $\frac{(15\%)}{\text{V is nomin}}$ | al valı | 10                      |     |        |

Table 1.2 V-band power amplifiers on 90-nm CMOS process.

\*DC/RF pads are neglected \*for only one chip \*\*2.4 V is nominal value

As to the issue of PAE, some had peak PAE lower than 10 % that would waste too much DC power and not practical for use, which are listed in the top eight columns of Table 1.2. The highest peak PAE of 19.3 % is achieved by a three-stage transformer couple power amplifier with 15 dB gain and 12.5  $P_{sat}$  [9]. However, as shown in the literature, it only has input return loss of 2 dB around 60 GHz, and the highest peak PAE is only achieved by one chip. Power amplifier with distributed active transformer (DAT) can provide 18-dBm  $P_{sat}$  and gain of 26.6 dB under 3 V supply voltage with 12.2% peak PAE [8]. A state-of-the-art four stage wikinson combine common source power amplifier is proposed in 2010 [22]. The PAE provides gain of 20.6 dB,  $OP_{1dB}$  of 18.2 dBm,  $P_{sat}$  of 19.9 dBm, and peak PAE of 14.2 %. The only disadvantage is its large size resulted from wikinson power combiner which is expensive.

45-nm and 65-nm CMOS are more advanced CMOS technology comparing to 90-nm CMOS technology. Since the technologies have higher  $f_{max}/f_T$ , almost all the power amplifiers fabricated by the two technologies have peak PAE more than 10 % from 2009, as listed in Table 1.3. Since the two technologies are similar to 90-nm CMOS, some design structures are just the same to those in Table 1.2 [12], [29]. A four-stage common source power amplifier with modified distributed active transformer provides the highest  $P_{sat}$  of 17.7 dBm and highest  $OP_{1dB}$  of 15.1 dBm among all the circuits designed by the two technologies [27]. Moreover, the power amplifier still has a peak PAE of 14.2 %, gain of 19.2 dB and small size, which shows a possibility for practical use. Another excellent power amplifier is also proposed in 2010, which provides  $P_{sat}$  of 14.5 dBm and  $OP_{1dB}$  of 11.2 dBm and gain of 20 dB [30]. Since the peak PAE is nearly 15%, it is more efficient than the former one. The best power amplifier is fabricated on the 65-nm SOI CMOS process [32]. The technology is one of the best and most expensive Si-based technologies. By the excellent performance of the technology, the power amplifier provides gain of 16 dB,  $P_{sat}$  of 14.5 dBm and  $OP_{1dB}$  of 12.7 dBm and amazing peak PAE of 25%.

| Ref.      | Topology                    | Process  | Freq. | Gain             | $OP_{1dB}$ | $P_{sat}$ | Peak    | Vdd | Area     |

|-----------|-----------------------------|----------|-------|------------------|------------|-----------|---------|-----|----------|

| Kei.      | Topology                    | FICESS   | (GHz) | Gain             | $OI_{1dB}$ | (dBm)     | PAE (%) | (V) | $(mm^2)$ |

| [25] 2008 | 3-stage                     | 65nm     | 62    | 4.5              | 6          | 9         | 8.5     | 1   | N/A      |

| RFIC      | CS                          | CMOS     | 02    | 4.3              | 0          | 9         | 8.3     | 1   | IN/A     |

| [12] 2009 | 3-stage                     | 65nm     | 57-64 | 15.8             | 2.5        | 11.5      | 11      | 1   | 0.05 🔆   |

| ISSCC     | CS (diff.)                  | CMOS     | 57-04 | 13.8             | 2.3        | 11.5      | (58 G)  | 1   | 0.03 %   |

| [26] 2010 | 4-stage                     | 65nm     | 58    | 13.4             | 12.2       | 13.8      | 7.6     | 1.2 | 1.28     |

| SIRF      | CS                          | CMOS     | 30    | 19.4             | 12.2       | 15.0      | 7.0     | 1.2 | 1.20     |

| [27] 2010 | 4-stage                     | 65nm     | 60    | 19.2             | -15.1      | 17.7      | 11.1    | 1   | 0.83     |

| ISSCC     | CS                          | CMOS     | 000   | 1.2              | Sec. 19    | -G.       | 11.1    | 1   | 0.05     |

| [29] 2010 | 3-stage                     | 65nm     | 62    | 15.5             | 4          | 11.5      | 15.2    | 1   | 0.05 🔆   |

| JSSCC     | CS (diff.)                  | CMOS     | 02    | 15.5             |            |           | 13.2    | 1   | 0.03 /•  |

| [32] 2010 | 2-stage                     | 65nm SOI | 60    | 16               | 12.7       | 14.5      | 25.7    | 1.8 | 0.04 🔆   |

| JSSCC     | Cascode                     | CMOS     | 00    | 10               | 12.7       | 14.5      | 23.1    | 1.0 | 0.047    |

|           |                             |          | 60    | 16               | 7.6        | 12        | 12.3    | 1.8 | 0.018 💥  |

| [31] 2009 | 2-stage                     | 45nm     | 00    | 1                |            | 12        | 12.5    | 1.0 | 0.010/•  |

| CSICS     | Cascode                     | CMOS     | 60    | 17               | 8.7        | 413.5     | 13.4    | 2.1 | 0.018 🔆  |

|           |                             | G        | (D)   |                  | 9.7        | AN AN     | 19.1    | 2.1 | 0.010/•  |

| [11] 2009 | 2-stage                     | 45nm LP  | 50-67 | ₹ <sub>6</sub> * | 學11        | 13.8      | 7       | 1.1 | 0.06 🔆   |

| ISSCC     | CS                          | CMOS     | 30-07 | 10701            | OTOIPIL    | 15.0      |         | 1.1 | 0.00/•\  |

| [30] 2010 | 3-stage                     | 45nm     | 60    | 20               | 11.2       | 14.5      | 14.4    | 2   | 0.04 🔆   |

| RFIC      | Cascode                     | CMOS     | 00    | 20               | 11.2       | 14.3      | 14.4    | Δ   | 0.04%    |

|           | DC/RE pads are not included |          |       |                  |            |           |         |     |          |

Table 1.3 V-band power amplifiers on 65-nm and 45-nm CMOS process.

\*DC/RF pads are not included

## 1.3 Contributions

This dissertation presents the research on the pre-distortion linearization technique for power amplifier in V-band using silicon-based 90-nm LP CMOS process. A modification to conventional cold-FET linearizer is proposed. The modification is to connect gate and drain of conventional linearizer together with a delay line with certain phase delay. The modification highly improved the pre-distortion function, and helps the linearizer to be transplanted to CMOS process from pHEMT process. An attempt of large signal analysis is performed in the investigation of possible effects resulted from the modification. Large signal analysis provides another path to understand the larger signal operation of non-linear device. Based on large signal analysis, we found the cause of three extra effects. The analysis also helps us to choose the proper phase delay, making a compromise between performance and chip size.

The stronger pre-distortion function of modified linearizer can hence be performed in high frequency on 90-nm LP CMOS process. We then try to verify its effectiveness by equipping it on two-stage power amplifier in V-band. Even under the disadvantages of CMOS process and the frequency we want to apply is a higher frequency that is more challenged, the great performance of modified linearizer can still help the power amplifier to have a better power performance. The design flow of inserting a pre-distortion linearizer to a multi-stage power amplifier is introduced. The design flow can ensure an effective design process and good performance. We also develop a device selection process for linearizer that can help us with choosing a most suitable linearizer for certain power amplifier.

The measurement result demonstrates a great power performance. It can provide  $P_{sat}$  of 15.4 dBm and  $OP_{1dB}$  of 13.7 dBm with an acceptable gain of more than 15 dB. It also has peak PAE value of 16% and 14% at  $OP_{1dB}$ . To our best knowledge, it is the CMOS power amplifier that has highest PAE at  $OP_{1dB}$  in V-band. Besides its good linearity, the power amplifier can also provide comparable peak PAE and saturation power to other power amplifiers using better technologies. In addition, this is the first amplifier that applies the pre-distortion linearizer under CMOS process in V-band.

### **1.4 Dissertation Organization**

The organization of this dissertation is outlined as follows:

Chapter 2 provides an overview of the important parameters and linearity issue of power amplifier. The introduction of important parameters helps us to understand the trade-off between several figure-of-merits.

Chapter 3 discusses a per-distortion linearization technique and introduces a low loss build-in linearizer based on HEMT process [6]. The operation principle is investigated. Based on the investigation, we propose a modification to the linearizer and give an intuitive explanation of its effectiveness. After a carefully examination, we find that there are three effects resulted from the modification. Examinations of the effects provide an instruction of selecting proper parameter of modification.

Chapter 4 presents the implementation process of a two-stage power amplifier with modified linearizer. Practical design process is provided and a bias optimization method of linearizer for specific power amplifier is proposed. A two-stage power amplifier is fabricated and measured to certify the effectiveness of linearizer. We then debug the negligence of simulation to make the measurement and simulation result to be similar.

The conclusions are drawn in Chapter 5.

# Chapter 2 Linearity of MMW Power Amplifier

The chapter introduces the important component in transceiver system, called power amplifier. Important parameters and brief design flow will be introduced in the first section. However, since the objective of this literature is to improve the linearity of power amplifier, the resources of non-linear effect would be investigated.

Several linearization techniques have been developed to enhance the linearity of power amplifier and overcome the critical demand of linearity in communication system using complex digital modulation schemes. These linearization techniques including feedback, feed-forward, pre-distortion and post-distortion are introduced.

# 2.1 Introduction of Power Amplifier

### 2.1.1 Introduction

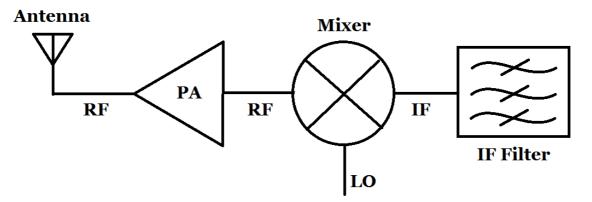

Power amplifier is one of the most challenged and important building blocks in RF communication system. As shown in Fig. 2.1, power amplifier is usually placed in the end of the active part of communication system. Therefore, it acts as the component that should provide largest output power, which should large enough overcome the loss of antenna and the free space.

Fig. 2.1 Simplified building blocks of conventional communication system.

### 2.1.2 Important Parameters

Important design parameters of power amplifier include output power, gain, linearity, and power added efficiency (PAE). We should notice that the input power under which the parameters are described is important. Taking output power for example, the description of output power includes the output power at 1-dB-compression point and saturation output power, which are the output power described under different phenomena.

Moreover, the premise of the above mentioned parameters is to have a stable power amplifier. Therefore, we should ensure the power amplifier is stable. However, once the amplifier is stable, we don't have to pay much attention on it. Followings are the introduction of the parameters.

#### A. Output power

Needless to say, the main objective of power amplifier is to provide enough output power that can transmit RF signal to the distance we want and can overcome the loss introduced by free space and antenna. For the basic understanding, if we can use the device that is large enough and equipped with a good output matching network, we can provide no matter how much output power we want. The highest output power level that a power amplifier can provide is called the saturation output power ( $P_{sat}$ ). The parameter can help us to measure the potential ability of the devices we use and also take the loss of output matching network into account.

However, power amplifier would encounter some non-ideal effect as the output power is getting larger. Those effects would make the gain of power amplifier to be reduced and the amplifier would have no gain at the largest output power. As a result, although it can provide high output power, we have to apply equal input power level to the PA, which means the power amplifier is nuisance of communication system. In order to consider linearity and output power level simultaneously, we would consider the output power at which the gain has an 1-dB-compression. We call it 1-dB-compression output power ( $OP_{1dB}$ ). In some cases, we would also consider the input power at which the output power is at  $OP_{1dB}$ . We call it input 1-dB-compression point ( $IP_{1dB}$ ). The two parameters has the benefits of define the largest output power that power amplifier still have linear gain when considering the linearity issue of power amplifier.

#### **B.** Linearity

The linearity consideration includes the parameters like AM-AM distortion, IP3, IMD3, ACPR and EVM. They can be roughly categorized as the non-linearity resulted from one-tone, two-tone and n-tone input signal. The first parameter is under the first category. The second one and the third one are under the second category while the last two parameters are under the third category. The definition and the cause of the parameters will be introduced in next section.

#### C. Power-added-efficiency

The efficiency is the most suitable parameter to measure the trade-off between DC-consumption and output power level. There two methods for calculating the efficiency of power amplifier. The first one is called drain efficiency while another one called power-added efficiency, which are defined respectively as

$$\eta = \frac{P_{out}}{P_{DC}} \tag{2.1}$$

and

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}}.$$

(2.2)

, where  $P_{out}$ ,  $P_{in}$ ,  $P_{DC}$  are output power, input power and DC consumption respectively.

The difference between the two definitions is the consideration of input power. The definition of drain efficiency only focuses on the ratio of transform dc power to output power. If the power amplifier has no gain but has large output power, we can still have high drain efficiency. This means the definition cannot honestly reflect the practicability of power amplifier. It only focuses on the ratio of signal current swing to dc current at output port of power amplifier.

On the other hand, power added efficiency calculates the ratio of the extra-added power to the dc consumption. The definition considers the amount of extra power the power amplifier can add on the input power. This perspective can rule out the possibility that the power amplifier has no gain and consider the signal power that power amplifier can contributes to whole communication system. The larger the PAE, more RF power is transformed from the dc power.

## 2.2 Linearity Consideration of Power Amplifier

### 2.2.1 Nonlinear Distortion Characterization

We usually approximate the characteristic of power amplifier to with a linear model when the amplitude of signal is small comparing to the dc value. However, when the amplitude is comparable to the dc value, the linear model is not suitable because the operation point on which the linear model depends on has been changed.

For consideration of linearity issue, we can use polynomial equation to describe the non-linear characteristic. Since the order more of three usually has small influence to the linearity issue, we would use the third order approximation, which is formulated as

$$y(t) \approx k_1 \cdot x(t) + k_2 \cdot x^2(t) + k_3 \cdot x^3(t)$$

(2.3)

, where  $k_i$  represents the coefficient for order i.

#### 2.2.2 AM-AM Characteristic

When a sinusoidal signal, which is

$$x(t) = A\cos\omega t \tag{2.4}$$

, is fed to the input of power amplifier, the output signal will be

$$y(t) = k_1 A \cos \omega t + k_2 A^2 \cos^2 \omega t + k_3 A^3 \cos^3 \omega t .$$

(2.5)

Rewrite the equation and organize it according to its frequency, we can have

$$y(t) = \frac{k_2 A^2}{2} + \left(k_1 A + \frac{3k_3 A^3}{4}\right) \cos \omega t + \frac{k_2 A^2}{2} \cos 2\omega t + \frac{3k_3 A^3}{4} \cos 3\omega t .$$

(2.6)

The coefficient in equation (2.6) that is combined with the  $\cos \omega t$  is the fundamental term of output signal. Other coefficients combined with other higher frequency signals  $\cos n\omega t$  are the amplitudes of *n*th-order harmonics.

Divide the coefficient of fundamental term of output signal by that of input signal is the value of fundamental gain, which can be represented as

$$Gain = \frac{\text{Output Fundamental}}{\text{Input Fundamental}} = \frac{\left(\frac{k_1 A + \frac{3k_3 A}{4}}{A}\right)}{A} = k_1 + \frac{3k_3 A^2}{4}$$

(2.7)

The numerator has a term proportioning to  $A^3$ , which would have a relatively small value when A is small. Therefore, the gain would be a constant value at small input power, which is called linear gain. However, as the input signal with larger amplitude is fed, the term can hardly be neglected. Since the coefficient  $k_3$  always has a negative value, the value of gain will be reduced and results in a compression of it.

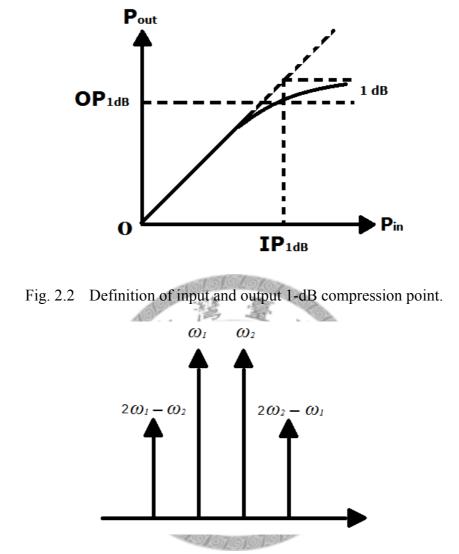

For description convenience, we define the output power at which the gain has been reduced by 1dB as 1-dB compression output power ( $OP_{1dB}$ ). The corresponding input power is called 1-dB compression input power ( $IP_{1dB}$ ). As shown in Fig. 2.2, when the output power has departed from the expected output power by 1 dB, the output power there is the  $OP_{1dB}$ .

Fig. 2.3 Spectrum around fundamental tone after intermodulation.

### 2.2.3 Nonlinearity from two-tone input signal

Instead of feed the signal with single frequency to power amplifier, feeding two signals with slightly different frequencies can produce some mixing products called intermodulation (IM). The signal with two different frequencies but equal amplitude is

$$x(t) = A\cos(\omega_{1}t) + A\cos(\omega_{2}t).$$

(2.8)

Apply the signal to equation (2.3) and expand the result according to different frequencies can have the spectrum with signals of different frequencies including  $\omega_1$ ,  $\omega_2$ ,  $2\omega_1$ ,  $2\omega_2$ ,  $\omega_1 \pm \omega_2$ ,  $2\omega_1 \pm \omega_2$ ,  $2\omega_2 \pm \omega_1$ ,  $3\omega_1$ ,  $3\omega_2$ . However the frequency that influences

the fundamental tone  $\omega_1$  and  $\omega_2$  most, are the signals with frequency  $2\omega_1 \pm \omega_2$ ,  $2\omega_2 \pm \omega_1$ . The spectrum around fundamental tone is shown in Fig. 2.3. The value of fundamental tone  $\omega_1$  and  $\omega_2$  is

$$k_1 A + \frac{9}{4} k_3 A^3 \tag{2.9}$$

, and the value of harmonics  $2\omega_1 \pm \omega_2$  and  $2\omega_2 \pm \omega_1$  is

$$\frac{3}{4}k_3A^3$$

. (2.10)

#### A. Third –order intermodulation ratio

The third-order intermodulation ratio (IMD3) is defined as the ratio of the amplitude of the third-order term of output signal to the linear fundamental term, which is

$$IMD3 = \frac{P_{fundamental}}{P_{IMD}} = \frac{P(\omega_1, \omega_2)}{P(2\omega_1 - \omega_2, 2\omega_2 - \omega_1)} = \frac{k_1 A}{\frac{3}{4}k_3 A^3} = \frac{4k_1}{3k_3 A^3}$$

(2.11)

The value can be calculated under different power level. For different power level, there is a corresponding IMD3. Specification of some communication standard would require the output power level to be measured under the IMD3 that is more than certain value.

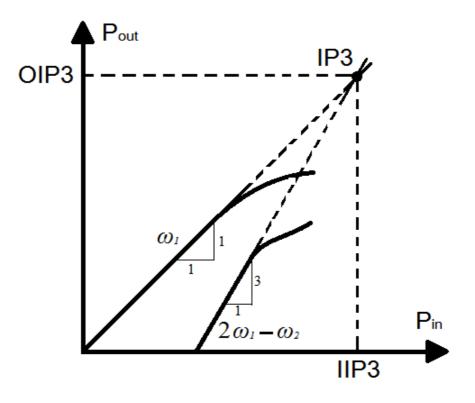

#### **B.** Third-order intercept point (IP3)

Unlike IMD3, IP3 is a certain point that the value of third-order harmonics is the same to value of fundamental. The equation is given by

$$|k_1|A_{IP3} = \frac{3}{4}|k_3|A_{IP3}^3.$$

(2.12)

When we refer the IP3 to input power and output power, it is called IIP3 and OIP3 and formulated as

$$IIP3 = A_{IP3} = \sqrt{\frac{3}{4} \left| \frac{k_1}{k_3} \right|}$$

(2.13)

and

$$OIP3 = k_1 A_{IP3} = \sqrt{\frac{3}{4} \left| \frac{k_1^3}{k_3} \right|}$$

(2.14)

,respectively.

If we draw the power of fundamental term and harmonic versus input power level respectively, the interception of the two curves is IP3, as shown in Fig. 2.4.

Fig. 2.4 Definition of third-order interception point.

# **Chapter 3** Cold-FET Linearizer with Delay Line

The objective of this chapter is to propose a modified low-loss build-in cold-FET linearizer for millimeter-wave CMOS power amplifier. Since the conductive substrate and severe parasitic effects of CMOS process will severely degrade the performance of conventional cold-FET linearizer in V-band, the modification is developed to overcome the difficulties.

Based on the modification, we successfully enhance the performance of the cold-FET linearizer and simultaneously maintain a low insertion loss even under the conductive substrate of CMOS process. To the best of our knowledge, this is the first demonstration of the pre-distortion technique to CMOS power amplifier for V-band.

The chapter first explains some general consideration of a pre-distortion linearizer, including the operation details, design criteria and the method to choose a proper linearizer for a specific power amplifier. Secondly, the operation details of the cold-mode linearizer will be introduced. The key point of exhibiting pre-distortion function is the saturation region of transistor. There are several difficulties to implement the conventional pre-distortion linearizer in CMOS technology for millimeter-wave frequencies.

In order to solve the difficulties, a modification to the cold-mode linearizer is proposed and gives an intuitive interpretation to its benefit. However, the modification has additional effects that need to be considered more carefully. Two major effects are assumed and described in detail. Mathematic equations are developed to find out the cause of the effects by observing the operation of the modified linearizer. Finally, more guide lines are proposed for choosing parameters of modified linearizer.

## 3.1 **Pre-distortion Linearizer**

This section will introduce the operation of the pre-distortion linearizer for a amplifier. Moreover, some important points about power performance curve of linearizer should be considered. Observing those points can help us to identity the performance of pre-distortion linearizer and to know whether the linearizer is suitable for a specific power amplifier. Finally, the method to place the linearizer on the best point of a multi-stage power amplifier will also be discussed.

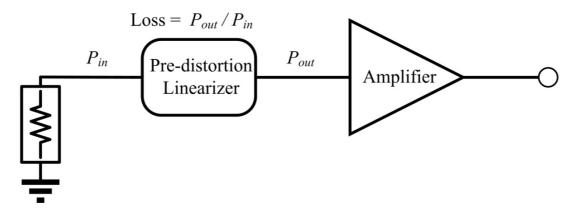

Fig. 3.1 Pre-distortion effect by cascading power amplifier with a linearizer.

### 3.1.1 Pre-distortion Technique

The principle of pre-distortion linearization technique is shown in Fig. 3.1. The power amplifier usually suffers from gain compression at high power level, which results in signal distortion. On the other hand, the pre-distortion linearizer has a constant loss at low input power level and has lower loss when input power level is high. After combining the two different tendencies of gain characteristic by cascading the two building blocks, we can have a power amplifier with larger linear output power region, which called gain extension.

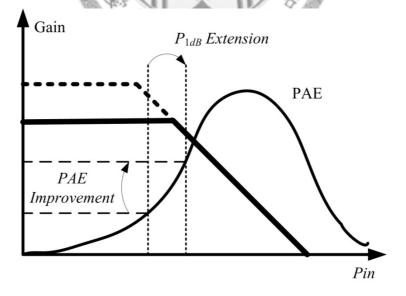

Fig. 3.2 shows the comparison of the power performance of a power amplifier with and without pre-distortion linearization technique. The pre-distortion effect can postpone the gain compression point. Since the PAE increases more rapidly around 1-dB compression point, PAE at 1-dB compression point can be improved significantly. With the higher PAE, the power amplifier can have a higher output power under the same DC consumption.

Fig. 3.2 Gain characteristics of power amplifier with and without pre-distortion technique.

### 3.1.2 Loss Characteristic of Pre-Distortion Linearizer

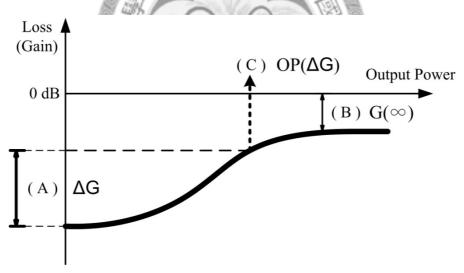

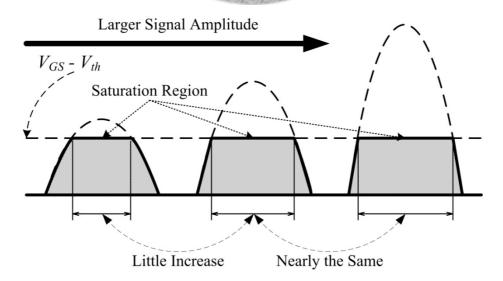

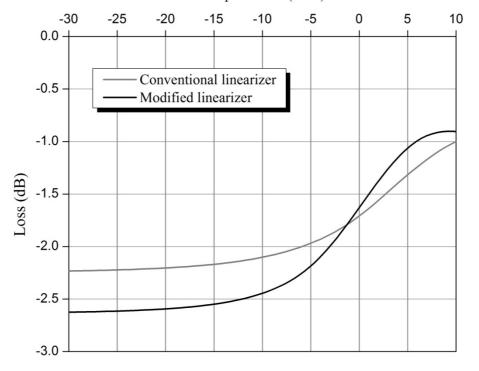

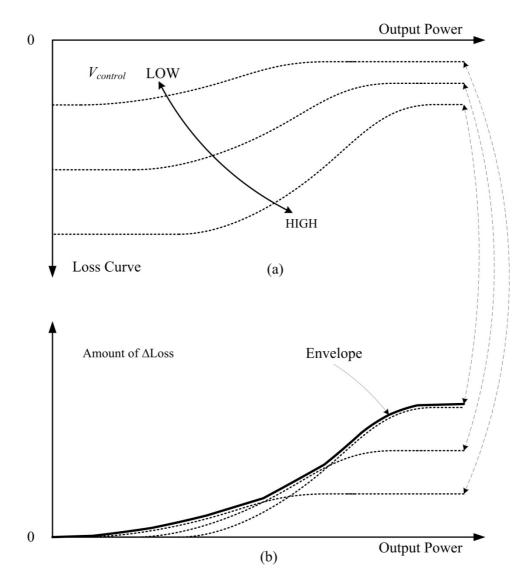

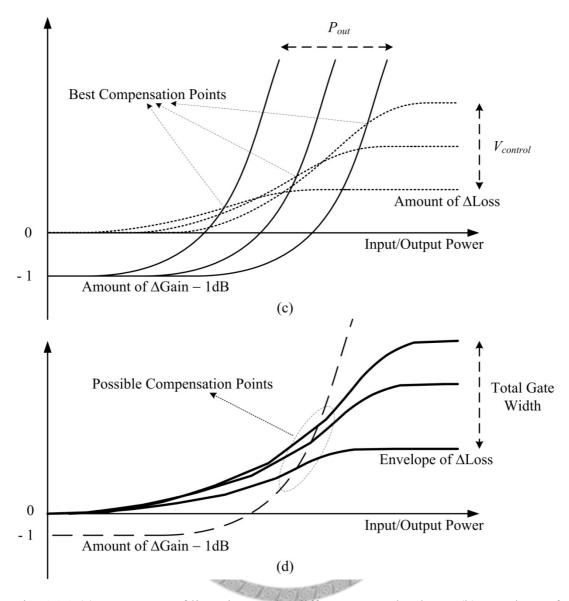

Different power amplifiers have different power performances. Therefore, it is impossible for a linearizer to be suitable for every power amplifier. Since the objective of a pre-distortion linearizer is to improve the power performance of power amplifier, we have to investigate the power performance of linearizer. The loss deviation of linearizer is the resource of pre-distortion effect. We should observe on the loss characteristic curve of linearizer.

Fig. 3.3 shows the loss versus the output power of a pre-distortion linearizer. The reason to define output power as x-axis will be introduced in following section. We should focus on three features which can be used to define the performance and specifications of a pre-distortion linearizer.

Fig. 3.3 Loss characteristic of a linearizer

#### A. Larger gain (loss) deviation:

A larger gain (loss) deviation can compensate more gain compression of a power amplifier. It means we can have stronger gain extension effect and make the power amplifier reach a higher  $OP_{1dB}$  and PAE. On the other hand, since the loss at high power level is decided by intrinsic factor, which cannot be changed by choosing device size or control voltage, the small-signal loss is the high power loss minus loss deviation. Therefore, we should consider whether the gain of power amplifier is larger enough, and check whether the small signal loss is a burden to the link budget. The severe small-signal loss may need to be compensated by an extra gain stage, and degrade the PAE. Moreover, even though the loss deviation is large enough, the slope of loss deviation should not be too high. It is because the slope of loss deviation which is higher than that of the gain compression of power amplifier will result in a composite power performance curve that is not flat.

#### **B.** Lower loss at high input power level:

The application of pre-distortion linearizer will definitely introduce extra loss. The loss is an inevitable disadvantage when we want the loss characteristic of pre-distortion linearizer. Ideally, the loss of linearizer should be zero at the power level at which the cascaded power amplifier reaches its  $OP_{1dB}$ . However, because of the intrinsic operation process of linearizer, there must left some power loss at the high power level. Since the key object of introducing linearizer is to improve the linearity and make the value of  $OP_{1dB}$  higher, the loss at the high power level would reversely damage the goal. We can regard the phenomena as the loss of linearizer overwhelms the improvement of output power.

#### C. Low output power with enough gain (loss) deviation:

Since the linearizer is directly cascaded with a power amplifier, alike the link budget consideration of cascade multi-stage power amplifier, the output power of the linearizer should be at some adequate value that can support the operation of power amplifier. When the oscillation ability of a device is weak, linearizer can only reach enough loss deviation value at a high output power level. In this condition, the linearizer is only suitable for a large power amplifier. In addition, the amount of power consumed by it will be relatively large.

In another condition that the linearizer can reach enough loss deviation at low power level, it can be suitable for a small power amplifier. If the size of power amplifier is larger, we can parallel several devices together to form a large linearizer which can provide enough power for power amplifier. For another solution, we can add another stage in front of power amplifier and put the linearizer at a low power level point.

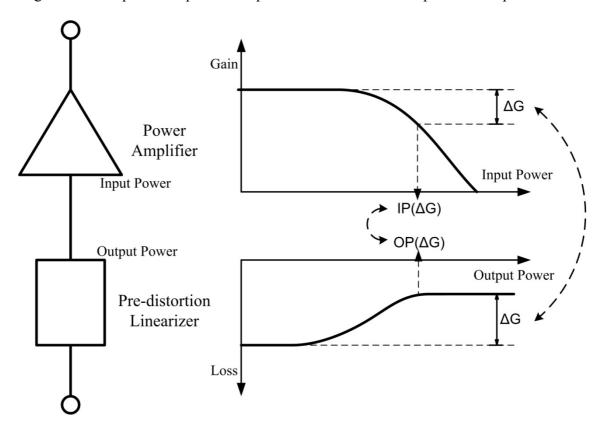

Fig. 3.4 Consideration of cascading a linearizer with a power amplifier.

#### 3.1.3 Cascading with Power Amplifier

The influence of output power range of linearizer when cascading with a power amplifier has been discussed before. Here we will illustrate the guide line to cascade the two building blocks. There are two set of values of pre-distortion linearizer and power amplifier that should be the same simultaneously. The first set is the output power value of linearizer and input power value of power amplifier, and the second set is the loss deviation value of linearizer and gain compression value of power amplifier. Fig. 3.4 clearly tells us the concept. The output power of pre-distortion linearizer when having enough loss deviation should be equal to the input power of power amplifier when have the same amount of gain compression.

Fig. 3.5 Composite power performance for that the output power level of linearizer is (a) lower than (b) higher than, and (c) equal to the input power of power amplifier at 1-dB compression point.

Fig. 3.5 shows characteristics of the composite power performance for that for that the output power of linearizer is higher than, lower than and equal to the input power of the power amplifier at 1-dB compression point. At Fig. 3.5 (a), the early rising of loss deviation makes the composite power performance has a convex around the gain compression point. The uneven curve has an improvement of  $IP_{1dB}$  when calculating the 1-dB compression point according to small-signal gain. However, some people will calculate it according to the peak gain value. This makes the point of  $OP_{1dB}$  unchanged.

On the other hand, as shown in Fig. 3.5 (b), if output power of linearizer is high, the linearizer provides enough loss deviation too late, hence has nothing benefit to power amplifier. The predicted gain extension effect would not happen. Finally, Fig. 3.5 (c) shows the adequate output power level of linearizer. When we want to improve the power performance of a specific power amplifier, we therefore should choose the linearizer that has the loss characteristic curve perfectly match to the gain curve of power amplifier.

Fig. 3.6 Former proposed cold-FET linearizer [6].

# **3.2 Cold FET Linearizer**

#### 3.2.1 Introduction

In order to achieve the function of pre-distortion, we need to find a device that has a constant loss for low input power and a lower loss for higher input power. A MMIC low-loss built-in linearizer that has pre-distortion characteristic has been demonstrated by GaAs pHEMT, which is a parallel transistor operated in cold-mode [6]. The cold-mode means the transistor has zero drain-to-source voltage ( $V_d = V_{bias}$ ), thus it requires zero dc consumption. The structure is shown in Fig. 3.6.

At large-signal operation, the cold-mode FET has gain expansion characteristic which can compensate gain compression of the power amplifier. In addition, since the gate bias of transistor exceeds the threshold voltage ( $V_{th}$ ), the drain and source voltages are likely to be equal. Therefore, the bias voltage of the following cascaded amplifier can be fed directly through the linearizer. No additional bias circuit for next stage amplifier is needed.

# 3.2.2 Operation Principle

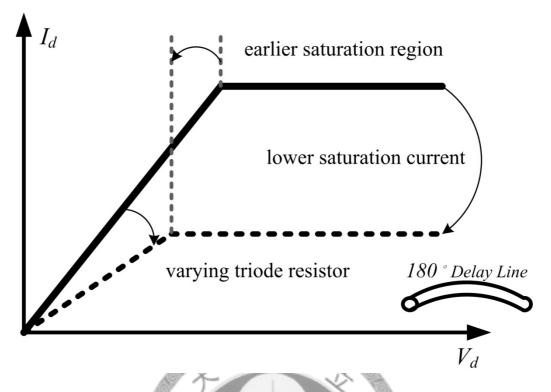

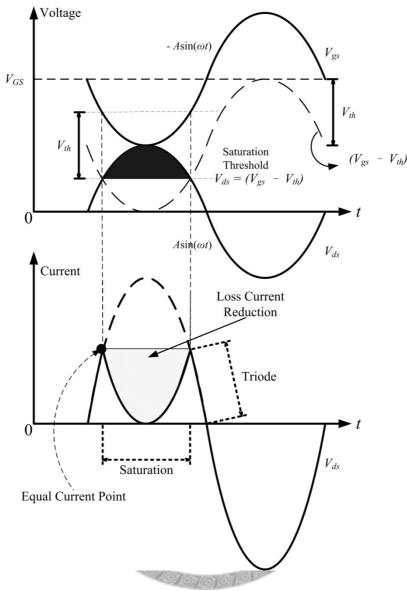

Thick line of Fig. 3.7 is the DC-IV curve of a transistor biased under some specific gate voltage. The bias point of a transistor biased under zero drain-to-source voltage condition is the point at the origin of Fig. 3.7. Considering the different characteristics between the triode region and the saturation region on the curve can help us to understand the operation of cold-FET linearizer.

When the swing of signal voltage is small, the operation of the parallel transistor biased under cold-mode can be modeled as a resistor whose value is defined by its gate voltage. The value of the resistor value is

$$R_{ds} = \frac{1}{k \times (V_{GS} - V_{th})} \tag{3.1}$$

Since the gate voltage  $V_{GS}$  remains unchanged when input voltage signal is swinging, the drain resistor  $R_{ds}$  is always a constant value. Therefore, the amount of signal current flowing into the transistor will vary along a constant slope DC-IV curve at triode and deep-triode region, and exhibit a constant loss.

However, since the drain current of transistor is unlikely to change with drain voltage when transistor operates in saturation region, current flowing into linearizer will not getting larger when input voltage swing over the saturation region. The voltage threshold for transistor to enter saturation region is

$$V_{ds} > V_{gs} - V_{th} \tag{3.2}$$

Based on the characteristic, the loss will become smaller when the input power level is high enough. It is because once the voltage value of the swing exceeds the saturation threshold, the linearizer cannot force more signal current to flow into it. Therefore, the cut-off part of current swing will occupy a larger ratio when the voltage swing at drain is getting larger. That means it will have smaller ratio of leakage current and exhibit smaller loss. We can call it cut-off effect, which is shown as the black part at the top of drain current swing in Fig. 3.7.

In conclusion, the saturation region provides a lower loss in high input power level while the triode region provides constant loss in low input power level. Since the cold-mode linearizer has a characteristic that meets the requirement of pre-distortion, it can help the power amplifier to have a larger linear output power region and a higher PAE at  $OP_{1dB}$ .

Moreover, since DC-IV curve of the transistor is asymmetry for positive and negative drain-to-source voltages, only positive voltage swing can really cause the gain extension effect when the transistor enter saturation region. Negative voltage swing can only force transistor to operate under deep-triode region, and provides a constant loss because of its similar slope comparing to operation under triode region.

## 3.2.3 Challenge of CMOS Process in V-band

The formerly introduced cold-mode linearizer was implemented on GaAs pHEMT technology has superior performance due to the higher electron mobility, higher breakdown voltage, and the availability of high quality-factor passive components.

On the other hand, the CMOS technology is one of the most important and widely used processes today. It has advantages like small size, repeatability, productivity and high-level integration. Since the size and cost are important design issue, modern CMOS technology is really attractive for MMW applications. If we want to make the pre-distortion technique more applicable, to transplant the conventional linearizer from III-V technology to CMOS technology is a possible solution.

However, although CMOS technology has already widely used in several area, they are just applications in lower frequency, in which the performance of CMOS is good enough to meet the specifications. If we want to simultaneously take advantages of CMOS technology and maintain acceptable performance, followings are some issues we would encounter when trying to transplant the cold-mode linearizer concept from pHEMT technology to CMOS technology.

#### A. High loss of conductive substrate

The CMOS technology is fabricated on a conductive substrate. Comparing with the semi-insulating substrate of III-V technology, the lossy substrate of CMOS is really a hardship for a same design to have similar performance. For example, the loss of linearizer at high input power level is one of design criteria of linearizer, as the second criteria shown in Fig. 3.3. The lower loss, the higher loss deviation can be accomplished. The loss substrate will damage the performance of linearizer.

#### **B.** Low maximum oscillation frequency fmax

The CMOS technology has lower electron mobility than III-V technology, and hence has lower fmax. This means the oscillation ability at high frequency like V-band is weaker and also not good enough for the voltage swing to follow the expected curve of Fig. 3.7. The cut off function which make the loss deviation to be accomplished will also be not obvious.

#### C. Severe parasitic effect

V-band is a millimeter-wave frequency that the fatal parasitic effect is relatively severe. The severe parasitic effect in V-band can highly detract the performance of linearizer because extra losses would overwhelm advantages introduced by linearizer and results in fewer output power and lower PAE.

All the above mentioned difficulties are the intrinsic problems that cannot be overcome by device selection or other design flow. We should otherwise try to improve the effectiveness of gain extension characteristic, which can be achieved by enhance the loss deviation ability and make the loss begin to decrease earlier. For the above mentioned purpose, a modification of cold-FET linearizer that can ensure the gain extension function is introduced in next section.

# 3.3 Modified Cold-Mode Linearizer Using Delay Line

In this section, we will propose the criteria for examining the performance of pre-distortion linearizer and provide the guide line to develop a modification that can effectively improve the performance of cold-mode linearizer. According to the guide line, we choose delay line as the solution and provide an intuitive interpretation to its benefit. However, we notice that the modification has extra benefit that can improve the pre-distortion function. Therefore, the mathematic equations of both advantages are formulated and their composite effect is analyzed. Finally, the figure that can best demonstrate performance of a linearizer is introduced. We will compare the conventional and modified linearizers by using the figure and hence verify the effectiveness of the proposed modified linearizer.

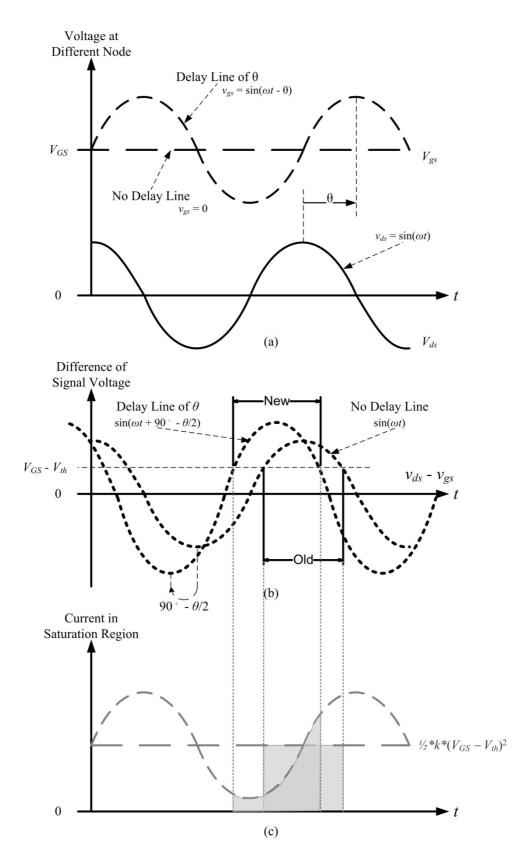

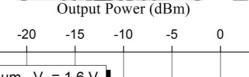

## 3.3.1 Guideline to Develop a Modified Linearizer

The modification for the linearizer is based on the knowledge that if the transistor is more likely to reach saturation region while input signal is getting larger, it can have a sharper gain deviation slope and earlier up-rising curve, hence more effectively compensates the gain compression slope of power amplifier. The condition that transistor should satisfy at saturation region has been shown at equation (3.2).

The conventional linearizer only utilizes drain-to-source voltage  $V_{ds}$  to force the transistor into saturation region [6]. However, as we can see in the equation (3.2), the gate-to-source voltage  $V_{gs}$  is also effective to force the transistor into saturation region. We can rewrite equation (3.2) as

$$V_{ds} - V_{gs} > -V_{th} \,. \tag{3.3}$$

If we want the saturation region to be reached earlier, we can otherwise increase the term faster while the power level is getting higher. Therefore, the linearizer will have a sharper loss characteristic and reach enough gain deviation at lower power level.

# 3.3.2 Modified Cold-Mode Linearizer

Based on the guideline, a pre-distortion linearizer with an effective modification is proposed. Fig. 3.8 shows the schematic of the modified linearizer. The proposed linearizer is modified by adding an extra delay line connecting drain and gate of the core transistor. The delay line can provide a phase delay of  $\theta$ , and produce a voltage signal swing at gate, unlike the signal ground of conventional linearizer at gate. Comparing with Fig. 3.6, the modified linearizer does not need extra passive component except the delay line. We can consider the modification as a trade-off between performance and chip size.

Fig. 3.9 The saturation condition of transistor of linearizer when the gate an drain are connected by (a) no delay line, and (b) a 180 degree delay line.

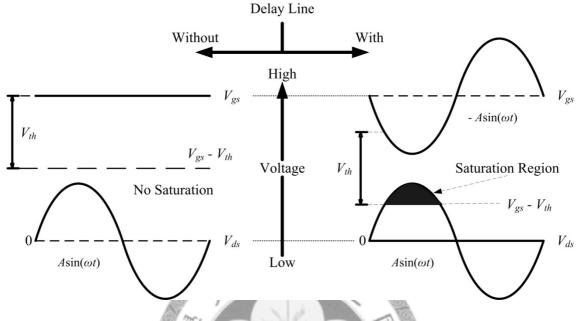

If the delay line provides a 180 degree phase delay, it can produce out-of-phase signals at the drain and the gate of the linearizer. The term  $(V_{ds} - V_{gs})$  will therefore be increased twice faster than that of conventional linearizer, and make the saturation condition equation (3.3) be satisfied earlier. In addition, even when the delay line cannot produce a 180 degree signal, the term can still change faster than no delay line.

# 3.3.3 Intuitive Interpretation of the Modification

Fig. 3.10 can provide us an explanation to the effect of extra delay line. The solid line in the figure is the voltage swing at drain while the dash line represents the voltage swing at gate. The vector pointing upward means drain-to-gate voltage  $(V_{ds} - V_{gs})$  is getting larger, hence easier to enter the saturation region. On the other hand, a circle or a vector pointing downward means  $(V_{ds} - V_{gs})$  remains unchanged or getting lower, which keep the linearizer remaining in triode region or being forced into deep triode region. Followings are the discussion of the operation when a 180 degree delay lines is applied or not.

## A. No delay line

It is a normal cold-FET linearizer which has no signal at gate of linearizer. Since only the vector pointing upward can enter the saturation region, we can observe from the figure that only half period of time has the possibility to enter saturation region.

#### B. 180 degree delay line

The gate voltage signal will have a negative swing while positive signal swing appears at drain. Since the voltage difference between drain and gate will therefore be twice, the transistor will be more likely to enter saturation region. Moreover, it would have an earlier loss deviation. In terms of the loss characteristic, it can produce earlier rising loss curve than no delay added, which means a lower output power for loss deviation is needed.

We should notice that the delay line can also produce extra negative drain-to-gate voltage period. However, the linearizer will still in triode region when suffering a negative drain-to-gate voltage, and having similar loss as in normal triode region. Therefore, the phenomena will not damage the effect of loss deviation. The linearizer can still be better because it can enter saturation region easier.

# **3.4** Operation Detail of Modified Linearizer

# 3.4.1 Analysis of Possible Effects during Operation

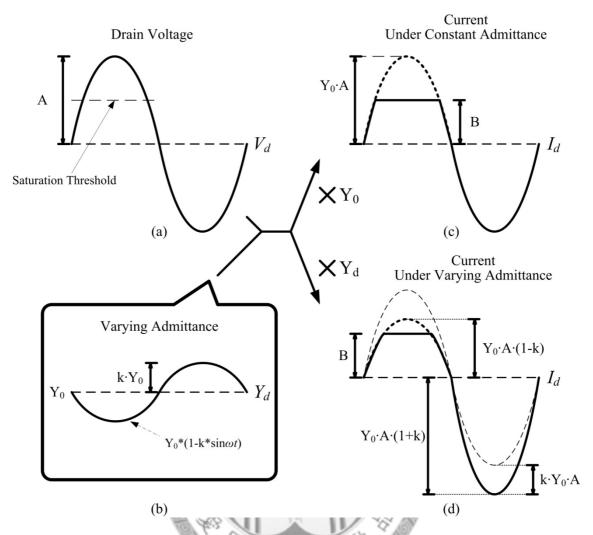

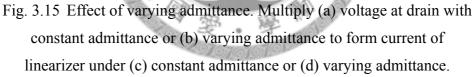

In order to give a systematic analysis of the proposed linearizer, we should investigate the large signal operation of the modified linearizer, and focus on the influence of the delay line to the power flowing into linearizer. The method of investigating the effect is based on comparing the amount of power produced by the both linearizer when a voltage signal swing is at drain. The power flowing into the linearizer can be formulated as

$$P_{loss} = I_d \times V_d \tag{3.4}$$

The drain voltage  $V_d$  is a sinusoidal wave. It is the same for linearizer with and without delay line. However, the current flowing into the linearizer is different in both conditions. Therefore, the comparison of power loss can be simplifies as comparison of the current flowing into linearizer with and without delay line.

Fig. 3.10 Large signal operation of cold-FET linearizer with delay line.

Fig. 3.10 illustrates the change of DC-IV curve when the gate of transistor has an adversely swinging signal, which is the result of adding a 180 degree delay line. The change of DC-IV curve is described under the up swinging of input voltage signal. Therefore, the voltage swinging at the gate is swinging downward.

There are three effects we can observe from Fig. 3.10. The first one is that the linearizer will be more likely to enter the saturation region, because the saturation region is reached simultaneously by increasing drain voltage and decreasing gate voltage. The second one is the continuously decreasing current under the saturation region. This is a major difference comparing to the unchanged drain current of the conventional linearizer without delay line, which can reduce the current flowing into the transistor instead of passively remain no increment. The third one is the varying slope of the DC-IV curve in triode region which results from the voltage swing at gate of transistor. According to equation (3.1), the value of the resistor is defined mainly by the value of gate voltage.