國立臺灣大學電機資訊學院電子工程學研究所

### 碩士論文

Graduate Institute of Electronics Engineering College of Electrical Engineering & Computer Science National Taiwan University master thesis

一個在切換頻率中利用電流平均控制來減低暫態漣波 的控制方法之直流降壓式轉換器

A Current Average Control Method for Transient-Ripple Reduction in Frequency Hopping DC-DC Converters

> 戴嘉南 Tai Jia-Nan

指導教授:陳信樹 博士

Advisor : Chen Hsin-Shu, Ph.D.

中華民國 100 年 1 月

January, 2011

# 國立臺灣大學(碩)博士學位論文 口試委員會審定書

一個在切換頻率中利用電流平均控制來減低暫態漣波 的控制方法之直流降壓式轉換器 A Current Average Control Method for Transient-Ripple Reduction in Frequency Hopping DC-DC Converters

本論文係戴嘉南(r97943143)在國立臺灣大學電子所完成之碩士 學位論文,於民國 100 年 1 月 26 日承下列考試委員審查通過及口試 及格,特此證明

口試委員:

| 3束 | イニー  | \$7寸 |    |    |

|----|------|------|----|----|

|    | (指導教 | 授)   |    |    |

| 陳怡 | ),状  | 東    | AL | Nh |

系主任、所長 張 耀 之

1

# A Current Average Control Method for **Transient-Ripple Reduction in Frequency Hopping DC-DC Converters**

By

Jia-Nan Tai

### THESIS

Submitted in partial fulfillment of the requirement for the degree of Master of Science in Electronics Engineering at National Taiwan University Taipei, Taiwan, R.O.C.

Jan. 2011

Approved by :

John

Advised by :

Approved by Director :

Harmen Chang

### 致謝

這本論文能順利完成,首先要感謝的是指導教授陳信樹博士這些日子來的指 導和照顧,老師豐富的經驗替我解決了不少研究上所遇到的問題,也教導我正確 的研究態度及獨立研究的能力,讓我的研究可以順利完成。此外,感謝陳怡然教 授及陳昭宏教授在我碩士生涯中不曾間斷的給予指導,使得我在研究之路上不致 偏離,同時也感謝以上三位教授撥冗擔任我的口試委員,他們寶貴的意見使我獲 益良多。

感謝實驗室的學長、同學、學弟們,宏維、菁華、裕翔、泓霖、偉賢、偉志、 威廷、碩宏、依峻、宏彦、邦寧、傑帆及學弟們。另外感謝逸霈、邦榮、濠瞬、 立偉、凱宇、立言、后鍾,感謝你們在研究上的幫助。

感謝大學同學博煌、國瑋、運鋼、育嘉,雖然在就讀研究所後研究領域不盡 相同,但是感謝你們在百忙之中抽空排解我的鬱悶。

碩士生涯路途漫漫,求學之外我想特別感謝一個人:郁文,在紙醉金迷的台 北,孤單地困在我編織的封閉世界中,和一隻貓咪Hiro癡癡地等著我。我希望能 像這本論文一樣,痛苦會過去,美會留下。

最後,感謝我的父母,不肖的我延長了您們的工作年限,希望我的畢業能為 家帶來些微的幫助,能讓我報答養育之恩。

### 摘要

本論文闡述一個切換頻率中利用電流平均控制來減低暫態漣波控制方法的直 流電壓轉換器,並以台積電0.35-µm 2P4M 3.3V/5V Mixed Signal CMOS製程製作。 當使用切換頻率技術時,由於電感的電流連續性,使得切換頻率前和切換頻率後 所產生的電感電流交流值不同,在輸出電容產生出一暫態漣波電壓,此論文提出 一個如何控制電感電流才能使之無此暫態漣波電壓,其方式為利用延長或縮短充 電(放電)電流的時間來達到平均電感電流,此時間為切換頻率前後充電(放電)電 感電流時間的平均值,實現方式是利用額外電路準確計算此時間後,以脈衝的型 式插入原本的脈衝調變訊號。

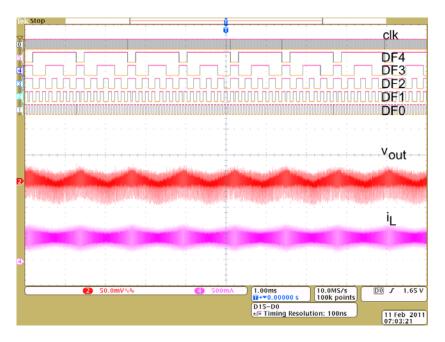

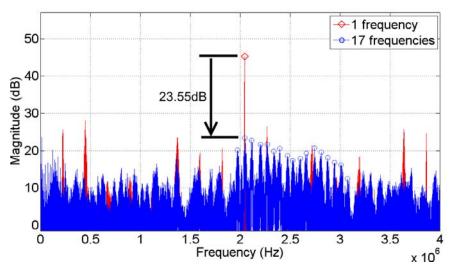

依據量測的結果,本晶片的切換頻率設定在880k-3.4MHz,暫態漣波在頻域上 改進14.1dB,時域上改進88%。跳頻技巧最多可使EMI降低23.55dB,功率效率最 高為90%。晶片總面積占2.126mm<sup>2</sup>,而其它的量測結果也包含在本論文內。

# Abstract

This thesis presents an inductor current average control method for transient-ripple reduction in frequency hopping DC-DC converters and is implemented in a standard 0.35-µm 2P4M 3.3V/5V Mixed Signal CMOS process. When using the frequency-hopping technique, there is transient ripple on the output voltage due to the difference of inductor current between two different frequencies. This thesis proposes a method which predicts the average inductor current and inserts a calculated-width pulse between two frequencies to reduce the transient ripple on the output voltage.

Measurement results are performed with the switching frequency of this chip operating between 0.88 MHz and 3.4 MHz. The transient ripple on the output voltage is reduced by 88% and the undesired spur is reduced by 14.1 dB. The frequency-hopping technique achieves 23.55 dB reduction of the EMI spur magnitude. The maximum power efficiency achieved 90%. The chip occupied 2.126 mm<sup>2</sup>, and the other detailed measurements are included in this thesis.

# **Table of Contents**

| 致謝              |                                                             | I   |

|-----------------|-------------------------------------------------------------|-----|

| 摘要              |                                                             | II  |

| Abstract        |                                                             | III |

| Table of Cont   | ents                                                        | IV  |

| List of Figures |                                                             | VI  |

| List of Tables. | •••••••••••••••••••••••••••••••••••••••                     | X   |

| Chapter 1       | Introduction                                                | 1   |

|                 | on                                                          |     |

|                 | rganization                                                 |     |

| Chapter 2       | Fundamental of DC-DC Buck Converter                         |     |

| 2.1 Performa    | ance Metrics<br>fficiency                                   |     |

| 2.1.1 E         | ficiency                                                    |     |

| 2.1.2 R         | egulation                                                   |     |

| 2               | 2.2 Load Regulation                                         | ,   |

| 2.              | 2.3 Temperature Regulation                                  | 5   |

| 2.1             | 3 Transient Response                                        |     |

| 2.2 Architec    | ture of DC-DC Converters                                    | 8   |

| 2.2.1 D         | C-DC Buck Converter Operation                               | 8   |

|                 | stimation of Output Voltage Ripple                          |     |

|                 | edback-Loop Stabilization                                   |     |

|                 | Frequency                                                   |     |

|                 | andom Switching                                             |     |

|                 | requency Hopping                                            |     |

| Chapter 3       | Proposed Architecture                                       | 23  |

| 3.1 Introduc    | tion                                                        | 23  |

|                 | tion of DC-DC Buck Converter                                |     |

| 3.3 System A    | Architecture                                                | 24  |

|                 | Current Average Control (ICAC)                              |     |

|                 | opping in Off Duty Cycle Period                             |     |

|                 | 4.1.1 Hopping frequency from low to high                    |     |

|                 | 4.1.2 Hopping frequency from high to low                    |     |

|                 | opping in On Duty Cycle Period                              |     |

|                 | 4.2.1 Hopping frequency from low to high & from high to low |     |

| Chapter 4       | Circuit Implementation and Simulation Results               |     |

| 4.1 Amplifie    | r Circuit                                                   | 35  |

| 4.1.1 E         | ror Amplifier                                               | 35  |

|                 | perational Amplifier                                        |     |

| 4.2 Compara     | tor Circuit                                                 | 40  |

| 4.3 Ramp Generator Circuit                                                | 41                                                             |

|---------------------------------------------------------------------------|----------------------------------------------------------------|

| 4.4 Digital-to-Analog Converter (DAC)                                     | 45                                                             |

| 4.5 Inductor Current Average Control (ICAC)                               |                                                                |

| 4.5.1 Sample and Hold Circuit (S&H)                                       | . 49                                                           |

| 4.5.2 Calculated Pulse Circuit                                            |                                                                |

| 4.5.3 Consideration of Delay Time                                         | 55                                                             |

| 4.6 Gate Driver with Dead Time Control                                    |                                                                |

| 4.7 Power Stage Circuit                                                   |                                                                |

| 4.8 Simulation Results                                                    |                                                                |

| 4.8.1 Frequency Hopping                                                   |                                                                |

| 4.8.1.1 Spectrum                                                          |                                                                |

| 4.8.1.2 Transient Ripple on the Output Voltage                            |                                                                |

| 4.8.2 Efficiency                                                          | . 69                                                           |

| 4.9 Performance Summary in simulation                                     |                                                                |

| Chapter 5 Experiment Results                                              | 71                                                             |

| Chapter 5 Experiment Results                                              |                                                                |

|                                                                           |                                                                |

| 5.1 Measurement Setup                                                     | . 71                                                           |

| <ul><li>5.1 Measurement Setup</li><li>5.2 Measurement Results</li></ul>   | 71<br>78                                                       |

| <ul> <li>5.1 Measurement Setup</li> <li>5.2 Measurement Results</li></ul> | 71<br>78<br>78                                                 |

| <ul> <li>5.1 Measurement Setup</li> <li>5.2 Measurement Results</li></ul> | 71<br>78<br>78                                                 |

| <ul> <li>5.1 Measurement Setup</li></ul>                                  | 71<br>78<br>78<br>78<br>79<br>79                               |

| <ul> <li>5.1 Measurement Setup</li></ul>                                  | 71<br>78<br>78<br>79<br>79<br>82                               |

| <ul> <li>5.1 Measurement Setup</li></ul>                                  | 71<br>78<br>78<br>79<br>79<br>82                               |

| <ul> <li>5.1 Measurement Setup</li></ul>                                  | 71<br>78<br>78<br>79<br>79<br>82                               |

| <ul> <li>5.1 Measurement Setup</li></ul>                                  | 71<br>78<br>78<br>79<br>79<br>82<br>88<br>90<br>92             |

| <ul> <li>5.1 Measurement Setup</li></ul>                                  | 71<br>78<br>79<br>79<br>82<br>88<br>90<br>92<br><b>93</b>      |

| <ul> <li>5.1 Measurement Setup</li></ul>                                  | 71<br>78<br>79<br>79<br>82<br>88<br>90<br>92<br>92<br>93       |

| <ul> <li>5.1 Measurement Setup</li></ul>                                  | 71<br>78<br>79<br>79<br>82<br>88<br>90<br>92<br>92<br>93<br>93 |

# **List of Figures**

## Chapter 2

| Fig. 2.1 The definition of efficiency in the switching regulator                 | 4   |

|----------------------------------------------------------------------------------|-----|

| Fig. 2.2 Circuit diagram of the switching converter                              | 7   |

| Fig. 2.3 The transient response of output voltage when a dynamic load is applied | 8   |

| Fig. 2.4 Buck converter (a) the switch in 1 (b) the switch in 2                  | 9   |

| Fig. 2.5 Steady-state output waveform $V_s(t)$                                   | 9   |

| Fig. 2.6 Output characteristic of buck converters                                | .10 |

| Fig. 2.7 (a) The diagram and waveforms of continuous mode (b) The waveforms of   |     |

| discontinuous mode                                                               | .12 |

| Fig. 2.8 Buck converter (a) circuit (b) steady-state inductor current waveform   | .13 |

| Fig. 2.9 Output capacitor voltage and current waveforms                          |     |

| for the buck converter in Fig.2.6                                                | .14 |

| Fig. 2.10 The simply operation of the PWM converter                              | 16  |

| Fig. 2.11 The transfer function of feedback system                               | .16 |

| Fig. 2.12 Type II compensator with two poles and a zero                          | 17  |

| Fig. 2.13 Type III compensator with three poles and two zeroes                   | .18 |

| Fig. 2.14 Switching parameters                                                   | .19 |

| Fig. 2.15 Switching signal with randomized modulation (a)RPPM (b)RPWM            |     |

| (c)RCFMFD (d)RCFMVD (e)FH                                                        | .20 |

| Fig. 2.16 Output spectrum of different switching schemes                         | .22 |

| Fig. 2.17 Transient waveform of different switching schemes                      | .22 |

| Chapter 3                                                                        |     |

| Fig. 3.1 Structure of a conventional PWM buck converter                          | .25 |

| Fig. 3.2 Energy spread to multiple frequencies with the FH technique             | .26 |

| Fig. 3.3 Transient waveforms of output voltage, inductor current and             |     |

| PWM signal in a conventional converter                                           | .27 |

| Fig. 3.4 Transient waveforms of output voltage, inductor current and             |     |

| PWM signal in the converter with the proposed ICAC technique                     | .28 |

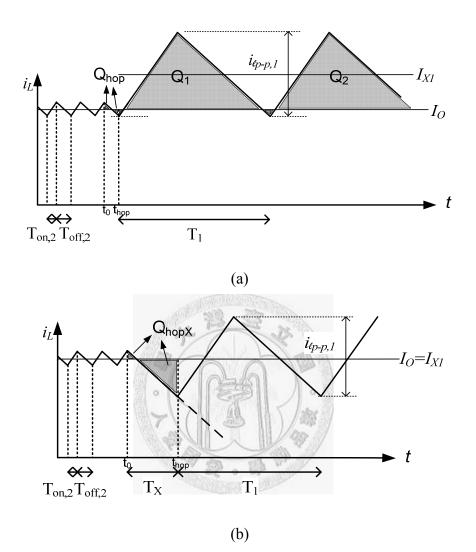

| Fig. 3.5 (a) Conventional and (b) proposed transient inductor current that hops  |     |

| frequency from low to high in off duty cycle                                     | 29  |

| Fig. 3.6 (a) Conventional and (b) proposed transient inductor current that hops  |     |

| frequency from high to low in off duty cycle period                                      |

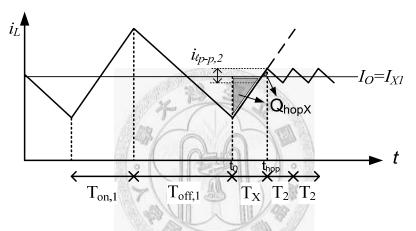

|------------------------------------------------------------------------------------------|

| Fig. 3.7 Proposed transient inductor current that hops frequency from low to high in on  |

| duty cycle period                                                                        |

| Fig. 3.8 Proposed transient inductor current that hops frequency from high to low in on  |

| duty cycle period                                                                        |

| Chapter 4                                                                                |

| Fig. 4.1 Block diagram of the FH buck converter with ICAC controller                     |

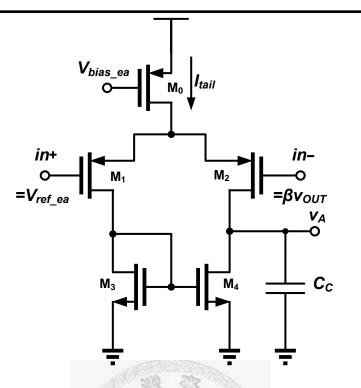

| Fig. 4.2 Schematic of the error amplifier                                                |

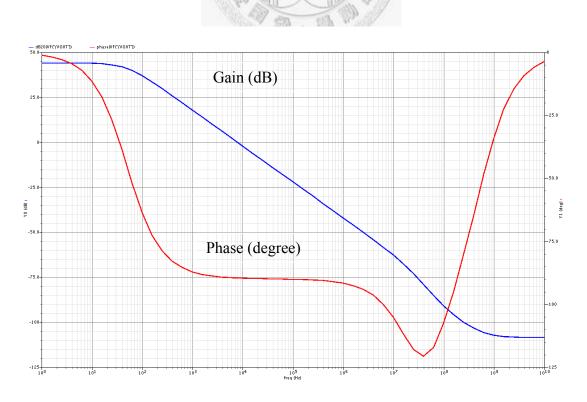

| Fig. 4.3 Frequency response of the error amplifier                                       |

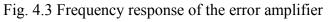

| Fig. 4.4 Schematic of folded-cascade operational amplifier                               |

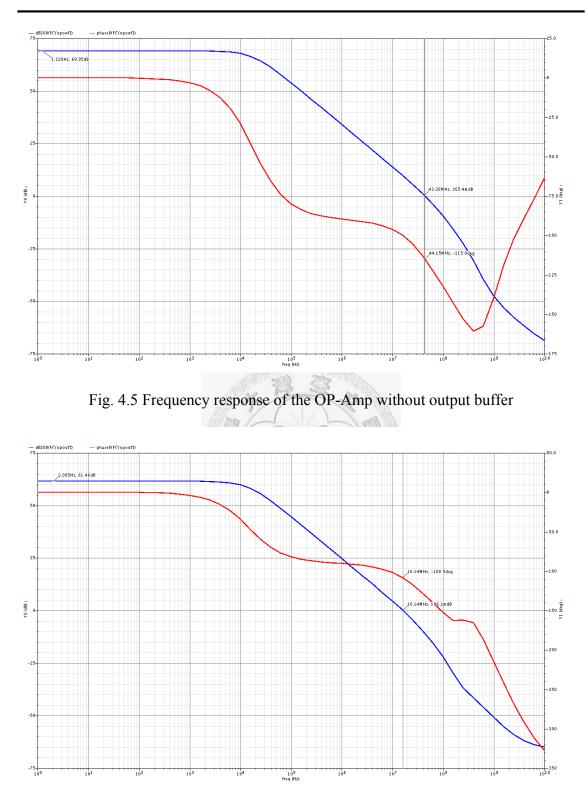

| Fig. 4.5 Frequency response of the OP-Amp without output buffer                          |

| Fig. 4.6 Frequency response of the OP-Amp with output buffer                             |

| Fig. 4.7 Common- drain output buffer (a) circuit. (b) small-signal equivalent circuit 40 |

| Fig. 4.8 Schematic of the comparator                                                     |

| Fig. 4.9 Schematic of ramp generator                                                     |

| Fig. 4.10 The circuit of SR latch                                                        |

| Fig. 4.11 The simulation result of ramp generator                                        |

| Fig. 4.12 The simulation of frequency considering process variation                      |

| Fig. 4.13 Schematic of DAC                                                               |

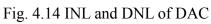

| Fig. 4.14 INL and DNL of DAC                                                             |

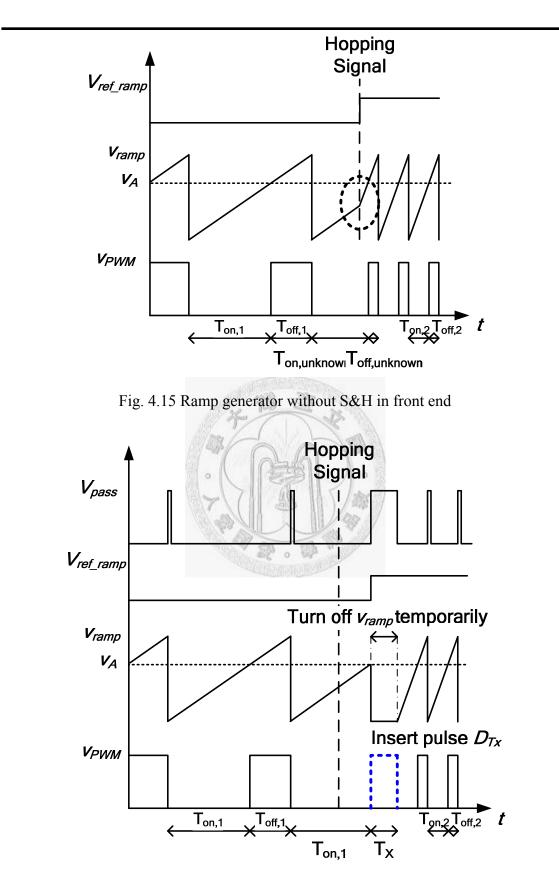

| Fig. 4.15 Ramp generator without S&H in front end                                        |

| Fig. 4.16 Ramp generator with S&H in front end and calculated pulse circuit in           |

| parallel48                                                                               |

| Fig. 4.17 Circuit of the sample and hold49                                               |

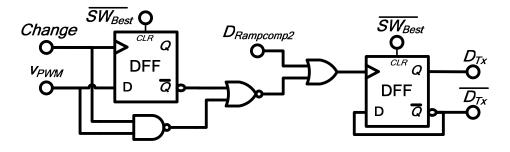

| Fig. 4.18 Diagram of the detector of hopping                                             |

| Fig. 4.19 Diagram of the control signal of sample time50                                 |

| Fig. 4.20 Relationship between voltage and time length in a ramp signal                  |

| Fig. 4.21 (a) Diagram of the additional ramp generators (b) Output of additional ramp    |

| generators                                                                               |

| Fig. 4.22 Diagram of full Ramp generators                                                |

| Fig. 4.23 Diagram of the calculated-width pulse circuit                                  |

| Fig. 4.26 Transient waveform of offset of the comparator                                       | 57   |

|------------------------------------------------------------------------------------------------|------|

| Fig. 4.27 Schematic of the gate driver with dead time control                                  | 59   |

| Fig. 4.28 The simulation result of the gate driver with dead time control                      | 60   |

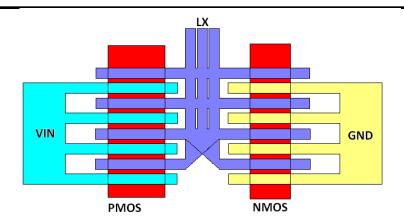

| Fig. 4.29 Schematic of the power stage                                                         | 61   |

| Fig. 4.30 Simulation of on-resistance of PMOS                                                  | 62   |

| Fig. 4.31 Floor plan of the power stage on chip                                                | 63   |

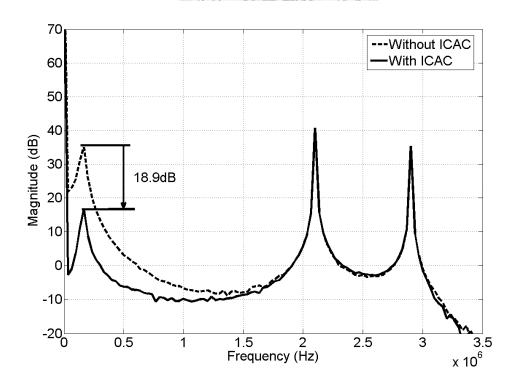

| Fig. 4.32 Output spectrums of the buck converter                                               | 65   |

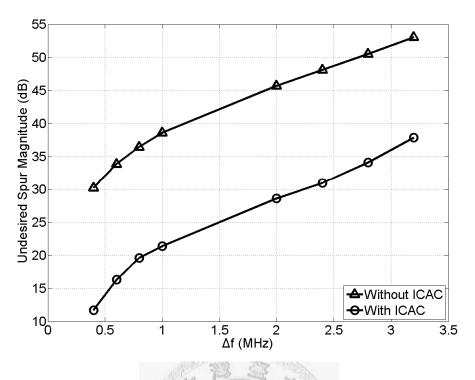

| Fig. 4.33 The undesired spur magnitude versus $\Delta f$                                       | 66   |

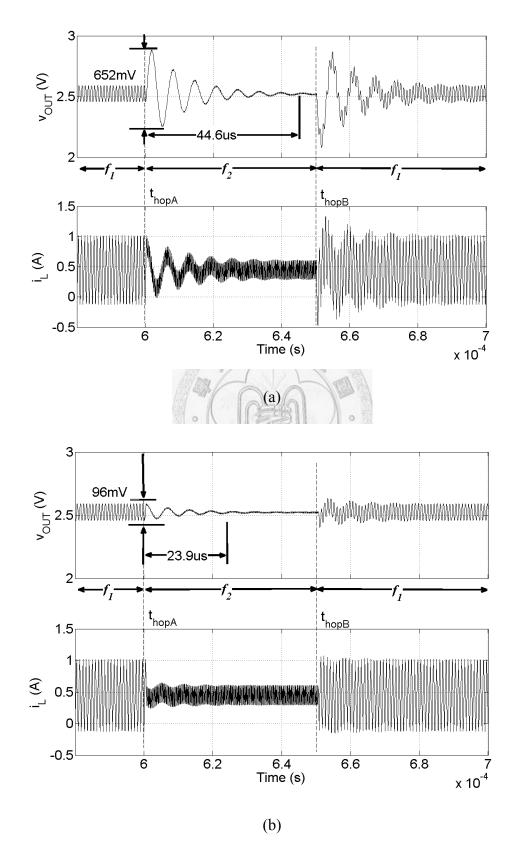

| Fig. 4.34 FH transient responses (a) Without ICAC (b) With ICAC                                | 67   |

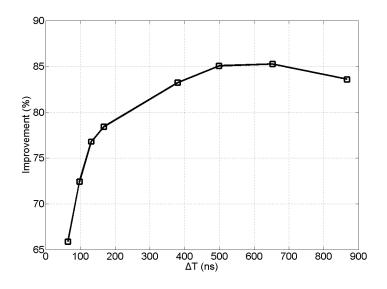

| Fig. 4.35 Simulated and analytical results of the transient-ripple output voltage ver          | sus  |

| $\Delta T$                                                                                     | 68   |

| Fig. 4.36 Improvement of transient ripple on the output voltage versus $\Delta T$              | 68   |

| Fig. 4.37 Simulated efficiency of using ICAC and without ICAC (a) with linear sca              | ale. |

| (b) with log scale                                                                             | 69   |

| Chapter 5                                                                                      |      |

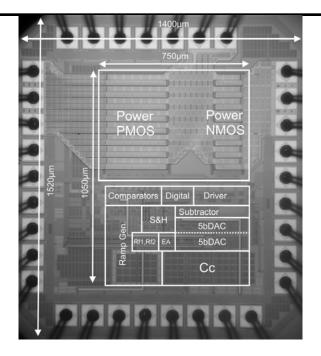

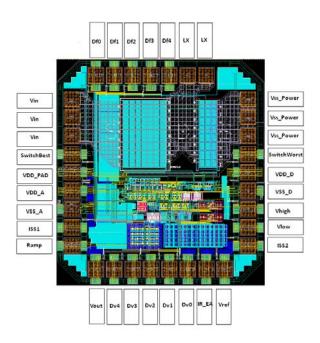

| Fig. 5.1 The floor plan of the DC-DC buck converter                                            | 71   |

| Fig. 5.2 Chip microphotograph                                                                  | 72   |

| Fig. 5.3 Layout for DC-DC buck converter with pin labels                                       |      |

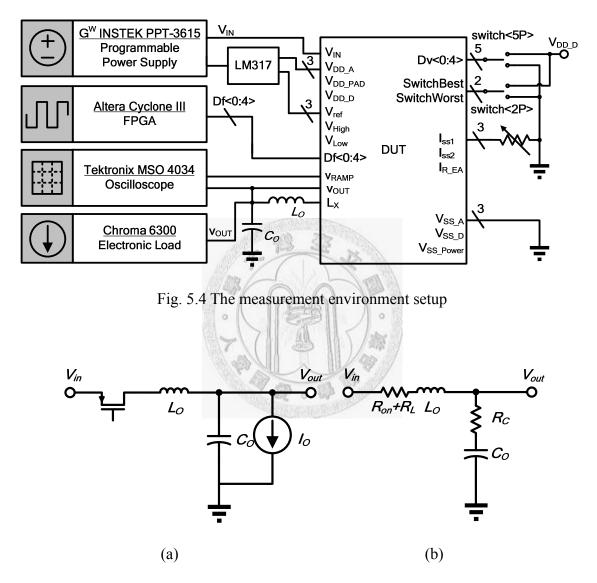

| Fig. 5.4 The measurement environment setup                                                     | 74   |

| Fig. 5.5 (a) output stage (b) equivalent circuit of output stage                               | 74   |

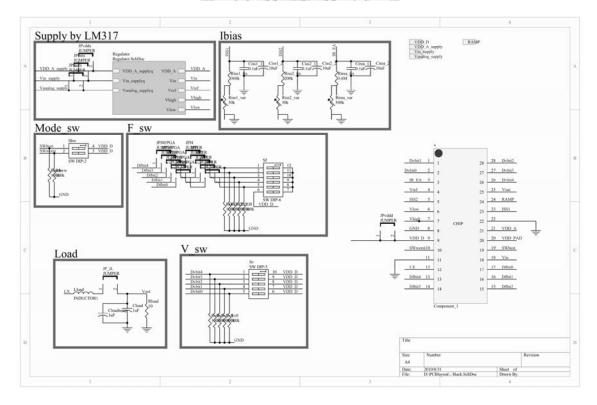

| Fig. 5.6 The schematic of power supplies and reference voltages on PCB                         | 76   |

| Fig. 5.7 The schematic of DC-DC converter side                                                 | 76   |

| Fig. 5.8 The test board                                                                        | 77   |

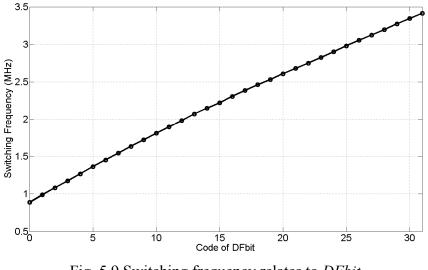

| Fig. 5.9 Switching frequency relates to <i>DFbit</i>                                           | 78   |

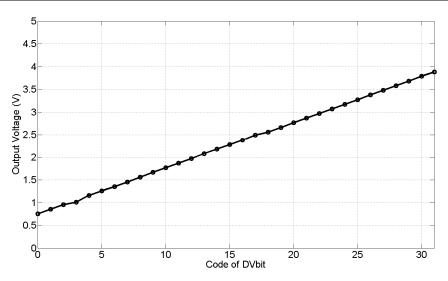

| Fig. 5.10 Output voltage relates to <i>DVbit</i>                                               | 79   |

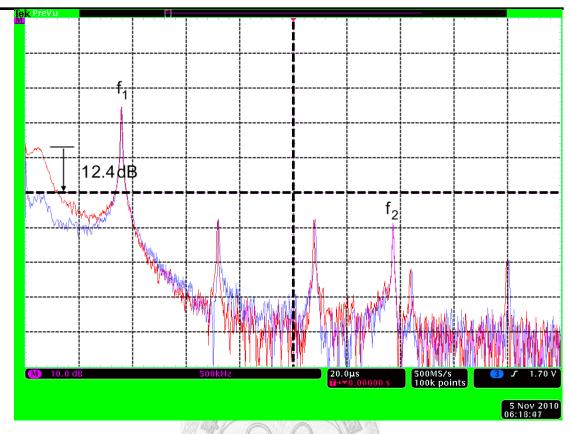

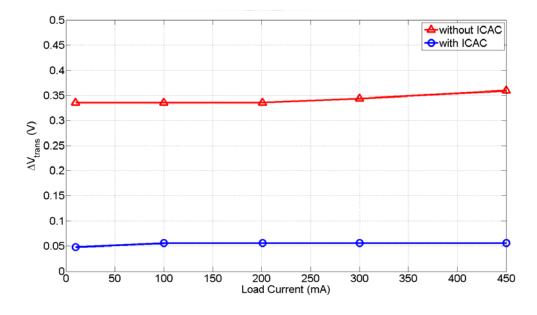

| Fig. 5.11 Frequency hopping between 0.85 MHz and 3.4 MHz                                       | 80   |

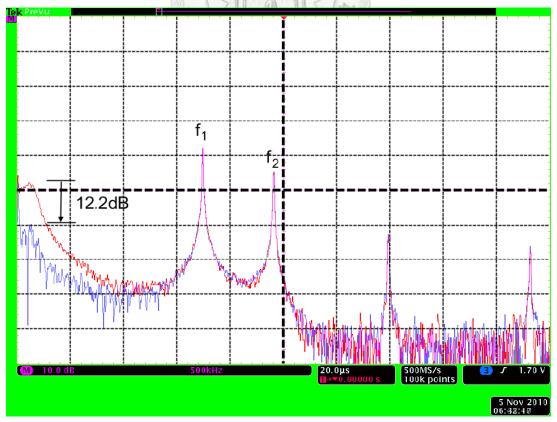

| Fig. 5.12 Frequency hopping between 1.7 MHz and 2.4 MHz                                        | 80   |

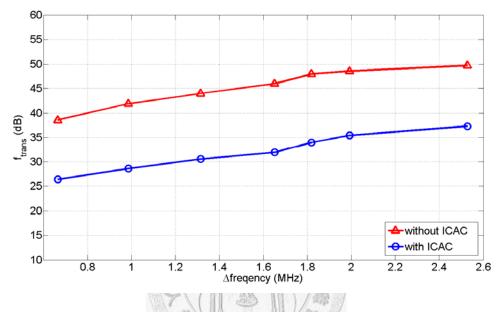

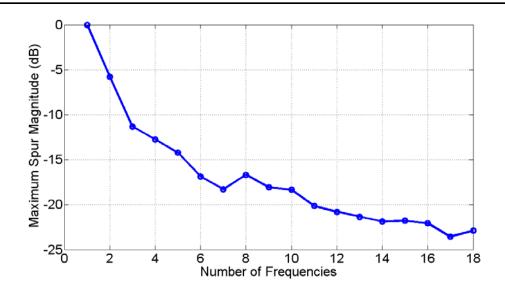

| Fig. 5.13 Spur magnitude sweeps different frequencies with $f_{\text{center}} = 2 \text{ MHz}$ | 81   |

| Fig. 5.14 Spur reduction sweeps different frequencies with $f_{center} = 2$ MHz                | 81   |

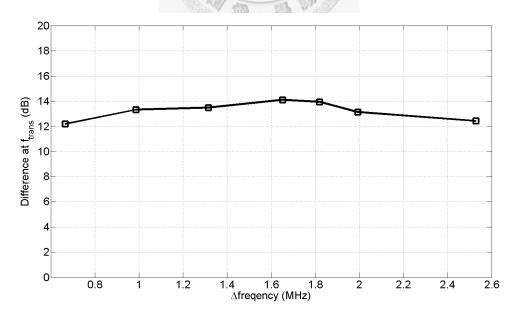

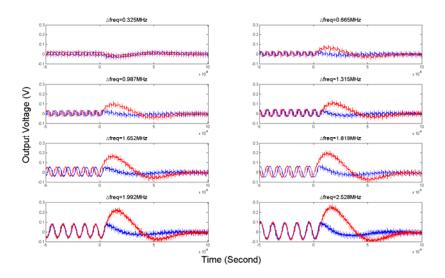

| Fig. 5.15 Transient waveform of frequency hopping from 0.88 MHz to 3.415 MHz                   |      |

| (a) without using ICAC and (b) with ICAC                                                       | 83   |

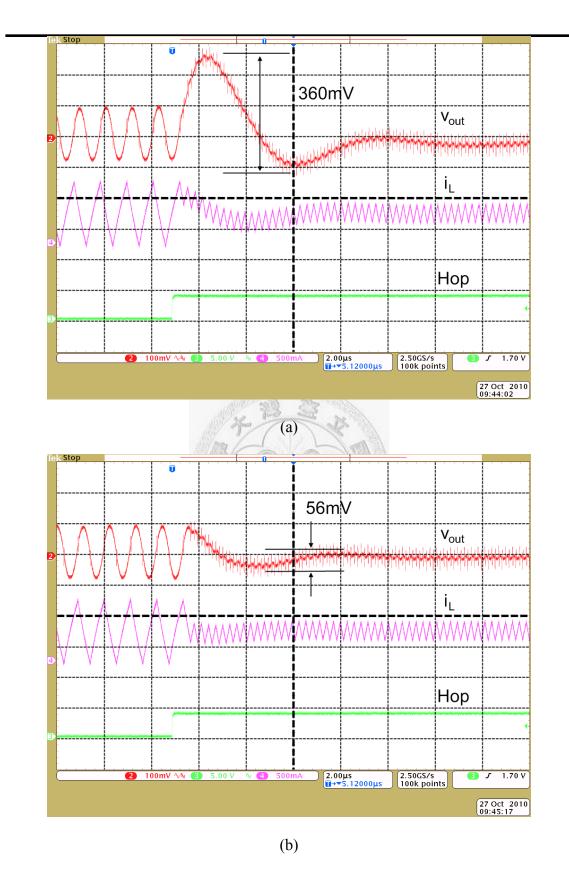

| Fig. 5.16 Transient waveform of frequency hopping from 3.415 MHz to 0.88 MHz                   |      |

| (a) without using ICAC and (b) with ICAC                                                       | 83   |

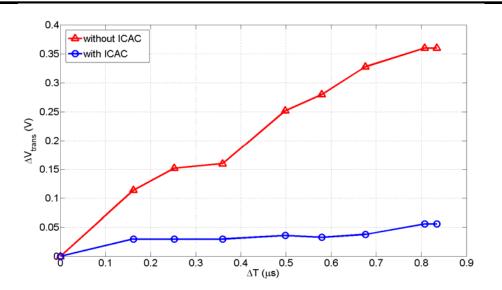

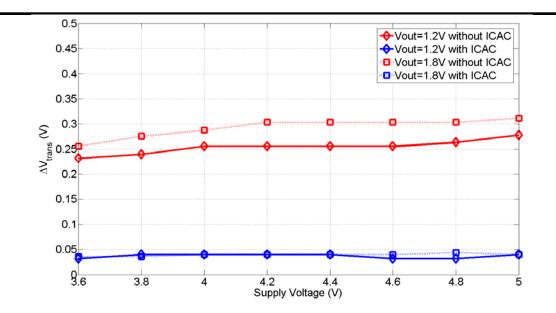

| Fig. 5.17 Comparison between conventional and proposed methods as sweeping                              |

|---------------------------------------------------------------------------------------------------------|

| different frequencies with <i>f</i> <sub>center</sub> =2 MHz85                                          |

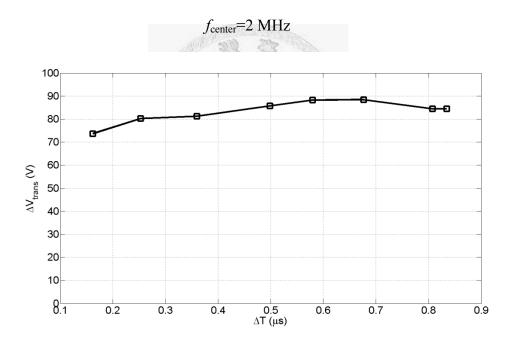

| Fig. 5.18 Transient ripple on the output voltage sweeps different frequencies with $f_{center}$         |

| =2 MHz                                                                                                  |

| Fig. 5.19 Improvement sweeps different frequencies with $f_{center}=2$ MHz86                            |

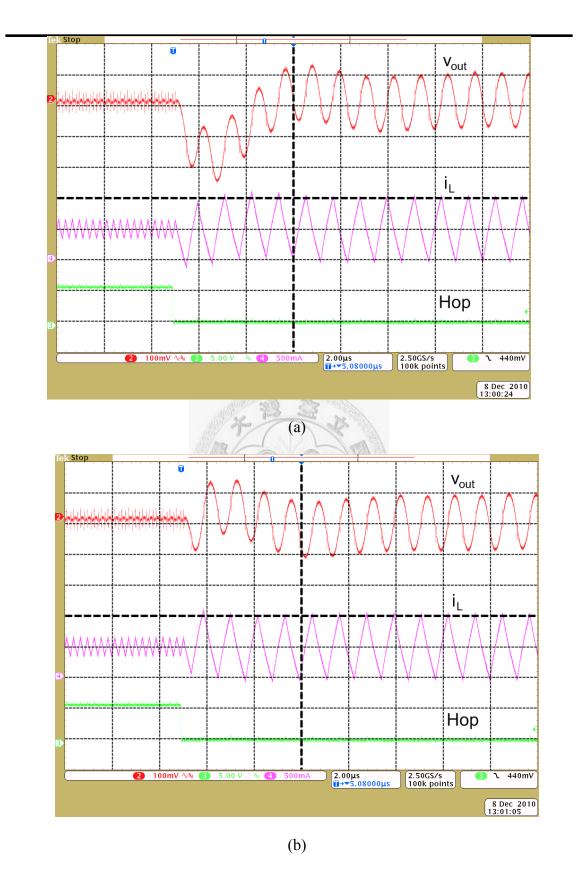

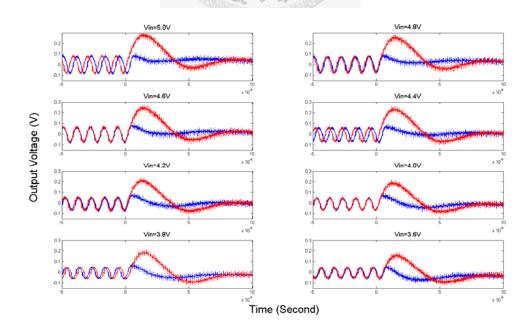

| Fig. 5.20 Comparison between conventional and proposed method as                                        |

| sweeping different supply voltage $V_{IN}$ at $v_{OUT} = 1.8$ V                                         |

| Fig. 5.21 Transient ripple on the output voltage sweeps different supply voltage $V_{IN}$ 88            |

| Fig. 5.22 Transient ripple on the output voltage sweeps different load current <i>I</i> <sub>0</sub> 88 |

| Fig. 5.23 Transient waveform of seventeen different switching frequencies                               |

| Fig. 5.24 Output spectrum using the frequency-hopping technique with seventeen                          |

| switching frequencies                                                                                   |

| Fig. 5.25 The spur magnitude of EMI with various of number of                                           |

| switching frequencies using the frequency-hopping technique90                                           |

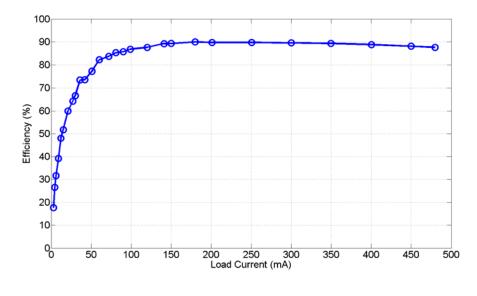

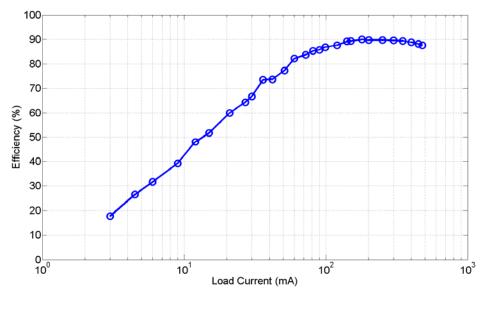

| Fig. 5.26 Efficiency at $v_{OUT} = 2.5$ V and $V_{IN} = 5$ V (a) with linear scale                      |

| (b) with log scale                                                                                      |

# **List of Tables**

### Chapter 2

| Chapter 5                                                         |    |

|-------------------------------------------------------------------|----|

| Table 4.9 Performance summary in simulation                       | 70 |

| Table 4.8 Design parameters and pin connections of the simulation |    |

| Table 4.7 Resistance of power stage                               | 63 |

| Table 4.6 Size of power transistors.                              |    |

| Table 4.5 Delay time of logic gate circuits                       |    |

| Table 4.4 Delay time of comparators                               |    |

| Table 4.3 Conclusion of control signal of sample time             | 50 |

| Table 4.2 The truth table of SR latch                             | 43 |

| Table 4.1 OP types used in this work                              |    |

| Chapter 4                                                         |    |

| Table 3.1 Specification of designed DC-DC buck converter          | 24 |

| Chapter 3                                                         |    |

| Table 2.2 Comparison of different switching schemes               | 22 |

| Table 2.1 Characteristics of different random switching schemes   | 20 |

| Table 5.1 The function of the pin in the DC-DC buck converter   | .73 |

|-----------------------------------------------------------------|-----|

| Table 5.2 The components on PCB for testing the DC-DC converter | .77 |

| Table 5.3 Performance summary in measurement.                   | 92  |

| Table 5.4 Performance comparison                                | 92  |

### **Chapter 1** Introduction

#### **1.1 Motivation**

The electromagnetic interference (EMI) problem of switched-mode power supplies [1] has received more and more attention with the introduction of the international electromagnetic compatibility (EMC) directive. The control of the switched-mode power supplies is generally associated with the use of the pulse-width-modulation (PWM) technique. Several variable frequency (VF) methods have been proposed for EMI-reduction such as random switching frequencies [2]-[4], frequency hopping (FH) [5]-[6], sigma-delta modulation [7]. While using these VF methods, there is a latent problem that the inductor current ripple varies with different frequencies. This variation results in an undesired spur in the frequency spectrum and a transient ripple on the output voltage.

These variable frequency techniques are widely used in mobile systems where different spectrum-sensitive circuits such as communication ICs are major application. Further, reducing the size of the passive filter in power converter design becomes an important consideration because of these mobile systems and portable devices. Unfortunately, when the inductor of the passive filter in buck converters is decreased, the inductor current ripple increases. Therefore, the undesired spur must be taken into account. Even if it is utilized in baseband applications, the transient ripple on the output voltage is still undesired in a typical DC-DC converter. This thesis presents an inductor current average control (ICAC) method for transient-ripple reduction in frequency hopping DC-DC converters. By using this method, it reduces the undesired spur without

increasing the size of the passive filter.

#### **1.2 Thesis Organization**

This thesis is organized as six chapters. In Chapter 2, the fundamental specification and requirements of the DC-DC converters are investigated such that limitations and trades-offs for designing can be understood easily. In Chapter 3, the algorithm for the proposed technique in a PWM DC-DC buck converter using variable frequency technique will be demonstrated and the detailed operations will be introduced. For simplicity, use the frequency-hopping technique to represent the variable frequency technique. In Chapter 4, the design and analysis of the circuits in each building block will be described. Furthermore, the simulation result will also be presented. In Chapter 5, the measurement results of the fabricated prototype DC-DC buck converter will be presented. Chapter 6 offers some conclusions and recommendations for future work.

### Chapter 2 Fundamental of DC-DC Buck Converter

#### **2.1 Performance Metrics**

#### 2.1.1 Efficiency

The efficiency of DC-DC converters is an important topic in electronic system. In general, the DC-DC converter converts a dirty voltage and current into a clean voltage and current. Therefore, the regulator is equal to a medium in electronic system. Since it is only a medium, the power loss is as less as it can be. The less energy the DC-DC converter requires, the more energy can be obtained by the other main electronic circuits. If the DC-DC converter has low efficiency, not only power is wasted but also unnecessary heat is generated, which will increase unnecessary cost for cooling and decrease reliability.

The efficiency of a switched-mode DC-DC converter is defined as the ratio of the output power and input power as follows:

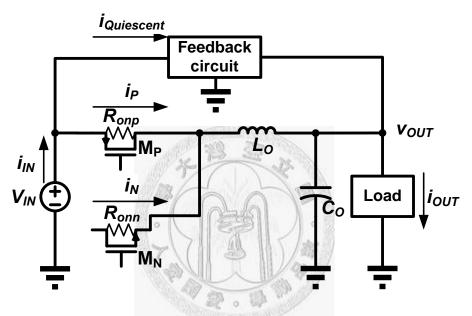

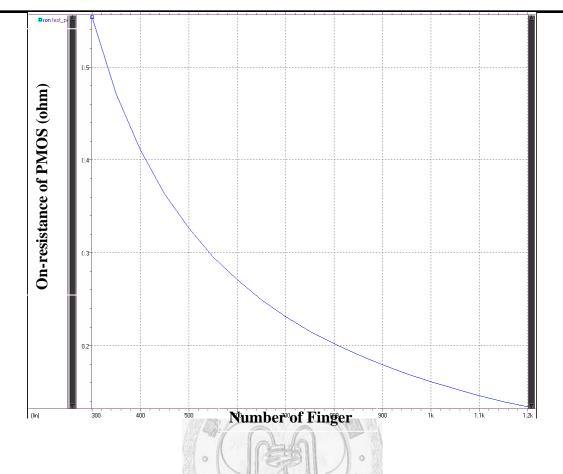

$$\eta = \frac{v_{OUT} \times i_{OUT}}{(V_{IN} \times i_{Quiescent}) + (R_{onp} \times i_P^2 + R_{onn} \times i_N^2) + P_{others} + (v_{OUT} \times i_{OUT})} \times 100\%$$

(2.1)

where the definition of  $V_{IN}$ ,  $v_{OUT}$ ,  $i_{OUT}$ ,  $i_{Quiescent}$ ,  $R_{onp}$ ,  $R_{onn}$ ,  $i_P$  and  $i_N$  are shown in Fig. 2.1.  $V_{IN}$  is the unregulated voltage and  $v_{OUT}$  is the regulated voltage.  $i_{IN}$  is the supply current and  $i_{OUT}$  is the load current.  $R_{onp}$ ,  $i_P$ ,  $R_{onn}$  and  $i_N$  are the on-resistance and current of power transistors  $M_P$  and  $M_N$ , respectively.  $i_{Quiescent}$  is the current flowing into the feedback circuit. In the denominator, the first term  $V_{IN} \times i_{Quiescent}$  means quiescent power consumption which is the power consumption in the chip when there is no output current (open circuit). The second term  $R_{onp} \times i_p^2 + R_{onn} \times i_N^2$  means power consumption in power transistors including conduction loss and switching loss, and the third term  $P_{others}$  means power consumption such as *I-V* overlap loss, current ripple loss and gate-driving loss. According to the above equation, the first term to the third term in denominator must be minimized to improve efficiency. Saving power consumption in feedback circuit decreases the value of the first term.

Fig. 2.1 The definition of efficiency in the switching regulator

#### 2.1.2 Regulation

This is an index about influence of environment on the output voltage. It is the measurement of how close the output voltage stays to its nominal value over full range of operating conditions. In general, it is divided into three components: line, load, and temperature regulation [8].

#### 2.1.2.1 Line Regulation

Line regulation is the effect the output voltage as varying the input voltage. There

are usually two methods to define line regulation. The first definition *line regulation* is percentage of changes in output voltage versus changes in input voltage. It is defined as

$$LNR = \left(\frac{\Delta V_{out}}{\Delta V_{in}}\right)\Big|_{I_o = const} \left(\frac{mV}{V}\right)$$

(2.2)

The second definition *percentage line regulation* includes the parameter of output nominal voltage into the first definition. So its value is highly related to output dc voltage. It is defined as

$$PLNR = \left(\frac{\frac{\Delta V_{out}}{V_{out,nom}} \times 100\%}{\Delta V_{in}}\right) \Big|_{I_o = const} \left(\frac{\%}{V}\right)$$

(2.3)

#### 2.1.2.2 Load Regulation

Load regulation is the percentage change in the steady state output voltage when the load current changes. There are usually two methods to define load regulation. The first definition *load regulation* is as

$$LOR = \left(\frac{\Delta V_{out}}{\Delta I_O}\right)\Big|_{V_{in}=const} \left(\frac{\mathrm{mV}}{\mathrm{A}}\right)$$

(2.4)

The second definition *percentage load regulation* includes the parameter of output nominal voltage into the first definition. So its value is highly related to output dc voltage. It is defined as

$$PLOR = \left(\frac{V_{out(\min L)} - V_{out(FL)}}{V_{O(FL)}}\right) \times 100\% \bigg|_{V_{in} = const} (\%)$$

(2.5)

#### 2.1.2.3 Temperature Regulation

Temperature Regulation is the effect of change in environmental temperature on the output voltage. The definition *thermal regulation* is as

$$THR = \frac{\frac{\Delta V_O}{V_{Onom}} \times 100\%}{\Delta P_D} \left|_{I_O = const \& V_W = const} \left(\frac{\%}{W}\right)\right|$$

(2.6)

Although many factors influence regulation of output voltage, the DC-DC converter has feedback circuit to compensate for such changes and keep the output within specified limits.

#### **2.1.3 Transient Response**

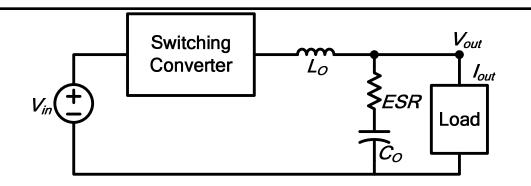

Transient Response is defined as a variation of output voltage when load current suddenly changes from one level to another level. The output voltage drops when load current steps up or increases when load current steps down since the additional or insufficient current supplied from the output capacitor. The transient response is a function of the bandwidth of DC-DC converter, output inductor, output capacitor, equivalent series resistance (ESR) of output capacitor and the load current as shown in Fig. 2.2. In past, this parameter is often ignored in industry. But in present age of high speed electronic manufactures, this parameter is more and more important because most kinds of electronic manufacture need to supply a large number of current in few microseconds even in few nanoseconds. If the DC-DC converter does not keep its output voltage which is supplied to electronic manufactures not change drastically in a big variation of load current, it will highly affect performance of electronic manufactures.

Fig. 2.2 Circuit diagram of the switching converter

Fig. 2.3 shows time characteristic of the transient response. During the time  $\Delta t_I$ , a large current is pulled from the load, the finite bandwidth of the switching converter is too slow to provide enough output current to the load. Therefore, the output capacitor must compensate the difference between switching converter current and load current. As a result, the voltage  $\Delta V_I$  can be calculated as

$$\Delta V_1 = \frac{\Delta I \times \Delta t_1}{C_o} + \Delta I \times ESR$$

(2.7)

The time period  $\Delta t_1$  is mainly determined by the bandwidth of the switching converter. Besides, a large output capacitor will keep on providing charges to the load and holding output voltage without transient spur. The sum of  $\Delta t_1$  and  $\Delta t_2$  is the "Recovery Time" and it takes for the output to return within the specified regulation limits.  $\Delta V_1$  is "Deviation of Output Voltage" between two different load current  $\Delta I$ . When the load steps down suddenly, the output voltage will jump. Before the inductor current is back to steady state, the excessive current charges the output capacitor. Therefore,  $\Delta V_2$  can be calculated as

$$\Delta V_2 = \frac{\Delta I \times \Delta t_3}{C_o} + \Delta I \times ESR$$

(2.8)

The length of the time period  $\Delta t_2$  and  $\Delta t_4$  is dependent on the time required for pass power transistors, M<sub>P</sub> and M<sub>N</sub>, in Fig. 2.1 to charge or discharge the output capacitor, and it is also dependent on the phase margin of the whole circuit loop.

Fig. 2.3 The transient response of output voltage when a dynamic load is applied

#### 2.2 Architecture of DC-DC Converters

A DC-DC converter is composed of a power stage and a feedback network. The power stage contains power transistors and an output filter. In the switched-mode DC-DC converter, the power stage contains power PMOS and NMOS transistors and the output filter which consists of an inductor L and a filtering capacitor C. Many feedback networks have been proposed and their goal in common is to provide a stable output voltage. These architectures will be discussed in detail as following.

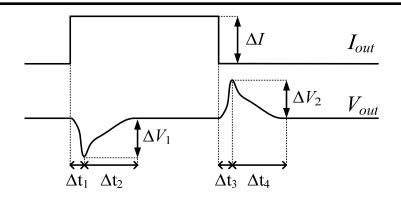

#### **2.2.1 DC-DC Buck Converter Operation**

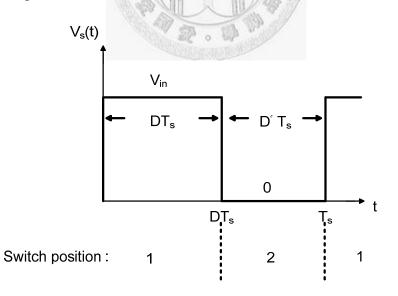

The buck converter, is a well-known converter that is capable of converting a higher voltage into a lower voltage. The switch produces a rectangular waveform  $V_s(t)$  as illustrated in Fig. 2.4. The voltage of  $V_s(t)$  is equal to the dc input voltage  $V_{IN}$  when the switch is in position 1, and is equal to zero when the switch is in position 2. In practical, the switch is realized using power semiconductor devices, such as transistors and diodes, which are controlled to turn on and turn off as required to perform the function of the ideal switch. The switching frequency  $f_{sw}$ , equals to the inverse of the

switching period  $T_s$ , generally lies in the range of 10 kHz to 10 MHz, depending on the switching speed of the semiconductor devices. The duty ratio D is the fraction of time that the switch spends in position 1, and is a number between zero and one. The complement of the duty ratio D' is defined as (*1-D*).

Fig. 2.4 Buck converter (a) the switch in 1 (b) the switch in 2

Fig. 2.5 Steady-state output waveform  $V_s(t)$

The switch reduces the dc component of the voltage: the switch output voltage  $V_s(t)$  has a dc component that is less than the converter dc input voltage  $V_{IN}$ . From Fourier analysis, we know that the dc component of  $V_s(t)$ , as shown in Fig. 2.5, is given by its average value  $\langle V_s \rangle$

$$\langle V_S \rangle = \frac{1}{T_S} \int_0^{T_S} V_S(t) dt = D V_{IN}$$

(2.9)

So the average value, or dc component, of  $V_s(t)$  is equal to the duty cycle times the dc input voltage  $V_{IN}$ . The output voltage is reduced from the input voltage by a factor of D.

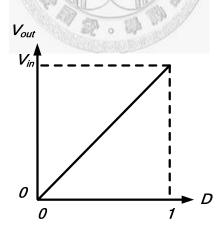

What remains is to insert a low-pass filter as shown in Fig. 2.4. The filter is designed to pass the average of  $V_s(t)$  but reject the components of  $V_s(t)$  at the switching frequency and its harmonics. The output voltage  $V_{out}$  is then essentially equal to the average of  $V_s(t)$ . Fig. 2.6 depicts the control characteristic of the converter and the buck converter has a linear control characteristic. Note that the output voltage is less than or equal to the input voltage, since  $0 \le D \le 1$ . Feedback systems are constructed to adjust the duty cycle D for regulating the converter output voltage. Inverters in digital controlled or error amplifiers in analog controlled could be built, in which the duty cycle varies slowly with time depending on feedback bandwidth.

Fig. 2.6 Output characteristic of buck converters

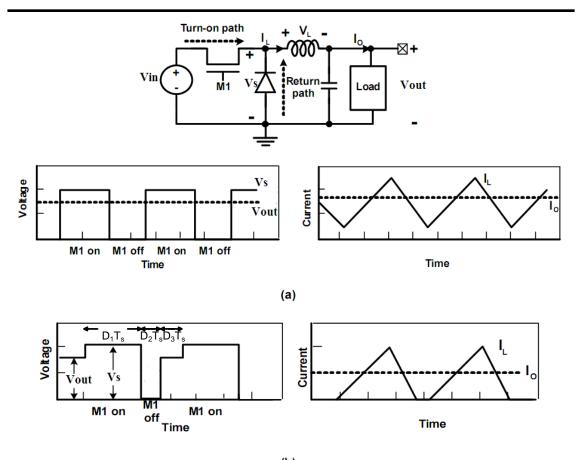

The conventional buck converter with inductor current and voltage waveforms shows in the Fig. 2.7. The transistor M1 is usually switched at high frequency to produce a chopped output voltage  $V_s$ . This is then filtered by the LC filter to generate a smooth load voltage  $V_{out}$ . When transistor M1 turns on,  $V_s=V_{in}$ , the voltage across the inductor is:

$$V_L = L \times \frac{di}{dt} = V_{in} - V_{out}$$

(2.10)

As a result,  $I_L$  increases linearly. When transistor M1 turns off, the current through the inductor cannot instantaneously fall to zero, so the diode provide a return path for the current to circulate through the load. During this period,  $V_s=0$ , so the voltage across the inductor is:

$$V_L = L \times \frac{di}{dt} = -V_{out} \tag{2.11}$$

So  $I_L$  decreases linearly. The peak-to-peak current ripple is:

$$\Delta I = t_{on} \times \frac{V_{in} - V_{out}}{L} = \frac{V_{in} \times T}{L} \times D \times (1 - D)$$

(2.12)

Therefore, the maximum current and the minimum current are defined separately as:

$$I_{\text{max}} = \frac{V_{out}}{R} + \frac{\Delta I}{2}$$

$$I_{\text{min}} = \frac{V_{out}}{R} - \frac{\Delta I}{2}$$

(2.13)

In Fig. 2.7(a), the continuous conduction mode (CCM) means that the minimum inductor current never falls to zero. When the minimum current falls to zero, it is discontinuous conduction mode (DCM) as shown in Fig. 2.7(b). In the steady state condition, the average voltage across an inductor over a complete is zero.

(b) Fig. 2.7 (a) The diagram and waveforms of continuous mode (b) The waveforms of discontinuous mode

In DCM,

$$\langle V_L(t) \rangle = D_1(V_{in} - V_{out}) + D_2(-V_{out}) + D_3(0) = 0$$

(2.14)

Solution for conversion ratio yields

Conversion ratio =

$$\frac{V_{out}}{V_{in}} = \frac{D_1}{D_1 + D_2}$$

(2.15)

From Fig. 2.7(b), the average inductor current is calculated:

$$\frac{1}{T_{s}} \int_{0}^{T_{s}} i_{L}(t) dt = \frac{1}{T_{s}} \left[ \frac{1}{2} i_{peak} (D_{1} + D_{2}) T_{s} \right]$$

(2.16)

Average inductor current =  $\frac{V_{out}}{R} = (V_{in} - V_{out}) (\frac{D_{1}T_{s}}{2L}) (D_{1} + D_{2})$

Elimination of  $D_2$  from conversion ratio equation and average inductor current equation, and solution for the conversion ratio  $V_{out}/V_{in}$ , yields

$$\frac{V_{out}}{V_{in}} = \frac{2}{1 + \sqrt{1 + \frac{4K}{D_1^2}}}, where \ K = 2L/RT_s$$

(2.17)

The result of conversion ratio M(D):

$$\begin{cases} D & \text{for CCM} \\ \frac{2}{1 + \sqrt{1 + \frac{4K}{D_1^2}}} & \text{for DCM} \end{cases}$$

(2.18)

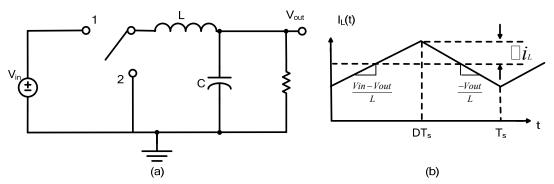

#### 2.2.2 Estimation of Output Voltage Ripple

Considering the buck regulator of Fig. 2.8(a), the inductor current  $i_L(t)$  with a dc component  $I_L$  and linear ripple of peak magnitude  $\Delta i_L$  are shown in Fig. 2.8(b). It is impossible to build a perfect low-pass filter that allows the dc component to pass but completely removes the components at the switching frequency and its harmonics. So the low-pass filter must allow at least some small amount of the high-frequency harmonics generated by the switch to reach the output.

The output voltage switching ripple should be small in any well-designed converter, since the object is to produce a dc output. For example, in a computer power supply having a 3.3 V output, the switching ripple is normally required to be less than a few tens of millivolts, or less than 1% of the dc output.

Fig. 2.8 Buck converter (a) circuit (b) steady-state inductor current waveform In a well designed converter, in which the capacitor provides significant filtering of

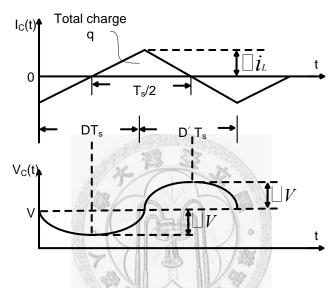

switching ripple, the capacitance is chosen large enough that its impedance at the switching frequency is much smaller than the load impedance. Hence nearly all of the inductor current ripple flows through the capacitor, and very little flows through load. As shown in Fig. 2.9, the capacitor current waveform  $I_C(t)$  is then equal to the inductor current waveform with the dc component removed. The current ripple is linear, with peak value  $\Delta i_L$ .

Fig. 2.9 Output capacitor voltage and current waveforms for the buck converter in Fig.2.6

From Fig. 2.9, by the capacitor relation Q=CV, the charge q is the integral of the current waveform between its zero crossings.

$$q = C(2\Delta V) \tag{2.19}$$

$$q = \frac{1}{2} \Delta i_L \frac{T_s}{2} \tag{2.20}$$

Substitution of equation (2.20) into equation (2.21), and solution for the voltage ripple peak magnitude  $\Delta V$  yields

$$\Delta V = \frac{\Delta i_L T_S}{8C} \tag{2.21}$$

This expression can be used to select a value for the capacitance C such that a given

voltage ripple is obtained. In practical, the additional voltage ripple caused by the capacitor equivalent series resistance (ESR) must also be included. The voltage ripple with ESR is calculated as

$$\Delta V = i_C(t) \times ESR + \frac{\Delta i_L T_S}{8C} = \Delta i_L \times (ESR + \frac{T_S}{8C})$$

(2.22)

In general, the ripple caused by first term "ESR" is much greater than caused by second term ( $T_s/8C$ ). So consideration of ESR is essential for estimation of output voltage ripple in switching converter.

#### 2.2.3 Feedback-Loop Stabilization

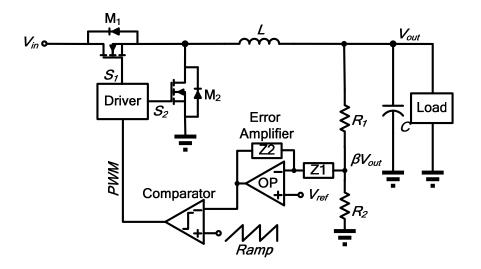

The simply feedback mechanism is illustrated in Fig. 2.10. The converter is composed of power stage and feedback network. The power stage contains a pair of switching elements, which consists of the power PMOS and NMOS transistors, and an output filter, which consists of an inductor and a capacitor. In feedback network, the difference of  $\beta V_{out}$  which the output voltage is scaled down by resistor series and the reference voltage  $V_{ref}$  is fed to the error amplifier. And then the output of the error amplifier and the ramp will pass through the comparator to define the duty cycle (PWM). The duty cycle controls the duration of the conducted time between the PMOS and the NMOS to achieve desired voltage such that the feedback is finished to regulate the output voltage The feedback system can be described as Fig. 2.11. The transfer function of the *LC* filter is defined as:

$$H_{LC}(s) = \frac{1}{s^2 L C + 1}$$

(2.23)

The transfer function of the feedback network is defined as:

$$H_{RR}(s) = \frac{R_2}{R_1 + R_2}$$

(2.24)

where  $T3(s) = H_{LC}(s) \times H_{RR}(s)$ .

Fig. 2.10 The simply diagram of the PWM converter

Fig. 2.11 The transfer function of feedback system

It is fixed-amplitude pulse of adjustable turn-on ratio of the PWM modulator. Therefore, the transfer function of the PWM modulator is defined as:

$$T2(s) = \frac{V_P}{V_T} \tag{2.25}$$

where  $V_T$  is amplitude of ramp waveform and  $V_P$  is the amplitude of PWM signal. The  $H_{RR}(s)$  and T2(s) do not effect on phase shift but they can decay the DC gain. As a result, there is only error amplifier T1(s) that can provide gain boost to increase the total gain and influence phase for better phase margin.

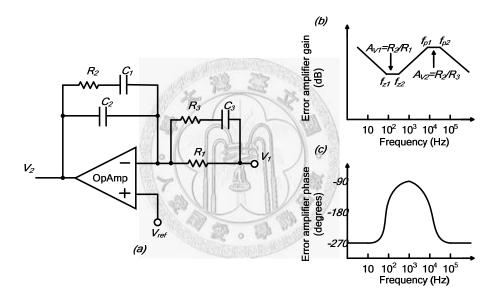

Next, two types of the error amplifier will be introduced. The first is type II shown in Fig. 2.12 (a), and it has two poles and one zero. The transfer function is calculated as:

$$\frac{V_2}{V_1} = -\frac{1 + sR_2C_1}{sR_1(C_1 + C_2)(1 + sR_2\frac{C_1C_2}{C_1 + C_2})}$$

$$\approx -\frac{1 + sR_2C_1}{sR_1(C_1 + C_2)(1 + sR_2C_2)} , assume \ C_1 \square \ C_2$$

(2.26)

The poles locate at the origin and the frequency  $f_p = \frac{1}{2\pi R_2 C_2}$ , the zero locates at the

frequency  $f_z = \frac{1}{2\pi R_2 C_1}$ . The frequency response is shown in Fig. 2.10(b) and (c). The

gain in the middle frequency is  $\frac{R_2}{R_1}$ . As a result, appreciate resistors are chosen, and it

can compensate the loss caused by the LC filter.

Fig. 2.12 Type II compensator with two poles and a zero

The second is type III, as shown in Fig. 2.13(a), and it has three poles and two zeros. The transfer function is calculated as:

$$\frac{V_1}{V_2} = -\frac{(1+sR_2C_1)(1+s(R_1+R_3)C_3)}{sR_1(C_1+C_2)(1+sR_3C_3)(1+sR_2\frac{C_1C_2}{C_1+C_2})}$$

$$\approx -\frac{(1+sR_2C_1)(1+sR_1C_3)}{sR_1(C_1+C_2)(1+sR_3C_3)(1+sR_2C_2)} , assume \ C_1 \square \ C_2, and \ R_1 \square \ R_3$$

(2.27)

The poles locate at the origin, the frequency  $f_{p1} \approx \frac{1}{2\pi R_2 C_2}$  and the frequency

$$f_{p2} \approx \frac{1}{2\pi R_3 C_3}$$

. The zeros locate at the frequency  $f_{z1} \approx \frac{1}{2\pi R_2 C_1}$  and the frequency

$f_{z2} \approx \frac{1}{2\pi R_1 C_3}$ . The gain and phase of this compensator is shown in Fig. 2.13 (b) and (c).

In summary, the maximum phase boost in type II compensator is 90 degrees, and in type III compensator is 180 degrees. According to stability and cost, the system will use the appropriate compensator to achieve desired performance.

Fig. 2.13 Type III compensator with three poles and two zeroes

#### **2.3 Variable Frequency**

In variable frequency techniques, there are four typical random switching methods discussed firstly. Then we will introduce a simplest method which is frequency hopping (FH). Since the main issue in this thesis focuses on the moment between different frequencies, the FH technique is a good choice to represent the main issue. Therefore, here uses the FH technique in following analysis,

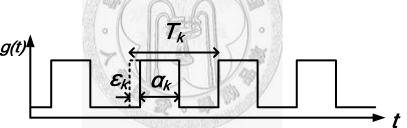

#### 2.3.1 Random Switching

There are four general random switching schemes for switched-mode DC-DC converters, including random-pulse-position-modulation (RPPM), random-pulse-width-modulation (RPWM), and random-carrier-frequency-modulation with fixed-duty-cycle (RCFMFD) and with variable-duty-cycle (RCFMVD), respectively. They are categorized by the random modulation of pulse which drives power transistors. The parameters of pulse are shown in Fig. 2.14.  $T_k$  is the duration of the *k*th cycle.  $\varepsilon_k$  is the delay time of the pulse.  $\alpha_k$  is the duration of the pulse in the *k*th cycle.  $d_k$  which equals to  $\alpha_k/T_k$  is the duty cycle period of the switch turning on in the *k*th period. The amplitude of pulse is rail to rail of input voltage. Their operation will be addressed as following paragraphs.

Fig. 2.14 Switching parameters

RPPM is similar to the classical PWM scheme with constant switching frequency. However, the position of the gate pulse or delay time  $\varepsilon_k$  is randomized within each switching period, instead of commencing at the start of each cycle. RPWM allows the pulse width  $\alpha_k$  to vary, but the average pulse width is equal to the required duty cycle. RCFMFD exhibits randomized switching period  $T_k$  and constant duty cycle  $d=\alpha_k/T_k$ , while RCFMVD exhibits randomized switching period  $T_k$  and constant pulse width  $\alpha$ . With the aid of Fig. 2.15, the characteristics of the pulse g(t) in each scheme are summarized in Table 2.1.

Fig. 2.15 Switching signal with randomized modulation (a)RPPM (b)RPWM (c)RCFMFD (d)RCFMVD (e)FH

| Switching<br>schemes | $T_k$        | $lpha_k$     | $d=\alpha_k/T_k$ | $arepsilon_k$ |

|----------------------|--------------|--------------|------------------|---------------|

| Standard<br>PWM      | Fixed        | Fixed        | Fixed            | Fixed         |

| RPPM                 | Fixed        | Fixed        | Fixed            | Randomized    |

| RPWM                 | Fixed        | Randomized   | Randomized       | Fixed         |

| RCFMFD               | Randomized   | Randomized   | Fixed            | Fixed         |

| RCFMVD               | Randomized   | Fixed        | Randomized       | Fixed         |

| FH                   | Integer sets | Integer sets | Fixed            | Fixed         |

Table 2.1 Characteristics of different random switching schemes

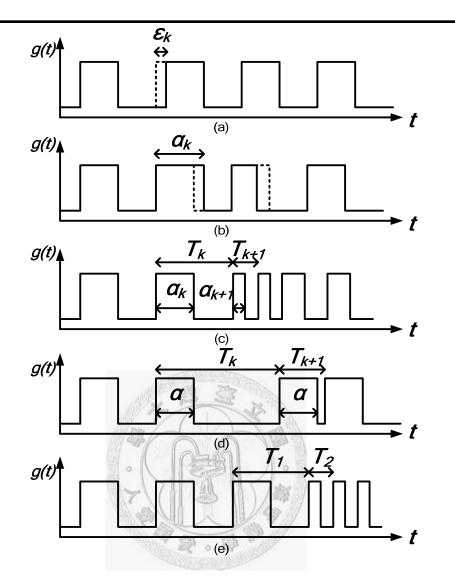

### 2.3.2 Frequency Hopping

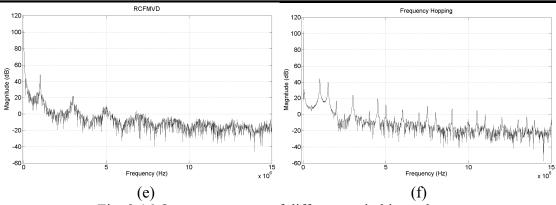

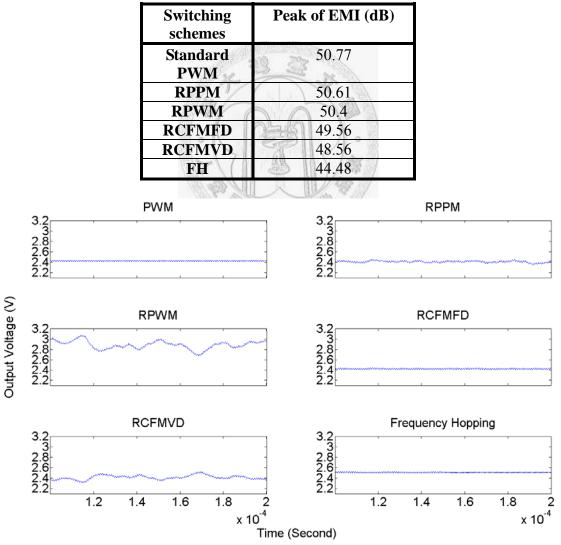

Compared to random switching schemes, the frequency-hopping (FH) technique utilizes couples of fixed switching frequencies to achieve EMI-peak reduction. Using predictable frequencies relax the complexity of the filter. Its characteristic of the pulse is shown in Fig. 2.15(e). The spectrum results of these variable frequency techniques are shown in Fig. 2.16. Table 2.2 aids to understand each reduction for peak of EMI. Another issue is the output voltage in time domain. In Fig. 2.17, these techniques have different phenomena in steady state. The reason is that the duty cycle varies in RPWM and RCFMVD.

Fig. 2.16 Output spectrum of different switching schemes

Table 2.2 Comparison of different switching schemes

Fig. 2.17 Transient waveform of different switching schemes

### Chapter 3 Proposed Architecture

#### **3.1 Introduction**

The inductor current average control (ICAC) is proposed in this paper. When using variable frequency techniques such as random switching or frequency hopping (FH), the inductor current ripple varies as the switching frequency changes. This variation of current ripple results in a transient ripple on the output voltage and undesired spur. In order to reduce this effect, this thesis discusses the best moment between different frequencies and how to implement. As aforementioned, the main issue focuses on the best moment between different frequencies and the FH technique adapts to this situation. Therefore, it discusses the hopping moment in following analysis

### **3.2 Specification of DC-DC Buck Converter**

The preliminary specification of DC-DC buck converter of this design is shown in Table 3.1. This work is used in portable devices to drive power amplifiers of RF circuits such as power-level tracking [14]. Therefore, the off-chip components must be small  $(L_0>4.7\mu\text{H} \text{ and } C_0>10\mu\text{F}$  in conventional circuits) and the output current is determined by the power amplifier. Output voltage range is utilized to the standby mode and active mode in portable devices for saving power. Input voltage range is determined by the battery type. Switching frequency is usually fixed in typical PWM converters, but in spread spectrum methods such as frequency hopping (FH), it needs a particular frequency range.

| Specification                           | Parameters |

|-----------------------------------------|------------|

| Input voltage, $V_{IN}$                 | 3.6-5 V    |

| Output voltage, <i>v</i> <sub>OUT</sub> | 0.8-3.4 V  |

| Max. output current, $I_O$              | 450 mA     |

| Output inductor, $L_O$                  | 1 μH       |

| Output capacitor, $C_O$                 | 1 μF       |

| Switching frequency, $f_{req}$          | 2-3 MHz    |

Table 3.1 Specification of designed DC-DC buck converter.

#### **3.3 System Architecture**

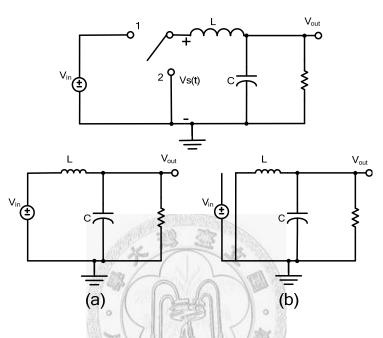

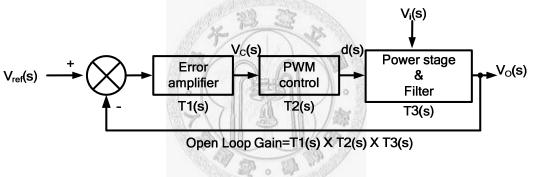

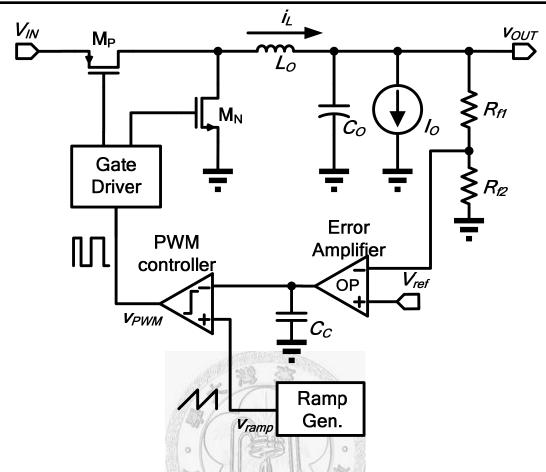

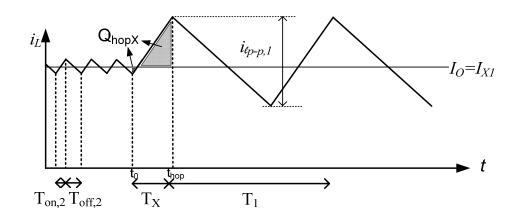

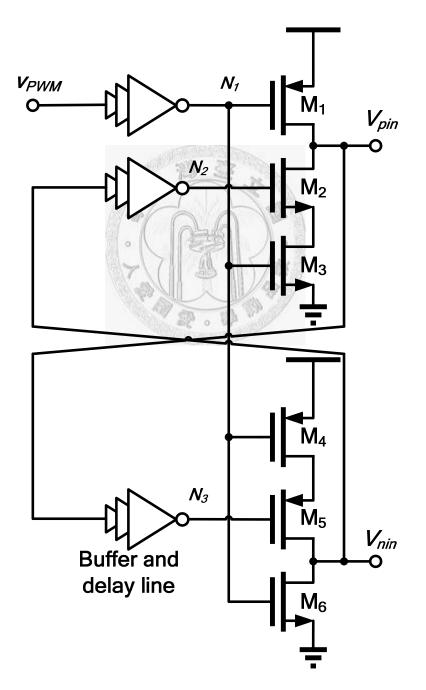

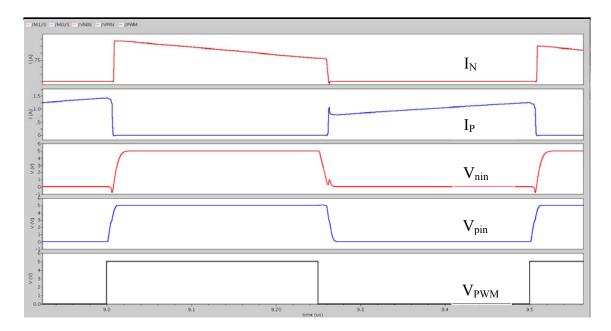

In this chapter, the detailed operation of the chip will be discussed. The typical architecture is illustrated in Fig. 3.1. A PWM buck converter provides a regulated output voltage  $v_{OUT}$  from an unregulated input voltage  $V_{IN}$ . The PWM controller compares the ramp signal,  $v_{ramp}$ , with the output of the error amplifier to generate a square wave,  $v_{PWM}$ , for voltage regulation. The gate driver drives the power transistors, M<sub>P</sub> and M<sub>N</sub>, with dead-time control to avoid a shoot-through current. The power transistors induce current passing a low pass filter which is composed with an inductor,  $L_O$ , and a capacitor,  $C_O$  to the load,  $I_O$ . Note that the frequency of  $v_{ramp}$  determines the operation frequency and is able to change for hopping the frequency.

Fig. 3.1 Structure of a conventional PWM buck converter.

## 3.4 Inductor Current Average Control (ICAC)

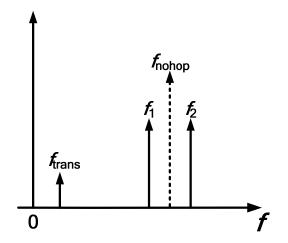

As shown in Fig. 3.2, the FH technique with a lower frequency,  $f_1$ , and a higher frequency,  $f_2$  [5] can avoid the energy concentrated on a single frequency at  $f_{nohop}$ . Their magnitudes are 6dB down as two frequencies hopping in comparison with the magnitude at only one frequency. However, the converter output suffers transient ripples for several periods after hopping and it would result in an undesired spur at  $f_{trans}$ .

Fig. 3.2 Energy spread to multiple frequencies with the FH technique.

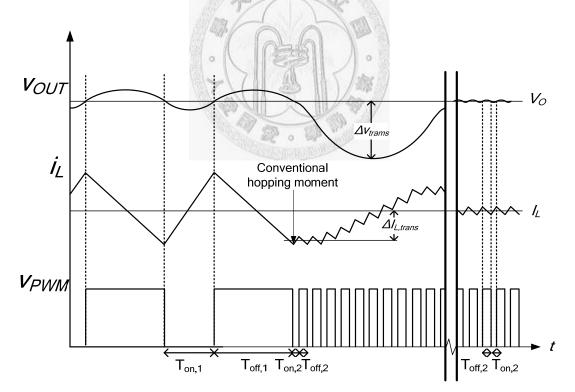

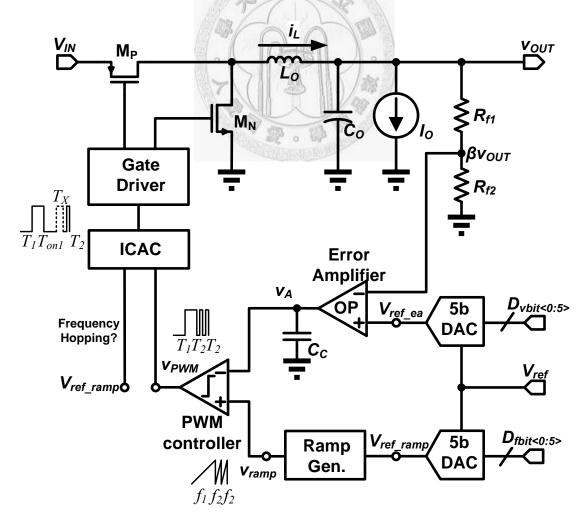

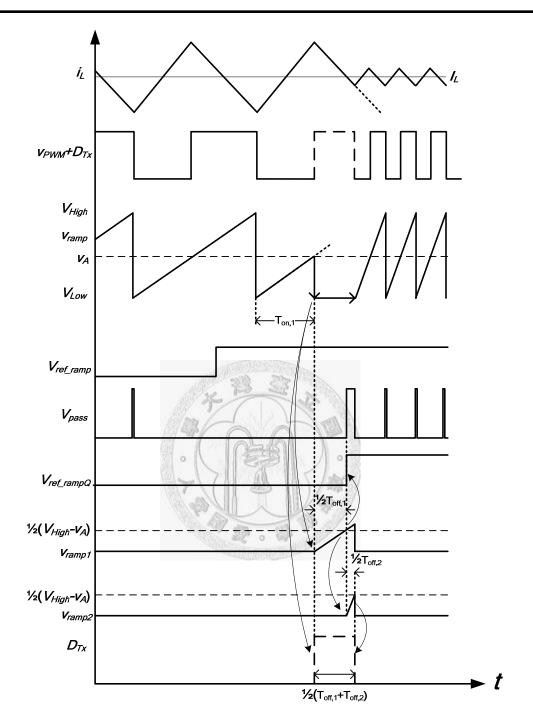

As shown in Fig. 3.3, in conventional PWM DC-DC converters [3], it assumes the frequency hopping at falling edge of  $v_{PWM}$  for simplicity and random in practically. The inductor current,  $i_L$ , increases during on duty cycle period, and decreases during off duty cycle period. In the example of Fig. 3.3,  $T_{on,1}$  and  $T_{on,2}$  represent the on duty cycle period of switching period at the low and high frequencies respectively.  $T_{off,1}$  and  $T_{off,2}$  represent the off duty cycle period of switching period at the low and high frequencies respectively. It reaches its peak/valley currents at the rising edge or the falling edge of  $v_{PWM}$ . After the hopping moment, the average of the transient inductor current would be different from that of the steady-state inductor current,  $I_L$ , due to the current continuity property of inductor. But, it would gradually approach  $I_L$  when the inductor current is back to steady state. Therefore, the difference,  $\Delta I_{L,trans}$ , charges (or discharges)  $C_O$  and generates transient ripple,  $\Delta v_{trans}$  on the output voltage. Its frequency response is the undesired spur at  $f_{trans}$  is dominated by  $L_O$  and  $C_O$  [15]. The undesired spur can be reduced by a larger capacitor but it pays a longer time to settle. Or, a larger inductor can

An Inductor Current Average Control (ICAC) technique for FH structure is

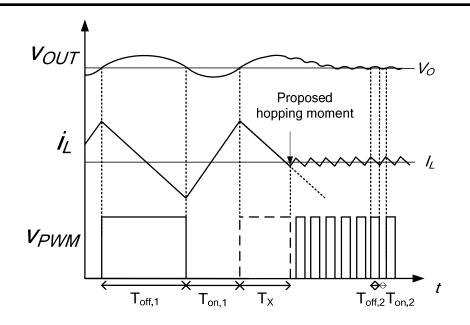

proposed in this paper. As shown in Fig. 3.4, the best hopping moment could be chosen. The best time length,  $T_X$ , is calculated to correspond to the best hopping state, which maintains the same  $I_L$  between the two frequencies. It modulates the off/on duty cycle period to be  $T_X$  width. The calculated value of  $T_X$  will be discussed in detail later. In the proposed hopping state, the output ripple voltage is improved by making the amount of charging close to the amount of discharging in the capacitor. If transient ripple on the output voltage is reduced, the undesired spur at  $f_{trans}$  in Fig. 3.4 is also reduced.

The best hopping state can be derived either in the off duty cycle period or the on duty cycle period. The proposed technique for FH from low to high and from high to low in these two different duty cycle periods will be discussed separately. Note that hopping in the off duty cycle period using ICAC is implemented in this chip.

Fig. 3.3 Transient waveforms of output voltage, inductor current and PWM signal in a conventional converter.

Fig. 3.4 Transient waveforms of output voltage, inductor current and PWM signal in the converter with the proposed ICAC technique.

# 3.4.1 Hopping in Off Duty Cycle Period

As mentioned before, there are two choices to hop, here discusses hopping in off duty cycle period with two parts. One is the frequency hopping from low to high, and another is the frequency hopping from high to low.

# 3.4.1.1 Hopping frequency from low to high

To reduce the complexity of transient response analysis, the loading is supposed to be a constant current source,  $I_O$  as indicated in Fig. 3.1. Therefore, the load current  $I_O$  is equal to the average or dc current  $I_L$ .

(a)

Fig. 3.5 (a) Conventional and (b) proposed transient inductor current that hops frequency from low to high in off duty cycle period.

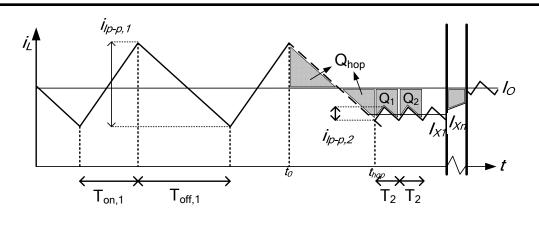

As shown in Fig. 3.5(a), the net charge on the capacitor,  $\Delta Q$ , after  $t_0$  is

$$\Delta Q = Q_{hop} + Q_1 + Q_2 + \cdots$$

$$= (I_{Xhop} - I_O)(t_{hop} - t_0) + (I_{X1} - I_O)T_2 + (I_{X2} - I_O)T_2 + \cdots$$

(3.1)

where  $I_{Xhop}$  is the average of transient inductor current from  $t_0$  to  $t_{hop}$  and  $I_{Xi}$ , i=1,2,... is the average of transient inductor current at the ith period of  $v_{PWM}$  after  $t_0$ .  $t_0$  is the time at which the inductor current is at its peak or valley and the capacitor voltage is at its dc value,  $V_O$ .  $t_{hop}$  is the hopping moment.  $T_2=T_{off,2}+T_{on,2}$  is the period of  $v_{PWM}$  after hopping. The transient response can be separated into two parts, the charge in the hopping interval  $Q_{hop}$  and total charge after hopping  $Q_T=Q_1+Q_2+...$  Since settling time is longer than one period,  $Q_{hop}$  is much smaller than  $Q_T$ .

$$\Delta Q = Q_{hop} + Q_T \cong Q_T \tag{3.2}$$

As illustrated in Fig. 3.5(a),  $Q_T$  is approximated with a triangular area. Its height is the difference between  $I_O$  and  $I_{XI}$ . Its width,  $T_T$ , is the time from  $t_{hop}$  to the steady state.

$$Q_{T} = \frac{1}{2} (I_{X1} - I_{O}) T_{T}$$

=  $\frac{1}{2} (-\frac{1}{2} i_{lp-p,1} + \frac{1}{2} i_{lp-p,2}) T_{T}$  (3.3)

$$m_{off} = \frac{-i_{\ell p-p,l}}{T_{off,2}} = \frac{-i_{\ell p-p,2}}{T_{off,2}} = \frac{-DV_{IN}}{L_O}$$

(3.4)

where  $i_{lp-p,1}$  and  $i_{lp-p,2}$  are the peak-to-peak values of the inductor current at low frequency and high frequency respectively.  $m_{off}$  is the slope of the decreasing inductor current. *D* is the duty cycle.

Then, the conventional transient ripple on the output voltage can be obtained as

$$\Delta v_{trans} \cong \frac{Q_T}{C_o} \cong \frac{1}{4} \frac{V_{IN} D (1 - D)}{L_o C_o} (T_1 - T_2) T_T$$

(3.5)

where  $T_1$ ,  $T_2$  are the periods of the low and high frequencies respectively.

In order to minimize  $Q_T$  in (3.3), the best time  $T_X$  of  $t_{hop}$  is proposed as follows. In Fig. 3.5(a),  $I_{XI}$  can be calculated as

$$I_{X1}(t_{hop}) = I_O + \frac{1}{2}i_{lp-p,1} + m_{off} \times (t_{hop} - t_0) + \frac{1}{2}i_{lp-p,2}$$

(3.6)

According to (3.3), if  $I_{XI}$  equals  $I_O$ ,  $Q_T=0$ , most charge during transient settling time can be eliminated.

$$I_{O} + \frac{1}{2}i_{\varphi - p, l} + m_{off} \times (t_{hop} - t_{0}) + \frac{1}{2}i_{\varphi - p, 2} = I_{O}$$

(3.7)

the proposed best time  $T_X$  can be calculated as

$$T_{X} = t_{hop} - t_{0} = -\frac{\frac{1}{2}i_{\varphi-p,l}}{m_{off}} - \frac{\frac{1}{2}i_{\varphi-p,2}}{m_{off}} = \frac{1}{2}T_{off,l} + \frac{1}{2}T_{off,2}$$

(3.8)

The proposed best time  $T_X$  is  $\frac{1}{2}(T_{off,I}+T_{off,2})$ , which is the average of off duty cycle period at low and high frequencies. Its corresponding transient waveform is illustrated in Fig. 3.5(b). Since  $I_X$  equals  $I_O$ , according to (3.3), only the rest of charge,  $Q_I$ , would affect transient ripple of the output voltage.

$$Q_{hopX} = \frac{1}{2} \left(\frac{1}{2} i_{lp-p,1}\right) \left(\frac{1}{2} T_{off,1}\right) - \frac{1}{2} \left(\frac{1}{2} i_{lp-p,2}\right) \left(\frac{1}{2} T_{off,2}\right)$$

$$= \frac{1}{2} \left(\frac{1}{2} i_{lp-p,1} - \frac{1}{2} i_{lp-p,2}\right) T_X$$

(3.9)

$$\Delta v_{trans,ICAC} = \frac{Q_{hopX}}{C_o} = \frac{1}{4} \frac{V_{IN} D(1-D)}{L_o C_o} (T_1 - T_2) T_X$$

(3.10)

According to (3.5) and (3.10), the conventional and proposed transient ripples on the output voltage are proportional to  $(T_1-T_2)T_T$  and  $(T_1-T_2)T_X$  respectively.

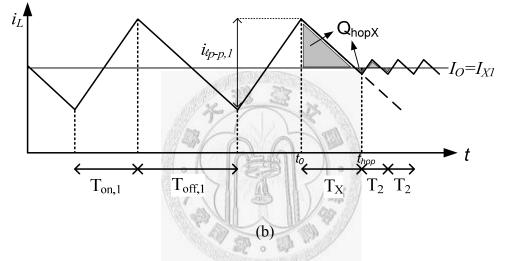

#### 3.4.1.2 Hopping frequency from high to low

As shown in Fig. 3.6(a), when the frequency hops from high to low, the average of transient inductor current  $I_{XI}$  is over the average inductor current  $I_O$ . Similarly,  $I_{XI}$  can be approximated as

$$I_{X1}(t_{hop}) = I_O + \frac{1}{2}i_{lp-p,2} + m_{off} \times (t_{hop} - t_0) + \frac{1}{2}i_{lp-p,1}$$

(3.11)

Likewise, if let  $I_{XI}$  in (3.11) equal to  $I_O$ , we obtain  $T_X = t - t_O = \frac{1}{2} (T_{off,I} + T_{off,2})$ .  $T_X$  is the same when it hops from high to low. It is the average of off duty cycle period at low and high

Fig. 3.6 (a) Conventional and (b) proposed transient inductor current that hops frequency from high to low in off duty cycle period

# 3.4.2 Hopping in On Duty Cycle Period

# 3.4.2.1 Hopping frequency from low to high & from high to low

Similar to the analysis in 3.4.1, the only different part is the average of transient inductor current  $I_{XI}$

$$I_{X1}(t_{hop}) = I_O + \frac{1}{2}i_{lp-p,1} + m_{on} \times (t_{hop} - t_0) + \frac{1}{2}i_{lp-p,2}$$

(3.12)

$$I_{X1}(t_{hop}) = I_O + \frac{1}{2}i_{lp-p,2} + m_{on} \times (t_{hop} - t_0) + \frac{1}{2}i_{lp-p,1}$$

(3.13)

$I_{XI}$  in (3.12) is hopping from low to high and  $I_{XI}$  in (3.13) is hopping from high to low. Let  $I_{XI}$  in (3.12) and (3.13) equals to  $I_O$  as shown in Fig. 3.7 and Fig. 3.8 respectively, we obtain the similar  $T_X=t-t_0=\frac{1}{2}(T_{on,I}+T_{on,2})$ . It is the average of on duty cycle period at low and high frequencies

Fig. 3.7 Proposed transient inductor current that hops frequency from low to high in on

duty cycle period.

Fig. 3.8 Proposed transient inductor current that hops frequency from high to low in on duty cycle period.

# Chapter 4 Circuit Implementation and Simulation Results

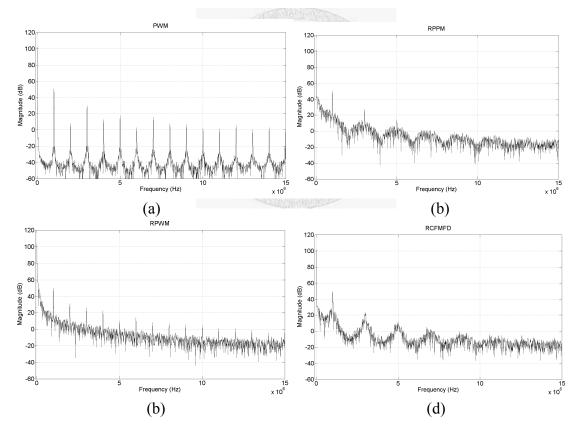

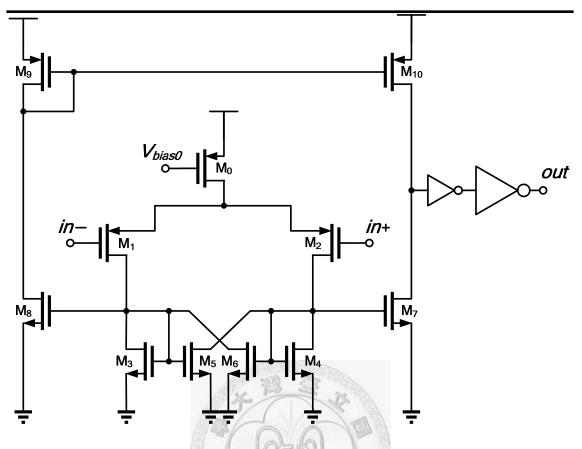

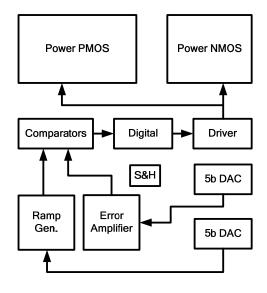

Based on above analysis, the proposed system circuit is shown as Fig. 4.1. Except for the conventional buck converter architecture, there are two DACs and an ICAC block. Two DACs change the output voltage and the switching frequency respectively. An ICAC block before the gate driver block is utilized to insert a calculated-width pulse for modulating the best time in frequency hopping.

Fig. 4.1 Block diagram of the FH buck converter with ICAC controller

## 4.1 Amplifier Circuit

There are two type amplifiers in this work. One is slower and only used in the error amplifier circuit. Another one is faster and provides higher DC gain in this work which needs operational amplifiers (OP).

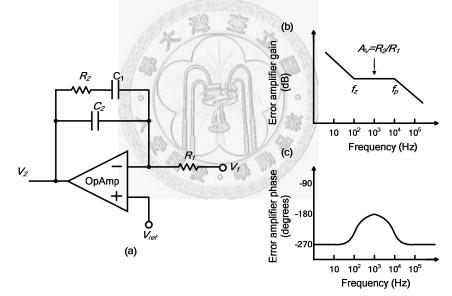

#### 4.1.1 Error Amplifier

There are many compensation methods such as type II and type III. But as the operation frequency changes in the FH technique, the feedback-loop stabilization is much more difficult since these methods compensate the particular frequency range. Based on the simplicity and independence from the switching frequency, a dominant-pole compensation is used in this error amplifier to compensate the stability of the system.

To avoid any second pole involving in this dominant pole, it uses a one-stage simple operational amplifier as shown in Fig. 4.2. The unit-gain frequency  $\omega_t$  is given by

$$\omega_t = \frac{g_{m1,2}}{C_C} \tag{4.1}$$

There are two components which define the unit-gain frequency. Firstly, to make lower unit-gain frequency for dominant-pole compensation, the compensation capacitor  $C_C$  is chosen as large as possible and is limited by the area on chip. Secondly, another component is the transconductance of input transistors,  $g_{m1,2}$ .

$$g_m = \sqrt{2C_{OX}\frac{W}{L}I_D}$$

(4.2)

To make smaller  $g_m$ , it is chose p-input, small W/L ratio and small bias current  $I_{tail}=2I_D$ .

Fig. 4.2 Schematic of the error amplifier

Fig. 4.3 shows the AC analysis of the error amplifier. Open loop DC gain is 44 dB. Phase margin is 90 degree and the unity gain bandwidth is 113 kHz as  $C_c$ =42 pF.

# 4.1.2 Operational Amplifier

In order to provide high DC gain, it chooses the folded-cascode structure as shown in Fig. 4.4 [11]. Its DC gain  $A_V$  and 3dB frequency  $\omega_{3dB}$  are given by

$$A_V = g_m r_0 \tag{4.3}$$

$$\omega_{3dB} = \frac{g_m}{C_L} \tag{4.4}$$

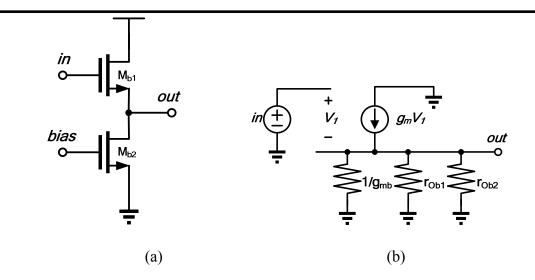

It is necessary to add an output stage when it drives resistance load. Therefore, some of these OPs have a NMOS common-drain stage as output buffer as listed in Table 4.1. Table 4.1 also shows two different tail currents. Several operational amplifiers do not need high frequency response, so they could use smaller tail current to save power. As shown in Fig. 4.5 and Fig. 4.6, their DC gain and 3dB frequencies are 69 dB, 43 MHz and 61.5 dB, 16 MHz respectively. The DC gain of OP with output buffer is lower due to the body effect. From Fig. 4.7, we have

$$A_{V} = \frac{\frac{1}{g_{mb}} / /r_{Ob1} / r_{Ob2}}{(\frac{1}{g_{mb}} / /r_{Ob1} / /r_{Ob2}) + \frac{1}{g_{m}}}$$

(4.5)

Equation (4.5) represents that body effect decreases the DC gain. Although it can by reduced by using PMOS common-drain stage, it needs a shift-down circuit rather than shift-up circuit in this work.

Fig. 4.4 Schematic of folded-cascade operational amplifier 11

| Table 4.1 | OP type | es used | in this | work |

|-----------|---------|---------|---------|------|

|           |         | C 11 .  | /1.     |      |

1801 21

|                             | I <sub>tail</sub> =2 μA | I <sub>tail</sub> =5 μA | With Buffer |

|-----------------------------|-------------------------|-------------------------|-------------|

| Subtractor                  | A da MI                 | 0                       | 0           |

| Input of RampGen.           | 2                       | 0                       |             |

| Input of S&H                | and the second          | 0                       | 0           |

| Buffer of V <sub>ref</sub>  | 0                       |                         |             |

| Buffer of v <sub>A</sub>    | 0                       |                         | 0           |

| Buffer of v <sub>ramp</sub> |                         | 0                       | 0           |

Fig. 4.6 Frequency response of the OP-Amp with output buffer

Fig. 4.7 Common-drain output buffer (a) circuit. (b) small-signal equivalent circuit

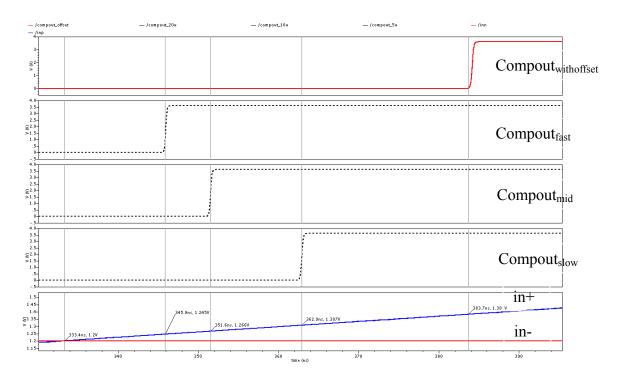

#### **4.2 Comparator Circuit**

A comparator is a circuit that compares the instantaneous value of an analog input voltage with a reference voltage, and then generates a logic output level depending on whether the input is larger or smaller than the reference level.

As shown in Fig. 4.8, it is implemented by a source-coupled differential pair with positive feedback to provide a high gain. The gain of the positive feedback gain stage is given by

$$Av = \sqrt{\frac{\mu_p(\frac{W}{L})_1}{\mu_n(\frac{W}{L})_3}} \times \frac{1}{1-\alpha}$$

(4.6)

where  $\alpha = (W/L)_5/(W/L)_3$  is the positive feedback factor.

The inverter chains are used to increase the response of the output signal and pull the output to digital level. The inverter stage acts as a driver stage such that the size of  $M_7$  and  $M_8$  can be made smaller. With the smaller size of  $M_7$  and  $M_8$ , the effect of the parasitic capacitance at the gates of  $M_7$  and  $M_8$  is decreased for a faster response.

Fig. 4.8 Schematic of the comparator

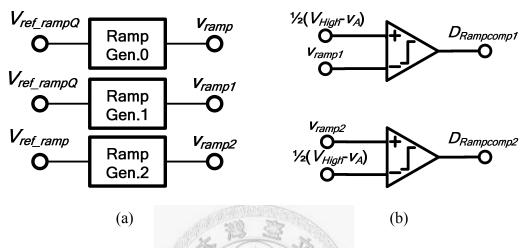

The comparators are needed one for the PWM controller, two for the ramp generator circuit (*RampGen.0*), two for the detector and two for the calculated pulse circuit (*RampGen.1* and *RampGen.2*) in the ICAC block.

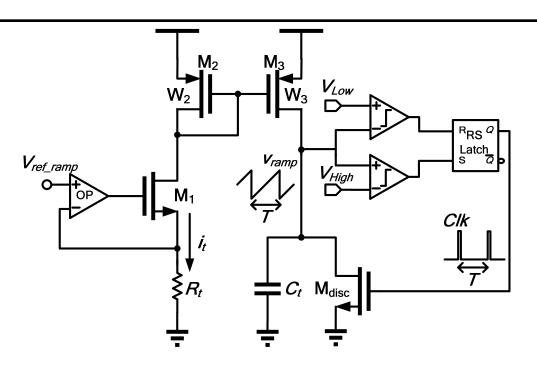

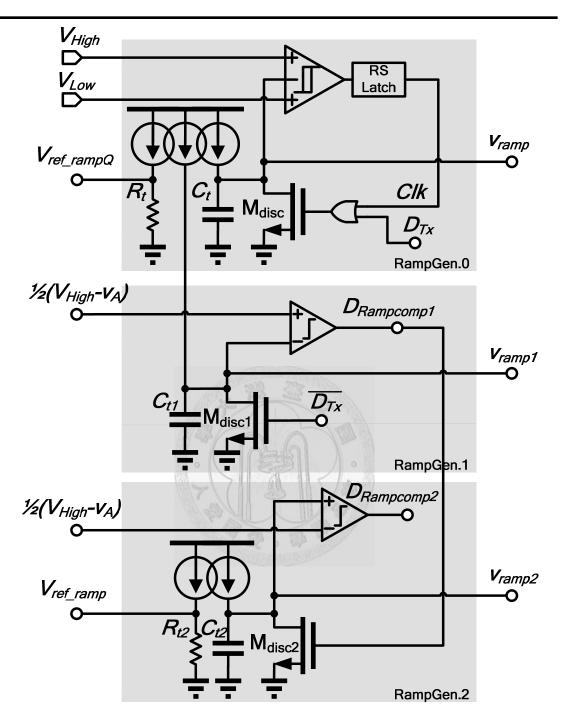

#### 4.3 Ramp Generator Circuit

The ramp generator is the circuit which generates a ramp signal for PWM controller as shown in Fig. 4.9. To clamp the upper band  $V_{High}$  and lower band  $V_{Low}$ , there are two comparators and one SR latch in the right side of Fig. 4.9. The reference voltage  $V_{ref,ramp}$  provides a current  $i_t$  through a resistor  $R_t$  and  $i_t$  is given by

$$\dot{i}_t = \frac{V_{ref\_ramp}}{R_t} \tag{4.7}$$

Then the current mirror copies  $i_t$  to charge the capacitor  $C_t$  to generate the ramp signal  $v_{ramp}$ . The comparators compare the amplitude of the ramp signal with  $V_{High}$  and  $V_{Low}$  to

turn on or turn off the transistor  $M_{disc}$  which is paralleled with  $C_t$ . When  $M_{disc}$  cuts off, current  $i_t$  charges the voltage of  $v_{ramp}$  up linearly to  $V_{High}$ , and then  $M_{disc}$  will turn on to discharge the voltage of  $v_{ramp}$  sharply back to  $V_{Low}$ . The charge stored in  $C_t$  is given by

$$Q = \frac{i_t}{f_{req}} = C_t \times (V_{High} - V_{Low})$$

(4.8)

where  $f_{req}$  is the switching frequency of the buck converter, and hence

$$\frac{V_{ref\_ramp}}{(f_{req} \times R_t)} = C_t \times (V_{High} - V_{Low})$$

(4.9)

to give the relationship of switching frequency of

$$f_{req} = \frac{1}{R_t C_t} \frac{V_{ref\_ramp}}{V_{High} - V_{Low}}$$

(4.10)

According to above equation (4.10), there are five choices to change the switching frequency in the buck converter. The passive components,  $R_t$  and  $C_t$ , are on-chip to shrink the area on PCB in this work so that they should be small. Here chooses changing the  $V_{ref\_ramp}$  to vary the slope of ramp since there is a feedback OP at  $V_{ref\_ramp}$  node for stability rather than  $V_{High}$  and  $V_{Low}$ .

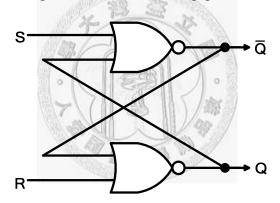

The circuit and the truth table of SR latch used in this circuit are shown in Fig. 4.10 and Table 4.2.

Fig. 4.9 Schematic of ramp generator

Fig. 4.10 The circuit of SR latch

Table 4.2 The truth table of SR latch

| S | R | Q(n+1) | Qbar(n+1) |

|---|---|--------|-----------|

| 0 | 0 | Q(n)   | Qbar(n)   |

| 0 | 1 | 0      | 1         |

| 1 | 0 | 1      | 0         |

| 1 | 1 | Forbi  | idden     |

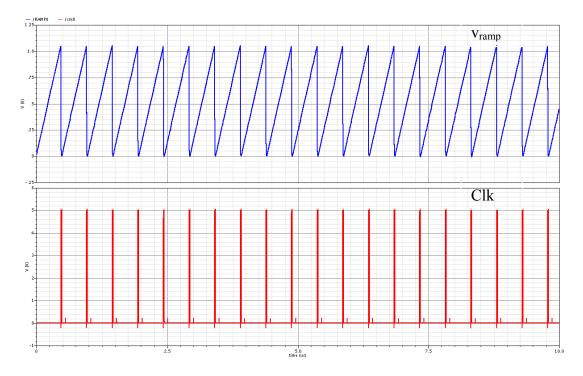

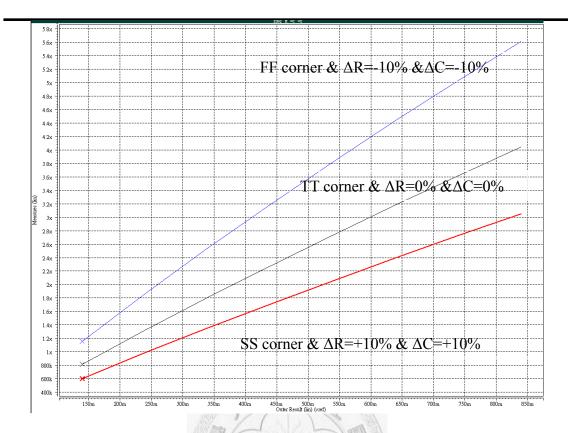

Fig. 4.11 shows the ramp signal  $v_{ramp}$  and the control signal of  $M_{disc}$ , *Clk*.  $V_{Low}$  is 0.1 V and  $V_{High}$  is 1 V. According to equation (4.10), the switching frequency is determined by the passive component values which are dependent on the process variation. Therefore, Fig. 4.12 shows the switching frequency considering FF, SS, and TT corners and 10% variation on the resistor  $R_t$  and capacitor  $C_t$ . The frequencies in these corners fit the specification of frequency (2-3 MHz)

Fig. 4.11 The simulation result of ramp generator

Fig. 4.12 The simulation of frequency considering process variation 4.4 Digital-to-Analog Converter (DAC)

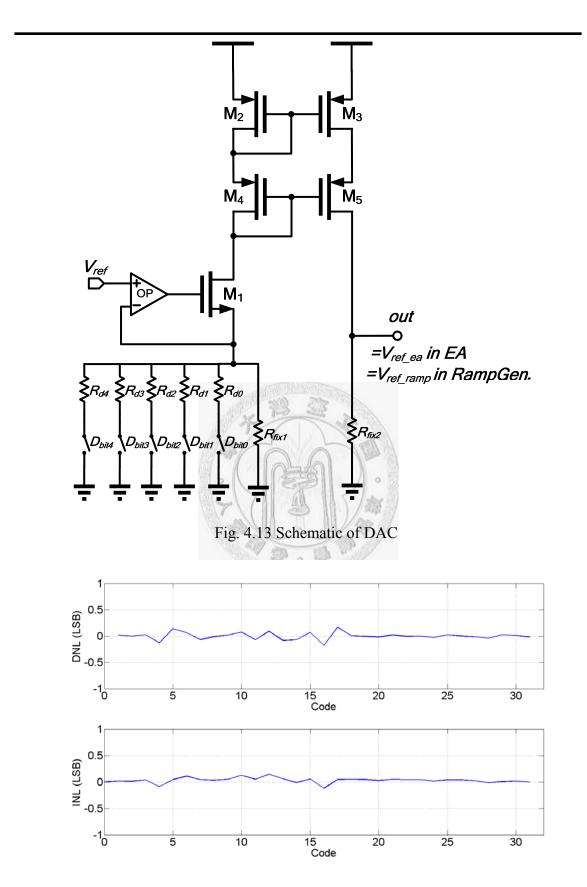

There are two group 5-bit digital inputs in this work to control the output voltage and switching frequency respectively. To convert the digital inputs into an analog voltage used in Ramp generator and error amplifier, it uses DACs. As shown in Fig. 4.13, a current-steering array is utilized. The left side transfer the sum of current from branches through a current mirror circuit to the right side. Finally, the current transfers into an analog voltage by a resistor  $R_{fix2}$ . There are two identical DAC in this design, one is  $V_{ref_ea}$  for error amplifier (*EA*) and another is  $V_{ref_ramp}$  for Ramp generator (*RampGen.0*). Its output voltage is given by

$$V_{ref\_ea}(orV_{ref\_ramp}) = V_{ref}(\frac{D_{bit4}}{R_{d4}} + \dots + \frac{D_{bit0}}{R_{d0}} + \frac{1}{R_{fix1}})R_{fix2}$$

(4.11)

The INL and DNL are shown in Fig. 4.14. It could be observed that  $\pm 0.17$  LSB for DNL and  $\pm 0.14$  LSB for INL.

#### 4.5 Inductor Current Average Control (ICAC)

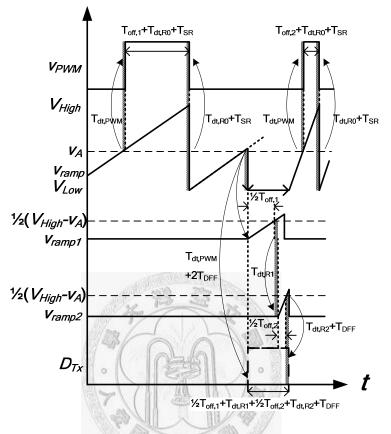

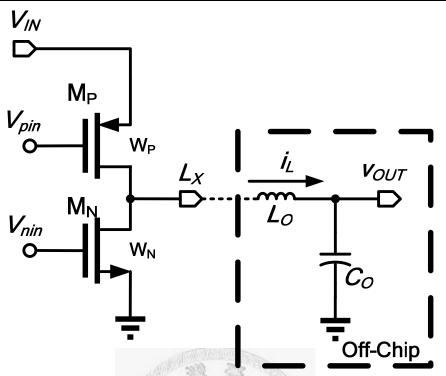

This circuit is the key to complete the inductor current average control method. According to the analysis in Chapter 3, it needs an additional pulse which pulse width equals  $T_X$ . To implement this pulse, there are two parts, sample and hold (S&H) circuit and calculated pulse circuit. If there is no S&H, the signal of hopping triggers the  $v_{ramp}$ changing slope synchronously as shown in Fig. 4.15. It causes a random shape ramp with two different slopes and an unpredicted period when hopping signal arrives. The unpredicted period of off cycle  $T_{off,unknown}$  perhaps equals  $T_{off,2}$  when the "Hopping Signal" arrives before  $v_{ramp}$  over  $v_A$ , but the unpredicted period of on cycle  $T_{on,unknown}$ becomes a random interval depending on the ratio between two different slope of  $v_{ramp}$ as depicted in Fig. 4.15. On the other hand, the  $T_{on,unknown}$  perhaps equals  $T_{on,1}$  when the "Hopping Signal" arrives after  $v_{ramp}$  over  $v_A$ , but  $T_{off,unknown}$  becomes a random interval depending on the ratio between two different slope of  $v_{ramp}$ . As it uses a S&H circuit in frond end of  $V_{ref ramp}$ , we can choose the time we want to hop the frequency of  $v_{ramp}$ without two slope in one period of  $v_{ramp}$ . All we have to do is turn off the  $v_{ramp}$  during the arrival of "Hopping Signal" and insert a calculated-width pulse  $D_{Tx}$  to be a pseudo period in  $v_{PWM}$  as shown in Fig. 4.16. It also relaxes the settling time of  $V_{ref_ramp}$ .  $V_{ref_ramp}$ needs a few nanoseconds without S&H, but  $D_{Tx}$  around hundred nanoseconds with S&H giving  $V_{ref ramp}$  more time to settle.

Fig. 4.16 Ramp generator with S&H in front end and calculated pulse circuit in parallel

## 4.5.1 Sample and Hold Circuit (S&H)

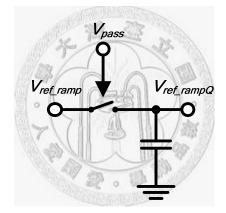

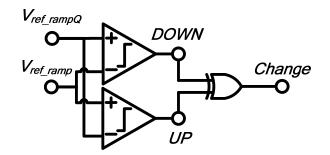

It utilizes a simple RC circuit to complete sample and hold (S&H) circuit where  $V_{ref\_ramp}$  is the input of S&H,  $V_{ref\_rampQ}$  is the output of S&H and  $V_{pass}$  is the control signal of sample phase as shown in Fig. 4.17. In Fig. 4.18, a detector circuit which detects if the  $V_{ref\_ramp}$  changes is implemented with dual comparators and one XOR logic gate. Its output signal *Change* represents that a "Hopping Signal" arrives to trigger DAC of  $V_{ref\_ramp}$  to change  $V_{ref\_ramp}$  larger or smaller synchronously. Note that larger  $V_{ref\_ramp}$  means higher frequency of  $v_{ramp}$ . We give attention to the  $V_{pass}$  of S&H in this paragraph.

Fig. 4.17 Circuit of the sample and hold

Fig. 4.18 Diagram of the detector of hopping

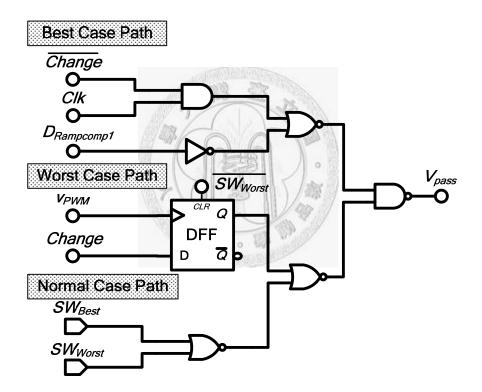

As illustrate in Fig. 4.19, there are three paths, Best Case Path, Worst Case Path and Normal Case Path. (1) In Normal Case Path, it turns on  $V_{pass}$  fully by  $SW_{Best}=0$  and  $SW_{Worst}=0$ . It causes that  $V_{ref\_rampQ}$  changes whenever  $V_{ref\_ramp}$  changes like shown in Fig. 4.15. (2) In Worst Case Path,  $V_{pass}$  turns on at the rising edge of  $v_{PWM}$ . It represents the frequency hops at the moment where the inductor current reaches peak value. By this way, the transient ripple gets the worst and largest voltage. (3) In Best Case Path,  $V_{pass}$  turns on as the same as *Clk* when *Change*=0(*Change*=1). *Clk* is the gate of M<sub>disc</sub> in the Ramp generator circuit in Fig. 4.9 and is the discharging phase of  $v_{ramp}$ . While the *Change* detects the difference between  $V_{ref\_ramp}$  and  $V_{ref\_rampQ}$ , it masks *Clk* by AND logic gate. During *Change*=1,  $V_{pass}$  is triggered by  $D_{Rampcomp1}$ .  $D_{Rampcomp1}$  is the rising edge of  $D_{Tx}$  and the width of  $D_{Tx}$  will be discussed later.

Fig. 4.19 Diagram of the control signal of sample time

| Case   | SW <sub>Best</sub> | $\mathrm{SW}_{\mathrm{Worst}}$ | $V_{pass}$                  |

|--------|--------------------|--------------------------------|-----------------------------|

| Normal | 0                  | 0                              | Always high                 |

| Best   | 1                  | 0                              | = <i>Clk</i> as not hopping |

|        |                    |                                | $=D_{Rampcomp1}$ as         |

|        |                    |                                | hopping                     |

| Worst  | 0                  | 1                              | = <i>Clk</i> as not hopping |

|        |                    |                                | $=v_{PWM}$ as hopping       |

| Х      | 1                  | 1                              | Х                           |

## 4.5.2 Calculated Pulse Circuit

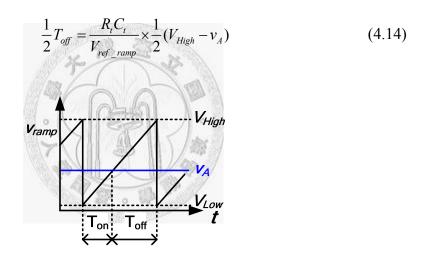

A calculate-width pulse  $D_{Tx}$  is analyzed in this paragraph. The width (or time length) of this pulse must equal to  $T_X = 0.5(T_{off,1}+T_{off,2})$  in Equation (3.8). It is composed by two parts, half of off duty cycle period of the previous frequency  $0.5T_{off,1}$  and half of off duty cycle period of the following frequency  $0.5T_{off,2}$ . From Fig. 4.20, we have

$$\frac{dv_{ramp}}{dt} = \frac{i_t}{C_t} = \frac{V_{ref\_ramp}}{R_t C_t}$$

(4.12)

$$T_{off} = \frac{R_t C_t}{V_{ref\_ramp}} \times (V_{High} - v_A)$$

(4.13)

Fig. 4.20 Relationship between voltage and time length in a ramp signal